# Burroughs SERIES E 2100 DIRECT ACCOUNTING COMPUTER

# INSTRUCTION BOOK Section IV

ELECTRONIC CIRCUIT DESCRIPTION

24

#### TABLE OF CONTENTS

#### ELECTRONIC CIRCUITS

#### CLOCK SYSTEM

|                      |  | Page |

|----------------------|--|------|

| Clock Driver         |  | 18   |

| Clock Generator      |  | 17   |

| Clock Output Driver  |  | 18   |

| Gated Clock          |  | 18   |

| Test and Adjustments |  | 19   |

| SINGLE SHOT CLOCK    |  | 21   |

| Clock Inhibit        |  | 22   |

| Inverter             |  | 22   |

| Pulse Standardizer   |  | 22   |

#### CONTROL CIRCUITS

|                          | CONTROL ORGOILO                                                                                                                                                                                                                     |   |    |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| FLIP-FLOP                |                                                                                                                                                                                                                                     | • |    |

| Delay Machine Reset      |                                                                                                                                                                                                                                     |   | 14 |

| Pulse Standardizer       |                                                                                                                                                                                                                                     |   | 11 |

| Reset 1 (R1)             | na tanàna amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'<br>Na fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin' |   | 14 |

| Reset 2 (R2)             |                                                                                                                                                                                                                                     |   | 13 |

| Reset 3 (R3)             |                                                                                                                                                                                                                                     |   | 13 |

| Reset & Reset Gate Outpu | t                                                                                                                                                                                                                                   |   | 9  |

| Reset Resistor Input     |                                                                                                                                                                                                                                     |   | 9  |

| Reset Standardizer       |                                                                                                                                                                                                                                     |   | 12 |

| Triggering               |                                                                                                                                                                                                                                     |   | 8  |

|                          |                                                                                                                                                                                                                                     |   |    |

|                          | INTRODUCTION                                                                                                                                                                                                                        |   |    |

| SIGNAL VOLTAGE LINES     |                                                                                                                                                                                                                                     |   | 5  |

|                          |                                                                                                                                                                                                                                     |   |    |

|                          | LOGIC CIRCUITS                                                                                                                                                                                                                      |   |    |

| And                      |                                                                                                                                                                                                                                     |   | 5  |

| And -Or                  |                                                                                                                                                                                                                                     |   | 6  |

| Heavy Buffer             |                                                                                                                                                                                                                                     |   | 7  |

| Inverter                 |                                                                                                                                                                                                                                     |   | 7  |

| Or                       |                                                                                                                                                                                                                                     |   | 6  |

|                          |                                                                                                                                                                                                                                     |   |    |

|                          | MEMORY CIRCUITS                                                                                                                                                                                                                     |   |    |

| MEMORY CARD              |                                                                                                                                                                                                                                     |   | 24 |

| Inhibit Winding          |                                                                                                                                                                                                                                     |   | 24 |

| Sense Amplifier          |                                                                                                                                                                                                                                     |   | 24 |

| Sense Pre Amplifier      |                                                                                                                                                                                                                                     |   | 26 |

| Sense Winding            |                                                                                                                                                                                                                                     |   | 24 |

| Tests and Adjustments    |                                                                                                                                                                                                                                     |   | 26 |

| X Lines                  |                                                                                                                                                                                                                                     |   | 24 |

Y Lines

### TABLE OF CONTENTS (Cont'd.)

| SECOND STAGE AMPLIFIER                   | Page<br>27 |

|------------------------------------------|------------|

| Indicator Circuit                        | 28         |

| MR Flip-flop                             | 27         |

| Noise Filter                             | 28         |

| Strobe Gate                              | 27         |

|                                          |            |

| MEMORY DRIVER                            |            |

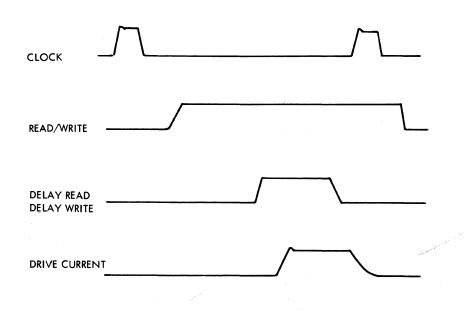

| Driver Input and Output Signals          | 31         |

| First Stage Amplifier - Circuits 1-2-3-4 | 30         |

| Input Gate                               | 30         |

| Noise Filters                            | 31         |

| Output Stage - Circuits 1-2              | 30         |

| Output Stage - Circuits 3-4              | 30         |

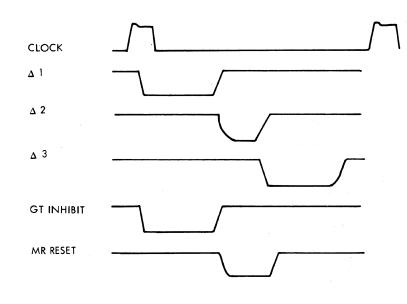

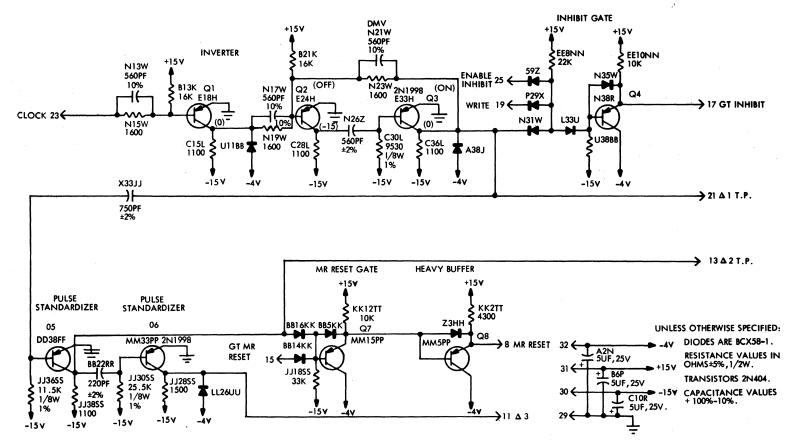

| MEMORY TIMING A                          |            |

| DMV                                      | 33         |

| Heavy Buffer                             | 35         |

| Inhibit Gate                             | 34         |

| Inhibit Gate Signals                     | 34         |

| Inverter                                 | 33         |

| Memory Timing A Logic                    | 33         |

| Memory Timing A Signals                  | 35         |

| MR Reset Gate                            | 35         |

| Noise Filters                            | 35         |

| Pulse Standardizer Q5 & Q6               | 34         |

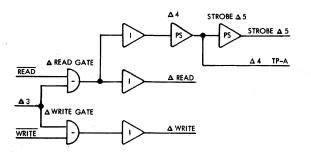

| MEMORY TIMING B                          |            |

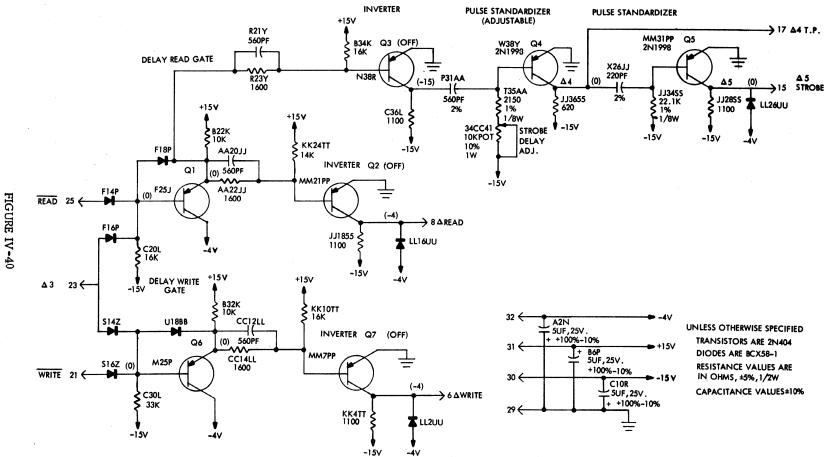

| Delay Read Inverter - Q2                 | 38         |

| Delay Read Inverter - Q3                 | 38         |

| Delay Read Gate                          | 37         |

| Delay Write Gate                         | 37         |

| Delay Write Inverter                     | 37         |

| Memory Timing B Logic                    | 37         |

| Pulse Standardizer Q4 & Q5               | 38         |

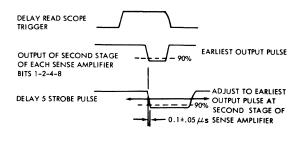

| Tests and Adjustments - Strobe           | 38         |

| MISCELL ANEOLIS CIPCILITS                |            |

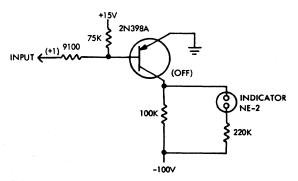

| MISCELLANEOUS CIRCUITS<br>Indicator      | 50         |

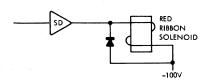

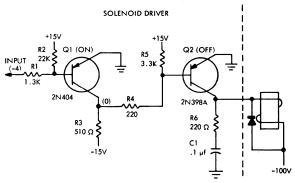

| Solenoid Driver                          | 51         |

| Solelioid Driver                         | 51         |

| SPECIAL CONTROL CIRCUITS                 |            |

| AMOUNT PROTECTION                        | 44         |

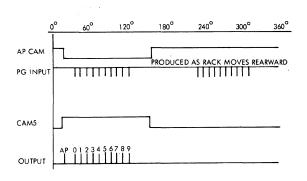

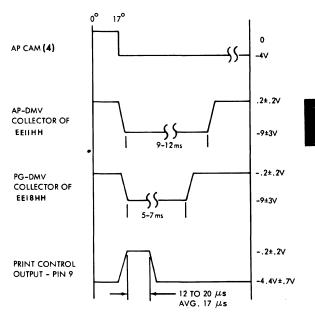

| Approximate Timing                       | 47         |

| Inverter                                 | <b>4</b> 6 |

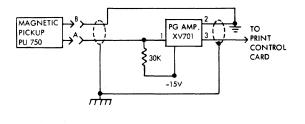

| Magnetic Pick Up Input (Pin 18)          | 46         |

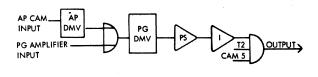

| PG - Delay MV                            | 45         |

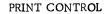

| Print Control Gate Circuit               | 45         |

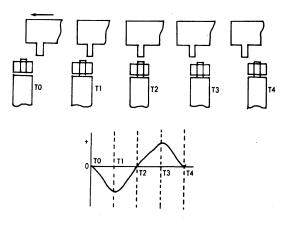

| Print Control Synchronization            | 47         |

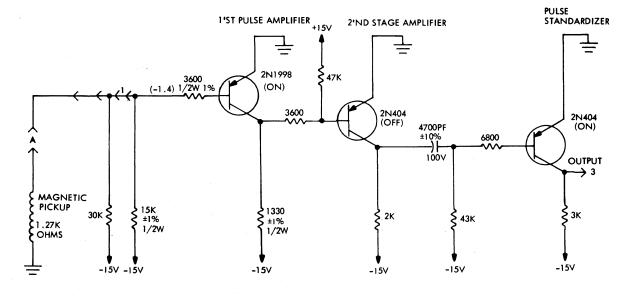

| Pulse Standardizer                       | 46         |

| TABLE OF CONTENTS (Con'td.)          |            |

|--------------------------------------|------------|

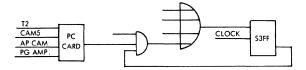

| PRINT CONTROL                        | Page<br>44 |

| MAGNETIC PICK UP PULSE GENERATOR     | 41         |

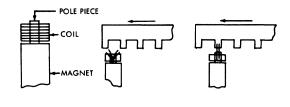

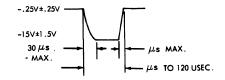

| Pulse Generator                      | 42         |

| Pulse Standardizer                   | 42         |

| Magnetic Pick Up                     | 41         |

| Second Stage Amplifier               | 42         |

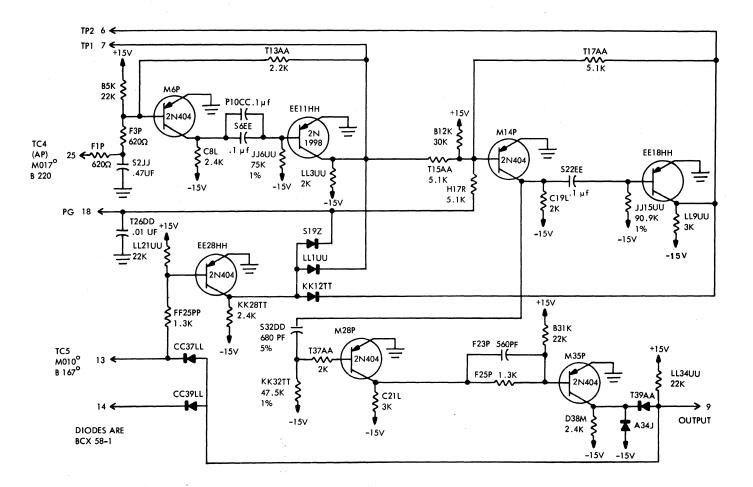

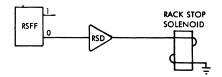

| RACK STOP DRIVER                     | 49         |

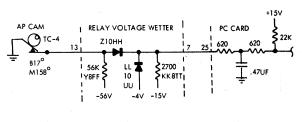

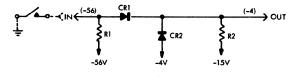

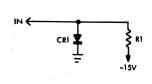

| VOLTAGE WETTING CIRCUITS             |            |

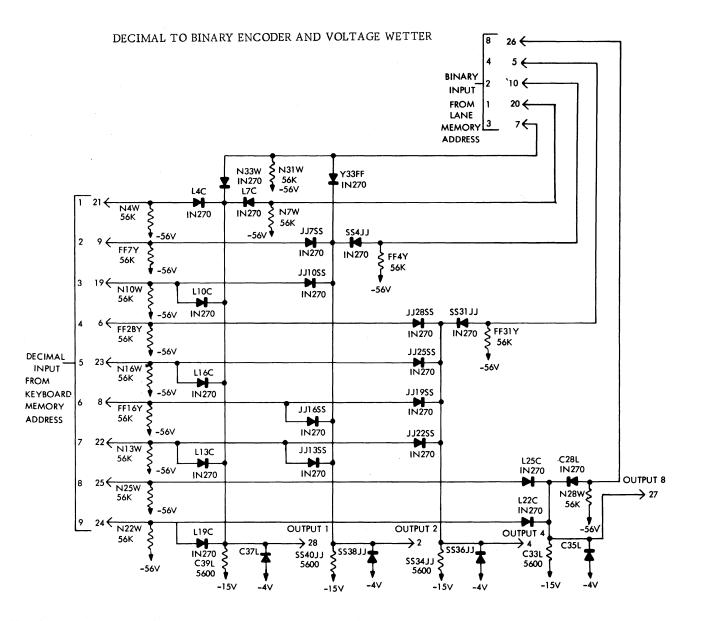

| Decimal to Binary Encoder and Wetter | 54         |

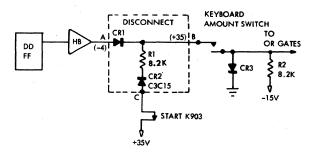

| Disconnect                           | 54         |

| Special Wetter and Relay Wetter      | 51         |

## **Electronic Circuit Description**

#### INTRODUCTION

This machine employs combination diodetransistor circuits which utilize the speed and cost advantage of diode gating, together with the current amplification and speed characteristics of non-saturating emitter follower output circuitry. The basic logic elements include the AND gate, OR gate and the AND-OR combination. A Heavy Buffer (emitter-follower circuit) is also provided for use whenever an increase in output drive current is required. One additional logic element, the Inverter, employs a common emitter circuit for both logical inversion and for re-establishing signal voltage levels after a signal has been attenuated by a logical chain.

A number of circuits are provided to Control the various operations. These include the basic Flip-Flop, the Reset Standardizer, the Clock Timing circuits, etc. These Control elements cause the Keyboard-Printer and the Arithmetic and Memory unit to operate together as an integrated system.

In addition to the Logic and Control elements, there are a number of circuits such as the Memory Driver and Sense-MR that are associated with Reading from and Writing into the Memory.

Finally, there are a number of miscellaneous circuits such as the Indicator circuit, which employs neon lamps for trouble shooting, various voltage wetting circuits, etc.

#### SIGNAL VOLTAGE LEVELS

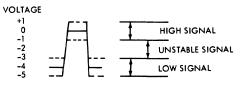

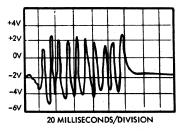

The waveform below shows the range of voltage levels for a High, Low and Unstable signal:

A signal voltage level between +1.0 volts and -1.0 volts is a "high" signal and between -3.0 volts and -5.0 volts a low signal. Signal levels between -1.01 volts and -2.99 volts are considered unstable.

Many of the following circuit drawings show in parathenses the voltage levels of significant points under static conditions.

#### LOGIC CIRCUITS

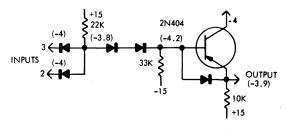

"AND" Gate

The diodes at input pins 2 and 3 form the diode gate together with the 22K ohm source resistor connected to  $\pm 15$  volts. If either or both of the inputs are low, for example -4.0 volts, then the output of the gate will be low (-4.0 volts less approximately .2 volts diode drop or -3.8 volts). Current flow from -15 volts thru the 33K ohm resistor, the two series level shifting diodes and the 22K ohm resistor to  $\pm 15$  volts shifts the level down to approximately -4.2 volts at the base of the transistor.

The emitter-follower circuit involving the 2N404 transistor at the gate output provides current to drive succeeding logical elements. With an emitter-follower a large current amplification can be obtained but the voltage gain is slightly less than 1 and there is no inversion of the input signal. In the case of a p-n-p emitter-follower the emitter output signal is always slightly positive with respect to the input signal at the base. For this reason the transistor conducts and there is emitter and collector current at all times. With the signal at the base of the transistor low due to one or both gate inputs being low, the output will be -4.2 volts less a small transistor drop or approximately -3.9 volts.

W ith both gate inputs at the high level, for example ground, the output of the gate diodes will be high (+.2 volts), at the base of the transistor -.2 volts due to the level shifting diodes and the output at the emitter will be near ground (-.1 volt approximately).

At the output of the AND gate, there is some stray capacity to ground and since a capacitance will not allow an instantaneous change of voltage, it affects the rise time of the signal. During the time the emitter-follower output is at the low level, the stray capacity becomes charged to -4 volts. In order for the emitter to closely follow the base when the input goes to ground a fast discharge path must be provided for this capacity. The diode connected between the emitter and base provides a low resistance discharge path around the transistor.

As the various signals pass thru a stage of logic the voltage levels deteriorate slightly with -4 volt signals becoming less negative and ground signals less positive. For example, a signal which at the input to a series of logic elements was at ground might deteriorate as follows:

After the first stage -.25 volts, second stage -.44 volts, third stage -.62 volts, fourth stage -.8 volts and fifth stage -.97 volts. This signal would then be very close to the -1 volt lower limit which the various circuits will accept as a high signal. As a rule, signals are never routed thru more than four stages of logic before they are applied to a circuit which will re-establish the -4 volt and ground levels.

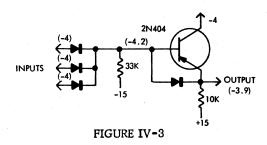

#### "OR" Gate

The electrical circuit for a three input positive OR gate is shown below:

The three input diodes form the OR gate together with the 33K resistor connected to -15 volts. With all three inputs at the low level, -4 volts for example, the voltage at the base of the transistor will be approximately -4.2volts. The transistor will be conducting and the output will be low (-4.2 volts less .3 volts transistor drop or -3.9 volts). The level shifting diodes are not necessary in the OR circuit since the diode voltage drop at the input is in the opposite direction to the transistor baseemitter drop.

When one or more of the OR gate inputs are high (ground) the voltage at the base will be ground less the diode voltage drop or -.2 volts. The transistor will be conducting and the output will be at approximately ground level.

At the output of the OR gate, there is a certain amount of stray capacity as with the AND gate and a diode is provided to discharge the stray capacity when the output voltage level switches from -4 volts to ground.

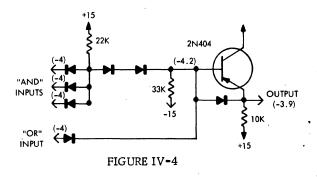

#### "AND-OR" Gate

The electrical circuit for a positive AND-OR gate is shown below:

It consists of a basic 3 input diode AND gate, together with an OR input, level shift diodes and emitter-follower output circuit. This circuit may be expanded to include as many as 8 AND inputs as provided on the logic cards LCE and LCD. The Output will be high when the 3 AND inputs are high or whenever the single OR input is high. The Output will be low when the OR input is low and at least one AND input is low. The diode between the emitter and base is provided to discharge any stray capacity when the output voltage level switches from -4 volts to ground.

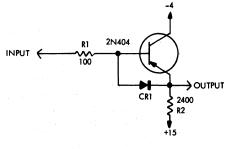

#### Heavy Buffer

The Heavy Buffer is an emitter-follower circuit that is used following logic elements whenever an increase in output drive current is required without inversion of the input signal. The output of the H.B. circuit, shown below, will be high when the input is high and low when the input is low. The 2N404 conducts at all times because a high input does not reverse bias the base-emitter junction.

In addition to a power gain without any inversion of the input signal, the H.B. also provides isolation between groups of logical elements and reduces tendency for stages of logic to oscillate. The 100 ohm resistor Rl is provided in series with the input as an oscillation suppressor. The diode CRl connected between the base and emitter discharges any stray capacity at the output when it switches from -4 volts to ground. In this way, the emitter can closely follow the base when the logic switches from a low input to a high input.

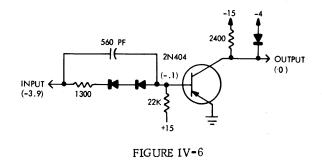

#### Inverter

The Inverter, as the name implies, provides a logical inversion of signals applied to its input. In addition, it re-establishes the -4 volt and ground levels to signals whose levels may have deteriorated after passing thru various stages of logic. Inverter circuits as shown below are included on Logic Cards A, B and C.

A grounded-emitter amplifier is used to perform the inversion. It must provide a high output signal (ground) when the input signal level is low (-3 to -5 volts) and a low output (volts) when the input is high (+1 to -1 volt). In addition, the Inverter provides isolation between groups of logical stages which prevents any tendencies toward oscillation.

If the input signal level is low, current will flow from the input thru the 1300 ohm resistor, the two series diodes and the 22K resistor to +15 volts. The base of the transistor will be slightly negative and it will conduct in saturation from -15 volts thru the 2400 ohm resistor and the collector-emitter to ground. With the transistor conducting the output signal level will be at ground.

If the input signal level is high, current will flow from the input, thru the 1300 ohm resistor, the two series diodes and the 22K resistor to +15 volts. The base will be slightly positive with respect to the emitter and the transistor will be cut off. The output will be at -4.2 volts due to current flow from -15 volts thru the 2400 ohm resistor and the clamp diode to -4 volts.

The two series diodes provide a voltage drop of .2 to .4 volts to insure that a deteriorated high input level (-1 volt) will cut off the transistor and produce a low output. The 560 PF capacitor is used to compensate for the phenomenon known as Stored Base Charge which involves the storage of minority charge carriers in the base region of a transistor conducting in saturation. These stored charges limit the speed with which the transistor can be turned off and the 560 PF capacitor is selected to provide minimum turnoff time.

#### CONTROL CIRCUITS

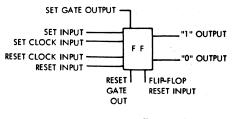

#### Flip-Flops

Each Flip-Flop (FF) card contains two independent flip-flop circuits. Each circuit contains two 2N404 transistors connected in a bistable multivibrator circuit. The FF has two stable states or two conditions of equilibrium, Set and Reset, and is able to switch from one state to the other at a high rate of speed.

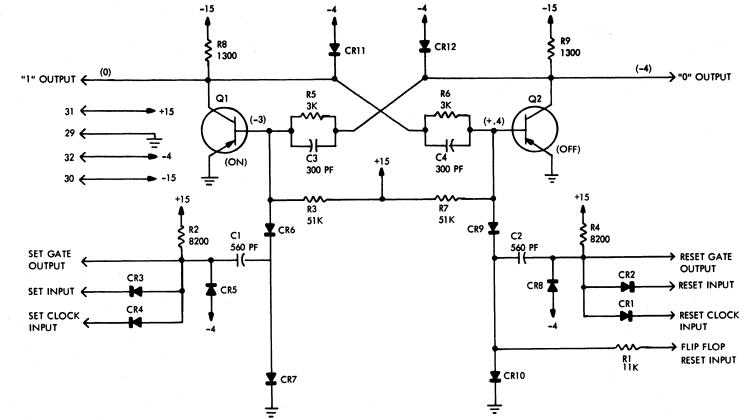

The FF has separate outputs from the Set and Reset stages. Since it is binary in nature, the outputs may be labeled "1" and "0" as shown on the block diagram below:

#### FIGURE IV-7

When the FF is Set the "1" output is high and the "0" output is low. When the FF is Reset, the "1" output is low and the "0" output is high.

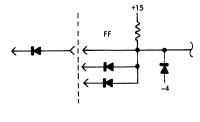

Three inputs to the FF are provided. The Set and Reset inputs are gated with Clock pulses thru AND gates which are located on the FF card. The output from these gates will Set or Reset the FF respectively. Also this output maybe taken from the FF card to other circuits. The third input is the FF Reset input which is a direct means of resetting the FF.

When examining the FF circuit, reference Figure 9, the symmetry of the two stages is immediately apparent, the only difference being the direct Flip-Flop Reset Input thru the llK ohm resistor R1.

Under static conditions, assuming the FF is Set, transistor Q1 will be ON (conducting). Its base-emitter will be forward biased due to current flow from -15 volts, thru resistors R9, R5 and R3 to +15 volts. With Ol conducting heavily from -15 volts thru load resistor R8, the collector of Q1 will be at ground and the "1" output will be high. At this time transistor Q2 will be OFF (not conducting) due to its base-emitter being reverse biased. Since the collector of Ql is at ground, current flow from -15 volts, thru R8, R6 and R7 to +15 volts will cause the base of Q2 to be slightly positive. With Q2 OFF, its collector is held at -4 volts due to collector load resistor R9 and clamp diode CR12 thus, the "0" output will be low.

#### Triggering

The FF is triggered from a negative voltage swing. It is designed primarily for triggering by the trailing edge of the clock pulse in conjunction with a logic control signal. It may, however, be triggered by any pulse that has a negative edge voltage swing of 2.5 volts minimum and pulse width of .6  $\mu$  s (minimum) at the output of the Set or Reset gates. In addition to the Set and Reset input positive AND gates, a separate reset resistor input has been provided by which the FF can be directly reset without going thru logic circuitry. This input is labeled "Flip Flop Reset".

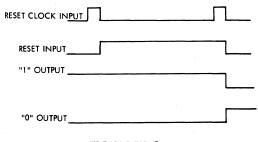

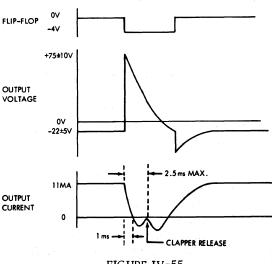

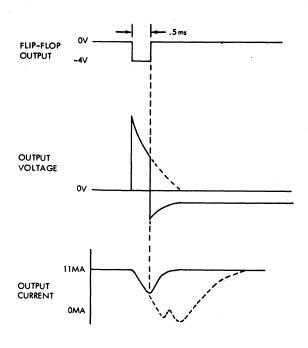

If, assuming the FF is Set, a logic signal is applied to the Reset Input together with clock pulses applied to the Reset Clock Input, the FF would reset as shown below:

FIGURE IV-8

As the signal at the Reset Input goes from -4 volts to ground the Clock pulse goes from ground to -4 volts and the output of the Reset positive AND gate, made up of CRI, CR2 and R4, remains low. When the next clock pulse goes from -4 volts to ground, the gate output goes from -4 volts to ground. This positive going signal is coupled thru the 560 PF capacitor to the cathode of diode CR9; however, since its plate is only slightly positive, the diode disconnects and no change in the status of the FF occurs. The base of the OFF transistor Q2 cannot go more than .2 to .4 volts positive due to the clamping action of diodes CR10 and CR9. As the gated clock pulse ends, the gate output

goes from ground to -4 volts. This negative signal is coupled thru the 560 PF capacitor and forward biased diode CR9 to the base of Q2. As the negative trigger pulse is applied to the base of Q2, it starts to conduct, its collector goes to ground making the "0" output high and, due to current flow thru voltage divider R5 and R3, the base of Q1 will go positive and Ql will be cut off. As Ql is cut off, its collector goes to -4 volts due to current flow thru resistor R8 and clamp diode CRll. The crossover or coupling resistors R5 and R6 are bypassed with capacitors C3 and C4. In this way, voltage changes at the collector of one stage are immediately coupled to the base of the other stage to speed up the switching time which, for the basic FF, is  $1.1 \ \mu$ s maximum required to completely reverse the states.

If the FF is Reset and the same logic and clock signals were applied to the Set inputs, the switching analysis would be the same except that Ql would be switched on and Q2 off.

Diodes CR5 and CR8 at the output of the Set and Reset gates are clamp diodes which prevent the output of the gates from going below -4 volts. In this way, any negative transient signals or voltage spikes that might occur on input lines at the low level will not get thru to trigger the FF.

#### Reset Resistor Input

The direct 11K resistor Reset Input requires a negative input signal that goes from ground to approximately -15 volts and remains at the lower level for 1  $\mu$ s or more. The FF will reset on the leading edge of the negative going signal since it is coupled thru the 11K resistor R1 and diode CR9 to the base of Q2. If the FF already is Reset, when the resistor reset input goes negative, it will remain Reset.

#### Set & Reset Gate Output

The output of the Set & Reset gates are

FIGURE IV-9

Burroughs - Series E 2100 Instruction Book

FLIP FLOP

10

Sec. IV

accessible thru a direct connection which may be used in two ways. First a diode remotely located from the FF card may be connected to form a three input gate for additional logic control.

FIGURE IV -10

Second, the Set or Reset gate outputs may be wired directly to other FF inputs to provide faster triggering of successive flip-flops.

#### Pulse Standardizer

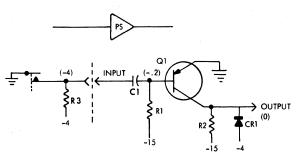

The logical symbol and circuit diagram for a typical Pulse Standardizer as used in this machine is shown below:

FIGURE IV-11

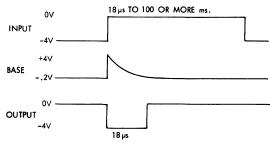

The circuit consists of a grounded emitter transistor (Q1), base input circuit (CIRI), collector load resistor (R2) and output clamp diode (CR1). In general the circuit requires a positive going, noise free input signal whose duration is equal to or longer than the output pulse. If the input signal

pulse that the circuit is designed to produce, then the output will have the same duration as the input. The waveforms below show a typical input signal, from a relay for example, the signal at the base and the standardized 18#s negative output signal. Under static conditions the Input is low, -4 volts. Transistor Ql is conducting in saturation due to resistor Rl connected to -15 volts which forward biases the baseemitter junction. Thus the base is clamped near ground by the base-emitter junction and Cl is charged to approximately 4 volts. The charge path for Cl is from -4 volts thru resistor R3 to the left hand plate and from the right hand plate thru the baseemitter junction to ground. With Ql conducting the Output is at ground or is slightly negative. Diode CRl is reverse biased and cutoff.

is less in time than the standardized output

When the input signal switches from -4 volts to ground the positive going voltage signal is coupled thru Cl to the base of Ql which cuts the transistor off. With Ql cutoff current flow from -15 volts thru R2 and CRl clamps the output to approximately -4 volts.

The transistor will remain cutoff until Cl discharges to a point where the base-emitter will become forward biased and the transistor will conduct. The discharge path for Cl is from -15 volts thru Rl to the right hand plate and from the left hand plate to the ground

FIGURE IV-12

input source. Thus, it is primarily the time constant of Cl and Rl which determines the cutoff time for Ql and the length of the negative output signal. Other factors including the rise time of the input signal and the switching time (from ON to OFF) of the transistor affect the discharge of the input capacitor and, consequently, the transistor cutoff time.

When the input signal returns to -4 volts, capacitor Cl again charges to approximately -4 volts thru resistor R3, and the Pulse Standardizer must not be triggered again until the capacitor has had sufficient time to recharge.

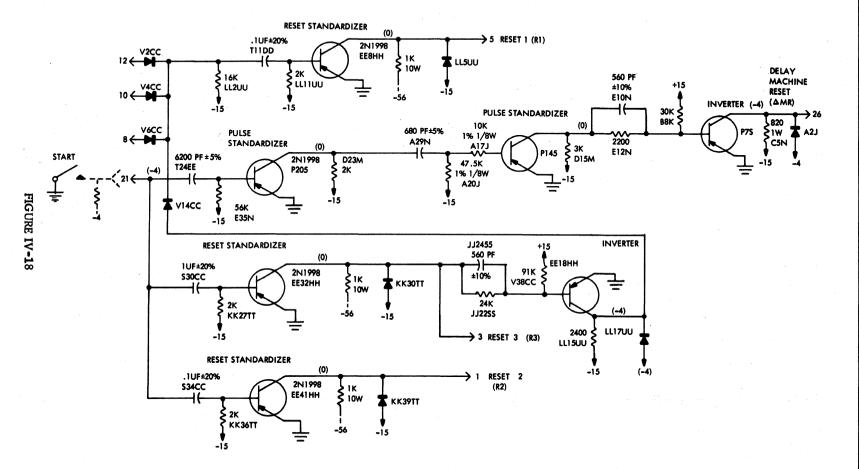

#### Reset Standardizers

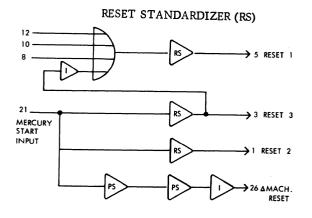

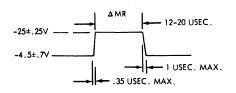

The Reset Standardizer (RS) card provides direct reset pulses to the Flip Flop Reset Input for most of the flip-flops. Four output stages are triggered from a common input. Three of these stages; the outputs of which are labeled Reset 1 (RI), Reset 2 (R2) and Reset 3 (R3), produce pulses which can reset 20 FF each. The fourth output, labeled Delay Machine Reset ( $\Delta$  MR), is a 12-20  $\mu$ s pulse which is produced following the reset pulses and is used to initate electronic operation immdeiately after the FF's are reset. A block diagram is shown below:

FIGURE IV-13

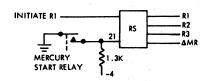

At the beginning of each machine operation, the RS is triggered when the Mercury Start Relay contacts pulse the RS input. The RS produces pulses at the R1, R2, R3 and  $\Delta$ MR outputs. An additional trigger input is provided for Reset 1 only. This is the initiate R1 input which is provided so that the DDFF's can be reset independently of the Mercury Start pulse. Reset 1 output resets the following 15FF's; DDO thru DDMSD; DDU; and the DDT. A logic diagram of the entire Reset Standardizer card is shown on figure 14. Pin 21 is the trigger input from the Mercury Start Relay. Each time the relay is energized the Rl, R2, R3 and  $\Delta$  MR signals will be produced. The Reset 1 Standardizer may also be triggered independently by the logic circuits. For this reason, it is triggered by Reset 3 thru an Inverter stage which produces the same signal level as the logic circuits.

#### FIGURE IV-14

The three Reset Standardizer stages, as shown on figure 18, employ 2N1998 transistors which are connected in normally conducting pulse standardizer circuits. The output of each of these circuits is normally at ground. When the circuit is triggered the transistor is cut off for a period of time determined primarily by the resistor-capacitor (RC) in the base circuit. During this cutoff time, the output goes to -15 volts due to the 1K ohm resistor connected to -56 volts and the clamp diode connected to -15 volts.

#### Reset 2 (R2)

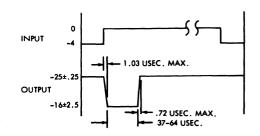

The required triggering input at pin 21 is a positive voltage step (-4.0 volt to ground) which must be noise free to give reliable circuit operation. For this reason, a relay (mercury start) with mercury wetted contacts is used to provide the trigger signal. Before the relay is energized, pin 21 is at -4 volts due to the 1.3K ohm resistor as shown on figure 13. Reset Standardizer R2 is conducting because its base-emitter is forward biased by the 2K ohm base resistor connected to -15 volts. Without a trigger the R2 output is at ground. The 1K ohm collector load resistor is located externally to the RS card due to power dissipation and physical size limitation. The transistor base will be slightly negative, and the pin 21 at -4 volts, thus, the input.1 UF capacitor will be charged to -4 volts After the Mercury Start relay is energized, the input pin 21 will go to ground. This positive step voltage will be coupled by the .1 UF capacitor to the base of the 2N1998. The transistor base-emitter will be reverse biased and the transistor will be cut off. The collector will start for -56 volts but will be clamped at -15 volts by diode KK39TT. The Input and Output signals are shown below:

#### FIGURE IV**-1**5

The output pulse will last until the .1 UF capacitor has discharged thru the 2K ohm resistor to the point where the base-emitter of the transistor is again forward biased. At this point the transistor will again conduct and its collector will return to ground. No output pulse is produced when the relay opens since the base-emitter will remain forward biased. The range of the output pulse length is due to parts tolerances, voltage supply variations, etc.

#### Reset 3 (R3)

The Reset Standardizer, R3, operates in the same manner as R2. Its collector is normally at ground, then goes to -15 volts for 37-64#s while the 2N1998 is cut off and returns to ground when the transistor again conducts. The Reset 3 output is also used to control an Inverter circuit which will trigger Reset 1.

#### Reset 1 (R1)

A four input OR gate, consisting of diodes V2CC, V4CC, V6CC, V14CC and the 16K ohm resistor connected to -15 volts, controls the triggering of Rl. Reset 1 may be triggered directly by the logic at input pins 8, 10 or 12 and is also triggered each time Reset 3 is triggered thru diode V14CC.

The Inverter produces a ground signal when its transistor is conducting since the emitter is grounded. A -4 volt level is produced when the transistor is off due to the 2400 ohm resistor that is connected to -15 volts and the clamp diode that is connected to -4 volts. Before R3 is triggered, the Inverter is off due to current flow from ground at the R3 output thru the 24K ohm and 91K ohm resistors to +15 volts. The -4 volts from the collector of the Inverter is applied thru diode Vl4CC to the .1 UF capacitor at the input to the Reset 1 circuit. As Reset 3 is triggered, its output goes to -15 volts, the Inverter is switched on, the Inverter collector goes to ground and the positive voltage step is applied thru diode V14CC and the .1 UF capacitor to the base of Reset 1. This triggers RI and produces the same pulse as R2 and R3. The pulse durations of R1, R2 and R3 may all be different but all will be in the range 37 to  $64 \mu$  s. The Reset Standardizer circuits require a positive going signal for triggering. If the Mercury Start relay was used to trigger Rl directly thru an OR input, the output of the OR gate would remain high during the entire time the Mercury Relay was energized. This would prevent the Logic from triggering Rl thru the other OR inputs. For this reason Rl is triggered by R3 thru an Inverter which returns the OR input to -4 volts after the Reset 3 pulse ends and this allows the Logic to trigger Rl thru the other OR inputs.

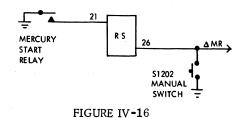

#### Delay Machine Reset ( $\Delta$ MR)

The  $\Delta$  MR signal is produced each time the mercury start relay is energized. It can also

be produced manually by depressing the  $\Delta$  MR push button prior to single-shot Clock operation.

The signal is used together with program signals from the panel or the keyboard to set various flip-flops which must hold information prior to the start of the first electronic operation.

Although  $\Delta$  MR is triggered by the start relay, it must not occur until after the Rl, R2 and R3 pulses have terminated. It is produced by two Pulse Standardizers (PS) and an Inverter which employ transistors P20S, Pl4S and P7S. The first PS delays the  $\Delta$ MR signal until after the Reset pulses have ended. The second PS produces a negative signal 12 to 20  $\mu$ s in length and the Inverter converts this to the positive  $\Delta$ MR signal.

Before the start relay is energized, the Input at pin 2l is at -4 volts. Transistor P20S is forward biased by the 56K ohm resistor E35N connected to -15 volts. With transistor P20S conducting thru the 2K ohm load resistor, its collector will be at approximately ground level.

The transistor Pl4S, used in the second PS stage, is normally conducting due to the 10K ohm resistor A17J and 47.5K ohm resistor A20J connected to -15 volts. The 10K ohm resistor establishes a threshold level for the PS base circuit so that any small voltage changes at it input will not cut it off. The Pl4S pulse standardizer controls the Inverter which produces the  $\Delta$ MR signal and if a small positive transient were to cut off Pl4S, a  $\Delta$ MR would be produced which could cause an erroneous electronic operation. With Pl4S conducting thru the 3K ohm load resistor connected to -15 volts, its collector will be at approximate ground.

With the collector of Pl4S at ground, the Inverter P7S will be reverse biased due to the 2200 ohm resistor El2N and 30K ohm resistor B8K connected to +15 volts. The Inverter transistor will be off and its collector ( $\Delta$ MR Output) will be low due to the 820 ohm resistor connected to -15 volts and the clamp diode connected to -4 volts.

When the start relay is energized, pin 21 goes from -4 volts to ground. This positive step voltage is applied thru the 6200 PF capacitor to the base of the first PS and cuts it off. With P20S no longer conducting thru the 2K load resistor, the collector goes to -15 volts. Transistor P20S will remain cut off for 67 to 97  $\mu$ s as determined by the discharge of the 6200 PF capacitor thru the 56K ohm base bias resistor. The negative voltage change at the collector of P20S is coupled thru the 680PF capacitor A29N but this does not alter the state of the second PS which continues conducting. When the 6200PF capacitor in the input to the first PS has discharged to the point where the base-emitter is again forward biased, the first stage will again conduct. Its collector will go from -15 volts to ground and this positive step voltage will trigger the second PS stage.

As the collector of P20S goes from -15 volts to ground, the positive signal is coupled thru the 680PF capacitor to the base circuit of the second PS which cuts off transistor P14S. As the collector current stops flowing thru resistor D15M, the collector goes to -5 or -6 volts which forward biases the Inverter transistor P7S. The second PS will remain cut off for 12 to 20  $\mu$ s as the 680PF capacitor discharges thru the 47.5K ohm resistor. After the capacitor discharges to the point where the base-emitter of P14S is again forward biased, transistor P14S will again conduct and its collector will return to ground.

When transistor Pl4S is conducting and its collector is at ground, the Inverter transistor P7S is reverse biased and cut off. Its collector is clamped at -4 volts thus the  $\Delta$  MR signal is low. When the second PS is triggered and its collector goes to -5 or -6 volts, the Inverter is forward biased and conducts. Its collector goes to ground and the  $\Delta$  MR signal becomes high. The second PS is cut off for 12-20  $\mu$ s thus the Inverter conducts for 12-20  $\mu$ s. The  $\Delta$ MR signal is shown below:

#### FIGURE IV-17

After the second PS again conducts, the Inverter will be reverse biased and the  $\Delta$ MR signal will return to -4 volts. The 560PF capacitor is included to provide minimum turn off time for the Inverter transistor.

#### RESET STANDARDIZER

Burroughs - Series E 2100 Instruction Book

Sec. IV

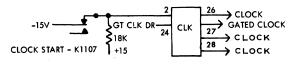

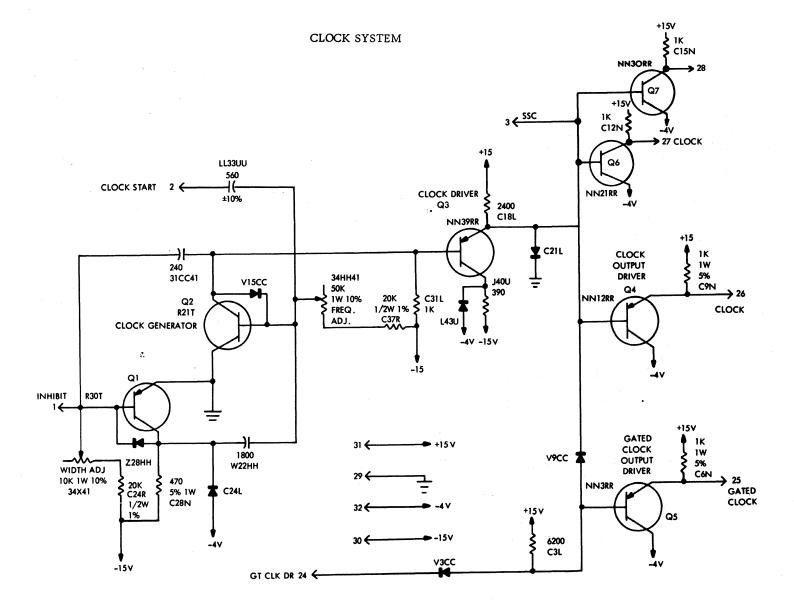

#### CLOCK SYSTEM

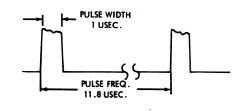

Clock pulses are the basic timing pulses used to synchronize the various electronic operations that take place during a machine cycle. The CLOCK is a continuous stream of regularly spaced pulses which are supplied to the Electronic Arithmetic and Memory Unit whenever the machine power is turned on. The GATED CLOCK is one or more pulses, occuring at the same time as CLOCK, which are supplied to the Electronic Unit only when gated by logic signals.

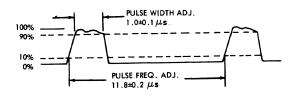

Since most electronic operations in the machine require CLOCK pulses, gated with logic, to begin each sequence of an operation, the basic speed at which the Electronic Unit operates is governed by the repetition rate at which CLOCK pulses occur. Since the Clock consists of 1  $\mu$ s pulses separated by an 11  $\mu$ s interval, the overall time period is 12  $\mu$ s which is a pulse repetition frequency of approximately 85KC.

A block diagram of the Clock is shown below.

#### FIGURE IV-19

There are three clock outputs A, B and C which are current amplifiers that are driven by the clock multivibrator. Not all clock outputs are used on the E 2100. The clock card is designed to supply signals for future developments.

The Clock outputs are taken from pins 26, 27 and 28. The Gated Clock Driver signal is a logic signal which is applied at pin 24 to control the Gated Clock output at pin 25. Gated Clock pulses are produced only when the Gt. Clk. Dr. signal is high. A Clock start circuit is provided to ensure the Clock will start each time the machine is turned ON. The input level at pin 2 is -15 volts after the DC voltages are established when the machine is turned on. When the Clock Start relay K1107 is energized, the input level at pin 2 goes to +15 volts. This positive going signal is coupled into the Clock card thru a capacitor and insures that the Clock will start operating.

#### Clock Generator

The Clock Generator is a free-running oscillator or astable multivibrator circuit which uses two 2N1998 high speed switching transistors (R30T, Q1 and R21T, Q2) for its active elements. The circuit is actually two common emitter amplifiers or pulse standardizers connected so that the output of one feeds the input of the other, reference Figure 23.

When the DC voltages are applied to the Clock generator, one transistor will usually conduct more than the other due to the variations in the tolerances of the electrical components. In case both transistors come on conducting equally, a start input is provided by K1107 to guarantee the Clock Generator will start. With the Single Shot Clock removed from the machine, the inputs at pins 1 & 3 are floating.

Assuming transistor Q1 begins conducting more than Q2, the increasing current thru the 470 ohm load resistor will cause the collector voltage to become less negative. This positive going signal is coupled thru the 1800 PF capacitor to the base circuit of Q2. As the base of Q2 is pulled toward cut off by the positive signal, the collector current of O2 thru the 1K load resistor C31L decreases and the collector of Q2 becomes more negative. This negative signal is coupled thru the 240PF capacitor, 3lCC41, to the base of Q1, causing it to conduct even more. Once one transistor conducts more than the other, the switching action is very fast as one transistor is cut off and the other conducts heavily. The conducting transistor does not go into saturation because of the diode connected between its base and collector. The diode prevents the collector from becoming positive with respect to the base, thus, the transistor can be switched off more rapidly. Thus, V15CC & Z28HH are speed-up diodes.

During the time Q2 is cut off, its collector is 4 to 5 volts negative due to current flow from -15 volts thru the lK resistor C3lL, thru the baseemitter of Q3 and the 2400 ohm resistor to +15 volts. Q2 will remain cut off for 8 to  $27 \ \mu s$ depending on the setting of the frequency adjustment control as the 1800 PF capacitor discharges thru it and the 20K ohm resistor in series. After the capacitor discharges to the point where the base-emitter of Q2 is again forward biased, transistor Q2 will begin to conduct.

As Q2 begins to conduct the increasing current thru the lK load resistor brings the collector of Q2 to ground. This positive voltage change is coupled thru the 240 PF capacitor and cuts off Q1. Transistor Q1 will remain cut off for .75 to 1.4  $\mu$ s depending on the setting of the width adjustment control. After the 240 PF capacitor has discharged thru the width adjustment and 20K ohm resistor in series to the point where the base-emitter of Q1 is again forward biased. Q1 will again conduct and Q2 will be cut off. The diode C24L clamps the collector of Q1 at -4 volts during the time Q1 is cut off.

Each time the machine is turned on, a positive 30 volt signal is coupled from the Clock Start relay thru the 560 PF capacitor LL33UU to the base of Q2. This signal will momentarily reduce the conduction of Q2 and insures the Clock Generator will start operating. The output from the Clock Generator is taken from the collector of Q2 which is connected to the base circuit of the emitter-follower driver Q3.

#### Clock Driver

Transistor NN39RR (Q3) is connected in an emitter-follower circuit which provides current to drive the base circuits of the Clock and Gated Clock Output Drivers. The signal from the collector of Q2 will, when properly adjusted, be at or near ground for  $1\mu$ s and negative for  $11\mu$ s. When the base of Q3 is at ground, the emitter-follower will be conducting and its emitter will also be near ground. When the base of Q3 is negative the emitterfollower will conduct heavily and its emitter will go to -4 volts. Diode L43U is a lower clamp for the collector of Q3 and is connected to -4 volts. Diode C21L prevents the emitter from ever going above ground.

#### Clock Output Driver

The Clock Output Drivers Q4, Q5 and Q6 have the capacity for driving up to 32 flip-flops each and under full load, the output signal level from this emitter-follower will not deteriorate any further than -3.8 to -3.7 volts. The Clock Output waveform is shown below:

#### Gated Clock

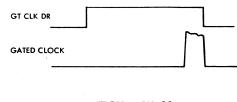

Diodes V3CC & V9CC form a two input AND gate together with resistor C3L. This AND gate controls the output of the Gated Clock Output Driver. One input to the gate is the standard clock waveform from transistor Q3. The second input at pin 24 is controlled by the logic. Whenever the Gt Clk Dr Signal is high during Clock time, a Gated Clock Pulse will be produced. Waveforms are shown below:

The Gated Clock Output has the capacity for driving up to 8 flip-flops.

#### Tests & Adjustments

#### Clock Pulse

Using an accurately calibrated oscilloscope, observe the Clock pulse at E3A-26 which is the output from the emitter of Q4. Synchronize the oscilloscope internally. The pulse width and frequency should be as shown below:

FIGURE IV-22

To Adjust:

(a) Turn the pulse width adjustment control.

- (b) Turn the frequency adjustment control.

- (c) Recheck the Clock pulse width and readjust the pulse width adjustment control if necessary.

#### Reason:

To ensure correct Clock pulses.

FIGURE IV-23

Burroughs - Series E 2100 Instruction Book

Sec. IV

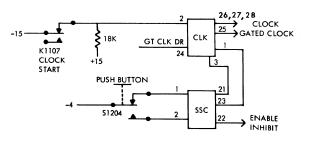

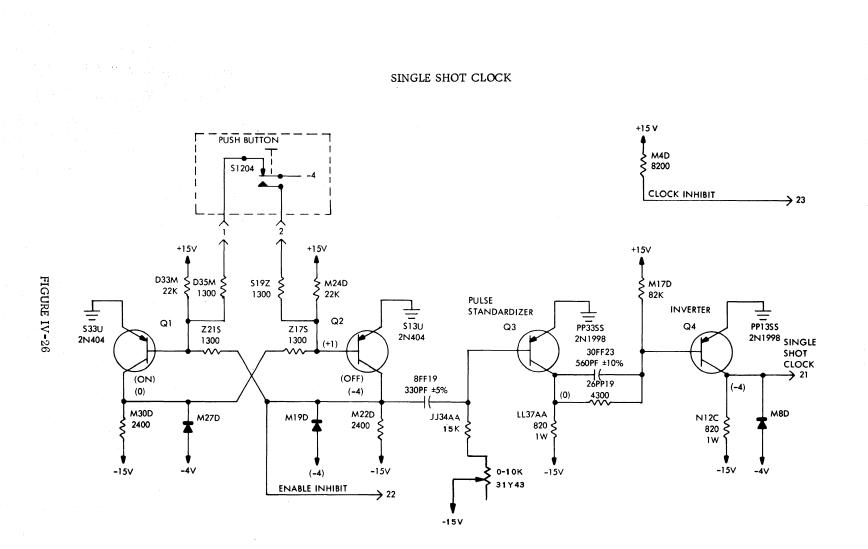

#### SINGLE SHOT CLOCK

The Single Shot Clock (SSC) is used to produce an output pulse of approximately the same width and amplitude as the standard clock output. Its main purpose is an aid in trouble-shooting. The SSC output is triggered by operating a pushbutton switch Sl204. When the SSC card is installed in the machine, the Clock Generator on the CLOCK card is inhibited and the signal produced by the SSC is used to drive the Clock Output Driver.

A block diagram of the Clock & Single Shot Clock Cards is shown below:

#### FIGURE IV-24

Each time the pushbutton is depressed, a single Clock pulse will be produced at pin 26 and/or pin 25 of the Clock card. The ENABLE INHIBIT signal is used to control the Inhibit Drivers which are associated with the Core Memory. When the SSC card is not installed and the Clock generator is running, the Inhibit Drivers are turned on shortly after a Clock pulse and turned off by the next Clock pulse. During SSC a Write operation might be initiated by depressing the button and the Inhibit Drivers would be turned on. They would remain on until the button was depressed again. This is not desirable because the Inhibit Drivers are not designed for continuous operation. The Enable Inhibit Signal from SSC will be high only as long as the button switch is depressed. Once it is released the Enable Inhibit will return to -4 volts and turn off the Inhibit Drivers.

The SSC circuitry, shown on figure 26, consists of a flip-flop which, under control of the Pushbutton S1204, triggers a pulse standardizer. The output of the pulse standardizer is then inverted to produce a positive pulse which drives the Clock Output Driver and a single Clock pulse results.

Transistor Q1, Q2 and associated components make up the SSC flip-flop. Before the button is depressed Q1 is conducting & Q2 is off. The two 1300 ohm resistors D35M and Z21S form a resistor OR gate together with the 22K ohm resistor connected to +15 volts. The -4 volts thru the normally closed contacts of the pushbutton forward biases Ol and it conducts thru the 2400 ohm load resistor M30D. With Ol conducting its collector is near ground. The two 1300 ohm resistors S19Z and Z17S form a resistor OR gate together with the 22K ohm resistor M24D connected to +15 volts. This OR gate controls the base circuit of Q 2. With one OR input not connected (button not depressed) and the other input at ground from the collector of Q1, transistor Q2 is reverse-biased and cutoff. Its collector is clamped at -4 volts due to the 2400 ohm load resistor M22D connected to -15 volts and the clamp diode M19D. The Enable Inhibit line is at -4 volts which prevents any Inhibit Drivers from conducting and the -4 volts from the collector of Q2 is also applied thru the OR gate to hold Ql conducting.

When the button is depressed the -4 volts is switched from the OR input of Q1 to the OR input of Q2. This triggers Q2 and it conducts thru the 2400 ohm load resistor connected to -15 volts. With Q2 conducting its collector switches from -4 volts to ground and this input to the base of Q1 reverse biases Q1 & it cuts off, (the other OR input to Q1 is open since the button is depressed). As Q1 cuts off its collector is clamped at -4 volts due to the load resistor M30D and clamp diode M27D. The -4 volts from the collector of Q1 is fed back to the base of Q2 and insures it will continue conducting even if the pushbutton switch contact bounces. This feedback insures only one trigger pulse into Q3 each time the button is depressed. During the time the button is depressed, the Enable Inhibit line will be at ground which will allow the Inhibit Drivers to conduct if a Write operation is in progress.

When the button is released, Ql is again switched on and in turn Q2 is switched off due to the ground signal from the collector of Ql. Once Q2 switches off the -4 volts from its collector is fed back thru the resistor OR to keep Ql conducting in case the pushbutton switch contact bounces on release. This insures that once Q2 is switched off when the button is released, it will not be triggered again and produce a second clock pulse for one switch depression. Once the button is released and Q2 switches off, its collector is clamped at -4 volts and the Enable Inhibit line is also at -4 volts which shuts off any Inhibit Drivers which may have been conducting.

#### Pulse Standardizer

since its base-emitter is forward biased by the 15K ohm resistor JJ34AA and the frequency adjusting Pot. at 31Y43 connected to -15 volts. When the pushbutton is depressed and the collector of O2 switches from -4 volts to ground, the positive voltage signal is coupled thru the 330 PF capacitor 8FF19 to the base of O3 and cuts it off. Transistor O3 will remain cut off for 1 to 2 s as the 330 PF capacitor discharges thru 15K ohm base resistor and 10K Pot. Once the 330 PF capacitor discharges to the point where Q3 is forward biased, Q3 will again conduct. When Q2 is switched off after the pushbutton is released, no output pulse will be produced since a negative signal at the base of Q3 does not alter its conducting state.

#### Inverter

The Inverter circuit involving transistor Q4 inverts the negative clock pulse from the pulse

standardizer Q3 and the Inverter output becomes the Single Shot positive Clock pulse which is routed to the Clock card, pin 3, to drive the Output Clock emitter-follower. When Q3 is conducting, its collector is at ground. This ground level causes the base-emitter of Q4 to be reversed biased due to the 4300 ohm resistor 26PP19 and 82K ohm resistor M17D connected to +15 volts. With Q4 cutoff, its collector is clamped at -4 volts by the 820 ohm load resistor connected to -15 volts and the clamp diode M8D. Thus, before the pulse standardizer is triggered, the single shot clock output is at -4 volts.

When the SSC button is depressed and Q3 cuts off, the base of Q4 goes negative due to the change current flow in the coupling network. With the base of Q4 negative, the transistor conducts and its collector goes to ground. It will remain at ground for 1 to 2  $\mu$ s while Q3 is cutoff. After Q3 again conducts, Q4 will again be reverse biased, and the output will return to -4 volts. The 560PF capacitor is selected to provide minimum turn off time for Inverter transistor. Thus, for each depression of the Single Shot Clock push button, a single positive clock pulse is produced.

#### Clock Inhibit

When the SSC card is installed a circuit is completed from +15 volts thru a 8200 ohm resistor M4D to the base of Ql transistor of the Clock Generator on the Clock card and this stops the operation of the Clock Generator during the time the SSC card is in use.

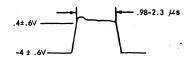

The Clock output, pin 26 and Gated Clock pin 25, when triggered by Single Shot Clock is shown below:

FIGURE IV-25

For Form 3737

Printed in U.S. America Revised 8-10-64

Sec. IV

Burroughs - Series E 2100 Instruction Book

#### MEMORY CIRCUITS

#### MEMORY CARD

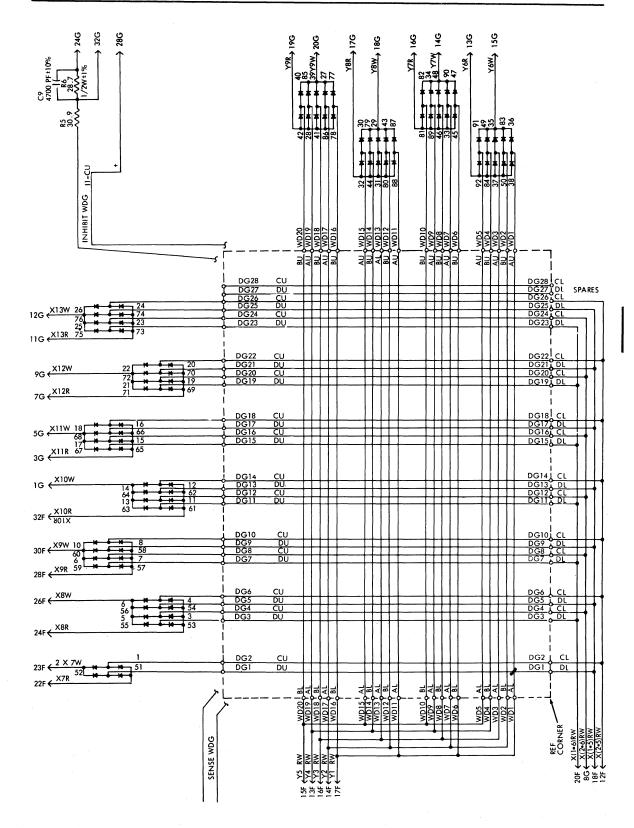

The purpose of the memory card is to store information in binary form. The memory card contains the four plane core memory package which consists of the magnetic cores, the X lines, Y lines, inhibit windings and sense windings. The memory card also contains disconnect diodes, which allow the read drivers to cause current flow in one direction through the X and Y lines and the write drivers to cause current flow in the same lines but in the opposite direction. The sense pre-amplifier is located on the memory card but is described elsewhere in this section. The Y lines furnish the word selection and the X lines furnish the digit selection. The following descriptions refer to the schematic on figure 27 and assume the read or write of a core selected at the intersection of the WDI and DGI lines.

#### Y Lines

The Y lines determine what is commonly termed word selection and also provide a half current for switching the core in either the read or write direction. During a read operation, current flows from the read driver Y1, through Y line WD1 & diode 38 to read driver Y6R. This provides a half current for all word one cores. The reverse of the current flow through this line occurs during the write operation.

#### X Lines

The X lines determine the digit selection and also provide a half current for switching the cores in either the read or write direction. During the read operation, current flows from the read driver X(1-5) through X line DGl, diode 51 to read driver X7R. This provides a half current to the digit one cores. The reverse of the current flow through this line occurs during the write operation. The coincidence of the X and Y line currents flowing through a core in the same direction, causes the core to switch if it is not already magnetically oriented in this direction.

#### Inhibit Winding

The inhibit winding is used only on the write or clear memory operation. It is used during the write when a core is not to be switched and furnishes a half current in an opposing direction to the Y line current. This cancels the effect of the Y line and prevents the core switching.

Current will flow from -15 volts through the 28.7 ohm resistor, the 30.9 ohm resistor and the inhibit winding II-CU, to the inhibit driver which is at ground level. The 28.7 ohm and 30.9 ohm resistors are for current limiting purposes. The 4700 pf capacitor is a peaking capacitor to help shape the leading edge of the inhibit signal. A full current is passed through each inhibit winding and causes all the cores to orient in the O state during a clear memory operation.

#### Sense Winding

The sense winding is covered under the heading SENSE PRE-AMPLIFIER.

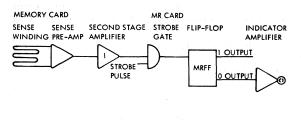

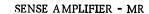

#### Sense Amplifier - MR

The primary purpose of the Sense Amplifier -MR circuit is to provide a means of sensing the switching of magnetic polarity in a memory core and temporarily storing this information in a flip-flop in order to control the logic elements. The sense amplifier - MR circuit also provides a means of pulse amplitude discrimination and gating in order to set the flip-flop only at a precise time during the read sequence. This prevents erroneous setting of the flip-flop from low amplitude pulses generated by partial core switching, noise pulses or the switching of the cores during the write sequence.

FIGURE IV-27

The following circuit descriptions refer to the schematic on figure 30.

#### Sense Pre-Amplifier

The sense winding and pre-amplifier are located on the memory card. The sense winding passes through all the cores on one plane of the memory and has a voltage induced in it when any of the cores through which it passes experiences a change or reversal (switch) of the flux. Due to the core orientation and the installation pattern of the sense winding, a switching core may induce a positive or negative pulse in the sense winding. Therefore, the following stage must be capable of handling both positive and negative pulses. The sense winding terminates in the primary of a 1:3 ratio pulse transformer and the two capacitors across the winding are noise suppressors. The sense pulse transformer has a center tapped secondary which is directly coupled to the bases of a pair of transistors which are connected in a symmetrical difference amplifier configuration and biased in the class AB range. The two 5uf capacitors from +15 and -15 to ground, at the bias voltage divider, are noise suppressors. The 825 ohm resistors, between +15 and -15, form a voltage divider to supply the base bias for the pre-amplifier stage. The 15uf capacitor across the 825 ohm resistor is a filter to provide a stable bias source. When a voltage is induced in the sense winding, it is applied to the primary of the 1:3 ratio pulse transformer.

The two 1100 pf capacitors across the winding are transient noise suppressors. The voltage on the primary of the transformer produces

voltages in the bifilar wound, center tapped secondary, which are out of phase and equal in amplitude with respect to the center tap. The 1000 ohm resistor across the transformer is an impedance match for the transformer. The voltage applied at the base of QA is equal in amplitude but 180 degress out of phase with the voltage applied to the base of QB. Therefore, as long as the amplitude of the signals applied to the bases of QA and QB does not exceed the cut off level between the base emitter junctions, the signals produced at the collectors will be equal in amplitude but 180 degress out of phase. Since the collectors are parallel connected, signals below this amplitude will cancel. Any inequality in the signals below the cut off amplitude may be corrected by adjustment of the 5000 ohm potentiometer in the emitter circuits; only if the proper, calibrated test equipment is available. The 15uf capacitors across the balance pot are filters to prevent any change in the static emitter bias, when the pulse currents cause a dynamic change in the emitter current.

When the sense pulse amplitude exceeds the emitter base cut off, one of the transistors is driven into the cut off region and ceases to conduct. However, the other transistor continues to conduct and causes a change in the current flowing in the 4990 ohm collector load resistor KK29TT on the MR card. This current change causes an increased voltage drop in the resistor which, in turn, causes a positive pulse to appear at the output of the sense amplifier. This circuit produces a positive pulse at its output, regardless of the polarity of the pulse induced in the sense winding. It should be remembered, however, that the pulse at the output will be the difference in the signals produced by QA and QB or only that portion created by the sense pulse amplitude greater than the emitter-base bias.

#### Test & Adjustment

The test and adjustment for the balance and sensitivity controls requires the use of an

accurately calibrated oscilloscope with a differential pre-amp which is not presently available to service. The Balance Pots and sensitivity should not be tampered with since misalignment may allow weak noise pulses to get through the amplifier or prevent legitimate pulses of proper amplitude getting through the amplifier.

#### SECOND STAGE SENSE AMPLIFIER

The second stage amplifier, strobe gate, MR flip-flop and indicator circuits are located on the MR card. The signal from the pre-amplifier is developed across the collector load resistor KK29TT. Resistor KK29TT is located on the MR card in order to provide voltage wetting of the card contacts between the memory and MR cards. The signal developed across resistor KK29TT is coupled to the sensitivity control 34EE41 by capacitor BB26PP. Sensitivity control 34EE41 and resistor KK31TT form a voltage divider to supply base bias to transistor LL13NN.

The signal from the sense amplifier is attenuated by the sensitivity control in order to vary the gain in the second stage amplifier and is then applied to the base of transistor LL13NN. Resistors JJ2UU and LL6UU form a voltage divider to supply emitter bias for transistor LLI3NN. Capacitor EE8RR is a filter to insure stability of the bias voltage. Resistor HH4RR is a stablizing resistor for transistor LL13NN and capacitor HH17TT is a bypass to stablize the emitter of transistor LL13NN. The attenuated positive pulse from the sense pre-amplifier is applied to the base of LL13NN which is biased near saturation. This causes LL13NN to cut off and reduce the current through the collector load resistor KK10TT which allows the collector voltage to go to -4 volts where it is clamped by diode Y15FF. The second stage amplifier inverts and amplifies any signal applied to its base.

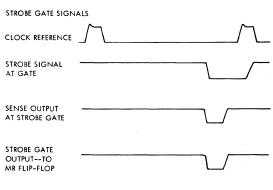

#### Strobe Gate

The negative pulse from the second stage sense amplifier is applied to one input diode (Y13FF) of the strobe gate which is a negative AND gate. If a simultaneous negative strobe pulse is applied to diode N13W of the gate, the voltage across the resistor C15L is reduced and the voltage on the base of transistor F20J is made more negative by an amount equal to the reduction across resistor C15L. Transistor F20J is an emitter-follower, biased on at normal and applying a negative signal to its base causes its emitter to go negative by approximately the same amount. This causes an increase in current and voltage drop across the emitter load resistor B17K. Test points are provided at terminals 2 and 24 of the MR card in order to observe the signals from the second stage amplifier and strobe gate.

FIGURE IV-29

#### MR Flip-Flop

The signal from the strobe gate is applied to the input of the MR flip-flop. The MR flipflop is of standard RTL configuration and is different from the usual flip-flop used in the E2100 in that it is directly coupled to the strobe gate and MR reset gate. This causes it to trigger at a given DC level rather than pulse amplitude. Since this is a negative trigger flip-flop and is triggered by a negative pulse, it triggers on the leading edge of the pulse. Starting with the flip-flop in the reset state, transistor F37J will not be conducting and transistor N39R will be conducting.

Resistors B17K, P21X, B26K, P28X and C31L make up the base bias voltage divider for transistor F37J. The junction of resistors P28X and C31L is at approximately 0 volts during the reset condition due to transistor N39R conducting. The strobe is at its high level which causes the base of the emitter follower transistor F20J to be at 0 volts. Consequently, the emitter of F20J and the junction of resistors B17K and P21X are also at 0 volts. Due to the current flow from the resistors P21X and P28X through resistors B26K, the voltage on the base of F37J will be positive and the transistor will not conduct.

A negative change on the emitter of transistor F20J and the junction of resistors B17K and P21X voltage divider resistors P21X and B26K. This increases the voltage drop in resistor B26K which makes the base of transistor F37J negative and causes it to conduct. Up to this point, transistor N39R has been conducting due to the negative voltage applied to its base by the voltage divider consisting of resistors C28L, M35V, U40BB and C40L. Transistor F37J conducting causes the voltage at the junction of resistors C28L and M35V to go to ground level. This, through the voltage divider, causes the base of transistor N39R to be positive which turns it off. Turning off transistor N39R reduces the current through resistor C31L which allows the collector voltage to go from 0 volts to -4 volts, where it is clamped by diode L23U. Changing the collector voltage of transistor N39R to -4 volts causes additional current through resistor P28X and B26K. This keeps the base of transistor J37J negative after termination of the signal from the strobe gate. Therefore, transistor F37J will continue conducting and the flip-flop will remain in its set state until it is reset. The capacitors P19X, P26X, M33V and U38BB are used to compensate for the stored base charge in transistors F37J and N39R. The flip-flop can be reset by applying the previous analysis to the reset input.

#### Indicator Circuit

The indicator circuit is connected to the reset side of the MR flip-flop and will be on when the flip-flop is set. The indicator circuit is a standart circuit and its description is covered elsewhere in this section.

#### Noise Filters

The three 5 microfarad capacitors A2N, B6P and Cl0R are used to filter or decouple any noise from the voltage supply lines to the MR card.

For Form 3737

Printed in U.S.

America Revised 8-10-64

Sec. IV

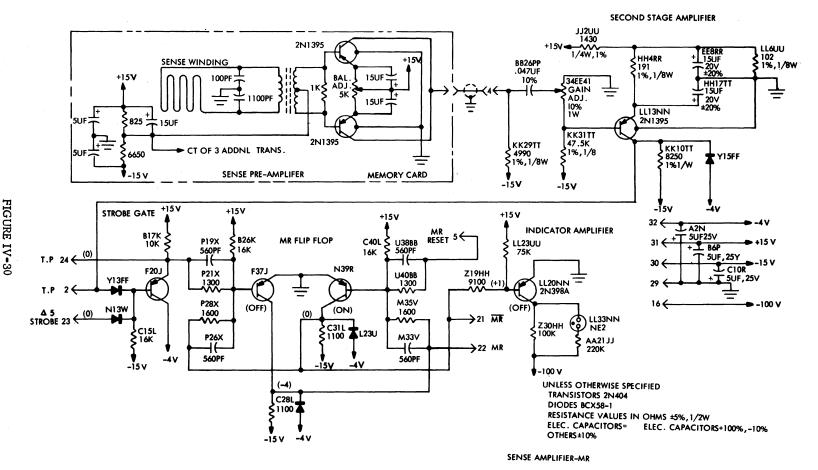

#### MEMORY DRIVER

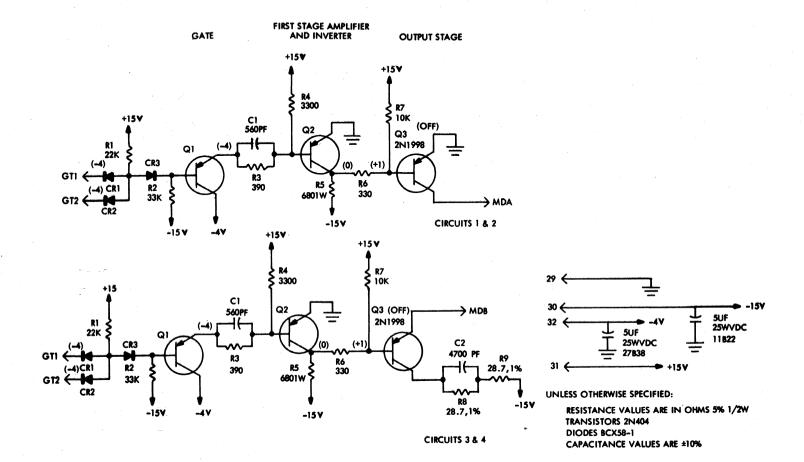

There are two types of memory driver circuits, differing only in the output stages and commonly called driver pairs. Each is a two stage amplifier preceded by an AND gate. Four of these circuits are packaged on each MD card. The output stage of types one or two, completes the circuit between one end of a memory drive line and ground. The output stage of types three or four completes the circuit between the other end of the memory drive line and -15 volts.

#### FIGURE IV-31

The following circuit descriptions refer to the schematic figure 33.

Input Gate -- Circuits 1-2-3-4--

The input gate to the memory driver is basically a standard AND gate. A simultaneous positive signal at both inputs of the gate (diodes CRI & CR2) reduces the voltage drop across the load resistor R1. This causes the voltage at the junction of the three diodes CR1, CR2 and CR3 to go positive, which through the level correction diode CR3 causes the base of Q1 to go positive. R2 is the base bias resistor for Q1. Q1 is an emitter follower and a positive voltage on its base causes a positive change in its emitter. A more detailed description of the AND gate may be found elsewhere in this section. First Stage Amplifier --Circuits 1-2-3-4

The first stage amplifier is a driver for the output stage. The signal from the gate is developed across the voltage divider made up of R3 and R4. R3 and R4 serve as the emitter load for Q1 and base bias for Q2. Due to the voltage drop across R3, the signal applied to Q2 from the junction of R3 and R4 is slightly positive in respect to ground and cuts off Q2. The capacitor Cl is a peaking capacitor used to compensate for the stored base charge in Q2. Transistor Q2 is connected in a grounded emitter configuration which amplifies and inverts the signal and is normally conducting. The positive pulse applied to the base of Q2 cuts it off and reduces the current through the collector load resistor R5. This reduces the voltage drop across R5 and causes more current to flow through the voltage divider formed by R6 and R7.

Output Stage -- Circuits 1-2--

The increased current through the base bias resistor R7 causes the voltage across it to increase, which makes the base of Q3 negative. This causes Q3 to conduct and its collector to go to approximately ground since the emitter is at ground level. This results in one end of the memory drive line being effectively at ground potential.

#### Output Stage -- Circuits 3-4--

The increased current through the base resistor R7 causes the voltage across it to increase which makes the base of Q3 negative. This causes Q3 to conduct which causes current to flow from -15 volts through R9, R8, Q3 and into the memory drive line. R8 and R9 are current limiting resistors. Capacitor C2 is a peaking capacitor, used to shape the leading edge of the signal and improve its rise time. There is approximately 250 milliamperes of current flow from -15 volts through R9, R8, Q3 (circuit 3 0r 4), the memory drive line and Q3 (circuit 1 or 2) to ground.

Noise Filters

The two 5 microfarad capacitors 11B22 and

Driver Input and Output Signals

27B38 are used to filter or decouple any noise from the DC voltage supply lines to the memory driver card.

FIGURE IV-32

#### MEMORY DRIVER

. .

Burroughs - Series E 2100 Instruction Book

Sec. IV

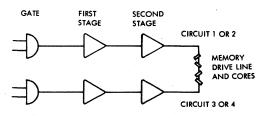

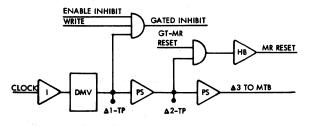

#### MEMORY TIMING A

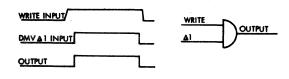

The memory timing A circuit is used to provide some of the delayed signals and gating required by the core memory. The delayed signals are developed by a multivibrator and two pulse standardizers connected so that their delays are consecutively added. The DMV is a negative trigger circuit; therefore, it is preceded by an inverter to allow its use with the positive clock pulses. The output of the DMV is gated with write and enable inhibit to produce the gated inhibit signal. The enable inhibit signal is used only with single shot clock, otherwise, this input to the gate is disconnected. The delayed signal from the DMV is also used to trigger the first pulse standardizer which adds its delay to that of the DMV. The delayed signal from the first pulse standardizer is gated with GT -MR reset and used through a heavy buffer to produce the MR reset signal. The delayed output of the first pulse standard izer is also used to trigger the second pulse standardizer. The second pulse standardizer then adds its delay to that of the DMV and the first pulse standardizer to produce the delay three signal. Delay three is used by the memory timing B circuit. Test points are provided at terminals 21 and 13 of the MTA card in order to observe the delay one and delay two signals.

#### Memory Timing A Logic

FIGURE IV-34

The following circuit descriptions refer to the schematic on figure 37.

#### Inverter

The inverter is a grounded emitter stage and is normally conducting due to the -4 volts applied to its input by the clock circuit. When a clock pulse occurs, a positive signal is applied to the base of transistor Q1 through capacitor N13W and the voltage divider consisting of resistors N15W and B13K. The capacitor N13W compensates for the stored base charge in Ql. The signal level applied to the base of Ql is slightly above ground level due to the voltage drop in resistor N15W. The positive signal cuts off Ql and reduces the collector current through resistor C15L. This allows the voltage at the collector to go negative and be clamped at -4 volts by diode UllBB. The voltage applied to the base of Q2 by the voltage divider resistors N19W and B21K will go negative due to the negative change on the collector of Ql.

#### DMV

Transistor Q2 is cut off and Q3 is conducting in their normal static state. The negative voltage applied to the base of O2 from the inverter stage causes it to conduct. The capacitor N17W is used to compensate for the stored base charge in Q2. When Q2 conducts, the current in resistor C28L increases causing a positive change in the voltage on the collector of Q2. This positive change on the collector of Q2 is coupled to the base of Q3 by capacitor N26Z until the capacitor discharges through the base bias resistor C30L. Th is causes Q3 to be cut off for the duration of the RC time of capacitor N26Z and C30L. During the time Q3 is cut off collector current through resistor C36L is eliminated, allowing the voltage at the collector of Q3 to go negative and be clamped at -4 volts by diode A38J. The negative change at the collector of Q3 is applied to the base of Q2 by capacitor N2IW and the voltage divider formed by resistors N23W and B21K. Th is causes Q2 to continue conducting after the termination of the clock pulse, until the RC time of capacitor N26Z and resistor C30L allows Q3 to conduct.

When the discharge of capacitor N26Z allows Q3 to conduct the collector current through resistor C36L causes the collector voltage to go to approximately ground level. This ground level, applied to the voltage divider resistors N23W and B21K causes the base of Q2 to become positive and Q2 ceases to conduct. The DMV is now back to its static state.

#### Inhibit Gate

The inhibit gate is used to produce a signal (GT INHIBIT), which with other logic, allows the selected memory core on a bit plane to switch. The gate is basically a standard AND gate and its emitter-follower stage is always conducting.

#### Inhibit Gate Signals

Assuming that the single shot clock is not being used, there is no input to terminal 25 and diode S9Z is inactive. Positive signals, simultaneously applied to diodes P29X and N3IW by write logic and the DMV (delay one) cause the emitter follower to go to approximately ground level. The emitter of the emitter-follower changes a corresponding amount and produces the gated inhibit signal. A more detailed description of an AND gate may be found elsewhere in this section.

#### Pulse Standardizer Q5

Pulse standardizer Q5 is normally conducting in its static state. The negative signal from the

DMV is applied to the base of Q5 through capacitor X33JJ. Since Q5 is conducting, the negative signal will not cause any change in its collector voltage, but capacitor X33JJ will charge through resistor JJ36SS. When the DMV times out, the positive signal from Q3 is applied to the base of Q5 by capacitor X33JJ and Q5 will cut off. When Q5 stops conducting, its collector no longer draws current through resistor JJ38SS and the voltage on its collector changes to -15 volts. Q5 remains cut off until capacitor x33JJ dischanges through resistor JJ36SS and the base of Q5 again goes negative. After the RC time of capacitor X33JJ and resistor JJ36SS, transistor Q5 will conduct and its collector current through resistor JJ38SS causes the collector voltage to change to approximately ground level. This has produced the 15 volt delay two pulse.

#### Pulse Standardizer Q6

Pulse standardizer Q6 is normally conducting in its static state. The negative signal from pulse standardizer Q5 is applied to the base of Q6 through capacitor BB22RR. Since Q6 is conducting, the negative signal will not cause any change in its collector voltage, but capacitor BB22RR will discharge through resistor JJ36SS. When the collector of pulse standardizer Q5 goes positive, the 15 volt positive change is applied to the base of Q6 by capacitor BB22RR and causes Q6 to stop conducting. When Q6 stops conducting, its collector no longer draws current through resistor JJ28SS and the voltage on its collector goes to -4 volts where it is clamped by diode LL26UU. Q6 remains cut off until capacitor BB22RR discharges through resistor JJ30SS and allows the base of Q6 to go negative. The negative voltage on the base of Q6 causes it to conduct again and its collector current through resistor JJ28SS causes the voltage on the collector to go to approximately ground level. This has produced the 4 volt delay three pulse.

#### MR Reset Gate

The MR reset gate is a standard positive OR gate used in this application as a negative AND gate. The negative delay two signal from pulse standardizer Q5 applied to diode BB16KK at the same time the negative GT -MR reset signal is applied to diode BB14KK, causes the base of transistor Q7 to go to -4 volts. Transistor Q7 is an emitter follower and is always conducting. The -4 volt signal on its base causes additional current in resistor KK12TT and the emitter of transistor Q7 goes to approximately -4 volts. The signal developed by this gate is the MR reset signal. necessary to reset the MR flip-flops. The signal from the emitter of the MR reset gate transistor Q7 is applied directly to the base of Q8. Q8 is an emitter follower and any change in its base voltage causes an equal change in its emitter voltage. The signal from the emitter of Q8 is used directly to reset the MR flip-flops.

#### Noise Filters

The three 5 microfarad capacitors A2N, B6P and C10R are used to filter or decouple any noise from the DC voltage supply lines to the MTA card.

#### Heavy Buffer

The heavy buffer is used to supply the current

Memory Timing "A" Signals

FIGURE IV-36

MEMORY TIMING "A"

## MEMORY TIMING B