PlayCD™ CL480 MPEG SYSTEM DECODER USER'S MANUAL

# **PlayCD**™

# **CL480 MPEG System**

# **Decoder User's Manual**

C-Cube Microsystems C-Cube Microsystems reserves the right to change any products described herein at any time and without notice. C-Cube Microsystems assumes no responsibility or liability arising from the use of the products described herein, except as expressly agreed to in writing by C-Cube Microsystems. The use and purchase of this product does not convey a licence under any patent rights, copyrights, trademark rights, or any other intellectual property rights of C-Cube Microsystems.

#### **Trademark Acknowledgment:**

PlayCD is a trademark of C-Cube Microsystems.

C-Cube and the corporate logo are registered trademarks of C-Cube Microsystems.

© C-Cube Microsystems 1994 All rights reserved

> C-Cube Microsystems 1778 McCarthy Boulevard Milpitas, CA 95035 Telephone (408) 944-6300 Fax (408) 944-6314

#### **Customer Comments and Feedback:**

If you have any comments about this document, send them to the C-Cube Technical Publications Department at the address listed above, or send e-mail to:

techpubs@c-cube.com

C-Cube Part # 92-0480-101

#### ii C-Cube Microsystems

# Preface

This manual is the primary source of technical information for the operation and programming of the C-Cube CL480 MPEG System Decoder.

This manual is intended for:

- System designers and managers who are evaluating the CL480 for possible use in a system.

- Design, software and system engineers developing a decoding system using the CL480 for whom a comprehensive programming background as well as a detailed understanding of MPEG compression is assumed.

In particular, readers should understand the MPEG standard: *Coded Representation of Picture, Audio and Multimedia/Hypermedia Information*, ISO 11172. This document is available from the American National Strandards Institute (ANSI), 11 West 42nd St., New York, NY 10036, (212) 642-4900.

This manual is divided into three main sections:

- Section I, General Information, presents an introduction to the CL480 and the MPEG standard that it implements.

- Section II, Hardware, describes signals, operational information for the external interfaces of the CL480, registers, and detailed electrical and mechanical specifications.

Audience

Related Publications

## Organization

Section III, Software, describes the CL480's microcode, and includes an alphabetical listing of all macro commands available to the programmer. Note: the microcode information in this manual applies to CL480 version 2.0.

## Conventions

Please note the following notation examples and conventions used in this manual:

| Notation                                              | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Examples                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ox1c3                                                 | "0x" prefix indicates a hexadecimal number.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11011 <sub>2</sub>                                    | "2" subscript indicates a binary number.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IMEM                                                  | Four-letter mnemonics indicate on-chip memories, starting with a letter to indi-<br>cate function of memory, and ending with "MEM." For example, IMEM is the<br>CL480's instruction memory.                                                                                                                                                                                                                                                                           |

| CPU_cntl<br>CD_cntl                                   | This format indicates a register name. The first part of a register name is a group specifier, given in all upper-case. The second part (separated from the first by an underscore and given in all lower-case) is a register specifier, indicating the function performed by the register within the group. In the examples shown, CPU_cntl and CD_cntl are separate registers, even though both have the same register specifier, "cntl."                           |

| VIE, Res                                              | Italicized acronyms or abbreviations (initial or all caps) indicate bit field names within registers or data words.                                                                                                                                                                                                                                                                                                                                                   |

| IMEM[3]<br>CPU_cntl[0]<br>IMEM[0][15]<br>IMEM[3][2:0] | Square bracket notation similar to C language array subscripting indicates words within memories, and bits within words and registers. IMEM[3], for example, is the 16-bit word at address 3 within IMEM, while CPU_cntl[0] is bit 0 of the CPU_cntl register. Similarly, IMEM[0][15] is the most significant bit of the word at IMEM address 0.                                                                                                                      |

|                                                       | Ranges of bits are indicated by numbers separated by a colon such as the three bits HMEM[3][2:0]. Ranges of words within a memory are indicated by numbers separated by a dash such as the eight words HMEM[0-7].                                                                                                                                                                                                                                                     |

| RESERVED or<br><i>Res</i>                             | Indicates bit fields within registers which are not defined. RESERVED bit fields may return any value when read and must be written with 0 (or 1 if so specified). Writing the incorrect value to a RESERVED CL480 register bit will cause indeterminate behavior. In addition, all CL480 registers which are not explicitly given names are also RESERVED, and accessing these registers may cause indeterminate results on current or future CL480 implementations. |

| leftBorder                                            | Bold-face type represents macro command arguments.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre>return();</pre>                                  | C-style syntax presented in courier typeface represents program pseudocode and equations.                                                                                                                                                                                                                                                                                                                                                                             |

| vbv_delay                                             | Names presented in courier represent names of items within the MPEG bit-<br>stream taken from the MPEG standard.                                                                                                                                                                                                                                                                                                                                                      |

# **Contents**

# **Section I. General Information**

# **1** Introduction

|   | 1.1 | PlayCD Family                                                 | 1-1 |

|---|-----|---------------------------------------------------------------|-----|

|   | 1.2 | CL480 Features                                                | 1-2 |

|   |     | 1.2.1 Flexible Video Interface with High-Quality Video Output | 1-2 |

|   |     | 1.2.2 Low Voltage, Low Power Operation in Small Package       | 1-3 |

|   |     | 1.2.3 Powerful, Easy-to-Use Microcode                         | 1-3 |

|   | 1.3 | Functional Description                                        | 1-4 |

|   |     | 1.3.1 Host Interface                                          | 1-5 |

|   |     | 1.3.2 CD Interface                                            | 1-5 |

|   |     | 1.3.3 DRAM/ROM Interface                                      | 1-5 |

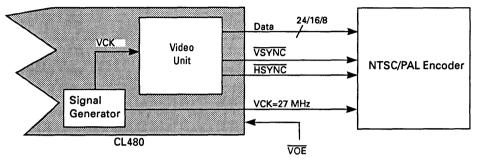

|   |     | 1.3.4 Video Interface                                         | 1-5 |

|   |     | 1.3.5 Audio Interface                                         | 1-5 |

|   | 1.4 | Consumer Electronics Application                              | 1-6 |

| 2 | MP  | EG Overview                                                   |     |

|   | 2.1 | MPEG Stream Structure                                         | 2-2 |

2.1.1 MPEG Stream Structure 2-2

|     | 2.1.2 General Decoding Process    | 2-2  |

|-----|-----------------------------------|------|

|     | 2.1.3 Video Stream Data Hierarchy | 2-3  |

| 2.2 | Inter-picture Coding              | 2-6  |

|     | 2.2.1 Picture Types               | 2-6  |

|     | 2.2.2 Video Stream Composition    | 2-7  |

|     | 2.2.3 Motion Compensation         | 2-8  |

| 2.3 | Intra-picture (Transform) Coding  | 2-10 |

| 2.4 | Synchronization                   | 2-11 |

|     | 2.4.1 System Clock References     | 2-11 |

|     | 2.4.2 Presentation Time Stamps    | 2-12 |

## Section II. Hardware

| 3 Si | 3 Signal Descriptions |      |  |  |

|------|-----------------------|------|--|--|

| 3.1  | Global Interface      | 3-2  |  |  |

| 3.2  | Host Interface        | 3-3  |  |  |

| 3.3  | CD Interface          | 3-5  |  |  |

| 3.4  | DRAM Interface        | 3-6  |  |  |

| 3.5  | Video Interface       | 3-8  |  |  |

| 3.6  | Audio Interface       | 3-10 |  |  |

| 3.7  | Programmable I/Os     | 3-11 |  |  |

|      |                       |      |  |  |

# 4 Host Interface Functional Description

| 4.1 | Functional Overview                      |     |  |

|-----|------------------------------------------|-----|--|

| 4.2 | Host Interface Registers                 | 4-2 |  |

|     | 4.2.1 Host Interface Address Registers   | 4-2 |  |

|     | 4.2.2 Host Interface Data Registers      | 4-2 |  |

|     | 4.2.3 Accessing Host Interface Registers | 4-3 |  |

|     | 4.2.4 DRAM/ROM Access                    | 4-3 |  |

|     | 4.2.5 Code FIFO Access                   | 4-5 |  |

|     | 4.2.6 Internal Register Access           | 4-6 |  |

| 4.3 | CL480 Read/write Operations              | 4-8 |  |

|     | 4.3.1 Host Write                         | 4-8 |  |

|     | 4.3.2 Host Read                          | 4-9 |  |

# 5 Local DRAM/ROM Interface

| 5.1 | General Description                 | 5-2  |

|-----|-------------------------------------|------|

|     | 5.1.1 DRAM: Amount and Organization | 5-2  |

|     | 5.1.2 ROM: Amount and Organization  | 5-3  |

| 5.2 | DRAM Memory Bus Interface           | 5-3  |

|     | 5.2.1 DRAM Address Mapping          | 5-4  |

|     | 5.2.2 DRAM Interface Connections    | 5-4  |

| 5.3 | ROM Memory Bus Interface and Timing | 5-5  |

|     | 5.3.1 DRAM_ROMTA Register           | 5-6  |

| 5.4 | DRAM Memory Bus Timing              | 5-7  |

|     | 5.4.1 DRAM Page-Mode Read Timing    | 5-7  |

|     | 5.4.2 DRAM Page-Mode Write Timing   | 5-8  |

|     | 5.4.3 DRAM Refresh Timing           | 5-10 |

|     | 5.4.4 DRAM_REF Register             | 5-10 |

| 5.5 | Memory Design Guidelines            | 5-11 |

|     |                                     |      |

| 6 | CD  | Interface                              |

|---|-----|----------------------------------------|

| 6 | 6.1 | General Description                    |

|   |     | 6.1.1 Mode Functions                   |

|   |     | 6.1.2 Mode Selection                   |

| 6 | 6.2 | Signal Interface                       |

| E | 5.3 | Disc and Signal Formats                |

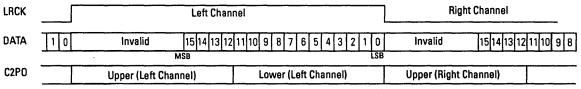

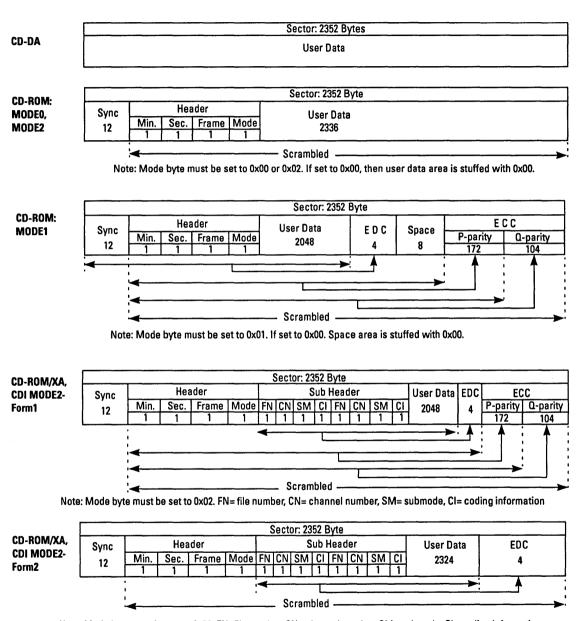

|   |     | 6.3.1 CD Interface Input Signal Format |

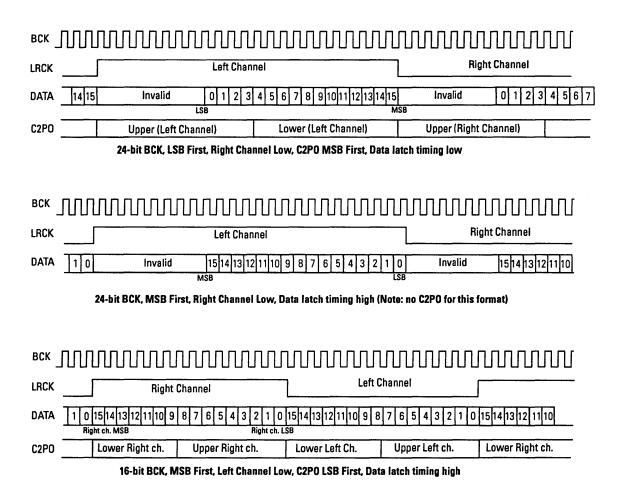

|   |     | 6.3.2 Compact Disc Sector Format       |

|   |     | 6.3.3 Data Alignment for CD-ROM        |

| E | 6.4 | Design and Operation Considerations    |

| ŀ | Design and Operation Considerations |                                             | 6-8 |

|---|-------------------------------------|---------------------------------------------|-----|

|   | 6.4.1                               | Effects of Varying CD-DSP Speed             | 6-8 |

|   | 6.4.2                               | Maximum BCK Frequency                       | 6-8 |

|   | 6.4.3                               | Maximum Rate for Error Correction           | 6-8 |

|   | 6.4.4                               | ROM Accesses during MPEG Decode and Display | 6-8 |

6-1 6-2 6-3 6-4 6-4 6-6 6-7

# 7 Video Display Interface

| Digital Video Standards               | 7-2                                                                                                                                                                                        |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video Display Unit                    | 7-3                                                                                                                                                                                        |

| Timing Generation                     | 7-3                                                                                                                                                                                        |

| 7.3.1 (VSYNC or CSYNC)/HSYNC/VCK Out  | 7-5                                                                                                                                                                                        |

| 7.3.2 VSYNC/HSYNC/VCK In              | 7-5                                                                                                                                                                                        |

| Video Operation and Design Guidelines | 7-6                                                                                                                                                                                        |

| 7.4.1 How to Set Video Output Mode    | 7-6                                                                                                                                                                                        |

| 7.4.2 Aspect Ratio Limitations        | 7-6                                                                                                                                                                                        |

|                                       | Video Display Unit<br>Timing Generation<br>7.3.1 (VSYNC or CSYNC)/HSYNC/VCK Out<br>7.3.2 VSYNC/HSYNC/VCK In<br>Video Operation and Design Guidelines<br>7.4.1 How to Set Video Output Mode |

|        | 7.4.3   | CD-I Pixel Output                                    | 7-6   |

|--------|---------|------------------------------------------------------|-------|

|        | 7.4.4   | Transferring Video Data Via Host Bus                 | 7-6   |

|        | 7.4.5   | Vertical Interpolation and Full-Screen Playback Mode | 7-6   |

| 8 Aud  | io Inte | erface                                               |       |

| 8.1    | Gene    | ral Description                                      | 8-1   |

| 8.2    | Signa   | I Interface                                          | 8-2   |

|        | 8.2.1   | Controling the Audio Output Level                    | 8-2   |

|        |         | Using Emphasis Flags to Identify the Data Stream     | 8-3   |

|        |         | Low Power Operation                                  | 8-3   |

| 8.3    |         | ing Modes                                            | 8-3   |

| 8.4    |         | ation and Design Guidelines                          | 8-4   |

|        | 8.4.1   | Audio Buffer Underflow                               | 8-4   |

|        | 8.4.2   | DA-XCK and Cycle Jitters                             | 8-4   |

| 9 Elec | ctrica  | I and Physical Specifications                        |       |

| 9.1    | Opera   | ating Conditions                                     | 9-1   |

|        | 9.1.1   | Duty Cycle                                           | 9-2   |

|        | 9.1.2   | Power Pin Supply Voltages                            | 9-2   |

|        | 9.1.3   | Power-up and Power-down Constraints                  | 9-3   |

| 9.2    | AC Ti   | ming Characteristics                                 | 9-3   |

|        | 9.2.1   | Host Bus Interface Timing                            | 9-5   |

|        | 9.2.2   | DRAM/ROM Bus Timing                                  | 9-6   |

|        |         | CD Interface Timing                                  | 9-11  |

|        |         | Video Bus Timing                                     | 9-14  |

|        |         | Audio Bus Timing                                     | 9-18  |

| 9.3    | Packa   | age Specifications                                   | 9-19  |

|        | 9.3.1   | Pin List                                             | 9-22  |

|        | 9.3.2   | Package Drawings                                     | 9-24  |

| 10 Re  | egiste  | rs                                                   |       |

| 10.1   | CL480   | Register Categories                                  | 10-2  |

|        |         | Direct-access Registers                              | 10-3  |

|        | 10.1.2  | Indirect-access Registers                            | 10-4  |

|        | Host I  | Interface Register                                   | 10-5  |

| 10.3   | Intern  | al CPU Registers                                     | 10-6  |

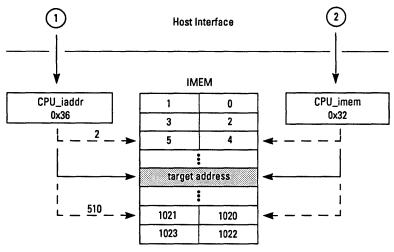

|        | 10.3.1  | CPU Execution Registers                              | 10-6  |

|        | 10.3.2  | IMEM Access Registers                                | 10-6  |

| 10.4   | CD In   | terface Registers                                    | 10-8  |

| 10.5   | DRAN    | / Interface Registers                                | 10-10 |

viii C-Cube Microsystems

| 10.6 | Audio Interface Registers | 10-12 |

|------|---------------------------|-------|

| 10.7 | Video Interface Register  | 10-13 |

# Section III. Software

| 11 M | icrocode Overview                           |       |

|------|---------------------------------------------|-------|

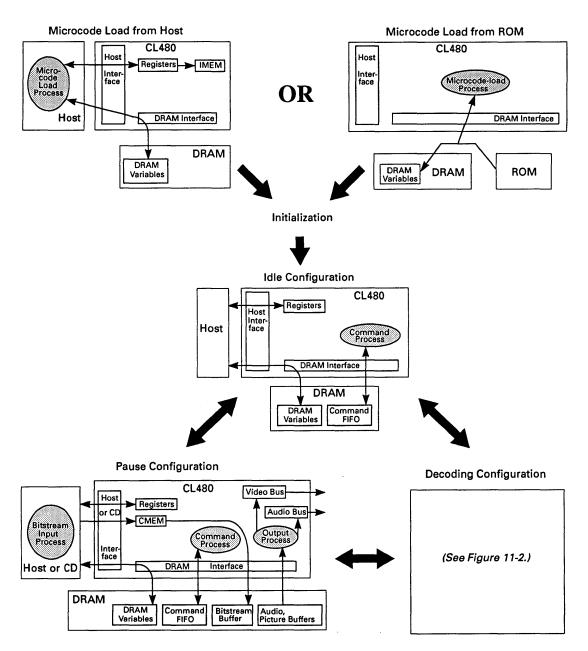

| 11.1 | Process Configurations                      | 11-1  |

|      | 11.1.1 Microcode-Load                       | 11-4  |

|      | 11.1.2 Initialization                       | 11-4  |

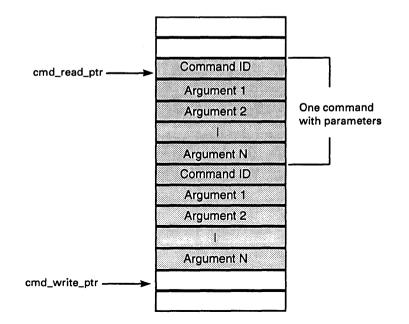

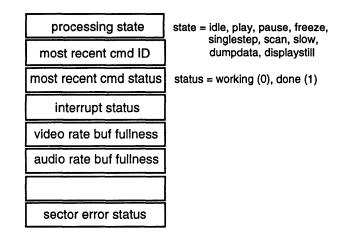

|      | 11.1.3 Command Process                      | 11-5  |

|      | 11.1.4 Bitstream Input Process              | 11-6  |

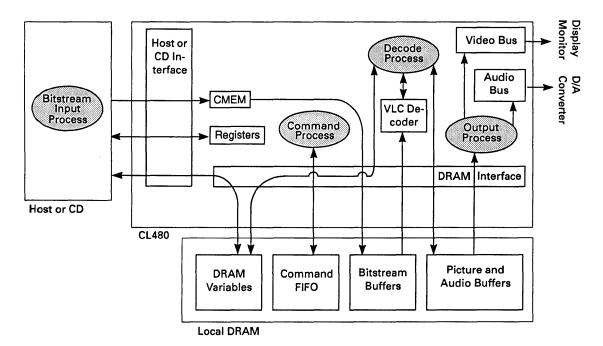

|      | 11.1.5 Decode Process                       | 11-7  |

|      | 11.1.6 Output Process                       | 11-7  |

| 11.2 | Error Handling                              | 11-7  |

| 11.3 | Interrupts                                  | 11-7  |

|      | Starting Operation                          | 11-9  |

| 11.5 | Bitstream Buffer Under- /Overflow           | 11-9  |

| 11.6 | Programmable I/Os                           | 11-10 |

| 11.7 | Fast-Forward and Fast-Reverse               | 11-10 |

| 12 M | lacro Commands                              |       |

| 12.1 | High Priority Commands                      | 12-2  |

| 12.2 | Low Priority Commands                       | 12-2  |

|      | 12.2.1 Command FIFO                         | 12-3  |

|      | 12.2.2 User Data FIFO                       | 12-4  |

| 12.3 | Writing Macro Commands                      | 12-5  |

| 12.4 | Macro Command Groups                        | 12-9  |

|      | 12.4.1 Set-type Commands                    | 12-9  |

|      | 12.4.2 Play-type Commands                   | 12-9  |

|      | 12.4.3 Control Commands                     | 12-9  |

| 12.5 | Macro Command Reference                     | 12-10 |

|      | DisplayStill()                              | 12-11 |

|      | DisplayStill(start1, start2)                | 12-12 |

|      | DisplayStill (start1, start2, stop1, stop2) | 12-13 |

|      | DumpData()                                  | 12-14 |

|      | FlushBitstream()                            | 12-16 |

|      | Freeze()                                    | 12-17 |

|      | InquireBufferFullness()                     | 12-18 |

|      | Pause()                                     | 12-19 |

|      | Play()                                      | 12-20 |

|      | Play(start1, start2, stop1, stop2)          | 12-21 |

| Dee        | a+/\                                   | 10.00 |

|------------|----------------------------------------|-------|

| Res        | et()                                   | 12-23 |

| Sca        | n()                                    | 12-24 |

| Set        | BorderColor()                          | 12-25 |

| Set        | ErrorLevel()                           | 12-26 |

| Setl       | nterruptMask()                         | 12-27 |

| Set        | Mute()                                 | 12-29 |

| Set        | Streams()                              | 12-30 |

| Set\       | /ideoFormat()                          | 12-31 |

| Set\       | Nindow()                               | 12-32 |

| Sing       | leStep()                               | 12-33 |

| Slov       | vMotion()                              | 12-34 |

| A CL480 D  | esign Guidelines                       |       |

| A.1        | Choosing a Microcontroller and Crystal | A-1   |

| <u>۸</u> ۵ | Initialization and ROM                 | ۸2    |

| ~   |                   |     |

|-----|-------------------|-----|

| A.3 | Pull-up/Pull-down | A-2 |

# Figures

| 1-1  | Block Diagram of the CL480                   | 1-4  |

|------|----------------------------------------------|------|

| 1-2  | CL480 in Consumer Electronics Configuration  | 1-6  |

| 2-1  | General MPEG Decoding System                 | 2-3  |

| 2-2  | MPEG Data Hierarchy                          | 2-3  |

| 2-3  | Location of Luminance and Chrominance Values | 2-4  |

| 2-4  | Macroblock Composition                       | 2-5  |

| 2-5  | Forward Prediction                           | 2-6  |

| 2-6  | Bidirectional Prediction                     | 2-7  |

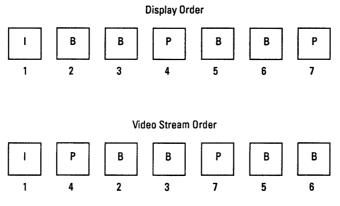

| 2-7  | Typical Display Order of Picture Types       | 2-8  |

| 2-8  | Video Stream versus Display Ordering         | 2-8  |

| 2-9  | Transform Coding Operations                  | 2-11 |

| 2-10 | SCR Flow in MPEG System                      | 2-12 |

| 3-1  | Bus Connection Diagram                       | 3-2  |

| 3-2  | Global Signals                               | 3-2  |

| 3-3  | Host Interface Signals                       | 3-4  |

| 3-4  | CD-Decoder Interface Signals                 | 3-5  |

| 3-5  | DRAM Interface Signals                       | 3-7  |

| 3-6  | Video Interface Signals                      | 3-9  |

| 3-7  | Audio Interface Signals                      | 3-10 |

| 4-1  | CL480 Host Interface                         | 4-1  |

|      |                                              |      |

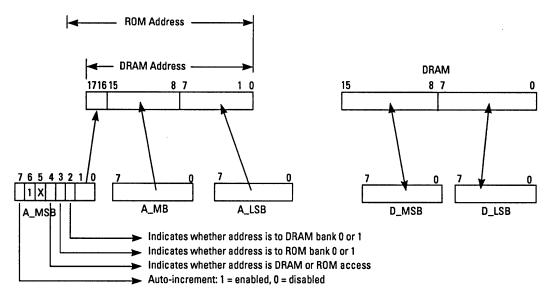

| 4-2 DRAM/ROM Address Formed by Host Address Registers              | 4-4  |

|--------------------------------------------------------------------|------|

| 4-3 Sending Coded Data on CD Interface                             | 4-5  |

| 4-4 Sending Coded data on Host Interface                           | 4-5  |

| 4-5 C-FIFO Register Address Formed by A_MSB                        | 4-6  |

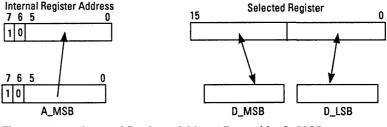

| 4-6 Internal Register Address Formed by A_MSB                      | 4-6  |

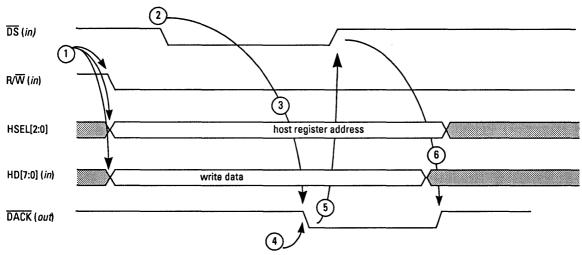

| 4-7 Host Interface Local Register, Write Operation                 | 4-8  |

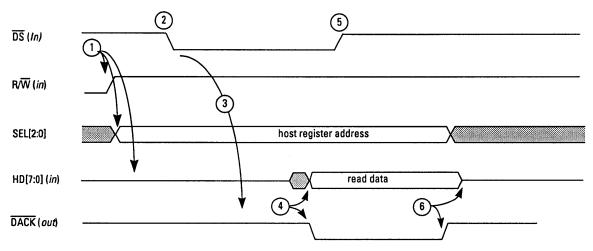

| 4-8 Host Interface Local Register, Read Operation                  | 4-9  |

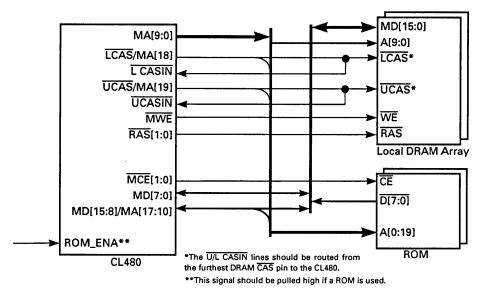

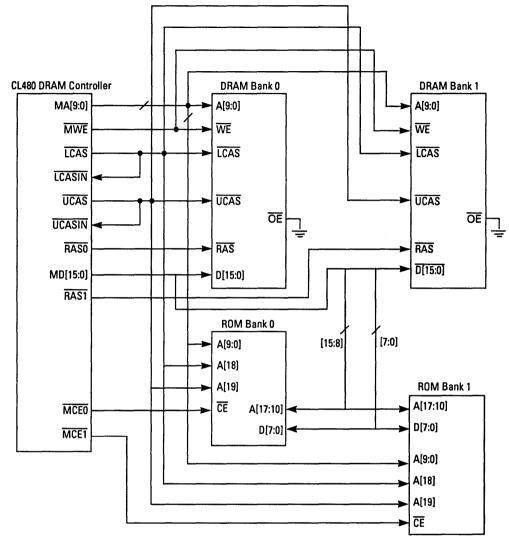

| 5-1 DRAM Interface                                                 | 5-2  |

| 5-2 Local DRAM/ROM Implementation with 256K x 16 DRAMs             | 5-5  |

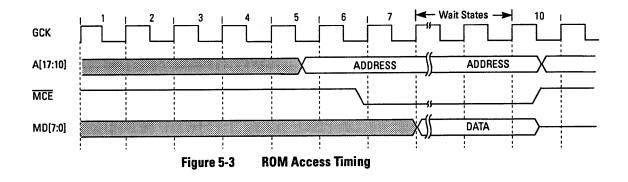

| 5-3 ROM Access Timing                                              | 5-6  |

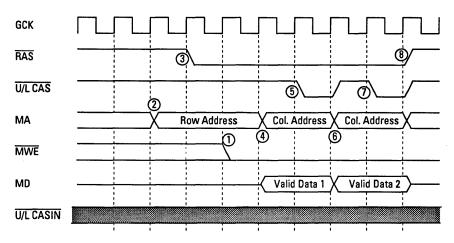

| 5-4 DRAM Page-Mode Read Timing                                     | 5-8  |

| 5-5 DRAM Page-Mode Write Timing                                    | 5-9  |

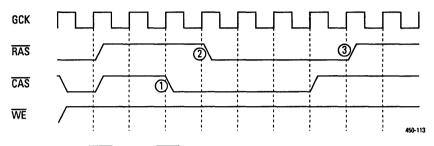

| 5-6 CAS-before-RAS Refresh Cycle                                   | 5-10 |

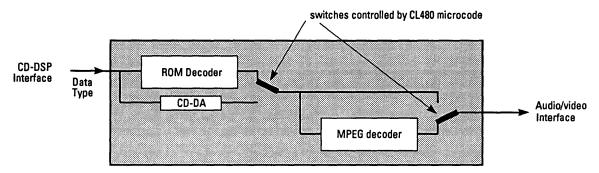

| 6-1 CD-Decoder Interface                                           | 6-1  |

| 6-2 System Block Diagram Showing Bypass of ROM Decoder             |      |

| 7-1 VCK versus HSYNC                                               | 7-4  |

| 7-2 VSYNC/HSYNC/VCK Out Mode                                       | 7-5  |

| 7-3 VSYNC/HSYNC/VCK In                                             | 7-5  |

| 8-1 Audio Interface Block Diagram                                  | 8-1  |

| 8-2 Audio Interface Clocking Modes                                 | 8-4  |

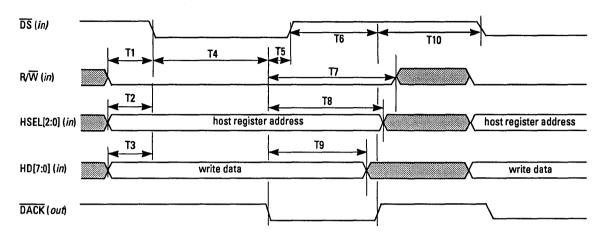

| 9-1 Host Interface Local Register, Write Operation                 | 9-5  |

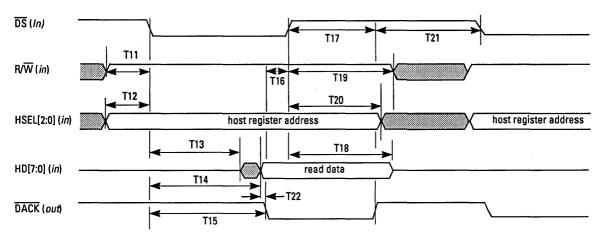

| 9-2 Host Interface Local Register, Read Operation                  | 9-6  |

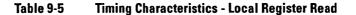

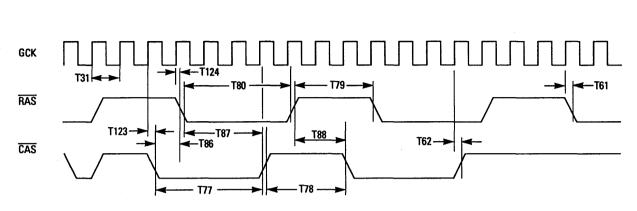

| 9-3 Local DRAM Bus Timing                                          | 9-7  |

| 9-4 Local DRAM CAS-before-RAS Refresh                              | 9-8  |

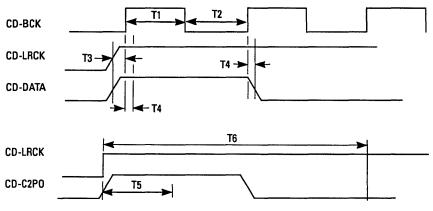

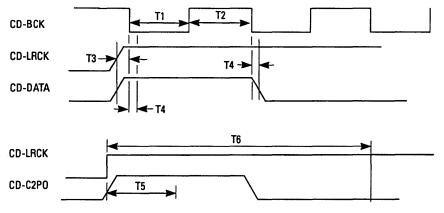

| 9-5 CD Input Timing: 32-bit CD-BCK, Data Latch Timing High         | 9-11 |

| 9-6 CD Input Timing: 32-bit CD-BCK, Data Latch Timing Low          | 9-11 |

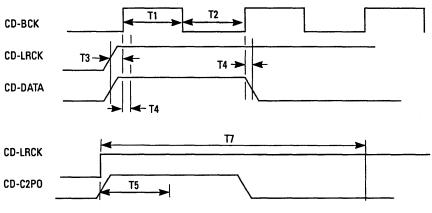

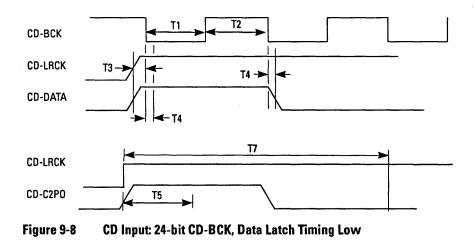

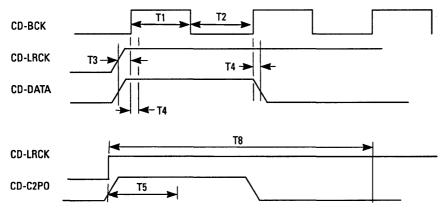

| 9-7 CD Input Timing: 24-bit CD-BCK, Data Latch Timing High         | 9-12 |

| 9-8 CD Input Timing: 24-bit CD-BCK, Data Latch Timing Low          | 9-12 |

| 9-9 CD Input Timing: 16-bit CD-BCK, Data Latch Timing High         | 9-13 |

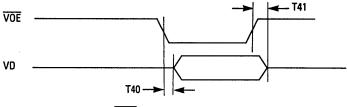

| 9-10 Timing - VOE and VD                                           | 9-14 |

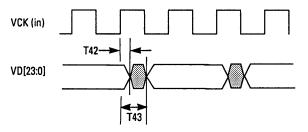

| 9-11 <u>Timing</u> - VCK in at 2 <u>7 MHz a</u> nd VD (pixel data) | 9-14 |

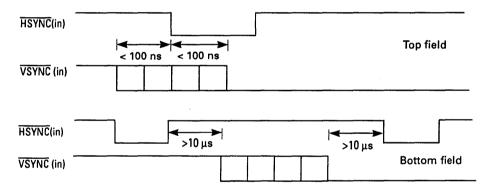

| 9-12 VSYNC Out versus HSYNC Out                                    | 9-15 |

| 9-13 VSYNC In versu <u>s HSYNC</u> In                              | 9-15 |

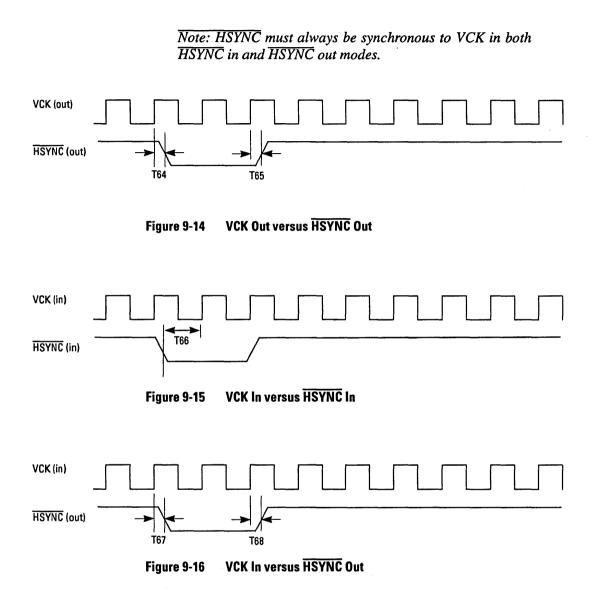

| 9-14 VCK Out versu <u>s HSYNC</u> Out                              | 9-16 |

| 9-15 VCK In versus HSYNC In                                        | 9-16 |

| 9-16 VCK In versus HSYNC Out                                       | 9-16 |

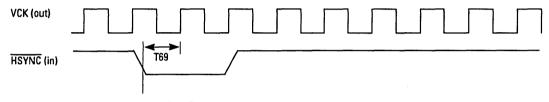

| 9-17 VCK Out versus HSYNC In                                       | 9-17 |

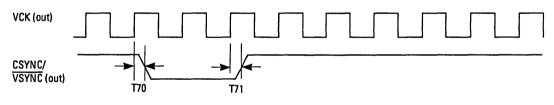

| 9-18 VCK Out versus CSYNC/VSYNC Out                                | 9-17 |

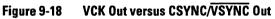

| 9-19 VCK In versus CSYNC/VSYNC Out                                 | 9-17 |

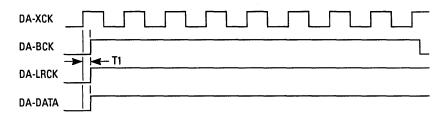

| 9-20 Audio Interface Timing Modes                                  | 9-18 |

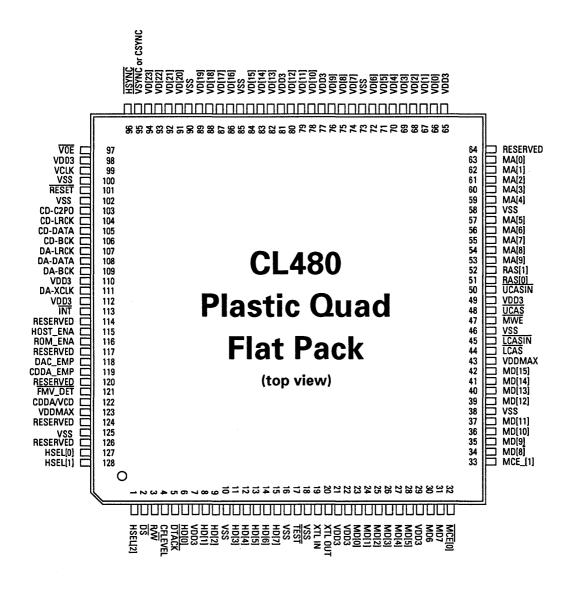

| 9-21 CL480 PQFP Pinout Diagram                                     | 9-20 |

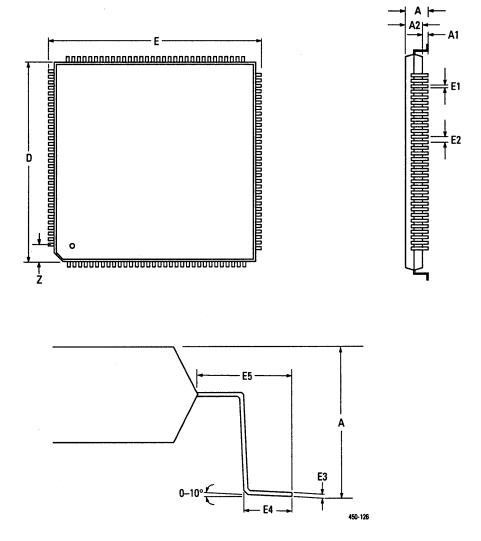

| 9-22 Plastic Quad Flat Pack Physical Dimensions                    | 9-24 |

|                                                                    |      |

| 10-1 IMEM Write Data Flow                             | 10-7  |

|-------------------------------------------------------|-------|

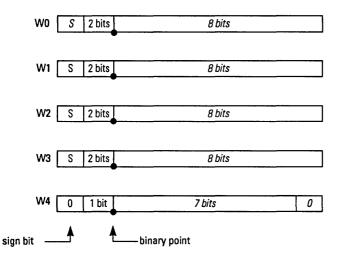

| 10-2 Binary Representation of Conversion Coefficients | 10-17 |

| 11-1 CL480 Microcode Process Configurations           | 11-2  |

| 11-2 CL480 Decoding Process Configuration             | 11-3  |

| 11-3 Mask Bit Allocation                              | 11-8  |

xiv C-Cube Microsystems

# **Tables**

| 4-1  | Register Address Bits Used to Access DRAM, C-FIFO, and GBUS | 4-2  |

|------|-------------------------------------------------------------|------|

| 4-2  | Summary of Host Interface Local Registers                   | 4-3  |

| 4-3  | Memory Address Map                                          | 4-4  |

| 4-4  | Internal Registers Decoded by A_MSB                         | 4-7  |

| 5-1  | DRAM Address Mapping                                        | 5-4  |

| 6-1  | BCK/Data Rate/LRCK Comparison for the CD-Decoder            | 6-3  |

| 7-1  | VD[23:0] Pin Assignments for RGB and YCbCr Data             | 7-3  |

| 8-1  | Audio Interface Signals                                     | 8-2  |

| 8-2  | Audio Attenuation Based on SetMute() or HOST_ENA=0          | 8-2  |

| 8-3  | Relationship between XCK, BCK and LRCK for 44.1 KHz         | 8-4  |

| 9-1  | Absolute Maximum Ratings                                    | 9-1  |

| 9-2  | Operating Conditions                                        | 9-2  |

| 9-3  | DC Characteristics                                          | 9-2  |

| 9-4  | Timing Characteristics - Local Register Write               | 9-5  |

| 9-5  | Timing Characteristics - Local Register Read                | 9-6  |

| 9-6  | Timing Characteristics - Local DRAM Bus                     | 9-9  |

| 9-7  | CD Input Timing                                             | 9-13 |

| 9-8  | Timing Characteristics: VOE and VD                          | 9-14 |

| 9-9  | Timing Characteristics: VCK and VD                          | 9-14 |

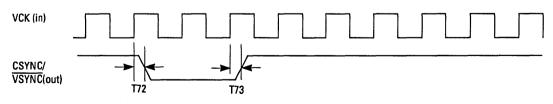

| 9-10 | Timing Characteristics: VCK, HSYNC, and CSYNC/VSYNC         | 9-17 |

| 9-11 | Timing Characteristics: VCK, HSYNC, and CSYNC/VSYNC         | 9-18 |

|      |                                                             |      |

| 9-12Timing Characteristics: Audio               | 9-19  |

|-------------------------------------------------|-------|

| 9-13 Host Bus Interface Pins                    | 9-21  |

| 9-14 CD Interface Pins                          | 9-21  |

| 9-15 Global Interface Pins                      | 9-21  |

| 9-16 DRAM/ROM Bus Interface Pins                | 9-22  |

| 9-17 Audio Bus Interface Pins                   | 9-22  |

| 9-18 Video Bus Interface Pins                   | 9-23  |

| 9-19 Power and Miscellaneous Pins               | 9-23  |

| 9-20 Plastic Quad Flat Pack Physical Dimensions | 9-25  |

| 10-1 CL480 Registers (listed by category)       | 10-2  |

| 10-2 Direct-access Registers                    | 10-3  |

| 10-3 Indirect-access Registers                  | 10-4  |

| 10-4 CD_cntl Register Bit Selection             | 10-8  |

| 10-5 CD_cnfg Register Bit Selection             | 10-9  |

| 10-6 DRAM_iaddr Register IDs                    | 10-10 |

| 10-7 Video Register IDs                         | 10-14 |

| 11-1 Macro Command Summary                      | 11-5  |

| 11-2 CL480 Interrupt Summary                    | 11-8  |

| 12-1 Macro Command Summary                      | 12-10 |

| 12-2 Mask Bit Assignments                       | 12-28 |

| 12-3 Audio Attenuation Based on SetMute()       | 12-29 |

|                                                 |       |

# Chapter 1 Introduction

The CL480 is an MPEG-1 audio/video decoder and the first member of C-Cube's PlayCD<sup>™</sup> family. Designed for consumer electronics products and multimedia PCs, the CL480 reduces system cost by requiring only 4Mbits of DRAM, providing CD-ROM decoding, and providing a serial CD interface. The CL480 reduces development time and effort by performing system stream processing and audio/video synchronization. The CL480 provides high-quality output through its advanced video post-processing, sophisticated error concealment and support for highresolution still pictures. The chip is particularly well suited for video CD players because it provides glueless interfaces to the CD-DSP, audio DAC and NTSC/PAL encoder.

The CL480 processes:

- CD-ROM data, CD-DA data, and constrained-parameters MPEG-1 video bitstreams (typically SIF-resolution) in real time.

- □ MPEG audio (Layer I or II) bitstreams.

The CL480 also features an extensive microcode set supplied with the hardware.

1.1 PlayCD Family

# 1.2 CL480 Features

The CL480 has these key features:

- Integrates on one chip: MPEG audio and video decoding, video timing generation, and CD-ROM decoding functions

- Fully supports Video CD 2.0 and 1.1, Karaoke CD 1.0 and CD-I Green Book<sup>1</sup>

- Accepts MPEG-1 system streams or CD data streams with no external parsing required

- Decodes and synchronizes SIF-resolution MPEG video and two channels of MPEG Layer 1 or 2 audio

- Resolutions include 352x240 at 30 Hz, 352x288 at 25 Hz, and 384x240 at 24 Hz

- □ Audio sample rates include 32, 44.1 and 48 kHz

- Decodes still images with coded resolutions up to 704x576 while decoding MPEG audio

- □ Requires only 4 Mbits of DRAM, even for PAL systems

- Accepts compressed data from 4-pin CD interface or from 8-bit host interface

- Glueless interfaces to CD-DSP, DRAM, ROM, audio DACs, and NTSC/PAL encoder

## 1.2.1 Flexible Video Interface with High-Quality Video Output

- Interpolates two different fields from each decoded frame to reduce flicker and improve image quality on interlaced displays

- Performs frame-rate conversion so that display rate (typically 50 or 60 Hz) is independent of coded frame rate (typically 24, 25 or 30 Hz)

- Performs horizontal interpolation of decoded video using a seventap filter

- Provides RGB or YCbCr video output using on-chip color space converter

- □ Supports HSYNC and VSYNC as inputs or outputs

<sup>1.</sup> The CL480 can implement CD-I but does not have all of the required microcode. To work in the current type of CD-I systems, the CL480 requires a glue chip between its host interface and a 68000.

- Supports VCK input or generates VCK output by dividing GCK (40.5 MHz) by 3/2

- □ Optionally generates NTSC and PAL composite sync

### 1.2.2 Low Voltage, Low Power Operation in Small Package

- □ Operates with a supply voltage of 2.7 to 3.6 volts

- □ Can accept 5-volt inputs

- Consumes less than 1 watt when decoding audio and video

- Automatically divides GCK by 4, 8, or 16 to reduce power when decoding MPEG audio only or when in CD-DA pass-through mode

- □ Packaged in a 128-pin small-outline PQFP (18mm x 18mm body)

### 1.2.3 Powerful, Easy-to-Use Microcode

- Performs audio/video synchronization

- D Provides high-quality error concealment for bitstream errors

- Performs error correction of CD-ROM data at 2.8 Mbps when not decoding MPEG

- □ Supports low-cost systems with no host processor

- □ Can initialize itself from ROM connected to the DRAM interface

- □ Provides high-level macro commands, allowing the host to monitor and control the input, decode and output processes:

- Play Decodes and displays at normal rate

- □ SlowMotion Decodes and displays at slower rate

- □ SingleStep Decodes and displays next picture

- □ Scan Decodes and displays next I-picture

- DisplayStill Decodes and displays high-resolution still picture with audio

- □ Pause Freezes display and decoding process

- □ Freeze Freezes display but continues decoding

- DumpData Performs error correction on CD-ROM data

- □ SetStreams Selects which streams to decode

- □ SetWindow Sets video window size and location

- SetBorderColor Sets border color

- □ SetErrorLevel Sets error level for DisplayStill

### SetMute - Sets audio mute and attenuation

- □ SetVideoFormat Sets format to NTSC, PAL or progressive

- SetInterruptMask Enables/disables interrupts to host

- FlushBitstream Discards contents of bitstream buffer

- □ InquireBufferFullness Measures data in bitstream buffers

- Reset Initializes the CL480 and its microcode

- Provides 13 interrupts, providing the host feedback on bitstream transition, display, and decoding processes

## 1.3 Functional Description

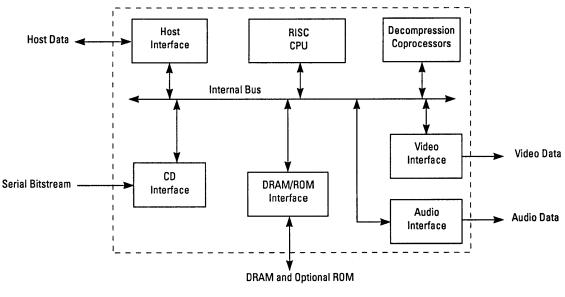

The CL480 decodes audio and video using a combination of hardwired coprocessors and a programmable RISC CPU, as shown in Figure 1-1. The coprocessors contain special-purpose logic to efficiently perform operations such as Huffman decoding. The RISC CPU is a general-purpose processor that controls the coprocessors and assists in the decoding process.

The microcode for the CPU is stored in DRAM and is loaded into onchip memory as needed. During power-up, the microcode can either be loaded into DRAM by a host processor or can be read from a ROM connected to the CL480.

Figure 1-1 Block Diagram of the CL480

Each of the interface modules is described next.

#### 1.3.1 Host Interface

The CL480's host interface is used to initialize the chip, supply compressed data, report status, and control operation. The CL480's host interface is based on an 8-bit bus tailored for low-cost applications; it minimizes pins while allowing the host to access DRAM, the code FIFO, and on-chip registers. These accesses are performed by writing the selected address to a series of three one-byte host address registers. Data is then read from or written to two one-byte data registers.

#### 1.3.2 CD Interface

This interface is designed to receive serial compressed data from a CD-DSP. The CL480 supports six different input formats so that many of the popular CD-DSP chips can be used.

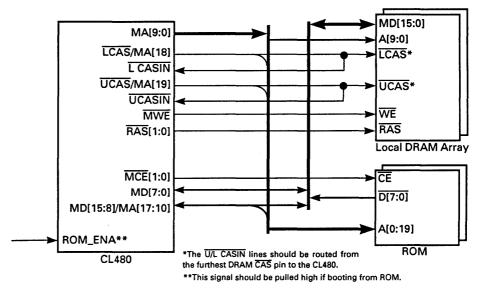

#### 1.3.3 DRAM/ROM Interface

The CL480's DRAM/ROM interface provides a glueless interface between the CL480 and external memory. It connects directly to fast pagemode DRAM, typically either one 256Kx16 DRAM or four 256Kx4 DRAMs. It can also be connected directly to an 8-bit ROM. The ROM access time can be programmed to be 3 to 34 GCKs. The ROM size required for storing the CL480's MPEG microcode is less than 45 Kbytes.

#### 1.3.4 Video Interface

The video interface performs horizontal and vertical interpolation of decoded video. It accepts decompressed video data from the local DRAM and outputs it in:

- □ 24- or 15-bit RGB mode (formatted as BGR-BGR)

- □ 16-bit YCbCr mode (formatted as CbY-CrY)

- □ 8-bit YCbCr mode (formatted as Cb-Y-Cr-Y)

In YCbCr mode, pixels are output in 4:2:2 format, meaning luminance (Y) has twice the horizontal resolution of chrominance (Cb and Cr).

#### 1.3.5 Audio Interface

The CL480 audio interface outputs decoded audio samples in bit-serial format and is able to control their attenuation. The CL480 also has a left/ right signal to indicate which channel is being output. The polarity of the left/right signal and the order and number of bits per audio sample are programmable so that any of the popular audio DACs can be used.

## 1.4 Consumer Electronics Application

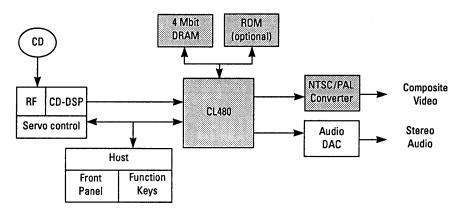

The CL480 is designed for low-cost applications that include the consumer electronics market. In consumer electronics products, such as the example shown in Figure 1-2, the CL480 typically receives a CD data stream from a CD-DSP chip via its 4-pin CD interface. This CD data stream could contain an MPEG-1 system stream, CD-DA data or CD-ROM data.

= Additional components needed to make Video CD player from Audio CD player

### Figure 1-2 CL480 in Consumer Electronics Configuration

# Chapter 2 MPEG Overview

This chapter presents an overview of the Moving Picture Experts Group (MPEG) standard that is implemented by the CL480. The standard is officially known as ISO/IEC Standard, *Coded Representation of Picture*, *Audio and Multimedia/hypermedia Information*, ISO 11172. It is more commonly referred to as the *MPEG-1 standard*.<sup>1</sup>

MPEG addresses the compression, decompression and synchronization of video and audio signals. The MPEG video algorithm can compress video signals to an average of about 1/2 to 1 bit per coded pixel. At a compressed data rate of 1.2 Mbits per second, a coded resolution of 352 x 240 at 30 Hz is often used, and the resulting video quality is comparable to VHS. Image quality can be significantly improved by using a more highly-compressed data rate (for example, 2 Mbits per second) without changing the coded resolution.

<sup>1.</sup> For documentation, contact the American National Standards Institute (ANSI), 11 West 42nd St., New York, NY 10036, (212) 642-4900.

## 2.1 MPEG Stream Structure

This section explains the structure of an MPEG system stream and introduces some concepts used in the rest of the chapter.

### 2.1.1 MPEG System Stream Structure

In its most general form, an MPEG system stream is made up of two layers:

- □ The system layer contains timing and other information needed to demultiplex the audio and video streams and to synchronize audio and video during playback.

- □ The *compression layer* includes the audio and video streams.

#### 2.1.2 General Decoding Process

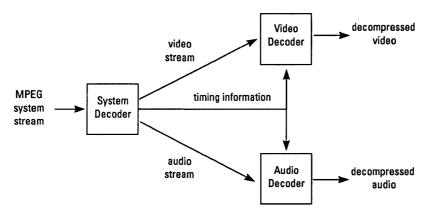

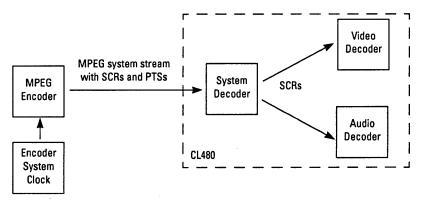

Figure 2-1 shows a generalized decoding system for the audio and video streams.

The system decoder extracts the timing information from the MPEG system stream and sends it to the other system components. (Section 2.4, Synchronization, has more information about the use of timing information for audio and video synchronization.) The system decoder also demultiplexes the video and audio streams from the system stream, and sends each to the appropriate decoder.

The *video decoder* decompresses the video stream as specified in Part 2 of the MPEG standard. (See Section 2.2, Inter-picture Coding, and Section 2.3, Intra-picture Coding, for more information about video compression.)

The *audio decoder* decompresses the audio stream as specified in Part 3 of the MPEG standard.

Figure 2-1 General MPEG Decoding System

### 2.1.3 Video Stream Data Hierarchy

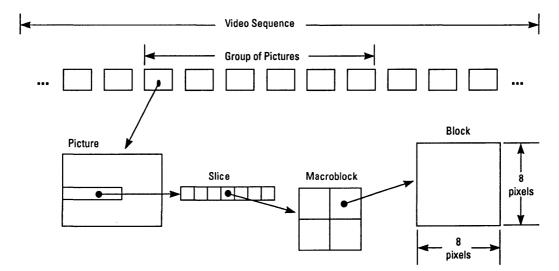

The MPEG standard defines a hierarchy of data structures in the video stream as shown schematically in Figure 2-2.

#### Video Sequence

Begins with a sequence header (may contain additional sequence headers), includes one or more groups of pictures, and ends with an end-ofsequence code.

#### Group of Pictures

A header and a series of one or more pictures intended to allow random access into the sequence.

#### Picture

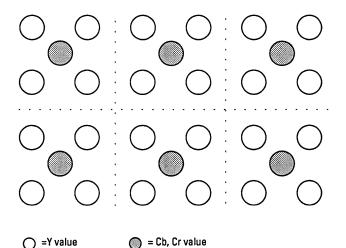

The primary coding unit of a video sequence. A picture consists of three rectangular matrices representing luminance (Y) and two chrominance (Cb and Cr) values. The Y matrix has an even number of rows and columns. The Cb and Cr matrices are one-half the size of the Y matrix in each direction (horizontal and vertical).

Figure 2-3 shows the relative x-y locations of the luminance and chrominance components. Note that for every four luminance values, there are two associated chrominance values: one Cb value and one Cr value. (The location of the Cb and Cr values is the same, so only one circle is shown in the figure.)

#### 2-4 C-Cube Microsystems

Slice

One or more "contiguous" macroblocks. The order of the macroblocks within a slice is from left to right and top to bottom.

Slices are important in the handling of errors. If the bitstream contains an error, the decoder can skip to the start of the next slice. Having more slices in the bitstream allows better error concealment but uses bits that could otherwise be used to improve picture quality.

## Macroblock

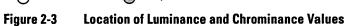

A 16-pixel by 16-line section of luminance components and the corresponding 8-pixel by 8-line section of the two chrominance components. See Figure 2-3 for the spatial location of luminance and chrominance components. A macroblock contains four Y blocks, one Cb block and one Cr block as shown in Figure 2-4. The numbers correspond to the ordering of the blocks in the data stream, with block 1 first.

Figure 2-4 Macroblock Composition

### Block

A block is an 8-pixel by 8-line set of values of a luminance or a chrominance component. Note that a luminance block corresponds to onefourth as large a portion of the displayed image as does a chrominance block.

# 2.2 Inter-picture Coding

Much of the information in a picture within a video sequence is similar to information in a previous or subsequent picture. The MPEG standard takes advantage of this temporal redundancy by representing some pictures in terms of their differences from other (reference) pictures, or what is known as *inter-picture coding*. This section describes the types of coded pictures and explains the techniques used in this process.

## 2.2.1 Picture Types

The MPEG standard specifically defines three types of pictures: intra, predicted, and bidirectional.

### Intra Pictures

Intra pictures, or I-pictures, are coded using only information present in the picture itself. I-pictures provide potential random access points into the compressed video data. I-pictures use only transform coding (as explained in section 2.3 on page 10) and provide moderate compression. I-pictures typically use about two bits per coded pixel.

### **Predicted Pictures**

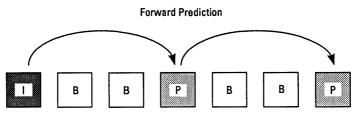

Predicted pictures, or P-pictures, are coded with respect to the nearest previous I- or P-picture. This technique is called *forward prediction* and is illustrated in Figure 2-5.

Like I-pictures, P-pictures serve as a prediction reference for B-pictures and future P-pictures. However, P-pictures use *motion compensation* (see section 2.2.3) to provide more compression than is possible with Ipictures. Unlike I-pictures, P-pictures can propagate coding errors because P-pictures are predicted from previous reference (I- or P-) pictures.

## **Bidirectional Pictures**

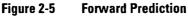

Bidirectional pictures, or B-pictures, are pictures that use both a past and future picture as a reference. This technique is called *bidirectional prediction* and is illustrated in Figure 2-6. B-pictures provide the most compression and do not propagate errors because they are never used as a reference. Bidirectional prediction also decreases the effect of noise by averaging two pictures.

**Bidirectional Prediction**

#### 2.2.2 Video Stream Composition

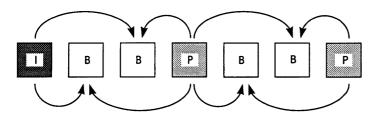

The MPEG algorithm allows the encoder to choose the frequency and location of I-pictures. This choice is based on the application's need for random accessibility and the location of scene cuts in the video sequence. In applications where random access is important, I-pictures are typically used two times a second.

The encoder also chooses the number of B-pictures between any pair of reference (I- or P-) pictures. This choice is based on factors such as the amount of memory in the encoder and the characteristics of the material being coded. For example, a large class of scenes have two bidirectional pictures separating successive reference pictures. A typical arrangement of I-, P-, and B-pictures is shown in Figure 2-7 in the order in which they are displayed.

Figure 2-7 Typical Display Order of Picture Types

The MPEG encoder reorders pictures in the video stream to present the pictures to the decoder in the most efficient sequence. In particular, the reference pictures needed to reconstruct B-pictures are sent *before* the associated B-pictures. Figure 2-8 demonstrates this ordering for the first section of the example shown above.

Figure 2-8 Video Stream versus Display Ordering

#### 2.2.3 Motion Compensation

*Motion compensation* is a technique for enhancing the compression of P- and B-pictures by eliminating temporal redundancy. Motion compensation typically improves compression by about a factor of three compared to intra-picture coding. Motion compensation algorithms work at the macroblock level.

When a macroblock is compressed by motion compensation, the compressed file contains this information:

- □ The spatial vector between the reference macroblock(s) and the macroblock being coded (*motion vectors*)

- □ The content differences between the reference macroblock(s) and the macroblock being coded (*error terms*)

Not all information in a picture can be predicted from a previous picture. Consider a scene in which a door opens: The visual details of the room behind the door cannot be predicted from a previous frame in which the door was closed. When a case such as this arises—i.e., a macroblock in a P-picture cannot be efficiently represented by motion compensation—it is coded in the same way as a macroblock in an I-picture using transform coding techniques (see Section 2.3, Intra-picture Coding).

The difference between B- and P-picture motion compensation is that macroblocks in a P-picture use the previous reference (I- or P-picture) only, while macroblocks in a B-picture are coded using any combination of a previous or future reference picture.

Four codings are therefore possible for each macroblock in a B-picture:

- □ Intra coding: no motion compensation

- Forward prediction: the previous reference picture is used as a reference

- □ Backward prediction: the next picture is used as a reference

- Bidirectional prediction: two reference pictures are used, the previous reference picture and the next reference picture

Backward prediction can be used to predict uncovered areas that do not appear in previous pictures.

## 2.3 Intra-picture (Transform) Coding

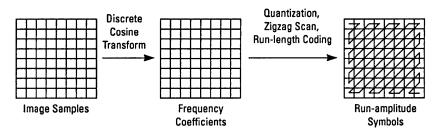

The MPEG transform coding algorithm includes these steps:

- □ Discrete cosine transform (DCT)

- Quantization

- □ Run-length encoding

Both image blocks and prediction-error blocks have high spatial redundancy. To reduce this redundancy, the MPEG algorithm transforms  $8 \times 8$  blocks of pixels or  $8 \times 8$  blocks of error terms from the spatial domain to the frequency domain with the Discrete Cosine Transform (DCT).

Next, the algorithm quantizes the frequency coefficients. Quantization is the process of approximating each frequency coefficient as one of a limited number of allowed values. The encoder chooses a quantization matrix that determines how each frequency coefficient in the 8 x 8 block is quantized. Human perception of quantization error is lower for high spatial frequencies, so high frequencies are typically quantized more coarsely (i.e., with fewer allowed values) than low frequencies.

The combination of DCT and quantization results in many of the frequency coefficients being zero, especially the coefficients for high spatial frequencies. To take maximum advantage of this, the coefficients are organized in a zigzag order to produce long runs of zeros (see Figure 2-9). The coefficients are then converted to a series of run-amplitude pairs, each pair indicating a number of zero coefficients and the amplitude of a non-zero coefficient. These run-amplitude pairs are then coded with a variable-length code, which uses shorter codes for commonly occurring pairs and longer codes for less common pairs.

Some blocks of pixels need to be coded more accurately than others. For example, blocks with smooth intensity gradients need accurate coding to avoid visible block boundaries. To deal with this inequality between blocks, the MPEG algorithm allows the amount of quantization to be modified for each macroblock of pixels. This mechanism can also be used to provide smooth adaptation to a particular bit rate.

Figure 2-9 Transform Coding Operations

The MPEG standard provides a timing mechanism that ensures synchronization of audio and video. The standard includes two parameters: the system clock reference (SCR) and the presentation time stamp (PTS).

The MPEG-specified "system clock" runs at 90 kHz. System clock reference and presentation time stamp values are coded in MPEG bitstreams using 33 bits, which can represent any clock cycle in a 24-hour period.

### 2.4.1 System Clock References

A system clock reference is a snapshot of the encoder system clock which is placed into the system layer of the bitstream, as shown in Figure 2-10. During decoding, these values are used to update the system clock counter in the CL480.

Figure 2-10 SCR Flow in MPEG System

# 2.4 Synchronization

#### 2.4.2 Presentation Time Stamps

Presentation time stamps are samples of the encoder system clock that are associated with video or audio *presentation units*. A presentation unit is a decoded video picture or a decoded audio time sequence. The PTS represents the time at which the video picture is to be displayed or the starting playback time for the audio time sequence.

The decoder either skips or repeats picture displays to ensure that the PTS is within one picture's worth of 90 kHz clock tics of the SCR when a picture is displayed. If the PTS is earlier (has a smaller value) than the current SCR, the decoder discards the picture. If the PTS is later (has a larger value) than the current SCR, the decoder repeats the display of the picture.

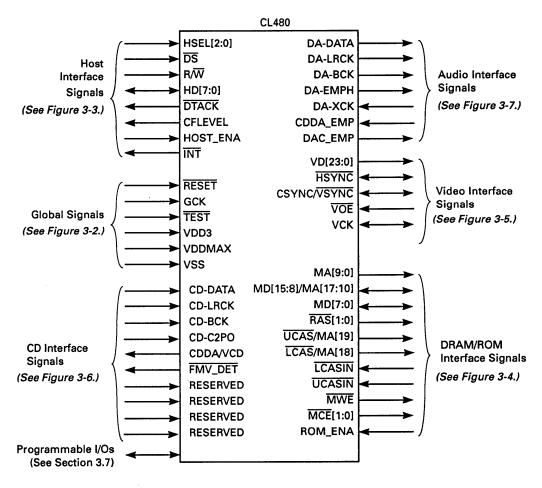

# Chapter 3 Signal Descriptions

This chapter describes the signals that comprise the external physical interface to the CL480. The information presented for each signal includes the signal mnemonic and name, type (input, output, or bidirectional), and description. (Note: The overbar symbol denotes active low polarity.) For information about the functional operation of the CL480, including functional and timing waveforms, see Chapters 4, 5, 6, 7 and 8.

This chapter is divided into the following seven sections that correspond to the components that interface to the CL480:

- □ 3.1: Global Interface

- □ 3.2: Host Interface

- □ 3.3: CD Interface

- □ 3.4: DRAM Interface

- □ 3.5: Video Interface

- □ 3.6: Audio Interface

- □ 3.7: Programmable I/Os

Figure 3-1 shows a diagram of the CL480 with all signals grouped together.

# **Global Interface**

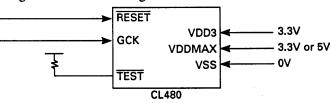

The CL480 global signals are composed of the  $\overline{\text{RESET}}$ , GCK,  $\overline{\text{TEST}}$ , and power signals as shown in Figure 3-2.

2 Global Signals

3-2 C-Cube Microsystems

**Global Interface**

3.1

#### **RESET** — Hardware Reset

Input

An external device asserts  $\overline{\text{RESET}}$  (active low) to force the CL480 to execute a hardware reset. To be recognized,  $\overline{\text{RESET}}$  must be asserted for at least ten complete GCK cycles. After a reset, the CL480 registers are in an indeterminate state, and the microcode should be reloaded as described in Chapter 11.

#### GCK — Global Clock

Input

The CL480 uses GCK to clock the internal processor. This oscillator is typically 40 MHz or 40.5 MHz. The host can write a register to internally divide the clock by 16 (2.5 MHz) to provide a low-power sleep mode.

#### TEST — Test

Input

Input

Input

This pin is used for chip testing. For normal operation,  $\overline{\text{TEST}}$  must be held HIGH (deasserted).

#### VDD3 — Power

2.7 to 3.6V internal power and output high voltage.

#### VSS — Power

Ground.

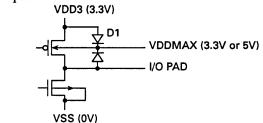

#### VDDMAX — Power

#### Input

Maximum input voltage connected to any CL480 pin. The VD-DMAX pin is connected to the N-well of the P-channel output transistor on I/O pads as shown in the figure below. The voltage of VDDMAX should be greater than or equal to the voltage driven on any input.

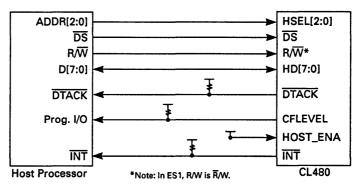

These signals are used to communicate between the CL480 and the host processor. Figure 3-3 shows how the data transfer signals of the CL480 connect to the host processor. The various modes of transferring data are discussed in Sections 4.2 and 4.3.

# 3.2 Host Interface

Figure 3-3 Host Interface Signals

#### HSEL[2:0] — Host Address Bus

#### Inputs

This three-bit address bus selects one of five host interface registers from which other resources within the CL480 may be accessed.

# DS —Data Strobe Input

The host processor asserts  $\overline{DS}$  to select the CL480 for a read or write operation. The falling edge of this signal triggers a new cycle.

# HD[7:0] — Host Data Bus Bidirectionals

HD[7:0] comprises the 8-bit bidirectional host data bus. The host processor uses HD[7:0] to write data to the CL480's Code FIFO, internal registers, and local DRAM. The CL480 uses HD[7:0] to send requested data to the host processor. The direction is determined by  $R/\overline{W}$  ( $\overline{R}/W$  in ES1).

# R/W — Read/Write

The host processor drives  $R/\overline{W}$  low to initiate a write operation, and drives  $R/\overline{W}$  high to initiate a CL480 read operation to the host data bus. (R/W polarity is reversed in ES1.)

# DTACK — Host Data Acknowledge Open-Drain Output

The CL480 asserts  $\overline{\text{DTACK}}$  (active low) when it is ready to receive or output data on HD[7:0]. When the CL480 responds to a read request, it holds  $\overline{\text{DTACK}}$  deasserted (high) until the requested data is ready. When the CL480 responds to a write request, it asserts  $\overline{\text{DTACK}}$  when it has received and latched the write data.

# Input

**DTACK** is an open-drain signal, which allows it to be wire-ORed with other components on the host bus. It requires a pullup resistor of at least 1.5K ohms.

#### CFLEVEL — Coded Data FIFO Level Status Output

When CFLEVEL is zero, the CL480 Coded Data FIFO has room for at least 44 bytes of compressed data. CFLEVEL is an open-drain signal. This allows it to be wire-ORed with other components on the host bus. It requires a pullup resistor of at least 1.5K ohms.

#### INT — Interrupt Request

#### Output

The CL480 asserts  $\overline{INT}$  to request an interrupt from the host processor. Interrupt events are determined from the SetInterruptMask() macro command. A 1.5K pull-up should be added on this pin.

HOST\_ENA—Host EnableInputEnables the host interface. By disabling HOST\_ENA(HOST\_ENA=0), host interface pins may be used for controlfunctions as described in Section 3.7 and 11.6.

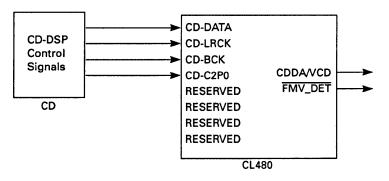

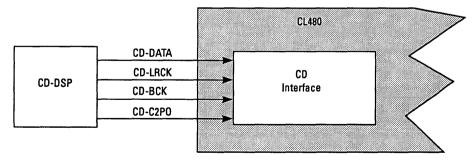

The CL480's CD interface is dedicated to receiving the serial-bit output of a CD DSP. A 4-wire serial bus connects the CD DSP directly with the CL480 as shown in Figure 3-5.

3.3 CD Interface

#### CD-BCK — Bit Clock

Input

BCK is the CD-Decoder bit clock. The CL480 can accept multiple BCK rates as detailed in Table 6-1 of Chapter 6.

#### CD-DATA — Data

Input

Output

The serial data input from the CD-DSP.

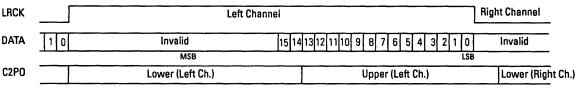

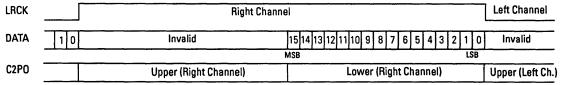

# CD-LRCK — Left-Right Clock Input

CD-LRCK provides 16-bit word synchronization to the CL480 and has programmable polarity (either left or right channel high).

# CD-C2P0 — CD-ROM Data Input

This signals a corrupted byte (error byte flag MSB or LSB first). It is used when receiving CD-ROM data but is ignored in CD-DA pass-through mode. This signal is high when an error occurs.

# CDDA/VCD— CDDA/V-CD Enable Output

Outputs whether incoming data is CDDA versus V-CD: CDDA = 1, V-CD = 0.

FMV\_DET— FMV Detected Output

Indicates a CD-I bitstream. Outputs zero if FMV is detected.

#### RESERVED — RESERVED

These four pins are reserved.

# 3.4 DRAM Interface

Figure 3-4 shows the signals that comprise the CL480's DRAM interface. The signal descriptions are presented following the figure. See Chapter 5 for more information about the DRAM memory architecture.

Figure 3-5 DRAM Interface Signals

#### MA[9:0] — Memory Address Bus

#### Outputs

The CL480 multiplexes the row and column addresses on these signals to address up to one Mbyte of DRAM and uses address bits 9:0 for ROM addresses. See Chapter 5 for details of addressing various DRAM components and DRAM array sizes.

# MD[15:0] — Memory Data Bus Bidirectionals

These signals comprise the memory data bus by which data is transferred between the CL480 and the local DRAM/ROM array. All 16 bits are used in DRAM accesses, the direction of which is determined by the state of  $\overline{\text{MWE}}$ .

For ROM accesses, MDATA[7:0] is the ROM data bus, and MDATA[15:8] becomes ROM address bits [17:10].

# RAS[1:0] — Row Address Strobe Outputs

The CL480 asserts these signals to latch the row address into the DRAM array.  $\overline{RAS1}$  (active low) latches the row address for bank 1, and  $\overline{RAS0}$  (low) latches the row address for bank 0.

# UCASUpper Column Address StrobeOutputLCASLower Column Address StrobeOutput

The CL480 asserts these signals to latch the column address into the DRAM array.  $\overline{\text{UCAS}}$  (active low) latches the column address for the upper memory data byte, MD[15:8], and  $\overline{\text{LCAS}}$ (active low) latches the address for the lower byte, MD[7:0].  $\overline{\text{UCAS}}$  is generated in response to the  $\overline{\text{UDS}}$  input, and  $\overline{\text{LCAS}}$  is generated in response to the  $\overline{\text{LDS}}$  input.

Note: The  $\overline{\text{LCAS}}$  and  $\overline{\text{UCAS}}$  bits are also used as bits A[18] and A[19], respectively, in ROM accesses.

# UCASIN — Upper Data Latch EnableInputsICASIN — Lower Data Latch EnableInputs

When the CL480 reads data from the local DRAM array, the data on MD[15:0] is latched into the CL480 on the rising edge of the two  $\overline{\text{CASIN}}$  signals.  $\overline{\text{UCASIN}}$  latches data coming from the high data byte, MD[15:8], and  $\overline{\text{LCASIN}}$  latches data coming from the low data byte, MD[7:0]. Typically, these are connected to the  $\overline{\text{UCAS}}$  and  $\overline{\text{LCAS}}$  pins, respectively.

# **MWE** — Write Enable

# The CL480 asserts $\overline{\text{MWE}}$ (active low) during write operations (data transfer from CL480 to DRAM). The CL480 leaves $\overline{\text{MWE}}$ high during a read operation (DRAM to CL480).

# **MCE**[1:0] —Chip Enable

# Output

Input

Output

The CL480 asserts  $\overline{\text{MCE}}$  (one for each ROM) during a read operation from ROM to the CL480.

# ROM\_ENA—Boot ROM Enable

Enables boot ROM. When this pin is high, the CL480 will initialize itself with the data in ROM bank 0.

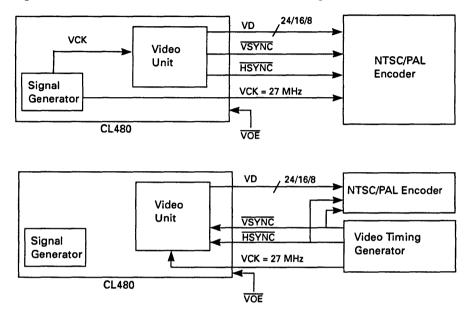

# 3.5 Video Interface

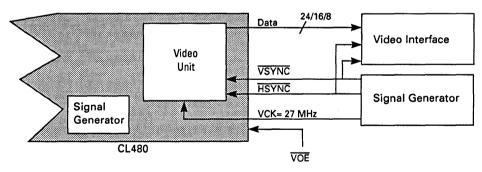

The CL480's video interface outputs pixel data to the video display subsystem in RGB or YCbCr format. Figure 3-5 shows two possible configurations of the signals in the CL480's video interface:  $\overline{VSYNC}/\overline{HSYNC}/VCK$  as outputs, and  $\overline{VSYNC}/\overline{HSYNC}/VCK$  as inputs. Note: depending on the video mode selected—RGB-24, YCb-Cr-16, and YCbCr-8—the pin count of the video interface varies, respectively, from 28, to 20, to 12 pins.

Operation of the video interface is discussed in Chapter 7.

Figure 3-6 Video Interface Signals

VD[23:0] — Pixel Data Bus

Outputs

The CL480 transmits pixel data to the video display subsystem using these signals. The definition of the signal lines differs for RGB and YCbCr formats as explained in Chapter 7.

# **HSYNC** — Horizontal Synchronization Bidirectional

The CL480 begins outputting pixel data for a new horizontal line after the rising (inactive) edge of  $\overline{\text{HSYNC}}$ .  $\overline{\text{HSYNC}}$  must be synchronous to VCK as shown in Chapter 7.

# **VSYNC** — Vertical Synchronization Bidirectional

The CL480 begins outputting the top border of a new field on the first  $\overline{\text{HSYNC}}$  after the rising edge of  $\overline{\text{VSYNC}}$ .  $\overline{\text{VSYNC}}$  can be asynchronous with respect to VCK. See Chapter 7 for more information on the relationship of  $\overline{\text{VSYNC}}$  to  $\overline{\text{HSYNC}}$ .

# **VOE** — Video Output Enable

Input

$\overline{\text{VOE}}$  must be asserted (active low) to enable the CL480 to drive the pixel bus, PD[23:0]. When  $\overline{\text{VOE}}$  is deasserted, the CL480 puts the pixel bus in a high-impedance state (Note: This signal is active high in ES1).

# VCK — Video Clock

#### Bidirectional

VCK is derived from GCK and can be either an input or an output signal (which is independent of the direction of  $\overrightarrow{VSYNC}$  and  $\overrightarrow{HSYNC}$ ). VCK does not need to be synchronous with GCK.

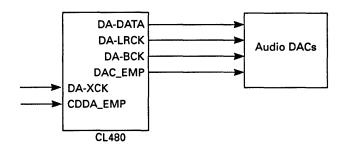

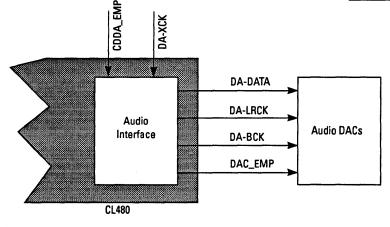

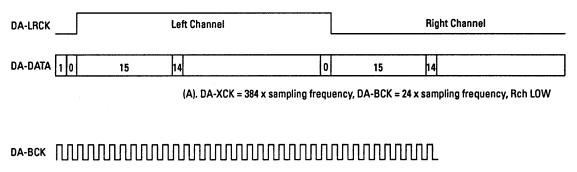

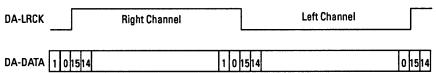

3.6 Audio Interface BCK, DA-DATA, DA-LRCK) audio output. It also takes as input two external sources, DA-XCK and CDDA\_EMP, and outputs DAC\_EMP.

DA-DATA — Data Output

This signal outputs bit serial audio samples based on the DA-BCK clock.

# DA-LRCK — Left-Right Clock Output

This signal identifies the channel for each audio sample.

# DA-BCK — Bit Clock Output

DA-BCK is the audio bit clock. Divided by 8 from DA-XCK, it can be either 48 or 32 times the sampling clock.

DAC\_EMP - Output Emphasis Flag Output In CD-DA pass-through mode, this signal is routed to the audio DACs.

DA-XCK — External Audio Frequency Clock Input Used to generate DA-BCK and DA-LRCK, DA-XCK can be ei-

ther 384 or 256 times the sampling frequency.

CDDA\_EMP — Input Emphasis FlagInputIn CD-DA pass-through mode, this imput is directly routed to<br/>the DAC\_EMP output pin.In compare the part of the part of

The CL480 provides programmable I/Os that may be used for control. These I/Os become available by disabling the host interface (HOST\_ENA=0) so that host interface pins may be used for control functions as shown in the following tables.

3.7 Programmable I/Os

| Pin Name | Name/Function                  | 1/0 |

|----------|--------------------------------|-----|

| HSEL[0]  | STOP/PLAY: 1 = Pause, 0 = Play | 1   |

| HSEL[1]  | SCAN: 1 = Scan                 | - 1 |

Note: In the table below, HD[0] and HD[1] perform the same functions normally set by SetMute().

| HD[0] (MUTEO) | HD[1] (MUTE1) | Attenuation on the PCM Samples |

|---------------|---------------|--------------------------------|

| 0             | 0             | 0 dB                           |

| 1             | 0             | -12 dB                         |

| 0             | 1             | -∞ (20 ms soft mute)           |

| 1             | 1             | -12 dB                         |

Programmable I/Os

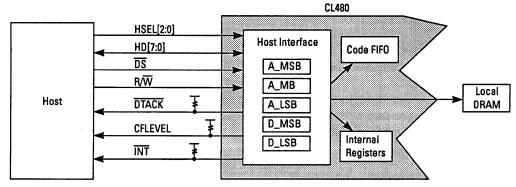

# 4 Host Interface Functional Description

4.1

**Functional**

**Overview**

The CL480's host interface, shown in Figure 4-1, is intended to provide a simple interface to an eight-bit microcontroller. The host interface provides three distinct functions:

Coded data input (coded data may be sent through the host interface if the CD interface is not used for this purpose)

- □ Local DRAM/ROM access

- □ Internal register access

Figure 4-1 CL480 Host Interface

The host communication functions also include device initialization and microcode loading (if the ROM is not used). Host accesses to the CL480 can be asynchronous to GCK.

# 4.2 Host Interface Registers

As shown in Figure 4-1, the host processor accesses CL480 resources by writing to address registers and reading or writing to data registers. A combination of five host interface registers are used:

- □ Three 8-bit address registers: A\_MSB, A\_MB, A\_LSB

- □ Two 8-bit data registers: D\_LSB and D\_MSB

# 4.2.1 Host Interface Address Registers

The CL480's address registers allow the host to access the CL480's C-FIFO, local DRAM array or internal GBUS registers by setting A\_MSB[7:6], as shown in Table 4-1.

# Table 4-1 Register Address Bits Used to Access DRAM/ROM, C-FIFO, and GBUS

| A_MSB[7:6] | Data From/To                |

|------------|-----------------------------|

| 00         | C-FIFO                      |

| 01         | DRAM/ROM (No autoincrement) |

| 10         | GBUS                        |

| 11         | DRAM/ROM (Autoincrement)    |

Thus the address register specifies which of four types of operations the CL480 can perform:

- □ Write to Code FIFO

- □ Read/write to GBUS (internal registers)

- □ Read/write to DRAM (external memory)

- Read/write to DRAM (external memory) with auto-increment addressing

# 4.2.2 Host Interface Data Registers

The two host 8-bit data registers, D\_LSB and D\_MSB, are buffers between the host bus and internal modules. Transfers from the data registers to the destination specified by the address registers are triggered on the write operation to D\_MSB and the read operation from D\_MSB. Therefore, the write and read sequences are as follows:

- □ Write:

- Set address registers

- Write D\_LSB register

- Write D\_MSB register

- $\square$  Read:

- □ Set address registers

- Read D\_MSB register

- □ Read D\_LSB register

Note: For back-to-back transactions to the C-FIFO, DRAM and internal registers, only the address bytes that differ from earlier transaction(s) need to be re-written a second time.

# 4.2.3 Accessing Host Interface Registers

The host accesses each of the five host interface registers by issuing a bus access with HSEL[2:0] set appropriately, as shown in Table 4-2.

| HSEL[2:0] <sup>1</sup> | Register Name | Contents              |

|------------------------|---------------|-----------------------|

| 001                    | A_LSB         | Address, byte 0 (LSB) |

| 010                    | A_MB          | Address, byte 1       |

| 011                    | A_MSB         | Address, byte 2(MSB)  |

| 100                    | D_LSB         | Data, byte 0 (LSB)    |

| 101                    | D_MSB         | Data, byte 1 (MSB)    |

Table 4-2

Summary of Host Interface Local Registers

1. Note: 000, 110 and 111 are illegal combinations which should not be used.

# 4.2.4 DRAM/ROM Access

Bit 4 of A\_LSB determines whether DRAM (set to 0) versus ROM (set to 1) is selected.

# **DRAM** Access

When bit 6 of A\_MSB is set to 1, the host sets A\_MSB, A\_MB, and A\_LSB to form a 21-bit memory address as shown in Figure 4-2.

This 21-bit memory address is a 16-bit word address, not a byte address. The address map is shown in Table 4-3.

Table 4-3 Memory Address Map

| A_MSB[4] | A_MSB[3] | A_MSB[2] | Memory Accessed |

|----------|----------|----------|-----------------|

| 1        | 1        | 1        | ROM Bank 1      |

| 1        | 1        | 0        | ROM Bank 1      |

| 1        | 0        | 1        | ROM Bank 0      |

| 1        | 0        | 0        | ROM Bank 0      |

| 0        | 1        | 1        | unused          |

| 0        | 1        | 0        | unused          |

| 0        | 0        | 1        | DRAM Bank 1     |

| 0        | 0        | 0        | DRAM Bank 0     |

# 4-4 C-Cube Microsystems

For DRAM accesses, bit 7 of Host address register A\_MSB controls autoincrementing. When autoincrementing is enabled (bit 7 = 1), each 16-bit data transfer between the host and the CL480 causes the DRAM address to be incremented to the next *word*.

# **ROM Access**

For access of ROM bank 0 versus 1, see Table 4-3.

# 4.2.5 Code FIFO Access

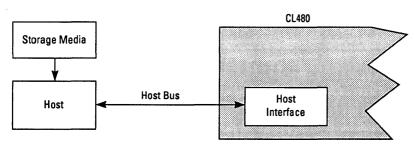

Host bus coded data may be sent to the CL480 in one of two basic modes:

- □ Serial mode (through the CD interface), as shown in Figure 4-3 and described further in Chapter 8.

- □ Parallel mode (through the host interface), as shown in Figure 4-4 and described in this section.

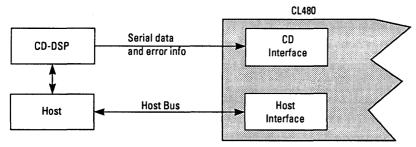

Figure 4-3 Sending Coded Data on CD Interface

Figure 4-4 Sending Coded Data on Host Interface

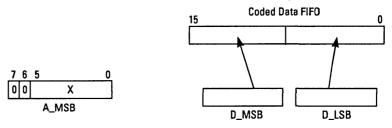

In code FIFO accesses through the Host interface, the Host specifies  $A_MSB[7:6]=00$  as shown in Figure 4-6. Then the words written to D\_MSB and D\_LSB will transfer to the Code FIFO.

Figure 4-5 C-FIFO Register Address Formed by A\_MSB

The CL480 can sustain a coded data input transfer rate of up to 2.5 Mbytes per second through the D\_MSB and D\_LSB registers. The C-FIFO holds 31 words, each of which is 16-bits wide.

#### 4.2.6 Internal Register Access

If the Host specifies A\_MSB[7:6]=10, then the access is an internal register access, as shown in Figure 4-6.

Figure 4-6 Internal Register Address Formed by A\_MSB

Internal registers that are accessible by the host are listed in Table 4-3.

Note: Registers are defaulted to the correct value through microcode initialization unless otherwise noted in the Configuration Area description given in Section 12.3.

| Access                | A_MSB[5:0] | Register Name | R/W | Description                                |

|-----------------------|------------|---------------|-----|--------------------------------------------|

|                       | 0x33       | CPU_cntl      | R/W | Selects type of data sent to the CL480     |

|                       | 0x3A       | CPU_pc        | R/W | CPU program counter                        |

|                       | 0x36       | CPU_iaddr     | R/W | IMEM write address                         |

|                       | 0x32       | CPU_imem      | R/W | Data for instruction memory (IMEM)         |

|                       | 0x0F       | HOST_int      | R/W | Host nterrupt register                     |

|                       | 0x07       | HOST_pio      | R/W | Direction and data for programmable I/Os   |

| Direct                | 0x20       | DRAM_iaddr    | R/W | Indirect address for DRAM controller       |

|                       | 0x21       | DRAM_data     | W   | Data for DRAM controller registers         |

|                       | 0x12       | CD_cntl       | R/W | Selects type of data sent to the CL480     |

|                       | 0x10       | CD_cnfg       | R/W | Selects data format for CD interface       |

|                       | 0x1B       | AUD_mode      | R/W | Data port to udio mode register            |

|                       | 0x03       | VID_iaddr     | R/W | Indirect address for video register access |

|                       | 0x04       | VID_data      | W   | Data for video registers                   |

|                       | 0x0B       | VID_csync     | R/W | Composite sync control                     |

|                       | 0x32       | DRAM_ROMTA    | W   | ROM access time                            |

|                       | 0x33       | DRAM_REF      | W   | DRAM refresh time                          |

|                       | 0xh2       | VID_WEIGHT0   | W   | W0 coefficient of YUV to RGB conversion    |

|                       | 0xh3       | VID_WEIGHT1   | W   | W1 coefficient of YUV to RGB conversion    |

|                       | Oxh4       | VID_WEIGHT2   | W   | W2 coefficient of YUV to RGB conversion    |

|                       | 0xh5       | VID_WEIGHT3   | W   | W3 coefficient of YUV to RGB conversion    |

| Indirect <sup>1</sup> | Oxh6       | VID_WEIGHT4   | W   | W4 coefficient of YUV to RGB conversion    |

|                       | Oxh7       | VID_MODE      | W   | Video modes                                |

|                       | OxhA       | VID_Cr        | W   | Border color: Cr                           |

|                       | OxhB       | VID_YCb       | W   | Border color: Y, Cb                        |

|                       | OxhC       | VID_HSYNC_LO  | W   | Width of HSYNC low                         |

|                       | OxhD       | VID_HSYNC_CYC | W   | Width of HSYNC high                        |

|                       | OxhE       | VID_VSYNCTOG  | W   | VSYNC toggle point                         |

|                       | OxhF       | VID_HINT      | W   | Horizontal interrupt position              |

Table 4-4

Internal Registers Decoded by A\_MSB

1. Indirect register addresses are written to either DRAM\_iaddr or VID\_iaddr.