### UNISTAR SYSTEM REFERENCE MANUAL

# 304040A

Copyright (C) 1982, Callan Data Systems

**DATA SYSTEMS** 2637 Townsgate Road Westlake Village, CA 91361 (805) 497-6837

#### COPYRIGHT

Copyright (C) 1982 by Callan Data Systems. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Callan Data Systems, 2645 Townsgate Road, Westlake Village, California 91361.

#### DISCLAIMER

Callan Data Systems makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Callan Data Systems reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Callan Data Systems to notify any person of such revision or changes.

#### TRADEMARKS

UNISTAR is a trademark of Callan Data Systems UNIX is a trademark of Bell Laboratories Multibus is a trademark of Intel Corporation

WARNING: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

# TABLE OF CONTENTS UNISTAR SYSTEM REFERENCE MANUAL

# CONTENTS

# SECTIONS

| CHAPTER 1 | SYSTEM HARDWARE OVERVIEW                                    | 5  |

|-----------|-------------------------------------------------------------|----|

| CHAPTER 2 | UNISTAR SYSTEM SPECIFICATIONS                               | 7  |

| 2.0       | CHAPTER OVERVIEW                                            | 7  |

| 2.1       | AC INPUT SPECIFICATIONS                                     | 7  |

| 2.2       | OPERATING ENVIRONMENT (EXCLUSIVE OF<br>FLEXIBLE DISK MEDIA) | 7  |

| 2.3       | DIMENSIONS AND WEIGHT                                       | 8  |

| 2.4       | POWER                                                       | 8  |

| 2.5       | INTERNAL D.C. POWER SPECIFICATIONS                          | 8  |

| 2.6       | SYSTEM BOARD OPERATING REQUIREMENTS                         | 9  |

| 2.7       | I/O PANEL CONNECTOR SLOTS                                   | 9  |

| 2.8       | SAFETY                                                      | 9  |

| CHAPTER 3 | POWER SYSTEM INFORMATION                                    | 11 |

| 3.0       | CHAPTER OVERVIEW                                            | 11 |

| 3.1       | POWER SYSTEM SCHEMATICS                                     | 11 |

| 3.2       | A.C. VOLTAGE RECONFIGURATION                                | 19 |

| 3.3       | MOTHERBOARD POWER CAPACITY                                  | 23 |

| CHAPTER 4 | SYSTEM INITIALIZATION, CHECKOUT<br>AND SHUTDOWN             | 25 |

| 4.1       | BRINGING UP THE UNISTAR SYSTEM                              | 25 |

# TABLE OF CONTENTS

| 4.2SHUTTING DOWN THE UNISTAR SYSTEM26CHAPTER 5TERMINAL CONTROLLER CONFIGURATION275.0GENERAL INFORMATION275.1TERMINAL RS-232C PHYSICAL INTERFACE275.2ALTERNATE CHARACTER ROM GENERATION335.3TERMINAL CONTROLLER GRAPHICS INTERFACE37CHAPTER 6DISK UNIT SPECIFICATIONS AND CONFIGURATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,<br>SI51 | CONTENTS  |                                                                      | PAGE |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------|------|

| 5.0GENERAL INFORMATION275.1TERMINAL RS-232C PHYSICAL INTERFACE275.2ALTERNATE CHARACTER ROM GENERATION335.3TERMINAL CONTROLLER GRAPHICS INTERFACE37CHAPTER 6DISK UNIT SPECIFICATIONS AND CONFIGURATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                        | 4.2       | SHUTTING DOWN THE UNISTAR SYSTEM                                     | 26   |

| 5.0GENERAL INFORMATION275.1TERMINAL RS-232C PHYSICAL INTERFACE275.2ALTERNATE CHARACTER ROM GENERATION335.3TERMINAL CONTROLLER GRAPHICS INTERFACE37CHAPTER 6DISK UNIT SPECIFICATIONS AND CONFIGURATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                        | CHAPTER 5 | TERMINAL CONTROLLER CONFIGURATION                                    | 27   |

| 5.1International for the problem internation5.2ALTERNATE CHARACTER ROM GENERATION335.3TERMINAL CONTROLLER GRAPHICS INTERFACE37CHAPTER 6DISK UNIT SPECIFICATIONS AND CONFIGURATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                            | 5.0       | GENERAL INFORMATION                                                  | 27   |

| 5.2ALTERNATE CHARACTER NON CONTENTION515.3TERMINAL CONTROLLER GRAPHICS INTERFACE37CHAPTER 6DISK UNIT SPECIFICATIONS AND CONFIGURATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                        | 5.1       | TERMINAL RS-232C PHYSICAL INTERFACE                                  | 27   |

| CHAPTER 6DISK UNIT SPECIFICATIONS AND CONFIGURATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                          | 5.2       | ALTERNATE CHARACTER ROM GENERATION                                   | 33   |

| CHAPTER 6DISK UNIT SPECIFICATIONS AND COMPLEXATION396.0GENERAL INFORMATION396.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                           | 5.3       | TERMINAL CONTROLLER GRAPHICS INTERFACE                               | 37   |

| 6.1MINIFLOPPY SPECIFICATIONS396.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                                                                                                       | CHAPTER 6 | DISK UNIT SPECIFICATIONS AND CONFIGURATION                           | 39   |

| 6.1MINIFLOPPI SPECIFICATION406.2MINIFLOPPY DRIVE CONFIGURATION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                                                                                                        | 6.0       | GENERAL INFORMATION                                                  | 39   |

| 6.2MINITION406.3WINCHESTER SPECIFICATION406.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                                                                                                                                                           | 6.1       | MINIFLOPPY SPECIFICATIONS                                            | 39   |

| 6.3WINCHESTER DRIVE CONFIGURATION446.4WINCHESTER DRIVE CONFIGURATION44CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                                                                                                                                                                  | 6.2       | MINIFLOPPY DRIVE CONFIGURATION                                       | 40   |

| CHAPTER 7I/O PANEL CONNECTOR INFORMATION47CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.3       | WINCHESTER SPECIFICATION                                             | 40   |

| CHAPTER /I/O PAREL CONNECTOR INFORMATION51CHAPTER 8SYSTEM BOARD CONFIGURATION518.0PRINTED CIRCUIT BOARD ASSEMBLIES,51                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.4       | WINCHESTER DRIVE CONFIGURATION                                       | 44   |

| 8.0 PRINTED CIRCUIT BOARD ASSEMBLIES, 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CHAPTER 7 | I/O PANEL CONNECTOR INFORMATION                                      | 47   |

| 8.0 PRINTED CIRCOTT BOARD ADDREDITED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CHAPTER 8 | SYSTEM BOARD CONFIGURATION                                           | 51   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.0       | PRINTED CIRCUIT BOARD ASSEMBLIES,<br>SWITCH AND SHUNT CONFIGURATIONS | 51   |

| 8.1 CALLAN-83 FDC, FLEXIBLE DISK CONTROLLER 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.1       | CALLAN-83 FDC, FLEXIBLE DISK CONTROLLER                              | 52   |

| 8.2 MSC-9205C, WINCHESTER DISK CONTROLLER 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.2       | MSC-9205C, WINCHESTER DISK CONTROLLER                                | 52   |

| 8.3 MM-8086D/64, RANDOM ACCESS MEMORY 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.3       | MM-8086D/64, RANDOM ACCESS MEMORY                                    | 54   |

| 8.4 PM-68K, 68000 CPU 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.4       | PM-68K, 68000 CPU                                                    | 55   |

. 2

.

| CONTENTS   |                                                       | PAGE |

|------------|-------------------------------------------------------|------|

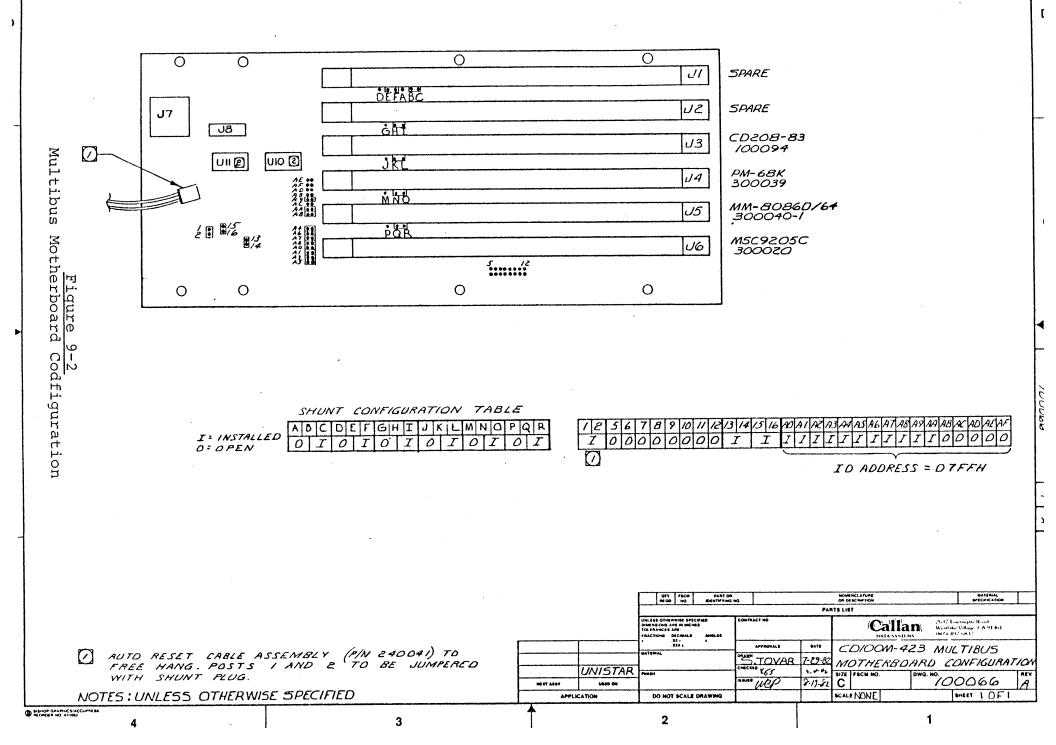

| CHAPTER 9  | MULTIBUS MOTHERBOARD CONFIGURATION<br>GUIDE           | 57   |

| 9.0        | INTRODUCTION                                          | 57   |

| 9.1        | MULTIBUS MOTHERBOARD AND PCBA CONFIGURATION           | 57   |

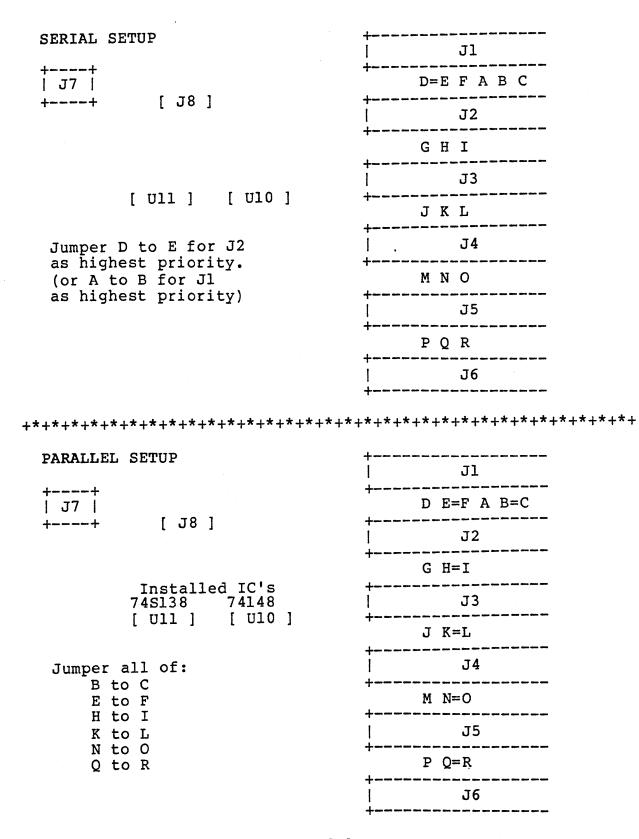

| 9.2        | SHUNT CONFIGURATION                                   | 57   |

| 9.3        | BUS ARBITRATION OPTIONS                               | 58   |

| 9.4        | RESET SWITCH LOGIC                                    | 63   |

| 9.5        | INTERRUPT SWITCH LOGIC CONFIGURATION                  | 63   |

| 9.6        | MULTIBUS/IEEE 796 DIFFERENCES                         | 65   |

| 9.7        | MOTHERBOARD POWER CAPACITY                            | 65   |

| CHAPTER 10 | UNIX SYSTEM CONFIGURATION INFORMATION                 | 67   |

| 10.1       | UNIX SYSTEM CONFIGURATION INFORMATION                 | 67   |

| 10.1.1     | UNISTAR MEMORY                                        | 67   |

| 10.1.2     | TERMINAL DEVICES                                      | 67   |

| 10.1.3     | WINCHESTER DISK DEVICES                               | 6.8  |

| 10.1.4     | MINIFLOPPY DEVICES                                    | 68   |

| 10.1.5     | UNISTAR UNIX                                          | 68   |

| CHAPTER 11 | SYSTEM REGENERATION PROCEDURE                         | 69   |

| 11.0       | GENERAL INFORMATION                                   | 69   |

| 11.1       | WINCHESTER REBUILD PROCEDURE                          | 69   |

| 11.2       | FLOPPY DISK TO WINCHESTER RESTORE<br>INSTRUCTOR (F2W) | 70   |

| 11.3       | WINCHESTER TO FLOPPY BACKUP INSTRUCTIONS (W2F)        | 71   |

# CONTENTS

# PAGE

-

#### FIGURES

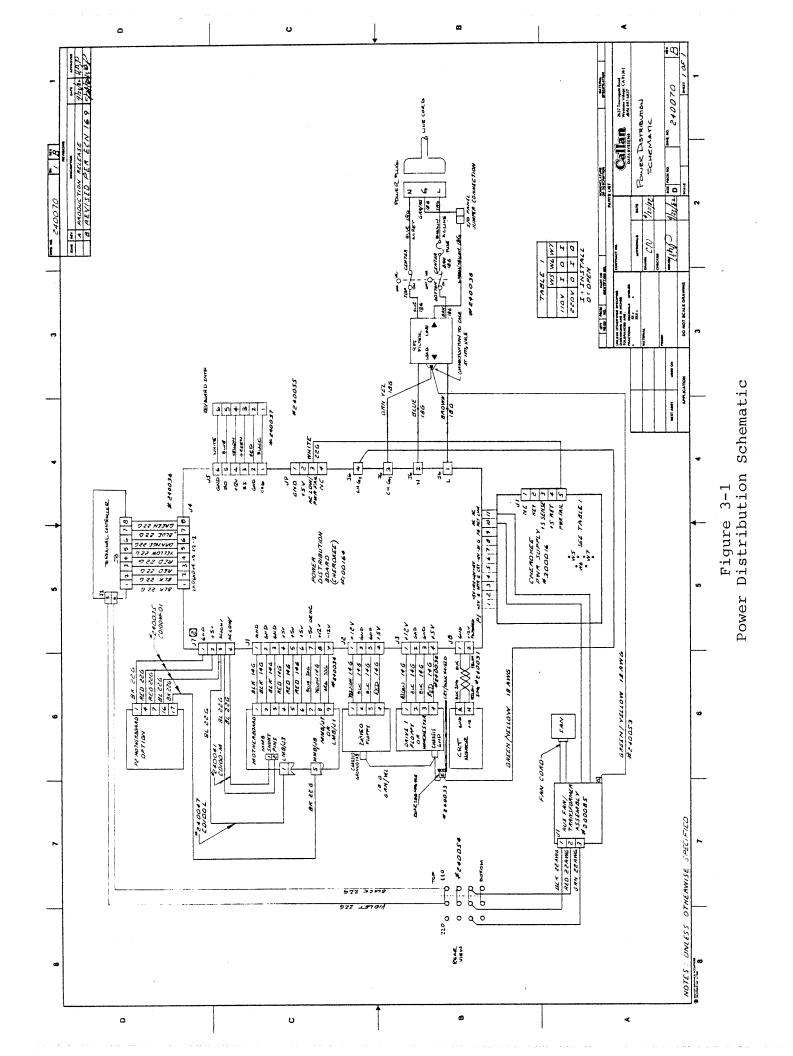

| Figure 3-1 | Power Distribution Schematic                  | 13 |

|------------|-----------------------------------------------|----|

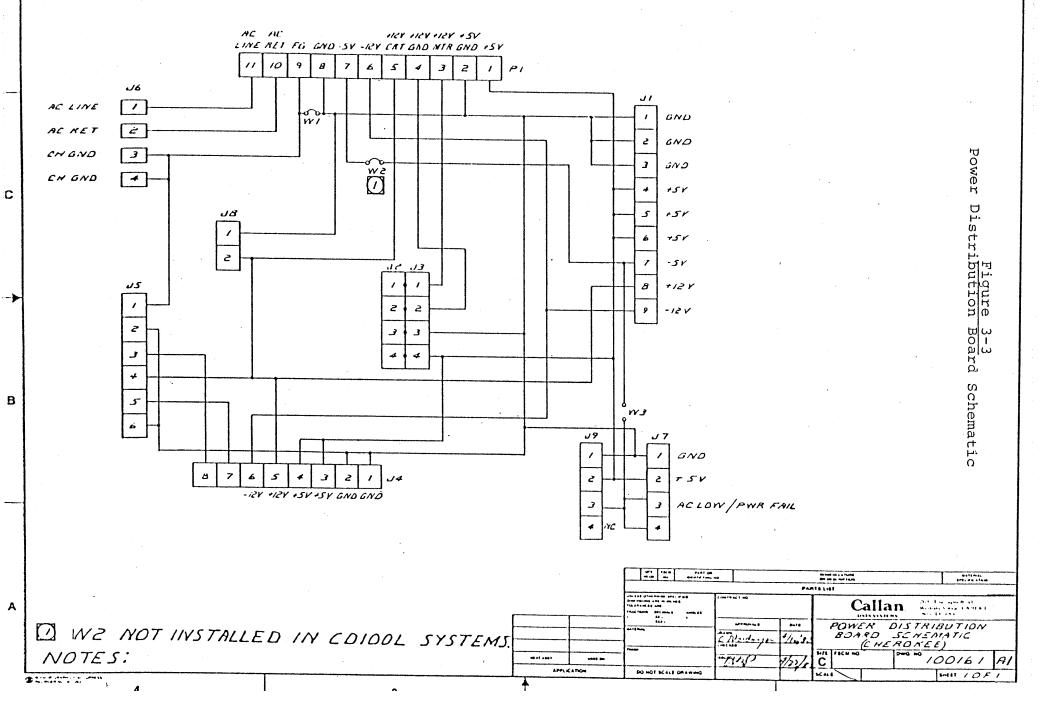

| Figure 3-2 | Power Distribution Board Schematic (Cherokee) | 15 |

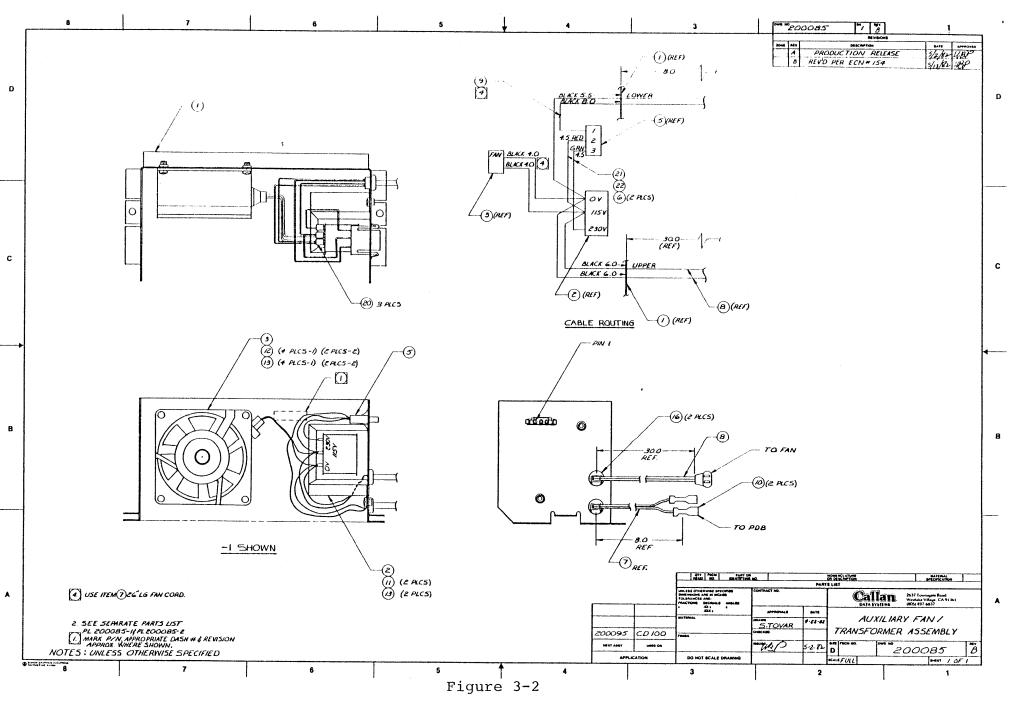

| Figure 3-3 | Auxiliary Fan/Transformer Assembly            | 17 |

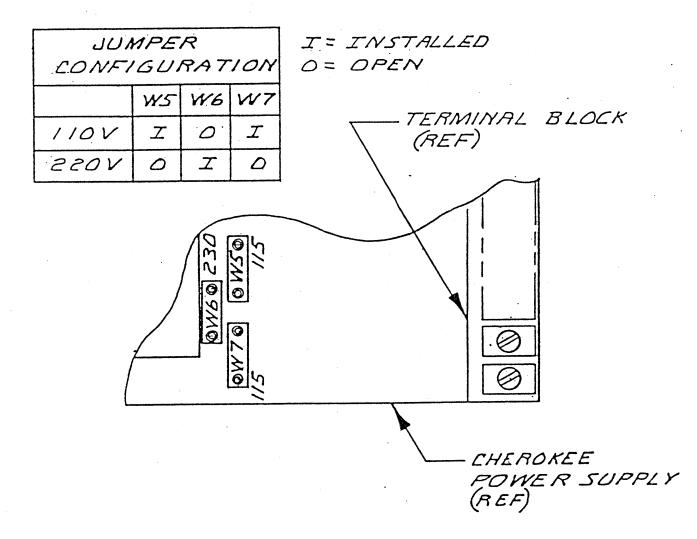

| Figure 3-4 | Power Supply 110V/220V Jumper Configuration   | 21 |

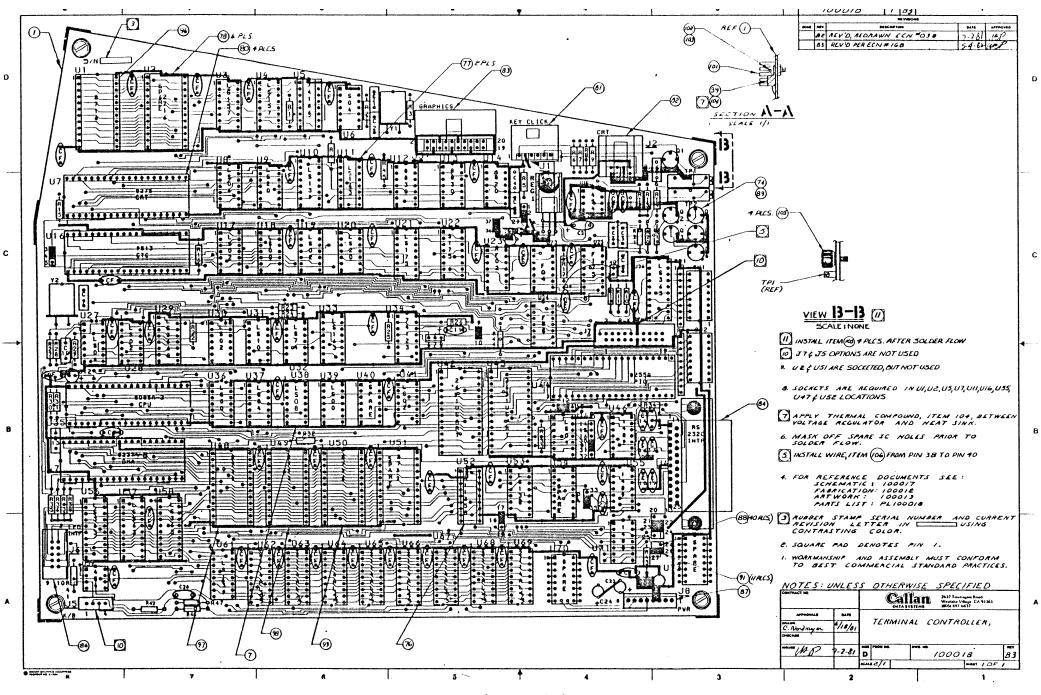

| Figure 5-1 | Terminal Controller Assembly                  | 29 |

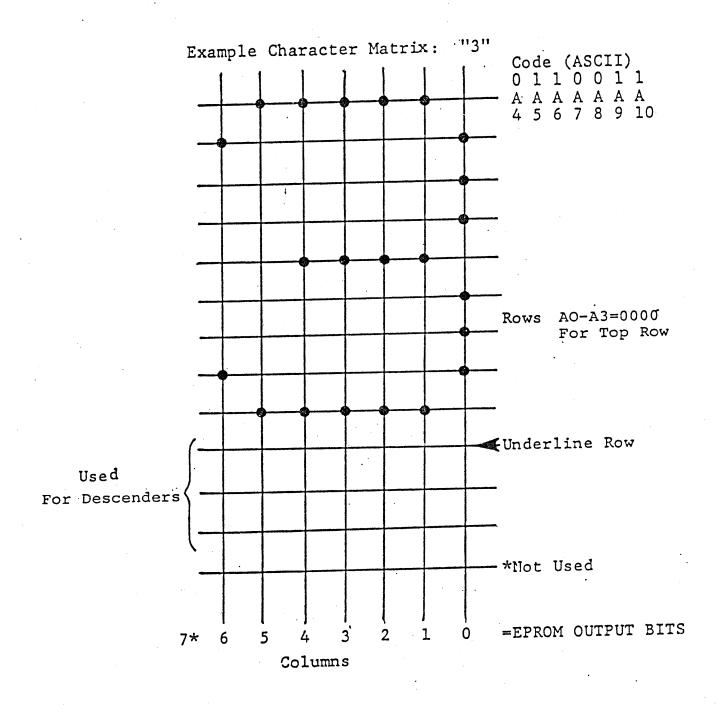

| Figure 5-2 | Character Matrix Format                       | 35 |

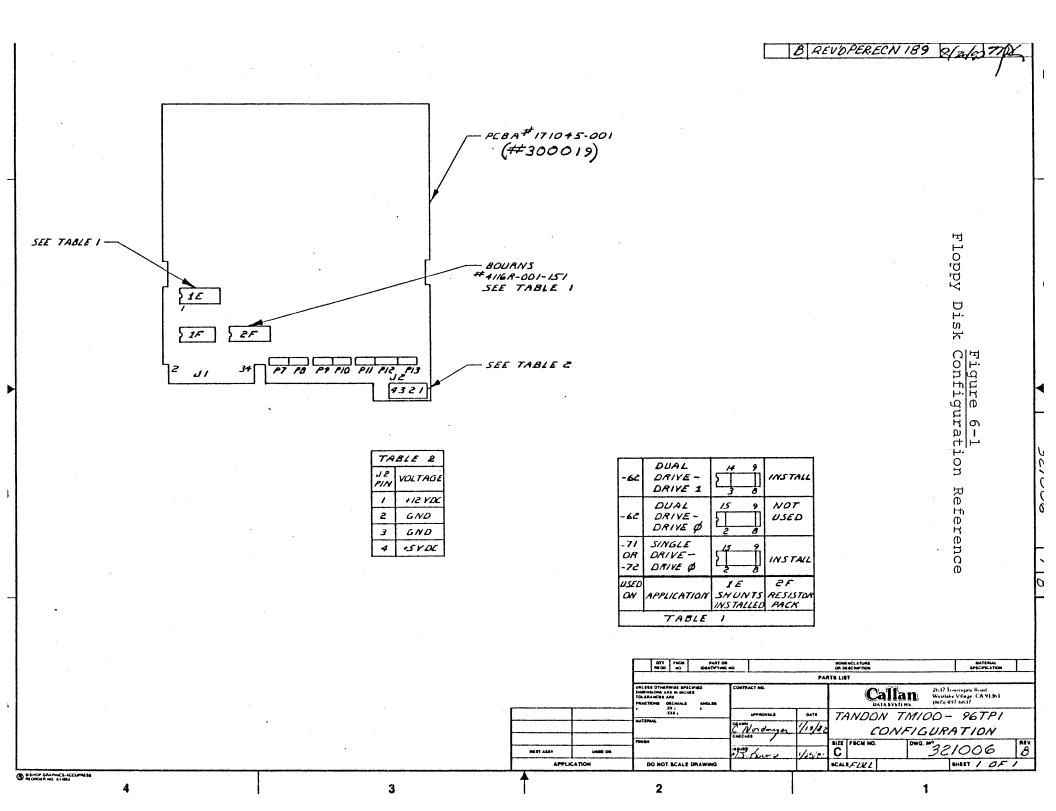

| Figure 6-1 | Minifloppy Configuration Reference            | 41 |

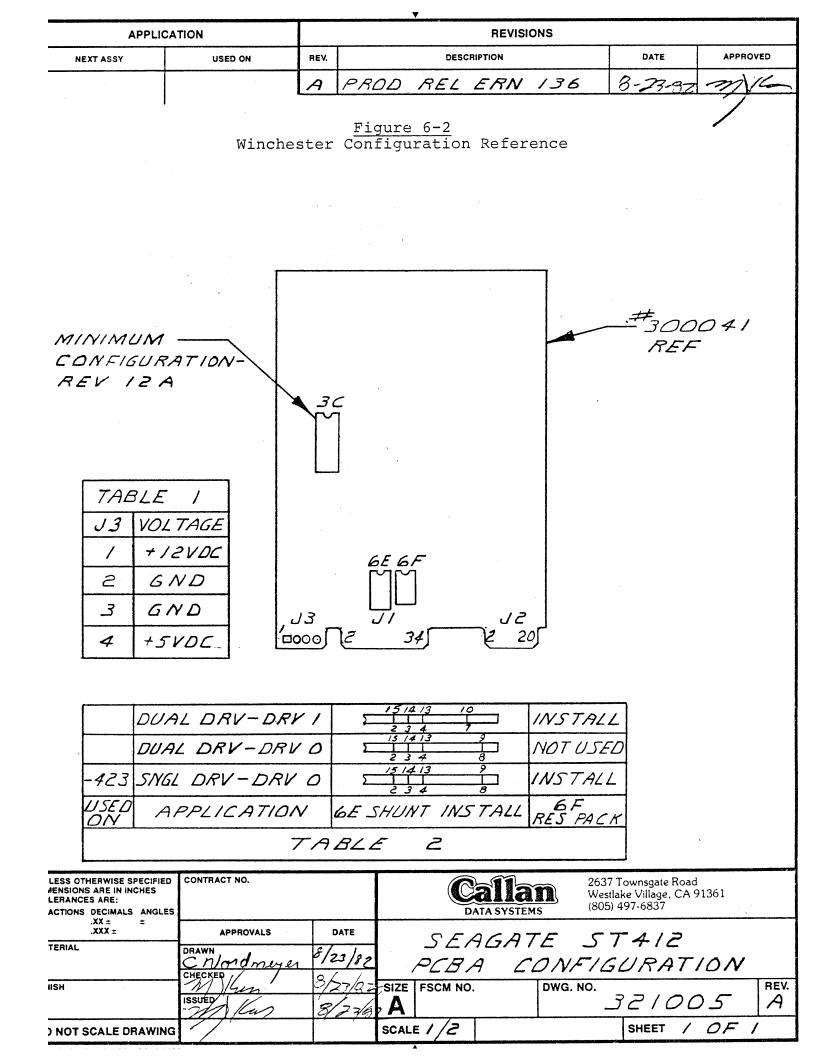

| FIgure 6-2 | Winchester Configuration Reference            | 45 |

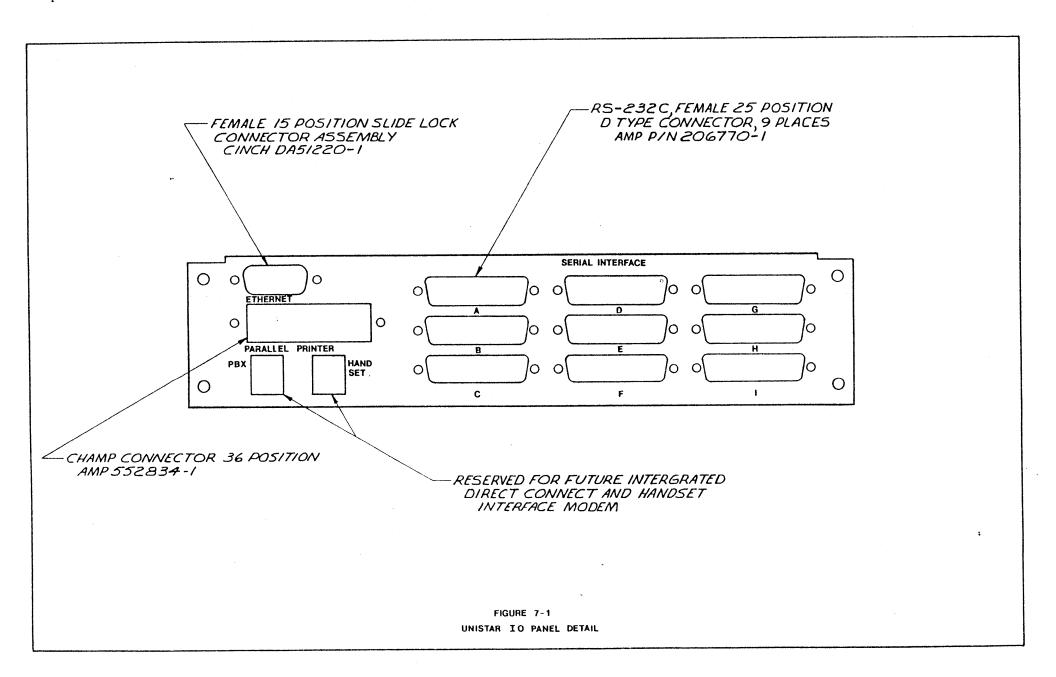

| Figure 7-1 | UNISTAR I/O Panel Detail                      | 49 |

| Figure 9-1 | Bus Arbitration Examples                      | 60 |

| Figure 9-2 | Multibus Motherboard Configuration            | 61 |

# TABLES

| Table 5-1<br>Table 5-2<br>Table 5-3 | RS-232C Jumper Selection<br>RS-232C Connector Pin Assignments<br>Terminal Controller Rear Panel Dip Switch<br>Default Settings for UNISTAR |    |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 9-1                           | Interrupt Switch Configuration Jumpers                                                                                                     | 64 |

| Table 9-2                           | Cardcage Power Specification                                                                                                               | 65 |

#### CHAPTER 1 SYSTEM HARDWARE

This manual provides the user a complete description and specifications for the hardware elements which comprise the UNISTAR family of system products. Sufficient information is provided to allow system installation, checkout and configuration. However, this manual is not intended as a service manual.

Chapter 2 provides the specifications for the basic UNISTAR system enclosure. The power system with both A.C. voltage reconfiguration and D.C. load capabilities is provided in Chapter 3.

WARNING: THE LABEL ON THE REAR PANEL OF THE UNISTAR INDICATES THE AC OPERATING VOLTAGE REQUIRED. ONLY TRAINED AND QUALIFIED SERVICE PERSONNEL SHOULD RECONFIGURE A.C. OPERATING VOLTAGES. INCORRECT RECONFIGURATION CAN CAUSE DAMAGE TO THE UNIT AND VOID CALLAN WARRANTY.

<u>First time UNISTAR operators</u> should refer immediately to Chapter 4 for System Initialization, Checkout and Shutdown procedures in order to insure the integrity of the systems' installed software.

The Basic 5 1/4" disk drive configuration information and performance specifications are provided in Chapter 6. The UNISTAR incorporates a variety of I/O panel configuration options which are defined in Chapter 7.

The UNISTAR incorporates a family of Multibus boards installed in the system card cage. Chapter 8 defines the boards and their factory installed jumper configuration tables. Detailed hardware manuals are provided for each board in Volume II of the UNISTAR Hardware Reference Manual.

The Multibus/IEEE 796 Card Cage Motherboard and its configuration options are described in Chapter 9 as well as standard installation configuration for the UNISTAR board set. Finally, Chapter 10 provides software system installation specific information and the system hard disk regeneration procedure from floppy disk.

The UNISTAR terminal controller which emulates VT100 style terminal, has certain configuration options which are covered in Chapter 5. Users requiring terminal programming information, should refer to the UNISTAR Intellegent Video Terminal Users' Manual included elsewhere in Volume I of the UNISTAR Hardware Reference Manual.

#### CHAPTER 2 UNISTAR SYSTEM SPECIFICATIONS

#### 2.0 CHAPTER OVERVIEW

General system level specifications are presented here in tabulated format. The information is aimed at providing an indication of the appropriate operating environment within which to use the UNISTAR system. Additional information provides the OEM with the requirements to be placed upon additional subassemblies that may be potentially installed within the UNISTAR enclosure.

#### 2.1 AC INPUT SPECIFICATIONS

Power is delivered to the UNISTAR enclosure via a standard male type power receptical on the rear I/O panel. The standard unit is delivered configured to operate at 115 VAC at 60 HZ nominal.

- \* 105 VAC 125 VAC at 60 HZ, 4A(RMS) max. load

- \* 210 VAC 250 VAC at 50 HZ, 2A(RMS) max. load

- \* Fans operate at 115 VAC nominal

- \* Maximum power-on inrush current 25 amps

- \* AC voltage internally reconfigurable

# 2.2 OPERATING ENVIRONMENT (EXCLUSIVE OF FLEXIBLE DISK MEDIA)

The following environmental specifications apply to normal operation of the UNISTAR and are specified to provide reliable system performance within the indicated ranges. The normal operating temperature range that applies to flexible disk media operation is 10 to 52 ° C (50 to 125° F).

- \* Temperature (rear access cover installed) 10.0 to 40.00 C (50 to 1040 F)

- \* Temperature (rear cover removed for service) 10 to 26.70 C(50 to 800 F)

- \* Altitude 8000 ft (2.4 Km)

# UNISTAR SYSTEM SPECIFICATIONS

|     | * Humidity, relative 10% to 90%                                                                                                                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | * Maximum wet bulb: 280 C (820 F)                                                                                                                                                |

|     | * Minimum dew point: 2º C (36º F)                                                                                                                                                |

| 2.3 | DIMENSIONS AND WEIGHT                                                                                                                                                            |

|     | * Width: 20 1/2" (52 cm)                                                                                                                                                         |

|     | * Depth: 19 1/4" (53 cm without keyboard)                                                                                                                                        |

|     | * Depth: 25" (63.5 cm with keyboard)                                                                                                                                             |

|     | * Height: 14 1/2" (37 cm)                                                                                                                                                        |

|     | * Weight: 75 lbs.                                                                                                                                                                |

|     | * Shipping weight: 87 lbs. not including documentation                                                                                                                           |

| 2.4 | POWER                                                                                                                                                                            |

|     | * Input Power 500 VA apparent<br>300 watts maximum<br>150 watts typical                                                                                                          |

|     | * Current Limiting Fuse<br>115 VAC 4A Type F, Callan P/N 663-0002<br>230 VAC 2A Type F, Callan P/N 663-0003                                                                      |

|     | * Power Cord<br>115 VAC Callan P/N 694-0002<br>230 VAC Callan P/N 694-0003                                                                                                       |

| 2.5 | INTERNAL D.C. POWER SPECIFICATIONS                                                                                                                                               |

|     | * Switching power supply outputs<br>+5V at 25 amps<br>+12V linear regulated at 4 amps<br>+12V motors at 4 amps, (10 amps peak start current)<br>-12V at 3 amps<br>-5V at 0.5 amp |

|     | * Reserve card cage D.C. power with the UNISTAR<br>CPU, 64K Multibus Memory,WDC and FDC Boards,<br>minifloppy drive and Winchester Drive installed.                              |

|     | Available power: +5V, 8.0 amps<br>+12V, 1.3 amps<br>-12V, 1.8 amps<br>-5V, .5 amps                                                                                               |

|     | * No combination of loads to exceed a maximum of<br>225 watts on power supply outputs.                                                                                           |

#### 2.6 SYSTEM BOARD OPERATING REQUIREMENTS

The standard family of UNISTAR system Multibus circuit boards and other optional boards installed by an OEM meet the following specifications so that they operate reliably within the system environment.

- \* Voltages ± 5%

- \* Temperature, operating 0-550 C

- \* IEEE 796, Multibus compatible

- \* Available UNISTAR card slots; two

I/O PANEL CONNECTOR SLOTS 2.7

> The rear panel of the UNISTAR contains an I/O connector area that has mounting provisions for the following connector options.

- \* One RS-423, pre-cabled to CPU

- \* Eight RS-232C

- \* One parallel, Centronics style printer interface, 36 pin, AMP 'champ style' cutout

- \* Ethernet 15 pin 'D type' cutout

- \* Two direct connect telephone line connector cutouts

#### 2.8 SAFETY

\* Designed to U.L. and C.S.A. requirements, approvals pending

# UNISTAR SYSTEM SPECIFICATIONS

# CHAPTER 3 POWER SYSTEM INFORMATION

#### 3.0 CHAPTER OVERVIEW

This chapter provides system information on the AC power input and DC output of the UNISTAR switching power supply. Information is provided on changing AC input voltage.

DC output specifications are provided for spare card cage capacity.

### 3.1 POWER SYSTEM SCHEMATICS

The schematics of figures 3-1 and 3-2 show the distribution of AC and DC power within the UNISTAR package. Note that the P2 motherboard option shown on schematic 3-1 is not incorporated in UNISTAR systems. This schematic shows the overall connection of power in the Callan Data Systems, UNISTAR package. Power is distributed from the switching power supply by a power distribution board which provides all necessary power interconnection to the system.

The system incorporates two 115 VAC fans which are operated with an autotransformer in assembly #200085. This circuit allows the system to be operated at 230 VAC without replacement of the fans. Schematic of Figure 3-3 shows the interconnection of the fan power.

#### POWER SYSTEM INFORMATION

14

Auxiliary Fan/Transformer Assembly

#### POWER SYSTEM INFORMATION

D

#### POWER SYSTEM INFORMATION

.

# 3.2 AC VOLTAGE RECONFIGURATION

WARNING: THE LABEL ON THE REAR PANEL OF THE UNISTAR INDICATES THE AC VOLTAGE OPERATING REQUIREMENTS OF THE SYSTEM. ONLY TRAINED AND QUALIFIED SERVICE PERSONNEL SHOULD RECONFIGURE AC OPERATING VOLTAGES. IN THE EVENT THAT A UNIT IS RECONFIGURED, THE RATING LABEL MUST BE CHANGED. FAILURE TO DO THIS OR INCORRECT AC VOLTAGE RECONFIGURATION WILL VOID THE CALLAN WARRANTY. THE LATTER MAY CAUSE DAMAGE TO THE UNIT. TURN THE UNIT <u>OFF</u> AND REMOVE LINE CORD BEFORE RECONFIGURING AC VOLTAGES OR OPENING THE UNIT.

Located inside the rear access cover on the vertical bulkhead is a switch for selecting the operating voltages of the internal system AC fans. It also selects the CRT screen refresh frame rate. Place the switch in the left position for 115V/60Hz operation; place the switch in the right position for 230V/50Hz operation. To change the switch setting, remove the set screw, move the switch to the desired position then replace and secure the set screw. UNISTAR systems use a switching power supply which must be reconfigured with AC voltage selection jumpers. Open the unit to access the base area and reconfigure jumpers W5, W6, and W7 as follows: for 115V operation, install W5 and W7 and for 230V operation, install W6 and remove W6 remove W5 and W7. See Figure 3-4 for location of the jumpers on the power supply.

WARNING: Set this switch and configure power supply jumpers PRIOR to turning the unit on. Failure to do so damages the power supply and/or fans and voids the warranty. .

·

.

Figure 3-4 Power Supply 110V/220V Jumper Configuration

21

# 3.3 MOTHERBOARD POWER CAPACITY

The following current and power capacities are available to the Multibus/UNISTAR motherboard.

The column "UNISTAR SPARE SLOT CURRENT" defines the current available at the two spare UNISTAR slots. These currents can be used only such that the maximum additional power dissipated in the spare slots does not exceed 45 watts.

# NOTICE: Failure to comply with the appropriate power or current limits voids the UNISTAR warranty.

| VOLTAGE SPECIFICATIONS | MOTHERBOARI<br>MAXIMUM<br><u>CURRENT</u> | D UNISTAR<br>SPARE SLOT<br><u>CURRENT</u> |

|------------------------|------------------------------------------|-------------------------------------------|

| +12 Volts ± 3.0%       | 2.0 Amps                                 | 1.3 Amps                                  |

| + 5 Volts ± 3.0%       | 21.5 Amps                                | 8.0 Amps                                  |

| -12 Volts ± 5%         | 2.5 Amps                                 | 1.8 Amps                                  |

| - 5 Volts ± 5%         | 0.5 Amps                                 | .5 Amps                                   |

CHAPTER 4 SYSTEM INITIALIZATION CHECKOUT AND SHUTDOWN

BRINGING UP THE UNISTAR SYSTEM

4.1

STEP 1: Turn the on/off switch to ON

STEP 2: Wait until the CRT screen warms up and begins to show the cursor. This takes about 30 seconds.

STEP 3: Depress the rocker switch marked "RESET". The "RESET" key is located just to the lower right of the CRT screen. Shortly after depressing the "RESET" key, the following message should appear on the CRT screen:

UniStar 68000 UNIX boot v2.2 (c) 1982 by Callan Data Systems Inc.

If the message does not appear, wait 5 seconds and depress the "RESET" again. If the message does not appear after several more depressions of the "RESET" key, then the UNISTAR is broken. The message normally appears approximately 3 seconds after release of the switch due to start up processing.

STEP 4: When the message shown in the above step is displayed, the UNISTAR UNIX system may be started up. To automatically start up the UNISTAR UNIX system, press the keyboard key marked, "RETURN". Immediately after the "RETURN" key is hit, the message shown below will appear:

#### w(0,0)/unix

This message shows that the Callan Data Systems UNIX Boot Monitor is loading UNIX into the UNISTAR. Loading UNIX into the UNISTAR will take about 20 seconds, during this loading process, several messages will appear, indicating such things as memory size of the UNISTAR and so on.

STEP 5: About 20 seconds after the "RETURN" was hit to load UNIX, a single line with a pound sign ('#') will appear. This indicates that UNIX is now running in the single-user mode. Since most UNIX systems will run in a multi-user mode, enter a

#### SYSTEM INITIALIZATION CHECKOUT AND SHUTDOWN

CONTROL-D to have UNIX begin execution of the multi-user mode. A CONTROL-D is entered by holding the "CTRL" key down while typing the "D" key.

If the single line with a pound sign does not appear, or if messages containing the word "error" appear during the UNIX loading process, then retry the entire procedure by turning off the machine and going back to STEP 1.

STEP 6: As UNIX begins execution of the multi-user mode, it will ask several questions of the user. These questions include the date and time, and whether the disk should be verified, and so on. Each question is explained. The entire time to boot UNIX for multi-user mode, including answering the questions, takes less than 2.5 minutes.

## 4.2 SHUTTING DOWN THE UNISTAR SYSTEM

STEP 1: Make sure that all users are either logged off the system or not actively entering UNIX commands.

STEP 2: Type in the command "shutdown". The shutdown command will shutdown UNIX from a multiuser system back to a single-user system. When the shutting down process is complete, "shutdown" will announce it as shown below(where <cr> denotes the RETURN key:

% shutdown <cr>

working ....

Shutdown complete

#

Once in the single-user mode, turn the power switch to OFF. NOTE: If the UNISTAR is going to be moved physically, you MUST perform the following steps before turning the power off.

STEP 3: This step is performed before turning the power off. It is needed ONLY if the UNISTAR machine is going to be physically moved. The purpose of this step is to position the arm of the Winchester disk to a "shipping zone" area so that hard shocks to the UNISTAR system do not damage the Winchester disk media. Depress the "RESET" button. Type in the following command:

#### w(0,0) ship

Now turn off the power immediately, do NOT depress"RESET" again.

# CHAPTER 5 TERMINAL CONTROLLER CONFIGURATION

#### 5.0 GENERAL INFORMATION

This section provides information necessary to configure the UNISTAR workstation's hardware options. Subsections cover configuring the terminal's RS-232C port, DIP switch settings for terminal mode control, and installation of alternate character sets. The graphics interface configuration and its use is also described.

# 5.1 TERMINAL RS-232C PHYSICAL INTERFACE

The UNISTAR terminal controller board provides a standard 25 pin "D" type female communication connector and circuitry per EIA Standard RS-232C. Configuration interface type "D" is used for Duplex operation with Request to Send used to indicate a non-transmit mode to the PM-68K. The one exception to the type "D" interface is that the terminal controller is not microprogrammed to respond to the Modem Ring Indicator signal (RS-232C Circuit CE).

Data transmission protocol is industry standard asynchronous start-stop protocol. One stop bit is used at baud rates above 150 baud and two bits are used at 110 baud and below.

The terminal controller is factory configured to disable use of various interchange circuits to accommodate a simpler three wire host interface with synchronization using XON/XOFF protocol. Table 5-1 summarizes thejumper option shunts for the terminal controller board. Refer to Figure 5-1 for the location of these jumper posts. The signal pinout summary for the terminal controller DB-25 RS-232C connector is given in Table 5-2. Other user options of the terminal controller are programmable by two DIP switches on the rear of the board. Table 5-3 summarizes all switch settings.

| SHUNT<br>SHUNT |                                                                         | RS-232C<br>INTERCHANGE<br>CIRCUIT |

|----------------|-------------------------------------------------------------------------|-----------------------------------|

|                |                                                                         |                                   |

| 31-32          | Enable Clear to Send from<br>Host                                       | (CKT CB)                          |

| 31-30*         | Disable Clear to Send from<br>Host                                      |                                   |

| 34-33          | Enable Data Set Ready from<br>Host                                      | (CKT CC)                          |

| 34-35*         | Disable Data Set Ready from<br>Host                                     |                                   |

| 18-19          | Enable Carrier Detect from<br>Host                                      | (CKT CF)                          |

| 17-18*         | Disable Carrier Detect from<br>Host                                     |                                   |

| 23-24*         | Use Internal Terminal Recei<br>Clock                                    | ve                                |

| 23-25          | Use Receive Signal Element<br>Timing from Host for Receiv<br>Data Clock |                                   |

| 20-21          | Use Transmitter Signal<br>Element Timing from Host fo<br>Transmit Clock | r<br>(CKT DB)                     |

| 21-22*         | Use Internal Terminal Baud<br>Clock normal.                             |                                   |

Note: The asteriks indicate the configuration of a standard factory delivered terminal controller.

> Table 5-1 RS-232C Jumper Selection

Figure 5-1 Terminal Controller Assembly

# TERMINAL CONTROLLER CONFIGURATION

# TABLE 5-2RS-232C CONNECTOR PIN ASSIGNMENTS

| SIGNAL NAMES                       | RS232<br><u>CIRCUIT</u> | CONNECTOR<br>PIN NUMBER | <u>1/0*</u> |

|------------------------------------|-------------------------|-------------------------|-------------|

| Transmit Signal Element<br>Timing. | DB                      | 15                      | I           |

| Receiver Signal Element<br>Timing. | DD                      | 17                      | I           |

| Transmitter Clock                  | DA                      | 24                      | 0           |

| Request to Send                    | CA                      | 4                       | 0           |

| Data Terminal Ready                | CD                      | 20                      | 0           |

| Transmit Data                      | BA                      | 2                       | 0           |

| Receive Data                       | BB                      | 3                       | I           |

| Clear to Send                      | СВ                      | 5                       | N/U         |

| Data Set Ready                     | СС                      | 6                       | N/U         |

| Carrier Detect                     | CE                      | 8                       | N/U         |

| Signal Ground                      | AB                      | 7                       | I/0         |

| Protective Ground                  | AA                      | 1                       | I/0         |

\* I implys an input to the terminal controller O implys an output from the terminal controller

N/U = Not used

×

## TERMINAL CONTROLLER CONFIGURATION

#### TABLE 5-3 TERMINAL CONTROLLER REAR PANEL DIP SWITCH DEFAULT SETTINGS FOR UNISTAR

# SW1 - UPPER SWITCH BANK

| SWITCH<br>NUMBER                                                               | SWITCH C<br><u>NAME</u>                                                                                                                                                                         | OFF POSITION<br>(LEFT)                                                                                                                                                                                                      | ON POSITION<br>(RIGHT)                                                                                              |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c} 1-8\\ 1-7\\ 1-6\\ 1-5\\ 1-4\\ 1-3\\ 1-2\\ 1-1 \end{array} $ | Autowrap<br>XON/XOFF<br>New line mode<br>Margin Bell<br>ANSI/VT52 mode<br>Cursor Blink<br>Cursor type<br>Screen mode                                                                            | Enabled<br>Disabled<br>Enabled<br>VT52 mode<br>Steady Cursor<br>Dash Cursor<br>Reverse Video                                                                                                                                | Disabled*<br>Enabled*<br>Disabled*<br>Disabled*<br>ANSI mode*<br>Blinking Cursor*<br>Block Cursor*<br>Normal Video* |

|                                                                                | SW2 - LOWE                                                                                                                                                                                      | ER SWITCH BANK                                                                                                                                                                                                              |                                                                                                                     |

| 2-8<br>2-7<br>2-6<br>2-5<br>2-4<br>2-3<br>2-2<br>2-1                           | Local/Online<br>Data length<br>Parity<br>Parity<br>Baud rate select cod<br>Baud rate select cod | le<br>le                                                                                                                                                                                                                    | Online*<br>8 data bits*<br>Odd parity*<br>Ignore parity*                                                            |

|                                                                                | 4 3 2 1 SW2                                                                                                                                                                                     | $\sum_{i=1}^{n} (i-i) = 0$                                                                                                                                                                                                  |                                                                                                                     |

|                                                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                            | (1 stop b<br>(1 stop b<br>(2 stop b<br>(2 stop b)<br>(2 stop b) | <pre>it) it) it) it) it) it) it) it) it) it)</pre>                                                                  |

\* INDICATES THE STANDARD UNISTAR SETTING

#### 5.2

#### ALTERNATE CHARACTER ROM GENERATION

An alternate character set can be incorporated in the UNISTAR terminal controller by installation of a 2716 EPROM or equivalent device in IC location U42 on the terminal controller board. Software driven commands are available for invoking the alternate character sets incorporated into this EPROM, the alternate character ROM standard character set and the alternate character ROM special Graphics character set. Up to 128 characters can be included in the alternate character ROM. Sixteen bytes are stored in sequence for each character to define its character font (see figure 5-1) A seven bit binary code is used to address each character as it is displayed in the same way that ASCII character codes are used to address characters in the standard set EPROM. Therefore, the seven bit character code is used on address lines A4-Al0 of the 2716 where A4 is the least significant bit of the character code sent to the terminal. Address lines A0-A3 are used to select the rows of the character matrix as each character is displayed.

Each byte stored in the EPROM character generator represents a row of the character matrix. The most significant bit position of each byte (bit 7) in the EPROM is used as a control bit for the video logic to support line graphics characters. This bit when true expands bits 0 and 6 into their adjacent inter-character spaces thus allowing continuous lines between characters. The displayable character matrix is 7 x 13 bits (60 Hz refresh) or 7 x 15 (50 Hz refresh). Refer to Figure 5-2 for an example of the character matrix format.

## Figure 5-2 Character Matrix Format

\* Bit 7 when true enables display of bit 0 and/or bit 6 in the intercharacter space if either is true.

### TERMINAL CONTROLLER GRAPHICS INTERFACE

The UNISTAR terminal controller incorporates a graphics interface which permits field or factory installation of a graphics display controller. Located at the top of the terminal controller and labeled "graphics", the 20 pin interface provides basic binary signals to the graphics controller, which permit it to operate in synchronization with the alphanumeric terminal controller. The graphics controller also uses the cable to return video display data and intensity control information to the terminal controller which then uses it to drive the video output electronics and CRT.

The normal jumper configuration of the terminal controller without graphics interface is:

| Jumper | Status: |

|--------|---------|

| 2-29   | IN      |

| 36-37  | IN      |

To install the graphics controller, the jumpers above are removed and DS8830's (P/N 404-8830) are installed in Ul2 and Ul3 and a DS8820A (P/N 404-8820) is installed in Ul4. These IC's are provided with the graphics field installation kit as well as a 20 conductor ribbon cable which connects the graphics interface connector to the Multibus resident graphics controller.

•

.

CHAPTER 6 DISK UNIT SPECIFICATIONS AND CONFIGURATION

## 6.0 GENERAL INFORMATION

The Callan UNISTAR contains two integral disk units; a 5 1/4" minifloppy and a 5 1/4" Winchester. The characteristics and specifications of these two devices are provided in this chapter. Format information, where applicable, is provided in the System Software Configuration chapter. For disk unit service information, please refer to the Service Manual.

## 6.1 MINIFLOPPY SPECIFICATIONS

Media\*: Certified for double sided double density reading. The approved source being Verbatim P/N: MD 557-01-18239

Note: Callan Data Systems does not warranty drive for use with non-approved media. Tracks per inch: 96 Tracks per side: 77 Seek Time: 3 msec/track Head Settling time: 15 msec Error Rates: 1 per 109 (recoverable) 1 per 1012 (non-recoverable) 1 per 106 (seeks) Head Life: 20,000 hours Media Life: 3.6 X 106 passes per track Disk Speed: 300 rpm  $\pm$  1.5% (long term) Instantaneous speed variation: ± 3.0% Start/Stop Time: 250/150 mSec (maximum) Transfer Rate: 250 Kbytes/sec Recording Mode: MFM Power: +12 vdc  $\pm$  0.6v 900 ma AVG + 5 vdc ± 0.25v 600 ma AVG Vendor: Tandon TM-100-4 or equivalent

\*NOTE: Callan Data Systems does not warranty drive for use with non-approved media.

#### DISK UNIT SPECIFICATIONS AND CONFIGURATION

6.2

#### MINIFLOPPY DRIVE CONFIGURATION

The minifloppy disk drive units are capable of being configured to operate in a variety of modes depending upon a shunt block contained upon the drive electronics circuit board. The shunt options are described as follows. (Note that "\*" denotes standard factory installed shunts for the UNISTAR system).

| Shunt         | Pins (lE)                                 | Fur                  | nction                                                                                          |

|---------------|-------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|

| * 2<br>3<br>4 | to 16<br>to 15<br>to 14<br>to 13<br>to 12 | NDSO<br>NDS1<br>NDS2 | Drive Motor from Select<br>Drive 0 Enable<br>Drive 1 Enable<br>Drive 2 Enable<br>Drive 3 Enable |

| 6<br>7        | to 11<br>to 10<br>to 9                    | MX<br>SPARE          | Daisy Chain Cable Disable<br>Not Used<br>Drive Motor from Cable                                 |

The TM-100 drive is provided with the capability of terminating input lines to the drive on the lines:

Motor On, Direction, Step, Write Data, Write Gate, and Side Select

If the TM-104 is used in a multiple drive setup then the termination network at location 2F on the circuit board must be removed from all units except the drive on the extreme end of the cable. For the standard UNISTAR in a single floppy installation the termination network is installed. The termination network is a 150 ohm pullup resistor for each line.

Figure 6-1 on the following page shows the configuration of the TM-104 drive electronics circuit board.

#### WINCHESTER SPECIFICATIONS

Capacity **Unformatted** Per Drive 12.76 Megabytes 3.19 Megabytes Per Surface 10416 Bytes Per Track Formatted \* Per Drive 10.0 Megabytes Per Surface 2.5 Megabytes Per Track 8192 Bytes 256 Bytes Per Sector Sectors per track 32 \*With vendor standard formatting

6.3

## DISK UNIT SPECIFICATIONS AND CONFIGURATION

WINCHESTER SPECIFICATIONS (Cont.)

Transfer Rate 5.0Mbits/sec 8.33 msec Average Latency Access Time Track to Track 3ms 85ms\*\* Average 205ms\*\* Maximum 15ms Setting Time \*\*using burst mode (including settling) Functional Specifications: Rotational speed 3600 rpm ±.1% 9074 bpi Recording density 9074 fci Flux density 345 tpi Track density Cylinders 306 1224 Tracks R/W Heads 4 2 Disks Max Accoustic Output: 50 DBA Shock Operating: 10G Non-operating: 20G DC Power Requirements +12V  $\pm$  5%, 1.8A typical, 4.5A max (at power on) +5V ± 5%,.7A typical, 1.0A max  $-12V \pm 5V$  Max Ripple = 50mV P-P Error Rates: Soft read errors. . . . 1 per 1010 bits read Hard read errors\* . . . 1 per 1012 bits read Seek errors . . . . . 1 per 106 seek \* Not recoverable within 16 retries

Vendor: Seagate ST412 or Equivalent.

#### DISK UNIT SPECIFICATIONS AND CONFIGURATION

6.4

#### WINCHESTER DRIVE CONFIGURATION

The Seagate ST-412 Winchester disk drive is capable of being configured in various ways depending upon a shunt block contained upon the drive electronics board. The shunt position functions are described as follows with an "\*" indicating the standard installed shunt configuration for the UNISTAR system.

| <u>Shunt Pins</u> | Function                |

|-------------------|-------------------------|

| 1 to 16           | Radial Enable           |

| * 2 to 15         | Defeat Auto Recal       |

| * 3 to 14         | Always Installed        |

| * 4 to 13         | Not Used                |

| 5 to 12           | DS4 Drive Unit 3 Enable |

| 6 to 11           | DS3 Drive Unit 2 Enable |

| 7 to 10           | DS2 Drive Unit 1 Enable |

| * 8 to 9          | DS1 Drive Unit 0 Enable |

The ST-412 drive is provided with the capability of terminating input lines to the drive on these lines:

Reduced Write Current, Write Gate, Head Address Lines, Step, and Direction

If the ST-412 is used in a multiple drive setup then the terminator network at location 6F on the circuit board must be removed from all units except the drive on the extreme end of the cable. For the standard UNISTAR in a single Winchester installation the terminator network is installed. The terminator network is a 220/330 ohm network for each line.

Figure 6-2 on the following page shows the configuration of the ST-412 drive electronics circuit board.

## DISK UNIT SPECIFICATIONS AND CONFIGURATION

## CHAPTER 7 I/O PANEL CONNECTOR INFORMATION

Figure 7-1 illustrates the UNISTAR I/O panel configuration. The panel supports the following I/O types.

. NINE RS-232C female D type communications connectors. One is cabled to the auxillary communication port on the PM-68KCPU board. The others are optionally cabled to an eight channel communication board on UNISTAR 200 systems (Multiuser).

. One Ethernet compatible 15 pin D connector Cinch type DA 51220-1 or equivalent cutout to be used for Ethernet options.

• One parallel printer, AMP 'champ' latch connector P/N 552834-7, cutout. This cutoutprovides for a future parallel printer.

. Two telephone cable, AMP modular jack P/N 520250-3, direct connect connector cutoutsto support a future integrated modem option.

.

## I/O PANEL CONNECTOR INFORMATION

.

## I/O PANEL CONNECTOR INFORMATION

#### CHAPTER 8 SYSTEM BOARD CONFIGURATION

PRINTED CIRCUIT BOARD ASSEMBLIES, SWITCH AND SHUNT 8.0 CONFIGURATIONS

> This section provides a description of the factory installed configurations for all Multibus PCBAs in the UNISTAR Multibus motherboard (Ref: Section 9 for individual PCBA card locations).

8.1 CALLAN -83 FDC, FLEXIBLE DISK CONTROLLER

Configuration of the Callan -83 FDC Flexible Disk Controller PCBA for operation with 68000 UNIX I/O, with an I/O base address equal to 100 Hex (16 bit decode) and interrupt level 3 (Ref: Dwg.No. 100096, Floppy Disk Controller Board Configuration and Dwg.No. 304004, Callan Data System Floppy Disk Controller Reference Manual).

Address Decode Switchs (SW1 and SW2):

| Switch                                                                                                                                       | Designation                                                                                                                                         | <u>Position</u>                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| SW1-1<br>SW1-2<br>SW1-3<br>SW1-4<br>SW1-5<br>SW1-6<br>SW1-7<br>SW1-8<br>SW2-1<br>SW2-2<br>SW2-2<br>SW2-3<br>SW2-4<br>SW2-5<br>SW2-6<br>SW2-7 | <pre>(not used)<br/>(not used)<br/>(not used)<br/>8B/16B<br/>(not used)<br/>A5<br/>A6<br/>A7<br/>A8<br/>A9<br/>AA<br/>AB<br/>AC<br/>AD<br/>AE</pre> | -<br>Closed<br>Closed<br>Closed<br>Closed<br>Open<br>Closed<br>Closed<br>Closed<br>Closed<br>Closed |

| SW2-8                                                                                                                                        | AF                                                                                                                                                  | Closed                                                                                              |

| Shunt Designation | Position                                                                                                                                                                                                                                    | Function                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| RDY-D             | l to 2<br>4 to 5<br>Installed<br>Installed<br>Installed<br>Installed<br>Removed<br>Removed<br>Removed<br>Removed<br>Installed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed | Two Sided Enable<br>Mini Floppy Head Enable<br>Ready From Drive Enable<br>Floppy Always Ready Enable |

|                   |                                                                                                                                                                                                                                             | -                                                                                                    |

### MSC-9205C, WINCHESTER DISK CONTROLLER

Configuration of the MSC-9205C Winchester Disk Controller PCBA for operation with 68000 UNIX I/O,with an I/O base address equal to 080 Hex (16 bits provided from CPU but only 8-bits decoded by controller) and interrupt level 5 (Ref: Dwg.No. MSC-9205C PCBA Configuration and Dwg.No. 304012, MSC-9205 Disk Controller Product Specification). As supplied, the MSC-9205C PCBA is configured for a disk drive with four heads, 512 byte sectors, 17 sectors per track, with parallel bus priority.

•

| Shunt Designation                                                       | Position                                                                                   | Function                                                                                                                                                                                                                |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W1<br>W2<br>W3<br>W4<br>W5<br>W6<br>W7<br>W8<br>W9<br>W10<br>W11<br>W12 | Installed<br>Removed<br>Removed<br>Installed<br>Installed<br>Removed<br>Removed<br>Removed | Increase Precomp Enabled<br>Write AM Enabled<br>BPRO Disabled<br>I/O Base Address<br>I/O Base Address<br>I/O Base Address<br>I/O Base Address<br>I/O Base Address<br>I/O Base Address<br>I/O Base Address<br>(not used) |

| W13                                                                     | Removed                                                                                    | (not used)                                                                                                                                                                                                              |

| W14<br>W15                                                              | Installed<br>Removed                                                                       | Four Heads Enabled                                                                                                                                                                                                      |

| W16<br>W17<br>W18                                                       | Removed<br>Removed<br>Removed                                                              | (not used)<br>512 Byte Sector Enabled<br>(not used)                                                                                                                                                                     |

| W19                                                                     | Removed                                                                                    | Interrupt 0 (not used)                                                                                                                                                                                                  |

| W20<br>W21                                                              | Removed<br>Removed                                                                         | Interrupt 1 (not used)<br>Interrupt 2 (not used)                                                                                                                                                                        |

| W22<br>W23                                                              | Removed<br>Removed                                                                         |                                                                                                                                                                                                                         |

| W24<br>W25                                                              | Installed<br>Removed                                                                       | Interrupt 5 (used)<br>Interrupt 6 (not used)                                                                                                                                                                            |

| W26<br>W27                                                              | Removed<br>Installed                                                                       | Interrupt 7 (not used)                                                                                                                                                                                                  |

## MM-8086D/64 RANDOM ACCESS MEMORY

Configuration for the UNISTAR Multibus RAM is for 64 Kilobytes (32 Kilowords) with a Multibus base address of zero to FFFF Hex that is mapped by the PM-68K CPU to address 100000 Hex (Ref: Dwg.No. 321003, MM8086D Memory PCBA Configuration and Dwg.No. 304039, MM-8086D/64 RAM Manual). Addressing switches and shunt installations are as follows:

Address Decode Switchs (SWl and SW2):

| Switch                  | Designation             |       |        | Position     |

|-------------------------|-------------------------|-------|--------|--------------|

| SW1-1                   | Upper                   | Limit | 1      | Closed       |

| SW1-2                   | Upper                   | Limit | 2      | Closed       |

| SW1-3                   | Upper                   | Limit | 3      | Closed       |

| SW1-4                   | Upper                   |       | 4      | Closed       |

| SW1-5                   | Upper                   | Limit | 5      | Open         |

| SW1-6                   | Upper                   | Limit | 6      | Open         |

| SW1-0<br>SW1-7<br>SW1-8 | Upper                   | Limit | 7<br>8 | Open<br>Open |

| SW2-1                   | Upper<br>Lower<br>Lower | Limit | 1<br>2 | Open<br>Open |

| SW2-2<br>SW2-3          | Lower                   | Limit | 3      | Open         |

| SW2-4                   | Lower                   | Limit | 4      | Open         |

| SW2-5                   | Lower                   | Limit | 5      | Open         |

| SW2-6                   | Lower                   | Limit | 6      | Open         |

| SW2-7                   | Lower                   | Limit | 7      | Open         |

| SW2-8                   | Lower                   | Limit | 8      | Open         |

| E1-E2-E3E2 to E3Delay XACK/E4-E5-E6E4 to E5+5 VDC for 64K DRAME7-E8-E9E8 to E9Delay Line Pin 11 RDCYC CLE10-E11-E12E11 to E12 64K DRAM TypeE13-E14-E15E14 to E15 64K DRAM TypeE16 thru E20(all open) Extended Address SelectionE21-E22-E23E22 to E23 No Delay on MWTC (write)Parity Error (Pad)J1-37 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

## 8.4 PM-68K, 68000 CPU

Configuration settings for the PM-68K 68000 CPU PCBA that are required to run 68000 UNIX I/O utilizing interrupt level 5 for the USART ('wireor' with MSC-9205 interrupt 5) and interrupt level 6 for timer channel #2 (Ref: Dwg.No. 304041, PM-68K CPU Manual), is as follows:

| Shunt Designation                                                                                        | Position                                            | Function                                                                                                                                |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| J100 l thru 8                                                                                            | l to 3                                              | Port B RS-423 RDATA DTE                                                                                                                 |

| J100 l thru 8                                                                                            | 2 to 4                                              | Port B RS-423 TDATA DTE                                                                                                                 |

| J100 l thru 8                                                                                            | 7 to 8                                              | Al2 to 2732 EPROM pin 23                                                                                                                |

| J800 l thru 8                                                                                            | l to 2                                              | INT6/Timer #2 Interrupt                                                                                                                 |

| J800 l thru 8                                                                                            | 3 to 4                                              | INT5/USART Interrupt                                                                                                                    |

| J9011 thru 10                                                                                            | l to 2                                              | Initialize Reset (receive)                                                                                                              |

| J901 1 thru 10                                                                                           | 5 to 6                                              | Bus Clock (master)                                                                                                                      |

| J901 1 thru 10                                                                                           | 9 to 10                                             | Constant Clock (master)                                                                                                                 |

| J902 l thru 16<br>J902 l thru 16 | 5 to 6<br>7 to 8<br>9 to 10<br>11 to 12<br>13 to 14 | Interrupt 5 (MSC-9205C)<br>Interrupt 4 (Memory Parity Err<br>Interrupt 3 (Callan -83 FDC)<br>Interrupt 2 (spare)<br>Interrupt 1 (spare) |

## SYSTEM BOARD CONFIGURATION

## CHAPTER 9 MULTIBUS MOTHERBOARD CONFIGURATION GUIDE

#### 9.0 INTRODUCTION

This section provides a description of user configurable options available on the UNISTAR Multibus Motherboard. User options are configured by the installation of shunts or by wirewrap. Options affect bus arbitration and the use of the front panel reset and interrupt switches. For further information regarding operation and use of the Multibus refer to Intel document order number 98000683.

### 9.1

## MULTIBUS MOTHERBOARD AND PCBA CONFIGURATION

The physical location of boards installed in the Multibus motherboard using the standard factory configured parallel bus arbitration scheme (see section 9.3), is as follows: (Note that J6 is located toward the rear connector panel of the UNISTAR Unit).

Connector PCBA

| Jl | (spare)                         |

|----|---------------------------------|

| J2 | (spare)                         |

| J3 | Callan -83 FDC, Disk Controller |

| J4 | PM-68K, 68000 CPU               |

| J5 | MM-8086D/64, 64 Kilobyte RAM    |

| J6 | MSC-9205C, Disk Controller      |

9.2

#### SHUNT CONFIGURATION

Shuntconfiguration for the Multibus motherboard is factory installed for parallel priority bus arbitration, front panel interrupt disabled, an I/O address of 07FF Hex (status on DATAO), and with power supply 'low power sense' disabled, as follows:

| Shunt Designation                                                                                                                                                            | Position                                                                                                                                                                                                                                                                                                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13-14<br>15-16<br>A-B-C<br>D-E-F<br>G-H-I<br>J-K-L<br>M-N-O<br>P-Q-R<br>A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8 | l to 2<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Installed<br>Installed<br>B to C<br>E to F<br>H to I<br>K to L<br>N to O<br>Q to R<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed | <pre>(not used; Power Supply INIT/)<br/>(not used; PINTR/ to INT6/)<br/>(not used; PINTR/ to INT7/)<br/>(not used; PINTR/ to INT4/)<br/>(not used; PINTR/ to INT5/)<br/>(not used; PINTR/ to INT2/)<br/>(not used; PINTR/ to INT3/)<br/>(not used; PINTR/ to INT0/)<br/>(not used; PINTR/ to INT1/)<br/>INT Switch Status DAT0/ Sense<br/>Backplane I/O Address Enable<br/>J1 BPRN/ Parallel<br/>J2 BPRN/ Parallel<br/>J3 BPRN/ Parallel<br/>J4 BPRN/ Parallel<br/>J5 BPRN/ Parallel<br/>J6 BPRN/ Parallel<br/>I/O Address 0<br/>I/O Address 1<br/>I/O Address 3<br/>I/O Address 5<br/>I/O Address 5<br/>I/O Address 7<br/>I/O Address 7<br/>I/O Address 8</pre> |

| A9<br>AA                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                       | I/O Address 9<br>I/O Address A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AA                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |