Ę

G

$\frown$

HARDWARE REFERENCE MANUAL

# **REVISION RECORD**

| REVISION  | DESCRIPTION                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------|

| 01        | Preliminary release                                                                                 |

| (12-73)   |                                                                                                     |

| 02        | Major revision; this edition obsoletes previous edition.                                            |

| (3-74)    |                                                                                                     |

| 03        | Manual revised; includes manual corrections and engineering changes. Pages affected are:            |

| (8-74)    | v, 1-1, 2-1, 2-2, 2-5, 2-6, 2-13, 2-15, 2-17, 2-26 through 2-32, 3-1, 4-4, 4-5, 4-6, 4-9            |

|           | through 4-15, 4-39, 5-2, 5-6, 5-18, 5-29 through 5-39, 5-42, 5-44, 5-47, A-1 through A-5,           |

|           | A-7. Pages added: 2-28.1, 2-33, 2-34, 2-35.                                                         |

| А         | Manual released; this edition obsoletes all previous editions and publication no. 19981200.         |

| (5-9-75)  |                                                                                                     |

| В         | Manua 14, 5-5, and A-1 through                                                                      |

| (7-7-75)  | <u>A-10 </u>                                                                                        |

| С         | Manua ges 2-57 and 5-40 are revised                                                                 |

| (9-1-75)  |                                                                                                     |

| D         | This r                                                                                              |

| (11-1-76) |                                                                                                     |

| E         | Manual Manual Manual obsoletes all previous                                                         |

| (11-1-76) | edition 9983600, and includes                                                                       |

|           | the info                                                                                            |

| <u>F</u>  | Manual revised; includes Engineering Change Order 37879 which updates models 172 through 175        |

| (4-1-77)  | information and adds preliminary information for models 171 and 176. Because of extensive           |

|           | changes to this manual, chart tape and dots are not used, and all pages reflect the latest revision |

|           | level. This manual obsoletes all previous editions.                                                 |

| G         | Manual revised; includes Engineering Change Order 37761. Pages 3-3 and 3-4 are revised.             |

| (8-24-77) |                                                                                                     |

| <u>H</u>  | Manual revised; includes Engineering Change Orders 37767 and 37971. Adds information for            |

| (8-24-77) | models 171C through 175C. This edition obsoletes all previous editions.                             |

|           |                                                                                                     |

|           |                                                                                                     |

|           |                                                                                                     |

|           |                                                                                                     |

|           |                                                                                                     |

|           |                                                                                                     |

|           | •                                                                                                   |

| +         |                                                                                                     |

| ł-        |                                                                                                     |

|           |                                                                                                     |

## REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1973, 1974, 1975, 1976, 1977 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 Lexington Avenue North St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

])

Ì

# LIST OF EFFECTIVE PAGES

| 6             |

|---------------|

| •             |

| $\frown$      |

|               |

| $\frown$      |

|               |

| l             |

| $\frown$      |

| $\frown$      |

| $\frown$      |

| $\overline{}$ |

| $\frown$      |

| $\frown$      |

| $\frown$      |

|               |

|               |

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| Encent C                    |        | PAGE                 |        |                |        |              |        |              |              |

|-----------------------------|--------|----------------------|--------|----------------|--------|--------------|--------|--------------|--------------|

|                             |        |                      | REV    | PAGE           | REV    | PAGE         | REV    | PAGE         | REV          |

| Front Cover<br>Inside Cover | -      | 2-24                 | Н      | 3-28           | Н      | 4-58         | F      | 5-43         | H            |

| Title Page                  | -      | 2-25/2-26<br>Divider | Н      | 4-1/4-2        | F      | 4-59/4-60    | F      | 5-44         | Н            |

| ii                          | н      | 2-27                 | -      | Divider<br>4-3 | -      | Divider      |        | 5-45         | Н            |

| iii/iv                      | н      | 2-21                 | H      | 4-3            | F      | 4-61         | F      | 5-46         | Н            |

| v                           | H      | Divider              | H      | 4-4            | F<br>F | 4-62         | F      | 5-47         | H            |

| vi                          | H      | 2-29                 | F      | 4-5            | F      | 4-63         | F<br>F | 5-48         | Н            |

| vii                         | H      | 2-30                 | H      | 4-7            | F<br>F | 4-64         | F<br>F | Divider      | -            |

| viii                        | H      | Divider              | -      | 4-8            | г<br>Н | 4-65         | F<br>H | 5-49<br>5-50 | H<br>F       |

| ix                          | H      | 2-31                 | F      | 4-9            | F      | 4-67         | F      | 5-50         | F            |

| x                           | H      | 2-32                 | F      | 4-10           | F      | 4-68         | F      | 5-52         | F            |

| xi                          | H      | 2-33                 | H      | 4-11           | F      | 4-69         | F      | 5-53         | F            |

| 1-1/1-2                     | F      | 2-34                 | F      | 4-12           | F      | 4-70         | F      | 5-54         | F            |

| Divider                     |        | Divider              |        | 4-13           | F      | 4-71         | F      | 5-55         | H            |

| 1-3                         | н      | 2 - 35/2 - 36        | F      | 4-14           | F      | 4-72         | H      | 5-56         | F            |

| 1-4                         | н      | Divider              | -      | 4-15           | F      | 5-1/5-2      | H      | 5-57         | H            |

| 1-5                         | Н      | 2-37                 | F      | 4-16           | F      | Divider      | -      | 5-58         | H            |

| 1-6                         | Н      | 2-38                 | F      | 4-17           | F      | 5-3          | F      | 5-59         | F            |

| 1-7                         | Н      | Divider              | -      | 4-18           | F      | 5-4          | F      | 5-60         | H            |

| 1-8                         | H      | 2 - 39/2 - 40        | F      | 4-19           | F      | 5-5          | F      | 5-61         | F            |

| 1-9/1-10                    | н      | Divider              | -      | 4-20           | F      | 5-6          | F      | 5-62         | F            |

| Divider                     | -      | 2-41                 | F      | 4-21           | F      | 5-7          | F      | 5-63         | H            |

| 1-11                        | H      | 2-42                 | F      | 4-22           | F      | 5-8          | F      | 5-64         | H            |

| 1-12                        | H      | 2-43                 | F      | 4-23           | H      | 5-9          | F      | 5-65         | F            |

| 1-13                        | H      | 2-44                 | F      | 4-24           | F      | 5-10         | F      | 5-66         | H            |

| 1-14<br>1-15                | H      | Divider              | -      | 4-25           | F      | 5-11         | F      | 5-67/5-68    | $\mathbf{F}$ |

| 1-15                        | H      | 2-45                 | Н      | 4-26           | F      | 5-12         | F      | Divider      | -            |

| 1~10                        | H<br>H | 2-46<br>2-47         | H      | 4-27           | F      | 5-13         | F      | 5-69         | F            |

| 1-18                        | H      |                      | F      | 4-28           | F      | 5-14         | F      | 5-70         | F            |

| 1-19/1-20                   | H      | 3-1/3-2<br>Divider   | F<br>- | 4-29<br>4-30   | F      | 5-15         | F      | 5-71         | F            |

| Divider                     | -      | 3-3                  | G      | 4-30           | F<br>F | 5-16         | F      | 5-72         | H            |

| 1-21                        | н      | 3-4                  | G      | 4-31           | F<br>F | 5-17<br>5-18 | F<br>F | 5-73<br>5-74 | H            |

| 1-22                        | H      | 3-5                  | H      | 4-32           | H H    | 5-19         | F<br>F | 5-75         | H<br>F       |

| 1-23                        | H      | 3-6                  | F      | 4-34           | F      | 5-20         | F      | 5-76         | H H          |

| 1-24                        | н      | 3-7                  | Ĥ      | 4-35           | F      | 5-21/5-22    | F      | 5-77         | F            |

| 2-1/2-2                     | F      | 3-8                  | н      | 4-36           | F      | Divider      |        | 5-78         | F            |

| Divider                     | -      | 3-9                  | H      | 4-37           | F      | 5-23         | F      | 5-79         | H H          |

| 2-3                         | Н      | 3-10                 | Н      | 4-38           | F      | 5-24         | F      | 5-80         | H H          |

| 2-4                         | н      | 3-11                 | н      | 4-39           | F      | Divider      |        | 5-81         | H H          |

| 2-5                         | F      | 3-12                 | Н      | 4-40           | F      | 5-25         | Н      | 5-82         | F            |

| 2-6                         | F      | 3-13                 | H      | Divider        | -      | 5-26         | н      | 5-83         | F            |

| 2-7/2-8                     | F      | 3-14                 | Н      | 4-41           | Н      | 5-27         | Н      | A-1          | F            |

| Divider                     | -      | 3-15                 | Н      | 4-42           | F      | 5-28         | F      | B-1          | F            |

| 2-9<br>2-10                 | Н      | 3-16                 | Н      | 4-43           | F      | 5-29         | F      | B-2          | F            |

| 2-10                        | H      | Divider              | -      | 4-44           | F      | 5-30         | Н      | Index-1      | н            |

| 2-11                        | F      | 3-17                 | H      | 4-45           | F      | 5-31/5-32    | F      | Index-2      | Н            |

| 2-12                        | F      | 3-18                 | F      | 4-46           | F      | Divider      | -      | Comment      |              |

| 2-13                        | F<br>H | Divider              | -      | 4-47           | F      | 5-33         | F      | Sheet        | H            |

| 2-14                        | F      | 3-19                 | H      | 4-48           | F      | 5-34         | F      | Back Cover   | -            |

| 2-16                        | F      | 3-20                 | H      | 4-49           | F      | 5-35/5-36    | F      |              |              |

| Divider                     | г<br>- | 3-21<br>3-22         | H      | 4-50           | F      | Divider      | -      |              |              |

| 2-17                        | н      | 3-22                 | H      | 4-51           | F      | 5-37         | F      |              |              |

| 2-18                        | H      | 3-23                 | F      | 4-52           | F      | 5-38         | F      |              |              |

| 2-19                        | F      | 3-24                 | F      | 4-53           | F      | Divider      | -      |              |              |

| 2-20                        | Ĥ      | 3-25                 | H<br>F | 4-54           | F      | 5-39         | F      |              |              |

| 2-21/2-22                   | H      | Divider              | F -    | 4-55<br>4-56   | F<br>F | 5-40         | F      |              |              |

| Divider                     | -      | 3-27                 | н      | 4-56           | F      | 5-41         | F      |              |              |

| 2-23                        | н      | с <b>ш</b>           |        |                | г      | 5-42         | F      |              |              |

60420000 H

e C P ļ 1 (

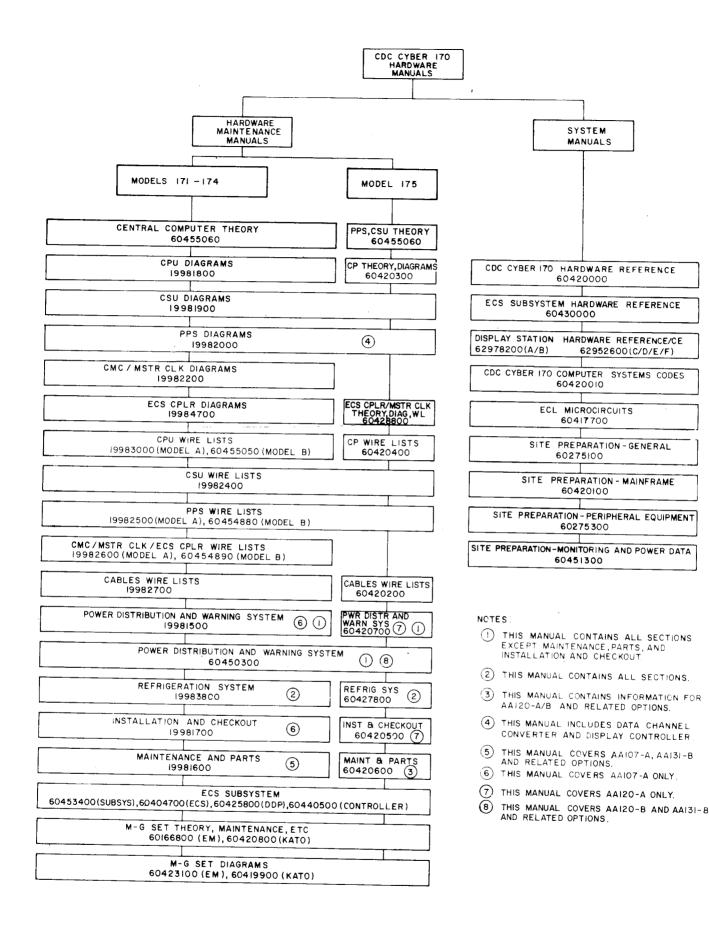

This manual contains hardware reference information for the CONTROL DATA® CYBER 170 Computer Systems, models 171 through 176. These model numbers are used throughout the manual to identify the reference information. In some parts of the manual, designators A, B, and C are used to identify information which is characteristic of systems produced after different production cut-in times. For instance, designator A relates to the original production models, B to later models, and C to the most recent models.

The manual describes the functional, operational, and programming characteristics of the computer systems hardware. Additional system hardware information is available for models 171 through 175 in the publications listed in the system publication index on the following page. Model 176 publications will be added to the index as they become available.

This manual is for use by customer, marketing, training, programming, and Engineering Services personnel who operate, program, and maintain the computer systems.

Publication ordering information and latest revision levels are available from the Literature Distribution Services catalog, publication number 90310500.

# CONTENTS

| 1. SYSTEM DESCRIPTIONS                 | 1 - 1      |

|----------------------------------------|------------|

| Introduction                           |            |

| Physical Characteristics               | 1-1        |

| Model 171 Configuration                | 1-3<br>1-4 |

| Model 172 Configuration                | 1-4        |

| Model 173 Configuration                | 1-4        |

| Model 174 Configuration                | 1-6        |

| . Model 175 Configuration              | 1-7        |

| Model 176 Configuration                | 1-9        |

| Functional Characteristics             | 1-11       |

| Model 171 System                       | 1-14       |

| Model 172 System                       | 1-15       |

| Model 173 System                       | 1-16       |

| Model 174 System                       | 1-17       |

| Model 175 System                       | 1-18       |

| Model 176 System                       | 1-19       |

| Major System Component Descriptions    | 1-21       |

| Central Processor - Models 171         |            |

| through 174                            | 1-21       |

| Central Processor - Models 175 and     |            |

| 176                                    | 1-21       |

| Central Memory - Models 171 through    |            |

| 176                                    | 1-22       |

| Extended Core Storage (Optional) -     |            |

| Models 171 through 175                 | 1-23       |

| Large Core Memory Extension - Model    |            |

| 176                                    | 1-23       |

| Peripheral Processor Units - Model     |            |

| 176                                    | 1-23       |

| Peripheral Processor Subsystem -       |            |

| Models 171 through 176                 | 1-24       |

| Display Station - Models 171 through   |            |

| 176                                    | 1 - 24     |

| Condensing Unit(s) - Models 171        |            |

| through 176                            | 1 - 24     |

| Power Distribution Unit - Model 176    | 1 - 24     |

|                                        |            |

|                                        |            |

| 2. FUNCTIONAL DESCRIPTIONS             | 2 - 1      |

|                                        |            |

| Central Processor - Models 171 through |            |

| 174                                    | 2-3        |

| Arithmetic Sections - Models 171       |            |

| through 174                            | 2-3        |

| Instruction Control Section - Models   |            |

| 171 through 174                        | 2-3        |

| Operating Registers - Models           |            |

| 171 through 174                        | 2-3        |

| Support Registers - Models 171         |            |

| through 174                            | 2-3        |

| Instruction Control Sequences -        |            |

| Models 171 through 174                 | 2-4        |

| Central Processor - Models 175 and 176 | 2-9        |

| Central Processing Unit - Models       |            |

| 175 and 176                            | 2-9        |

| Operating Registers - Models           |            |

| 175 and 176                            | 2-10       |

| Support Registers - Model 175          | 2 - 10     |

| Support Registers - Model 176          | 2-11       |

| Instruction Control Sequences -        |            |

| Models 175 and 176                     | 2 - 13     |

|                                        |            |

.

| Functional Units - Models 175 and                  |                    |

|----------------------------------------------------|--------------------|

| 176                                                | 2-15               |

| Boolean Unit                                       | 2-15               |

| Shift Unit                                         | 2 - 15             |

| Normalize Unit                                     | 2-15               |

| Floating-Add Unit                                  | 2-15               |

| Long Add Unit<br>Multiply Unit                     | 2-16               |

| Divide Unit                                        | 2-16<br>2-16       |

| Population-Count Unit                              | 2 - 16<br>2 - 16   |

| Increment Unit                                     | $\frac{2}{2} - 16$ |

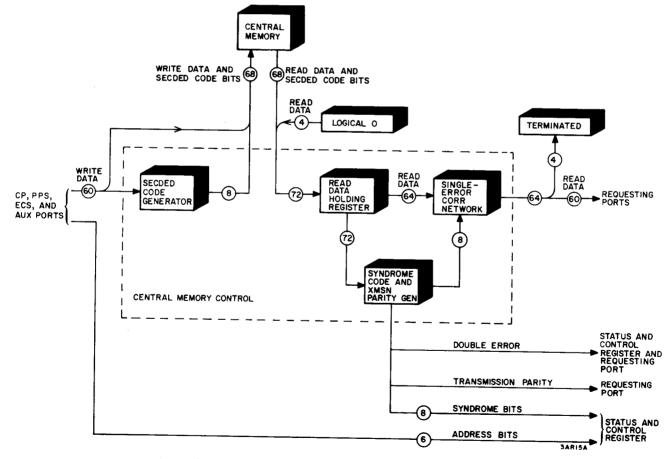

| Central Memory Control - Models 171                |                    |

| through 175                                        | 2 - 17             |

| Reference Priorities<br>SECDED Mode                | 2-17               |

| Error Detection and Response                       | 2-18               |

| Address Parity                                     | 2-20<br>2-20       |

| Data Parity                                        | 2-20               |

| Breakpoint Check                                   | 2 - 21             |

| Central Memory - Models 171 through 175            | 2 - 23             |

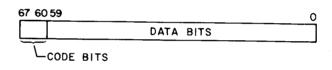

| Data Format                                        | 2 - 23             |

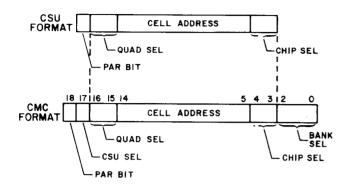

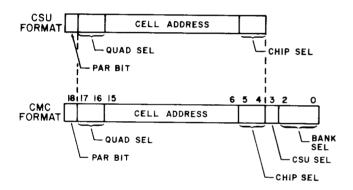

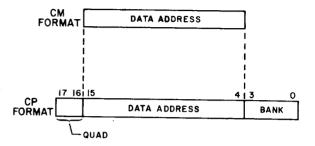

| Address Format                                     | 2 - 23             |

| Address Parity<br>Reference Operations             | 2-24               |

| Reference Operations<br>Reconfiguration            | 2-24               |

| Refresh Fault                                      | 2-24<br>2-25       |

| Central Memory - Model 176                         | 2 - 23<br>2 - 27   |

| Data Format                                        | 2-27               |

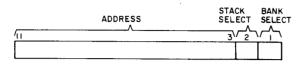

| Address Format                                     | 2-27               |

| SECDED Mode                                        | 2-27               |

| Parity Mode                                        | 2 - 28             |

| Maintenance Mode<br>Test Mode                      | 2-28               |

| Inhibit Log SBE Mode                               | 2-28               |

| Reconfiguration                                    | 2-28<br>2-28       |

| Large Core Memory Extension - Model 176            | 2-29               |

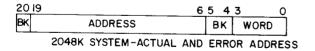

| Address Format                                     | 2-29               |

| SECDED Mode                                        | 2-29               |

| Parity Mode                                        | 2 - 29             |

| Maintenance Mode                                   | 2-30               |

| Test Mode                                          | 2 - 30             |

| Inhibit Log SBE Mode                               | 2-30               |

| Test Complement Mode<br>Block Copies               | 2 - 30             |

| Direct (Single-Word) Transfers                     | 2-30<br>2-30       |

| Bank Selection                                     | 2-30               |

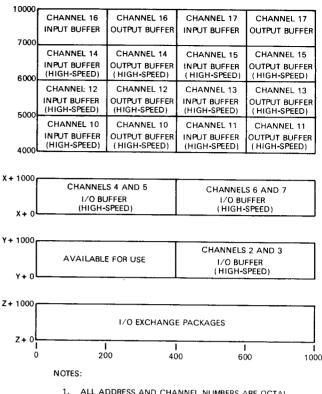

| Input/Output Multiplexer - Model 176               | 2-31               |

| Normal PPU to CM Data Transfer                     | 2-32               |

| Normal CM to PPU Data Transfer                     | 2 - 32             |

| High-Speed PPU to CM Data Transfer                 | 2 - 33             |

| High-Speed CM to PPU Data Transfer                 | 2-33               |

| Logic Scanner - Model 176                          | 2-35               |

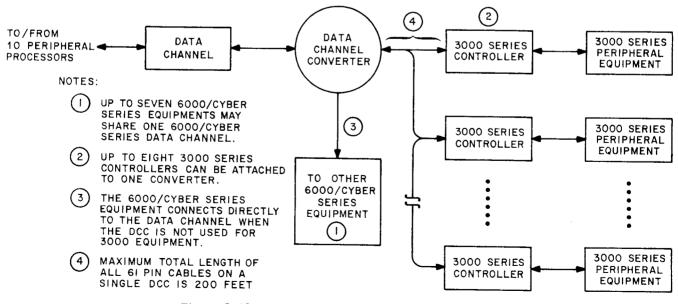

| Data Channel Converter - Models 171 through<br>176 |                    |

| 3000 Series Interrupt Feature                      | 2 - 37<br>2 - 37   |

| 3000 Power Failure Mode                            | 2 - 38             |

| Buffer Flushing                                    | 2-38               |

| Display Controller - Models 171 through            |                    |

| 176                                                | 2 - 39             |

| Peripheral Processor Units - Model 176             | 2-41               |

| Computation Section                                | 2-41               |

| A Register<br>P Register                           | 2-41               |

| i negister                                         | 2 - 41             |

N ....

· . . .

| Q Register                                       | 2 <b>-</b> 41 |

|--------------------------------------------------|---------------|

| X Register                                       | 2-41          |

| Sk Register                                      | 2-41          |

| fd Register<br>k Register                        | 2-41<br>2-41  |

| PPU Memory                                       | 2-41          |

| PPU Input/Output                                 | 2-42          |

| Input Channel Control                            | 2-42          |

| Output Channel Control                           | 2-42          |

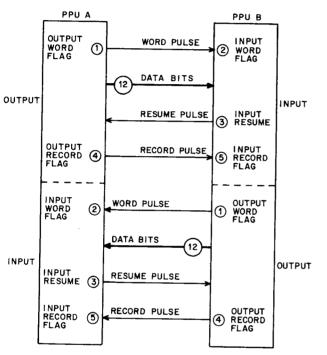

| PPU to PPU Data Transfers                        | 2-42          |

| PPU to Peripheral Equipment Data                 |               |

| Transfers                                        | 2-44          |

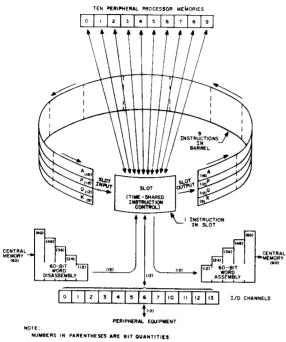

| Peripheral Processor Subsystem - Models          |               |

| 171 through 176                                  | 2-45          |

| Real-Time Clock<br>Deadstart                     | 2-45          |

| PP Memory                                        | 2-45<br>2-45  |

| Barrel and Slot                                  | 2-45          |

| A Register                                       | 2-46          |

| P Register                                       | 2-46          |

| Q Register                                       | 2-46          |

| K Register                                       | 2-46          |

| PP Input/Output                                  | 2 - 47        |

| Status and Control Register                      | 2 - 47        |

|                                                  |               |

| 3. OPERATING INSTRUCTIONS                        | 3 - 1         |

|                                                  | 0 1           |

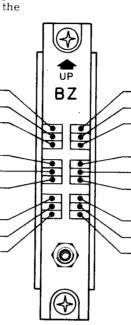

| Controls and Indicators - Models 171             |               |

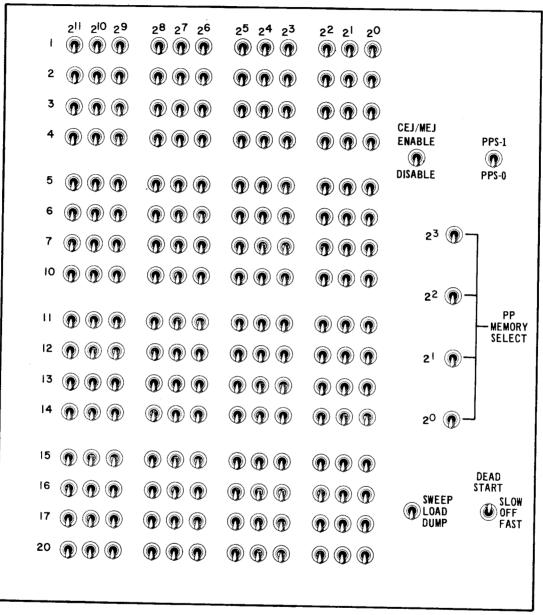

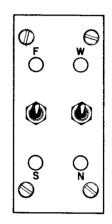

| through 174<br>Deadstart Panel                   | 3-3           |

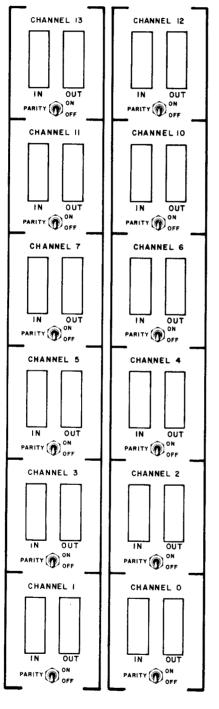

| I/O Channel Parity Switches                      | 3-3<br>3-5    |

| ECS Parity Switch                                | 3-5           |

| Clock Selection Switches and Indicators          | 3-5           |

| CSU Maintenance Switches                         | 3-7           |

| P Register and Status Bit Selection              | 01            |

| Switches                                         | 3-7           |

| Keyboard Display Selection Switches              | 3-8           |

| Power Sense Monitor Indicators                   | 3-8           |

| Status and Control Register Indicators           | 3-9           |

| CPU Instruction Register and P                   |               |

| Register Indicators                              | 3-13          |

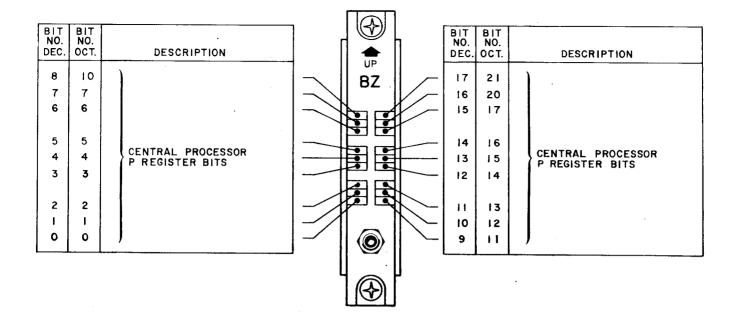

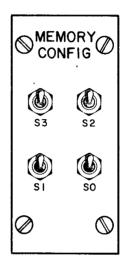

| CM Configuration and SECDED/Parity               |               |

| Mode Switches                                    | 3-14          |

| Controls and Indicators - Model 175              | 3-17          |

| Deadstart Panel<br>I/O Channel Parity Switches   | 3-17          |

| ECS Parity Switch                                | 3-17<br>3-17  |

| Clock Selection Switches and Indicators          | 3-17          |

| CSU Maintenance Switches                         | 3-17          |

| P Register and Status Bit Selection              | 0-11          |

| Switches                                         | 3-17          |

| Keyboard Display Selection Switches              | 3-17          |

| Power Sense Monitor Indicators                   | 3-17          |

| Status and Control Register Indicators           | 3 - 17        |

| CM Configuration and Clock Switches              |               |

| and Indicators                                   | 3-17          |

| Controls and Indicators - Model 176              | 3-19          |

| Deadstart Panel                                  | 3 - 19        |

| I/O Channel Parity Switches                      | 3-19          |

| P Register and Status Bit Selection<br>Switches  | 0 10          |

| Keyboard Display Selection Switches              | 3-19<br>3-19  |

| CP Clock Frequency Selection Switches            | 3-19          |

| and Indicators                                   | 3-19          |

| PPS Clock Frequency Selection                    | 0 10          |

| Switch                                           | 3-20          |

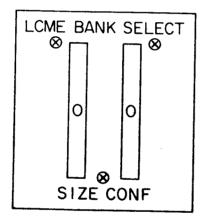

| CM Configuration Switches                        | 3-20          |

| LCME Bank Selection Switches                     | 3 - 21        |

| Power Sense Monitor Indicators                   | 3 - 21        |

| PPS-0 Status and Control Register                |               |

| Indicators<br>PPS-1 Status and Control Deviators | 3-22          |

| PPS-1 Status and Control Register<br>Indicators  | 3-25          |

|                                                  |               |

| Power-On and Power-Off Procedures -<br>Models 171 through 176<br>Operating Procedures - Models 171 through<br>176  | 3 - 2 7<br>3 - 2 7                   |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Control Checks<br>Deadstart Program Selection<br>Deadstart<br>Load Mode                                            | 3-27<br>3-27<br>3-27<br>3-27<br>3-27 |

| Sweep Mode<br>Dump Mode                                                                                            | 3 - 2 7<br>3 - 2 8                   |

| 4. INSTRUCTION DESCRIPTIONS                                                                                        | 4 - 1                                |

| Central Processor Instructions - Models<br>171 through 176                                                         | 4-3                                  |

| CP Instruction Formats<br>CP Instruction Descriptions<br>CP Instruction Timing - Models 171<br>through 174         | 4-3<br>4-5<br>4-31                   |

| CP Instruction Timing - Model 175<br>CP Instruction Timing - Model 176<br>Peripheral Processor Unit Instructions - | 4-31<br>4-34<br>4-37                 |

| Model 176<br>PPU Instruction Formats<br>PPU Instruction Designators                                                | 4-41<br>4-42                         |

| PPU Instruction Addressing Modes<br>No Address                                                                     | 4-42<br>4-42<br>4-42                 |

| Constant Address<br>Direct Address                                                                                 | 4 - 42<br>4 - 42                     |

| Indirect Address<br>Indexed Direct Address                                                                         | 4-43<br>4-43                         |

| PPU Instruction Descriptions<br>PPU Instruction Timing<br>Peripheral Processor Subsystem                           | 4-44<br>4-57                         |

| Instructions - Models 171 through 176<br>PPS Instruction Descriptions<br>PPS Instruction Timing                    | 4 - 6 1<br>4 - 6 1<br>4 - 7 1        |

| 5. PROGRAMMING INFORMATION                                                                                         | 5-1                                  |

| Central Processor Programming<br>Exchange Jump - Models 171 through<br>175                                         | 5-3                                  |

| Exchange Jump - Model 176                                                                                          | 5-3<br>5-4                           |

| Exchange Exit Instructions<br>Error Exit                                                                           | 5-5                                  |

| Input/Output Interrupt                                                                                             | 5-5<br>5-6                           |

| Real-Time Interrupt<br>Step Mode                                                                                   | 5-6                                  |

| Operating Characteristics - Models                                                                                 | 5-6                                  |

| 171, 172, or 174 with Two CPs<br>Operating Characteristics - Model 176<br>Instruction Execution - Models 171       | 5-6<br>5-6                           |

| through 174<br>Instruction Execution - Models 175 and<br>176                                                       | 5-7<br>5-8                           |

| Floating-Point Arithmetic - Models<br>171 through 176                                                              | 5-9                                  |

| Format                                                                                                             | 5-9                                  |

| Packing<br>Overflow                                                                                                | 5-9<br>5 <b>-</b> 10                 |

| Underflow                                                                                                          | 5-10                                 |

| Indefinite<br>Nonstandard Operands                                                                                 | 5-10                                 |

| Normalized Numbers                                                                                                 | 5-10<br>5-12                         |

| Rounding                                                                                                           | 5-12                                 |

| Double-Precision Results<br>Fixed-Point Arithmetic - Models 171<br>through 176                                     | 5-12<br>5-13                         |

| Integer Arithmetic - Models 171<br>through 176                                                                     | 5-13                                 |

~

\_\_\_\_\_

/

/

/

----

| Compare/Move Arithmetic - Models       |        |

|----------------------------------------|--------|

| 171 through 174                        | 5-13   |

| Processing Differences                 | 5-14   |

| Multiply Differences                   | 5 - 14 |

| Floating-Add Differences               | 5-14   |

| Floating-Divide Condition              |        |

| Differences                            | 5-15   |

| Round-Divide Differences               | 5-15   |

| Instructions 22 and 23 Differences     | 5-15   |

| Illegal Instructions - Models 171      |        |

| through 175                            | 5-15   |

| Exit Mode/Error Response - Models      |        |

| 171 through 175                        | 5-15   |

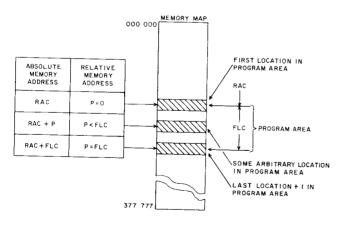

| Central Memory Programming             | 5 - 23 |

| Central Memory - Models 171            |        |

| through 175                            | 5-23   |

| Central Memory - Model 176             | 5 - 23 |

| Breakpoint - Models 171 through 175    | 5 - 24 |

| Data Channel Converter Programming     | 5 - 25 |

| Codes                                  | 5 - 25 |

| Function Codes                         | 5 - 25 |

| Status Reply Codes                     | 5 - 27 |

| Selecting the Data Channel Converter   | 5 - 27 |

| Deselecting the Data Channel Converter | 5 - 27 |

| Connecting to 3000 Series Equipment    | 5 - 27 |

| Mode I Connect                         | 5-28   |

| Mode II Connect                        | 5-28   |

| Sending Function Codes to 3000 Series  |        |

| Equipment                              | 5 - 29 |

| Mode I Function                        | 5 - 29 |

| Mode II Function                       | 5 - 29 |

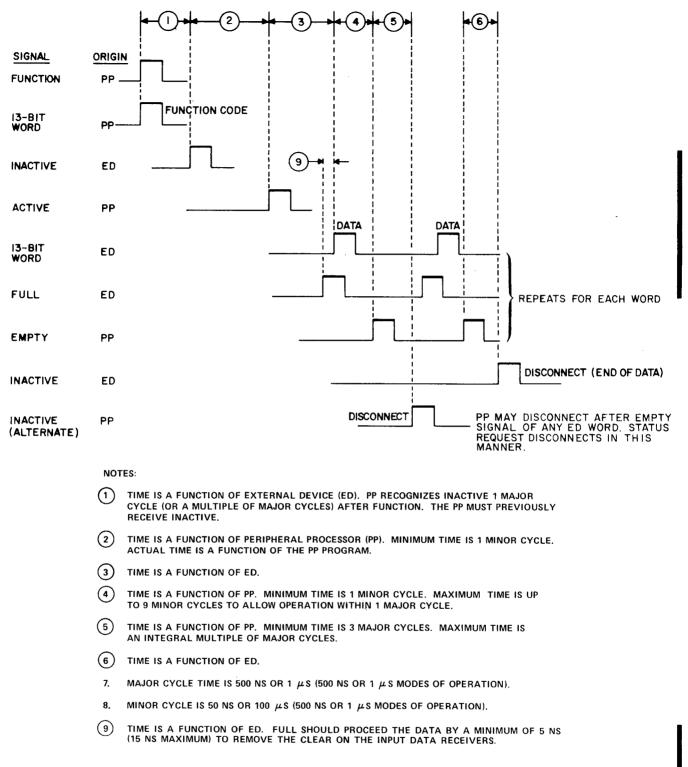

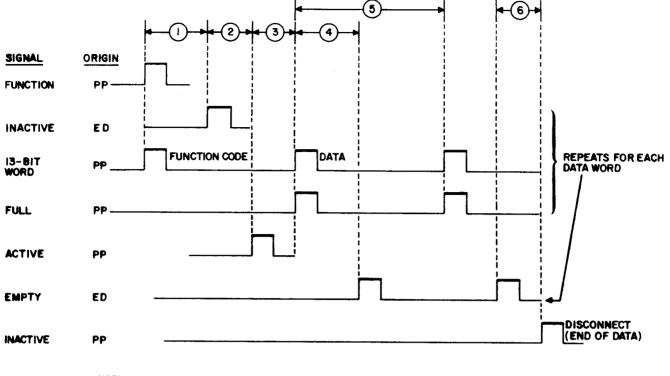

| Data Transfer                          | 5-30   |

| Input Operation                        | 5-30   |

| Output Operation                       | 5-30   |

| Parity Checking                        | 5-30   |

| Function Codes from PPS to DCC         | 5-30   |

| Data from PPS to DCC                   | 5-31   |

| Data from DCC to PPS                   | 5-31   |

|                                        | APF    |

|                                        |        |

| Status Words from DCC to PPS<br>Clearing a Parity Error<br>Display Station Programming<br>Keyboard<br>Data Display<br>Character Mode<br>Dot Mode | 5-31<br>5-33<br>5-33<br>5-33<br>5-33<br>5-33<br>5-33 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Codes                                                                                                                                            | 5 - 34                                               |

| Programming Example                                                                                                                              | 5 - 34                                               |

| Programming Timing Consideration                                                                                                                 | 5 - 34                                               |

| Peripheral Processor Unit Programming -<br>Model 176                                                                                             | - 05                                                 |

|                                                                                                                                                  | 5-37                                                 |

| Restrictions on Instruction Loops                                                                                                                | 5-37                                                 |

| Programming Considerations                                                                                                                       | 5-37                                                 |

| Control Signals<br>Data Signals                                                                                                                  | 5-38                                                 |

| Sequence Timing                                                                                                                                  | 5-38                                                 |

| Peripheral Processor Programming                                                                                                                 | 5-38<br>5-39                                         |

| Central Memory Read                                                                                                                              | 5-39                                                 |

| Central Memory Write                                                                                                                             | 5-39                                                 |

| Channel Description                                                                                                                              | 5-39                                                 |

| Channel Signal Description                                                                                                                       | 5-39<br>5-39                                         |

| Channel Operation                                                                                                                                | 5-35<br>5-41                                         |

| Channel Conflicts in a Basic PPS                                                                                                                 | 5 - 43                                               |

| 2X Operating Speed                                                                                                                               | 5-43                                                 |

| 1X Operating Speed                                                                                                                               | 5-43                                                 |

| Channel Conflicts in an Expanded                                                                                                                 | 0 10                                                 |

| System                                                                                                                                           | 5-43                                                 |

| 2X Operating Speed                                                                                                                               | 5-43                                                 |

| 1X Operating Speed                                                                                                                               | 5 - 43                                               |

| Inter-PP Communication of I/O                                                                                                                    |                                                      |

| Control                                                                                                                                          | 5 - 44                                               |

| Input/Output Transfers                                                                                                                           | 5-44                                                 |

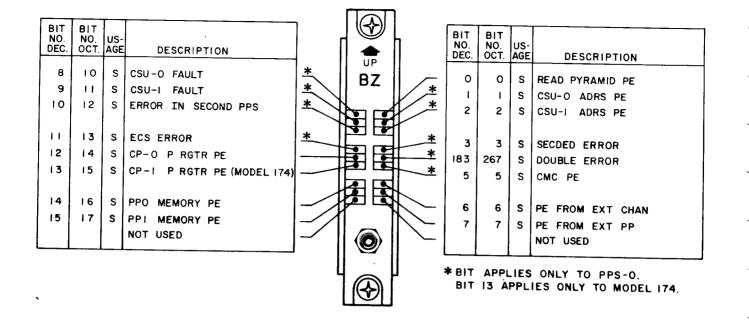

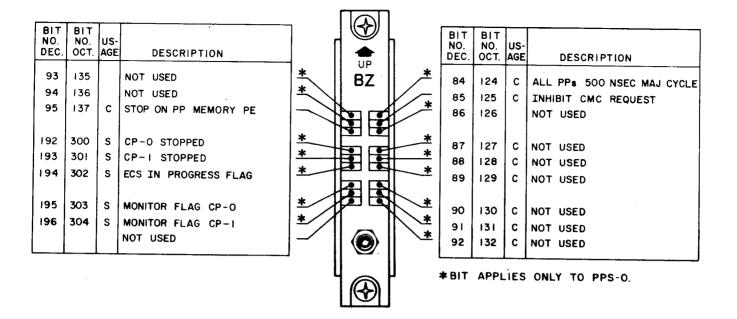

| Status and Control Register Bit Descrip-                                                                                                         |                                                      |

| tions - Models 171 through 175                                                                                                                   | 5-49                                                 |

| Status and Control Register Bit Descrip-                                                                                                         |                                                      |

| tions - Model 176                                                                                                                                | 5-69                                                 |

|                                                                                                                                                  |                                                      |

### **APPENDIXES**

А Glossary

.

× ....

A - 1

B Models 175 and 176 Differences B-1

## INDEX

## **FIGURES**

| 1-1  |                                    | 1 - 1 | 1-12 | Model 174 C |

|------|------------------------------------|-------|------|-------------|

| 1-2  | Model 171 Maximum Chassis Configu- |       | 1-13 | Model 175 C |

|      | ration (Top Cutaway View)          | 1-4   | 1-14 | Model 176 C |

| 1-3  | Model 172 Maximum Chassis Configu- |       | 2-1  | Models 175  |

|      | ration (Top Cutaway View)          | 1-5   |      | tion Flow   |

| 1-4  | Model 173 Maximum Chassis Configu- |       | 2-2  | PSD Registe |

|      | ration (Top Cutaway View)          | 1-5   | 2-3  | SECDED Ne   |

| 1-5  | Model 174 Maximum Chassis Configu- |       |      | (SECDED ]   |

|      | ration (Top Cutaway View)          | 1-6   | 2-4  | CMC Error   |

| 1-6  | Models 175 A and B Maximum Chassis |       | 2-5  | Models 171  |

|      | Configuration (Top Cutaway View)   | 1-7   |      | Format      |

| 1-7  | Model 175C Maximum Chassis Con-    |       | 2-6  | Models 171  |

|      | figuration (Top Cutaway View)      | 1-8   |      | Formats     |

| 1-8  | Model 176 Maximum Chassis Configu- |       | 2-7  | Model 175 C |

|      | ration (Top Cutaway View)          | 1-9   | 2-8  | Model 176 C |

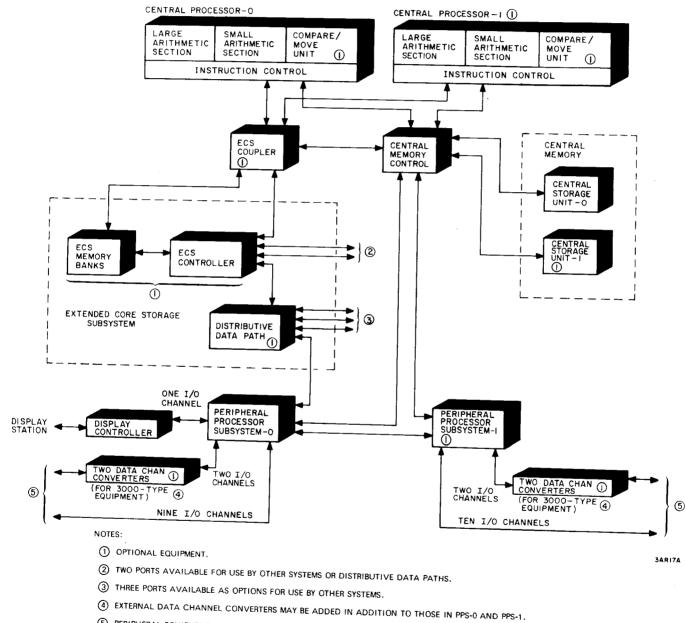

| 1-9  | Model 171 Computer System          | 1-14  | 2-9  | Model 176 L |

| 1-10 | Model 172 Computer System          | 1-15  |      |             |

| 1-11 | Model 173 Computer System          | 1-16  |      |             |

|      |                                    |       |      |             |

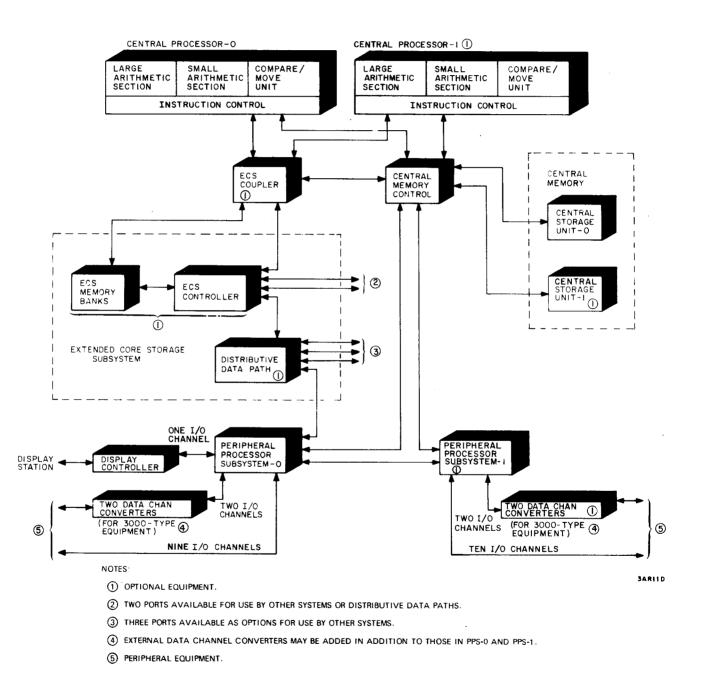

| 1 - 12 | Model 174 Computer System         | 1 - 17             |

|--------|-----------------------------------|--------------------|

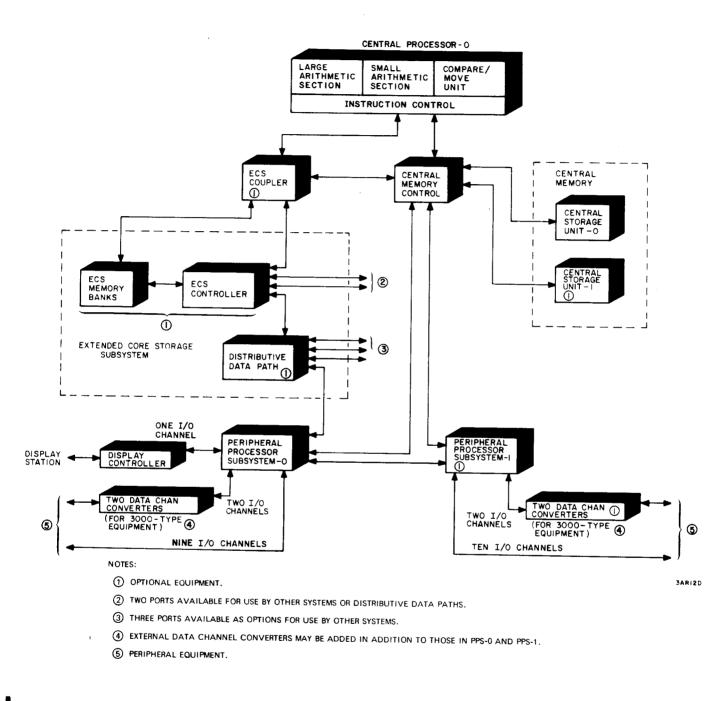

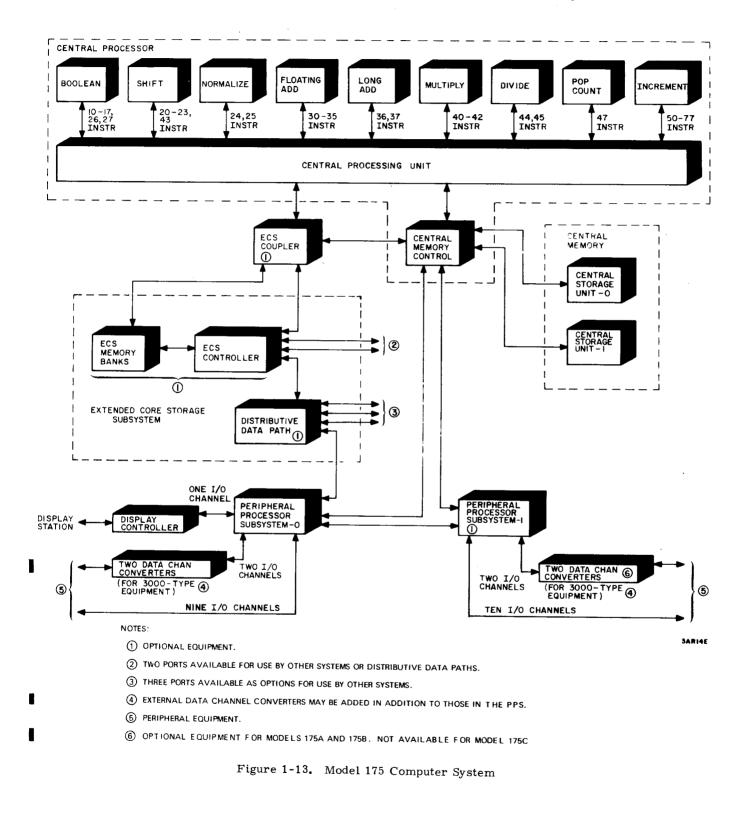

| 1-13   | Model 175 Computer System         | 1-18               |

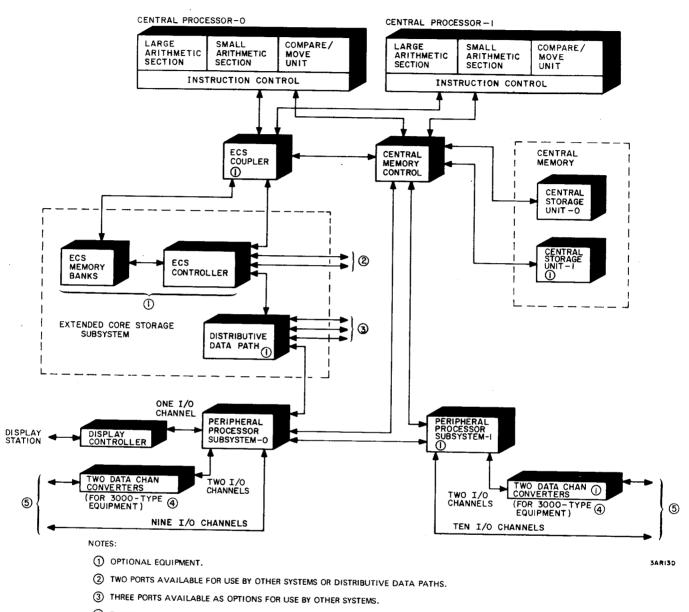

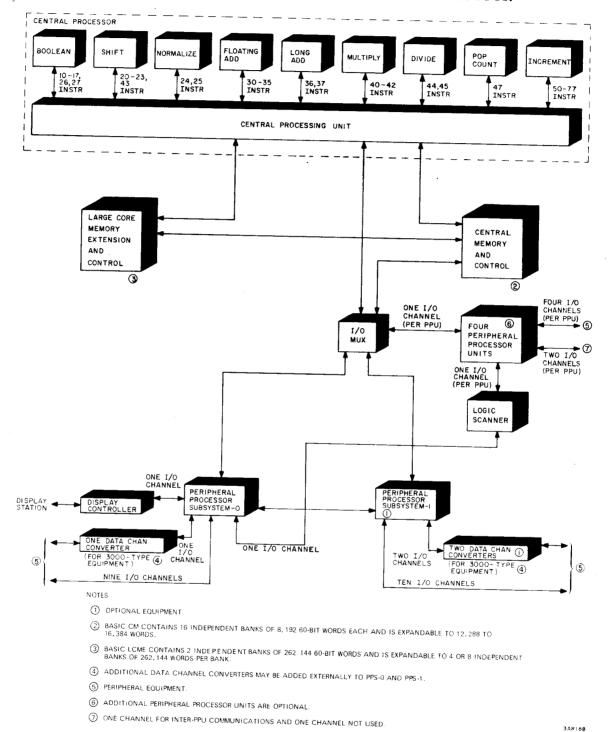

| 1-14   | Model 176 Computer System         | 1-19               |

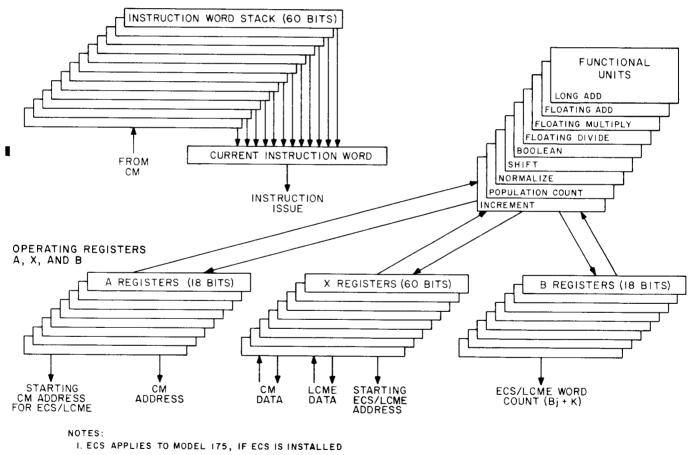

| 2-1    | Models 175 and 176 CPU Informa-   |                    |

|        | tion Flow                         | 2-9                |

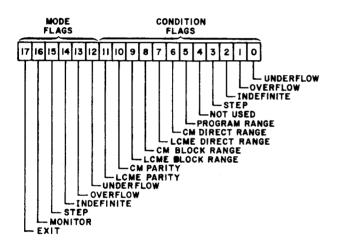

| 2-2    | PSD Register Flag Bit Arrangement | 2 - 12             |

| 2-3    | SECDED Network Block Diagram      |                    |

|        | (SECDED Mode)                     | 2-18               |

| 2-4    | CMC Error Communications          | 2-20               |

| 2-5    | Models 171 through 175 CM Data    |                    |

|        | Format                            | 2 - 23             |

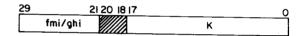

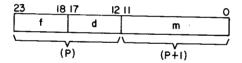

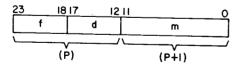

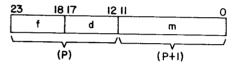

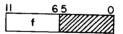

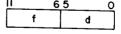

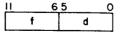

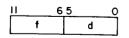

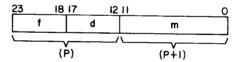

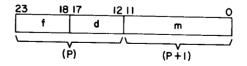

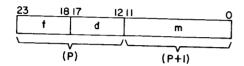

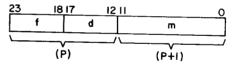

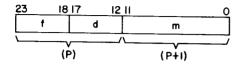

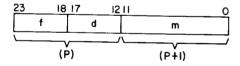

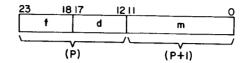

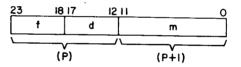

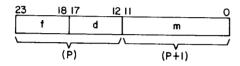

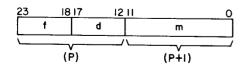

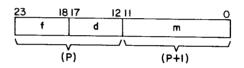

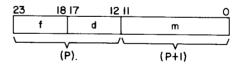

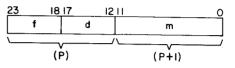

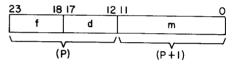

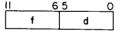

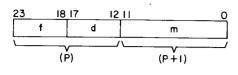

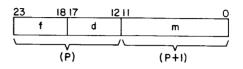

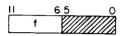

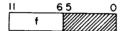

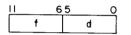

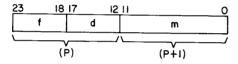

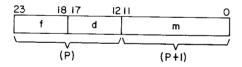

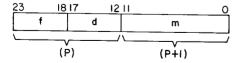

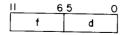

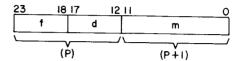

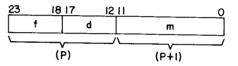

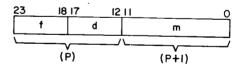

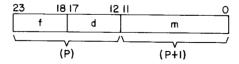

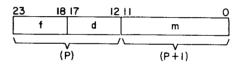

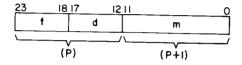

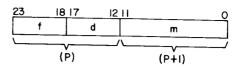

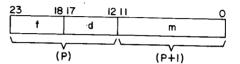

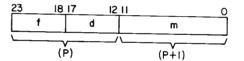

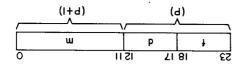

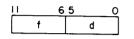

| 2-6    | Models 171 through 174 CM Address |                    |

|        | Formats                           | 2 - 24             |

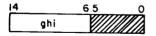

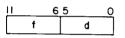

| 2-7    | Model 175 CM Address Formats      | 2 - 24             |

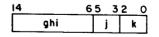

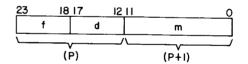

| 2-8    | Model 176 CM Address Format       | $\frac{1}{2}$ - 27 |

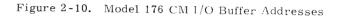

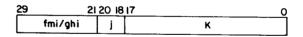

| 2-9    | Model 176 LCME Address Format     | 2-29               |

|        |                                   | . =0               |

| $2 - 10 \\ 2 - 11$ | Model 175 CM 1/O Buffer Addresses<br>Model 176 CM 1/O Exchange Package | 2 - 31           |

|--------------------|------------------------------------------------------------------------|------------------|

| 2-12               | Areas<br>Data Channel Converter                                        | 2-31             |

|                    | Configuration                                                          | 0.05             |

| 2-13               | PPU/PPU Communications                                                 | 2-37<br>2-43     |

| 2 - 14             | Barrel and Slot Operation                                              | 2 - 45<br>2 - 46 |

| 3 - 1              | Deadstart Panel - Models 171                                           | 2-40             |

|                    | through 176                                                            | 3-3              |

| 3-2                | Typical I/O Channel Parity Switches<br>for PPS                         | 3-5              |

| 3-3                | Module at 4B34 - Models 171                                            |                  |

|                    | through 174                                                            | 3-5              |

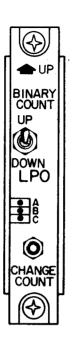

| 3-4                | Module at 4R39 - Models 171                                            | 5-5              |

|                    | through 174                                                            | 3-6              |

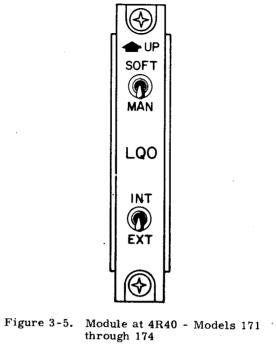

| 3-5                | Module at 4R40 - Models 171                                            | 3-0              |

|                    | through 174                                                            | 3-6              |

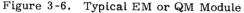

| 3-6                | Typical EM or QM Module                                                | 3-7              |

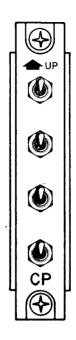

| 3-7                | Modules at 2J40 and 6J40 - Models                                      | 01               |

|                    | 171 through 174                                                        | 3-7              |

| 3-8                | Modules at 2P38 and 2R36 - Models                                      | 0 1              |

|                    | 171 through 174                                                        | 3-8              |

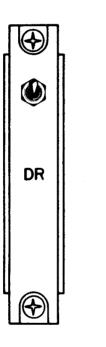

| 3-9                | PL Module                                                              | 3-9              |

| 3-10               | PM Module                                                              | 3-9              |

| 3-11               | Module at PPS F19 - Models 171                                         |                  |

| 0.40               | through 175                                                            | 3-10             |

| 3-12               | Module at PPS F22 - Models 171                                         |                  |

| 0 10               | through 175                                                            | 3-10             |

| 3-13               | Module at PPS F25 - Models 171                                         |                  |

| 3-14               | through 175                                                            | 3-11             |

| 9-14               | Module at PPS F28 - Models 171<br>through 175                          |                  |

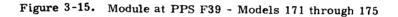

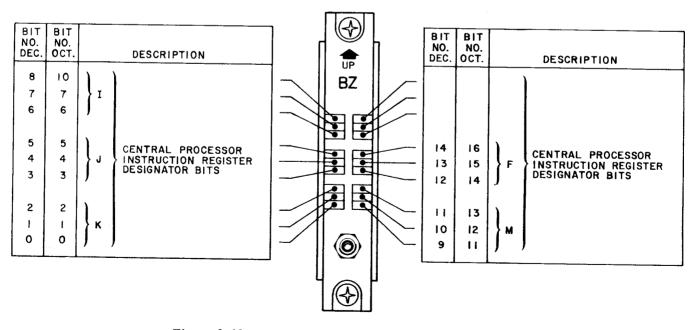

| 3-15               | Module at PPS F39 - Models 171                                         | 3-11             |

| 0 10               | through 175                                                            | 0 10             |

| 3-16               | Module at PPS F42 - Models 171                                         | 3-12             |

|                    | through 175                                                            | 0 10             |

| 3-17               | Module at PPS H33 - Models 171                                         | 3-12             |

|                    | through 175                                                            | 3-13             |

| 3-18               | Modules at 1C21 - Models 171                                           | 0 10             |

|                    | through 173 and at 5C21 - Model                                        |                  |

|                    | 174                                                                    | 3-13             |

| 3-19               | Modules at 1K38 - Models 171                                           | 0 10             |

|                    | through 173 and at 5K38 - Model                                        |                  |

|                    | 174                                                                    | 3-14             |

| 3-20               | Modules at 4N24 and 4N25 - Models                                      | -                |

|                    | 171 through 174                                                        | 3-14             |

| 3-21               | Controls on Modules 5A1 through                                        |                  |

| 0 00               | 5A3 - Model 175                                                        | 3-17             |

| 3-22               | Switches and Indicators on Module                                      |                  |

|                    | at 7M06 - Model 176                                                    | <b>3 -</b> 19    |

|                    |                                                                        |                  |

| 3-23   | Module at 2R29 - Model 176                               | 11 A A |

|--------|----------------------------------------------------------|--------|

| 3-24   | Switches on Module at 8K14 - Model                       | 3-20   |

|        | 176                                                      | 3-20   |

| 3-25   | Modules at 2B42 and 4B42 - Model                         | 0 20   |

| 3-26   |                                                          | 3-21   |

| 3-26   | Module at 2F19 - Model 176                               | 3-22   |

| 3-28   | Module at 2F22 - Model 176                               | 3-22   |

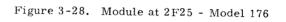

| 3-20   | Module at 2F25 - Model 176                               | 3-23   |

| 3-30   | Module at 2F28 - Model 176                               | 3-23   |

| 3-31   | Module at 2F39 - Model 176                               | 3-24   |

| 3-32   | Module at 2F42 - Model 176                               | 3-24   |

| 3-33   | Module at 2H33 - Model 176                               | 3-25   |

| 3-34   | Module at 4F22 - Model 176<br>Module at 4F25 - Model 176 | 3-25   |

| 3-35   | Module at 4H33 - Model 176                               | 3-26   |

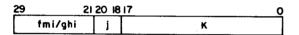

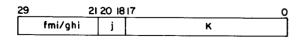

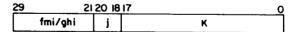

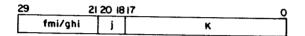

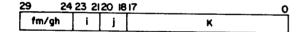

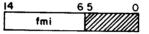

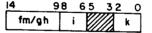

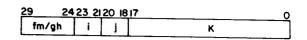

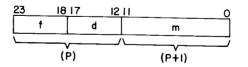

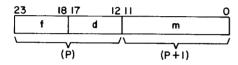

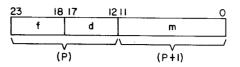

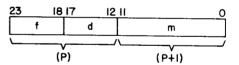

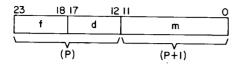

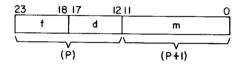

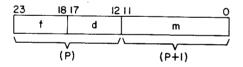

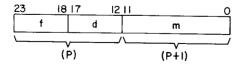

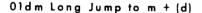

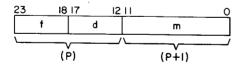

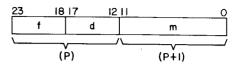

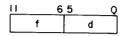

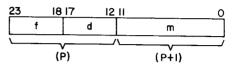

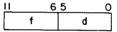

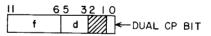

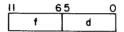

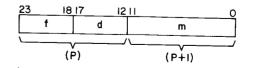

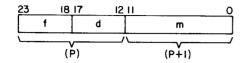

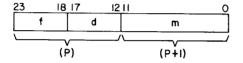

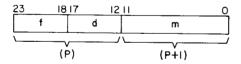

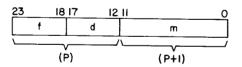

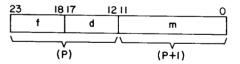

| 4-1    | CP Instruction Parcel Arrangement                        | 3-26   |

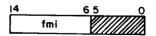

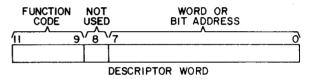

| 4-2    | Descriptor Word Format                                   | 4-3    |

| 4-3    | Compare/Move Instruction Format                          | 4-26   |

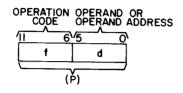

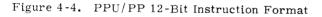

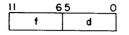

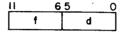

| 4-4    | PPU/PP 12-Bit Instruction Format                         | 4-27   |

| 4-5    | PPU/PP 24-Bit Instruction Format                         | 4-42   |

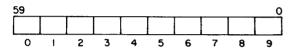

| 5-1    | Exchange Package - Models 171                            | 4-42   |

| 0 1    | through 175                                              |        |

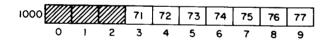

| 5-2    | Exchange Package - Model 176                             | 5-3    |

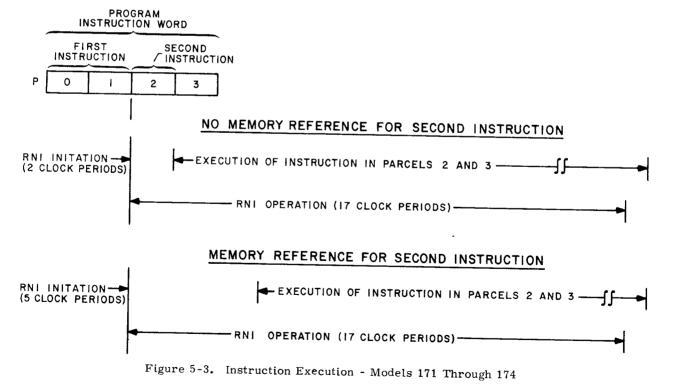

| 5-3    | Instruction Execution - Models                           | 5-5    |

| 00     | 171 through 174                                          |        |

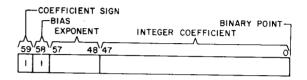

| 5-4    | Floating-Point Format                                    | 5-7    |

| 5-5    | Floating-Add Result Format                               | 5-9    |

| 5-6    | Multiply Result Format                                   | 5-12   |

| 5-7    | Format of Relative Address Zero                          | 5-12   |

|        | on Error Exit - Models 171                               |        |

|        | through 175                                              | 5-16   |

| 5-8    | Memory Map - Models 171 through                          | 3-10   |

|        | 175                                                      | 5-23   |

| 5-9    | Memory Map - Model 176                                   | 5-23   |

| 5-10   | DCC Connect Code Format                                  | 5-28   |

| 5-11   | Display Station Output Function Code                     | 5-34   |

| 5 - 12 | Coordinate Data Word                                     | 5-34   |

| 5-13   | Character Data Word                                      | 5-34   |

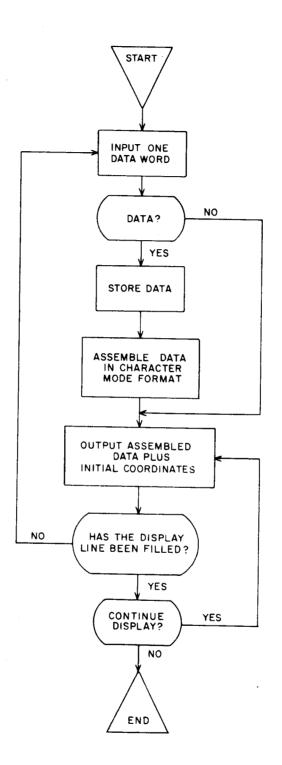

| 5-14   | Receive and Display Program                              | 0 04   |

|        | Flowchart                                                | 5-35   |

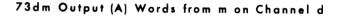

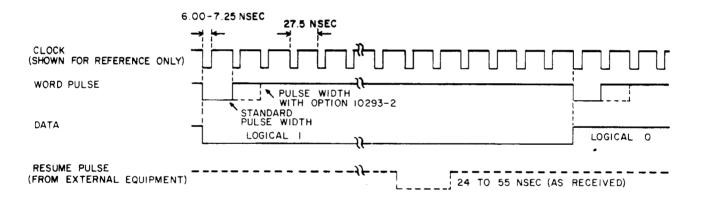

| 5-15   | Output Channel Timing                                    | 5-38   |

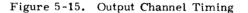

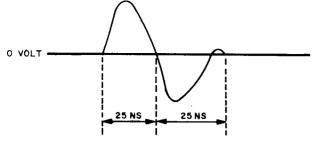

| 5-16   | Input Channel Timing                                     | 5-38   |

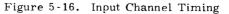

| 5-17   | Channel Output Pulse Characteristics                     | 5-40   |

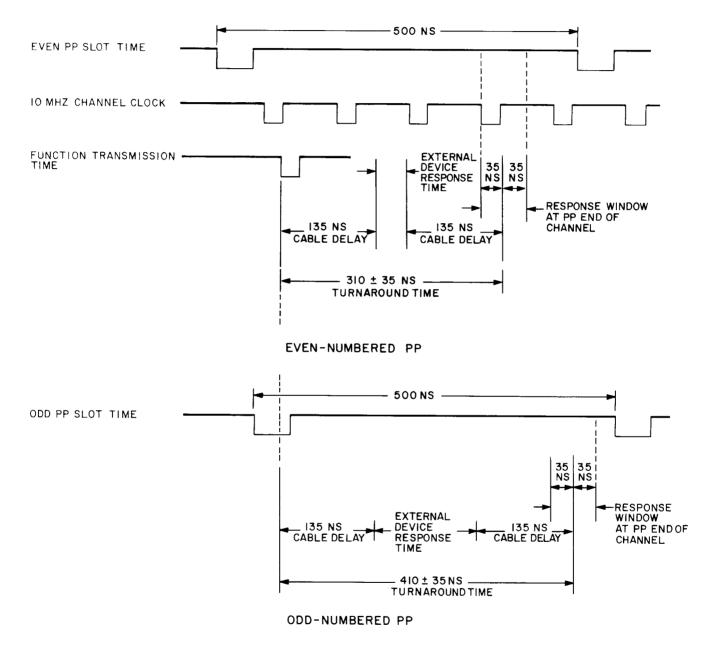

| 5-18   | Channel Transfer Timing                                  | 5-42   |

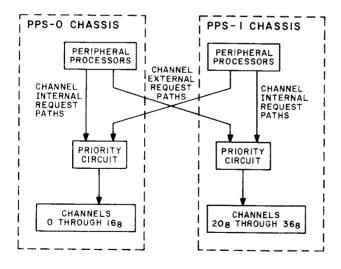

| 5-19   | PP Channel Request Paths                                 | 5-43   |

| 5-20   | Data Input Sequence Timing                               | 5-45   |

| 5-21   | Data Output Sequence Timing                              | 5-46   |

| 5-22   | CP Chassis Quadrants (Viewed from                        | - 10   |

|        | Module Side) - Model 175                                 | 5-65   |

|        |                                                          |        |

/

----

١

1

~

$\checkmark$

-

-

~

/

/

1

~

/

# TABLES

| 1-1 | CDC CYBER 170 System                                    |      | 2-2 | ] |

|-----|---------------------------------------------------------|------|-----|---|

| 1-2 | Components<br>Central Processor Functional              | 1-3  | 2-3 | ľ |

|     | Characteristics                                         | 1~11 | 2-4 | I |

| 1-3 | Central Memory Functional                               |      | 2-5 | ľ |

| 1-4 | Characteristics<br>Peripheral Processor Subsystem       | 1-11 | 3-1 | Ι |

|     | Functional Characteristics                              | 1-12 | 3-2 | Ŧ |

| 1-5 | Peripheral Processor Unit                               |      | 0 - |   |

| 1-6 | Functional Characteristics<br>Data and Address Checking | 1-12 | 3-3 | C |

| -   | Functional Characteristics                              | 1-13 | 3-4 | F |

| 2-1 | SECDED Syndrome Codes/                                  |      | 0 1 | T |

|     | Corrected Bits                                          | 2-19 |     |   |

| 2-2   | Breakpoint Control Translations    | 2 - 21 |

|-------|------------------------------------|--------|

| 2-3   | Models 171 through 174 Central     |        |

| _     | Memory Sizes                       | 2-23   |

| 2-4   | Model 175 Central Memory Sizes     | 2-23   |

| 2-5   | Model 176 Central Memory Sizes     | 2 - 27 |

| 3 - 1 | Deadstart Panel Functions - Models |        |

|       | 171 through 176                    | 3-4    |

| 3-2   | Functions of Modules at 4R39 and   |        |

|       | 4R40 - Models 171 through 174      | 3-6    |

| 3-3   | CSU Maintenance Switch             | 0 0    |

|       | Functions                          | 3-7    |

| 3-4   | Functions of Modules at 2J40 and   | 0 1    |

|       | 6J40 - Models 171 through 174      | 3-8    |

|       |                                    | 0 0    |

60420000 H

| • | x |

|---|---|

| - |   |

| 3-5        | Functions of Module at 4N24 -        |        |

|------------|--------------------------------------|--------|

|            | Models 171 through 174               | 3-15   |

| 3-6        | Functions of Module at 4N25 -        |        |

|            | Models 171 through 174               | 3-15   |

| 3-7        | Memory Selection Scheme - Models     |        |

|            | 171 through 174                      | 3-16   |

| 3-8        | Functions of Controls on Modules     |        |

|            | 5A1 through 5A3 - Model 175          | 3-18   |

| 3-9        | Memory Selection Scheme - Model      |        |

|            | 175                                  | 3-18   |

| 3-10       | Functions of Switches and Indicators | 0 10   |

|            | on Module at 7M06 - Model 176        | 3-19   |

| 3-11       | Memory Selection Scheme - Model      | 0 10   |

| •          | 176                                  | 3-20   |

| 3-12       | Functions of Switches on Modules     | 3-20   |

| • ••       | at 5H14 and 5H15 - Model 176         | 3-21   |

| 4 - 1      | Central Processor Instruction        | 5-21   |

|            | Designators                          | 4-4    |

| 4-2        | Collating Table                      |        |

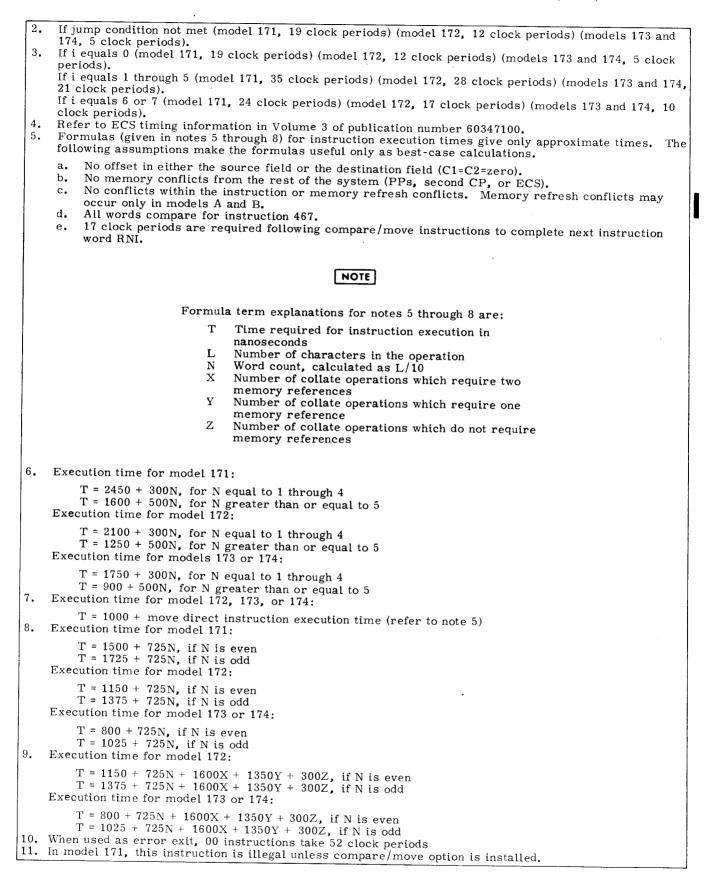

| 4-3        | CP Instruction Timing - Models       | 4 - 27 |

| τJ         | 171 through 174                      | 4 0 1  |

| 4-4        |                                      | 4-31   |

| 4-5        | CP Instruction Timing - Model 175    | 4-34   |

| 4-3<br>4-6 | CP Instruction Timing - Model 176    | 4-37   |

| 4-0        | PPU and PP Instruction Differences   | 4-41   |

|            | PPU and PP Instruction Designators   | 4 - 42 |

| 4-8        | PPU and PP Instruction Addressing    |        |

|            | Modes                                | 4-43   |

| 4-9        | PPU Instruction Timing               | 4-57   |

| 4-10       | PPS Instruction Timing               | 4-71   |

| 5-1        | Bits 58 and 59 Configurations        | 5-9    |

|            |                                      |        |

|   | 5-2  | Xj Plus Xk (30, 32, 34 Instructions)   | 5-11   |

|---|------|----------------------------------------|--------|

|   | 5-3  | Xj Minus Xk (31, 33, 35                |        |

|   |      | Instructions)                          | 5-11   |

|   | 5-4  | Xj Multiplied by Xk (40, 41, 42        |        |

|   |      | Instructions)                          | 5-11   |

|   | 5-5  | Xj Divided by Xk (44, 45 Instructions) | 5 - 12 |

|   | 5-6  | CP Program Interrupt Conditions -      |        |

|   |      | Models 171 through 175                 | 5-16   |

|   | 5-7  | Error Response with CEJ/MEJ            |        |

|   |      | Enabled, MF Set - Models 171           |        |

|   |      | through 175                            | 5-16   |

|   | 5-8  | Error Response with CEJ/MEJ            |        |

|   |      | Enabled, MF Clear - Models 171         |        |

|   |      | through 175                            | 5-18   |

|   | 5-9  | Error Response with CEJ/MEJ            |        |

|   |      | Disabled - Models 171 through          |        |

|   |      | 175                                    | 5-20   |

|   | 5-10 | Keyboard Character Codes               | 5-33   |

|   | 5-11 | Display Character Codes                | 5-34   |

|   | 5-12 | I/O Cable Line Characteristics         | 5-40   |

|   | 5-13 | Data Channel Coaxial Cable Lines       | 5-41   |

|   | 5-14 | Channel Conflict Conditions at 2X      |        |

|   |      | Operating Speed                        | 5-43   |

|   | 5-15 | Descriptor Word Function Codes         | 5-47   |

| ļ | 5-16 | Status and Control Register Bit        | · ·    |

|   |      | Assignments - Models 171               |        |

|   |      | through 175                            | 5-49   |

| 4 | 5-17 | Status and Control Register Bit        | 0 40   |

|   |      | Assignments - Model 176                | 5-69   |

|   |      |                                        | 0-09   |

·----

This section introduces the CDC CYBER 170 Computer Systems, gives physical and functional characteristics, and provides descriptions of major system components.

## INTRODUCTION

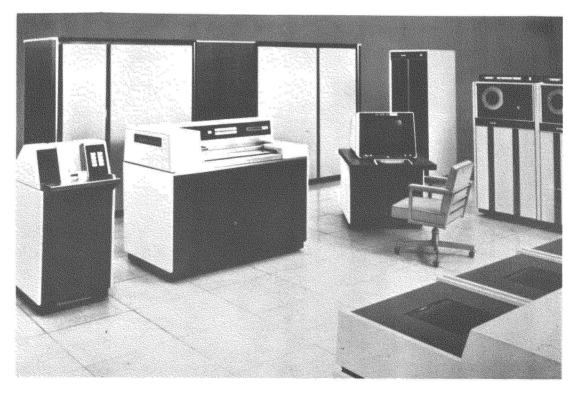

The CDC CYBER 170 systems (figure 1-1) include models 171 through 176. These are general purpose digital computer systems that provide varying degrees of processing power, data storage, and input/output (I/O) capabilities.

Depending upon options and design differences, the systems include one or more of the following components.

- Central processor (CP)

- Central memory control (CMC) in models 171 through 175 and memory control in model 176

- Central memory (CM), includes one or two central storage units (CSUs) in models 171 through 175 and small semiconductor memory (SSM) in model 176

- Large core memory extension (LCME) in model 176

- Extended core storage (ECS), optional, in models 171 through 175

- Peripheral processor subsystem (PPS), includes 10 peripheral processors (PPs)

- Peripheral processor units (PPUs) in model 176

- Data channel converter (DCC)

- Display station

- Condensing unit(s)

- Power distribution unit (PDU)

Table 1-1 provides a comparison of the individual systems on a component level. In some systems, one or more of the components is duplicated. In such cases, manual references to the components by name or abbreviations are followed by a -0 or -1 for identification. For example, model 174 contains central processor -0 (CP-0) and central processor -1 (CP-1).

Figure 1-1. Typical CDC CYBER 170 System

PHYSICAL CHARACTERISTICS

/ ノ  $\smile$ / / / / / /

## **PHYSICAL CHARACTERISTICS**

Many components of the system models are functionally the same or similar. For these components, the manual provides a common description. Components with different functions have individual descriptions that are identified by the system model number (table 1-1).

| Company 1                                                                                  |     |     | ·   | dels |     | r   |

|--------------------------------------------------------------------------------------------|-----|-----|-----|------|-----|-----|

| Components                                                                                 | 171 | 172 | 173 | 174  | 175 | 176 |

| Mainframe:                                                                                 |     |     |     |      |     |     |

| Central processor-0                                                                        | x   | x   | x   | x    | x   | x   |

| Central processor-1                                                                        | *   | 柴   | -   | x    | -   | -   |

| Compare/move unit for CP-0                                                                 | *   | x   | x   | x    | -   | -   |

| Compare/move unit for CP-1 (optional compare/move<br>unit must be installed for model 171) | *   | x   | -   | x    | -   | -   |

| Central memory control                                                                     | x   | x   | x   | x    | x   | -   |

| Memory control                                                                             | -   | -   | -   | -    | -   | x   |

| Central memory, eight banks in CSU-0                                                       | x   | x   | x   | x    | x   | -   |

| Central memory, eight banks in CSU-1                                                       | *   | *   | *   | *    | x   | -,  |

| Central memory, 16 banks                                                                   | -   | -   | -   | -    | -   | x   |

| Peripheral processor subsystem-0                                                           | x   | x   | x   | x    | x   | x   |

| Peripheral processor subsystem-1                                                           | *   | *   | *   | *    | *   | *   |

| Peripheral processor units                                                                 | -   | -   | -   | -    | -   | x   |

| I/O multiplexer                                                                            | -   | -   | -   | -    | -   | x   |

| Logic scanner                                                                              | -   | -   | -   | -    | -   | x   |

| One data channel converter for PPS-0                                                       | *   | -   | -   | -    | -   | x   |

| Two data channel converters for PPS-0                                                      | *   | x   | x   | x    | x   | -   |

| Two data channel converters for PPS-1                                                      | *   | 水   | *   | *    | *   | *   |

| Display controller                                                                         | x   | x   | x   | x    | x   | x   |

| Extended core storage coupler                                                              | *   | *   | *   | *    | *   | -   |

| One 3-ton internally mounted condensing unit                                               | x   | x   | x   | -    | -   | -   |

| Two 3-ton internally mounted condensing units                                              | *   | **  | *   | x    | -   | -   |

| Large core memory extension                                                                | -   | -   | -   | -    | -   | x   |

| Extended core storage subsystem                                                            | *   | *   | *   | *    | *   | -   |

| One 10-ton externally mounted condensing unit                                              | -   | -   | -   | -    | x   | *   |

| Two 10-ton externally mounted condensing units                                             | -   | -   | -   | -    | -   | x   |

| Power distribution unit                                                                    | -   | -   | -   | -    | -   | x   |

| Display station (first)                                                                    | x   | x   | x   | x    | x   | x   |

| Display station (second)                                                                   | *   | *   | *   | 25   | *   | *   |

| Standard                                                                                   |     |     |     |      | ]   |     |

| TABLE 1-1. CDC | CYBER | 170 SYSTEM | COMPONENTS |

|----------------|-------|------------|------------|

|----------------|-------|------------|------------|

The following model configurations describe the physical arrangements of cabinets, bays, and chassis in basic and maximally configured systems. Additional physical characteristics of the computer systems are on data sheets in the CDC CYBER 170 Section 2 Site Preparation Manual, listed in the preface. The data sheets include separate descriptions of the mainframe models, associated condensing units, and display station. The sheets also include weight, power consumption, and certain code requirements.

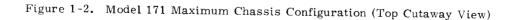

#### MODEL 171 CONFIGURATION

The model 171 basic configuration (figure 1-2) includes a display station and mainframe bay 1, which contains a condensing unit and four chassis for logic and memory modules. The maximum configuration includes a second mainframe bay 2. This bay contains a second condensing unit and up to three chassis for additional logic and memory modules. Installation of the optional ECS requires the addition of a stand-alone cabinet for a controller and from one to four cabinets for the ECS, depending upon the options.

#### MODEL 172 CONFIGURATION

The model 172 basic configuration (figure 1-3) includes a display station and mainframe bay 1, which contains a condensing unit and four chassis for logic and memory modules. This configuration is the maximum configuration of the original model 172 system. Development of additional equipment options makes later model 172 systems available in a maximum configuration that includes a mainframe bay 2. This bay contains a second condensing unit and up to three chassis for additional logic and memory modules. Installation of the optional ECS requires the addition of a stand-alone cabinet for a controller and from one to four cabinets for the ECS, depending upon the options.

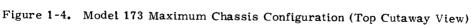

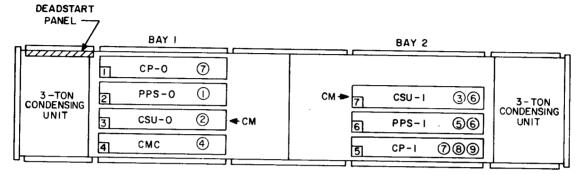

#### MODEL 173 CONFIGURATION

The model 173 basic configuration (figure 1-4) includes a display station and mainframe bay 1, which contains a condensing unit and four chassis for logic and memory modules. The maximum configuration includes a mainframe bay 2. This bay contains a second condensing unit and up to two chassis for additional logic and memory modules. Installation of the optional ECS requires the addition of a stand-alone cabinet for a controller and from one to four cabinets for the ECS, depending upon the options.

NOTES:

- () CHANNEL 2 ALSO CONTAINS A DISPLAY STATION CONTROLLER.

- ② CSU-0 IS EXPANDABLE FROM 65, 536 TO 98.304 TO 131, 072 WORDS.

- ③ CSU-1 EXPANDS MEMORY TO 196,608 TO 262,144 WORDS

- (4) WHEN ECS IS INSTALLED, CHASSIS 4 ALSO CONTAINS THE ECS COUPLER.

- (5) CHASSIS 2 AND 6 MAY EACH CONTAIN TWO OPTIONAL CHANNEL CONVERTERS.

- 6 BAY 2 AND CHASSIS 5, 6, AND 7 ARE OPTIONAL.

- ⑦ CHASSIS 1 AND 5 MAY EACH CONTAIN AN OPTIONAL COMPARE/MOVE UNIT.

- (8) IF CHASSIS 5 IS INSTALLED AND CHASSIS 7 IS NOT INSTALLED, CHASSIS 5 MOUNTS IN THE CHASSIS 7 LOCATION.

6A A 208

DEADSTART PANEL

7777777

3 -TON CONDENSING

UNIT

PANEL

mm

3 -TON CONDENSING

UNIT

NOTES:

NOTES:

BAY I

$\overline{7}$

$\bigcirc$

2

(4)

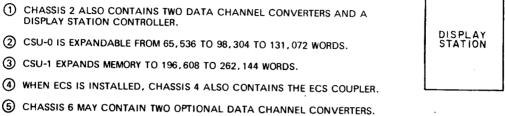

() CHASSIS 2 ALSO CONTAINS TWO DATA CHANNEL CONVERTERS AND A

(2) CSU-0 IS EXPANDABLE FROM 65, 536 TO 98, 304 TO 131, 072 WORDS.

(3) CSU-1 EXPANDS MEMORY TO 196,608 TO 262,144 WORDS.

(6) BAY 2 AND CHASSIS 5. 6, AND 7 ARE OPTIONAL.

BAY I

CP

PPS-0

Π

2

🗲 СМ

CP-0

PPS-0

CSU-0

СМС

DISPLAY STATION CONTROLLER.

2

3

4

- (4) WHEN ECS IS INSTALLED, CHASSIS 4 ALSO CONTAINS THE ECS COUPLER.

- (5) CHASSIS 6 MAY CONTAIN TWO OPTIONAL DATA CHANNEL CONVERTERS.

- (6) BAY 2 AND CHASSIS 6 AND 7 ARE OPTIONAL.

() CHASSIS 1 ALSO CONTAINS A COMPARE/MOVE UNIT.

- 3 CSU-1 EXPANDS MEMORY TO 196,608 TO 262,144 WORDS.

- ① CHASSIS 2 ALSO CONTAINS TWO DATA CHANNEL CONVERTERS AND A DISPLAY STATION CONTROLLER.

- (2) CSU-0 IS EXPANDABLE FROM 65, 536 TO 98, 304 TO 131, 072 WORDS.

- 2 31 CSU-0 🗲 СМ (4) CMC 4

$\bigcirc$

$\bigcirc$

DEADSTART

6

СМ 🖷

6

Figure 1-3. Model 172 Maximum Chassis Configuration (Top Cutaway View)

6

СМ 🔶

7

6

5

⑦ CHASSIS 1 AND 5 EACH CONTAIN A COMPARE/MOVE UNIT. IF CHASSIS 5 IS INSTALLED AND CHASSIS 7 IS NOT INSTALLED, CHASSIS 5 MOUNTS IN THE CHASSIS 7 LOCATION.

36

56

678

BAY 2

CSU-I

PPS-I

CP-I

BAY 2

CSU-I

PPS-I

36

66

64430

3 - TON CONDENSING

UNIT

6AA4D

3 - TON CONDENSING

UNIT

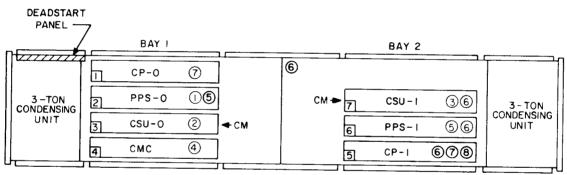

### MODEL 174 CONFIGURATION

The model 174 basic configuration (figure 1-5) includes a display station and mainframe bays 1 and 2, which contain two condensing units, four chassis in bay 1, and one chassis in bay 2. The maximum configuration includes up to two additional chassis in bay 2 for logic and memory modules. Installation of the optional ECS requires the addition of a stand-alone cabinet for a controller and from one to four cabinets for the ECS, depending upon the options.

NOTES:

- () CHASSIS 2 ALSO CONTAINS TWO DATA CHANNEL CONVERTERS AND A DISPLAY STATION CONTROLLER.

- (2) CSU-0 IS EXPANDABLE FROM 65, 536 TO 98, 304 TO 131, 072 WORDS.

- ③ CSU-1 EXPANDS MEMORY TO 196,608 TO 262,144 WORDS.

- ④ WHEN ECS IS INSTALLED, CHASSIS 4 ALSO CONTAINS THE ECS COUPLER.

- ⑤ CHASSIS 6 MAY CONTAIN TWO OPTIONAL DATA CHANNEL CONVERTERS.

- 6 CHASSIS 6 AND 7 ARE OPTIONAL.

- () CHASSIS 1 AND 5 EACH CONTAIN A COMPARE/MOVE UNIT.

- (8) CP-1 MAY MOUNT IN CHASSIS 7 LOCATION, IF CSU-1 AND PPS-1 CHASSIS ARE NOT INSTALLED.

- (9) IF CHASSIS 5 IS INSTALLED AND CHASSIS 7 IS NOT INSTALLED, CHASSIS 5 MOUNTS IN THE CHASSIS 7 LOCATION.

Figure 1-5. Model 174 Maximum Chassis Configuration (Top Cutaway View)

6AA5E

#### MODEL 175 CONFIGURATION

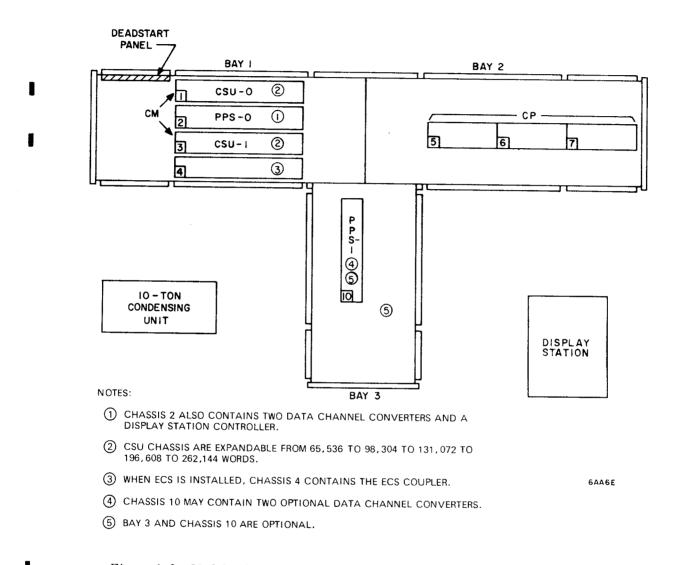

The models 175 A and B basic configuration (figure 1-6) includes a display station, a stand-alone condensing unit, and mainframe bays 1 and 2, which contain four chassis in bay 1 and three chassis in bay 2. The maximum configuration includes one additional chassis in bay 3. Installation of the optional ECS requires the addition of a stand-alone cabinet for a controller and from one to four cabinets for the ECS, depending upon the options.

Figure 1-6. Models 175A and B Maximum Chassis Configuration (Top Cutaway View)

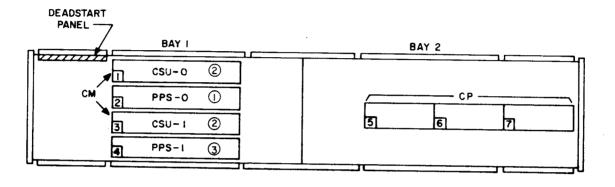

The model 175C basic configuration (figure 1-7) includes a display station, a stand-alone condensing unit, and mainframe bays 1 and 2, which contain four chassis in bay 1 and three chassis in bay 2. The maximum configuration has the same bays

and chassis except for options added to the chassis. Installation of the optional ECS requires the addition of a stand-alone cabinet for a controller and from one to four cabinets for the ECS, depending upon the options.

Figure 1-7. Model 175C Maximum Chassis Configuration (Top Cutaway View)

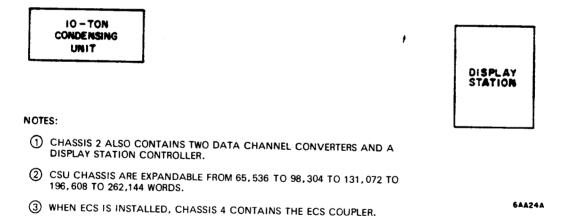

#### MODEL 176 CONFIGURATION

The model 176 basic configuration (figure 1-8) includes a display station, two condensing units, a stand-alone cabinet with one chassis, and nine mainframe chassis. The maximum configuration includes one additional condensing unit, one additional chassis in the stand-alone cabinet, and five additional mainframe chassis.

Figure 1-8. Model 176 Maximum Chassis Configuration (Top Cutaway View)

FUNCTIONAL CHARACTERISTICS

/

# FUNCTIONAL CHARACTERISTICS

r

Tables 1-2 through 1-6 summarize the functional characteristics of the CP, CM, PPS, and data address and checking for each system.

| Example 1 cu                                                   | Models |     |     |     |     |     |  |  |

|----------------------------------------------------------------|--------|-----|-----|-----|-----|-----|--|--|

| Functional Characteristics                                     | 171    | 172 | 173 | 174 | 175 | 176 |  |  |

| 60-bit internal word                                           | x      | x   | х   | x   | x   | x   |  |  |

| Computation in fixed- and floating-point arithmetic            | x      | x   | х   | x   | x   | x   |  |  |

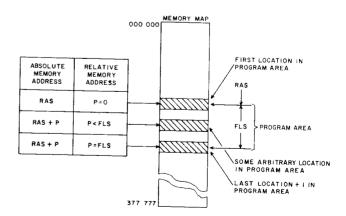

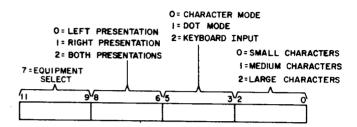

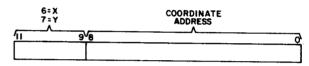

| Eight 60-bit operand X registers                               | x      | x   | х   | х   | х   | x   |  |  |