# SERIAL PORT CONTROLLER MANUAL

CGC 7900 SERIES COLOR GRAPHICS COMPUTERS

CHROMATICS CGC 7900 Series

Serial Port Controller Application Guide

# CHROMATICS

# CGC 7900 SERIES COLOR GRAPHICS COMPUTER SYSTEM

SERIAL PORT CONTROLLER (SPC) APPLICATION GUIDE

Copyright (c) 1982 by Chromatics, Inc. 2558 Mountain Industrial Boulevard Tucker, Georgia 30084

> Phone (404) 493-7000 TWX 810-766-8099

> > May, 1982

#### INTRODUCTION

This Application Guide describes the Serial Port Controller, or SPC, an optional card in Chromatics' CGC 7900 series. The SPC is designed to handle low-level data communications chores in the 7900 system, for up to 4 RS-232 ports.

By relieving the main CPU of the burden of handshaking and buffering, the SPC can greatly enhance system throughput. The SPC contains its own Z80 processor, and firmware which runs the normal "read character, write character" operations. This Application Guide is intended for the user who wants to customize SPC firmware for special purposes. We will discuss the SPC architecture, and provide programming examples.

This document is written for the experienced programmer. The SPC firmware is written in Z80 assembly language, and you will need access to a Z80 assembler and development system, or a compiler capable of generating Z80 code. For high-speed applications, running one or more ports at high baud rates, you will probably have to write the majority of the firmware directly in assembly language for efficiency. Current SPC firmware was developed on Chromatics' CG series color graphic computer systems.

We will begin by describing the SPC, its architecture, and how it operates in a standard CGC 7900 system. From there, we will proceed to the advanced features of the hardware, including some which are not normally used (but are installed). These features include the ability to run one or more ports with external clocks; daisy-chaining up to four SPC boards in a system; and interrupt-driven I/O.

Other CGC 7900 documentation available from Chromatics includes the CGC 7900 User's Manual, OEM Manual, and Disk Operating System Manual. Additional SPC documentation includes the circuit descriptions, test procedures, schematics, and source listing for the firmware. Some of this documentation is considered proprietary, and you may be required to file a non-disclosure agreement.

#### ARCHITECTURE

The SPC consists of a Z80 processor running at 2.5 MHz, two 2532-type EPROMs for onboard firmware (up to 8K bytes), 4K bytes of onboard RAM, and 1K bytes of two-port RAM. The four serial ports are each handled by a 2661 Enhanced Programmable Communications Interface (a friendly USART). The remainder of the circuitry is "glue" logic which holds the system together, and provides interrupts, interprocessor signalling, and i/o decoding.

The SPC is, in fact, a complete Z80 computer system. It only requires a few signals from the 7900 bus in order to function. This means that the SPC can continue to run during times when the main 68000 system processor is unable to operate (during DMA transfers, for example). Within the 4K of onboard memory, each port has two buffers (transmit and receive), each of which is 256 bytes long. A substantial amount of data can be buffered in this onboard RAM before 68000 intervention is required.

The memory map on the following page details the SPC memory allocation. Onboard EPROM occupies 0000 through 1FFF hex. Two-port RAM is from 2000 to 23FF. All i/o is memory-mapped, and resides from 3000 to 301F. This includes the 2661 chips and the Flags (used for signalling between processors). Onboard RAM is located at 7000 through 7FFF. Most of onboard RAM is available for buffer area, although a small amount must be used for the Z80 stack and temporary data storage areas.

From the 68000 point of view, the SPC occupies 2K of address space, from FF0000 to FF07FF. All odd-numbered bytes in this range are mapped into the two-port RAM. Even bytes are used to access the Flags. Since the SPC is an 8-bit system, all 68000 programs talking to it must use 8-bit (byte) operations only. Using word or long word instructions will cause unhappy behavior.

The 68000 can only address the two-port RAM and the Flags. It cannot access other items in the SPC address space directly; that is the Z80's job.

The two-port RAM (known as TRAM) is the method by which the two processors communicate their needs. The firmware contains a set of commands which can be passed to the Z80 in TRAM; the Z80 will act on these commands and return results to the 68000. The command set is described in a later section of this document.

Current SPC firmware occupies only the first of the two EPROM sockets. The second EPROM is available for user-written firmware <u>at this time</u>. Chromatics reserves the right to expand SPC functions and utilize the second EPROM at some future date... swim at your own risk.

# MEMORY MAP

- Z80 Side -

| 0000 - OFFF            | EPROM #0                 |

|------------------------|--------------------------|

| 1000 – 1FFF            | EPROM #1                 |

| 2000 <del>-</del> 23FF | Two-port RAM             |

| 3000 - 301F            | I/O space: USARTs, flags |

| 7000 <b>-</b> 7FFF     | Onboard RAM              |

I/O space is allocated as follows:

| 3000        | Port 0 data                          |

|-------------|--------------------------------------|

| 3001        | Port 0 status                        |

| 3002        | Port 0 mode                          |

| 3003        | Port 0 command                       |

| 3004 - 3007 | Port 1 (as above)                    |

| 3008 - 300B | Port 2                               |

| 300C - 300F | Port 3                               |

| 3010        | RTC reset                            |

| 3018        | Flag 1 (read examines, write SETs)   |

| 3019        | Flag 2 (read examines, write CLEARs) |

301C Flag 3 (read or write interrupt's 68000)

# - 68000 Side -

| FF0001 - FF07FF | (odd bytes only) Two-port RAM                     |

|-----------------|---------------------------------------------------|

| FF0000          | Flag 1 (read examines, write CLEARs)              |

| FF0002          | Flag 2 (write SETs Z80 interrupt)                 |

| FF0004          | Flag 4 (write RESETs Z80, read allows Z80 to run) |

| FF0006          | Flag 3 (write CLEARs 68000 interrupt)             |

NOTE: Due to redundant addressing, some items also appear at addresses other than those listed above. For example, on the Z80 side, TRAM also appears at 2400-27FF, 2800-2BFF, and 2C00-2FFF. On the 68000 side, TRAM is uniquely addressed, but the Flags are not. Therefore, programmers should be careful not to access any addresses other than those listed above.

Since the SPC is inherently an 8-bit device, all 68000 programs using the SPC should use <u>byte</u> instructions only. Using 16-bit or 32-bit instructions will access the TRAM and the Flags simultaneously, causing strange results. Be **especially careful when accessing the two-port RAM:** the program must read a byte, skip over a byte, and read the next byte from the next odd address. A sample program fragment might be:

|      | LEA     | TRAM, AO    | ;A0 $\rightarrow$ 2-port RAM |

|------|---------|-------------|------------------------------|

| Loop | MOVE, B | (AO)+,(A1)+ | ; copy one byte from TRAM    |

|      | ADDQ.L  | #1,A0       | ;skip odd bytes              |

|      | DB RA   | DO,Loop     | ;continue                    |

NOTE: Any time the Z80 accesses Flag 3, whether during a read OR a write, it will set an interrupt to the 68000. Be careful when examining memory in the I/O space, since reading it can cause unwanted interrupts.

Page 7

## FIRMWARE

The SPC firmware operates with the 7900 Terminal Emulator, TERMEM. Version 2 firmware, and later versions, also support the Idris operating system. Interaction with Idris is more complex than TERMEM, and we will describe TERMEM first.

It is TERMEM's purpose in life to read characters from logical devices and write them to other logical devices. A device assignment structure allows each logical device to be "connected" to one or more physical devices. Each of the ports on the SPC is considered to be one physical device, assignable for input, output, or both.

When TERMEM is running with the SPC, two basic operations are possible: write a character to a port, and read a character from a port. TERMEM operates on a character-at-a-time basis, so more complex interactions are not required. A third operation "reconfigures" a port, setting up baud rate, handshaking, and character format. Each of these is discussed in the "Commands" section of this document.

When the SPC is powered-up or reset, the Z80 begins executing code from its onboard EPROM. It initializes the four serial ports with default parameters, and enters a simple loop which performs these functions:

Service port 0. Service port 1. Service port 2. Service port 3. Check for commands from the 68000, and process them if necessary.

To service any port, the Z80 reads the port status from the 2661 chip. If a character has been received, it is loaded into onboard RAM. If a buffer becomes full, the proper handshaking protocol is performed. Then the transmitter side of the port is serviced. If a port shows "transmitter ready," a character is pulled from onboard RAM and transmitted. The firmware also transmits and times a "break" pulse if requested. Sending an FF hex to any port will generate the break pulse.

To simplify interaction with TERMEM, all SPC operation is in polled mode no interrupts are used. Since the SPC can asynchronously buffer all transmitted and received data, there is no need for interrupts under TERMEM. A sample exchange between the processors might be as follows:

# <u>68000</u>

<u> Z80</u>

Wait for Flags to signal that the TRAM is available for a command.

Put "read character" command into TRAM, along with the port number.

Release TRAM to the Z80.

Recognize that TRAM is available, and read the command.

Read a character from the appropriate buffer.

Put the character into TRAM and send it away.

Wait for TRAM to return.

Read the character from TRAM.

Process the character.

This is the basic method of operation for all transactions between the Z80 and the 68000. The Flags are used to synchronize TRAM accesses, and also to allow each processor to interrupt the other. These Flags are discussed next.

#### FLAGS

Any multiprocessor system must use some form of signal between the processors, to insure orderly transfer of data. The SPC uses a set of semaphores, or Flags, which may be tested or set under various conditions. The Flags are actually hardware flip-flops which can each store one bit of information. When you read a Flag, its information appears on the high bit of the byte (bit 7). This allows a simple "branch-if-minus" instruction to act on the state of the flag.

Flag 1 is a semaphore which controls access to the two-port RAM (TRAM). When Flag 1 is SET, the 68000 owns the TRAM. When it is CLEAR, the Z80 owns the TRAM. Each processor may give up the TRAM by writing to Flag 1, but <u>may not</u> "grab" the TRAM. Each processor must wait for TRAM access by testing the state of Flag 1. Other Flags, discussed below, are used to request ownership of the TRAM. Flag 1 is CLEARED after a reset.

Flag 2 is used by the 68000 to send a signal to the Z80. The 68000 sets this Flag by writing to it. The Z80 can test this Flag by reading it. Alternatively, if the Z80 has enabled interrupts, Flag 2 will interrupt the Z80. In either case, the Z80 will write to Flag 2 to clear it. The 68000 cannot read back the state of Flag 2, so some other means must be used to tell whether the Flag 2 signal has been serviced. (This can be accomplished by Flag 1 or Flag 3.) Flag 2 is CLEARED after a reset.

Flag 3 is used by the Z80 to interrupt the 68000. When the Z80 writes or reads Flag 3, logic on the SPC requests an interrupt of the specified priority (set by switches on the SPC card). The interrupt will be acknowledged by the 68000 when its execution priority drops below the SPC's request priority. The 68000 clears this interrupt by writing to Flag 3. Since the Z80 cannot read back the state of Flag 3, one of the other Flags must be used to tell whether the interrupt has been serviced. Flag 3 is CLEARED after a reset.

Flag 4 allows the 68000 to reset the SPC board. This is equivalent to a hardware reset signal, and causes the SPC to clear all Flags and begin executing onboard firmware at address zero. It allows the 68000 to bring the Z80 to a known state, without resetting any other system hardware. Writing to Flag 4 resets the SPC and holds it in a reset state. Reading from Flag 4 allows the Z80 to run. Note that the Z80's firmware initializes some onboard RAM locations and sets up the USARTs; this may interfere with RAM-resident Z80 programs. Flag 4 is CLEARED by a system reset, but a system reset pulse will also reset the SPC.

| FL AG1<br>FL AG2<br>FL AG3<br>FL AG4 | EQU<br>EQU<br>EQU<br>EQU | \$FF0000<br>\$FF0002<br>\$FF0006<br>\$FF0004 | ;Equates for Flags                     |

|--------------------------------------|--------------------------|----------------------------------------------|----------------------------------------|

| Wait                                 | BTST<br>BEQ.S            | #7,FLAG1<br>Wait                             | ;This loop waits<br>; for TRAM access. |

| Away                                 | CLR.B                    | FLAG1                                        | ;Release TRAM to Z80.                  |

| HeyYou                               | CLR.B                    | FL AG2                                       | ;Holler at Z80                         |

| Clrint                               | CLR.B                    | FL AG3                                       | ;Clear 68000 interrupt                 |

| Reset                                | CLR.B<br>TST.B           | FL AG4<br>FL AG4                             | Reset the Z80,<br>; then let it run.   |

# Examples of Flag usage (Z80 side):

| FL AG1<br>FL AG2<br>FL AG3 | EQU<br>EQU<br>EQU | 3018H<br>3019H<br>301CH   | ;Equates for Flags                                          |

|----------------------------|-------------------|---------------------------|-------------------------------------------------------------|

| Wait                       | LD<br>OR<br>JP    | A,(FLAG1)<br>A<br>M,Wait  | ;This loop waits<br>; for TRAM access.<br>; (loop if minus) |

| Away                       | LD                | (FLAG1),A                 | ;Release TRAM to 68000.                                     |

| Poll                       | LD<br>OR<br>JP    | A,(FLAG2)<br>A<br>M,IsSet | ;Check Flag 2<br>; and jump if set                          |

| Clrint                     | LD                | (FLAG2),A                 | ;Clear Flag 2                                               |

| HeyYou                     | LD                | (FLAG3),A                 | ;Interrupt the 68000                                        |

|                            |                   |                           |                                                             |

#### INTERRUPTS

The SPC allows operation in polled or interrupt-driven modes. Standard firmware in the SPC, when operating with TERMEM (the 7900 Terminal Emulator program), uses only polled mode. In this mode, each processor examines the Flags to determine the status of the two-port RAM, and acts according to this status. The two-port RAM is used to pass commands and data between the two processors.

In some applications, greater system throughput is achieved by letting the SPC interrupt the 68000 when it requires service. This interrupt-driven mode of operation is effective whenever the 68000 is busy with other tasks; for example, running an operating system or applications program.

Three interrupts exist in the SPC. The first is a real-time clock interrupt, which is tied to the NMI (non-maskable interrupt) input of the Z80. This interrupt is set every 60th of a second, by the vertical retrace signal in the 7900. (Systems running on 50 Hz power will receive 50 Hz interrupts).

The clock interrupt must be cleared by the Z80 before it can occur again. The Z80 clears this interrupt by accessing address 3010 hex.

The following code is extracted from version 1 of the standard firmware, and is executed every "tick" of the real-time clock:

| VERT | equ                                         | 3010H ;addr to reset int                                                                  |

|------|---------------------------------------------|-------------------------------------------------------------------------------------------|

| TIME | Equ                                         | 7FFEH ;clock bytes                                                                        |

| Tick | LD<br>EXX<br>LD<br>INC<br>LD<br>EXX<br>RETN | (VERT),A ;clear the NMI<br>;flip to alt. regs<br>HL,(TIME) ;bump clock<br>HL<br>(TIME),HL |

Several things are important about this code. Note that the upper two bytes of onboard RAM are used as a 16-bit counter, incremented every 60th of a second. Also, remember that the Z80 will always do a CALL to address 0066 hex when an NMI occurs, so this code must live at 0066, which is in the first EPROM. We use alternate register pair HL' in this service routine, which precludes use of the alternate registers anywhere else (NMI's cannot be disabled). Finally, notice that a RETN is used to end the routine. RETN restores the Z80 maskable interrupts to the state they were in before the NMI occurred.

The firmware uses this clock interrupt to time the length of a generated "break" signal. It is customary to assert "break" for about 200 milliseconds, or 12 ticks.

Version 2 of firmware includes a more complex clock service routine, for support of the Idris device drivers. In addition to the functions above, it can also execute a "wakeup" task after a certain number of clock ticks. This wakeup task is used in Idris to periodically interrupt the operating system and request SPC service.

Chromatics CGC 7900 Series

| VERT EQU<br>FLAG2 EQU<br>WAKEUP EQU<br>WAKTIM EQU<br>OFTEN EQU<br>TIME EQU                                                               | 3019H ;F2 add<br>7FF7H ;what t<br>7FF6H ;runnin                                                                                                                           | o do when awakened<br>ng counter<br>'ten to wake                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nmi LD<br>PUSH<br>PUSH<br>LD<br>INC<br>LD<br>CR<br>JP<br>LD<br>DEC<br>JR<br>DEC<br>LD<br>INC<br>LD<br>CALL<br>Nmi9<br>POP<br>POP<br>RETN | (VERT),A<br>HL<br>AF<br>HL,(TIME)<br>HL<br>(TIME),HL<br>A,(FLAG2)<br>A<br>P,Nmi9<br>HL,WAKTIM<br>(HL)<br>NZ,Nmi9-\$<br>HL<br>A,(HL)<br>HL<br>(HL),A<br>WAKEUP<br>AF<br>HL | <pre>;clear the NMI<br/>;save regs<br/>;bump clock<br/>;see if F2 set<br/>;jmp/no, don't wakeup<br/>;point to wakeup timer<br/>;tick it<br/>;jmp if not time to go<br/>;point to OFTEN<br/>;get it<br/>;reload WAKTIM<br/>;service the clock<br/>;restore &amp; return</pre> |

If Flag 2 is not set when the clock ticks, this routine degenerates into the code from version 1, except that it doesn't use the HL' register. This allows other routines to use the alternate registers, and the Idris device driver does.

If Flag 2 is set when the clock ticks, the RAM location WAKTIM is decremented. If it goes to zero, it gets reloaded from location OFTEN. Then we call location WAKEUP, which will execute the clock-driven task. WAKEUP is three bytes long and is initialized to a jump to a RET instruction. This allows other programs to use Flag 2, and if WAKEUP is left alone, the clock servicer won't affect anything.

To make use of the clock service routine, store the "tick rate" into OFTEN, and the service routine address into WAKEUP+1:

| LD | A,3            | ;every 3 ticks |

|----|----------------|----------------|

| LD | (OFTEN),A      |                |

| LD | HL,Addr        | ;whom to call  |

| LD | (WAKEUP+1), HL |                |

This would cause the routine at "Addr" to be executed every three clock ticks, 20 times a second. Of course, Flag 2 must be set or WAKTIM won't get decremented, and WAKEUP will never get called. WAKEUP is called at the interrupt level, so it must be fast, and must save all registers it uses. Note that if the wakeup task is not complete by the next clock tick, it could get re-entered at the interrupt level. This almost surely leads to disaster.

- Flag 2 -

The next type of interrupt is produced by Flag 2, and is used by the 68000 to interrupt the Z80. When the 68000 writes to address FF0002, Flag 2 is set. The Z80 can poll Flag 2 if polling mode is desired, or Flag 2 can generate a maskable interrupt to the Z80. Maskable interrupts are enabled and disabled by the EI and DI instructions. (Standard firmware does not use maskable interrupts, so interrupts are always disabled.) The Z80 clears this interrupt by writing to Flag 2.

Since only one source of maskable interrupts exists (Flag 2), the SPC is designed to operate in Interrupt Mode 1 as defined in the Z80 literature. Interrupt Mode 1 provides the simplest hardware interface to the Z80. The processor enters this mode by executing the instruction

IM

1

which must be included before interrupts are enabled. (Standard firmware does this.) In Mode 1, the Z80 performs a CALL to address 0038 hex when an interrupt occurs. The maskable interrupt service routine must be located at this address. It must be terminated with the instructions

> EI RET

which re-enables interrupts and continues the previous program. Of course, the interrupt service routine must save and restore any registers it uses. (The Z80 "RETI" instruction is acceptable in place of "RET", but not necessary. In any case, the "EI" must be included to allow future interrupts.)

When a maskable interrupt occurs, the standard firmware does a jump to address 7FFB. This address is initialized to contain a jump to a RET instruction. The address of your interrupt service routine should be loaded into location 7FFC. This could be done as follows:

INTJP EQU 7FFBH ;where to go when int'd

LD HL,Isr ;service routine addr LD (INTJP+1),HL ;store it

Now if interrupts are enabled and Flag 2 is set, the Z80 will execute code at address "Isr".

- Flag 3 -

The third type of SPC interrupt is used by the Z80, to interrupt the 68000. The Z80 can set an interrupt to the 68000 by writing <u>or reading</u> Flag 3. If the execution priority of the 68000 is currently below the priority of the SPC interrupt, the 68000 will begin its interrupt service routine. To clear the interrupt, the 68000 must write to address FF0006, its name for Flag 3.

> FLAG3 EQU \$FF0006 CLR.B FLAG3 ;reset the int

Page 13

Chromatics CGC 7900 Series

The address of the 68000 interrupt service routine must be loaded into one of the interrupt vectors, usually vector number \$7C, which is at address \$1F0. This means that before any SPC interrupts can be fielded by the 68000, you must do the following:

MOVE.L #SPCisr, \$1F0 ;set the vector

Where "SPCisr" is the address of the SPC interrupt service routine, to be executed when the Z80 rings for service.

To minimize the amount of interrupt servicing, plan your software so that certain things are implicit. For example, when the Z80 interrupts the 68000, the 68000 should not have to wait for two-port RAM access. The Z80 should insure that Flag 1 is SET before it interrupts the 68000:

| LD | (FLAG1),A | ;send away TRAM |

|----|-----------|-----------------|

| LD | (FLAG3),A | ;set the int    |

The 68000 can then immediately read from two-port RAM to determine why the Z80 interrupted it.

Page 14

#### ONBOARD RAM USAGE

The 4096 bytes of onboard RAM are allocated for i/o buffers, parameter areas for ports, stack space, and system constants. The allocation shown below is for version 2 firmware.

7000-7800 i/o buffers: 7000-70FF port 0 receiver buffer 7100-71FF port 0 transmit buffer 7200-73FF port 1 buffers 7400-75FF port 2 buffers 7600-77FF port 3 buffers 7800-781F port 0 parameter area 7820-783F port 1 parameter area 7840-785F port 2 parameter area 7860-787F port 3 parameter area 7880-7DFF expansion 7E00-7EEF Idris coroutine stack 7EF0-7FEF system stack 7FF0-7FFF system RAM constants: 7FF0-7FF1 COSP: Idris stack pointer storage 7FF2-7FF3 MAINSP: main stack pointer storage 7FF4 SERV: Idris clock service flag **7FF5** OFTEN: clock service rate WAKTIM: running clock counter 7FF6 7FF7-7FF9 WAKEUP: clock service routine 7FFA ENABLE: port-enable byte 7FFB INTJP: Flag 2 interrupt service routine 7FFE-7FFF TIME: 16-bit running timer

Note the area from 7880 to 7DFF. This is free RAM in version 1 and 2 firmware, and can be used for loading user-written code. Bear in mind that future versions of firmware may use this RAM space; don't get too attached to it.

INITIALIZATION: After a reset, certain RAM areas are loaded by the Z80. The buffers from 7000 to 77FF are not cleared out, but their contents are ignored. Parameter areas from 7800 to 787F are copied from PROM; these include the buffer counts and pointers, handshake flags, USART initialization values, and other per-port information. The area from OFTEN through INTJP is initialized as follows:

OFTEN is set to 1. WAKTIM is set to 0.

WAKEUP jumps to a RET instruction.

Page 16

ENABLE is set to OF hex, enabling all four ports.

INTJP jumps to an EI followed by a RET.

The area from 7E00 to 7FEF is used for stack space. The system stack pointer is initialized to 7FF0 and grows down from there. Part of the Idris code requires a separate stack, which grows down from 7EF0. About 256 bytes of space are allocated for each stack, which is probably a bit much. COSP and MAINSP each hold the value of the SP (stack pointer) during use of the other stack.

If future versions require more RAM space, it will probably be allocated as follows: simple one- or two-byte values will be allocated down from 7FF0, moving the stacks down to make room. If larger chunks of RAM are needed, they will be allocated up from 7880. Use this as a guide in plaaning your RAM allocation.

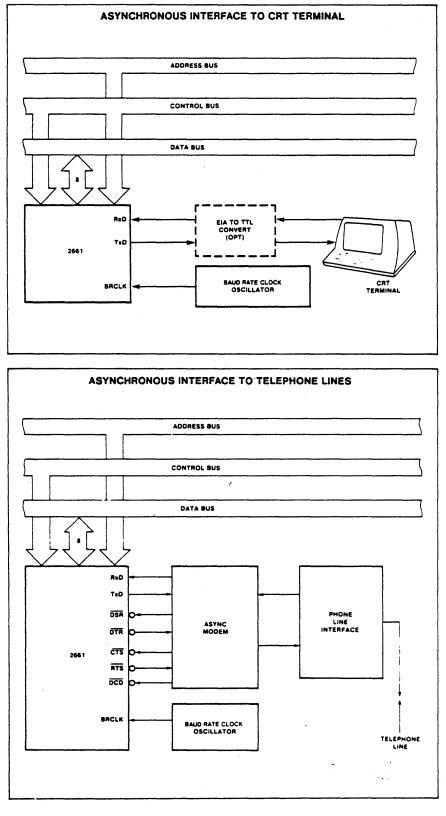

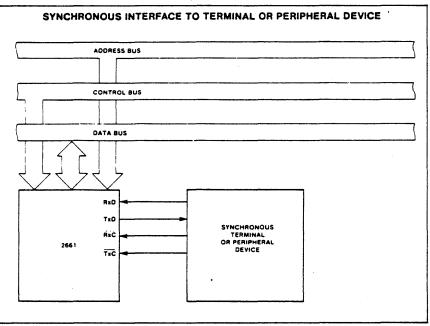

#### THE ENHANCED PROGRAMMABLE COMMUNICATIONS INTERFACE

This section discusses the EPCI, otherwise known as the 2661 communications chip. We will point out some salient features of the chip in this section, including the basic methods of programming it (in asynchronous mode). The Appendix contains a 2661 data sheet with full programming details.

Programmers who are familiar with the 8251 USART device will be pleasantly surprised by the 2661. The 2661 is similar in function, and the signal mnemonics are familiar enough that it will be easy to learn the 2661. Yet, the 2661 eliminates many of the 8251 and 8251A headaches: most of the 2661 registers are read/write, so that the Z80 "bit" instructions work conveniently for testing and changing bits. (Indeed, the designer chose to use memory-mapped I/O in the SPC to allow use of "bit" set/reset/test instructions.)

Nearly all of the 2661's functional characteristics can be altered "on the fly." This includes the number of bits per character, parity, stop bits, and other parameters which created programming nightmares in the 8251. The 2661 has an internal baud-rate generator which provides 16 standard rates. (External clocking is available, and is discussed in a separate section of this document.)

The 2661 contains nine registers, five of which are used in asynchronous applications. Four of these are available all the time, as read/write locations. The fifth is only used during initialization (usually), but is quite easy to access during operation if necessary. The registers are:

#### Offset Register

- 0 Data in/out

- 1 Status

- 2 Mode registers 1 and 2

- 3 Command

The offset lists the amount which must be added to the base address of a port, in order to access a given register of that port. It is convenient in Z80 code to use the index registers, IX and IY, to access the various registers of a port. For example:

| LD  | IX,PORTO | ;IX-> base of port |

|-----|----------|--------------------|

| SET | 1,(IX+3) | ;turn on DTR       |

| BIT | 7,(IX+1) | ;test DSR          |

All of the bits will be explained momentarily. For now, note the ease of operating the 2661 through the Z80 index registers.

#### Register Contents

The **data input/output** register is written into in order to transmit a character. Read from this register to get a received character. (Before reading or writing, you should test bits in the status register to insure that the 2661 is ready.)

#### Chromatics CGC 7900 Series

The status register bits are defined below. All status register bits are similar to corresponding bits in the 8251, with two exceptions: The IR (internal reset) bit is not present, since all 2661 registers are read/write and it is never necessary to software-reset the chip. Also, bit 2 has taken on an additional meaning, as described below.

| Status Re | egister |

|-----------|---------|

|-----------|---------|

| 7   | 6   | 5              | 4  | 3              | 2               | 1     | 0     |

|-----|-----|----------------|----|----------------|-----------------|-------|-------|

| DSR | DCD | FE/<br>SYN det | OR | PE/<br>DLE det | TxEMP/<br>DSchg | RxRDY | TxRDY |

Bits 7 and 6 indicate the state of the corresponding modem control signals on the interface. (The DCD input is not present in the 8251. This input must be TRUE in order for the 2661 receiver to function. In the SPC, if the DCD line is unconnected, it is held in a TRUE state by a resistor.)

Bit 5 indicates FE, framing error, in asynchronous mode. It is set when a character does not contain a valid stop bit. This may that the 2661 is receiving a "break" condition on the data line. (Break is indicated by FE occuring while a null character, 00, is present in the data register.)

Bit 4 indicates OR, overrun error. It is set when the Z80 has not read characters out of the 2661 fast enough, and data has been lost.

Bit 3 indicates PE, parity error, in asynchronous mode. The software may choose to ignore this bit, if parity checking is not required.

NOTE: Bits 3, 4, and 5 are all reset by a "reset errors" command to the command register. See the command register description.

Bit 2 is set when the transmitter is totally empty. (Being double-buffered, the transmitter can be ready without being empty. See Bit 0.) This bit is also set if either the DSR or DTR inputs has changed, indicating a possible change in the status of the communication link. This "DSchg" indicator is not present in the 8251.

Bit 1 indicates the receiver is ready, and data should be read from the data register.

Bit 0 indicates the transmitter is ready, and data should be written into the data register if any is available.

Two mode registers exist, MR1 and MR2. This is the only case in the 2661 where a register is not always read/writable, and we will discuss these registers in detail so you can avoid pitfalls.

Both MR1 and MR2 are accessed through the same address, which is PORT plus two (PORT being the base address of a chip). Mode register 1 is identical to the mode register in an 8251:

Page 18

| 7                                           | 6                 | 5                       | 4    | 3            | . 2                          | 1                                    | 0              |

|---------------------------------------------|-------------------|-------------------------|------|--------------|------------------------------|--------------------------------------|----------------|

| 00=sync<br>01=1 sto<br>10=1.5 s<br>11=2 sto | p bit<br>top bits | pari<br>0=even<br>1=odd | 0=n0 | 01=6<br>10=7 | bits<br>bits<br>bits<br>bits | 00=synd<br>01=1X<br>10=16x<br>11=64x | clock<br>clock |

Mode Register 1

Bits 7 and 6 define the number of stop bits per character.

Bits 5 and 4 define the parity (odd, even, or none).

Bits 3 and 2 define the number of data bits per character.

The total number of bits transmitted per character is actually the total of: stop bits, data bits, and parity (if enabled).

Bits 1 and 0 select the baud rate multiplier, or select synchronous mode if 00. Note that if the internal baud rate generator is being used (see MR2 below), the multiplier is ignored and any of the asynchronous multiplier values may be used.

Mode register 2 is unlike anything in the 8251. It controls the internal baud rate generator in the 2661, and also specifies the function of certain pins on the chip. These pins are used in external clocking applications.

The upper four bits of MR2 select internal or external clocking, synchronous or asynchronous operation, and define pins 9 and 25 on the chip, as follows:

| Bits 7-4 | TxC | RxC | <u>Pin 9</u> | <u>Pin 25</u> | <u>Mode</u> |

|----------|-----|-----|--------------|---------------|-------------|

| 0000     | ext | ext | TxC in       | RxC in        | sync        |

| 0001     | ext | int | TxC in       | 1x out        | async       |

| 0010     | int | ext | 1x out       | RxC in        | sync        |

| 0011     | int | int | 1x out       | 1x out        | async       |

| 0100     | ext | ext | TxC in       | RxC in        | sync        |

| 0101     | ext | int | TxC in       | 16x out       | async       |

| 0110     | int | ext | 16x out      | RxC in        | sync        |

| 0111     | int | int | 16x out      | 16x out       | async       |

| 1000     | ext | ext | xsync        | RxTxC in      | sync        |

| 1001     | ext | int | TxC in       | brkdet        | async       |

| 1010     | int | ext | xsync        | RxC in        | sync        |

| 1011     | int | int | 1x out       | brkdet        | async       |

| 1100     | ext | ext | xsync        | RxTxC in      | sync        |

| 1101     | ext | int | TxC in       | brkdet        | async       |

| 1110     | int | ext | xsync        | RxC in        | sync        |

| 1111     | int | int | 16x out      | brkdet        | async       |

Bits 7 through 4 of MR2 must be set to select the proper source (internal or external) of the baud rate clock, and the proper mode (sync or async). Pins 9 and 25 of the 2661 are not connected to anything unless jumpers are installed by the user, so their meaning need not concern us at this point.

Bits 3 through 0 of MR2 select the frequency of the internal baud rate generator. The available rates are listed below.

| <u>Bits 3-0</u> | Baud Rate |

|-----------------|-----------|

| 0000            | 50        |

| 0001            | 75        |

| 0010            | 110       |

| 0011            | 134.5     |

| 0100            | 150       |

| 0101            | 200       |

| 0110            | 300       |

| 0111            | 600       |

| 1000            | 1050      |

| 1001            | 1200      |

| 1010            | 1800      |

| 1011            | 2000      |

| 1100            | 2400      |

| 1101            | 4800      |

| 1110            | 9600      |

| 1111            | 19200     |

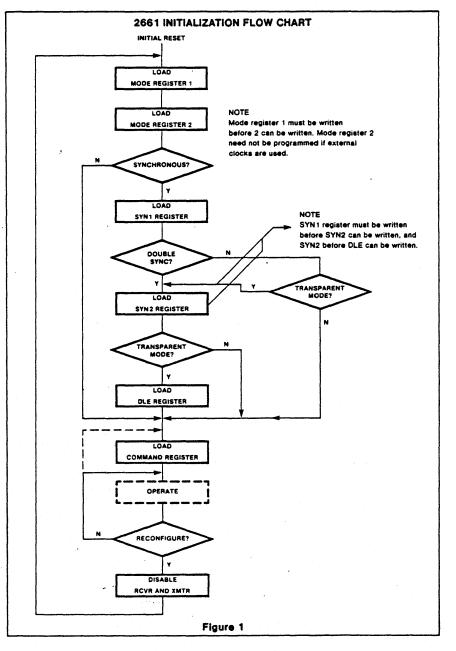

Interaction between MR1 and MR2. After a hardware reset, the 2661 expects you to load the first mode register (MR1). It then expects you to load MR2. This sequence is necessary, since both registers must be loaded before the 2661 can be used. After loading both registers, the 2661 is again addressing MR1.

If you reload the mode registers after initialization, or if you want to read data from one or both mode registers, there is a way to tell which is which: the 2661 always points back to MR1 after you read from the command register. So, to be absolutely safe when accessing the mode regsters, use this procedure:

- Always read from the command register before accessing any mode regsister.

- Always read both mode registers, or write both mode registers. Your software may require a RAM copy of the mode register contents, to insure that you write proper data into both registers.

The command register of the 2661 is similar to the corresponding 8251 register. Bits 7 and 6 have been given additional meaning to support the 2661's self-test modes. Bit 3 is used in synchronous mode to support DLE transmission.

Page 20

| 7                                            | 6               | 5   | 4              | 3                     | 2            | 1   | 0            |

|----------------------------------------------|-----------------|-----|----------------|-----------------------|--------------|-----|--------------|

| 00=norma<br>01=auto-<br>10=local<br>11=remot | •echo<br>. loop | RTS | error<br>reset | send<br>break/<br>DLE | Rx<br>enable | DTR | Tx<br>enable |

Command Register

Bits 7 and 6 are 00 for normal operation. The other modes are described in 2661 literature, and are used for self-test and loopback operations without processor intervention.

Bit 5 controls the RTS modem control signal.

Bit 4 resets the PE, FE, and OR error bits in the status register. Writing a "1" to this bit will reset the errors, and the bit will automatically return to zero:

SET 4,(IX+3) ;reset errors

Bits 2 and 0 control the receiver and transmitter, respectively. The receiver-ready and transmitter-ready bits of the status register will not go true unless these control bits have been enabled.

Bit 1 controls the DTR modem control signal.

Bit 0 (TXEN) and bit 3 (break) perform in a friendly fashion. They do not affect any character which may be transmitting at the time of the command. These commands take effect after the current character (if any) has been completed. <u>However</u>, since the 2661 is double-buffered, the character being transmitted may not be the only character in the USART. If you turn off the TXEN bit, any character that has been written to the USART but has not yet begun transmission will be lost. It's best to wait for TXEMT before dropping TXEN.

#### Programming Example

The following code might be used to initialize a 2661.

| LD . | IX, PORT    | ;IX-> 2661 chip                             |

|------|-------------|---------------------------------------------|

| LD   | A,(IX+3)    | ;read the command register; to sync MR1/MR2 |

| LD   | (IX+2),7AH  | ;MR1= 7 bits, even parity,<br>; 1 stop bit  |

| LD   | (IX+2),0FEH | ;MR2= internal clocks,<br>;9600 baud        |

| LD   | (IX+3),27H  | ;turn on Tx, Rx, DTR, DSR                   |

#### COMMANDS

Commands are passed to the SPC in the two-port RAM (known affectionately as TRAM). Each command consists of an opcode, which is placed in the first byte of TRAM. This is followed by one or more bytes to specify details of the transaction.

If the SPC is required to return a response for a given command, the opcode byte is left intact in TRAM, and is followed by the returning arguments. If no response is required, the opcode will be zeroed out, and other bytes in the TRAM are irrelevant. In all cases, when running under the firmware used by TERMEM, the SPC will return ownership of the TRAM to the 68000 when an operation is complete.

If an invalid opcode is passed to the SPC, or if the arguments to that opcode are invalid, the opcode will be zeroed out and ignored.

In the following charts, "Offset in TRAM" is given from the Z80 side. From the 68000 side, the offset would be doubled, since every other byte must be skipped.

Note that opcodes 7 and above did not exist in version 1 firmware. Opcode 8 can be used to test the firmware version of an SPC.

Chromatics CGC 7900 Series

#### Opcode 1: Transmit Character

Offset in TRAM Contents 0 1 1 port # (0..3) 2 character <u>Returns:</u>

0

Opcode 1 is used by TERMEM to transmit a single character to a port. The character is buffered in onboard RAM and transmitted when possible. If the buffer is full, the SPC keeps TRAM ownership until there is room for at least one character in the buffer.

0

#### Opcode 2: Read Character

Offset in TRAM Contents 0 2 1 port number (0..3) <u>Returns:</u> 0 2 1 port number (0..3) 2 buffer count 3 character

Opcode 2 checks the count of received characters in a port's buffer. If the count is not zero, it also returns the oldest character in the buffer. TERMEM uses this and Opcode 3 (below) to read from a device.

The buffer count returned by opcode 2 is the number of characters in the buffer <u>before</u> the returning character was removed. If the count is 1, you are now reading the last character. If the count is zero, no characters are available and the contents of TRAM+3 are invalid.

## Opcode 3: Check Port Status

Offset in TRAM O

1

Contents 3 port number (0..3)

#### <u>Returns:</u>

031port number (0..3)2buffer count3character snapshot

Opcode 3 is used by TERMEM to check if any characters are available from a port. It returns the count of received characters, and also a "snapshot" of the oldest character in the buffer. This allows TERMEM and DOS to check for the presence of certain characters (control-S to pause a listing, for example) without actually reading characters from the device.

No matter how many times you execute Opcode 3, the "snapshot" will always be the same character. Opcode 3 does not remove any characters from the buffer.

If you execute Opcode 3 and then Opcode 2, each will return the same character. Opcode 3 will produce a snapshot of that character, and Opcode 2 will read it again (and remove it from the buffer).

#### Opcode 4: Reconfigure a Port

Offset in TRAM Contents 0 4 1... character string

0

#### <u>Returns:</u>

Opcode 4 takes a literal string and parses it to gather commands. These commands reconfigure a port, setting handshaking, baud rate, number of bits, parity, and number of stop bits. The characters loaded into TRAM+1 and succeeding bytes must constitute an ASCII string of the following form:

<port>, <hand>, <baud>, <bits> <par> <stop>

<port> is a decimal number, 0 to 3, delimited by a comma.

0

<hand> is also a decimal number, delimited by a comma. It sets the port's

handshake parameters as follows:

| <hand></hand> | Effect                        |

|---------------|-------------------------------|

| 0             | No handshaking                |

| 1             | Software (Xon, Xoff) Protocol |

| 2             | Hardware (DTR, DSR) Protocol  |

| 3             | Both SW and HW Protocols      |

<baud> is a decimal number, delimited by a comma, which must be one of the following legal baud rates: 50, 75, 110, 134, 150, 200, 300, 600, 1050, 1200, 1800, 2000, 2400, 4800, 9600, 19200. Entering 134 actually produces 134.5 as a baud rate.

<bits> is a single ASCII character, which sets the number of bits per character (not counting parity). <bits> must be either 5, 6, 7, or 8. Note that the ASCII equivalent of these characters is used, so '5' is actually 35 hex.

<par> is a single ASCII character, either E, O (alphabetic "Oh"), or N, to select even, odd, or no parity.

<stop> is a single ASCII character, which selects the number of stop bits. <stop> can be either 1, 2, or 3. (Use the character '3' to select 1.5 stop bits.)

If any of the parameters is not within legal range, the entire command is ignored. However, it is possible to "fool" the firmware by entering an invalid sequence for <bits><par><stop>. An invalid sequence, but one which would not be detected as invalid, would be one in which characters from one set are interchanged with characters from another set. For example, to set 7 bits, even parity, one stop bit, <bits><par><stop> would be '7E1'. The incorrect sequence '7EE' would not be thrown out as illegal, yet would produce anomalous results. This type of incorrect sequence is not rejected, due to the way in which these characters are parsed. The moral is, "don't do this." Page 28

A sample character string would be:

# 0,1,1200,8N2

which would set port 0 to software handshaking, 1200 baud, 8 bits, no parity, 2 stop bits.

# Opcode 5: Jump to Monitor

Offset in TRAM Contents 0 5

# Returns:

---does not return----

Opcode 5 causes entry into the SPC onboard Monitor. The Monitor uses an entirely different protocol for communication with the 68000. It is discussed in a later section of this document.

#### Opcode 6: Test a Port

Offset in TRAM 0

1

6

Contents

test subcode

#### <u>Returns:</u>

---depends on subcode---

Opcode 6 enters the diagnostic routines used by Chromatics' Field Service and Production departments. The diagnostic tests are designed to be used with a dedicated program (SPCTEST.SYS) running on the 68000. These diagnostics allow the serviceman to test most of the hardware on the SPC board. Tests include:

Real-time clock (NMI).

Flag 2, polled and interrupt-driven.

Flag 3, interrupt-driven.

PROM checksums.

Memory tests, both onboard and TRAM, using unique address tests, walking ones, and walking zeroes.

Port tests, including data transmit/receive at all baud rates, break send and detect, DTR and RTS outputs, DSR and DCD inputs.

#### Opcode 7: Load ENABLE Byte

## Offset in TRAM Contents 0 7 1 ENABLE value

#### Returns:

0

0

Opcode 7 loads the ENABLE cell with a 4-bit value. ENABLE is used to select which of the 4 ports is active, and is defaulted to value OF hex. Bit 0 of this byte enables port 0, and so on.

The ENABLE cell can be altered for several reasons. Eliminating one or more ports from the processing loop will increase the time available for servicing other ports, increasing SPC throughput to some degree. This may be useful for applications in which only one or two ports are in use.

When developing programs on the SPC, and loading these programs into RAM (see Opcodes 9 through 11), it is possible that received characters could be loaded into onboard RAM and demolish your program. Setting the ENABLE byte to zero will prevent any port from being serviced, and no received characters will be buffered.

# Chromatics CGC 7900 Series

# Opcode 8: Return Firmware Version

Offset in TRAM Contents 0 8

# Returns:

0

8 version number

Programs can use Opcode 8 to determine the revision level of SPC firmware. Versions 2 and higher support Opcode 8. (Version 1 will zero out the opcode and not provide a version number.)

This function is used primarily by the Idris operating system. Version 2 of SPC firmware, or higher, is needed to be compatible with Idris.

•

#### Opcode 9: Load Onboard Memory from TRAM

| Offset in TRAM | Contents           |

|----------------|--------------------|

| 0              | 9                  |

| 1              | destination low    |

| 2              | destination high   |

| 3              | count low          |

| 4              | count high         |

| 5              | bytes to be loaded |

0

#### Returns:

0

Opcode 9 downloads data from the 68000 into SPC onboard memory. This function is designed for code development. The opcode is followed in TRAM by the least significant byte of the onboard memory address, the most significant byte of the address, the count LS byte, and the count MS byte. (The Z80 uses byte-swapped notation for 16-bit numbers.)

This is followed by the bytes to be loaded into memory. No limit-checking is performed: the user must insure that all parameters are valid. It is entirely possible to bomb the SPC by loading into unsuspecting areas of RAM, and the user must know what he/she is doing.

#### Opcode 10: Readout onboard memory into TRAM

| Contents    |

|-------------|

| 10          |

| source low  |

| source high |

| count low   |

| count high  |

|             |

#### <u>Returns:</u>

| 0 | 10                     |

|---|------------------------|

| 1 | source low             |

| 2 | source high            |

| 3 | count low              |

| 4 | count high             |

| 5 | bytes from onboard RAM |

This command is the complement of Opcode 9. Again, no limit-checking is performed.

#### Serial Port Controller Application Guide

#### Opcode 11: Jump to Address

Offset in TRAM Contents 0 11 1 address low 2 address high

Returns:

--- does not return---

,

The use (and risk) of this command is obvious.

Chromatics CGC 7900 Series

#### Opcode 12: Execute Idris Routine

Offset in TRAM Contents 0

#### Returns:

--- does not return---

12

Opcode 12 runs the SPC code which communicates with the Idris operating system. Idris thinks of the SPC as four devices, /dev/port0, /dev/port1, /dev/port2, and /dev/port3. See the Idris documentation for details on using these devices.

Idris divides up TRAM into four 256-byte areas, assigning one area to each port. While any port is open, the corresponding bit in ENABLE is set, allowing service for that port. The SPC periodically interrupts Idris and provides the status of each port, along with any received characters. Idris interprets this data and returns commands and characters to the SPC.

Idris can send up to 240 characters per port to the SPC in one transaction. The SPC can also send up to 240 characters to Idris. Buffering and unbuffering these characters can take a fairly long time; and during this time, the SPC might miss incoming characters. Remember that at 9600 baud, a character can arrive about once per millisecond, and if four ports are open, characters are arriving four times a millisecond. To increase receiver throughput, the Idris handler uses a coroutine to process commands from the operating system. The coroutine begins execution when WAKTIM counts to zero, and periodically pauses to allow the main Idris loop to check for received characters.

Page 37

#### ONBOARD MONITOR

The SPC firmware contains a Z80 Monitor program, which was used during SPC software development. This Monitor program is accessable as an aid in developing user-written SPC code.

The SPC Monitor is very similar to the "CPUOS" program available in Chromatics' CG Series of color graphic computers. Current SPC firmware was developed on the CG, using Chromatics' Z80 Assembler and Text Editor. The object code was then downloaded over one of the SPC's serial ports for testing.

The following is a list of the Monitor's commands. (Refer to the CG Series manuals for detailed information.) Commands are entered as single capital letters. No delimiter is entered between the command and its first argument. A delimiter must exist between the first argument and subsequent arguments. <add1> and <add2> are hex addresses, up to 4 digits. <val> is a hex value, up to 2 digits. A delimiter must follow the complete command. Valid delimiters are the space, comma, and carriage return, except that the carriage return must not be used between arguments.

The E, H, N and P commands were contained in version 1 firmware, but were removed in version 2 to save PROM space. They were not especially useful in the SPC environment.

D - dump memory

usage: D<add1> <add2>

"D" dumps memory in hexadecimal and ASCII. If <add2> is missing,

or less than <add1>, only 16 bytes are displayed.

F - fill memory

usage: F<add1> <add2> <val>

"F" fills memory from <add1> to <add2> with <val>.

G - go with breakpoints usage: G<add1> <add2> <add3> "G" begins execution, with optional breakpoints. Breakpoints are set at <add2> and <add3>, if they are present. Execution begins at <add1> unless it is absent, in which case execution begins at the current "PC" value (see the "X" command). If a breakpoint is hit, registers are displayed and the Monitor takes over.

K - compare memory

usage: K<add1> <add2>

"K" compares two area of memory. Any bytes which differ are

displayed. After each byte, press RETURN to quit the "K"

function, or any other key to proceed.

L - load object records usage: L<add1> "L" loads object records, in Intel hex format, into memory from serial port 0. The "L" function continues until an EOF record is found (see "E"). <add1> is an optional hex offset for the load function. Page 38

M - move data usage: M<add1> <add2> <add3> "M" moves bytes from the area <add1> to <add2>, to the area beginning at <add3>. After "M", "K" can be used to verify the data.

Q - search for byte usage: Q<add1> <add2> <val> <mask> "Q" searches the range of memory from <add1> to <add2>, for the byte <val>. Before comparing, each memory byte is masked with <mask>. This allows "Q" to search for a byte with "don't care" bits.

S - set memory

usage: S<add1>

"S" displays each byte of memory, beginning with the byte at

(add1) You may prove the area how to ship that but on anter

<add1>. You may press the space key to skip that byte, or enter a new value and press the space key. Pressing the RETURN key instead of space will quit the "S" function.

X - examine registers usage: X<reg>

"X" allows you to display and change the register values which will be used when the "G" command is given. "X" followed by RETURN displays all registers. "X" followed by a register name will display the register and allow you to enter a new value.

#### Serial Port Controller Application Guide

The following program can be used to communicate with the SPC onboard Monitor. This program runs under CGC 7900 DOS, and can be assembled on the CGC's MC68000 Resident Assembler. The program first resets the SPC, then waits for TRAM access which indicates the Z80 is running. It places opcode 5 in the first byte of TRAM, which is a command for the SPC to jump to its Monitor.

From this point on, the command protocol has changed: the Z80 becomes the host system, and the 68000 is now the terminal. The Monitor will send TRAM to the 68000 with one of two opcodes: 1 for read-character, or 2 for write-character. Our main loop processes both these opcodes by calling TERMEM's character i/o routines.

Since we call CTRLIN for character-in, we can escape from this program through a User code sequence such as the DOS or MONITOR key.

¥ Program to talk to the SPC Monitor. Ŧ CHAROUT EQU \$800008 :TERMEM char-out CTRL IN EQU \$800014 ;and char-in w/esc FLAG1 EQU \$FF0000 ;TRAM access flag TRAM EQU \$FF0001 ;odd bytes only FLAG4 EQU \$FF0004 ;reset to Z80 ORG.L \$1C3C ;run in DOS area Start CLR.B FLAG4 ;reset the SPC TST.B FLAG4 ;and let it run BSR Wait ;wait for TRAM #5,TRAM ;put "jmp monitor" code MOVE.B CLR.B FLAG1 ;send it ÷ 푶 Main loop reads/writes characters from the Monitor. BSR Wait ;wait for Monitor ... Main #1,TRAM CMP.B ;charin request? BEQ.S In CMP.B #2,TRAM ;charout request? BEQ.S Out ;invalid opcode! write an error-handler someday. #\$2700 STOP ; but for now, die. In CLR.L D1 ;use device 0 JSR CTRL IN ;(keyboard) BEQ.S ;wait until ready In MOVE, B DO, TRAM+2 ;put char for Z80 CLR.B FL AG1 :send it BRA Main Out MOVE.B TRAM+2,DO ;get outgoing char CLR.L ;use device 0 D1 JSR CHAROUT ;(screen) CLR.B FLAG1 ;release TRAM BRA Main Wait BIST #7,FLAG1 ;wait for TRAM BEQ.S Wait RTS END Start

#### DOWNLOADING CODE

Addresses 7880 through 7DFF are currently available for user-written code. Two methods are available for downloading code into the SPC, and both have been successfully used by Chromatics in developing the current firmware.

The first method uses the SPC onboard monitor. The procedure is:

Reset the SPC, to clear any previous operations.

Establish contact with the onboard monitor, using a program such as the one listed in the "Onboard Monitor" chapter of this document.

Give the "L" command, which loads object code from port 0. Port 0 is normally initialized to 9600 baud.

Transmit Intel-format hex records from a Z80 development system, such as a Chromatics CG series computer. End the data with an "end record" mark.

If all is well, the monitor prompt will return after the end record mark is detected. You may then set breakpoints and execute the downloaded code.

The second method uses opcode 9 (load onboard memory from TRAM). This method is useful when the Z80 code has been developed on the 7900, and can be downloaded through the two-port RAM. The procedure is:

Reset the SPC, to clear any previous operations.

Use opcode 7 to set the ENABLE byte to zero. This step is only necessary if you are loading into low memory (below address 7880). If so, you should insure that received characters do not get buffered on top of your program code. The way to do this is to prevent the receivers from being serviced, by zapping the ENABLE byte.

Use opcode 9 to copy your code into onboard memory. You can load up to 1019 bytes at a time.

Use opcode 11 to execute the downloaded code.

Page 41

.

Chromatics CGC 7900 Series

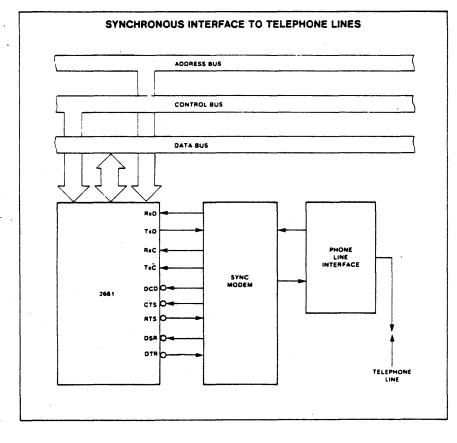

The SPC card contains jumpers which allow external clocks to feed the 2661 USARTs. The 2661's internal clocks may also be fed out to an external device. This might be necessary for a synchronous modem, for example.

#### EXTERNAL CLOCKING IS SUPPORTED BY SPC HARDWARE, BUT NOT BY SPC FIRMWARE. USE OF EXTERNAL CLOCKING WILL REQUIRE CUSTOM USER-WRITTEN FIRMWARE. Chromatics does not provide or support firmware for external clocking (synchronous) SPC operation.

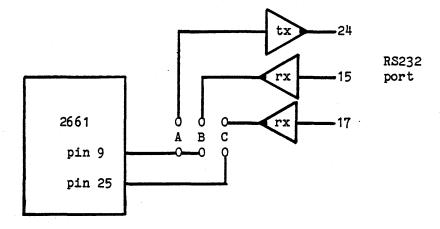

Pin 9 of the 2661 can act as a transmitter clock input, or an output from the internal baud rate generator (1x or 16x clock rate). Pin 25 of the 2661 can act as a receiver clock input, a transmitter/receiver common clock input, or a 1x or 16x clock output. Jumpers near each 2661 can be used to connect pin 9 to the RS232 port pin 15 (through a line receiver for input), or pin 15 (through a line driver for output). A jumper can also connect pin 25 of the 2661 to pin 17 of the RS232 port, through a line receiver.

NOTE: Custom firmware is NECESSARY before installing the jumpers. Standard firmware will program pins 9 and 25 to be <u>output</u> pins. If the jumpers are installed, signals from the 2661 can conflict with signals from the RS232 receivers. Pins 9 and 25 are protected internally on the 2661 in case a conflict occurs, but good engineering practice will not allow the problem to arise in the first place. See the Signetics literature attached to this Application Note, and the descriptions of the 2661 contained in this Note.

The jumper configuration is as follows:

"tx" represents an RS232 transmitter, and "rx" is an RS232 receiver. 24, 15, and 17 are the RS232 connector pin numbers. A, B and C are the locations where jumpers may be installed. This configuration is repeated for each of the four SPC ports, so each port can be jumpered differently.

#### Chromatics CGC 7900 Series

Pins 24, 15 and 17 are defined to be clock signals in many RS232 interfaces. Often, the arrangement is as follows:

| <u>Pin</u> | Usage    | Direction  |

|------------|----------|------------|

| 15         | Tx Clock | From Modem |

| 17         | Rx Clock | From Modem |

| 24         | Tx Clock | To Modem   |

If the SPC's internal clock is to be fed to external devices, install jumper A and the clock will appear on pin 24 of the RS232 connector.

For applications where external clocks must be used for both the transmitter and receiver, install jumpers B and C, and feed the clocks to the SPC on pins 15 and 17 of the RS232 connector, respectively.

If a single external clock is to be used for both transmitting and receiving, install jumper C only, and provide the external clock at pin 17.

External clock timing requirements are listed in the attached Signetics literature. Note that the RS232 transmitters and receivers perform a logical inversion of the clock signal.

#### DIP SWITCHES

Three 8-position DIP switches are used on the SPC to select the board's interrupt vector, interrupt priority level, base address, and card number (if more than one card is installed).

Switch SW1 selects the vector number. Position 1 on SW1 is the most significant bit of the vector number, and position 8 is the least significant bit. The low two bits of SW1 (positions 7 and 8) also select the base address of the card, either FF0000, FF0800, FF1000, or FF1800. The value set by SW1 sets the interrupt vector number, which is multiplied by 4 to determine the vector address. For example: the recommended setting for SW1 is 01111100 (zero is selected when the switch position is ON). In this case, the low two bits are 00, which set the board address at its lowest value, FF0000. The vector number is the switch value, 01111100, or 7C hex. The vector address is 7C times 4, or 1F0 hex.

Switch SW2 selects the card number in a system using multiple SPCs, in a daisy-chained interrupt configuration. (This is discussed in full in the next section.) SW2 positions 1 and 2 should be closed for the first (or only) card in a system; positions 3 and 4 must be closed for the second card, and so on. Two adjacent switches will always be closed on SW2.

Switch SW3 selects the interrupt priority level for the card. Positions 1 and 2 must be closed for level 1; positions 3 and 4 for level 2; positions 5 and 6 for level 3; and positions 7 and 8 for level 6. Level 1 is recommended for SPC interrupts. This is the lowest priority level available. Since the SPC performs onboard buffering, its need for service will be less than most other devices; this is why we recommend level 1. In any case, all SPC cards in a system should be at the same interrupt level, and this level must not be used by any other hardware in the system. Page 46

#### RECOMMENDED SWITCH SETTINGS

("X" means the switch is ON, "." means OFF.)

|         | Switch 1<br>12345678 | Switch 2<br>12345678 | Switch 3<br>12345678 | Base<br>Address | Vector<br>Address |

|---------|----------------------|----------------------|----------------------|-----------------|-------------------|

| Board O | XXX                  | XX                   | XX                   | FF0000          | 1F0               |

| Board 1 | XX.                  | ••XX••••             | XX                   | FF0800          | 1F4               |

| Board 2 | XX                   | ••••XX••             | XX                   | FF1000          | 1F8               |

| Board 3 | X                    | XX                   | XX                   | FF1800          | 1FC               |

#### NOTES:

If only one board is installed in a system, it must be configured as "Board 0".

This table assumes interrupt priority level 1 is used by all SPC boards (set by SW3), and is not used by any other system hardware.

Read the next section before attempting to use multiple SPC boards in a system!

#### Serial Port Controller Application Guide

Page 47

#### INSTALLING MULTIPLE SPCS

The SPC hardware design supports up to four cards in a system. This provides up to 16 serial ports, with each set of four ports controlled by its own Z80 processor. Note that current 7900 firmware and SPC firmware does not support more than one card in a system. You will have to write your own firmware to support a multiple-SPC arrangement.

All four cards should be set to the same interrupt priority level, selected by switch SW3 (see the preceding section). Alternatively, each card could be set to a different level, but this is wasteful of system resources and allows no interrupt levels for other expansion hardware. We strongly advise against this.

Assuming all four cards are at the same priority level, a mechanism is needed to arbitrate between cards when more than one card has an interrupt request pending. This mechanism is provided by SW2 and the daisy-chain connector, P7.

Switch SW2 selects a card's priority within the daisy-chain. Board 0 (see the preceding section) will have the highest priority of the group, followed by board 1 and 2. Board 3 will have the lowest priority of the group. SW2 must be set consecutively for each of the boards in a system.

The daisy-chain cable is connected to P7, and runs in parallel to all boards. This cable is constructed of 10-conductor ribbon cable, and 10-position card edge connectors. It should be as short as possible for best noise rejection. Ideally, all SPCs in a system will be located in adjacent card slots.

The daisy-chain mechanism works as follows: when any card has an interrupt request pending, all cards below it in the chain are prevented from responding to interrupt acknowledge. The next INTACK (interrupt acknowledge) from the CPU, of the correct priority level, will be responded to by the highest SPC in the chain with an interrupt request pending. After the INTACK is complete, other cards in the chain are again enabled. SW2 and P7 provide a gated path for INTACK between cards.

As a result, the highest board in a chain (board 0) will, ideally, get slightly more attention from the 68000 than the other boards. If this is a concern, you should connect the most important devices to the ports on board 0, and the least important devices to board 3.

Software interrupt handlers, running in the 68000, can use much of the same code for all four SPC boards. The interrupt vector (1F0 to 1FC) will determine the base address of the interrupting board (FF0000 to FF1800). Since all four cards are at the same interrupt priority level, there is no concern that the routine will be re-interrupted by another SPC interrupt request. Re-entrant code should not be required.

#### PORT PINOUT

Each of the four SPC ports uses a male 25-pin "D" connector. The port is wired as a <u>terminal</u>.

To connect to a modem, use a straight cable, wired one-to-one, with a female connector on the SPC end and a male on the modem end. To connect to a terminal, you must construct a cable which interchanges pins 2 and 3, pins 4 and 5, and pins 6 and 20.

In some applications, only pins 2, 3, and 7 are necessary for proper operation.

<u>Pin</u> #

<u>Usage</u>

1 Ground 2 Transmit Data (output) Receive Data (input) 3 4 Request to Send (output) 5 6 Clear To Send (input) Data Set Ready (output) Ground 7 8 Data Carrier Detect (input) 20 Data Terminal Ready (output) 15, 17, 24 User-defined (see below)

Pins 5, 6, and 8 are control inputs. They are normally driven by the corresponding outputs of a modem. Internal pullup resistors on the SPC will hold these signals in a "true" state if the external device does not connect to them.

Pin 4 (RTS) is always asserted "true" by standard firmware, when the SPC is running. Pin 20 (DTR) is also "true" unless hardware handshaking is in use; then it becomes "false" when the SPC is unable to accept characters. Idris also uses pin 20 as a modem-control signal.

Pins 15, 17 and 24 are disconnected unless jumpers are installed. See the "External Clocking" section of this document for details.

Other pins are not connected.

Page 50

Chromatics CGC 7900 Series

#### 2661 DATA SHEET

The following material is reprinted by permission of Signetics Corporation, a subsidiary of U.S. Philips Corporation, 1077 East Arques Avenue, Sunnyvale California 94086.

Copyright (c) 1981 by Signetics Corporation.

.

Reprinted by Chromatics, Inc. with Permission of Signetics Corp., a subsidiary of U.S. Philips Corp., 1077 E. Arques Ave., Sunnyvale, Ca 94086.

# Signetics SC2661 November 1981

# Enhanced Programmable Communications Interface (EPCI)

Signetics reserves the right to make changes in the products contained in this document in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and Signetics makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

1

## ENHANCED PROGRAMMABLE COMMUNICATIONS INTERFACE (EPCI) SC2661

#### DESCRIPTION

The Signetics 2661 EPCI is a universal synchronous/asynchronous data communications controller chip that is an enhanced pin compatible version of the 2651. It interfaces directly to most 8-bit microprocessors and may be used in a polled or interrupt driven system environment. The 2661 accepts programmed instructions from the microprocessor while supporting many serial data communications disciplines synchronous and asynchronous—in the full or half-duplex mode. Special support for BISYNC is provided.

The EPCI serializes parallel data characters received from the microprocessor for transmission. Simultaneously, it can receive serial data and convert it into parallel data characters for input to the microcomputer.

The 2661 contains a baud rate generator which can be programmed to either accept an external clock or to generate internal transmit or receive clocks. Sixteen different baud rates can be selected under program control when operating in the internal clock mode. Each version of the EPCI (A, B, C) has a different set of baud rates.

The EPCI is constructed using Signetics n-channel silicon gate depletion load technology and is packaged in a 28-pin DIP.

#### FEATURES

- Synchronous operation

to 8-bit characters plus parity

Single or double SYN operation

Internal or external character

synchronization

- Transparent or non-transparent mode Transparent mode DLE stuffing (Tx) and detection (Rx) Automatic SYN or DLE-SYN insertion

- SYN, DLE and DLE-SYN stripping Odd, even, or no parity Local or remote maintenance loop back.

- mode Baud rate: dc to 1M bps (1X clock)

- Asynchronous operation

5 to 8-bit characters plus parity

1, 1% or 2 stop bits transmitted

Odd, even, or no parity

Parity, overrun and framing error

detection

Line break detection and generation

False start bit detection

- Automatic serial echo mode (echoplex) Local or remote maintenance loop back mode

- Baud rate: dc to 1M bps (1X clock) dc to 62.5K bps (16X clock) dc to 15.625K bps (64X clock)

#### OTHER FEATURES

- Internal or external baud rate clock

- 3 baud rate sets

- 16 internal rates for each set

Double buffered tennemittee

- Double buffered transmitter and receiver

- Dynamic character length switching

- Full or half duplex operation

- Fully compatible with 2650 CPU

- TTL compatible inputs and outputs

- RxC and TxC pins are short circuit protected

- 3 open drain MOS outputs can be wire-ORed

- Single 5V power supply

- No system clock required

- 28-pin dual in-line package

#### **APPLICATIONS**

- Intelligent terminals

- Network processors

- Front end processors

- Remote data concentrators

- Computer to computer links

- Serial peripherals

- **BISYNC** adaptors

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGES<br>$V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to 70°C |                            |  |

|-------------|-------------------------------------------------------------------------|----------------------------|--|

| Ceramic DIP | SC2661ACSI28<br>SC2661BCSI28<br>SC2661CCSI28                            | See table 1 for baud rates |  |

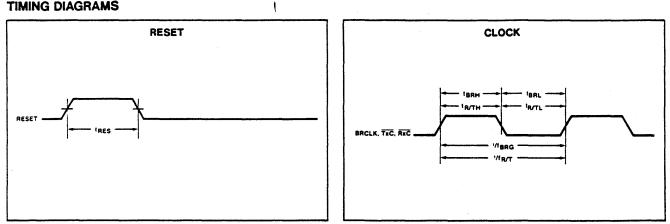

| Plastic DIP | SC2661ACSN28<br>SC2661BCSN28<br>SC2661CCSN28                            | See table 1 for baud rates |  |

#### PIN DESIGNATION

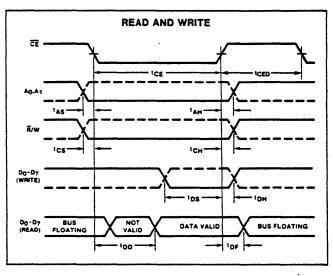

| PIN NO.  | SYMBOL      | NAME AND FUNCTION                    | TYPE |

|----------|-------------|--------------------------------------|------|

| 27,28,1, |             |                                      |      |

| 2,5-8    | D0-D7       | 8-bit data bus                       | 1/0  |

| 21       | RESET       | Reset                                | 1    |

| 12,10    | A0-A1       | Internal register select lines       | 1    |

| 13       | R/W         | Read or write command                | t t  |

| 11       | CE          | Chip enable input                    | l I  |

| 22       | DSR         | Data set ready                       | i l  |

| 24       | DTR         | Data terminal ready                  | 0    |

| 23       | RTS         | Request to send                      | 0    |

| 17       | CTS         | Clear to send                        | . 1  |

| 16       | DCD         | Data carrier detected                | 1    |

| 18       | TxEMT/DSCHG | Transmitter empty or data set change | 0    |

| 9        | TxC/XSYNC   | Transmitter clock/external SYNC      | 1/0  |

| 25       | RxC/BKDET   | Receiver clock/break detect          | .1/0 |

| 19       | TxD         | Transmitter data                     | 0    |

| 3        | RxD         | Receiver data                        | 1    |

| 15       | TxRDY       | Transmitter ready                    | , O  |

| 14       | RxRDY       | Receiver ready                       | 0    |

| 20       | BRCLK       | Baud rate generator clock            | 1    |

| 26       | Vcc         | +5V supply                           | 1    |

| 4        | GND         | Ground                               | 1    |

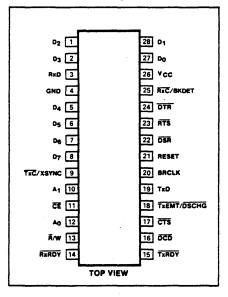

#### **PIN CONFIGURATION**

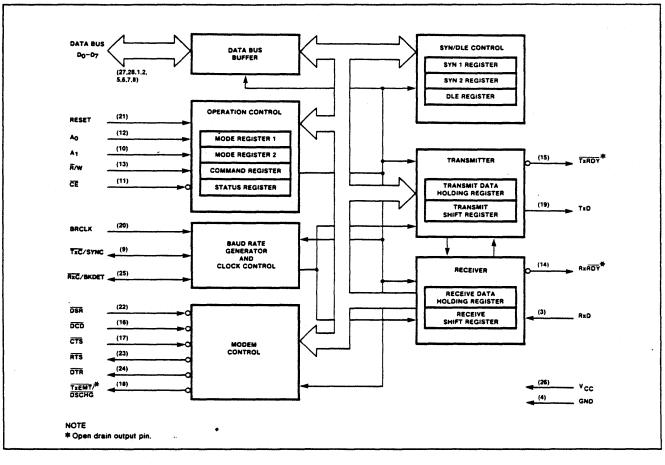

#### BLOCK DIAGRAM

#### **BLOCK DIAGRAM**

The EPCI consists of six major sections. These are the transmitter, receiver, timing, operation control, modem control and SYN/DLE control. These sections communicate with each other via an internal data bus and an internal control bus. The internal data bus interfaces to the microprocessor data bus via a data bus buffer.

#### **Operation Control**

This functional block stores configuration and operation commands from the CPU and generates appropriate signals to various internal sections to control the overall device operation. It contains read and write circuits to permit communications with the microprocessor via the data bus and contains mode registers 1 and 2, the command register, and the status register. Details of register addressing and protocol are presented in the EPCI programming section of this data sheet.

# Table 1 BAUD RATE GENERATOR CHARACTERISTICS SC2661A (BRCLK = 4.9152MHz)

| MR23-20 | BAUD<br>RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|---------|--------------|----------------------------------|------------------|---------|

| 0000    | 50           | 0.8kHz                           | -                | 6144    |

| 0001    | 75           | 1.2                              | -                | 4096    |

| 0010    | 110          | 1.7598                           | -0.01            | 2793    |

| 0011    | 134.5        | 2.152                            | -                | 2284    |

| 0100    | 150          | 2.4                              | -                | 2048    |

| 0101    | 200          | 3.2                              | -                | 1536    |

| 0110    | 300          | 4.8                              | -                | 1024    |

| 0111    | 600          | 9.6                              |                  | 512     |

| 1000    | 1050         | 16.8329                          | 0.196            | 292     |

| 1001    | 1200         | 19.2                             | -                | 256     |

| 1010    | 1800         | 28.7438                          | -0.19            | . 171   |

| 1011    | 2000         | 31.9168                          | -0.26            | 154     |

| 1100    | 2400         | 38.4                             | -                | 128     |

| 1101    | 4800         | 76.8                             | -                | 64      |

| 1110    | 9600         | 153.6                            | -                | 32      |

| 1111    | 19200        | 307.2                            | -                | 16      |

#### Timing

The EPCI contains a baud rate generator (BRG) which is programmable to accept external transmit or receive clocks or to divide an external clock to perform data communications. The unit can generate 16 commonly used baud rates, any one of which can be selected for full duplex operation. See table 1.

#### Receiver

The receiver accepts serial data on the RxD pin, converts this serial input to parallel format, checks for bits or characters that are unique to the communication technique and sends an "assembled" character to the CPU.

#### Transmitter