# 68000 central processing unit hardware reference manual

CODATA SYSTEMS CORP.

# LIMITED WARRANTY

CODATA SYSTEMS, CORP. electrical and mechanical products are warranted for a period of one hundred eighty days from the date of shipment from CODATA SYSTEMS, CORP. Equipment supplied by CODATA SYSTEMS, CORP. is designed and intended for use in commercial applications. This Limited Warranty provides for the repair or replacement of any product which may prove defective in materials or workmanship during this time. CODATA SYSTEMS, CORP. reserves the right to decide if the equipment will be repaired or replaced. All equipment to be repaired or replaced under terms of this Limited Warranty must be returned to a CODATA SYSTEMS CORP. Service Facility. Please see the instructions in the user's manual to arrange service under this Limited Warranty.

This Limited Warranty is not valid if the equipment has been subjected to abuse or misuse. In case of damage to the product due to shipping, handling or incorrect installation, standard repair charges will be assessed.

THERE ARE NO WARRANTIES WHICH EXTEND BEYOND THE DESCRIPTION ON THE FACE HEREOF. BUYER AFFIRMS THAT HE HAS NOT RELIED ON SELLER'S SKILL OR JUDGMENT TO SELECT OR FURNISH SOFTWARE FOR ANY PARTICULAR PURPOSE AND THIS SALE IS MADE WITHOUT ANY WARRANTY BY SELLER THAT SUCH SOFTWARE IS SUITABLE FOR ANY PARTICULAR PURPOSE. SELLER MAKES NO WARRANTY OF MERCHANTABILITY IN RESPECT TO THE SOFTWARE SOLD UNDER THIS AGREEMENT.

All statements regarding this Limited Warranty are contained in this document. Representatives or Distributors of CODATA SYSTEMS, CORP. products may not make any statements regarding the expansion or extension of this Limited Warranty, unless those statements are in writing and signed by a corporate officer of CODATA SYSTEMS, CORP.

This Agreement constitutes the entire contract and exclusively determines the rights and obligations of the parties hereto, any prior course of dealing, custom or usage of trade or course of performance notwithstanding.

| ILLUSTRATIONS                                                                                      | PAGE |

|----------------------------------------------------------------------------------------------------|------|

| Figure 2-1 – 68000 Central Processing Unit –                                                       |      |

| - ·                                                                                                |      |

| 92-1012-xx                                                                                         | 4    |

|                                                                                                    | 6    |

| Table 2-1 — Test Points                                                                            | 7    |

| Figure 3-1 – 68000 Central Processing Unit Block                                                   | _    |

| Diagram                                                                                            | 8    |

| Table 3-1 – 68000 CPU Logical Address Locations                                                    | 11   |

| Figure 3-2 – Memory Map Block Diagram                                                              | 12   |

| Table 3-2 – Segment Level Protection Attributes .                                                  | 14   |

| Table 3-3 – Memory Map Register Bit Map     .       Figure 3.2     Op Cond 25 Gld Button DAM Block | 16   |

| Figure 3-3 – On-Card 256k Byte RAM Block                                                           | 47   |

| Diagram                                                                                            | 17   |

| Eleven 2 E LIADT Disch Discuss                                                                     | 19   |

| Figure 2.C. Times Disals Disaus                                                                    | 20   |

| Financial Table Bolt A Distance                                                                    | 21   |

| Figure 3-7 – 796 Bus Interface Block Diagram                                                       | 22   |

| Figure 3-9 – Device Decoder Block Diagram                                                          | 23   |

| Figure 3-10 – Power-On-Reset Block Diagram                                                         | 24   |

| Figure 3-11 – System Timing Block Diagram                                                          | 25   |

| -                                                                                                  | 26   |

| Table 3-4 – 68000 Central Processing Unit Active                                                   | 07   |

| 796 Bus Signals                                                                                    | 27   |

| Figure 3-12 – On-Card RAM Read Cycle Timing                                                        | 28   |

| Figure 3-13 – On-Card RAM Write Cycle Timing                                                       | 29   |

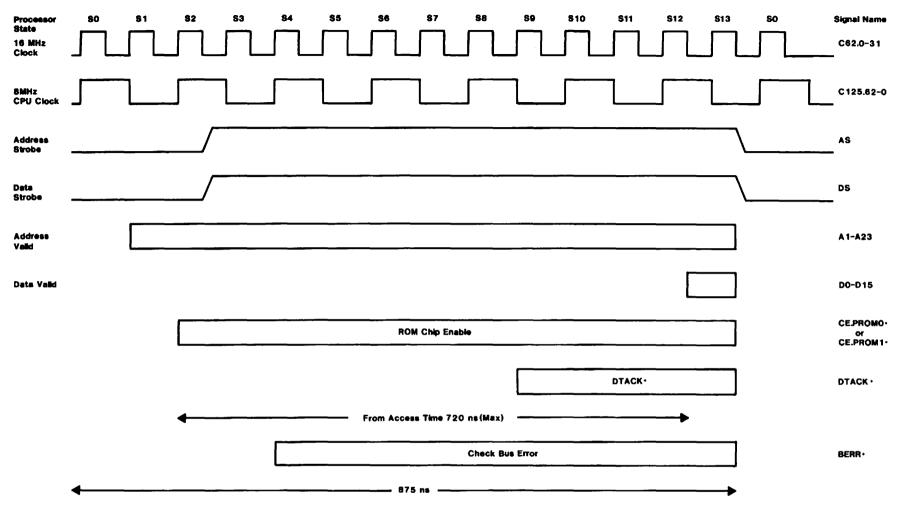

| Figure 3-14 — On-Card ROM Read Cycle Timing .<br>Figure 3-15 — Off-Card RAM and Input Output       | 30   |

| Read Cycle Timing                                                                                  | 31   |

| Figure 3-16 – Off-Card RAM and Input Output                                                        | 31   |

| Write Cycle Timing                                                                                 | 32   |

| Table 4-1 – 68000 Central Processing Unit                                                          | 32   |

| 92-1012-xx — Specifications                                                                        | 33   |

| Table 5-1 – 68000 Central Processing Unit Options                                                  |      |

| P/N 91-1012-xx                                                                                     | 36   |

| Figure 5-1 – UART Register Values                                                                  | 39   |

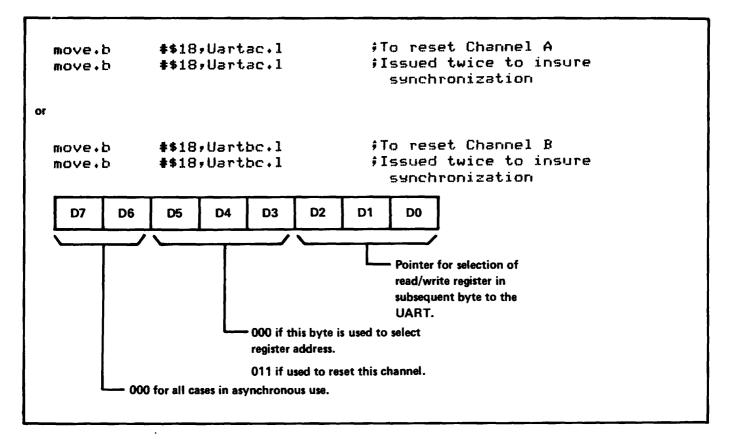

| Figure 5-2 – Write Register 0 Routine and                                                          |      |

| Register Map                                                                                       | 40   |

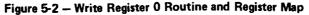

| Figure 5-3 – Write Register 1 Routine and                                                          |      |

| Register Map                                                                                       | 40   |

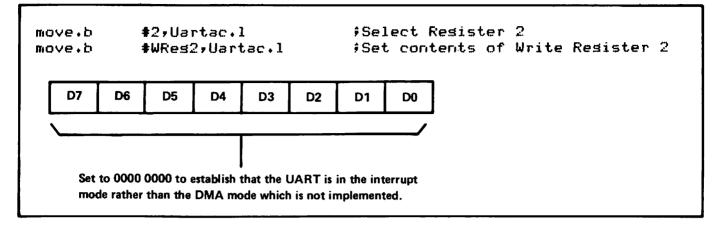

| Figure 5-4 – Write Register 2 Routine and                                                          |      |

| Register Map                                                                                       | 41   |

| Figure 5-5 — Write Register 3 Routine and                                                          |      |

| Register Map                                                                                       | 41   |

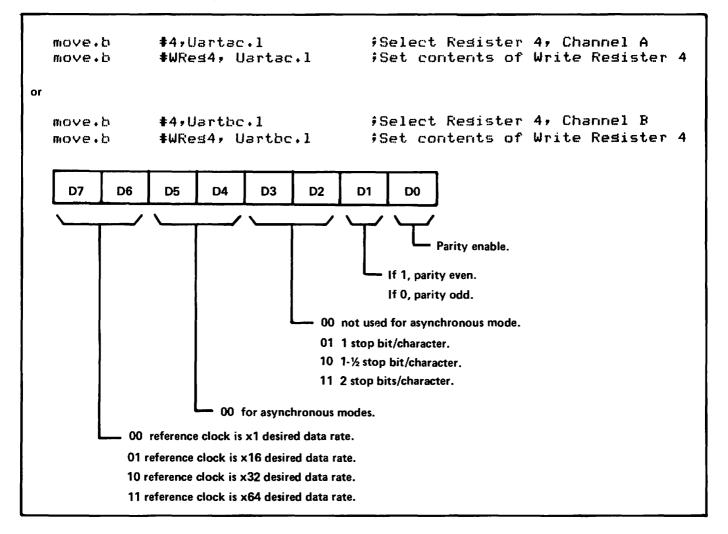

| Figure 5-6 Write Register 4 Routine and                                                            |      |

| Register Map                                                                                       | 42   |

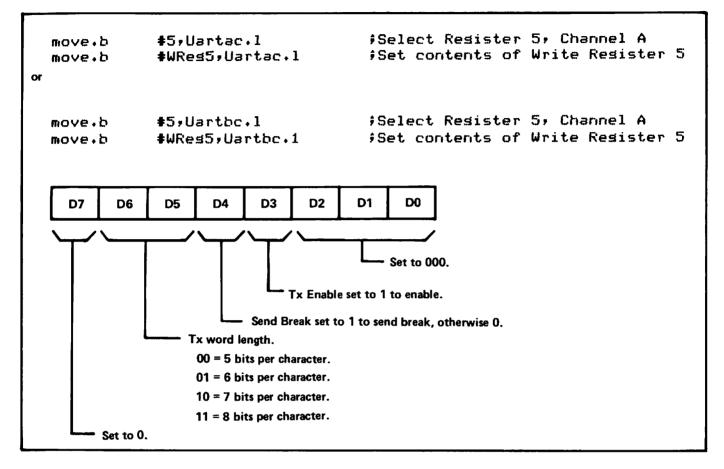

| Figure 5-7 — Write Register 5 Routine and                                                          |      |

| Register Map                                                                                       | 43   |

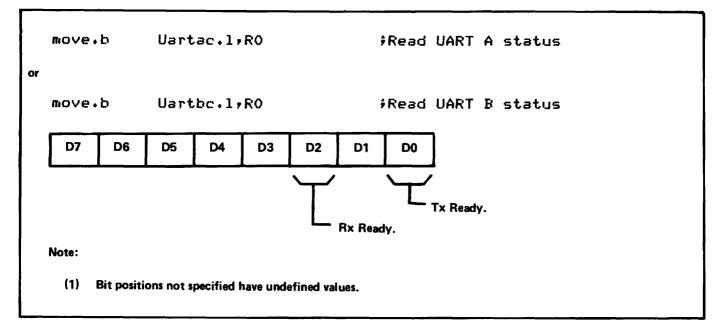

| Figure 5-8 — Read UART A or B Status Routine                                                       |      |

| and Register Map                                                                                   | 44   |

| Figure 5-9 — Send Data to UART A or B Routine                                                      |      |

| and Register Map                                                                                   | 44   |

| Figure 5-10 – Receive Data from UART A or B                                                        |      |

| Routine                                                                                            | 44   |

# ILLUSTRATIONS

# PAGE

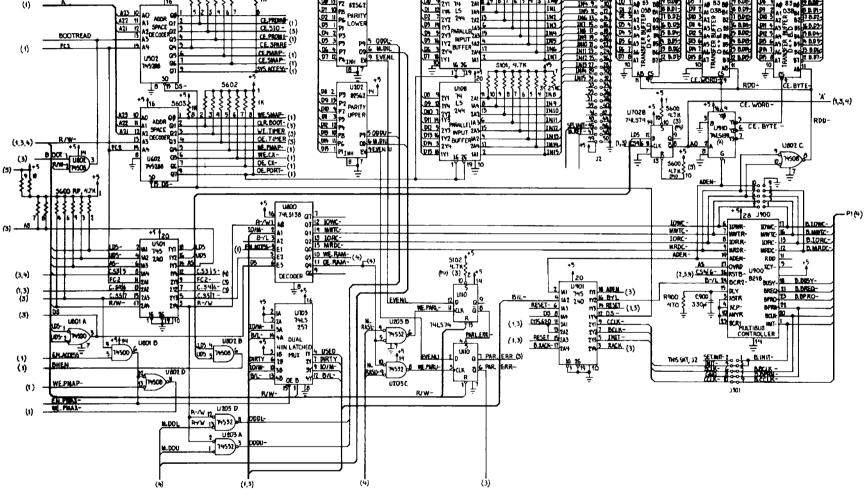

| Figure 5-11 – Timer Initialization Routine     |     |    | 46 |

|------------------------------------------------|-----|----|----|

| Figure 5-12 - Watchdog Timer Set Up Routine    |     |    | 47 |

| Figure 5-13 - RTC and Refresh Timer Set Up     |     |    |    |

| Routines                                       |     |    | 47 |

| Figure 5-14 – RTC and Refresh Timer Clear      |     |    | 47 |

| Routine                                        |     |    | 48 |

| Figure 5-15 - Values for Period Between Interr | upt | ts | 40 |

| on Resets                                      |     |    | 48 |

| Figure 5-16 – Values for Divisor Constant      |     |    | 48 |

| Figure 5-17 – UART Timer Set Up Routines       |     |    | 49 |

| Figure 5-18 — Values of Constants Used to      |     |    | 43 |

| Program Timer Device                           |     | -  | 50 |

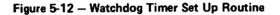

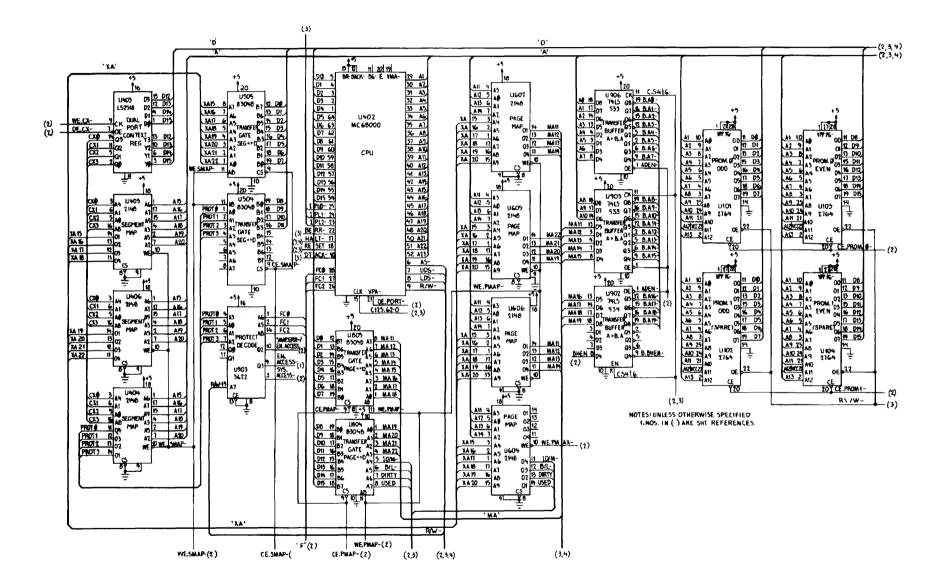

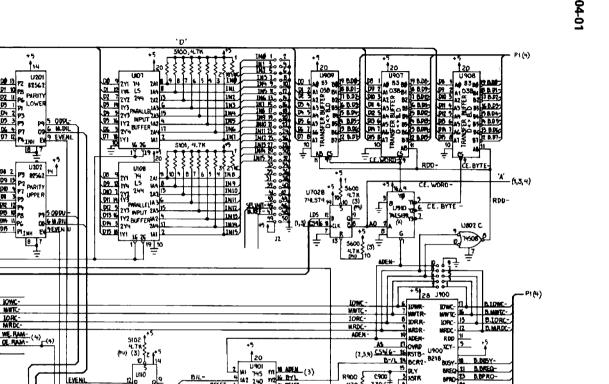

| Figure 7-1 - 68000 Central Processing Unit Log | jic |    | 50 |

| Diagram                                        |     |    | 53 |

| Table 7-1 – 68000 Central Processing Unit      |     |    | 55 |

| Replaceable Parts List                         |     |    | 57 |

| Table 7-2 - Pin Assignments on 796 Bus Board   |     |    | 0, |

| Connector (P1)                                 |     |    | 62 |

| Table 7-3 - Pin Assignments on 796 Bus Board   |     |    | 02 |

| Connector (P2)                                 |     |    | 63 |

| Table 7-4 – 68000 CPU Connector P1 Pin         |     |    | 00 |

| Assignments                                    |     |    | 64 |

| Table 7-5 – 68000 CPU Connector P2 Pin         |     |    | •• |

| Assignments                                    |     |    | 66 |

| Table 7-6 - Pin Assignments of RS-423 Serial I | 0   |    |    |

| Board Connector (J1)                           |     |    | 68 |

| Table 7.7 Pin Assignments of 16-Bit Parallel   |     |    |    |

| Input Port (J2)                                |     |    | 69 |

|                                                | -   | -  |    |

# 1. GENERAL

**1.01** This manual provides a physical description, functional description and operating theory

for effective maintenance of the Codata Systems Corp. 68000 Central Processing Unit, 92-1012-xx.

1.02 The 68000 Central Processing Unit (CPU) is supplied as a single printed circuit assembly (PCA) for use as a system component in the Codata Systems Corp:

- (1) CTS-Series Mainframe,

- (2) CTW-Series Mainframe.

#### Features

1.03 The 68000 CPU is a powerful single card processor designed around the MCL68000L microprocessor ( $\mu$ P) device. CPU features include:

- The 68000  $\mu$ P operates at 8 MHz.

- IEEE 796 Microcomputer Bus compatible.

- Multimaster capability.

- The entire CPU is on a single PCA.

- 20-bit 796 Bus providing 1M byte addressing.

- A segmented, paged, memory management method.

- Up to 256k bytes of on-card parity-checked dynamic Random Access Memory (RAM). The RAM operates without wait states.

- Up to 32k bytes of on-card Read Only Memory (ROM).

- Two universal asynchronous receiver transmitters (UARTs) for serial input output (I/O). EIA RS-423A compatible.

- Five 16-bit timer channels.

- One 16-bit parallel input port.

- Seven level interrupt with priority set by option jumpers.

- Single +5 Vdc power requirement.

#### NOTE

The following reference notations apply in this technical manual:

- (1) A \* suffix to a single name indicates logical NOT and active low.

- (2) In and out references are in respect to CPU or bus master.

- (3) 1k byte equals 1,024 bytes, i.e., 64k bytes equals 65,536 bytes.

- (4) Codata Systems part numbers are made up of eight digits, e.g., the part number of this manual is 05-0004-01.

- (5) A suffix -xx to a part number indicates the part or assembly may have more

than one configuration in production, i.e.,

the 68000 Central Processing Unit is

92-1012-xx.

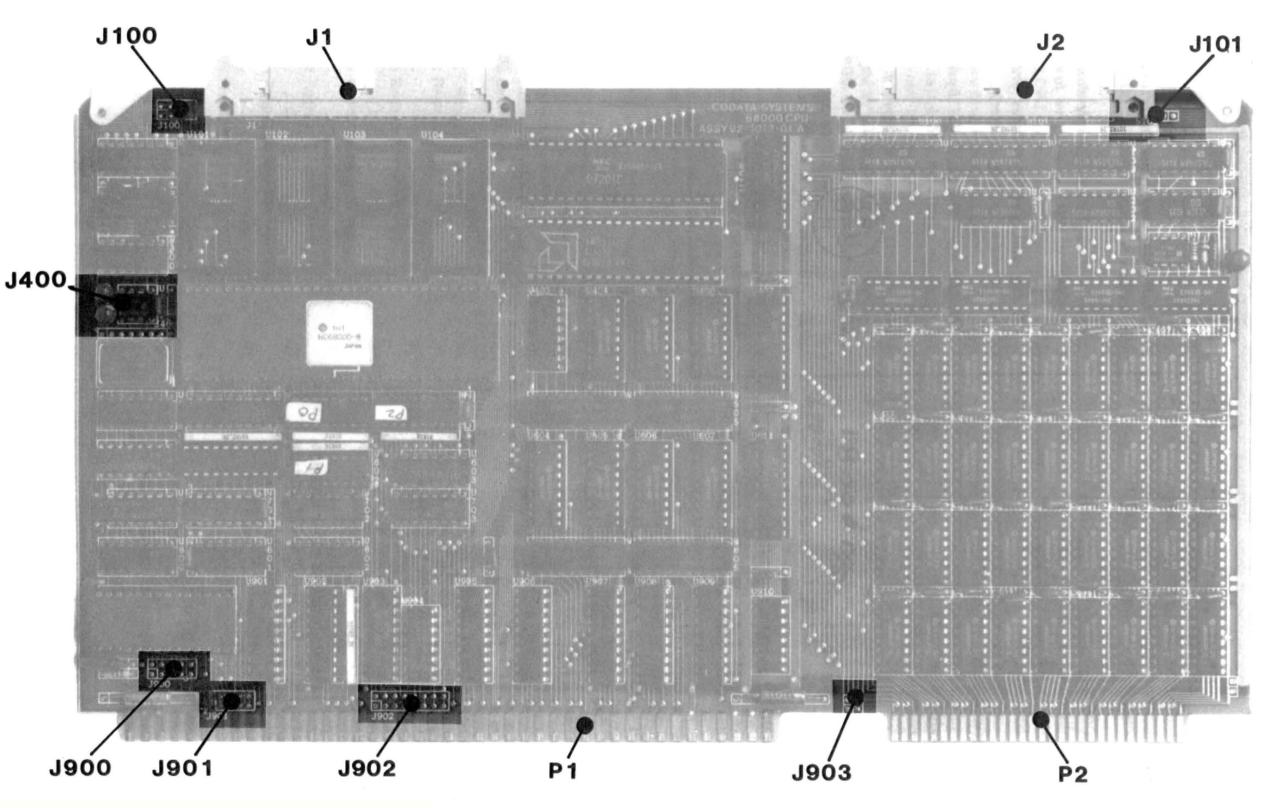

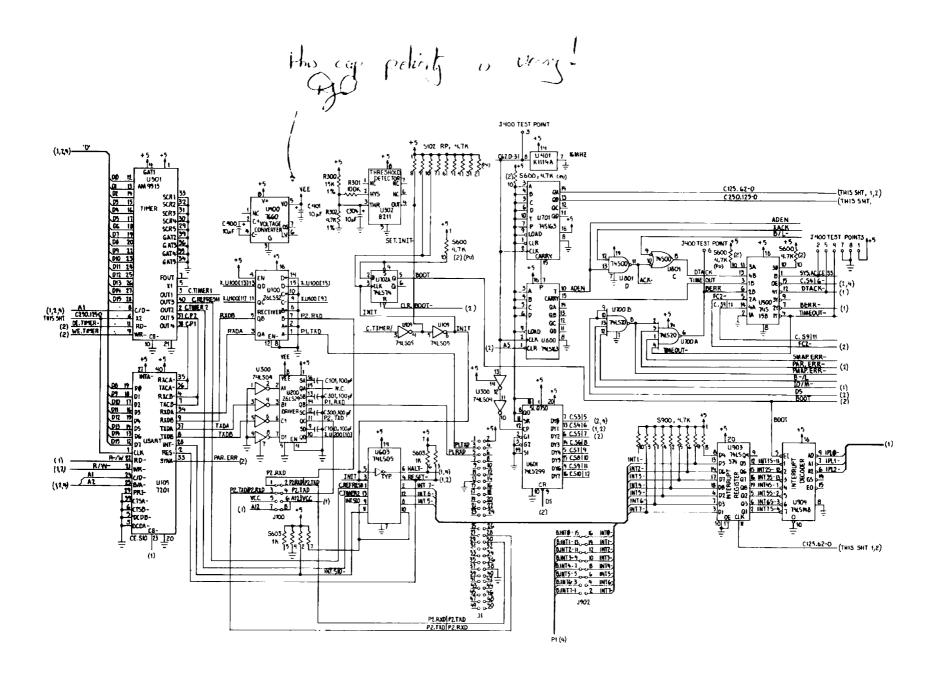

Figure 2-1 - 68000 Central Processing Unit - 92-1012-xx

#### 2. PHYSICAL DESCRIPTION

2.01 The 68000 Central Processing Unit (CPU) 92-1012-xx is an integrated system component incorporating all the necessary component parts to provide the Mainframe with a single PCA CPU. Figure 2-1 illustrates the 68000 CPU. The PCA contains:

- (1) A 68000  $\mu$ P section. This is a 16-bit  $\mu$ P operating at 8 MHz.

- (2) A Memory Management section.

- (3) A Memory Control section.

(4) A 256k byte RAM section providing the  $\mu$ P with up to 256k bytes of dynamic memory independent from the Mainframe RAM.

- (5) A 32k ROM section providing the  $\mu$ P with up to 32k firmware.

- (6) A UART section. This provides two RS-423A serial I/O ports for the Mainframe.

- (7) A Timer section providing the programmer with five 16-bit programmable timers.

- (8) A 796 Bus Interface section.

- (9) A 16-bit Parallel Input Port section.

- (10) A Clocks and Logic section.

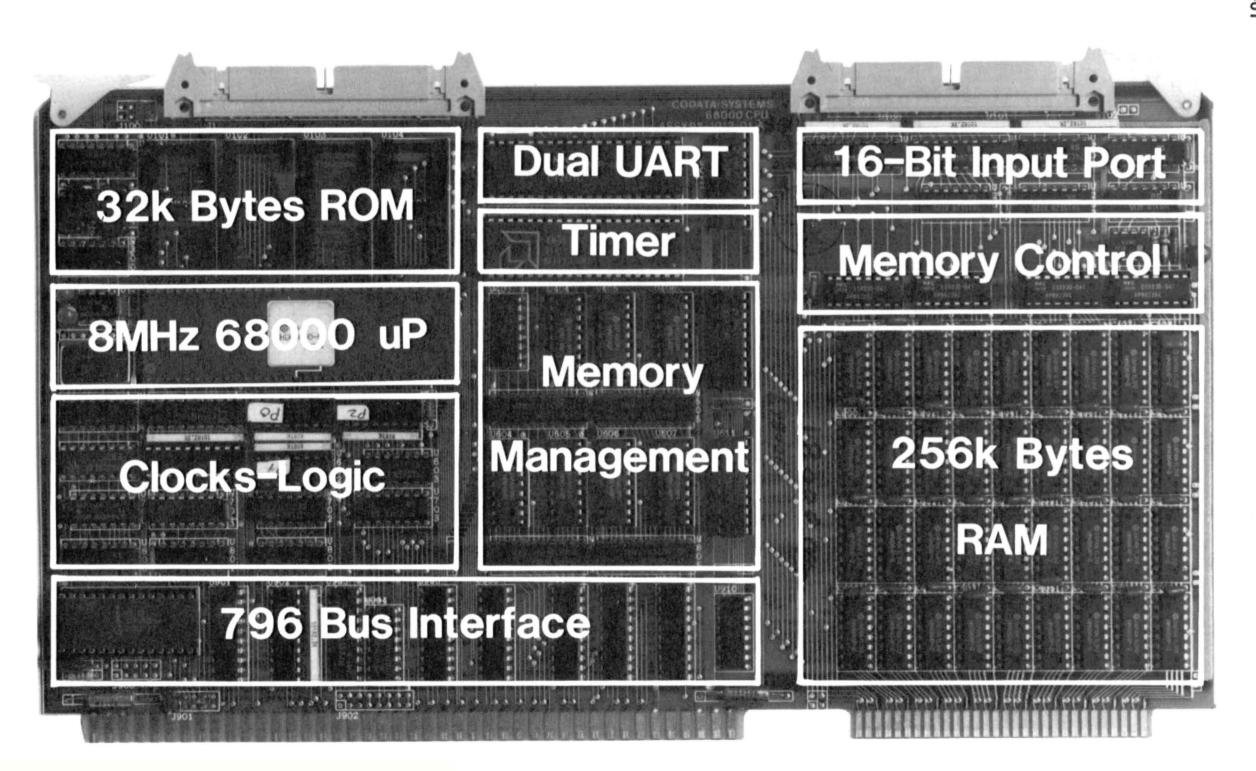

Figure 2-2 illustrates the physical locations of these sections on the PCA.

2.02 The PCA measures 6.0 inches by 12.0 inches. A pair of edge-type pc connectors, P1 and P2, mate with the 796 Bus Backplane connectors.

P1 is a dual 43-position, 86-conductor pc connector. The pin assignments conform to the 796 Bus specification.

#### IMPORTANT

The 68000 should not be installed in a backplane having the connector mating with P2 wired to the 796 Bus specification.  (2) P2 is a dual 30-position, 60-conductor pc connector. These pins are used for off-card RAM expansion. The pin assignments do not conform to the 796 Bus specification.

2.03 A pair of flat ribbon cable recepticals are provided at the top of the PCA for connection to external I/O devices.

- The J1 connector provides data and status/control lines from two RS-423A

data communication lines (DCL). The 50-conductor interconnect cable is terminated by two DB-25S connectors on the Mainframe Rear Panel. Refer to Table 7-6 for individual PCA pin assignments.

- (2) The J2 connector provides data input lines for the 16-bit Input Port and lines for an external reset switch. Refer to Table 7-7 for individual PCA pin assignments.

2.04 Distinctive white silkscreen marking has been provided on the component side of the PCA. Component reference designators are marked where practical. They facilitate locating individual parts on the logic diagram or replaceable parts list.

Options

2.05 Several alternate features can be configured through option jumpers on the PCA. Refer to Figure 2-1.

- (1) J100 configures UART B as a DCE or DTE port and selects the ROM size.

- (2) J900 generates the 796 Bus control signals with or without using the 8218 device.

- (3) J901 selects the source or destination of INIT\* and Bus Clocks.

- (4) J902 selects the interrupt levels.

# **Test Points**

2.06 Test points for the 68000 CPU have been provided on the PCA for repair and maintenance. Table 2-1 tabulates these by location and function.

Figure 2-2 - 68000 Central Processing Unit Layout

Table 2-1 — Test Points

| Reference                                                                    | Mnemonic                                                                                                                                                                                                                     | Function                                                                                                              |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|                                                                              | Halt Indicator                                                                                                                                                                                                               |                                                                                                                       |

| J101.1                                                                       | VCC                                                                                                                                                                                                                          | +5 Vdc                                                                                                                |

| J101.2                                                                       | M.REF*                                                                                                                                                                                                                       | Memory Refresh — Halt                                                                                                 |

|                                                                              | NOTE                                                                                                                                                                                                                         |                                                                                                                       |

|                                                                              | An LED with an internal<br>current limiting resistor<br>may be installed between<br>J101.1 and J101.2 to act<br>as an indicator that the μP<br>is HALTED. An LED is<br>not supplied in the<br>standard PCA<br>configuration. |                                                                                                                       |

|                                                                              | General Test Points                                                                                                                                                                                                          |                                                                                                                       |

| J400.1<br>J400.2<br>J400.3<br>J400.4<br>J400.5<br>J400.6<br>J400.7<br>J400.8 | VCC<br>SYS.ACCESS*<br>C62.0-31<br>TIMEOUT*<br>DTACK*<br>BERR<br>GND<br>GND                                                                                                                                                   | +5 Vdc<br>System Access<br>16 MHz Clock<br>Timeout<br>Data Acknowledge<br>Bus Error<br>Signal Ground<br>Signal Ground |

|                                                                              | Memory Column Address<br>Strobe Test Points                                                                                                                                                                                  |                                                                                                                       |

| J903.1<br>J903.2<br>J903.3                                                   | M.CAS0*<br>M.CAS1*<br>M.CAS2*                                                                                                                                                                                                | Memory CAS0<br>Memory CAS1                                                                                            |

| J903.4                                                                       | M.CAS2*<br>M.CAS3*                                                                                                                                                                                                           | Memory CAS2<br>Memory CAS3                                                                                            |

# 3. FUNCTIONAL DESCRIPTION

Overview

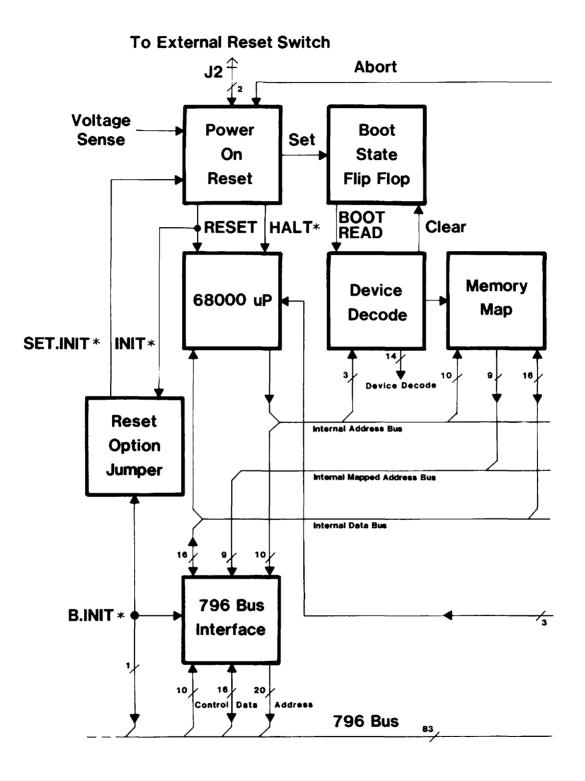

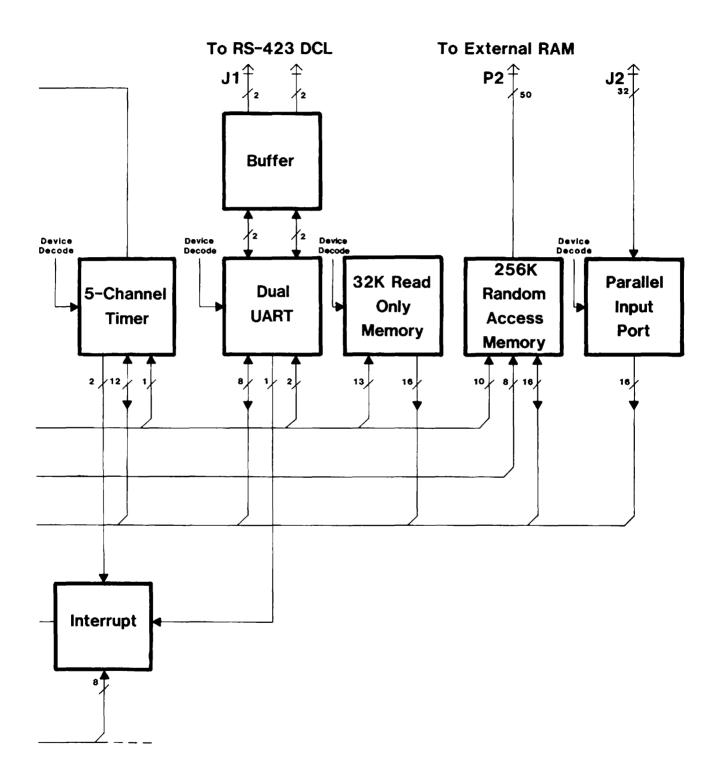

3.01 The basic function of a central processing unit (CPU) in a computing system is to

accept data and processing instructions, perform processing operations and deliver the processed data. Several additional functions are provided by the 68000 CPU besides this basic function. Figure 3-1 illustrates each function in block diagram.

Figure 3-1 - 68000 Central Processing Unit Block Diagram

Figure 3-1 - 68000 Central Pricessing Unit Block Diagram (Cont.)

- (1) 68000 microprocessor ( $\mu$ P),

- (2) Memory Map,

- (3) Random Access Memory,

- (4) Interrupt,

- (5) Dual UART Serial Input Output (I/O),

- (6) Five-Channel Timer,

- (7) 796 Bus Interface,

- (8) Parallel Input Port,

- (9) Device Decode,

- (10) Power-On-Reset,

- (11) System Timing.

The following paragraphs will discuss each function in detail. Figures 3-2 through 3-11 furnish detailed block diagrams of the sections. CPU timing is illustrated in Figures 3-12 through 3-16. These figures should be used in conjunction with the logic diagram, Figure 7-1, for the descriptions which follow.

#### 68000 Microprocessor

3.02 The principle device on the CPU is the 68000  $\mu$ P. This is a high-performance  $\mu$ P with 32-bit architecture and a large uniform memory space. This  $\mu$ P features sixteen 32-bit registers divided into two sets of eight address registers and eight data registers.

3.03 The  $\mu P$  instruction set and addressing modes are both extremely regular in their implementation with a minimum of special cases thus making high-level language code generation fairly simple.

- **3.04** The  $\mu$ P manipulates three major data formats:

- (1) 8-bit words,

- (2) 16-bit words,

- (3) 32-bit words.

The  $\mu P$  can operate in supervisor or user states assuring a secure operating system. The 68000 CPU has been designed to fully utilize the high performance of the  $\mu P$  by providing on-card RAM that will operate without wait states at the 8 MHz speed of the system.

#### **Bus Structure**

- 3.05 The 68000 CPU has two principle data busses:

- An internal 16-bit synchronous bus to communicate with on-card RAM/ROM and I/O devices. Since on-card accesses do not require the 796 Bus, the 796 Bus is available for use by other 796 Bus Masters, e.g., Diskette or Winchester Disk Controllers.

- (2) The 796 Bus for accessing off-card RAM and I/O devices.

#### NOTE

While the CPU has complete access to the 796 Bus, the 796 Bus cannot access on-card memory or I/O devices.

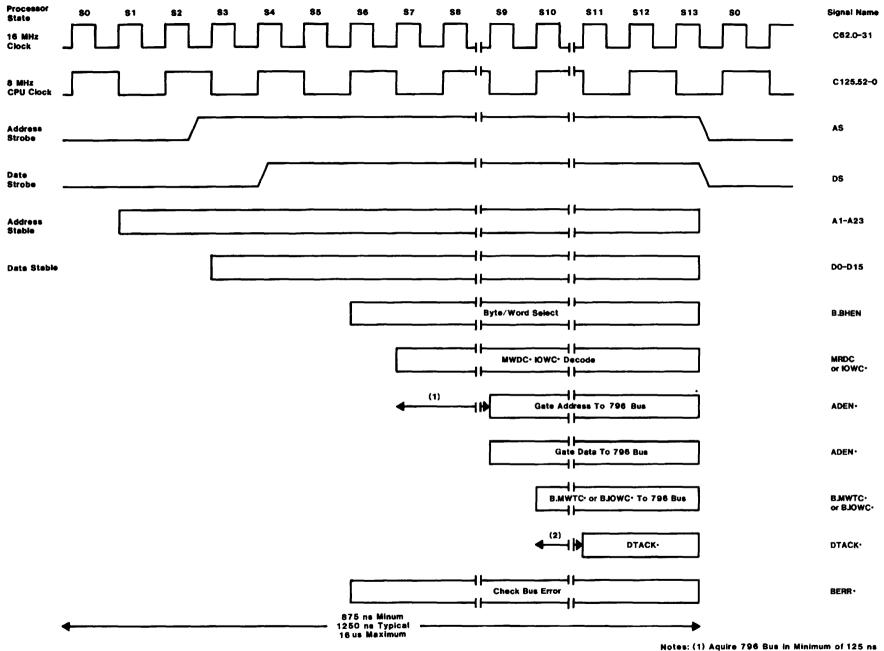

Accesses to 796 Bus devices are slower than on-card devices. The  $\mu P$  cycles are stretched by an amount appropriate to the 796 Bus device being accessed. Refer to Figures 3-15 and 3-16.

3.06 The 68000 CPU is initialized through a reset which can be activated through several channels. The reset logic is detailed in 3.54 below.

- 3.07 The  $\mu P$  is reset when both the HALT\* and RESET\* lines are held low. A card reset can be initiated by the  $\mu P$  noting the logical condition of these two lines and holding the RESET\* line low.

- 3.08 Several operations take place after a reset:

- (1) The *Boot State Flip-Flop* is set and the boot state is entered.

- (2) The Device Decode enables the Read Only Memory (ROM).

(3) Instructions stored in ROM are overlaid into address space normally occupied by RAM starting at location 000 000H. These instructions form what is usually called the Boot Strap process. During this process, the exception vectors located at address 000 008H to 000 0FFH are copied to RAM by reading the data from ROM and writing the data to RAM. This process is called shadow RAM.

- (4) The last instruction in the boot strap program is a write to ROM location

200 000H causing the *Device Decode* to clear the *Boot State Flip Flop*.

- (5) After the Boot State Flip Flop has cleared the ROM, instructions are removed from

000 000H and the RAM locations become available for program variables, e.g., exception vectors and program. The boot state is exited.

#### Addressing

3.09 Table 3-1 lists the 68000 CPU address mapping for memory-managed RAM, and

all on-card devices. All addresses above 200 000H are not memory managed and are absolute addresses for the named devices.

ROM

- 3.10 Up to 32k bytes of ROM may be installed on the 68000 CPU in two separate groups,

ROM 0 and ROM 1, whose addresses begin at 200 000H and 400 000H, respectively. The ROM 0 group is also addressed starting at location 000 000H while the 68000 CPU is in boot state.

- 3.11 Sockets on the printed circuit assembly provide for three ROM types:

- (1) The 2716 device for two groups of 2k x 16-bit words or 8k bytes.

- (2) The 2732 device for two groups of 4k x 16-bit words or 16k bytes.

- (3) The 2764 device for two groups of 8k x 16-bit words or 32k bytes.

| Ac       | dress    | Function                                             |

|----------|----------|------------------------------------------------------|

| From     | То       |                                                      |

| 000 000н | 1FF FFFH | Mapped RAM and I/O <sup>1</sup>                      |

| 200 000H | 3FF FFFH | ROM 0                                                |

| 400 000H | 5FF FFFH | ROM 1                                                |

| 600 000н | 7FF FFFH | UART A and B                                         |

| 800 000H | 9FF FFFH | Five Channel Timer                                   |

| A00 000H | BFF FFFH | Page Map (read/write)                                |

| СОО ОООН | DFF FFFH | Segment Map (read/write)<br>Context Register (read)  |

| E00 000H | FFF FFFH | Context Register (write)<br>16-bit Input Port (read) |

| Table 3-1 | Logical | Address | Locations |

|-----------|---------|---------|-----------|

|-----------|---------|---------|-----------|

Note:

During Boot State, Boot Strap instructions stored in ROM are shadowed into this area starting at 000 000H.

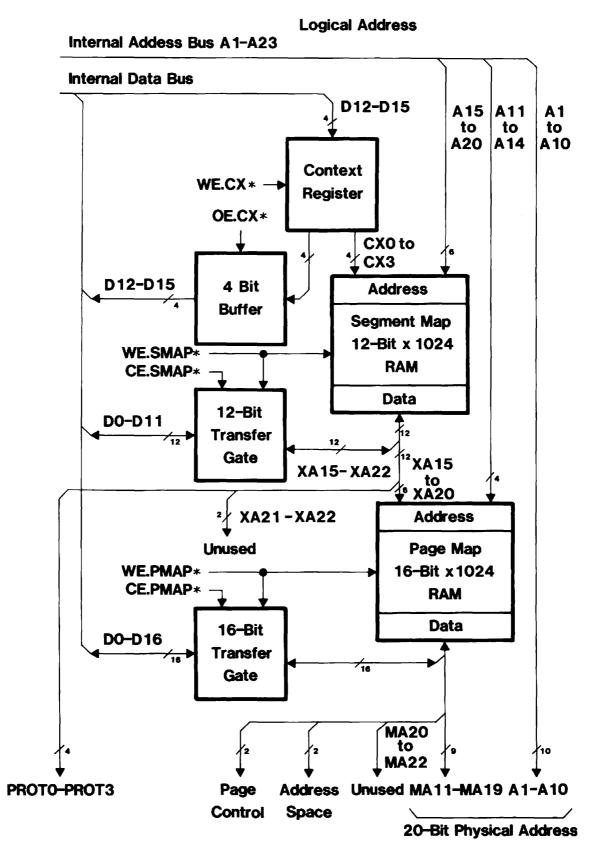

Figure 3-2 - Memory Map Management Block Diagram

3.12 The 68000 CPU employs a segmented, paged memory management method to facilitate the effective use of memory in large and complex programs. The  $\mu P$  is aware of an address space which is 24 bits wide. Thus the  $\mu P$ can directly address 16M bytes of memory. Multi-user 16M byte systems, however, require addressing methods which are more sophisticated than just a linear array of bytes ranging from 0 to 16M bytes. There is a need to partition user programs into separate logical address spaces such as execute-only code, read-only data, stack area and so on. This need is met by dividing programs into segments. There is a need for efficient management of the physical layout and allocation of such large address spaces and support features such as demand paging in a virtual memory system. This need is met by dividing the address spaces into pages.

3.13 A multi-tasking operating system needs a means to switch quickly between contexts, that is, to have the CPU work on a new program while a previous program is suspended, e.g., waiting for some peripheral transfer to complete. This need is met by providing separate contexts, addressed through a context register, which points the CPU at a fresh set of segments and pages. Figure 3-2 illustrates the Memory Management in block diagram.

3.14 The Memory Management section provides address translation, sharing and memory allocation control for multiple processes executing on the CPU. The address space is divided into pages of 2k bytes each. The page address bits, A0 through A10, pass through the translation process unmodified. Address bits, A11 through A20, are subject to translation. Bits A21 through A23 are reserved for special system functions and take no part in the address translation. The maximum logical address space for a process on the CPU is thus 21 bits or 2M bytes. This 21-bit address is further extended with a four-bit Context Register also known as the process or user number.

3.15 The 23-bit logical addresses, A1 through A23, from the  $\mu P$  are translated into 20-bit physical addresses in two stages. In the first stage, the logical address from the  $\mu P$  is translated by the Segment Map look-up table into a virtual address, XA15-XA20. In the second stage, this

virtual address is translated by the Page Map look-up table into a 20-bit physical address, A1-A10 and MA11-MA19.

3.16 A0 is not generated by the  $\mu$ P. The  $\mu$ P uses LDS\* and UDS\* to select the appropriate byte or bytes from a 16-bit word addressed by A1-A23. A0 is generated by other hardware on the 68000 CPU only for use in 796 Bus accesses.

3.17 Protection is associated with the Segment Map. Four protection bits, PROTO-PROT3, are provided or disallow read, write and execute access to two levels, the system level and the user level. Refer to Table 3-2.

3.18 Page access control and address space control are provided at the page map level.

Page access control consists of two bits which remember that a page has been referenced, used and written to, dirty. Address space control determines in which physical address space, on-card or off-card 796 Bus, a page is located as well as whether it references memory or input/output. Since no input/output addressing is done on card by the Memory Management System, this designation is interpreted as an invalid page in which case a reference to a word in that page causes a page default.

# Memory Management - Context Register

3.19 In a system with multiple executing processes, it is important to be able to switch quickly between processes without having to reload all the state information relating to the address translation for a particular process. The *Context Register* is a four-bit register, writable and readable under supervisor controls, that selects one of 16 unique sections of the *Segment Map*. This memory management method can thus contain the maps for 16 distinct process or user translations at the same time.

# Memory Management - Segment Map

3.20 The Segment Map is a 1024 entry table indexed by the four-bit Context Register and the six most significant bits of the logical address, A15-A20. The output of the Segment Map is six virtual address bits, XA15-XA20, and four protection bits, PROTO-PROT3. Each context thus has up to 64 segments and each segment has

| Protect | Access Allowed |     |     |     |        |       |  |  |  |

|---------|----------------|-----|-----|-----|--------|-------|--|--|--|

| Code    | PR3            | PR2 | PR1 | PRO | System | User  |  |  |  |

|         |                |     |     |     |        |       |  |  |  |

| 0       | 0              | 0   | 0   | 0   |        |       |  |  |  |

| 1       | 0              | 0   | 0   | 1   | x      |       |  |  |  |

| 2       | 0              | 0   | 1   | 0   | r      |       |  |  |  |

| 3       | 0              | 0   | 1   | 1   | r - x  | •••   |  |  |  |

| 4       | 0              | 1   | 0   | 0   | r w -  |       |  |  |  |

| 5       | 0              | 1   | 0   | 1   | rwx    |       |  |  |  |

| 6       | 0              | 1   | 1   | 0   | r      | r     |  |  |  |

| 7       | 0              | 1   | 1   | 1   | rw-    | r     |  |  |  |

| 8       | 1              | 0   | 0   | 0   | r      | rw-   |  |  |  |

| 9       | 1              | 0   | 0   | 1   | rw-    | rw-   |  |  |  |

| 10      | 1              | 0   | 1   | 0   | r w -  | r - x |  |  |  |

| 11      | 1              | 0   | 1   | 1   | rw-    | rwx   |  |  |  |

| 12      | 1              | 1   | 0   | 0   | r - x  | r - x |  |  |  |

| 13      | 1              | 1   | 0   | 1   | rwx    | r - x |  |  |  |

| 14      | 1              | 1   | 1   | 0   | rwx    | x     |  |  |  |

| 15      | 1              | 1   | 1   | 1   | rwx    | rwx   |  |  |  |

Table 3-2 - Segment Level Protection Attributes

Notes:

(1) r = read.

(2) w = write.

(3) x = execute

(4) -= attribute not enabled.

individual protection attributes. Segments may be kept private to a process or shared with other processes. The six-bit virtual address from a segment entry refers to a block of 16 consecutive page entries in the *Page Map*. A segment can be as large as 32k bytes by using all 16 of the associated Page Map entries. A segment may be as small as 2k bytes by invalidating the unused page entries in the *Page Map*. By concatenating consecutive *Segment Map* entries, a process can have a single address space of 2M bytes.

# Memory Management - Segment Level Protection

3.21 Each entry in the segment table contains four bits of protection information which may be used to control the access rights of that specific portion of the logical address space. The access codes are assigned to the  $Unix^{(B)}$  notation rwx where:

- (1) r is read access allowed,

- (2) w is write access allowed,

- (3) x refers to execute-only access allowed,

- (4) denote absence of that privilege.

Full access is denoted rwxrwx where the first rwx applies to system access and the second rwx to user access. The assignment of the four-bit protection code to the six-level protection is illustrated in Table 3-2.

#### Memory Management - Page Map

3.22 In the Page Map the six-bit virtual address from the Segment Map and the next four logical address bits from the  $\mu$ P are translated into a physical address and a physical address space. Each segment virtual address refers to a block of 16 consecutive page entries in the Page Map.

3.23 The output of the *Page Map* is the upper nine bits of the physical address which is concatenated with the lower 11 bits of the logical address to form a 20-bit Physical Address.

3.24 As well as determining the upper nine bits of the physical address, a page entry also determines to which physical address space the address belongs. By setting the address space control bits appropriately, a page may be declared to be in one of these address spaces:

- (1) 0 -On-card memory space,

- (2) 1 -Invalid page,

- (3) 2-796 Bus RAM,

- (4) 3-796 Bus I/O.

Notice that each of these address spaces is 20 bits or 1M bytes even though the on-card memory is at most 256k bytes and the off-card memory is at most 1M byte. It is up to the supervisory software to initialize the memory management segment and page maps correctly for a particular system configuration.

# Memory Management - Page Control

3.25 Each Page Map entry has two bits of page access control information. The referenced bit, often called the *used* bit, indicates that this page has been referenced:

- (1) Data read reference,

- (2) Data write reference,

- (3) Execute reference.

The modified bit, often called the *dirty* bit, indicates that this page has been written to. These bits are automatically updated on every valid mapped reference. These bits are intended for future use in virtual memory systems as described below. Refer to Table 3-3.

#### Memory Management - Virtual Memory

**3.26** The page map organization, together with the page control bits, provide enough information to implement virtual memory and demand paging.

3.27 The current implementation of the  $\mu$ P cannot recover from page faults to the extent required. Specifically, it does not store enough internal state information to be able to restart an instruction which was aborted because of a page fault. However, by limiting the set of operations that can cause page faults, it is possible to provide a limited form of virtual memory capability. For example, limiting virtual memory access to load and store operations makes recovery possible. Thus virtual data spaces can be achieved. The current version of the CPU does not yet employ virtual memory.

# Allocation of Logical Address Space

The 68000 CPU does not provide the 3.28 capability to access the full 16M bytes of memory that the  $\mu$ P address lines will accommodate. Rather, the logical address space of the  $\mu P$ has been allocated to various device functions. The address allocation is described in Table 3-1 and 3-3. Note the dual functions of the Segment Map and the Context Register locations. On a write to an entry, the upper four bits of the data are ignored and only the lower twelve bits are used to write to a segment entry. On a read from a Segment Map entry, the upper four bits are the contents of the Context Register and the lower twelve bits are the contents of the addressed Segment Map. On a write to location E00 000H, data is written to the Context Register. On a read from location E00 000H, data is read from the 16-Bit Input Port.

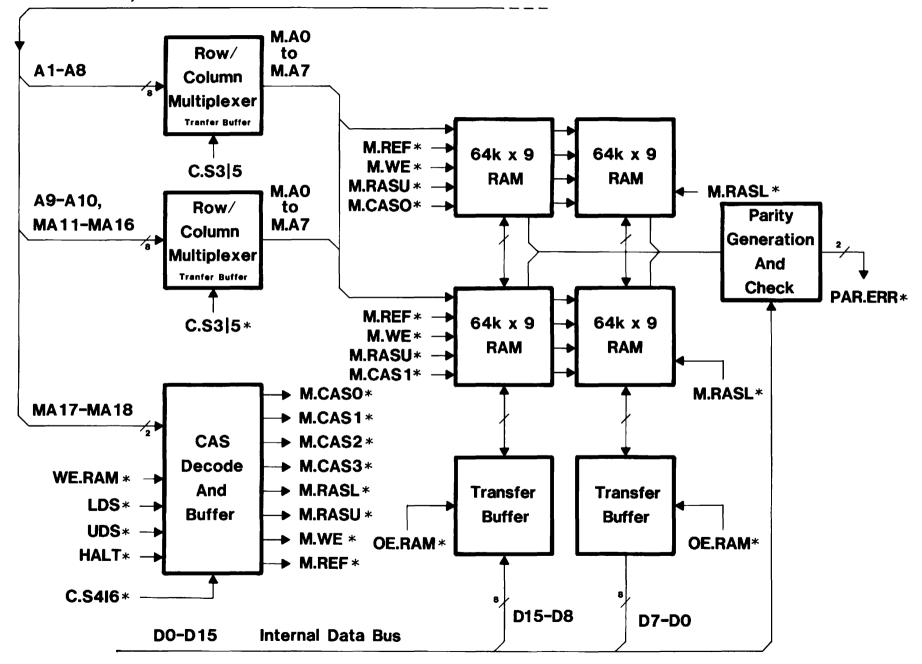

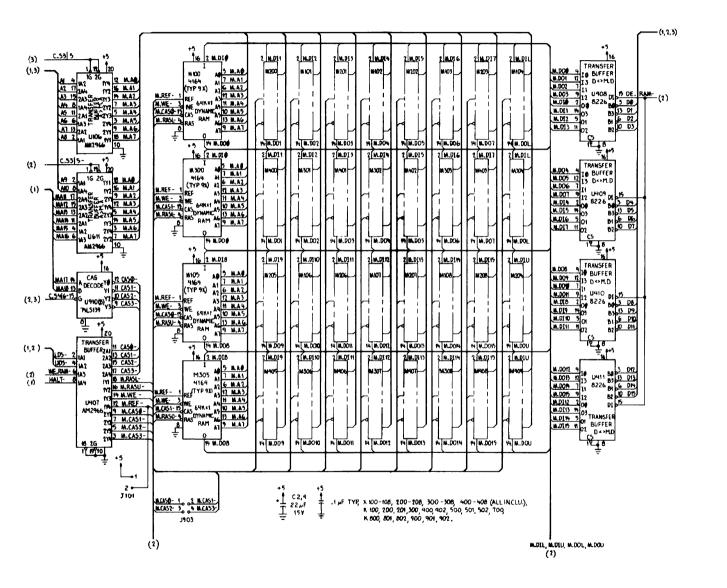

# On-Card 256k RAM

3.29 Figure 3-3 illustrates the 256k Random Access Memory in block diagram. 64k dynamic RAM devices are used to implement the on-card RAM. The RAM is organized as follows:

- (1) Two 64k x 16-bit word banks, 0 and 1, on-card with provision to expand to an additional two banks off-card,

- (2) Each bank is divided into an upper and lower byte.

|          | A                | Deviator                      |          |          |          |          |          | D        | ata Bu   | s Bit    | Specif   | ication  | ns       |          |          |          |          |          |

|----------|------------------|-------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Address  | Attribute<br>(1) | Register                      | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

| A00 000H | R/W              | Page Map                      | D        | U        | PD<br>1  | PD<br>0  | MA<br>22 | MA<br>21 | MA<br>20 | MA<br>19 | MA<br>18 | MA<br>17 | MA<br>16 | MA<br>15 | MA<br>14 | MA<br>13 | MA<br>12 | MA<br>11 |

| С00 000Н | w                | Segment<br>Map                | na       | na       | na       | na       | PR<br>03 | PR<br>02 | PR<br>01 | PR<br>00 | XA<br>22 | XA<br>21 | XA<br>20 | XA<br>19 | XA<br>18 | XA<br>17 | XA<br>16 | XA<br>15 |

| С00 000Н | R                | Segment<br>Map and<br>Context | CX<br>03 | CX<br>02 | CX<br>01 | CX<br>00 | PR<br>03 | PR<br>02 | PR<br>01 | PR<br>00 | XA<br>22 | XA<br>21 | XA<br>20 | XA<br>19 | XA<br>18 | XA<br>17 | XA<br>16 | XA<br>15 |

| E00 000H | w                | Context                       | CX<br>03 | CX<br>02 | CX<br>01 | CX<br>00 | na       |

| Е00 000Н | R                | P <b>ara</b> llel<br>Input    | IN<br>15 | IN<br>14 | IN<br>13 | IN<br>12 | IN<br>11 | IN<br>10 | IN<br>09 | IN<br>08 | IN<br>07 | IN<br>06 | IN<br>05 | IN<br>04 | IN<br>03 | IN<br>02 | IN<br>01 | IN<br>00 |

Notes:

(2) D = Dirty means this page has been written to.

U = Used means this page has been accessed.

(3) PDnn = Page definition Bits 0-1.

PD1 PD0 Definition

- 0 1 On-Card RAM

- 0 0 Invalid Page 1 0 796 Bus RAI

- 1 0 796 Bus RAM 1 1 796 Bus I/O.

- (4) MAnn = Translated or mapped page address bits 11-22.

- (5) PRnn = Segment protect code bits 0-3. Refer to Table 3-2.

- (6) XAnn = Translated segment address bits 15-22.

- (7) CXnn = Context register bits 0-3.

- (8) INnn = 16-bit parallel input register bits 0-15.

Attribute R = Read.

W = Write.

R/W = Read or Write.

A1-A10,MA11-MA18 Internal Address Bus

Bit 9 is used for byte parity checking. The organization of memory is in bytes. Read and write operations are performed in words.

#### NOTE

The 796 Bus provides both byte and word addressing. The 68000  $\mu$ P performs full word addressing, i.e., the least significant bit, A0, is not used for internal addressing operations.

3.30 The internal data and address lines are passed through Transfer Buffers. The data Transfer Buffers are transceivers. These *Transfer Buffers* are provided for several reasons:

- (1) Testing of memory is facilitated by isolating RAM from the internal address and data busses.

- (2) They furnish load buffering for internal address and data busses.

3.31 Internal Address Lines, MA17-MA18, are decoded and buffered to form column address strobe lines, M.CAS0\*-M.CAS3\*. These lines are also used to select the bank.

- **3.32**  $\mu$  P Control Signals:

- (1) UDS\*, upper data strobe, becomes M.UDS\* and selects the upper byte of the bank,

- (2) LDS\*, lower data strobe, becomes M.LDS\* and selects the lower byte of the bank.

- 3.33 Device decoder signal write enable RAM, WE.RAM\*, becomes M.WE\* the strobe for writing into RAM.

- 3.34 To read a word from RAM:

- (1) UDS\* and LDS\* are asserted,

- (2) M.CASO\*-M.CAS3\* selects the bank,

- (3) OE.RAM\* active.

Refer to Figure 3-12 for the timing relationships.

3.35 To write a word to RAM:

- (1) UDS\* and LDS\* are asserted,

- (2) M.CASO\*-MCAS3\* selects the bank,

- (3) M.WE\* is asserted.

Refer to Figure 3-13 for the timing relationships.

3.36 The row address strobe lines, M.RASU\* and M.RASL\*, which are associated with the upper and lower byte are common to banks.

3.37 The Parity Generation and Check generates the parity for the upper and lower byte simultaneously and stores the parity bits in bit positions designated DL and DU for lower and upper bytes respectively.

3.38 Parity checking is performed by checking parity of bytes, D0-D7, and D8-D15, and comparing with the respective parity bits DL and DU. A detected parity error activates PAR.ERR\* which causes a bus error. Refer to 5.33.

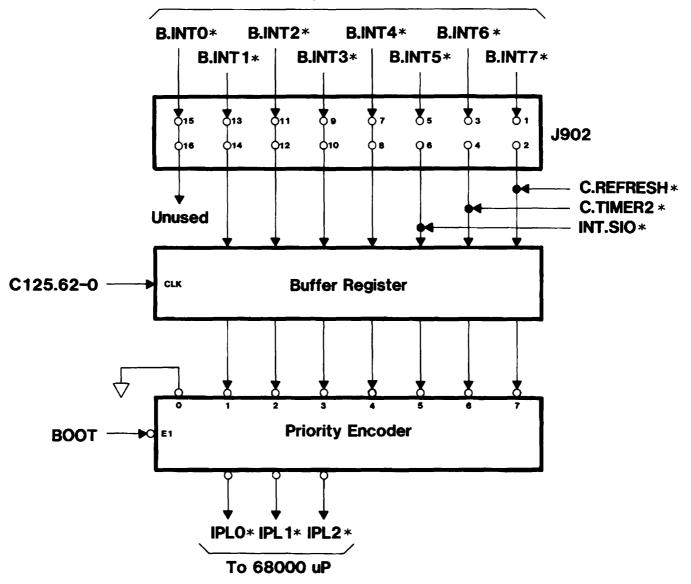

#### Interrupt

3.39 The 68000 CPU has seven interrupt levels numbered 1 through 7. Level 7 is the highest priority and level 1 is the lowest priority. At any time the 68000 CPU has an interrupt priority number set as part of the  $\mu$ P status register. Interrupts are acknowledged for all priority levels greater than the current  $\mu$ P priority contained in the  $\mu$ P status register. Interrupts are prohibited for all priority levels less than or equal to the current  $\mu$ P priority contained in the process status register. When an interrupt is acknowledged, the  $\mu$ P priority is set to the level of the interrupt request. Figure 3-4 illustrates the interrupt in block diagram.

3.40 A level 7 interrupt is special in that it is acknowledged even if the mask in the 68000  $\mu$ P status register is set to 7. This means that the level 7 interrupt is a *non-maskable* interrupt. A level 7 interrupt is acknowledged every time the interrupt request changes from a lower level to a level 7, that is, level 7 interrupts are *edge triggered*.

- 3.41 The 796 Bus Specification defines eight interrupt lines, INTO\* through INT7\* with INTO\* being the highest priority. The standard also recommends that interrupts be level triggered instead of edge triggered to provide for multiple interrupt sources on each interrupt line.

- **3.42** Option jumpers are provided if alternate interrupt assignments are needed.

#### IMPORTANT

To avoid confusion for MCL68000L device programmers, the number designation of the interrupt lines of the 796 Bus and the interrupt priorities were made to correspond to the definition of the MCL68000L device. INT7\* on the 796 Bus is the highest priority interrupt, and INT1\* is the lowest priority. INT0\* is not implemented. INT7\* is nonmaskable and edge triggered, whereas all other interrupts are maskable and level triggered.

From 796 Bus

Figure 3-4 - Interrupt Block Diagram

3.43 Three interrupt lines INT7\*, INT6\* and INT5\* are option jumpered to on-card devices. The interrupt lines available for system use are:

- (1) INT7\* Refresh Timer, C.REFRESH\*, highest priority, non-maskable,

- (2) INT6\* User Timer, C.TIMER2\*,

- (3) INT5\* UART A and B, INT.SIO\*,

- (4) INT4\* unassigned,

- (5)  $INT3^*$  unassigned,

- (6)  $INT2^*$  unassigned,

- (7) INT1\* unassigned lowest priority, and

- (8) INTO\* not available.

3.44 The seven interrupt lines are clocked through the Buffer Register to the Priority Encoder and output as three encoded lines, IPLO\*-IPL2\*, to the  $\mu$ P. BOOT is asserted during the boot state to inhibit interrupts.

3.45 The 68000 CPU acknowledges interrupts in an *auto-vector* mode. That is, the 68000 CPU generates the interrupt vector internally rather than it being supplied by the device. Thus the INTA\* signal of the 796 Bus is never asserted and the 796 Bus vectored interrupt capabilities are not used.

**Dual UART**

3.46 The *Dual UART* device provides two asynchronous serial I/O channels to the *RS-423A Drivers* and *Receivers*. Refer to Figure 3-5. Jumper option, J100, provides for Channel B to be configured as a DCE or DTE port.

Figure 3-5 - UART Block Diagram

3.47 Both UART channels are almost identical, the minor differences being in the raising of interrupt pending status.

3.48 A 7201 Multi-Protocol Serial Controller device is used for the UART. This device can handle a number of different signal formats and is software programmable.

3.49 The data rate of Channels A and B can be set independently under software control.

Two channels from the *Timer*, CP.1 and CP.2, furnish the clocking to the UARTs. Refer to 5.14 and 5.37 for programming of UARTs and Timer.

- **3.50** The EIA RS-423A specification was selected for several reasons:

- (1) The RS-423A is downward compatible with RS-232C,

- (2) The RS-423A allows higher data rates than RS-232C,

- (3) The RS-423A can support longer cable lengths than RS-232C.

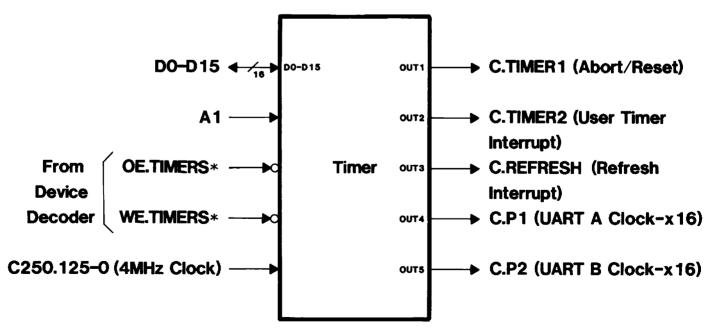

#### **Five Channel Timer**

**3.51** A 9513 Counter/Timer device is used to implement the *Five Channel Timer*. Refer

to Figure 3-6. Four of the five timers are preassigned to specific functions on the 68000 CPU. One timer is available for user-programmed timing functions. The timer channels are assigned as follows:

- (1) Watchdog Timer, C.TIMER1, furnishes a programmable abort/reset capability in case the  $\mu$ P should unexpectedly halt,

- (2) RTC Timer, C.TIMER2, furnishes a user interrupt on a programmably selectable time base,

- (3) Refresh Timer, C.REFRESH, furnishes an interrupt to execute dynamic RAM refresh program,

- (4) UART A, C.P1, furnishes UART Channel A clock,

- (5) UART B, C.P2, furnishes UART Channel B clock.

3.52 The Five-Channel Timer clock, C250.125-0, is a 4 MHz clock derived from a 16 MHz crystal oscillator in the System Timing section.

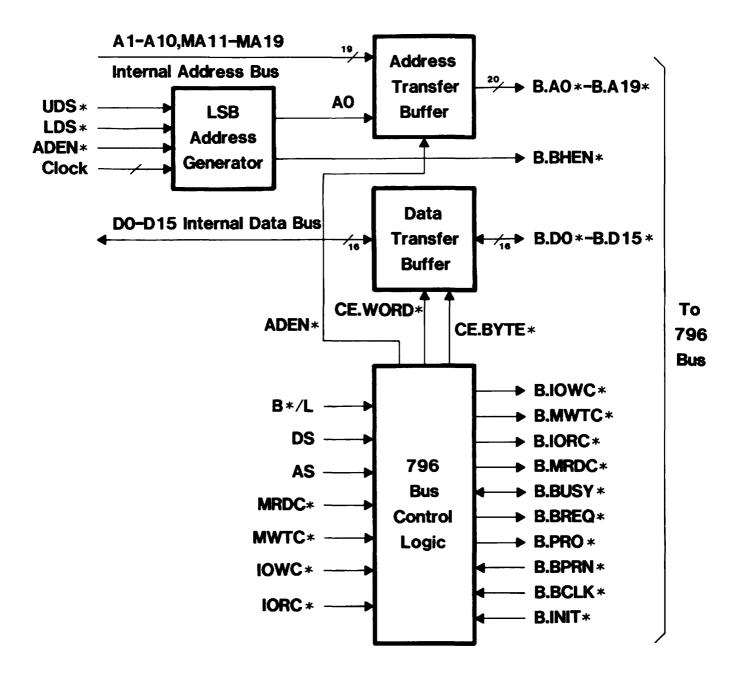

# 796 Bus Interface

3.53 Figure 3-7 illustrates the 796 Bus Interface in block diagram.

Figure 3-6 - Timer Block Diagram

Figure 3-7 - 796 Bus Interface Block Diagram

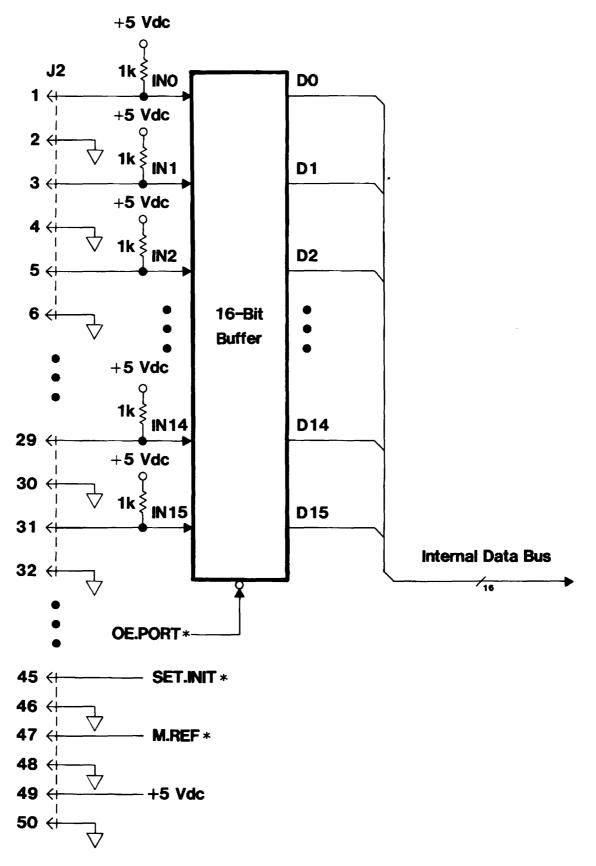

#### **Parallel Input Port**

- 3.54 The 16-Bit Parallel Input Port can be used as a general purpose 16-bit input port. Refer to Figure 3-8.

- 3.55 Several auxiliary lines are extended out to PCA connector, J2, for user applications:

- (1) +5 Vdc,

- (2) Signal ground,

- (3) SET.INIT\* pulled low, e.g., external switch closure will initiate a 68000 CPU reset,

- (4) M.REF\* active low indicates the  $\mu P$  is halted.

Figure 3-8 - Parallel Input Block Diagram

Figure 3-9 – Device Decoder Block Diagram

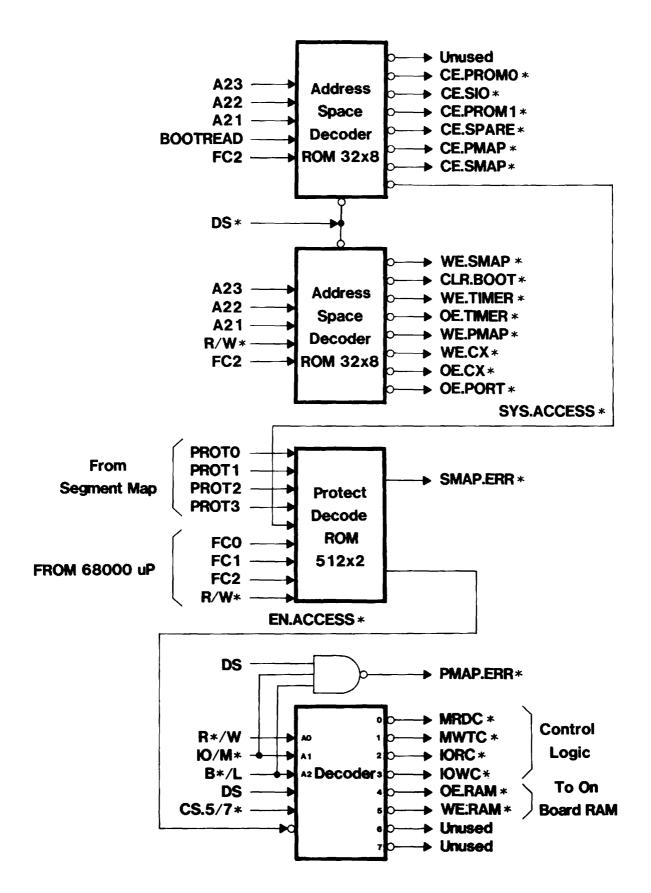

#### **Device** Decode

3.56 The *Device Decoder* is detailed in Figure 3-9. The 68000 CPU internal address and control lines are decoded and used to enable memory management functions:

- (1) Write Enable Control Register, WE.CX\*,

- (2) Output Enable Control Register, OE.CX\*,

- (3) Write Enable Segment Map, WE.SMAP\*,

- (4) Chip Enable Segment Map, CE.SMAP\*,

- (5) Write Enable Page Map, WE.PMAP\*,

- (6) Chip Enable Page Map, CE.PMAP\*,

and to enable five-channel timer functions:

(7) Write Enable Timer, WE.TIMER\*,

(8) Output Enable Timer, OE.TIMER\*,

and to enable 32k ROM:

- (9) Chip Enable ROM0, CE.PROM0\*,

- (10) Chip Enable ROM1, CE.PROM1\*,

and clear the boot state:

(11) Clear Boot, CLR.BOOT\*,

and enable the 16-Bit Parallel Input Port:

(12) Output Enable Port, OE.PORT\*.

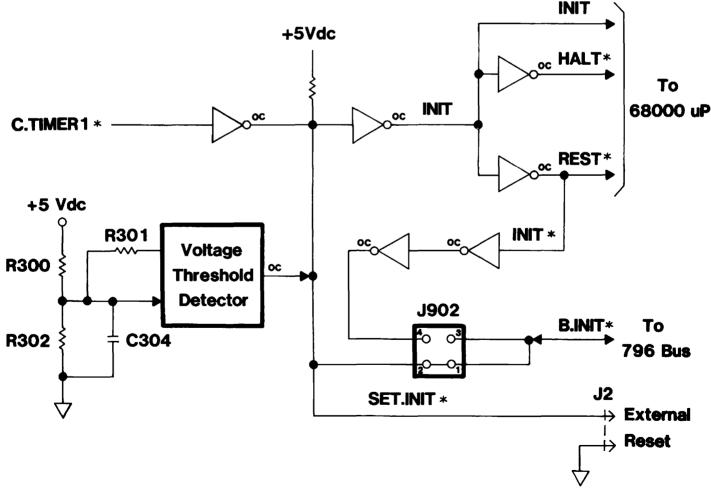

#### Power-On-Reset

3.57 Refer to Power-On-Reset block diagram, Figure 3-10, for the description which follows. A reset, RESET\* and HALT\*, can be initiated through several channels.

Figure 3-10 - Power-On-Reset Block Diagram

The Voltage Threshold Detector monitors the +5 Vdc supply for a change. When the voltage is greater than 4.65 V, the reset is removed. If the voltage falls below 4.25 V, a reset is issued, e.g., when the Mainframe is powered on or the line voltage suddenly drops,

- (2) The Watchdog Timer determines that the  $\mu P$  has halted and activates C.TIMER1\*,

- (3) An INIT\* is issued from the 796 Bus. Jumper Option J902 provides for issuing an INIT\* to the 796 Bus,

- (4) An external switch closure from J2 the *Parallel Input Port Connector*.

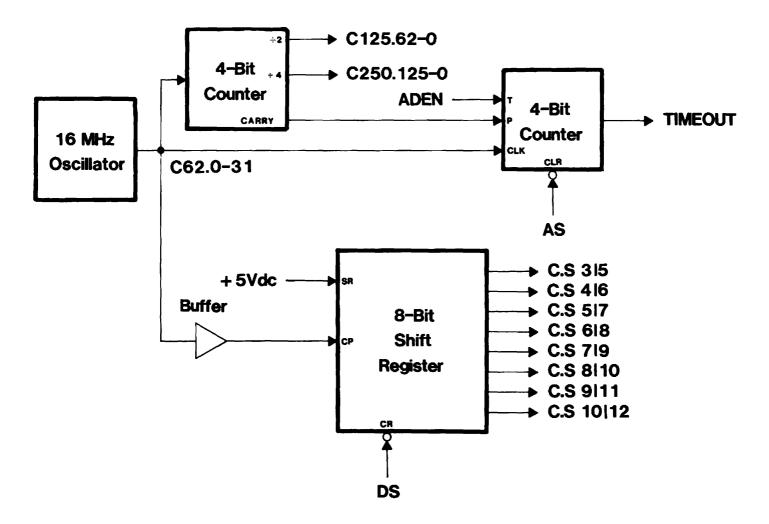

#### System Timing

- 3.58 A 16 MHz crystal-controlled oscillator is used in the System Timing to count down to:

- (1) 8 MHz C125.62-0 for the  $\mu$ P clock,

- (2) 4 MHz C250.125-0 for the Five Channel Timer.

Refer to Figure 3-11.

- 3.59 C.S3|5 through C.S10|12 are generated in a 8-bit Shift Register clocked by the buffered 16 MHz line.

- **3.60** 796 Bus TIMEOUT\* is issued from the *4-Bit Counter*.

Figure 3-11 - System Timing Block Diagram

| Diagram<br>Mnemonic                                 | 796 Bus<br>Mnemonic (1)                                  | Pin                                                                               | Function                                                                                                                                                                                                          |

|-----------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                                                          | Pin<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>21<br>22<br>27 | Function<br>Bus Clock<br>Initialize<br>Bus Priority In<br>Bus Priority Out<br>Bus Busy<br>Bus Request<br>Memory Read Command<br>Memory Write Command<br>I/O Read Command<br>I/O Write Command<br>Byte High Enable |

| B.CCLK*<br>B.INT0 7<br>B.A0* B.A19*<br>B.D0* B.D16* | CCLK*<br>INTO* — INT7*<br>ADR0* — AD10*<br>DAT0* — DATF* | 31<br>35–42<br>Various<br>Various                                                 | Constant Clock<br>Parallel Interrupt Requests<br>20-Bit Address Bus<br>16-Bit Data Bus                                                                                                                            |

Table 3-4 - 68000 Central Processing Unit Active 796 Bus Signals

Note:

(1) Address and data bus lines are in hexadecimal notation.

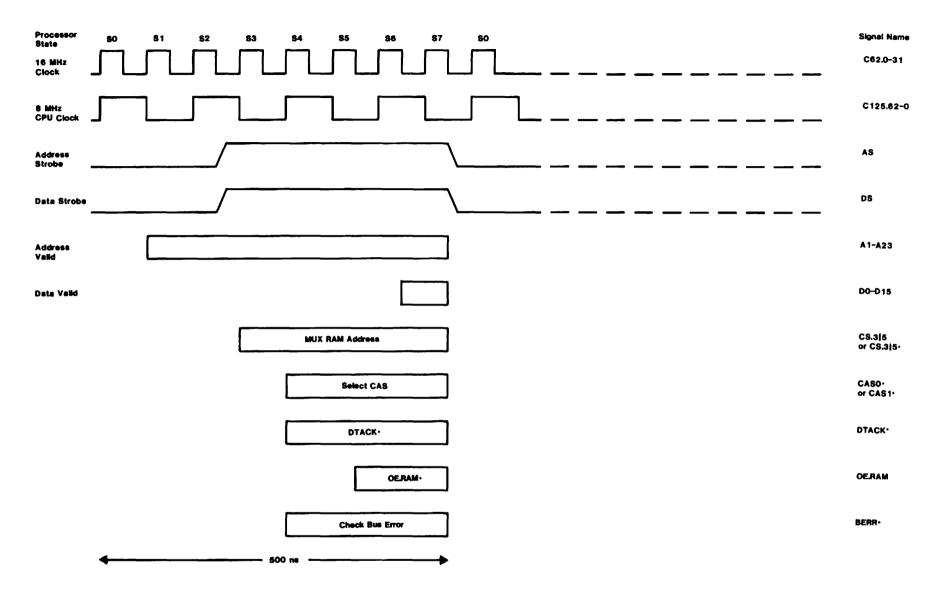

Figure 3-12 - On-Card RAM Read Cycle Timing

| Processor<br>State<br>16 MHz<br>Clock | 50 51 52 53 54 85 56 57 |            | gnal Name<br>:62.0-31 |

|---------------------------------------|-------------------------|------------|-----------------------|

| 8 MHz<br>CPU Clock                    |                         |            | :125.62-0             |

| Address<br>Strobe                     |                         | AS         | S                     |

| Data<br>Strobe                        |                         | BO         | 8                     |

| Address<br>Valid                      |                         | A1         | 1-A23                 |

| Data Valid                            |                         | xx         | 0-D15                 |

|                                       | MUX RAM Addres          | • MI       | IUX RAM<br>.ddress    |

|                                       | Select C                | CAS Se     | elect CAS             |

|                                       | DTAC                    | то         | TACK                  |

|                                       |                         | WE.RAM.    | VE.RAM.               |

|                                       | Check BU                | 6 Error BE | ERR                   |

|                                       | 62 ns                   |            |                       |

(1) Aquire 796 Bus in Minimum of 125 ns (2) Off-Card RAM or I/O Access Time is Minimum of 63 ns and Typical 437 ns

Figure 3-16 - Off-Card RAM and Input Output Write Cycle Timing

# 4. SPECIFICATIONS

4.01 The following furnishes the user with information for shipping and installation and should be used to establish acceptance criteria

if they are performed. Minor deviations from the specifications tabulated in Table 4-1 which do not affect the 68000 Central Processing Unit performance are excluded from the Codata Systems Corp. warranty.

| Table 4-1 – 68000 Central | Processing Unit 92-1012-xx Specifications |

|---------------------------|-------------------------------------------|

|---------------------------|-------------------------------------------|

| PARAMETER                                                                                                                                                     | CHARACTERISTICS                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor<br>Device<br>Clock Rate<br>Instruction Cycle<br>Instruction Types                                                                              | MCL68000L or Equivalent.<br>8 MHz.<br>500 ns.<br>56.                                                                                                                                                                                                                                                  |

| Memory Management<br>Context Switching<br>Logical Address Size<br>Physical Address Size<br>Segment Size<br>Segment Protection<br>Page Size<br>Page Definition | Two level; segmented and paged.<br>16 users.<br>2M bytes.<br>1M byte - 796 Bus.<br>256k - on card. Expandable off card to 512k bytes maximum.<br>32k byte.<br>6 levels coded to 16 states.<br>2k bytes.<br>4 levels.<br>(1) On-card RAM.<br>(2) Invalid Page.<br>(3) 796 Bus RAM.<br>(4) 796 Bus I/O. |

| Page Control                                                                                                                                                  | 2 levels.<br>(1) Used.<br>(2) Dirty.                                                                                                                                                                                                                                                                  |

| Interrupt Controller<br>Device<br>Operation<br>Levels<br>Priority                                                                                             | SN74LS148N.<br>Auto-vector.<br>Seven.<br>7-Memory Refresh or 796 Bus defined.<br>6-Real Time Clock or 796 Bus defined.<br>5-UART or 796 Bus defined.<br>4-796 Bus defined.<br>3-796 Bus defined.<br>2-796 Bus defined.<br>1-796 Bus defined.<br>0-not available.                                      |

| Bus Interface<br>Mode<br>Address<br>Data Width                                                                                                                | IEEE 796 Bus specification.<br>Multi-master; serial or parallel priority.<br>20 bit.<br>8 or 16 bit.                                                                                                                                                                                                  |

# Table 4-1 - 68000 Central Processing Unit 92-1012-xx Specifications (Continued)

| PARAMETER                              | CHARACTERISTICS                                 |

|----------------------------------------|-------------------------------------------------|

| Connector, P1<br>, P2                  | 796 Bus pin assignments.                        |

| , 12                                   | Pin assignments for off-board memory expansion. |

| Timer                                  | Five channel.                                   |

| Device                                 | AM9513.                                         |

| Operation, Timer 1                     | Watchdog Timer.                                 |

| <b>Operation</b> , Timer 2             | RTC Timer.                                      |

| Operation, Timer 3                     | Refresh Timer.                                  |

| Operation, Timer 4                     | UART A Data Rate Generator.                     |

| Operation, Timer 5                     | UART B Data Rate Generator.                     |

| Input Output Borts                     |                                                 |

| Input Output Ports<br>UART Port-Device | NEC7201.                                        |

| Channels                               | Two.                                            |

| Interface                              | RS-423A asynchronous.                           |

| Data Rate                              | 75 to 125k baud.                                |

| Data Format                            | Programmable.                                   |

|                                        |                                                 |

| Parallel Input Port                    | One.                                            |

| Device                                 | SN74LS244N.                                     |

| Interface, number                      | 16 bit.                                         |

| , level                                | TTL.                                            |

| Memory                                 |                                                 |

| Data Width                             | 8 or 16 bit.                                    |

| Random Access Memory                   |                                                 |

| Туре                                   | 64k bit dynamic.                                |

| Size                                   | 256k byte on-card.                              |

| Expandable                             | 256k byte off-card.                             |

| Read Only Memory                       |                                                 |

| Type 2716                              | 8k byte.                                        |

| Type 2732                              | 16k byte.                                       |

| Туре 2764                              | 32k byte.                                       |

|                                        |                                                 |

| Reset, Vcc Sense                       | 4.65 Vdc ±1%                                    |

| , Watchdog Timer                       | Time Interval is user programmable.             |

| , 796 Bus INIT*                        | Jumper option; master or slave.                 |

| , External                             | Switch contact closure.                         |

| PCA Dimensions                         | 796 Bus Specification.                          |

| Length                                 | 30.5 cm (12.0 inch).                            |

| Width                                  | 17.1 cm (6.75 inch).                            |

| Spacing                                | 1.3 cm (0.5 inch).                              |

| -                                      |                                                 |

|                                        |                                                 |

|                                        |                                                 |

|                                        |                                                 |

|                                        |                                                 |

# Table 4-1 - 68000 Central Processing Unit 92-1012-xx Specifications (Continued)

| PARAMETER                                                      | CHARACTERISTICS                                                                           |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Environment<br>Temperature<br>Operating<br>Storage<br>Humidity | 0°C to 55°C (32°F to 131°F).<br>0°C to 65°C (32°F to 149°F).<br>5% to 90%, noncondensing. |

| Power Requirements<br>+5 Vdc Bus                               | 2.5 A.                                                                                    |

| Weight                                                         | 454 g (16 oz.).                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

|                                                                |                                                                                           |

| Options                                                                                          |                                                                                                              |                                                     | Flag<br>02 03 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |  |  |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

|                                                                                                  |                                                                                                              |                                                     |               | Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |  |  |

| J100-1<br>J100-3<br>J100-1<br>J100-2                                                             | J100-2<br>J100-4<br>J100-3<br>J100-4                                                                         | x<br>x                                              |               | Connects P2.RXD as DTE.<br>Connects P2.TXD as DTE.<br>Connects P2.RXD as DCE.<br>Connects P2.TXD as DCE.                                                                                                                                                                                                                                                                                                                                             |                    |  |  |

|                                                                                                  |                                                                                                              |                                                     |               | ROM Type Sele                                                                                                                                                                                                                                                                                                                                                                                                                                        | ect                |  |  |

| J100-5<br>J100-7                                                                                 | J100-6<br>J100-8                                                                                             | x                                                   |               | Connects U100 U104 (23) to VCC f<br>Connects U100 U104 (23) to A12 f                                                                                                                                                                                                                                                                                                                                                                                 |                    |  |  |

|                                                                                                  |                                                                                                              |                                                     |               | 796 Bus Signa                                                                                                                                                                                                                                                                                                                                                                                                                                        | ls                 |  |  |

| J900-1<br>J900-3<br>J900-5<br>J900-7<br>J900-9<br>J901-1<br>J901-3<br>J901-5<br>J901-7<br>J901-9 | J900-2<br>J900-4<br>J900-6<br>J900-8<br>J900-10<br>J901-2<br>J901-2<br>J901-4<br>J901-6<br>J901-8<br>J901-10 | x<br>x<br>x                                         |               | IOWC* to 796 Bus. Connect for Operation without 8218.<br>MWTC* to 796 Bus. Connect for Operation without 8218.<br>IORC* to 796 Bus. Connect for Operation without 8218.<br>MRDC* to 796 Bus. Connect for Operation without 8218.<br>ADEN* to GND. Connect for Operation without 8218.<br>Receive BINIT* from 796 Bus.<br>Drive BINIT* on 796 Bus.<br>Drive BCLK* to 796 Bus.<br>Ground BPRN* for Highest Master in Chain.<br>Drive CCLK* to 796 Bus. |                    |  |  |

|                                                                                                  |                                                                                                              |                                                     |               | Interrupt Level Assi                                                                                                                                                                                                                                                                                                                                                                                                                                 | gnment             |  |  |

| J902-1<br>J902-3<br>J902-5<br>J902-7<br>J902-9<br>J902-11<br>J902-13<br>J902-15                  | J902-2<br>J902-4<br>J902-6<br>J902-8<br>J902-10<br>J902-12<br>J902-14<br>J902-16                             | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x |               | <ul> <li>B.INT7* to INT7* Non-maskable Interrupt used by Refresh Timer.</li> <li>B.INT6* to INT7* User Timer.</li> <li>B.INT5* to INT5* UART.</li> <li>B.INT4* to INT4*.</li> <li>B.INT3* to INT3*.</li> <li>B.INT2* to INT2*.</li> <li>B.INT1* to INT1*.</li> <li>(Not Used).</li> </ul>                                                                                                                                                            |                    |  |  |

|                                                                                                  |                                                                                                              |                                                     |               | Memory Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                     | Board              |  |  |

| J903-1<br>J903-3                                                                                 | J903-2<br>J903-4                                                                                             |                                                     |               | Drives MCASO* from MCAS1*.<br>Drives MCAS2* from MCAS3*.                                                                                                                                                                                                                                                                                                                                                                                             |                    |  |  |

| Opt                                                                                              | Option                                                                                                       |                                                     | Flag          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |  |  |

|                                                                                                  |                                                                                                              | 010                                                 | 2 03          | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                             | Codata Part Number |  |  |

| U101<br>U103<br>U602<br>U502<br>U503                                                             |                                                                                                              | x<br>x<br>x<br>x<br>x<br>x                          |               | MON-027-0019-01MON-E27-0020-01P127-0021-01P027-0022-01P227-0023-01                                                                                                                                                                                                                                                                                                                                                                                   |                    |  |  |

## Table 5-1-68000 Central Processing Unit Options - P/N 92-1012-xx

#### Options

5.01 Before the 68000 CPU is installed into the Mainframe card cage, the PCA options should be verified.

- (1) Check the J100, J900, J901, J902 and J903 jumper options. Refer to Table 5-1.

- (2) Check the U101, U102, U103, U602, U502 and U503 ROM. Refer to Table 5-1.

- 5.02 Install the PCA into card cage position 4 and connect the serial I/O cable to J1.

#### RS-423A

5.03 When the serial I/O port(s) is connected to RS-232C compatible devices some restrictions apply:

- Data rates and cable lengths must be restricted to those allowed under RS-232C.

Data rates to 9600 baud maximum and cable lengths to 50 feet maximum.

- (2) Signal level of RS-232C drivers kept to ±12 Vdc or less.

- (3) Rise times of RS-423A drivers must be set to meet RS-232C specifications.

The 68000 CPU is designed to operate with RS-232C devices at data rates up to 9600 baud.

5.04 When the 68000 CPU is connected to other RS-423A compatible devices, cable lengths can be increased to 4000 feet maximum at transmission rates to 3000 baud. At higher data rates, cable length must be reduced. For example, transmission at 9600 baud requires cables no longer than 40 feet.

5.05 Transmission at high data rates requires careful design of cables and system grounding as well as adjustment of driver rise times by selecting timing capacitors on the 68000 CPU. The standard configuration of the 68000 CPU allows transmission at rates up to 40k baud with cable lengths up to 250 feet. For longer cables or higher baud rates, the standard capacitor values must be changed to change the driver rise and fall

times. The system designer is strongly urged to consult EIA RS-423A specification to select the optimum value needed for the particular application.

#### Power-On-Reset — Entering Boot State