μ-PAC integrated circuit modules Instruction Manual

# Instruction Manual

# µ-PAC INTEGRATED CIRCUIT MODULES

September 23, 1966

COMPUTER CONTROL DIVISION

COPYRIGHT 1966 by Honeywell Inc., Computer Control Division, Framingham, Massachusetts. Contents of this publication may not be reproduced in any form in whole or in part, without permission of the copyright owner. All rights reserved.

Printed in U.S.A.

,

#### TABLE OF CONTENTS

| Paragraph | Title                                                                         | Page    |  |  |

|-----------|-------------------------------------------------------------------------------|---------|--|--|

|           | SECTION I<br>INTRODUCTION                                                     |         |  |  |

| 1 - 1     | Scope                                                                         | 1 - 1   |  |  |

| 1-2       | µ-PAC Product Line                                                            | 1 - 1   |  |  |

| 1 - 3     | Microcircuits                                                                 | 1-4     |  |  |

| 1-4       | µ-PAC Modules                                                                 | 1-4     |  |  |

| 1-5       | Auxiliary Equipment                                                           | 1-5     |  |  |

| 1-5.1     | μBLOCs                                                                        | 1-5     |  |  |

| 1-5.2     | Power Supplies                                                                | 1 - 5   |  |  |

| 1-5.3     | Jumper Lead Set                                                               | 1-6     |  |  |

| 1-5.4     | Logic Symbol Stickers                                                         | 1-6     |  |  |

| 1-5.5     | Accessories                                                                   | 1 - 6   |  |  |

| 1-6       | Product Line Features                                                         | 1 - 6   |  |  |

|           | SECTION II<br>PRODUCT LINE SPECIFICATIONS AND<br>MICROCIRCUIT CHARACTERISTICS |         |  |  |

| 2 - 1     | Introduction                                                                  | 2-1     |  |  |

| 2-2       | General µ-PAC Specifications                                                  | 2-1     |  |  |

| 2-2.1     | Input Switching Thresholds                                                    | 2 - 1   |  |  |

| 2-2.2     | Output Logic Levels                                                           | 2-1     |  |  |

| 2-2.3     | Frequency Range (DC to 5 MC)                                                  | 2 - 1   |  |  |

| 2-2.4     | Temperature Range                                                             | 2-3     |  |  |

| 2-2.5     | Power Supplies                                                                | 2-3     |  |  |

| 2-2.6     | Loading Rules                                                                 | 2-3     |  |  |

| 2-2.7     | Current Requirements                                                          | 2-4     |  |  |

| 2-2.8     | Worst Case Delays                                                             | 2-4     |  |  |

| 2-2.9     | Typical Delay Characteristics                                                 | 2-4     |  |  |

| 2-2.10    | Typical Waveform Characteristics                                              | 2-8     |  |  |

| 2 - 3     | NAND Gate F-01 and F-02 Characteristics                                       | 2-9     |  |  |

| 2-3.1     | Basic NAND Circuit                                                            | 2-9     |  |  |

| 2-3.2     | F-01 and F-02 NAND Microcircuits                                              | 2-9     |  |  |

| 2-3.3     | Loading                                                                       | 2-9     |  |  |

| 2-3.4     | Fan-In Expansion Using Nodes                                                  | 2-9     |  |  |

| 2-3.5     | Circuit Delay                                                                 | 2-11    |  |  |

| 2-3.6     | Load Resistors in Parallel                                                    | 2 - 1 1 |  |  |

| 2-3.7     | Paralleling Outputs with One Load Resistor                                    | 2 - 1 1 |  |  |

| 2-4       | Type F-03 Power Amplifier Characteristics                                     | 2 - 1 1 |  |  |

| 2-4.l     | Input Loading                                                                 | 2 - 1 1 |  |  |

| 2-4.2     | Output Drive Capability                                                       | 2 - 1 1 |  |  |

# $\mu$ -PAC DIGITAL MODULES

# TABLE OF CONTENTS (Cont)

| Paragraph      | Title                                                        | Page           |

|----------------|--------------------------------------------------------------|----------------|

| 2-4.3          | Circuit Delay                                                | 2-12           |

| 2-5            | Type F-04 Flip-Flop Characteristics                          | 2-12           |

| 2-5.1          | Pulse Dodging                                                | 2-12           |

| 2-5.2          | DC Operation                                                 | 2-14           |

| 2-5.3          | Control Inputs Used to Steer Clock Pulses                    | 2-14           |

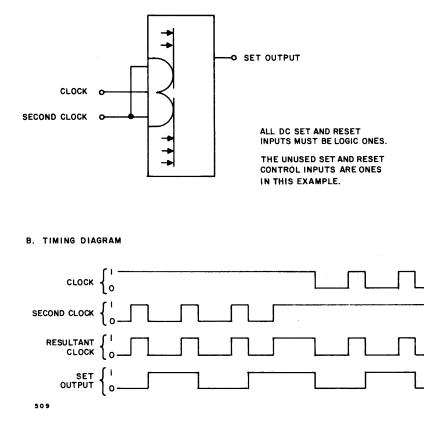

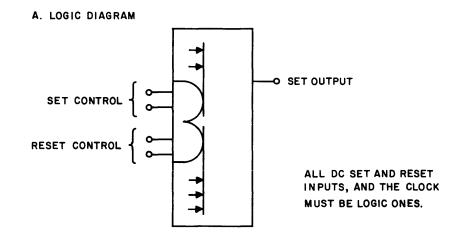

| 2-5.4          | Control Inputs Used as a Second Clock                        | 2-18           |

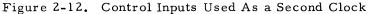

| 2-5.5          | Control Inputs Used Directly to Set or Reset                 | 2-18           |

| 2-5.6          | Input Loading                                                | 2-18           |

| 2-5.7          | Output Drive Capability                                      | 2-20           |

| 2-5.8          | Circuit Delay                                                | 2-20           |

| 2-5.9          | Clock and Control Input Timing Requirements                  | 2-20           |

| 2-5.10         | DC Input Timing Requirements                                 | 2-20           |

| 2-5.11         | Control Inputs                                               | 2-20           |

| 2-5.12         | Maximum Allowable Clock Skew                                 | 2-20           |

|                | SECTION III DESCRIPTIONS OF $\mu$ -PAC MODULES AND EQUIPMENT |                |

| 3-0            | AS-330, Copper Clad PAC Kit                                  | 3 - 0          |

| 3-1            | BC-335, Counter PAC                                          | 3 <b>-</b> 1   |

| 3-2            | BC-336, Binary Counter PAC                                   | 3 – 5          |

| 3-3            | BC-337, Fast Carry Counter PAC                               | 3-11           |

| 3-4            | BL-330, BL-331, BL-332, and BL-333, $\mu$ -BLOCs             | 3-17           |

| 3-5            | BM-330, BM-335, and BM-337, µ-BLOCs                          | 3-19           |

| 3-5A           | BP-330, Blank PAC                                            | 3-22A          |

| 3-6            | BR-335, Buffer Register PAC                                  | 3-23           |

| 3-7            | DC-335, Multi-Input NAND PAC                                 | 3 <b>-</b> 29  |

| 3-7A           | DD-330, Display Driver PAC                                   | 3 <b>-</b> 32A |

| 3-8            | DG-335, Selection Gate Type 1 PAC                            | 3-33           |

| 3-9            | DG-336, Selection Gate Type 2 PAC                            | 3-37           |

| 3-10           | DI-335, NAND Type 1 PAC                                      | 3-43           |

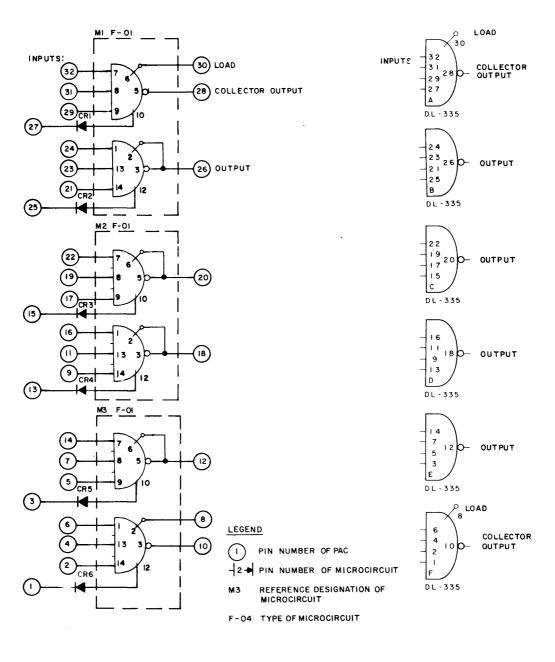

| 3-11           | DL-335, NAND Type 2 PAC                                      | 3-47           |

| 3-12           | DM-335, Delay Multivibrator PAC                              | 3-51           |

| 3 <b>-</b> 12A | DM-335, Delay Multivibrator PAC (Ser. No. 1000 and beyond)   | 3 <b>-</b> 58A |

| 3-12B          | DM-336, Adjustable Delay Multivibrator PAC                   | 3 <b>-</b> 58L |

| 3 - 1 3        | DN-335, Expandable NAND PAC                                  | 3-59           |

| 3-14           | EO-335, Exclusive OR PAC                                     | 3-63           |

| 3-15           | FA-335, Gated Flip-Flop PAC                                  | 3-67           |

| 3-16           | FF-335, Basic Flip-Flop PAC                                  | 3-75           |

| 3-17           | JT-330, Taper Pin Jumper Lead Set                            | 3-81           |

# TABLE OF CONTENTS (Cont)

| Paragraph      | Title                                      | Page            |

|----------------|--------------------------------------------|-----------------|

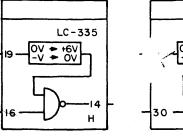

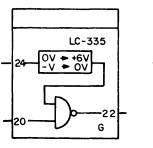

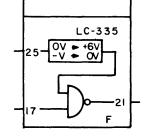

| 3-17A          | LC-335, Negative Logic Level Converter PAC | 3 <b>-</b> 82A  |

| 3-18           | LD-330, Lamp Driver PAC                    | 3-83            |

| 3-18A          | LD-331, High-Drive Lamp Driver PAC         | 3 <b>-</b> 88A  |

| 3-18B          | LD-335, Negative Logic Level Driver PAC    | 3 <b>-</b> 88G  |

| 3-19           | MC-335, Master Clock PAC                   | 3-89            |

| 3-20           | MV-335, Multivibrator Clock PAC            | 3 <b>-</b> 99   |

| 3-21           | OD-335, Octal/Decimal Decoder PAC          | 3-107           |

| 3-22           | PA-335, Power Amplifier PAC                | 3-117           |

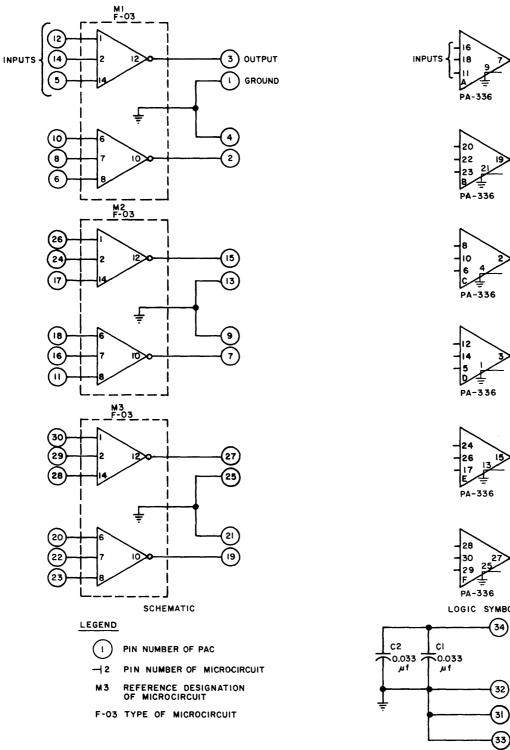

| 3 <b>-</b> 22A | PA-336, Power Amplifier PAC                | 3 <b>-</b> 120A |

| 3-23           | PB-330 and PB-331, Plug-In Power Supplies  | 3-121           |

| 3-23A          | PM-330 and PM-331, Mounting Panels         | 3 <b>-</b> 132A |

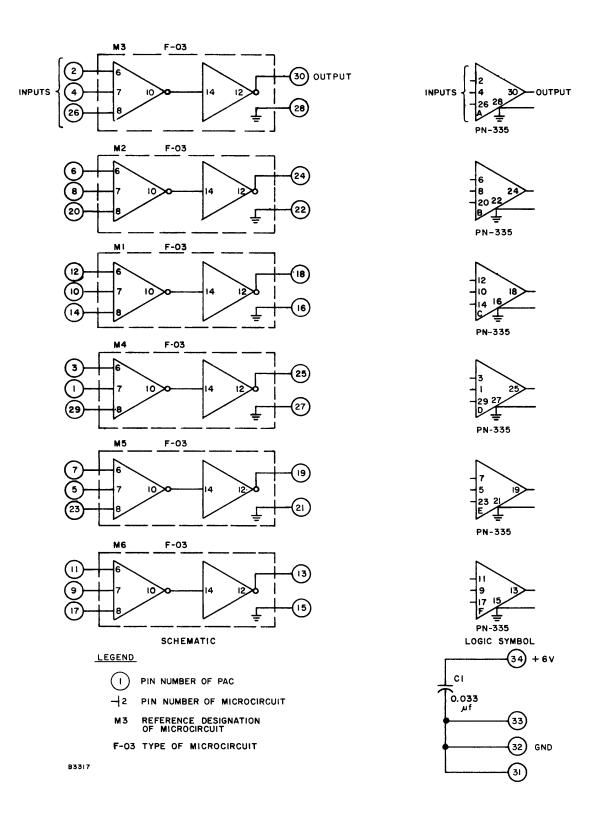

| 3 <b>-</b> 23B | PN-335, Non-Inverting Power Amplifier PAC  | 3 <b>-</b> 132C |

| 3-24           | RP-330, Power Supply                       | 3-133           |

| 3-25           | SD-330, Solenoid Driver PAC                | 3-141           |

| 3 <b>-</b> 25A | SR-335, Shift Register PAC                 | 3 <b>-</b> 146A |

| 3-26           | ST-335, Schmitt Trigger PAC                | 3-147           |

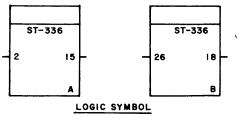

| 3 <b>-</b> 26A | ST-336, Adjustable Schmitt Trigger PAC     | 3 <b>-</b> 158A |

| 3-27           | TG-335, Transfer Gate PAC                  | 3-159           |

| 3-27A          | TP-330, Test Point PAC                     | 3 <b>-</b> 162A |

| 3-28           | UF-335, Universal Flip-Flop PAC            | 3-163           |

| 3 <b>-</b> 28A | UI-110, Transistorized Unit Indicator      | 3 <b>-</b> 168A |

| 3 <b>-</b> 28B | UI-330, Transistorized Unit Indicator      | 3 <b>-</b> 168C |

| 3-29           | XD-335, Transmission Line Driver PAC       | 3-169           |

| 3-29A          | XD-336, Transmission Line Driver PAC       | 3 <b>-</b> 176A |

| 3-30           | XP-330, Extender PAC                       | 3-177           |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                  | Page         |

|--------|--------------------------------------------------------|--------------|

| 1-1    | Dimensions of Standard Microcircuit                    | 1 - 4        |

| 1 - 2  | Dimensions of Standard $\mu$ -PAC                      | l <b>-</b> 5 |

| 2-1    | Switching Thresholds                                   | 2-2          |

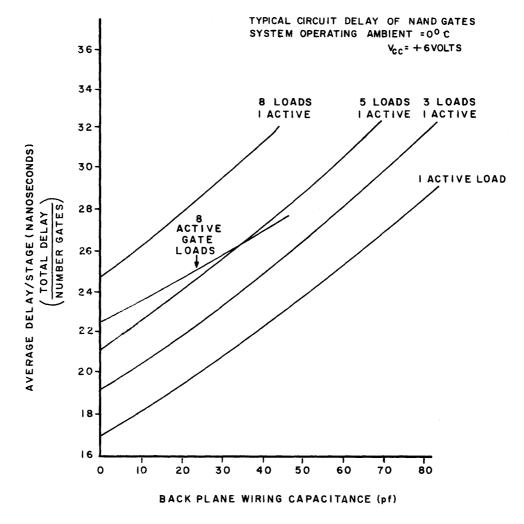

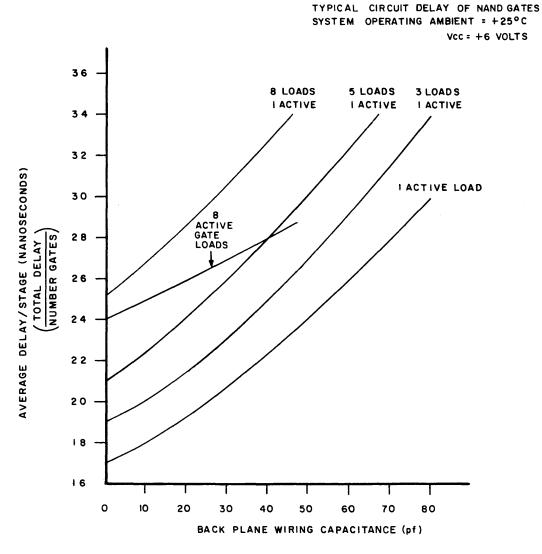

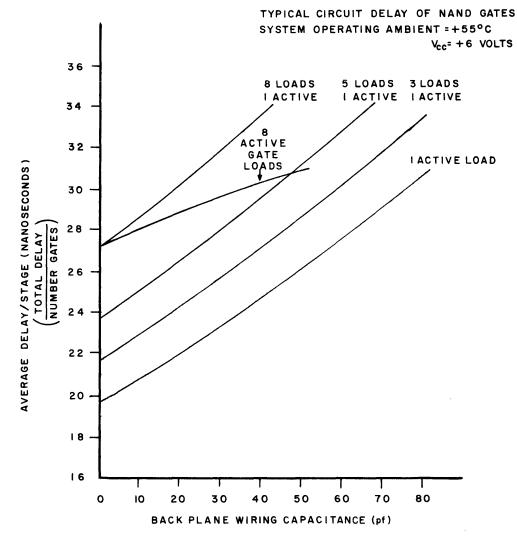

| 2-2    | Typical NAND Gate Circuit Delays (Sheet 1 of 3)        | 2-5          |

| 2-2    | Typical NAND Gate Circuit Delays (Sheet 2 of 3)        | 2-6          |

| 2-2    | Typical NAND Gate Circuit Delays (Sheet 3 of 3)        | 2-7          |

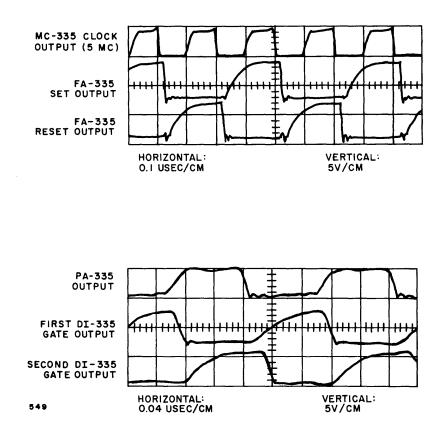

| 2-3    | Typical µ-PAC Waveforms                                | 2-8          |

| 2-4    | Basic NAND Gate Logic                                  | 2-10         |

| 2-5    | Types F-01 and F-02 NAND Gate Equivalent Logic Symbols | 2-10         |

| 2-6    | Paralleled NAND Gates with Common Load Resistors       | 2-10         |

| Figure          | Title                                                                                              | Page           |

|-----------------|----------------------------------------------------------------------------------------------------|----------------|

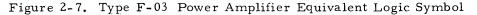

| 2-7             | Type F-03 Power Amplifier Equivalent Logic Symbol                                                  | 2-12           |

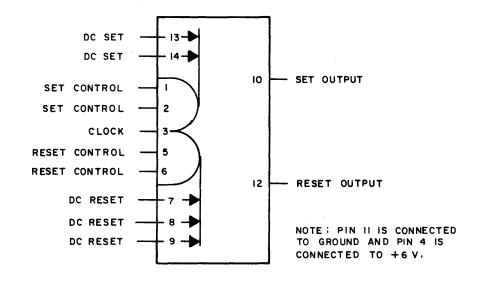

| 2-8             | Type F-04 Flip-Flop Logic Symbol and Equivalent<br>Logic Circuit                                   | 2-13           |

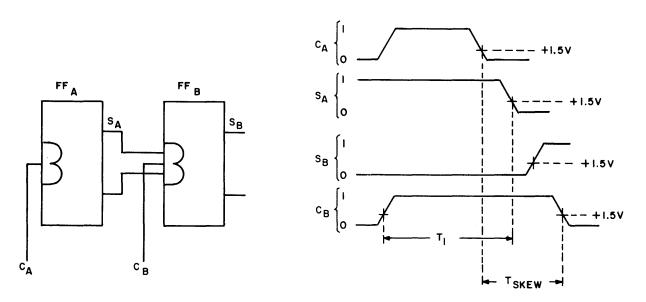

| 2-9             | Double-Rank Flip-Flop Pulse Dodging, Timing Diagram                                                | 2-14           |

| 2-10            | DC Operation                                                                                       | 2-15           |

| 2-11            | Control Inputs Used to Gate Clock Pulses (Sheet 1 of 2)                                            | 2-16           |

| 2-11            | Control Inputs Used to Gate Clock Pulses (Sheet 2 of 2)                                            | 2-17           |

| 2-12            | Control Inputs Used As a Second Clock                                                              | 2-18           |

| 2-13            | Control Inputs Used Directly to Set or Reset                                                       | 2-19           |

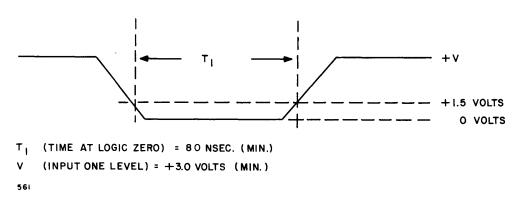

| 2-14            | Flip-Flop Input Pulse Requirements                                                                 | 2-21           |

| 2-15            | DC Set and Reset Input Signal Requirements                                                         | 2-21           |

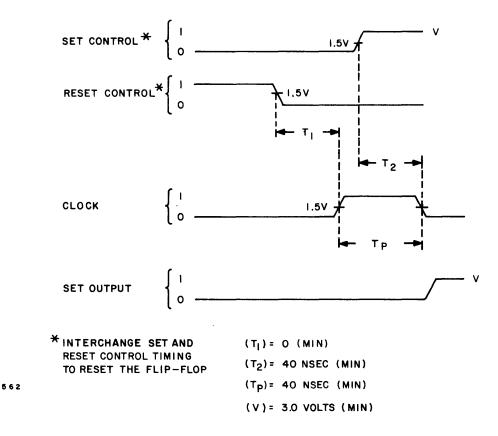

| 2-16            | Timing Requirements for Control Inputs, Using Clock<br>Triggering                                  | 2-22           |

| 2-17            | Allowable Clock Skew, Logic and Timing                                                             | 2-22           |

| 3-0.1           | Copper Clad PAC Kit, Model AS-330, Dimensions                                                      | 3-0            |

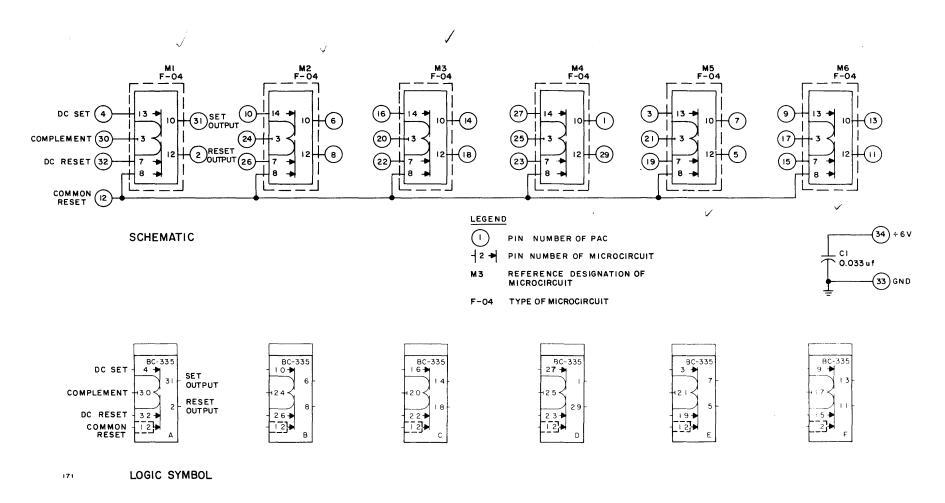

| 3-1.1           | Counter PAC, Model BC-335, Schematic Diagram and Logic Symbol                                      | 3-2            |

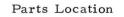

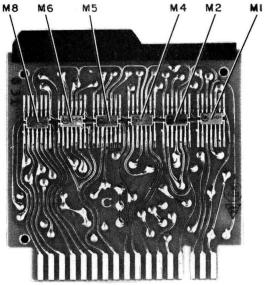

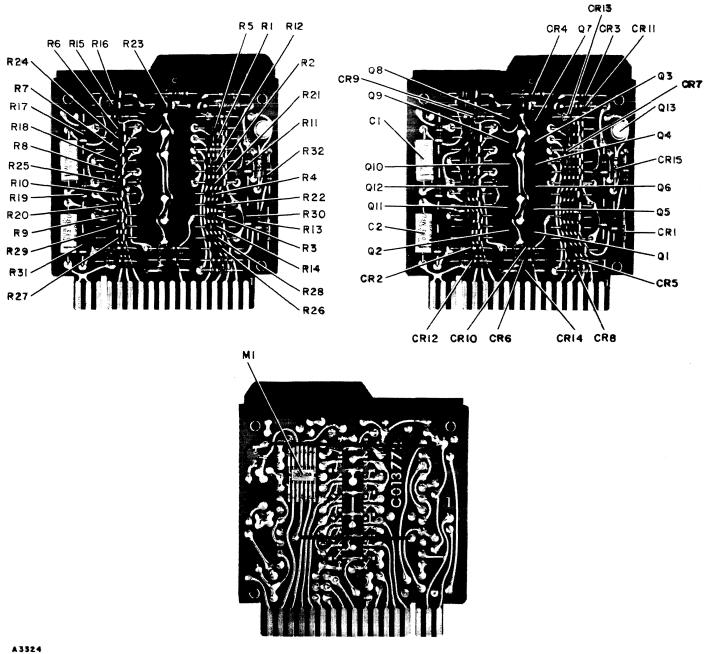

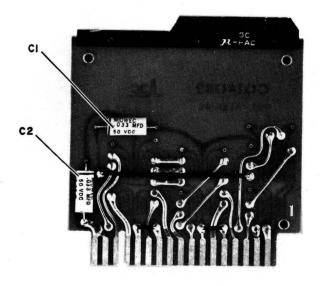

| 3-1.2           | Counter PAC, Model BC-335, Parts Location and Identification                                       | 3-3            |

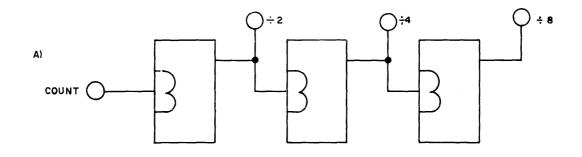

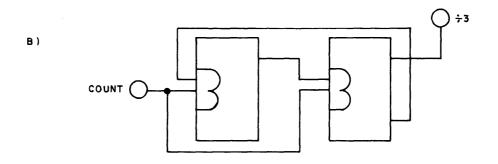

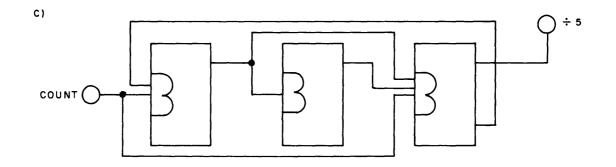

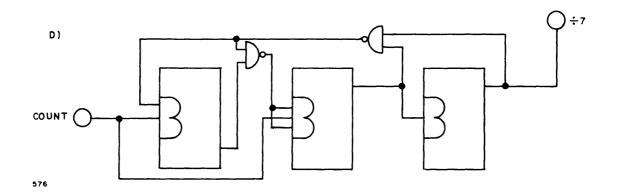

| 3-1.3           | Counter PAC, Model BC-335, Operation as a Frequency Driver                                         | 3-4            |

| 3-1.1A          | Counter PAC, Model BC-335 (Ser. No. 979 and beyond),<br>Schematic Diagram and Logic Symbol         | 3 <b>-</b> 4A  |

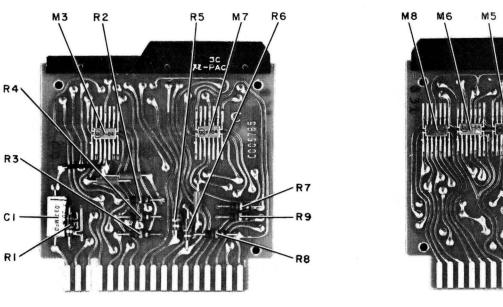

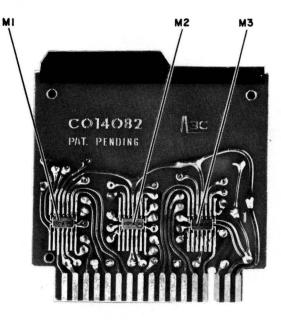

| 3 <b>-</b> 1.2A | Counter PAC, Model BC-335 (Ser. No. 979 and beyond)<br>Parts Location and Identification           | 3 <b>-</b> 4B  |

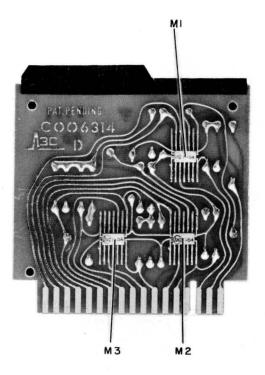

| 3-2.1           | Binary Counter PAC, Model BC-336, Schematic Diagram and Logic Symbol                               | 3-7            |

| 3-2.2           | Binary Counter PAC, Model BC-336, Parts Location and Identification                                | 3-9            |

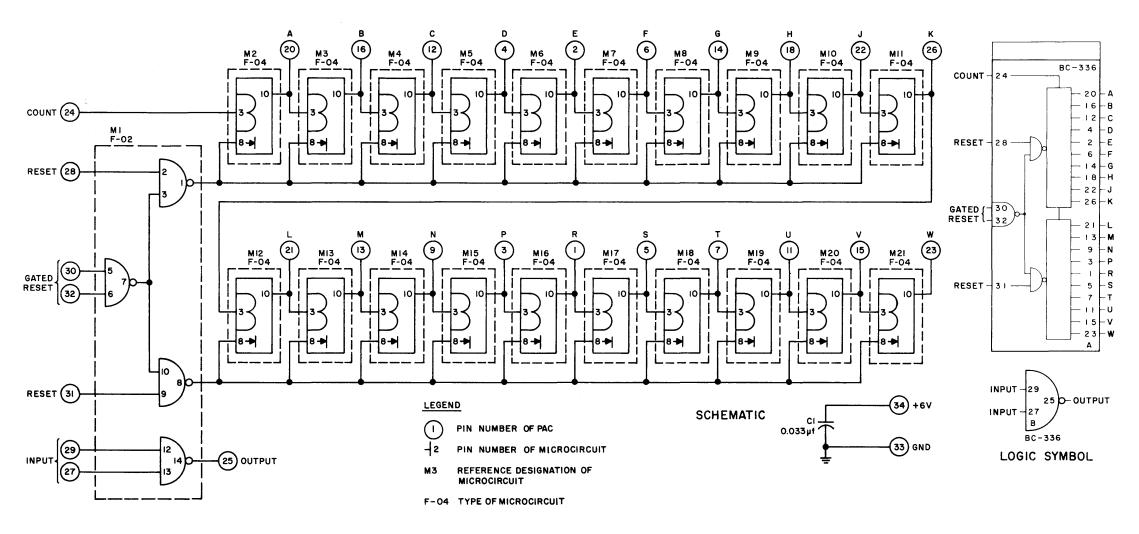

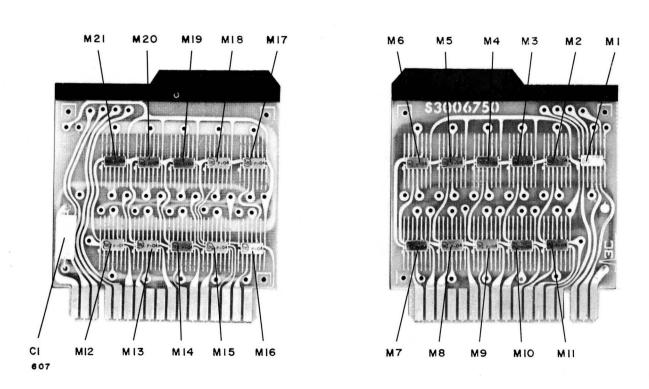

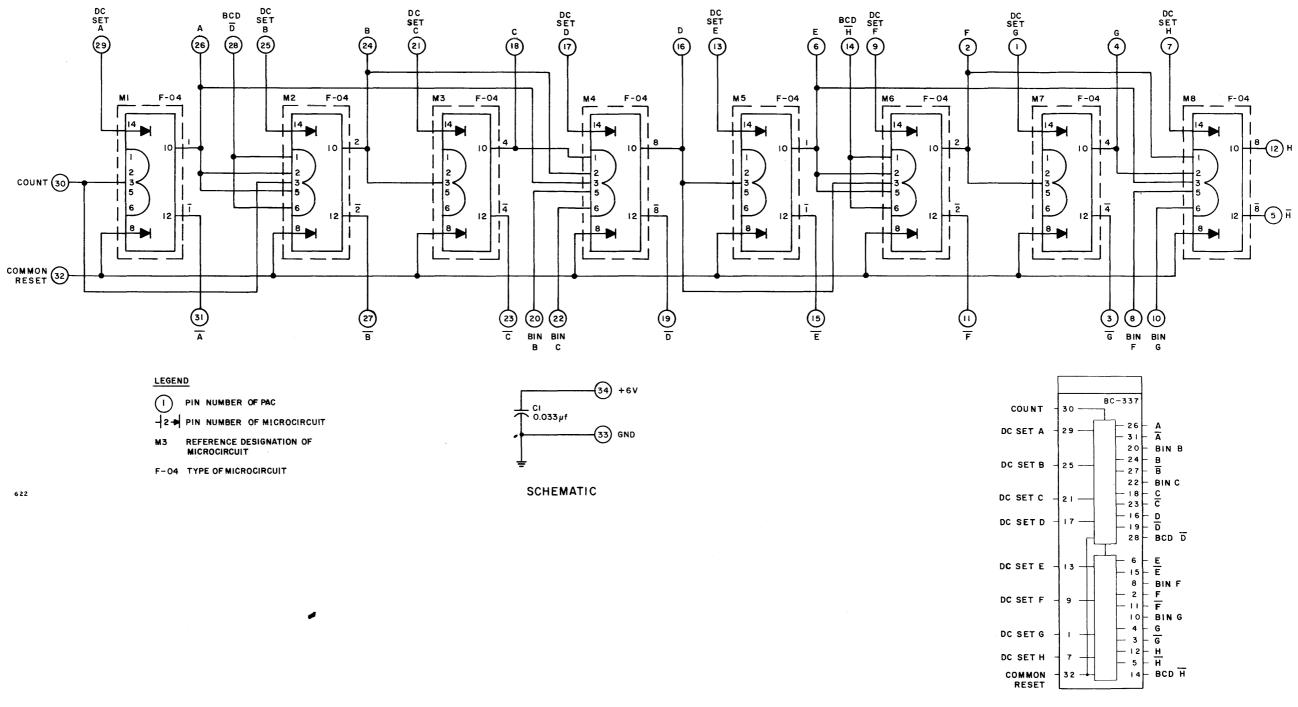

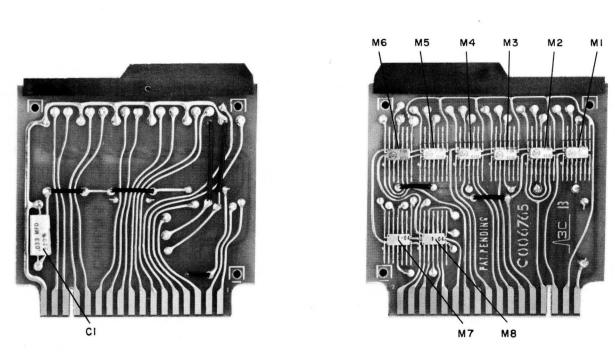

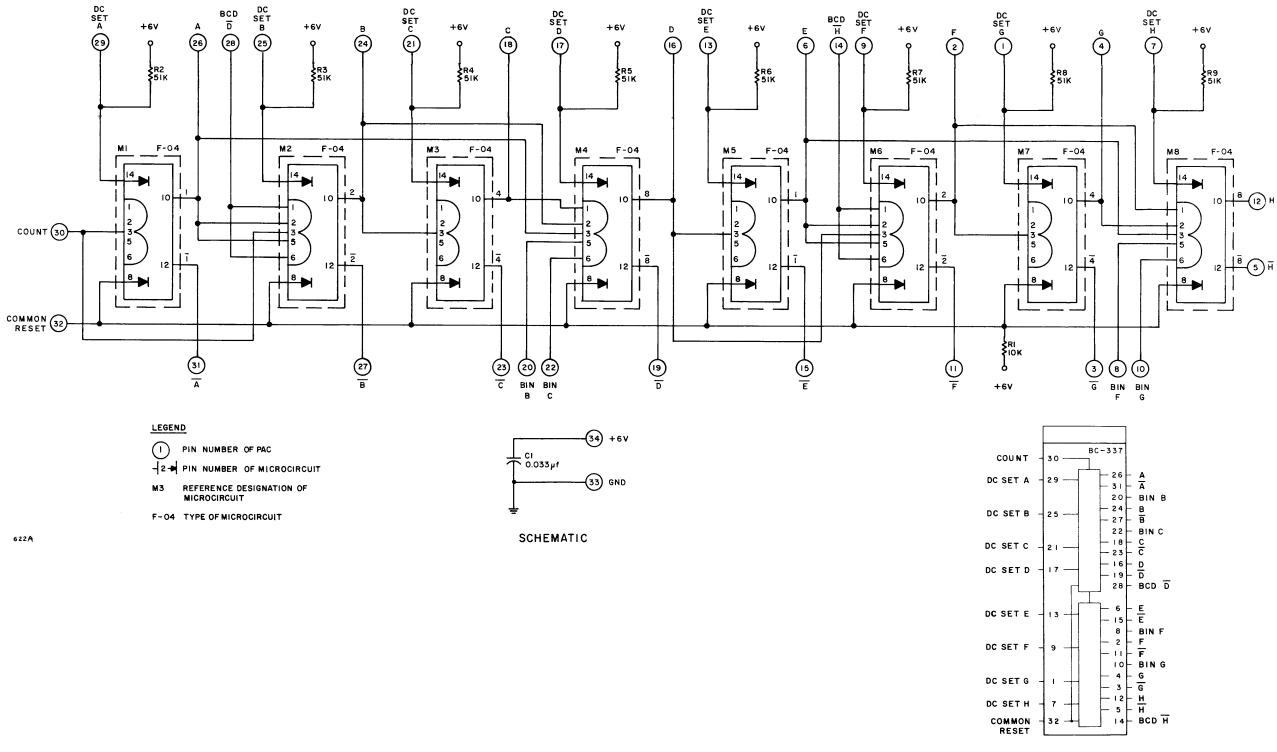

| 3-3.1           | Fast Carry Counter PAC, Model BC-337, Schematic Diagram and Logic Symbol                           | 3-13           |

| 3-3.2           | Fast Carry Counter PAC, Model BC-337, Parts Location and Identification                            | 3-15           |

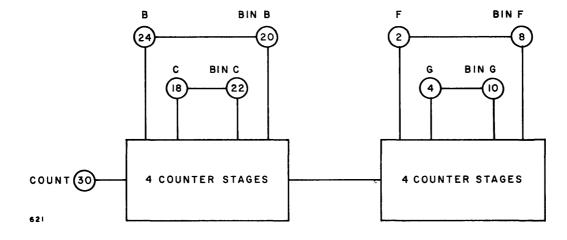

| 3-3.3           | Fast Carry Counter PAC, Model BC-337, Jumper Connections for Binary Counting                       | 3-16           |

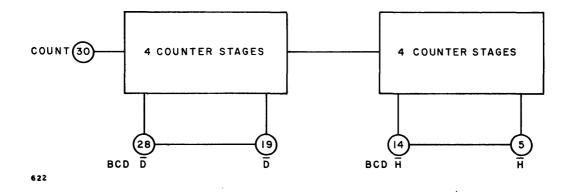

| 3-3.4           | Fast Carry Counter PAC, Model BC-337, Jumper Connections for BCD Counting                          | 3-16           |

| 3-3.1A          | Fast Carry Counter PAC, Model BC-337 (Ser. No. 800 and beyond), Schematic Diagram and Logic Symbol | 3 <b>-</b> 16A |

| 3-3.2A          | Fast Carry Counter PAC, Model BC-337 (Ser. No. 800 and beyond), Parts Location and Identification  | 3-16C          |

| 3-4.1           | Mechanical Arrangement of BL-330                                                                   | 3 <b>-</b> 18A |

| Figure | Title                                                                                               | Page           |

|--------|-----------------------------------------------------------------------------------------------------|----------------|

| 3-5.1  | $\mu$ -BLOC, Model BM-337, with Adapter Panel                                                       | 3-21           |

| 3-5A.1 | Blank PAC, Model BP-330                                                                             | 3 <b>-</b> 22A |

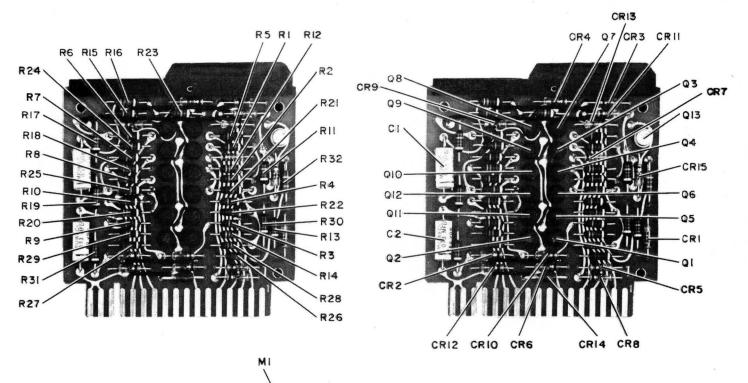

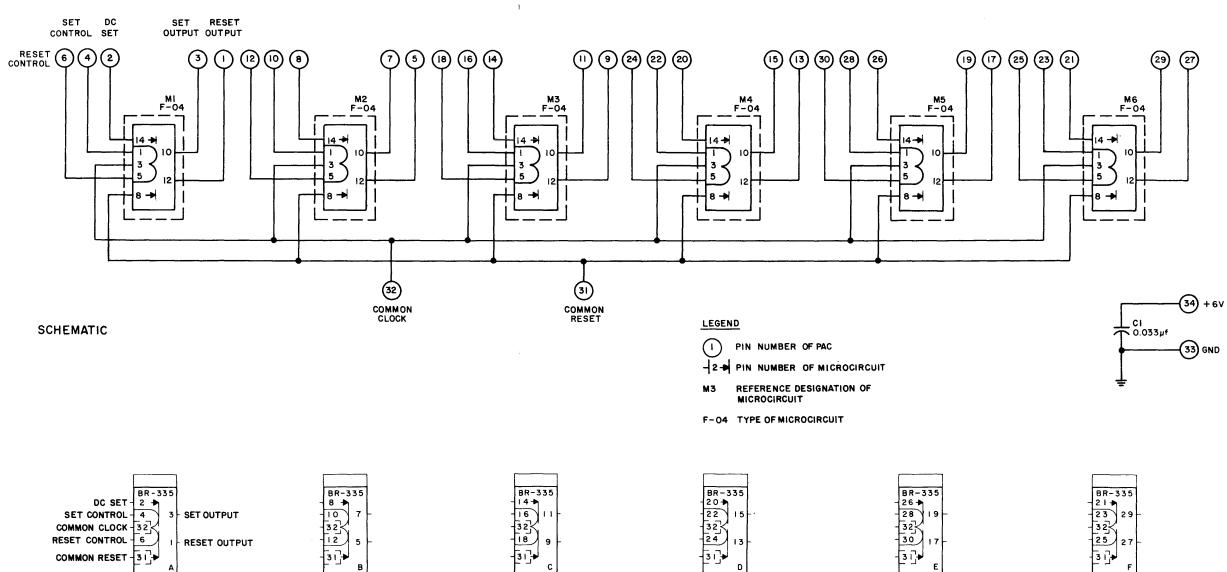

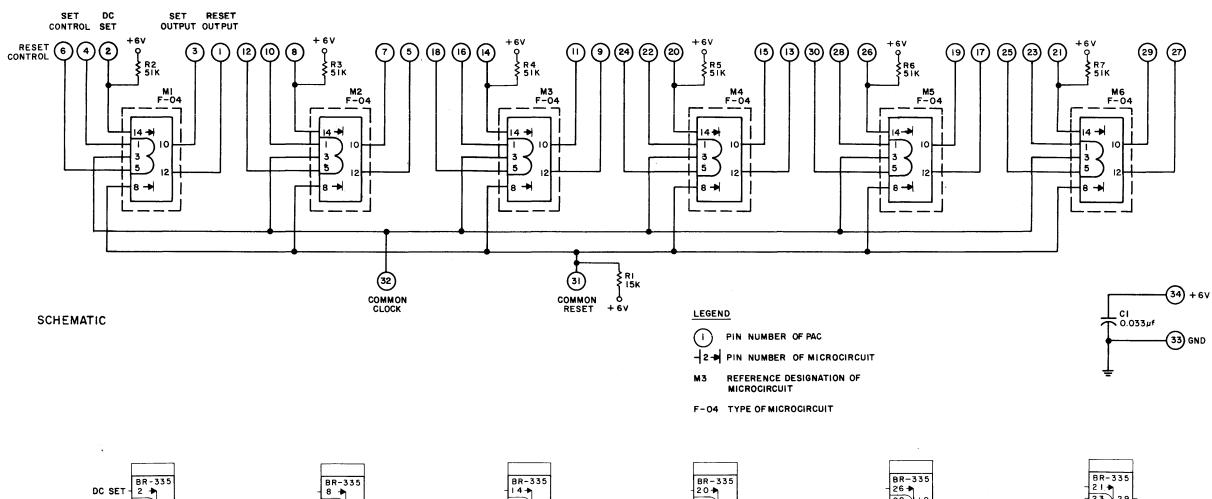

| 3-6.1  | Buffer Register PAC, Model BR-335, Schematic Diagram and Logic Symbol                               | 3-25           |

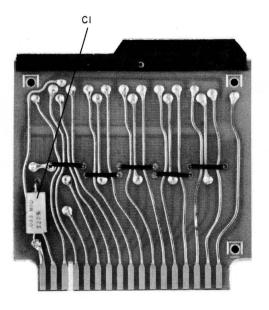

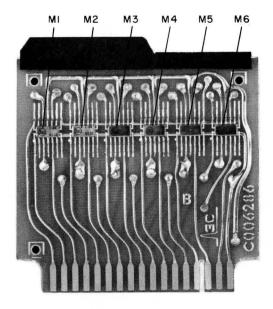

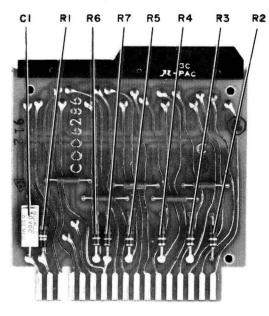

| 3-6.2  | Buffer Register PAC, Model BR-335, Parts Location and Identification                                | 3-27           |

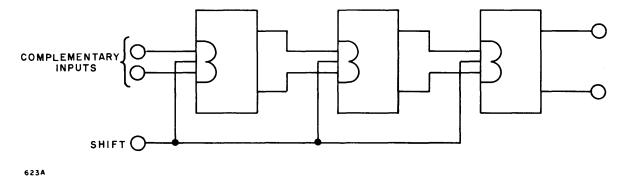

| 3-6.3  | Buffer Register PAC, Model BR-335, Shift Register Operation                                         | 3-28           |

| 3-6.4  | Buffer Register PAC, Model BR-335, Parallel Information<br>Drop-In                                  | 3-28           |

| 3-6.1A | Buffer Register PAC, Model BR-335 (Ser. No. 1186 and beyond),<br>Schematic Diagram and Logic Symbol | 3-28A          |

| 3-6.2A | Buffer Register PAC, Model BR-335 (Ser. No. 1186 and beyond),<br>Parts Location and Identification  | 3-28C          |

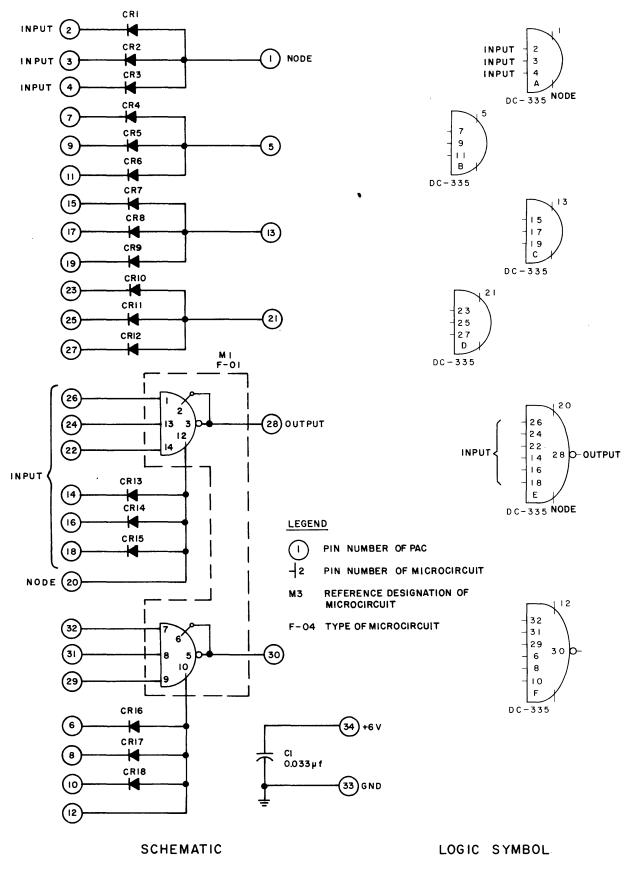

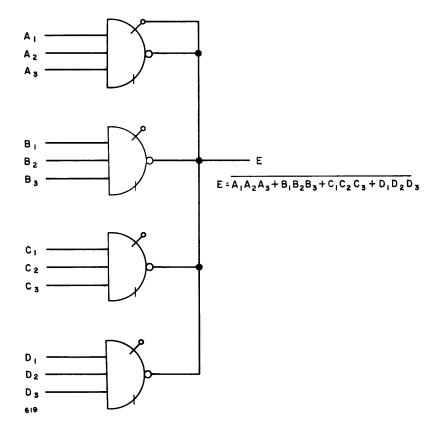

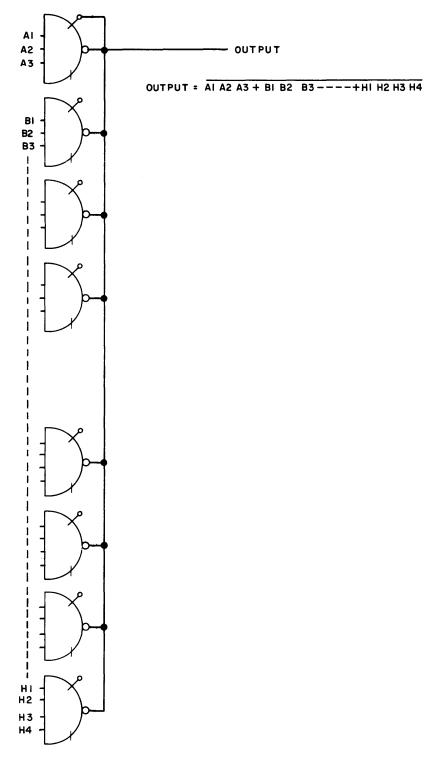

| 3-7.1  | Multi-Input NAND PAC, Model DC-335, Schematic Diagram and Logic Symbol                              | 3-30           |

| 3-7.2  | Multi-Input NAND PAC, Model DC-335, Parts Location and Identification                               | 3-31           |

| 3-7.3  | Multi-Input NAND PAC, Model DC-335, Expansion of Gate Inputs                                        | 3-32           |

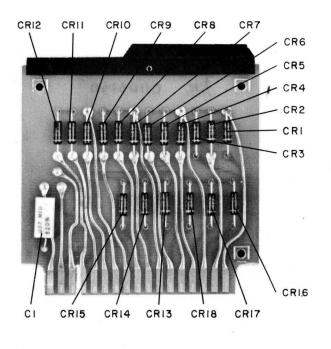

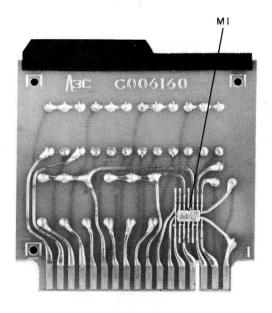

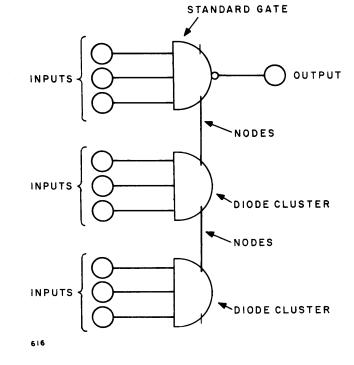

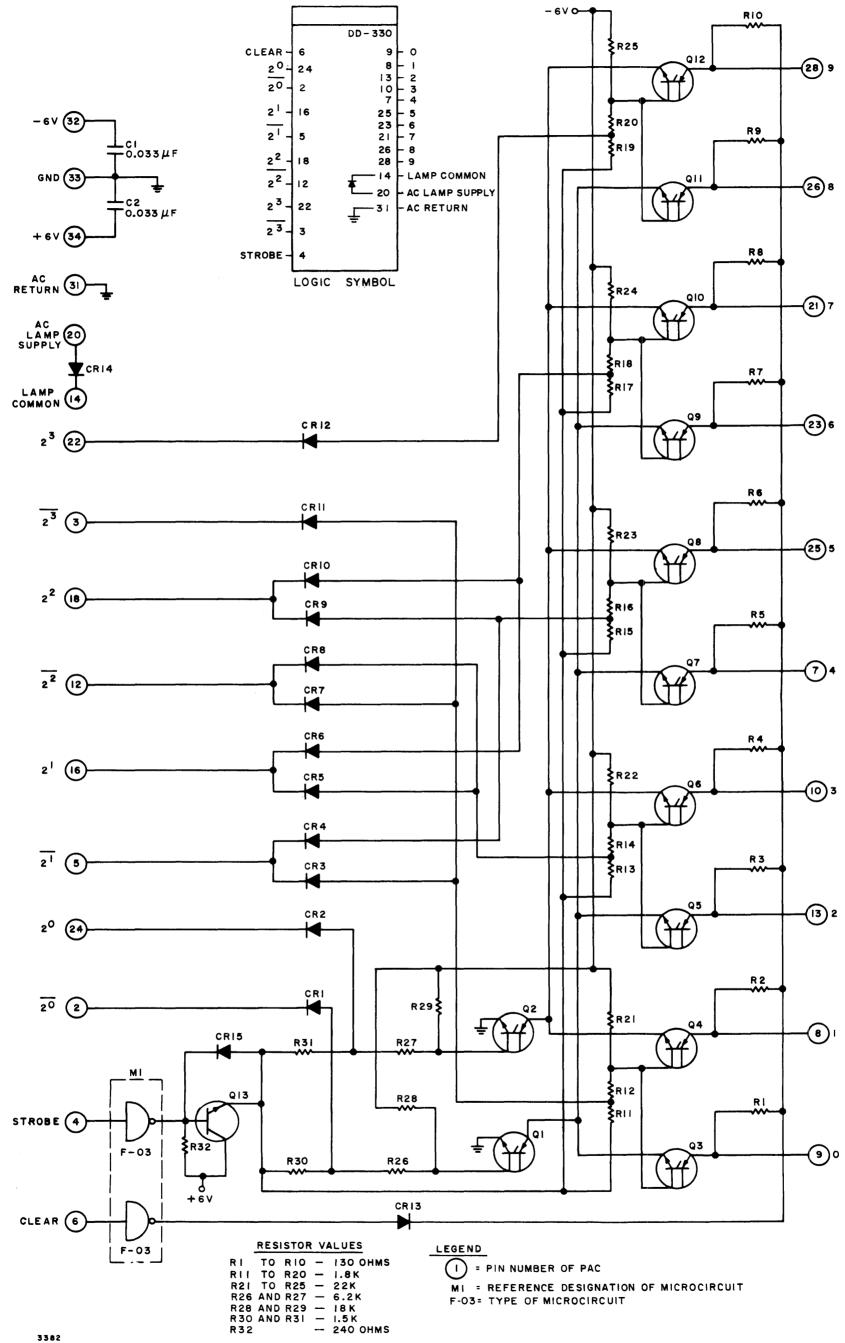

| 3-7A.1 | Display Driver PAC, Model DD-330, Schematic Diagram and Logic Symbol                                | 3-32C          |

| 3-7A.2 | Display Driver PAC, Model DD-330, Parts Location and<br>Identification (Sheet 1 of 2)               | 3-32E          |

| 3-7A.2 | Display Driver PAC, Model DD-330, Parts Location and<br>Identification (Sheet 2 of 2)               | 3 <b>-</b> 32F |

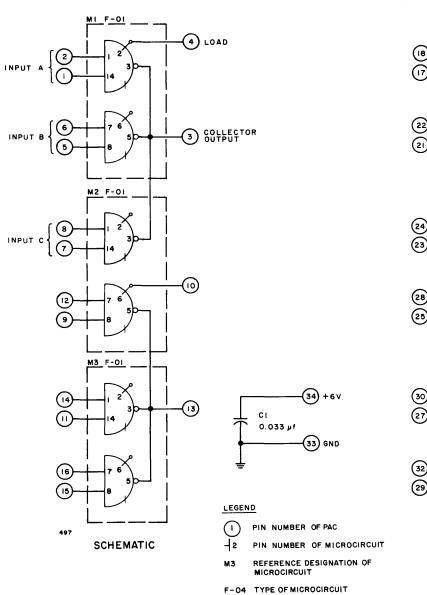

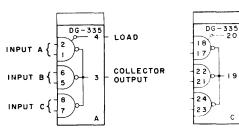

| 3-8.1  | Selection Gate Type 1 PAC, Model DG-335, Schematic Diagram and Logic Symbol                         | 3-34           |

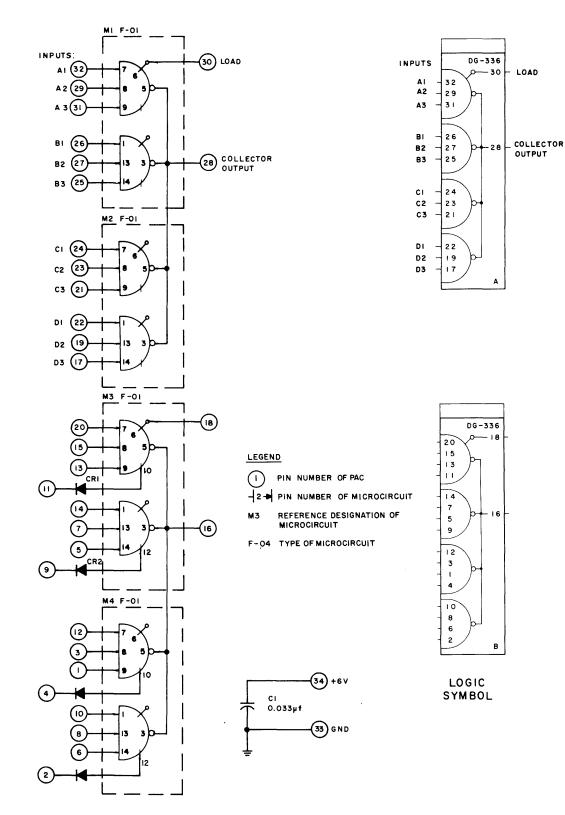

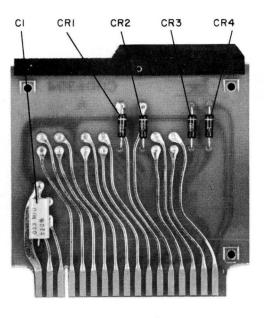

| 3-8.2  | Selection Gate Type 1 PAC, Model DG-335, Parts Location and Identification                          | 3-35           |

| 3-8.3  | Selection Gate Type 1 PAC, Model DG-335, Logic of Gate Structure                                    | 3-36           |

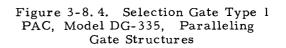

| 3-8.4  | Selection Gate Type 1 PAC, Model DG-335, Paralleling<br>Gate Structure                              | 3-36           |

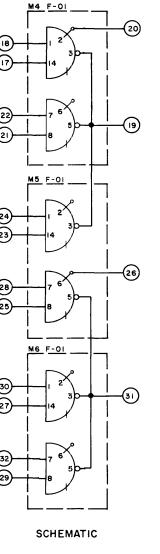

| 3-9.1  | Selection Gate Type 2 PAC, Model DG-336, Schematic Diagram and Logic Symbol                         | 3-38           |

| 3-9.2  | Selection Gate Type 2 PAC, Model DG-336, Parts Location and Identification                          | 3-39           |

| 3-9.3  | Selection Gate Type 2 PAC, Model DG-336, Logic of Gate Structure                                    | 3-40           |

| 3-9.4  | Selection Gate Type 2 PAC, Model DG-336, Paralleling Gate Structure                                 | 3-41           |

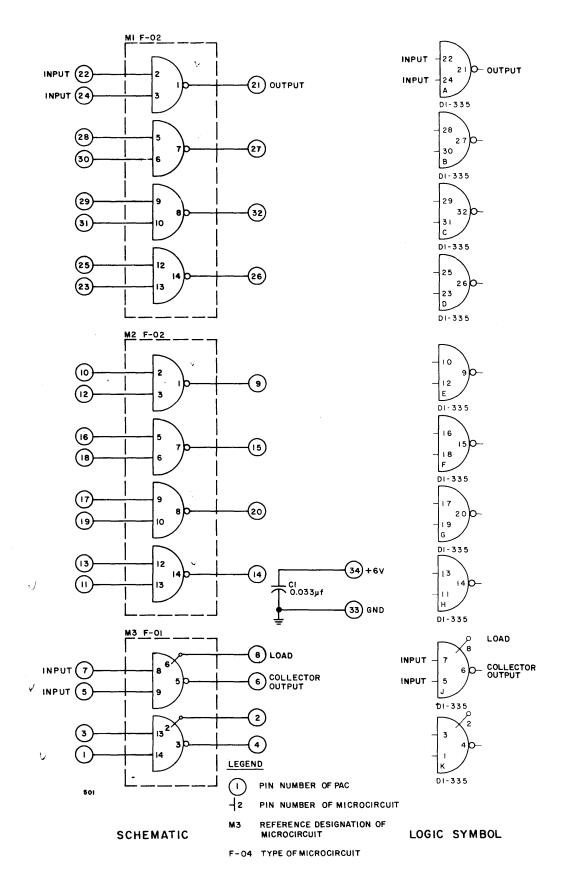

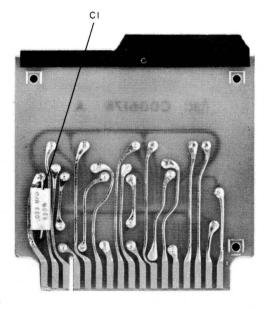

| 3-10.1 | NAND Type 1 PAC, Model DI-355, Schematic Diagram and Logic Symbol                                   | 3-44           |

| 3-10.2 | NAND Type 1 PAC, Model DI-335, Parts Location and Identification                                    | 3-45           |

| 3-10.3 | NAND Type 1 PAC, Model DI-335, Gates Used in Parallel                                               | 3-46           |

| Figure           | Title                                                                                                 | Page            |

|------------------|-------------------------------------------------------------------------------------------------------|-----------------|

| 3-11.1           | NAND Type 2 PAC, Model DL-335, Schematic Diagram and<br>Logic Symbol                                  | 3-48            |

| 3-11.2           | NAND Type 2 PAC, Model DL-335, Parts Location and Identification                                      | 3-49            |

| 3-11.3           | NAND Type 2 PAC, Model DL-335, Gates Used in Parallel                                                 | 3-50            |

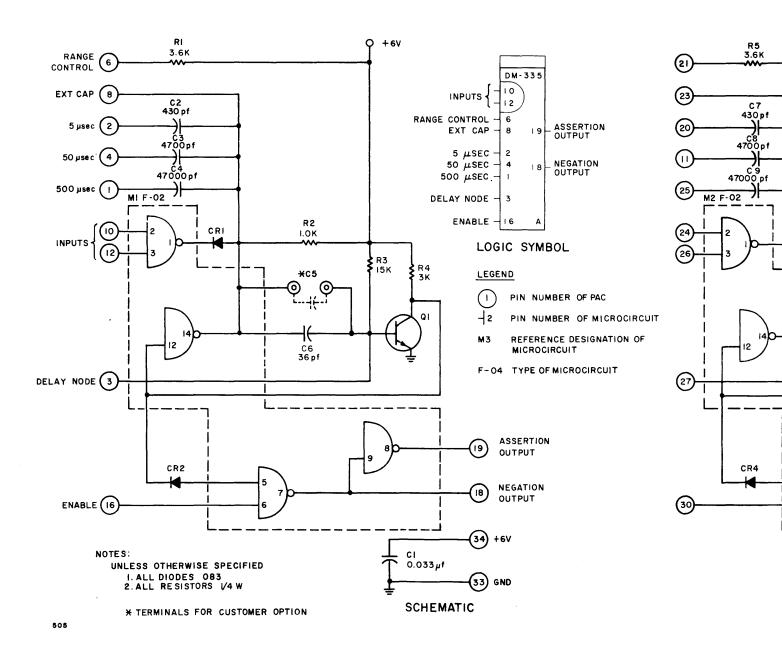

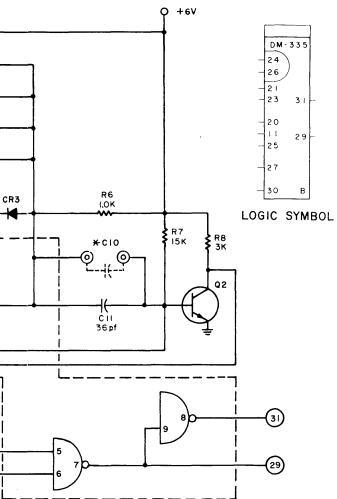

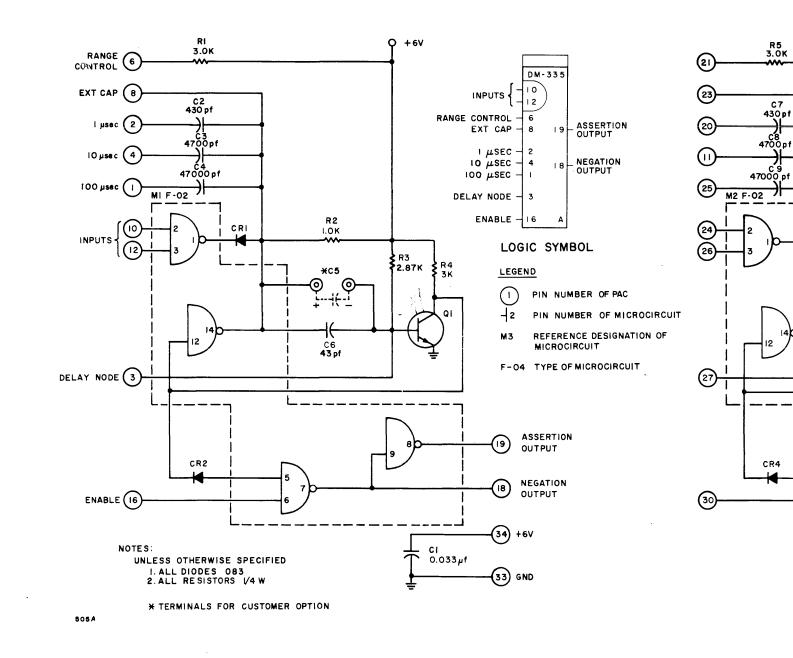

| 3-12.1           | Delay Multivibrator PAC, Model DM-335, Schematic Diagram<br>and Logic Symbol (Ser. No. 1 through 999) | 3 <b>-</b> 53   |

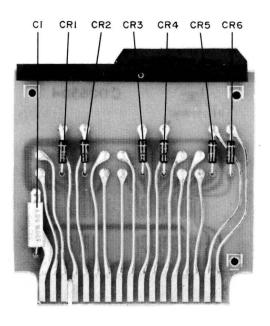

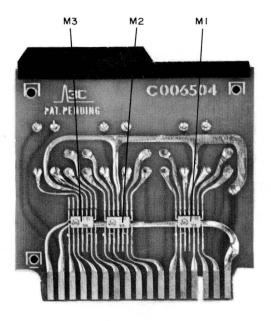

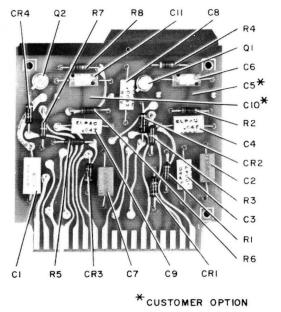

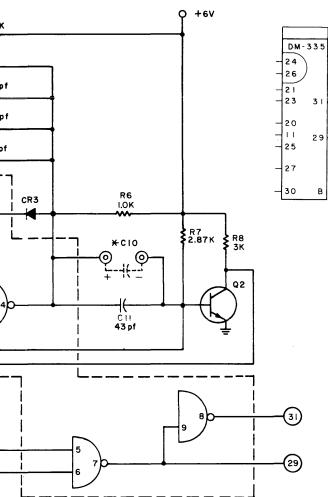

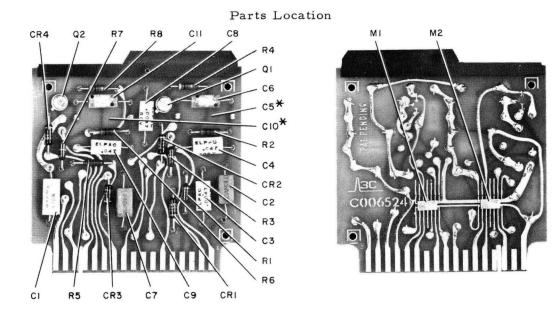

| 3-12.2           | Delay Multivibrator PAC, Model DM-335, Parts Location and Identification                              | 3 <b>-</b> 55   |

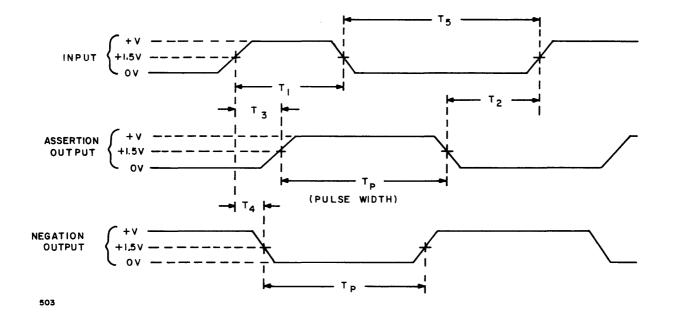

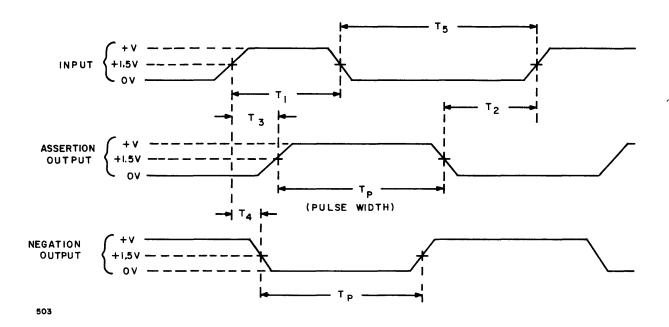

| 3-12.3           | Timing of the Delay Multivibrator PAC, Model DM-335                                                   | 3-57            |

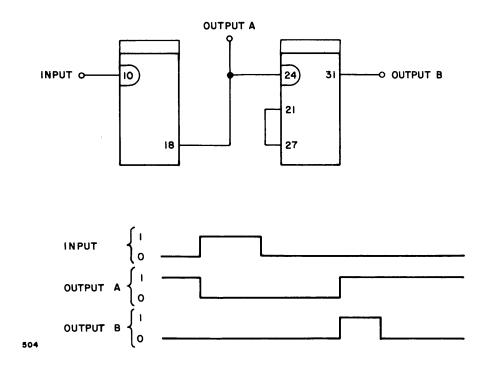

| 3-12.4           | Delay Multivibrator PAC, Model DM-335, Delayed Pulse<br>Generator                                     | 3-58            |

| 3-12A.1          | Delay Multivibrator PAC, Model DM-335, Schematic Diagram and Logic Symbol                             | 3 <b>-</b> 58E  |

| 3-12A.2          | Delay Multivibrator PAC, Model DM-335, Parts Location and Identification                              | 3 <b>-</b> 58G  |

| 3 <b>-</b> 12A.3 | Timing of the Delay Multivibrator PAC, Model DM-335                                                   | 3 <b>-</b> 58J  |

| 3-12A.4          | Delay Multivibrator PAC, Model DM-335, Delayed Pulse<br>Generator (Ser. No. 1000 and beyond)          | 3 <b>-</b> 58K  |

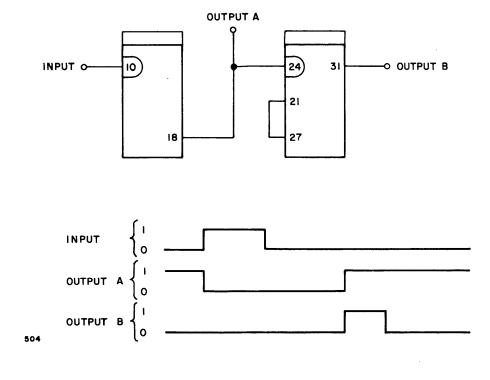

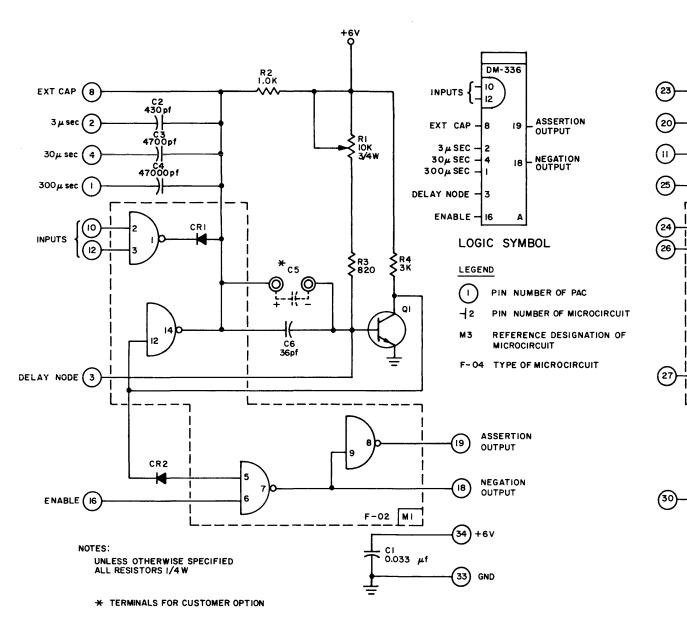

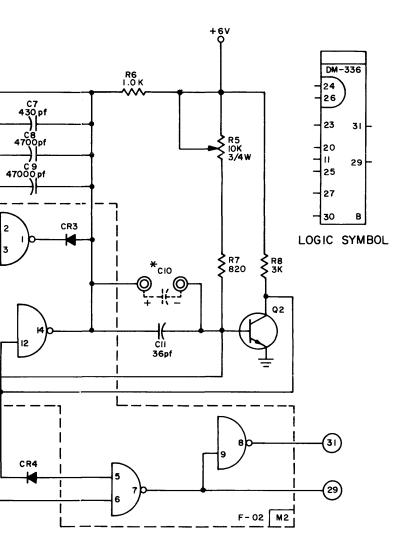

| 3-12B.1          | Adjustable Delay Multivibrator PAC, Model DM-336, Schematic<br>Diagram and Logic Symbol               | 3 <b>-</b> 58N  |

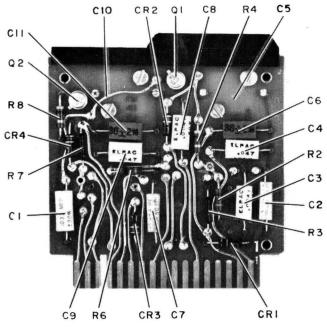

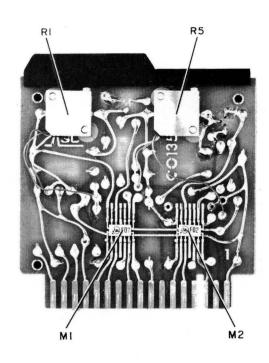

| 3-12B.2          | Adjustable Delay Multivibrator PAC, Model DM-336, Parts<br>Location and Identification (Sheet 1)      | 3 <b>-</b> 58Q  |

| 3-12B.2          | Adjustable Delay Multivibrator PAC, Model DM-336, Parts<br>Location and Identification (Sheet 2)      | 3 <b>-</b> 58R  |

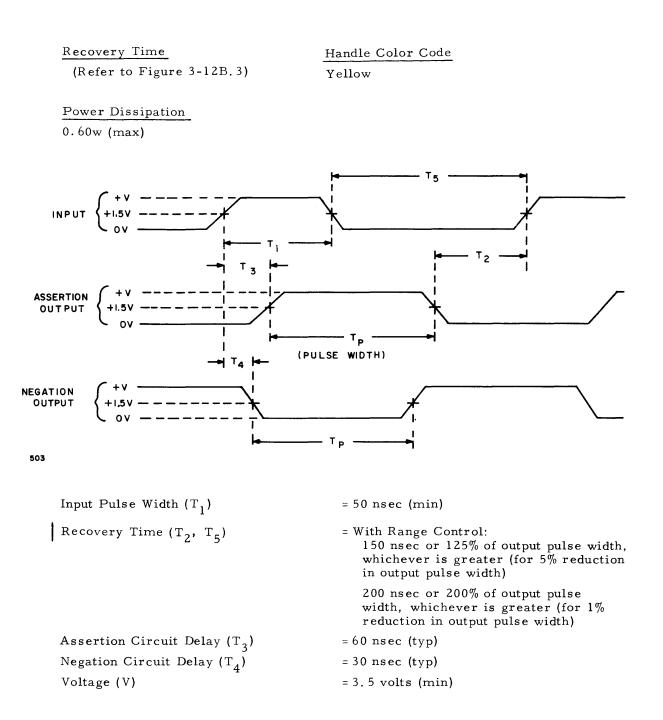

| 3-12B.3          | Timing of the Delay Multivibrator PAC, Model DM-336                                                   | 3 <b>-</b> 58S  |

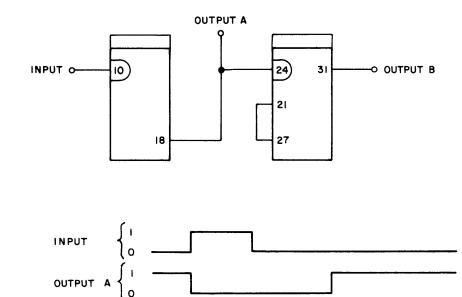

| 3-12B.4          | Delay Multivibrator PAC, Model DM-336, Delayed Pulse<br>Generator                                     | 3 <b>-</b> 58 T |

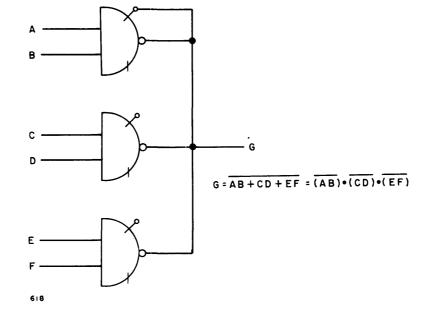

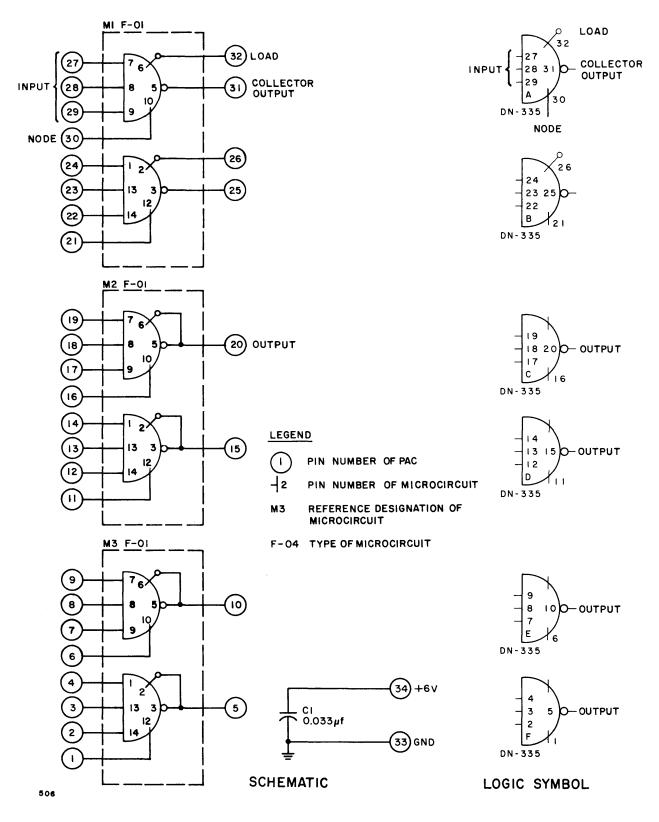

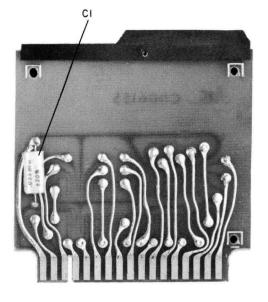

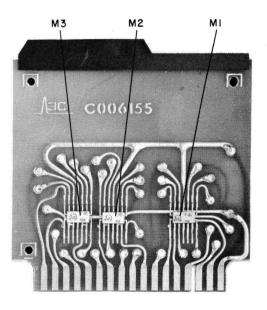

| 3-13.1           | Expandable NAND PAC, Model DN-335, Schematic Diagram and Logic Symbol                                 | 3-60            |

| 3-13.2           | Expandable NAND PAC, Model DN-335, Parts Location and Identification                                  | 3-61            |

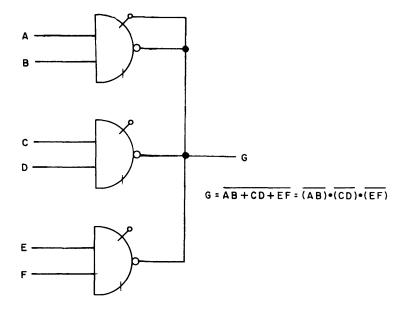

| 3-13.3           | Gates Used in Parallel                                                                                | 3-62            |

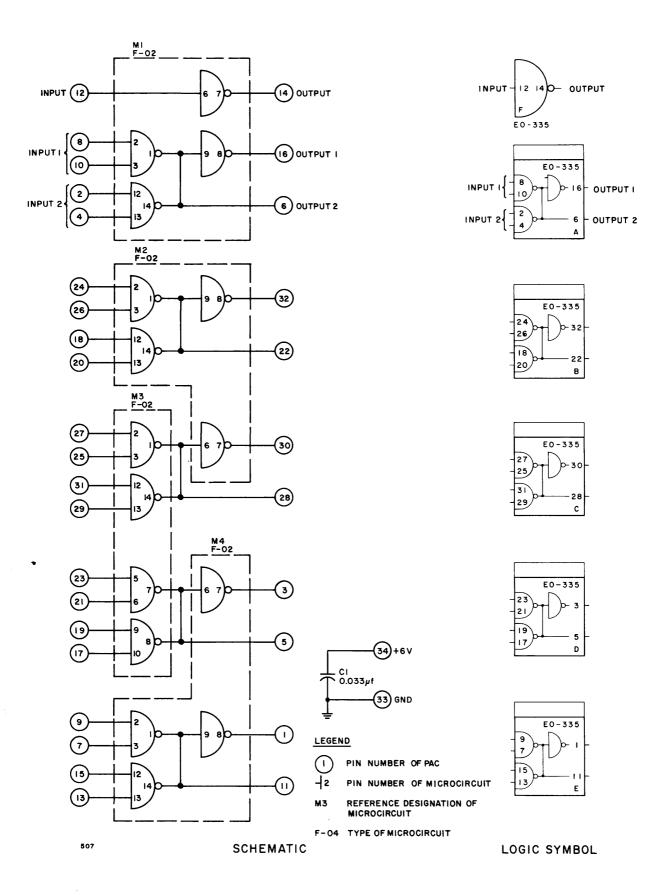

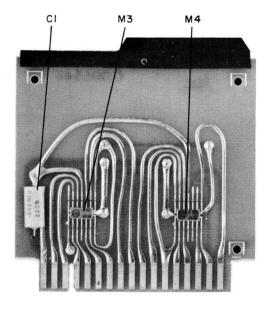

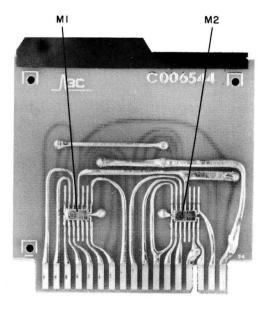

| 3-14.1           | Exclusive OR PAC, Model EO-335, Schematic Diagram and Logic Symbol                                    | 3-64            |

| 3-14.2           | Exclusive OR PAC, Model EO-335, Parts Location and Identification                                     | 3-65            |

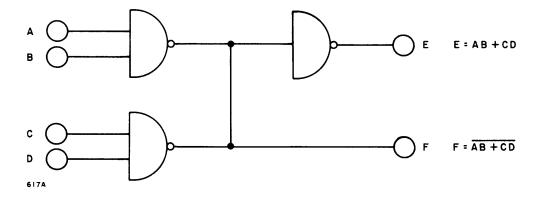

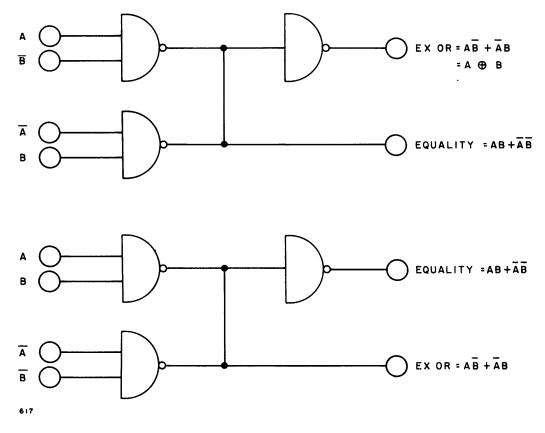

| 3-14.3           | Logic of EO-335 Gate Structure                                                                        | 3-66            |

| 3-14.4           | Exclusive OR and Equality Functions                                                                   | 3-66            |

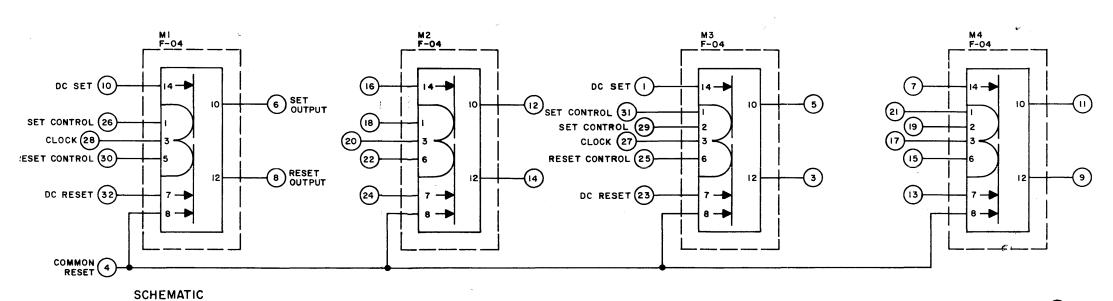

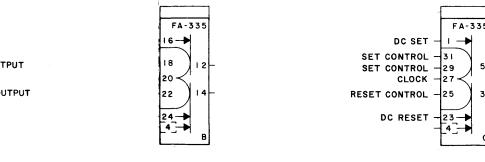

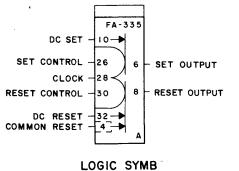

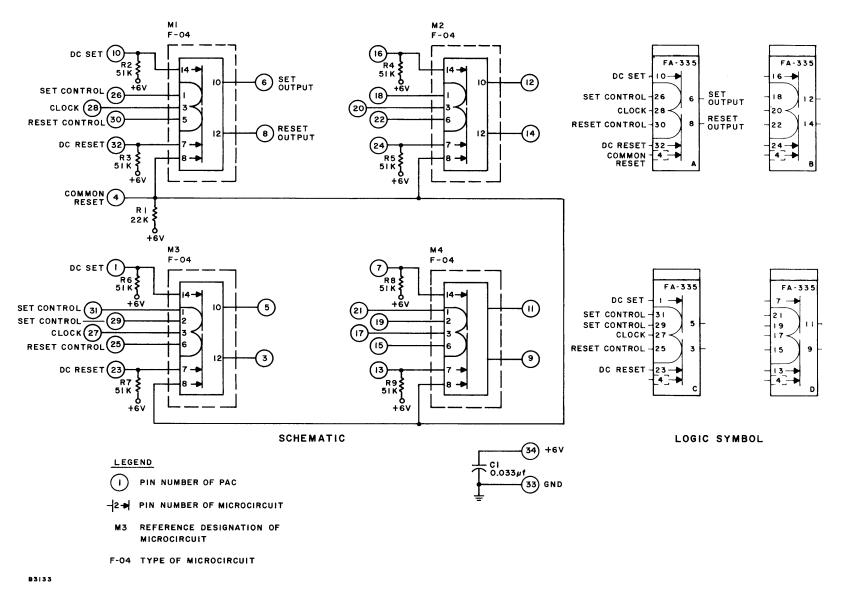

| 3-15.1           | Gated Flip-Flop PAC, Model FA-335, Schematic Diagram and Logic Symbol                                 | 3-69            |

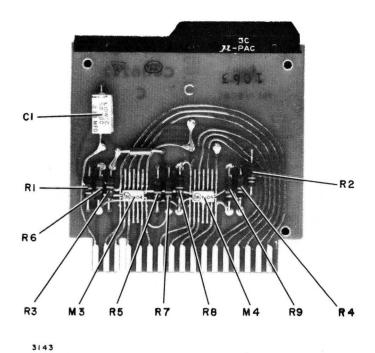

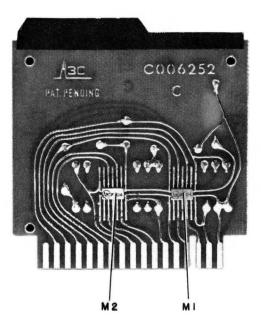

| 3-15.2           | Gated Flip-Flop PAC, Model FA-335, Parts Location and Identification                                  | 3-71            |

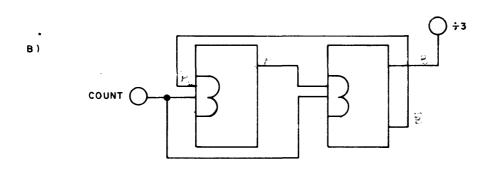

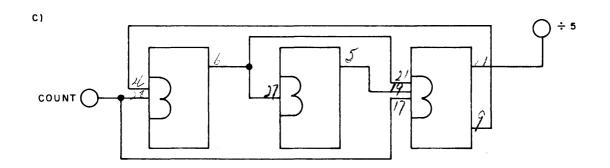

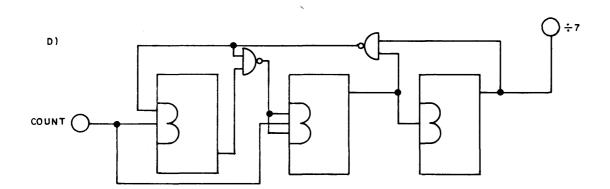

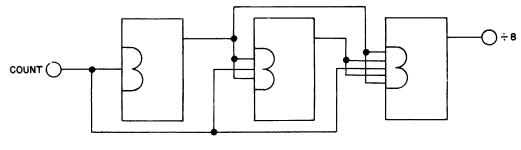

| 3-15.3           | Gated Flip-Flop PAC, Model FA-335, Counter Operation                                                  | 3-72            |

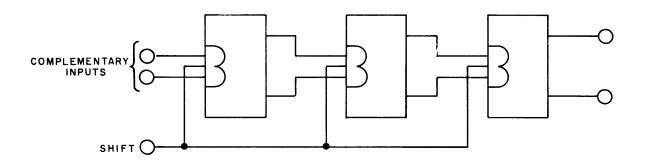

| 3-15.4           | Gated Flip-Flop PAC, Model FA-335, Shift Register Operation                                           | 3-73            |

| Figure           | Title                                                                                           | Page           |

|------------------|-------------------------------------------------------------------------------------------------|----------------|

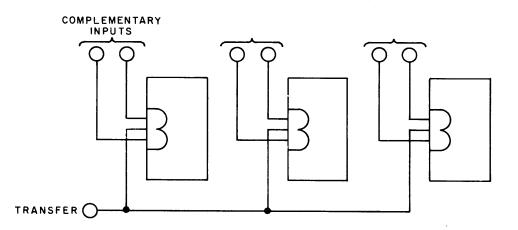

| 3-15.5           | Gated Flip-Flop PAC, Model FA-335, Parallel Information<br>Drop-In                              | 3-73           |

| 3-15.1A          | Gated Flip-Flop PAC, Model FA-335 (Ser. No. 831 and beyond), Schematic Diagram and Logic Symbol | 3 <b>-</b> 74A |

| 3-15.2A          | Gated Flip-Flop PAC, Model FA-335 (Ser. No. 831 and beyond), Parts Location and Identification  | 3 <b>-7</b> 4B |

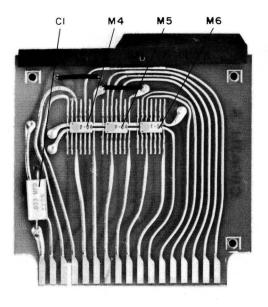

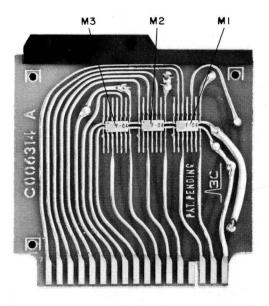

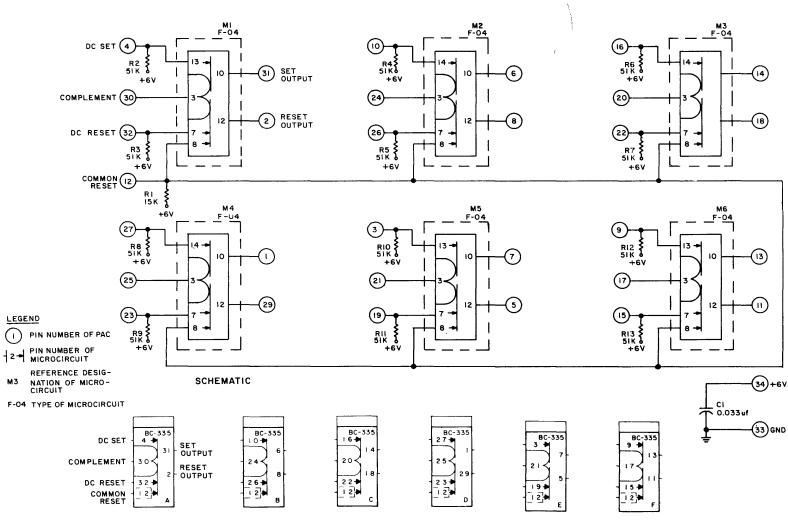

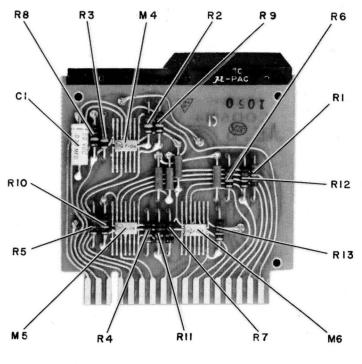

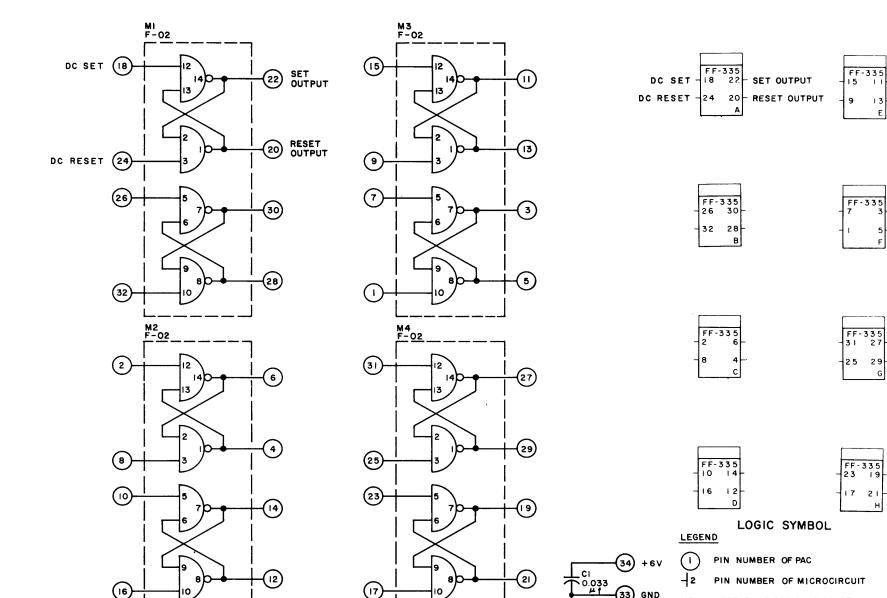

| 3-16.1           | Basic Flip-Flop PAC, Model FF-335, Schematic Diagram<br>and Logic Symbol                        | 3-76           |

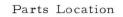

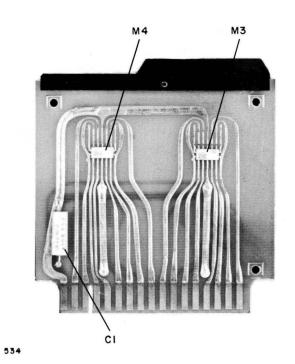

| 3-16.2           | Basic Flip-Flop PAC, Model FF-335, Parts Location and Identification                            | 3 <b>-</b> 77  |

| 3-16.3           | Basic Flip-Flop PAC, Model FF-335, Logic Operation                                              | 3-78           |

| 3-16.4           | Basic Flip-Flop PAC, Model FF-335, Input and Output Logic                                       | 3-79           |

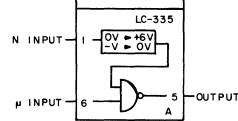

| 3-17A.1          | Negative Logic Level Converter PAC, Model LC-335,<br>Schematic Diagram and Logic Symbol         | 3-82C          |

| 3-17A.2          | Negative Logic Level Converter PAC, Model LC-335, Parts<br>Location and Identification          | 3-82E          |

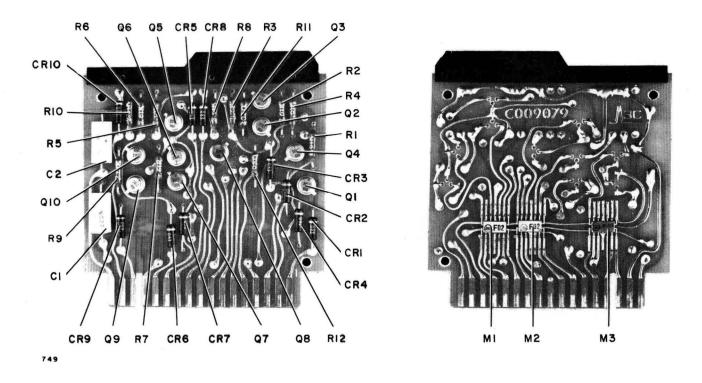

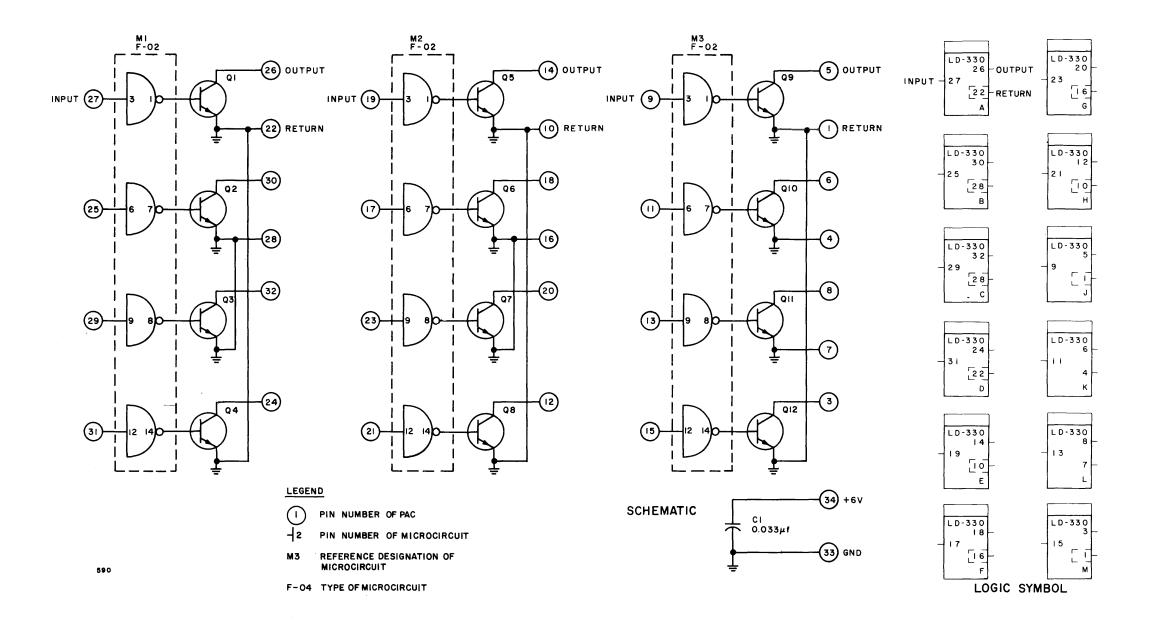

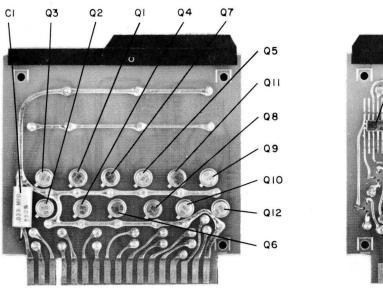

| 3-18.1           | Lamp Driver PAC, Model LD-330, Schematic Diagram and<br>Logic Symbol                            | 3-85           |

| 3-18.2           | Lamp Driver PAC, Model LD-330, Parts Location and Identification                                | 3-87           |

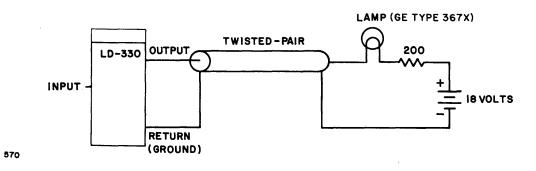

| 3-18.3           | Lamp Driver PAC, Model LD-330, Driving a Remote Lamp                                            | 3-88           |

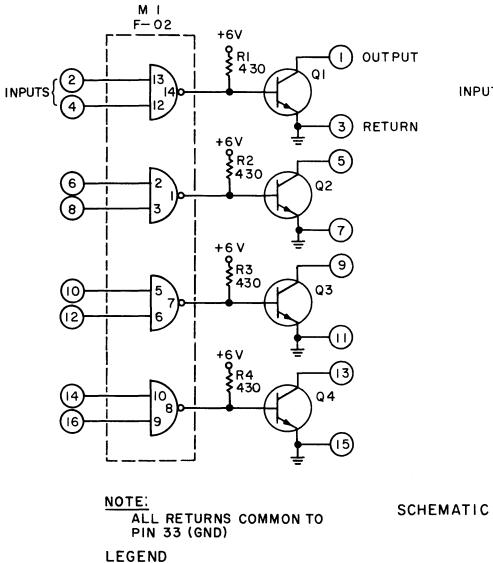

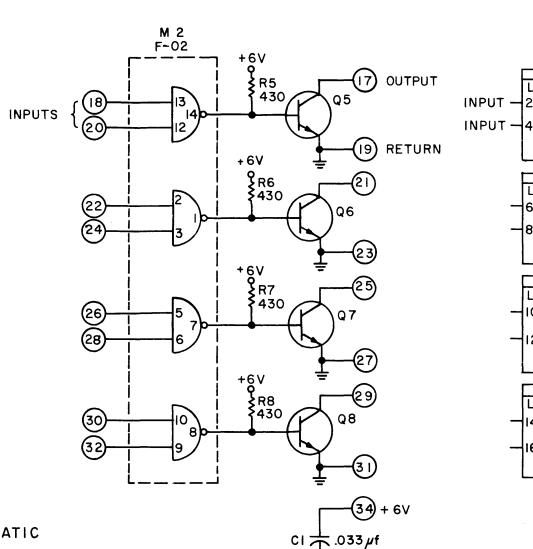

| 3-18A.1          | High-Drive Lamp Driver PAC, Model LD-331, Schematic<br>Diagram and Logic Symbol                 | 3 <b>-</b> 88C |

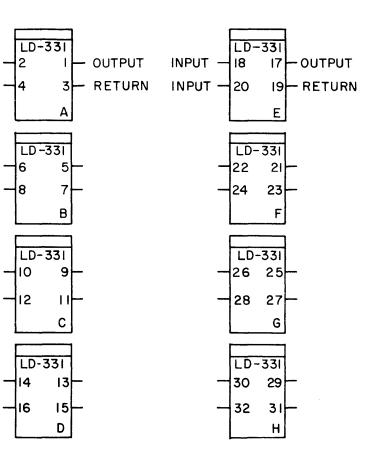

| 3 <b>-</b> 18A.2 | High-Drive Lamp Driver PAC, Model LD-331, Parts<br>Location and Identification                  | 3-88E          |

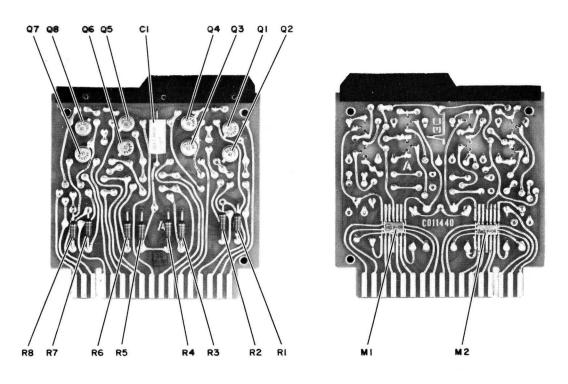

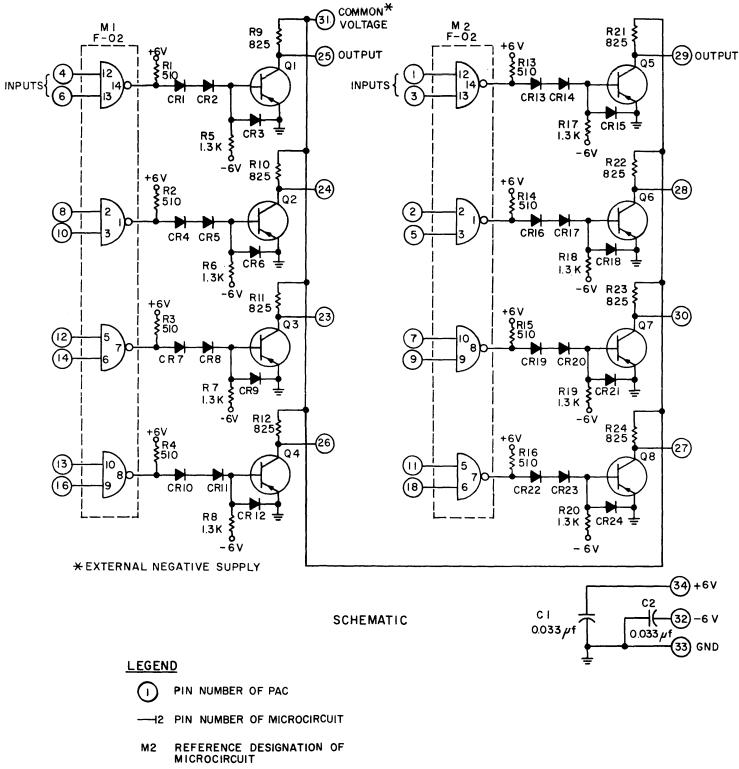

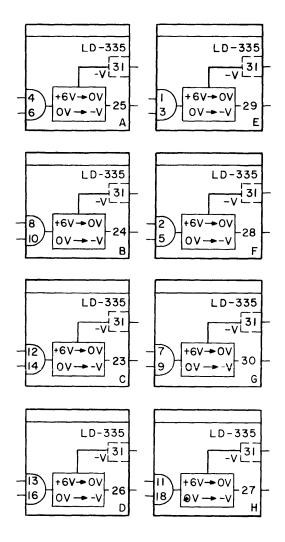

| 3-18B.1          | Negative Logic Level Driver PAC, Model LD-335, Schematic<br>Diagram and Logic Symbol            | 3-88J          |

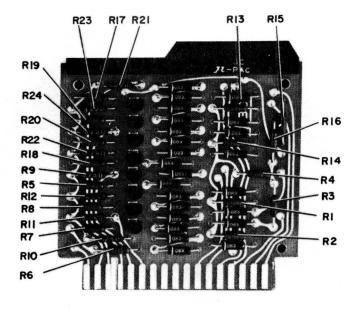

| 3-18B.2          | Negative Logic Level Driver PAC, Model LD-335, Parts<br>Location and Identification             | 3-88L          |

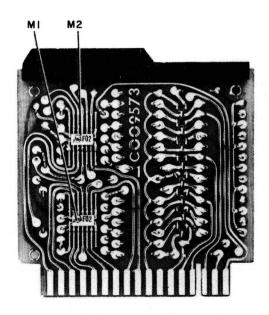

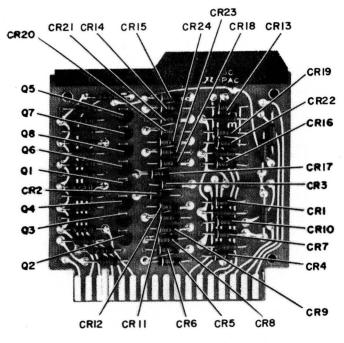

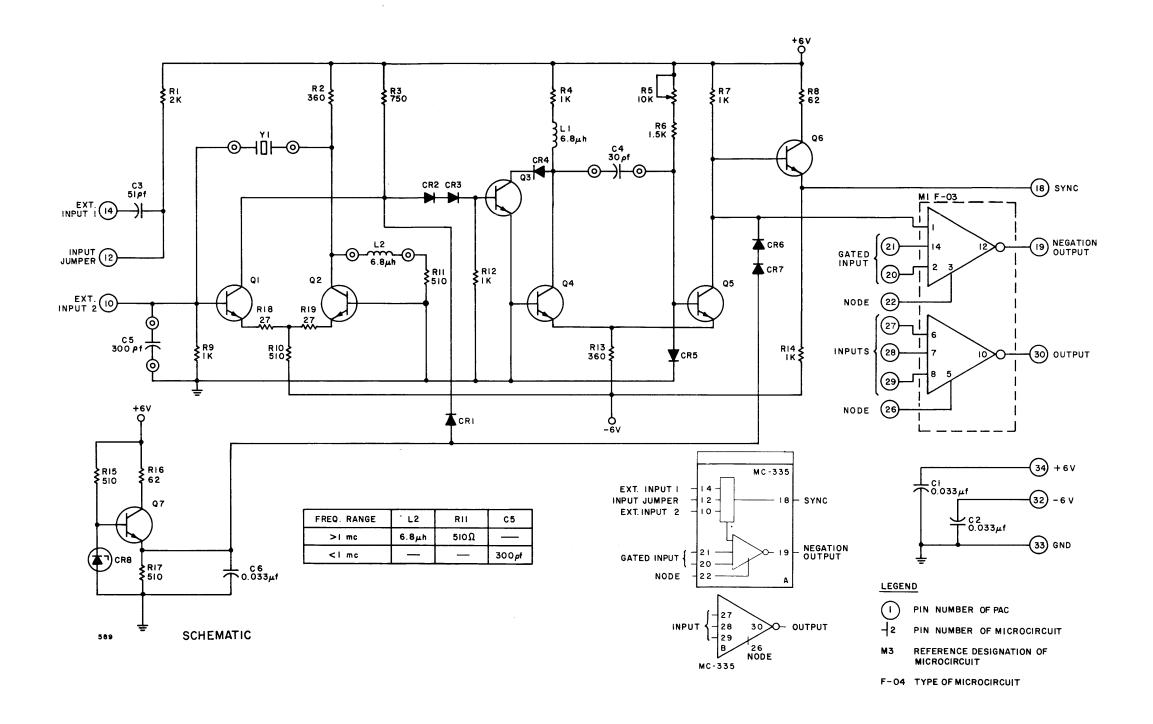

| 3-19.1           | Master Clock PAC, Model MC-335, Schematic Diagram and Logic Symbol                              | 3-93           |

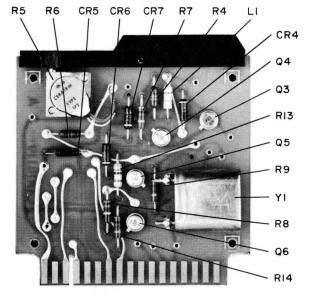

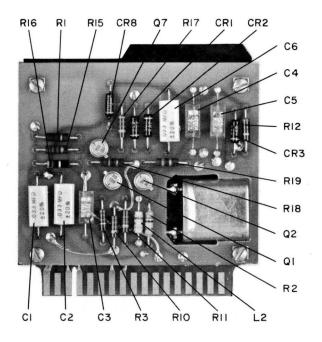

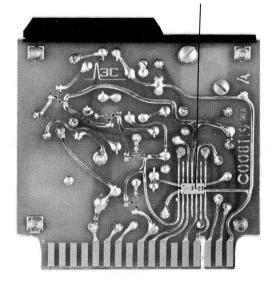

| 3-19.2           | Master Clock PAC, Model MC-335, Parts Location and Identification (Sheet 1 of 2)                | 3-95           |

| 3-19.2           | Master Clock PAC, Model MC-335, Parts Location and Identification (Sheet 2 of 2)                | 3-96           |

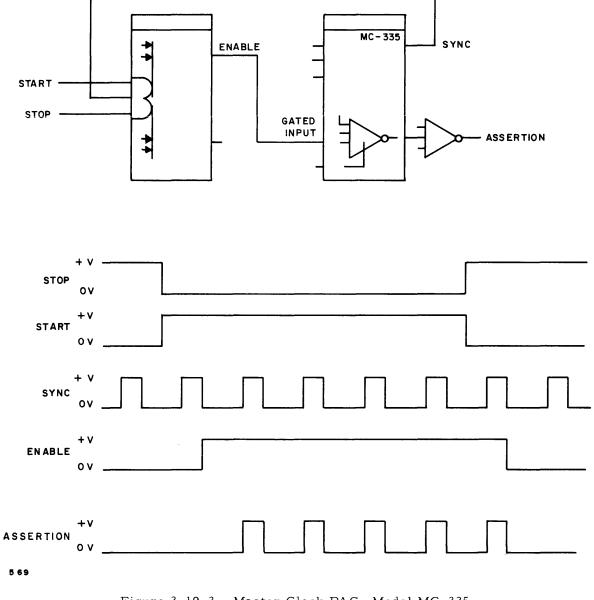

| 3-19.3           | Master Clock PAC, Model MC-335, Synchronous Clock Control                                       | 3-97           |

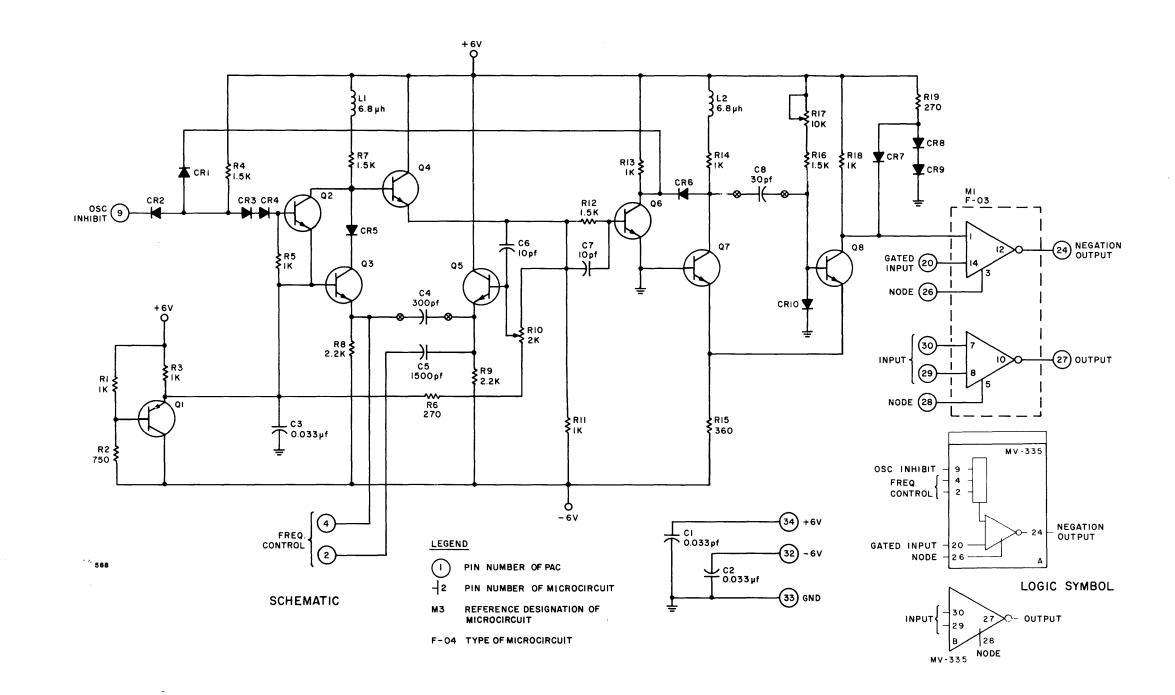

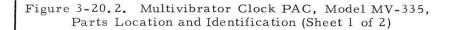

| 3-20.1           | Multivibrator Clock PAC, Model MV-335, Schematic Diagram<br>and Logic Symbol                    | 3-101          |

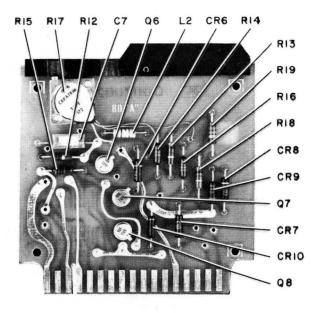

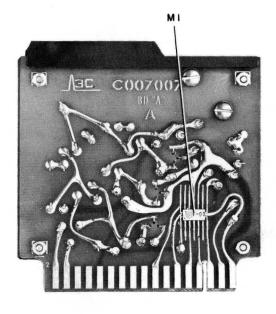

| 3-20.2           | Multivibrator Clock PAC, Model MV-335, Parts Location and<br>Identification (Sheet 1 of 2)      | 3-103          |

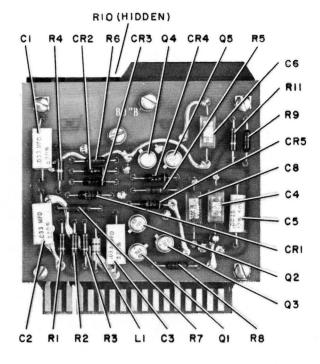

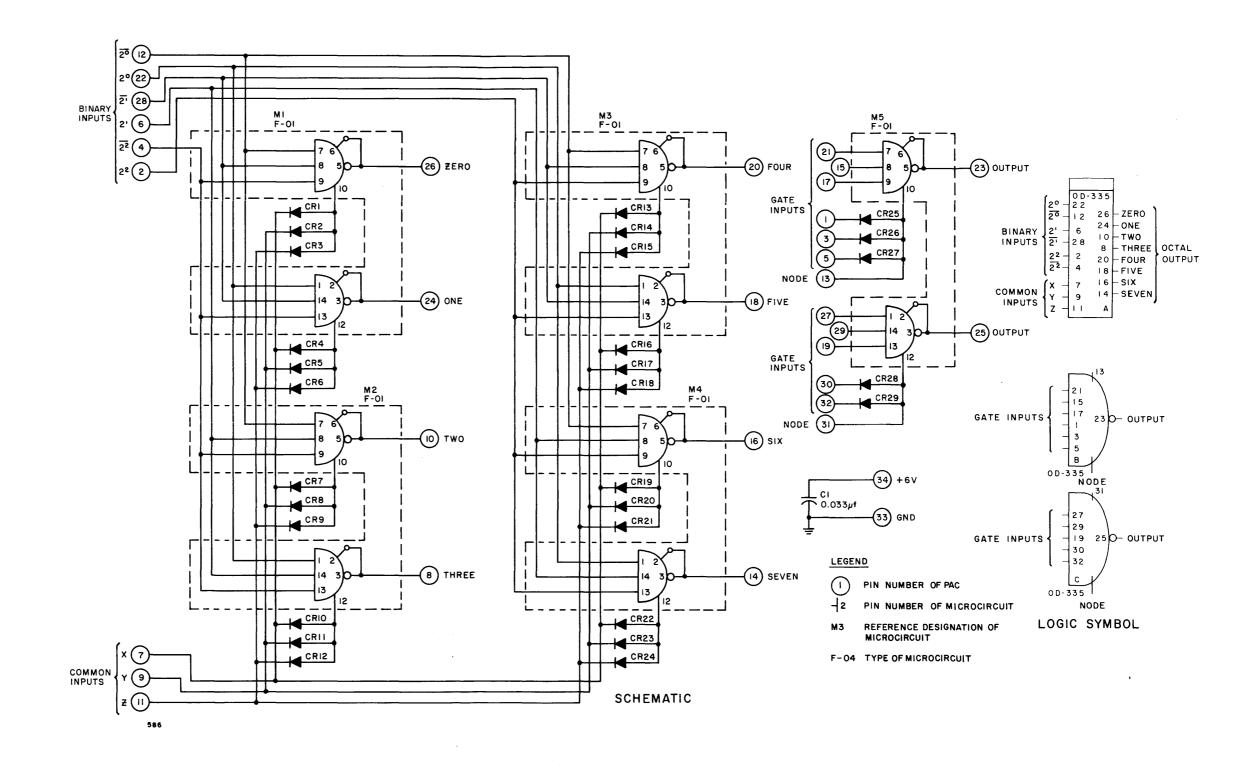

| 3-20.2           | Multivibrator Clock PAC, Model MV-335, Parts Location and<br>Identification (Sheet 2 of 2)      | 3-104          |

| 3-21.1           | Octal/Decimal Decoder PAC, Model OD-335, Schematic Diagram and Logic Symbol                     | 3-111          |

| 3-21.2           | Octal/Decimal Decoder PAC, Model OD-335, Parts Location and Identification                      | 3-113          |

| Figure  | Title                                                                                  | Page            |

|---------|----------------------------------------------------------------------------------------|-----------------|

| 3-21.3  | Octal/Decimal Decoder PAC, Model OD-335, Multioctal<br>Matrices                        | 3-114           |

| 3-21.4  | Octal/Decimal Decoder PAC, Model OD-335, BCD-to-Decimal Decoder                        | 3-115           |

| 3-22.1  | Power Amplifier PAC, Model PA-335, Schematic Diagram and<br>Logic Symbol               | 3-118           |

| 3-22.2  | Power Amplifier PAC, Model PA-335, Parts Location and Identification                   | 3-119           |

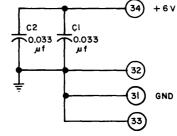

| 3-22A.1 | Power Amplifier PAC, Model PA-336, Schematic Diagram and Logic Symbol                  | 3-120B          |

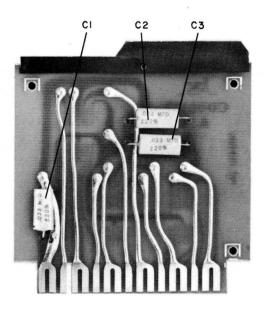

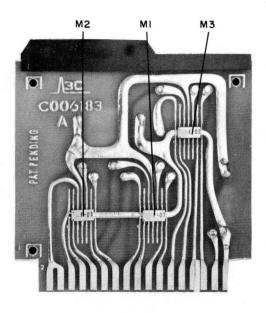

| 3-22A.2 | Power Amplifier PAC, Model PA-336, Parts Location and Identification                   | 3-120C          |

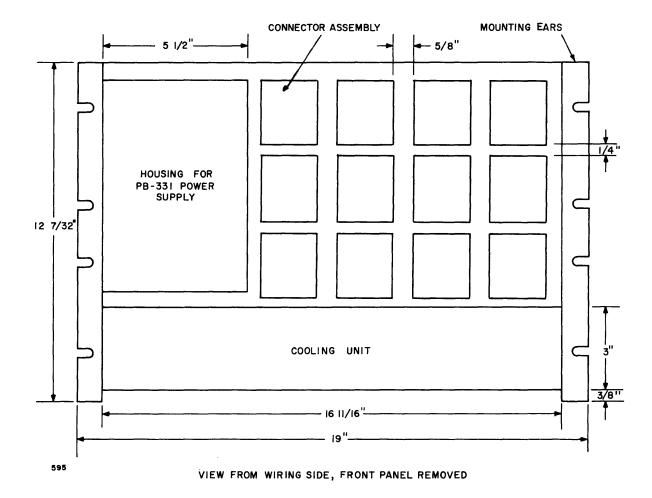

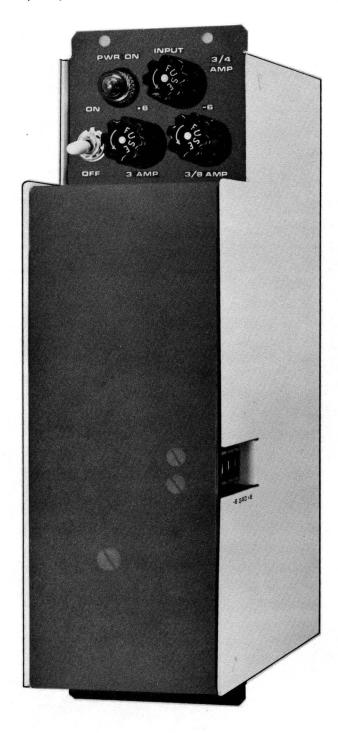

| 3-23.1  | Plug-In Power Supply, Model PB-330                                                     | 3-123           |

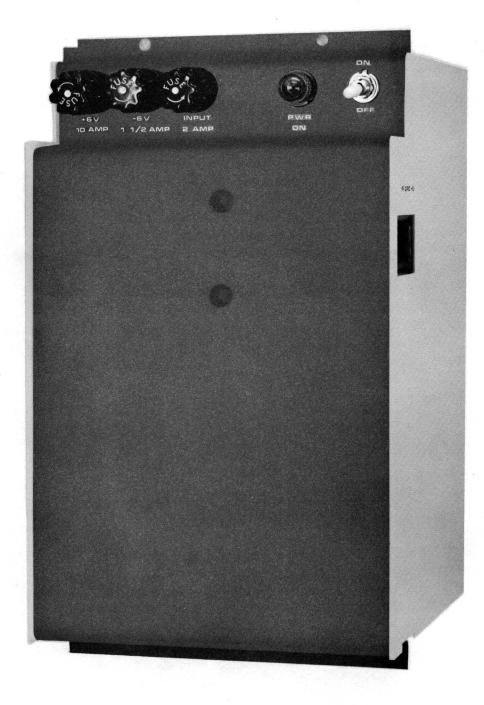

| 3-23.2  | Plug-In Power Supply, Model PB-331                                                     | 3-124           |

| 3-23.3  | Plug-In Power Supply, Model PB-330, Schematic Diagram                                  | 3-125           |

| 3-23.4  | Plug-In Power Supply, Model PB-331, Schematic Diagram                                  | 3-127           |

| 3-23A.1 | µ-BLOC and Mounting Panel Assembly                                                     | 3 <b>-</b> 132B |

| 3-23B.1 | Non-Inverting Power Amplifier PAC, Model PN-335,<br>Schematic Diagram and Logic Symbol | 3 <b>-</b> 132D |

| 3-23B.2 | Non-Inverting Power Amplifier PAC, Model PN-335,<br>Parts Location and Identification  | 3 <b>-</b> 132E |

| 3-24.1  | Power Supply, Model RP-330                                                             | 3-134           |

| 3-24.2  | Power Supply, Model RP-330, Schematic Diagram                                          | 3-135           |

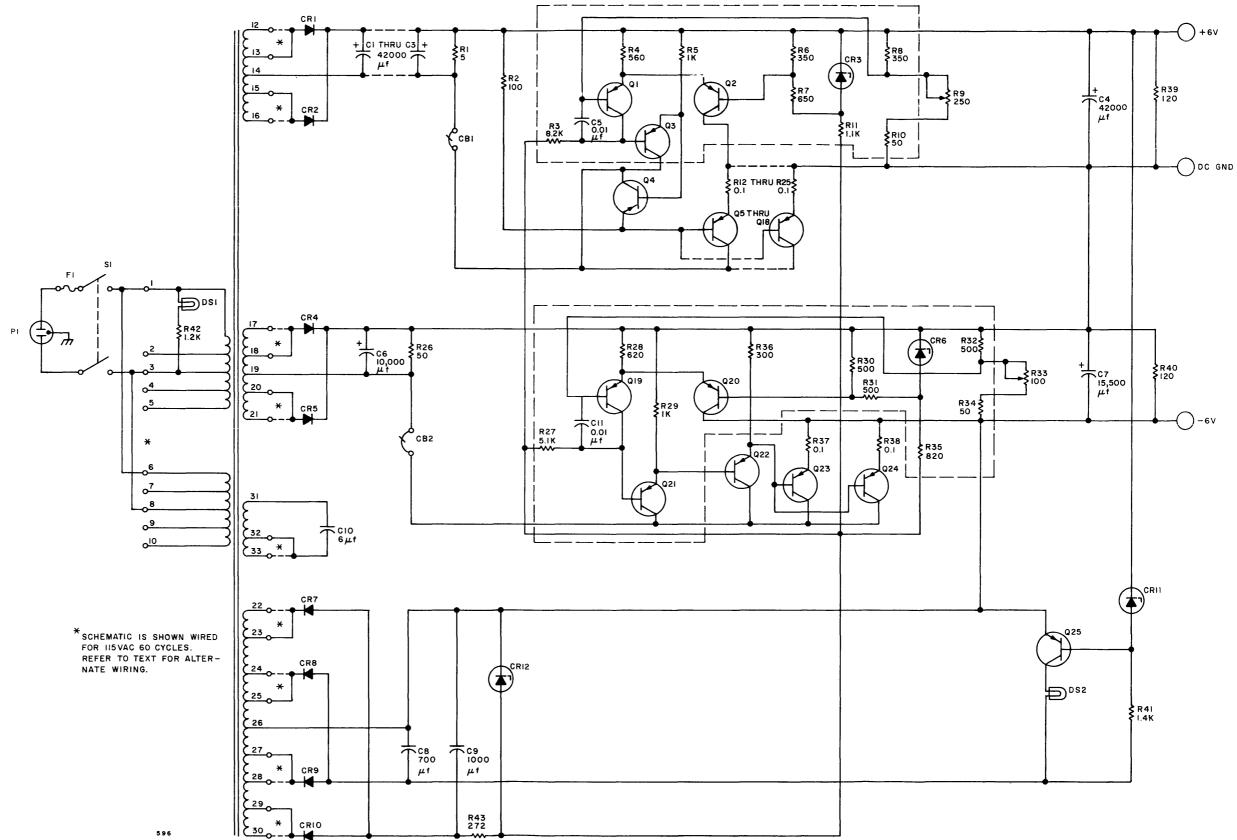

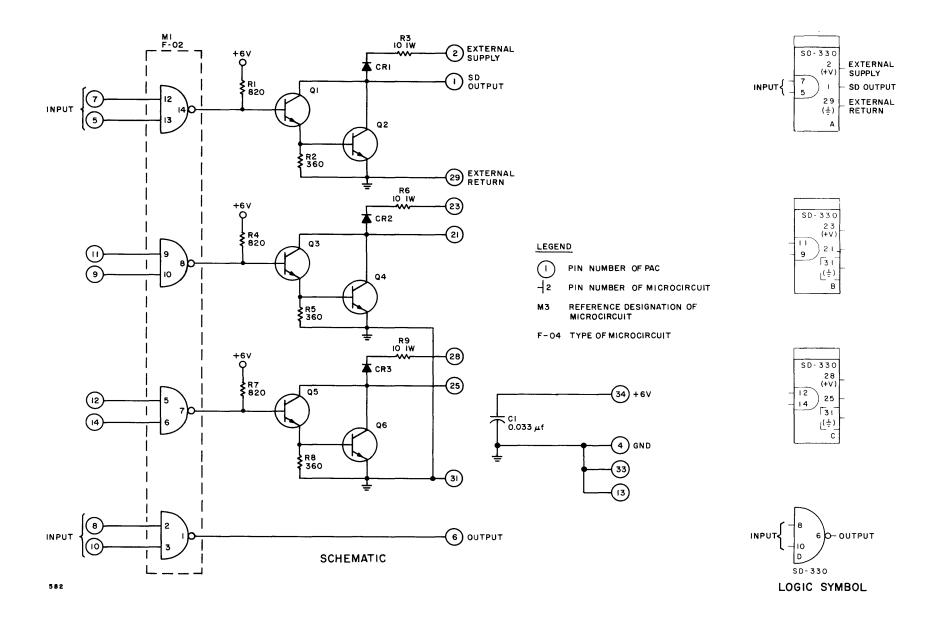

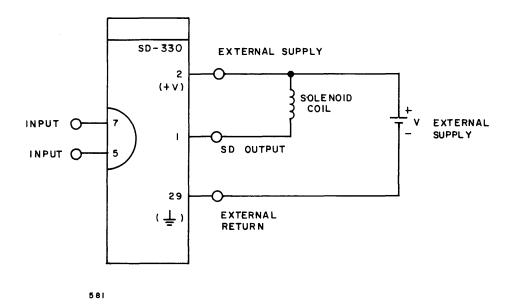

| 3-25.1  | Solenoid Driver PAC, Model SD-330, Schematic Diagram and<br>Logic Symbol               | 3-143           |

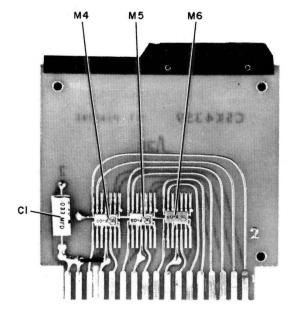

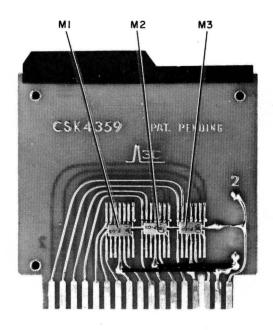

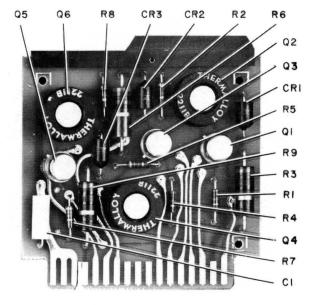

| 3-25.2  | Solenoid Driver PAC, Model SD-330, Parts Location and Identification                   | 3-144           |

| 3-25.3  | Solenoid Driver PAC, Model SD-330, Driving a Solenoid Coil                             | 3-145           |

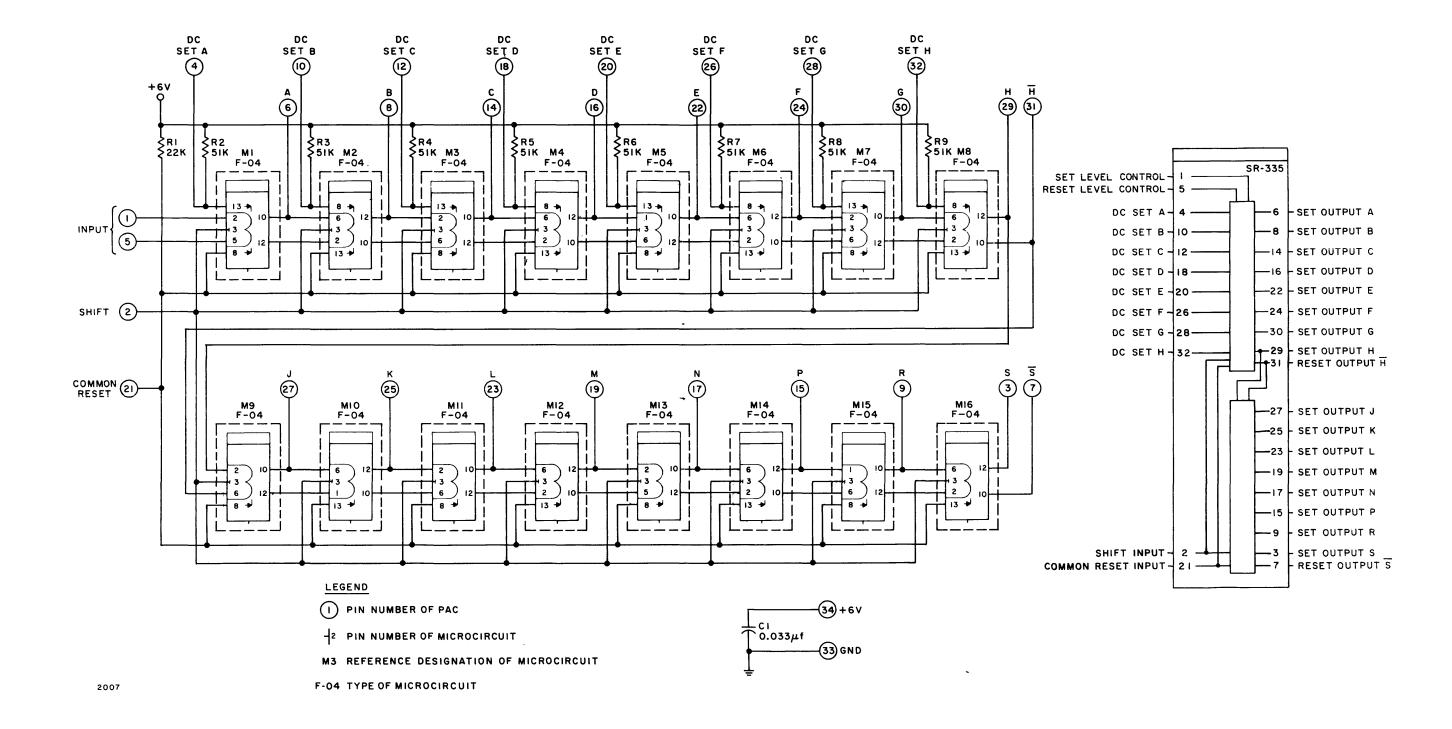

| 3-25A.1 | Shift Register PAC, Model SR-335, Schematic Diagram and Logic Symbol                   | 3 <b>-</b> 146C |

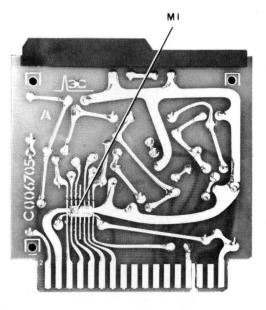

| 3-25A.2 | Shift Register PAC, Model SR-335, Parts Location and Identification                    | 3 <b>-</b> 146E |

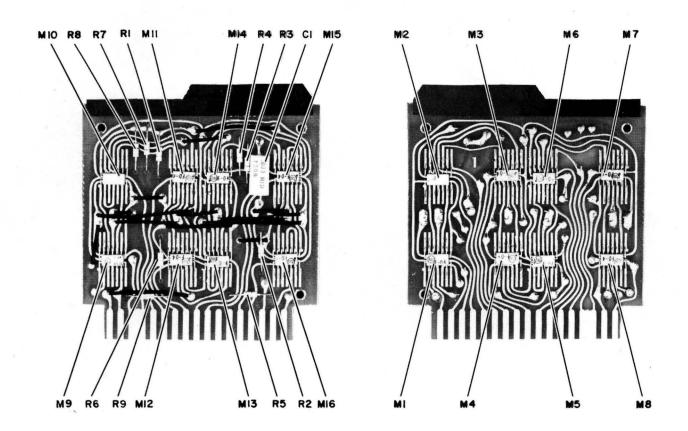

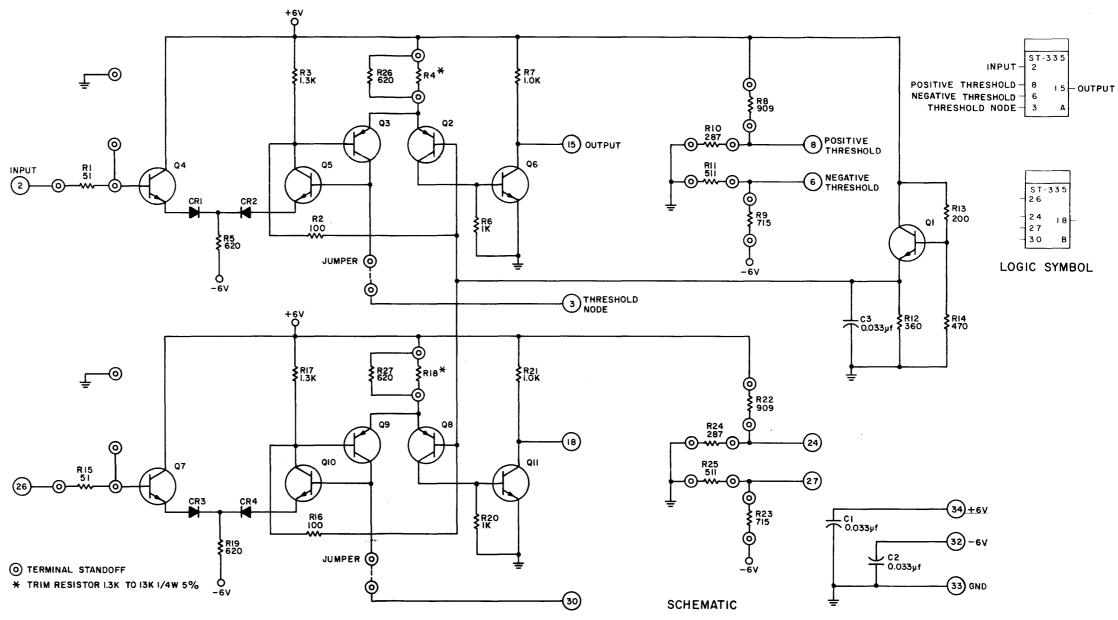

| 3-26.1  | Schmitt Trigger PAC, Model ST-335, Schematic Diagram and Logic Symbol                  | 3-149           |

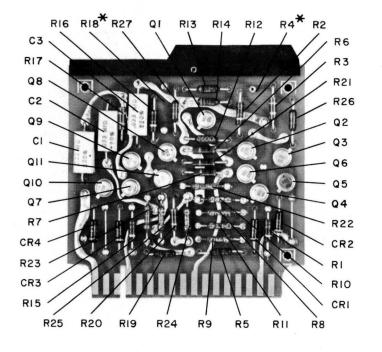

| 3-26.2  | Schmitt Trigger PAC, Model ST-335, Parts Location and<br>Identification (Sheet 1 of 2) | 3-151           |

| 3-26.2  | Schmitt Trigger PAC, Model ST-335, Parts Location and<br>Identification (Sheet 2 of 2) | 3-152           |

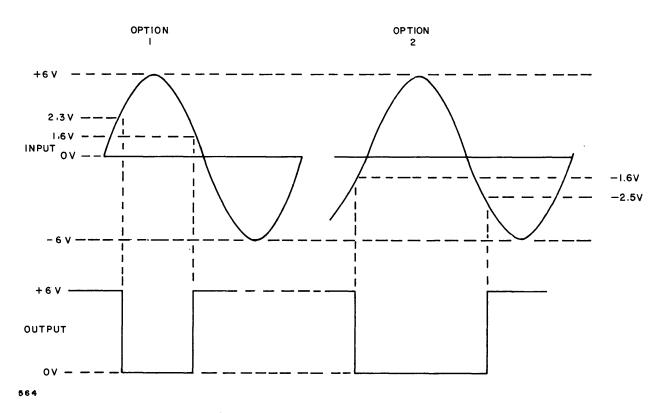

| 3-26.3  | Schmitt Trigger PAC, Model ST-335, Typical Waveforms                                   | 3 <b>-</b> 153  |

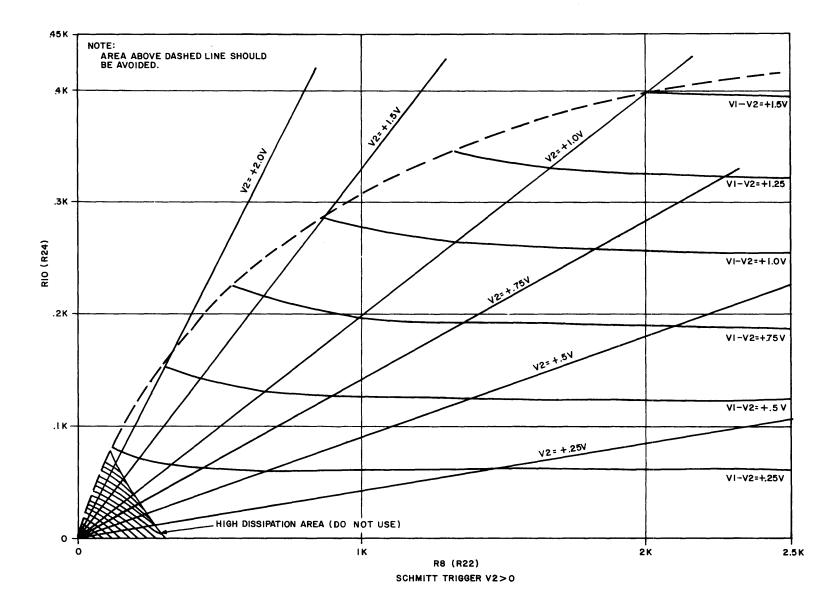

| 3-26.4  | Schmitt Trigger PAC, Model ST-335, Graph I                                             | 3-155           |

| 3-26.5  | Schmitt Trigger PAC, Model ST-335, Graph II                                            | 3-156           |

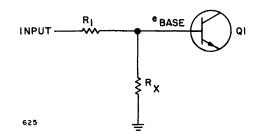

| 3-26.6  | Schmitt Trigger PAC, Model ST-335, Shifting Input Signal<br>Network                    | 3-158           |

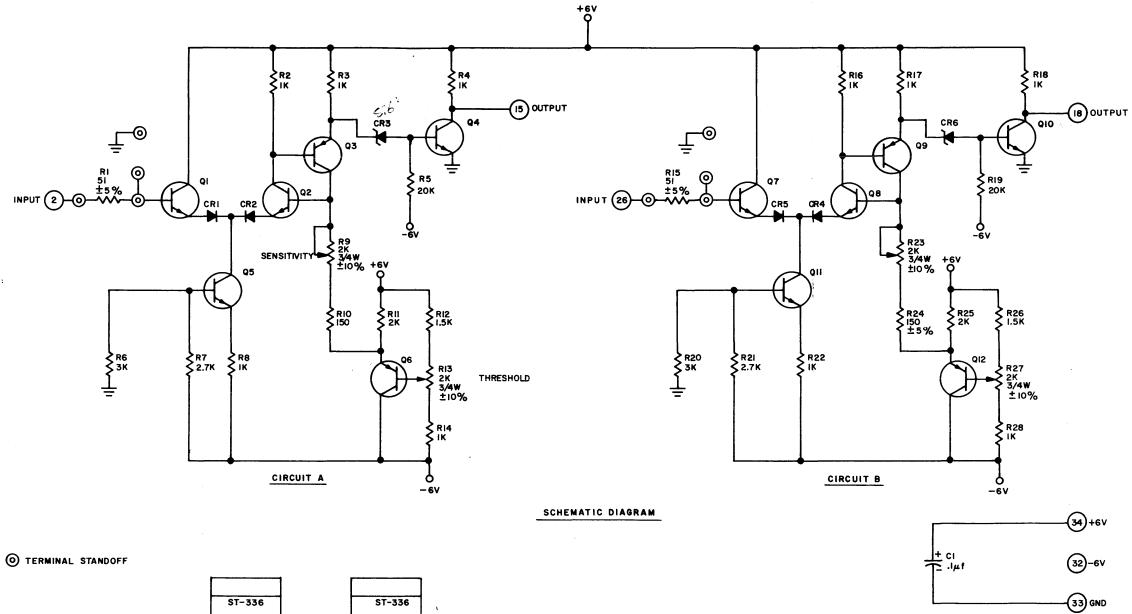

| 3-26A.1 | Adjustable Schmitt Trigger PAC, Model ST-336, Schematic<br>Diagram and Logic Symbol    | 3-158C          |

| Figure  | Title                                                                                                  | Page            |

|---------|--------------------------------------------------------------------------------------------------------|-----------------|

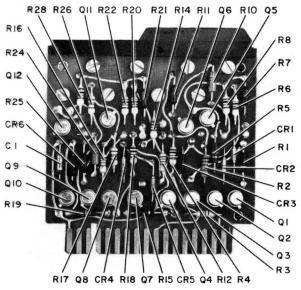

| 3-26A.2 | Adjustable Schmitt Trigger PAC, Model ST-336, Parts Location and Identification                        | 3-158E          |

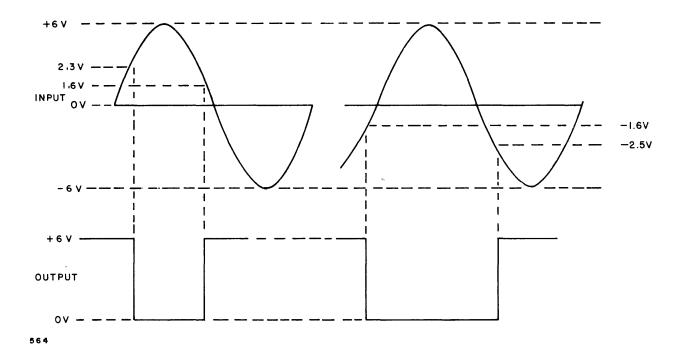

| 3-26A.3 | Adjustable Schmitt Trigger PAC, Model ST-336, Typical<br>Waveforms                                     | 3 <b>-</b> 158F |

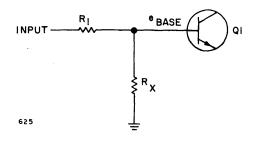

| 3-26A.4 | Adjustable Schmitt Trigger PAC, Model ST-336, Shifting Input<br>Signal Network                         | 3 <b>-</b> 158G |

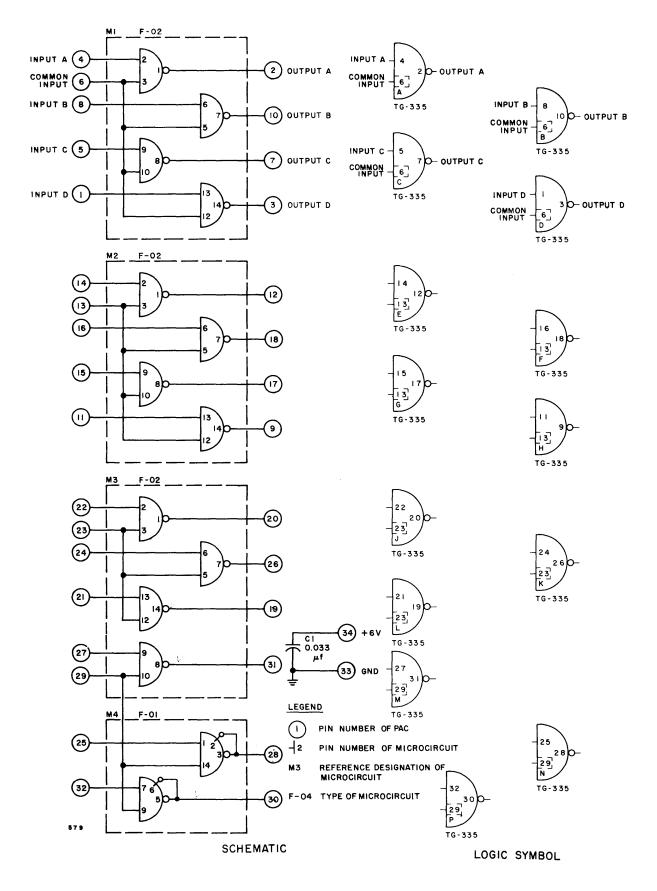

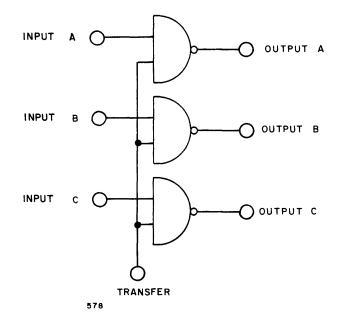

| 3-27.1  | Transfer Gate PAC, Model TG-335, Schematic Diagram and Logic Symbol                                    | 3-160           |

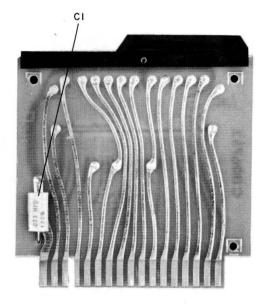

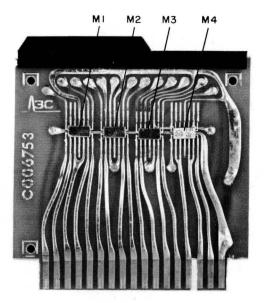

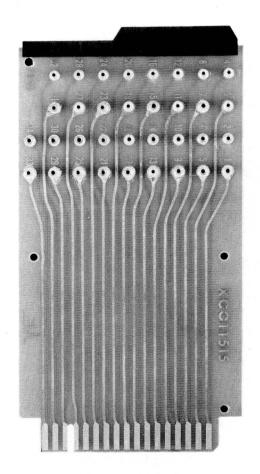

| 3-27.2  | Transfer Gate PAC, Model TG-335, Parts Location and Identification                                     | 3-161           |

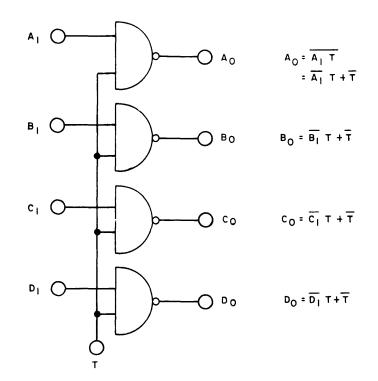

| 3-27.3  | Transfer Gate PAC, Model TG-335, Gate Structure Logic                                                  | 3-162           |

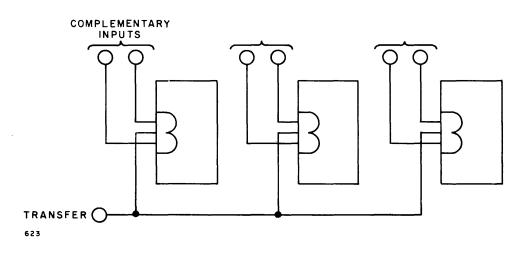

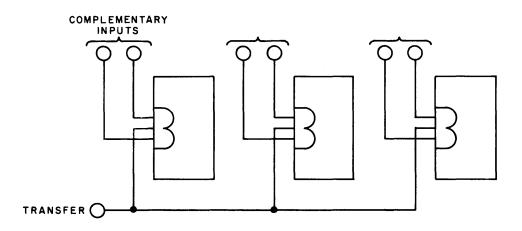

| 3-27.4  | Transfer Gate PAC, Model TG-335, Controlling Transfer of Three Signals                                 | 3-162           |

| 3-27A.1 | Test Point PAC, Model TP-330                                                                           | 3 <b>-</b> 162A |

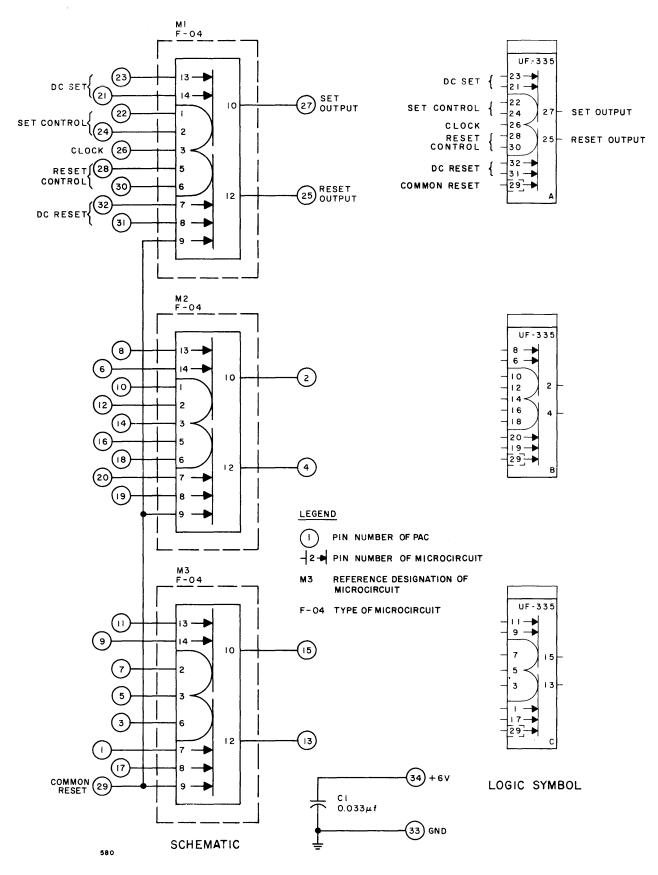

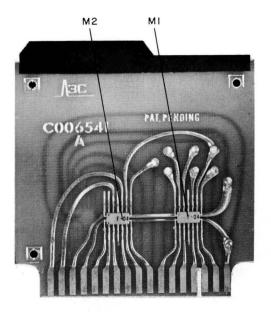

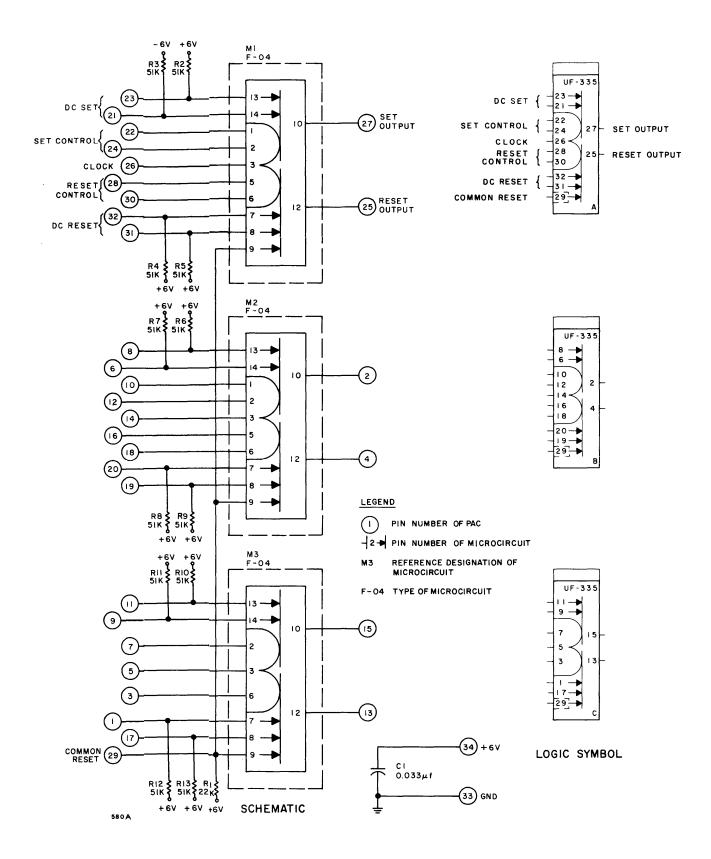

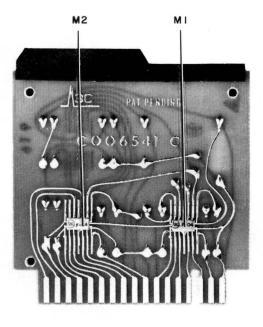

| 3-28.1  | Universal Flip-Flop PAC, Model UF-335, Schematic Diagram and Logic Symbol                              | 3-165           |

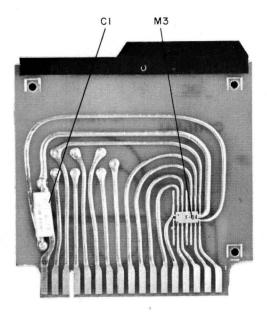

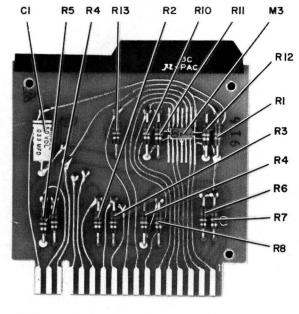

| 3-28.2  | Universal Flip-Flop PAC, Model UF-335, Parts Location and Identification                               | 3-166           |

| 3-28.1A | Universal Flip-Flop PAC, Model UF-335 (Ser. No. 825 and beyond), Schematic Diagram and Logic Symbol    | 3 <b>-</b> 166A |

| 3-28.2A | Universal Flip-Flop PAC, Model UF-335 (Ser. No. 825 and beyond), Parts Location and Identification     | 3 <b>-</b> 166C |

| 3-28.3  | Universal Flip-Flop PAC, Model UF-335, Counter Operation                                               | 3-167           |

| 3-28.4  | Universal Flip-Flop PAC, Model UF-335, Three-Stage<br>Instantaneous Carry Operation                    | 3-168           |

| 3-28.5  | Universal Flip-Flop PAC, Model UF-335, Shift Register<br>Operation                                     | 3-168           |

| 3-28.6  | Universal Flip-Flop PAC, Model UF-335, Parallel Information<br>Drop-In                                 | 3-168           |

| 3-28A.1 | Transistorized Unit Indicator, Model UI-110                                                            | 3 <b>-</b> 168B |

| 3-28B.1 | Transistorized Unit Indicator, Model UI-330                                                            | 3-168D          |

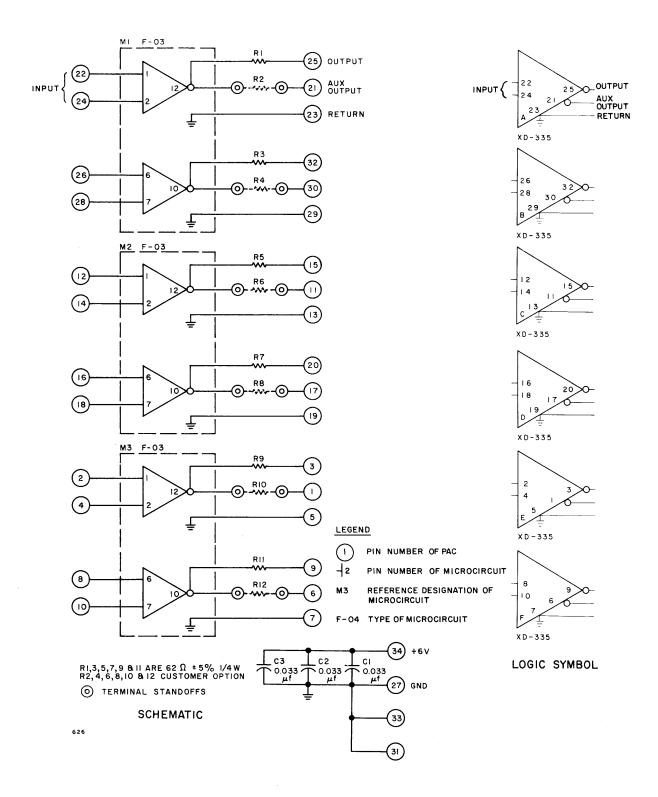

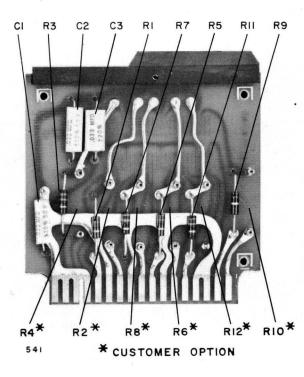

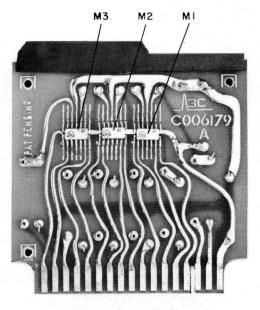

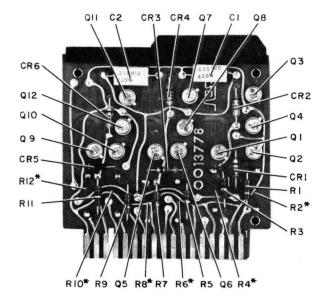

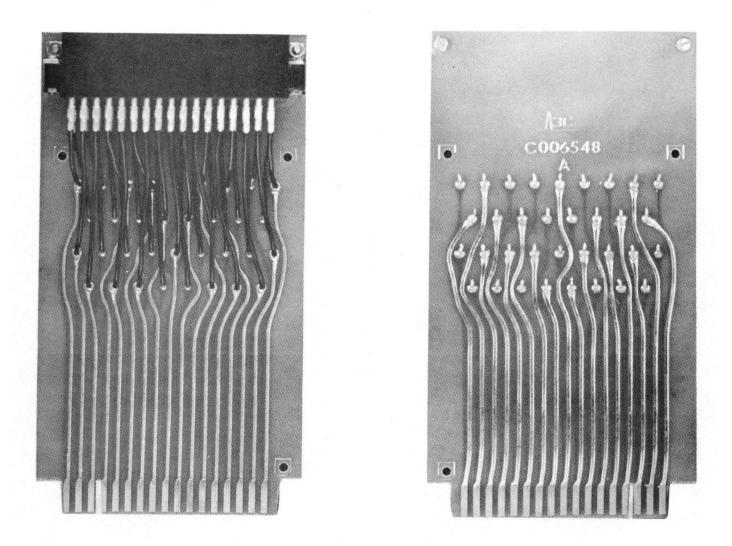

| 3-29.1  | Transmission Line Driver PAC, Model XD-335, Schematic<br>Diagram and Logic Symbol                      | 3-172           |

| 3-29.2  | Transmission Line Driver PAC, Model XD-335, Parts Location and Identification                          | 3-173           |

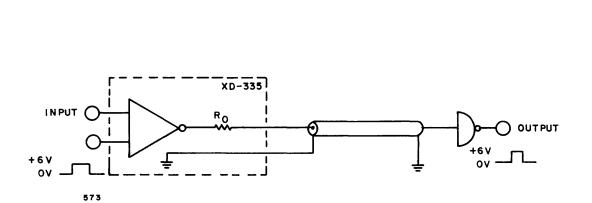

| 3-29.3  | Transmission Line Driver PAC, Model XD-335, Line Termination at the Driving End with Matched Impedance | 3-174           |

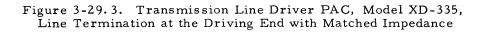

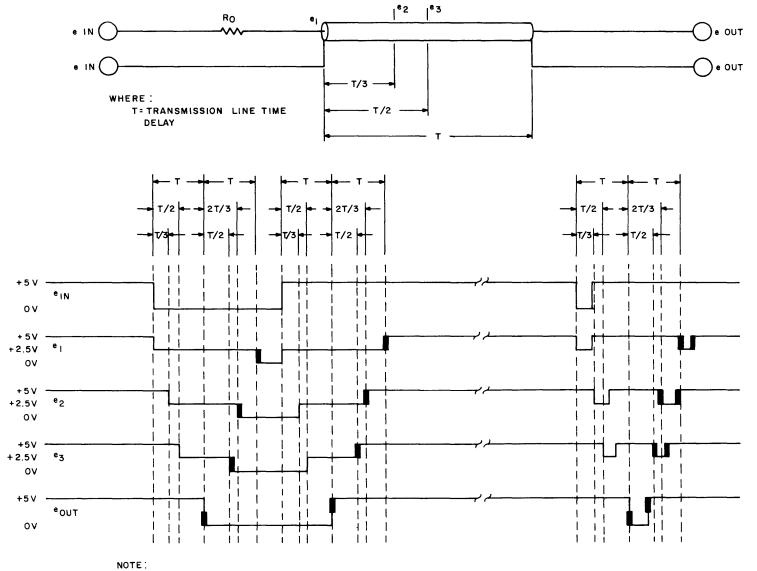

| 3-29.4  | Transmission Line Driver PAC, Model XD-335, Transmission<br>Line Waveform Characteristics              | 3-175           |

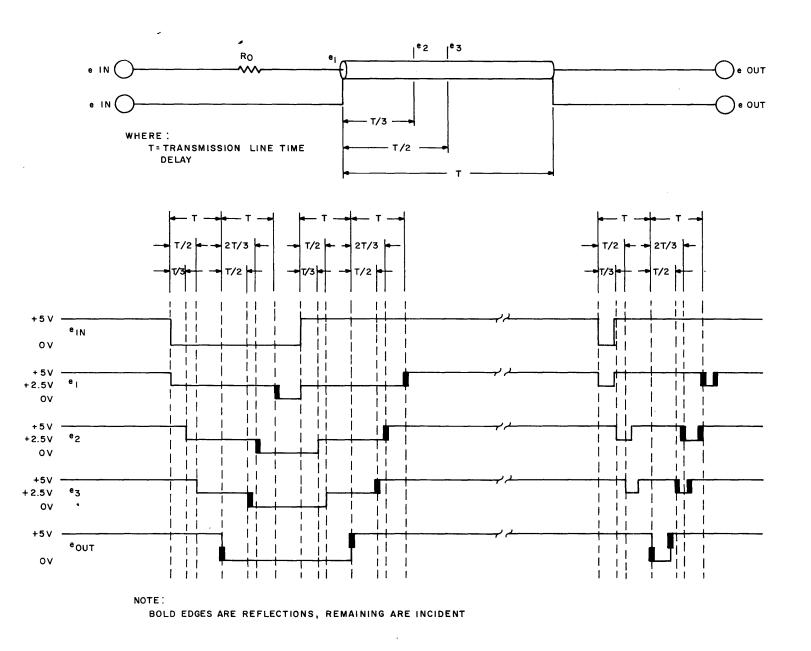

| 3-29.5  | Transmission Line Driver PAC, Model XD-335, Line<br>Terminated with Matched Impedance                  | 3-176           |

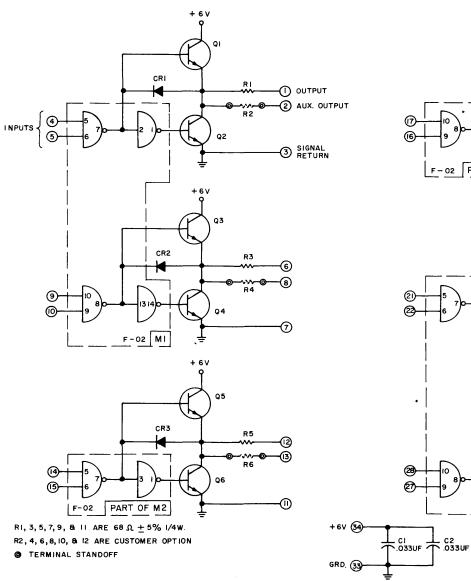

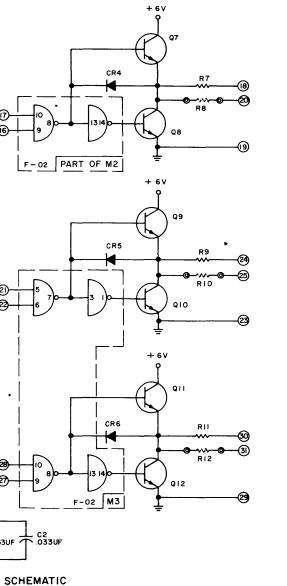

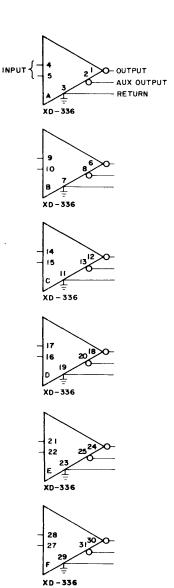

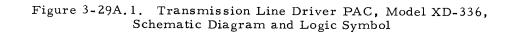

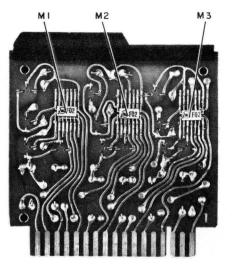

| 3-29A.1 | Transmission Line Driver PAC, Model XD-336, Schematic<br>Diagram and Logic Symbol                      | 3-176C          |

| 3-29A.2 | Transmission Line Driver, Model XD-336, Parts Location<br>and Identification                           | 3 <b>-</b> 176D |

| Figure  | Title                                                                                                     | Page            |

|---------|-----------------------------------------------------------------------------------------------------------|-----------------|

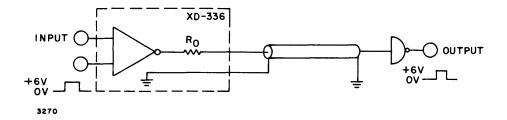

| 3-29A.3 | Transmission Line Driver PAC, Model XD-336, Line<br>Termination at the Driving End with Matched Impedance | 3 <b>-</b> 176E |

| 3-29A.4 | Transmission Line Driver PAC, Model XD-336, Transmission<br>Line Waveform Characteristics                 | 3 <b>-</b> 176F |

| 3-30.1  | Extender PAC, Model XP-330                                                                                | 3-177           |

#### LIST OF TABLES

| Table   | Title                                                                     | Page           |

|---------|---------------------------------------------------------------------------|----------------|

| 1-1     | Product Line Summary (Modules)                                            | 1-1            |

| 1 - 2   | Product Line Summary (Auxiliary Equipment)                                | 1 - 3          |

| 3-4.1   | BL-Series $\mu$ -BLOC Characteristics                                     | 3-17           |

| 3-5.1   | BM-Series $\mu$ -BLOC Characteristics                                     | 3-19           |

| 3-12.1  | Connections for Internally Provided Pulse Widths                          | 3-52           |

| 3-12A.1 | Connections for Internally Provided Pulse Widths (DM-335)                 | 3 <b>-</b> 58B |

| 3-12.1A | Connections for Internally Provided Pulse Widths (DM-336)                 | 3 <b>-</b> 58M |

| 3-17.1  | Jumper Lead Set                                                           | 3-81           |

| 3-17A.1 | Logic Truth Table                                                         | 3 <b>-</b> 82A |

| 3-17A.2 | Voltage Truth Table                                                       | 3 <b>-</b> 82A |

| 3-18.1  | Truth Table                                                               | 3-83           |

| 3-19.1  | Pulse Widths with Replacement Capacitors (MC-335)                         | 3-89           |

| 3-20.1  | Frequency Ranges with Replacement Capacitors                              | 3-105          |

| 3-20.2  | Pulse Widths with Replacement Capacitors (MV-335)                         | 3-105          |

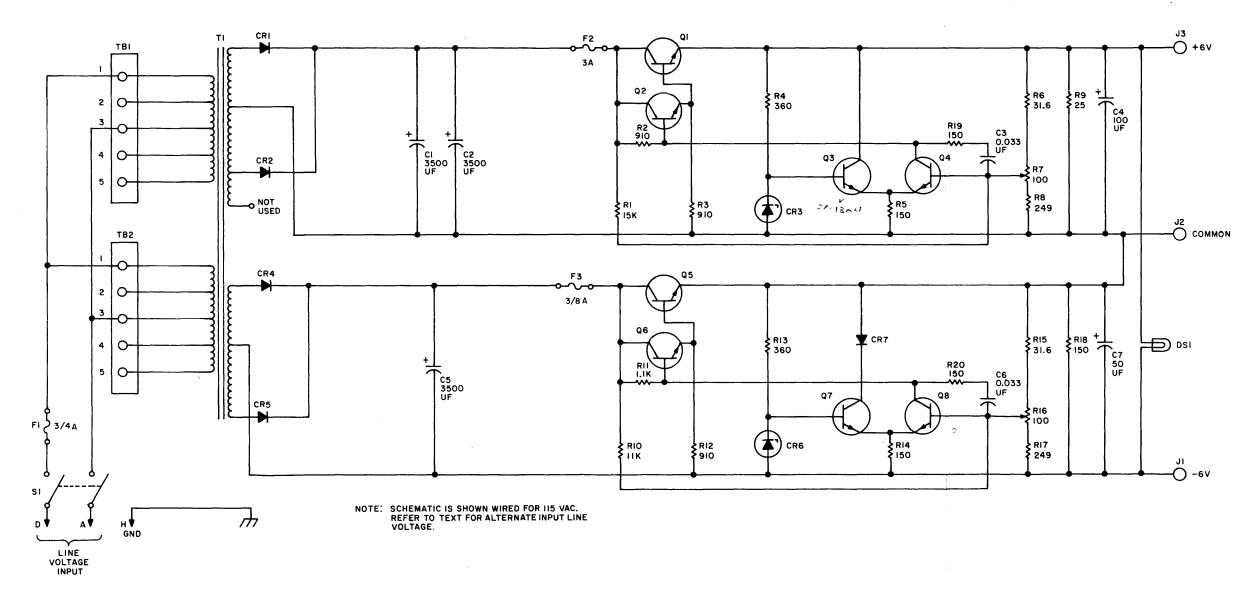

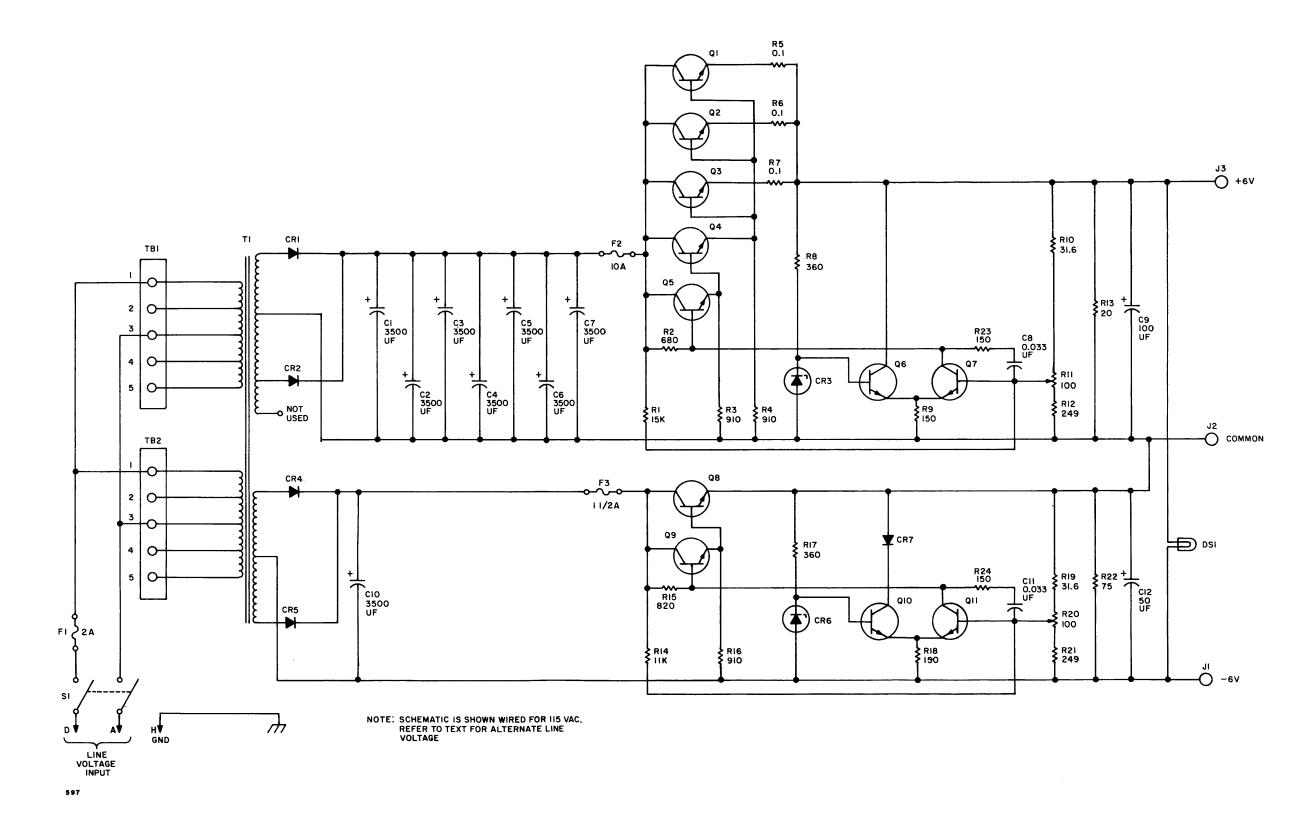

| 3-23.1  | Transformer Primary Connections for Different Input Voltages              | 3-121          |

| 3-23.2  | Plug-In Power Supply, Model PB-330, Parts List                            | 3-129          |

| 3-23.3  | Plug-In Power Supply, Model PB-331, Parts List                            | 3-131          |

| 3-24.1  | Transformer Primary Connections for Alternate Input Voltage and Frequency | 3-134          |

| 3-24.2  | Transformer Secondary Connections for Alternate Frequency                 | 3-134          |

| 3-24.3  | Power Supply, Model RP-330, Parts List                                    | 3-137          |

| 3-25.1  | Truth Table                                                               | 3-142          |

| 3-26.1  | Typical Input Variations                                                  | 3-153          |

#### PREFACE

#### MANUAL REVISION

To ensure continued usefulness of this manual, each revised page of technical material (text, schematic, photo assembly, and parts list) is identified with the date of revision. A revision bar is also provided to facilitate the location of the change. Undated pages are unchanged pages of the original issue (8/1/65).

#### COMPONENT REPLACEMENT

Some components supplied in the equipment have slightly different specifications than more readily available commercial equivalents. All parts manufactured by or specifically for Computer Control should be ordered directly from Computer Control. These parts are assigned a 3C 9-digit part number only. In cases where the supplied components are interchangeable, the type numbers of the commercial equivalents are listed in the parts list.

#### SECTION I INTRODUCTION

#### 1-1 SCOPE

This instruction manual provides complete descriptive and reference material for the  $\mu$ -PAC digital modules and auxiliary equipment of Computer Control. The manual is divided into three sections. Section I contains a general description of the equipment, capabilities and design of the module line. Section II contains the product line specification and detailed descriptions of the basic logic circuits. Section III contains specific information on each  $\mu$ -PAC product, including specifications and applications data.

#### 1-2 μ-PAC PRODUCT LINE

$\mu$ -PAC is a complete product line of logic modules (PACs), mounting assemblies (BLOCs), power supplies, and other supporting equipment that together provide a complete capability for the design and fabrication of computers and data processing systems. A list of the products appears in Tables 1-1 and 1-2.

While incorporating the reliability and economic advantages of integrated circuits, the  $\mu$ -PAC product line retains the versatile logic flexibility of S-PAC, a product line of Computer Control that has received wide customer acceptance.

The  $\mu$ -PACs are compact, functionally efficient modules using standard types of integrated circuits interconnected on an etched board. This approach simplifies design and allows more logic to be included on each PAC. Some special-purpose PACs of moderate or low usage are hybrid in construction, being composed of integrated circuits and discrete components. All PACs use static logic, and in general have an operating frequency range between dc and 5 mc.

| Functional Type<br>and Color Code    | Model No. | PAC Type         | Contents                                                                           |

|--------------------------------------|-----------|------------------|------------------------------------------------------------------------------------|

|                                      | DC-335    | Multi-Input NAND | Four 3-input diode clusters;<br>Two 6-input NAND gates with<br>nodes               |

| PACs with Independent<br>Gates (Red) | DI-335    | NAND type 1      | Eight 2-input NAND gates;<br>Two 2-input NAND gates with<br>separate load circuits |

|                                      | DL-335    | NAND type 2      | Four 4-input NAND gates;<br>Two 4-input NAND gates with<br>separate load circuits  |

Table 1-1. Product Line Summary (Modules)

1 - 1

Table 1-1. (Cont) Product Line Summary (Modules)

| Functional Type<br>and Color Code           | Model No.       | РАС Туре                         | Contents                                                                                                                                |

|---------------------------------------------|-----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PACs with Independent<br>Gates (Cont) (Red) | DN-335          | Expandable NAND                  | Four 3-input NAND gates with<br>nodes;<br>Two 3-input NAND gates with<br>nodes and separate load<br>circuits                            |

|                                             | BC-335          | Counter                          | Six flip-flops for binary counting or complementing operations                                                                          |

|                                             | BR-335          | Buffer register                  | Six flip-flops with prewired<br>common clock and common<br>reset                                                                        |

| PACs with Independent<br>Flip-Flops (Blue)  | FA-335          | Gated flip-flop                  | Four flip-flops with independent<br>dc, clock and control inputs.<br>A prewired common reset is<br>also provided                        |

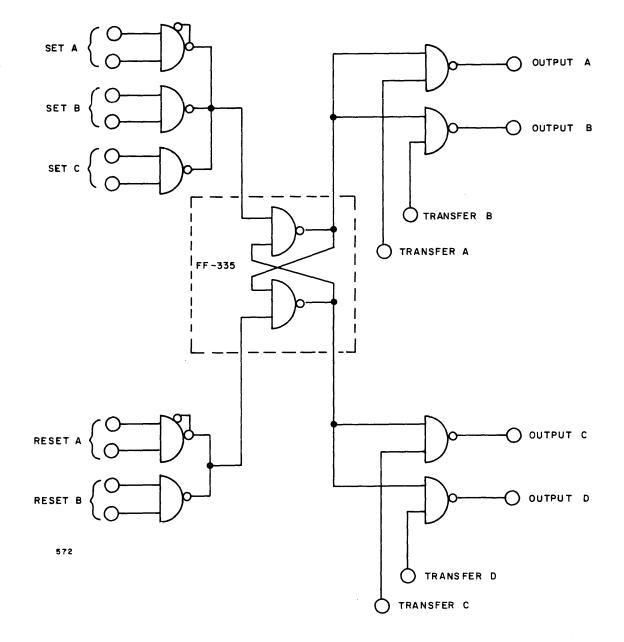

|                                             | FF-335          | Basic flip-flop                  | Eight flip-flops with dc input gating                                                                                                   |

|                                             | FF-335          | Basic flip-flop                  | Eight flip-flops with dc input gating                                                                                                   |

|                                             | SR-335          | Shift register                   | Eight to 16-bit shift register                                                                                                          |

|                                             | UF-335          | Universal flip-flop              | Three flip-flops with multiple clocked and dc inputs                                                                                    |

|                                             | DG <b>-</b> 335 | Selection gate<br>type l         | Four selection gate structures<br>each having three 2-input<br>selection gates                                                          |

|                                             | DG-336          | Selection gate<br>type 2         | Two selection gate structures.<br>One has four 3-input gates;<br>the other has four 4-input<br>selection gates                          |

| Functional<br>Gating PACs<br>(Purple)       | EO-335          | Exclusive OR                     | Five exclusive OR gate struc-<br>tures and a single-input<br>NAND circuit                                                               |

|                                             | OD-335          | Octal/Decimal<br>decoder         | One prewired binary-to-octal<br>decoder plus two independent<br>NAND gates for expanding the<br>matrix for BCD-to-decimal<br>conversion |

|                                             | TG <b>-</b> 335 | Transfer gate                    | Four transfer gate structures<br>each having a common input                                                                             |

| Functional Flip-Flop<br>PACs (Blue)         | BC-336          | Binary counter                   | Eight to 20 flip-flops prewired for binary counting                                                                                     |

|                                             | BC-337          | Fast carry counter               | Eight flip-flops for BCD or binary counting                                                                                             |

| Power Amplifier PACs<br>(Green)             | PA-335          | Power amplifier                  | Six 3-input inverting<br>amplifiers                                                                                                     |

|                                             | PN-335          | Non-inverting<br>power amplifier | Six 3-input non-inverting<br>power amplifiers                                                                                           |

| Delay Multivibrator<br>PAC (Yellow)         | DM-335          | Delay<br>multivibrator           | Two monostable multivibrators<br>with step-adjustable pulse<br>widths                                                                   |

|

| Functional Type<br>and Color Code          | Model No. | PAC Type                          | Contents                                                                                                                        |

|--------------------------------------------|-----------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Delay Multivibrator<br>PAC (Yellow) (Cont) | DM-336    | Adjustable delay<br>multivibrator | Two monostable multivibrators<br>with continuously adjustable<br>pulse width                                                    |

| Clock PACs<br>(Yellow)                     | MC-335    | Master clock                      | One crystal-controlled clock<br>with variable pulse shaper<br>output                                                            |

|                                            | MV-335    | Multivibrator<br>clock            | One free-running multivibrator<br>with adjustable frequency and<br>pulse widths and also synchro-<br>nous start/stop capability |

|                                            | DD-330    | Display driver                    | BCD-to-decimal converter,<br>10 lamp-driver circuits                                                                            |

|                                            | LC-335    | Negative logic<br>level converter | Ten converter circuits                                                                                                          |

|                                            | LD-330    | Lamp driver                       | Twelve lamp driver circuits                                                                                                     |

| Input/Output PACs<br>(Orange)              | LD-331    | High-drive lamp<br>driver         | Eight lamp driver circuits                                                                                                      |

|                                            | LD-335    | Negative logic<br>level driver    | Eight converter circuits                                                                                                        |

|                                            | SD-330    | Solenoid driver                   | Three 2-input solenoid driver<br>circuits plus an additional<br>gate                                                            |

|                                            | ST335     | Schmitt trigger                   | Two Schmitt trigger circuits                                                                                                    |

|                                            | ST-336    | Adjustable Schmitt<br>trigger     | Two Schmitt trigger circuits<br>with adjustable threshold and<br>sensitivity                                                    |

|                                            | XD-335    | Transmission line<br>driver       | Six 2-input transmission line<br>drivers                                                                                        |

|                                            | XD-336    | Transmission line<br>driver       | Six 2-input transmission line<br>drivers                                                                                        |

|                                            | AS-330    | Copper clad PAC<br>kit            | Unetched card with separate handle                                                                                              |

|                                            | BP-330    | Blank PAC                         | Blank PAC with etched power lines                                                                                               |

| Special Purpose<br>PACs (Black)            | TP-330    | Test Point PAC                    | For access to μ-BLOC con-<br>nector pins from μ-PAC side                                                                        |

|                                            | XP-330    | Extender PAC                      | Used for access to $\mu$ -PAC in operation                                                                                      |

Table 1-1. (Cont) Product Line Summary (Modules)

| General Type            | Model No. | Description                                                                                                                      |                     |                                |

|-------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------|

| Power Supplies          | PB-330    | Regulated supply rated for 2.5 amp at +6v and<br>0.25 amp at -6v<br>Regulated supply rated for 10 amp at +6v and 1 amp<br>at -6v |                     |                                |

|                         | PB-331    |                                                                                                                                  |                     |                                |

|                         | RP-330    | Regulated supply rated for 25 amp at +6v and 2.5 amp at -6v                                                                      |                     | at +6v and                     |

|                         |           | Connector Type                                                                                                                   | $\mu$ -PAC Capacity | Provisions for<br>Power Supply |

|                         | BL-330    | Solderless wrap                                                                                                                  | 96                  | PB-331                         |

| BLOCs                   | BL-331    | Taper pin                                                                                                                        | 48                  | PB-331                         |

|                         | BL-332    | Solderless wrap                                                                                                                  | 144                 | None                           |

|                         | BL-333    | Taper pin                                                                                                                        | 72                  | None                           |

|                         | BM-330    | Solderless wrap                                                                                                                  | 24                  | PB-330                         |

|                         | BM-335    | Taper pin                                                                                                                        | 24                  | PB-330                         |

|                         | BM-337    | Taper pin                                                                                                                        | 36                  | None                           |

| Indicators              | UI-110    | Transistorized unit indicator                                                                                                    |                     |                                |

|                         | UI-330    | Transistorized unit indicator                                                                                                    |                     |                                |

| PM-3<br>Mounting panels |           | Mounting panel for use with BM-335 and BM-337<br>BLOCs                                                                           |                     |                                |

| mounting pariers        | PM-331    | Mounting panel for use with BM-330 $\mu$ -BLOC                                                                                   |                     |                                |

| Jumper lead set         | JT-330    | Assorted taper pin jumper leads                                                                                                  |                     |                                |

Table 1-2. Product Line Summary (Auxiliary Equipment)

.....

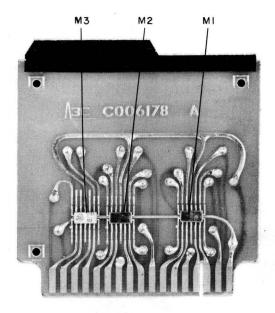

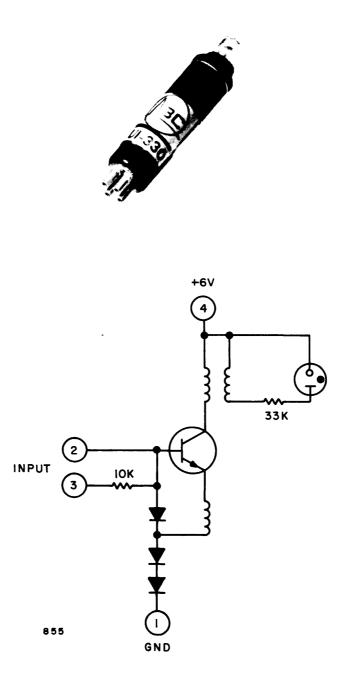

#### 1-3 MICROCIRCUITS

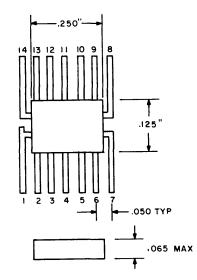

The monolithic integrated circuits are packaged in standard 14-lead 1/8 in. by 1/4 in. flat packs. (See Figure 1-1.) Up to 22 flat packs can be soldered to the etched wiring of a single  $\mu$ -PAC card for high-density logic. Resistance soldering methods enable simple replacement of components. Production techniques proven by major integrated circuit manufacturers and Computer Control Company's own facility guarantee quality control and environmental stability consistent with military standards. At present the  $\mu$ -PAC line employs four standard microcircuit types:

- a. F-01, dual NAND gate, two 3-input gates with input nodes

- b. F-02, quad NAND gate, four 2-input gates

- c. F-03, power amplifier, two 3-input power gates

- d. F-04, flip-flop, one J-K flip-flop

Detailed microcircuit descriptions appear in Section II.

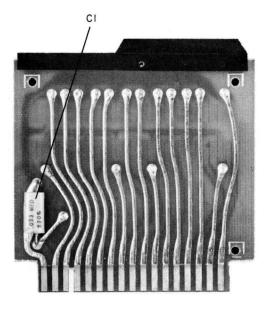

Figure 1-1. Dimensions of Standard Microcircuit

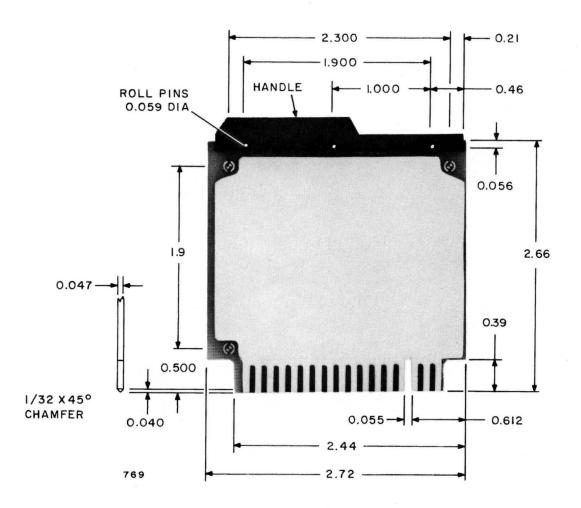

l-4 μ-PAC MODULES

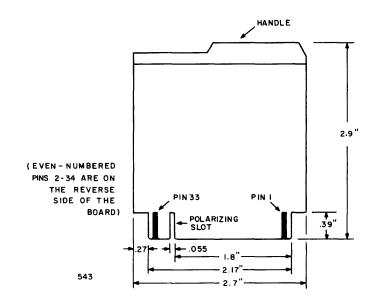

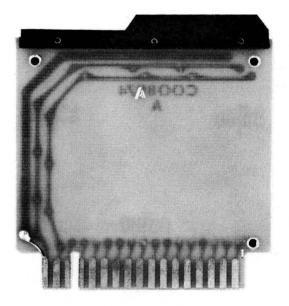

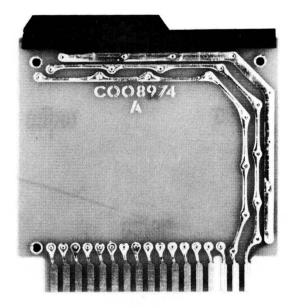

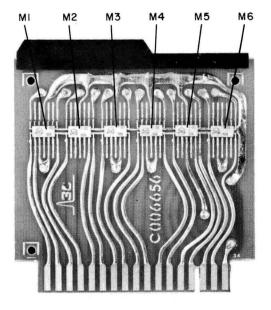

The  $\mu$ -PAC modules contain integrated circuit assemblies and some discrete hybrid combinations mounted on glass-impregnated epoxy cards with 1-ounce copper-clad printed circuits. Dimensions are shown in Figure 1-2. The PAC type is clearly indicated on the molded nylon handle by model number. Color coding on the handle indicates functional type (see Table 1-1). All PACs feature gold-plated etched fingers to guarantee reliable electrical contact with a 34-pin polarized connector.

#### 1-5 AUXILIARY EQUIPMENT

#### 1-5.1 µBLOCs

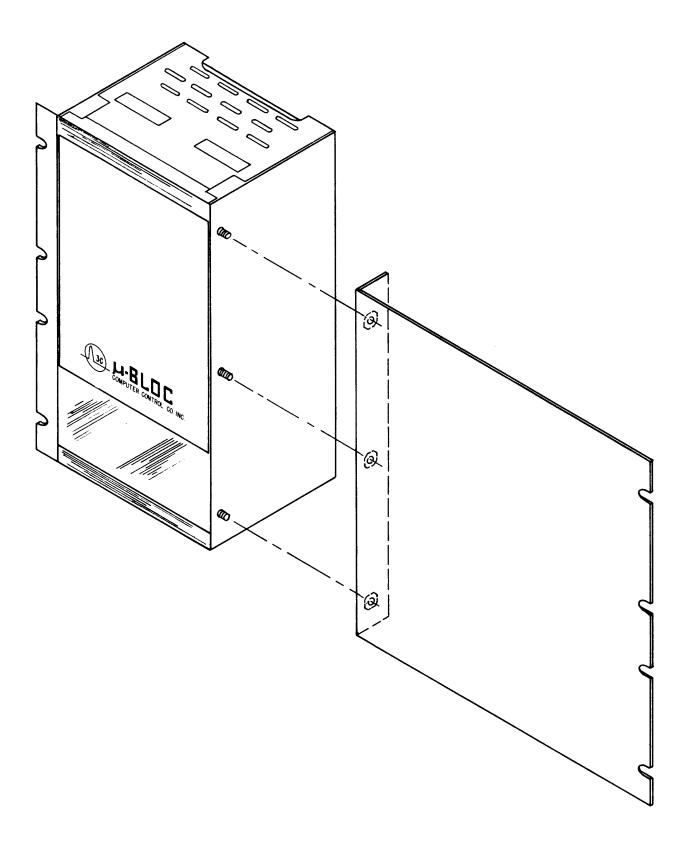

Several types of  $\mu$ -BLOCs are available for  $\mu$ -PAC installation flexibility. All models use the same basic structure, but differ in dimensions, number of  $\mu$ -PAC connectors, power supply provisions, and the use of taper-pin or solderless-wrap connectors.

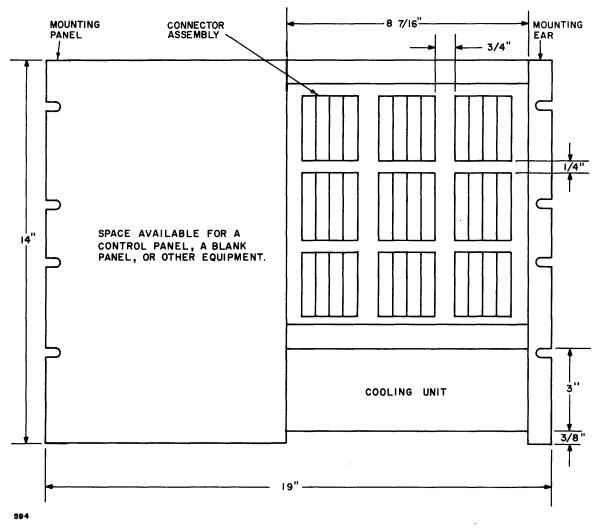

The BL-series is directly mountable in standard 19-inch rack panels. BM-335 and BM-337 BLOCs can be adapted to mount in a 19-inch rack by using a mounting panel. If desired, this panel can then be used as a control panel. The BM-335 and BM-337 BLOCs can also be coupled for side-by-side mounting in a 19-inch rack.

Figure 1-2. Dimensions of a Standard  $\mu$ -PAC

Solderless-wrap or taper-pin connectors are mounted in BLOCs with ground and power prewired. The connector plane is easily removable for convenient wiring.

Mounting ears are detachable and allow front or back mounting of the connector plane.

Built-in cooling units are contained in each BLOC. When two BL-series BLOCs are used together, the fans can be utilized in a push-pull manner.

#### 1-5.2 Power Supplies

Plug-in Power Supplies, Models PB-330 and PB-331, are integrally packaged units that can be mounted directly into BLOCs. PB-330 mounts in BM BLOCs; PB-331 mounts into BL BLOCs. They supply current at both  $\mu$ -PAC voltage levels, +6v and -6v, and are designed to drive all modules contained in their respective BLOCs. By making the necessary internal connections, these supplies can accommodate input voltages of 115 or 220v ac at standard input frequencies of 50, 60 and 400 cps.

Front panels include the following features: on/off switch, power on indicator, three fuses, and voltage adjustment potentiometers.

#### 1-5.3 Jumper Lead Set

Jumper Lead Set, Model JT-330, provides an assortment of taper-pin connectors in a variety of lead lengths and colors for system wiring of taper pin  $\mu$ -BLOCs.

#### 1-5.4 Logic Symbol Stickers

To aid in the use of  $\mu$ -PACs, individual sheets of logic symbol stickers are available for all PAC types. The stickers are printed on precut sections of transparent mylar for direct application to a reproducible drawing base. The stickers simplify system logic design and generation of wire lists, and minimize drafting requirements for final engineering drawings. The logic symbol, pin numbers, and logic function are printed directly on each sticker. In addition, space is provided for designating the physical location of the PAC in the  $\mu$ -BLOC.

#### 1-5.5 Accessories

$\mu\text{-}PAC$  accessories include the Model XP-330 Extender PAC, automatic wire-wrap kits, wire-wrap and taper-pin wiring tools, and a module extractor.

#### 1-6 PRODUCT LINE FEATURES

The integrated circuit designs were developed at Computer Control Company to meet the specific needs of a versatile 5-megacycle product line. Emphasis in design was on reliable systems operation and on efficient interconnection of logic functions. Types of logic circuits suitable for fabrication in monolithic form were investigated; certain types, including resistance-coupled transistors, transistor-coupled transistors, diode-coupled emitter followers, and transistor-coupled emitter followers, operated in very high speed systems but at a sacrifice in ease of logical or electrical interconnection. Their stability in a noisy system environment often proved to be marginal. These factors led to the selection of DTL, or diode gating followed by an inverting saturated transistor, as the basic  $\mu$ -PAC gating element. DTL logic combines a high immunity to noise with an operating speed in excess of 5 mc. On critical inputs, such as clock inputs to the flip-flop,  $\mu$ -PAC noise thresholds compare favorably with discrete component circuitry. Other inherent features of DTL, such as input gate expansion and output cascading, have been exploited in the design.

Several features not normally available in integrated circuit products have been included. Power amplifiers employ a technique for switching to an idling mode when the output is short-circuited. The unique flip-flop circuit has negligible set-up time, low dc input loading, low transient input loading, a short clock pulse-width requirement, J-K and R-S operation, dc control independent of clock input level, and a highly versatile input gating structure.

#### $\mu$ -PAC DIGITAL MODULES

Design and specification of the equipment are conservative. For example, the flipflop will toggle at rates greater than 10 mc under moderate loading conditions, but this capability is not logically useful except in limited applications. At the specified frequency limit of 5 mc, data can be transferred from one register to another through three gates (up to five or six logic functions) in one clock period. Additionally, all applicable circuitry has been laboratory-tested under full load over the temperature range at frequencies up to 8 mc.

#### SECTION II PRODUCT LINE SPECIFICATIONS AND MICROCIRCUIT CHARACTERISTICS

#### 2-1 INTRODUCTION

This section contains general specifications for the  $\mu$ -PAC digital module line and detailed technical data on the four basic integrated circuit types used throughout the product line for digital logic functions. The detailed descriptions of each module type, in Section III of this manual, make reference to these general specifications.

#### 2-2 GENERAL µ-PAC SPECIFICATIONS

All performance specifications listed below are guaranteed minimums based on worst-case tolerances. Actual performance will invariably exceed these guaranteed minimums. The following specifications apply to all  $\mu$ -PAC types. Any exceptions are listed in the individual specifications.

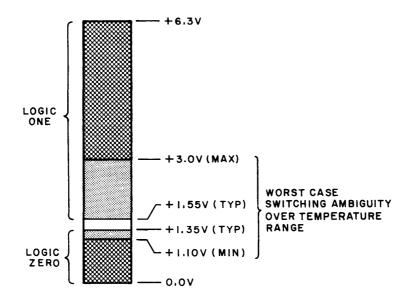

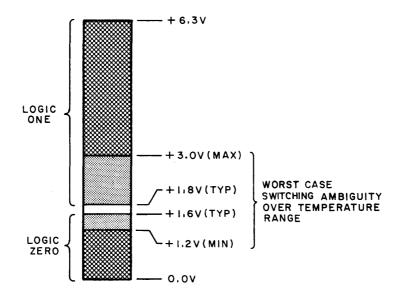

#### 2-2.1 Input Switching Thresholds (Refer to Figure 2-1.)

# a. NAND gate and flip-flop dc inputs ZERO level: +1.lv (min), +1.35v (typ) ONE level: +3.0v (max), +1.55v (typ)

- b. Power Amplifier and flip-flop clock and control inputs

ZERO level: +1.2v (min), +1.6v (typ)

ONE level: +3.0v (max), +1.8v (typ)

- 2-2.2 Output Logic Levels (Guaranteed for all circuit types)

Logic ONE: +4.0v (min) to +6.3v (max) Logic ZERO: 0v to +0.35v (max)

When referring to the outputs of circuits, the terms "set" and "reset" denote level outputs and "assertion" and "negation" denote pulse outputs. Flip-flops produce level outputs; one-shots and clocks produce pulse outputs.

## 2-2.3 Frequency Range (DC to 5 MC)

One common way of describing the speed of a digital circuit is to state the highest frequency square or rectangular wave that can be applied to the input of a circuit and still reliably produce a specified output. Applied to a flip-flop, this method specifies the highest toggling or complementing rate possible; and for a gate, an input discrimination capability dependent on its circuit delay. Of course, these circuits would be driving light loads. Such

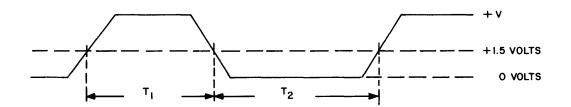

b. POWER AMPLIFIER AND FLIP-FLOP CLOCK AND CONTROL INPUTS

Figure 2-1. Switching Thresholds

an approach is often misleading and unusable for the systems designer. When many of the same types of circuits are used in a system, the system capability or operating frequency depends on accumulated circuit delays. There must also be a reasonable fanout from any logic circuit; otherwise extra circuits would be needed in parallel or series in order to drive a moderate amount of logic. Rise and fall times of individual circuits are primarily meaningful only to the extent that they affect circuit delay.

An alternate measure of the efficiency of a system is the number of stages or levels of logic through which a signal can pass during a clock period. Computer Control Company, Inc. has chosen to specify the  $\mu$ -PAC digital circuit line from this standpoint of system operating frequency. The standard flip-flop can actually toggle at 10 mc, but is specified as having an operating frequency of 5 mc. The flip-flop requires only 40 nsec set up time before triggering. At a 5 mc clock rate, 160 nsec is available for going through logic, enough time for the initial clocked flip-flop delay plus three gate delays. All logic circuits in the chain have a fanout of eight at this frequency.

## 2-2.4 Temperature Range

| Operating ambient (System): | 0°C   | to | +55°C  |

|-----------------------------|-------|----|--------|

| Storage:                    | -65°C | to | +150°C |

#### 2-2.5 Power Supplies

| a. | Positive | voltage |

|----|----------|---------|

|----|----------|---------|

| Nominal:                 | +6.0v            |

|--------------------------|------------------|

| Operating range:         | +5.1v to $+6.3v$ |

| Absolute maximum rating: | +8.0v            |

| raung.                   |                  |

b. Negative voltage (used on hybrid modules only)

| Nominal:                 | -6.0v          |

|--------------------------|----------------|

| Operating range          | -5.7v to -6.3v |

| Absolute maximum rating: | -8.0v          |

Absolute maximum voltage ratings cannot be exceeded without the risk of circuit damage.

## 2-2.6 Loading Rules

Loading specifications for  $\mu$ -PACs are expressed in terms of "unit loads," both for input loading and output drive capability. The unit load concept simplifies calculation of total loading imposed on a driving stage that is fanned out to a number of different circuit types. For  $\mu$ -PAC, a unit load is defined as the power required to drive the input circuit of a NAND gate (nominally 1.6 ma dc). Unit load ratings apply to the logic ZERO (ground) signal condition at a gate input. (Gates require no input power when all inputs are at logic ONE or are not connected.)

#### 2-2.7 Current Requirements

Current requirements are listed in the specifications for each individual  $\mu$ -PAC. The requirements are calculated on a nominal worst-case basis, in which the circuit inputs are assumed to be in the condition capable of causing the maximum current drain for a particular voltage. The nominal worst-case is selected instead of the extreme worst-case to provide a more realistic figure for power requirements and therefore permit more equipment to be driven by a power supply. Since it is very unlikely that all gates in a system would be on at the same time, the nominal worst-case calculations provide a considerable safety factor.

The current specifications include only the current used in the specific  $\mu$ -PAC and do not include the current going to external loads. Since the input load current is included in the specification, total system current requirements can be calculated by adding the rated currents for all  $\mu$ -PACs in the system.

#### 2-2.8 Worst Case Delays

In the detailed  $\mu$ -PAC descriptions of Section III, worst-case delays are specified over the full temperature range and under loading conditions which result in the longest propagation delay. (Eight dc gate loads are assumed for turn-on and one active dc gate load is assumed for turn-off.) For a gating circuit, the delay is specified as the average of the turn-on and turn-off delays. The total capacitance driven under the specified worst-case condition is 15 pf of wiring capacitance plus the capacitance accumulated in a  $\mu$ -BLOC system when driving eight unit loads. This capacitance may be present during turn-off as well as turn-on, since it is possible to fan out to eight unit loads and yet have only one gate active. (The other seven loads may be inhibited by inputs at ground.) The effect of additional wiring capacitance on gate delays is discussed in Paragraph 2-2.9.

The preceding conditions apply to all gate and flip-flop circuits. Power amplifier delay specifications assume the condition of driving 25 active dc gate loads plus a total of 250 pf of capacitance.

#### 2-2.9 Typical Delay Characteristics

The curves in Figure 2-2 show typical circuit delays of the basic NAND gate, plotted against variations in temperature, system wiring capacitance, and dc and capacitive loading conditions. For example, the "5 loads, 1 active" curve shows the delay characteristic of a gate output that fans out to five gates, four of which are inhibited by logic ZERO signals on other inputs. Connector, printed circuit, and input capacitance when fanning out to 5 unit loads are taken into consideration. The worst-case condition is also plotted. This is the "8 loads, 1 active" curve, where 1 active load is being driven from an output that fans out to 8 unit loads. In this situation, the maximum stray capacitance is being driven by the minimum charging current, resulting in longer turn-off delays.

Although the curves are plotted beyond 40 picofarads of additional wiring capacitance, that amount of wiring capacitance is unlikely to appear on any output in a  $\mu$ -BLOC

Figure 2-2. Typical NAND Gate Circuit Delays (Sheet 1 of 3)

Figure 2-2. Typical NAND Gate Circuit Delays (Sheet 2 of 3)

Figure 2-2. Typical NAND Gate Circuit Delays (Sheet 3 of 3)

system. The stray wiring capacitance will vary between 6 and 12 picofarads per foot, depending on the system wiring density. Due to the relatively small size of a  $\mu$ -BLOC the wiring runs are minimized.

#### 2-2.10 Typical Waveform Characteristics

The waveforms shown in Figure 2-3 are typical of a Model MC-335 clock driving a flip-flop, power amplifier, and two NAND gates in a series chain, with all logic elements operating at one-half their rated full load.

Figure 2-3. Typical  $\mu$ -PAC Waveforms

## 2-3 NAND GATE F-01 AND F-02 CHARACTERISTICS

#### 2-3.1 Basic NAND Circuit

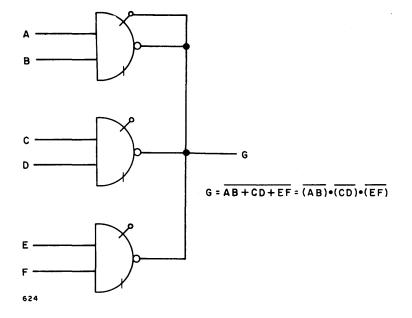

The standard  $\mu$ -PAC NAND gate is a grounded-emitter, inverter amplifier. All inputs are diode-buffered, and the output is either the voltage of a saturated transistor or the supply voltage. Accidental grounding of the output will not damage the circuit.

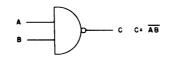

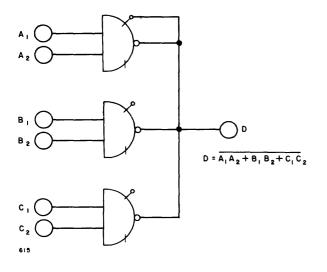

The gate performs the NAND function with conventional positive logic (+6v = ONE, 0v = ZERO). For negative logic, the gate performs the NOR function. (See Figure 2-4.)

When all inputs are at logic ONE (+6v) or open, the output transistor is turned on, and the output is logic ZERO (ground). If any input is at ground, the transistor is turned off, and the output is logic ONE (the supply voltage, +6v).

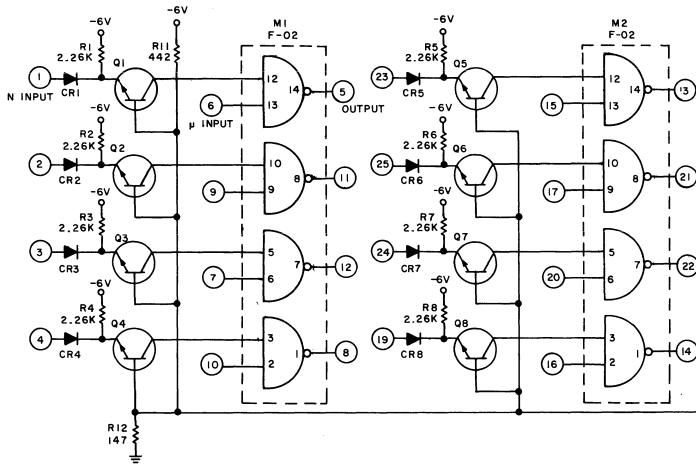

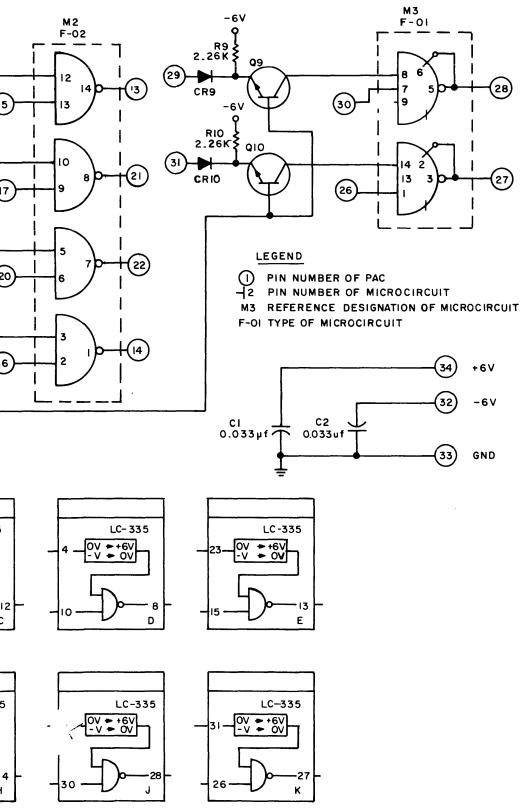

#### 2-3.2 F-01 and F-02 NAND Microcircuits

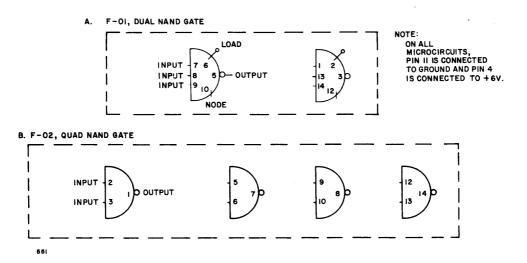

In order to obtain maximum logic flexibility two types of NAND gate microcircuits are used, the F-Ol dual NAND gate and the F-O2 quad NAND gate. The two NAND gate types have similar specifications and differ only in logic capability. (See Figure 2-5.)

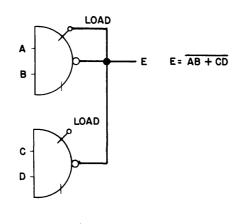

The F-01 dual NAND gate microcircuit contains two 3-input gates, each with an input node and a separate load resistor. The number of inputs to any gate can be expanded by tying the node of a gate to the node of a diode cluster. Outputs of gates with separate load resistors can be tied together as shown in Figure 2-6, to perform the AND-OR-INVERT function without loss of output drive capability.

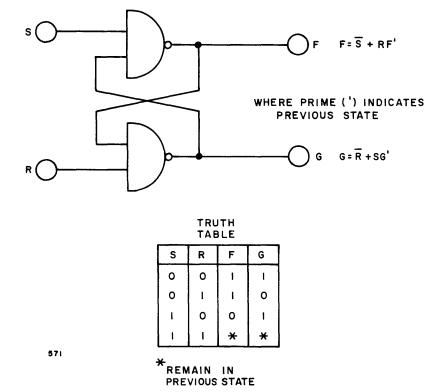

The F-02 quad NAND gate microcircuit contains four 2-input NAND gates. Pairs of gates can be wired back to back to form a dc set-reset flip-flop.

2-3.3 Loading

Input Loading: l unit load Output Drive Capability: 8 unit loads (capable of also driving 75 pf total capacitance with delays as specified)

Outputs of gates with separate load resistors can be tied together to 1 load resistor with no loss in output drive capability.

#### 2-3.4 Fan-In Expansion Using Nodes

12 at 5 mc 24 at 1 mc

Maximum fan-in is limited primarily by the maximum tolerable delays. The average propagation delay increases 3 nsec with each diode cluster that is tied to a node. The wire between nodes should be kept as short as possible by locating the PACs as close as possible to one another.

A. LOGIC FUNCTION

B. TRUTH TABLE

| INPUT 1 | INPUT 2 | OUTPUT |

|---------|---------|--------|

| 0       | 0       | I      |

| 0       | i i     | I      |

| I.      | o       | 1      |

| I       | 1       | 0      |

Figure 2-4. Basic NAND Gate Logic

Figure 2-5. Types F-01 and F-02 NAND Gate Equivalent Logic Symbols

Figure 2-6. Paralleled NAND Gates with Common Load Resistors

.

552

#### 2-3.5 Circuit Delay

(Measured at the +1.5v level, and averaged over 2 stages)

24 nsec (typ)

30 nsec (max)

The maximum delay specifications stated in the detailed  $\mu$ -PAC descriptions in Section III are based on worst-case loading conditions for both turn on and turn off. Typical delays are based on one-half maximum rated loading. (See paragraph 2-2.8.)

#### 2-3.6 Load Resistors in Parallel

When the outputs of two type F-02 NAND gates are tied together, the structure has a fanout capability of 4 unit loads (two load resistors are in parallel.) When the outputs of three type F-02 NAND gates are tied together, the structure has a fanout of 1 unit load (three load resistors are in parallel).

| Load Resistors<br>in Parallel | Output Drive<br>Capability |  |

|-------------------------------|----------------------------|--|

| 1 ,                           | 8                          |  |

| 2                             | 4                          |  |

| 3                             | 1                          |  |

#### 2-3.7 Paralleling Outputs with One Load Resistor

The maximum number of type F-01 NAND gate collector outputs that can be connected to one load resistor is limited by the maximum tolerable delay. The average propagation delay increases 3 nsec for each additional collector output that is jumpered through a connector to a standard output.

#### 2-4 TYPE F-03 POWER AMPLIFIER CHARACTERISTICS

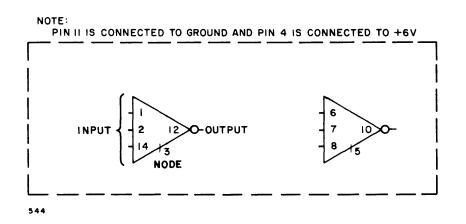

The type F-03 power amplifier microcircuit has two 3-input inverter amplifiers with nodes for input gating expansion. (See Figure 2-7.) The power amplifier circuit is logically equivalent to the NAND gate but has about three times the output drive capability. It has a short circuit protection network such that accidental grounding of the output will not damage the circuit.

2-4.1 Input Loading

2 unit loads

#### 2-4.2 Output Drive Capability

25 unit loads (capable of also driving 250 pf total capacitance with delays as specified)

#### 2-4.3 Circuit Delay

(Measured at the +1.5v level, averaged over two stages)

24 nsec (typ) 30 nsec (max)

The maximum delay is specified with a total of 250 pf capacitance and a dc current equivalent to 25 input gates.

#### 2-5 TYPE F-04 FLIP-FLOP CHARACTERISTICS

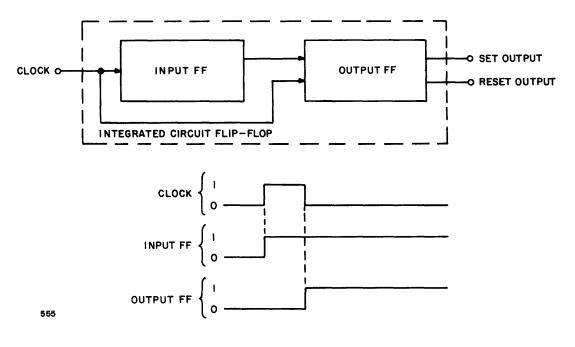

The standard  $\mu$ -PAC integrated circuit flip-flop, type F-04, is a double-rank, J-K flip-flop with dc set and reset capability. Figure 2-8 shows the logic symbol and equivalent logic circuit.

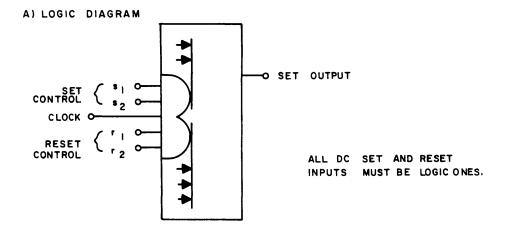

The clock gate portion of the flip-flop is composed of the clock and the set and reset control inputs. The control inputs are energized by logic ONEs. A ZERO-ONE-ZERO pulse on the clock will cause the flip-flop to assume the state determined by the condition of the control inputs. With J-K circuitry, no combination of the control input signals can cause an ambiguous state.

The set and reset control inputs may be used as follows.

- a. To gate clock pulses

- b. As direct set and reset inputs

- c. As another clock input when a set and a reset control are tied together.

For dc operation, voltage levels are used on the dc inputs. Signals applied to the dc set and reset inputs take precedence over any ac gating. However, output spikes may occur when the reset clock gate is activated during a dc set, or vice-versa. Such spikes can be eliminated by tying the dc set input to a reset control input and tying the dc reset input to a set control input.

#### 2-5.1 Pulse Dodging

The flip-flop utilizes the double-rank technique of pulse dodging (Figure 2-9). When the clock input makes the transition from ZERO to ONE, the state of the input flip-flop

A. LOGIC SYMBOL

B. EQUIVALENT LOGIC CIRCUIT

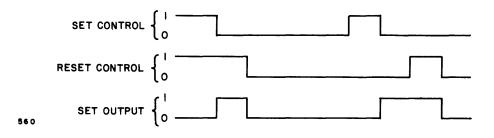

Figure 2-9. Double-Rank Flip-Flop Pulse Dodging, Timing Diagram

is fixed and data transfer from the input flip-flop to the input of the output flip-flop is inhibited. On the ONE to ZERO transition of the clock input, data from the input flip-flop is shifted to the output flip-flop and the inputs to the input flip-flop are inhibited. Thus the clock provides intrinsic pulse dodging by means of trailing edge triggering. This feature permits strobing of the flip-flop output with input triggering signals.

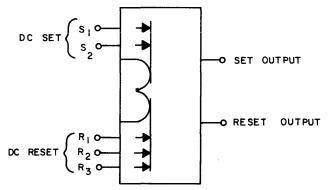

#### 2-5.2 DC Operation

If either dc set goes to logic ZERO, the flip-flop will assume the ONE state; if any dc reset goes to ZERO, the flip-flop will assume the ZERO state. If both a dc set and a dc reset go to ZERO at the same time, both the set and the reset outputs will go to logic ZERO. Figure 2-10 contains diagrams and equations describing this mode of flip-flop operation.

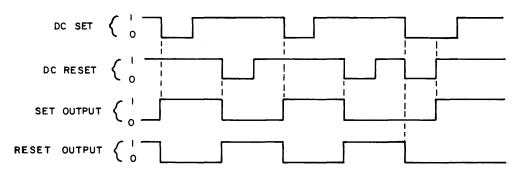

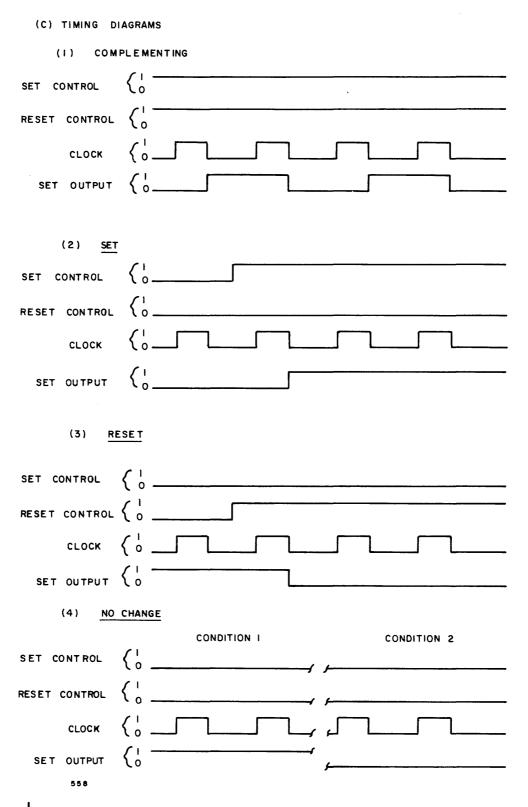

# 2-5.3 Control Inputs Used to Steer Clock Pulses

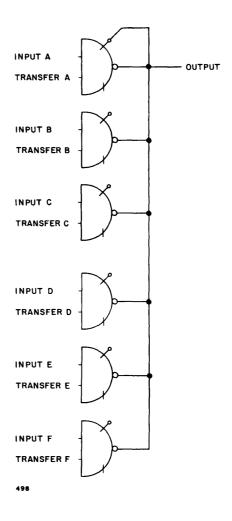

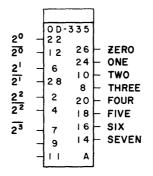

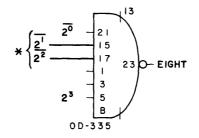

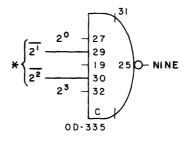

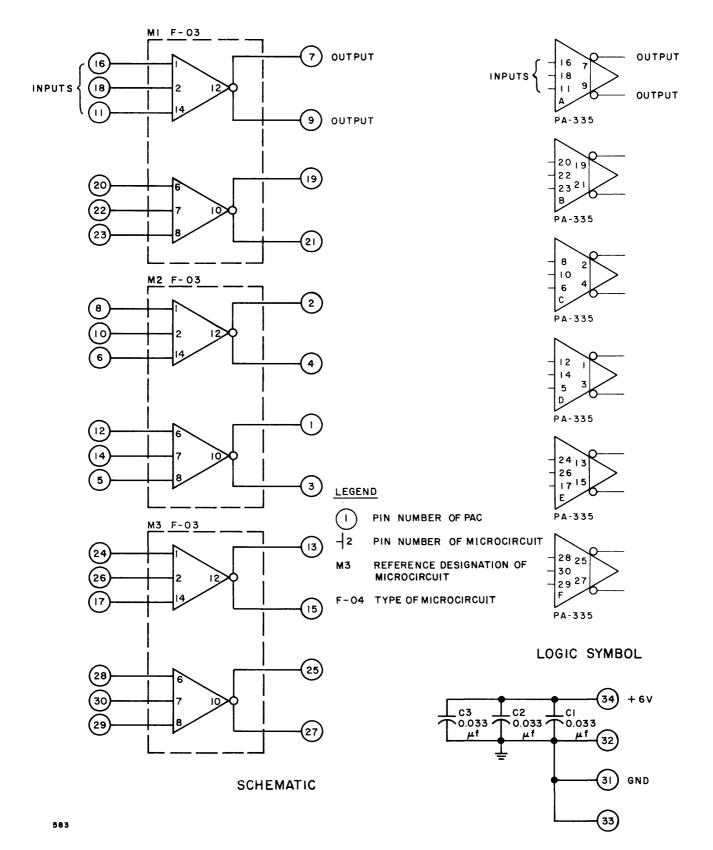

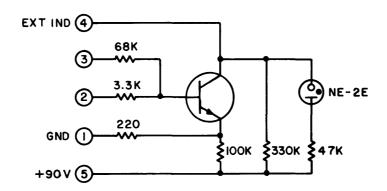

If both the set controls  $(S_C)$  and the reset controls  $(R_C)$  are logic ONES, the flipflop will be complemented by the application of a clock pulse. If only  $S_C$  or  $R_C$  is a ONE, the state of the flip-flop will be a ONE or ZERO, respectively, after the clock is energized. If both  $S_C$  and  $R_C$  are ZERO, the flip-flop will remain in its previous state. One restriction is that when a control input is used to gate the clock, the control input cannot change from the ONE to the ZERO state while the clock is a ONE. Figure 2-11 contains diagrams and equations describing this mode of flip-flop operation.