# S/MT™ SERIES DIAGNOSTICS MANUAL

**.**....

#### NOTICE

Copyright © 1988 by Convergent, Incorporated, San Jose, CA. Printed in USA.

All rights reserved. Title to and ownership of the documentation contained herein shall at all times remain in Convergent, Inc., and/or its suppliers. The full copyright notice may not be modified except with the express written consent of Convergent, Inc.

Specifications Subject to Change.

Convergent Technologies is a registered trademark of Convergent Technologies, Inc. CTIX, S/120, S/220, S/320, S/480, S/640, S/1280, Multibus, and TeleCluster are trademarks of Convergent Technologies, Inc

Second Edition – November 1988 09-02110-01

#### WARNING

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

٣ (-----

# S/MT Series Diagnostics Quick Reference

## Loading the Diagnostics with CTIX Running

- 1. Shut down the operating system.

- 2. Insert the diagnostic tape in the tape drive when the following prompt appears:

OK to stop or reset processor

3. Type reboot, then press **RETURN** (or simply press the reset switch).

### Loading the Diagnostics with Power Off \_\_\_\_\_

1. Insert the diagnostic tape into the tape drive.

2. Turn on the power by pressing the power switch to the on position.

The diagnostics screen is displayed as follows:

| MIGHTYFRAME MC68020 DIAGNOSTIC DEBUGGER V2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COPYRIGHT 1983, 1984, 1985, 1987 BY CONVERGENT TECHNOLOGIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MIGHTYFRAME DIAGNOSTICS-V <6.XX.XX > release (XX)<br>(XXX XXX X XX:XX:XX PST 19XX - /usr/src/miti/diag)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| System configuration:<br>X mega bytes of memory<br>XMb memory board in slot MX<br>MC68881 coprocessor is not present<br>VME expansion board is not present<br>Ethernet Combo board in slot X is configured for dma slot X<br>RS232 channels 2 to 11 22 to 27 in slots: IO1 IO3<br>IOP board is present<br>Drive 0 is present [6.0bt]<br>Drive 1 is present [6.0bt]<br>Drive 1 is present [5.1bt]<br>Memory tests will begin at 0xXXXXX, end at 0xXXXXXX<br>Parity interrupts enabled, Disk/QIC Interrupt Mode enabled<br>The time on the clock calendar is: XXX XXX XXXXXXX GMT 19XX |

| command >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Two-Letter Commands -

The two-letter commands are shown in Table 1. A complete description of the commands is provided in Chapter 4, "Two-Letter Commands."

| Table 1. | Two-Letter | Commands |

|----------|------------|----------|

|----------|------------|----------|

| Command        | Description                              |

|----------------|------------------------------------------|

| General        |                                          |

| ??             | list available two\-letter commands      |

| HE             | help screen                              |

| PM             | page mode                                |

| LE             | line printer echo                        |

| Disk and Tape  |                                          |

| RC             | repeat count                             |

| EC             | ECC error correction enable/disable      |

| SEx            | disk soft error count                    |

| DD             | display disk error statistics            |

| CD             | clear disk error statistics              |

| IM             | interrupt mode                           |

| Unit Selection |                                          |

| DN             | disk drive number                        |

| TN             | tape drive number                        |

| EN             | Ethernet Combo board number              |

| MN             | VME Communication Controller card number |

| System Mode    |                                          |

| RE             | reboot                                   |

| PE             | NMI/parity enable                        |

| CA             | cache enable                             |

| SPx            | system priority level                    |

|                | · · · ·                                  |

| Table 1. Two-Letter Commands (continued) |                                                                          |

|------------------------------------------|--------------------------------------------------------------------------|

| Command                                  | Description                                                              |

| <b>Display Status</b>                    |                                                                          |

| CN<br>DE<br>DS                           | system configuration<br>display errors<br>display test sequence subtests |

| User Selection                           |                                                                          |

| CO<br># =                                | change console<br>user-defined test sequence                             |

## Test Sequence Summary

Number refers to test by number and is used to run subtests. A letter can be used to run an entire test sequence. Table 2 describes the test sequence numbers and letters.

### Table 2. Test Sequences

| Number      | Letter    | Description                                     |

|-------------|-----------|-------------------------------------------------|

| CPU Tests   |           |                                                 |

| 0           | m         | memory                                          |

| 1           | р         | page map (CPU-01 systems only)                  |

| 2           | ō         | physical memory                                 |

| 3           | r         | parity (CPU-01 systems only)                    |

| 4           | с         | clock                                           |

| 10          | a         | Map RAM (CPU-01 systems only)                   |

| 10          | а         | data cache and PTC RAM (CPU-02<br>systems only) |

| 12          | e         | page protection                                 |

| 13          | 1         | line printer                                    |

| Disk and Ta | pe        |                                                 |

| 6           | w         | hard disk drive tests                           |

| 9           | u         | general disk tests                              |

| 16          | t         | QIC tape drive tests (CPU-01 systems only)      |

| 20          | j         | general tape tests                              |

| I/O Process | or Boards |                                                 |

| 11          | h         | RS-232-C tests                                  |

| 5           | i         | IOP tests                                       |

| 15          | n         | Ethernet Combo board tests                      |

| 14          | k         | RS-422 tests                                    |

| VME         |           |                                                 |

| 17          | v         | VME subsystem (ethernet)                        |

| 19          | b         | VME Communication Controller care tests         |

| Miscellaneo | us        |                                                 |

| 18          | z         | miscellaneous tests                             |

۴ (<u>.</u>...

# **Table of Contents**

# S/MT Series Diagnostics Quick Reference

| Loading the Diagnostics with CTIX Running | i  |

|-------------------------------------------|----|

| Loading the Diagnostics with Power Off    | i  |

| Two-Letter Commands                       | ii |

| Test Sequence Summary                     | iv |

# Chapter 1. Overview

| INTRODUCTION               | 1-1 |

|----------------------------|-----|

| ABOUT THIS MANUAL          | 1-3 |

| Who Should Use This Manual | 1-3 |

| Purpose of This Manual     | 1-3 |

| Manual Organization        | 1-4 |

| How to Use This Manual     | 1-6 |

| RELATED DOCUMENTATION      | 1-7 |

# Chapter 2. Getting Started

| INTRODUCTION                                                        | 2-1                  |

|---------------------------------------------------------------------|----------------------|

| CONNECTING THE TERMINAL                                             | 2-2                  |

| STARTING UP THE TERMINAL                                            | 2-4                  |

| CONNECTING A PARALLEL PRINTER                                       | 2-8                  |

| LOADING THE DIAGNOSTIC TESTS<br>With CTIX Running<br>With Power Off | 2-10<br>2-11<br>2-12 |

| DIAGNOSTIC SCREEN                                                   | 2-13                 |

| DIAGNOSTIC TEST CONDITIONS                                          | 2-15                 |

| Chapter 3. Command Interpreter    |     |

|-----------------------------------|-----|

| INTRODUCTION                      | 3-1 |

| DIAGNOSTIC TEST MODES             | 3-2 |

| Attended Mode                     | 3-2 |

| Unattended Mode                   | 3-4 |

| TWO-LETTER COMMANDS               | 3-5 |

| Listing the Two-Letter Commands   | 3-5 |

| Executing the Two-Letter Commands | 3-6 |

# Chapter 3. Command Interpreter (continued)

| TESTS AND TEST SEQUENCES<br>Subtests<br>Listing Test Sequence Subtests | 3-8<br>3-9<br>3-9 |

|------------------------------------------------------------------------|-------------------|

| COMMAND STRUCTURE                                                      | 3-11              |

| SAMPLE COMMANDS                                                        | 3-14              |

| HELPFUL HINTS                                                          | 3-17              |

| Chapter 4. Two-Letter Commands            |      |

|-------------------------------------------|------|

|                                           |      |

| INTRODUCTION                              | 4-1  |

| DISPLAY TWO-LETTER COMMANDS               | 4-2  |

| Help (HE)                                 | 4-2  |

| DISPLAY MODE COMMANDS                     | 4-4  |

| Page Mode (PM)                            | 4-4  |

| Line Printer Echo (LE)                    | 4-5  |

| DISK AND TAPE COMMANDS                    | 4-7  |

| Repeat Count (RC)                         | 4-7  |

| Error Correction Code Enable/Disable (EC) | 4-10 |

| Disk Soft Error Count (SE x)              | 4-11 |

| Display Disk Error Statistics (DD)        | 4-12 |

| Clear Disk Error Statistics (CD)          | 4-13 |

| Chapter 4. Two Letter Commands (continued) |      |  |

|--------------------------------------------|------|--|

|                                            |      |  |

| Interrupt Mode (IM)                        | 4-13 |  |

| UNIT SELECTION COMMANDS                    | 4-15 |  |

| Disk Drive Number (DN)                     | 4-15 |  |

| Tape Drive Number (TN)                     | 4-18 |  |

| Ethernet Combo Board Number (EN)           | 4-20 |  |

| VME Communication Controller Board         |      |  |

| Number (MN)                                | 4-21 |  |

| SYSTEM MODE COMMANDS                       | 4-22 |  |

| Reboot (RE)                                | 4-22 |  |

| NMI/Parity Enable (PE)                     | 4-23 |  |

| Cache Enable (CA)                          | 4-24 |  |

| System Priority Level (SP x)               | 4-25 |  |

| DISPLAY STATUS COMMANDS                    | 4-27 |  |

| System Configuration (CN)                  | 4-27 |  |

| Display Errors (DE)                        | 4-28 |  |

| Display Test Sequence Subtests (DS)        | 4-29 |  |

| USER SELECTION COMMANDS                    | 4-31 |  |

| Change Console (CO)                        | 4-31 |  |

| User-Defined Test Sequence (# = )          | 4-32 |  |

| Chapter 5. CPU-01 Diagnostic Tests            |            |

|-----------------------------------------------|------------|

|                                               | <b>r</b> 1 |

| INTRODUCTION                                  | 5-1        |

| TEST 0: MEMORY (m)                            | 5-4        |

| Noninteractive Memory Subtests                | 5-6        |

| Interactive Memory Subtests                   | 5-9        |

| TEST 1: PAGE MAP (p)                          | 5-24       |

| TEST 2: PHYSICAL MEMORY MAP (o)               | 5-26       |

| Subtest 1: Test All Bit Combinations in One   |            |

| Access Register                               | 5-27       |

| Subtest 2: Test Access Register Bits          | 5-28       |

| Subtest 3: Walk 0 and 1 Through Modified Bits |            |

| of Access Registers                           | 5-29       |

| TEST 3: PARITY (r)                            | 5-31       |

| Subtest 1: Test GSR Parity Error Bits         | 5-32       |

| Subtest 2: Test All Available GSR Physical    |            |

| Page Numbers                                  | 5-33       |

| Subtest 3: Executes Program with Parity Error | 5-34       |

| TEST 4: CLOCK (c)                             | 5-36       |

| Subtest 1: Data Path Check to 8259 and 8253   | 5-37       |

| Subtest 2: Test Timer 0                       | 5-38       |

| Subtest 3: Test Timer 1                       | 5-38       |

| Subtest 4: Test Timer 2                       | 5-39       |

| Subtest 5: Test Clock Calendar                | 5-39       |

| Subtest 6: Set Clock Calendar                 | 5-40       |

| Subtest 7: Read Date and Time                 | 5-41       |

# Chapter 5. CPU-01 Diagnostic Tests (continued)

| Subtest 8: Special Frequency Calibration            | 5-42 |

|-----------------------------------------------------|------|

| TEST 10: MAP RAM (a)                                | 5-43 |

| Subtest 1: Write and Read 0x00000000s               | 5-46 |

| Subtest 2: Write and Read 0xFFFFFFFFs               | 5-46 |

| Subtest 3: Write and Read 0xAAAAAAAA                | 5-47 |

| Subtest 4: Write and Read 0x55555555                | 5-47 |

| Subtest 5: Write and Read Addresses                 | 5-48 |

| Subtest 6: Write and Read Address                   |      |

| Complements                                         | 5-48 |

| TEST 12: PAGE PROTECTION (e)                        | 5-49 |

| Subtest 1: Check Hardware Page Protection<br>Status | 5-50 |

| Subtest 2: Read and Write to Mapped RAM             |      |

| and Unused I/O Space                                | 5-52 |

| TEST 13: LINE PRINTER (1)                           | 5-54 |

| Subtest 1: Check and Display Line Printer           |      |

| Status Register                                     | 5-55 |

| Subtest 2: Print and Check Rotating Pattern         |      |

| on Printer Using Interrupts                         | 5-56 |

| Subtest 3: Check Printer Connector Control          |      |

| Lines                                               | 5-57 |

| Subtest 4: Check/Display IOP or RS-422              |      |

| Line Printer Status Register                        | 5-57 |

| Subtest 5: Check Interrupt Status                   | 5-58 |

----

# Chapter 5. CPU-01 Diagnostic Tests (continued)

### Subtest 6: Check IOP or RS-422 Printer Connector Control Lines

5-59

## Chapter 6. CPU-02 Diagnostic Tests

| INTRODUCT   | ION                                  | 6-1  |

|-------------|--------------------------------------|------|

| TEST 0: MEM | ORY (m)                              | 6-4  |

| Nonintera   | ctive Memory Subtests (1-13, 14, 16) | 6-5  |

|             | Memory Subtests (15 and 20-32)       | 6-9  |

| TEST 2: PHY | SICAL MEMORY MAP (0)                 | 6-23 |

| Subtest 1:  | Test All Bit Combinations in One     |      |

| Acces       | s Register                           | 6-24 |

| Subtest 2:  | Test Access Register Bits            | 6-25 |

|             | Walk 0 and 1 Through Modified Bits   |      |

|             | cess Registers                       | 6-26 |

| TEST 4: CLO | CK (c)                               | 6-28 |

| Subtest 1:  | Data Path Check to 8259 and 8253     | 6-29 |

| Subtest 2:  | Test Timer 0                         | 6-30 |

| Subtest 3:  | Test Timer 1                         | 6-30 |

| Subtest 4:  | Test Timer 2                         | 6-31 |

| Subtest 5:  | Test Clock Calendar                  | 6-31 |

| Subtest 6:  | Set Clock Calendar                   | 6-32 |

| Subtest 7:  | Read Date and Time                   | 6-33 |

# Chapter 6. CPU-02 Diagnostic Tests (continued)

| Subtest 8: Special Frequency Calibration    | 6-34 |

|---------------------------------------------|------|

| TEST 10: DATA CACHE AND PAGE TABLE          |      |

| CACHE RAM (a)                               | 6-35 |

| Subtest 1: Data Cache Memory                | 6-38 |

| Subtest 2: Data Cache Tag Memory            | 6-39 |

| Subtest 3: DMA Map Memory                   | 6-40 |

| Subtest 4: Group Table Memory               | 6-40 |

| Subtest 5: Page Table Cache Memory          | 6-41 |

| Subtest 6: Page Table Cache Tag Memory      | 6-41 |

| Subtest 7: Force NMI on PTC Fill            | 6-42 |

| Subtest 8: Page Table Cache Fill            | 6-42 |

| Subtest 9: Pointer Register                 | 6-43 |

| Subtest 10: Indirect Pointer Register       | 6-44 |

| Subtest 11: Data Cache Memory Through       |      |

| Virtual Space: 0x100000) – 0x120000         | 6-45 |

| TEST 12: PAGE PROTECTION (e)                | 6-46 |

| Subtest 1: Check Hardware Page Protection   |      |

| Status                                      | 6-47 |

| Subtest 2: Read and Write to Virtual Memory |      |

| and Unused I/O Space                        | 6-49 |

| TEST 13: LINE PRINTER (1)                   | 6-50 |

| Subtest 1: Check and Display Line Printer   |      |

| Status Register                             | 6-51 |

| Subtest 2: Print and Check Rotating Pattern |      |

| on Printer Using Interrupts                 | 6-52 |

# Chapter 6. CPU-02 Diagnostic Tests (continued)

| Subtest 3: Check Control Lines of Printer   |      |

|---------------------------------------------|------|

| Connector                                   | 6-53 |

| Subtest 4: Check/Display IOP or RS-422 Line |      |

| Printer Status Register                     | 6-53 |

| Subtest 5: Check Interrupt Status           | 6-54 |

| Subtest 6: Check IOP or RS-422 Printer      |      |

| Connector Control Lines                     | 6-54 |

| SUBTESTS 7 AND 8: BIDIRECTIONAL             |      |

| PRINTER PORT                                | 6-55 |

# Chapter 7. Disk and Tape Diagnostic Tests

| INTRODUCTION                                                                                                                                        | 7-1                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| DISK DRIVE TESTS (w AND u)<br>Bad Block Information for Non-SCSI Drives<br>Bad Block Information for SCSI Drives<br>Disk Drive Controller Registers | 7-3<br>7-4<br>7-5<br>7-6 |

| SPECIFYING A REPEAT COUNT                                                                                                                           | 7-15                     |

| EXECUTING THE DISK DRIVE TEST<br>SEQUENCE<br>Subtest 1: Recalibrate Disk<br>Subtest 2: Format Disk                                                  | 7-16<br>7-17<br>7-18     |

# Chapter 7. Disk and Tape Diagnostic Tests (continued)

| Subtest 3: Write                            | 7-21 |

|---------------------------------------------|------|

| Subtest 4: Read                             | 7-24 |

| Subtest 5: Random Seeks                     | 7-25 |

| Subtests 6-7: Write/Read Multiple Blocks    | 7-26 |

| Subtest 8: Spare a Sector                   | 7-29 |

| Subtest 9: Force DMA Faults                 | 7-32 |

| Subtest 10: Initialize VHB and BBT          | 7-32 |

| Subtest 11: Write VHB and BBT               | 7-34 |

| Subtest 12: Print VHB and BBT               | 7-35 |

| Subtest 14: Toggle Alien Disk Mode          | 7-36 |

| Subtest 20: Print CTIX File System          | 7-39 |

| Subtest 21: Find Unreadable Blocks          | 7-40 |

| Subtest 23: Surface                         | 7-41 |

| Subtest 25: Sort Bad Block Table            | 7-42 |

| Subtest 29: Harmonic Seek Stress            | 7-44 |

| Subtest 30: Clone a Disk                    | 7-45 |

| Subtest 31: Quick Disk Write and Check Read | 7-47 |

| TEST 16: QIC CARTRIDGE TAPE (t)             | 7-48 |

| Subtest 1: Reset and Initialize Tape        | 7-51 |

| Subtest 2: Adverse DMA                      | 7-52 |

| Subtest 3: Rewind Tape                      | 7-53 |

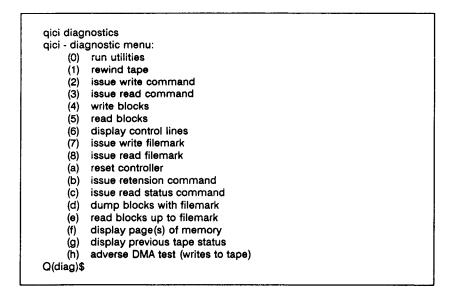

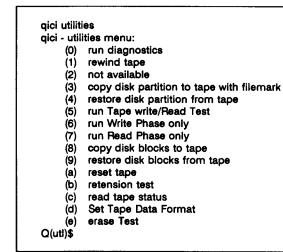

| Subtest 4: Run Interactive Diagnostics      | 7-54 |

| Subtest 5: Run Interactive Utilities        | 7-62 |

| Subtest 6: Write Phase of Tape              | 7-70 |

| Subtest 7: Read Phase of Tape               | 7-71 |

| Subtest 8: Set up Parameters for Tape       | 7-72 |

| Subtest 9: Erase Tape                       | 7-73 |

# Chapter 7. Disk and Tape Diagnostic Tests (continued)

| Subtest 10: Retension Tape                   | 7-73 |

|----------------------------------------------|------|

| TEST 20: GENERAL TAPE DRIVE (j)              | 7-75 |

| Selecting the Tape Drive                     | 7-76 |

| Executing the Tape Drive Test Sequence       | 7-78 |

| Warning Messages                             | 7-79 |

| Subtest 1: Reset and Initialize              | 7-80 |

| Subtest 2: Set Default Controller Parameters | 7-81 |

| Subtest 3: Show Drive Status and Parameters  | 7-81 |

| Subtest 4: Set Tape Drive Parameters         | 7-83 |

| Subtest 5: Change Tape Speed/Density         | 7-86 |

| Subtest 6: Rewind the Tape                   | 7-86 |

| Subtest 7: Erase Tape                        | 7-87 |

| Subtest 8: Seek to Next Filemark             | 7-88 |

| Subtest 9: DMA Address Counter               | 7-91 |

| Subtest 10: Write                            | 7-90 |

| Subtest 11: Read                             | 7-91 |

| Subtest 12: Copy Disk Partition to Tape      | 7-92 |

| Subtest 13: Restore Disk Partition from Tape | 7-93 |

| Subtest 14: Copy Disk Blocks to Tape         | 7-95 |

| Subtest 15: Restore Disk Blocks from Tape    | 7-96 |

| Subtest 16: Toggle Tape Drive Modes          | 7-97 |

|                                              |      |

## Chapter 8. RS-232-C Channel Diagnostic Tests

### INTRODUCTION

| 0  | 1 |

|----|---|

| 0- | T |

| TEST 11: RS-232-C (8530) (h)             | 8-2  |

|------------------------------------------|------|

| Subtest 1: Data Path Check to 8530       | 8-5  |

| Subtest 2: Program All Options           | 8-6  |

| Subtest 3: Simultaneous Data Transfers   | 8-7  |

| Subtest 4: Force Error Conditions        | 8-9  |

| Subtest 5: Test Driver Pins: RTS, DTR    | 8-10 |

| Subtest 6: Select Channel for Subtest 1  | 8-11 |

| Subtest 7: Select Channel for Subtest 2  | 8-12 |

| Subtest 8: Select Channel for Subtest 3  | 8-12 |

| Subtest 9: Select Channel for Subtest 4  | 8-14 |

| Subtest 10: Select Channel for Subtest 5 | 8-15 |

|                                          |      |

# Chapter 9. IOP Accelerator Board Diagnostic Tests

| INTRODUCTION                           | 9-1 |

|----------------------------------------|-----|

| TEST 5: IOP ACCELERATOR BOARD (i)      | 9-2 |

| Subtests 1 to 6: IOP Memory            | 9-5 |

| Subtest 7: Upload IOP Resident         | 9-6 |

| Subtest 8: Run Interrupt               | 9-7 |

| Subtest 9: Run Data Path Check to 8253 | 9-8 |

| Subtest 10: Run Clock 0                | 9-8 |

| Subtest 11: Run Clock 1                | 9-9 |

## Chapter 9. IOP Accelerator Board Diagnostic Tests (continued)

| Subtest 12: Run Clock 2                     | 9-10 |

|---------------------------------------------|------|

| Subtest 13: Run Data Path Check to Existing |      |

| RS-232-C Expansion Channels                 | 9-10 |

## Chapter 10. Ethernet Combo Board Diagnostic Tests

#### INTRODUCTION 10-1 TEST 15: ETHERNET COMBO BOARD (n) 10-2Subtest 1: RAM Write/Read 10-4 Subtest 2: Host Memory Write/Read 10-5 Subtest 3: EEPROM Write/Read 10-5 Subtest 4: EEPROM Write Pattern 10-6 Subtest 5: EEPROM Read Pattern Set by 4 10-6Subtest 6: Interrupt 10-7Subtest 7: Loopback, CRC, and Collision 10-7 Subtest 8: Time Domain Reflectometry 10-8 Subtest 9: External Loopback 10-9 Subtest 10: Configure/Select a Board 10-9 Subtest 11: Toggle Debug Mode 10 - 10Subtest 12: Toggle Packet Print Mode 10-11 Subtest 13: Send a Test Packet 10-12 Subtest 14: Retransmit Packet Sent in Subtest 13 10-12 Subtest 15: Ping-Pong with Data Check 10-13

## Chapter 10. Ethernet Combo Board Diagnostic Tests (continued)

| Subtest 16: Reverse Ping-Pong with Data    |       |

|--------------------------------------------|-------|

| Check                                      | 10-14 |

| Subtest 17: Transmit Serially-Numbered     |       |

| Packets                                    | 10-15 |

| Subtest 18: Send Back-to-Back Packets to   |       |

| Station Zero                               | 10-16 |

| Subtests 19 and 20: Monitor Line           | 10-16 |

| Subtest 21: Enable Board and Leave Running | 10-17 |

| Subtest 22: Toggle DMA Channel             | 10-18 |

| Subtest 23: Set Station Address to Zero    | 10-19 |

| Subtest 24: Toggle Interactive Mode        | 10-19 |

## Chapter 11. RS-422 Expansion Board Diagnostic Tests

| INTRODUCTION                                | 11 <b>-</b> 1 |

|---------------------------------------------|---------------|

| TEST 14: RS-422 EXPANSION BOARD (k)         | 11-2          |

| Subtest 1: Data Path Check (DMA Count       |               |

| Registers and PCSAR)                        | 11-3          |

| Subtest 2: Auto Send/Receive (2 Channel)    | 11-4          |

| Subtest 3: Auto Send/Receive (All Channels) | 11-4          |

| Subtest 4: Transmit/Receive User-Specified  |               |

| Channel                                     | 11-5          |

| Subtest 5: Transmit User-Specified Memory   |               |

| Block                                       | 11-7          |

|                                             |               |

## Chapter 11. RS-422 Expansion Board Diagnostic Tests (continued)

| Subtest 6: Receive User-Specified Memory |      |

|------------------------------------------|------|

| Block                                    | 11-7 |

| Subtest 7: Parity Error Read             | 11-8 |

| Subtest 8: DMA Address Counter           | 11-8 |

# Chapter 12. VME Subsystem Diagnostic Tests

| 12-1 |

|------|

| 12-2 |

| 12-3 |

| 12-4 |

| 12-4 |

| 12-5 |

| 12-5 |

| 12-6 |

| 12-6 |

| 12-7 |

|      |

| Chapter 13. VME Communication Controller<br>Board Diagnostic Tests |       |

|--------------------------------------------------------------------|-------|

| INTRODUCTION                                                       | 13-1  |

| TEST 19: VME COMMUNICATION                                         |       |

| CONTROLLER BOARD (b)                                               | 13-2  |

| TEST FAILURES                                                      | 13-4  |

| Subtest 1: MPCC Memory Access                                      | 13-5  |

| Subtest 2: Write Address and Complement to                         |       |

| MPCC Memory                                                        | 13-5  |

| Subtest 3: Load and Boot MPCC Tester                               | 13-5  |

| Subtest 4: Mutual Interrupts                                       | 13-6  |

| Subtest 5: MPCC Local Memory                                       | 13-7  |

| Subtest 6: MPCC CIO Data Path                                      | 13-7  |

| Subtest 7: MPCC SCC Asynchronous Data                              |       |

| Path                                                               | 13-8  |

| Subtest 8: MPCC SCC Synchronous Data Path                          | 13-8  |

| Subtest 9: MPCC VME DMA                                            | 13-9  |

| Subtest 10: MPCC OSCC DMA                                          | 13-9  |

| Subtest 11: External Loopback                                      | 13-10 |

| Subtest 12: CPU Bus Load                                           | 13-11 |

| Subtest 13: MPCC Board Reset                                       | 13-11 |

| Subtest 14: Multiple Subtests                                      | 13-12 |

| Subtest 15: Board Test Mode                                        | 13-12 |

| Subtest 16: Screen Message Mode                                    | 13-13 |

| Subtest 17: MPCC Board Configuration                               | 13-14 |

(\_\_\_\_\_

## Chapter 13. VME Comunication Controller Board Diagnostic Tests (continued)

|             | and 19: User-Defined Sequence  | 13-15 |

|-------------|--------------------------------|-------|

| Subtest 20: | Print Last Message and Timeout |       |

| Flag        |                                | 13-16 |

| Subtest 21: | Extensive Onboard VME DMA      | 13-17 |

## Chapter 14. Miscellaneous Diagnostic Tests

| INTRODUCTION                               | 14-1  |

|--------------------------------------------|-------|

| LIMITS ON WRITING TO THE EEPROM            | 14-3  |

| Subtest 1: MC68881                         | 14-3  |

| Subtest 2: UPS Port Line Driver            | 14-4  |

| Subtest 3: VME Bus Cycle Timeout           | 14-6  |

| Subtest 4: VME Protection Register         | 14-7  |

| Subtest 5: VME Read Pattern                | 14-8  |

| Subtest 6: VME Write Pattern               | 14-9  |

| Subtest 7: VME Clear (Write All Zeros)     | 14-10 |

| Subtest 8: VME Set (Write All 0xFFs)       | 14-11 |

| Subtest 9: VME Set Type                    | 14-12 |

| Subtest 10: VME Set Checksum               | 14-13 |

| Subtest 11: VME Set Address and Board Type | 14-13 |

| Subtest 12: VME Print the Board Types and  |       |

| Addresses                                  | 14-15 |

| Subtest 13: VME Clear the Addresses and    |       |

| Board Types                                | 14-16 |

|                                            |       |

# Chapter 14. Miscellaneous Diagnostic Tests (continued)

| Subtest 14: VME Set Up 'Default' Table of |       |

|-------------------------------------------|-------|

| Board Types                               | 14-17 |

| Subtest 15: VME Save Contents on EEPROM   | 14-18 |

| Subtest 16: VME Restore EEPROM to State   |       |

| Before Write                              | 14-19 |

| Subtest 17: VME Confirm Checksum          |       |

| Correctness                               | 14-20 |

| Subtest 20: Serial Number ROM Test        | 14-21 |

| Appendix A. Cable and Connector<br>Specifications | (            |

|---------------------------------------------------|--------------|

| INTRODUCTION                                      | A-1          |

| RS-232-C 25-PIN TO 25-PIN CROSSED CABLE           | A-3          |

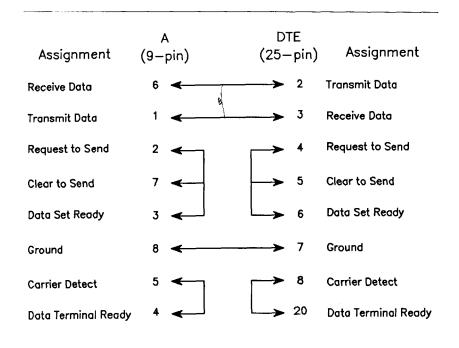

| RS-232-C 9-PIN TO 25-PIN CROSSED CABLE            | <b>A-</b> 7  |

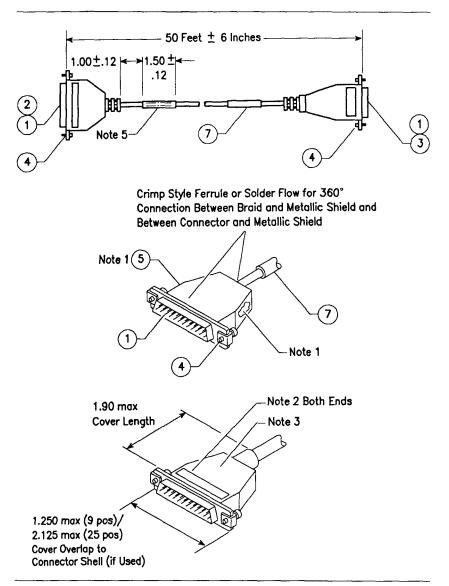

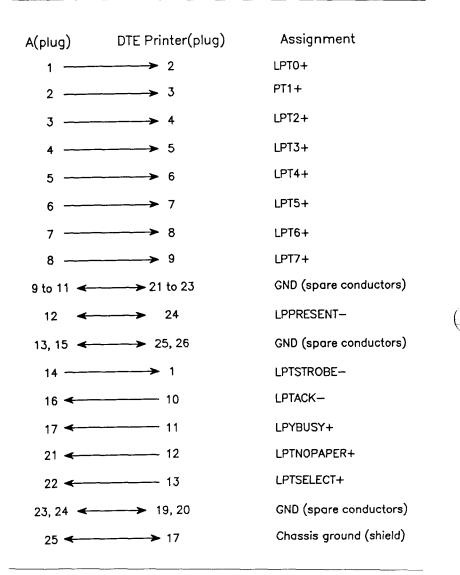

| PARALLEL LINE PRINTER CABLE                       | <b>A-</b> 11 |

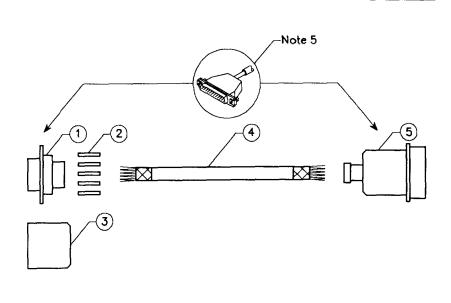

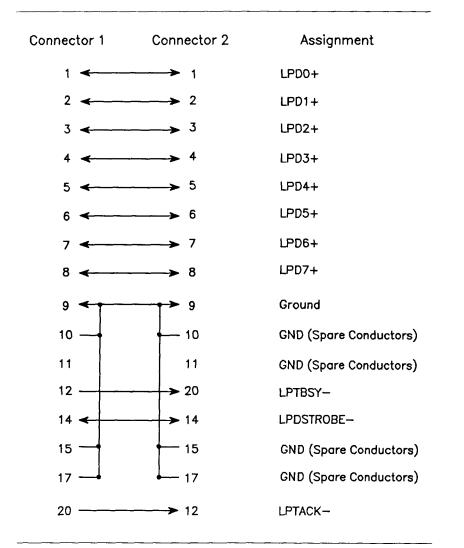

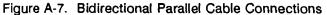

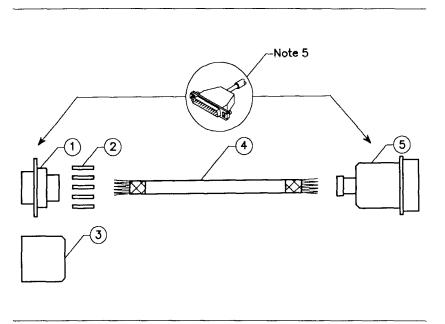

| BIDIRECTIONAL PARALLEL PRINTER PORT<br>CABLE      | A-16         |

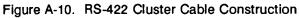

| RS-422 CLUSTER COMMUNICATIONS CABLE               | A-21         |

| 50-PIN SCSI CONNECTOR                             | A-25         |

| Appendix A. Cable and Connector<br>Specifications (continued) |      |

|---------------------------------------------------------------|------|

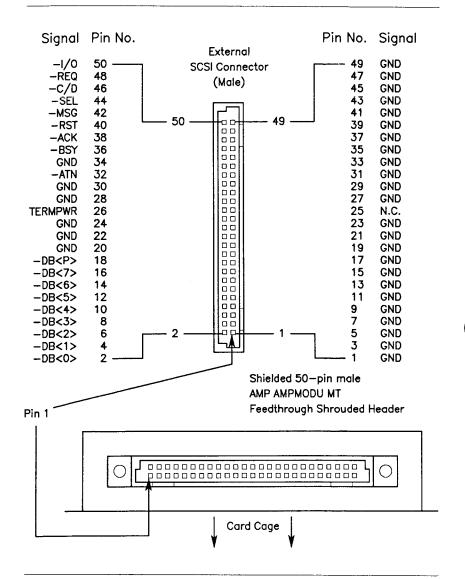

| RS-232-C 25-PIN LOOPBACK PLUG                                 | A-27 |

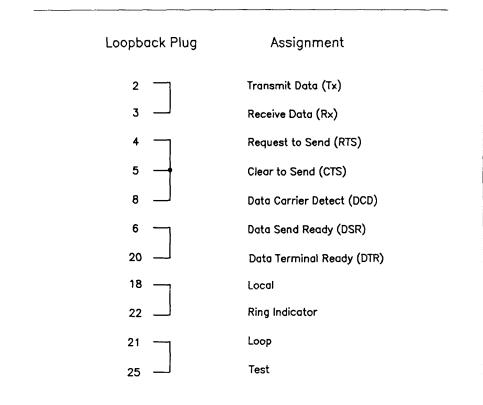

| RS-232-C 9-PIN LOOPBACK PLUG                                  | A-29 |

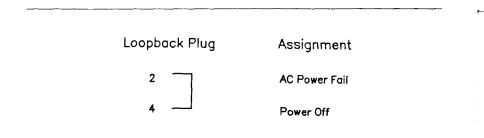

| UPS LOOPBACK PLUG                                             | A-31 |

| LINE PRINTER LOOPBACK PLUG                                    | A-32 |

Glossary

Index

(\_\_\_\_\_\_

# Illustrations

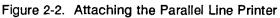

| Connecting a Terminal to Channel 0<br>Attaching the Parallel Line Printer | 2-5<br>2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main Processor Board<br>(CPU-01 Version)                                  | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                           | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

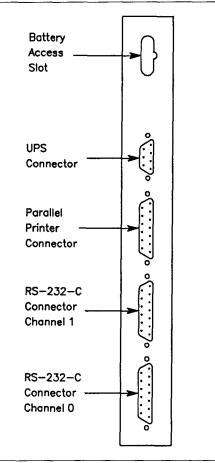

| (CPU-02 Version)                                                          | 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Crossed RS-232-C Cable Connections                                        | A-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Crossed RS-232-C Cable Construction                                       | A-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9-Pin to 25-Pin Cable Connections                                         | A-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

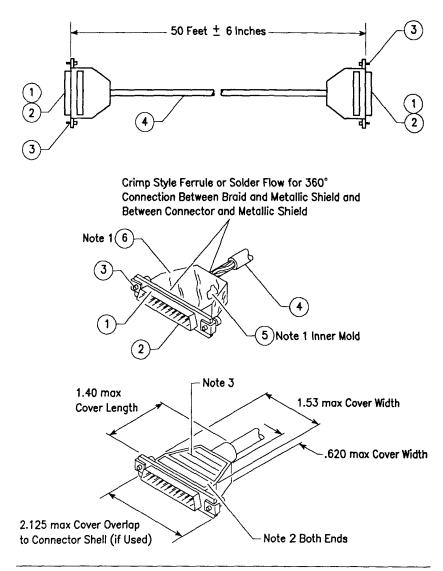

| 9-Pin to 25-Pin Cable Construction                                        | A-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Parallel Line Printer Cable                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Connections                                                               | A-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Parallel Line Printer Cable                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Construction                                                              | A-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bidirectional Parallel Cable                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Connections                                                               | A-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bidirectional Parallel Cable                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Construction                                                              | A-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RS-422 Cluster Cable Connections                                          | A-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RS-422 Cluster Cable Construction                                         | A-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 50-Pin SCSI Connector                                                     | A-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RS-232-C 25-Pin Loopback Plug                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Connections                                                               | A-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                           | Attaching the Parallel Line Printer<br>Main Processor Board<br>(CPU-01 Version)<br>Main Processor Board<br>(CPU-02 Version)<br>Crossed RS-232-C Cable Connections<br>Crossed RS-232-C Cable Construction<br>9-Pin to 25-Pin Cable Construction<br>9-Pin to 25-Pin Cable Construction<br>Parallel Line Printer Cable<br>Connections<br>Parallel Line Printer Cable<br>Construction<br>Bidirectional Parallel Cable<br>Connections<br>Bidirectional Parallel Cable<br>Construction<br>RS-422 Cluster Cable Connections<br>RS-422 Cluster Cable Construction<br>50-Pin SCSI Connector<br>RS-232-C 25-Pin Loopback Plug |

# Illustrations (continued)

| Figure A-13. | RS-232-C 9-Pin Loopback Plug  |      |

|--------------|-------------------------------|------|

| -            | Connections                   | A-29 |

| Figure A-14. | UPS Loopback Plug Connections | A-31 |

| Figure A-15. | Line Printer Loopback Plug    |      |

| -            | Connections                   | A-32 |

# Tables

| Table 1.   | Two-Letter Commands                   | iii  |

|------------|---------------------------------------|------|

| Table 2.   | Test Sequences                        | V    |

| Table 3-1. | Diagnostic Test Sequences             | 3-8  |

| Table 4-1. | Drive Identification Numbers          | 4-16 |

| Table 4-2. | System Priority Levels (SPLs)         | 4-25 |

| Table 5-1. | CPU-01 Diagnostic Tests               | 5-3  |

| Table 5-2. | Memory Subtests                       | 5-4  |

| Table 5-3. | Memory Subtests 2 Through 13          | 5-7  |

| Table 5-4. | Memory Subtests 20 Through 32         | 5-10 |

| Table 5-5. | Input for Memory Subtests 15, $20-32$ | 5-11 |

| Table 5-6. | Clock Subtests                        | 5-36 |

| Table 5-7. | Map RAM Subtests                      | 5-43 |

| Table 5-8. | Page Protection Subtests              | 5-49 |

| Table 5-9. | Line Printer Subtests                 | 5-54 |

| Table 6-1. | CPU-02 Diagnostic Tests               | 6-3  |

| Table 6-2. | Memory Subtests                       | 6-4  |

| Table 6-3. | Memory Subtests 2 Through 7           | 6-6  |

| Table 6-4. | Memory Subtests 15 and 20-32          | 6-10 |

| Table 6-5. | Input for Memory Tests 15 and 20-32   | 6-10 |

| Table 6-6. | Clock Subtests                        | 6-28 |

| Table 6-7. | Data Cache and Page Table Cache       |      |

|            | Subtests                              | 6-36 |

| Table 6-8. | Page Protection Subtests              | 6-47 |

| Table 6-9. | Line Printer Subtests                 | 6-51 |

$\overleftarrow{\Box}$

# Tables (continued)

| 7-3<br>7-5<br>7-6<br>7-7<br>7-8 |

|---------------------------------|

| 7-5<br>7-6<br>7-7               |

| 7-6<br>7-7                      |

| 7-7                             |

|                                 |

| 7-8                             |

|                                 |

| 7-10                            |

| 7-11                            |

| 7-11                            |

| 7-49                            |

| 7-76                            |

| 8-2                             |

| 8-8                             |

| 9-3                             |

| 10-3                            |

|                                 |

| 11-2                            |

| 12-3                            |

|                                 |

| 13-3                            |

| 14-2                            |

|                                 |

# Tables (continued)

| Table A-1. | Crossed RS-232-C Cable Parts List    | A-6  |

|------------|--------------------------------------|------|

| Table A-2. | 9-Pin to 25-Pin RS-232-C Cable Parts |      |

|            | List                                 | A-9  |

| Table A-3. | Parallel Printer Cable Parts List    | A-14 |

| Table A-4. | Parallel Printer Cable Parts List    | A-19 |

| Table A-5. | RS-422 Cable Parts List              | A-23 |

| Table A-6. | RS-232-C 25-Pin Loopback Plug Parts  | A-28 |

| Table A-7. | RS-232-C 9-Pin Loopback Plug Parts   | A-30 |

| Table A-8. | UPS Loopback Plug Parts              | A-31 |

| Table A-9. | Line Printer Loopback Plug Parts     | A-33 |

(\_\_\_\_\_

# **CHAPTER 1**

# **Overview**

## INTRODUCTION

The diagnostic tests enable you to comprehensively test all the equipment and capabilities of any S/MT Series computer system. You can execute the diagnostic tests regardless of your system configuration. The diagnostic performs the tests for equipment that is present and ignores the tests for equipment that is absent.

Note There are two different diagnostic tapes available for S/MT systems. Both are documented in this manual and each contain tests specific to the CPU-01 and CPU-02 versions of the Main Processor (CPU) board. Except where called out in the text, the tests for the rest of the system hardware are identical. The diagnostics tapes are not interchangeable. The CPU-02 version of the diagnostics will not run on a CPU-01 version of the Main Processor board, and vice versa. Make sure you have the right tape for your system.

The installation manual shipped with your system contains information on the different hardware components available with your system. Systems that can be tested with the diagnostics include:

- S/120 (a CPU-01 system)

- S/220 (a CPU-01 system)

- S/221 (a CPU-01 system)

- S/222 (a CPU-01 system)

- S/320 (a CPU-01 system)

- S/480 (a CPU-02 system)

- S/640 (a CPU-02 system)

Consult the current sales guide for a complete list and description of all S/MT Series computer systems and their Main Processor (CPU) boards.

(

### ABOUT THIS MANUAL

This manual documents S/MT Series diagnostics for release levels 6.0 and up.

#### Who Should Use This Manual -

This manual is intended for use by service personnel who are familiar with the S/MT Series computer systems and are capable of performing diagnostic tests on computerized equipment. Each diagnostic test is described according to what it tests, the language required to execute the test, and what the test output means.

#### Purpose of This Manual

This purpose of this manual is to:

- Help you ensure proper computer operation.

- Show you how to identify problems when they occur.

- Refer you to related documentation.

### **Manual Organization**

This manual consists of the following chapters that are organized to provide a guide to the diagnostic tests. The following paragraphs tell you which chapters to consult for the specific task you want to perform.

- Chapter 1, "Overview," provides a brief introduction to the S/MT Series diagnostics and this manual.

- Chapter 2, "Getting Started," explains how to properly connect the terminal and the optional parallel printer, and load the diagnostic programs from the QIC tape.

- Chapter 3, "Command Interpreter," describes the language required to execute the diagnostic programs.

- Chapter 4, "Two-Letter Commands," presents individual descriptions of two-letter commands.

- Chapter 5, "CPU-01 Diagnostic Tests," describes the diagnostic tests for systems using the CPU-01 version of the Main Processor (CPU) board.

- Chapter 6, "CPU-02 Diagnostic Tests," describes the diagnostic tests for systems using the CPU-02 version of the Main Processor (CPU) board.

- Chapter 7, "Disk and Tape Diagnostic Tests," contains hard disk and tape drive tests for systems using the CPU-01 and CPU-02 versions of the Main Processor (CPU) board.

- Chapter 8, "RS-232-C Diagnostic Tests," documents the diagnostic tests for the RS-232-C channels in your system.

- Chapter 9, "IOP Accelerator Diagnostic Tests," describes the tests for the Input/Output Processor (IOP) Accelerator Expansion board.

- Chapter 10, "Ethernet Combo Board Diagnostic Tests," describes the tests for the Ethernet Combo board.

- Chapter 11, "RS-422 Expansion Board Diagnostic Tests," documents the diagnostic tests for the RS-422 Expansion boards.

- Chapter 12, "VME Subsystem Diagnostic Tests," contains the subtests specific to the CMC VME board used to verify VME functions.

- Chapter 13, "VME Communication Controller Diagnostic Tests," documents the tests used to ensure the functionality of one or more VME Communication Controller cards.

- Chapter 14, "Miscellaneous Diagnostic Tests," includes tests for the MC68881 coprocessor, the Uninterruptible Power Supply (UPS), the VME Interface board, and some EEPROM tests.

- Appendix A, "Cable Specifications," contains pin assignments and information for making your own cables and the loopback connectors required for some diagnostic tests.

A glossary and appendix are also included.

#### How to Use This Manual

Each set of diagnostic tests is documented by hardware type and organized into chapters. Each chapter is separated and identified by a tabed page.

As you run a series of tests, refer to the specific chapter for a description of what each test does, how to run the test, and what you will see on the screen as the test is running.

Before beginning, read Chapters 1 through 4 to become familiar with the test requirements and command syntax.

#### **RELATED DOCUMENTATION**

The documents described below provide additional information related to the S/MT Series diagnostic tests.

#### • Installation

S/120 Installation S/220 Installation S/221 and S/222 Installation S/320 and S/640 Installation S/480 Installation

#### • Hardware

S/220 and S/320 Hardware S/120 Addendum to the S/220 and S/320 Hardware Manual S/MT Series CPU-02 Technical Reference S/480 Technical Reference S/MT Series I/O Processor (IOP) Expansion Technical Reference S/MT Series RS-422 Expansion Technical Reference S/MT Series RS-232-C Expansion Technical Reference S/MT Series VME Communications Controller Card Technical Reference S/MT Series VME Expansion Technical Reference S/MT Series Ethernet Combo Board Technical Reference

#### • System Administration S/MT Series CTIX Administrator's Reference

The S/120 Installation Manual contains procedures for locating, inspecting, and booting the S/120, and for attaching peripherals and installing expansion boards and hard disk drives. It also includes a summary of system status codes and instructions for building required cables.

The S/220 Installation Manual contains procedures for locating, inspecting, and booting an S/220 system, and for attaching peripherals and installing expansion boards and hard disk drives. The manual also includes a summary of system status codes and instructions for building required cables.

The S/221 and S/222 Installation Manual contains procedures for locating, inspecting, and booting S/221 and S/222 systems, and for attaching peripherals and installing expansion boards and hard disk drives. The manual also includes summaries of system status codes and instructions for building required cables.

The S/320 and S/640 Installation Manual contains procedures for installing, powering on, and booting S/320 and S/640 systems, and for connecting peripherals and adding expansion cards and hard disk drives.

The S/480 Installation Manual contains procendres for installing, powering on, and booting the S/480 system, and for connecting peripherals and adding expansion boards and hard disk drives.

The S/320 and S/220 Hardware Manual (Vols. 1 and 2) contains a functional description, software interface, and theory of operation for the S/320 and S/220 computer systems.

The S/MT Series CPU-02 Technical Reference Manual contains a functional description and user interface definition for the 25MHz Main Processor (CPU) board.

The S/480 Technical Reference Manual contains a functional description, software interface, and theory of operation for the S/480 system.

The S/MT Series I/O Processor (IOP) Expansion Board Technical Reference Manual contains a functional and circuitry description of the Input/Output Processor board, and a theory of operation and software interface description.

The S/MT Series RS-422 Expansion Technical Reference Manual describes the hardware on the RS-422 Expansion board including the clock, bus, and channel control. An onboard line printer interface is also described.

The S/MT Series RS-232-C Expansion Technical Reference Manual describes the hardware incorporated on the 10-port and 20-port boards at a functional block and component level, including descriptions of interrupt handling, processor interface, and RS-232-C I/O operations. The S/MT Series VME Communications Controller Card Technical Reference Manual contains a functional description and user interface for the VME Communications Controller card.

The S/MT Series VME Expansion Technical Reference Manual contains the functional and circuit description, theory of operation, and software interfaces for the VME Interface board.

The S/MT Series Ethernet Combo Board Technical Reference Manual contains the functional and circuitry description, and software interfaces for the Ethernet Combo board.

The S/MT Series CTIX Administrator's Reference Manual defines the responsibilities of a system administrator and provides procedures for the administrator to follow. The manual explains the concepts an administrator must understand to maintain the S/MT Series computer system, including user support, CTIX modes, CTIX file systems, peripheral devices, and troubleshooting procedures.

# **CHAPTER 2**

# **Getting Started**

#### INTRODUCTION

This chapter introduces the S/MT Series diagnostic tests. Procedures are included to connect a terminal and a parallel line printer to your system and to load the diagnostic tests. Also included is a brief description of how the tests operate.

The diagnostic tests are used to ensure correct system operation and to diagnose computer malfunctions when they occur. There are three levels of diagnostic tests:

- Tests evaluate specific S/MT Series subsystems.

- Subtests individual parts of a test (which combine to form the test).

- Test sequences predefined combinations of tests and subtests.

### CONNECTING THE TERMINAL

Before you begin, make sure that you connect only *one* terminal to Channel 0 on the Main Processor (CPU) board. You must follow the directions in this section to ensure that the diagnostics will work properly.

You can use several types of terminals:

- Convergent Technologies TO-250 and TO-300

- Any terminal with asynchronous RS-232-C protocol, such as the Freedom 100 or VT-100 terminals

- A PT or GT-type terminal used in Emulate mode (see "Starting Up Terminals in Emulate Mode" later in this chapter)

- Any ASCII or ANSI compatible terminal

Consult the installation manual for the terminal you are using and make sure the terminal is configured to operate as follows:

- Baud rate 9600

- Data bits 8

- Stop bits -1

- Parity none

You need a crossed (twisted) RS-232-C cable with 25-pin connectors on both ends to complete the connection (see Appendix A, "Cable Specifications," for cabling information and pin assignments).

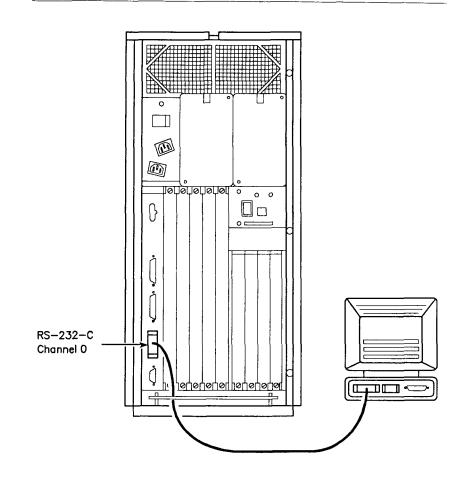

To connect a terminal to Channel 0 on the Main Processor (CPU) board (see Figure 2-1):

- 1. Attach the 25-pin connector on one end of the cable to Channel 0 on the Main Processor (CPU) board.

- 2. Attach the 25-pin connector at the other end of the cable to the RS-232-C channel on the terminal.

- Note The diagnostics contain a command that lets you change the port after you load the diagnostic program. To issue diagnostic commands from another port, refer to the two-letter command CO as described in Chapter 4, "Two-Letter Commands."

### STARTING UP THE TERMINAL

Any RS-232-C terminal will operate as the console terminal for displaying the diagnostics command modes and subtests. However, if you use a PT or GT-type terminal, you need to start up the terminal in Emulate mode, which makes the system see the PT or GT as an RS-232-C terminal.

To start up a PT or GT terminal in Emulate mode:

1. Connect the PT or GT to Channel 0 on the Main Processor (CPU) board as shown in Figure 2-1.

Figure 2-1. Connecting a Terminal to Channel 0

2. Turn the terminal off.

- 3. Press the space bar while simultaneously turning the terminal on. (The boot ROM prompt does not appear if you release the space bar before the prompt is displayed.)

- 4. Continue to hold the space bar down until the boot ROM prompt is displayed.

The prompt for a GT with version 1.0 or 2.0 boot ROM looks like this:

V 2.0 T 222 F 801 R 09 P 00 1 B,C,E,F,I,P,R,S,T:

The prompt for a PT with version 1.0 boot ROM looks like this:

V 1.0 B,C,E,F,M,R,S,T:

The prompt for a PT with Version 2.0 boot ROM looks like this:

V 2.0 B,C,E,F,I,P,R,S,T,W:

#### 5. Type e.

The terminal now starts up in Emulate mode and functions like an RS-232-C terminal. Until you install the diagnostics, the screen will be blank.

There are some restrictions for PT and GT terminals that contain a version 1.0 boot ROM:

- You cannot use the SHIFT key. This means that you cannot use the question mark (?), colon (:), the backslash (\), or any lowercase letters. Use the following keystrokes in place of these:

- Type / instead of ?

- Type . instead of :

- Type uppercase letters instead of lowercase letters.

- Use the character 8 on the numeric keypad to type a vertical bar (|).

You can still display the command modes and subtests when using a terminal containing a version 1.0 boot ROM. Simply type the two letter command (if toggling a command mode) or the test sequence letter (if executing a test sequence). You can also execute tests and subtests by specifying their respective numbers.

## CONNECTING A PARALLEL PRINTER

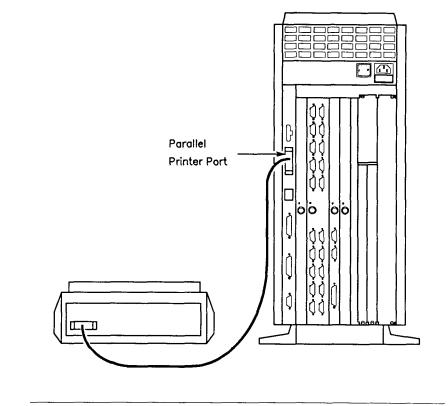

A parallel line printer can be attached to the Parallel Printer connector on the Main Processor (CPU) board to print the output from the diagnostic tests. (You cannot connect a serial printer to the Main Processor board.)

You need a parallel printer cable to complete the connection (see Appendix A, "Cable and Connector Specifications," for cabling information and pin assignments). Be sure that the end of the cable that attaches to the Main Processor (CPU) board has a DB25 connector.

Connect the parallel line printer as follows:

- 1. Attach the DB25 end of the Centronicscompatible parallel printer cable to the connector labeled Parallel Printer on the Main Processor (CPU) board.

- 2. Attach the connector at the other end of the cable to the connector on the parallel line printer as shown in Figure 2-2.

- Note Load the diagnostic test program as described under "Loading the Diagnostic Tests." Then enable the parallel printer by performing the line printer echo test as described in Chapter 4.

ĺ,

#### LOADING THE DIAGNOSTIC TESTS

After you connect the terminal and, if necessary, the parallel line printer, you can load the diagnostic tests from the quarter-inch cartridge (QIC) tape. The diagnostic tests can be loaded when the system is running the CTIX operating system or when the power is turned off. The following information describes each situation.

Note If you power up your system with the QIC tape in the tape drive and without first connecting a terminal to Channel 0, the diagnostic executes system test sequence d (described in Chapter 3, "Command Interpreter") until an error occurs. If an error does occur. the error light-emitting diode (LED) on the status panel illuminates. The error message is displayed when you connect a terminal to Channel 0 on the Main Processor (CPU) board. Refer to the installation manual for your system for a summary of error and status codes. Refer to the hardware manual for your system for a complete description of the boot sequence.

### With CTIX Running

When the CTIX operating system is running, you must terminate all currently running processes before loading the diagnostic tests. Refer to the *S/MT Series CTIX Administrator's Reference Manual* for instructions on properly shutting down the operating system.

Wait for the following prompt to appear on the screen:

OK to stop or reset processor

Then load the diagnostics as follows:

- 1. Insert the diagnostic tape into the tape drive.

- 2. Type reboot

- 3. Press **RETURN**, or press down the Reset switch on the front of the Main Processor (CPU) board.

An example of the screen that is displayed when the diagnostics are fully loaded is given in the section "Diagnostic Screen."

#### With Power Off

To load the diagnostic tests when power is off:

- 1. Insert the diagnostic tape into the tape drive.

- 2. Lock the system in "reset" by placing the Reset switch on the front of the Main Processor (CPU) board in the up position.

- 3. Press the power switch on the rear of your system to the ON position.

- 4. If applicable, power on any external expansion devices connected to your system.

- 5. Press down the Reset switch on the front of the Main Processor (CPU) board.

The system powers up and loads the diagnostic tests into memory. An example of the screen that is displayed when the tests are fully loaded is given in the section "Diagnostic Screen." (

## DIAGNOSTIC SCREEN \_\_\_\_\_

The diagnostic screen looks like this:

| MIGHTYFRAME MC68020 DIAGNOSTIC DEBUGGER V2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COPYRIGHT 1983, 1984, 1985, 1987 BY CONVERGENT TECHNOLOGIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MIGHTYFRAME DIAGNOSTICS-V <6.XX.XX > release (XX)<br>(XXX XXX X XX:XX PST 19XX - /usr/src/miti/diag)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| System configuration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| X mega bytes of memory<br>XMb memory board in slot MX<br>MC68881 coprocessor is not present<br>VME expansion board is not present<br>Ethernet Combo board in slot X is configured for dma slot X<br>RS232 channels 2 to 11 22 to 27 in slots: IO1 IO3<br>IOP board is present<br>Drive 0 is present [6.0bt]<br>Drive 1 is present [6.0bt]<br>Drive 2 is present [5.1bt]<br>Memory tests will begin at 0xXXXXX, end at 0xXXXXX<br>Parity interrupts enabled, Disk/QIC Interrupt Mode enabled<br>The time on the clock calendar is: XXX XXX XXXXXXX GMT 19XX |

| command >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

The diagnostic screen displays the following information:

- The system configuration, which lists the equipment acknowledged by the diagnostic

- The location in memory occupied by the diagnostic programs

• The diagnostic command prompt

This information becomes more significant as you progress through this manual. For now, leave the screen displayed on the terminal while you continue with this chapter.

### **DIAGNOSTIC TEST CONDITIONS**

Listed below are several conditions to consider before you execute the diagnostic tests: