# QUARTER-INCH CARTRIDGE TAPE HARDWARE MANUAL

This equipment generates, uses, and can radiate radio frequency energy. If not installed and used in accordance with the installation it may interfere with instructions, radio The equipment has been tested communications. and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, which users may be required to correct at their own expense.

#### Specifications Subject to Change.

Convergent Technologies and NGEN are registered trademarks of Convergent Technologies, Inc.

Convergent, CT-DBMS, CT-MAIL, CT-Net, CTIX, CTOS, DISTRIX, Document Designer, The Operator, AWS, CWS, IWS, MegaFrame, MiniFrame, MiniFrame Plus, and X-Bus are trademarks of Convergent Technologies, Inc.

CP/M-86 is a registered trademark of Digital Research. MS and GW are trademarks of Microsoft Corp. UNIX is a trademark of Bell Laboratories.

First Edition (December 1985) A-09-00929-01

Copyright © 1985 by Convergent Technologies, Inc., San Jose, CA. Printed in USA.

All rights reserved. Title to and ownership of the documentation contained herein shall at all times remain in Convergent Technologies, Inc., and/or its suppliers. The full copyright notice may not be modified except with the express written consent of Convergent Technologies, Inc.

NOTE

### QUARTER-INCH TAPE: USE AND MAINTENANCE

#### -CAUTION-

You must follow the guidelines outlined below to ensure satisfactory performance and full service life of your quarter-inch cartridge (QIC) drive and tapes. Be sure the writeprotect cam is in the correct position. You should attain a soft (correctable) error rate of 1 in  $1 \times 10^8$  bit transfers, a cartridge life of 2000 passes (one pass is equivalent to winding the tape its full length from one end to the other), and a drive life of 5 years.

Failure to follow these guidelines can result in poor performance (excessive errors); damage to the tape cartridges, tape drive, or both; loss of interchangeability; or a combination of these conditions.

Drive and Cartridge Care. Treat cartridges with care and use them in an environment with the following conditions:

Maximum wet bulb temperature:

79°F (26°C)

Operating temperature: 41°F to 113°F (5°C to 45°C)

20% to 80% noncondensing

Relative humidity:

Altitude: -1000 feet to 15,000 feet

Be sure to retension the cartridge before its initial pass (see below). Protect the drive and cartridges from excessive shocks, which can impair the drive alignment and cartridge tension. Do not expose the tape cartridge to magnetic fields, such as from CRT screens or power sources. Approved Cartridge Use. Use only approved tape cartridges to attain the specified error rate standard. Other cartridges may initially meet this standard, yet degrade in reliability over the specified cartridge life. The following cartridge tapes are approved: the DC-600A and DC-615A (3M Corp.), and the 10000FTPI (Data Electronics, Inc.).

<u>Cartridge Retensioning.</u> Keep the cartridge properly tensioned to ensure full life service and data reliability. Failure to adequately tension the cartridge will damage the cartridge and destroy data on the tape. To retension the cartridge, use the tape unit retension command. (See Section 4 of the Quarter-Inch Cartridge Tape for NGEN Manual for details.)

With normal use, retension the cartridge every eight hours. When using the tape drive extensively in start/stop mode, retension the cartridge once every two hours.

Tape Head Cleaning. Clean the tape drive read/write head assembly after any initial pass of a new cartridge; once after two hours (of actual tape movement) when using a new cartridge; and at least once every eight hours thereafter for the life of the tape. In addition, if the tape drive has not been used for a week or longer (or if you are not sure how long the tape drive has been unused), clean the tape head before use.

Failure to clean the heads will result in excessive data errors and may decrease the life of the drive. (See Appendix B of the Quarter-Inch Cartridge Tape for NGEN Manual for details.)

# CONTENTS

| RE | LATED DOCUMENTATION                              | vii  |

|----|--------------------------------------------------|------|

| CO | NVENTIONS                                        | ix   |

| 1  | OVERVIEW                                         | 1-1  |

|    | INTRODUCTION TO THE MANUAL                       | 1-1  |

|    | GENERAL DESCRIPTION                              | 1-2  |

|    | MAJOR COMPONENTS                                 | 1-3  |

| 2  | ARCHITECTURE                                     | 2-1  |

|    | INTRODUCTION                                     | 2-1  |

|    | X-BUS INTERFACE                                  | 2-3  |

|    | Module Identification                            | 2-3  |

|    | Implementation                                   | 2-4  |

|    | Tape Control/Status Registers                    | 2-5  |

|    | TAPE DRIVE READ/WRITE                            | 2-8  |

|    | Reading Data from Tape to Processor              |      |

|    | Module<br>Writing Data from the Processor Module | 2-8  |

|    | to Tape                                          | 2-10 |

|    | COMMAND AND STATUS REGISTERS                     | 2-12 |

|    | Read Tape Status Byte Register                   | 2-12 |

|    | CONTROL CIRCUITRY TO TAPE DRIVE                  |      |

|    | INTERFACE                                        | 2-17 |

|    | DMA TRANSFER MODE 3                              | 2-17 |

|    | Direct Memory Access                             | 2-17 |

|    | Mode 3                                           | 2-18 |

|    | ROM ADDRESSING                                   | 2-18 |

|    | MODULE I/O ADDRESS SUMMARY                       | 2-19 |

| 3           | THEORY OF OPERATION                    | 3-1   |

|-------------|----------------------------------------|-------|

|             | CIRCUIT DESCRIPTIONS                   | 3-2   |

|             | X-BUS GATE ARRAY                       | 3-2   |

|             | Module Identification                  | 3-8   |

|             | Module Identification Read             | 3-1Ø  |

|             | Module Identification Write            | 3-11  |

|             | I/O Read and Write                     | 3-13  |

|             | Bootstrap Requests from the CPU        | 3-16  |

|             | CPU ROM Read                           | 3-17  |

|             | TAPE DRIVE OPERATION                   | 3-20  |

|             | Read Status Command                    | 3-20  |

|             | Read Tape Data Command                 | 3-26  |

|             | Write Tape Data Command                | 3-39  |

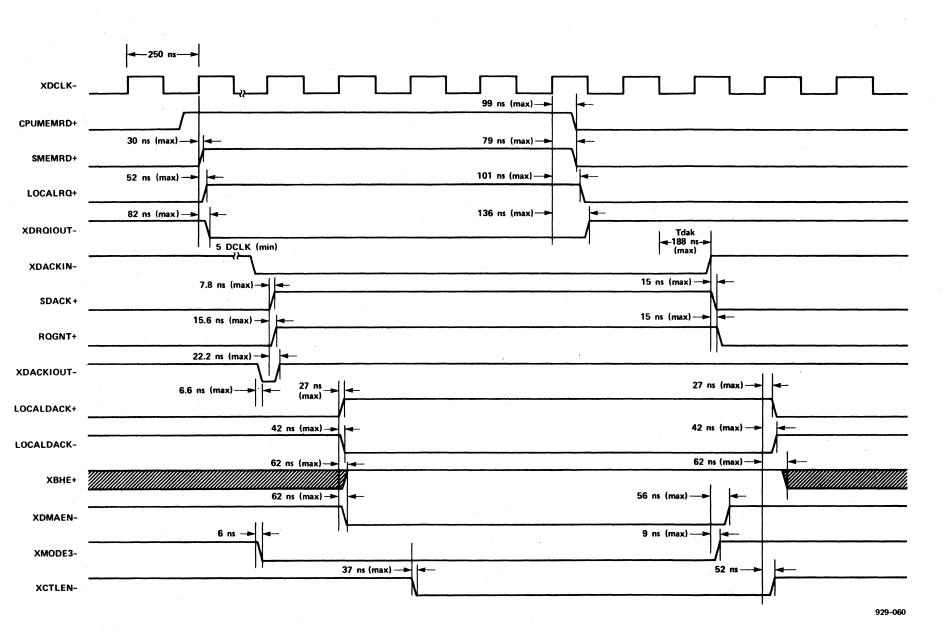

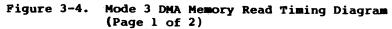

|             | MODE 3 DMA                             | 3-46  |

|             | Control Arbitration                    | 3-46  |

|             | DMA Memory Read                        | 3-46  |

|             | DMA Memory Write                       | 3-58  |

|             | TAPE DRIVE INTERFACE LOGIC             | 3-61  |

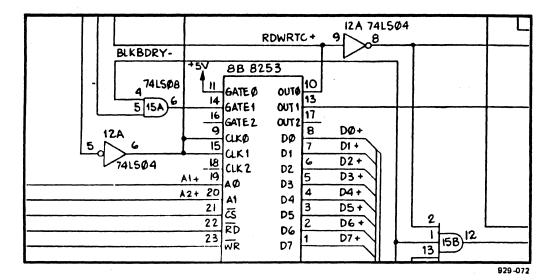

|             | 8253 PROGRAMMABLE INTERVAL TIMER       | 3-64  |

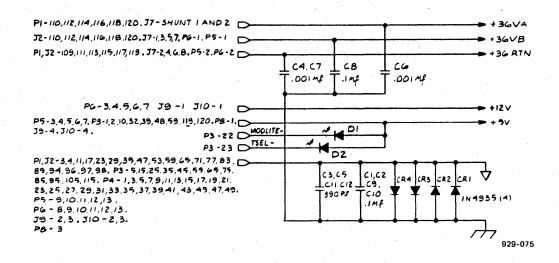

|             | POWER SUPPLIES                         | 3-69  |

|             | QIC TAPE MODULE INTERCONNECT           |       |

|             | WIRE LIST                              | 3-70  |

|             |                                        |       |

|             |                                        |       |

| 4           | DRIVE SPECIFICATIONS                   | 4-1   |

|             |                                        |       |

|             |                                        |       |

| API         | PENDIX A: QUARTER-INCH CARTRIDGE TAPE  |       |

|             | MODULE SPECIFICATIONS                  | A-1   |

|             |                                        |       |

|             |                                        |       |

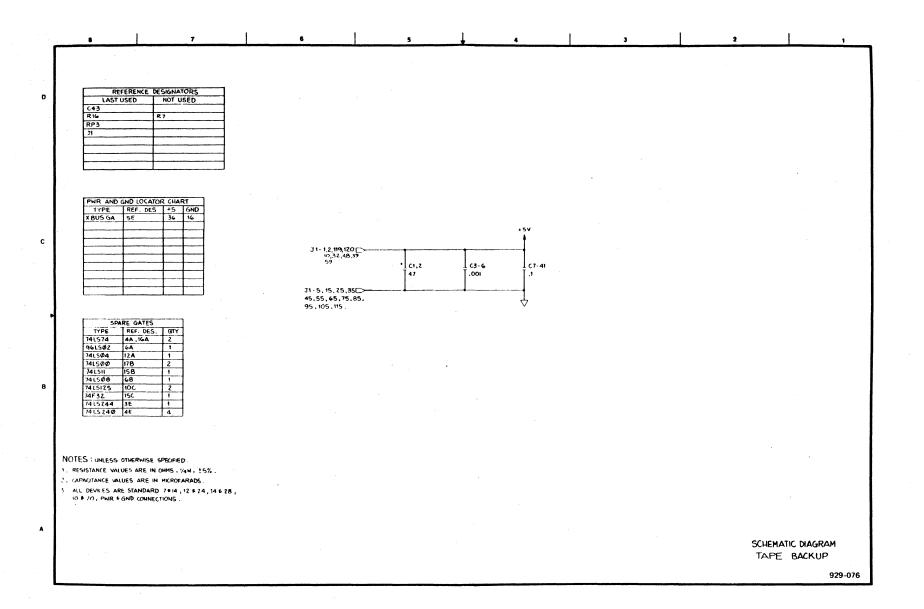

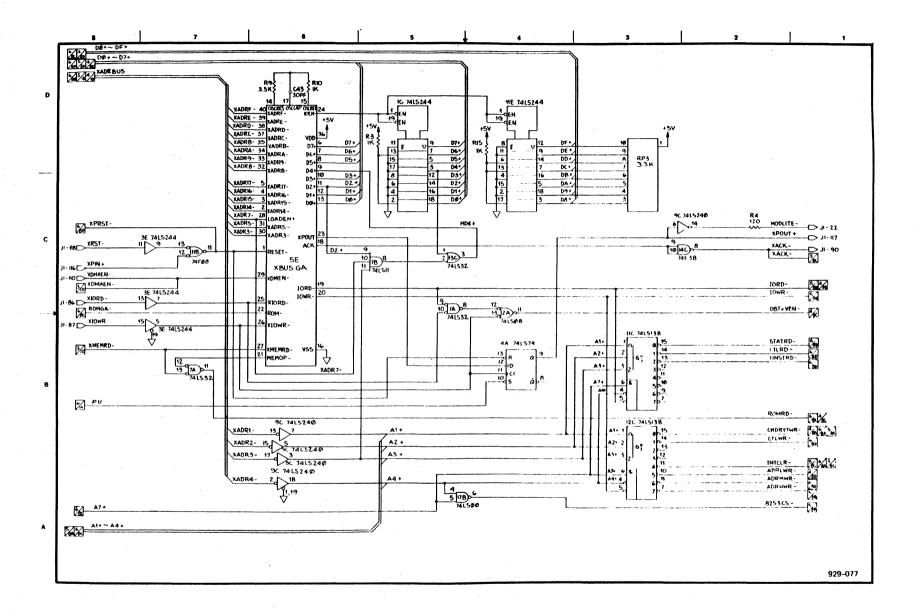

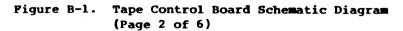

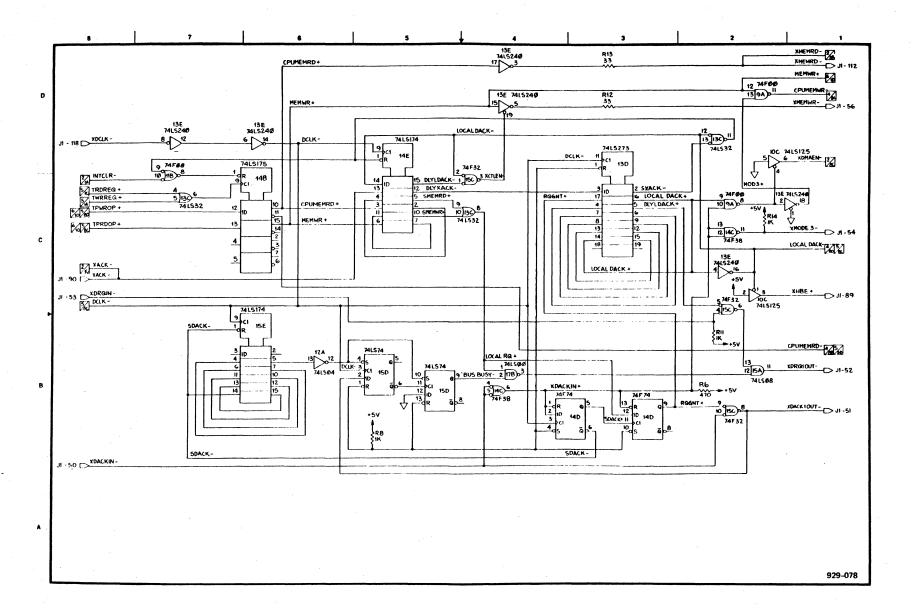

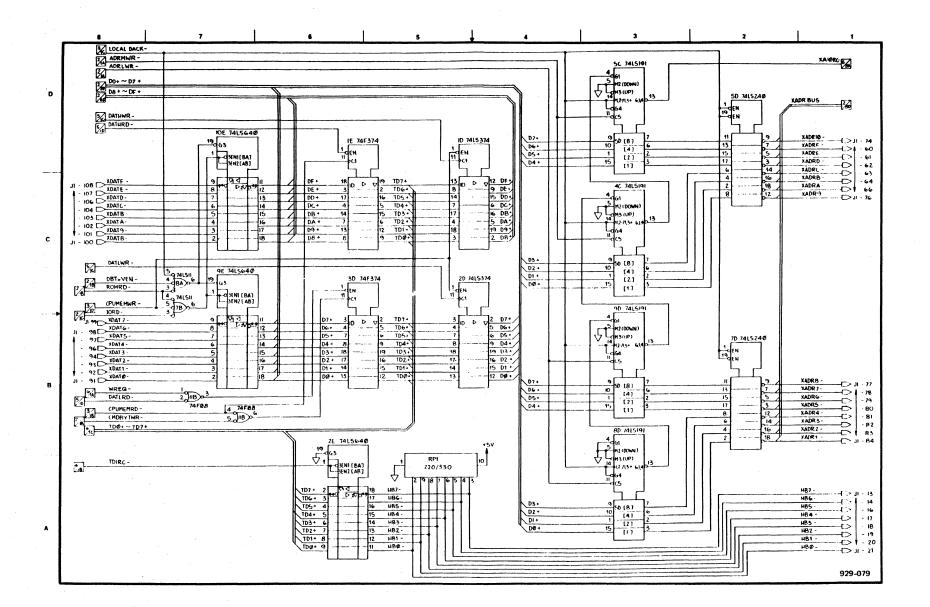

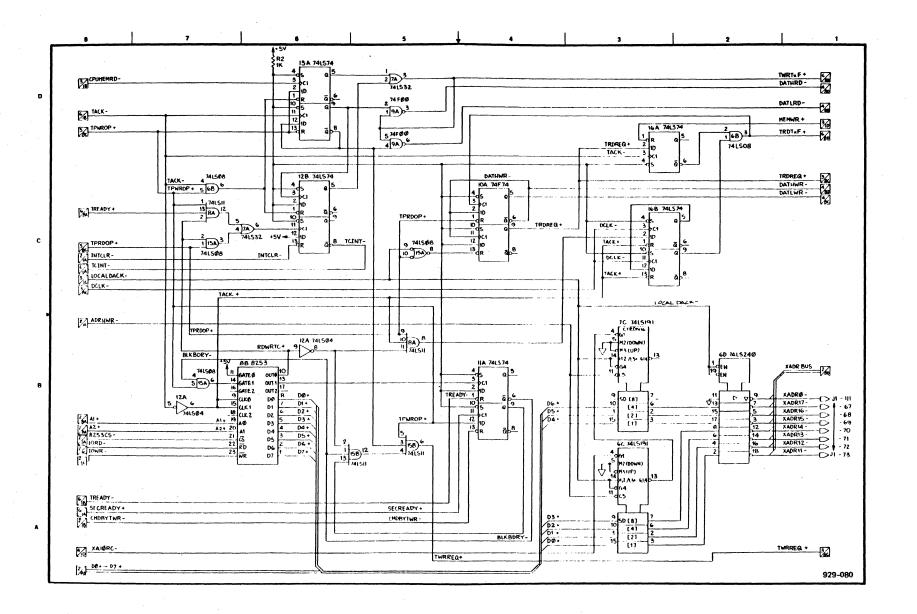

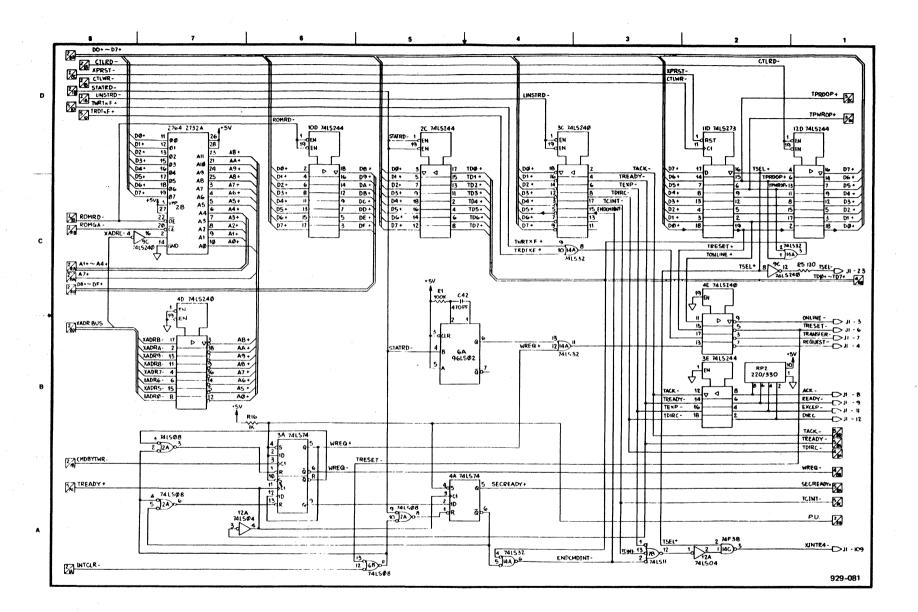

| APF         | PENDIX B: TAPE CONTROL BOARD SCHEMATIC |       |

|             | DIAGRAMS                               | B-1   |

|             |                                        |       |

|             |                                        |       |

| A DE        | PENDIX C: MAINTENANCE                  | C-1   |

| AF E        | ENDIA C: MAINIENANCE                   | C-1   |

|             |                                        |       |

| <b>01</b> 0 |                                        |       |

| GIIC        | OSSARY Glossa                          | iry-1 |

|             |                                        |       |

|             |                                        |       |

| IND         | DEX Inc                                | lex-1 |

|             |                                        |       |

iv Quarter-Inch Cartridge Tape Hardware Manual

# LIST OF FIGURES

# Figure

| 1-1. | Quarter-Inch Cartridge Tape Module | 1-2  |

|------|------------------------------------|------|

| 2-1. | Quarter-Inch Cartridge Tape Module |      |

|      | Functional Block Diagram           | 2-2  |

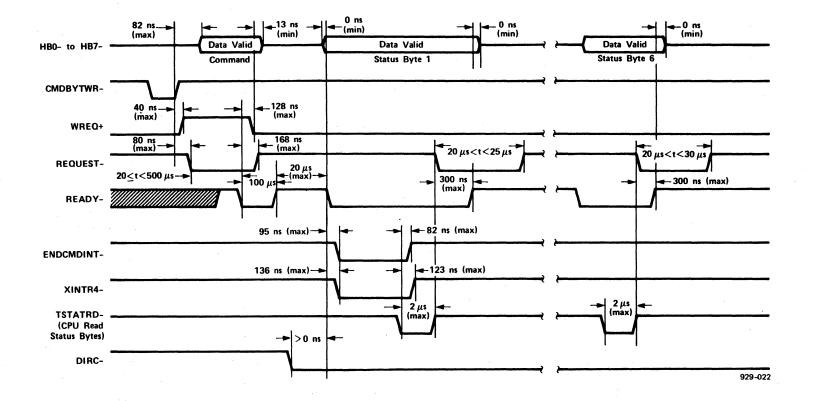

| 3-1. | Read Status Command Timing Diagram | 3-21 |

| 3-2. | Read Tape Data Command Timing      |      |

|      | Diagram                            | 3-27 |

| 3-3. | Write Tape Data Command Timing     |      |

|      | Diagram                            | 3-41 |

| 3-4. | Mode 3 DMA Memory Read Timing      |      |

|      | Diagram                            | 3-49 |

| 3-5. | Mode 3 DMA Memory Write Timing     |      |

|      | Diagram                            | 3-59 |

| B-1. | Tape Control Board Schematic       |      |

|      | Diagrams                           | B-3  |

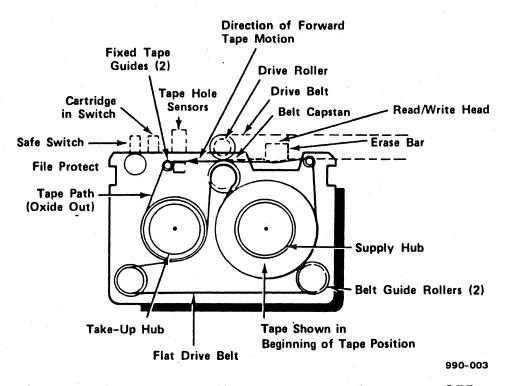

| C-1. | Internal Components of the DC-600A |      |

|      | Quarter-Inch Cartridge Tape        | C-1  |

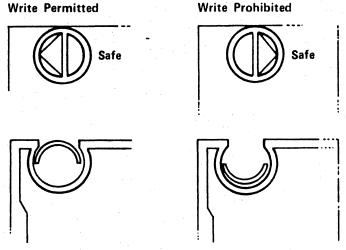

| C-2. | Tape Write Protect Plug Positions  | C-2  |

# LIST OF TABLES

# Table

# Page

| 2-1.<br>3-1. | I/O Address Summary<br>X-Bus Gate Array Pin Assignments | 2-20 |

|--------------|---------------------------------------------------------|------|

| 3-2.         | and Functions<br>Tape Drive Control Circuitry Control   | 3-3  |

|              | Lines                                                   | 3-62 |

| 3-3.<br>3-4. | Tape Drive Control Lines                                | 3-63 |

|              | Pin Assignments and Functions                           | 3-66 |

## **RELATED DOCUMENTATION**

The documents described below provide additional information related to the contents of this For Convergent manual. a complete list of Technologies<sup>®</sup> documentation, see the "Guide to Technical Documentation" in the Executive Manual or similar command-line interpreter manual for your operating system.

#### CONVERGENT TECHNOLOGIES DOCUMENTATION

Introductory

Installation Guide (NGEN) Operator's Guide (NGEN)

Hardware

Diagnostics Manual Floppy/Hard Disk Manual Processor Manuals Software Debugger

The NGEN <u>Installation Guide</u> describes the procedure for unpacking, assembling, cabling, and powering up an NGEN workstation.

The NGEN <u>Operator's Guide</u> is a link between the user and the workstation. It describes the operator controls, use of the floppy disk drives, how to verify workstation operations, and how to use software release notices.

The NGEN <u>Diagnostics Manual</u> outlines the tests used to verify proper operation of the modules of a workstation. The manual describes tests for individual modules, along with bootstrap procedures and customization programs. The <u>Floppy/Hard Disk Manual</u> describes the architecture and theory of operation for the Floppy/ Hard Disk Module. It discusses the applicable disk drives and controllers, and contains the applicable OEM disk drive manuals.

The <u>Processor Manuals</u> describe the respective Processor Modules. Each manual (a two-volume set) covers one processor module and details the architecture and theory of operation of the printed circuit boards, external interfaces, and memory expansion, as well as the X-Bus specifications.

The <u>Debugger Manual</u> describes the Debugger, which is designed for use at the symbolic instruction level. It can be used in debugging C, FORTRAN, Pascal, and assembly language programs. (COBOL and BASIC, in contrast, are more conveniently debugged using special facilities described in their respective manuals.)

#### VENDOR DOCUMENTATION

The boards that make up the Quarter-Inch Cartridge Tape Module are dependent upon programmable largescale integration (LSI) circuitry to perform their functions. Since only hardware functions and software interfaces of the LSI circuitry are summarized in this manual, see the following for additional information:

- <u>Intel Component Data Catalog</u>. Santa Clara,

CA: Intel Corporation, 1980.

- Intel Microprocessor and Peripheral Handbook. Santa Clara, CA: Intel Corporation, 1980.

# viii Quarter-Inch Cartridge Tape Hardware Manual

# CONVENTIONS

# NUMBERS

Numbers used in this manual are written in decimal unless suffixed with "h" for hexadecimal. For example, 10h = 16 and 0FFh = 255.

# SIGNAL NAMES

Signal names used in this manual are suffixed with plus (+) and minus (-) to distinguish active-high from active-low signals, respectively. An example of a RD (Read) signal is as follows:

| Signal Name | Logical State              | Voltage Level |

|-------------|----------------------------|---------------|

| RD-         | Ø (active)<br>l (inactive) | Low<br>High   |

| RD+         | Ø (inactive)<br>l (active) | Low<br>High   |

### 1 OVERVIEW

#### INTRODUCTION TO THE MANUAL

This manual is written for the engineer who tests or services the Quarter-Inch Cartridge (QIC) Tape Module electronics, or writes or modifies system software for use with the workstation. This manual does not, however, support modifications to existing hardware. The manual is divided into the following chapters:

o Overview

- o Architecture

- o Theory of Operation

- o Drive Specifications

Chapter 1, "Overview," describes the capabilities of the QIC Tape Module and its major components.

Chapter 2, "Architecture," covers the tape control circuitry in terms of its applicable software interface to hardware components. Applicable command and status registers for the control circuitry are defined. In addition, the X-Bus identification scheme is summarized.

Chapter 3, "Theory of Operation," details the component-level circuit description of the QIC Tape Module. In addition, an interconnect wire list is provided.

Chapter 4, "Drive Specifications," contains the manufacturer's manual for the tape drive.

In addition, Appendix A contains QIC Tape Module specifications, Appendix B contains the schematic diagrams for the QIC Tape Module, and Appendix C contains the cleaning instructions for the drive heads.

## GENERAL DESCRIPTION

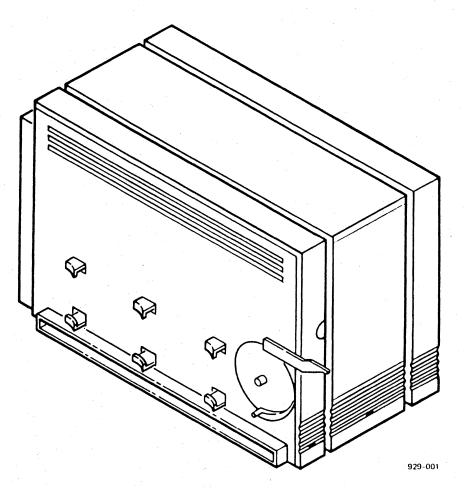

The QIC Tape Module, shown in Figure 1-1, consists of a single modular assembly and contains the circuitry necessary to provide 55M bytes of storage on one DC-600A, quarter-inch cartridge tape.

Figure 1-1. Quarter-Inch Cartridge Tape Module

#### MAJOR COMPONENTS

The major components of the QIC Tape Module include the following:

- o the enclosure, which houses the drive and the Tape Drive Control board

- o the Tape Drive Control board, mounted vertically on the left side of the enclosure (with module facing front)

- o one tape drive, mounted vertically in the enclosure

- o the motherboard, which lies on the bottom of the enclosure

- o two dc/dc power converters that plug into the motherboard, one supplying +12 Vdc and one supplying +5 Vdc

The major components used for tape drive control logic are on the Tape Drive Control board, and include

- o tape drive control circuitry

- o one X-Bus Gate Array, for the X-Bus interface

- o one 8253 programmable interval timer

#### 2 ARCHITECTURE

# INTRODUCTION

This chapter provides information for the systems programmer, engineer, or technician, who needs to understand the Quarter-Inch Cartridge (QIC) Tape Module hardware at a functional block level, and who must program the devices within the QIC Tape Module.

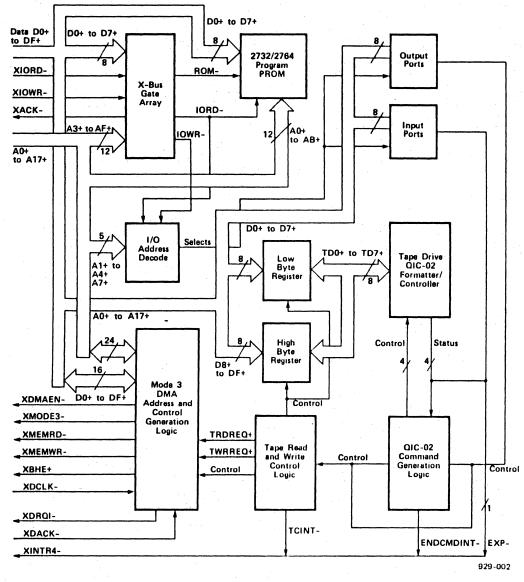

A functional block diagram is shown in Figure 2-1. Each block is described in this chapter in relation to the programmable device or devices performing the applicable function in the workstation. The nature of the function and how it is implemented is described. In addition, specific status and command registers are examined.

The following subjects are discussed:

- o X-Bus interface

- o tape control/status registers

- o tape drive read/write operation

- o tape drive command and status registers

- o tape drive control to tape drive interface

- o DMA transfer mode 3

- o ROM addressing

- o Module I/O address summary

Figure 2-1. Quarter-Inch Cartridge Tape Module Functional Block Diagram

#### X-BUS INTERFACE

The I/O ports on the QIC Tape Module are partially defined by the module base I/O address issued by the Processor Module. For example, the Status register resides at port XX80h, where XX is the module address and 80h is the register address. Upon either a power-up or a manual reset, the bootstrap ROM program in the Processor Module assigns a unique I/O base address to each module that is physically attached to the X-Bus.

### MODULE IDENTIFICATION

A power-up reset, manual (push-button) reset, or any I/O operation to specific ports in your Processor Module, resets all X-Bus modules except the Processor Module. Only the module immediately to the right of the Processor Module is enabled. This module identifies itself by placing a type/state word on the data bus when port  $\emptyset$  is read by the Processor Module.

The Processor Module writes to port  $\emptyset$ , a base I/O address that corresponds to a register in the module and defines the range of I/O addresses reserved for the module's use. Writing to port  $\emptyset$ also causes the module to reenable the X-Bus connection to the next module, and to ignore subsequent reads and writes to and from port  $\emptyset$ . This allows the Processor Module, to repeat the process for each module, beginning at the module adjacent to the Processor Module and repeating the process for each module to the right.

A ready timeout, signaled by a nonmaskable interrupt (NMI) when accessing port Ø, indicates that no additional modules are available.

#### IMPLEMENTATION

The module identification scheme is implemented by hardware as follows:

- o All modules on the X-Bus are assigned an input signal line (XPIN) and are required to generate an output signal line (XPOUT). The input signal always enters a module on the module's left side, and the output signal always exits the module on the module's right side.

- o During power-up, all modules reset an internal flip-flop to drive XPOUT low.

- o The XPIN line of the module closest to the Processor Module is controlled by the Processor Module. When XPIN is low, the I/O register clears.

- o When a module's XPIN is high and its XPOUT is low, the base I/O address is zero.

- reads 0 The Processor Module port Ø to identify the module (in this case, the QIC Tape Module) and then writes a byte to the low-order eight bits of the data bus, which become the high-order eight bits of the module's I/O address range (256 byte-ports or 128 word-ports). This write also enables the XPOUT line in the module, which allows the next module on the right to undergo the same operation.

Eight-bit devices are not required to scan the high-order byte of a port. Therefore, the base I/O address is written to the low-order byte of port 0. This corresponds to the high-order byte of the 16-bit base address, and defines a range of up to 256 port addresses reserved for the QIC Tape Module's use.

2-4 Quarter-Inch Cartridge Tape Hardware Manual

The Processor Module is always referred to as module  $\emptyset$ , the first module to the right of the Processor Module is referred to as module 1, and The bootstrap ROM always writes this so on. module number to the low byte of port Ø when it performs the identification polling sequence. Therefore, the module to the right of the Processor Module uses I/O ports ØlØØh through ØlFFh, the next module to the right uses ports Ø2ØØh through Ø2FFh, and so on, depending on how many modules are used. The bootstrap ROM also builds an array of the module type/state words returned by each module, and stores this table in memory for the system.

#### TAPE CONTROL/STATUS REGISTERS

The following registers are described in detail:

- o Read Tape Control registers

- o Write Tape Control registers

- o Read Tape Line Status registers

#### READ TAPE CONTROL REGISTER (XX82h)

#### Data Bit Function

- Ø Tape Reset (TRESET+). Resets the tape drive when asserted for at least 20 microseconds. This signal is the inverted RESET- of the drive.

- 1 Tape On Line (TONLINE+). This signal is the inverted ONLINE- signal of the drive.

- 2 to 4 Reserved.

| Data | Bit | Function |

|------|-----|----------|

|      |     |          |

Tape Write Operation (TPWROP+). When high, it enables the tape write operation.

Tape Read Operation (TPRDOP+). When high, it enables the tape read operation.

Tape Select (TSEL+). Tape selected light on the motherboard and interrupt enabled.

# WRITE TAPE CONTROL REGISTER (XX82h)

## Data Bit Function

Ø

1

5

6

5

6

7

Tape Reset (TRESET+). Resets the tape drive when asserted for at least 20 microseconds. This signal is the inverted RESET- of the drive.

Tape On Line (TONLINE+). This signal is the inverted ONLINE- signal of the drive.

2 to 4 Reserved.

Tape Write Operation (TPWROP+). When high, it enables the tape write operation.

Tape Read Operation (TPRDOP+). When high, it enables the tape read operation.

Tape Select (TSEL+). Tape selected light on the motherboard and interrupt enabled.

#### READ TAPE LINE STATUS REGISTER (XX84h)

## Data Bit Function

2

4

5

- Ø Tape Acknowledge (TACK+). Reflects the inverted ACKNOWLEDGE- signal of the tape drive.

- 1 Tape Ready (TREADY+). Reflects the inverted READY- signal of the drive.

- Tape Exception (TEXP+). Reflects the inverted EXCEPTION- signal of the drive.

- 3 Tape Direction (TDIRC+). Reflects the DIRECTION- signal of the drive.

- Terminal Count Interrupt (TCINT+). When set, TCINT+ signals that terminal count is reached in the read/write operation.

- End of Command Interrupt (ENDCMDINT+). When set, ENDCMDINT+ signals the completion of a command.

- 6 Reserved.

- 7 Reserved.

#### INTERRUPT CLEAR REGISTER (PORT XX88h)

A write to this register with any value clears the interrupt condition bits TCINT+ (bit 4) and ENDCMDINT+ (bit 5) in the Read Tape Line Status register (XX84h).

## TAPE DRIVE READ/WRITE

READING DATA FROM TAPE TO PROCESSOR MODULE

The sequence to issue the read command is as follows:

- The Processor Module sets up the DMA word address by writing the 23-bit word address to the DMA Address registers (ports XX8Ah, XX8Ch, and XX8Eh).

- 2. Timer counter Ø (port XX9Øh) is set by the Time Mode Control register (port XX96h) to mode Ø (interrupt on terminal count) and loaded with the value of the number of bytes in a multiple of 512 bytes to be transferred, minus one byte.

- TSET+, TONLINE+, TSEL+, and TPRDOP+ bits are set in the Tape Control register (port XX82h).

- 4. Assertion of TREADY+ is checked in the Tape Line Status register (port XX84h).

- 5. Command byte 80h is issued to the Tape Command Byte register (port XX80h).

- 6. The Processor Module waits for an interrupt for completion of the read operation.

- 8. Upon interrupt, the Tape Line Status register (port XX84h) is read for the in-terrupt condition.

- 9. The TSEL+ bit in the Tape Control register (port XX82h) is reset to free the X-Bus interrupt line.

## 2-8 Quarter-Inch Cartridge Tape Hardware Manual

- 10. A write is performed to the Clear Pending Interrupt register (port XX88h) to clear the interrupt.

- 11. The TPRDOP+ bit in the Tape Control register (port XX82h) is reset to inhibit erroneous read on tape.

- 12. If the TEXP+ interrupt in the Tape Line Status register (port XX84h) is asserted, a file mark is encountered. Operation is terminated by issuing a read status command.

- 13. If TCINT+ interrupt in the Tape Line Status register (port XX84h) is not asserted, an error exit routine is performed.

- 14. If not the last buffer block, then go to

step 16.

- 15. The Processor Module may deassert TONLINE+ in the Tape Control register (port XX82h). Either a Read File Mark or another Read Data command is issued. End.

- 16. The Processor Module waits for TREADY+, which signals that the drive is ready for the next data block.

- 17. The address counters and timer counter Ø are reloaded with the value of bytes in a multiple of 512 bytes to be transferred, minus two bytes.

- 18. TPRDOP+ is set to continue the read operation. TSEL+ is set to enable the interrupt and light the LED.

- 19. Go to 6.

### WRITING DATA FROM THE PROCESSOR MODULE TO TAPE

The sequence to issue the write command is as follows:

- The Processor Module sets up the DMA word address by writing the 23-bit addresses to the DMA Address registers (ports XX8Ah, XX8Ch, XX8Eh).

- 2. Timer counter Ø (port XX9Øh) is set by the Timer Mode Control register (port XX96h) to mode Ø (interrupt on terminal count) and loaded with the value of the number of bytes to be transferred in a multiple of 512 bytes, minus one byte.

- 3. Timer counter 1 (port XX92h) is set by the Timer Mode Control register (port XX96h) to a programmable one-shot mode 1, and loaded with 510 bytes (512 bytes minus two).

- 4. TSET+, TONLINE+, TSEL+, and TPWROP+ bits are set in the Tape Control register (port XX82h).

- 5. TREADY+ for drive ready is checked in the Tape Line Status register (port XX84h).

- Command byte 40h is issued to the Tape Command Byte register (port XX80h).

- 7. The Processor Module waits for an interrupt for completion of the write operation.

- 8. Upon interrupt, the Tape Line Status register (port XX84h) is read to verify the existence of TCINT+.

## 2-10 Quarter-Inch Cartridge Tape Hardware Manual

- 9. The TSEL+ bit in the Tape Control register (port XX82h) is reset.

- 10. A write to the Clear Pending Interrupt register (port XX88h) is performed to clear the interrupt condition.

- 11. The TPWROP+ bit in the Tape Control register (port XX82h) is set to inhibit an erroneous write to tape.

- If not the last buffer block, then go to step 16.

- 13. The Tape Line Status register (port XX84h) is read, and there is a wait for TREADY+.

- 14. The Processor Module may either issue a Write File Mark command or reset TONLINE+ to terminate the Write Data to Tape operation.

- 15. End.

- 16. To continue writing from the buffer, the address counters and the timer counter  $\emptyset$  are loaded with the number of bytes to be transferred, minus one byte.

- 17. TPWROP+ is set to restart the tape write operation. TSEL+ is set to enable the interrupt and LED.

- 18. Go to 7.

#### COMMAND AND STATUS REGISTERS

READ TAPE STATUS BYTE REGISTER (PORT XX80h)

Six bytes are read from this register; bytes  $\emptyset$  through 5.

BYTE Ø

Data bit functions of this register are as follows:

- Data Bit Function

- Ø

1

2

3

File Mark Detected. Tape control circuitry sets this bit when it detects a file mark during a Read Data or Read File Mark operation. A Read Tape Status sequence resets the bit.

Block-in-Error Not Located. The tape control circuitry sets this bit when an unrecoverable read error occurs and the control circuitry cannot confirm that the last block transmitted was the block in error. A Read Tape Status sequence resets the bit.

Unrecoverable Data Bit Error. The tape control circuitry sets this bit when a hard error occurs during a read or write operation. A Read Tape Status sequence resets the bit.

End of Media. The tape control circuitry sets this bit when it detects the logical early warning hole of the last track during a write operation. A Read Tape Status sequence resets the bit.

#### Data Bit Function

4

5

6

Write Protect. The tape control circuitry sets this bit if the cartridge write protect plug is set in the file's protect position. Changing the plug position resets the bit.

- Drive Not Online. The tape control circuitry sets this bit if the drive is not physically connected or is not receiving power.

- Cartridge Not in Place. The tape control circuitry sets this bit if a cartridge is not fully inserted into the drive.

- Exception Byte  $\emptyset$ . This bit is set if any of the other bits in status byte  $\emptyset$ are set.

#### BYTE 1

7

Data bit functions of this register are as follows:

## Data Bit

#### Function

ø

Reset/Power-Up Occurred. The tape control circuitry sets this bit after the Processor Module issues a reset, or when the QIC Tape Module is powered up. A Read Tape Status sequence resets the bit.

1

2

End of recorded data.

Parity error on data bus.

## Data Bit Function

3

4

5

6

7

Beginning of Media. The tape control circuitry sets this bit when the cartridge is at the beginning of tape. This bit is reset when the drive leaves the beginning of the tape.

Eight or more retries.

No Data Detected. The tape control circuitry sets this bit when an unrecoverable data error occurs due to lack of recorded data. This occurs when the QIC Tape Module does not detect a data block within a tape control circuitry timeout. A Read Tape Status sequence resets the bit.

Illegal Command. The tape control circuitry sets this bit if any of the following conditions occur:

- o the Processor Module asserts ONLINE- when a data transfer command is received

- o the Processor Module sends a command other than Write or Write File Mark during a write operation

- o the Processor Module sends a command other than Read or Read File Mark during a read operation

- o the Processor Module sends a Select command when the cartridge in the drive is not at the beginning of the tape

Exception byte 1.

# BYTE 2

Tape status byte 2 is the most significant byte, with a soft-error count.

## BYTE 3

Tape status byte 3 is the least significant byte, with a soft-error count.

# BYTE 4

Tape status byte 4 is the most significant byte, with a buffer-underrun count.

# BYTE 5

Tape status byte 5 is the least significant byte, with a buffer-underrun count.

# WRITE TAPE COMMAND BYTE REGISTER (XX80h)

Bytes of this Write register can be configured for one of the following:

|                           |   |   | Da | ta Bi | ts |   |   |   |

|---------------------------|---|---|----|-------|----|---|---|---|

| Command                   | 7 | 6 | 5  | 4     | 3  | 2 | 1 | Ø |

| Select<br>Drive           | Ø | Ø | Ø  | 1     | Ø  | Ø | Ø | 1 |

| Begin-<br>ning of<br>Tape | Ø | Ø | 1  | Ø     | Ø  | Ø | Ø | 1 |

| Erase<br>Tape             | Ø | Ø | 1  | Ø     | Ø  | Ø | 1 | Ø |

| Reten-<br>sion            | Ø | Ø | 1  | Ø     | Ø  | 1 | Ø | Ø |

| Read<br>Data              | 1 | Ø | Ø  | Ø     | Ø  | Ø | Ø | Ø |

| Read<br>File<br>Mark      | 1 | Ø | 1  | Ø     | Ø  | Ø | Ø | Ø |

| Write<br>Data             | Ø | 1 | Ø  | Ø     | Ø  | Ø | Ø | Ø |

| Write<br>File<br>Mark     | Ø | 1 | 1  | Ø     | Ø  | Ø | Ø | Ø |

| Read<br>Tape<br>Status    | 1 | 1 | Ø  | Ø     | Ø  | Ø | Ø | Ø |

2-16 Quarter-Inch Cartridge Tape Hardware Manual

### CONTROL CIRCUITRY TO TAPE DRIVE INTERFACE

Communication between the Tape Drive Control board and the tape drive takes place through the tape drive interface, which consists of the following:

- o four control lines from the Processor Module

- o four control lines from the tape drive

- o the 8-bit bidirectional data bus

For detailed information on the tape drive interface, see the manufacturer's tape drive manual in Chapter 4, "Drive Specifications."

#### DMA TRANSFER MODE 3

#### DIRECT MEMORY ACCESS

Direct memory access (DMA) transfer operations are bus operations that access data differently than conventional master/slave I/0 the or memory DMA transfer operations allow other operations. masters besides the Processor Module bus to independently access the buses and support data transfers without direct program control. Bus masters can retain the bus for more than one cycle at a time. The X-Bus has four DMA transfer modes, mode Ø through mode 3. Since the QIC Tape Module uses only mode 3, only mode 3 is described here. For information about modes  $\emptyset$  through 2, see the Processor Manual for your system.

#### MODE 3

During a mode 3 transfer, the Processor Module only provides the arbitration for bus acquisition signals. The requesting module, which must be a master, generates the control and addresses. Mode 3 is only valid on DMA channels 1 through 3 of the Processor Module; however, more than one mode 3 master may share the same data transfer channel. The QIC Tape Module uses DMA channel 1.

The data requests and acknowledges are daisychained through priority arbitration logic. When the Processor Module asserts XDACK- (X-Bus DMA Acknowledge), each mode 3 module determines if it has a valid request. If the applicable mode 3 module has asserted X-Bus DMA Request (XDRQ-), then it controls the channel and inhibits X-Bus DMA Acknowledge (XDACK-) for the next X-Bus mode 3 master module downstream. If no request is pending for the applicable module, the mode 3 master module asserts XDACK- for the next module on the X-Bus.

## ROM ADDRESSING

The ROM address is mapped in the module memory address by writing I/O address XX10h with bit 2 of the data bus set. Input/output address XX20h is the memory select register, which is loaded with 00h through 0Fh, specifying a 1M-byte X-Bus window that can be used for ROM.

The following is an example of how to read the bootstrap ROM when connected to a Processor Module with an 80186 CPU:

o Write a value of ØCØ38h to the 80186 CPU upper memory chip select (UMCS) address ØFFAØh to specify a 256K-byte memory block size.

#### 2-18 Quarter-Inch Cartridge Tape Hardware Manual

- o Write a value of 2880h to port ØFAØ0h, the Extended Address register (EAR) of the Processor Module, to set to the fifth IM-byte boundary with a window size of 224K.

- O Output byte value 5 to port XX20h, and set the EAR of the X-Bus Gate Array to respond to the fifth 1M-byte boundary.

- o Output byte value 4 to port XXØAh for boot enable.

- o Read the bootstrap ROM contents starting from address ØCØØØØh.

# MODULE I/O ADDRESS SUMMARY

A summary of the I/O ports defined for the QIC Tape Module is provided in Table 2-1. Port number, input information, and output information are listed.

| Table 2-1.   | I/O Address Summa<br>(Page 1 of 2)    | ıry                                      |

|--------------|---------------------------------------|------------------------------------------|

| Port No. (h) | Read                                  | Write                                    |

| XX8Ø         | Tape Status<br>Byte<br>register       | Tape Command<br>Byte register            |

| XX82         | Tape<br>Control<br>register           | Tape Control<br>register                 |

| XX84         | Tape Line<br>Status                   |                                          |

|              | register                              |                                          |

| XX86         |                                       |                                          |

| XX88         |                                       | Clear Pending<br>Interrupt<br>register   |

| XX8A         | <b></b>                               | DMA Low 8<br>Address Bits<br>register    |

| XX8C         | · · · · · · · · · · · · · · · · · · · | DMA Middle 8<br>Address Bits<br>register |

| XX8E         |                                       | DMA High 8<br>Address Bits<br>register   |

2-20 Quarter-Inch Cartridge Tape Hardware Manual

| Port No. (h) | Read                           | Write                             |

|--------------|--------------------------------|-----------------------------------|

| XX9Ø         | Timer<br>Counter Ø<br>register | Timer Counter Ø<br>register       |

| XX92         | Timer<br>Counter l<br>register | Timer Counter l<br>register       |

| XX94         | Timer<br>Counter 2<br>register | Timer Counter 2<br>register       |

| XX96         |                                | Timer Mode<br>Control<br>register |

Table 2-1. I/O Address Summary (Page 2 of 2)

#### **3 THEORY OF OPERATION**

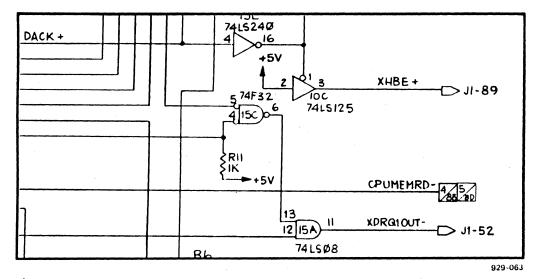

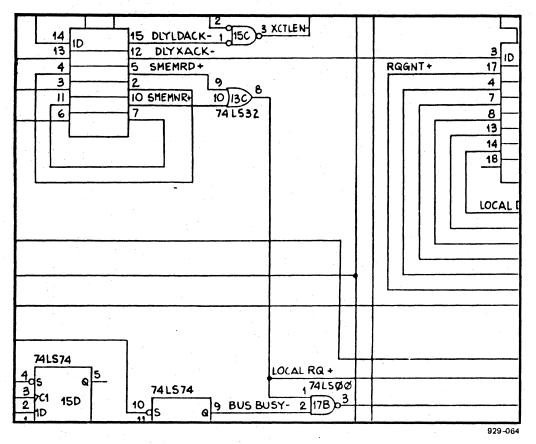

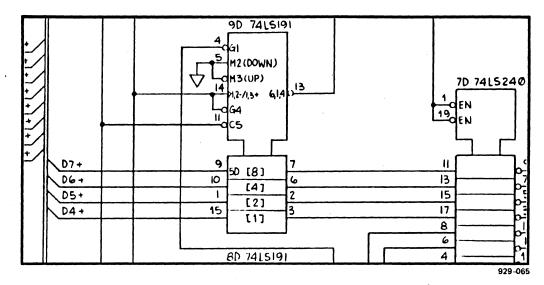

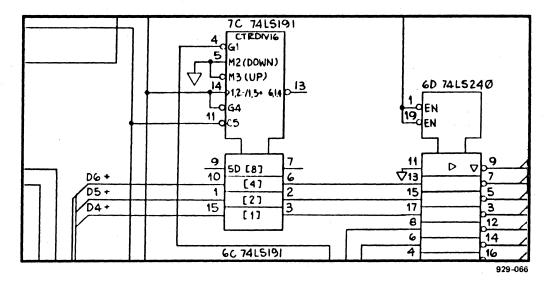

This chapter, which provides detailed componentlevel descriptions of the hardware incorporated in the Quarter-Inch Cartridge (QIC) Tape Module, is directed to the engineer who needs to understand the QIC Tape Module at the component level. Each functional block is described in relation to the logic that performs the function. Schematic windows are provided on each applicable page to supplement the text. In addition, a complete set of schematic drawings is provided in Appendix B.

Each schematic window represents an applicable portion of the schematic diagram. The page of the schematic diagram and location (coordinate) within that page is provided below each window, as shown in the following example:

(From Figure B-1, Page 2, Coordinate 8B.)

This window comes from the second page of the schematic drawing in Figure B-1 (Appendix B). The exact location, taken from the top left corner of the window, is at coordinate 8B.

### CIRCUIT DESCRIPTIONS

Detailed component-level circuit descriptions are given for the following:

- o X-Bus Gate Array

- o tape drive operation

- o mode 3 DMA

- o tape drive interface logic

- o 8253 programmable interval timer

- o power supplies

# X-BUS GATE ARRAY

The X-Bus Gate Array at 5E is used for the following:

- o module identification

- o I/O read and I/O write

- o Bootstrap requests from the CPU

The pin assignments and functions of the X-Bus Gate Array are listed in Table 3-1.

| Table 3-1. | X-Bus Gate Array Pin Assignments<br>and Functions<br>(Page 1 of 5)                                                                                                                             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin        | Function                                                                                                                                                                                       |

| 1          | Reset (RESET-). Low true input ini-<br>tializes the device and suspends all<br>operations.                                                                                                     |

| 2 to 5     | X-Bus Address Bus (XADR14- through XADR17-). Low true input reflects the module memory base address.                                                                                           |

| 6 to 9     | Data Bus (DAT7+ through DAT4+).<br>High true input reflects data to be<br>written into the X-Bus Gate Array<br>when the proper control signals are<br>valid.                                   |

| 10 to 12   | Data Bus (DAT3+ through DATØ+).<br>Bidirectional, high true data bits<br>reflect data to be written into or<br>read from the X-Bus Gate Array when<br>the proper control signals are<br>valid. |

| 14         | Oscillator Resistor (OSCRES+). High<br>true output pin is used for connec-<br>tion of a timing resistor for the<br>on-chip oscillator.                                                         |

| 15         | <b>Oscillator Return (OSCRET+).</b> High<br>true input pin is used for connec-<br>tion of the oscillator RC network<br>through a protection resistor.                                          |

Theory of Operation 3-3

| Т  | able 3-1. | X-Bus Gate Array Pin Assignments<br>and Functions<br>(Page 2 of 5)                                                                                                                                              |

|----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P  | in        | Function                                                                                                                                                                                                        |

| 1  | 6         | <b>Power (VSS-).</b> This input is a power connection required by the X-Bus Gate Array.                                                                                                                         |

| 1  | 7         | Oscillator Capacitor (OSCCAP+).<br>High true output pin is used for<br>connection of a timing capacitor for<br>the on-chip oscillator.                                                                          |

| 11 | 8         | Acknowledge (ACK+). High true out-<br>put indicates to the X-Bus that the<br>data has been transferred and the<br>bus cycle can be terminated. ACK+<br>is generated only for I/O operations<br>and ROM reading. |

| 19 | 9         | I/O Read (IORD-). Low true output<br>read strobe is generated by the<br>X-Bus Gate Array only if the module                                                                                                     |

|    |           | is selected for an I/O read opera-<br>tion.                                                                                                                                                                     |

| 20 | 3         | I/O Write (IOWR-). Low true output<br>write strobe is generated by the<br>X-Bus Gate Array only if the module<br>is selected for an I/O write opera-<br>tion.                                                   |

| 21 | L         | Memory Operation (MEMOP-). Low true<br>output indicates the module is<br>selected for a memory operation.                                                                                                       |

3-4 Quarter-Inch Cartridge Tape Hardware Manual

| Table 3-1. | X-Bus Gate Array Pin Assignments<br>and Functions<br>(Page 3 of 5)                                                                                                                                                                                               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin        | Function                                                                                                                                                                                                                                                         |

| 22 -       | ROM Enable (ROM-). Low true output<br>enables the ROM device.                                                                                                                                                                                                    |

| 23         | X-Bus Priority Out (XPOUT+). Posi-<br>tive true output is a daisy-chained<br>signal that allows the next module<br>to initialize.                                                                                                                                |

| 24         | Identification Enable (IDEN-). Low<br>true output signifies that DMA is<br>active on the X-Bus.                                                                                                                                                                  |

| 25         | X-Bus I/O Read (XIORD-). Low true<br>input indicates that an I/O read<br>operation is to be performed on the<br>X-Bus. This signal is used in con-<br>junction with the XADR8- through<br>XADRF- lines to determine if the I/O<br>operation is for the module.   |

| 26         | X-Bus I/O Write (XIOWR-). Low true<br>input indicates that an I/O write<br>operation is to be performed on the<br>X-Bus. This signal is used in con-<br>junction with the XADR8- through<br>XADRF- lines to determine if the I/O<br>operation is for the module. |

# Table 3-1. X-Bus Gate Array Pin Assignments and Functions (Page 4 of 5)

## Pin Function

27

28

X-Bus Memory Read (XMEMRD-). Low true signal indicates that a memory read operation is to be performed on the X-Bus. This signal is used only to enable the CPU to read the module ROM.

Load Address Enable (LOADEN+). High true input allows access to the on-chip locations (memory select registers and ROM shadow bit). When this input is high, these two functions are not decoded and the I/O operation is intended for external devices. When LOADENis low, XADR3- and XADR5- decode the I/O operation as follows:

| XADR3- | XADR5- | I/O Operation             |

|--------|--------|---------------------------|

| Ø      | Ø      | External                  |

| 1      | Ø      | ROM shadow<br>bit         |

| Ø      | 1      | Memory Select<br>register |

| 1      | 1      | External                  |

| Table 3-1. | X-Bus Gate Array Pin Assignments<br>and Functions<br>(Page 5 of 5)                                                                                           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin        | Function                                                                                                                                                     |

| 29         | X-Bus DMA Enable (XDMEN-). Low true<br>input indicates that the DMA is<br>active on the X-Bus.                                                               |

| 30 to 31   | X-Bus Address Bus (XADR3- and XADR5-). Low true inputs. (See pin 28 above.)                                                                                  |

| 32 to 35   | X-Bus Address Bus (XADR8- through<br>XADRB-). Low true inputs. XADR8-<br>through XADRF- reflect module I/O<br>base address, except during<br>initialization. |

| 36         | <b>Power (VDD+).</b> This input is a power connection required by the X-Bus Gate Array.                                                                      |

| 37 to 40   | X-Bus Address Bus (XADRC- through<br>XADRF-). Low true inputs. (See pins<br>32 to 35 above.)                                                                 |

## MODULE IDENTIFICATION

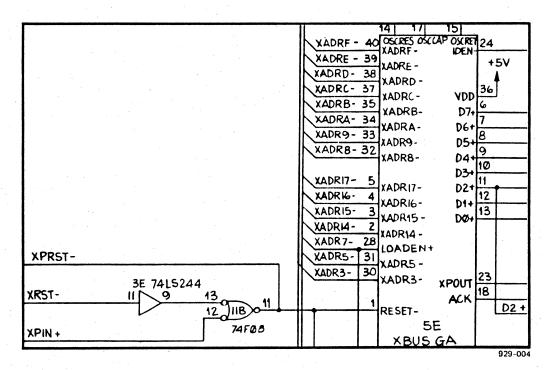

Base addresses for the various I/O ports and registers are assigned by the Processor Module when a power-up or manual reset occurs on the X-Bus as XRST- (X-Bus Reset), or when XPIN+ (X-Bus Priority In) is reset low, signifying that activity on the X-Bus for the QIC Tape Module is suspended.

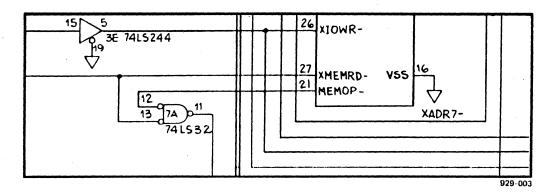

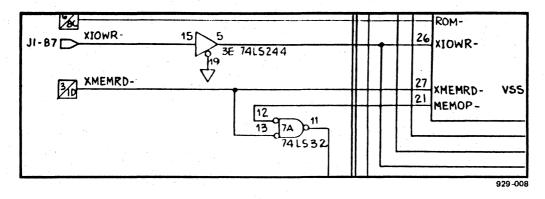

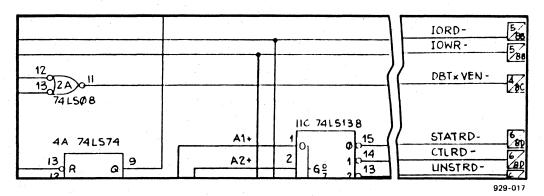

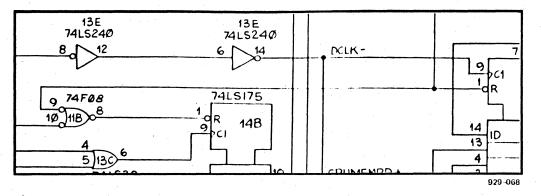

As shown in the following window, XRST-, connecting from Jl, pin 88, is buffered at 3E (pin 9) and driven through gate 11B to the X-Bus Gate Array (5E). Resetting 5E clears all the internal registers. After reset, the Processor Module performs a read, and since the X-Bus Gate Array is clear, it responds to I/O port address, location  $\emptyset$ .

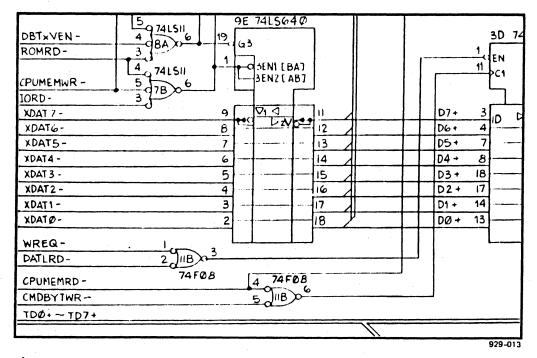

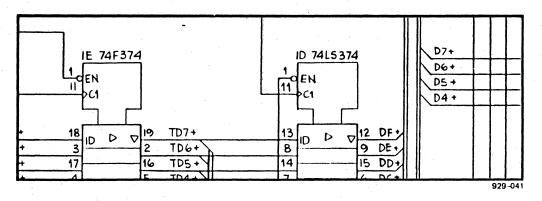

(From Figure B-1, Page 2, Coordinate 8D.)

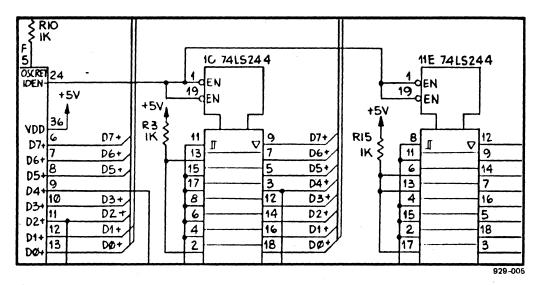

When XIORD- (X-Bus I/O Read) is low, 5E generates a low at pin 24 (IDEN-), enabling 1C and 11E. The data from the input of 1C and 11E is transferred to the data bus DØ+ through D7+, and D8+ through DF+.

(From Figure B-1, Page 2, Coordinate 6D.)

The identification codes are as follows:

- o high byte 31 (which is the QIC Tape Module identification type)

- o low byte 41 (which means this is a bootable device, the boot ROM can be read through DMA channel Ø, and can support a non-80186 CPU)

## Module Identification Read

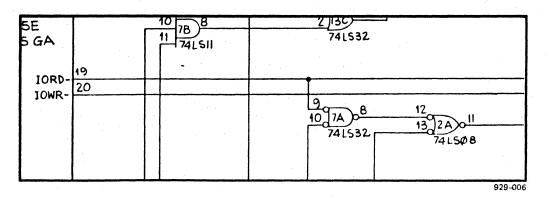

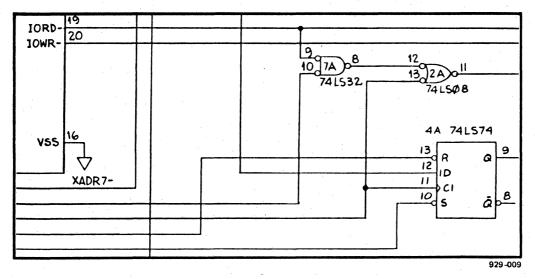

Pin 19 of 5E (IORD-) is a modifier signal that is enabled and goes to pin 9 of 7A.

(From Figure B-1, Page 2, Coordinate 6C.)

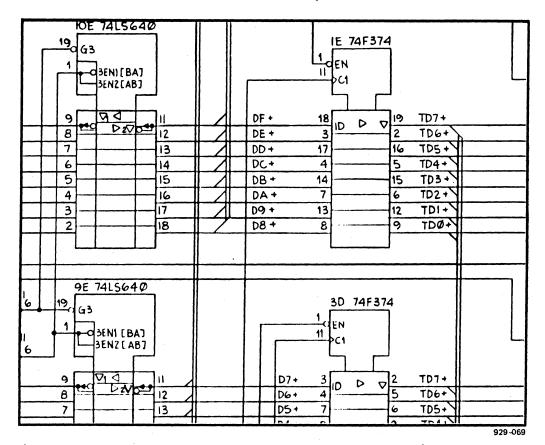

When pin 8 of 7A is low, the output of 2A (pin 11) is low. The signal coming from pin 11 is DBTXVEN-(Data Bus Transceiver Enable), which enables data bus transceivers, 9E and 10E.

Since pin 4 of 8A is low, pin 19 of both 9E and 10E are low. The direction is controlled by pin 1 of 9E and 10E, which are tied to pin 6 of 7B. IORD- (from pin 19 of 5E) is low and goes to AND gate 7B, forcing pin 6 of 7B low, and thus pin 1 of 9E and 10E are also low, enabling the direction of the data to flow to the CPU.

(From Figure B-1, Page 4, Coordinate 8D.)

## Module Identification Write

After the Processor Module reads the identification code of 31 and 41, it writes to port  $\emptyset$ , an internal register of the X-Bus Gate Array (the value of the base address of the module it selected).

(From Figure B-1, Page 2, Coordinate 8C.)

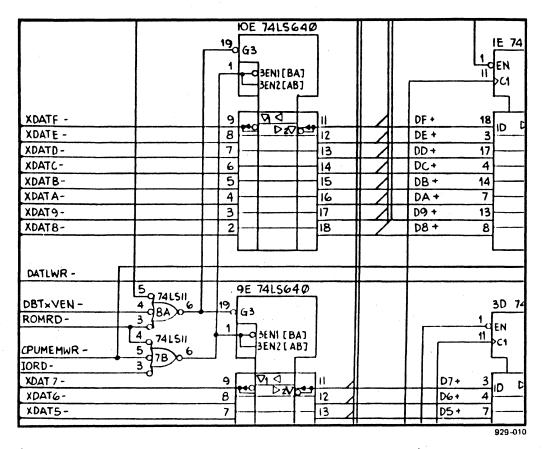

As shown above, XIOWR- from J1-87 is asserted and buffered through pin 5 of 3E to pin 13 of AND gate 2A (pin 13). Pin 11 of 2A (DBTXVEN-) goes low and enables transceivers 9E and 10E.

(From Figure B-1, Page 2, Coordinate 6C.)

Since this is not a read operation, pin 6 of 7B remains high. As shown in the following window, pin 1 of 9E, and pin 1 of 10E are high, enabling data to be transferred from the X-Bus data bus to the X-Bus Gate Array.

(From Figure B-1, Page 4, Coordinate 8D.)

## I/O READ AND WRITE

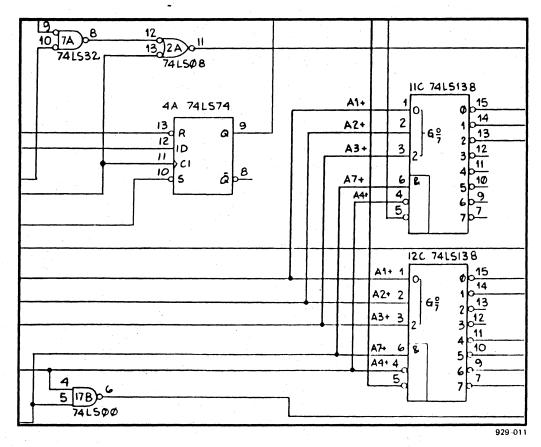

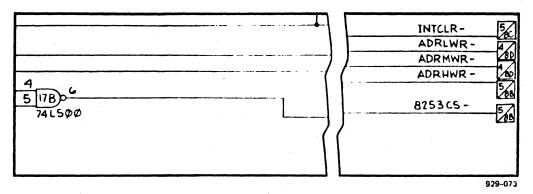

Decoders 11C and 12C decode the proper I/O addresses for various I/O ports. Decoder 11C is used for input read, and decoder 12C is used for output write. The select and enable lines of the decoders are connected to the address lines Al+ through A4+, and A7+. The range of the outputdecoded address is from XX80 through XX8E. The timer chip select enable is connected to pin 6 of 17B, which is enabled when A4+ and A7+ are high. Thus, the timer responds to address space XX90.

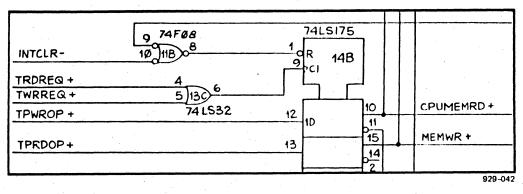

(From Figure B-1, Page 2, Coordinate 5C.)

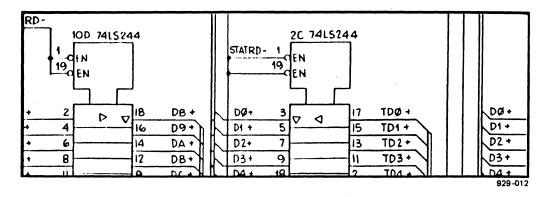

The X-Bus Gate Array compares the module base address and generates a low signal at pin 19 of 5E (IORD-), enabling pin 5 of 11C. At the same time, a low enable signal is generated at pin 15 of 11C. Since pin 15 is connected to pins 1 and 19 of 2C, the 8-bit data on the TDØ+ through TD7+ bus is sent to the CPU through transceiver 9E.

(From Figure B-1, Page 6, Coordinate 6D.)

In a write operation, pin 20 of 5E is enabled, which means that pin 5 of 12C is also enabled. A low signal is generated at pin 15 of 12C. The data is latched to register 3D at the trailing edge of the IOWR-. IOWR- is modified from XIOWRto provide the proper address setup time and data hold time.

(From Figure B-1, Page 4, Coordinate 8C.)

## BOOTSTRAP REQUESTS FROM THE CPU

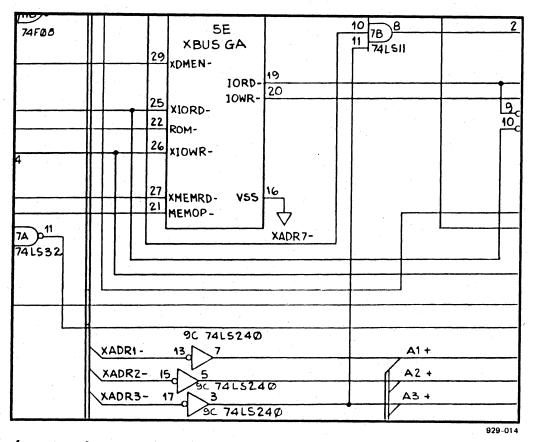

When the CPU boots from the tape, it asserts boot bit D2 (pin 11 of 5E) to port XXØAh. XX is the base address assignment the CPU gives to a particular module. When bit D2 is enabled, pin 9 of 7B is high. Since the CPU is writing to the X-Bus Gate Array at XXØAh, XADR7- is not asserted at pin 28 of the X-Bus Gate Array, and thus it is high. Pin 17 of 9C (XADR3-) is asserted and inverted at pin 3 of 9C. Pin 11 of 7B (A3+) is set to 1 and enabled.

When D2+ is set to 1, pin 8 of 7B and pin 3 of 13C are also set to 1, indicating at pin 9 of 5E that there is a boot enable. When there is no boot enable, data bit D4+ goes through pin 1 of 13C to pin 3 of 13C, and then back to pin 9 of the X-Bus Gate Array.

(From Figure B-1, Page 2, Coordinate 6C.)

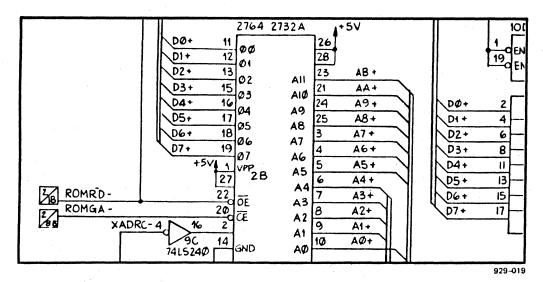

#### CPU ROM Read

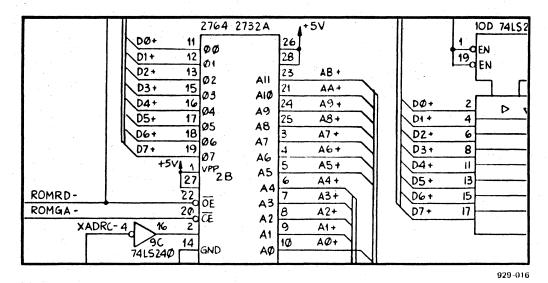

The CPU bootstrap ROM in the Processor Module does not have the code to boot from the tape. The program in the 2732A EPROM (2B) contains instructions for the CPU to boot from the tape. The CPU reads the bootstrap program into its memory and then executes the program.

(From Figure B-1, Page 6, Coordinate 8D.)

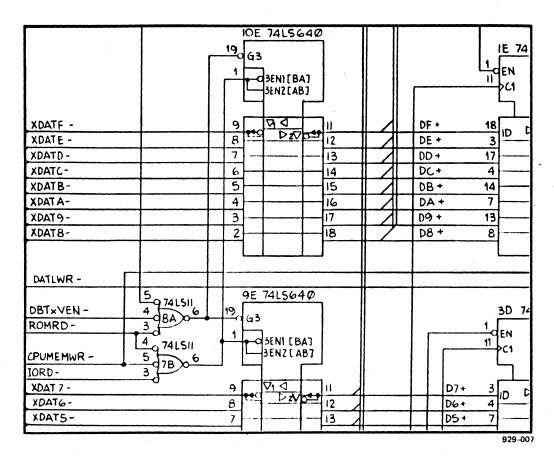

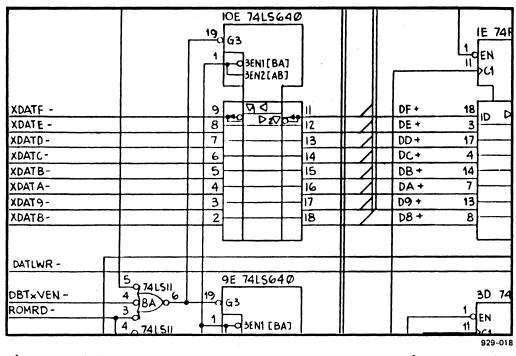

After setting the proper X-Bus window, the CPU performs an I/O read to the ROM. IORD- is asserted, which enables transceivers 9E and 10E. 2A (pin 11) enables DBTXVEN- (data bus transceiver enable).

DBTXVEN- is now low, enabling transceivers 9E and 10E, which provide the data for an I/O operation.

3-18 Quarter-Inch Cartridge Tape Hardware Manual

(From Figure B-1, Page 2, Coordinate 4C.)

The X-Bus Gate Array (5E) asserts the ROM at pin 20 of 2B, which is the CS- (Chip Select) pin. During the I/O read cycle, 5E also enables MEMOP- (Memory Operation) at pin 21 to read data from the ROM. Once the content of the ROM is loaded into the CPU, the CPU can execute the code read from the 2732A.

(From Figure B-1, Page 6, Coordinate 8D.)

### TAPE DRIVE OPERATION

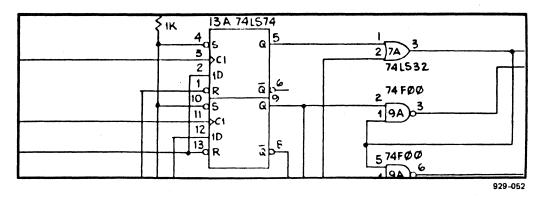

#### READ STATUS COMMAND

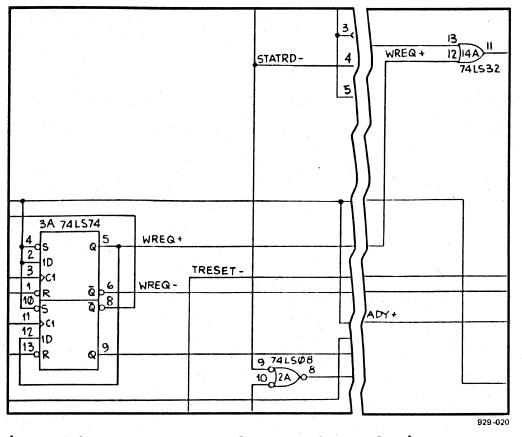

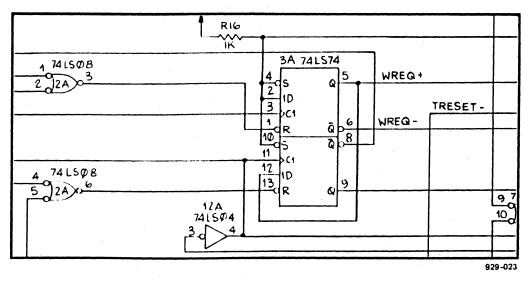

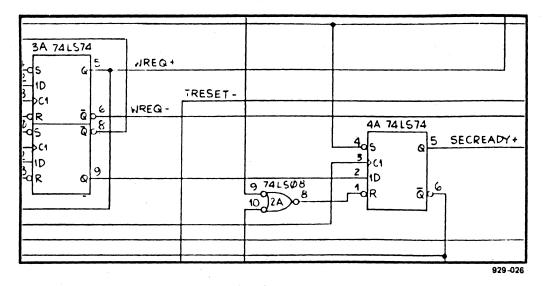

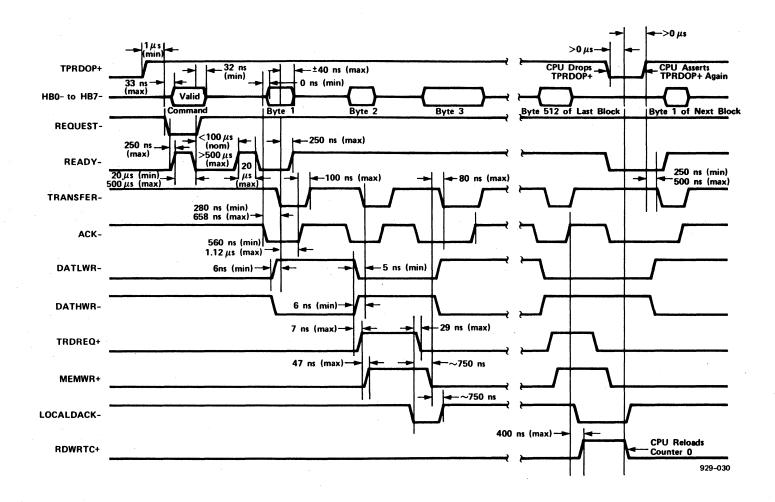

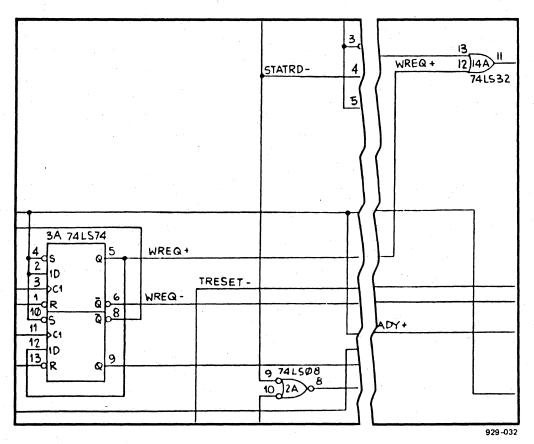

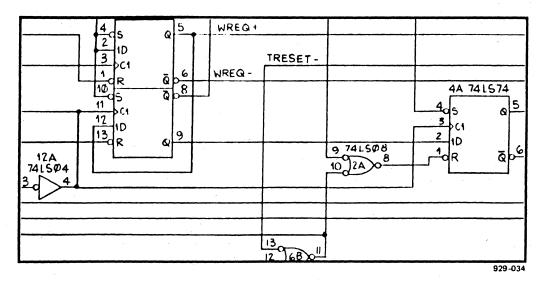

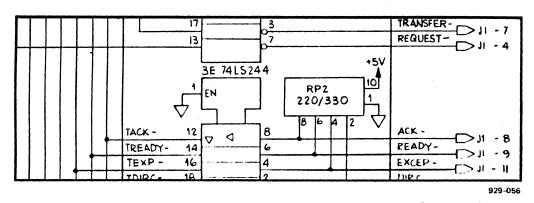

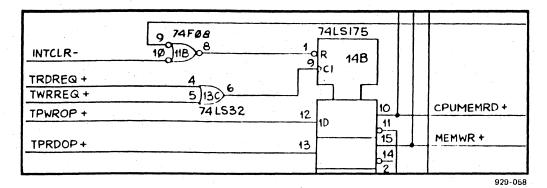

The CPU issues a read status command (ØCØh to port XX8Øh). At the trailing edge of the command byte write, pin 5 of flip-flop 3A is clocked high (since the input of 3A is high). When pin 5 of 3A goes high, WREQ+ (Write Request) at pins 11 and 12 of 14A are also high. A timing diagram for the read status command is shown in Figure 3-1.

(From Figure B-1, Page 6, Coordinate 3C.)

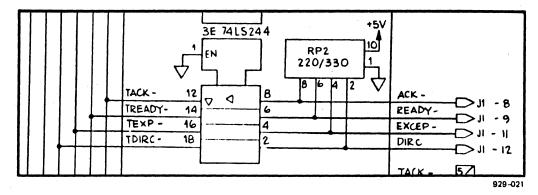

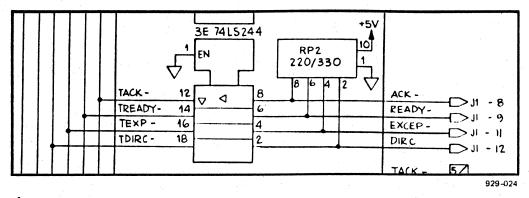

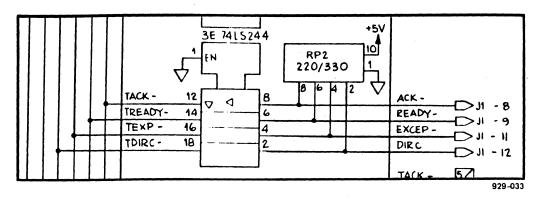

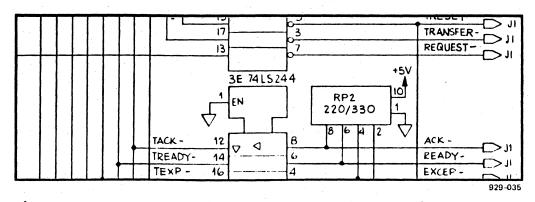

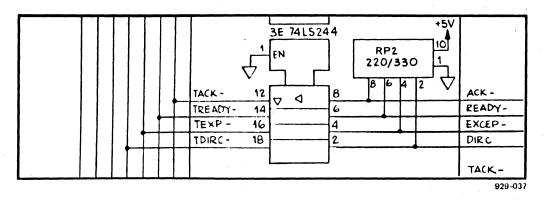

Pin 11 goes to pin 13 of 4E, which is output at pin 7 of 4E as REQUEST-. Some time after REQUESTis set, the tape drive will set READY-. READY-(coming in from J1-9 at pin 6 of buffer 3E) is output at pin 14 as TREADY-.

3-20 Quarter-Inch Cartridge Tape Hardware Manual

(From Figure B-1, Page 6, Coordinate 3B.)

When TREADY- is low, it goes to 12A, pin 3. Pin 4 of 12A is high and latches the data into pin 11 of flip-flop 3A. Pin 8 of 3A goes low, thus the output of AND gate 2A (pin 3) goes low, clearing 3A (pin 5) and removing the WREQ+.

The tape drive deasserts READY- some time after REQUEST- goes false. The tape drive asserts READY- again when the status byte is available to be read, and asserts DIRC- in preparation for sending the first status byte. DIRC-, coming from J1, pin 12, goes to pin 2 of 3E.

(From Figure B-1, Page 6, Coordinate 3B.)

The buffered output at pin 18 (TDIRC-) goes to pin 1 of 2E. When pin 1 is asserted, the transceiver data path direction is from the HBØ- through HB7bus, to the TDØ+ through TD7+ bus.

(From Figure B-1, Page 4, Coordinate 8B.)

## 3-24 Quarter-Inch Cartridge Tape Hardware Manual

Since pin 9 of 3A is high, the assertion of READYforces pin 5 of 4A, SECREADY+ (Second Ready), high.

(From Figure B-1, Page 6, Coordinate 6B.)

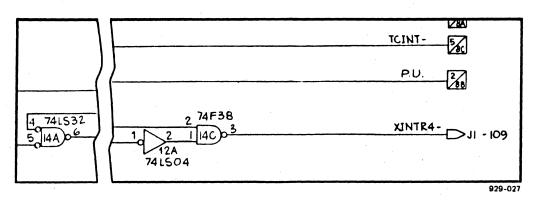

Because pin 4 of 14A is performing a read status only, it is low. So pin 6 of 14A is also low, and pin 2 of 12A is high. When the drive is selected at pin 2 of 14C, an interrupt is generated at J1-109 to inform the CPU that the status byte is available.

(From Figure B-1, Page 6, Coordinate 4A.)

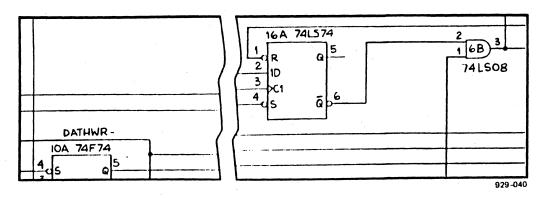

After receiving the interrupt, the Processor Module reads port XX84h (LINSTRD-) to verify that ENDCMDINT+ is set. The Processor Module then performs six reads on port XX80h (STATRD-) to fetch the six status bytes.

When the tape does a read from port XX80h (STATRD-), the output of 2A goes low to clear SECREADY+. When SECREADY+ is clear, pin 6 of 4A goes high, which removes the interrupt. Every time the CPU reads the status, it triggers one-shot flip-flop 6A, and 6A goes high for 20 microseconds. Pin 6 of 6A and pins 13 and 11 of 14A go high. Thereafter, REQUEST-, coming from pin 7 of 4E, remains low for 20 microseconds.

(From Figure B-1, Page 6, Coordinate 5C.)

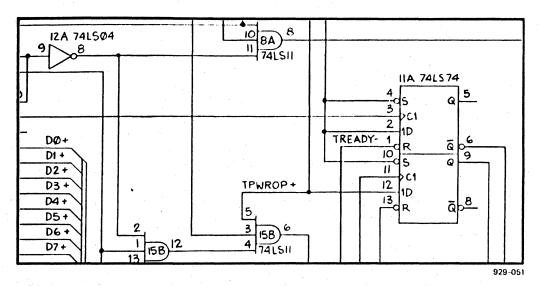

#### READ TAPE DATA COMMAND

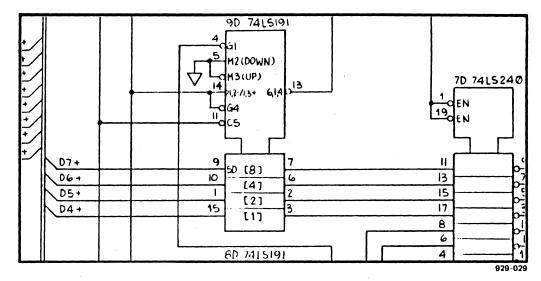

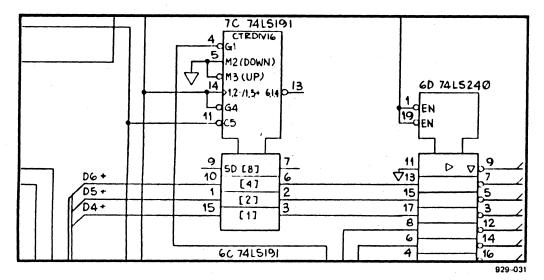

As shown in the following two windows, the CPU sets the DMA word address by writing the 23-bit address to address registers 8D, 9D, 4C, 5C, 6C, and 7C. A timing diagram of the Read Tape Data command is shown in Figure 3-2.

## 3-26 Quarter-Inch Cartridge Tape Hardware Manual

Figure 3-2. Read Tape Data Command Timing Diagram

(From Figure B-1, Page 4, Coordinate 4C.)

(From Figure B-1, Page 5, Coordinate 4C.)

The CPU is reading data from the tape and writing to the memory, so it needs to know the address of the memory to be written. The 23-bit word address (Al+ through Al7+), is loaded into the address counter by writing to ports XX8Ah, XX8Ch, and XX8Eh. Each write loads 8 bits of address into the counter. Address  $\emptyset$  is asserted automatically during DMA. The CPU also sets up the 8253 programmable interval timer, telling it how many bytes need to be transferred from the tape. The CPU then issues the command byte 40h to the CMDBTWR- (Command Byte Write) port. At the trailing edge of CMDBTWR-, flip-flop 3A is clocked at pin 3, then at pin 5, which goes high. The output of pin 5, WREQ+ (Write Request), goes through 14A (pin 12), indicating to the drive that there is a write request.

(From Figure B-1, Page 6, Coordinate 3C.)

The tape drive asserts a ready through Jl, pin 9, which is then buffered through pin 6 of 3E as TREADY- (Tape Ready).

3-30 Quarter-Inch Cartridge Tape Hardware Manual

(From Figure B-1, Page 6, Coordinate 3B.)

TREADY- is inverted at pin 3 of 12A and clocks pin 11 of 3A. Since pin 5 of 3A is set to 1, pin 9 goes high, and pin 8 goes low, clearing the request. The tape drive deasserts and asserts READY- again. The second time that READY- is asserted, SECREADY+ (Second Ready) at pin 5 of 4A is asserted, indicating that the data is ready to be read.

(From Figure B-1, Page 6, Coordinate 7B.)

The handshake between the Tape Drive Control board and the QIC-02 interface is through ACK-(Acknowledge) and TRANSFER- (Transfer), via Jl, pins 8 and 7, respectively.

(From Figure B-1, Page 6, Coordinate 3B.)

During a read operation, the tape asserts ACK-. When the tape control circuitry on the Tape Drive Control board receives the data, it asserts TRANSFER-, notifying the tape drive that the data has been received. The tape drive monitors the transfer. When the transfer has been asserted, the tape drive drops the acknowledge and asserts an acknowledge for the second byte.

Since counter  $\emptyset$  of the 8253 programmable interval timer (8B) is set in the interrupt on terminal count mode, pin 1 $\emptyset$  is low, and pin 8 of 12A and pin 11 of 8A are high, set in the initial condition.

(From Figure B-1, Page 5, Coordinate 7B.)

Pin 9 of 8A is tied to TPRDOP+ (Tape Read Operation), and is high because it is reading. Pin 10 of 8A is tied to TACK+ (Tape Acknowledge), originating from pin 6 of 12A through pin 12 of buffer 3E.

(From Figure B-1, Page 6, Coordinate 3B.)

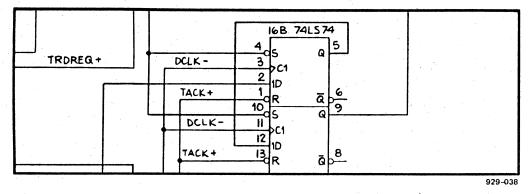

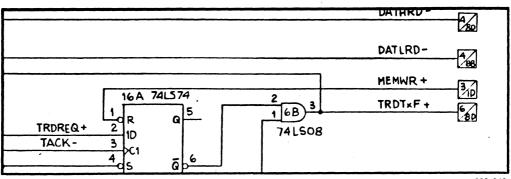

When the tape drive has data available, TACK- is low, and pin 6 of 12A is high. Pin 10 of 8A goes high, indicating that a byte is available. Pin 3 of 16B is tied to DCLK- (Data Clock), which is running at 250 nanoseconds. When a byte is available, pin 2 of 16B is high.

(From Figure B-1, Page 5, Coordinate 4C.)

At the next clock (250 nanoseconds later), DCLKis asserted again, and pin 9 of 16B goes high. Because this clock is asynchronous, 16B prevents metastable conditions. Data from the tape drive may be valid as late as 40 nanoseconds after ACKis asserted.

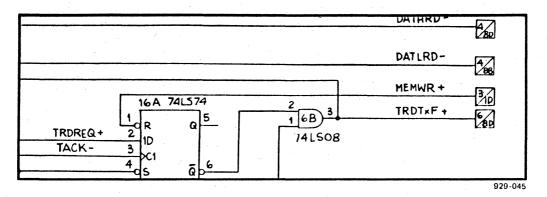

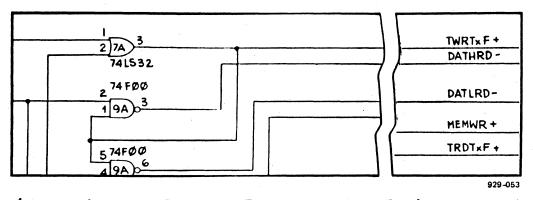

Pin 9 of 16B goes to pin 1 of 6B. There is as yet no write to CPU memory, and no DMA operation occurring at this time. (At this point, pin 2 of 6B is high, because MEMWR+ (Memory Write) is low.) TRDTXF+ (Tape Read Transfer) comes from pin 3 of 6B, indicating that the tape is available.

TRDTXF+ now goes to pin 10 of 14A, while pin 8 of 14A goes into pin 17 of 4E, indicating that the data has been received.

(From Figure B-1, Page 6, Coordinate 4C.)

Pin 3 of 6B clocks pin 3 of 10A. This causes pin 5 of 10A to go high, deasserting DATLWR- (Data Low Write).

(From Figure B-1, Page 5, Coordinate 4D.)

DATLWR- clocks into pin 11 of 2D, and the tape data lines (HBØ- through HB7-), coming through 2E, are latched into 2D. When the second byte is available, the tape drive asserts TACK- once again. Pin 3 of 6B goes high, notifying the tape drive that it has received the data. 10A now clocks the flip-flop (pin 6 of 10A goes high and clocks pin 11). DATHWR- at pin 6 of 10A goes high and latches the data into register 1D.

(From Figure B-1, Page 4, Coordinate 6D.)

Pin 9 of 10A also goes high, issuing TRDREQ+. Two bytes have already been received at this point, and are ready to do a DMA transfer to the CPU memory. TRDREQ+ goes to pin 4 of 13C and clocks pin 9 of 14B, generating a DMA request.

(From Figure B-1, Page 3, Coordinate 8D.)

3-36 Quarter-Inch Cartridge Tape Hardware Manual

At the same time, TRDREQ+ also goes to pin 2 of 16A to inhibit further returning of a TRANSFERsignal to the tape drive until DMA is complete.

929-043

(From Figure B-1, Page 5, Coordinate 3D.)

MEMWR+ (pin 15 of 14B) is asserted, and one clock later, SMEMWR+ (Synchronous Memory Write) goes high, indicating a local request with LOCAL RQ+.

(From Figure B-1, Page 3, Coordinate 7D.)

If the third byte is available before the DMA is complete, TACK- clocks pin 3 of 16A, and pin 6 of 16A has a  $\emptyset$ .

When the Processor Module is signaled that the DMA is finished, it clears 11B and 14B, thus clearing MEMWR+ at pin 15. MEMWR+ then goes low, forcing pin 1 of 16A low, and forcing pin 6 of 16A high. At this point, pin 3 of 16A gives a transfer acknowledge back to the tape drive.

From Figure B-1, Page 5, Coordinate 3D.)

If the DMA is completed before the third byte count, the MEMWR+ still clears pin 6 of flip-flop 14E, which goes high and is enabled.

(From Figure B-1, Page 3, Coordinate 6D.)

The flip-flop is cleared when LOCAL DACK- is low and goes through 15A (pin 9), indicating that the request is not finished.

(From Figure B-1, Page 5, Coordinate 6C.)

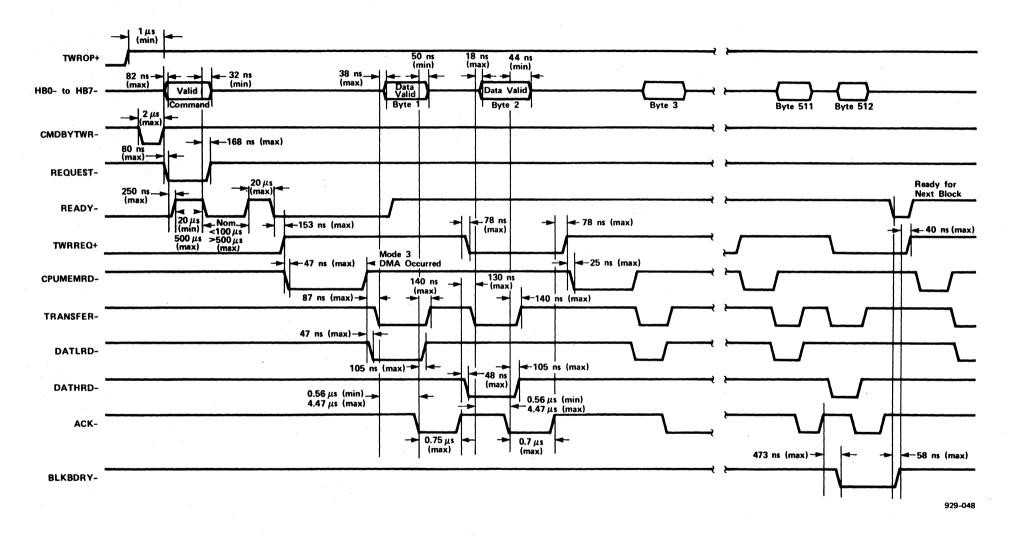

## WRITE TAPE DATA COMMAND

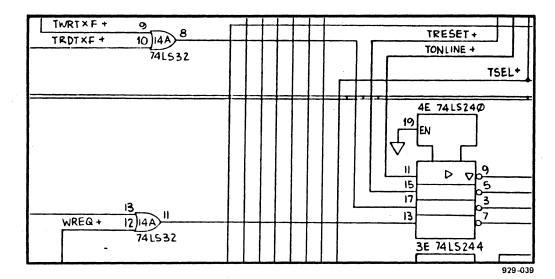

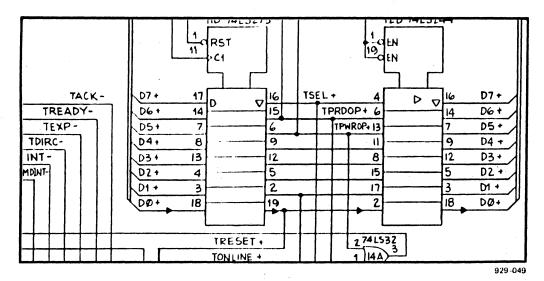

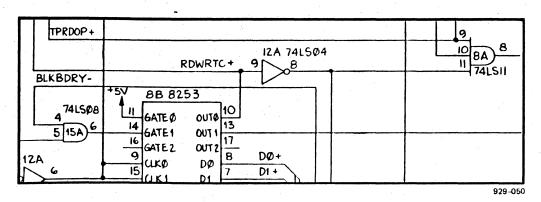

When writing data to the tape, the CPU enables TSEL+ (T-Select) and TONLINE+ (T-On Line) at 11D, and enables the bit write operation. A timing diagram of the write tape data command is shown in Figure 3-3.

(From Figure B-1, Page 6, Coordinate 3D.)

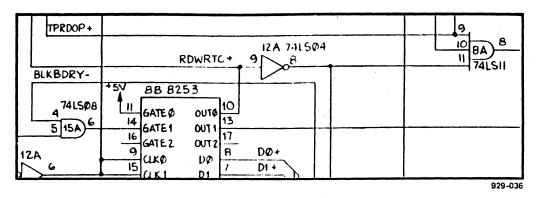

7A writes to the tape. The 8253 programmable interval timer at 8B enables OUTØ (the internal counter) at pin 1Ø, generating RDWRTC+ (Read Write Terminal Count).

(From Figure B-1, Page 5, Coordinate 7B.)

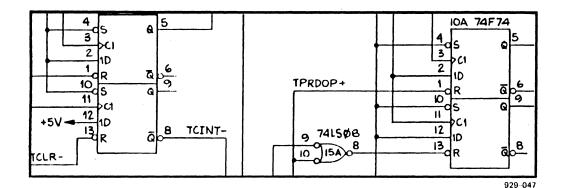

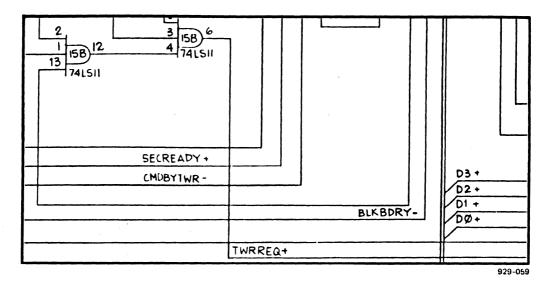

When SECREADY+ goes high, TREADY- clears flip-flop 11A. At this time, pin 6 of 11A and pin 1 of 15B are high, and pin 2 of 15B is high.

(From Figure B-1, Page 5, Coordinate 6B.)

Figure 3-3. Write Tape Data Command Timing Diagram

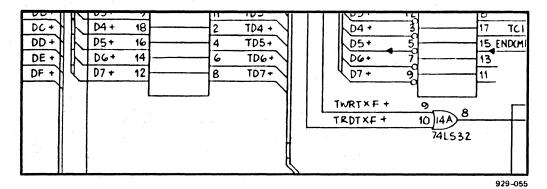

Pin 6 of 11B causes pin 1 of 15B to go high. Pin 10 of 8B goes low, then gets inverted to high at 12A, generating a SECREADY+. At this time, the outputs of pin 12 (11A and 15B) are high. When pins 3, 4, and 5 of 15B go high, their outputs go to pin 8 of 13A, which is a divide-by-two flipflop that controls the high-low byte. Then, pins 2 and 13 of 13A issue TPWROP+ (Tape Write Operation), giving a DMA request.

(From Figure B-1, Page 5, Coordinate 7D.)

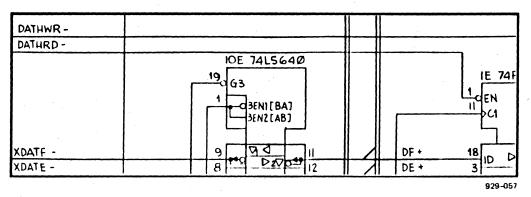

Pin 6 of gate 9A goes low, issuing a DATLRD- (Data Low Read). DATLRD- is driven through gate 11B

(From Figure B-1, Page 5, Coordinate 5D.)

(pin 2), and the output of 11B (pin 3) enables 3D at pin 1.

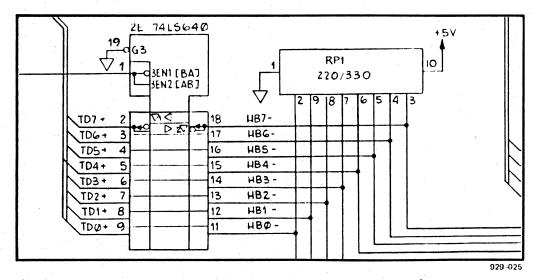

| 5 74L5II<br>4 8A 06 19<br>3 74L5II<br>5 78 6<br>3 78 6 | O 3ENI [BA]<br>3EN2 [AB]     |     |   |      | - 41 | 3D 74F37<br>EN<br>>C1 | 4  |       |

|--------------------------------------------------------|------------------------------|-----|---|------|------|-----------------------|----|-------|

| 9                                                      | $\nabla_1 \langle 0 \rangle$ | 11  |   | D7-  | + 3  |                       | 2  | TD7+  |

| 8                                                      | DAVC                         | 12  |   | D6-  | 4 4  |                       | 5  | TD6+` |

| 7                                                      | ·                            | -13 |   | D5   | + 7  |                       | 6  | TD5+  |

| 6                                                      | <b>}}</b>                    | -14 |   | D4   | + 8  | ]                     | 9  | TD4+  |

| 5                                                      |                              | 15  |   | D3   | + 18 | 1                     | 19 | TD3+  |

| 4                                                      |                              | 16  |   | D2   | + 17 | 1                     | 16 | TD2+  |

| 3                                                      | ]                            | 17  |   | D1 - | 14   | 1                     | 15 | TD1+  |

| 2                                                      | ┠┈╩╉┈╧                       | 18  | , | DØ   | + 13 | 1                     | 12 | TDØ+  |

|                                                        |                              |     |   |      |      | 1                     |    |       |

929-054

(From Figure B-1, Page 4, Coordinate 7C.)

The control circuitry asserts TRANSFER- to inform the tape drive that data is available. The tape drive receives the data, asserts acknowledge, and the control circuity removes the transfer. This is called a handshake operation. When pin 1 or pin 3 of 7A is high, the tape generates a transfer to pin 9 of 14A.

(From Figure B-1, Page 6, Coordinate 5C.)

3-44 Quarter-Inch Cartridge Tape Hardware Manual

The high output (pin 8) then goes to pin 17 of 4E, and lowers the transfer, indicating to the tape drive that there is data available. The tape drive then issues an ACK- from connector Jl, pin 8, to pin 8 of buffer 3E. ACK- is buffered, bringing pin 12 of 3E low and issuing a TACK-(Tape Acknowledge). When TACK- is low, there is a transfer pending, and the acknowledge is coming back from the tape drive.

(From Figure B-1, Page 6, Coordinate 3B.)

When TACK- is high, it clocks pin ll of flip-flop 13A. Pin 9 of 13A is then driven high through gate 9A, where the output (pin 3) enables pin l of 1E.

(From Figure B-1, Page 4, Coordinate 8D.)

#### MODE 3 DMA

# CONTROL ARBITRATION

The tape control circuitry operates asynchronously to the CPU and performs reads and writes at any time. The CPU responds to the tape control circuitry with an XACK- after each transfer.

# DMA MEMORY READ

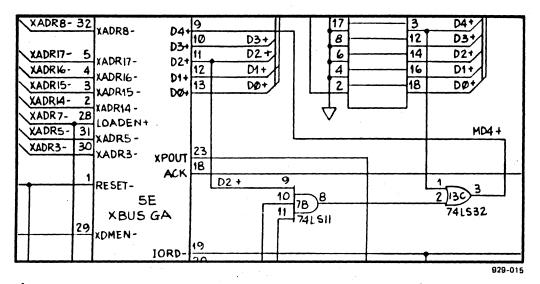

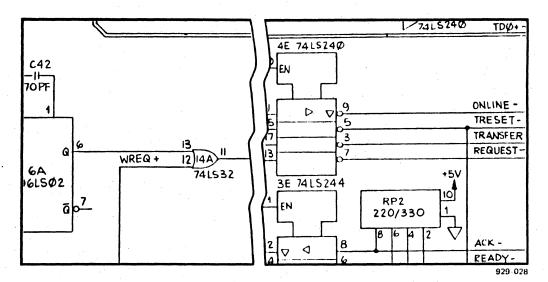

When the tape control circuitry performs a tape write operation, TPWROP+ (at pin 12 of control register 14B) is set.

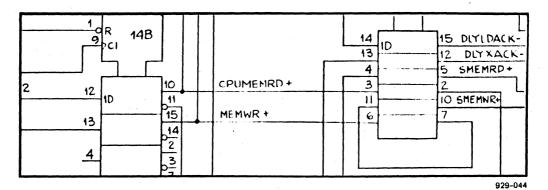

(From Figure B-1, Page 3, Coordinate 8D.)

TWRREQ+, from pin 6 of 15B, is asserted to request a word of data to be read from CPU memory, through mode 3 DMA.

(From Figure B-1, Page 5, Coordinate 5B.)

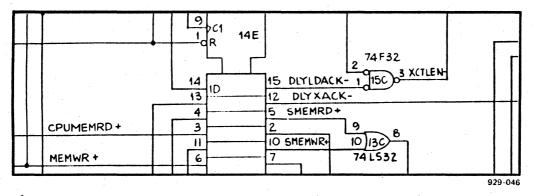

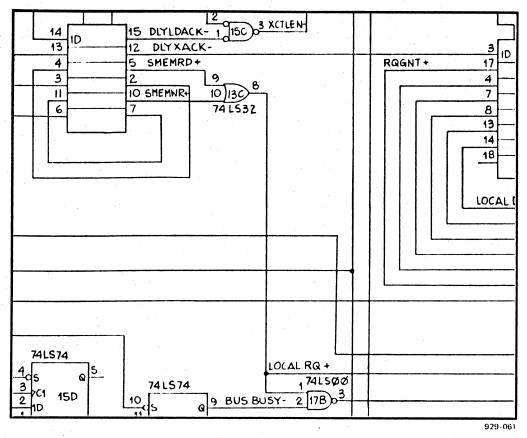

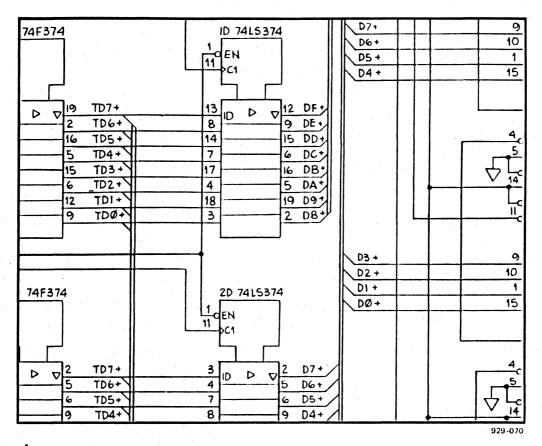

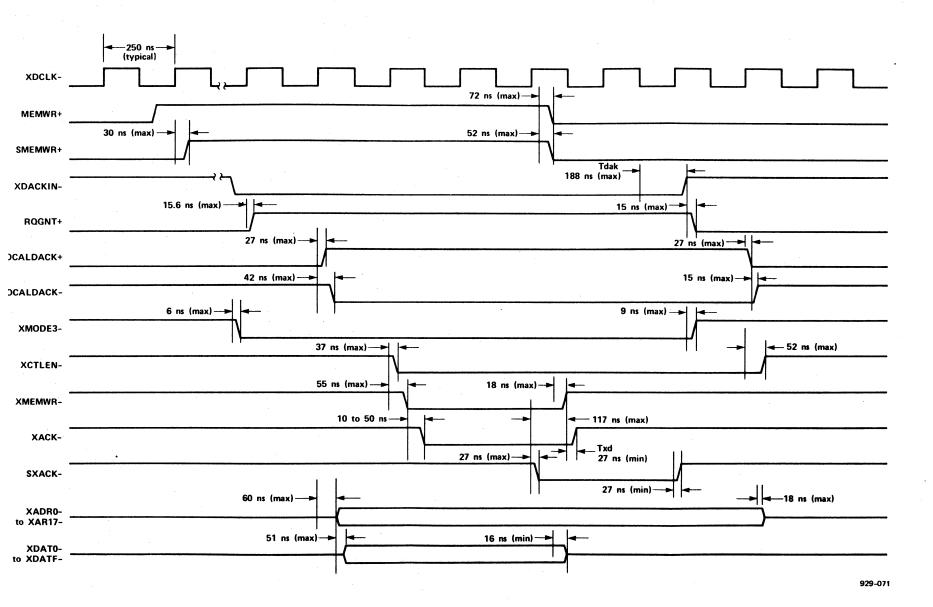

This causes pin 5 of 13C to go high. At the same time, pin 6 of 13C goes high and is driven to the clock of 14B (pin 9). The output of pin 10, CPUMEMRD+ (CPU Memory Read), is high. This means that data is read from the memory, and then written to the tape. CPUMEMRD+ is high, so pin 3 of 14E is also high. (See Figure 3-4.)

One clock later, pin 2 of 14E goes high, and then the output of pin 5 goes high, which is SMEMRD+ (Synchronous Memory Read). Pin 8 of 13C generates LOCAL RQ+ (Local Request), which is high and goes to pin 1 of 17B. Pin 3 of 17B then goes low and drives pin 11 of 15A (XDRQ10UT-) low, which indicates that there is a DMA request pending.

(From Figure B-1, Page 3, Coordinate 6C.)

The CPU acknowledges the request by lowering XDACKIN- (DMA Acknowledge In) via connector Jl, pin 50.

(From Figure B-1, Page 3, Coordinate 8B.)

XDACKIN- goes low, pin 6 of 14C goes high, and DCLK- (Data Clock) clocks pin 5 of 14D, which also goes high. SDACK+ (Synchronous DMA Acknowledge) clocks pin 11 of 14D. Since pin 8 of 13C is high, there is a request pending. Pin 8 is tied to pin 12 of 14D. This means that pin 9 of 14D will be high, indicating that there is a bus available and the request has been granted. One clock later, LOCAL DACK- goes high, and LOCAL DACK- at pin 16 of 13E goes low, which enables the DMA.

(From Figure B-1, Page 3, Coordinate 3C.)

When XACKIN+ is high, pin 11 of 14C generates XMODE3-, which is low-asserted. This means that the address line is asserted, so a read is being performed from the CPU. When pin 3 of 15C is low, XCTLEN- enables transceiver 13E, generates XMEMRDat pin 3, and sends it to the CPU.

(From Figure B-1, Page 3, Coordinate 6C.)

When LOCAL DACK- is asserted, the address is driven on the X-Bus address lines through inverted buffers 7D, 5D, and 6D. As shown in the following two windows, the address counters (8D, 9D, 4C, 5C, 6C, and 7C) are incremented at the trailing edge of LOCAL DACK-.

(From Figure B-1, Page 4, Coordinate 4C.)

(From Figure B-1, Page 5, Coordinate 4C.)

The mode 3 master DMA supplies the address and control lines during the DMA cycle. When the CPU receives a DMA, and when an XMEMRD- from pin 3 of 13E is asserted, the CPU issues XACK-, indicating that the data has been supplied.

| CPUMEMRD+ |  |                                       | 13E<br>74L5240<br>17 3 |

|-----------|--|---------------------------------------|------------------------|

|           |  | · · · · · · · · · · · · · · · · · · · |                        |

|           |  |                                       |                        |

|           |  | , •                                   | 13E 741                |

| MEMWR+    |  |                                       | 15 5                   |

|           |  | <u> </u>                              | P19                    |

| -         |  |                                       | K -                    |

(From Figure B-1, Page 3, Coordinate 6D.)

Two clocks later, the CPU issues a XACK-. The delay on XACK- at pin 3 of 13D goes low, pin 2 of 13D goes low, and pin 11 of 13C goes low, clearing the request. When the CPU returns with XACK-(indicating that the CPU has supplied the data and cleared the request), pin 8 of 13C goes low. One clock later, pin 2 of 13D goes low, forcing XACKlow. Since LOCAL DACK- is already low, pin 11 of 13C and pin 8 of 11B are low, clearing pin 1 of 14E and 14B.

(From Figure B-1, Page 3, Coordinate 7D.)

This sequence clears the CPU memory, inverting it from high to low, bringing XMEMRD- high. Since pin 17 of 13E is low, the output of pin 3 (XMEMRD-) is high and completes the memory read cycle. At the same time, CPUMEMRD- at pin 11 of 14B goes high and clock the data on the data bus at pin 11 of 1E and 3D.

(From Figure B-1, Page 4, Coordinate 7D.)

Upon completion of DMA, pin 11 of 14B goes high, and CPUMEMRD- clocks flip-flop 13A at pin 3. It then clocks the data on the X-Bus data bus to register 1E and 3D. Pin 5 of 3A is driven high by gate 7A, requesting that a byte be written to the tape drive.

#### DMA MEMORY WRITE

The DMA memory write operation is identical to the DMA memory read operation, except for the following:

- o TPRDOP+ is enabled

- MEMWR+ is asserted to write the content from registers 1D and 2D to memory

A timing diagram for the DMA Memory Write operation is shown in Figure 3-5.

3-58 Quarter-Inch Cartridge Tape Hardware Manual

Figure 3-5. Mode 3 DMA Memory Write Timing Diagram

# TAPE DRIVE INTERFACE LOGIC

The tape drive control circuitry communicates with the tape drive through a QIC-02 interface, which contains

- o four control lines from the tape drive control circuitry

- o four control lines from the tape drive

- o one 8-bit bidirectional bus (TBUS)

The control lines for the tape drive control circuitry and the tape drive are shown in Table 3-2 and Table 3-3, respectively.

For detailed information on the tape drive interface, see the manufacturer's drive manual in Chapter 4, "Drive Specifications," which includes the following:

o control lines

o bidirectional bus lines

- o pin assignments

- o interface signal timing

- o signal terminations

- o signal loading

- o power interface

Table 3-2. Tape Drive Control Circuitry Control Lines

| Signal | Function |

|--------|----------|

|        |          |

REQUEST- Driven by the control circuitry to signal the tape drive that a command is present on the TBUS

ON LINE- Host-generated control signal asserted prior to initiating a read or write operation and reset to terminate a read or write operation

TRANSFER- Data handshake signal from the Processor Module, used with ACKNOWLEDGE- from the tape drive to transfer data asynchronously across the interface

RESET-

Causes the tape drive to perform power-on/reset sequence

| Table | 3-3. | Tape  | Drive | Control | Lines |

|-------|------|-------|-------|---------|-------|

|       |      | (Page | l of  | 2)      |       |

# Signal Function

READY- Tape drive generated signal which indicates one of the following:

o a command has been taken from the TBUS

o data has been placed on the TBUS during a read-status sequence

- o a beginning-of-tape, retention, or erase sequence has been completed

- o a buffer is ready to be filled by the host, or a Write File Mark command can be issued, or ONLINE- deasserted during a write-data sequence

- o a Write File Mark command has been completed during a writefile-mark sequence

- o a buffer is ready to be emptied in the read mode

- o the tape drive is ready to receive a new command

| Table 3 | -3. Ta | pe Dri | ve ( | Control | Lines |

|---------|--------|--------|------|---------|-------|

|         | (P     | age 2  | of 2 | 2)      |       |

# Signal Function

EXCEPTION- Signals the termination of an operation. The termination referred to may be a normal completion or an interruption due to a fault. The host must initiate a sense interrupt status.

- ACKNOWLEDGE-Handshake signal from the tape with TRANSFERdrive, used to transfer data across the TBUS asynchronously.

- DIRECTION- When true, data flows to the control circuitry. When false, data flows to the tape drive.

#### 8253 PROGRAMMABLE INTERVAL TIMER

The tape control circuitry uses an 8253 programmable interval timer (8B) resident on the Tape Drive Control board. Counter Ø is used to count the number of bytes to be transferred to the tape drive. Counter 1 is used to detect the 512-byte block boundary. Counter 2 is not used. The pin assignments and functions of timer 8B are provided in Table 3-4.

# 3-64 Quarter-Inch Cartridge Tape Hardware Manual

(From Figure B-1, Page 5, Coordinate 7B.)

8B is selected when 17B issues 8253 CS- from pin 6. When selected, the CPU writes to several registers in 8B (using the XIOWR- strobe) to set the timing mode.

(From Figure B-1, Page 2, Coordinate 5A.)

| Table 3-4. | 8253 Programmable Interval Timer 8B<br>Pin Assignments and Functions<br>(Page 1 of 2)                       |

|------------|-------------------------------------------------------------------------------------------------------------|

| <u>Pin</u> | Function                                                                                                    |

| 1 to 8     | Data Bus Lines (DØ+ through D7+).<br>Bidirectional buffered data bus,<br>which interfaces to system bus.    |

| 9          | <b>Clock Ø (CLKØ+).</b> Clock input of counter Ø.                                                           |

| 10         | <b>Output Ø (OUTØ+).</b> Used for counting<br>the number of bytes to be trans-<br>ferred to the tape drive. |

| 11         | <b>Gate Ø (GATEØ+).</b> Gate input of counter Ø; strapped to +5 V.                                          |

| 12         | Ground.                                                                                                     |

| 13         | <b>Output 1 (OUT1+).</b> Used for the 512-byte block boundary counter.                                      |

| 14         | <b>Gate l (GATEl+).</b> Gate input of counter l.                                                            |

| 15         | <b>Clock l (CLKl+).</b> 1-MHz clock input<br>of counter l.                                                  |

| 16         | Gate 2 (GATE2+). Not used.                                                                                  |

| 17         | Output 2 (OUT2+). Not used.                                                                                 |

3-66 Quarter-Inch Cartridge Tape Hardware Manual

| Table 3-4. | 8253 Programmable Interval Timer 8B<br>Pin Assignments and Functions<br>(Page 2 of 2)                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin        | Function                                                                                                                                                                                   |