Any shipment to a country outside of the United States requires a U.S. Government export license.

## **CRAY COMPUTER SYSTEMS**

CRAY X-MP SERIES

MODELS 22 & 24

MAINFRAME REFERENCE MANUAL

HR-0032

Copyright® 1982, 1984 by CRAY RESEARCH, INC. This manual or parts thereof may not be reproduced in any form without permission of CRAY RESEARCH, INC.

#### RECORD OF REVISION

PUBLICATION NUMBER HR-0032

Each time this manual is revised and reprinted, all changes issued against the previous version in the form of change packets are incorporated into the new version and the new version is assigned an alphabetic level. Between reprints, changes may be issued against the current version in the form of change packets. Each change packet is assigned a numeric designator, starting with 01 for the first change packet of each revision level.

Every page changed by a reprint or by a change packet has the revision level and change packet number in the lower righthand corner. Changes to part of a page are noted by a change bar along the margin of the page. A change bar in the margin opposite the page number indicates that the entire page is new; a dot in the same place indicates that information has been moved from one page to another, but has not otherwise changed.

Requests for copies of Cray Research, Inc. publications and comments about these publications should be directed to: CRAY RESEARCH, INC.,

1440 Northland Drive,

Mendota Heights, Minnesota 55120

| Revision | Description |      |   |          |           |

|----------|-------------|------|---|----------|-----------|

|          | November,   | 1982 | _ | Original | printing. |

A July, 1984 - Reprint with revision. Instructions were added for hardware performance monitoring and SECDED maintenance functions. Information was also added to explain how the Second Vector Logical functional unit is used although this functional unit is not available on all systems. Numerous technical and editorial changes and corrections were also made. This revision obsoletes all previous printings.

# **PREFACE**

This publication describes the functions of CRAY X-MP Series dual-processor computer systems, models 22 and 24. It is written to assist programmers and engineers and assumes a familiarity with digital computers.

The manual describes the overall computer system, its configurations, and equipment. It also describes the operation of the Central Processing Units that execute instructions, provide memory protection, report hardware exceptions, and provide interprocessor communications within the computer systems.

Details of the I/O Subsystem, the disk storage units, and the Solid-state Storage Device are given in the following publications:

HR-0030 I/O Subsystem Hardware Reference Manual

HR-0630 Mass Storage Subsystem Hardware Reference Manual

HR-0031 Solid-state Storage Device (SSD®) Reference Manual

#### WARNING

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

# CONTENTS

| PRE | FACE                                       | • | • | • | • | • | • | iii  |

|-----|--------------------------------------------|---|---|---|---|---|---|------|

| 1.  | SYSTEM DESCRIPTION                         |   | • | • |   | • | • | 1-1  |

|     | INTRODUCTION                               | _ |   |   | _ | _ | _ | 1-1  |

|     | CONVENTIONS                                |   |   |   |   |   | • | 1-4  |

|     | Italics                                    |   |   |   |   |   | • | 1-4  |

|     | Register conventions                       |   |   |   |   |   |   | 1-4  |

|     | Number conventions                         |   |   |   |   |   |   | 1-4  |

|     | Clock period                               |   |   |   |   |   |   | 1-4  |

|     | SYSTEM COMPONENTS                          |   |   |   |   |   | • | 1-5  |

|     | Central Processing Units                   |   |   |   |   |   |   | 1-5  |

|     | Interfaces                                 |   |   |   |   |   |   | 1-7  |

|     | I/O Subsystem                              |   |   |   |   |   |   | 1-9  |

|     | Disk storage units                         |   |   |   |   |   |   | 1-11 |

|     | Solid-state Storage Device                 |   |   |   |   |   |   | 1-12 |

|     | Condensing units                           |   |   |   |   |   |   | 1-13 |

|     | Power distribution units                   |   |   |   |   |   |   | 1-14 |

|     | Motor-generator units                      |   |   |   |   |   |   | 1-15 |

|     | SYSTEM CONFIGURATION                       |   |   |   |   |   |   | 1-16 |

| 2.  | CPU SHARED RESOURCES                       | • | • | • | • | • | • | 2-1  |

|     | INTRODUCTION                               |   |   |   |   |   | • | 2-1  |

|     | CENTRAL MEMORY                             |   |   |   |   |   |   | 2-1  |

|     | Memory organization                        |   |   |   |   |   |   | 2-2  |

|     | Memory addressing                          |   |   |   |   |   |   | 2-3  |

|     | Memory addressing for 6-column mainframe . |   | • | • | • | • | • | 2-3  |

|     | Memory addressing for 12-column mainframe  | • | • | • | • | • | • | 2-4  |

|     | Memory access                              |   |   |   |   |   |   | 2-4  |

|     | Conflict resolution                        | • | • | • | • | • | • | 2-7  |

|     | Bank Busy conflict                         |   |   |   |   |   |   | 2-7  |

|     | Simultaneous Bank conflict                 |   |   |   |   |   |   | 2-7  |

|     | Section Access conflict                    |   |   |   |   |   |   | 2-7  |

|     | Memory access priorities                   | • | • | • | • | • | • | 2-7  |

|     | 16-bank phasing                            | • | • | • | • | • | • | 2-8  |

|     | Memory error correction                    |   |   |   |   |   |   | 2-8  |

|     | INTER-CPU COMMUNICATION SECTION            |   |   |   |   |   |   | 2-10 |

|     | Real-time clock                            |   |   |   |   |   |   | 2-10 |

|     | Inter-CPU communication and control        |   |   |   |   |   |   | 2-11 |

|     | Shared Address and Shared Scalar registers | • | • | • | • | • | • |      |

|     | Compohera registers                        |   |   |   |   |   |   | 2_12 |

### 2. CPU SHARED RESOURCES (continued)

|    | CPU INPUT/OUTPUT SECTION                                              |    | • | • | • | • | • | • | 2-14         |

|----|-----------------------------------------------------------------------|----|---|---|---|---|---|---|--------------|

|    | Data transfer for Solid-state Storage Device                          | •  | • | • | • | • | • | • | 2-15         |

|    | Data transfer for I/O Subsystem                                       | •  | • | • | • | • | • | • | 2-16         |

|    | 6 Mbyte per second channels                                           | •  | • | • | • | • | • | • | 2-16         |

|    | Multi-CPU programming                                                 | .• | • | • | • | • | • | • | 2-17         |

|    | 6 Mbyte per second channel operation                                  | •  | • | • | • | • | • | • | 2-18         |

|    | Input channel programming                                             | •  | • | • | • | • | • | • | 2-19         |

|    | Input channel error conditions                                        | •  | • | • | • | • | • | • | 2-20         |

|    | Output channel programming                                            | •  | • | • | • | • | • | • | 2-20         |

|    | Programmed master clear to external device .                          | •  | • | • | • | • | • | • | 2-21         |

|    | Memory access                                                         | •  | • | • | • | • | • | • | 2-21         |

|    | I/O lockout                                                           |    | • | • | • | • | • | • | 2-24         |

|    | Memory bank conflicts                                                 | •  | • | • | • | • | • | • | 2-24         |

|    | I/O memory conflicts                                                  | •  | • | • | • | • | • | • | 2-24         |

|    | I/O memory request conditions                                         |    |   |   |   |   |   |   | 2-25         |

|    | I/O memory addressing                                                 | •  | • | • | • | • | • | • | 2-25         |

|    |                                                                       |    |   |   |   |   |   |   |              |

|    |                                                                       |    |   |   |   |   |   |   |              |

| 3. | CPU CONTROL SECTION                                                   | •  | • | • | • | • | • | • | 3–1          |

|    |                                                                       |    |   |   |   |   |   |   |              |

|    | INTRODUCTION                                                          |    |   |   |   |   |   |   | 3-1          |

|    | INSTRUCTION ISSUE AND CONTROL                                         |    |   |   |   |   |   |   | 3-1          |

|    | Program Address register                                              |    |   |   |   |   |   |   | 3-2          |

|    | Next Instruction Parcel register                                      |    |   |   |   |   |   |   | 3-2          |

|    | Current Instruction Parcel register                                   |    |   |   |   |   |   |   | 3-2          |

|    | Lower Instruction Parcel register                                     |    |   |   |   |   |   |   | 3-3          |

|    | Instruction buffers                                                   |    |   |   |   |   |   |   | 3-3          |

|    | EXCHANGE MECHANISM                                                    |    |   |   |   |   |   |   | 3-5          |

|    | Exchange Package                                                      |    |   |   |   |   |   |   | 3-5          |

|    | Processor number                                                      |    |   |   |   |   |   |   | 3-7          |

|    | Vector not used (VNU)                                                 |    |   |   |   |   |   |   | 3-7          |

|    | Enable second vector logical (ESVL)                                   |    |   |   |   |   |   |   | 3-8          |

|    | Memory error data                                                     |    |   |   |   |   |   |   | 3-8          |

|    | Exchange registers                                                    |    |   |   |   |   |   |   | 3-9          |

|    | Exchange Address register                                             |    |   |   |   |   |   |   | 3-9          |

|    | Mode register                                                         |    |   |   |   |   |   |   | 3-9<br>3-11  |

|    | Flag register                                                         |    |   |   |   |   |   |   |              |

|    | Cluster Number register                                               | •  | • | • | • | • | • | • | 3-12         |

|    | Program State register                                                |    |   |   |   |   |   |   | 3-12         |

|    | A registers                                                           |    |   |   |   |   |   |   | 3-12         |

|    | S registers                                                           |    |   |   |   |   |   |   | 3-12         |

|    | Program Address register                                              |    |   |   |   |   |   |   | 3-13         |

|    | Memory field registers                                                |    |   |   |   |   |   |   | 3-13         |

|    | Active Exchange Package                                               |    |   |   |   |   |   |   | 3-13         |

|    | Exchange sequence                                                     |    |   |   |   |   |   |   | 3-13         |

|    | Exchange initiated by deadstart sequence                              |    |   |   |   |   |   |   | 3-14         |

|    | Exchange initiated by Interrupt flag set                              |    |   |   |   |   |   |   | 3-14<br>3-14 |

|    | Exchange initiated by program exit Exchange sequence issue conditions |    |   |   |   |   |   |   |              |

|    | Exchange sequence issue conditions                                    | •  | • | • | • | • | • | • | 3-15         |

|    |                                                                       |    |   |   |   |   |   |   |              |

### 3. CPU CONTROL SECTION (continued)

|    | MEMORY FIELD PROTECTION                    | 3-16 |

|----|--------------------------------------------|------|

|    | Instruction Base Address register          | 3-17 |

|    | Instruction Limit Address register         | 3-17 |

|    | Data Base Address register                 | 3-18 |

|    | Data Limit Address register                | 3-18 |

|    | Program range error                        | 3-18 |

|    | Operand range error                        | 3-19 |

|    | PROGRAMMABLE CLOCK                         | 3-19 |

|    | Instructions                               | 3-19 |

|    | Interrupt Interval register                | 3-19 |

|    | Interrupt Countdown counter                | 3-20 |

|    | Clear programmable clock interrupt request | 3-20 |

|    | PERFORMANCE MONITOR                        | 3-20 |

|    | DEADSTART SEQUENCE                         |      |

|    |                                            | J 22 |

|    |                                            |      |

| 4. | CPU COMPUTATION SECTION                    | 4-1  |

|    |                                            |      |

|    | INTRODUCTION                               | 4-1  |

|    | OPERATING REGISTERS                        | 4-3  |

|    | ADDRESS REGISTERS                          | 4-3  |

|    | A registers                                | 4-3  |

|    | B registers                                | 4-5  |

|    | SCALAR REGISTERS                           | 4-6  |

|    | S registers                                | 4-6  |

|    | T registers                                | 4-8  |

|    | VECTOR REGISTERS                           | 4-9  |

|    | V registers                                | 4-9  |

|    | V register reservations and chaining       | 4-12 |

|    | Vector control registers                   | 4-13 |

|    | Vector Length register                     | 4-13 |

|    | Vector Mask register                       | 4-13 |

|    | FUNCTIONAL UNITS                           | 4-14 |

|    | Address functional units                   | 4-14 |

|    | Address Add functional unit                | 4-15 |

|    | Address Multiply functional unit           | 4-15 |

|    |                                            | 4-15 |

|    | Scalar functional units                    | 4-15 |

|    | Scalar Shift functional unit               | 4-16 |

|    | Scalar Logical functional unit             | 4-16 |

|    | Scalar Population/Parity/Leading Zero      | 4-T0 |

|    | functional unit                            | 4-16 |

|    | Vector functional units                    | 4-16 |

|    | Vector functional unit reservation         | 4-17 |

|    | Vector Add functional unit                 | 4-17 |

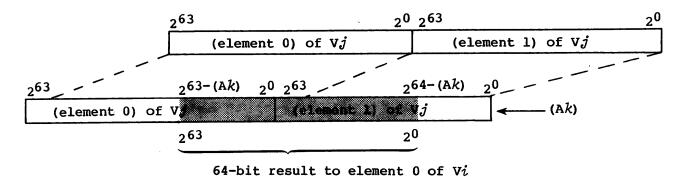

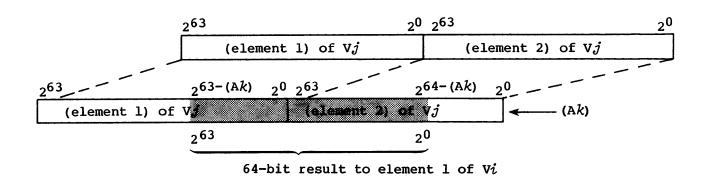

|    | Vector Shift functional unit               | 4-17 |

|    | Full Vector Logical functional unit        | 4-17 |

|    | Second Vector Logical functional unit      | 4-18 |

|    | Voctor Population/Parity functional unit   | 4-10 |

|    |                                            |      |

### FUNCTIONAL UNITS (continued)

|     | Floating-point functional units                             | • | • | • | • | • | 4-20 |

|-----|-------------------------------------------------------------|---|---|---|---|---|------|

|     | Floating-point Add functional unit                          |   |   |   |   |   | 4-20 |

|     | Floating-point Multiply functional unit                     | • | • | • | • |   | 4-20 |

|     | Reciprocal Approximation functional unit                    |   |   |   |   |   |      |

|     | ARITHMETIC OPERATIONS                                       |   |   |   |   |   |      |

|     | Integer arithmetic                                          |   |   |   |   |   |      |

|     | Floating-point arithmetic                                   |   |   |   |   |   | 4-22 |

|     | Normalized floating-point numbers                           |   |   |   |   |   | 4-23 |

|     | Floating-point range errors                                 |   |   |   |   |   |      |

|     | Floating-point Add functional unit                          |   |   |   |   |   |      |

|     | Floating-point Multiply functional unit                     |   |   |   |   |   |      |

|     | Floating-point Reciprocal Approximation                     |   | Ť | • |   | • |      |

|     | functional unit                                             |   | _ | _ | _ | _ | 4-27 |

|     | Double-precision numbers                                    |   |   |   |   |   |      |

|     | Addition algorithm                                          |   |   |   |   |   |      |

|     |                                                             |   |   |   |   |   |      |

|     | Multiplication algorithm                                    |   |   |   |   |   |      |

|     | Division algorithm                                          |   |   |   |   |   |      |

|     | Newton's method                                             |   |   |   |   |   |      |

|     | Derivation of the division algorithm                        |   |   |   |   |   |      |

|     | LOGICAL OPERATIONS                                          | • | • | • | • | • | 4-35 |

|     |                                                             |   |   |   |   |   |      |

| _   |                                                             |   |   |   |   |   | - 1  |

| 5.  | CPU INSTRUCTIONS                                            | • | • | • | • | • | 2-T  |

|     | TVOMPTOMION PODMAM                                          |   |   |   |   |   | E 1  |

|     | INSTRUCTION FORMAT                                          | • | • | • | • | • | 2-I  |

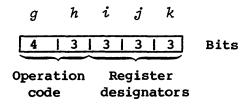

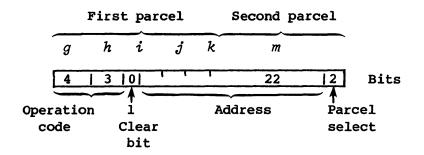

|     | 1-parcel instruction format with discrete $j$               |   |   |   |   |   |      |

|     | and $k$ fields                                              | • | • | • | • | • | 5-1  |

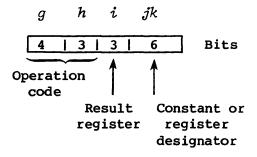

|     | 1-parcel instruction format with combined $j$               |   |   |   |   |   |      |

|     | and $k$ fields                                              | • | • | • | • | • | 5-2  |

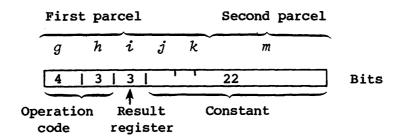

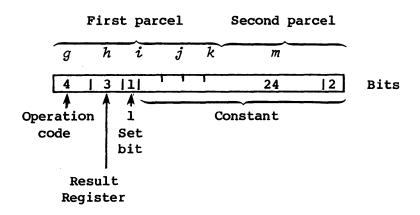

|     | 2-parcel instruction format with combined $j$ , $k$ ,       |   |   |   |   |   |      |

|     | and $m$ fields                                              |   |   | • | • | • | 5-2  |

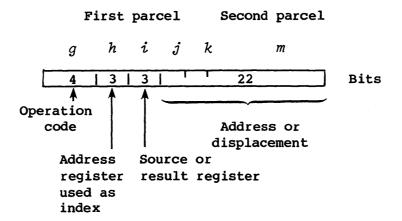

|     | 2-parcel instruction format with combined $i$ , $j$ , $k$ , |   |   |   |   |   |      |

|     | and <i>m</i> fields                                         |   |   |   |   |   |      |

|     | SPECIAL REGISTER VALUES                                     | • | • | • | • | • | 5-4  |

|     | INSTRUCTION ISSUE                                           |   |   |   |   |   |      |

|     | INSTRUCTION DESCRIPTIONS                                    | • | • | • | • | • | 5-6  |

|     |                                                             |   |   |   |   |   |      |

|     |                                                             |   |   |   |   |   |      |

| APE | PENDIX SECTION                                              |   |   |   |   |   |      |

|     |                                                             |   |   |   |   |   |      |

|     |                                                             |   |   |   |   |   |      |

| A.  | INSTRUCTION SUMMARY FOR CRAY X-MP MODELS 22 AND 24          | • | • | • | • | • | A-l  |

|     |                                                             |   |   |   |   |   |      |

|     |                                                             |   |   |   |   |   |      |

| В.  | 6 MBYTE PER SECOND CHANNEL DESCRIPTIONS                     |   |   |   | _ |   | B-1  |

|     |                                                             | - | - | - | - | - |      |

|     | INTRODUCTION                                                |   | _ | _ | _ | _ | B-1  |

|     | 6 MBYTE PER SECOND INPUT CHANNEL SIGNAL SEQUENCE            |   |   | • | - | • | B-1  |

|     | Data bits 20 through 215                                    | • | • | • | • | • | B-1  |

|     | Darity hite 0 through ?                                     | • | • | • | • | • | B-2  |

| (                  | 6 MBYTE PER SECOND INPUT CHANNEL SIGNAL SEQUENCE (CONTINUED)                     |            |

|--------------------|----------------------------------------------------------------------------------|------------|

|                    | Ready signal                                                                     | B-3        |

|                    | Resume signal                                                                    | B-3        |

|                    | Disconnect signal                                                                | B-3        |

| (                  | 6 MBYTE PER SECOND OUTPUT CHANNEL SIGNAL SEQUENCE                                | B-3        |

|                    | Data bits 2 <sup>0</sup> through 2 <sup>15</sup>                                 | B-4        |

|                    | Parity bits 0 through 3                                                          | B-5        |

|                    | Ready signal                                                                     | B-5        |

|                    | Resume signal                                                                    |            |

|                    |                                                                                  | B-5        |

|                    | Disconnect signal                                                                | B-5        |

| <b>c.</b> <u>1</u> | PERFORMANCE MONITOR                                                              | C-1        |

|                    | INTRODUCTION                                                                     | C-1        |

|                    | SELECTING PERFORMANCE EVENTS                                                     |            |

|                    | READING PERFORMANCE RESULTS                                                      | C-3        |

|                    | TESTING PERFORMANCE COUNTERS                                                     | C-3        |

| •                  | IEDITING PERFORMACE COUNTERD                                                     | C-3        |

| D. <u>s</u>        | SECDED MAINTENANCE FUNCTIONS                                                     | D-1        |

|                    | TIMPODUOMION                                                                     | n 1        |

|                    | INTRODUCTION                                                                     | D-1        |

|                    | VERIFICATION OF CHECK BIT STORAGE                                                | D-1        |

|                    | VERIFICATION OF CHECK BIT GENERATION                                             | D-2        |

|                    | VERIFICATION OF ERROR DETECTION AND CORRECTION                                   | D-2        |

| (                  | CLEARING MAINTENANCE MODE FUNCTIONS                                              | D-3        |

| FIGUI              | RES                                                                              |            |

| 1-1                | CRAY X-MP Model 22 or 24 12-column mainframe with a                              |            |

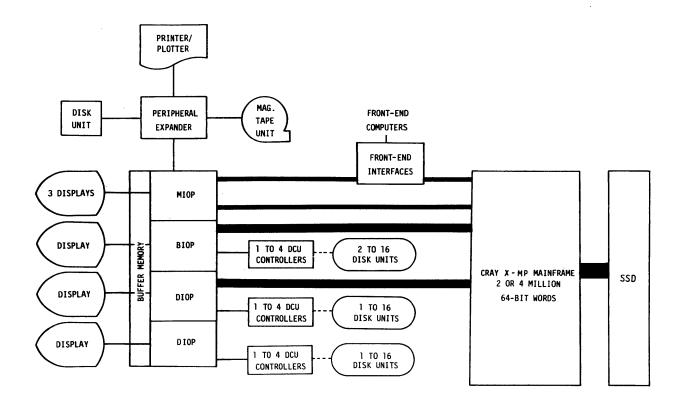

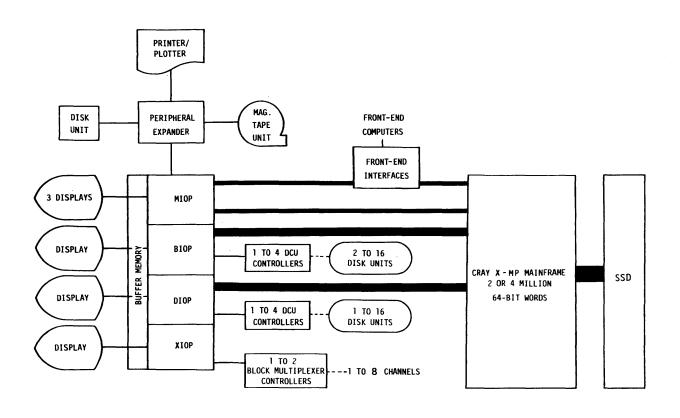

|                    | Cray I/O Subsystem and an SSD                                                    | 1-2        |

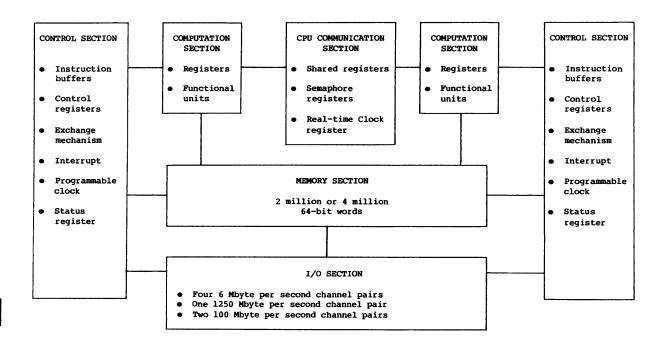

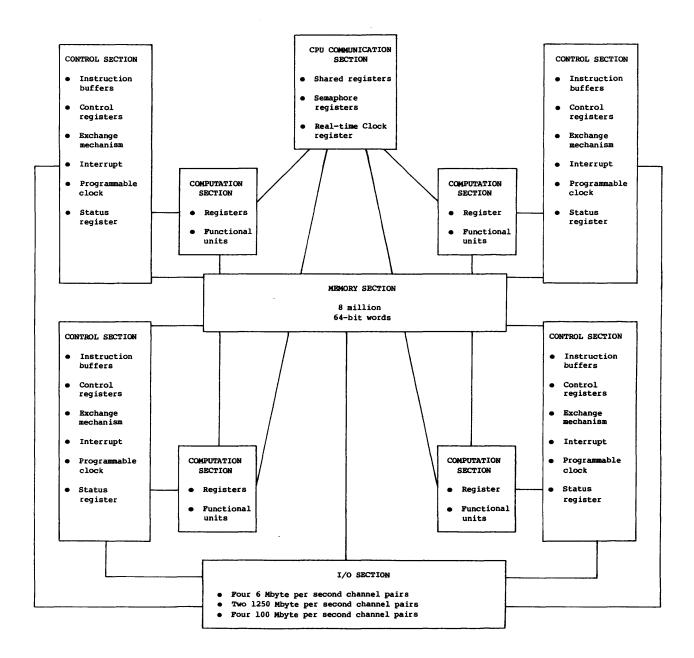

| 1-2                | Basic organization of the dual-processor system                                  | 1-5        |

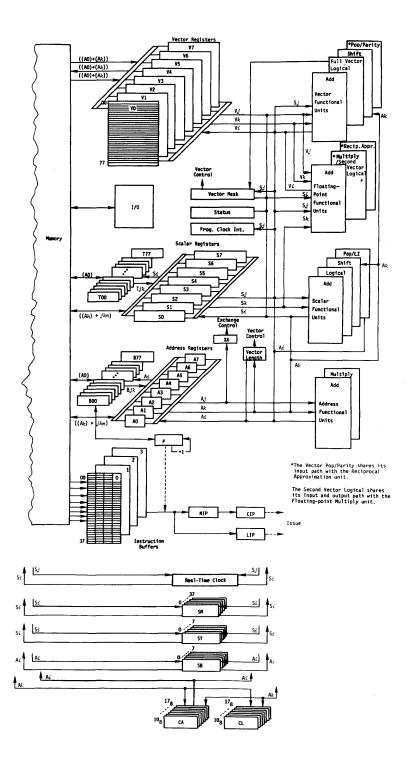

| 1-3                | Control and data paths for a single CPU                                          |            |

| 1-4                | CRAY X-MP Models 22 or 24 6-column mainframe chassis                             |            |

| 1-5                | Typical interface cabinet                                                        | -          |

| 1-6                | I/O Subsystem chassis                                                            |            |

| 1-7                | •                                                                                |            |

| 1-8                | DD-29 Disk Storage Unit                                                          | 1-11       |

|                    | Solid-state Storage Device chassis                                               | 1-12       |

| 1-9                | Condensing unit                                                                  | 1-13       |

| 1-10               |                                                                                  | 1-14       |

| 1-11               |                                                                                  | 1-15       |

| 1-12               |                                                                                  |            |

|                    | with full disk capacity                                                          | 1-16       |

| 1-13               | Block diagram of CRAY X-MP dual-processor system with block multiplexer channels | 1-17       |

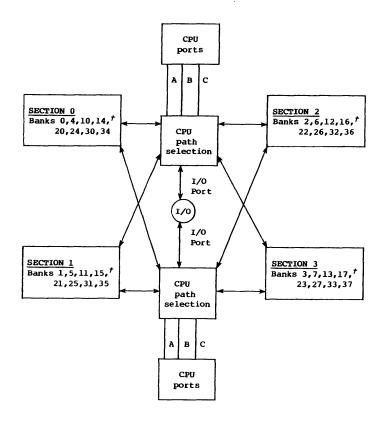

| 2-1                | Central Memory organization for a dual-processor system                          | 2-2        |

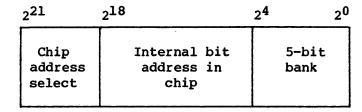

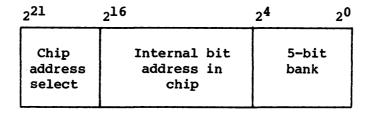

| 2-2                | 6-column memory address (32 banks)                                               | 2-3        |

| 2-2                | 6-column memory address (16 banks)                                               | 2-3        |

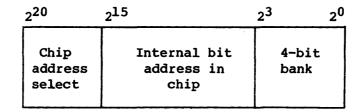

| 2-3<br>2-4         |                                                                                  | 2-3<br>2-4 |

| 4-4                | 12-column memory address (32 banks)                                              | <b>4</b>   |

HR-0032 ix A

# FIGURES (continued)

| 2-5          | 12-column memory address (16 banks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-4         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

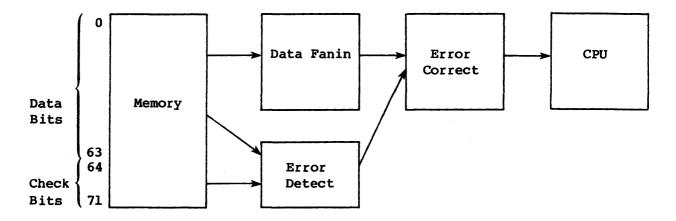

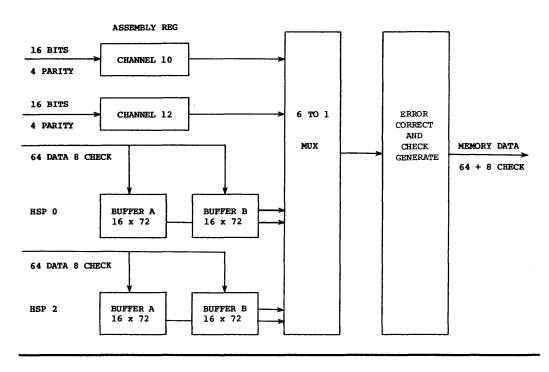

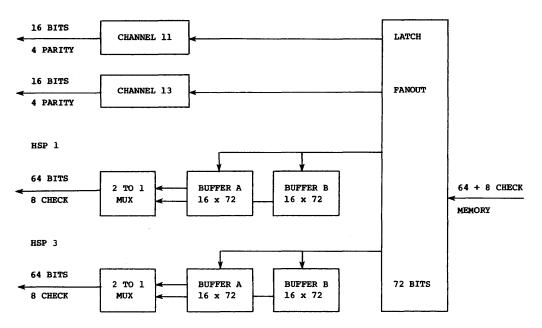

| 2-6          | Memory data path with SECDED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-8         |

| 2-7          | Error correction matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-9         |

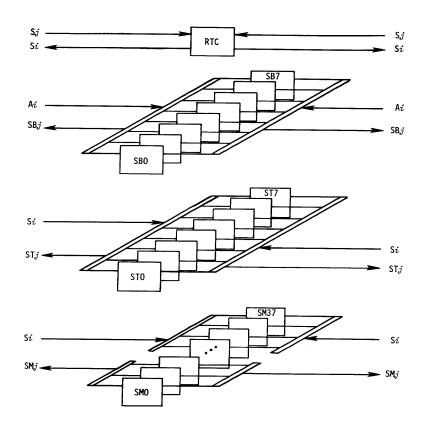

| 2-8          | Shared registers and real-time clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-11        |

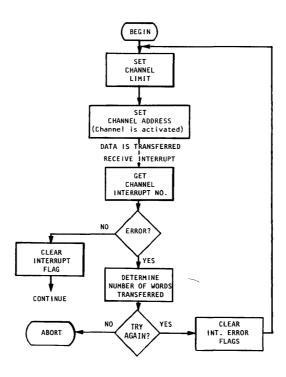

| 2-9          | Basic I/O program flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-19        |

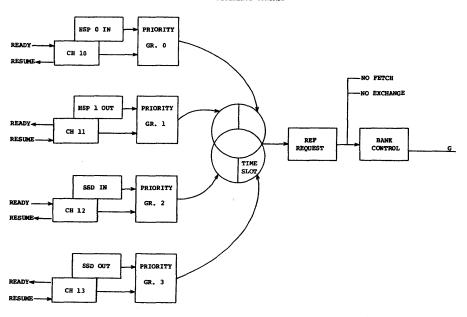

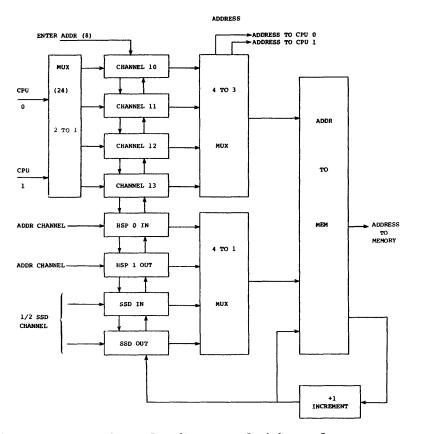

| 2-10         | Channel I/O control (shown for one processor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-22        |

| 2-11         | Input/output data paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-23        |

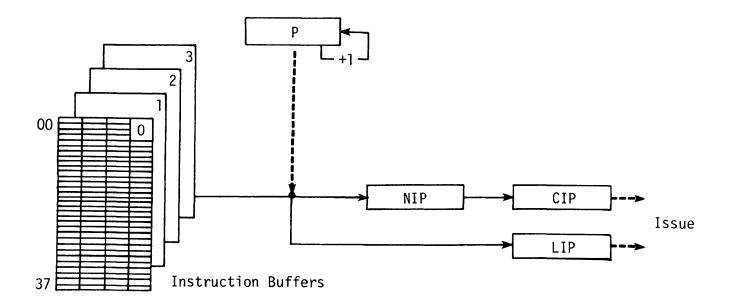

| 3-1          | Instruction issue and control elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-1         |

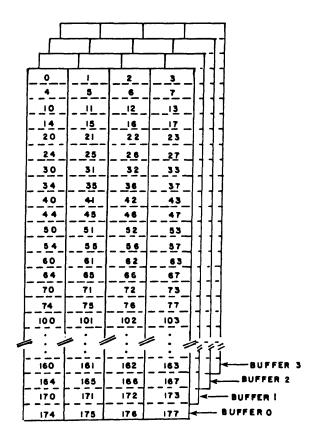

| 3-2          | Instruction buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-3         |

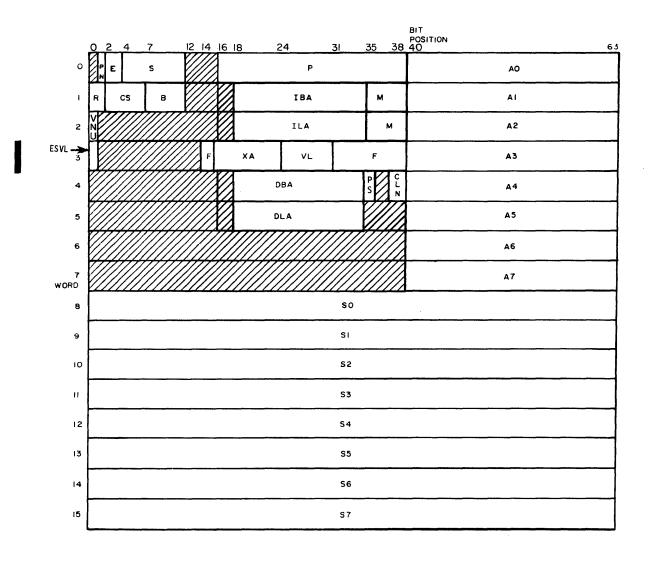

| 3-3          | Exchange Package for a dual-processor system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-6         |

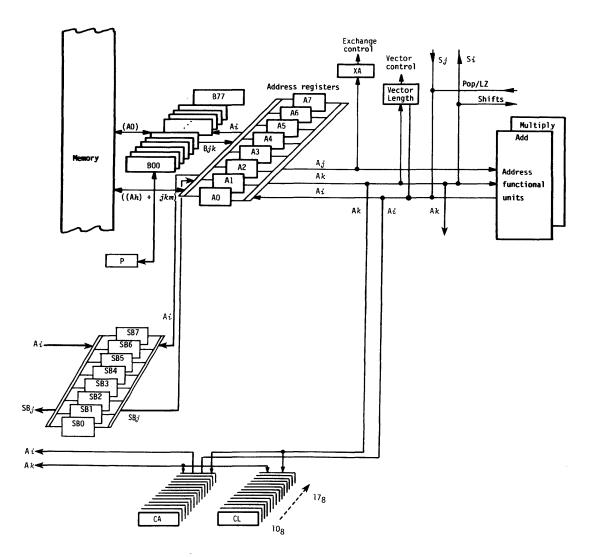

| 4-1          | Address registers and functional units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-4         |

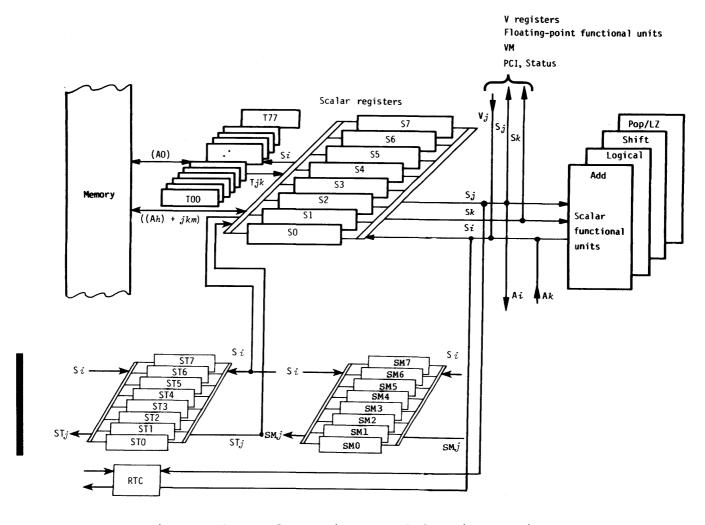

| 4-2          | Scalar registers and functional units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-7         |

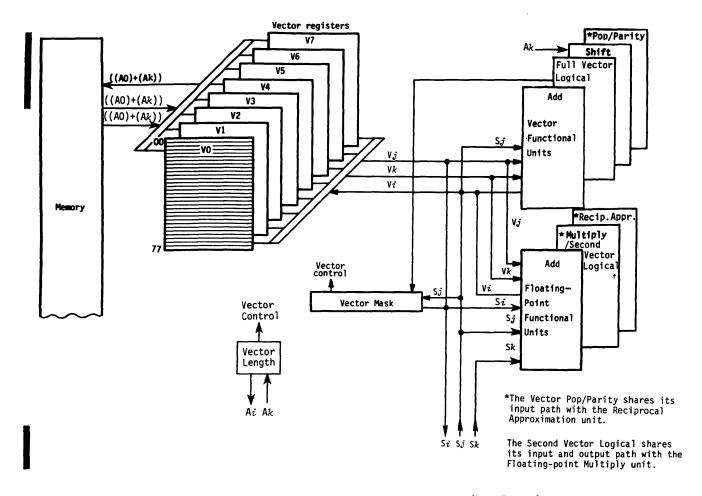

| 4-3          | Vector registers and functional units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-10        |

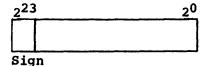

| 4-4          | Integer data formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-22        |

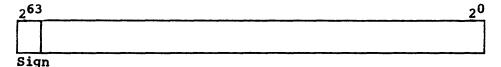

| 4-5          | Floating-point data format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-23        |

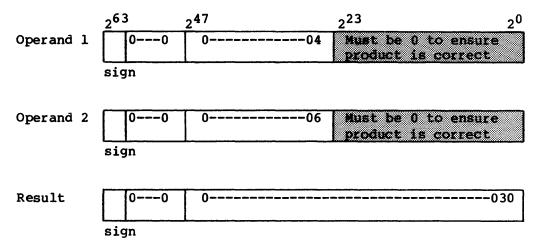

| 4-6          | Exponent matrix for Floating-point Multiply unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-25        |

| 4-7          | Integer multiply in Floating-point Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

|              | functional unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-27        |

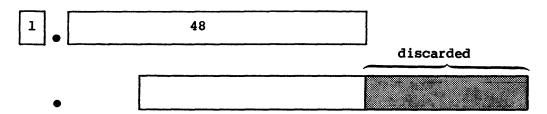

| 4-8          | 49-bit floating-point addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-28        |

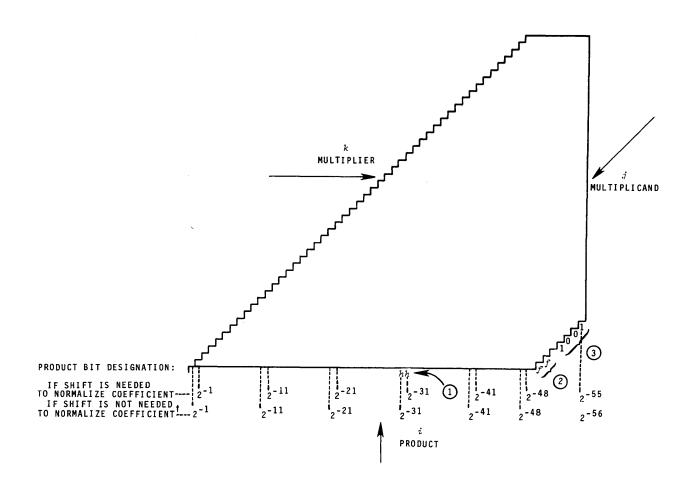

| 4-9          | Floating-point multiply partial-product sums pyramid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-29        |

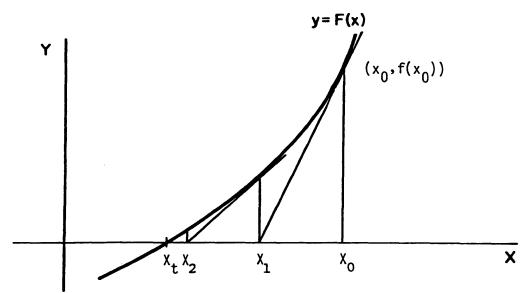

| 4-10         | Newton's method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-31        |

| 5-1          | General form for instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1         |

| 5-2          | 1-parcel instruction format with discrete $j$ and $k$ fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5–2         |