Product specification and hardware reference manual

June 1979 Document No. 60430 Copyright<sup>©</sup> 1979 Datapoint Corporation. Printed in U.S.A.

The "D" logo and Datapoint are trademarks of Datapoint Corporation, registered in the U.S. Patent Office. "The leader in dispersed data processing" is a trademark of Datapoint Corporation.

# PREFACE

The computer-oriented user will find this manual useful for evaluation of Datapoint 6600 system capabilities and limitations. However, only the hardware considerations are covered in this manual. The full utility of the Datapoint 6600 system cannot be appreciated until the available software support for the machine has been reviewed.

A complete family of software packages available for the Datapoint 6600 system includes high-level languages, operating systems, source code and text editors, communications programs, utility programs, etc. Reference should be made to the latest issue of the Datapoint Software Catalog for more complete information.

i

# TABLE OF CONTENTS

| PART 1  | GENERAL FEATURES Pag                                             | je |

|---------|------------------------------------------------------------------|----|

|         | 1.1 Introduction                                                 |    |

|         | 1.2 System Elements                                              |    |

|         | 1.3 CRT Display                                                  |    |

|         | 1.4 Keyboard                                                     |    |

|         | 1.5 Processor                                                    |    |

|         | 1.6 Cassette Tape Decks1                                         |    |

|         | 1.7 General Specifications                                       |    |

|         | 1.8 Peripherals                                                  |    |

| PART 2  | KEYBOARD                                                         |    |

|         | 2.1 General                                                      |    |

|         | 2.2 Keyboard Operation                                           |    |

|         | Table 2-1 Keyboard Codes                                         |    |

| PART 3  | DISPLAY                                                          |    |

|         | 3.1 General Description                                          |    |

|         | 3.2 Display Operations                                           |    |

| PART 4  | CASSETTE TAPES                                                   |    |

| 17411 4 | 4.1 General Description                                          |    |

|         | 4.2 Operations                                                   |    |

|         | 4.3 Status                                                       |    |

|         | 4.3 Control (Table 4-2)                                          |    |

|         | PROCESSOR                                                        |    |

| FARIO   | 5.1 Processor Registers                                          |    |

|         | 5.2 Comparison with Datapoint 5500 and 2200                      |    |

|         | 5.2.1 Input/Output                                               |    |

|         | 5.2.2 Input Parity Checking                                      |    |

|         | 5.2.2 Input Parity Checking                                      |    |

|         | 5.2.4 Compatibility with 5500 and 2200 Systems Peripherals.      |    |

|         |                                                                  |    |

|         | 5.3 Memory                                                       |    |

|         | 5.3.1 Parity Checking                                            |    |

|         | 5.3.2 Physical Layout                                            |    |

|         | 5.3.3 Address Generation                                         |    |

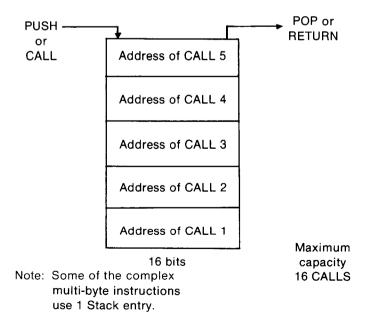

|         | 5.4 Pushdown Stack                                               |    |

|         | 5.5 Control Flip-Flops.                                          |    |

|         | 5.6 System ROM Functions.                                        |    |

|         | 5.7 Interrupt Handling                                           |    |

|         | 5.8 Processor Instructions.                                      |    |

|         | 5.8.1 Comparison to 2200 System Instructions                     |    |

|         | 5.8.2 Presentation Format.                                       |    |

|         | 5.8.3 Category 1 - 2200 Instructions                             |    |

|         | 5.8.4 Category 2 - Augmented Category 1 Instructions             |    |

|         | 5.8.5 Category 3 - Multi-Byte (string) Operations                |    |

|         | 5.8.6 Category 4 - Processor State Save and Restore Instructions |    |

|         | 5.8.7 Category 5 - Address Manipulation Instructions             |    |

|         | 5.8.8 Category 6 - Operating System Control                      |    |

|         | 5.8.9 Category 7 - 6600 Instruction Set                          |    |

|         | 5.8.10 Instructions Timing                                       |    |

# APPENDIX A SYSTEM ROM OPERATING DESCRIPTION

| Chapter | 1. System ROM Functions.     | 35 |

|---------|------------------------------|----|

|         | 1.1 Introduction             | 35 |

|         | 1.2 Power Up                 | 35 |

|         | 1.3 Restart                  | 36 |

| Chapter | 2. Debug                     | 37 |

|         | 2.1 Introduction             | 37 |

|         | 2.2 Starting Procedure.      | 37 |

|         | 2.3 Saving the Machine State | 37 |

|         | 2.4 Display Format           | 37 |

|         | 2.5 Command Syntax           | 37 |

|         | 2.6 Input Command List       | 10 |

.

ŧ

# PART 1 GENERAL FEATURES

#### **1.1 Introduction**

The Datapoint 6600 is a new addition to the Datapoint family of processors. The Datapoint 6600 highlights such features as expanded memory capability to 120K user memory and faster memory and processor cycle times. The Datapoint 6600 is also completely compatible with the Datapoint 1100, 2200, 5500 and 1150.

Note: All numerics preceeded with a leading zero (0) represent an octal value.

### **1.2 System Elements**

There are four basic elements in the 6600 system plus the capability to interface to a number of external peripheral devices.

This chapter introduces the basic elements: CRT, keyboard, processor and cassettes. Further information may be obtained from the following chapters.

# **1.3 CRT Display**

The CRT Display provides the following features:

- a. 7" x 31/2" viewing area;

- b. 960 characters;

- c. 80-character by 12-line format;

- d. Software defined 128-character font;

- e. 60 frames-per-second refresh rate (50 frames-persecond when using 50 hertz power);

- f. 5 x 7 matrix character generation;

- g. 5 x 7 solid, blinking cursor, alternates with characters, nondestructive;

- h. Single control line erasure, frame erasure, page roll-up and roll-down;

- i. Direct control of all CRT functions by the processor, providing tab, editing, form control, etc; and

- j. Writing rate up to 50,000 characters per second.

# 1.4 Keyboard

The integral keyboard provides a basic 55-key alphanumeric group, an 11-key numeric group and five system control keys.

The keyboard provides a unique multi-key roll-over characteristic providing maximum ease of typing. Transfer of characters from the keyboard is under control of the processor. An audible "click" providing an acoustical feedback to the typist is available under processor control.

A programmable audio "beep" is also provided when it is desired to gain a typist's attention.

#### 1.5 Processor

The integral processor provides all control functions and

includes:

- \* 8-bit memory word length (plus parity)

- \* Complete parallel I/O system

- \* Automatic power-up restart

The instruction set contains all instructions used in the Datapoint 1100, 2200, 1150 and 5500 systems, providing complete upward program and input-output compatibility. In addition, the processor characteristics of the 6600 provide:

- \* Higher operating speed

- \* Hardware Multiply/Divide

- \* String moves

- \* Greater speed

- \* Expanded memory

This gives the 6600 considerably greater processing capability than found in the 5500 processors.

#### **1.6 Cassette Tape Decks**

Two read-write tape decks are provided for program and data storage. The deck accepts Norelco (Phillips)-type cassettes and provides:

- a. 47 characters per inch density;

- b. Bi-directional operation; and

- c. Processor controlled data transfer, direction control, and high-speed rewind.

#### **1.7 General Specifications**

POWER REQUIREMENTS: 115 or 240 VAC (+/--10%), 60 or 50 Hz

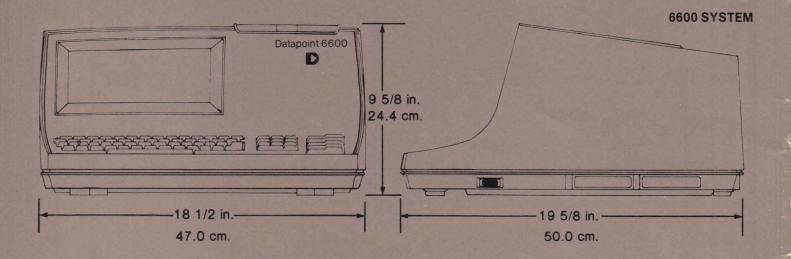

EQUIPMENT DIMENSIONS: Width: 18.5 in. (47 cm) Height: 9.6 in. (24.5 cm) Depth: 19.6 in. (50 cm) Weight: 47 lbs. (21.3 kg)

OPERATING ENVIRONMENT: (excluding media) 10° to 38°C (50° to 100°F) 20 to 80% Relative Humidity (Non-Condensing)

#### **1.8 Peripherals**

The 6600 will accommodate a wide variety of external peripherals, such as asynchronous and synchronous communications adaptors, printers, disks, and magnetic tapes.

# 2.1 General

The keyboard on the Datapoint 6600 processor performs the functions of data entry and processor control.

The integral keyboard provides a basic 55-key alphanumeric key group, an 11-key numeric group and five system control keys.

The keyboard provides a unique multi-key roll-over characteristic providing maximum ease of typing. Transfer of characters from the keyboard is under control of the processor. An audible "click" providing an acoustical feedback to the operator is available under software control.

A programmable audio "beep" is also provided when it is desired to gain the operator's attention.

The 11-key matrix may be optionally supplied with control key coding rather than numeric key coding and with keytops engraved to customer specifications.

The five control keys exert control over the processor. Their names and associated functions are as follows:

# RUN

Momentary contact switch which, when depressed, causes the processor to begin execution of the instruction located at the address in memory currently addressed by the program counter.

# STOP

Momentary contact switch which, when depressed, causes instruction execution to halt at the completion of the current instruction.

# **KEYBOARD**

Momentary contact switch which sets a status bit that may be tested at any time by the processor.

# DISPLAY

Momentary contact switch with a function similar to that of KEYBOARD switch.

# RESTART

Momentary contact switch which causes the processor to halt and executes the Restart routine contained in ROM. To protect against accidental restart, the restart function is inhibited unless the RESTART and RUN keys are depressed simultaneously.

# **2.2 Keyboard Operation**

The keyboard is addressed by the processor by loading the A register\* with 0341 octal and executing an EX ADR command. (The CRT display also uses this address. Data transfers to the processor are from the keyboard and transfers from the processor are to the display.) Following the address sequence the CRT/keyboard status word can be loaded into the A register by executing an INPUT instruction. Bit 1 of the A register may be tested by the program to determine if a character is ready for transfer from the keyboard. The keyboard is single buffered under processor control and is designed such that when a character is entered from the key-

board, another character will not be recognized from the keyboard until the processor accepts the first character entered. Bits 2 and 3 will indicate if either the KEYBOARD or DISPLAY control switch is pressed.

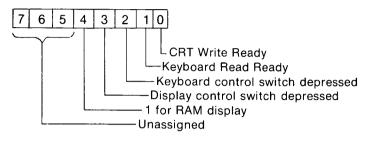

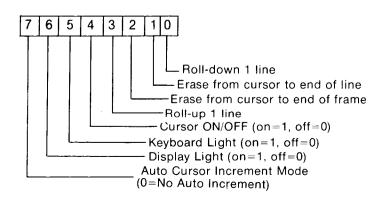

CRT/Keyboard Status Word

The External Commands associated with the operation of the keyboard are as follows:

- a. EX BEEP. This command produces a 1500 Hertz tone for a duration of about 400 msec. The tone could be used as an error or ready signal to the keyboard operator.

- b. EX CLICK. This command produces an audible click which could be used to acknowledge receipt of a valid character when a key is depressed.

- c. EX COM1 (Command 1). Presents a control word contained in the A register to the keyboard. Bit 5 of the control word controls the KEYBOARD switch light and bit 6 controls the DISPLAY switch light as follows:

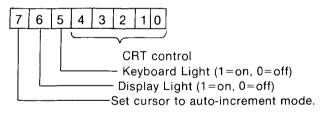

# CRT/Keyboard Control Word

Note: The CRT Write Ready must be true before the EX COM1 can be issued.

\* For I/O transfers in the 6600, the A register is used if another register is not specified. See Part 5, category 2, for further information.

# TABLE 2-1 KEYBOARD CODING (ASCII)\*

~

.

. .....

| a - 141 | 0-060                                                                                                                                                                                                                                                                                 | :-072                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b - 142 | 1-061                                                                                                                                                                                                                                                                                 | ;-073                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| c - 143 | 2-062                                                                                                                                                                                                                                                                                 | <-074                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| d - 144 | 3-063                                                                                                                                                                                                                                                                                 | =-075                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| e - 145 | 4-064                                                                                                                                                                                                                                                                                 | >-076                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| f - 146 | 5-065                                                                                                                                                                                                                                                                                 | ?-077                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| g - 147 | 6-066                                                                                                                                                                                                                                                                                 | [-133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| n - 150 | 7-067                                                                                                                                                                                                                                                                                 | <b>~</b> -176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| i - 151 | 8-070                                                                                                                                                                                                                                                                                 | ]-135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| j - 152 | 9-071                                                                                                                                                                                                                                                                                 | <b>^</b> -136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| k - 153 | Space-040                                                                                                                                                                                                                                                                             | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 - 154 | !-041                                                                                                                                                                                                                                                                                 | @ - 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| m - 155 | ·' <b>-</b> 042                                                                                                                                                                                                                                                                       | { - 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| n - 156 | #-043                                                                                                                                                                                                                                                                                 | × - 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| o - 157 | \$-044                                                                                                                                                                                                                                                                                | <b>'</b> - 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| p - 160 | <i>%-</i> 045                                                                                                                                                                                                                                                                         | ! <b>- 17</b> 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| q - 161 | &-046                                                                                                                                                                                                                                                                                 | } - 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| r - 162 | '-047                                                                                                                                                                                                                                                                                 | Enter - 015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| s - 163 | (-050                                                                                                                                                                                                                                                                                 | Cancel - 030                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| t - 164 | )-051                                                                                                                                                                                                                                                                                 | Backspace - 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| u - 165 | *-052                                                                                                                                                                                                                                                                                 | Del - 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| v - 166 | +-053                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| w - 167 | ,-054                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| x - 170 | -055                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| y - 171 | 056                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| z - 172 | /-057                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | $b - 142 \\ c - 143 \\ d - 144 \\ e - 145 \\ f - 146 \\ g - 147 \\ h - 150 \\ i - 151 \\ j - 152 \\ k - 153 \\ I - 154 \\ m - 155 \\ n - 156 \\ o - 157 \\ p - 160 \\ q - 161 \\ r - 162 \\ s - 163 \\ t - 164 \\ u - 165 \\ v - 166 \\ w - 167 \\ x - 170 \\ y - 171 \\ \end{cases}$ | $\begin{array}{cccccccc} b & - \ 142 & 1 & -061 \\ c & - \ 143 & 2 & -062 \\ d & - \ 144 & 3 & -063 \\ e & - \ 145 & 4 & -064 \\ f & - \ 146 & 5 & -065 \\ g & - \ 147 & 6 & -066 \\ h & - \ 150 & 7 & -067 \\ i & - \ 151 & 8 & -070 \\ j & - \ 152 & 9 & -071 \\ k & - \ 153 & Space & -040 \\ I & - \ 154 & ! & -041 \\ m & - \ 155 & `` & -042 \\ n & - \ 155 & $'' & -042 \\ n & - \ 156 & $\# & -043 \\ o & - \ 157 & $& -044 \\ p & - \ 160 & $& & & & & & & \\ r & - \ 162 & $& & & & & & & \\ r & - \ 162 & $& & & & & & & \\ r & - \ 163 & $& & & & & & & & \\ r & - \ 164 & $& & & & & & & & \\ r & - \ 165 & $& & & & & & & & \\ v & - \ 166 & $& & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & \\ v & - \ 166 & $& & & & & & & & \\ v & - \ 166 & $& & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & \\ v & - \ 167 & $& & & & & & & & & & & & & \\ v & - \ 171 & $& & & & & & & & & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & & & & \\ v & - \ 166 & $& & & & & & & & & & & & & & & & & $ |

# SPECIAL NUMBER PAD OPTION

| (.)-016 |

|---------|

| (0)-020 |

| (1)-021 |

| (2)-022 |

| (3)-023 |

| (4)-024 |

| (5)-025 |

| (6)-026 |

| (7)-027 |

| (8)-030 |

| (9)-031 |

|         |

\*These codes are all represented in octal

~

# PART 3 DISPLAY

# **3.1 General Description**

The 6600 display provides extended character generation flexibility and fast character transfer rates. The display system includes: CRT Display of 12 lines of 80 characters, power line screen refresh rate, 960 cells of random access memory holding the screen image, a program loadable random access character generation memory capable of producing 128 individual 5 by 7 dot matrix characters, a group of registers utilized to position the cursor, and automatic cursor increment provisions. The maximum character transfer rate to the CRT is determined by processor input/output speed. The upper limit of the display transfer rate is approximately 50,000 characters per second.

# **3.2 Display Operation**

The CRT is addressed by the processor by loading the A register with octal 0341 and executing an EX ADR command. (Note that the keyboard also uses this address, see Part 2.) Following the address sequence, the CRT/ keyboard status word can be loaded into the A register by executing an INPUT instruction. The CRT status assignment is as follows: Bit 0 of the status word indicates that the CRT is ready to accept data or commands if it is set to a logical 1. (Note that this status bit will indicate a logical one if the cursor is positioned to an invalid screen position.) Bits 1, 2 and 3 are used for keyboard status.

# CRT/Keyboard Status Word

Control of the CRT is accomplished through the use of the following external commands:

a. EX COM1 (Command 1) transfers a control word contained in the A register to the CRT. The applicable bit assignments and their functions are as follows:

The following explanations assume that the CRT has been addressed.

- BIT 0: Each execution of EX COM1 with this bit set to 1 causes the roll-down operation to occur. All displayed characters (not the cursor) are moved down one line. The bottom line on the screen is lost and the top line is filled with the pattern in position 040 octal of the character generation memory. The Write Ready status bit goes false until the roll-down operation is complete; another EX COM1 must not be issued during this time.

- BIT 1: Each execution of EX COM1 with this bit set to 1 causes erasure from (including) the current cursor position to the end of the line. The character displayed in the erased positions is determined by the pattern in position 040 octal of the character generation memory. The Write Ready status bit goes false until this operation is complete; another EX COM1 must not be issued during this time.

- BIT 2: Each execution of EX COM1 with this bit set to 1 causes erasure from (including) the current cursor position to the end of the frame. The character displayed in the erased position is determined by the pattern in position 040 octal of the character generation memory. The Write Ready status bit goes false until this operation is complete; another EX COM1 must not be issued during this time.

- BIT 3: Each execution of EX COM1 with this bit set to 1 causes the roll-up operation to occur. All displayed characters (not the cursor) are moved up one line. The top line on the screen is lost and the bottom line is filled with the pattern in position 040 octal of the character generation memory. The Write Ready status bit goes false until the roll-up operation is complete; another EX COM1 must not be issued during this time.

- BIT 4: The cursor image may be turned on or off through the control word. The cursor position is the same in either case. The cursor image is automatically turned off whenever the processor is in the HALT state, and will be turned on again when RUN is depressed if the cursor was on prior to the HALT.

- BITS

- 5, 6: Keyboard & Display Light See Part 2.

- BIT 7: When this bit is set to 1, the automatic cursor increment feature is in effect. In auto cursor increment mode, the cursor moves one character to the right after each EX WRITE command. The vertical position of the cursor does not change. If the last character (horizontal position 79) is written, the cursor will increment off the screen and the CRT Write Ready status bit will stay true until the cursor is re-positioned back onto the screen.

b. EX COM2 (Command 2) positions the cursor to the horizontal character slot designated by the contents of the A register. Character positions 0-79 (decimal) or 0-0117 (octal) are valid.

c. EX COM3 (Command 3) positions the cursor to the line designated by the contents of the A register. Line numbers 0-11 (decimal) or 0-013 (octal) are valid.

d. EX COM4 (Command 4) places the character generator memory in the load mode and sets the load pointer to the contents of the A register. Character positions 0-127 (decimal) or 0-0177 (octal) are valid.

e. EX WRITE transfers the character in the A register to the screen image memory at the position indicated by the cursor position. The cursor need not be on for this transfer to occur. If the auto cursor increment feature is enabled the cursor position will be incremented after the transfer. When the character generation memory has been set to the load mode, the above transfer is inhibited (as is the automatic cursor increment) and EX WRITE transfers data from the A register to the character generation memory. Execution of an EX WRITE (to either the screen image memory or the character generation memory) causes the Write Ready status bit to go false for up to 17 microseconds. Unless a delay of at least this duration is guaranteed by the program, the Write Ready status bit should be checked before execution of an EX WRITE, EX COM1, EX COM2, EX COM3 or EX COM4 after a previous EX WRITE. Note that EX COM2 and EX COM3 do not affect the Write Ready status.

Five successive byte transfers are required to load a complete 5 by 7 character dot pattern. The loading format is illustrated by the following diagram which illustrates the letter "A" loaded into memory:

| 6 |                       | х                                           | x                                                            | х                                       |                                                                                                                         |

|---|-----------------------|---------------------------------------------|--------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 5 | х                     |                                             |                                                              |                                         | X                                                                                                                       |

| 4 | х                     |                                             |                                                              |                                         | X                                                                                                                       |

| 3 | х                     | х                                           | х                                                            | X                                       | х                                                                                                                       |

| 2 | Х                     |                                             |                                                              |                                         | х                                                                                                                       |

| 1 | х                     |                                             |                                                              |                                         | Х                                                                                                                       |

| 0 | х                     |                                             |                                                              |                                         | Х                                                                                                                       |

|   | 1                     | 2                                           | 3                                                            | 4                                       | 5                                                                                                                       |

|   |                       | Tra                                         | anst                                                         | fer                                     |                                                                                                                         |

|   |                       | Nι                                          | ımb                                                          | er                                      |                                                                                                                         |

|   | (                     | EΧ                                          | WR                                                           | ITE                                     | )                                                                                                                       |

|   | 5<br>4<br>3<br>2<br>1 | 5 X<br>4 X<br>3 X<br>2 X<br>1 X<br>0 X<br>1 | 5 x<br>4 x<br>3 x x<br>2 x<br>1 x<br>0 x<br>1 2<br>Tra<br>Nu | 5 x 4 x 4 x 4 x 4 x 4 x 4 x 4 x 4 x 4 x | 5       x          4       x          3       x       x       x         2       x          1       x          0       x |

For example, the procedure for loading the character location 0101 with an "A" as illustrated would consist of the following character transfers:

LA 0101 Set load pointer to COM4 EΧ Location 0101 LB 077 CALL DWRITE Load column 1 LB 0110 DWRITE CALL Load column 2 CALL DWRITE Load column 3 CALL DWRITE Load column 4 LB 077 CALL DWRITE Load column 5

The DWRITE subroutine below is used here instead of an EX WRITE instruction to guarantee the 17 microseconds delay required between executions of EX WRITE instructions:

|        | •   |        |

|--------|-----|--------|

|        | •   |        |

| DWRITE | LAB |        |

|        | EX  | WRITE  |

| DWRITW | IN  |        |

|        | SRC |        |

|        | JFC | DWRITW |

|        | RET |        |

After all five columns of a character have been loaded, the character load pointer is automatically incremented to the following character. In the case of the above example the load pointer will be incremented to location 0102. Note that it is only necessary to issue additional EX COM4, when nonsequential character locations are being loaded. The display logic card is removed from the load mode by the execution of an EX COM1 (with A=0 if no other function is desired).

As mentioned previously, the Write Ready status bit goes false during the roll-up, roll-down, erase-to-end-of-line and erase-to-end-of-frame operations. The maximum periods during which Write Ready will be false for each of these operations is tabulated below for 60 Hz and 50 Hz primary power frequency:

| OPERATION             | 50HZ      | 60HZ      |

|-----------------------|-----------|-----------|

| Roll up               | 21.1 msec | 17.8 msec |

| Roll down             | 21.1 msec | 17.8 msec |

| Erase to-end-of-line  | 21.1 msec | 17.8 msec |

| Erase-to-end-of-frame | 35 msec   | 31.7 msec |

# CASSETTE TAPES

# 4.1 General Description

The Datapoint 6600 contains two cassette tape recording devices for storage of programs and data. Since the hardware Restart (Appendix A, 1.3) uses the rear deck (number one), programs will typically be on it while data areas will be on the front deck (number two). However, once the machine is initially loaded, either deck may be used for both purposes.

Data on the tape is organized by record (of any length). Records are written and read at 350 eight-bit characters per second. See Table 4-1 for a list of physical specifications.

# 4.2 Operations

Data is recorded or read in bit serial fashion on one track. Each eight bit character is framed by three sync bits on either side of the character.

The first eight bit string framed by valid sync code groups (010) indicates the beginning of a record. The appearance of eleven ones in a row indicates the end of a record. Sync code groups after the first character in a record and before the end of the record are ignored.

Note that the sync codes are valid for tape motion in either direction so the tape may be read backwards, although in the reverse direction the data bits will appear reversed (bit 0 will be bit 7, 1 will be 6, etc.)

This is what a typical record looks like:

| 111                  | 111   | 010             | d d d | d d d            | d d | 010            | d d  | d d d |     |                     |     |

|----------------------|-------|-----------------|-------|------------------|-----|----------------|------|-------|-----|---------------------|-----|

| Inter<br>Reco<br>Gap |       | Sync<br>Code    |       | Charac<br>lecord | ter | Sync<br>Code   | 2n   | d Cha | ura | icte                | r   |

| 010                  | d d d | dddd            | d d   | 010              | 11  | 1111           | 11   | 111   |     | 11                  | 1   |

| Sync<br>Code         |       | Charac<br>ecord | cter  | Sync<br>Code     |     | End of<br>Mark | Reco | ord   | F   | ntei<br>Reci<br>Gap | ord |

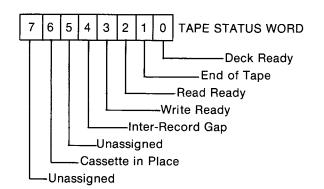

# 4.3 status

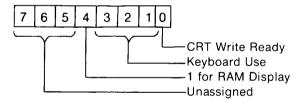

The cassette tape unit is addressed by the processor by loading the A register with 0360 octal and executing the EX ADR instruction. Following this sequence, the tape unit status can be loaded into the A register by executing an INPUT instruction. The bit assignments are as follows:

- DECK READY Deck Ready will be set whenever the tape unit is ready to accept another command. (Only the TSTOP command should be issued if this bit is false). When Deck Ready is true the tape will be stopped, a cassette in the selected deck, and the head engaged. This bit should be checked after selecting a deck.

- END OF TAPE End of Tape indicates that the cassette has run onto leader (in either direction).

- READ READY Read Ready indicates that the selected deck has read another character.

- WRITE READY Write Ready indicates that the selected deck is ready to write another character.

- INTER-RECORD Inter-Record Gap indicates selected GAP deck has come across an inter-record gap (invalid sync code).

| CASSETTE IN | Cassette in Place indicates that a cassette  |

|-------------|----------------------------------------------|

| PLACE       | is physically in place in the selected deck. |

# 4.4 Control (Table 4-2)

When the cassette tape unit is addressed the following instructions will control the action of the tape:

a. EX TSTOP causes any motion of either deck to be stopped and any read or write operations to be terminated. When everything has settled, the Ready status bit will come true and operations may be resumed.

- b. EX DECK 1 causes deck one (rear) to be the currently selected deck. Before commanding a deck selection, care should be taken that the currently selected deck has completed all operations.

- c. EX DECK 2 causes deck two (front) to be the currently selected deck. Note the precaution in (b).

- d. EX RBK causes the currently selected deck to be set in forward motion and, after 70 msec, for the read circuitry to be enabled. The Read Ready status bit will come true upon appearance of a valid character. When an invalid sync code is encountered the Inter-Record Gap status bit comes true and tape motion is automatically stopped. Note that this will happen only after at least one valid character has been found. Once the Read Ready status bit comes true, the character must be taken within 2.8 msec. or it will be overwritten with the next one. The tape read hardware double-buffers incoming characters to allow the 2.8 msec. character availability.

- e. EX BSP is similar to EX RBK except that tape motion is in the reverse direction so the data bits will be reversed.

- f. EX SF is similar to EX RBK except the tape is not stopped upon appearance of an Inter-Record Gap, and if allowed to continue will start to read the next record on the tape. In this case, the Read Ready status bit will come true again after the first character of the next

record is read. Only EX TSTOP will stop the motion initiated by EX SF.

- g. EX SB is similar to EX SF except that tape motion is in the reverse direction and the data bits are reversed.

- h. EX WBK causes the currently selected deck to be set in forward motion and all status bits except the Write Ready to go false. A character must then be presented within 2.8 msec. (the first character will be accepted at once due to the buffering in the tape hardware and then there will be a pause while the tape comes up to speed), at which time the Write Ready will go false until the writing circuitry is ready to accept another character. An end of record is signaled to the hardware by withholding a character for a period of time longer than the 2.8 msec. specified above. When this is done, the Write Ready will go false, an Inter-Record Gap will be written, the tape motion will cease and the Deck Ready status bit will come true again.

- i. EX REWIND causes the tape to be rewound to the beginning on the selected deck. Worst case rewind time is approximately 40 seconds.

- j. PUNCH TABS on the cassette cartridge are used for "write protect" and "automatic restart." The punch tab on the left (as you face the processor) inhibits the ability to write on tape, when punched. When the tab on the right is punched, it causes an automatic restart whenever a halt or power-up occurs.

# TABLE 4-1

### TAPE UNIT PHYSICAL SPECIFICATIONS

Density Speed Recording Rate Capacity Start/Stop time (Inter-Record Gap) Start/Stop Distance (Inter-Record Gap) Rewind Speed Rewind Time (max 300 ft.) Character Transfer Time

47 characters/inch 7.5 ips 350 c.p.s. 130,000 characters (typical) 280 msec. 2 inches 90 ips 40 sec. 2.8 msec.

| <b>TABLE 4</b> |

|----------------|

|----------------|

| COMMAND<br>NUMBER |          | OCTAL<br>CODE | COMMAND                | DESCRIPTION                                             | DEVICE<br>ADDRESS |

|-------------------|----------|---------------|------------------------|---------------------------------------------------------|-------------------|

| 15                | DECK1    | 155           | Select Deck 1          | Connects deck 1 to I/O bus                              | 0360              |

| 16                | DECK2    | 157           | Select Deck 2          | Connects deck 2 to I/O bus                              |                   |

| 17                | RBK      | 161           | Read Block             | Enables read circuitry and sets tape in forward motion  |                   |

| 18                | WBK      | 163           | Write Block            | Enables write circuitry and sets tape in forward motion | 0360              |

| 19                | <u> </u> | 165           | (Unassigned)           |                                                         |                   |

| 20                | BSP      | 167           | Backspace<br>One Block | Backs up the selected tape<br>one record                |                   |

| 21                | SF       | 171           | Slew Forward           | Sets selected tape deck in forward motion               |                   |

| 22                | SB       | 173           | Slew Backward          | Sets selected tape deck in<br>backward motion           |                   |

| 23                | REWIND   | 175           | Rewind                 | Rewinds the selected deck to beginning of tape          |                   |

| 24                | TSTOP    | 177           | Stop Tape              | Halts motion of the selected tape deck                  | 0360              |

|                   |          | 1             | 1                      |                                                         | 1                 |

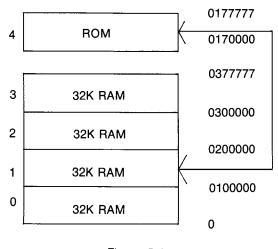

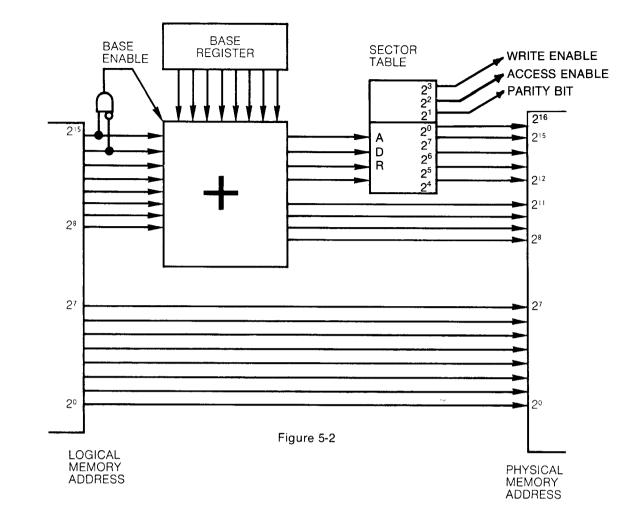

The processor in the 6600 is comprised of two sets of eight 8-bit program accessible registers, two sets of 4 control flags, 128K bytes of memory (120K bytes of user program memory), a 16-bit program counter, an 8-bit instruction register, an 8-bit base register, a 16-level push down Stack, a special 4-bit instruction modification register and a 16-word memory sector table.

#### **5.1 Processor Registers**

The eight programmable registers are named A, B, C, D, E, H, L, and X. The flag flip-flops are named C (carry), Z (zero), S (sign), and P (parity). There are two sets of these registers and flags and access to them depends upon the mode the processor is in. Upon Restart or whenever the Alpha mode instruction is executed, all Alpha mode registers and flags are accessible by the program. Whenever a Beta mode instruction is executed, the Beta mode registers and flags are accessible. No other registers or functions within the machine are affected by the processor mode.

Registers A-L are general purpose registers which may be interchanged with each other as to their functions. When an arithmetic, logical or I/O instruction is performed and a register is not specified, the "A" register is over stored with the result.

When using registers for addressing, they may be paired together to form a 16-bit address; XA, BC, DE and HL. If a pair of registers is not specified, the HL registers will be assumed.

The X register is a working page register and is not normally used for the same functions as registers A-L, except to form the upper 8 bits of a 16-bit address word.

P - The P register is the "location counter" for the program and contains the address of the next instruction to be executed. This register is stored in the pushdown Stack upon the execution of a "CALL" instruction and is loaded with the effective address upon execution of a "JUMP", "CALL" or "RETURN" instruction. The P register is 16 bits wide.

I - The I register is the register which holds the "operation code" of the instruction currently being executed. The contents of I are gated through a decoding network to determine what operation, internal or external, is to be performed. I is 8 bits wide. This register is for internal hardware sequencing and is transparent to the user.

#### **5.2 Comparison With Datapoint 5500 and 2200** Systems

#### 5.2.1 Input/Output

Besides simply executing I/O instructions faster than the 5500 and 2200 systems, the 6600 system I/O has parity check-

ing while maintaining control over compatibility with 5500 and 2200/1100 devices.

# **5.2.2 Input Parity Checking**