TECHNICAL MANUAL

FOR THE

MOVING HEAD DISK CONTROLLER 4046

AND

DISK CARTRIDGE ADAPTERS 4047 & 4049

Users of this manual are cautioned that the specifications contained herein are subject to change by DGC at any time without prior notice. Users should refer to the latest revision before using this manual in connection with the operation of DGC equipment. DGC is not responsible for errors which may appear in the drawings and specifications in this manual.

Any comments concerning this publication should be forwarded to:

Publications Dept.

Data General Corp.

Route 9

Southboro, Mass. 01772

# TABLE OF CONTENTS

## SECTION I GENERAL DESCRIPTION

| Paragraph |                                                                                                                                                                                                                                                                                              | Page                                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1-1       | INTRODUCTION                                                                                                                                                                                                                                                                                 |                                      |

| 1-2       | GENERAL FUNCTIONAL DESCRIPTION 1-2.1 Disk Controller Model 4046 1-2.2 Adapter Model 4047 1-2.3 Instructions 1-2.3.1 Seek Instructions 1-2.3.2 Read/Write Instructions                                                                                                                        | 1-5<br>1-10<br>1-11<br>1-11          |

| 1-3       | PHYSICAL DESCRIPTION                                                                                                                                                                                                                                                                         | 1-13                                 |

| 1-4       | PERTINENT DOCUMENTS                                                                                                                                                                                                                                                                          | 1-13                                 |

| 1-5       | ABBREVIATIONS                                                                                                                                                                                                                                                                                | 1-13                                 |

|           | SECTION II<br>INSTALLATION                                                                                                                                                                                                                                                                   |                                      |

| 2-1       | GENERAL                                                                                                                                                                                                                                                                                      | 2-1                                  |

| 2-2       | INSTALLATION AND CHECKOUT PROCEDURES. 2-2.1 Installation Procedures. 2-2.2 Checkout Procedures.                                                                                                                                                                                              | 2-1                                  |

|           | SECTION III<br>OPERATION                                                                                                                                                                                                                                                                     |                                      |

| 3-1       | GENERAL                                                                                                                                                                                                                                                                                      | 3-1                                  |

|           | SECTION IV<br>THEORY OF OPERATION                                                                                                                                                                                                                                                            |                                      |

| 4-1       | INTRODUCTION                                                                                                                                                                                                                                                                                 |                                      |

| 4-2       | CONTROLLER TYPE 4046 FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                  | 4-1                                  |

| 4-3       | 4047 & 4049 ADAPTER UNIT FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                              | 4-13                                 |

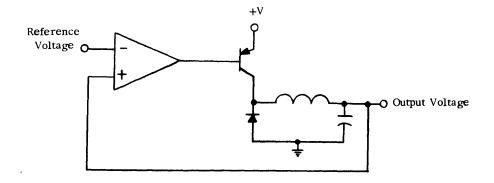

| 4-4       | 4047 DISK POWER SUPPLY FUNCTIONAL DESCRIPTION         4-4.1 + 30 VNR @ 15 Amps Generation         4-4.2 + 5 Volt Regulator         4-4.3 + 15 Volt Regulator         4-4.4 + 30 Volt @ 4 Amps Generation         4-4.5 - 15 Volt Regulator         4-4.6 Power Low Monitor Signal Generation | 4-22<br>4-22<br>4-23<br>4-23<br>4-23 |

# TABLE OF CONTENTS (Continued)

## SECTION V MAINTENANCE

| Paragraph |                                  | Page |

|-----------|----------------------------------|------|

| 5-1       | GENERAL                          | 5-1  |

| 5-2       | SPECIAL TOOLS AND TEST EQUIPMENT | 5-1  |

| 5-3       | DIAGNOSTIC PROGRAMS              | 5-1  |

| 5-4       | TROUBLE SHOOTING PHILOSOPHY      | 5-3  |

| 5-5       | ADAPTER POWER SUPPLY CHECKOUT    | 5-3  |

| 5-6       | IC IDENTIFICATION                | 5-4  |

### LIST OF ILLUSTRATIONS

| Figure | <u>Title</u>                                                                                          | Page    |

|--------|-------------------------------------------------------------------------------------------------------|---------|

| 1-1    | Basic Disk Cartridge System for Adapter 4047 or Adapter 4049                                          | 1 -2    |

| 1 -2   | Component Configurations for Data General Disk Cartridge Systems                                      | 1-3     |

| 1-3    | Typical Dual Processor Disk Cartridge System                                                          | 1-4     |

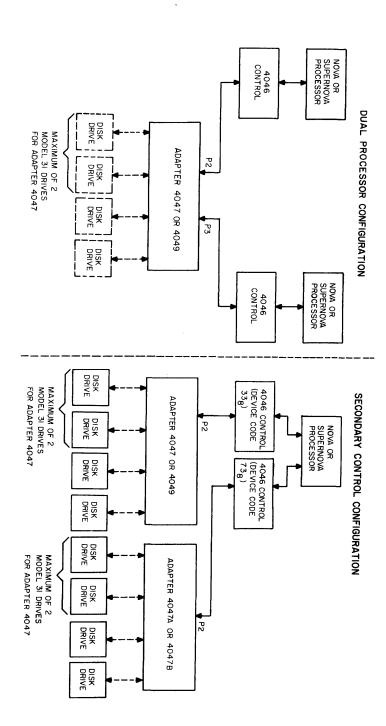

| 1-4    | Components of a Dual Processor, or a Secondary Control Configuration                                  | 1-6     |

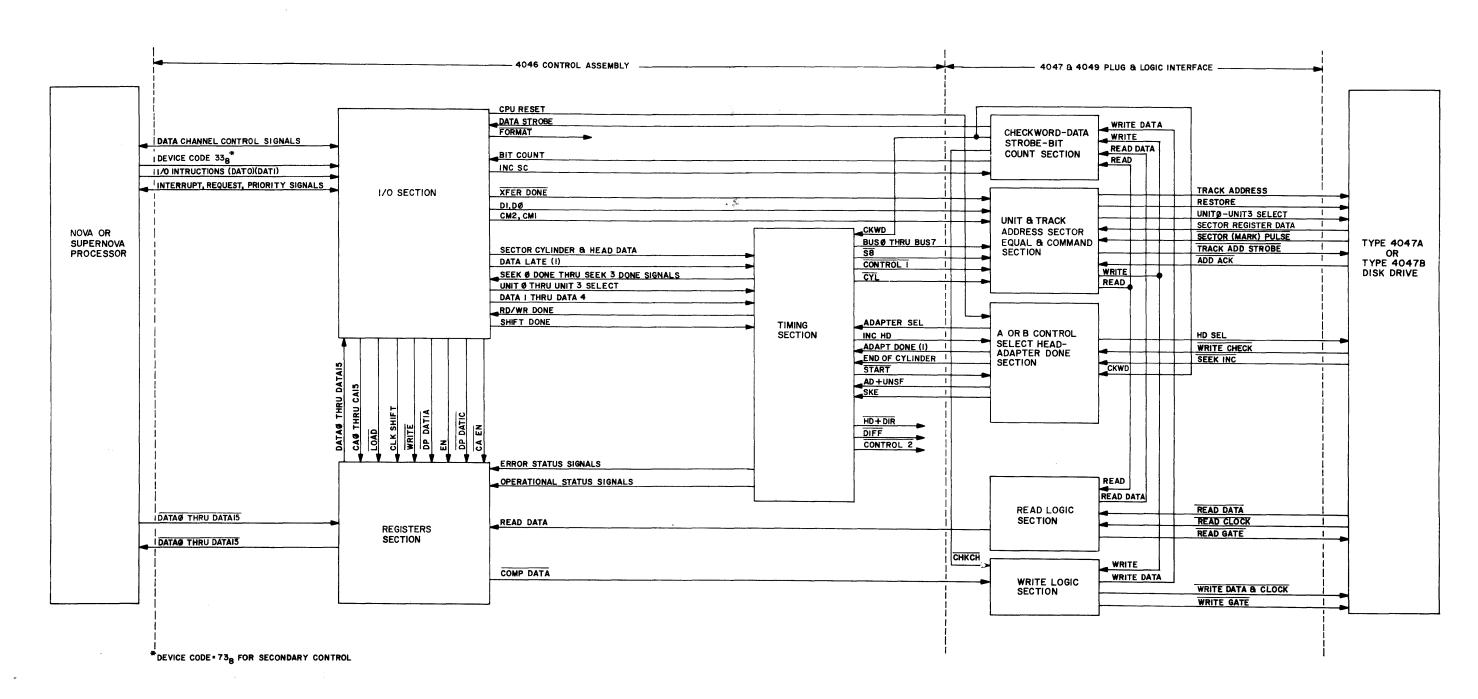

| 1 -5   | General Functional System Block Diagram for the 4046 Disk Controller and Adapter 4047 or Adapter 4049 | 1-7/1-8 |

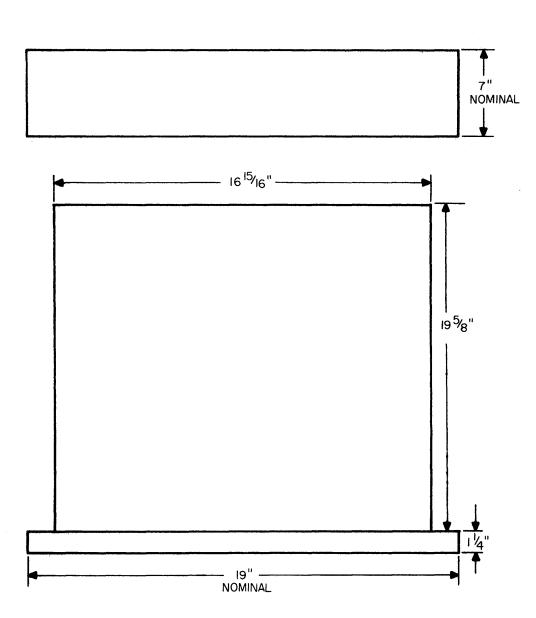

| 1-6    | Outline of Adapters 4047 and 4049.                                                                    | 1-14    |

| 2-1    | Relative Positions of Outer and Inner Shipping Cartons                                                | 2-2     |

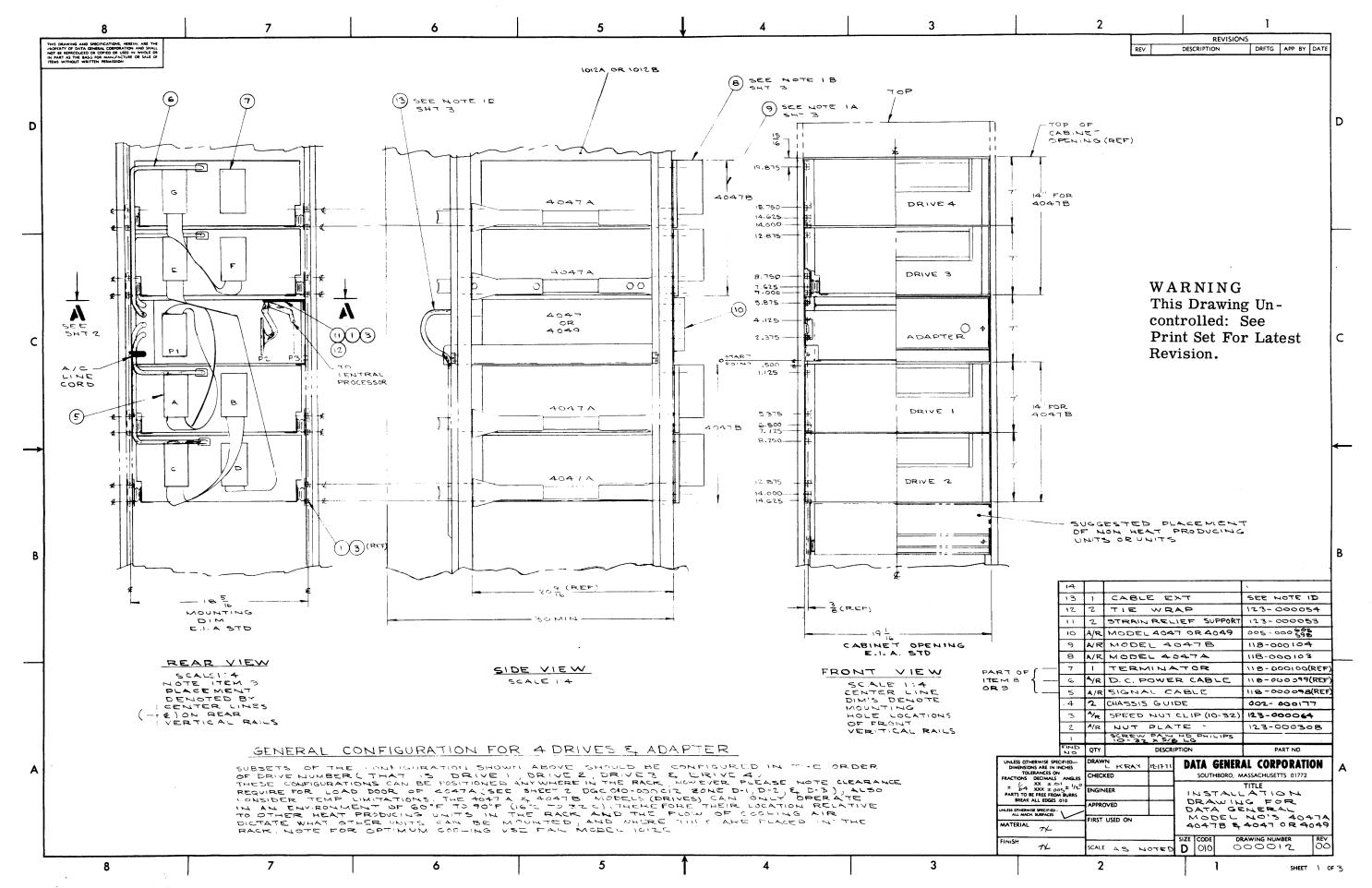

| 2-2    | Installation Drawing for Data General Model No's 4047A, 4047B & 4047 or 4049 (Sheet 1 of 3)           | 2-3/2-4 |

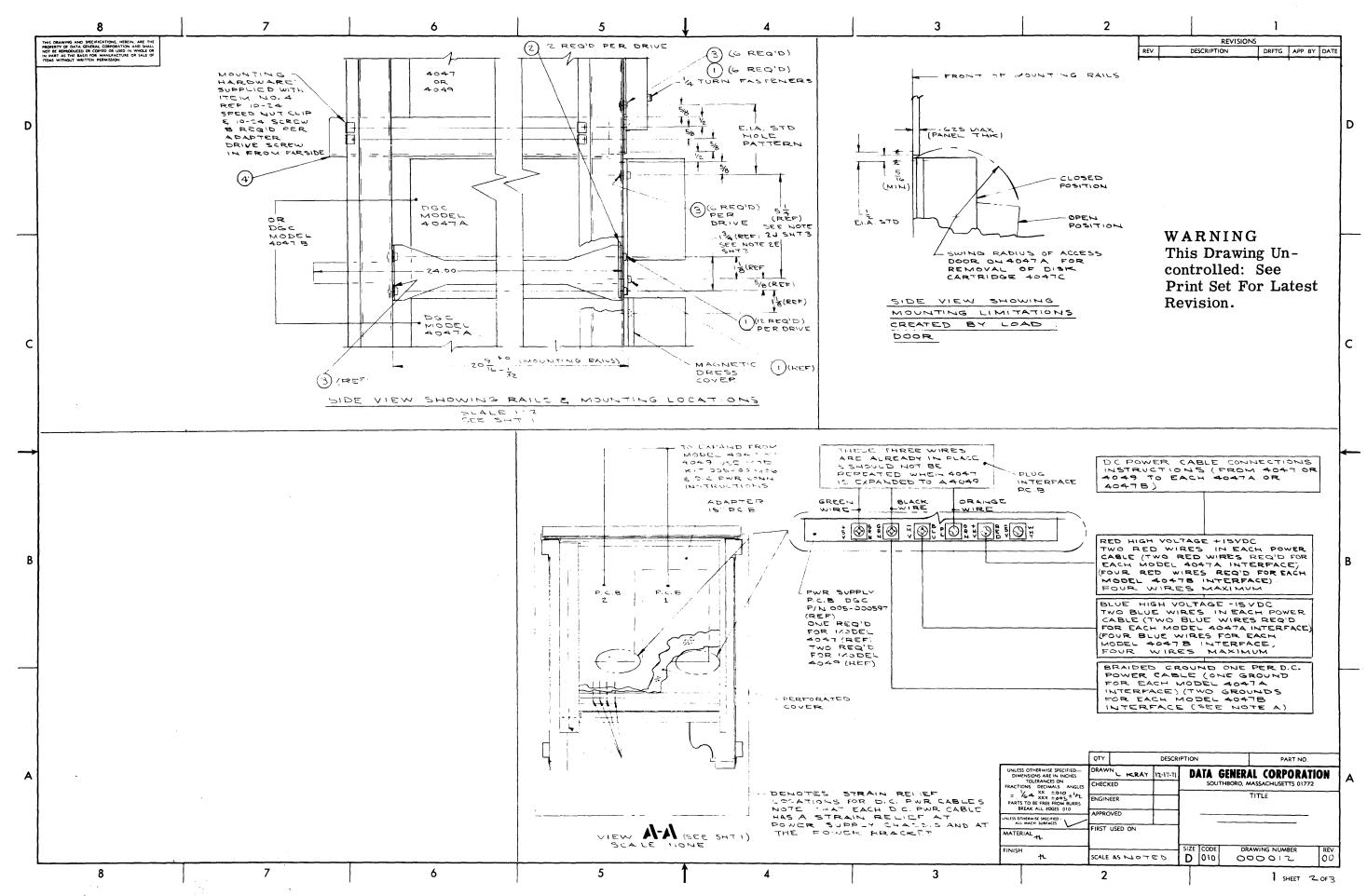

| 2-2    | Installation Drawing for Data General Model No's 4047A, 4047B & 4047 or 4049 (Sheet 2 of 3)           | 2-5/2-6 |

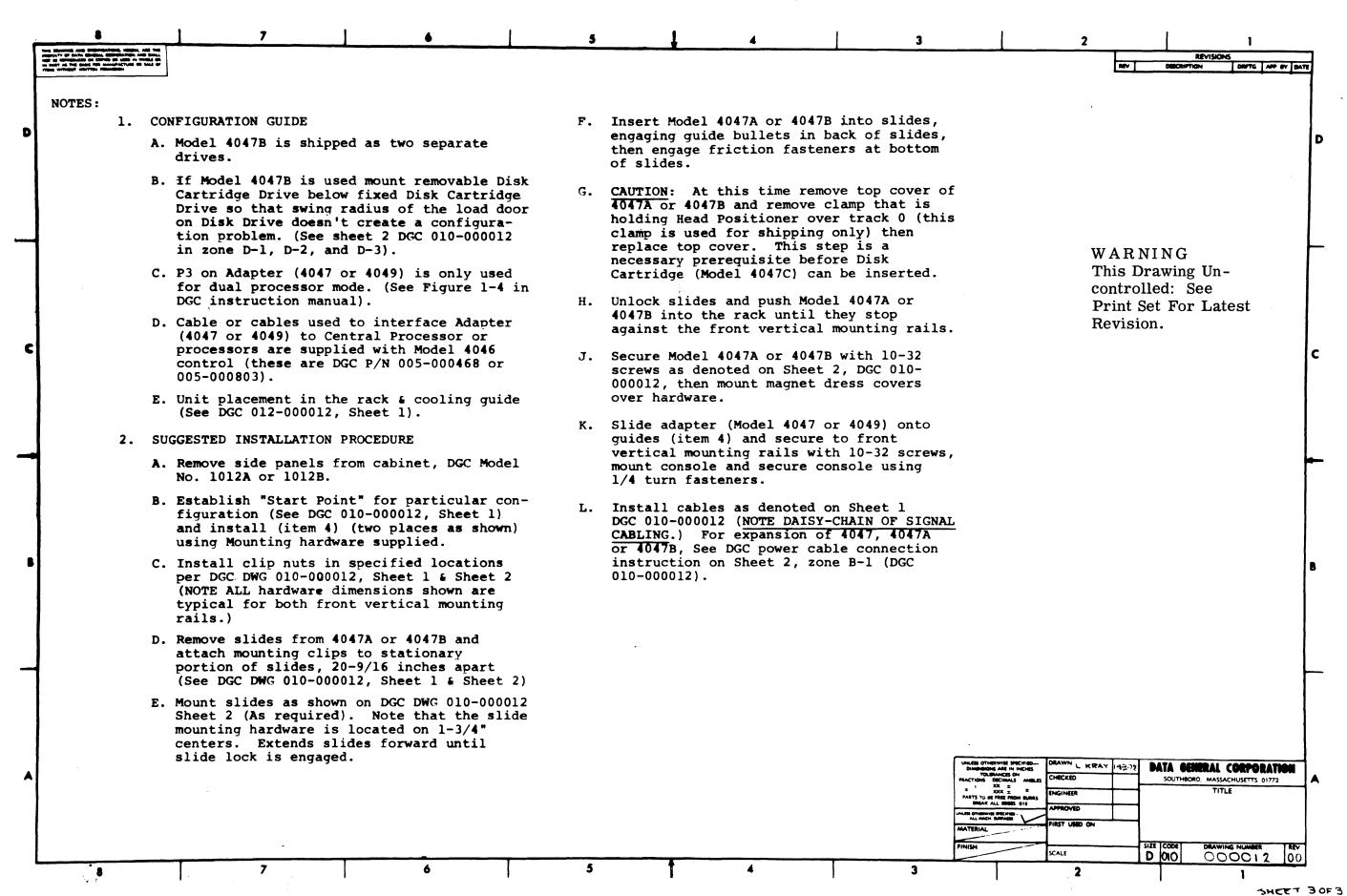

| 2-2    | Installation Drawing for Data General Model No's 4047A, 4047B & 4047 or 4049 (Sheet 3 of 3)           | 2-7/2-8 |

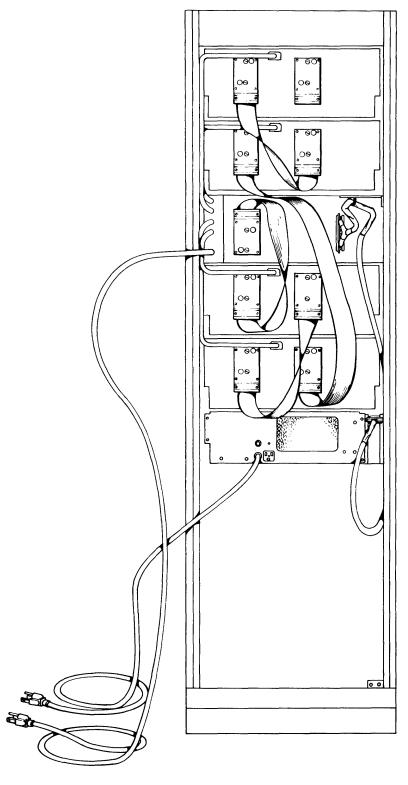

| 2-3    | Inter-Unit Cabling for Controller 4046 and Adapter 4047 or 4049                                       | 2-10    |

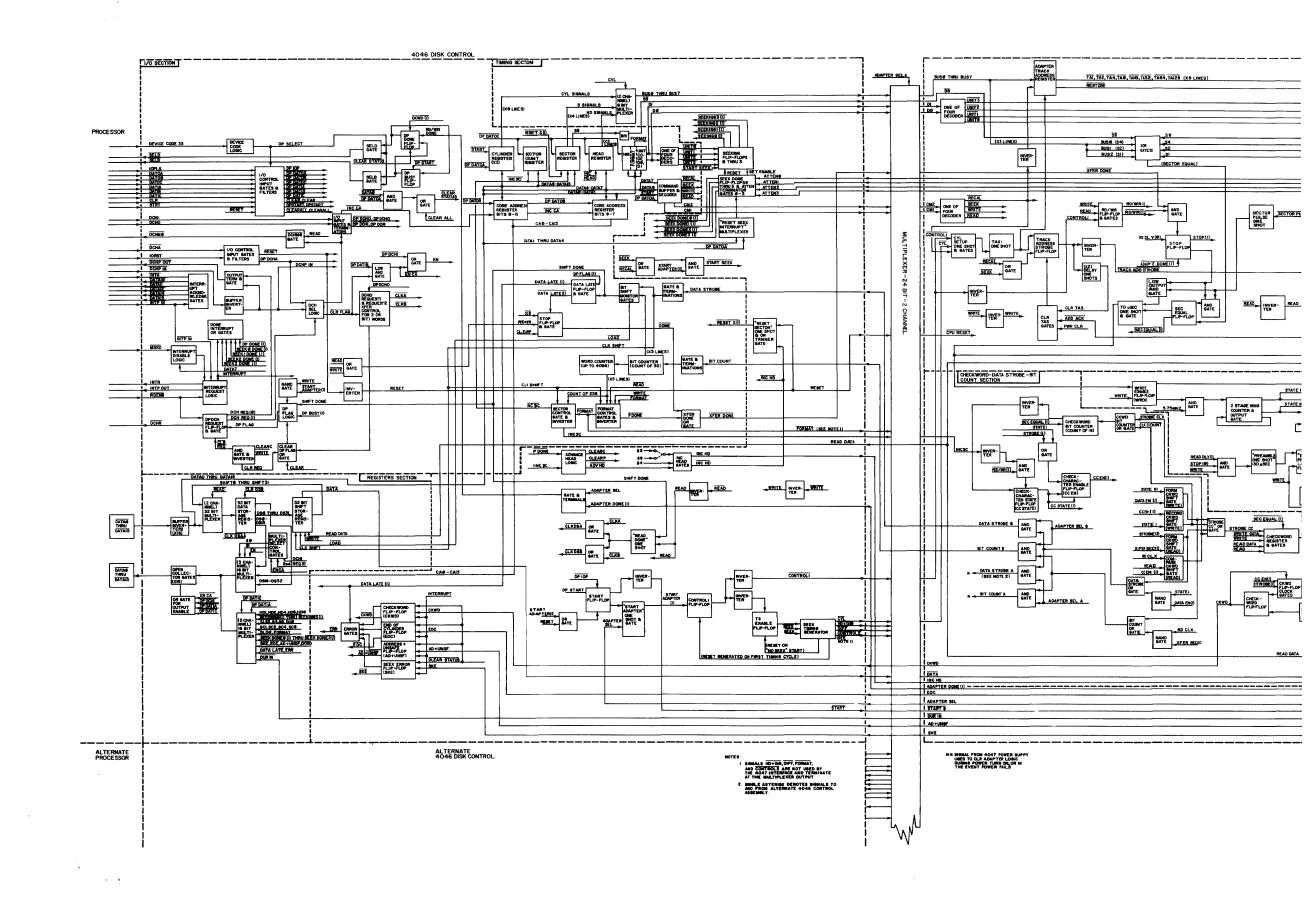

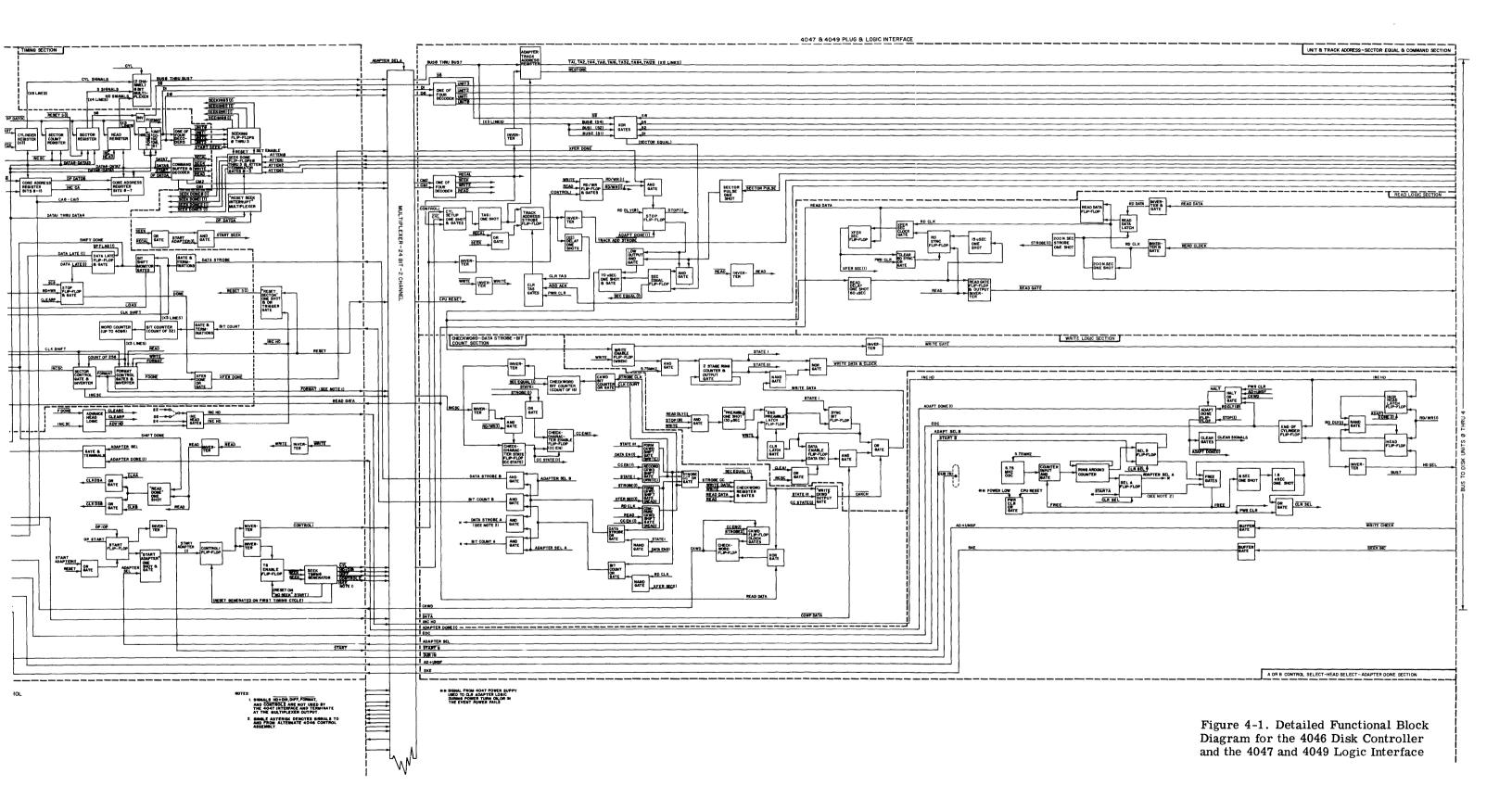

| 4-1    | Detailed Functional Block Diagram for the 4046 Disk Controller and the 4047 and 4049 Logic Interface  | 4-3/4-4 |

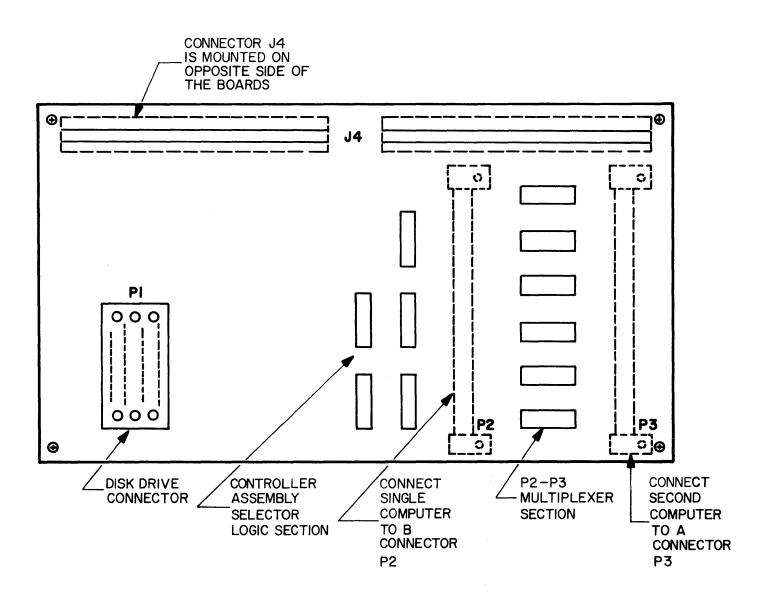

| 4-2    | 4047 Adapter Plug Interface and Back Panel                                                            | 4-14    |

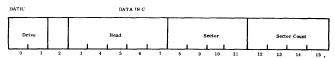

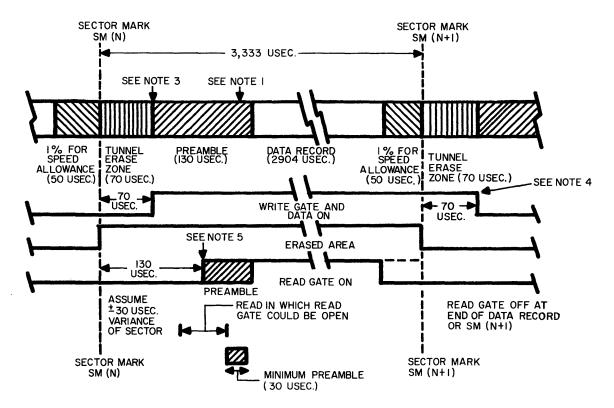

| 4-3    | Data Format                                                                                           | 4-16    |

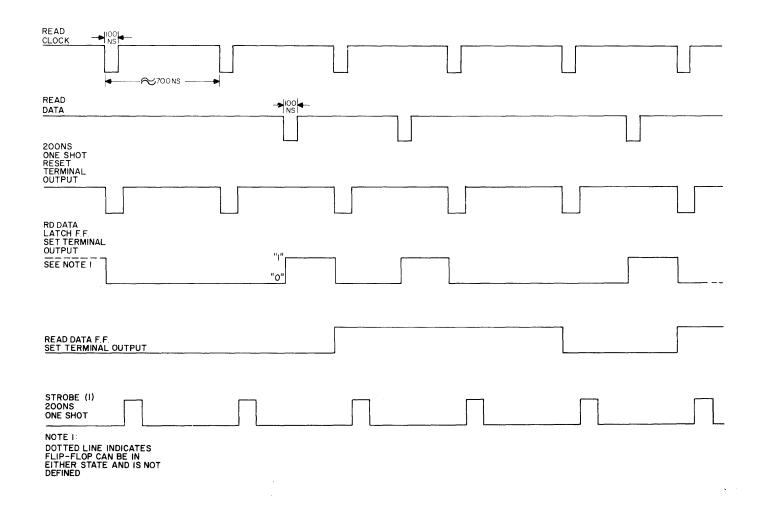

| 4-4    | Read Data Timing Example for 01101 Input Data Series                                                  | 4-19    |

| 4-5    | +5 Volt Regulator Functional Diagram                                                                  | 4-22    |

# LIST OF TABLES

| Tabl | <u>e</u>                                  | Page |

|------|-------------------------------------------|------|

| 1-1  | Specification Data-Adapters 4047 and 4049 | 1-13 |

| 4-1  | 3 Channel Multiplexer Control Signals     | 4-8  |

| 4-2  | Power Supply Outputs                      | 4-21 |

| 5-1  | IC Identification List                    | 5-4  |

#### SECTION I

### GENERAL DESCRIPTION

### 1-1 INTRODUCTION

Data General Moving Head Disk Controller No. 4046 is designed to operate a wide variety of Moving Head Disk Drives, and is a basic component for each Moving Head Disk system. The Controller is functionally positioned between any Nova or Supernova Processor and the appropriate Moving Head Disk Adapter unit. Data General provides two types of Adapters for Disk Cartridge systems, each engineered specifically to interface with one of the two Disk Cartridge Drive units offered by Data General. From a general design point of view, Adapters 4047 and 4049 are similar in that they both operate the same type of Disk Drive equipment. (The basic difference is that the 4047 Adapter has a smaller power supply facility than the 4049 Adapter.) Adapters 4047 and 4049 are designed to interface with both the Data General Model 31 Disk Drive and the Data General Model 33 Disk Drive, and whereas the Adapter Supplies  $\pm$  15 Volt dc power to the Disk Drive; the 4047 Adapter is designed to handle two Model 31 Drives or one Model 33 Drive. The 4049 Adapter on the other hand, is designed to handle four Model 31 Drives or two Model 33 Drives. From herein all technical references to Adapter 4047 will be applicable to Adapter 4049 also, unless the 4049 Adapter is called out specifically.

The appropriate technical and maintenance manuals for either Model Disk Drive ordered from Data General are packed and shipped with the selected equipment. Thus, the information provided in this manual is intended to supplement these publications and will describe only the required Controller and Adapter equipment. Additional information concerning the operation of the Data General standard Processor Data Channels may be referenced in the "How to Use the Nova Computers" reference manual, published by Data General under separate cover.

This manual is divided into five sections: General Description, Installation, Operation, Theory of Operation, and Maintenance. It is supported by a set of engineering drawings listed below, and an Illustrated Parts List document number 005-000804-00.

It is assumed that the reader has a thorough understanding of TTL logic and the fundamentals of computers.

| Disk Pack Control I/O       | 001-000122(Sheet 1) |

|-----------------------------|---------------------|

| Disk Pack Control Timing    | 001-000122(Sheet 2) |

| Disk Pack Control Registers | 001-000122(Sheet 3) |

| 4047 Plug Interface         | 001-000142          |

| 4047 Logic Interface        | 001-000143          |

4047 Disk Power Supply External Cable Adapter (4047 or 4049) to Computer 001-000186

005-000468

### 1-1.1 Disk Cartridge System Components

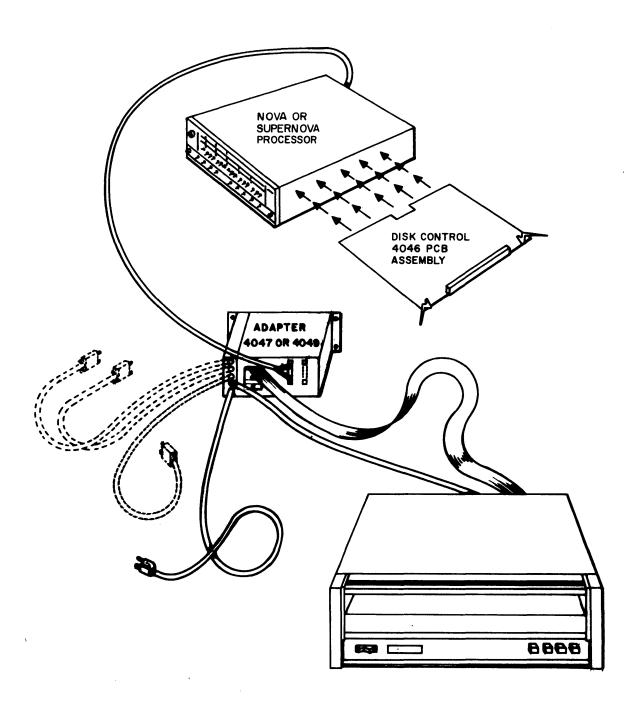

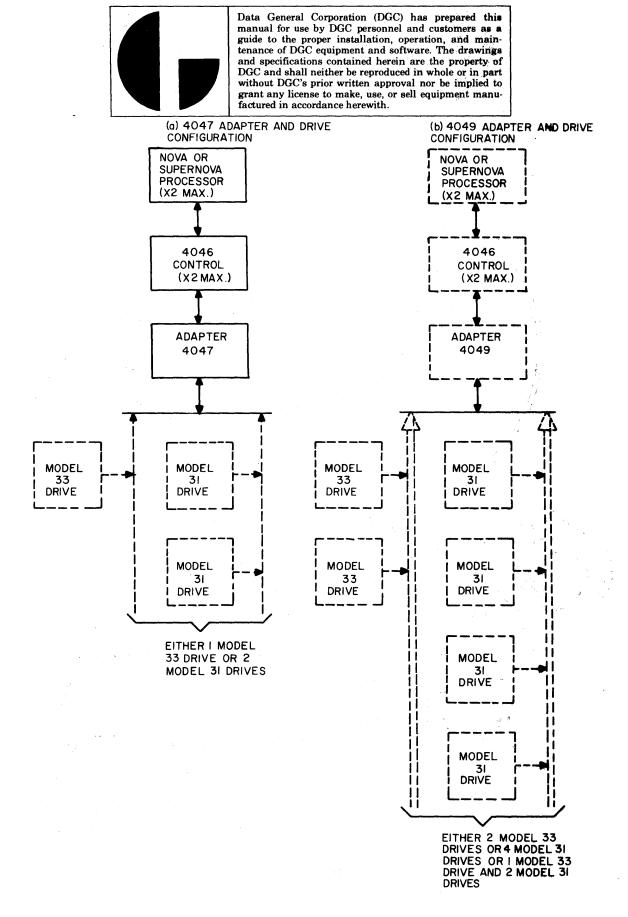

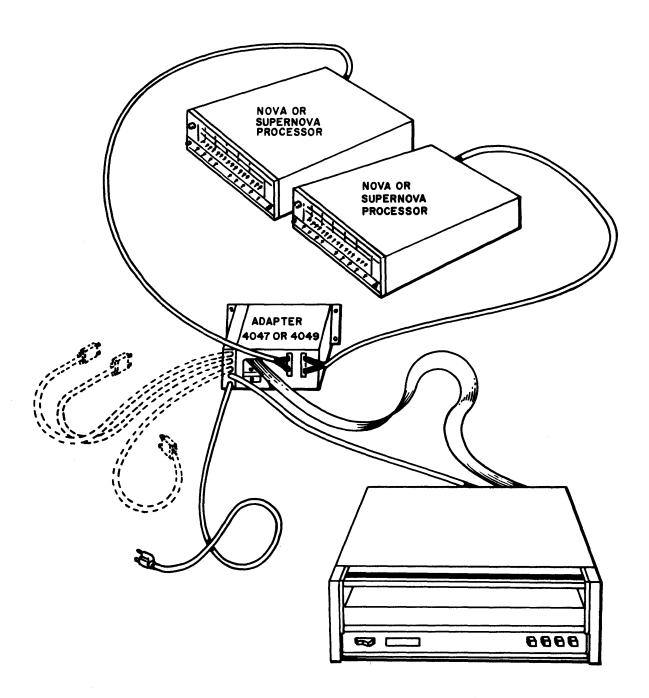

The basic Disk Cartridge system components are shown on Figure 1-1, and consists of the Disk Controller 4046 PCB assembly, one Disk Cartridge Adapter, and a Disk Cartridge Drive. This illustration, like the previous figure, shows only one drive in the interest of simplifying the illustration, but more than one drive can be installed. As mentioned previously two types of Disk Cartridge drives are available, either a model 31 or a model 33, and if Adapter 4047 is installed the configuration will support one model 33 drive or two model 31 drives. Mixing is not possible on the 4047 Adapter without exceeding the capabilities of the Adapter power supply. If the Adapter 4049 is installed the Adapter will provide sufficient power for two model 33 drives or four model 31 drives. Mixing is allowed on this Adapter as long as the total number of drives does not exceed the equivalence of four model 31 drives. In other words, one model 33 drive is equal (loadwise) to two model 31 drives. Therefore a configuration of one model 33 drive and two model 31 drives can be installed. An installation of three model 31 drives and one model 33 drive. or two model 33 drives and one model 31 drive would exceed the capabilities of the Adapter (4049) power supply. The difference between the two drives is storage capacity. (1.247 million 16-Bit words for the model 31 drive, and 2.494 million 16-Bit words for the model 33 drive.) The connector facilities for Adapter 4047 and Adapter 4049 are similar, with the sole exception that the 4047 Adapter has a maximum of two DC cables (left rear of the chassis) whereas the 4049 Adapter has a maximum of four DC cables (also left rear of the chassis). Each Adapter unit contains its own power supply which operates from standard 115 Volt, 50 or 60 Hertz lines. A line cord is provided in the lower left section of the connector panel mounted in the rear of the Adapter chassis for connecting the Adapter to standard 115 Volt single phase power. Either Adapter provides (in addition to DC cables) a signal bus line, which for multiple drive configurations is daisychained between drives. This signal bus must be terminated at the last drive in the chain.

Figure 1-2 is a block diagram of the various possible configurations comprising Disk Cartridge systems. This figure is included here for reference purposes, and diagrammatically summarizes the configuration descriptions of this paragraph. The 4046 Controller and 4047 Adapter combination are shown in solid lines as being one typical system. The remain blocks are shown in dotted lines as representing other system configurations that can be installed with the Nova or Supernova Processor and 4046 Controller PCB assembly.

Figure 1-3 shows a typical dual Processor Disk Cartridge system. In this particular configuration the Adapter (either 4047 or 4049) is shared between two Processors. Each

Figure 1-1. Basic Disk Cartridge System for Adapter 4047 or Adapter 4049

Figure 1-2. Component Configurations for Data General Disk Cartridge Systems

Figure 1-3. Typical Dual Processor Disk Cartridge System

Processor contains a 4046 Controller PCB assembly, which is selected alternately for control by the Adapter logic. (However, each Controller can communicate with one Adapter only.) The number of Disk Cartridge Drives included in the dual Processor system are exactly as described previously (and as shown on Figure 1-2).

Figure 1-4 is a block diagram of a dual Processor or Secondary 4046 Controller configuration that may be used to form a Disk Cartridge system. It suffices to say that the ground rules governing the number and type of Disk Cartridge Drives connected to the appropriate Cartridge Adapter are exactly the same as described previously. As mentioned above either type Cartridge Adapter (4047 or 4049) contains control logic which selectively alternates transfer operations between Processors (through the facilities of each 4046 Controller). It is also possible to have two 4046 Controllers in one Processor (each with a unique Device Select Code). In this configuration, like the dual Processor configuration, each control can communicate with One Adapter only, with all of the previously described configuration rules still applicable. A configuration with one computer housing two Controllers, with each Controller connected to a separate Adapter will support up to 8 model 31 Disk Drive units.

#### 1-2 GENERAL FUNCTIONAL DESCRIPTION

Data General's Disk Cartridge systems are composed of devices which provide direct-access storage of data on a removable Disk Cartridge. Functional descriptions concerning the operation of the Disk Cartridge Drive supplied by Data General can be referenced from the installation and operation manual shipped with each drive. The functional descriptions of the remaining system components are presented in this paragraph starting with the 4046 Controller, which is followed by a brief description of the function of the Adapter unit. As mentioned previously all references to the 4047 Adapter are also applicable to the 4049 Adapter.

### 1-2.1 Disk Controller Model 4046

The general functional relationships between the 4046 Controller and the other components of a Disk Cartridge system are shown on Figure 1-5. The 4046 Controller assembly as shown, consists of three major logic sections; the I/O section, the Registers section, and the Timing section. The I/O section received I/O instructions from the Nova or Supernova Processor in the form of DATO (data out) and DATI (data in) instructions. The data out instructions load various control registers within the assembly with command and control data, whereas the data in instructions read the contents of the various control registers in the assembly back into the Processor. The I/O section also receives the Device select code from the Processor via the DS lines. The 4046 Controller assembly recognizes Device Code 33. If two 4046 Controllers are installed in the same Processor, the second Controller is conditioned to recognize Device Code 73. The I/O section also receives and transmits the various Data Channel control signals used to control the exchange of sector data. The remaining I/O bus interrupt, request, and priority signals exchange between the Processor and the Controller are also handled by the I/O section. The operation and function of the I/O bus and Data Channel signals are described in Data General publication "How to use the Nova Computers," (available under separate cover) and consequently will not be repeated in this discussion. Specific instruction data pertinent to Disk Cartridge systems are described at the end of this main paragraph.

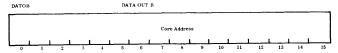

The I/O bus data lines DATA0 through DATA15 are terminated in the Registers section for both receiving and transmitting data transfer Operations. Data being received by the 4046 Controller Assembly is inverted by a group of buffer inverters and sent to the I/O section as DATA0 through DATA 15. These signals load the various operation control registers in the I/O section (e.g., Unit, Sector, Head, Sector Count, and Cylinder registers) with control data governing the upcoming operation. The I/O section contains the core Address (CA) register or address counter, which can be examined under program control. The outputs from the CA register, CA0 through CA15 are routed through the Registers section, which provides the logical manipulation for placing the CA contents onto the I/O bus lines. The I/O section also generates an accompanying CA EN (CA Enable) signal which enables this logic to selectively output the data present on the CA output lines (CA0 through CA15) to the I/O bus lines. The I/O section also produces a basic EN signal for output transmissions of either CA data or stored data read from the Disk. Operational and Error status signals from the Timing section are also routed through the Registers section for transmission to the Processor via the I/O bus lines. Operational status data, e.g., contents of Unit, Head, Sector, and Sector Count registers is read back to the Processor under program control by the DATIC instruction. Error status data is read back to the Processor under program control by the DATIA instruction. The selective signals either DP DATIC or DP DATIA are derived from the standard DATIA and DATIC bus signals in the I/O section and perform the selected output enabling function in the Registers section.

In addition to multiplexing address, operational status, and error status signal into the I/O bus data lines, the Registers section assembles serial data read from the Disk for transfer back to the Processor, and disassembles parallel input data from the Processor to be written serially onto the Disk. The 4046 Controller transfers two (16 bit) words at a time, hence the assembly or disassembly is performed on a double word (32 bit) basis for any one data transfer operation. Serial data to be written onto the Disk is transmitted from the Registers section to the 4047 logic interface via the COMP DATA (Computer Data) line. Serial data to be assembled into words and sent back to the Processor is transmitted from the 4047 logic interface to the Registers section via the READ DATA line. The Write and Load signals from the I/O section to the Registers section together enable the 32 bit shift register (functioning as a series-to-parallel, parallel-to-series converter for the Disk data) to be parallel loaded with the next two words to be written on the Disk. The CLK SHIFT signal is also produced in the I/O section and being derived from the basic Data Strobe signal (from the 4047 logic interface) functions as a shift clock for the shift register during read and write operations.

Figure 1-5. General Functional System Block Diagram For the 4046 Disk Controller and Adapter 4047 or Adapter 4049

The I/O section transmits the INC SC, XFER DONE, D1, D0, CM1 and CM2 signals to the 4047 logic interface. The INC SC signal (Increment Sector Counter) steps the Sector Counter within the I/O section. It also actuates the Checkword logic in the 4047 logic interface for either writing the assembled checkword during a write operation or comparing the assembled checkword with that written at the end of the sector during a read operation. XFER DONE is a signal informing the 4047 Adapter (both the plug and logic interface thereof) that the present transfer operation is finished. The D0 and D1 signals to the 4047 logic encode the address of the Disk Drive to be used during the upcoming operation. The CM1 and CM2 signals to the 4047 logic interface encode the commanded operation that the system is to perform (i.e., seek, read, write, or recalibrate). The BIT COUNT signal from the 4047 logic interface is used to increment the Bit Counter within the I/O section. This counter keeps track of the number of data bits transferred and counts up to 32, the capacity of the shift register.

The I/O section also exchanges a group of significant signals with the Timing section. The I/O section sends functional signals SECTOR, CYLINDER and HEAD DATA, UNIT 0 through UNIT3 SELECT, DATA1 through DATA4, SHIFT DONE and LATE (1). The SECTOR, CYLINDER and HEAD DATA is multiplexed in the Timing section onto interassembly lines BUS0 through BUS7, to the 4047 logic interface. Sector register bit 8, S8, is transmitted directly to the 4047 logic interface over a single line, and hence is not multiplexed. The UNIT0 through UNIT3 Select signals are used in conjunction with the Seek control logic of the Timing section and indicate which one of the four possible Disk Drive units have been selected. This same logic section sends SEEK DONE0 thru SEEK DONE3 signals back to the I/O section to indicate that the selected Disk Drive (UNIT0 thru UNIT3) has finished the commanded (track) seek operation. The DATA1 thru DATA4 signals are those bits which reset the Seek control logic of the selected unit. (DATA0 clears the Read/Write Done interrupt indicator, however this flag is in the I/O section.) The SHIFT DONE signal performs an important function relative to both the read and write modes. The SHIFT DONE signal sent to the Timing section is allowed to trigger a one shot, in the read mode, which in turn loads the disk data contained in the Shift Register (in the Register section) into the Data Storage Register (also in the Registers section) in preparation for multiplexing onto the I/O bus lines to the Processor.

SHIFT DONE also performs a clocking for the DP Flag and Data Late flip-flops in the I/O section. (The Data Late flip-flop becoming set, sets the Stop flip-flop, which in turn (providing the "Read Done" one shot is not cycling) produces a DONE signal. DONE in turn drives an OR gate to produce XFER DONE which terminates the transfer.) A momentary digression at this point to explain the basic function of Data Late will serve to clarify later detailed discussion of this logic. The DP (Data) Flag flip-flop is set (during write operations) initially on a start of a write operation. This Flag is cleared when the Data Channel Acknowledgement from the second Data Channel Request is received at the Control assembly. Two (16 bit word) requests are required as 32 bits are written as one word by the Control assembly. If the Flag flip-flop is set and a SHIFT DONE signal occurs the Data Late

flip-flop will be set. This condition indicates that for some reason the Processor did not respond to the Data Channel Request in time to load (or finish loading) the Shift Register before it finished a 32 bit shifting (and writing) sequence. Hence, a data error condition will exist and the transfer will be terminated. Initially the (Data) Flag flip-flop is set by the WRITE and START ADAPTER signals. It is cleared by CLR FLAG (derived from DCHP IN, DCHR, DCH SEL, and DCHA) and the resetting of the REQ1 flip-flop (indicating second request has been acknowledged). The (Data) Flagflip-flop is clocked to the set state during the remainder of the writing operation (as long as the Busy flip-flop remains set) by each SHIFT DONE signal. Setting the Flag flip-flop causes the next DCHR to be issued (if requests are enabled). The Flag flip-flop is cleared during the remainder of the write operation exactly as described above. Hence, during the writing operation a "window" exists between SHIFT DONE pulses during which the Flag flip-flop is set (requesting the next two 16 bit data words from the Processor), to which the Processor must respond by servicing the request (long before SHIFT DONE can occur in normal operation). The worst case (Processor response delay) condition exceeding the width of the time window (between subsequent SHIFT DONE pulses) defines the Data Late error condition.

The Timing section sends a RD/WR DONE signal back to the I/O section. This signal is derived from the ADAPT DONE (1) signal from the 4047 Adapter to indicate the Adapter has completed (or terminated) the command operation. RD/WR DONE sets the Done flip-flop in the I/O section.

The Timing section receives the CKWD, ADAPT SEL, ADAPT DONE (1), END OF CYLINDER, AD+UNSF, and SKE signals from the 4047 Adapter (Plug and Logic Interface). Four of these signals, CKWD, END OF CYLINDER (EOC), AD+UNSF, and SKE are errors indicators. The CKWD signal is generated in the Checkword section of 4047 logic to indicate a Checkword error has been detected. The EOC signal is generated in the Head Select section of the 4047 logic whenever an attempt to increment to a non-existent head is detected, i.e., increment beyond the number of heads available in the Disk Drive. AD+UNSF is derived from a WRITE CHECK signal produced in the Disk Drive unit electronics and indicates that a condition exists within the drive unit that will interfere with writing valid data on the Disk, or possible damage to other records already written on the Disk will occur if writing is attempted. SKE is the Seek Error signal, which is derived from the SEEK INC signal from the Disk Drive unit. SEEK INC denotes SEEK INComplete, and indicates the failure of the present seek operation to successfully position the heads over the selected cylinder. Signal ADAPT SEL is produced in the A or B Control Select section of the 4047 logic and indicates that an operational connection has been established between the 4046 Control assembly and the 4047 Adapter. The Adapter is designed to select one of two possible 4046 Control assemblies for operation (if the Control has been started and is waiting for service). The ADAPT DONE(1) signal, as described previously, is produced in the Adapter Done section of the 4047 logic, and causes the DP Done flip-flop (of the I/O section of the 4046 Control) to become set (via the RD/WR DONE signal function).

The Timing section contains a Seek Timing Generator, which provides a precise sequence of signals used to control the various calculations and mechanical selections involved in moving the Disk heads to the selected cylinder position. There signals are CONTROL1, CYL, HD+DIR, DIFF, and CONTROL2, of which only CONTROL1 and CYL are used by the 4047 Adapter. CONTROL1 is used as one of the enabling signals for setting up the RD/WR (read/write) control logic in the Unit and Track Address section of the 4047 logic. CON-TROL1 is also gated together with RECAL (Recalibrate) to implement the Track Address logic to command repositioning of the Disk heads back at the 000 starting location. Signal CYL is also used, independently, to trigger the Track Address logic. When CYL occurs the Track Address register is loaded with the Cylinder address data. This data is subsequently sent to the (selected) 4047A or 4047B Disk Drive unit electronics where it is positionally interpreted as track address data. It is pointed out here as a matter of clarification, that both CONTROL1 and CYL will be produced in the Timing section if a SEEK command is present. For all other commands (RECAL, READ, WRITE) only CONTROL1 will be produced by the Timing section. Hence, in a sense CYL and RECAL (and all other commands except SEEK) are operationally mutually exclusive. (RECAL is decoded in the 4047 logic to generate a RESTORE signal. This signal clears the track address register in the Disk Drive unit to 000, and commands the head positioner to locate the heads over track 000. In the event of a Seek Error a RESTORE command is required by the Disk Drive electronics before it will remove the SEEK INCOMPLETE level from the interface line.)

The Timing section also sends the INC HD and START signals to the Head Select and the A or B Control Select sections of the 4047 logic. The INC HD signal will increment read or write operations to the next numerically selectable head in the Disk Drive unit. Since the 4047A and 4047B Disk Drive units each contain two heads, incrementing (without an End of Cylinder error) is not possible beyond head 1, selected by placing a 1 on the BUS7 line (which results from coding a 1 in bit 7 of the Accumulator selected for the DATOC instruction). The INC HD signal is generated when the Sector Register reaches a count of 12 (S8 and S4 = 1), and an Increment Sector Counter (INC SC) signal is present. This function facilitates the 12 sector format established for the 4047A and 4047B Disk Drive units. Therefore after Sector No. 12, the 4046 Control assembly logic automatically advances or increments the head to operate on the 12 sectors on the opposite side of the Disk (in the same track location). INC HD also implements logic within the 4046 Control to clear out the Sector register. It should be emphasized that it is Sector No. 12 not necessarily the 12th sector that causes the INC HD signal to be produced. Normally the Sector register is loaded with the number of the sector in which the specified operation will be performed, and the Sector register will be incremented from this point on up to Sector No. 12. The START signal, on the other hand, is simply representative that the 4046 Control has been started by either an I/O "P" (Pulse) control function for either a SEEK or RECAL operation, or an I/O "S" (Start) control function for the other (Read or Write) operations. After transmitting the START signal

the 4046 Control must wait for the 4047 Adapter to respond with an ADAPTER SEL before operation can proceed.

# 1-2.2 Adapter Model 4047

The Adapter Model 4047 is functionally located between the 4046 Control assembly and the 4047A or 4047B Disk Drive unit (or units). Functionally, the Adapter contains the following five logic sections:

- 1) Check-Data Strobe-Bit Count section.

- Unit and Track Address-Sector Equal and command section.

- 3) A or B Control Select-Head-Adapter Done section.

- 4) Read Logic section.

- 5) Write Logic section.

The Checkword-Data Strobe-Bit Count section produces the CKWD, DATA STROBE and BIT COUNT signals. The Checkword logic of this section forms the 16 bit checkword during read and write operations. The assembled checkword is the last word written into each sector. The assembled checkword is transmitted serially from the checkword shift register to the Write logic section via the CHKCH line, where it is gated out to the Disk Drive unit via the WRITE DATA and CLOCK line. The checkword assembled during a read operation is compared with the checkword written on the Disk for equality at the end of the read operation. Comparison is performed on a bit-by-bit basis. As each bit (of the recorded checkword) is read in from the Disk, it is compared with the least significant bit of the Checkword register. Each bit of the recorded checkword read in (after the first comparison) also causes the Checkword register to be (right) shifted for the comparison. The recorded checkword bit is presented to the checkword logic via the READ DATA line. READ DATA also provides the information required to form the checkword during the read operation. (It is noted that READ DATA is also the information line which carries the data read from Disk to the Register section.) Likewise, the WRITE DATA line provides the Checkword logic with the information required to form the checkword during a write operation. The READ and WRITE are Commands decoded from the signals on the CM1 and CM2 lines.

A  $\overline{WRITE}$  GATE or  $\overline{READ}$  GATE signal is produced by the appropriate (write or read) logic section for the Disk Drive unit. The  $\overline{WRITE}$  GATE signal turns on write current and erase current simultaneously in the selected Disk head, therefore  $\overline{WRITE}$  GATE is held on (or true) for the entire write operation. The  $\overline{READ}$  GATE signal, on the other hand, enables the  $\overline{READ}$  CLOCK and  $\overline{READ}$  DATA outputs from the Disk Drive unit electronics, and also is held on (or true) for the entire read operation.

The READ CLOCK line from the Disk Drive electronics provides pulses that represent clock signals which have been separated from data signals (within the Disk Drive unit) during reading. Conversely the READ DATA line from the Disk Drive electronics provides pulses that represent data signals which have been separated from clock signals (within the Disk Drive unit) during reading. The READ CLOCK signal is used to synchronize and control the Read logic and Checkword logic

during the read operation. During the write mode of operation the Write logic and Checkword logic are synchronized by the outputs from a two stage ring counter driven by the 5.75 MHz Adapter oscillator, which together function as the write clock.

Sector register data from the Disk Drive unit is compared, in the Sector Equal logic, with the Sector Address data transmitted from the 4046 Control via BUS lines 0 thru 2, and the  $\overline{88}$  lines. This comparison is basically a four bit binary exclusive OR comparison to determine equality. The output from the comparison logic is tested upon the arrival of each SECTOR (MARK) PULSE from the Disk Drive unit. SEC-TOR MARKS are generated within the Disk Drive unit as each sector slot (on the Disk shaft assembly) as it rotates by the sector transducer. The leading edge of this pulse provides a mechanical reference as to the start of the associated sector. (The SECTOR MARK also increments the Sector Address register within the Disk Drive unit.) An equality signal from the comparison logic together with a  $\overline{\text{SECTOR PULSE}}$ (a slight nomenclature change to this signal line occurs as it passes through the interface between the Disk Drive unit and the 4047 Adapter, i.e., SECTOR MARK becomes SECTOR PULSE) will allow the commanded read or write operation to begin.

The data loaded into the Track Address register of the Track Address logic section is transmitted to the Disk Drive unit via eight interface lines (binary lines 1 thru 128). Initially and after the data has been loaded into the Track Address and given a chance to settle, a TRACK ADD STROBE signal is sent to the Disk Drive unit. The Disk Drive unit interprets this signal as a command to sample either the eight TRACK ADDRESS lines or the RESTORE line. The TRACK ADD STROBE signal and the TRACK ADDRESS data must be held in their specified states until the ADD ACK (ADDress ACKnowledge) signal is issued by the Disk Drive unit. This requires a holding interval between 22.5 and 37.5 microseconds. The TRACK ADD STROBE is released as soon as ADD ACK is received.

As described previously, the 4047A and 4047B Disk Drive units contain two heads. The HD SEL (Head Select) line allows selection of either head relative to the logic level presented on this interface line. A logic 0 (0 voltnominal) signal selects the upper head whereas a logic 1 (+ 5 volts nominal) signal selects the lower head. The selected level placed on the HD SEL line is held for the entire duration of the read or write operation.

#### 1-2.3 Instructions

The I/O instructions for the Disk Control Model 4046 are provided in other Data General publications (e.g., Nova Disk Pack Drive Option Bulletin), and are included here for general reference purposes. The Device Select code for the 4046 Control is octal 33.

1-2.3.1 <u>Seek Instructions</u>. The SEEK instruction is initiated with an I/O "P" pulse. It has no effect on BUSY or DONE but does require 50 microseconds to initiate (for the

4047A or 4047B Disk Drive units). The Adapter will hold the SEEK for 6 seconds or until READ or WRITE DONE occurs.

If no READ or WRITE instruction follows a SEEK, the Adapter will accept another SEEK. This prevents consecutive SEEK instructions with no READ or WRITE from tying up an Adapter. SEEK DONE is set at the completion of a SEEK, and will cause an interrupt on the control initiating the SEEK.

1-2.3.2 Read/Write Instructions. The disk control is placed into operation to READ or WRITE with the I/O "S" pulse. If the Adapter is busy or the Disk Drive is not ready, BUSY is set, and the READ/WRITE instruction is held.

The setting of DATA LATE indicates the transfer rate of the disk was greater than that of the I/O channel during peak periods of I/O traffic. If this condition exists, the program will automatically reposition the READ/WRITE heads to cylinder 000, SEEK and try again.

If there is no error condition, the control waits until the selected track sector is encountered and then processes the information in the block making data channel requests whenever it has a word ready for memory in READ or when one of the buffers is ready for WRITE.

In READ, if the checkword read from the disk does not agree with that computed by the control, data transfer is halted and the head and sector in error may be read via DIC. During the transfer of several sectors, if the end of the cylinder was detected and the sector count was not zero, END CYLINDER will be set and no automatic SEEK to the next cylinder takes place.

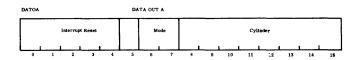

### 1-2.3.3 Function and Format

Load Interrupt-Reset Register, Mode and Cylinder address into the disk control. Perform the function specified by F.

The mode bits (6 and 7) generate the disk pack command as follows:

| BIT | <u>6</u> | 7 | FUNCTION    |

|-----|----------|---|-------------|

|     | 0        | 0 | READ        |

|     | 0        | 1 | WRITE       |

|     | 1        | 0 | SEEK        |

|     | 1        | 1 | RECALIBRATE |

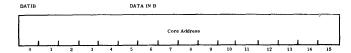

Load the contents of AC 1-15 into the Core Address Register with the STARTING Core Address.

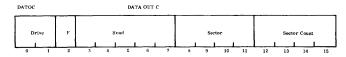

Load the contents of AC 1-15 into the disk UNIT, HEAD, SECTOR and SECTOR COUNT address register. Select the UNIT, HEAD and SECTOR from which data is to be transferred initially, and select the two's complement number of consecutive sectors to be transferred.

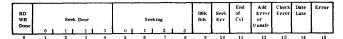

Read the status of the disk system into the AC bits 0-15 as shown.

AC bits 0-9 indicate status of the drive. Bits 10-15 indicate error conditions.

AC 10 Selected disk drive did not complete a SEEK.

AC 11 The HEAD address register has incremented be-

yond the last HEAD of the cylinder. This condition will cause a consecutive sector READ or WRITE to stop transfer.

C 12 The disk selected by the

AC 12 The disk selected by the program is unsafe for operation or the address selected on the disk does not agree. Address errors are a mismatch between the header data and the cylinder head being sought.

AC 13 In READ, the cyclic checkword read from the disk surface did not agree with the checkword computed by the control.

AC 14 The data channel failed to respond in time to a request for access. (This can occur because of a long instruction or channel pre-emption by a faster device.)

AC 15 The "OR" condition of bits 10-14 exists.

Read the contents of the Address Counter into AC bits 0-15. NOTE: Core Address Register (C) = Starting Core Address + 256N + 2, where N = Number of Sectors Written.

Read the present contents of the UNIT, HEAD address, SECTOR address, and SECTOR COUNT registers into AC bits 1-15.

#### 1-3 PHYSICAL DESCRIPTION

The Disk Control Assembly Model 4046 is a 15 X 15 inch printed circuit board (PCB) Assembly designed for plug mounting in the multiple printed circuit board connector located within the Nova or Supernova Enclosure Chassis. The 4046 Control Assembly PCB is inserted horizontally into the Enclosure Chassis and on a plane with the particular slot previously wired for this assembly. An outline drawing typical of the standard printed circuit boards provided by Data General is provided in Appendix A of the "How to use the Nova Computers" reference manual.

The physical and electrical specifications for the 4047 and 4049 Adapters are listed in Table 1-1. An outline drawing of the Adapter enclosure is shown on Figure 1-6. The performance specifications for Data General Disk Drive types, 4047A & 4047B are presented in the Drive publications under separate cover.

#### 1-4 PERTINENT DOCUMENTS

The following documents serve as source material and complement the information in this manual. Publications available from sources other than Data General are listed with the address of the alternate source. Publications listed without an alternate source address are available only from Data General.

How to Use the Nova Computers

Series 30 Disk Drives Product Description No. D3031-670

Diablo Systems Incorporated 24500 Industrial Blvd. Hayward, California 94545

Maintenance Manual

For Model 31 Disk Drive No. D3140-171

Diablo Systems Incorporated

24500 Industrial Blvd.

Hayward, California 94545

Moving Head Disk Control

Diagnostic DGC Manual 097-000039

Moving Head Disk Reliability Program DGC Manual 097-000038

#### 1-5 ABBREVIATIONS

Listed below are the most commonly used abbreviations of registers, operations, components, instructions, and signal names. It will be noted that this listing has been compiled in alphabetical-numeric order to facilitate referencing.

Table 1-1. Specification Data-Adapters 4047 and 4049

| i doite I II bpec                     | Physical Data                                 | . 4114 1015          |

|---------------------------------------|-----------------------------------------------|----------------------|

|                                       | Adapter 4047                                  | Adapter 4049         |

| Enclosure Height                      | 7 inches (nominal)                            | 7 inches (nominal)   |

| Enclosure Width (Mounting)            | 19 inches (nominal)                           | 19 inches (nominal)  |

| Enclosure Width (Enclosure)           | 16 15/16 inches                               | 16 15/16 inches      |

| Enclosure Depth                       | 19 5/8 inches                                 | 19 5/8 inches        |

| Weight                                | 30 Lbs.                                       | 55 Lbs.              |

| * * * * * * * * * * * * * * * * * * * | Electrical Data                               |                      |

| Power Requirements                    | 115V or 230V *Single                          | 115V or 230V *Single |

| •                                     | phase, + 20% 47 to                            | phase, + 20% 47 to   |

|                                       | 63 Hz. Maximum                                | 63 Hz. Maximum       |

| \$                                    | Current 2 amperes,                            | Current 4 amperes.   |

|                                       | 230 watts.                                    | 460 watts.           |

| Power Supply Outputs**                |                                               |                      |

| +15 volt                              | 8 amperes (Max.)                              | 17 amperes (Max.)    |

| -15 volt                              | 5 amperes (Max.)                              | 10 amperes (Max.)    |

| + 5 volt                              | 3 amperes (Max.)                              | 3 amperes (Max.)     |

| Logic Signals                         | Low = 0 volts to<br>+.4 volt<br>nominal       | Same as 4047         |

|                                       | High = +2.5 volts to<br>+3.5 volts<br>nominal | Same as 4047         |

- \* 230 volt on special order

- \*\* Maximums specified are based on maximum configurations as defined in Paragraph 1-1.1 of this manual.

Figure 1-6. Outline of Adapters 4047 and 4049

## ABBREVIATIONS

| ADAPT DONE (1)                 | . Adapter Done (flip-flop output)                                             |

|--------------------------------|-------------------------------------------------------------------------------|

| ADAPTER SEL                    | . Adapter Select                                                              |

| AD+UNSF                        | . Addressing (error) or Unsafe                                                |

| AD+UNSF (1)                    |                                                                               |

| ADV HD                         |                                                                               |

| ADV HD.                        |                                                                               |

|                                | ,                                                                             |

| ATTEN0-ATTEN3                  |                                                                               |

| BIT COUNT                      |                                                                               |

| BUS0-BUS7                      | Bus Line 0 thru Bus Line 7 (to Disk Units)                                    |

| CA0-CA15                       | Current Address Register Outputs 0 thru 15                                    |

| CKWD (1)                       | Checkword (flip-flop output)                                                  |

| CKWD (1)                       |                                                                               |

| CLEAR ALL                      | Clear All (logic reset function)                                              |

| CLEAR ALL                      |                                                                               |

| CLEAR                          |                                                                               |

| CLEAR.                         |                                                                               |

|                                |                                                                               |

| CLEAR C                        |                                                                               |

| CLEAR P                        |                                                                               |

| CLK A                          |                                                                               |

| CLK B                          |                                                                               |

| CLK B                          | . (Complement of above)                                                       |

| CLEAR STATUS                   | Clear (error) Status flip-flops                                               |

| CLK SHIFT                      |                                                                               |

| CLK SHIFT                      |                                                                               |

| CLK DSA                        |                                                                               |

| CLK DSB                        |                                                                               |

|                                |                                                                               |

| CLK DSB                        | · · · · · · · · · · · · · · · · · · ·                                         |

| CLR FLAG                       |                                                                               |

| CM1                            |                                                                               |

| CM2                            | · · ·                                                                         |

| CONTROL1                       | (Start Adapter function) Control 1                                            |

| CONTROL1                       |                                                                               |

| CONTROL2                       | (Seek Timing function) Control 2*                                             |

| CONTROL2                       | (Complement of above)                                                         |

| CLR                            | · - ·                                                                         |

| CLR REQ                        |                                                                               |

| CYL                            |                                                                               |

| <u>CYL</u>                     |                                                                               |

| CYL1, CYL2, CYL4, CYL8, CYL16, | (Complement of above)                                                         |

| CYL32, CYL64, CYL128           | O. N. J. D. D. determinate                                                    |

|                                |                                                                               |

| <u>DATA</u>                    |                                                                               |

| DATA LATE (1)                  |                                                                               |

| DATA LATE (1)                  | (Complement of above, flip-flop output)                                       |

| DATA STROBE                    | . Data Strobe (controls serial-parallel, parallel-serial                      |

|                                | movement of data)                                                             |

| D0-D1                          | . Disk (unit select) Lines 0 and 1                                            |

| DATA0-DATA15                   |                                                                               |

| DATA0-DATA15                   |                                                                               |

| DATIA                          |                                                                               |

| DATIB                          |                                                                               |

|                                |                                                                               |

| DATIC                          | , , ,                                                                         |

| DATOA                          |                                                                               |

| DATOB                          |                                                                               |

| DATOC                          |                                                                               |

|                                |                                                                               |

| DCHA                           | (I/O Bus signal) Data Channel Acknowledge                                     |

|                                | (I/O Bus signal) Data Channel Acknowledge                                     |

| DCHA                           | (I/O Bus signal) Data Channel Acknowledge<br>(I/O Bus signal) Data Channel In |

<sup>\*</sup>Not used with Adapters 4047 and 4049

# ABBREVIATIONS (Continued)

| DCHO                             |                                               |

|----------------------------------|-----------------------------------------------|

| DCHP IN                          | , ,                                           |

| DCHP IN                          | • •                                           |

| DCHP OUT                         |                                               |

| DIFF                             |                                               |

| DIFF                             | (Complement of above)                         |

| DONE                             |                                               |

| $\overline{	extsf{DP}}$          | . Disk Pack (mnemonic for 4046 Control)       |

| DP BUSY (1)                      | . Disk Pack Busy (flip-flop output)           |

| DP BUSY                          | Disk Pack Busy (flip-flop)                    |

| DP DATIA                         | Disk Pack Data In A                           |

| DP DATIB                         | Disk Pack Data In B                           |

| DP DATIC                         | Disk Pack Data In C                           |

| DP DATIC                         | (Complement of above)                         |

| DP DATOA                         |                                               |

| DP DATOB                         | . Disk Pack Data Out B                        |

| DP DCHA                          |                                               |

| DP DCHI                          | •                                             |

| DP DCHI                          |                                               |

| DP DCHO                          | ,                                             |

| DP DCHO.                         |                                               |

| DP DCH REQ                       | • =                                           |

| DP DONE                          | <del>-</del>                                  |

| DP DONE (1).                     | `/                                            |

| DP FLAG                          |                                               |

| DP FLAG (1)                      |                                               |

| DP INT                           |                                               |

| DP INT DISABLE                   |                                               |

|                                  | •                                             |

| DP INT REQ                       |                                               |

| DP INT REQ (1)                   |                                               |

| DP IOP                           |                                               |

| DP SELECT                        |                                               |

| DP START                         |                                               |

| DP START                         |                                               |

| DS0-DS31                         |                                               |

| DS0-DS5                          |                                               |

| DUR                              |                                               |

| EN                               |                                               |

| EN CA                            |                                               |

| EOC                              |                                               |

| EOC (1)                          | , /                                           |

| ERR                              |                                               |

| F DONE                           |                                               |

| FORMAT                           |                                               |

| FORMAT                           | , -                                           |

| <u>HD1, HD</u> 2, HD4, HD8, HD16 |                                               |

| HD + DIR                         | Head and Direction (Seek Timing function)*    |

| <u>HD + DIR</u>                  |                                               |

| INC CA                           | Increment Current Address Register            |

| INC HEAD                         |                                               |

| INC SC                           |                                               |

| INC SC                           | (Complement of above)                         |

| INTA                             |                                               |

| INTERRUPT                        | . (Present operation done, request) Interrupt |

| INT P IN                         | (I/O Bus signal) Interrupt Priority In        |

| INTP OUT                         | (I/O Bus signal) Interrupt Priority Out       |

|                                  | · · · · · · · · · · · · · · · · · · ·         |

<sup>\*</sup>Not used with Adapters 4047 and 4049

### ABBREVIATIONS (Continued)

| <u>INTR</u> (1                        | I/O Bus signal) Interrupt Request               |

|---------------------------------------|-------------------------------------------------|

| IOPLS(I                               |                                                 |

| IO RST(I                              | I/O Bus signal) IO Reset                        |

| LOAD I                                | Load Shift Register from Data Storage Register) |

| MSKO                                  | I/O Bus signal) Mask Out                        |

| RD•WR                                 |                                                 |

| RD/WR DONE                            |                                                 |

| READR                                 | <b>,</b>                                        |

| READ(0                                |                                                 |

| READ DATA                             |                                                 |

|                                       | ,                                               |

| RECAL                                 |                                                 |

| RECAL(                                | . •                                             |

| RESET                                 |                                                 |

| RESET                                 |                                                 |

| RESET S (1)                           |                                                 |

| REQ1                                  | First data request or) Request 1                |

| RQENB                                 | I/O Bus signal) Request Enable                  |

| SEEK S                                | Seek (Command decode)                           |

| <u>SEEK</u>                           | Complement of above)                            |

| SEEK DONE                             |                                                 |

| SEEK DONE0 (1)                        |                                                 |

| SEEK DONE0 (1)(                       | · · · · · · · · · · · · · · · · · · ·           |

| SEEK DONE1 (1)                        |                                                 |

| SEEK DONE1 (1)                        |                                                 |

|                                       |                                                 |

| SEEK DONE2 (1)S                       |                                                 |

| <u>SEEK DONE2</u> (1)(                |                                                 |

| SEEK DONE3 (1)                        | ` · · · · · · · · · · · · · · · · · · ·         |

| SEEK DONE3 (1)                        |                                                 |

| SEEKING0                              | (Disk Unit 0) Seeking (indicator flip-flop)     |

| SEEKING1(                             | (Disk Unit 1) Seeking (indicator flip-flop)     |

| SEEKING2                              | (Disk Unit 2) Seeking (indicator flip-flop)     |

| SEEKING3                              | (Disk Unit 3) Seeking (indicator flip-flop)     |

| SEEKINGO (1)                          | Seeking 0 (flip-flop output)                    |

| SEEKING1 (1)                          | Seeking 1 (flip-flop output)                    |

| <u>SEEKING2</u> (1)                   |                                                 |

| SEEKING3 (1)                          |                                                 |

| SELB                                  | 9 ( /                                           |

| SELD                                  | ,                                               |

| SHIFT DONE                            |                                                 |

| SHIFT DONE SHIFT31(                   | ,                                               |

| ,                                     | , ,                                             |

| SKES                                  |                                                 |

| <u>SKE</u> (                          | •                                               |

| START                                 | · · ·                                           |

| <u>START</u> (                        | `                                               |

| START (1)                             |                                                 |

| START ADAPTER (1)                     | - '                                             |

| START SEEK                            | ,                                               |

| STOP(0)                               | Stop (flip-flop output)                         |

| STRT (                                | (I/O Bus signal) Start                          |

| S0, S1, S2, S4, S8, $\overline{S8}$   | Sector Register outputs                         |

| SC1, SC2, SC4, SC8                    |                                                 |

| TS ENABLE                             |                                                 |

| TS ENABLE (1)                         |                                                 |

| UNITO                                 |                                                 |

| <u>UNIT1</u> (                        |                                                 |

| UNIT1<br>UNIT2                        |                                                 |

| · · · · · · · · · · · · · · · · · · · | , ,                                             |

| <u>UNIT3</u> (                        | (Disk) Out 3 (Select)                           |

|                                       |                                                 |

## ABBREVIATIONS (Continued)

| WRITE       | Write (Command decode)                                 |

|-------------|--------------------------------------------------------|

| <u> </u>    | (Complement of above)                                  |

| XFER DONE   | Transfer (of data) Done                                |

| 2nd Request | Second (data) Request (from 4046 Control to Processor) |

#### SECTION II

#### INSTALLATION

#### 2-1 GENERAL

This section provides detailed information and procedures for installing the Data General Disk Cartridge System. The Disk Drive unit (4047A or 4047B) is packed and shipped in a special reusable container which may be retained for reshipmentuse. Place the shipping container right side up and open the center flaps. Exercise care when opening the container to prevent damage to the finished surfaces of the unit. The equipment manuals and unpacking instructions should now be accessible from the carton. Follow the unpacking and installation procedures as listed. It is recommended that three people be used to remove the Disk Drive unit, two people to lift the unit from the carton, and one person to assist in clearing away the empty carton. The next important step in unpacking the Disk Drive unit is to remove the shipping clamp from inside the unit. This should be done as soon as the unit is removed from its shipping carton, to eliminate the possibility of damage due to any inadvertent attempt to operate the unit with the shipping clamp still in place within the unit. The top cover will have to be removed from the unit first to provide access to the Shipping Clamp. The clamp holds the head positioner over track 0. The presence of this clamp prevents the insertion of a cartridge. No other shipping clamps are included. Inspect the unit both internally and externally for evidence of shipping damage. If any damage is present do not attempt to operate or connect power to the unit, rather notify Data General Field Service and the carrier company immediately. If no visible damage is present reinstall the top cover and complete the rest of the installation procedures for the Disk Drive unit.

The Disk Adapter unit, 4046 Control assembly and cables, are shipped together in one container. This container actually consists of two protective containers which are packaged in the form of a box within a box. The inside container rather than a box is a special styrofoam container used to hold the Disk Adapter unit and cables. The 4046 Control Assembly is wrapped in a cardboard container and packaged on top of the styrofoam container. The cables are packed inside the styrofoam container in the rear of the Adapter unit. Inspect both shipping containers for any visible intransit damage such as would result from dropping or being punctured or crushed. Contact the carrier and Data General Field Service immediately if any damage is discovered, specifying the nature and extent of damage.

### 2-2 INSTALLATION AND CHECKOUT PROCEDURES

The following paragraphs describe the proper method of unpacking the Disk Adapter unit and 4046 Control assembly, and procedures for verifying, operationally, and proper installation. It is recommended that all shipping hardware, packing material and cartons be saved and stored (after unpacking) in the event the Adapter unit and 4046 Control assembly are ever reshipped.

#### 2-2.1 Installation Procedures

The following procedures are used in unpacking and installing the Disk Adapter unit and 4046 Control assembly:

- a) Placethe shipping container right side up and open center flaps. Figure 2-1 shows the relative positions of the outer and inner carton.

- b) Remove top layers of cardboard.

- c) Remove the 4046 Control assembly and Document packages from top of the styrofoam container.

- d) Remove the four foam cushions from each corner. These cushions are used both to secure the inner box in position and absorb shock and vibration during shipment.

- e) Open the 4046 Control assembly package and examine the PCB assembly closely for any possible shipping damage. If any damage is evident do not install the PCB assembly in the Processor, rather notify Data General Field Service immediately.

- f) If no visible damage is present install the 4046 Control assembly into the Multiple PCB Connector slot (within the Nova or Supernova) prewired for the 4046 Disk Control.

### CAUTION:

MAKE SURE ALL POWER HAS BEEN REMOVED FROM THE PROCESSOR BEFORE INSTALLING THE 4046 CONTROL PCB ASSEMBLY, OR ATTACHING THE COMPUTER-TO-ADAPTER CABLE.

g) At this point it is assumed that the Disk Drive unit has been removed from its carton, the shipping clamp has been removed, and the unit has been inspected. Preparatory to installing the unit into a standard 19" rack, each supporting slide rail for the unit must be mounted to the rack cabinet. The procedures for securing the slide rails and subsequent mounting of the unit onto these rails are as follows:

- Slide rail dimensions are 20 9/16" from (mounting) face to face.

- 2) See the Installation drawing, Figure 2-2 for the proper placement of nut plate and speed nut clip hardware. The amount of clearance required between the top of the Disk Drive unit and any panel or equipment located immediately above it in the rack is also specified on the Installation drawing. Use the (12) #10/32 machine screws shipped in the container along with the Disk Drive unit to fasten the slide rails to the rack cabinet.

- 3) Verify rails are opened to the stop position and remain in this position while the Disk Drive unit is being placed onto the rails. This is required to facilitate alignment of the holes in the rear of the drive unit enclosure

Figure 2-1. Relative Positions of Outer and Inner Shipping Cartons.

Figure 2-2. Installation Drawing for Data General Model No's 4047A, 4047B & 4047 or 4049. (Sheet 1 of 3)

Figure 2-2. Installation Drawing for Data General Model No's 4047A, 4047B & 4047 or 4049. (Sheet 2 of 3)

with the alignment studs located on the rear of the slide shaft. The two holes in the bottom of the drive unit enclosure should also align with nylon expansion washer. (This washer is expanded by compression and is screw adjusted as part of the Disk Drive unit securing hardware.)

- 4) Push the unit back into the cabinet. Remove magnetic covers from the sides of the front panel. Secure front panel of unit to rack with hardware supplied, making sure that the nut place and speed nut clips are in the proper position (as shown on the installation drawing) before inserting the screws.

- h) Release the straps on the styrofoam container, and remove the cover from the container.

- Using three people (two to lift the unit from the container, and one person to remove the container once the equipment has been lifted clear) remove the Adapter unit from its container.

- j) Verify that the source end of the Disk Drive dc power cable is connected inside the Adapter unit as follows:

- 1) Remove the logic interface board from the Adapter enclosure. The perforated cover should now be exposed.

- 2) Peek through the perforated cover and verify that the Disk Drive dc cable is connected to the screw terminals located on the rear edge of the power supply Printed Circuit board.

- 3) Verify that the dc power cable is connected as follows; the two blue wires connect to the HV (or BLU) screw terminal. The two red wires connect to the +HV (or RED) screw terminal. The braided ground wire connects to the GND (or BLK/BRN)screw terminal. Screw terminal markings identified above are etched onto the printed circuit board. Additional dc power cable connection data may be found on the Installation drawing referenced above. (The Data General part No. for the dc power cable is 118-000099.)

- 4) After verifying that the dc power cable is properly connected, reinstall the logic interface board back into its original position within the Adapter enclosure. If the dc power cable is not connected notify Data General Field Service.

- 5) Insert key into Power lock switch on Adapter front panel, and verify lock switch is in the "Off" or far left rotational position. Plug in the 110 volt ac line cord. Turnkey, rotationally, to the far right, or "On" position and verify that the Fan within the unit comes on. Do not attempt further installation if the Fan is inoperative.

- k) Using the same number of personnel mount the Adapter in a standard 19" rack, securing it into position as follows:

- 1) The supporting rails for the Adapter unit and hardware are shipped in the Adapter container and should be installed as shown on the Installation drawing referenced above.

- Position speed nut clips as shown on Installation drawing.

- 3) Place Adapter unit on rails and slide into position in the cabinet. (A rear stop is provided for the unit.)

- 4) Secure Adapter to rack with hardware supplied.

- 5) Install console panel, secure by the two 1/4 turn fasteners.

- Connect the Adapter unit dc cable into the power connector on the rear panel of the Disk Drive. Figure 2-3 is a simplified drawing showing cable installation

- m) Connect (Adapter to Drive) ribbon type signal cable (Data General #118-000098) to Adapter connector P1 (Plug Interface back panel in rear of Adapter.) Connect other end of cable to Disk Drive unit. (If this is a single Drive installation connect terminator card (Data General #118-000100) into opposite input/output connector. Reference Figure 2-2, the Installation drawing, for proper daisychaining of input/output cabling in multiple drive installations.

Note; Model 4047B will require one level of daisy-chaining to be installed. An additional ribbon type signal cable is provided for this purpose. Terminate unit the end of the daisy-chain as described above.

- n) Connect Computer I/O Cable (#005-000468) into Connector P2 of the Plug Interface back panel (located in the rear of the Adapter unit. The connector should be installed with the ground tabs pointing toward the ground tabs of connector P3 (also on the back panel PCB). Secure connector ground tabs with two #4/40 Phillips head screws. Connect other end of cable into the designated 50\* pin mating connector located in rear of the processor enclosure.

- o) Set the LOAD RUN switch on the Disk Drive unit to the LOAD connect position. Adapter ac line cord to a standard 110 volt outlet. Insert key into POWER lock switch on Adapter front panel and turn to the ON position. (The key is removable when the lock is turned to the far right rotational (ON) position.)

- p) Verify POWER indicator of Disk Drive unit or (units) comes on. Do not attempt to operate until all power distribution is verified.

- q) Verify that the LOAD indicator of the Disk Drive unit is also illuminated and the READY indicator (of the Disk Drive unit) is extinguished.

- r) Open the cartridge receiver door, insert a Cartridge.

Close the cartridge receiver door and press the LOAD

RUN switch to the RUN position. Verify that the READY

light comes on approximately one minute after switching

to RUN. Verify the CHECK indicator on the Disk Unit

drive is extinguished. If CHECK comes on with READY

switch back to LOAD, wait until the drive stops, then

switch to RUN again. If this still fails to clear CHECK

perform these procedures again using a different Cartridge. If this fails to clear CHECK discontinue further

operation and notify Data General Field Service.

- s) After the Disk Drive has been loaded with a Cartridge and is READY (with CHECK extinguished) power may be applied to the Processor in preparation for performing the checkout procedures.

- \* 100 pin connector for 4 and 10 slot 800 and 1200 Computers.

Figure 2-3. Inter-Unit Cabling for Controller 4046 and Adapter 4047 or 4049

#### 2-2.2 Checkout Procedures

The following procedures are used in initial start-up and operational checkout of the Disk Cartridge System installation.

- a) Using the Binary Loader load the Moving Head Disk Control Diagnostic test (DGC Tape #095-000069) into the Processor through the teletype or high speed reader. Review the test description presented in DGC document #097-000039.

- b) Start the program at location 0000028. Teletype will request input data as to type and Disk Unit number of system under test:

Teletype:

"TYPE 0 FOR CARTRIDGE

1 FOR 10 SURFACE DISK PACK

2 FOR 20 SURFACE DISK PACK"

User Response: 0

Teletype:

"TYPE UNIT NUMBERS (0-3) TO TEST"

User Response:

n Carriage Return

Where n is the Unit number of the Disk Drive to be used during the test.