# DataGeneral

## Technical Reference microNOVA<sup>™</sup> COMPUTER SYSTEMS

014-000073-03

#### NOTICE

Data General Corporation (DGC) has prepared this manual for use by DGC personnel and customers as a guide to the proper installation, operation, and maintenance of DGC's equipment and software. The drawings and specifications contained herein are the property of DGC and shall neither be reproduced in whole or in part without DGC's prior written approval nor be implied to grant any license to make, use, or sell equipment manufactured in accordance herewith.

DGC reserves the right to make changes without notice in the specifications and materials contained herein and shall not be responsible for any damages (including consequential) caused by reliance on the materials presented, including but not limited to typographical or arithmetic errors, company policy and pricing information. The information contained herein on DGC software is summary in nature. More detailed information on DGC software is available in current released publications.

NOVA, SUPERNOVA, ECLIPSE and NOVADISC are registered trademarks of Data General Corporation, Southboro, Mass.

> Ordering No. 014-000073 © Data General Corporation, 1976 All Rights Reserved. Printed in the United States of America Revision 03, January 1977

## **TABLE OF CONTENTS**

## SECTION I microNOVA COMPUTER SYSTEMS

| TRODUCTION AND OVERVIEW I-1  |

|------------------------------|

| CPU and 2K/4K RAM Boards I-1 |

| Memory Boards                |

| Peripherals                  |

| General Purpose Boards I-3   |

| Chassis                      |

| Power Supply I-4             |

| CKAGED SYSTEMS               |

| DDING AIDS                   |

| LATED MANUALS                |

## SECTION II CPU AND 2K/4K RAM BOARD

| OVERVIEW AND INTRODUCTION II-1     |

|------------------------------------|

| SUMMARY OF CHARACTERISTICS II-2    |

| BLOCK DIAGRAM II-2                 |

| CPU to Memory Bus II-2             |

| CPU to I/O Bus                     |

| Power Up/Fail and Run Control II-4 |

| On Board Memory                    |

| Special Function Jumpers II-4      |

| CPU and Console                    |

| Auto-restart                       |

| Automatic Program Load Option II-5 |

| ROGRAMMING                  | 11-5 |

|-----------------------------|------|

| IXED POINT ARITHMETIC       | 11-6 |

| OGICAL OPERATIONS           | 11-6 |

| TACK MANIPULATION           | 11-6 |

| ROGRAM FLOW ALTERATION      | 11-7 |

| ΝΡυτ/Ουτρυτ                 | 11-7 |

| CENTRAL PROCESSOR FUNCTIONS | 11-8 |

| EAL TIME CLOCK              | 11-8 |

## SECTION III RANDOM ACCESS MEMORY BOARDS

| OVERVIEW AND INTRODUCTION  | -1    |

|----------------------------|-------|

| SUMMARY OF CHARACTERISTICS |       |

| BLOCK DIAGRAM              | 111-3 |

## SECTION IV PROGRAMMABLE READ-ONLY MEMORY BOARDS

| OVERVIEW AND INTRODUCTION  | IV-1 |

|----------------------------|------|

| SUMMARY OF CHARACTERISTICS |      |

| BLOCK DIAGRAM              | IV-2 |

## SECTION V HAND-HELD CONSOLE SUBSYSTEM

| OVERVIEW AND INTRODUCTION  | V-1 |

|----------------------------|-----|

| SUMMARY OF CHARACTERISTICS | V-1 |

÷ ...

| OCK DIAGRAM          | <b>V-3</b>          |              |

|----------------------|---------------------|--------------|

| I/O Interface        | . V-3               |              |

| HHC Memory           | HC Memory           | . <b>V-3</b> |

|                      | . <b>V-3</b>        |              |

|                      | Display and Control | . <b>V-3</b> |

| Keyboard and Control |                     |              |

| OGRAMMING            | . <b>V-4</b>        |              |

| OGRAMMING SUMMARY    | . <b>V-4</b>        |              |

| Instructions         | . V-5               |              |

| Instructions        | V-5 |

|---------------------|-----|

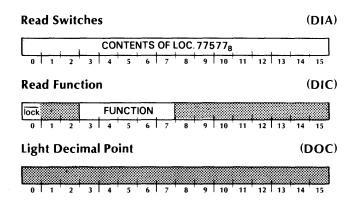

| Read Switches       | V-5 |

| Light Decimal Point | V-5 |

| Read Function       | V-5 |

## SECTION VI ASYNCHRONOUS INTERFACE BOARD

| OVERVIEW AND INTRODUCTION ····································      |

|---------------------------------------------------------------------|

| SUMMARY OF CHARACTERISTICS · · · · · · · · · · · · · · · · · · ·    |

| BLOCK DIAGRAM · · · · · · · · · · · · · · · · · · ·                 |

| Asynchronous Serial Interface · · · · · · · · · · · · · · · · · · · |

| Console Debug Option                                                |

| PROGRAMMING VI-5                                                    |

| PROGRAMMING SUMMARY                                                 |

| Instructions                                                        |

| Read Character                                                      |

| Write Character                                                     |

| Read Modem Status                                                   |

| Control Data Terminal Ready                                         |

· •

## TABLE OF CONTENTS (Continued) SECTION VII DISKETTE SUBSYSTEM

| OVERVIEW AND INTRODUCTION                      |                              |

|------------------------------------------------|------------------------------|

| SUMMARY OF CHARACTERISTICS                     |                              |

| BLOCK DIAGRAM                                  |                              |

| Subsystem Interface and Controller             |                              |

| Data Format                                    |                              |

| 2F Data Transcription                          |                              |

| Dual Drive Multiplexors                        |                              |

| Information Flow and Control Sequences         |                              |

| Setup and Status Transfers                     |                              |

| Head Positioning                               |                              |

| Address Verification                           |                              |

| Data Writing                                   |                              |

| Data Reading                                   |                              |

| Drive Interlocks and Status Flags              | VII-5                        |

| INSTRUCTIONS                                   | VII-5                        |

| PROGRAMMING SUMMARY                            |                              |

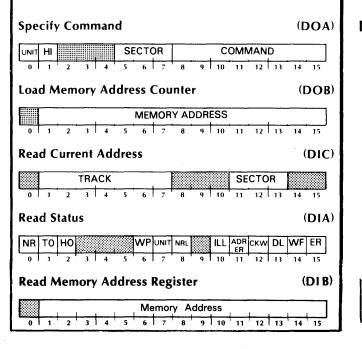

| Specify Command                                |                              |

| Load Memory Address Counter                    |                              |

| Read Current Address                           |                              |

| Read Status                                    |                              |

| Read Memory Address Register                   | <b>VII-7</b>                 |

| PROGRAMMING                                    | <b>VII-8</b>                 |

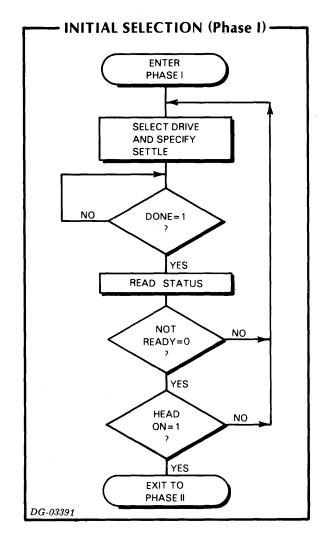

| Phase I: Select the Drive and Determine Status | · · · · · · · · <b>VII-8</b> |

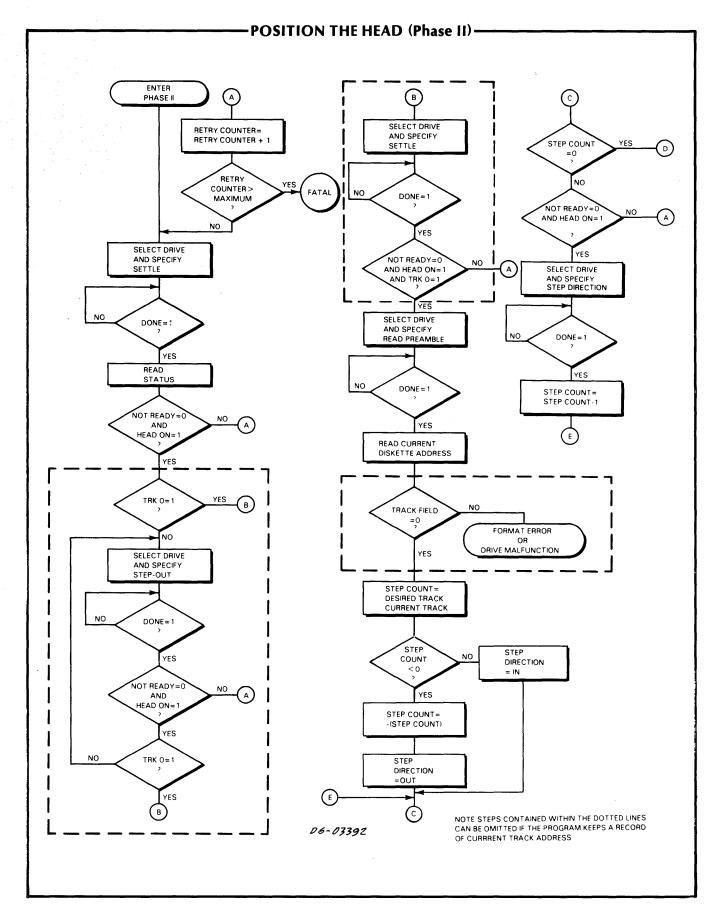

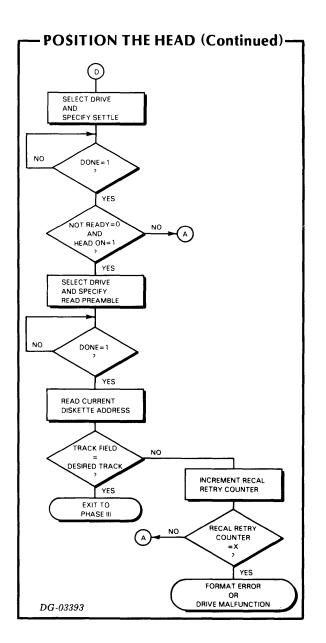

| Phase II: Position the Head                    | <b>VII-9</b>                 |

| Phase III: Read or Write                       | · · · · · · <b>VII-11</b>    |

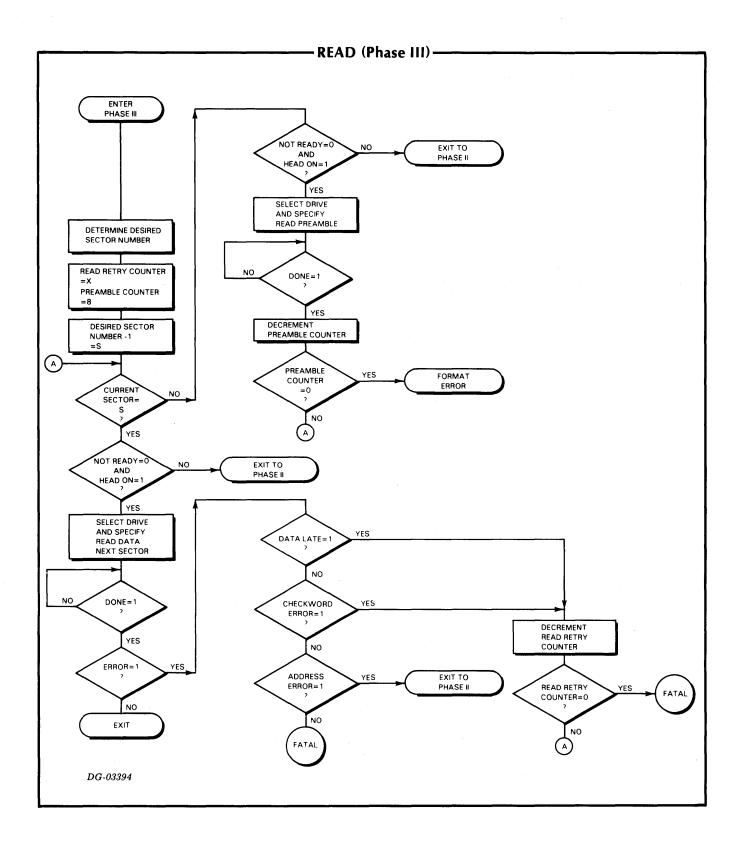

| Read                                           | · · · · · · VII-11           |

| Write                                          |                              |

| TIMING                                         | · · · · · · VII-13           |

| FORMAT                                         | <b>VII-14</b>                |

| ERROR CONDITIONS                               | <b>VII-14</b>                |

| During Initial Selection                       | <b>VII-14</b>                |

| During Head Positioning                        | VII-14                       |

| During Reading                                 |                              |

| During Writing                                 | VII-15                       |

| Illegal Indications                            | VII-15                       |

## SECTION VIII PROM PROGRAMMER BOARD

| OVERVIEW AND INTRODUCTION  | VIII-1 |

|----------------------------|--------|

| SUMMARY OF CHARACTERISTICS | VIII-1 |

| BLOCK DIAGRAM              | VIII-2 |

| PROGRAMMING                | VIII-5 |

| PROGRAMMING SUMMARY        | VIII-5 |

| Instructions               | VIII-6 |

| Specify Address            | VIII-6 |

| Loading Programming Buffer | VIII-6 |

| Verify                     | VIII-6 |

## SECTION IX GENERAL PURPOSE INTERFACE BOARDS

|                               | (-1 |

|-------------------------------|-----|

| SUMMARY OF CHARACTERISTICS IX | (-1 |

| BLOCK DIAGRAM                 | (-3 |

| PROGRAMMING                   | ί-3 |

| Instructions                  | (-3 |

| No I/O Transfer               | (-3 |

| Data In A                     |     |

| Data In B                     | (-4 |

| Data In C                     | (-4 |

| Data Out A                    | (-4 |

| Data Out B                    | (-4 |

| Data Out C                    | (-4 |

| ۱/O Skip                      | (-4 |

| I/O Reset                     | (-4 |

| Mask Out                      | (-4 |

| Interrupt Acknowledge         | -4  |

| SUM | MMARY OF GPIO BUS SIGNALS       |

|-----|---------------------------------|

| 1   | Data IX-9                       |

| ·   | Programmed I/O                  |

| I   | Program Interrupt               |

| 1   | Data Channel                    |

| 1   | System Control                  |

| 1   | Interface Timing                |

|     | Programmed Transfers            |

| I   | Data Channel Transfers          |

|     | Jumpers                         |

|     | Data Lines and Drive Capability |

|     | Busy/Done                       |

|     | Interface Wire Wrap Pins        |

## SECTION X MISCELLANEOUS PRINTED CIRCUIT BOARDS

| OVERVIEW AND INTRODUCTION | ••••••••••••••••••••••••••••••••••••••• | · · · · · · · · · X-1 |

|---------------------------|-----------------------------------------|-----------------------|

## SECTION XI microNOVA CHASSIS

| OVERVIEW AND INTRODUCTION        | XI-1 |

|----------------------------------|------|

| SUMMARY OF CHARACTERISTICS       | XI-1 |

| CHASSIS                          |      |

| CARDFRAME                        | XI-3 |

| POWER SUPPLY                     | XI-5 |

| Power Supply with Battery Backup |      |

## SECTION XII POWER SUPPLY ASSEMBLIES

| OVERVIEW AND INTRODUCTION XII-1     | ł |

|-------------------------------------|---|

| SUMMARY OF CHARACTERISTICS XII-2    | 2 |

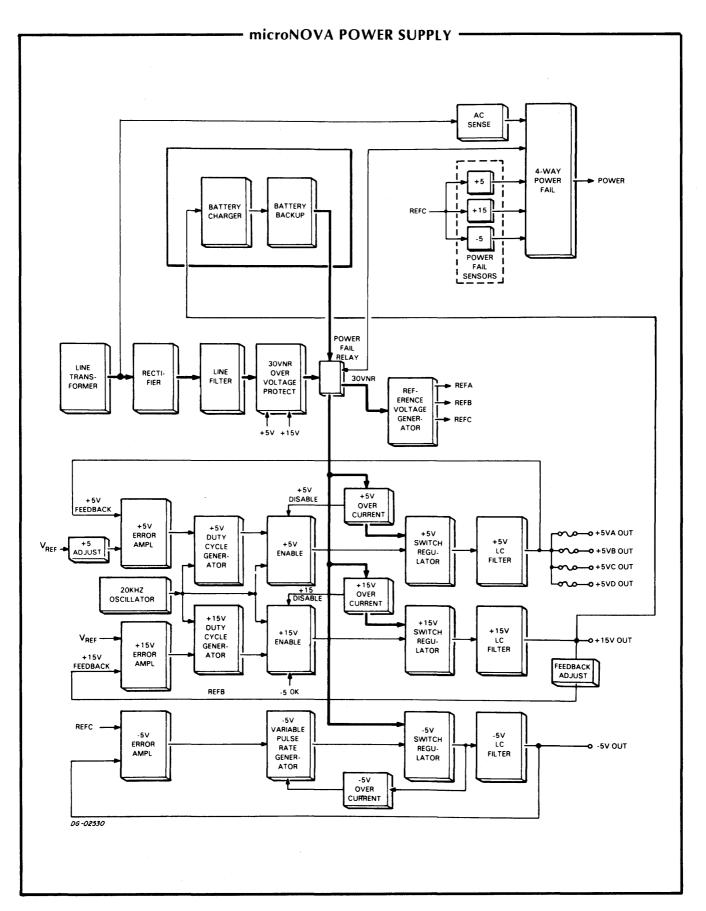

| BLOCK DIAGRAM XII-2                 | 2 |

| AC to DC Conversion                 | 2 |

| Reference Voltage Generation XII-2  | 2 |

| +5V Regulation                      | 2 |

| +15V Regulation                     | ŧ |

| -5V Regulation                      | ŧ |

| Power-fail Detection XII-4          | 4 |

| Battery Backup Implementation XII-4 | 4 |

## APPENDICES

| I/O BUS CONSIDERATIONS          | A-1 |

|---------------------------------|-----|

| microNOVA - NOVA CONSIDERATIONS | B-1 |

This page intentionally left blank.

## SECTION I microNOVA COMPUTER SYSTEMS

### INTRODUCTION AND OVERVIEW

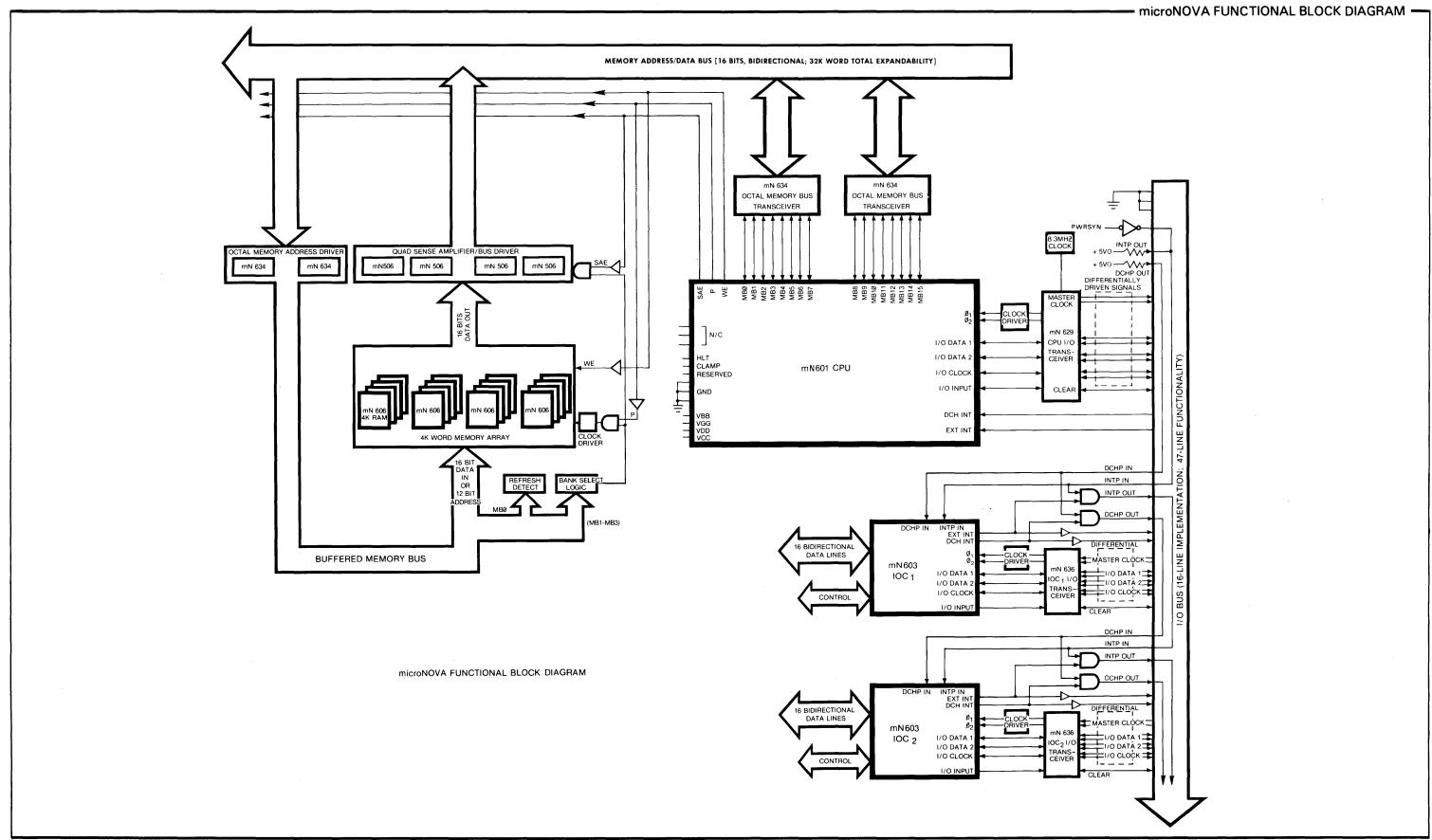

The microNOVA computer systems are organized around the microNOVA microprocessor, a generalpurpose, user-programmable processor which resides on a single LSI N-channel MOS chip. The microNOVA processor has a word length of 16 bits, four accumulators for arithmetic and logical operations, and the capability to address up to 32,768 words of dynamic RAM and/or programmable ROM (PROM) memory. Two independent buses are used to communicate with memory and with I/O devices. The memory bus is used to both access and refresh memory, and consists of sixteen bidirectional data lines and four control lines. The I/O bus is capable of driving I/O devices as far as 100 feet from the microNOVA processor, and consists of a 2-bit bidirectional differential data bus, timing lines, and control lines. The microNOVA computer is softwarecompatible with Data General's NOVA line of computers, and is similar to the NOVA 3 instruction set (see Appendix for greater detail).

The microNOVA computer is available as a complete computer system, as assemblies such as the CPU and 2K/4K RAM board, and as chips such as the CPU and the I/O Controller (IOC). The availability of the separate assemblies and chips gives the customer the flexibility either to construct a computer system tailor-made to his particular applications from the parts available or to purchase the complete microNOVA computer system packaged by Data General. The assemblies which can be purchased separately or combined to form a complete microNOVA computer system are as follows: CPU and 2K/4K RAM Board 4K/8K MOS RAM Board Programmable Read-Only Memory Board Hand-held Console Subsystem Asynchronous Interface Board Diskette Subsystem PROM Programmer Board General Purpose Interface Board General Purpose Wiring Board Extender Board 9-slot/18-slot Main Chassis Card Frame Assembly Power Supply Assemblies

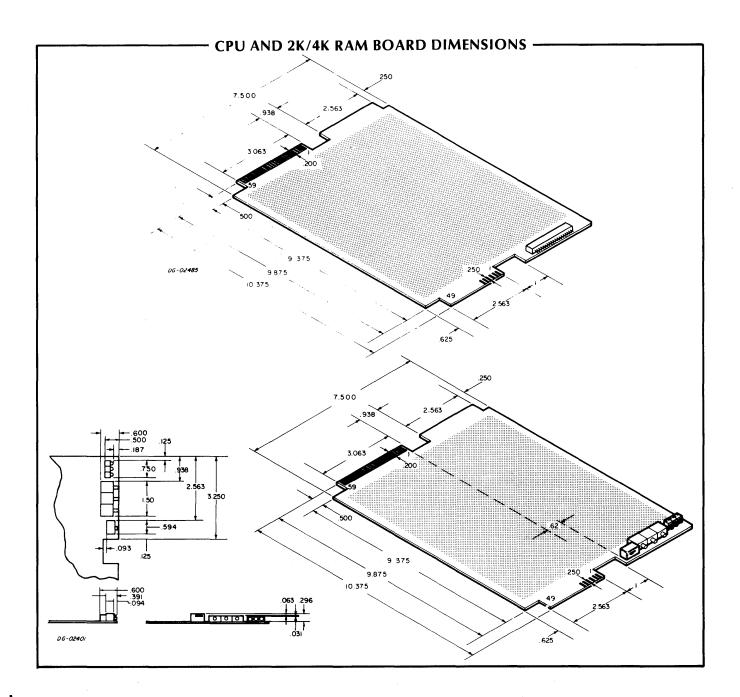

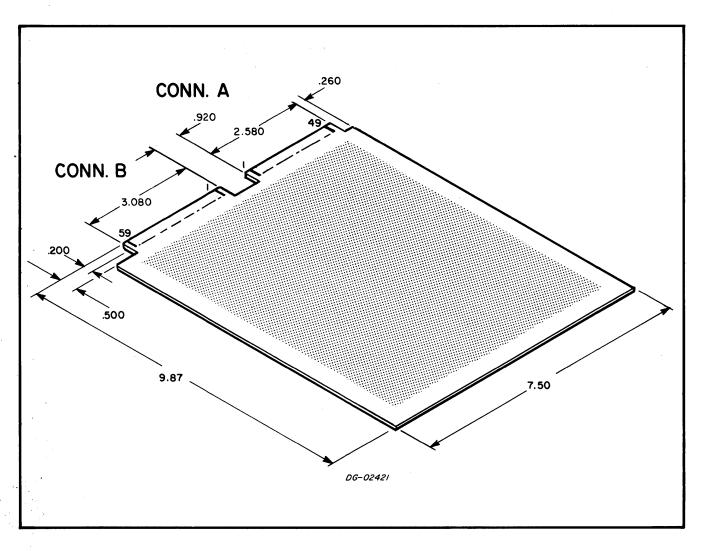

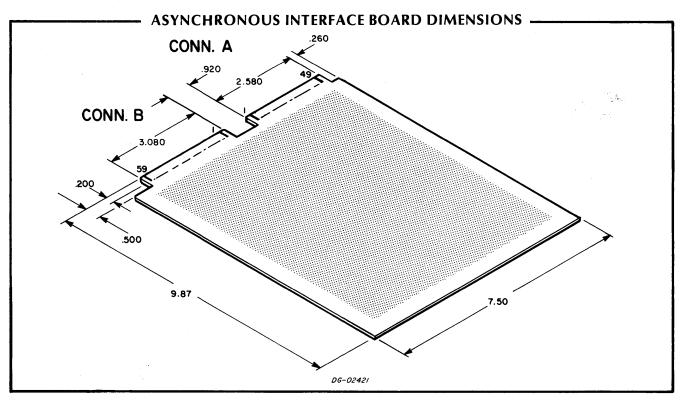

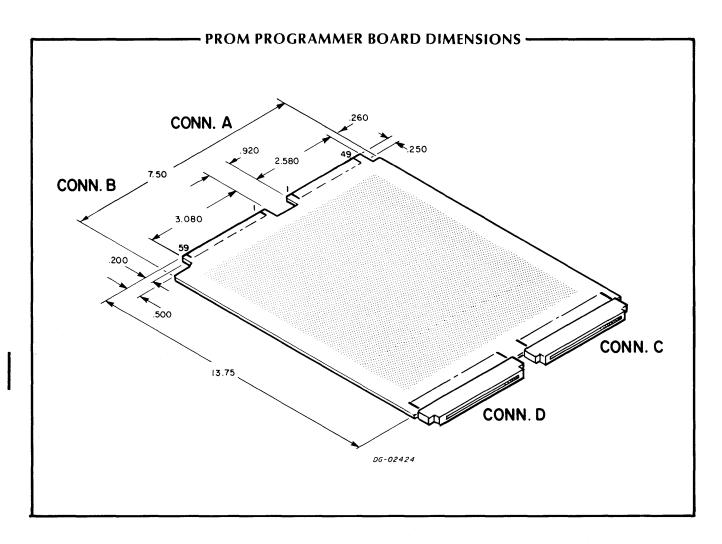

Each of the boards in the system is a 7.5 inch wide printed circuit board suitable for installation in the microNOVA main chassis or the microNOVA card frame assembly. The boards vary in length from 9.9 to 11.7 inches.

On the following page a microNOVA functional block diagram is displayed to show the System user how the various modules are implemented together.

### CPU and 2K/4K RAM Boards

A microNOVA CPU and 2K/4K RAM board is a single 7.5 by 10.4 inch printed circuit board containing a microNOVA CPU, 2K or 4K words of dynamic N-channel MOS random access memory, a timing generator, and interface circuitry for the memory bus and the I/O bus. The word length for both the CPU and the memory is sixteen bits. The CPU contains four accumulators, a program counter, a stack pointer, a frame pointer, and a real-time clock. A general-purpose instruction set, which includes multiply and divide functions as standard features, is available for programming the microNOVA

I

The memory buffering and control circuitry contained on the CPU and 2K/4K RAM board can support up to 32K words of memory within a microNOVA computer system. Memory refresh operations for dynamic RAM are totally hidden, since the memory is refreshed in parallel with processor operations during cycles in which memory is neither read nor written.

The I/O capabilities supported by the CPU and 2K/4K RAM board are programmed data transfer, 16-level programmed priority interrupts, and a data channel capability. The I/O bus can support up to 30 I/O devices, and can be up to 100 feet in length.

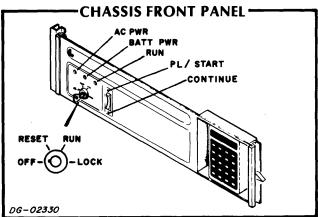

Edge-mounted controls and indicator lights are available as an option with the CPU and 2K/4K RAM board. The controls are start, halt, continue, and lock, and the indicator lights are run, AC power, and battery power. These controls and lights provide a means for controlling the operation of the CPU when the board is not part of a complete microNOVA computer system.

A power fail/auto-restart capability is standard with the CPU and 2K/4K RAM board. An automatic program load capability is optional. The starting address and the device code for automatic program load procedures used are determined by jumper settings on the board. Two features are available to provide user flexibility in start and program load procedures: 1) For program start capability, memory location  $77777_8$  contains the contents of the Jumper Word Register to specify the starting address. 2) For the automatic program load (APL) option, 64 words of local ROM can be enabled to override memory location  $77776_8$  contains the contents of the Jumper Word Register with the option device code.

#### Memory Boards

The microNOVA 4K/8K MOS RAM board contains either 4K or 8K 16-bit words of dynamic random access memory and associated logic. The memory has a cycle time of 960 nanoseconds and must be refreshed once every 1.8432 milliseconds. Each refresh operation will refresh a single block of 64 words. The block of addresses associated with the memory is selected with jumpers.

The programmable read-only memory (PROM) boards contain sockets for 512, 1024, 2048, or 4096 16-bit words of programmable read-only memory and associated logic. The 512 word and 1024 word PROM boards contain eight sockets and 16 sockets respectively for 1024-bit (256 x 4) PROM chips. The 2048 word and 4096 word PROM boards contain 32 sockets for either 1024-bit (256 x 4) or 2048-bit (512 x 4) PROM chips. The block of addresses associated with the memory is selected with jumpers. Within a microNOVA computer system, RAM and PROM can be mixed in any combination up to 32K words of memory.

#### **Peripherals**

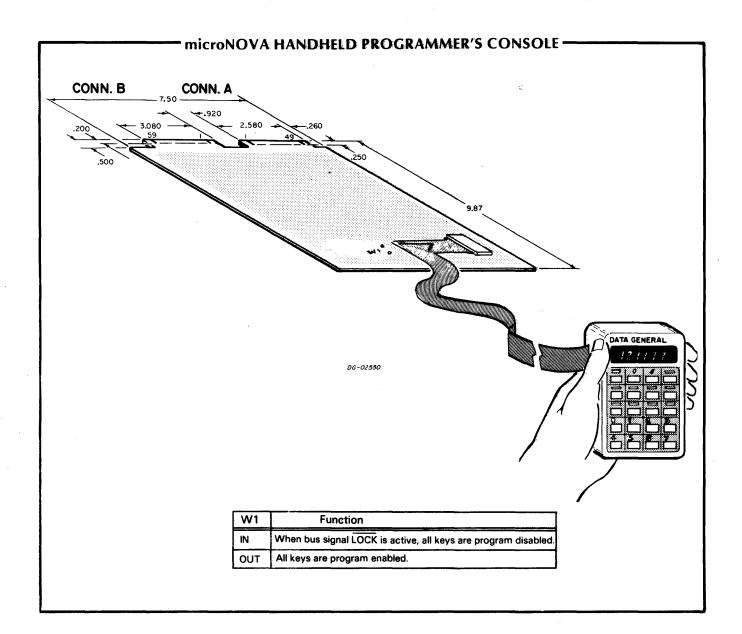

The hand-held console subsystem consists of a hand-held programmer's console, an I/O controller on a 7.5 by 9.9 inch printed circuit board, and a 10-foot 16-conductor ribbon cable which connects the console to the controller. The hand-held console is calculator-like in appearance with 20 push-button keys and a 6-digit display area. The I/O controller contains 256 words of ROM and RAM, corresponding to and taking precedence over any other RAM associated with addresses  $77400-77777_8$ . The controller memory contains standard software which enables the hand-held console to be used to examine and modify the contents of memory locations and internal CPU registers, and to control the operation of the processor with functions such as start, stop, and reset. The standard software also includes an automatic program load capability. User software can be used in place of the standard software to redefine the functions associated with the console keys.

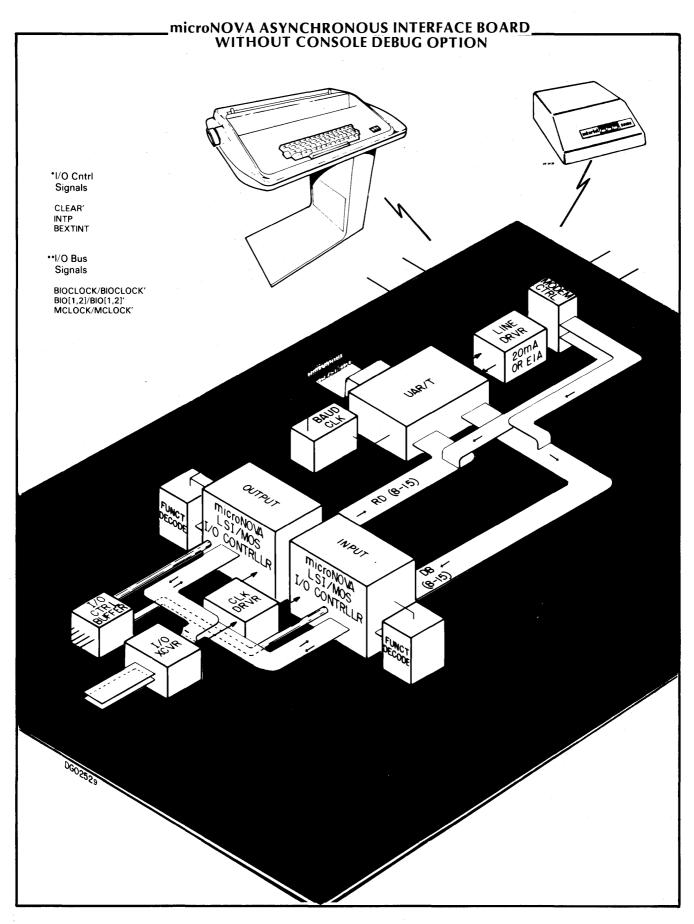

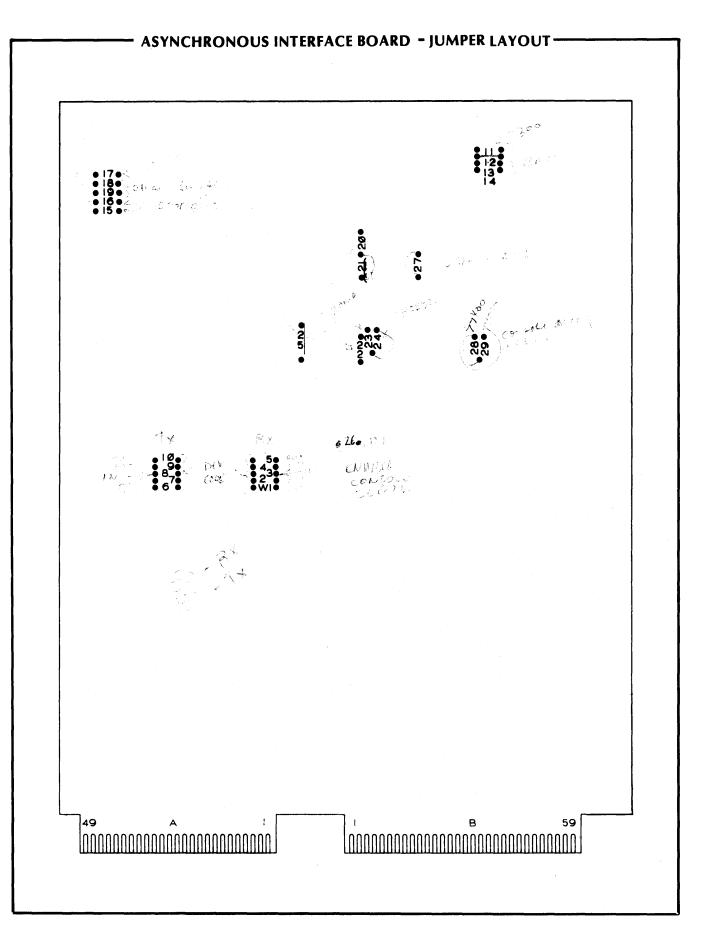

The asynchronous interface board consists of a controller for a single asynchronous terminal or communications line and, optionally, a console debugger. The controller performs full-duplex character assembly and disassembly, with the input and output signals conforming to either EIA RS232-C (CCITT V-24) or 20mA current loop specifications. Any standard transmission speed from 50 baud to 19,200 baud is available. The transmission speed, the number of data bits and stop bits per character, the type of parity associated with each character, and the line specifications (EIA RS232-C or 20mA current loop) are selected with jumpers. In addition, the controller includes a modem control capability.

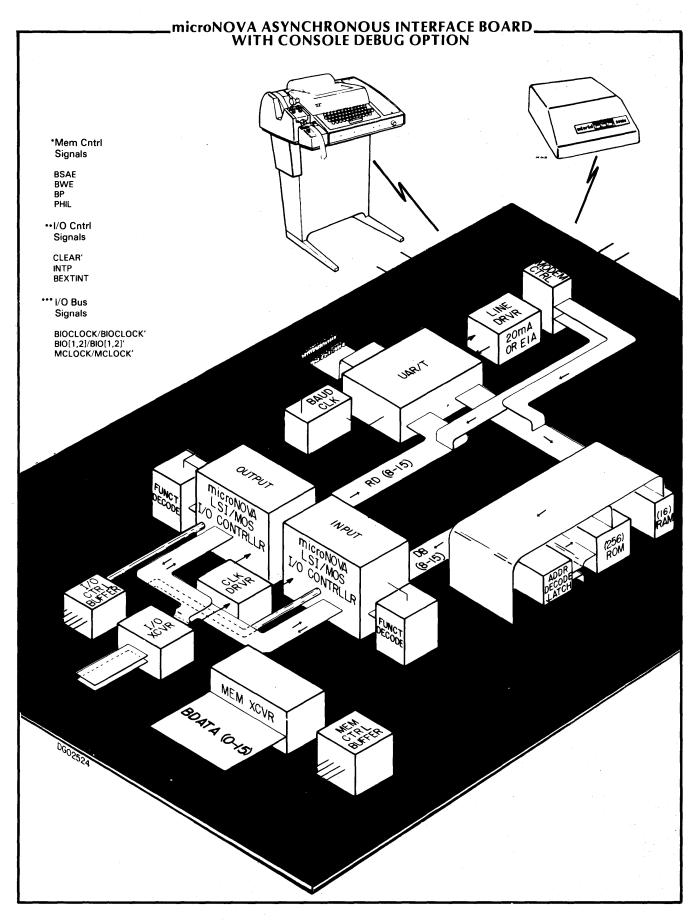

The console debug option available with the asynchronous interface board allows any ASCII terminal to be used as a system debugging console. With this option, the terminal can be used to examine and modify the contents of memory locations and internal CPU registers, to control the operation of the processor with functions such as start and continue, and to set and clear breakpoints. An automatic program load capability is also included with the console debug option. The console debug option program resides in 256 words of ROM and RAM on the asynchronous interface board. This ROM and RAM correspond to and take precedence over any other RAM associated with addresses 77400-777778. Since both the console debug option and the hand-held console subsystem contain ROM associated with addresses  $77400-77777_8$ , they are mutually exclusive options within a microNOVA computer system.

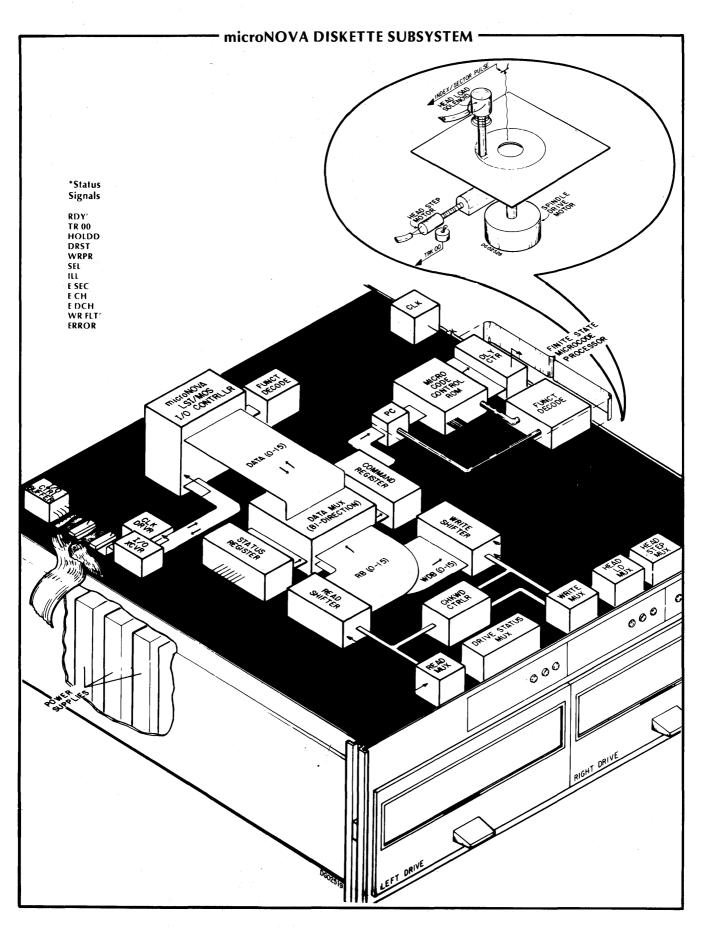

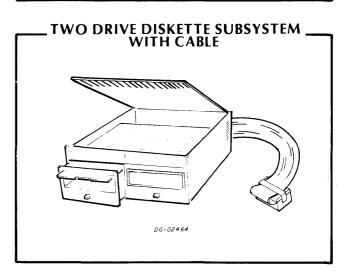

The diskette subsystem provides removable, direct access, moving head disc memory for the microNOVA computer systems. The subsystem consists of one or two drive units in a rack-mountable chassis, a controller on a 15" square printed circuit board contained within the drive unit chassis, and an external I/O bus cable for connection to the I/O bus of a microNOVA computer. Each diskette can store up to 157,696 16-bit words in blocks of 256 words. The maximum data transfer rate is 15,625 words per second.

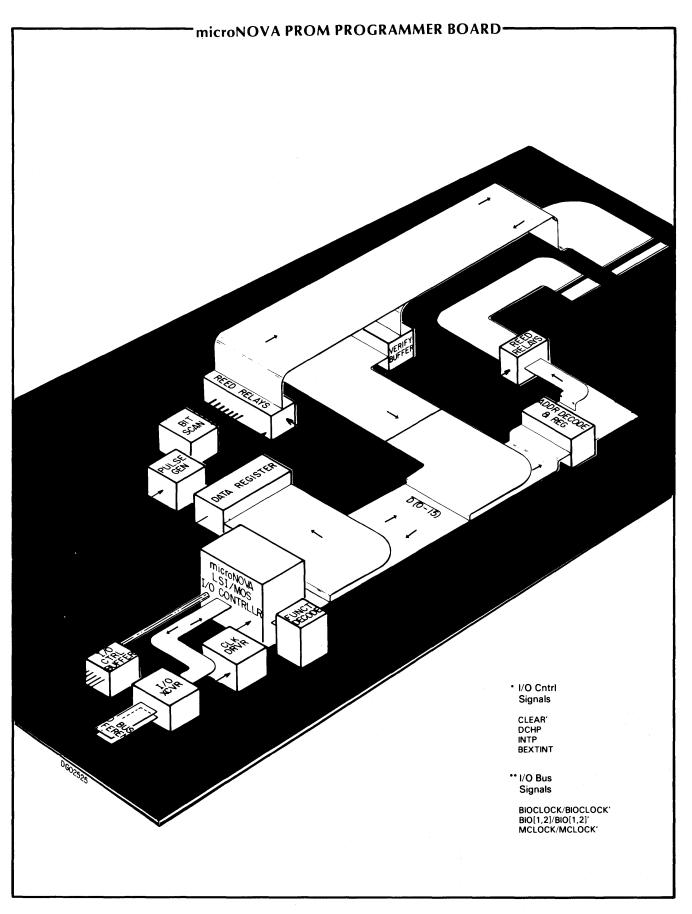

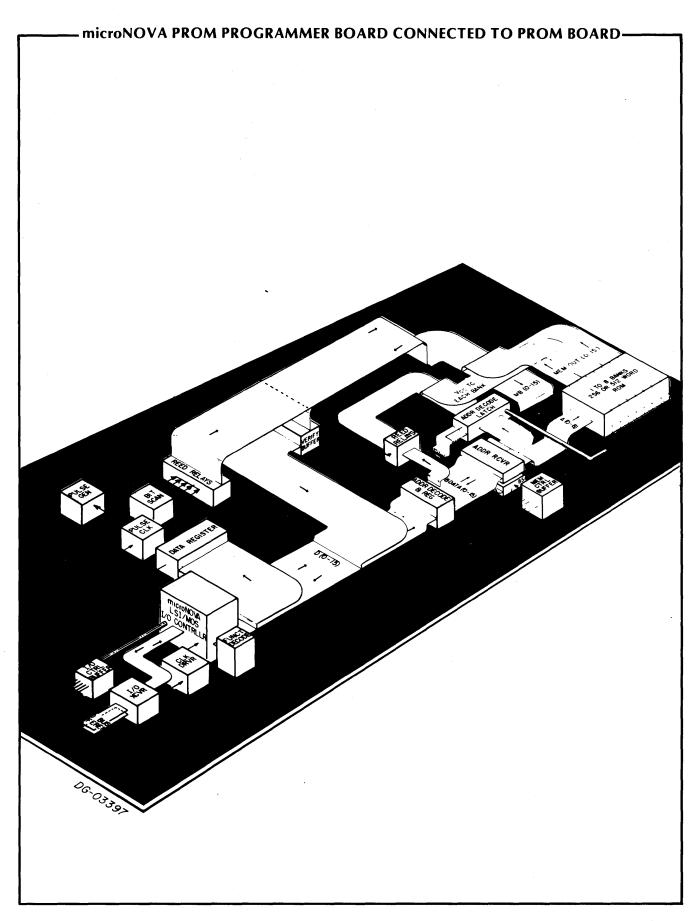

The PROM programmer board provides the capability to program and verify a complete PROM board, one word at a time, under program control. The PROM programmer board has two female board connectors along one 7.5 inch edge of the board for connection to any of the microNOVA PROM boards. The memory on a PROM board is programmed by inserting PROM chips in the sockets of the PROM board, inserting the PROM board in the PROM programmer board connector, and issuing the appropriate I/O instructions to program and verify the contents of memory.

#### **General Purpose Boards**

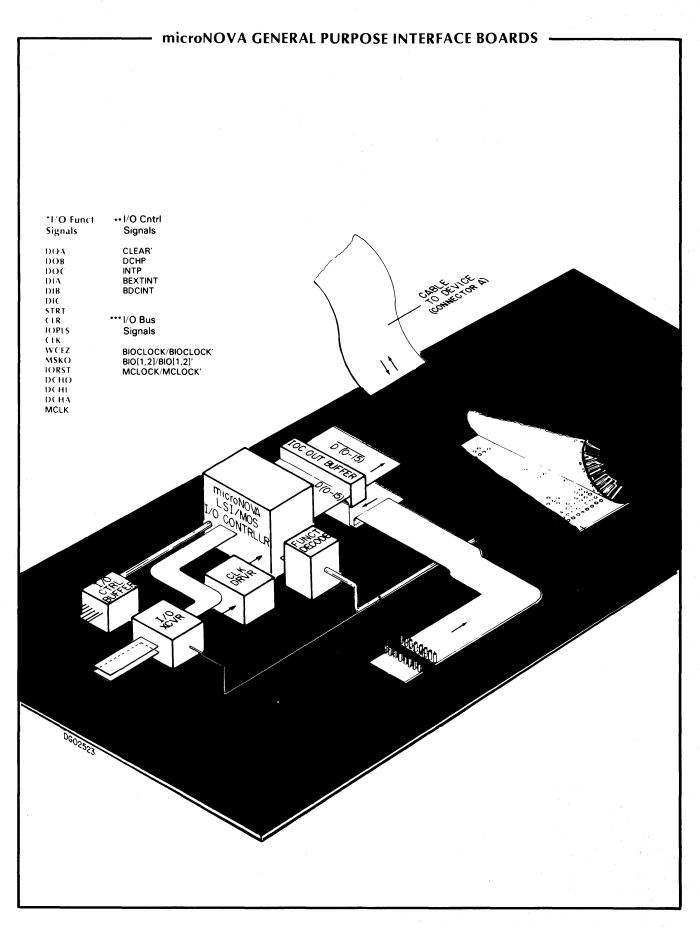

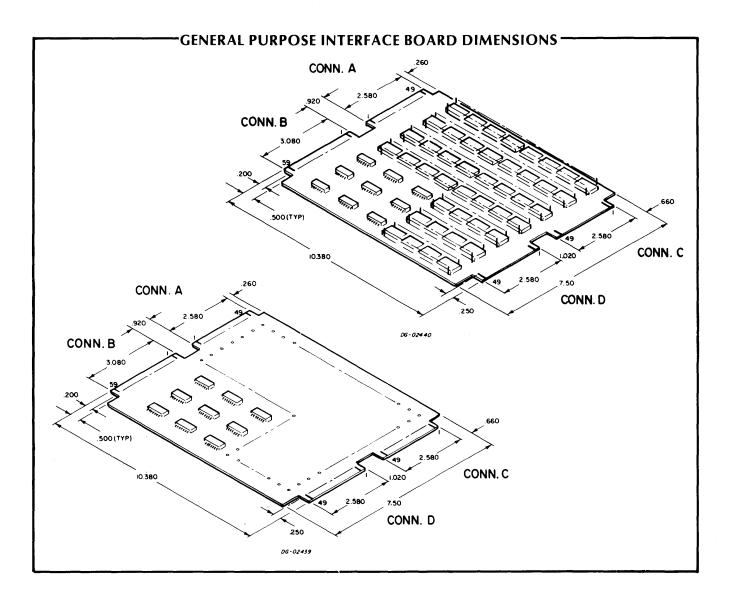

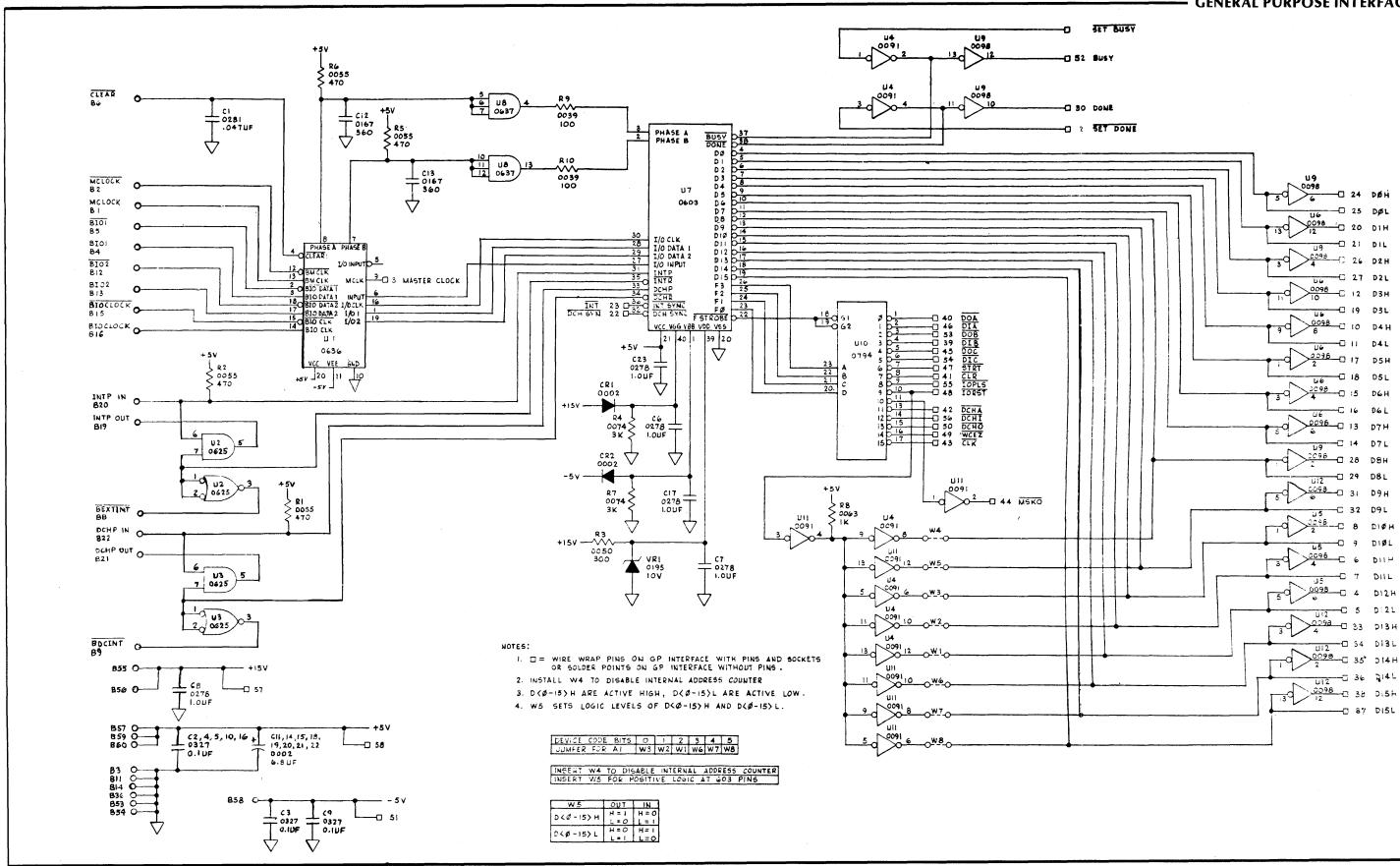

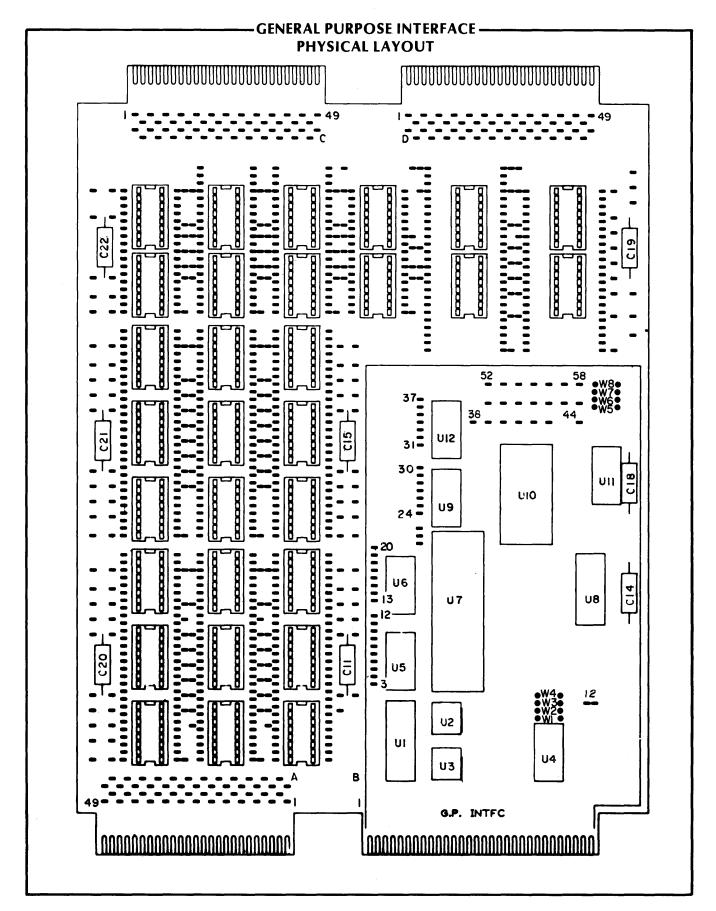

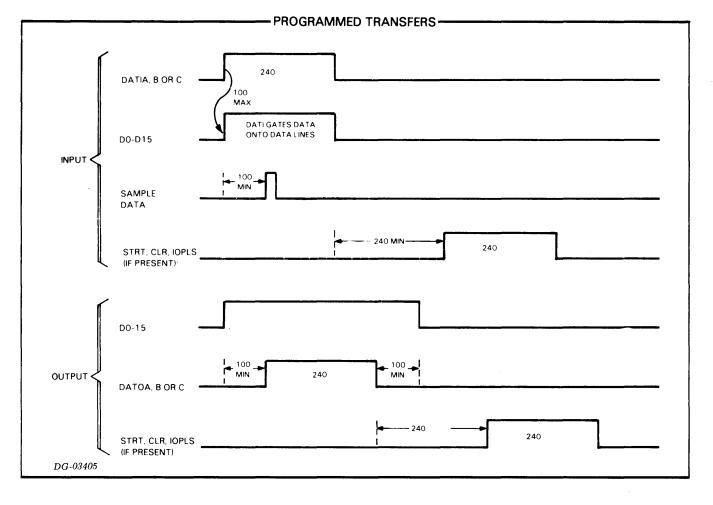

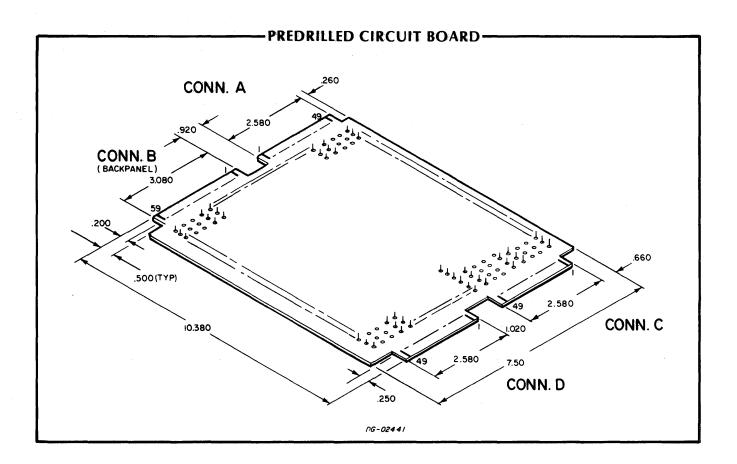

The general purpose interface board provides the basic logic required by a customer building an I/O device controller for inclusion in a microNOVA computer system. The board contains an IOC, an I/O bus transceiver, and supporting logic for a generalized I/O interface including programmed I/O, program interrupts, and a data channel capability. In addition, the board has drilled holes and etched conductors to accommodate chips in 14, 16, 18, 20, 22, 24, 28, and 40-pin packages. The maximum number of chips that can be added to a general purpose interface board is 32 14-pin chips. The general purpose interface board is also available with sockets and wire wrap pins to accommodate a combination of up to 27 14-pin and 16-pin packages.

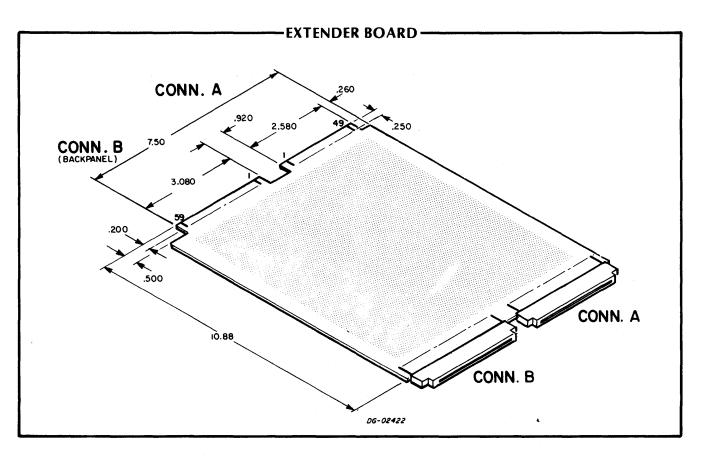

The general purpose wiring board is a 7.5 by 10.4 inch printed circuit board containing only drilled holes and etched conductors to wire wrap pins. The board is designed to be used by the customer building his own assembly for inclusion in a microNOVA computer system. The board can accommodate up to 50 chips in 14-pin packages, and can accommodate a lesser number of chips in combinations of 14, 16, 18, 20, 22, 24, 28, and 40-pin packages. The extender board provides the capability to gain direct access to the components of another printed circuit board in a microNOVA computer system for debugging and maintenance purposes. The board has two female board connectors along one 7.5 inch edge of the board for connection to any microNOVA computer system board. The extender board is inserted into the chassis slot of the board to be tested, and the board to be tested is plugged into the extender board. Etched conductors on the extender board carry all the back panel connections to the extended printed circuit board.

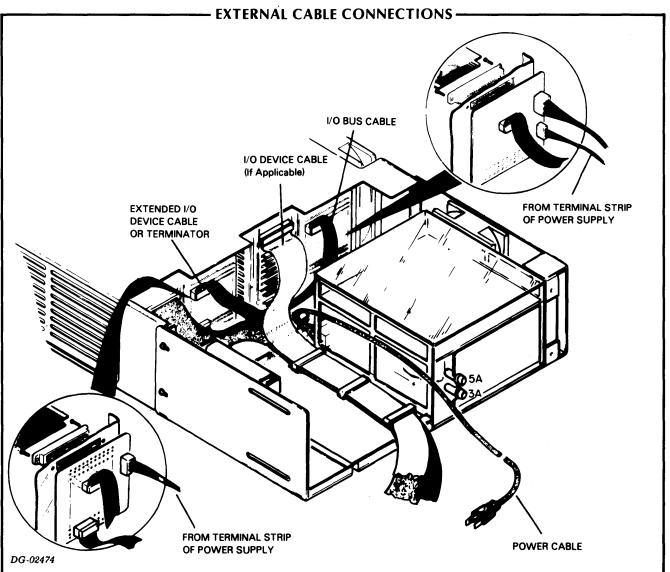

#### Chassis

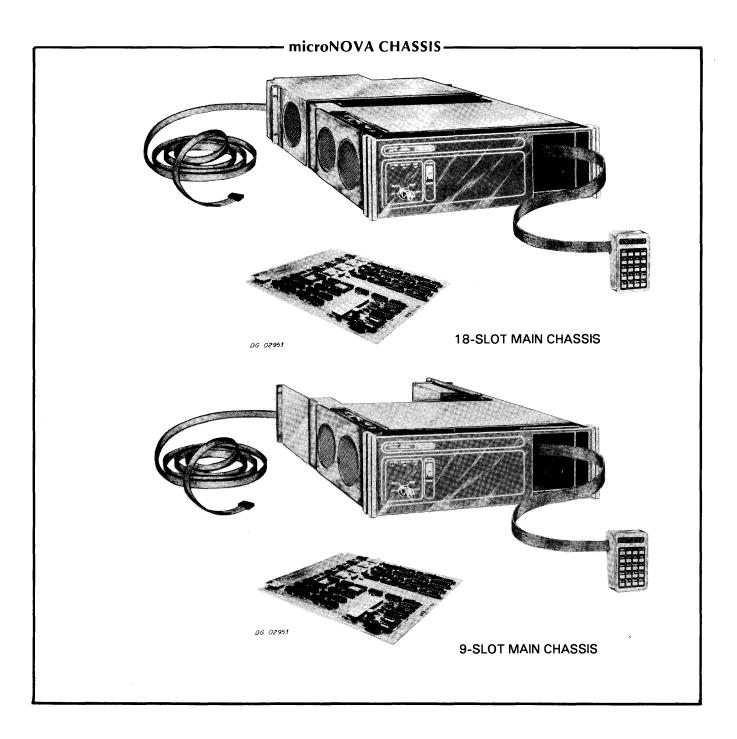

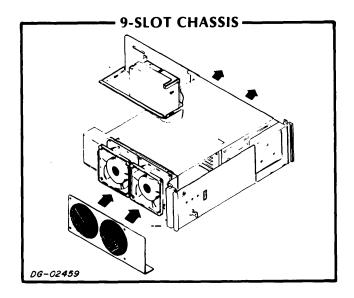

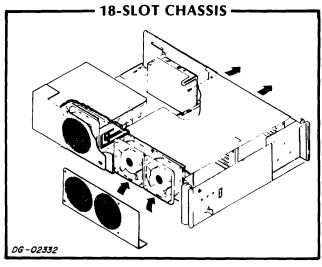

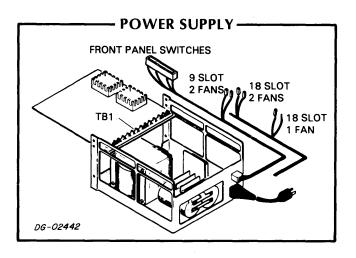

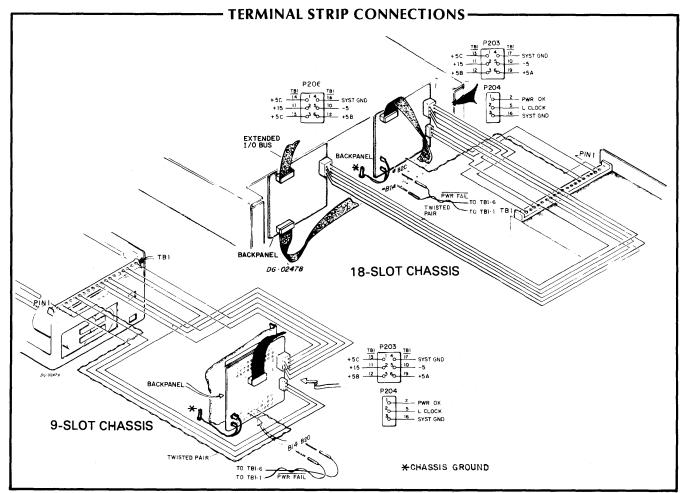

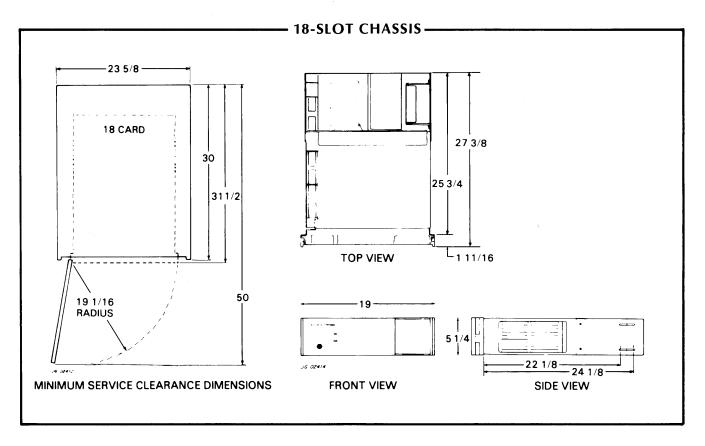

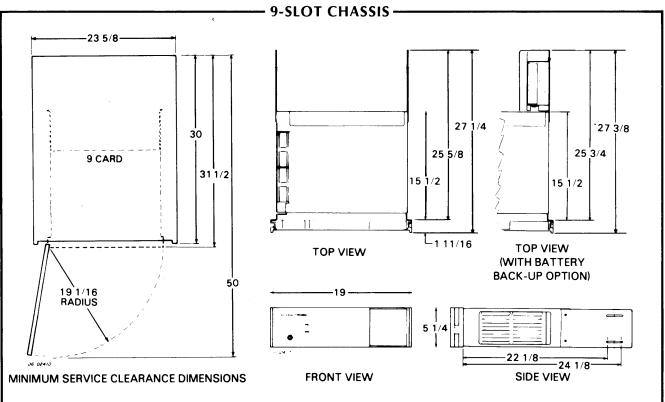

The microNOVA main chassis is a 19" rackmountable chassis available in both 9-slot and 18-slot configurations. The 9-slot chassis contains a 9-slot card frame and a power supply mounted side-by-side across the front of the chassis. The battery backup option, if present, is mounted on a support behind the power supply. The 18-slot chassis contains two 9-slot card frames mounted side-by-side across the front of the chassis, and a power supply mounted behind the left card frame. The battery backup option, if present, is mounted behind the right card frame. Both chassis have a front panel which swings aside to provide front access to the printed circuit boards. The front panel contains a power-on keylock switch, a rocker switch, three indicator lights, and a place to attach the hand-held console. I/O device cables connect directly to the I/O controller printed circuit boards at the rear of the card frames. Strain relief is provided for the I/O device cables at the rear of the chassis.

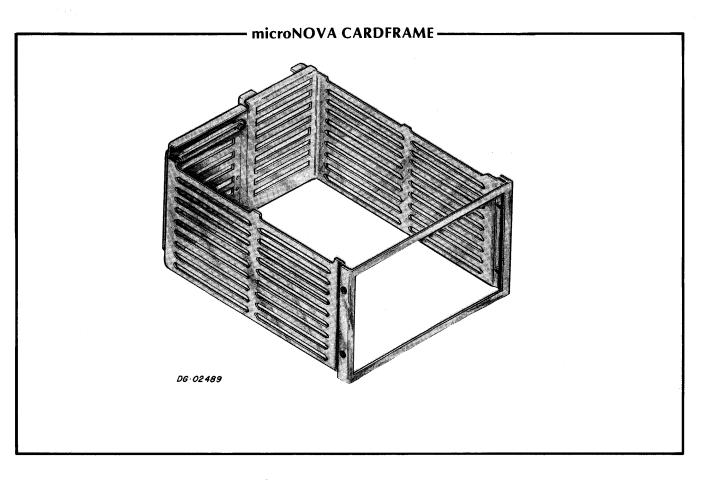

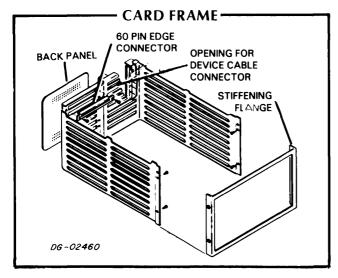

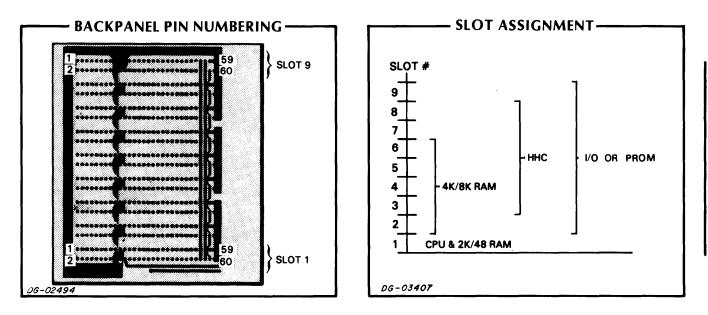

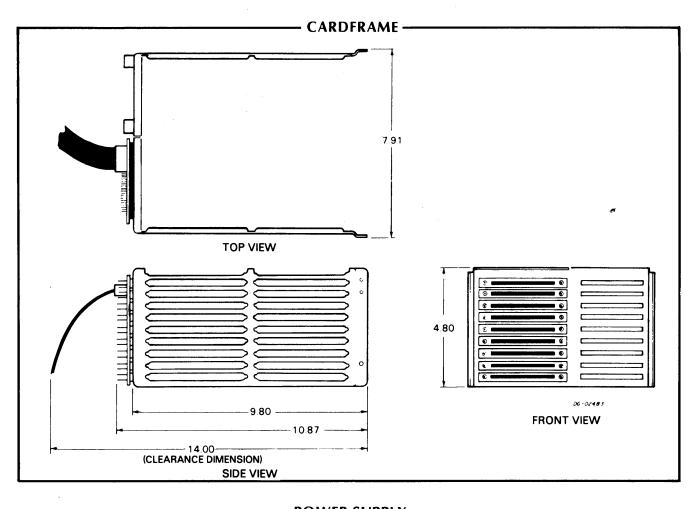

The microNQVA card frame assembly contains 9 slots for 7.5 inch wide printed circuit boards. The assembly consists of a stamped metal frame with stiffener and card guides, an etched backpanel, and female board connectors to the backpanel. The backpanel carries the memory bus signals and I/O bus signals to the boards mounted in the card frame. The memory bus signals are enabled only when a CPU and 2K/4K RAM board is mounted in the bottom slot of the card frame. The I/O bus signals can be chained from the CPU card frame to other card frames with an external I/O bus cable. Each slot has a metal retainer for attaching an I/O device cable connector. The card frame includes a DC power cable for connection to the power supply.

#### **Power Supply**

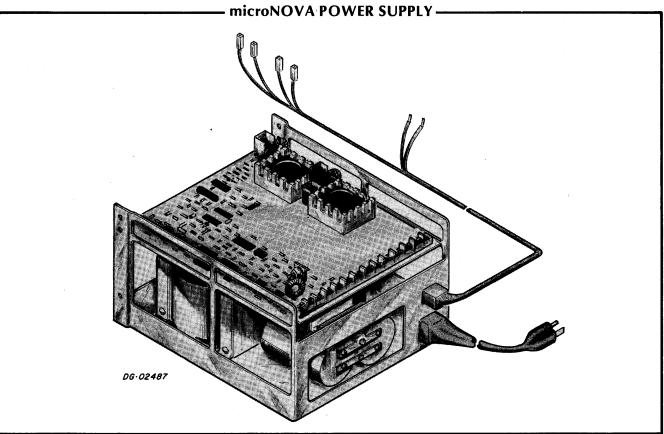

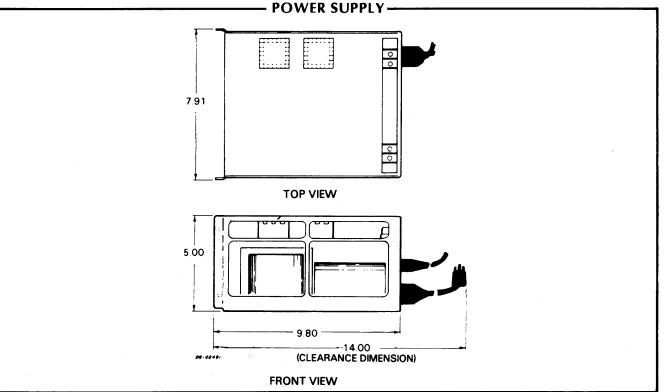

The power supply provides 18 amps at +5 volts dc, 2.5 amps at +15 volts dc, and 1.2 amps at -5 volts dc. This is sufficient power to support a fully-loaded 18-slot chassis containing standard microNOVA computer system boards. Low voltage switching regulators control the +5 volt and +15 volt portions of the power supply by independent pulse width modulation, and control the -5 volt portion of the power supply by variable pulse rate generation. An AC line filter, independent overvoltage and overcurrent sensing, and a power-fail monitor provide system protection. Any of the standard line voltages of 100 volts, 120 volts, 220 volts, or 240 volts in the frequency range of 47-63Hz may be used to drive the power supply; only the AC line cord is different for the different line voltages. The arrangement of the pins within the AC line cord/power supply connector selects the correct transformer taps for the line voltage being supplied.

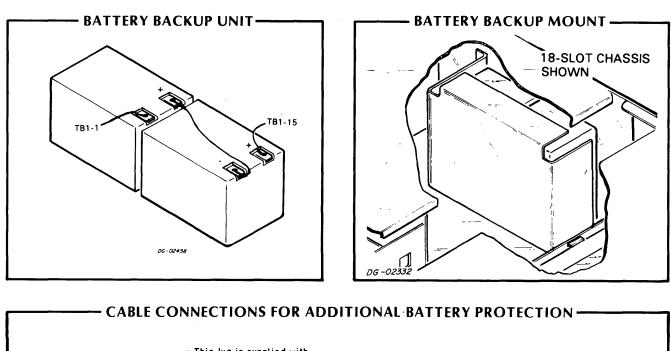

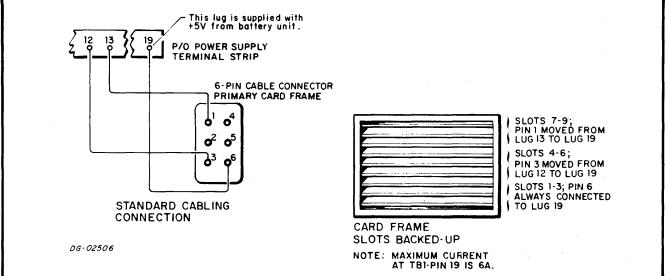

A battery backup option is available with the power supply to provide sufficient power to keep the CPU and up to 32K (using three 8K RAM's) of dynamic random-access memories refreshed for approximately 30 minutes during a power failure. Normal system operation is not intended. However, since the fans do not operate on battery, time is limited by temperature rise. At normal room temperature (25 C), the system is typically refreshed for approximately 20 minutes before the thermal circuit shuts down the system.

The battery backup option consists of two 12-volt battery packs connected in series, battery switchover circuitry, and battery recharge circuitry.

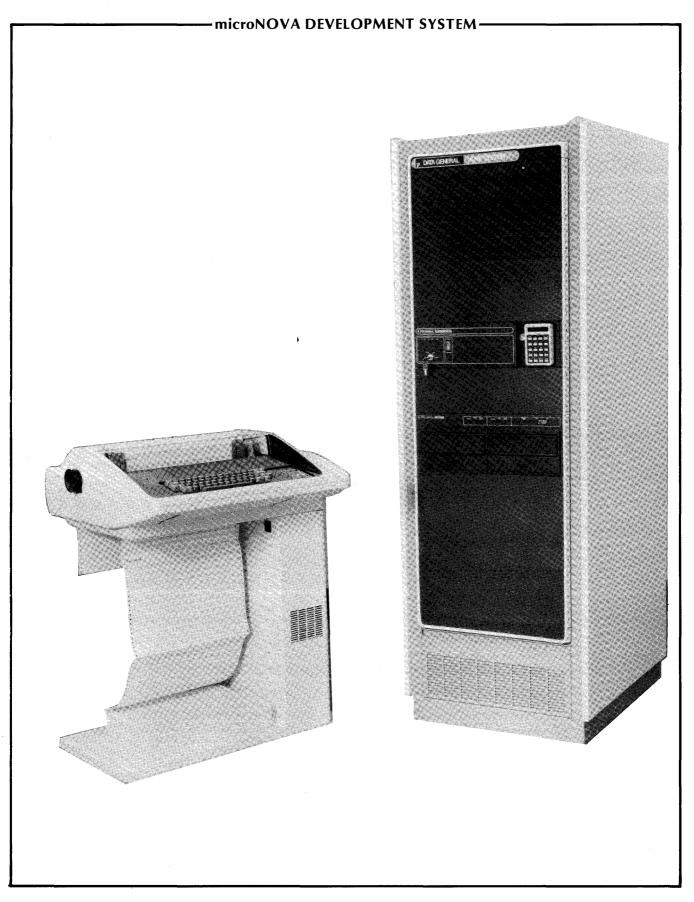

## PACKAGED SYSTEMS

A microNOVA computer system can be purchased in any one of several packaged system configurations. The CPU and 4K RAM board can be purchased with either a 9-slot or 18-slot chassis. In addition, a complete microNOVA development system can be purchased, where the development system includes a CPU, 16K RAM, an 18-slot chassis with the battery backup option, a hand-held console subsystem, a dual diskette subsystem, a box of 10 diskettes, an asynchronous interface board, either an ASR33 or KSR35 Teletype<sup>®</sup>, a 72" equipment cabinet with filler panels, and all applicable system cabling.

The microNOVA development system is fully supported by Data General software. This software includes the diskette-based Disc Operating System (DOS), FORTRAN IV with real-time extensions and library routines, an editor, a macro assembler, a relocatable loader, and a symbolic debugger.

Teletype<sup>®</sup> is a registered trademark of Teletype Corporation, Skokie, Illinois. All references to teletypes in this manual shall apply to this mark.

#### **CODING AIDS**

In the descriptions of the separate instructions, the general form in which the instruction is coded in assembly language is given along with the instruction format and the description of the instruction. The general form in which an instruction may be coded has the following format:

#### MNEMONIC loptional mnemonics | OPERAND STRING

The mnemonic must be coded exactly as shown in the instruction description. Some instructions have optional mnemonics that may be appended to the main mnemonic if the option is desired. The operand string is made up of the operands for the given instruction.

Square brackets "[]" or "[]" along with boldface- and italic-printed symbols are used in this manual to aid in defining the instructions. These conventions are used to help describe how an instruction should be written so that it can be recognized by the assembler and translated into the correct binary, or machine language, representation. Their general definition is given below.

- I, I Square brackets indicate that the enclosed symbol is an optional operand or mnemonic. The operand enclosed in the brackets (e.g., *l,skipl*) may be coded or not, depending on whether or not the associated option is desired.

- **BOLD** Operands or mnemonics printed in boldface must be coded exactly as shown. For example, the mnemonic for the MOVE instruction is coded MOV.

*italic* Operands or mnemonics printed in italics require a specific substitution. Replace the symbol with the number of a desired accumulator, or address, or with a user-defined symbol that the assembler recognizes as a specific name, address, number, or mnemonic.

The following abbreviations are used throughout this manual:

AC = Accumulator

ACS = Source Accumulator

ACD = Destination Accumulator

F = Flag Control Function

When describing the format or a word involved in an information transfer between the computer and an I/O device, the various fields and bits in the word are labeled with names descriptive of their functions. Bits in the word which are not used by the I/O device controller are shaded. Shaded bits are ignored on output and are undefined on input.

#### **RELATED MANUALS**

Two other manuals describe portions of the microNOVA computer family. The Technical Reference for microNOVA Integrated Circuits (DGC no. 014-000074) describes the major integrated circuits which form the basis of a microNOVA computer system, including detailed timing diagrams and electrical specifications for each integrated circuit. The Programmer's Reference Manual for microNOVA Computers (DGC no. 015-000050) describes the instruction set of the microNOVA computers.

**Rev 03**

## SECTION II CPU AND 2K/4K RAM BOARD

The microNOVA CPU board is an LSI minicomputer on a single 7.5 by 10.4 inch printed circuit board; it contains a complete, Data General NOVA-line, 16-bit word length, central processor in a single 40-pin package, and includes a real-time clock, Power Fail/Auto-restart, plus provision for automatic program load and on board console options. The board contains all support and interface circuits needed to connect the processor to separate, external, I/O and memory buses and to a turnkey console. It also contains 2,048 or 4,096 16-bit words of 960ns read-write memory (RAM). By itself, the CPU board can be integrated into a variety of special applications; combined with other microNOVA system pieces, it is the basis of a complete microprocessor-based computer system.

## **OVERVIEW AND INTRODUCTION**

The quality and power of a general purpose, microprocessor-based, computer system depends to a large measure on: i) the flexibility of its instruction set and the power of its central processing unit (CPU); ii) the availability of utility and development software; iii) the type and structure of the information paths into and out of the CPU; and iv) the size and power needs of the pieces that make up the system.

Data General's microNOVA CPU board executes the proven NOVA (NOVA 3) instruction set. It is a powerful, flexible, instruction set that combines high speed, multiple operation, fixed point, logical operations with hardware multiply/divide, hardware PUSH/POP stack, and a tightly optimized I/O handling capability. Most importantly, it is an instruction set for which Data General has already developed extensive software. This means that users can develop and optimize new applications software on any NOVA line computer system with all the resources available in proven Data General operating systems. compilers, run-time libraries, and peripherals.

The microNOVA CPU board exchanges information with memory and peripherals over two independent information transfer paths: the memory bus and the I/O bus. The CPU board contains a transceiver and control buffers for the memory bus; a 16-bit wide, parallel, synchronous, TTL-level bus by which the central processor communicates with microNOVA memory boards, or with special customer-designed memories. The board also contains the drivers and control buffers for a 2-bit wide, differential, serial I/O bus by which the central processor communicates with microNOVA peripherals or customer-designed I/O interfaces containing the microNOVA IOC.

The microNOVA CPU is packaged as a complete minicomputer on a single 7.5 by 10.4 inch printed circuit board. Built around a single-chip microprocessor that is designed and fabricated by Data General's semiconductor division, the CPU board is compact, and it easily lends itself to special applications when used alone, or when it is combined with other pieces in the growing microNOVA family of computers.

## SUMMARY OF CHARACTERISTICS

| ······································ |                                                  |                       |

|----------------------------------------|--------------------------------------------------|-----------------------|

| CENTRAL PROCESSO                       | DR                                               |                       |

| Operations:                            | Instruction Execution                            |                       |

|                                        | Fixed Point Arithm                               |                       |

|                                        | Logical Operations<br>Stack Manipulation         |                       |

|                                        | Program Flow Alte                                |                       |

|                                        | Input/Output                                     |                       |

| }                                      | Interrupts                                       |                       |

|                                        | Power Fail/Auto-re                               | estart                |

|                                        | Real-time Clock                                  |                       |

|                                        | Stack Overflow                                   |                       |

|                                        | External                                         |                       |

|                                        | Data Channel Transfer                            |                       |

|                                        |                                                  | conds/16-bit word     |

|                                        | Output: 5.8 micro                                | seconds/16-bit word   |

|                                        | Automatic Program Lo                             | ad (optional)         |

|                                        | Memory Refresh (hidde                            | en)                   |

| Registers:                             | 4 16-bit accumulators                            |                       |

|                                        | 1 15-bit stack pointer                           |                       |

|                                        | 1 15-bit frame pointer                           |                       |

|                                        | 1 15-bit program coun<br>1 interrupt enable flag | ter                   |

|                                        | 1 real-time clock enabl                          | e flaq                |

|                                        | 1 carry bit                                      |                       |

|                                        | 1 stack overflow flag                            |                       |

| Buses:                                 | Memory                                           |                       |

|                                        | 16 address/data l                                | ines                  |

|                                        | 4 control signals                                |                       |

|                                        | I/O                                              | · · · ·               |

|                                        | •                                                | ronous, bidirectional |

|                                        | I/O clock                                        |                       |

|                                        | Master clock                                     |                       |

|                                        | 2 request lines<br>2 priority lines              |                       |

|                                        | 1 clear line                                     |                       |

|                                        | Maximum total le                                 | ngth: 100 ft. (30.5m) |

| MEMORY                                 |                                                  |                       |

| Memory Type:                           | Dynamic MOS N-chan                               | nel RAM.              |

|                                        | <b>,</b>                                         |                       |

| Board Capacity:                        | 2,048 or 4,096 16-bit                            | t words.              |

| Cycle Time:                            | Read                                             | 960ns.                |

|                                        | Write                                            | 960ns.                |

|                                        | Read/Modify/Write                                | 1920ns.               |

|                                        | Refresh                                          | 960ns.                |

| Maximum                                | 1.8432 milliseconds.                             |                       |

| Refresh Period:                        |                                                  |                       |

| Board Dimensions:                      | 7.5 x 10.4 in. (19 x 26                          | cm.)                  |

| Maximum                                | al a                                             |                       |

| Operating                              | 131°F (55°C)                                     |                       |

| Temperature:                           | ·                                                |                       |

|                                        |                                                  |                       |

## **BLOCK DIAGRAM**

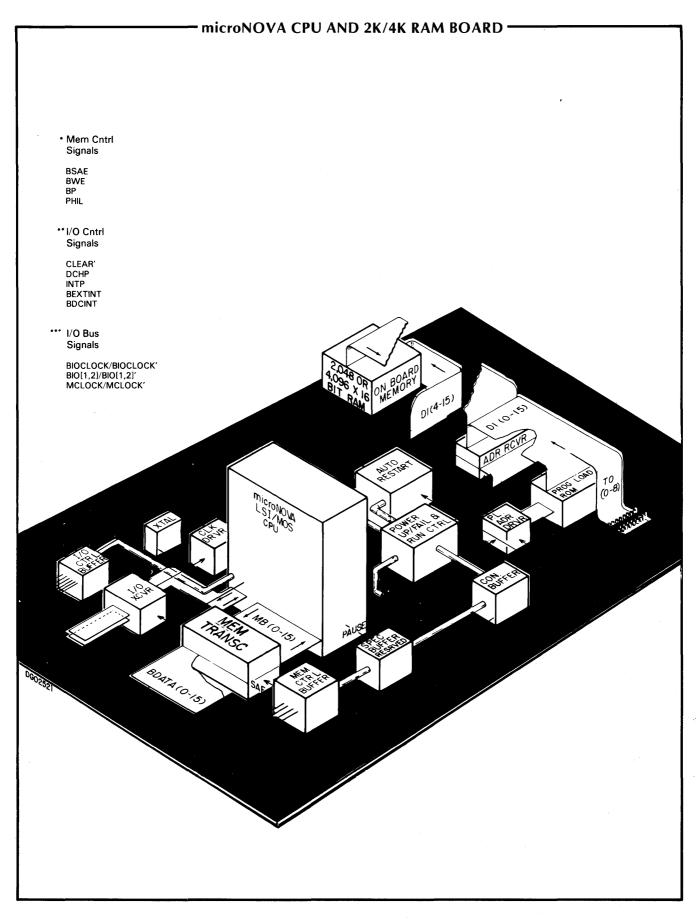

The block diagram on the opposite page shows the principal components plus the data and control paths of a microNOVA CPU board. This board contains a microNOVA microprocessor (CPU), 2,048 or 4,096 words of dynamic read-write memory (RAM), and power fail and restart controls. It has connections to the memory and I/O buses and front panel. The board may also contain the automatic program load option.

The CPU board contains two principal data paths and six functional blocks. These are:

CPU to memory bus CPU to I/O bus Power up/fail and run control On board memory Special function jumpers CPU and front panel controls Auto-restart Automatic program load option

The first five items in the above list encompass the basic structure of the CPU board. The front panel controls, auto-restart, and the program load option take effect by gaining, on an exceptional basis, overriding control over that basic structure.

#### **CPU to Memory Bus**

Communication between the processor and memory take place along a memory bus. The memory bus operates at TTL levels; it is a wired OR, half duplex, 16-bit wide, address and data path. The operations which take place on it occur synchronously, under CPU direction. Such operations include Read memory, Write memory, Read-Modify-Write memory, and Refresh memory. All information that moves on the memory bus does so in bit-parallel fashion, 16-bits at a time.

A 16-bit memory transceiver and the memory control buffer interface the CPU integrated circuit to the memory bus. Four memory control signals direct the flow of information along the 16-bit bi-directional address and data path.

The CPU's memory interface supports the flow of information between the central processor's memory port and the microNOVA memory bus. The protocols by which the CPU communicates with memory are described in the Technical Reference for microNOVA Integrated Circuits (DGC no. 14-000074).

#### **CPU to I/O Bus**

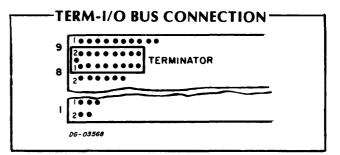

Communication between the processor and peripherals take place along the I/O bus. The microNOVA I/O bus is a bidirectional, 2-bit, synchronous data path from the CPU to any device that needs direct program control or data channel service. It consists of 9 signals, four of them differential. All information is placed on and read from two differential lines in conjunction with an I/O clock signal carried on a third differential line; the remaining differential lines carry the system clock. The single-ended control lines include a reset signal, plus priority and request lines for program interrupt and data channel service. Information moves on the bus in bit-serial fashion, 2 bits at a time, with a two-bit wide coded header and 16 bits of data. The I/O bus is carried up the chassis backpanel and may extend a total of 100 feet from the CPU using 16-wire ribbon cable.

A CPU I/O transceiver, consisting of 4 differential I/O bus ports, includes 3 bidirectional lines (2 data, 1 I/O clock) and 1 system clock driver. A single-ended clear line completes the transceiver I/O interface. The master clock for a microNOVA computer system is derived from the crystal oscillator connected to the CPU's I/O transceiver.

The CPU's I/O interface supports the flow of information between the central processor's I/O port and the microNOVA I/O bus. The protocols by which the CPU communicates with peripherals are described in the technical reference cited above.

#### Power Up/Fail and Run Control

The CPU board includes control circuits to direct the CPU's operation when power is first applied to the microprocessor, while it its running, and as power drops. These circuits include the a power up/fail and run control, and a CPU clock driver.

The power up monitor holds the CPU in a well defined state and resets the computer during a cold startup. It then allows the processor to start, when directed to do so, by the console controls or self-starting options. The power up requirements of the microNOVA CPU are described in the technical reference cited above. The power fail monitor senses the power beginning to fail and alerts the processor, via a power fail interrupt, that there is a guaranteed 2 milliseconds of operation before power actually fails.

The CPU clock driver amplifies the system master clock which is derived from a crystal oscillator connected to the I/O bus transceiver. It provides precise, non-overlapping clock signals required to run the processor.

#### **On Board Memory**

The CPU board holds an entire read-write memory module which connects directly to the microNOVA memory bus. The memory consists of one bank of dynamic RAM with 2,048 or 4,096 16-bit words, 16-bit wide data in and data out paths, a 12-bit address path, four memory control lines, and a 16-bit memory transceiver. Memory address jumpers assign the 4K memory address boundary in which the on board memory will operate within the total system. Because of hardware restrictions, it is not recommended that the on board memory be assigned the highest 4K position.

The construction of the on board memory is similar to that of other RAM modules for the microNOVA systems. The flow of information within the module and also between it and the memory bus is described in section III.

#### **Special Function Jumpers**

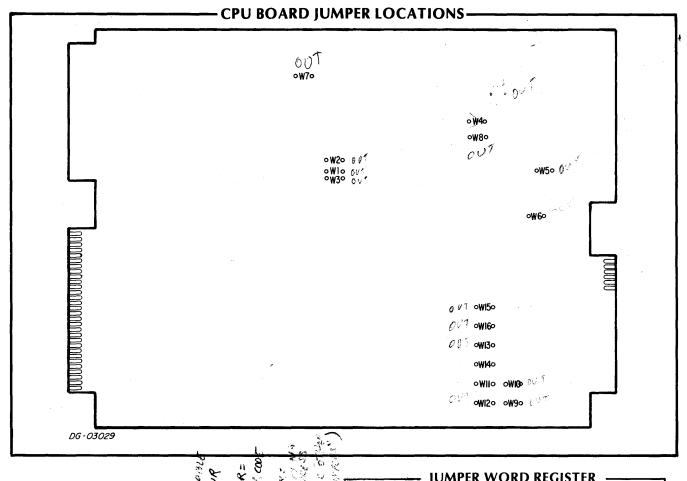

The board utilizes a Jumper Word Register to configure two types of automatic operation. They are:

- 1. Starting Address/Auto-Restart

- 2. Automatic Program Load (APL)

Inserting jumper W4 enables the Jumper Word Register.

Inserting a jumper in W5 or W6 controls the function of the Jumper Word Register. If a jumper is inserted in W5, the Jumper Word Register becomes a device code for the Automatic Program Load option. If a jumper is inserted in W6, the Jumper Word Register becomes a starting address used by the start functions and Auto-Restart. W5 and W6 should not be both inserted at any time.

Inserting jumper W7 disables Auto-Restart after a power failure if no battery power is present (i.e., battery backup not provided or batteries are discharged). This jumper is normally inserted if battery backup is not installed, or a restart program in PROM is not utilized.

Inserting jumper W8 enables 64 words of ROM associated with addresses  $077700-077777_8$  for the APL option.

Refer to sheet II-10 for chart configurations of these jumpers.

#### **CPU and Console**

The CPU board includes a control circuit and signal buffer for the switches and indicators of the microNOVA turnkey console; the board may optionally have a group of switches and indicator lights for console functions.

Signals from the console switches and indicators pass through the console buffer to the power up/fail and run monitor, to the program load address driver, and to the auto-restart monitor to start and continue functions of the board.

#### Auto-restart

Auto-restart includes a circuit that monitors the conditions of a backup battery, the position of the LOCK switch of the turnkey console, and the configuration of the setup jumpers. When power returns after a power failure, this circuit can initiate an automatic restart by gaining control over selected I/O and memory control lines.

#### Automatic Program Load Option

When the automatic program load option is installed, it includes a 16-bit information path through the CPU memory transceiver to the memory bus, control lines to the console buffer and the power up/fail and run control, a 64 word ROM, and a 6-bit address driver. When an automatic program load is initiated, the option gains control over selected I/O and memory control lines. The CPU executes a series of instructions stored in the program load ROM, and transfers the microNOVA bootstrap program from there to memory locations  $2-37_8$ .

### PROGRAMMING

The microNOVA CPU processes information one word at a time, where a word is 16 bits in length. The CPU has four accumulators which are also 16 bits in length and are used for arithmetic and logical operations. Furthermore, two of the accumulators can be used as index registers. Memory can be addressed either directly or by using indirect addressing. Chains of indirect addresses may be up to eight addresses long.

The instruction set for the CPU contains instructions that perform fixed point arithmetic and logical operations between accumulators, transfer of operands between accumulators and memory, transfer of program control, stack manipulations, I/O operations, and processor control operations. All instructions are one word in length. The instruction set of the microNOVA computer is similar to the instruction set of the NOVA line of computers (see Appendix for greater detail).

The table on the following pages summarizes the instruction set of the microNOVA computer. For a more detailed description of the instructions, consult the Programmer's Reference Manual for microNOVA Computers (DGC no. 015-000050).

## FIXED POINT ARITHMETIC

#### Load Accumulator

| LDA | ac.l@ | ldisplacement[,index] |

|-----|-------|-----------------------|

|-----|-------|-----------------------|

| 0 | 0 | 1 | A | c | @ | IN | DEX |   |   | DISPLACEMENT |    |    |    |    |    |  |

|---|---|---|---|---|---|----|-----|---|---|--------------|----|----|----|----|----|--|

| 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7   | 8 | 9 | 10           | 11 | 12 | 13 | 14 | 15 |  |

#### Store Accumulator

| <b>STA</b> ac,[@]displacement[ | l,index] |

|--------------------------------|----------|

|--------------------------------|----------|

| 0 | 1 | 0 | A | c | @ | IND | DEX |   |   | DIS | PLA | CEM | ENT |    |    |

|---|---|---|---|---|---|-----|-----|---|---|-----|-----|-----|-----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8 | 9 | 10  | 11  | 12  | 13  | 14 | 15 |

#### Add

ADD [c][sh][ # ] acs,acd[,skip]

| 1 | A | C S | A | D | 1 | 1 | 0  | S | н | 0  | -  | #  |    | SKIP |    |  |

|---|---|-----|---|---|---|---|----|---|---|----|----|----|----|------|----|--|

| 0 | 1 | 2   | 3 | 4 | 5 | 6 | .7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |  |

#### Subtract

**SUB** [c][sh][ # ] acs,acd[,skip]

| 1 | AC | <u>s</u> | AC | D | 1 | 0 | 1 | SI | Η | 0  | 2  | #  |    | SKIP |    |

|---|----|----------|----|---|---|---|---|----|---|----|----|----|----|------|----|

| 0 | 1  | 2        | 3  | 4 | 5 | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

#### Negate

NEG [c][sh][ # ] acs,acd[,skip]

| ſ | 1 |   | A | C <b>S</b> | A | D | 0  | 0 | 1 | S | Н | (  | 2  | #  |    | SKIP |    |

|---|---|---|---|------------|---|---|----|---|---|---|---|----|----|----|----|------|----|

| 7 | 0 | Ţ | 1 | 2          | 3 | 4 | 5. | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

#### **Add Complement**

ADC [c][sh][ # ] acs,acd[,skip]

| 1 | Γ | AC | S | A | D | 1 | 0 | 0 | S | Н | (  | -<br>- | #  |    | SKIP |    |

|---|---|----|---|---|---|---|---|---|---|---|----|--------|----|----|------|----|

| 0 | Γ | 1  | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11     | 12 | 13 | 14   | 15 |

#### Move

**MOV** [c][sh][#] acs,acd[,skip]

| 1 | A | CS . | A | D | 0 | 1 | 0 | SI | 1 | 0  | 2  | #  |    | SKIP | 2  |

|---|---|------|---|---|---|---|---|----|---|----|----|----|----|------|----|

| 0 | 1 | 2    | 3 | 4 | 5 | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

#### Increment

INC [c][sh][ # ] acs,acd[,skip]

| _        |       |            |   |    |   |       |     |       |   |    |      |    |    |         |          |

|----------|-------|------------|---|----|---|-------|-----|-------|---|----|------|----|----|---------|----------|

| 1        | ۸(    | ~ <b>c</b> |   | 'n | 0 | 1     | 1   | 51    | - | (  | -    | #  |    | SKIP    |          |

| 111      | 1 ~ ` |            |   | .0 |   |       | . • | 31    | • |    | -    | 1  | l  | 3617    | - 1      |

| <u> </u> |       |            |   |    |   | · · · | -   | · _ · | - | 10 |      | 12 |    | · · · · | <u> </u> |

| 0        | 1 1   | 2          | 3 | 14 | 5 | 6     | 17  | 8     | 9 | 10 | - 11 | 12 | 13 | 14      | 15       |

#### **Multiply**

#### MUL

| ſ | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Divide

#### DIV

| Ō | 1  | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|----|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 11 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

## LOGICAL OPERATIONS

#### Complement

COM [c][sh][ # ] acs,acd[,skip]

| 1 | A | CS | A | D | 0 | 0 | 0 | SI | 1 | Ċ  | 2  | #  |    | SKIP |    |

|---|---|----|---|---|---|---|---|----|---|----|----|----|----|------|----|

| 0 | 1 | 2  | 3 | 4 | 5 | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

#### And

#### AND [c][sh][ # ] acs,acd[,skip]

| ſ | 1 |   | A | CS . | A | D | 1 | 1 | 1 | SF | 1 | 0  | 2  | #  |    | SKIP |    |

|---|---|---|---|------|---|---|---|---|---|----|---|----|----|----|----|------|----|

| Ĵ | 0 | Г | 1 | 2    | 3 | 4 | 5 | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

## **STACK MANIPULATION**

#### **Push Accumulator**

PSHA ac

| 0 | 1 | 1 | A | Ċ | 0 | 1 | 1   | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|-----|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | ] 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### **Pop Accumulator**

#### POPA ac

| 0 |   | 1 | 1 | A | C | 0 | 1 | 1 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | Т | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Save

#### SAV

| 0 | 1  | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|----|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 11 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### **Move To Stack Pointer**

#### MTSP ac

| 0 | 1 | 1 | A | c | 0 | 1 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 6 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Move To Frame Pointer

MTFP ac

#### **Move From Stack Pointer**

MFSP ac

| 0 | 1 | 1 | A | C | 0 | 1 | 0 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### **Move From Frame Pointer**

#### MFFP ac

| 0 | 1 | 1   | A | C | 0 | 0 | 0 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|-----|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | - 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

## **PROGRAM FLOW ALTERATION**

Jump

#### JMP [@]displacement[,index]

| 0 | 0 | 0 | 0 | 0 | @ | IND | DEX |   |   | DIS | PLAC | EM | ENT |    |    |

|---|---|---|---|---|---|-----|-----|---|---|-----|------|----|-----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8 | 9 | 10  | 11   | 12 | 13  | 14 | 15 |

#### **Jump To Subroutine**

JSR [@]displacement[,index]

| 0 | 0 | 0 | 0 | 1 | @ | IN | DEX |   |   | DIS | PLA | CEM | ENT |    |    |

|---|---|---|---|---|---|----|-----|---|---|-----|-----|-----|-----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7   | 8 | 9 | 10  | 11  | 12  | 13  | 14 | 15 |

#### **Increment And Skip If Zero**

**ISZ** [@]displacement[,index]

| 0 | 0 | ) | 0 | 1 | 0 | @ | INE | DEX |   |   | DIS | PLAC | CEM | ЕМТ |    |    |

|---|---|---|---|---|---|---|-----|-----|---|---|-----|------|-----|-----|----|----|

| 0 | 1 | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8 | 9 | 10  | 11   | 12  | 13  | 14 | 15 |

#### **Decrement And Skip If Zero**

DSZ [@]displacement[,index]

| 0 | 0 | 0 | 1 | 1 | @ | INE | DEX |   |   | DIS | PLA | CEM | ENT |    |    |

|---|---|---|---|---|---|-----|-----|---|---|-----|-----|-----|-----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8 | 9 | 10  | 11  | 12  | 13  | 14 | 15 |

#### Return

#### RET

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Trap

#### **TRAP** acs,acd,trap number

| 1 | AC | 25 | AC | D |   | T | RAP | N | JMB | ER |    | 1  | 0  | 0  | 0  |

|---|----|----|----|---|---|---|-----|---|-----|----|----|----|----|----|----|

| 0 | 1  | 2  | 3  | 4 | 5 | 6 | 7   | 8 | 9   | 10 | 11 | 12 | 13 | 14 | 15 |

## **INPUT/OUTPUT**

#### No I/O Transfer

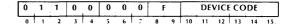

NIO [f] device

#### Data In A

DIA [f] ac, device

| 0 | 1 | 1 | A | C | 0 | 0 | 1 |   | F |    | DE | VICE | со | DE |    |

|---|---|---|---|---|---|---|---|---|---|----|----|------|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13 | 14 | 15 |

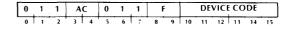

#### Data In B

**DIB** [f] ac, device

#### Data In C

**DIC** [f] ac, device

| • | 0 | 1 | 1 | A | C | 1 | 0 | 1 | i | F |    | DE | VICE | со | DE |    |

|---|---|---|---|---|---|---|---|---|---|---|----|----|------|----|----|----|

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13 | 14 | 15 |

#### Data Out A

| DOA ( | ti ac | ,device |

|-------|-------|---------|

| ſ | 0 | 1 | 1 | A | C | 0 | 1 | 0 | F |   |    | DE   | <b>VICE</b> | со | DE |    |

|---|---|---|---|---|---|---|---|---|---|---|----|------|-------------|----|----|----|

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | - 11 | 12          | 13 | 14 | 15 |

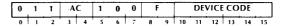

#### Data Out B

DOB [f] ac, device

#### Data Out C

**DOC** *[f]* ac, device

| ſ | 0 | 1 | 1 | A | C | 1 | 1 | 0 | F |   |    | DE | VICE | со | DE |    |

|---|---|---|---|---|---|---|---|---|---|---|----|----|------|----|----|----|

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13 | 14 | 15 |

#### I/O Skip

**SKP** *[t]* device

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | - |    | DE | VICE | co | DE |    |

|---|---|---|---|---|---|---|---|---|---|---|----|----|------|----|----|----|

| 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13 | 14 | 15 |

## **CENTRAL PROCESSOR FUNCTIONS**

Interrupt Enable

INTEN

NIOS CPU

0

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Interrupt Disable

INTDS

NIOC CPU

| [ | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1  | 1  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Interrupt Acknowledge

INTA ac DIB [f] ac, CPU

0

1

1

AC

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

#### Mask Out

MSKO ac

DOB [f] ac, CPU

| 0 | 1 | 1 | 1 | A | C | -1 | 0 | 0 | F |   | 1  | 1  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|---|----|---|---|---|---|----|----|----|----|----|----|

| _ |   | 1 | 2 | 3 | 4 | 5  | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Reset

IORST

DOA [f] 0,CPU

| 0 | 1 | 1 | A | C | 0 | 1 | 0 | I |   | 1  | 1  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Halt

HALT

DOC 0,CPU

| 0 | 1 | 1 | A | c | 1 | 1 | 0 | F   | 1  | 1  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|---|---|---|-----|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### **CPU Skip**

SKP [t] CPU

| 0 | 1 | 1 | 0 | 0 | - 1 | 1 | 1 | Т   | 1  | 1  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|-----|---|---|-----|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5   | 6 | 7 | 8 9 | 10 | 11 | 12 | 13 | 14 | 15 |

## **REAL TIME CLOCK**

**Real-time Clock Enable**

RTCEN

DOA [f] 2,CPU

| 0        | 1 | 1 | 1 | 0 | 0 | 1 | 0              | F   | 1  | 1  | 1  | 1  | 1  | 1  |

|----------|---|---|---|---|---|---|----------------|-----|----|----|----|----|----|----|

| <b>5</b> | 1 | 2 | 3 | 4 | 5 | 6 | <del>,</del> , | 8 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Real-time Clock Disable

RTCDS

DOA (f) 1,CPU

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | F |   | 1  | 1  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| · · · · · · · · · · · · · · · · · · · | 35   | n and a second | 25 | E B |                   | 6   |     | $\dot{\lambda}$ |     | <u>)</u> | ι κ | Ą   |

|---------------------------------------|------|----------------|----|-----|-------------------|-----|-----|-----------------|-----|----------|-----|-----|

| JUMPER NUMBER                         | W4   | W5             | W6 | W8  | W9                | W10 | W11 | W12             | W13 | W14      | W15 | W16 |

|                                       | IN   | IN             |    | IN  | IN FOR<br>DCH DEV |     | DS0 | DS1             | DS2 | DS3      | DS4 | DS5 |

| STARTING ADDRESS                      | IN   | Ουτ            | IN | OUT | A0                | A1  | A2  | A3              | A4  | A5       | A6  | A7  |

| HHC OR CONSOLE DEBUG OPTION           | ίουτ |                |    |     |                   |     |     |                 |     |          |     |     |

| <i>DG-03395</i> NOTE:                 |      |                |    |     |                   |     |     |                 |     |          |     |     |

1. DS[0-5] AND A[0-7] INSERT JUMPER TO SPECIFY 1.

2. A[8-15] = 00 000 001.

JUMPER WORD ADDRESS

| ADDRESS             | INSERT JUMPER |

|---------------------|---------------|

| 077776 <sub>8</sub> | W5            |

| 077777 <sub>8</sub> | W6            |

If W5 is inserted, memory address  $077776_8$  shall contain the contents of the Jumper Word Register. with the device address of the APL option.

If W6 is inserted, memory address 0777778 shall contain the contents of the Jumper Word Register with the starting address of Auto-Restart.

Jumpers W1-W3 determine which 4K address group out of 32K is resident on the CPU board. Because of hardware restrictions, it is not recommended that on board memory be assigned the highest 4K position.

#### **ADDRESS SELECTION JUMPERS**

|                                   | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 1999 - C. | 1.1.2 |

|-----------------------------------|----------------------------------------|-----------|-------|

| BIT POSITIONS OF STARTING ADDRESS | 1.                                     | 2         | 3     |

| INSERT JUMPER TO SPECIFY 1        | W1                                     | W2        | W3    |

#### **OTHER JUMPERS**

| JUMPER             | FUNCTION                                                                                                                                                                 |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W4 004             | Insert jumper to enable jumper word register                                                                                                                             |

| w <sup>7</sup> ęúr | Insert jumper to disable auto-restart after a power failure if power is not supplied by battery back-up. <b>or</b> <i>REST, PROG, Nor IN</i> <sup>(SC</sup> <i>Ort</i> ) |

| W8 207             | Insert jumper to enable 64 words of local ROM associated with addresses 077700-077778.<br>Used for APL.                                                                  |

## SECTION III RANDOM ACCESS MEMORY BOARDS

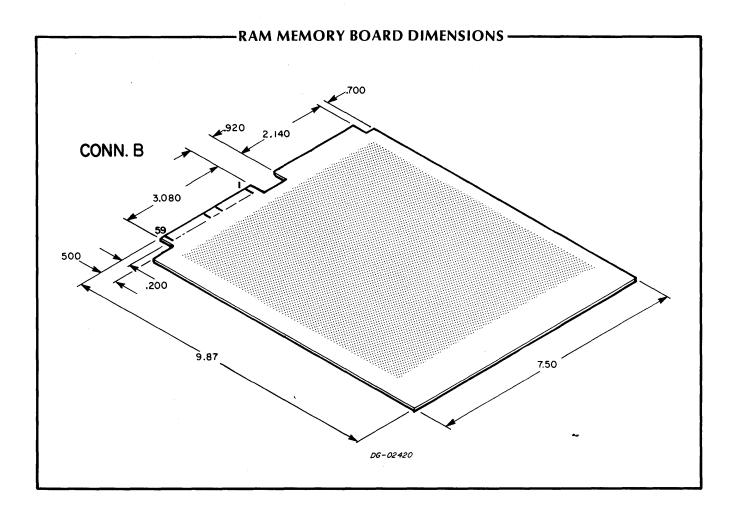

Data General's model 8572 and model 8573 random access memory (RAM) boards contain either 4K or 8K of dynamic MOS read/write memory and the circuitry to interface that memory to the microNOVA memory bus. Model 8572 contains 4,096 16-bit words and model 8573 contains 8,192 16-bit words of RAM. These RAM modules perform read, write, and refresh operations in 960ns. A read-modify-write operation can be performed in 1920ns.

## **OVERVIEW AND INTRODUCTION**

Random access memory (RAM) is a local storage medium whose contents can be read and modified, one word at a time. Dynamic MOS RAM is random access memory that has been constructed using metal-oxide semiconductor (MOS) technology. Dynamic MOS RAM must be refreshed at frequent intervals in order for its contents to be maintained.

The microNOVA 4K/8K MOS RAM board contains 4K or 8K 16-bit words of dynamic MOS random access memory. A microNOVA computer system can access up to 32K words of memory; all 32K words of memory may be RAM.

## **SUMMARY OF CHARACTERISTICS**

| Memory Type                         | Dynamic MOS N-channel RAM.                    |                                       |  |

|-------------------------------------|-----------------------------------------------|---------------------------------------|--|

| Board Capacity                      | 4,096 or 8,192 16-bit words.                  |                                       |  |

| Cycle Time                          | Read<br>Write<br>Read/Modify/Write<br>Refresh | 960ns.<br>960ns.<br>1920ns.<br>960ns. |  |

| Maximum<br>Refresh Period           | 1.8432 milliseconds.                          |                                       |  |

| Location<br>Requirement             | Within Slots 2-6                              | -                                     |  |

| Board Dimensions                    | 7.5 x 9.9 in. (19 x 24.9 cm.)                 |                                       |  |

| Maximum<br>Operating<br>Temperature | 131°F (55 C)                                  |                                       |  |

## **BLOCK DIAGRAM**

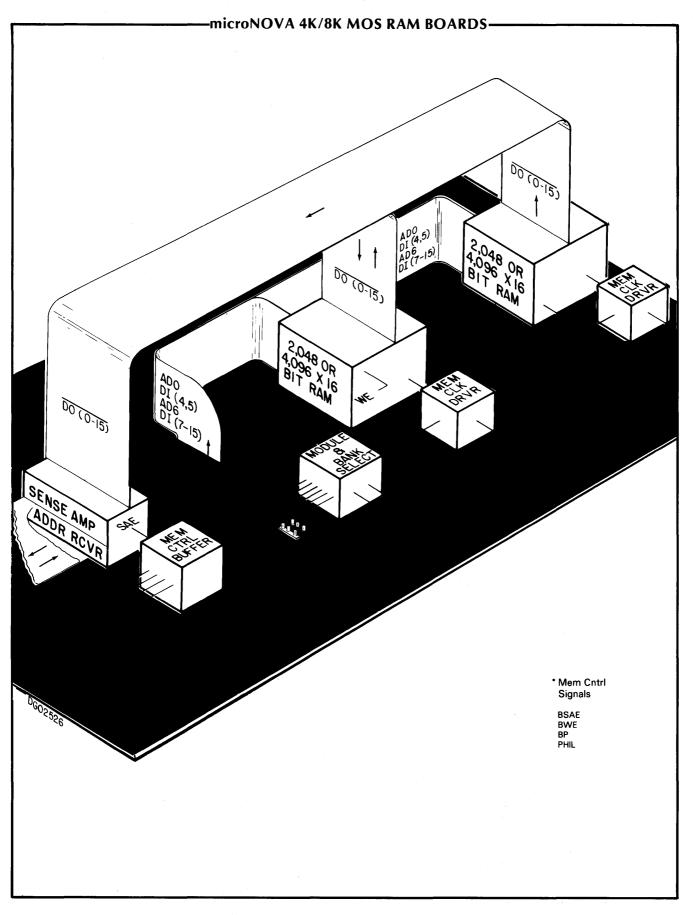

The block diagram on the opposite page shows the principal components plus the control and data paths of microNOVA RAM boards. The board is organized into two banks of dynamic RAM memory, each with 2,048 or 4,096 16-bit memory locations. The board contains clock drivers for each memory bank, an address selection/configuration network, a memory bus sense amplifier/bus driver, a control buffer, and address data paths for moving information within the board.

The memory address receivers and sense amplifier/bus drivers and memory control buffer connect the RAM board to the microNOVA memory bus. The protocols by which the microNOVA CPU communicates with memory are detailed in the Technical Reference for microNOVA Integrated Circuits (DGC no. 014-000074).

When an address appears on the memory bus at the start of a memory operation, the board and bank selection network enables the board if the address on the bus falls within the range of addresses assigned to the board by the placement of its starting address jumpers. The network enables the clock driver in the appropriate memory bank, and the twelve low-order bits of the address are driven onto the RAM address lines. The action taken next by the board depends on the type of memory operation to be performed. If the operation is a memory read, the memory control signals drive the contents of the addressed memory location onto the board's data out lines to the memory sense amplifier. If the RAM disable signal **PHIL** has not been asserted by a ROM board assigned to the same address, the memory bus driver places the 16-bit memory word on the memory bus.

If the operation is a memory write, the memory control signals drive the 16-bit word to be written in memory onto the the board's data in (DI) path and load it into the addressed memory location.

If the operation is a memory read-modify-write, the memory control signals first drive the contents of the addressed memory location onto the data out (**DO**) path and onto the bus if no ROM is assigned to the same address. The location read remains active until the new data for that address arrives on the bus, and moves onto the boards's data in path; then, the memory control signals load the new data into the memory location just read.

If the operation is a memory refresh, the memory control signals initiate a refresh operation simultaneously on 1/64 th of the memory; no data moves on either the data input or output paths.

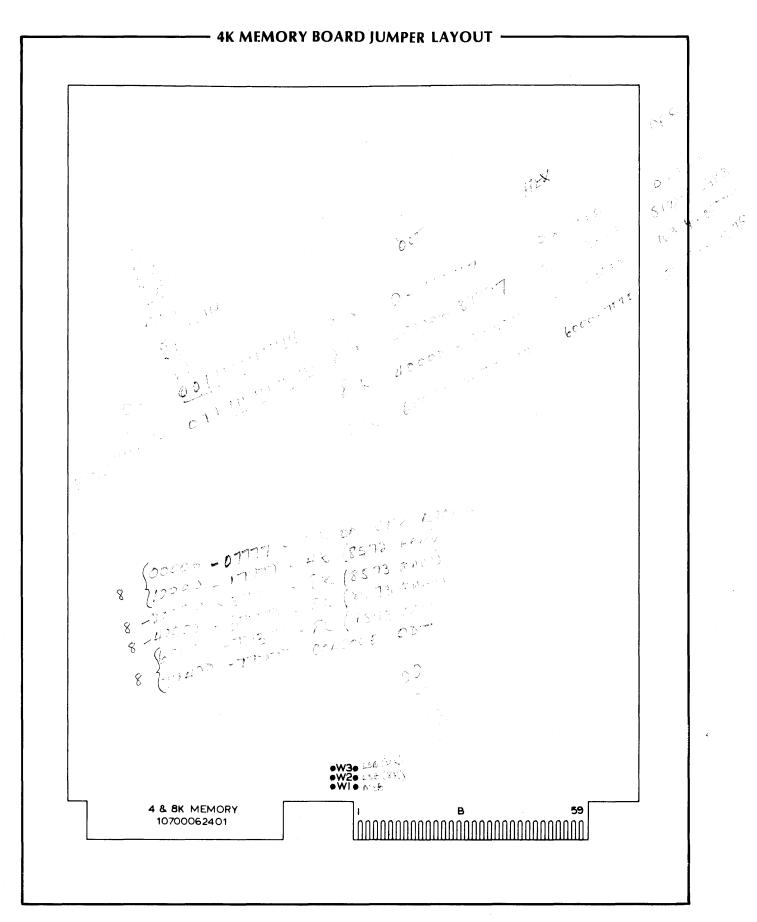

#### ADDRESS SELECTION JUMPERS

| BIT POSITIONS OF STARTING ADDRESS | 1  | 2  | 3  |

|-----------------------------------|----|----|----|

| INSERT JUMPER TO SPECIFY 1        | W1 | W2 | w3 |

\*Jumper W3 is ignored on the 8K RAM board.

The Address Selection Jumpers control the group selection of 4K/8K RAM memories on each board. System maximum is 32K. Jumper W1 is the MSB and W3 is the LSB for implementation of the address selection. For 8K group selection, jumper W3 is ignored.

This page intentionally left blank.

۱

## SECTION IV PROGRAMMABLE READ-ONLY MEMORY BOARDS

Data General's microNOVA read-only memories are programmable, 200ns, semiconductor, PROM boards containing from 512 to 4096 16-bit words of directly accessible memory. Any amount of PROM, up to the maximum system memory size of 32K words, may be placed in a microNOVA system; board starting addresses can be assigned to any 2K boundary in memory. PROM may overlay any alterable (RAM) memory locations, where a RAM/ROM priority line arbitrates memory conflicts in favor of ROM. ROM/ROM conflicts (e.g. 4K PROM at the top of memory conflicts with both the hand-held console and the console debug option) can be avoided by programming all ones in the conflicting locations in one of the memories.

### **OVERVIEW AND INTRODUCTION**

Certain programs and data contained in a computer system are never changed, but are used frequently enough to justify their being permanently located within the address space of the CPU. Read-only memory (ROM) provides a medium on which such information can be stored. The contents of a ROM location cannot be changed under program control while the ROM is in the address space of the CPU. However, since the contents of ROM cannot be changed, the information contained in ROM is protected from software and hardware malfunctions.

Some ROM is field programmable; that is, the contents of the ROM are initially all zeros or all ones, and the appropriate ones or zeros can be "programmed" or "burned" into the ROM after the memory is purchased. Such programmable ROM is called PROM.

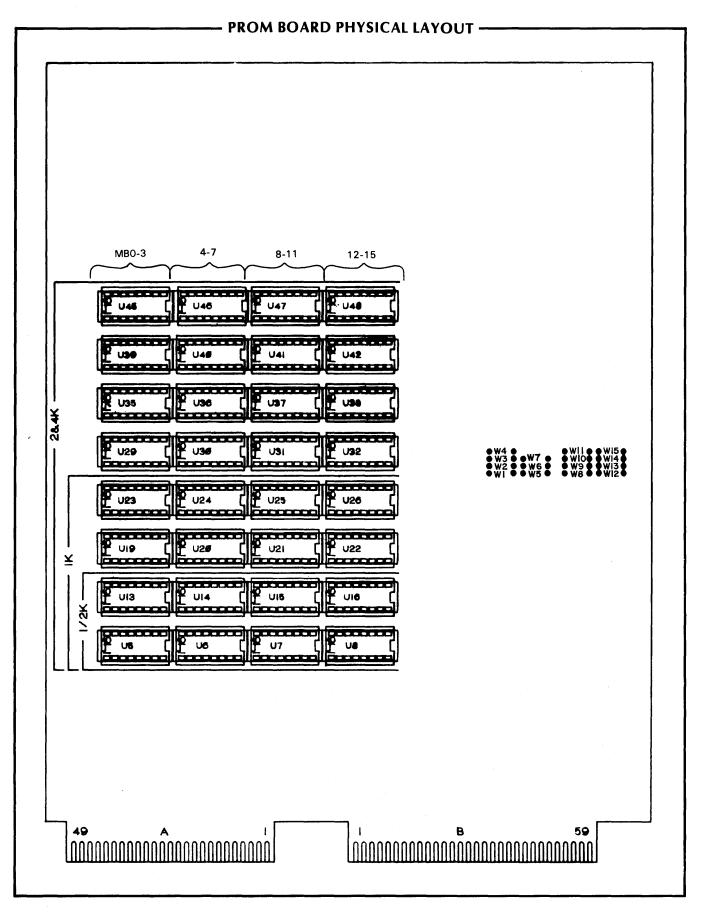

The microNOVA programmable read-only memory boards contain sockets for 512 to 4096 16-bit words of PROM available in 256 by 4 bit or 512 by 4 bit packages. The contents of the memory on a microNOVA PROM board can be programmed, one word at a time, using the microNOVA PROM programmer board.

## SUMMARY OF CHARACTERISTICS

| PROM Type:                           | Signetics 82S126 or 82S130                |

|--------------------------------------|-------------------------------------------|

| Board Capacity:                      | 512; 1,024; 2,048; or 4,096 16-bit words. |

| Access Time:                         | 200ns.                                    |

| Board Dimensions:                    | 7.5 x 9.9 in. (19 x 24.9 cm.)             |

| Maximum<br>Operating<br>Temperature: | 131°F (55°C)                              |

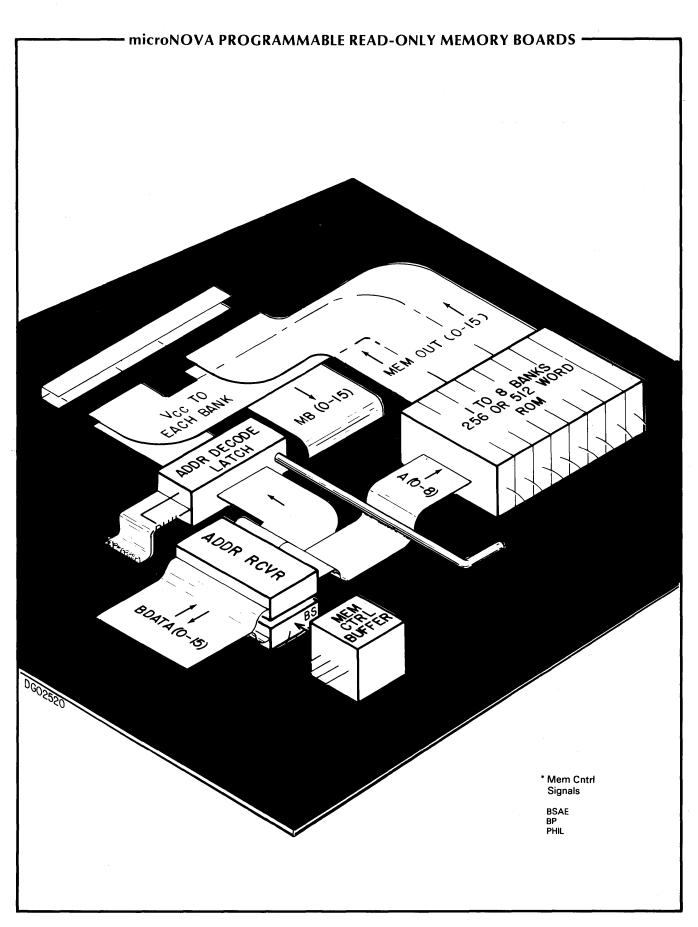

#### **BLOCK DIAGRAM**

The block diagram on the opposite page shows the principal components plus the control and data paths of microNOVA ROM boards. The board contains a memory bus address receiver and latch, from 1 to 8 banks of PROM, each with 256 or 512 16-bit words, a memory driver, and a memory control buffer. For normal PROM operation, there is also a shorting block located on connector "A".

When an address appears on the memory bus at the start of a Read operation, the address latches in the address receiver. The high-order bits select one of the eight banks by applying power  $(V_{CC})$  through the shorting block to that bank, while the low-order bits of the address pass directly to all PROM banks. (To reduce dc power dissipation, the PROM banks remain

unpowered when not being read). The addressed word is driven onto the memory bus while the memory control buffer asserts the signal **PHIL** to disable any RAM in the system from placing data on the bus.

The PROM board is designed so that PROMS can be programmed on the board using the microNOVA PROM programmer. (The programmer plugs directly into the microNOVA chassis, and the PROM board plugs directly into the programmer.) Two groups of signals, the bank select signals and taps from the data out lines of the PROM banks, are carried to connector "A" because they are used by the microNOVA PROM programmer when programming PROMS. For the PROM board's normal use, a shorting plug must be installed on the "A" connector to close the internal paths carried to that connector.

# **PROM SIZE JUMPERS**

| SIZE OF PROM CHIPS | INSERT JUMPERS |

|--------------------|----------------|

| 256 x 4 bits       | W1, W3, W6     |

| 512 x 4 bits       | W2, W4, W5, W7 |

#### **ADDRESS SELECTION JUMPERS**

| BIT POSITIONS OF STARTING ADDRESS | 1   | 2   | 3   | 4* |

|-----------------------------------|-----|-----|-----|----|

| INSERT JUMPER TO SPECIFY 1        | W13 | W15 | W11 | W9 |

| INSERT JUMPER TO SPECIFY 0        | W12 | W14 | W10 | W8 |

\*Jumpers W8 and W9 are removed on the 4K PROM board.

**NOTE** All of the address selecton jumpers must be removed when the board is being programmed with the microNOVA PROM programmer.

.

This page intentionally left blank.

.

.

. .

# SECTION V HAND-HELD CONSOLE SUBSYSTEM

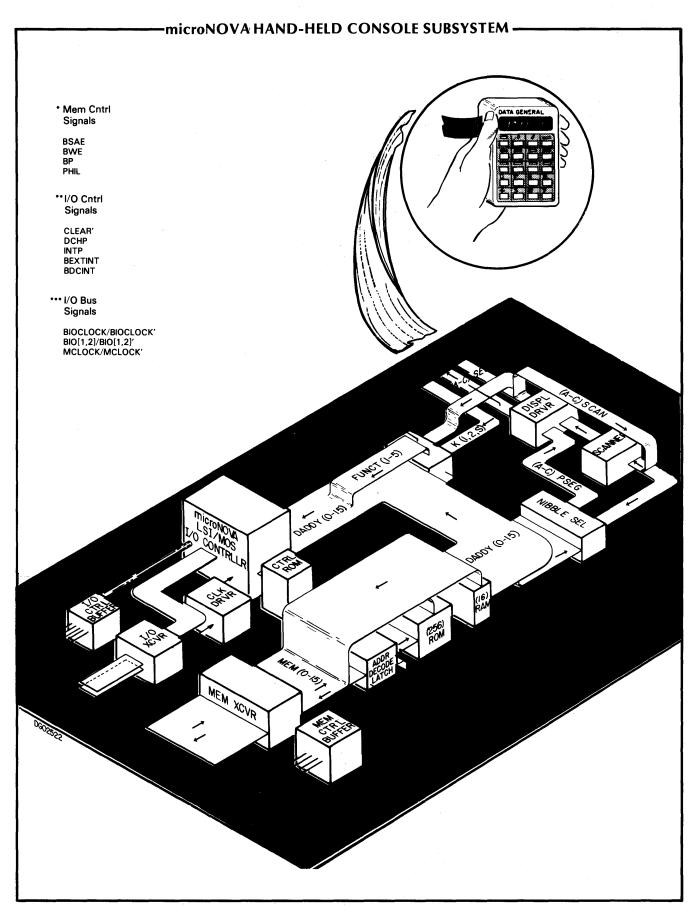

Data General's model 8564 hand-held console is a portable device that mounts on the chassis front panel and is connected by a 10' ribbon cable to its IOC-based controller, which occupies a single slot in the main chassis. Data is retrieved from the 20-key pad via programmed I/O on an interrupt-per-key basis. The contents of memory location 077576<sub>s</sub> are constantly displayed as 6 octal digits via the 7-segment LED display. The standard console software, supplied in 256 16-bit word of ROM/RAM on the controller board, provides reset, program load, start/stop/continue, and octal examination and modification of memory and CPU registers. With suitable software, the actions of all keys may be redefined by the user.

# **OVERVIEW AND INTRODUCTION**

Computer consoles usually are hard-wired extensions of the central processor used to monitor system performance and to aid in fault finding when the system malfunctions. For large computer systems, the processor console is the province of the field serviceman. With the advent of minicomputers, the processor console has also been used by programmers both as an aid in debugging programs and as an I/O device. As an I/O device, the minicomputer processor console is sometimes used to enter information into the system and to display the status of an application program.

The microNOVA hand-held console, when used with the standard console software, provides functions normally found on a minicomputer processor console and can be used both for trouble shooting and program debugging. The fact that the hand-held console is fully user-programmable means that it is extremely versatile and may be used in many application environments as a key-entry/visualresponse I/O device.

The hand-held console subsystem consists of a lightweight, portable console which contains a 20-key pad and a digital readout which displays the contents of one 16-bit word of memory as 6 octal digits. The

# SUMMARY OF CHARACTERISTICS

| Kẹၞy Pad:                            | 20-key, calculator format. Keys are<br>0.425in(w) by 0.250in(h) on centers of<br>0.625in.                               |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Display:                             | 6-digit, 7-segment LED. Each digit is 0.3in(h).                                                                         |

| Interface<br>Requirements:           | IOC-based controller occupies 1 slot in main chassis. Controller connects to console via 16-conductor 10' ribbon cable. |

| Packaging:                           | Injected molded, 2-piece case with living hinge key pad as part of top.                                                 |

| Location<br>Requirement:             | Within slots 3-8                                                                                                        |

| Mounting:                            | Attaches to depression in front panel with<br>Dzus fastener. Cable is held behind front<br>panel.                       |

| HHC<br>Dimensions:                   | 4.85in(h), 3.30in(w), 1.2(d). 12.3cm(h),<br>8.4cm(w), 3cm(d).                                                           |

| Board<br>Dimensions:                 | 7.50 x 9.9 in (19 x 24.9 cm)                                                                                            |