# **DISTRIBUTED LOGIC CORPORATION**

# MODEL DQ235 DISC CONTROLLER INSTRUCTION MANUAL

## MODEL DQ235 DISC CONTROLLER INSTRUCTION MANUAL

January 1986

DISTRIBUTED LOGIC CORPORATION 1555 S. Sinclair Street P.O. Box 6270 Anaheim, California 92806 Telephone: (714) 937-5700 Telex: 6836051 Copyright ©1986 by Distributed Logic Corporation Printed in the United States of America

### TABLE OF CONTENTS

| Section |                                          | Page          |

|---------|------------------------------------------|---------------|

| 1       | DESCRIPTION                              | . 1-1         |

|         | INTRODUCTION                             | 1-1           |

|         | CONTROLLER CHARACTERISTICS               | . 1-1         |

|         | LSI-11 Q BUS INTERFACE                   | 1-2           |

|         | INTERRUPT                                | 1-3           |

|         | DISC INTERFACE                           | . 1 <b>-3</b> |

|         | CONTROLLER SPECIFICATIONS                | . 1-4         |

| 2       | INSTALLATION                             | 2-1           |

|         | INSPECTION                               |               |

|         | PRE-INSTALLATION CHECKS                  |               |

|         | INSTALLATION                             | . 2-3         |

| 3       | OPERATION                                |               |

|         | INTRODUCTION                             |               |

|         | PRECAUTIONS AND PREOPERATIONAL CHECKS    |               |

|         | BOOTSTRAP PROCEDURE                      |               |

|         | FORMAT AND DIAGNOSTIC TEST PROGRAM       | -             |

|         | Description                              |               |

|         | Partitioning Program                     |               |

|         | Diagnostic Test Program                  | . 3-12        |

| 4       | PROGRAMMING                              | . 4-1         |

|         | PROGRAMMING DEFINITIONS                  |               |

|         | DISC CONTROLLER FUNCTIONS                | 4-1           |

|         | Select Drive                             | 4-1           |

|         | Pack Acknowledge                         | 4-1           |

|         | Drive Clear                              | 4-1           |

|         | Recalibrate                              | . 4-1         |

|         | Offset                                   | . 4-1         |

|         | Seek                                     | 4-1           |

|         | Read Data                                | 4-2           |

|         | Write Data                               | . 4-2         |

|         | Read Headers                             | . 4-2         |

|         | Write Headers                            | <b>4-2</b>    |

|         | Write Check                              |               |

|         | Mapping and Map Override                 |               |

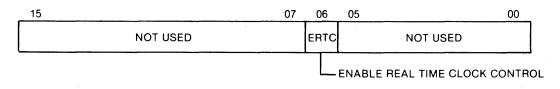

|         | ENABLE REAL TIME CLOCK CONTROL           |               |

|         | REGISTERS                                |               |

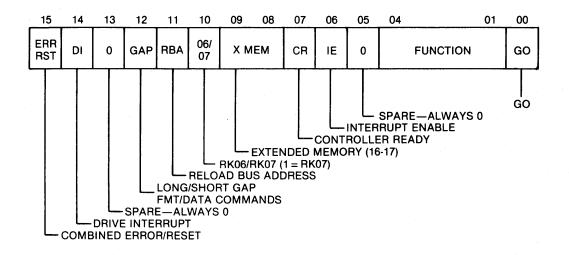

|         | Control and Status Register 1            |               |

|         | Word Count Register                      |               |

|         | Bus Address Register                     |               |

|         | Disc Address (Track and Sector) Register |               |

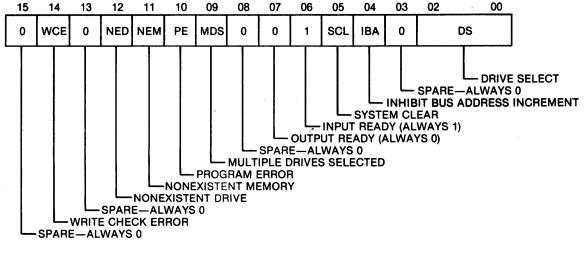

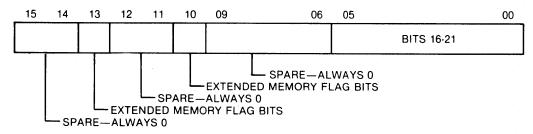

|         | Control and Status Register 2            |               |

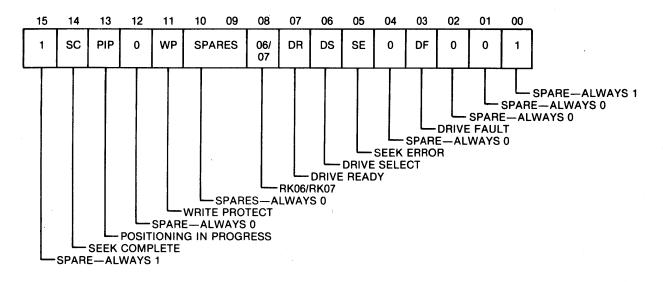

|         | Drive Status Register                    |               |

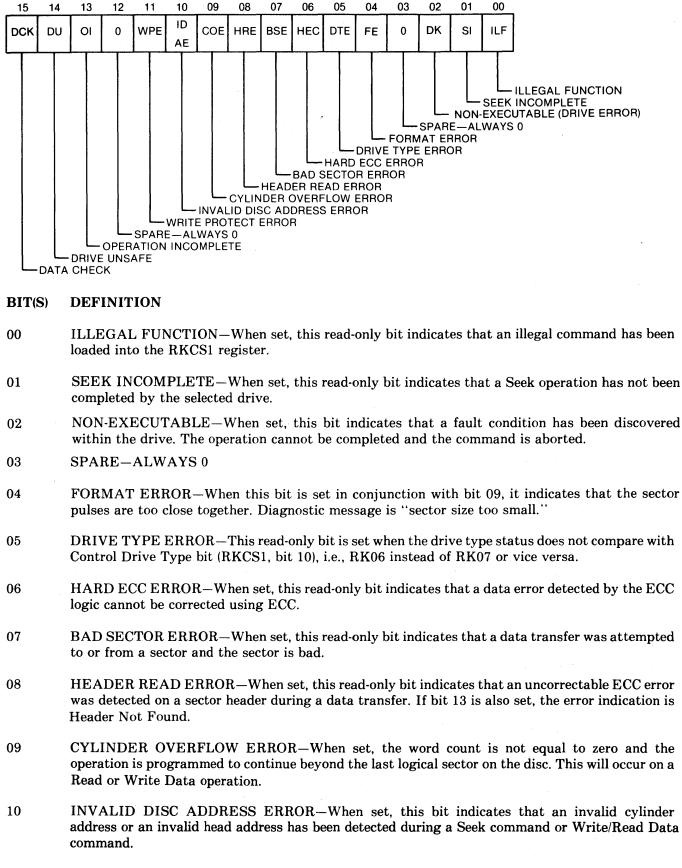

|         | Error Register                           |               |

|         | Attention Summary and Offset Register    | 4-11          |

### **TABLE OF CONTENTS (Continued)**

Page

#### Section

#### Desired Cylinder Address Register 4-12 5

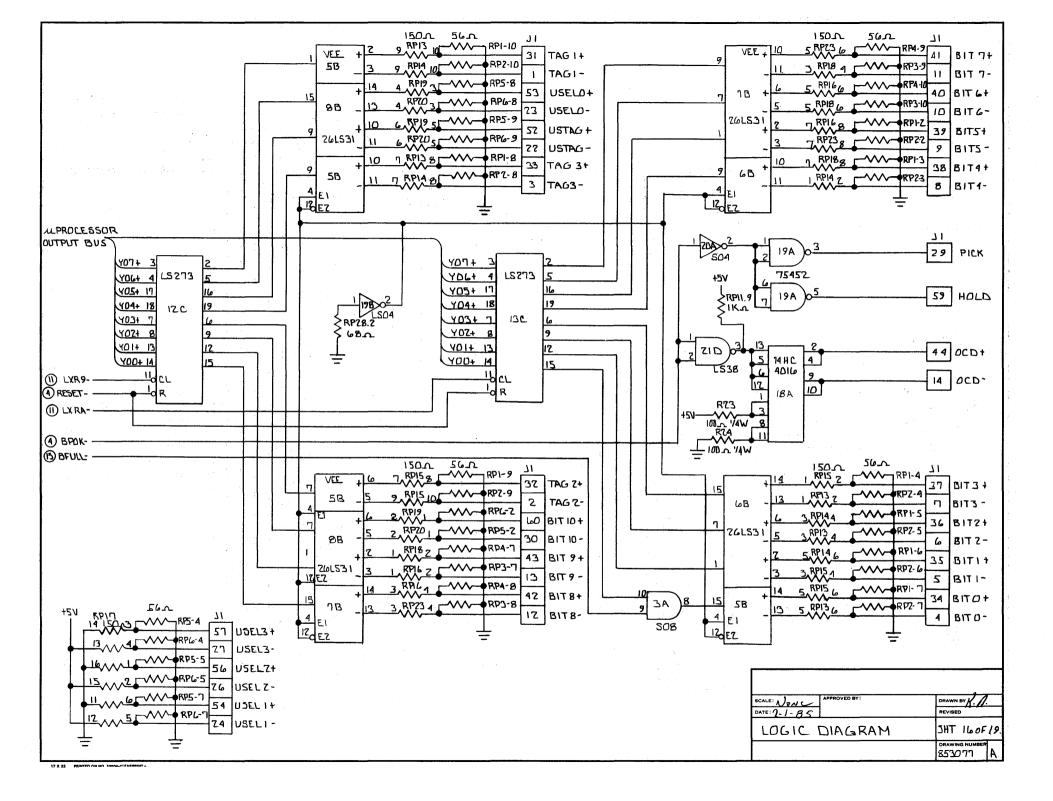

#### 6 LOGICS

U

iv

### **ILLUSTRATIONS**

### Figure

### Page

Page

| 1-1 | Disc Controller System Simplified Diagram | -1 |

|-----|-------------------------------------------|----|

| 2-1 | Controller Configuration                  |    |

| 2-2 | Typical Backplane Configuration           |    |

| 3-1 | Partitions                                |    |

| 4-1 | Controller Register Configurations        | -4 |

| 5-1 | Board Layout                              | -3 |

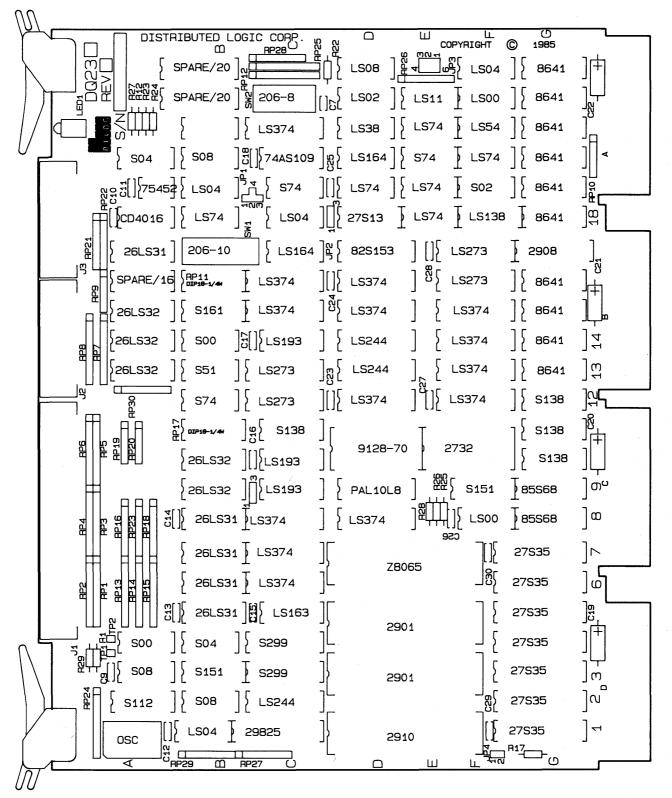

| 5-2 | Simplified Block Diagram                  | -6 |

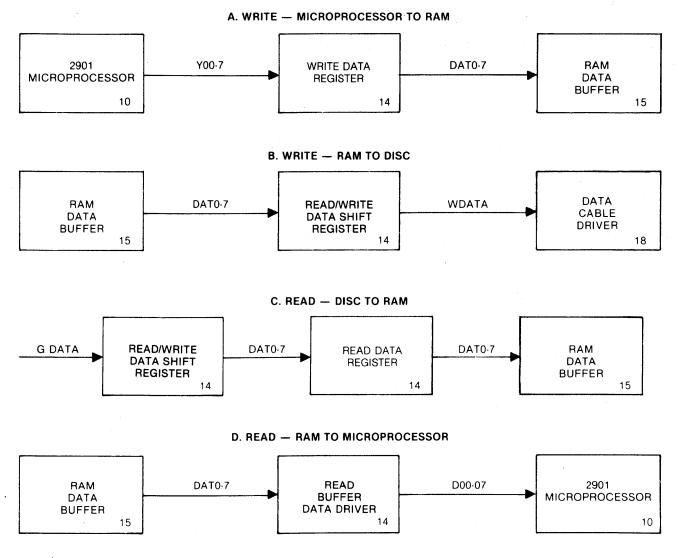

| 5-3 | Data Paths                                |    |

### **TABLES**

### Table

| 1-1              | Controller/Q-Bus Interface Lines                        | . 1-2        |

|------------------|---------------------------------------------------------|--------------|

| 1-2              | Controller To Drive I/O Interface—"A" Cable             | . 1-3        |

| 1-3              | Controller To Drive I/O Interface—"B" Cable             | . 1-3        |

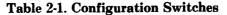

| 2-1              | Configuration Switches                                  | . <b>2-2</b> |

| 2-2              | Jumper Installation                                     | 2-2          |

| 3-1              | Values for Partitioning with Universal Firmware (DQ235) | 3-3          |

| 4-1              | Function Codes                                          | . 4-1        |

| 5-1              | Controller Symptoms                                     | 5-2          |

| 5-2 <sup>-</sup> | Term Listing                                            | . <b>5-4</b> |

### SECTION 1 DESCRIPTION

#### INTRODUCTION

This manual describes the installation, operation, programming, troubleshooting, and theory of operation of Distributed Logic Corporation (DILOG) Model DQ235 Disc Controller. The controller interfaces DEC\* LSI-11 based computer systems to one or two SMD I/O disc drives, including 8- and 14-inch Winchester, SMD pack and CMD cartridge type drives. The complete controller occupies one quad module in the backplane. Full sector buffering in the controller matches the transfer rate of the disc drive and the CPU. The controller is compatible with RK06/RK07 software drivers in RT-11, RSX-11 and RSTS. Block mode transfers permit faster DMA transfers to and from memory.

#### **CONTROLLER CHARACTERISTICS**

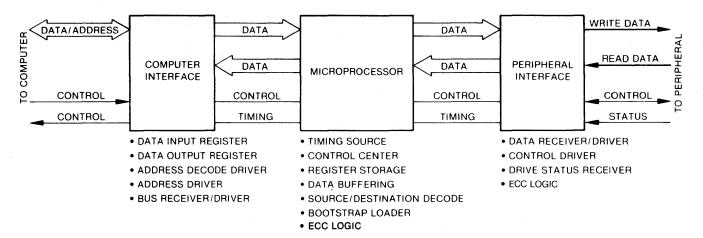

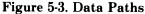

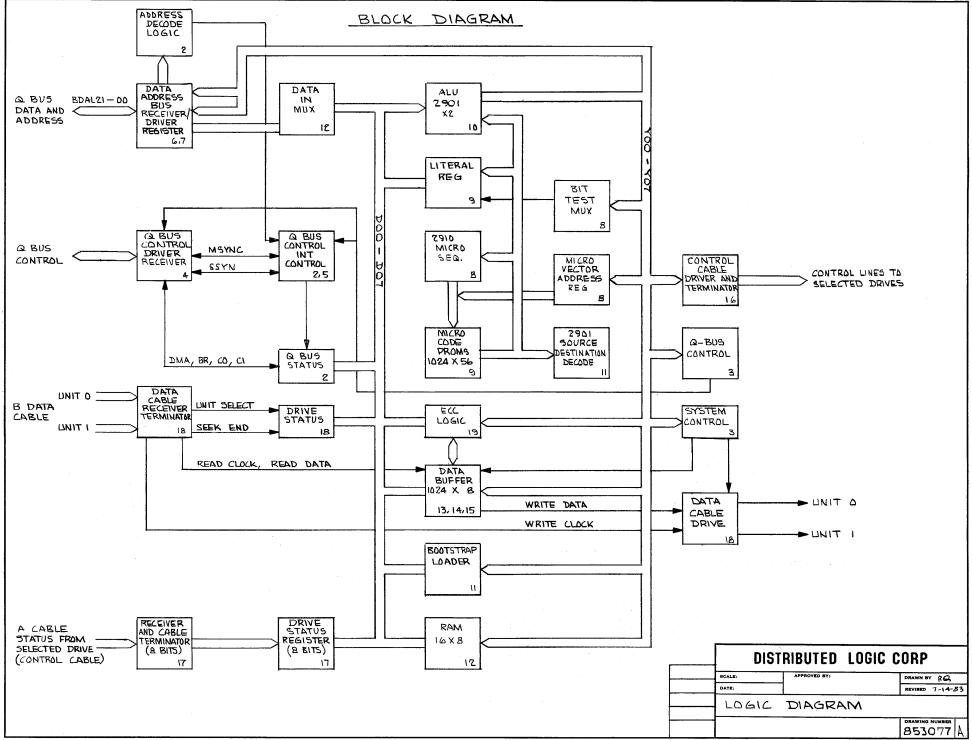

The disc controller links the LSI-11 computer to one or two disc storage units. Commands from the computer are received and interpreted by the controller and translated into a form compatible with the disc units. Buffering and signal timing for data transfers between the computer and the discs are performed by the controller. A microprocessor is the sequence and timing center of the controller. The control information is stored as firmware instructions in read-onlymemory (ROM) on the controller board. One section of the ROM contains a diagnostic program that tests the functional operation of the controller. This self-test is performed automatically each time power is applied. A green diagnostic indicator on the controller board lights if self-test passes.

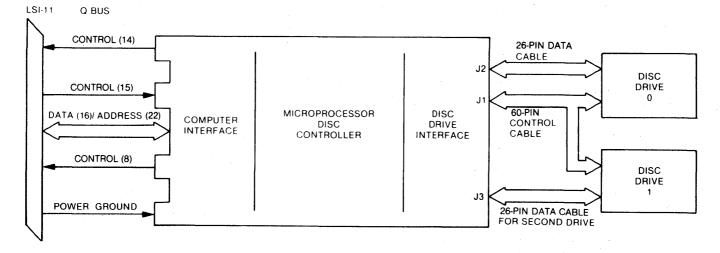

Data transfers are directly to and from the computer memory using the DMA facility of the LSI-11 I/O bus. Switch selectable DMA bursts of two or four words may be used with or without block mode. In addition, the controller monitors the status of the disc units and the data being transferred and presents this information to the computer upon request. An error correction code with a 56-bit checkword corrects error bursts up to 11 bits. To compensate for media errors, bad sectors are skipped and alternates assigned, and there is an automatic retry feature for read errors. The controller is capable of addressing four megabytes and controlling up to two disc drives in various configurations up to a total on-line formatted capacity of 220.32 megabytes. Figure 1-1 is a simplified diagram of a disc system.

Figure 1-1. Disc Controller System Simplified Diagram

<sup>\*</sup>DEC, RSX and RSTS are registered trademarks of Digital Equipment Corporation.

#### **LSI-11 Q BUS INTERFACE**

Commands, data and status transfers between the controller and the computer are executed via the parallel I/O bus (Q bus) of the computer. Data trans-

fers are direct to memory via the DMA facility of the Q bus; commands and status are under programmed I/O. Controller/Q bus interface lines are listed in Table 1-1.

| Bus Pin                                                                                 | Mnemonic                                     | Controller<br>Input/<br>Output | Description                                                                                                                                                   |

|-----------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC2, AJ1, AM1, AT1, BJ1,<br>BM1, BT1, BC2, CC2, CJ1,<br>CM1, CT1, DC2, DJ1, DM1,<br>DT1 | GND                                          | 0                              | Signal Ground and DC return.                                                                                                                                  |

| AN1                                                                                     | BDMR L                                       | 0                              | Direct Memory Access (DMA) request from controller: active low.                                                                                               |

| AP1                                                                                     | BHALT L                                      | N/A                            | Stops program execution. Refresh and DMA is enabled.<br>Console operation is enabled.                                                                         |

| AR1                                                                                     | BREF L                                       | 1                              | Memory Refresh, also signifies block mode memory.                                                                                                             |

| BA1                                                                                     | BDCOK H                                      | 1                              | DC power ok. All DC voltages are normal.                                                                                                                      |

| BB1                                                                                     | врок н                                       | N/A                            | Primary power ok. When low activates power fail trap sequence.                                                                                                |

| BN1                                                                                     | BSACK L                                      | 0                              | Select Acknowledge. Interlocked with BDMGO indicating<br>controller is bus master in a DMA sequence.                                                          |

| BR1                                                                                     | BEVNT L                                      | 0                              | External Event Interrupt Request. Real Time Clock Control.                                                                                                    |

| AA2, BA2, BV1, CA2, DA2                                                                 | + 5                                          | I                              | +5 volt system power.                                                                                                                                         |

| AD2, BD2                                                                                | + 12                                         | N/A                            | + 12 volt system power.                                                                                                                                       |

| AE2                                                                                     | BDOUT L                                      | 1/0                            | Data Out. Valid data from bus master is on the bus. Interlocked with BRPLY.                                                                                   |

| AF2                                                                                     | BRPLY L                                      | 1/0                            | Reply from slave to BDOUT or BDIN and during IAK.                                                                                                             |

| AH2                                                                                     | BDIN L                                       | 1/0                            | Data Input. Input transfer to master (states master is ready for data). Interlocked with BRPLY.                                                               |

| AJ2                                                                                     | BSYNC L                                      | 1/0                            | Synchronize: becomes active when master places address on bus; stays active during transfer.                                                                  |

| AK2                                                                                     | BWTBT L                                      | 1/0                            | Write Byte: indicates output sequence to follow (DATO or DATOB) or marks byte address time during a DATOB.                                                    |

| AA1, AB1, AL2, BP1                                                                      | BIRQ4L,5,6,7                                 | 0                              | Interrupt Request.                                                                                                                                            |

| AM2<br>AN2<br>CM2<br>CN2                                                                | BIAK1I L<br>BIAK1O L<br>BIAK2I L<br>BIAK2O L | <br>0<br> <br>0                | Serial Interrupt Acknowledge input and output lines routed from<br>Q-Bus, through devices, and back to processor to establish an<br>interrupt priority chain. |

| AT2                                                                                     | BINIT L                                      | 1                              | Initialize. Clears devices on I/O bus.                                                                                                                        |

| AU2, AV2, BE2, BF2, BH2,<br>BH2, BK2, BL2, BM2, BN2,<br>BP2, BR2, BS2, BT2, BU2,<br>BV2 | BDAL0 L<br>through<br>BDAL15 L               | 1/0                            | Data/address lines, 0-15                                                                                                                                      |

| AR2<br>AS2<br>CR2<br>CS2                                                                | BDMG11 L<br>BDMG10 L<br>BDMG21 L<br>BDMG20 L | <br>0<br>                      | DMA Grant Input and Output. Serial DMA priority line from<br>computer, through devices and back to computer.                                                  |

| AP2                                                                                     | BBS7 L                                       | I/O                            | Bank 7 Select. Asserted by bus master when address in upper 4K bank is placed on the bus, also asserted when requesting block mode transfer.                  |

| AC1, AD1, BC1, BD1, BE1,<br>BF1                                                         | BDAL 16 L<br>-BDAL 21 L                      | 0                              | Extended Address Bits 16-21                                                                                                                                   |

#### Table 1-1. Controller/Q-Bus Interface Lines

#### INTERRUPT

The interrupt vector address is factory set to address 210 (alternate 254). The vector address is programmed in a PROM on the controller, allowing user selection.

Interrupt requests are generated under the following conditions:

- 1. When the Controller Ready bit is set upon completion of a command.

- 2. When any drive sets an associated Attention Flat in the Attention register and the Controller Ready bit is set.

- 3. When the controller or any drive indicates the presence of an error by setting the combined Error/Reset bit in the Control and Status register.

- 4. When the Controller Ready bit is set by conventional initialization upon completion of a controller command or when an error condition is detected. For test purposes, a forced interrupt may be generated by the Controller Ready and Interrupt Enable bits.

#### **DISC INTERFACE**

The controller interfaces one or two disc drives through 60- and 26-pin cables. If two drives are used, the 60-pin control cable ("A" cable) is daisy chained to drive 0 and 1. The 26-pin cables ("B" cable) are connected separately from the controller to each drive. The maximum length of the 60-pin cable is 100 feet. The maximum length of the 26-pin cable is 50 feet. Table 1-2 lists the 60-pin interface signals, and Table 1-3 lists the 26-pin interface signals.

Table 1-2. Controller To Drive I/O Interface— "A" Cable

| Signal Name        | Pin Po<br>(Act<br>– | olarity<br>ive)<br>+ | Source     |

|--------------------|---------------------|----------------------|------------|

| DEVICE SELECT 0    | 23                  | 53                   | Controller |

| DEVICE SELECT 1    | 24                  | 54                   | Controller |

| DEVICE SELECT 2    | 26                  | 56                   | Controller |

| DEVICE SELECT 3    | 27                  | 57                   | Controller |

| SELECT ENABLE      | 22                  | 52                   | Controller |

| SET CYLINDER TAG   | 1                   | 31                   | Controller |

| SET HEAD TAG       | 2<br>3<br>4         | 32                   | Controller |

| CONTROL SELECT     | 3                   | 33                   | Controller |

| BUS OUT 0          | 4                   | 34                   | Controller |

| BUS OUT 1          | - 5                 | 35                   | Controller |

| BUS OUT 2          | 6                   | 36                   | Controller |

| BUS OUT 3          | 7                   | 37                   | Controller |

| BUS OUT 4          | 8                   | 38                   | Controller |

| BUS OUT 5          | 9                   | 39                   | Controller |

| BUS OUT 6          | 10                  | 40                   | Controller |

| BUS OUT 7          | 11                  | 41                   | Controller |

| BUS OUT 8          | 12                  | 42                   | Controller |

| BUS OUT 9          | 13                  | 43                   | Controller |

| BUS OUT 10         | 30                  | 60                   | Controller |

| DEVICE ENABLE      | 14                  | 44                   | Controller |

| INDEX              | 18                  | 48                   | Drive      |

| SECTOR MARK        | 25                  | 55                   | Drive      |

| FAULT              | 15                  | 45                   | Drive      |

| SEEK ERROR         | 16                  | 46                   | Drive      |

| ON CYLINDER        | 17                  | 47                   | Drive      |

|                    | 19                  | 49                   | Drive      |

| WRITE PROTECTED    | 28                  | 58                   | Drive      |

|                    | 20                  | 50                   | Drive      |

| BUS-DUAL-PORT ONLY | 21                  | 51                   | Drive      |

| SEQUENCE IN        | 29<br>59            |                      | Controller |

| HOLD               | 59                  |                      | Controller |

Table 1-3. Controller To Drive I/O Interface— "B" Cable

| Signal                       | Pin Polarity<br>(Active)<br>-   +   Ground |    |    | Source     |

|------------------------------|--------------------------------------------|----|----|------------|

| Ground                       |                                            |    | 1  |            |

| Servo Clock                  | 2                                          | 14 |    | Drive      |

| Ground                       |                                            |    | 15 |            |

| Read Data                    | 3                                          | 16 |    | Drive      |

| Ground                       |                                            |    | 4  |            |

| Read Clock                   | 5                                          | 17 |    | Drive      |

| Ground                       |                                            |    | 18 | - · · ·    |

| Write Clock                  | 6                                          | 19 |    | Controller |

| Ground                       |                                            |    | 7  |            |

| Write Data                   | 8                                          | 20 |    | Controller |

| Ground                       |                                            | ~  | 21 | Data       |

| Unit Selected                | 22                                         | 9  |    | Drive      |

| Seek End                     | 10                                         | 23 | 44 | Drive      |

| Ground<br>Reserved for Index | 12                                         | 24 | 11 |            |

| Ground                       | 12                                         | 24 | 25 |            |

| Reserved for Sector          | 13                                         | 26 | 20 |            |

#### **CONTROLLER SPECIFICATIONS\***

Mechanical—The Model DQ235 is completely contained on one quad module 10.44 inches wide by 8.88 inches deep, and plugs into and requires one slot in any DEC LSI-11 based backplane.

#### **Computer I/O**

- **Register Addresses** (PROM selectable)

- -Control/Status Register 1 (RKCS1) 777 440

- -Word Count Register (RKWC) 777 442

- -Bus Address Register (RKBA) 777 444

- -Disc Address Register (RKDA) 777-446

- -Control/Status Register 2 (RKCS2) 777 450

- -Drive Status Register (RKDS) 777 452

- -Error Register (RKER) 777 454

- -Attention Summary/Offset Register (RKAS/ OF) 777 456

- -Desired Cylinder Register (RKDC) 777 460

- -Extended Memory Address Register (RKXMA) 777 462

- -Data Buffer Register (RKDB) 777 464

- -Maintenance Register 1 (RKMR1) 777 466

- -ECC Position Register (RKECPS) 777 470

- -ECC Pattern Register (RKECPT) 777 472

- -Maintenance Register 2 (RKMR2) 777 474

- -Maintenance Register 3 (RKMR3) 777 476

- -Enable Real Time Clock Control (RKERTC) 777 546

#### **Data Transfer**

- -Method: DMA with or without block mode.

- -Maximum block size transferred in a single operation is 64K words.

- -2 or 4 word DMA burst transfer.

**Bus Load**

-1 std unit load

#### Address Ranges

- -Disc drive: up to 220.32 megabytes

- -Computer Memory: to 2 megawords

#### **Interrupt Vector Address**

--PROM selectable, factory set at 210 (alternate 254) priority level BR5

#### **Disc Drive I/O**

**Connector**—one 60-pin type "A" flat ribbon cable mounted on outer edge of controller module Two 26pin type "B" ribbon cables (1 for each drive interfaced with).

Signal-SMD A/B flat cable compatible

**Power**—+5 volts at 3.5 amps from computer power supply.

**Environment**—Operating temperature 40°F. to 140°F., humidity 10 to 95% non-condensing.

Shipping Weight-5 pounds, includes documentation and cables.

\*Specifications subject to change without notice.

### SECTION 2 INSTALLATION

#### **INSPECTION**

The padded shipping carton that contains the controller board also contains an instruction manual and cables to the first disc drive if this option is exercised. The controller is completely contained on the quad-size printed circuit board. Disc drives, if supplied, are contained in a separate shipping carton. Inspect the controller and cables for damage.

#### CAUTION

If damage to any of the components is noted, do not install. Immediately inform the carrier and DILOG.

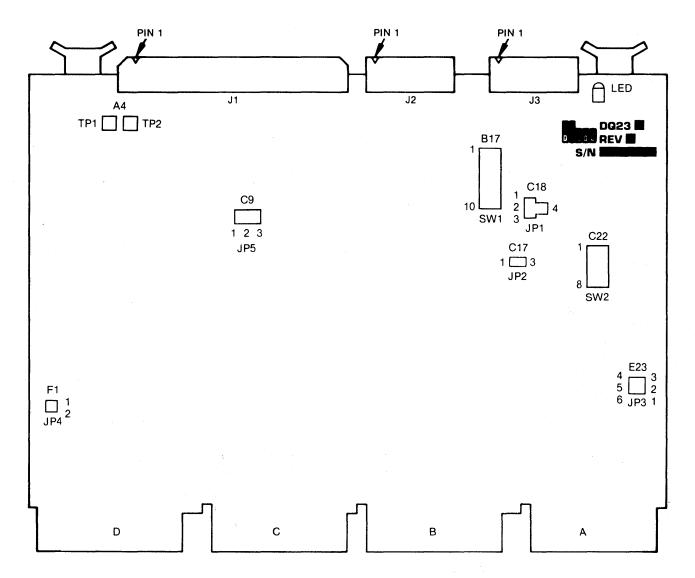

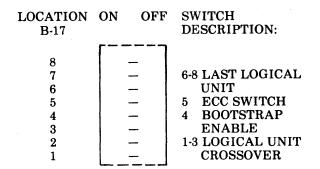

Installation instructions for the disc drive are contained in the disc drive manual. Before installing any components of the disc system, read Sections 1, 2 and 3 of this manual. Figure 2-1 illustrates the configuration of the controller. Tables 2-1 and 2-2 describe switch and jumper settings.

2-1

\*DEFAULT SETUP

\*\*On an LSI-11/23 PLUS computer, bootstrap address 775 000 must be used.

1-2

For drives with data rates of less than 1.2 megabytes (9.677 megabits)

per second.

#### **PRE-INSTALLATION CHECKS**

There are various LSI-11 configurations, many of which were installed before DEC made a hard disc available for LSI-11 based systems. Certain configurations require minor modifications before operating the disc system. These modifications are as follows:

- A. If the system contains a REV11-C module, it must be placed closer to the processor module (higher priority) than the controller if the DMA refresh logic on the REV11-C is enabled.

- B. If the 4K memory on the DK11-F is not used and the memory in the system does not require external refresh, the DMA refresh logic on the REV11-C should be disabled by removing jumper W2 on the REV11-C module.

- C. If the system contains a REV11-A module, the refresh DMA logic must be disabled since the module must be placed at the end of the bus (REV11-A contains bus terminator).

- D. If the REV11-C module is installed, cut the etch to pin 12 on circuit D30 (top of board) and add a jumper between pin 12 and pin 13 of D30.

- E. If the system requires more than one backplane, place the REV-11 terminator in the last available location in the last backplane.

#### INSTALLATION

To install the controller module, proceed as follows:

#### CAUTION

Remove DC power from mounting assembly before inserting or removing the controller module.

Damage to the backplane assembly may occur if the controller module is plugged in backwards.

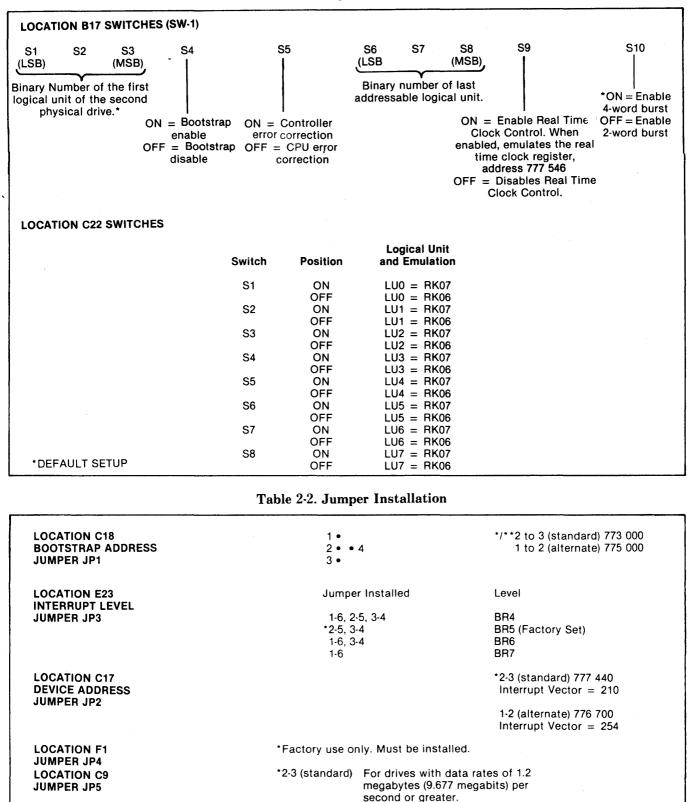

1. Select the backplane location into which the controller is to be inserted. Be sure that the disc controller is the lowest priority DMA device in the computer except if the DMA refresh/bootstrap ROM option module is installed in the system. The lowest priority device is the device farthest from the processor module. Note that the controller contains a bootstrap ROM.

There are several backplane assemblies available from DEC and other manufacturers. Figure 2-2 shows typical backplane configurations. Note that the processor module is always installed in the first location of the backplane or in the first location in the first backplane of multiple backplane systems.

It is important that all option slots between the processor and the disc controller be filled to ensure that the daisy-chained interrupt (BIAK) and DMA (BDMG) signals be complete to the controller slots. If there must be empty slots between the controller and any option board, the following backplane jumpers must be installed:

| FROM        | то         | SIGNAL   |

|-------------|------------|----------|

| C0 x NS     | C0 x M2    | BIAK1/L0 |

| C0 x S2     | C0 x R2    | BDMG1/L0 |

| <b>†</b>    | +          |          |

| Last Full   | Controller |          |

| Option Slot | Slot       |          |

2. Insert the controller into the selected backplane position. Be sure the controller is installed with the components facing row one, the processor.

The controller module is equipped with handles on the side opposite the slot connectors. Gently position the module slot connectors into the backplane then press until the module connectors are firmly seated into the backplane. Both handles must be pressed simultaneously. When removing the module, apply equal pulling pressure to both handles.

- 3. Feed the module connector end of the disc I/O cables into the controller module connectors. Ensure pin 1 is matched with the triangle on the connector as shown in Figure 2-1. Install the cable connectors into the module connectors. Verify that the connectors are firmly seated.

- 4. Connect the disc-end of the I/O cables to the disc I/O connectors. Be sure that the bus terminator is installed at the last disc in the system.

- 5. Refer to the disc manual for operating instructions and apply power to the disc and computer.

- 6. Observe that the green DIAGnostic LED on the controller board is lit.

- 7. The system is now ready to operate. Refer to Section 3 for operating instructions, diagnostics, and formatting.

CONTROLLER LOCATION DDV11-B BACKPLANE MODULE INSERTION SIDE SLOTS

NOTE

MEMORY CAN BE INSTALLED IN ANY SLOT; IT IS NOT PRIORITY DEPENDENT AND DOES NOT NEED TO BE ADJACENT TO THE PROCESSOR. CONTROLLERS ARE ALSO COMPATIBLE WITH H9273A MODULES.

| Figure          | 2-2. | Typical   | Backplane | Configuration |

|-----------------|------|-----------|-----------|---------------|

| 1 1 1 1 1 1 1 1 |      | a y prout | Duciplunc | Company       |

#### GROUNDING

To prevent grounding problems, DILOG recommends standard ground braid be installed from the computer DC ground point to the disc drive DC ground point and also between disc drives at the DC ground points.

### SECTION 3 OPERATION

#### **INTRODUCTION**

This section contains procedures for operating the computer system with the controller and a disc drive or drives. An understanding of DEC operating procedures is assumed. The material here is provided for "first time users" of disc subsystems and describes procedures for bootstrapping, formatting, and diagnostic testing.

The programs supplied with each controller are on floppy disc or magnetic tape media, depending on what is specified on the sales order.

# PRECAUTIONS AND PREOPERATIONAL CHECKS

The following precautions should be observed while operating the system. Failure to observe these precautions could damage the controller, the disc cartridge, the computer, or could erase a portion or all of the stored software.

- 1. If the controller bootstrap is to be used, set controller switch S4 ON, and disable other bootstraps that reside at that address.

- 2. See Figure 2-1 for proper positions of the switches and jumpers. See Tables 2-1 and 2-2 for switch and jumper settings.

- 3. Do not remove or replace the controller board with power applied to the computer.

- 4. If system does not operate properly, check operating procedures and verify that the items in Section 2 have been performed.

Before operation the following checks should be made:

- 1. Verify that the controller board is firmly seated in backplane connector.

- 2. Verify that the cables between the controller and the disc drive are installed.

- 3. Be sure the disc drive cartridge is installed (if it is to be used).

- 4. Apply power to the computer and the console device.

- 5. Verify that green DIAG light on front edge of the controller board lights.

- 6. Be sure power is applied to disc drive and READY light is on.

#### **BOOTSTRAP PROCEDURE**

The following assumes the system is in ODT mode. Note that the bootstrap can be used under processor Power Up Mode 2 conditions. Refer to the appropriate DEC manual for a discussion of the Power Up Modes. Further note that the disc drive does not need to be READY to enter the bootstrap.

Reset the system by pressing RESET or enter the following (characters underlined are output by the system; characters not underlined are input by the operator):

@ 773000G or 775000G

Depends on jumper configuration above.

Enter one of the following: DM0, DP0, DL0, DR0, MS0, MT0, DY0 or FT <CR>.

Definitions are as follows:

DM = RK06/07 Disc DP = RP02/03 Disc DL = RL01/02 Disc DR = RM02/03 Disc MS = TS11 Tape MT = Tape DY = RX02 Floppy Disc

Booting can be executed from logical units other than "0" shown above by entering the desired logical unit number, i.e.,  $1, 2, 3, \ldots$  or 7.

#### FORMAT AND DIAGNOSTIC TEST PROGRAM

#### Description

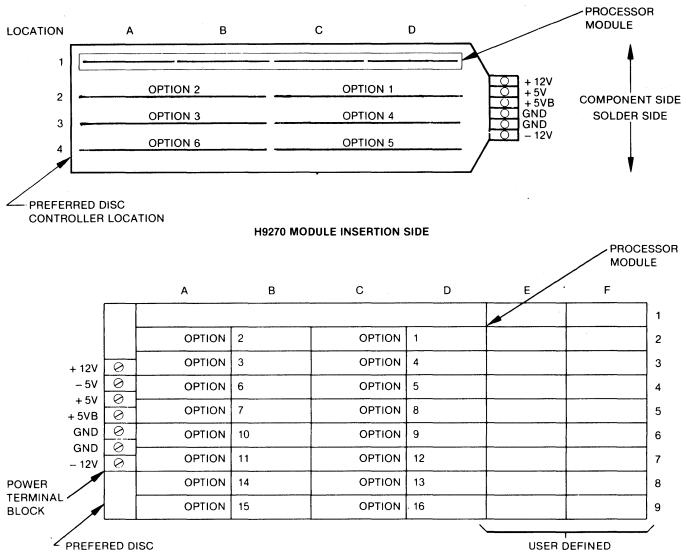

DILOG's Universal Firmware and Diagnostic Program permits the user to format a disc pack for his particular application; compensate for media errors; and test the controller and drive. When formatted, the disc may be partitioned horizontally or vertically. Either way the pack is divided into logical units which the computer recognizes. The user may select one of three types of partitioning: 1-head, 2-head or vertical.

The constraints for selecting each are:

Subsystem:

• Maximum number of logical units is 8.

1-head:

- Maximum number of heads (surfaces) is 8.

- Maximum size of logical units is 270,336 records.

2-head:

- Maximum number of heads (surfaces) is 16.

- Number of fixed and removable heads (surfaces) must be even.

- Maximum size of logical units is 270,336 records.

Vertical:

• Maximum size of logical units is 270,336 records.

Drive types CMD or DFR are formatted for a 1-head partition. SMD or MMD types are usually formatted vertically.

The disc pack is divided vertically by cylinders and horizontally by heads (or data surfaces). Each head (surface) is further divided into tracks. A track is addressed by cylinder number and head number. Tracks are further divided into sectors (or records or blocks) which the computer recognizes as increments within a logical unit. Sectors consist of overhead bytes (such as address, sync, error correction) and data bytes. The standard number of data bytes, bytes usable by the computer, is 512 data bytes per sector. Figure 3-1 illustrates vertical and head partitioning.

Table 3-1 is a partial list of disc drives and specifications for partitioning. Column 1 lists the manufacturer. Column 2 lists the model number. Column 3 lists the number of sectors (also called records and blocks) per track. Column 4 lists the number of heads (also called data surfaces) per drive. Column 5 lists the number of cylinders per drive. Columns 6

\* NUMBER OF CYLINDERS AND HEADS VARIES WITH TYPE OF DRIVE

#### **Figure 3-1. Partitions**

and 7 list the emulations, the number of megabytes per logical unit, and the number of sectors per logical unit. Column 8 lists the megabyte capacity and number of sectors of the last logical unit partitioned. For CMD drives (Note c), the value listed is for all logical units as well as the last.

To use the table, consider Ampex Capricorn 165 as an example. The drive is efficiently partitioned into five RK07 units with capacity and number of sectors shown at the top of Column 6. The remaining capacity is assigned as one RK06 unit with the capacity and sectors shown at the top of Column 7; however, the RK06 unit is the remainder after partitioning five RK07 units, and as such, this remainder is not a complete RK06 unit. Instead of 13.88 Mbytes with 27,126 sectors, the partial RK06 unit is assigned the remaining 8.78 Mbytes and 17,150 sectors. Notes a and b in Column 8 state

| (1)<br>Manufacturer | (2)<br>Model<br>Number | (3)<br>Sectors<br>(Records)<br>(Blocks)/<br>Track | (4)<br>Head<br>(Data Surf<br>Drive<br>Removable | aces)/    | (5)<br>Cylinders/<br>Drive* | (6)<br>Total Logi<br>RK07<br>Units<br>27.54MB<br>53,790 | RK06<br>Units | (8)**<br>Last Log<br>MB                 | ical Unit<br>Sectors |

|---------------------|------------------------|---------------------------------------------------|-------------------------------------------------|-----------|-----------------------------|---------------------------------------------------------|---------------|-----------------------------------------|----------------------|

| AMPEX               | Capricorn 165          | 35                                                | 0                                               | 10        | 823                         | 5                                                       | 1             | 8.78ª                                   | 17,150               |

| AMPEX               | Capicorn 330           | 35                                                | 0                                               | 16        | 1024                        | 5                                                       | 8             | 1.14 <sup>d</sup>                       | 2,240                |

| AMPEX               | Scorpio 48             | 35                                                | 0                                               | 3         | 823                         | 1                                                       | 1<br>4        | 16.45 <sup>b</sup><br>2.25 <sup>a</sup> | 32,130<br>4,410      |

| AMPEX               | Scorpio 80             | 35                                                | 0                                               | 5         | 823                         | 2                                                       | 1<br>6        | 18.18 <sup>b</sup><br>3.49 <sup>a</sup> | 35,525<br>6,825      |

| AMPEX               | DFR-932                | 34                                                | 1                                               | 1         | 823                         |                                                         | 2             | 14.25°                                  | 27,846               |

| AMPEX               | DFR-964                | 34                                                | 1                                               | 3         | 823                         |                                                         | 4             | 14.25 <sup>c</sup>                      | 27,846               |

| AMPEX               | DFR-996                | 34                                                | 1                                               | 5         | 823                         |                                                         | 6             | 14.25°                                  | 27,846               |

| AMPEX               | DM980                  | 34                                                | 5                                               | 0         | 823                         | 2                                                       | 1<br>6        | 16.10 <sup>b</sup><br>1.65 <sup>a</sup> | 31,450<br>3,230      |

| BALL                | BD50                   | 23                                                | 5                                               | 0         | 815                         | 1                                                       | 1<br>4        | 20.19 <sup>b</sup><br>6.06 <sup>a</sup> | 39,445<br>11,845     |

| BALL                | BD80                   | 34                                                | 5                                               | 0         | 815                         | 2                                                       | 1<br>6        | 15.40 <sup>b</sup><br>.95ª              | 30,090<br>1,870      |

| BASF                | 6172                   | 23                                                | 0                                               | 3         | 600                         |                                                         | 2             | 7.13 <sup>a</sup>                       | 13,938               |

| CENTURY DATA SYS.   | M80                    | 35                                                | 0                                               | 6         | 650                         | 2                                                       | 1             | 14.86 <sup>b</sup><br>.12 <sup>a</sup>  | 29,028<br>246        |

| CENTURY DATA SYS.   | M160                   | 35                                                | 0                                               | 6         | 837                         | 5                                                       | 1             | 3.04ª                                   | 5,940                |

| CENTURY DATA SYS.   | Trident T-82RM         | 34                                                | 5                                               | 0         | 823                         | 2                                                       | 1<br>6        | 16.10 <sup>b</sup><br>1.65 <sup>a</sup> | 31,450<br>3,230      |

| CENTURY DATA SYS.   | T-302                  | 34                                                | 19                                              | 0         | 823                         | 3                                                       | 5             | 7.60 <sup>a</sup><br>7.60 <sup>a</sup>  | 14,058<br>14,858     |

| CONTROL DATA CORP.  | CMD 9448-32            | 34                                                | 1                                               | 1         | 823                         |                                                         | 2             | 14.25 <sup>c</sup>                      | 27,846               |

| CONTROL DATA CORP.  | CMD 9448-64            | 34                                                | 1                                               | 3         | 823                         |                                                         | 4             | 14.25 <sup>c</sup>                      | 27,846               |

| CONTROL DATA CORP.  | CMD 9448-96            | 34                                                | 1                                               | 5         | 923                         |                                                         | 6             | 14.25 <sup>c</sup>                      | 27,846               |

| CONTROL DATA CORP.  | FSD 9715               | 35                                                | 0                                               | 10        | 823                         | 6                                                       | 8             | 8.78 <sup>a</sup>                       | 17,150               |

| CONTROL DATA CORP.  | FSD 9715-340           | 35                                                | 0                                               | 24        | 711                         | 8                                                       | 8             | d                                       |                      |

| CONTROL DATA CORP.  | FSD 9715-500           | 50                                                | 0                                               | 24        | 711                         | 8                                                       | 8             | d                                       |                      |

| CONTROL DATA CORP.  | MMD 9730-24            | 35                                                | 0                                               | 2(2) = 4  | 320                         |                                                         | 2             | 8.74 <sup>a</sup>                       | 17,080               |

| CONTROL DATA CORP.  | MMD 9730-80            | 35                                                | 0                                               | 5         | 823                         | 2                                                       | 1<br>6        | 18.18 <sup>b</sup><br>3.49 <sup>a</sup> | 35,525<br>6,825      |

| CONTROL DATA CORP.  | MMD 9730-160           | 35                                                | . 0                                             | 2(5) = 10 | 823                         | 5                                                       | 1             | 8.78ª                                   | 17,150               |

| CONTROL DATA CORP.  | SMD 9762               | 34                                                | 5                                               | 0         | 823                         | 2                                                       | 1<br>6        | 16.10 <sup>b</sup><br>1.65ª             | 31,450<br>3,230      |

| CONTROL DATA CORP.  | Lark II                | 35                                                | 0                                               | 10        | 823                         | 2                                                       | 3             | 6.63ª<br>6.27ª                          | 12,950<br>12,250     |

| CONTROL DATA CORP.  | SMD 9764               | 34                                                | 19                                              | 0         | 411                         | 4                                                       | 1             | 23.48 <sup>b</sup>                      | 45,866               |

Table 3-1. Values for Partitioning with Universal Firmware (DQ235)

\*For a 1-head partition, the value of cylinders/drive = tracks/surface. \*\*Calculated using 4 alternates.

<sup>a</sup>Less than standard RK06

<sup>b</sup>Greater than standard RK06

°CMD

<sup>d</sup>Most efficient use is not standard RK06/07 logical units but as one large logical unit or up to eight equal-size nonstandard units.

|                     | (2)             | (3)<br>Sectors<br>(Records) | (4)<br>Head<br>(Data Surf | aces)/    | (5)                  | (6)<br>Total Log<br>RK07<br>Units | RK06<br>Units | (8)**                                    |                  |

|---------------------|-----------------|-----------------------------|---------------------------|-----------|----------------------|-----------------------------------|---------------|------------------------------------------|------------------|

| (1)<br>Manufacturer | Model<br>Number | (Blocks)/<br>Track          | Drive<br>Removable        | Fixed     | Cylinders/<br>Drive* | 27.54MB<br>53,790                 | 27,126        |                                          | Sectors          |

| CONTROL DATA CORP.  | SMD 9766        | 34                          | 19                        | 0         | 823                  | 3                                 | 5             | 7.60 <sup>a</sup><br>7.60 <sup>a</sup>   | 14,858<br>14,858 |

| FUJITSU             | M-2283          | 35                          | · 0                       | 4         | 823                  | 2                                 | 1<br>5        | 3.51 <sup>a</sup><br>3.08 <sup>a</sup>   | 6,860<br>6,020   |

| FUJITSU             | M-2284          | 35                          | 0                         | 2(5) = 10 | 815                  | 5                                 | 1             | 7.34 <sup>a</sup>                        | 14,350           |

| FUJITSU             | 2311            | 35                          | 0                         | 4         | 589                  | 1                                 | 1<br>4        | 14.33 <sup>b</sup><br>0.21ª              | 28,000<br>420    |

| FUJITSU             | M-2333K         | 65                          | 0                         | 10        | 823                  | 8                                 | 8             | d                                        |                  |

| FUJITSU             | 2312            | 35                          | 0                         | 7         | 589                  | 2                                 | 1<br>6        | 18.18 <sup>b</sup><br>3.76 <sup>a</sup>  | 35,525<br>7,350  |

| FUJITSU             | M-2351A         | 47                          | 20                        | 0         | 842                  | 4                                 | 8             | 17.32 <sup>a</sup><br>3.36 <sup>a</sup>  | 33,840<br>6,580  |

| KENNEDY             | 5305            | 35                          | 0                         | 5         | 700                  | 2                                 | 1<br>5        | 7.16 <sup>a</sup><br>6.45 <sup>a</sup>   | 14,000<br>12,600 |

| KENNEDY             | 5380            | 35                          | 0                         | 5         | 823                  | 2                                 | 1<br>6        | 18.18 <sup>b</sup><br>3.49 <sup>a</sup>  | 35,525<br>6,825  |

| MITSUBISHI          | 2860-2          | 23                          | 0                         | 7         | 548                  | 1                                 | 1<br>4        | 17.22 <sup>b</sup><br>3.05 <sup>a</sup>  | 33,649<br>5,957  |

| NEC                 | D1220           | 35                          | 0                         | 4         | 530                  | 1                                 | 1<br>3        | 10.10 <sup>a</sup><br>9.89 <sup>a</sup>  | 19,740<br>19,320 |

| NEC                 | D1240           | 35                          | 0                         | 2(4) = 8  | 530                  | 2                                 | 1<br>6        | 20.07 <sup>b</sup><br>5.87 <sup>a</sup>  | 39,200<br>11,480 |

| NIPPON PERIPHERALS  | NP30-40         | 35                          | 0                         | 5         | 370                  | 1                                 | 1<br>3        | 5.19 <sup>a</sup><br>4.03 <sup>a</sup>   | 10,150<br>9,450  |

| NIPPON PERIPHERALS  | NP30-80         | 35                          | 0                         | 11        | 370                  | 2                                 | 1<br>6        | 16.95 <sup>b</sup><br>2.16 <sup>a</sup>  | 33,110<br>4,235  |

| NIPPON PERIPHERALS  | NP30-120        | 35                          | 0                         | 11        | 555                  | 3                                 | 1<br>8        | 25.82 <sup>b</sup><br>10.64 <sup>a</sup> | 50,435<br>20.790 |

| PRIAM               | 806             | 35                          | 0                         | 11        | 850                  | 7                                 | 8             | 1.18ª<br>d                               | 2,310            |

| PRIAM               | 807             | 35                          | 0                         | 11        | 1489                 | 8                                 | 8             | d                                        |                  |

| PRIAM               | 808             | 50                          | 0                         | 11        | 1489                 | 8                                 | 8             | d                                        |                  |

| PRIAM               | DISKOS 3350     | 35                          | 0                         | 3         | 561                  | 1                                 | 1<br>3        | 2.36 <sup>a</sup><br>2.09 <sup>a</sup>   | 4,620<br>4,095   |

| PRIAM               | 6650            | 35                          | 0                         | 3         | 1121                 | 2                                 | 1<br>5        | 4.89 <sup>a</sup><br>4.35 <sup>a</sup>   | 9,555<br>8,505   |

| PRIAM               | 15450           | 35                          | 0                         | 7         | 1121                 | 5                                 | 1             | 2.38ª                                    | 4,655            |

| TECSTOR             | Sapphire 160    | 35                          | 0                         | 12        | 700                  | 5                                 | 1             | 10.96 <sup>a</sup>                       | 21,420           |

| TECSTOR             | Sapphire 165    | 35                          | 0                         | 10        | 823                  | 5                                 | 1             | 8.78 <sup>a</sup>                        | 17,150           |

Table 3-1. Values for Partitioning with Universal Firmware (DQ235) (Continued)

\*For a 1-head partition, the value of cylinders/drive = tracks/surface. \*\*Calculated using 4 alternates.

<sup>a</sup>Less than standard RK06

<sup>b</sup>Greater than standard RK06

°CMD

<sup>d</sup>Most efficient use is not standard RK06/07 logical units but as one large logical unit or up to eight equal-size nonstandard units.

whether the last unit is an expanded or a partial unit.

The values in the table are calculated for the most efficient use of the drive; that is, total formatting capacity of the drive with a standard number of spare cylinders. The user may require another type of partitioning for a particular application, in which case the program will prompt and calculate for that application.

Parameters for disc drives not listed in Table 3-1 may be determined from manufacturer's specifications and the following: Determine the number of bytes per track from the manufacturer's specification. The number of bytes per sector (data and overhead) for DILOG controllers is 576. Divide the number of bytes per track by the number of bytes per sector. Drop the remainder. This value is the number of sectors per track. Then, number of sectors per track  $\times$  number of heads  $\times$  number of cylinders per drive = number of sectors per drive.

The user may require alternate cylinders, or spares, to compensate for media flaws, soft errors, or marginal drive conditions. The values in the table provide for four alternate cylinders. All three types of partitioning in the program make provisions for sparing. The program accounts for alternates when calculating the number and size of logical units.

If the number of logical units is to be changed, the configuration switches, shown in Figure 2-1, should also be changed after completion of format and test.

The descriptions below indicate what parameters will be changed as various elements are changed; for example, if the number of logical units is changed, the size of the logical units will change.

#### **1-Head Partition**

A 1-head partition is used for CMD drives. The column numbers below refer to Table 3-1. Parameters are developed as follows:

- 1. Determine the number of sectors per track (Column 3), heads per drive (Column 4), and tracks per surface (Column 5). For a 1-head partition, the number of tracks per surface is the same as cylinders per drive in the table.

- 2. Determine the number of alternate tracks (cylinders) per drive. The standard number of alternates is four.

- 3. Subtract the number of alternates from the tracks per surface.

- 4. The number of heads corresponds to the number of logical units.

- 5. Then, sectors per track  $\times$  heads per drive  $\times$  (tracks per surface minus alternates) = sectors per drive.

- 6. Sectors per drive  $\times$  512 = byte capacity.

For example, an AMPEX DFR-932 has 34 sectors per track, 2 heads per drive and 823 tracks/surface. If 4 alternates are required, then:

$34 \times 2 \times (823 - 4) = 55,692$  sectors/drive

Because there are two heads, there are two logical units.

$$\frac{55,692}{2} = 27,846 \text{ sectors/logical unit}$$

and

$27,846 \times 512 = 14.25$  megabytes/logical unit

#### 2-Head Partition

The parameters for 2-head partitioning are the same as for 1-head except the number of sectors/ logical unit is multiplied by 2:

- 1. Determine the number of sectors per track (Column 3), heads per drive (Column 4), and tracks per surface (Cylinders per Drive, Column 5).

- 2. Determine the number of alternate tracks (cylinders) per drive. The standard number of alternates is four.

- 3. Subtract the number of alternates from the tracks per surface.

- 4. Then, sectors per track × heads per drive × (tracks per surface minus alternates) = sectors per drive.

- 5. Sectors per drive  $\times$  512 = byte capacity.

For example, a CDC 9730-24 has 35 sectors per track, 4 heads per drive and 320 tracks per surface. If 4 alternates are required, then:

$35 \times 4 \times (320-4) = 44,240$  sectors/drive

Because there are four heads, and two heads comprise one logical unit, there are two logical units.

$$\frac{44,240}{2} = 22,120 \text{ sectors/logical unit}$$

and

$22,120 \times 512 = 11.32$  megabytes/logical unit

#### Vertical Partition

With vertical partitioning, the user may select the number of logical units or the size of the logical unit. If the number of logical units is selected, the logical units will be of equal size. If the size of the logical units is selected, all logical units may not be of equal size. For example there may be 2 equal RK07 logical units of 53,790 sectors/logical unit and a partial RK06 logical unit of 31,450 sectors/logical unit.

Parameters for vertical partitioning are determined as follows:

The user specifies the number of logical units (all logical units are of equal size):

- 1. Determine the required number of alternate cylinders per drive. Subtract the number of alternates from the number of cylinders per drive (Column 5). This value is the usable cylinders per drive.

- 2. Determine the number of logical units per drive required. Then,

- 3. Number of usable cylinders per drive divided by number of logical units required = Number of cylinders per logical unit. The remainder is assigned as alternate.

- 4. Number of cylinders per logical unit × sectors per track × number of heads = Number of sectors per logical unit.

- 5. Number of sectors per logical unit  $\times$  512 = Megabyte capacity per logical unit.

For example, if the user has a Century Data drive, Model T-82RM and 4 alternates (standard) and 3 logical units are required, then

823 - 4 = 819 usable cylinders

and

$\frac{819}{3} = 273$

If there was a remainder, the number of alternates would be more than initially selected.

Then,

$273 \times 34 \times 5 = 46,410$  sectors per logical unit and

$46,410 \times 512 = 23.76$  Mbytes per logical unit

The user specifies the size of logical units in sectors per logical unit (the last logical unit will be a different size).

- 1. Determine the required number of alternate cylinders per drive. Subtract the number of alternates from the number of cylinders per drive (Column 5). This value is the usable cylinders per drive.

- 2. Determine the required number of sectors (blocks) per logical unit. Then,

- 3. Sectors per track (Column 3)  $\times$  number of heads (Column 4) divided into sectors per logical unit = cylinders per logical unit. If there is a remainder, the number of cylinders per logical unit is rounded off to the next higher number.

- 4. Number of usable cylinders divided by cylinders per logical unit = number of logical units. If there is a remainder, the number of logical units is rounded off to the next higher number.

- 5. Number of cylinders per logical unit  $\times$  number of full (equal size) logical units = Number of cylinders full (equal size) logical units.

- 6. Number of usable cylinders per drive minus number of cylinders in full logical units = Number of cylinders in partial logical unit.

For example, if the user has a Century Data drive, Model T-82RM, and 4 alternates and 53,790 sectors per logical unit (standard RK07) are required, then

$$823 - 4 = 819$$

usable cylinders

and

$$\frac{53,790}{34 \times 5} = 316.41$$

which becomes

317 cylinders per logical unit

then,

$$\frac{819}{317} = 2.58 \text{ logical units per drive}$$

or 2 RK07 units and 1 partial RK06 unit.

For the partial logical unit,

$317 \times 2 = 634$

819 - 634 = 185 cylinders per partial logical unit

Sectors per the partial unit are calculated as follows:

$185 \times 34 \times 5 = 31,450$  sectors per partial logical unit.

#### **Partitioning Program**

The name of the program is DMXXD, where XX is the revision number of the program.

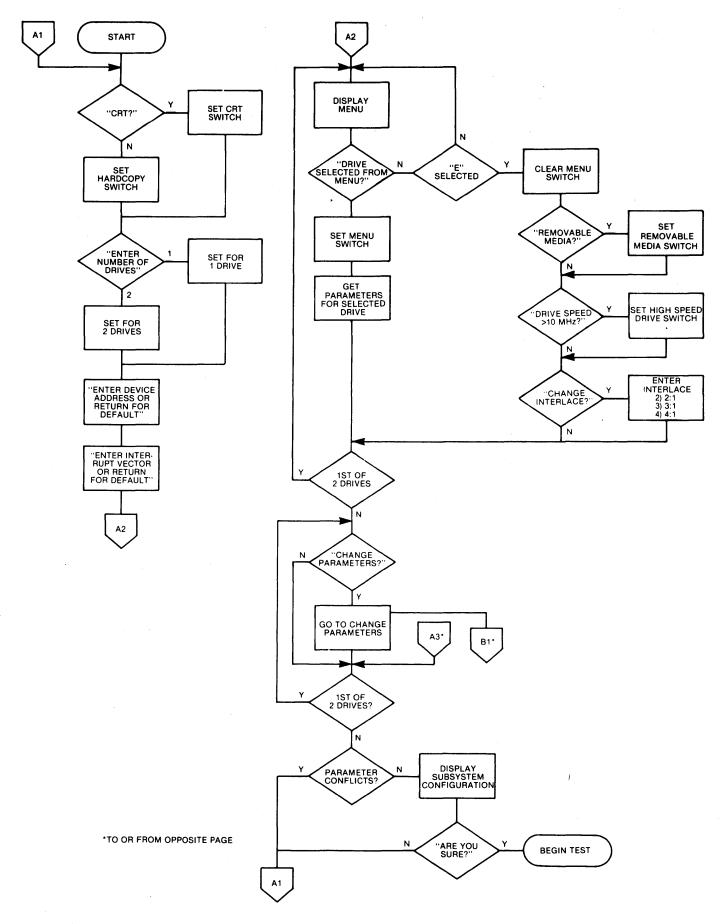

Figure 3-2 is a flow diagram of the program. The statements in quotes are program prompts. The pentagonoid symbols with a letter and number, such as "A1." are reference points for breaks in the flow. The "A" designation refers to the first page (Format) and the "B" designations refer to the second page (Change Parameters). The following descriptions refer to the first (Format) page of the diagrams.

The following paragraphs may contain values enclosed in "<>." These values are the default values and may be selected by pressing the RETURN key. To assist in determining whether a parameter needs to be changed, the current values are displayed enclosed in "()." The program prompts and displays are indicated in capital letters.

When the program is initialized the following display will appear on the terminal:

DILOG'S UNIVERSAL FIRMWARE AND DIAGNOSTIC PROGRAM VERIFIES PROP-ER FUNCTIONING OF THE DILOG RK06/ **RK07 EMULATING DISC CONTROLLER** AND FORMATS THE DISC TO YOUR SPECIFICATIONS.

YOUR DEFAULT PARAMETERS ARE:

SECTORS HEADS \_\_\_\_\_ CYLINDERS \_\_\_\_

ALTERNATES. SIZE OF LOGICAL UNIT (RECORDS)

The parameters displayed are calculated for the efficiency of most applications. The units of measure are as follows: sectors/track; heads/drive; cylinders/drive: alternates/drive: and the size of logical unit in sectors/logical unit.

The next display will be:

\*\*\*\*\*\* \*\*\*\*\* RESTART ADDRESS IS 2000 \*\*\*\*\* \*\*\*\*\*^C RESTARTS CURRENT TEST \*\*\*\* \*\*\*\*\*\*\*

To restart, press the CTRL and X keys at the same time, or CTRL and C.

The next query is:

ARE YOU RUNNING THE DIAGNOSTIC VIA A CRT?  $\langle Y \rangle$

If the answer is NO, the CRT will not display the current cylinder address during the test program.

The next prompt is:

ENTER THE NUMBER OF DRIVES <1>

Enter 1 or 2. If 1 is entered, the next queries will refer only to Drive 0. If 2 drives are selected, the program will prompt for Drive 0 and Drive 1.

The next displays will be:

#### ENTER DM DEVICE ADDRESS <777440>? ENTER DM INTERRUPT VECTOR <000210>?

Enter the proper device address and interrupt vector. The address and interrupt vector are factory set unless the user requested an alternate address or vector (see Section 2).

The next question will be:

LSI (Y OR N)?

Answer Yes.

The menu of drives will appear next, with the following:

#### \*\*\*\*\* DRIVE 0 \*\*\*\*\*

#### ENTER NUMBER CORRESPONDING TO DISC DRIVE

#### N = NEXT PAGE P = PREVIOUS PAGE E =ENTER DRIVE PARAMETERS

#### ENTER >

From the menu, the appropriate drive may be selected. If E is pressed, the program will prompt for drives not listed in the menu or will prompt to change parameters in case of conflicts in constraints. If the drive selected is not listed in the menu, the program will prompt:

#### DOES DRIVE 0 HAVE REMOVABLE MEDIA? <N> IS DRIVE 0'S SPEED GREATER THAN 10 MHZ? <N>CHANGE DRIVE 0 INTERLACE FACTOR

(X:1)? <N> Enter the appropriate response (available from

the drive manufacturer's manual). If the answer to the interlace factor question is Yes, the following will be displayed:

#### SELECT ONE OF THE FOLLOWING INTER-LACE FACTORS

| (2) | 2:1 |

|-----|-----|

| (3) | 3:1 |

| (4) | 4:1 |

| (5) | 5:1 |

| (6) | 6:1 |

(

\*TO OR FROM OPPOSITE PAGE

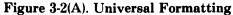

#### Figure 3-2(B). Universal Formatting-Change Parameters

#### PLEASE ENTER THE CORRESPONDING NUMBER >

Enter the desired interlace factor (2, 3, 4, 5, or 6). An interlace of 4:1 is recommended for drives with speeds greater than 10 MHz, and the default will automatically be set at 4:1 if Yes was answered to the query to change the interlace factor.

#### Note

The program responds with the minimum number of inquiries; for example, if a drive is selected from the menu, the program will not prompt for the number of sectors, heads and cylinders, because these responses are predetermined.

If a drive is selected from the menu, the next display will be:

DO YOU WISH TO CHANGE FORMAT PARAMETERS? <N>

#### Note

The format parameters are those last entered. Each time there is a change, the program will retain that change.

If the response is No, the next display will show the configuration. An example of RK07 is as follows:

#### DISC SUBSYSTEM CONFIGURATION

| LOGICAL<br>UNIT | PHYSICAL<br>DRIVE | MEGABYTES | RECORD<br>SIZE |

|-----------------|-------------------|-----------|----------------|

| DM0             | 0                 | 27.59     | 53900          |

| DM1             | 0                 | 27.59     | 53900          |

| DM2             | 0                 | 27.59     | 53900          |

| DM3             | 0                 | 25.82     | 50435          |

| DM4             | 1                 | 27.59     | 53900          |

| DM5             | 1                 | 27.59     | 53900          |

| DM6             | 1                 | 27.59     | 53900          |

| DM7             | 1                 | 25.82     | 50435          |

PHYSICAL DRIVE 0 HAS 44 ALTERNATE TRACKS

PHYSICAL DRIVE 1 HAS 44 ALTERNATE TRACKS

#### ARE YOU SURE?

If the answer to this prompt is No, the program will return to the beginning. If the answer is Yes, the program will continue.

The following descriptions refer to the second (Change Parameters) page of the diagram.

If the answer is Yes to the prompt:

#### DO YOU WISH TO CHANGE FORMAT PARAMETERS? <N>

the next prompt will be:

#### CHANGE NUMBER OF SECTORS (XX)? <N> CHANGE NUMBER OF HEADS (XX)? <N> CHANGE NUMBER OF CYLINDERS (XXX)? <N>

These prompts are for adding a drive that is not on the menu. The values (after HOW MANY?) to be entered are in the drive manufacturer's manual. The next prompt of change parameters is for drives which are or are not on the menu:

CHANGE NUMBER OF ALTERNATES (XX)? <N>

The standard number of alternates selected is 4. If a CMD drive is selected, there will be no further questions. If Yes, HOW MANY? will appear. The next query is:

CHANGE TYPE OF PARTITION (XXXXXX)? <N>

If the answer is Yes, the following display will appear:

SELECT ONE OF THE FOLLOWING TYPES OF PARTITIONING

- (1) 1-Head partition

- (2) 2-Head partition

- (3) Vertical partition

PLEASE ENTER THE CORRESPONDING NUMBER>

Enter the number corresponding to the type of partition desired. If 1-Head or 2-Head partitioning is selected there will be no further queries.

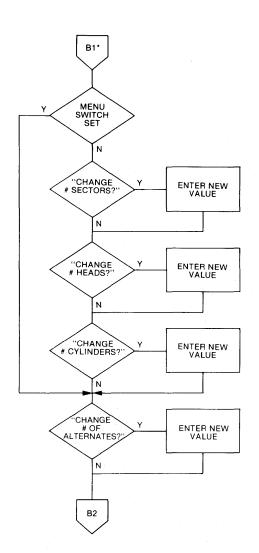

Next to appear is:

STANDARD SIZE UNITS? <N>

If Yes, the program will prompt with selection of RK07 or RK06. If RK07 is selected, the program will divide the record size into RK07 units, and the remaining records will be an RK06 unit. Standard sizes are shown in Table 3-1. After selection of standard units, the next message will be:

AFTER CALCULATING STANDARD SIZE UNITS ON DRIVE 0, YOU HAVE \_\_\_\_\_\_ CYLINDERS NOT YET ALLOCATED (\_\_\_\_\_\_ MEGABYTES).

IF YOU WOULD LIKE, I COULD CREATE ANOTHER UNIT, WHICH WILL BE SMALLER THAN YOUR STANDARD SIZE UNITS, OR I COULD ALLOCATE THE CYLINDERS AS ALTERNATES.

PLEASE ENTER THE NUMBER OF CYLINDERS YOU WOULD LIKE ME TO

ALLOCATE AS ALTERNATES, ANY RE-MAINDER WILL BE ALLOCATED AS ANOTHER UNIT.

If the standard number of alternates previously selected is adequate (default is 4), enter 0. The next display will be:

CHANGE SIZE OF LOGICAL UNIT (RECORDS) (XXXXX)? <N> CHANGE NUMBER OF LOGICAL UNITS (X)? <N>

The program will pause for a response after each question. If Yes is answered to either of the above questions, the system will respond with "HOW MANY?" Enter the desired value and the system will respond with the next question. The user may change the size of the logical units or the number of logical units, but not both.

If two drives were selected, the program will repeat the above sequence for the second drive, beginning with:

#### \*\*\*\*\* DRIVE 1 \*\*\*\*\* ENTER NUMBER CORRESPONDING TO DISK DRIVE N=NEXT PAGE P=PREVIOUS PAGE E=ENTER DRIVE PARAMETERS

If the constraints are not violated, the Disc Subsystem Configuration and ARE YOU SURE? will appear. If the subsystem constraints have been violated, a message will be displayed explaining the violation. Any violations must be corrected in order to continue. Some possible errors are:

- 1) More than 8 logical units on the subsystem

- 2) More than 8 heads with 1-head partition

- 3) More than 16 heads with 2-head partition

- 4) Odd number of heads with 2-head partition

- 5) Maximum logical unit size exceeded

To resolve this conflict, the Change Format Parameters option may be used to change the number of logical units on Drive 0. To provide logical units of equal size on both drives, the number of logical units may be changed to 4 on each drive. Restart the current address with ^C, repeat the sequence above up to the question CHANGE NUMBER OF LOGICAL UNITS?, and answer Y. When HOW MANY? appears, answer 4. Repeat this sequence for Drive 1.

Examples of errors on a single drive when changing the type of partition are as follows:

#### FORMAT PARAMETER CONFLICTS DRIVE 0

MAXIMUM NUMBER OF HEADS WITH 1-HEAD PARTITION IS 8 or

#### FORMAT PARAMETER CONFLICTS DRIVE 1

MAXIMUM NUMBER OF HEADS WITH 2-HEAD PARTITION IS 16

#### or

#### FORMAT PARAMETER CONFLICTS DRIVE 0

#### MAXIMUM NUMBER OF HEADS MUST BE AN EVEN NUMBER WITH 2-HEAD PARTITION

Examples of errors on a single drive when changing the size of the logical units is as follows:

> FORMAT PARAMETER CONFLICTS DRIVE 0

LOGICAL UNIT SIZE IS 270, 720 MAXIMUM LOGICAL UNIT SIZE IS 270, 336

or

#### FORMAT PARAMETER CONFLICTS DRIVE 0

#### LOGICAL UNIT SIZE IS BIGGER THAN THE DISC

The algorithm for mapping, that is, what the controller should map, is as follows:

| Record Number   | = | Correct Cylinder Address |

|-----------------|---|--------------------------|

| Sector/Cylinder |   | + Remainder (1)          |

| Remainder (1)   | - | Correct Head Address     |

| Sector/Track    |   | + Remainder (2)          |

Remainder (2) = Sector Address

A mapping error is displayed during the Random Read test as follows:

#### \*\*\*\*\*MAPPING ERROR\*\*\*\*\*

RECORD NUMBER = XXX SECTOR/CYLINDER = XXX SECTOR/TRACK = XXX DRIVE NUMBER = XXX

CORRECT ADDRESS CYLINDER = XXX HEAD = XXX SECTOR = XXX

CONTROLLER ADDRESS CYLINDER = XXX HEAD = XXX SECTOR = XXX

If the response to "ARE YOU SURE" is Yes, the program will begin the Diagnostic Test Program.

#### **Diagnostic Test Program**

To begin the Diagnostic Test Program, the following display will appear:

####

As tests are performed, the system will indicate that activity by displaying:

TESTING CONTROLLER REGISTERS TESTING DATA BUFFERS TESTING DMA TESTING ECC LOGIC

The next display will be the switches:

**DEFINITIONS:**

L/U CROSSOVER: 1ST LOGICAL UNIT ON 2ND DRIVE

BOOTSTRAP ENABLE: ON = ENABLED, OFF = DISABLED

ECC SWITCH: ON = CONTROLLER MODE, OFF = SOFTWARE MODE

LAST L/U: LAST LOGICAL UNIT ON SUBSYSTEM

SET SWITCHES 1-3 TO A BINARY WEIGHTED VALUE OF X.

SET SWITCHES 6-8 TO A BINARY WEIGHTED VALUE OF X.

USE (C) TO CONTINUE

If the switches are set incorrectly, the message will repeat. Switch settings are described in Section 2. If the switches are set correctly, the program will skip to "Test Disc Drive."

Pressing the SPACE bar will cause the diagnostic to halt the current test and proceed to the next one. If any of the tests fail, an error message will be displayed, followed by:

USE (C) TO CONTINUE USE (O) TO TRANSFER TO ODT USE (L) TO REBOOT YOUR SYSTEM

The format/test program contains the following:

1. TEST CONTROLLER A. Registers B. Data Buffer C. DMA

- D. ECC

- 2. TEST DISC DRIVE A. Disc Ready

- A. Disc Ready

- B. Disc Restore (seek to cylinder 0)

- 3. FORMAT

- A. Write Headers

- **B.** Read Headers

- C. Write Data Test Pattern

- D. Read Data Test Pattern

- 4. SEQUENTIAL READ

- 5. SELECTED READ

- 6. RANDOM SEEK, READ

- 7. RANDOM SEEK, WRITE, READ, AND COMPARE

- 8. ASSIGN ALTERNATE TRACK

#### **Test Controller**

The program will automatically test the controller registers and data buffer. The program will only display error messages during this test; the display will be:

#### DATA BUFFER ERROR

or the mnemonics of the controller registers and the location and contents (in Octal). The display of the registers is followed by a 4-line message to aid in isolating the specific problem.

#### Note

Whenever an error occurs and the registers are displayed, an audio alarm signal is generated to notify the operator.

The 4-line message is as follows:

| DISC ADDRESS |              |  |  |  |

|--------------|--------------|--|--|--|

| HEAD         | CYLINDER     |  |  |  |

| TYPE OF C    | OMMAND       |  |  |  |

| CONTROL S    | STATUS ERROR |  |  |  |

| DRIVE STA    | TUS          |  |  |  |

"DISC" lists the sector, head and cylinder (in decimal) where the error occurred. An example of Type of Command is Read Data Command. An example of Control Status is Seek Error.

The ECC logic test is as follows: The program selects whether a correctable or noncorrectable error is to be programmed; then the program creates an error; writes the data with an error to the controller; reads to memory; then the program decides whether the error is noncorrectable or correctable.

If noncorrectable, the program checks to ensure an error has been returned by the controller.

If correctable, the program checks to make sure there has been no error returned by the controller, and checks to ensure the error was corrected in the proper manner. If this test fails, the message is one or more of the following:

CONTROLLER INDICATES CORRECTABLE ERROR CONTROLLER INDICATES NONCORRECT-ABLE ERROR ERROR BURST IS CORRECTABLE ERROR BURST IS NONCORRECTABLE ERROR BURST WAS NOT CORRECTED

The space bar (SP) is used to exit from this test.

The program will next display:

USE C TO CONTINUE USE O TO TRANSFER TO ODT USE L TO REBOOT YOUR SYSTEM

"C" is used to continue the test. "O" is used for ODT (on-line debugging technique). "L" is used to initiate the system bootstrap.

#### Test Disc Drive

After the controller test is performed, the program will automatically test the drive for ready and restore. The disc address is not displayed during this test. If the disc will not restore, the program will display the register for cylinder 0.

#### Format

If all tests are successful, the program will display the proper switch settings for the specified configuration, followed by:

#### USE (C) TO CONTINUE

The program will next display:

AUTOMATICALLY ASSIGN ALTERNATES?

If the response to this question is Yes, the diagnostic program will assign an alternate cylinder without waiting for operator approval when a media flaw is detected during formatting.

The program will then ask what part of the system to format. Some of these questions will be suppressed if the response is Yes to a previous question.

The operator may either select logical units sequentially or select one or more specific logical units to be formatted. Program messages are presented for formatting in logical unit number sequence:

FORMAT ENTIRE SUBSYSTEM? <N>

- FORMAT ENTIRE DRIVE 0? <N>

- FORMAT ENTIRE DRIVE 1? <N>

FORMAT ALTERNATE CYLINDERS DRIVE 0? <N>

FORMAT ALTERNATE CYLINDERS DRIVE 1? <N>

| FORMAT DM0? <n></n> |

|---------------------|

| FORMAT DM1? <n></n> |

| FORMAT DM2? <n></n> |

| FORMAT DM3? <n></n> |

| FORMAT DM4? <n></n> |

| FORMAT DM5? <n></n> |

| FORMAT DM6? <n></n> |

| FORMAT DM7? <n></n> |

#### Note

Before any write operation, the program will display ARE YOU SURE? This aids the operator in preventing reformatting of a previously formatted logical unit (possibly destroying good data).

During formatting, the following messages will appear sequentially:

WRITING HEADERS CURRENT CYLINDER ADDRESS -----

READING HEADERS CURRENT CYLINDER ADDRESS -----

WRITING DATA TEST PATTERN -----CURRENT CYLINDER ADDRESS -----

READING DATA TEST PATTERN ———— CURRENT CYLINDER ADDRESS ————

When reading and writing headers, the program will display the cylinder addresses sequentially. The test pattern tests are also sequentially selected, and the cylinder address displayed will correspond to the current address being read.

#### Note

During formatting and testing, the current cylinder address will appear only if the diagnostic test program is being run on a CRT.

After each logical unit is formatted, the display will be:

#### DM \_\_\_\_\_ FORMAT AND VERIFICATION COMPLETE

If an error occurs during formatting, a message will be displayed. If a media flaw is detected but automatic alternate assignment was not selected, the program will display:

#### ASSIGN ALTERNATE CYLINDER? <Y>

A Yes response will map out the detected media flaw.

When formatting is complete, the diagnostic program will proceed to the Sequential Read portion of the test.

#### Sequential Read

For this test, the display will be: