# SYS68K/IBC-20 Rev.2 Hardware User's Manual

Edition No. 2 April 1997

P/N 202728 FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE COMPUTERS

# **INTRODUCTION**

## **Table of Contents**

| 1. | GENERAL DESCRIPTION          | 1-1 |

|----|------------------------------|-----|

| 2. | FEATURES OF THE IBC-20       | 2-1 |

| 3. | SPECIFICATIONS OF THE IBC-20 | 3-1 |

| 4. | ORDERING INFORMATION         | 4-1 |

| 5. | HISTORY OF MANUAL REVISIONS  | 5-1 |

# List of Figures

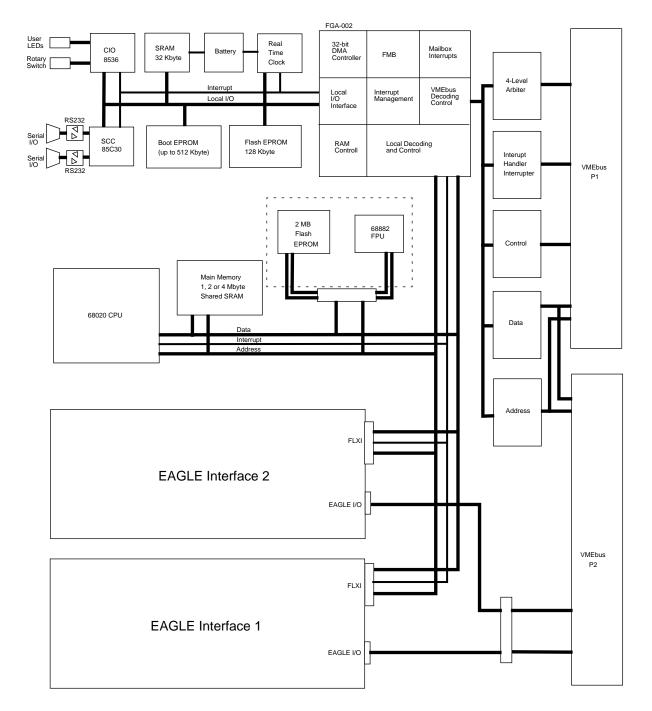

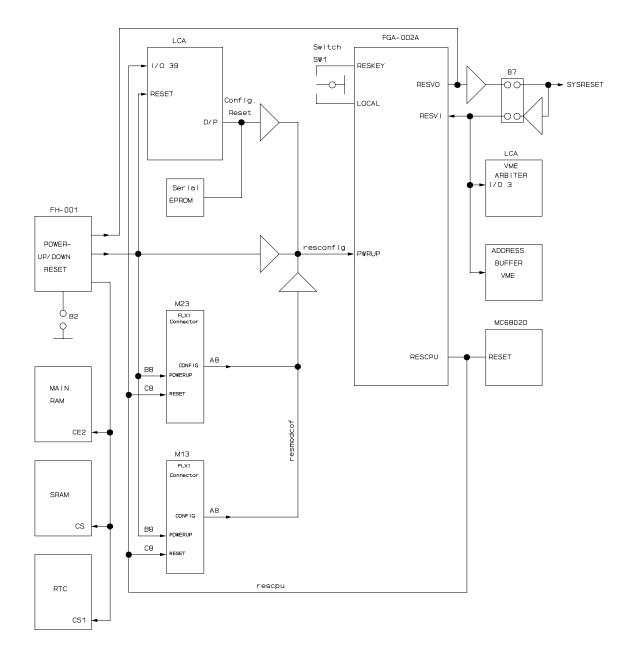

| Figure 1-1: Block Diagram of the IBC-20 |

|-----------------------------------------|

|-----------------------------------------|

This page intentionally left blank

### 1. GENERAL DESCRIPTION

The IBC-20 is a high performance basic controller board which uses the Motorola MC68020 32-bit microprocessor.

The board design provides System Control functions for the VMEbus environment. It uses all features of the powerful FORCE COMPUTERS Gate Array FGA-002A.

A total of up to 4 Mbytes of static RAM is provided for the Shared Main Memory which is also accessible from VME.

The IBC-20 can be upgraded with the Floating Point Unit MC68882. The IBC-20 can also be upgraded with up to 8 Mbyte System Memory with FLASH EPROM devices by installing the IBC MOD-1 module on the board. The IBC MOD-1 is described in detail in Section 8 of this manual.

Additional features include a serial I/O debugging port, three 16-bit counters/timers, 128 Kbytes of nonvolatile read/write RAM by Flash Memory, a Real Time Clock/Calendar and 32 Kbytes of local SRAM, with battery backup on board.

The powerful real-time monitor VMEPROM with file manager and Real Time Kernel (PDOS compatible) is included.

The IBC-20 board is compatible to the following standards:

IEEE 1014-87 IEC 821 IEC 297

The block diagram is presented on the next page in Figure 1-1.

#### FIGURE 1-1: Block Diagram of the IBC-20

## 2. FEATURES OF THE IBC-20

#### • MC68020 Microprocessor

The board provides the MC68020 microprocessor running at 25 MHz clock frequency for onboard intelligence and performance.

#### • 32-bit DMA Controller

An independent 32-bit DMA Controller provides high speed data transfer between the VMEbus and the Main RAM. The DMA controller is contained in the FGA-002A. The DMA Controller transfers data entirely independent from the local processor and is able to transfer data across the VMEbus without affecting the performance of the processor. To increase the data throughput, the DMA controller uses a 32-byte FIFO for internal data storage. The read and write operations are executed in bursts of eight transfer cycles.

#### • MC68882 Floating Point Coprocessor Upgrade

The IBC-20 board may be upgraded with MC68882 Floating Point Coprocessor by installing the module IBC MOD-1 on the baseboard.

#### • FLXi/EAGLE Module Interfaces

Two EAGLE Module interfaces on the base board are provided for the installation of one or two EAGLE modules. The interfaces are built according to the EAGLE Module specification of FORCE COMPUTERS, which allows installing any module that conforms to this standard. The EAGLE module interfaces provide the nonmultiplexed, asynchronous FLXibus, supporting 32-bit data and address bus architecture with dynamic bus sizing and master/slave capability. The FLXibus allows the EAGLE module to access all resources on the base board and the VMEbus. In addition, the 64 VMEbus user I/O pins are connectable to the I/O Connector of the EAGLE Module Interface 1, or may be shared by the two EAGLE modules, one using the pins of row A and the other using the pins of row C.

#### • 4 Mbyte Shared Main Memory

The Main RAM is built with low power static memory devices which provide up to 4 Mbyte capacity. Backup capability is given through the VMEbus +5V STBY line. The Main memory is accessible by the DMA controller, by any FLXibus master and also from the VMEbus.

#### • 8 Mbyte System Flash-EPROM Upgrade

Up to 8 Mbyte System Memory (FLASH EPROM devices) is available by using the module IBC MOD-1.

#### • 32 Kbyte Local SRAM

32 Kbyte of battery backed up memory is provided by the local SRAM. The battery backs up the SRAM during power-off for at least one year. Backup capability is also given through the +5V STDBY line of the VMEbus.

#### • 128 Kbyte FLASH EPROM

The local FLASH EPROM provides 128 Kbyte of nonvolatile read/write memory without the need of battery backup for saving data.

#### • 512 Kbyte Boot EPROM Socket

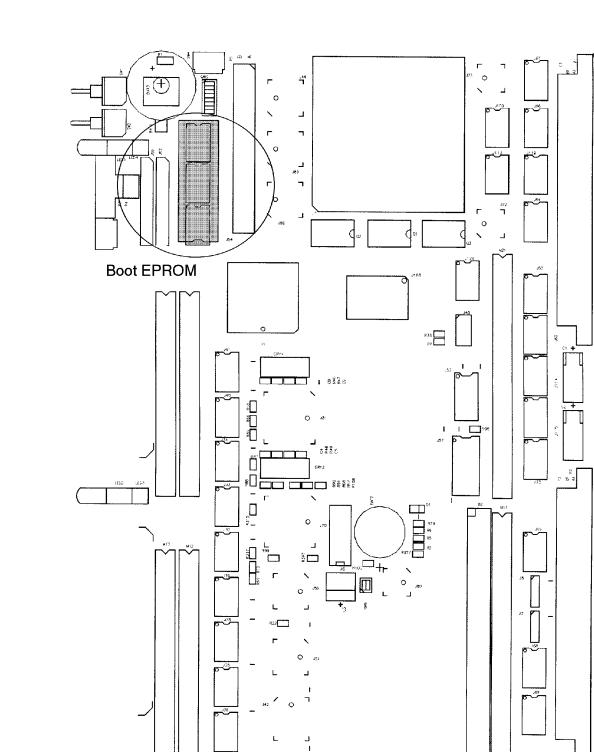

A single EPROM socket is provided for 128Kx8 to 512Kx8 JEDEC compatible memory devices. The base board EPROM contains the boot firmware and the real-time monitor VMEPROM.

#### • Two RS-232 Serial I/O Ports

Two serial I/O ports are available on the front panel providing RS-232C compatible interface signals at the 9-pin micro D-Sub connectors. This enables direct connection to standard terminals and allows the channels to be used as console and debugging ports.

#### • RTC 72423 Real Time Clock

The Real Time Clock (RTC 72423) provides battery backed up time-of-day, date counter with auto leap year, 12 and 24 hour format and interrupt capability.

#### • 4 Timers

A total of four independent timers are available on the IBC-20 board. The FGA-002A gate array contains an 8-bit timer with programmable source clocks. Three 16-bit timers are located in the 8536 Counter/Parallel-I/O device (CIO), two of them internally linkable to a 32-bit timer unit. Each timer can be used for interrupt generation to the microprocessor. The FGA-002A timer is also usable as system watchdog timer which is able to assert the SYSFAIL\* signal of the VMEbus.

#### • VMEbus Master/Slave Interface

The VMEbus interface of the IBC-20 allows the board to act as master and slave for data transfers on the VMEbus. The 32-bit addressing capability together with support of extended, standard, and short I/O address modifier codes allows the user to interface to a wide range of VMEbus products. Unaligned transfers and Read-Modify-Write cycles are fully supported.

#### • VMEbus Interrupter and Interrupt Handler

The IBC-20 provides an Interrupter function which enables the board to send interrupts to the VMEbus on each of the seven interrupt lines. Interrupt requests from the VMEbus are handled by the FGA-002A device, which is able to convert the VME interrupt level to any interrupt level for the local processor.

#### • 4-Level VMEbus Arbiter

A four-level bus arbiter allows arbitration of the data transfer bus in the round robin, the prioritized and the prioritized round robin algorithm. Several bus release functions are implemented for multiprocessor applications.

#### • VMEbus System Control Functions

The board features Slot-1 system control functions such as SYSCLOCK driver, IACK Daisy Chain driver and 4-Level bus arbiter with Bus clear generation. The VMEbus system control signal lines ACFAIL\* and SYSFAIL\* are supported and may generate interrupts to the local processor. SYSRESET is driven to and received from the VMEbus.

#### • 2 Message Broadcast Channels (FMB)

Two independent 8-bit wide Message Broadcast Channels provide a fast and effective mechanism to communicate with and synchronize up to 20 CPU boards in VMEbus system in only one write cycle.

#### 8 Mailboxes

Multiprocessing support is provided by the eight Mailboxes. The Mailboxes are local, VME addressable and generate an interrupt to the local processor on a programmable level.

This page intentionally left blank

## 3. SPECIFICATIONS OF THE IBC-20

| CPU type                                                                                                | 68020            |

|---------------------------------------------------------------------------------------------------------|------------------|

| CPU clock frequency                                                                                     | 25.0 MHz         |

| Coprocessor IBC-20/x-2                                                                                  | 68882            |

| DMA controller (FGA-002)                                                                                | 32-bit           |

| Shared SRAM capacity IBC-20/1<br>IBC-20/2<br>IBC-20/4                                                   | 2 Mbyte          |

| SRAM capacity with on-board battery backup                                                              | 32 Kbyte         |

| FLASH EPROM capacity IBC-20/x<br>IBC-20/x-2<br>IBC-20/x-2N                                              | <b>,</b>         |

| No. of EPROM Sockets<br>Maximum capacity                                                                | 1<br>512 Kbyte   |

| Serial I/O interfaces (85C30)                                                                           | 2 (RS232C)       |

| 16-bit timer<br>8-bit timer                                                                             | 3<br>1           |

| Real Time Clock with on-board battery backup                                                            | 72423            |

| VMEbus interface A32, A24,A16:D8,D16,D32,UAT,RMW A32,A24:D8,D16,D32,RMW                                 | Master<br>Slave  |

| Four-level arbiter<br>SYSCLK driver                                                                     | yes<br>yes       |

| EAGLE module interfaces with FLXibus (Master/Slave)<br>EAGLE module interfaces with access to VMEbus P2 | 2 of 2<br>2 of 2 |

| Mailbox interrupts                                                                                      | 8                |

Specifications of the IBC-20 are continued on the next page.

## Specifications of the IBC-20 continued

| FORCE Message Broadcast FMB-FIFO 0 (standard FMB-FIFO 1 (high                                                                                                                                   |                                                                                |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| VMEbus and local interrupt handler<br>VMEbus interrupter<br>Software programmable IRQ level and vector<br>IACK Daisy Chain Driver                                                               | 1 to 7<br>1 to 7<br>yes<br>yes                                                 |  |

| RESET/ABORT Switch                                                                                                                                                                              | yes                                                                            |  |

| VMEPROM based firmware installed on all versions                                                                                                                                                | yes                                                                            |  |

| (without EAGLE modules) +1                                                                                                                                                                      | 5V max 3.0A<br>2V max 100 mA<br>2V max 70 mA                                   |  |

| Operating temperature with forced air cooling<br>Storage temperature<br>Relative humidity (non-condensing in %)<br>Board Dimensions<br>No. of slots used, with optional EAGLE modules installed | 0°C to +50°C<br>-40°C to +85°C<br>5 to 95<br>234 x 160 mm / 9.2 x 6.3 in.<br>1 |  |

## 4. ORDERING INFORMATION

| SYS68K/IBC-20/1        | 25.0 MHz MC68020 based intelligent I/O controller board with DMA, 1 Mbyte shared SRAM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included.                               |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS68K/IBC-20/2        | 25.0 MHz MC68020 based intelligent I/O controller board with DMA, 2 Mbyte shared SRAM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included.                               |

| SYS68K/IBC-20/4        | 25.0 MHz MC68020 based intelligent I/O controller board with DMA, 4 Mbyte shared SRAM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included.                               |

| SYS68K/IBC-20/2-2      | 25.0 MHz MC68020, MC68882 based intelligent I/O controller board with DMA, 2 Mbyte shared SRAM, 2 Mbyte FLASH-EPROM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included. |

| SYS68K/IBC-20/2-2N     | 25.0 MHz MC68020 based intelligent I/O controller board with DMA, 2 Mbyte shared SRAM, 2 Mbyte FLASH-EPROM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included.          |

| SYS68K/IBC-20/4-2      | 25.0 MHz MC68020, MC68882 based intelligent I/O controller board with DMA, 4 Mbyte shared SRAM, 2 Mbyte FLASH-EPROM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included. |

| SYS68K/IBC-20/4-2N     | 25.0 MHz MC68020 based intelligent I/O controller board with DMA, 4 Mbyte shared SRAM, 2 Mbyte FLASH-EPROM, 2 serial I/O ports, 2 EAGLE module interfaces (FLXibus), VMEPROM. Documentation included.          |

| SYS68K/IBC-20/UM       | User's Manual set for the SYS68K/IBC-20 product including hardware, firmware and FGA-002 manuals.                                                                                                              |

| SYS68K/CABLE MICRO-9/1 | Adapter cable 9-pin micro D-sub male connector to 9-pin D-sub female connector, length 2 meters.                                                                                                               |

| EAGLE MODULE SPEC/UM   | EAGLE Module Specification including FLXibus and software interface description.                                                                                                                               |

This page intentionally left blank

## 5. HISTORY OF MANUAL REVISIONS

| Revision No. Description |                                                                    | Date of Last Change |

|--------------------------|--------------------------------------------------------------------|---------------------|

| 0                        | This manual describes the IBC-20 revision 2 printed circuit board. | FEB/05/1993         |

| 1                        | Editorial changes have been made throughout this manul             | SEP/06/1993         |

| 2                        | Editorial changes have been made.                                  | APRIL/1997          |

# **INSTALLATION**

This page was intentionally left blank

## WARNING

TO AVOID MALFUNCTIONS AND COMPONENT DAMAGE, PLEASE READ THE COMPLETE INSTALLATION PROCEDURE BEFORE THE BOARD IS INSTALLED IN A VMEBUS ENVIRONMENT. This page was intentionally left blank

## TABLE OF CONTENTS

| 1.  | GENERAL                    | 1-1 |

|-----|----------------------------|-----|

| 1.1 | The MODE Switch            |     |

| 1.2 | The Toggle Switches        | 1-1 |

| 1.3 | Connection of the Terminal |     |

| 1.4 | The Default Hardware Setup | 1-5 |

| 2.  | INSTALLATION IN THE RACK   | 2-1 |

| 2.1 | Power ON                   | 2-1 |

| 2.2 | Correct Operation          | 2-2 |

| 3.  | ENVIRONMENTAL REQUIREMENTS | 3-1 |

## LIST OF FIGURES

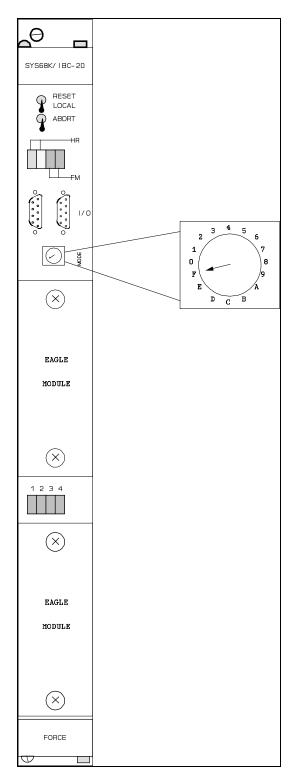

| Figure 1-1: | Front Panel of the Board                      | 1-2 |

|-------------|-----------------------------------------------|-----|

| Figure 1-2: | Pinout of the Micro D-Sub and D-Sub Connector | 1-4 |

This page was intentionally left blank

## 1. GENERAL

The IBC-20 comes ready to be installed in a VMEbus environment. The battery is installed on the board with an isolation strip on top of it. Please remove the isolation strip on the battery to enable it.

The front panel accessible rotary switch is set to \$F to boot the VMEPROM monitor after powerup. The monitor sets all necessary board functions enabling a standard terminal connected to the micro-D-Sub front panel connector to communicate with VMEPROM. Set the terminal for 9600 baud, 8 bits per character, no parity, one stop bit.

By default the IBC-20 acts as VME system controller and can become VMEbus master. The board should be installed in slot 1 of the VMEbus system and no other board should be generating SYSCLK or functioning as Arbiter. To disable the system controller function of the board, switch SW5-8 must be set to the OFF position.

### 1.1 The MODE Switch

The Mode switch which is accessible through the front panel, configures the startup of the VMEPROM or a user program. By default, the switch is set to \$F.

The various setup functions determined by the Mode switch are described in detail in the "*Firmware User's Manual*".

### **1.2 The Toggle Switches**

The IBC-20 board contains two toggle switches mounted on the top of the front panel. The switches are:

- RESET/LOCAL Switch

- ABORT Switch

Both switches are double function switches which have their normal position in the middle. The upper position of the switches activates the function momentarily, while in the down position the function is enabled continuously.

Set the switches to the middle position for proper operation.

In order to detect mechanical damage to the switches during transport, please toggle each switch before installing the board in the rack.

### **1.3 Connection of the Terminal**

A terminal can be connected to either of the two 9-pin Micro D-Sub connectors on the front panel.

An adapter cable from 9-pin Micro D-Sub to 9-pin D-Sub adapter cable is optionally available.

The following communication setup is used for interfacing the terminal. Please configure the terminal to this setup.

No Parity 8 Bits per character 1 Stop Bit 9600 Baud Asynchronous Protocol

The hardware interface is RS-232C compatible. The following signals are supported on both 9-pin Micro D-Sub connectors on the front panel:

| Signal | Input | Output | Required | 9-Pin Micro<br>D-Sub<br>Connector | Description         | 9-Pin D-Sub of the<br>Adapter Cable |

|--------|-------|--------|----------|-----------------------------------|---------------------|-------------------------------------|

| DCD    | х     |        |          | 1                                 | Data Carrier Detect | 1                                   |

| RXD    | Х     |        | Х        | 2                                 | Receive Data        | 2                                   |

| TXD    |       | Х      | Х        | 3                                 | Transmit Data       | 3                                   |

| DTR    |       | Х      |          | 4                                 | Data Terminal Ready | 4                                   |

| GND    |       |        |          | 5                                 | Signal GND          | 5                                   |

| DSR    | Х     |        |          | 6                                 | Data Set Ready      | 6                                   |

| RTS    |       | Х      | Х        | 7                                 | Request to Send     | 7                                   |

| CTS    | Х     |        | Х        | 8                                 | Clear to Send       | 8                                   |

| GND    |       |        | Х        | 9                                 | Signal GND          | 9                                   |

## CAUTION

- 1) The terminal used must not drive a signal line which is marked to be an output of the board.

- 2) All signals marked as "Required" must be supported from the terminal to enable the transmission.

- If the terminal is configured to the listed setup, please connect the 9-pin Micro D-Sub connector to the terminal with a cable which supports all of the required signals.

## Figure 1-2: Pinout of the Micro D-Sub and D-Sub Connector

A) Micro D-Sub Male Connector Soldered on the Board B) Micro D-Sub and D-Sub Female Connectors on the Adapter/Terminal Cable

## **1.4 The Default Hardware Setup**

The IBC-20 is configured to be used immediately. This results in a default hardware setup which may conflict with other boards installed in the rack.

The following VMEbus signals are driven/received by the board:

| Signal     | Driven | Received |

|------------|--------|----------|

| SYSCLK     | Х      |          |

| BR3*       | Х      |          |

| BR[30]*    |        | Х        |

| BG[30]OUT* | Х      |          |

| ACFAIL*    |        | Х        |

| SYSFAIL*   |        | Х        |

| SYSRESET*  | Х      | Х        |

## CAUTION

- 1) The on-board 4-level arbiter is enabled and responds to every Bus Request.

- 2) The board is configured as a VMEbus system controller (Slot 1 functions enabled).

This page intentionally left blank

## 2. INSTALLATION IN THE RACK

The board can immediately be mounted into a VME rack at slot 1.

## CAUTION

- 1) Switch off power before installing the board to avoid electrical damage to the components.

- 2) The board contains a special ejector (the handles). The board must be plugged in, and the screws on the front panel tightened up to guarantee proper installation.

- 3) Unplug every other VMEbus board to avoid conflicts.

### 2.1 Power ON

Power the VMEbus rack when the board is correctly installed, the switches are in the correct positions, and the terminal is correctly configured and under power.

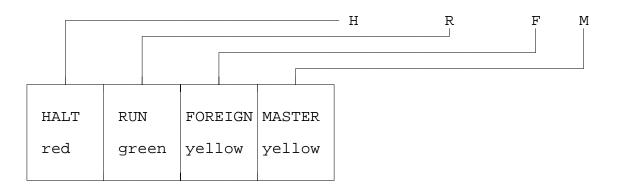

Initially, the red "H"-LED (HALT/RESET) will light up until the green "R"-LED (RUN) ist turned on. Now the VMEPROM banner should appear on the screen.

The terminal is now at the user's discretion. At this point, it is advised to make a few carriage returns, to obtain the question mark (?\_) prompt.

## 2.2 Correct Operation

To test the correct operation of the board, the following command should be typed in:

#### ? SELFTEST<cr>

It is a matter of a few seconds until all tests are completed. Once all tests are completed, the following messages will appear on the screen:

#### **VMEPROM Hardware Selftest**

I/O test .....passed

- Memory test .....passed

- Clock test . . . . . . . . . passed

Any errors will be reported as they occur.

If an error message is displayed, please refer to *Firmware User's Manual* containing the command description "*SELFTEST*".

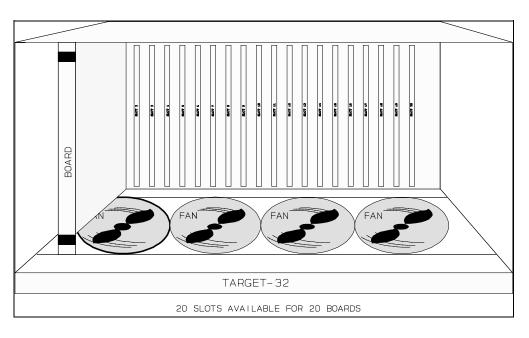

## 3. ENVIRONMENTAL REQUIREMENTS

This board was specified and tested for reliable operation under certain environmental conditions. Based on our performance tests, this board is capable of operating within the temperature range of 0°C to 50°C when used inside of a FORCE TARGET-32 chassis. The following chart details the calculated rate of forced air cooling.

| Rate of | Forced | Air | Cooling |

|---------|--------|-----|---------|

|---------|--------|-----|---------|

| Air Cooling per Board                                         | Total Air Cooling - Target-32   |  |  |

|---------------------------------------------------------------|---------------------------------|--|--|

| 5.5 CFM* = 0.0026 cubic meter/sec                             | 131 CFM = 0.062 cubic meter/sec |  |  |

| 275 LFM** = 1.4 meter/sec                                     | 275 LFM = 1.4 meter/sec         |  |  |

| * CFM = Cubic Feet per Minute ** LFM = Linear Feet per Minute |                                 |  |  |

The TARGET-32 chassis performs forced air cooling using four axial fans. The amount of airflow needed for cooling and normal operation is reflected by certain factors such as ambient temperature, number and location of boards in the system, and outside heat sources. Sufficient air cooling is normally obtained when 5.5 CFM and 275 LFM is circulating around each board at an ambient temperature between 0°C and 50°C. Allowable storage temperatures may range between -40°C and 85°C. The rate of relative humidity (non-condensing) should not be less than **5**%, and should not exceed **95**%. The following illustration is a pictorial view of the fan placement in the chassis.

# HARDWARE USER'S MANUAL

This page intentionally left blank

## TABLE OF CONTENTS

| I.                                                         | GENERAL DESCRIPTION                                                                                                                                                                                                                    | 1-1                                                  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| П.                                                         | DEFAULT CONFIGURATION OF THE IBC-20                                                                                                                                                                                                    | . 2-1                                                |

| 1.<br>1.1<br>1.2                                           | The Switches of the IBC-20 board<br>The Slide Switch SW5<br>The Slide Switch SW6                                                                                                                                                       | 2-2                                                  |

| III.                                                       | ADDRESS MAP OF THE IBC-20                                                                                                                                                                                                              | 3-1                                                  |

| IV.                                                        | HARDWARE DESCRIPTION                                                                                                                                                                                                                   | 4-1                                                  |

| 1.<br>1.1<br>1.2<br>1.3                                    | THE MICROPROCESSOR MC68020                                                                                                                                                                                                             | 4-1<br>4-1                                           |

| 2.<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8 | THE GATE ARRAY FGA-002A<br>The Processor Interface<br>The VMEbus Interface<br>The Local I/O Interface<br>The 32-bit DMA Controller<br>The FORCE Message Broadcast Channels (FMB)<br>Mailboxes<br>The Timer<br>The Interrupt Management | 4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5 |

| 3.                                                         | THE EXPANSION MODULE CONNECTOR (IBC MOD-1)                                                                                                                                                                                             | 4-6                                                  |

| 4.<br>4.1<br>4.2<br>4.2.1<br>4.2.2                         | THE EAGLE INTERFACE         The EAGLE Module Slots         The EAGLE I/O Connectors (Slots 1 & 2) and VME/P2 Connection         The I/O Selection Field B2         The Pin Assignment of the I/O Selection Field B2                    | 4-6<br>4-8<br>4-8                                    |

| 5.<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                      | THE SHARED MAIN MEMORY         Main Memory Access by the MC68020         Main Memory Access by the DMA Controller         Main Memory Access by EAGLE Modules         Main Memory Access by VME         Summary of the Main Memory     | 4-14<br>4-15<br>4-15<br>4-15<br>4-16<br>4-16         |

| 6.                                                         | THE BOOT EPROM                                                                                                                                                                                                                         | 4-17                                                 |

| 7.                                                         | THE LOCAL SRAM                                                                                                                                                                                                                         | 4-19                                                 |

| 8.               | THE FLASH EPROM                                | 4-20         |

|------------------|------------------------------------------------|--------------|

| 9.<br>9.1<br>9.2 | THE LOGIC CELL ARRAY LCA                       | 4-23<br>4-23 |

| 9.3              | The Arbiter Control Register ARBCON            | 4-24         |

| 9.4              | The Register A24REG                            | 4-25         |

| 9.5              | The Register CTL1                              | 4-26         |

| 10.              | THE SERIAL COMMUNICATION CONTROLLER SCC Z85C30 | 4-27         |

| 10.1             | Address Map of the SCC Registers               | 4-28         |

| 10.2             | Summary of the SCC                             | 4-28         |

| 11.              | THE SERIAL I/O PORTS                           | 4-29         |

| 11.1             | The Front Panel Connector Pinout               | 4-29         |

| 12.              | THE COUNTER/TIMER-I/O UNIT CIO Z8536           | 4-29         |

| 12.1             | CIO Interrupt Support                          | 4-30         |

| 12.2             | The I/O Port Control Functions                 | 4-31         |

| 12.3             | Description of the I/O Port Control Functions  | 4-32         |

| 12.4             | CIO Register Address Map                       | 4-34         |

| 12.5             | Summary of the CIO                             | 4-35         |

| 13.              | THE REAL TIME CLOCK RTC 72423                  | 4-35         |

| 13.1             | Address Map of the RTC Registers               | 4-36         |

| 13.2             | RTC Programming                                | 4-36         |

| 13.3             | Summary of the RTC                             |              |

| 14.              | SWITCHES AND LED INDICATORS                    | 4-38         |

| 14.1             | The RESET/LOCAL Switch                         | 4-39         |

| 14.2             | The ABORT Switch                               | 4-39         |

| 14.3             | The STATUS LEDs                                | 4-40         |

| 14.4             | The MODE Switch                                | 4-41         |

| 14.5             | The USER LEDs                                  | 4-41         |

| 15.              | THE RESET STRUCTURE                            | 4-42         |

| 15.1             | Power-Up/Down Reset                            | 4-42         |

| 15.2             | The RESET/LOCAL Function Switch                | 4-43         |

| 15.3             | The Reset Instruction                          | 4-44         |

| 15.4             | The Local Reset Call                           | 4-44         |

| 15.5             | The VME Reset Call                             | 4-44         |

| 15.6             | The VME Signal SYSRESET*                       | 4-44         |

| 16.<br>16.1      | THE INTERRUPT STRUCTURE OF THE BOARD           | 4-45<br>4-46 |

| 17.              | BUS ARBITRATION OF THE FLXibus                 | 4-47         |

| 18.<br>18.1                                                 | THE VME MASTER INTERFACE The VME Address Space                                                                                                                                                                                               | 4-48<br>4-48                                                 |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 19.                                                         | SUPPORTED AM CODES                                                                                                                                                                                                                           | 4-50                                                         |

| 20.<br>20.1<br>20.2<br>20.3<br>20.4<br>20.5                 | THE VME SLAVE INTERFACE                                                                                                                                                                                                                      | 4-54<br>4-55<br>4-55<br>4-56<br>4-57<br>4-57                 |

| 21.<br>21.1<br>21.2                                         | THE VME INTERRUPTER The Interrupt Generation Register IRQGEN The Interrupt Vector Register IRQVEC                                                                                                                                            | 4-58<br>4-58<br>4-59                                         |

| 22.                                                         | THE VME INTERRUPT HANDLER                                                                                                                                                                                                                    | 4-59                                                         |

| 23.<br>23.1<br>23.2<br>23.3<br>23.4<br>23.5                 | VMEbus SYSTEM CONTROL FUNCTIONS<br>The SYSCLK Signal<br>The SYSRESET* Signal<br>The SYSFAIL* Signal<br>The ACFAIL* Signal<br>The IACK Daisy Chain Driver                                                                                     | 4-60<br>4-60<br>4-61<br>4-62<br>4-62                         |

| 24.2.2 Round                                                | THE 4-LEVEL VMEbus ARBITER<br>Enabling/Disabling the Arbiter<br>The Arbitration Modes<br>ized Arbitration Mode<br>d-Robin Arbitration Mode<br>bus Clear Generation (BCLR*)                                                                   | 4-62<br>4-63<br>4-63<br>4-64<br>4-64<br>4-64<br>4-65         |

| 25.<br>25.1<br>25.2<br>25.3<br>25.4<br>25.5<br>25.6<br>25.7 | VMEbus REQUEST and RELEASE<br>VMEbus Request Level<br>VMEbus Release<br>Release Every Cycle (REC)<br>Release on Request (ROR)<br>Release Voluntary (RV)<br>Release on Bus Clear (RBCLR)<br>Release on ACFAIL (RACFAIL)                       | 4-66<br>4-68<br>4-68<br>4-68<br>4-69<br>4-69<br>4-69         |

| 26.<br>26.1<br>26.2<br>26.3<br>26.4<br>26.5<br>26.6<br>26.7 | THE BATTERY BACKUP FACILITIES         General         Functional Description         Low Voltage Alarm Interrupt         Primary Battery Backup         Primary Battery Insertion         Secondary Battery Backup         VMEbus STDBY-line | 4-70<br>4-70<br>4-71<br>4-71<br>4-71<br>4-72<br>4-72<br>4-72 |

## LIST OF FIGURES

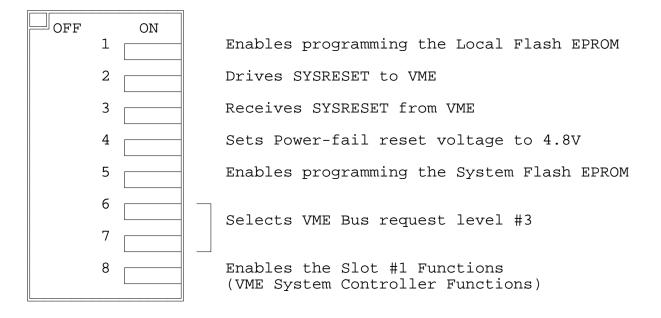

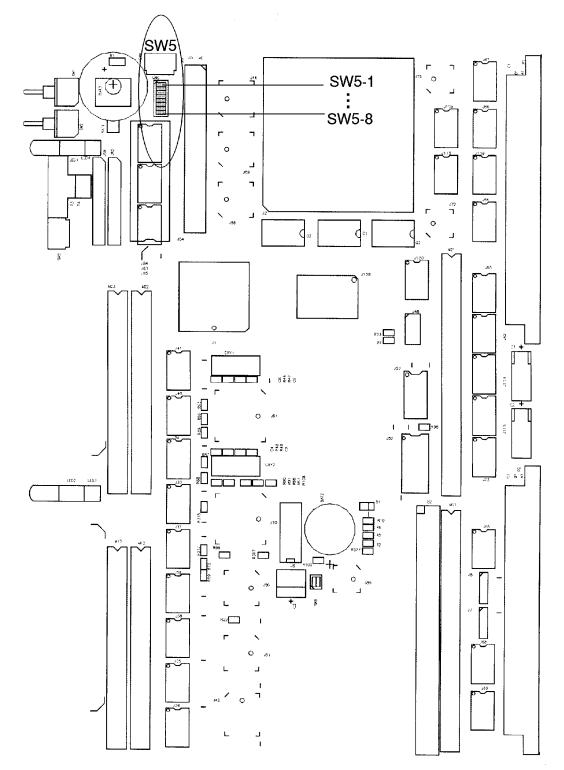

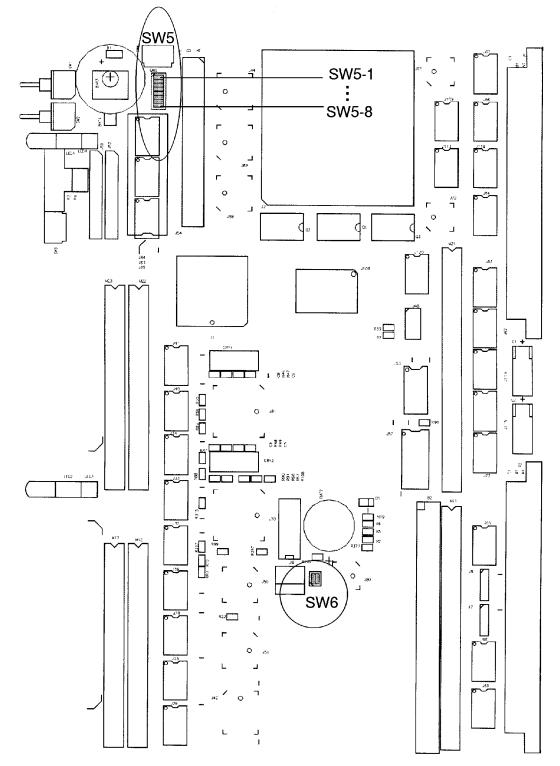

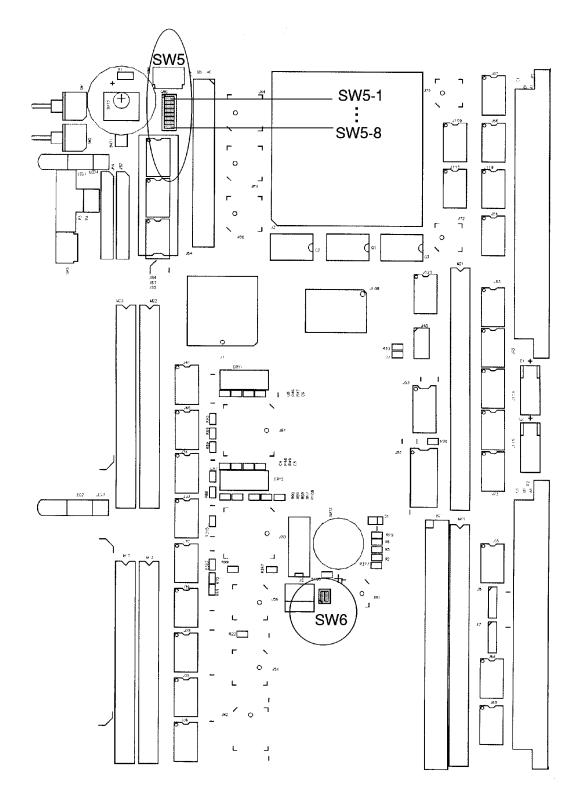

| Figure 1:  | Default Settings for Slide Switch SW5                           | 3  |

|------------|-----------------------------------------------------------------|----|

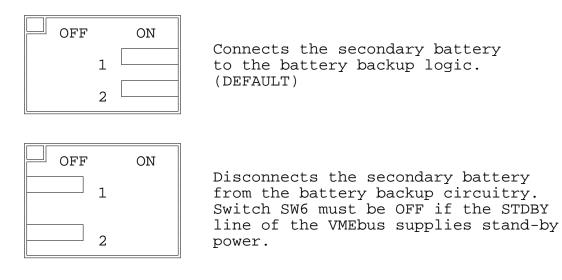

| Figure 2:  | Default Setting for Slide Switch SW6                            | 5  |

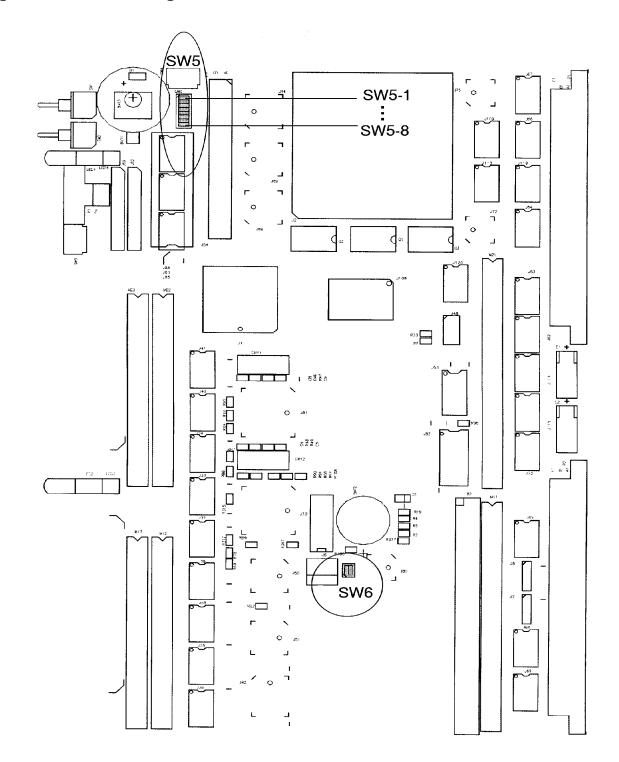

| Figure 3:  | Location Diagram of Slide Switches SW5 and SW6                  | 6  |

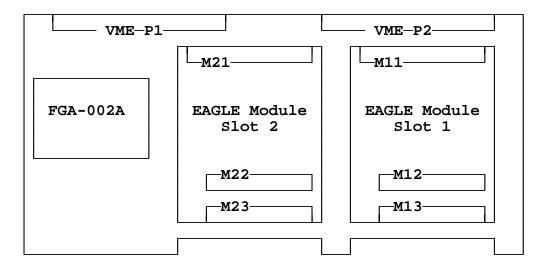

| Figure 4:  | The EAGLE Module Slots                                          | 7  |

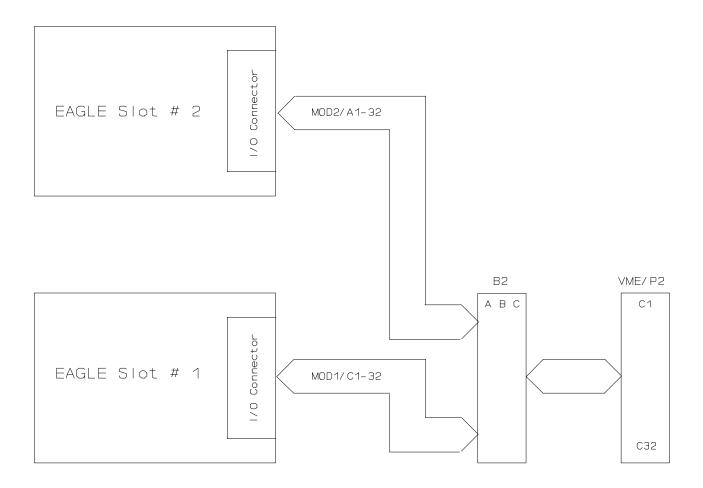

| Figure 5:  | Block Diagram of the EAGLE I/O Connectors to the VME/P2         | 11 |

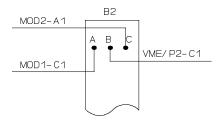

| Figure 6:  | Connection Diagram of the I/O Selection Field                   | 11 |

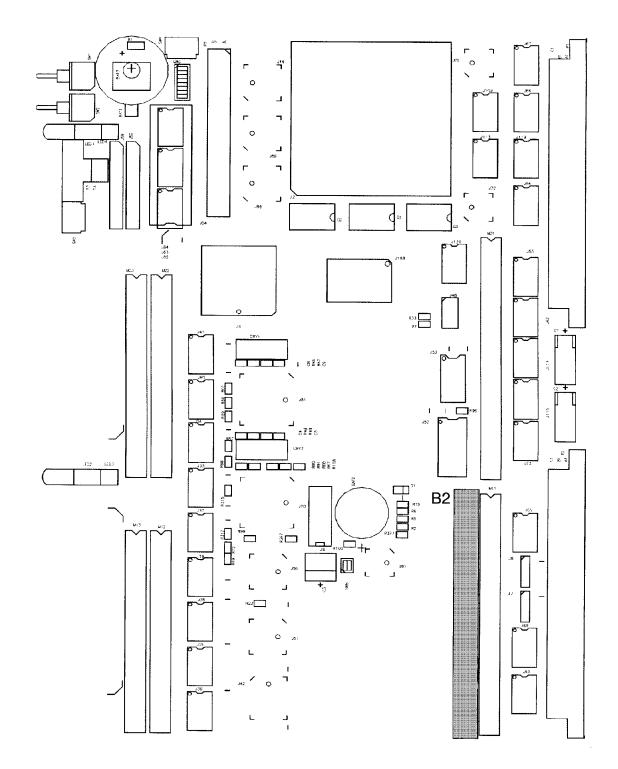

| Figure 7:  | Location Diagram of the I/O Selection Field                     | 12 |

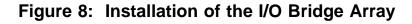

| Figure 8:  | Installation of the I/O Bridge Array                            | 13 |

| Figure 9:  | Location Diagram of the Boot EPROM                              | 18 |

| Figure 10: | Location Diagram of Switch SW5                                  | 21 |

| Figure 11: | Pinout of the Front Panel Connector and Adapter Cable Connector | 29 |

| Figure 12: | RTC Programming Example                                         | 37 |

| Figure 13: | The Reset Structure                                             | 43 |

| Figure 14: | Location Diagram of Slide Switches SW5 and SW6                  | 67 |

## LIST OF TABLES

| Table 1:  | Slide Switch SW5                              | 2  |

|-----------|-----------------------------------------------|----|

| Table 2:  | Functions of Slide Switch SW5                 | 4  |

| Table 3:  | Functions of Slide Switch SW6                 | 5  |

| Table 4:  | Base Addresses of the Local I/O Devices       | 1  |

| Table 5:  | The Address Map                               | 2  |

| Table 6:  | Exception Vector Assignments                  | 2  |

| Table 7:  | Pin Assignments of the I/O Selection field B2 | 10 |

| Table 8:  | Shared Main Memory                            | 14 |

| Table 9:  | Setting the FLASH EPROM Programming Voltage   | 20 |

| Table 10: | LCA Register Summary                          | 22 |

| Table 11: | Interrupt Generation Register (\$FF803E00)    | 23 |

| Table 12: | Interrupt Vector Register (\$FF803E01)        | 23 |

| Table 13: | Arbiter Control Register ARBCON (\$FF803E02)  | 24 |

| Table 14: | The A24-Register (\$FF803E10)                 | 25 |

| Table 15: | The CTL1 Register (\$FF803E11)                | 26 |

| Table 16: | SCC Register Address Map                      | 28 |

| Table 17: | The I/O Port Control Functions                | 31 |

| Table 18: | Directly accessible CIO Registers             | 34 |

| Table 19: | RTC Register Layout                           | 36 |

| Table 20: | VME Address Ranges                            | 49 |

| Table 21: | VME Data Bus Usage with Bus Size D32          | 49 |

| Table 22: | VME Data Bus Usage with Bus Size D16          | 50 |

| Table 23: | Supported AM-Codes as VME Master              | 51 |

| Table 24: | VME Address Modifier Codes                    | 52 |

| Table 25: | Supported AM-Codes for Slave Access           | 54 |

| Table 26: | Valid Extended Addressing AM Codes            | 55 |

| Table 27: | Valid AM Codes with the A24 Mode              | 56 |

| Table 28: | VMEbus Interrupter Registers                  | 58 |

| Table 29: | Interrupt Generation Register Format          | 58 |

# I. GENERAL DESCRIPTION

The IBC-20 is an 68020 based intelligent basic controller board for the VMEbus, providing the FLXibus (FORCE Local eXpansion interface) for local I/O and memory expansion capability. The FLXibus is available at two slots which allow the installation of up to two EAGLE modules. The 32-bit wide FLXibus supports master as well as slave operation and enables intelligent I/O subsystems which are built on an EAGLE module to communicate with the base board at high data transfer rates.

The IBC-20 board uses the features of the FORCE COMPUTERS Gate Array FGA-002A, providing a high performance 32-bit DMA Controller, two independent Message Broadcast Channels (FMB), eight Mailboxes, an 8-bit watchdog timer, Interrupt Management and support for local control logic.

This page intentionally left blank

# **II. DEFAULT CONFIGURATION OF THE IBC-20**

### 1. The Switches of the IBC-20 board

It is easy to configure the IBC-20 since there are only two slide switches to set for the required board functions. Descriptions of these two slide switches, SW5 and SW6, follow here. The switch functions of SW5 are printed on the solder side of the printed circuit board near switch SW5.

Slide switch SW5 selects various system functions. Slide switch SW6 enables the secondary battery (NiCd Accumulator) to backup the SRAM and the RTC. By default, both switches of SW6 are set to the "ON" position.

The rotary switch (also designated MODE switch) is accessible through the front panel. There is also a second on-board rotary switch SW4. Firmware reads these two switches and selects the startup conditions of VMEPROM or a user program. For detailed information, please see the *"IBC-20 Firmware User's Manual"*. By default, both switches are set to \$F.

Located on the front panel are the toggle switches RESET/LOCAL and ABORT. These switches remain idle when set to their middle position.

Figure 3, on page 2-6, shows the location diagram of slide switches SW5 and SW6.

## 1.1 The Slide Switch SW5

The following table describes the functions which are controlled by the slide switch SW5.

# Table 1: Slide Switch SW5

| SWITCH         | FUNCTION-CONTROL                                                                                                                                                                                                                                                   |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SW5-1          | Selects whether the Local Flash EPROM on the IBC-20 base board can be written to be erased/reprogrammed                                                                                                                                                            |  |

| SW5-2          | Selects whether the board drives the SYSRESET* signal to the VMEbus                                                                                                                                                                                                |  |

| SW5-3          | Selects whether the board receives the SYSRESET* signal from the VMEbus                                                                                                                                                                                            |  |

| SW5-4          | Sets the power-fail reset voltage to 4.85V/4.20V.<br>(The board will be reset as long as the +5V supply<br>voltage is lower than the selected voltage).                                                                                                            |  |

| SW5-5          | Selects whether the System Flash EPROM on the IBC MOD-1 module can be written to be erased/re-<br>programmed. (The System Flash-EPROM is only available with the IBC MOD-1 module)                                                                                 |  |

| SW5-6<br>SW5-7 | Select the VMEbus request level                                                                                                                                                                                                                                    |  |

| SW5-8          | Enables/disables the SLOT 1 functions (VMEbus<br>System controller functions) of the board.<br>If the SLOT 1 function is enabled (Board is System<br>Controller), the 4-level-Arbiter will be enabled, the<br>SYSCLOCK* line and the BCLR* line will be<br>driven. |  |

### Figure 1: Default Settings for Slide Switch SW5

The following figure shows default setting of the SW5 switches with the selected board function.

Figure 3, on page 2-6, shows the location diagram of slide switches SW5 and SW6.

# Table 2: Functions of Slide Switch SW5

| Switch         | Name             | Selections                                                                   |  |  |

|----------------|------------------|------------------------------------------------------------------------------|--|--|

| SW5-1          | IBCFLASH         | ON Local Flash EPROM is writable<br>OFF Local Flash EPROM write protected    |  |  |

| SW5-2          | VMERESOT         | ON SYSRESET driven<br>OFF SYSRESET not driven                                |  |  |

| SW5-3          | VMERESIN         | ON SYSRESET received<br>OFF SYSRESET not received                            |  |  |

| SW5-4          | MIN4.85V         | ON Power-fail reset voltage 4.8V<br>OFF Power-fail reset voltage 4.2V        |  |  |

| SW5-5          | MODFLASH         | ON Module Flash EPROM programmable<br>OFF Module Flash EPROM write protected |  |  |

| SW5-6<br>SW5-7 | BRSEL1<br>BRSEL0 | BR0BR1BR2BR3OFFOFFONONOFFONOFFON                                             |  |  |

| SW5-8          | SLOT 1           | ON Slot #1 function enabled<br>OFF Slot #1 function disabled                 |  |  |

# **1.2 The Slide Switch SW6**

The switches SW6-1 and SW6-2 connect the chargeable secondary battery with the battery backup logic for the local SRAM and the RTC. When the switches are set "ON", the Real Time Clock and the local SRAM will be backed up by the secondary battery. This saves the SRAM and RTC during replacement of the primary battery (Lithium Battery CR2032). In order to guarantee the charging of the secondary battery during run time of the board, the switches have to be set to "ON". If the STDBY-line of the VMEbus supplies power to the board, both switches must be set to the "OFF" position. Otherwise, damage to the chargeable secondary battery may occur.

Switches SW6-1 and SW6-2 are functionally considered one switch. Figure 3, on page 2-6, shows the location diagram of slide switches SW5 and SW6.

### Table 3: Functions of Slide Switch SW6

| Switch SW6      | Selections                         |                           |  |

|-----------------|------------------------------------|---------------------------|--|

| SW6-1 and SW6-2 | ON/ON                              | Secondary Battery enabled |  |

| SW6-1 and SW6-2 | OFF/OFF Secondary Battery disabled |                           |  |

## Figure 2: Default Setting for Slide Switch SW6

### Slide Switch SW6

# Figure 3: Location Diagram of Slide Switches SW5 and SW6

# III. ADDRESS MAP OF THE IBC-20

The 68020 processor of the IBC-20 board addresses four gigabytes by its 32-bit address bus. This address space is decoded by the FGA-002A Gate Array. Table 5, which appears on the next page, shows the Address Map of the decoded areas.

The address range of the Main memory is software selectable and will be programmed by the onboard firmware depending on the assembled memory capacity. Other addresses are hard decoded by FGA-002A. One area is provided to address devices on EAGLE Modules via the FLXibus interface.

The following table shows the base addresses of the local I/O devices.

## Table 4: Base Addresses of the Local I/O Devices

| Base Address | Device                             |  |

|--------------|------------------------------------|--|

| \$FF802000   | SCC Z85C30 Serial Comm. Controller |  |

| \$FF800C00   | CIO Z8536 Counter-Timer I/O Unit   |  |

| \$FF803E00   | LCA XC3042 VME Arbiter/Interrupter |  |

| \$FF803000   | RTC 72423 Real Time Clock          |  |

# Table 5: The Address Map

| Addres                                       | s Range                                      |                                                                                                                                                          |  |

|----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| From                                         | То                                           | Access to                                                                                                                                                |  |

| 00000000<br>00000000<br>00000000<br>00000000 | 0007FFFF<br>000FFFFF<br>001FFFFF<br>003FFFFF | Main Memory (512 Kbyte) or<br>Main Memory (1 Mbyte) or<br>Main Memory (2 Mbyte) or<br>Main Memory (4 Mbyte)                                              |  |

| 00080000<br>00100000<br>00200000<br>00400000 | F9FFFFF<br>F9FFFFFF<br>F9FFFFFF<br>F9FFFFFF  | VMEbus (512 Kbyte Main Memory)<br>VMEbus (1 Mbyte Main Memory)<br>VMEbus (2 Mbyte Main Memory)<br>VMEbus (4 Mbyte Main Memory)<br>A32: D32, D24, D16, D8 |  |

| FA000000                                     | FAFFFFF                                      | Message Broadcast Area (FMB)<br>(Slave and Master Mode)                                                                                                  |  |

| FB000000                                     | FBFEFFFF                                     | VMEbus A24: D32, D24, D16, D8                                                                                                                            |  |

| FBFF0000                                     | FBFFFFFF                                     | VMEbus A16: D32, D24, D16, D8                                                                                                                            |  |

| FC000000                                     | FCFEFFFF                                     | VMEbus A24: D16, D8                                                                                                                                      |  |

| FCFF0000                                     | FCFFFFF                                      | VMEbus A16: D16, D8                                                                                                                                      |  |

| FD000000                                     | FEFFFFF                                      | EAGLE Module Devices via FLXibus                                                                                                                         |  |

| FF000000                                     | FF7FFFFF                                     | System EPROM (optional with Expansion Module)                                                                                                            |  |

| FF800000                                     | FFBFFFFF                                     | Local I/O Devices                                                                                                                                        |  |

| FFC00000                                     | FFC7FFFF                                     | Local SRAM                                                                                                                                               |  |

| FFC80000                                     | FFCFFFFF                                     | Local FLASH EPROM                                                                                                                                        |  |

| FFD00000                                     | FFDFFFFF                                     | FGA-002A Registers                                                                                                                                       |  |

| FFE00000                                     | FFEFFFFF                                     | BOOT EPROM                                                                                                                                               |  |

| FFF00000                                     | FFFFFFF                                      | Reserved                                                                                                                                                 |  |

# IV. HARDWARE DESCRIPTION

# 1. THE MICROPROCESSOR MC68020

The IBC-20 board is equipped with the MC68020 processor running at 25 MHz. The chip is housed in a 132-pin plastic quad flat pack (PQFP). The processor features 32-bit wide internal and external data paths. A 32-bit address bus allows to address a total of 4 gigabyte physical memory. The 68020 incorporates a 256 byte onchip cache memory used to store the instruction prefetches from the main memory. The instruction cache offers 64 long word entries with a tag field for each cache entry. The 68020 is object code compatible with earlier 68000 microprocessors. Its instruction set includes eight addressing modes and supports 8-, 16-, and 32-bit data types.

# 1.1 General Operation

The MC68020 uses a nonmultiplexed bus with 32-bit wide address and 32-bit wide data bus. The asynchronous bus structure allows easy interfacing to the outside world. The processor can transfer data in a minimum of three clock cycles. Otherwise, wait states in clock period increments will be inserted. The processor drives the address lines (A0-A31), the size lines (SIZ0, SIZ1) and the function code signals (FC0-FC2) on every cycle, independent of a cache hit or miss.

The address and data strobes indicate that the current cycle is not a cache cycle and that the outputs are strobed to be valid.

The MC68020 supports accesses to 8/16/32 bit devices with its dynamic bus sizing mechanism. During operand transfer cycles, the size of the data transfer is indicated by the SIZ0, SIZ1 output signals. The slave device uses the DSACK0, DSACK1 signal according to its data bus width to terminate the cycle. If the cycle is terminated with bus error (BERR signal sensed by the processor), exception handling starts based on the current cycle. The exception vector table occupies 1 Kbyte memory space.

The bus controller inside the MC68020 manages the bus mastership of the local bus FLXibus. The bus controller arbitrates the local bus in such a way that the processor itself has lowest priority in becoming bus master. This means that on request of an alternate master, the MC68020 will grant the bus to the alternate device as soon as possible.

## **1.2 The Instruction Set**

For the 68020 instruction set as well as further information, please refer to the "MC68020 User's Manual".

## **1.3 Exception Vector Table of the 68020**

The following table lists all exception vectors defined for the 68020 Processor.

# Table 6: Exception Vector Assignments

| Vector Number(s) | Vector Offset (Hex) | Assignment                                       |

|------------------|---------------------|--------------------------------------------------|

| 0                | 000                 | Reset Initial Interrupt Stack Pointer            |

| 1                | 004                 | Reset Initial Program Counter                    |

| 2                | 008                 | Access Fault (Bus Error)                         |

| 3                | 00C                 | Address Error                                    |

| 4                | 010                 | Illegal Instruction                              |

| 5                | 014                 | Integer Divide by Zero                           |

| 6                | 018                 | CHK, CHK2 Instruction                            |

| 7                | 01C                 | FTRAPcc, TRAPcc, TRAPV Instructions              |

| 8                | 020                 | Privilege Violation                              |

| 9                | 024                 | Trace                                            |

| 10               | 028                 | Line 1010 Emulator (Unimplemented A-Line Opcode) |

| 11               | 02C                 | Line 1111 Emulator (Unimplemented F-Line Opcode) |

| 12               | 030                 | (Unassigned, Reserved)                           |

| 13               | 034                 | Defined for MC68020/MC68030, not for MC68040     |

| 14               | 038                 | Format Error                                     |

| 15               | 03C                 | Uninitialized Interrupt                          |

| 16-23            | 040-05C             | (Unassigned, Reserved)                           |

| 24               | 060                 | Spurious Interrupt                               |

| 25               | 064                 | Level 1 Interrupt Autovector                     |

| 26               | 068                 | Level 2 Interrupt Autovector                     |

| 27               | 06C                 | Level 3 Interrupt Autovector                     |

| 28               | 070                 | Level 4 Interrupt Autovector                     |

| 29               | 074                 | Level 5 Interrupt Autovector                     |

| 30               | 078                 | Level 6 Interrupt Autovector                     |

| 31               | 07C                 | Level 7 Interrupt Autovector                     |

| 32-47            | 080-0BC             | TRAP #0-15 Instruction Vectors                   |

| 48               | 0C0                 | FP Branch or Set on Unordered Condition          |

| 49               | 0C4                 | FP Inexact Result                                |

| 50               | 0C8                 | FP Divide by Zero                                |

| 51               | OCC                 | FP Underflow                                     |

| 52               | ODO                 | FP Operand Error                                 |

| 53               | OD4                 | FP Overflow                                      |

| 54               | 0D8                 | FP Signaling NAN                                 |

| 55               | ODC                 | FP Unimplemented Data Type                       |

| 56               | 0E0                 | Defined for MC68030 and MC68851, not for MC68040 |

| 57               | 0E4                 | Defined for MC68851, not for MC68040             |

| 58               | 0E8                 | Defined for MC68851, not for MC68040             |

| 59-63            | 0EC-0FC             | (Unassigned, Reserved)                           |

| 64-255           | 100-3FC             | User Defined Vectors (192)                       |

# 2. THE GATE ARRAY FGA-002A

The IBC-20 board is equipped with the powerful FORCE Computers Gate Array FGA-002A. It provides a 68020/30 processor compatible interface, a local I/O bus supporting 68000- and 8080- family I/O devices and a VMEbus interface with system controller facility. The 281-pin device features a high performance 32-bit DMA Controller, two independent Message Broadcast Channels (FMB), eight Mailboxes, an 8-bit watchdog timer, Interrupt Management and local control logic. The gate array contains decoding and timing circuitry and controls access to the Local I/O bus, the VMEbus and to the Main Memory. The FGA-002A is clocked by a 32.0 MHz clock and a 25.0 MHz clock. The 32.0 MHz clock is used by internal control logic and the Timer. The 25.0 MHz clock drives the DMA controller and control logic which is associated with the processor bus. The registers of FGA-002A are accessible by the processor and by alternate FLXibus masters. Detailed description of the FGA-002A features with corresponding registers can be found in the FGA-002A Gate Array User's Manual.

## 2.1 The Processor Interface

The processor interface signal lines of the FGA-002A are connected to the MC68020 microprocessor and to the FLXibus (Force Local eXpansion interface bus). The gate array monitors the FLXibus/68020 signals and decodes accesses to the Main RAM, the VMEbus, the local I/O devices and to its own registers. The FGA-002A becomes bus master of the FLXibus if the VMEbus or the DMA Controller accesses the shared Main memory or the EAGLE Module.

## 2.2 The VMEbus Interface

The VMEbus compatible interface of FGA-002A provides control of the data transfer bus, the priority interrupt bus and features system control functions. Since there is a 4-level arbiter provided outside in the LCA device, the single level arbiter of FGA-002A cannot be used on this board. By default, the board boots up with the single level arbiter disabled. The VMEbus control-, address-, and data-lines are connected to the gate array through buffers and transceivers.

# 2.3 The Local I/O Interface

The Local I/O interface of FGA-002A is 8-bits wide. It supports 68000 family devices as well as 8080 family devices with separate read and write strobes. The FGA-002A manages the data flow to/from the onboard devices of IBC-20 and generates the access cycle to the Local I/O bus. The devices which are connected to the Local I/O interface of FGA-002A are the Boot EPROM, the Local SRAM, the FLASH EPROM, the SCC Serial I/O controller, the CIO Counter/Timer unit, the LCA and the Real Time Clock.

# 2.4 The 32-bit DMA Controller

The 32-bit DMA Controller provides high speed data transfer between the VMEbus and through the FLXibus interface to the on-board Main RAM and to devices on the EAGLE modules.

The DMA Controller can be programmed and started by the processor or alternate masters of the FLXibus.

The DMA controller supports aligned and unaligned data transfers. Internal logic first aligns the data transfers to take full advantage of the 32-bit structure of the VMEbus and the local FLXibus. The DMA transfers data in bursts of 32 byte. After being started, the DMA reads the data from the source port into a 32 byte deep internal FIFO. Then the bus of the source port will be released and the bus of the destination port will be requested for the next transfer burst. This operation scheme guarantees that the DMA does not block any bus and therefore increases overall system performance. It will also maintain real time capability of the system. Data transfers by the DMA Controller on the VMEbus will let the processor access all local I/O devices, the EPROM area, the shared Main RAM and the FLXibus without performance degradation. Data transfers between VME and the Main RAM allows the local processor to operate at 60-70%.

The DMA Controller runs with 25.0 MHz clock and executes 68020/30 processor compatible cycles to the FLXibus. The access time of the Main Memory devices guarantee the DMA a 5-clock access cycle what results in a maximum transfer speed of 20 Mbytes/second. Depending on the successful completion of the task, the DMA generates either a normal termination interrupt or an error termination interrupt, if the task has been aborted or a bus error occurred.

## 2.5 The FORCE Message Broadcast Channels (FMB)

The FGA-002A provides two fully independent message broadcast channels supporting high level multiprocessor communication. Channel A is capable of storing eight byte messages and channel B stores a single byte message. Each channel receives the message from a VMEbus master through a dual ported FIFO. After having received the message byte, the addressed channel (A or B) requests interrupt service from the processor. The interrupt level is selectable individually for the channels inside the FGA-002A. The address range in which FGA-002A decodes FMB message cycles from VME is software programmable inside the gate array. This area only can be used for cycles according to the FMB message protocol.

### 2.6 Mailboxes

The FGA-002A includes eight Mailboxes. Each of them may interrupt the local processor. The interrupt level is programmable with individual interrupt vector for the Mailboxes. The Mailboxes are accessible from VMEbus side as well as by the processor or a FLXibus master.

### 2.7 The Timer

The timer of FGA-002A consists of an 8-bit synchronous down counter/timer and can be clocked by frequencies from 1 MHz to 0.5 Hz. The clock frequencies and the operation modes are selectable by software. The counter/timer may generate periodical interrupts or a single interrupt after timeout. It can also be used as a watchdog timer which may indicate a hardware failure of the board by asserting the VMEbus signal line SYSFAIL\* to low state.

## 2.8 The Interrupt Management

The FGA-002A gate array handles interrupt requests of the onboard I/O devices, the seven VMEbus interrupts and the interrupt sources inside FGA-002A. The request level of an interrupt source can be programmed to interrupt the processor at any level. The interrupt vector can be created by the FGA-002A itself or may be fetched from the I/O device or the VMEbus. Prioritization of the interrupt sources which are supported by FGA-002A is done inside the gate array.

# 3. THE EXPANSION MODULE CONNECTOR (IBC MOD-1)

This new IBC-20 revision 2 board includes the Expansion Module Connector P5, which allows the user to enhance the functions of the base board by using the optionally available IBC MOD-1 Module. The IBC-20 board may be upgraded with a Floating Point Coprocessor and additional Flash EPROM with the IBCMOD-1.

The IBC MOD-1 module is described in Section 8 of this manual.

## 4. THE EAGLE INTERFACE

The IBC-20 board features I/O and memory expansion capability by providing two EAGLE slots. The slots are interfaced to the Force Local eXpansion interface bus (FLXibus). Both I/O connectors of the EAGLE slots can use the VME/P2 I/O signals.

The EAGLE interface is built according to the EAGLE MODULE Specification by FORCE COMPUTERS.

### 4.1 The EAGLE Module Slots

The IBC-20 provides two slots at which EAGLE modules can be mounted. Both EAGLE slots of the IBC-20 board are able to hold the same EAGLE Module. Each module may become local bus master on the FLXibus and send interrupts to the processor.

The IBC-20 board recognizes an EAGLE module as being plugged in when the module drives the MODINS pin to low level. In this case, the IACK Daisy Chain (IACKIN/IACKOUT) and the local arbitration daisy chain (BGIN/BGOUT) pass through the EAGLE module. If the MODINS pin is high, the daisy chain signals bypass the EAGLE module slots.

The bus mastership of the FLXibus is prioritized by a local Bus Grant daisy chain signal line. The order of the bus mastership on the FLXibus is as follows:

| 1st (highest) | priority: | EAGLE Slot 2           |

|---------------|-----------|------------------------|

| 2nd           | priority: | EAGLE Slot 1           |

| 3rd           | priority: | FGA-002A Gate Array    |

| 4th (lowest)  | priority: | MC68020 microprocessor |

Additional information is given in " Bus Arbitration of the FLXibus".

Interrupts which use the same request level are prioritized by a local IACKIN/IACKOUT daisy chain line. Please refer to *"The Interrupt Structure of the Board"* for more details.

The pinout of the EAGLE I/O interface connectors can be found in Section 4, "The Appendix to the Hardware User's Manual."

Figure 4 shows the location of the EAGLE Module slots 1 and 2 with their FLXibus connectors M12, M13, M22, M23, and the EAGLE I/O connectors M11 and M21.

## 4.2 The EAGLE I/O Connectors (Slots 1 & 2) and VME/P2 Connection

A new feature on the IBC-20 revision 2 board is that the EAGLE I/O connector of module slot #2 can now be connected to the VME/P2 connector. On previous board revisions, the 64 I/O pins of the VME/P2 were connected to the EAGLE I/O connector of slot #1 only.

The connection of EAGLE slot #2 to the VME/P2 is achieved through the I/O selection field B2. The I/O selection field connects 32 pins of the VME/P2 connector (P2/C1-C31) either to Eagle slot #1 (default) or to Eagle slot #2. The VME/P2 A1-31 pins are hard wired to the Eagle Slot #1.

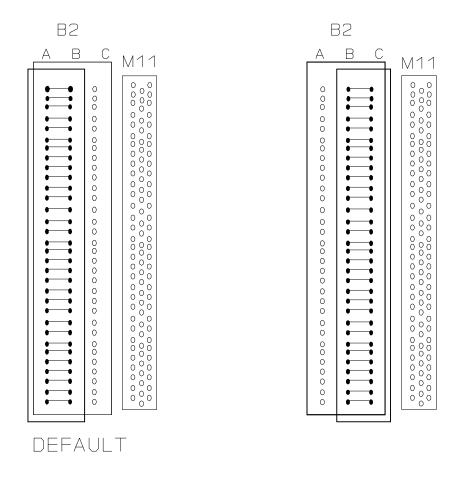

### 4.2.1 The I/O Selection Field B2

The I/O selection field B2 allows both Eagle module slots to be connected to the VME/P2 connector.

The I/O selection field B2 is a socket with 3 x 32 pin matrix. A bridge array with 32 bridges is plugged into the B2 socket. This connects the VME/P2 pins to the I/O connectors of the corresponding eagle slot. The bridge array can be used for both configurations.

By default, the bridge array connects rows A and B of the I/O selection field. It attaches the VME/P2 pins C1-31 to the I/O connector of Eagle slot #1. This configuration is compatible to earlier revisions of the IBC-20.

If the application requires that the I/O connector of Eagle slot #2 needs to be attached to the VME/P2 pins C1-31, the bridge array must be plugged in so that it connects the rows B and C of the I/O selection field.

# 4.2.2 The Pin Assignment of the I/O Selection Field B2

The table on the following page shows the pin assignment of the I/O selection field. The A row pins are connected to the Eagle slot #1, while the C row pins go to Eagle slot #2. The B row pins are attached to the VME/P2 connector.

Please note that Eagle slot #2 is connected to the I/O selection field by its A1-31 pins, while the A1-31 pins of slot #1 are hard wired to the VME/P2 connector. This layout allows the A1-31 pins of both eagle module slots to be available at the VME/P2 connector.

The I/O selection field also allows various connections between the VME/P2 connector and the Eagle I/O connectors.

The following pages contain figures which highlight the VME/P2 connection to the I/O connectors of EAGLE slots #1 and #2. Figure 5 shows a simplified block diagram of the EAGLE I/O and VME/P2 Connection. Figure 6 shows a connection diagram of I/O Selection Field B2 and Figure 7 is a location diagram of B2. Figure 8 shows the two possible configurations for the installation of the bridge array on selection field B2.

| PIN                                     | A                                      | В          |          |

|-----------------------------------------|----------------------------------------|------------|----------|

| 4                                       |                                        |            | С        |

| 1                                       | MOD1-C1                                | VME/P2-C1  | MOD2-A1  |

| 2                                       | MOD1-C2                                | VME/P2-C2  | MOD2-A2  |

| 3                                       | MOD1-C3                                | VME/P2-C3  | MOD2-A3  |

| 4                                       | MOD1-C4                                | VME/P2-C4  | MOD2-A4  |

| 5                                       | MOD1-C5                                | VME/P2-C5  | MOD2-A5  |

| 6                                       | MOD1-C6                                | VME/P2-C6  | MOD2-A6  |

| 7                                       | MOD1-C7                                | VME/P2-C7  | MOD2-A7  |

| 8                                       | MOD1-C8                                | VME/P2-C8  | MOD2-A8  |

| 9                                       | MOD1-C9                                | VME/P2-C9  | MOD2-A9  |

| 10                                      | MOD1-C10                               | VME/P2-C10 | MOD2-A10 |

| 11                                      | MOD1-C11                               | VME/P2-C11 | MOD2-A11 |

| 12                                      | MOD1-C12                               | VME/P2-C12 | MOD2-A12 |

| 13                                      | MOD1-C13                               | VME/P2-C13 | MOD2-A13 |

| 14                                      | MOD1-C14                               | VME/P2-C14 | MOD2-A14 |

| 15                                      | MOD1-C15                               | VME/P2-C15 | MOD2-A15 |

| 16                                      | MOD1-C16                               | VME/P2-C16 | MOD2-A16 |

| 17                                      | MOD1-C17                               | VME/P2-C17 | MOD2-A17 |

| 18                                      | MOD1-C18                               | VME/P2-C18 | MOD2-A18 |

| 19                                      | MOD1-C19                               | VME/P2-C19 | MOD2-A19 |

| 20                                      | MOD1-C20                               | VME/P2-C20 | MOD2-A20 |

| 21                                      | MOD1-C21                               | VME/P2-C21 | MOD2-A21 |

| 22                                      | MOD1-C22                               | VME/P2-C22 | MOD2-A22 |

| 23                                      | MOD1-C23                               | VME/P2-C23 | MOD2-A23 |

| 24                                      | MOD1-C24                               | VME/P2-C24 | MOD2-A24 |

| 25                                      | MOD1-C25                               | VME/P2-C25 | MOD2-A25 |

| 26                                      | MOD1-C26                               | VME/P2-C26 | MOD2-A26 |

| 27                                      | MOD1-C27                               | VME/P2-C27 | MOD2-A27 |

| 28                                      | MOD1-C28                               | VME/P2-C28 | MOD2-A28 |

| 29                                      | MOD1-C29                               | VME/P2-C29 | MOD2-A29 |

| 30                                      | MOD1-C30                               | VME/P2-C30 | MOD2-A30 |

| 31                                      | MOD1-C31                               | VME/P2-C31 | MOD2-A31 |

| 32                                      | MOD1-C32                               | VME/P2-C32 | MOD2-A32 |

| MOD1-C0132:<br>MOD2-A01_32 <sup>.</sup> | Eagle Slot #1 I/O Connector pins row C |            |          |

# Table 7: Pin Assignments of the I/O Selection field B2

VME/P2-C01..32: VME/P2 Connector pins row C

MOD2-A01..32: Eagle Slot #2 I/O Connector pins row A

Figure 6: Connection Diagram of the I/O Selection Field

# Figure 7: Location Diagram of the I/O Selection Field B2

By default, the bridge array connects rows A and B of the I/O selection field. This attaches the VME/P2 pins C1-31 to the I/O connector of EAGLE slot #1. This configuration is compatible to earlier revisions of the IBC-20.

If the I/O connector of EAGLE slot #2 needs to be attached to the VME/P2 pins C1-31, the bridge array has to be plugged in so that it connects rows B and C of the I/O selection field.

# 5. THE SHARED MAIN MEMORY

The IBC-20 board is available with 512 Kbyte, 1 Mbyte, 2 or 4 Mbyte Main memory capacity for system and user code and data. The Main memory of the IBC-20 board is built of static RAM which can be backed up by the +5VSTDBY line of the VMEbus. When power is applied to the +5VSTDBY line data is saved.

The Main RAM is accessible by the local processor, the DMA controller, the VMEbus and by EAGLE modules through the FLXibus. Accesses from the VMEbus to the Main RAM is handled via the FGA-002A gate array.

The size of the Main memory is software selectable inside FGA-002A and is determined by the Boot software. Assuming that the Main memory covers the maximum memory size of 4 Mbyte, the routine tests this space in 64 Kbytes steps for writable/readable memory. After having found the last writable/readable memory location, the required FGA-002A registers will then be set to the appropriate memory size.

In the following address ranges, the Main memory is accessible for the processor, the EAGLE modules and the FGA-002A DMA controller:

### Table 8: Shared Main Memory

| <ul><li>512 Kbyte memory capacity:</li><li>1 Mbyte memory capacity:</li><li>2 Mbyte memory capacity:</li><li>4 Mbyte memory capacity:</li></ul> | \$00000000 - \$000FFFF<br>\$00000000 - \$001FFFFF |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

# 5.1 Main Memory Access by the MC68020

The processor accesses the Main memory by using the control, address and data lines of the FLXibus. However, the access will be terminated by a private DSACK for the processor and no DSACK will be generated to the FLXibus. The access time of the SRAM devices guarantees a 1-wait-state access to the Main memory for the local processor.

## 5.2 Main Memory Access by the DMA Controller

The DMA controller accesses the Main memory via the local FLXibus. The DMA controller operates with 25 MHz clock frequency and drives 68020 compatible cycles to the FLXibus. The access time of the Main memory permits a 2-wait-state operation for the DMA controller.