# SYS68K/ASCU-1/2

.

## HARDWARE USER'S MANUAL

First Edition May 1985

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE Computers®

#### NOTE

The information in this document has been carefully checked and is believed to be entirely reliable. FORCE COMPUTERS makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors that may appear in this document. FORCE COMPUTERS reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance or design.

FORCE COMPUTERS assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of FORCE COMPUTERS GmbH/Inc.

FORCE COMPUTERS does not convey to the purchaser of the product described herein any license under the patent rights of FORCE COMPUTERS GmbH/Inc. nor the rights of others.

FORCE COMPUTERS Inc. 727 University Avenue Los Gatos, CA 95030 U.S.A.

Phone : (408) 354 34 10 Telex : 172465 FAX : (408) 395 77 18

FORCE COMPUTERS GmbH Daimlerstrasse 9 D-8012 Ottobrunn/Munich West Germany

Phone : (Ø89) 6 Ø9 2Ø 33 Telex : 5 24 19Ø forc-d FAX : (Ø 89)6 Ø9 77 93

FORCE COMPUTERS FRANCE Sarl 11, rue Casteja 92100 Boulogne France

Phone : (1) 62Ø 37 37 Telex : 2Ø6 3Ø4 forc-f Fax : (1) 621 35 19

## Page

| 1.<br>1.1<br>1.2 | General Description SYS68K/ASCU-1/2<br>Features of the SYS68K/ASCU-1Additional Features of the SYS68K/ASCU-2                                                       | 13<br>14<br>16 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.               | Access to the SYS68K/ASCU-1/2                                                                                                                                      | 18             |

| 2.1              | Board Base Address Selection                                                                                                                                       | 19             |

| 2.2              | Address Modifier Decoding                                                                                                                                          | 23             |

| 2.3              | Application Example                                                                                                                                                | 29             |

| 3.               | The Front Panel.                                                                                                                                                   | 31             |

| 3.1              | RESET Function Switch.                                                                                                                                             | 31             |

| 3.2              | TEST Function Switch.                                                                                                                                              | 31             |

| 3.3              | The SYSFAIL LED.                                                                                                                                                   | 31             |

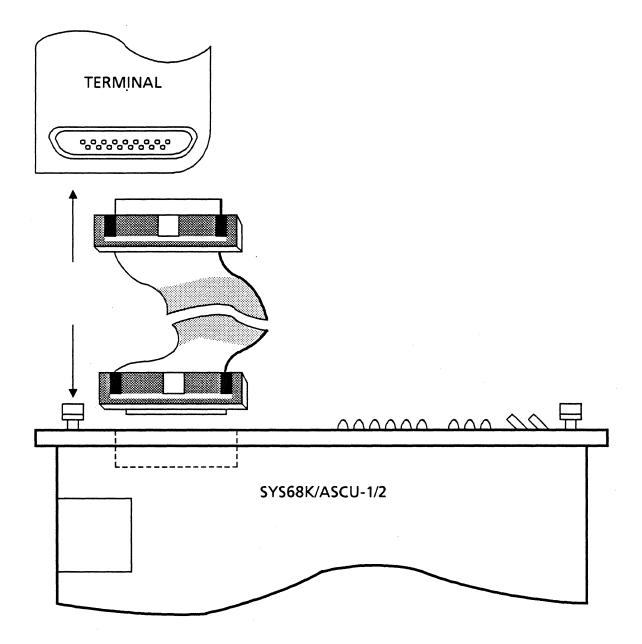

| 3.4              | The ACFAIL LED.                                                                                                                                                    | 31             |

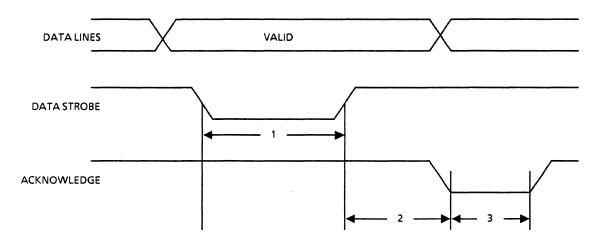

| 3.5              | Bus Arbitration Status LEDs.                                                                                                                                       | 33             |

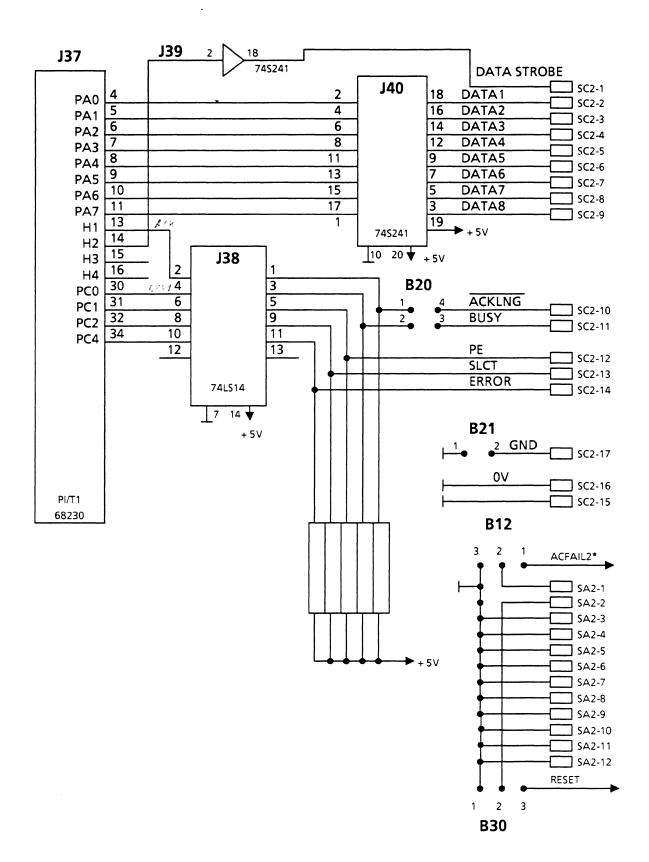

| 3.6              | The T/L Switch.                                                                                                                                                    | 34             |

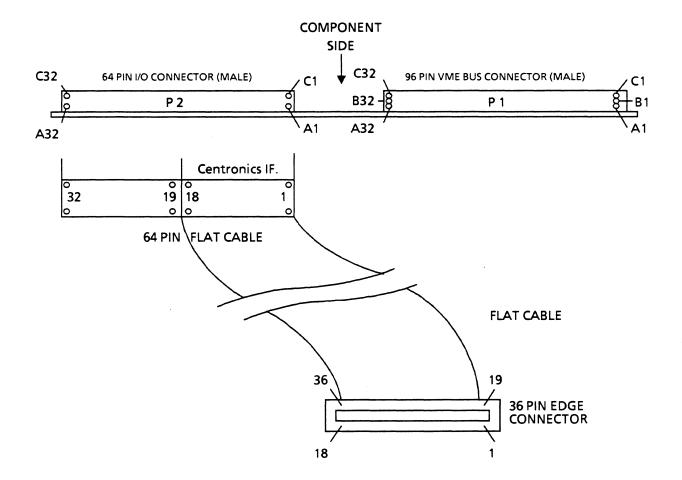

| 3.7              | IEEE 488 GPIB Connector.                                                                                                                                           | 35             |

| 3.8              | Serial Interface Connector                                                                                                                                         | 36             |

| 4.<br>4.1<br>4.2 | Interrupt Structure of the SYS68K/ASCU-1/2<br>Programming of the BIM on the ASCU-1/2<br>Interrupt Sources and IACK Daisy Chain Structure of<br>the SYS68K/ASCU-1/2 | 37<br>41<br>42 |

| 4.3              | Interrupt Vector Structure                                                                                                                                         | 44             |

| 5.               | Utility Signal Handling                                                                                                                                            | 48             |

| 5.1              | The SYSRESET* Signal                                                                                                                                               | 48             |

| 5.2              | The SYSFAIL* Signal                                                                                                                                                | 54             |

| 5.3              | The ACFAIL* Signal                                                                                                                                                 | 55             |

| 6.               | Functional Groups on the SYS68K/ASCU-1/2                                                                                                                           | 6Ø             |

| 7.               | Software Control                                                                                                                                                   | 66             |

| 7.1              | Addressing of the PI/T Devices                                                                                                                                     | 66             |

| 8.               | Power Monitor Module                                                                                                                                               | 71             |

| 8.1              | The RESET Generator                                                                                                                                                | 73             |

| 9.               | The SYSCLOCK Driver                                                                                                                                                | 77             |

| 1Ø.              | The 4-Level Bus Arbiter                                                                                                                                            | 79             |

| 1Ø.1             | The PRI Arbiter                                                                                                                                                    | 86             |

| 1Ø.2             | The RRS Arbiter                                                                                                                                                    | 87             |

| 1Ø.3             | The PRR Arbiter                                                                                                                                                    | 88             |

| 11.              | The Bus Timer                                                                                                                                                      | 89             |

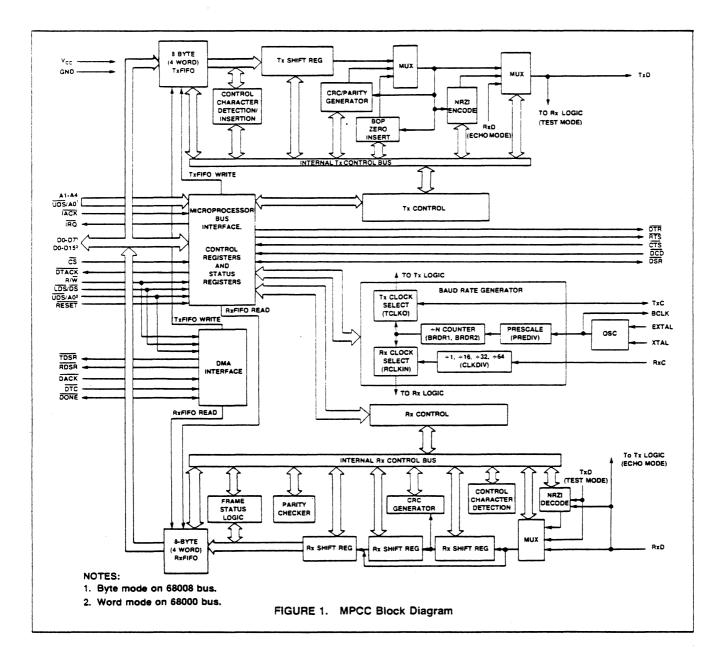

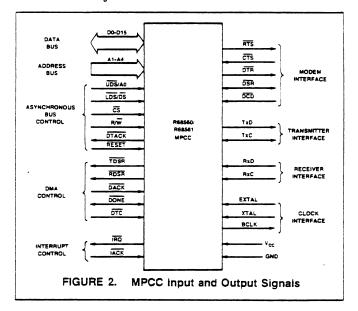

| 12.              | The Serial I/O Interface                                                                                                                                           | 91             |

| 12.1             | The MPCC Interrupt Scheme                                                                                                                                          | 1Ø5            |

| 12.2             | Programming Example for an MPCC Initialization                                                                                                                     | 1Ø6            |

٠

|                                             |                                                                                                                                                                                                                       | Page                                   |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 13.<br>13.1                                 | Centronics Interface<br>Interrupt Scheme of the Centronics Interface                                                                                                                                                  | 1Ø8<br>115                             |

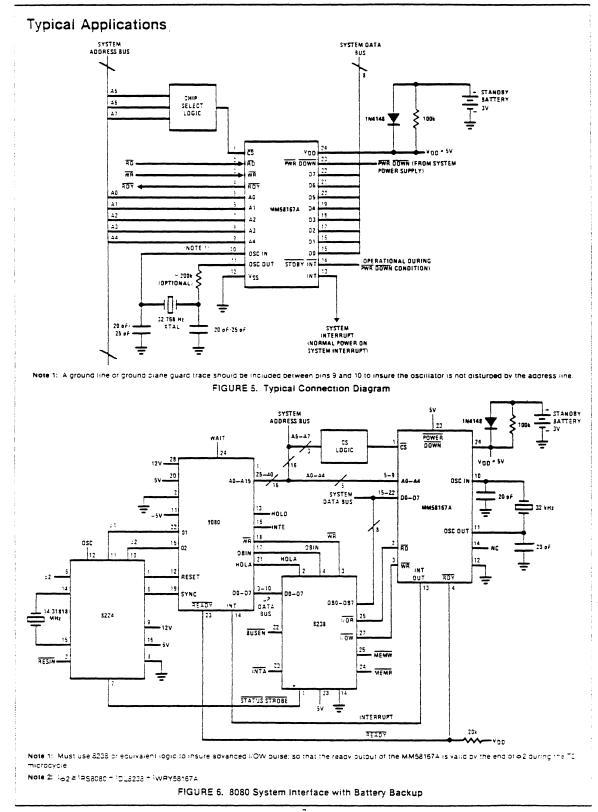

| 14.<br>14.1<br>14.2<br>14.3                 | The Real Time Clock<br>Features of the RTC<br>Timing of the RTC<br>The RTC Interrupt Scheme                                                                                                                           | 117<br>119<br>121<br>125               |

| 15.<br>15.1<br>15.2<br>15.3                 | Special Interrupts<br>The TEST Interrupt<br>The User Interrupt 1<br>The User Interrupts 2-5                                                                                                                           | 126<br>126<br>129<br>13Ø               |

| 16.                                         | Timer Interrupt                                                                                                                                                                                                       | 131                                    |

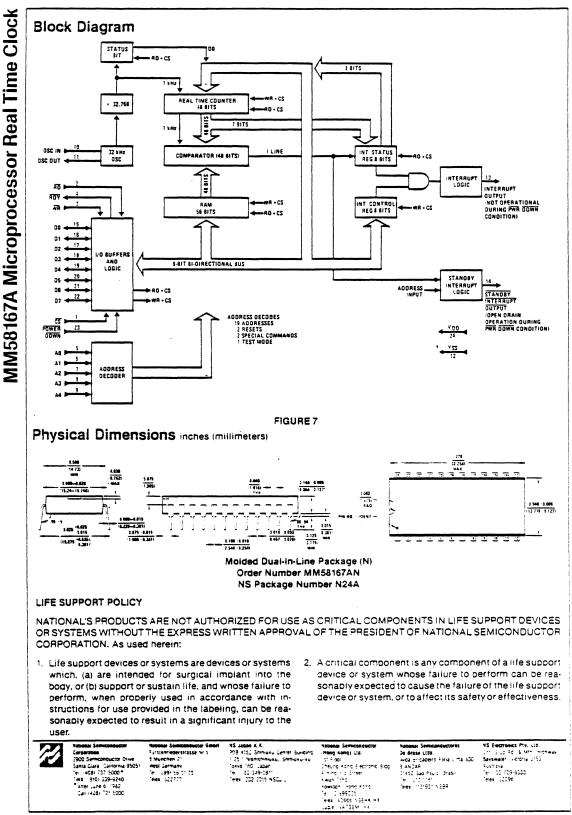

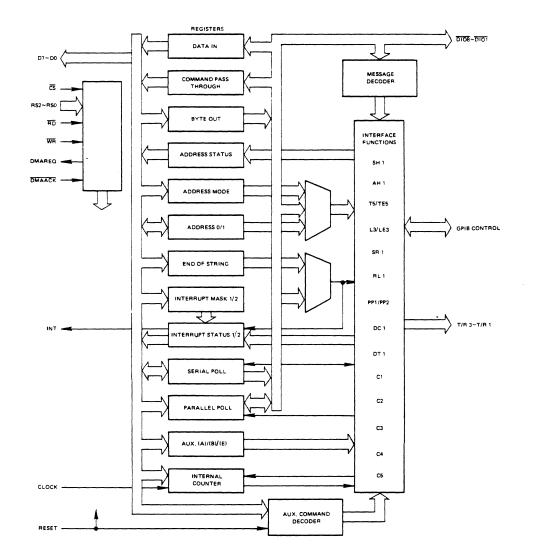

| 17.<br>17.1<br>17.2<br>17.3<br>17.4<br>17.5 | The IEEE 488 GPIB Interface<br>Features of the NEC 7210<br>Hardware Realization of the GPIB Interface<br>Addressing of the GPIB Controller<br>The GPIB Interrupt Scheme<br>Programming Example of the GPIB Controller | 132<br>136<br>137<br>141<br>142<br>144 |

| 18.                                         | Software Programmable Interrupts                                                                                                                                                                                      | 146                                    |

| 19.<br>19.1<br>19.2                         | The BCLR* Timing Function<br>BCLR* Signal Generation Structure<br>The BCLR* Timer                                                                                                                                     | 148<br>148<br>148                      |

| 20.                                         | Board Register Summary                                                                                                                                                                                                | 153                                    |

| 21.                                         | General Information                                                                                                                                                                                                   | 17Ø                                    |

| 22.                                         | Installation of the SYS68K/ASCU-1/2                                                                                                                                                                                   | 171                                    |

|                                             |                                                                                                                                                                                                                       |                                        |

.

,

#### APPENDIX:

- A: Specification of the SYS68K/ASCU-1/2

- B: Address Assignment of the SYS68K/ASCU-1/2 Devices

- C: Description of the Jumperfields

- D: PIN-Assignment on the SYS68K/ASCU-1/2

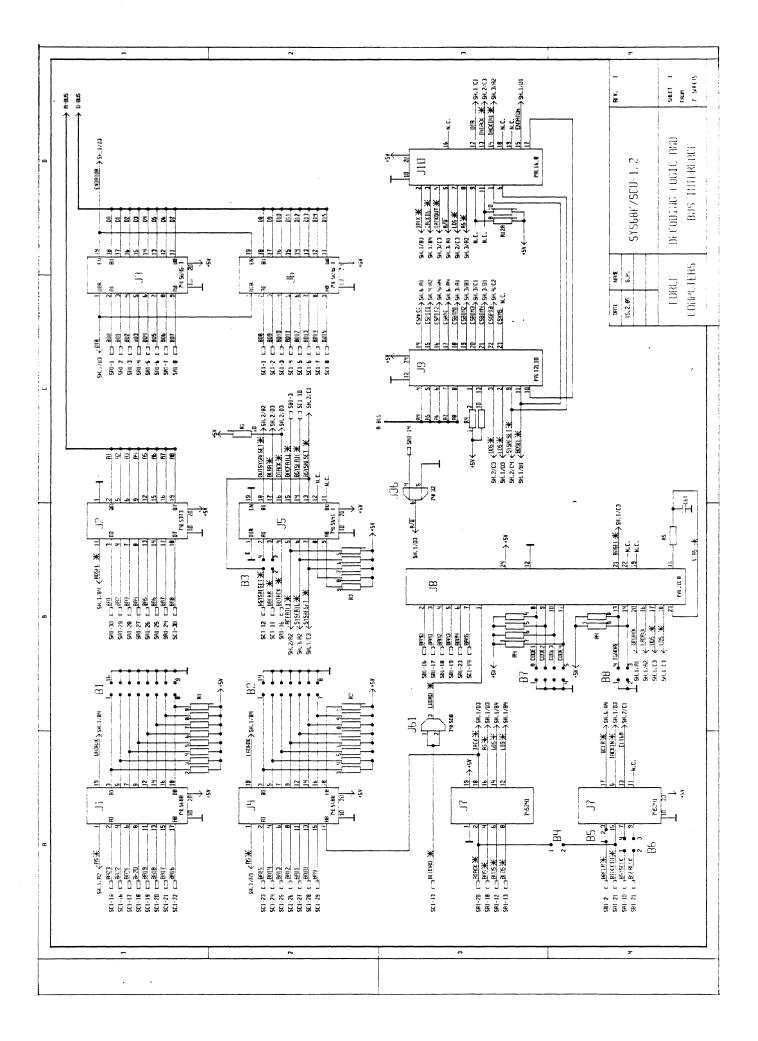

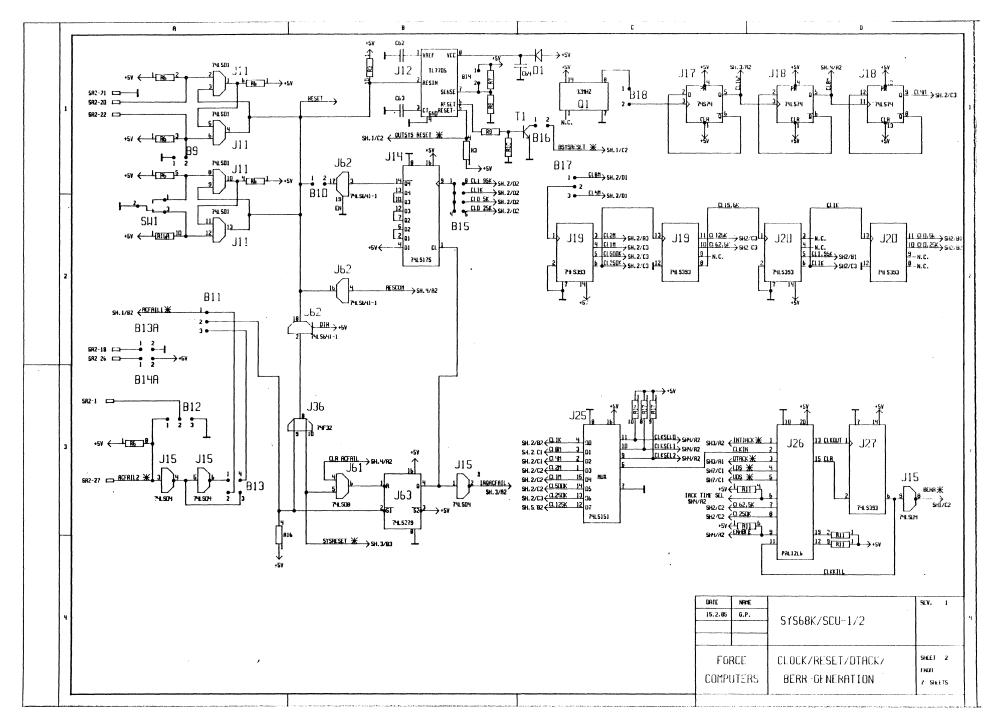

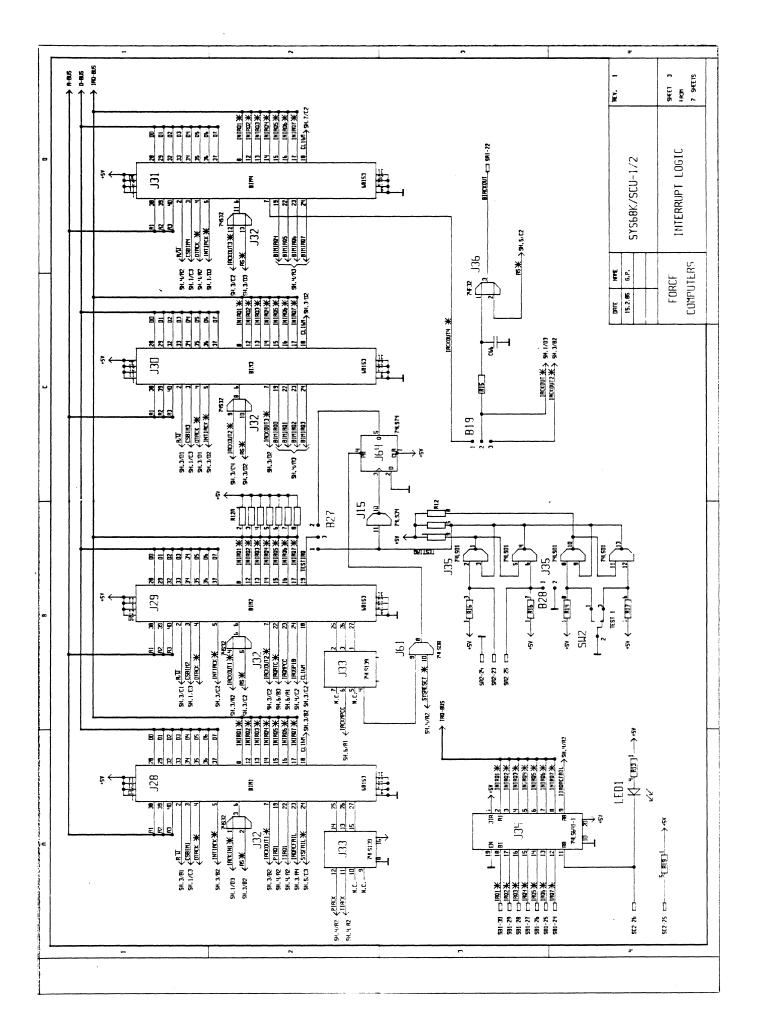

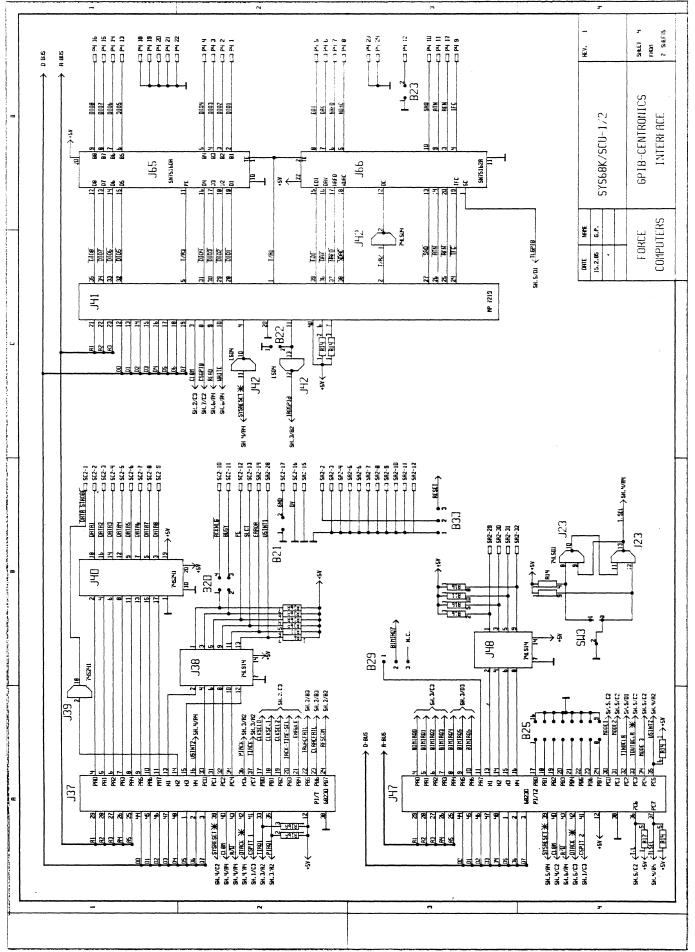

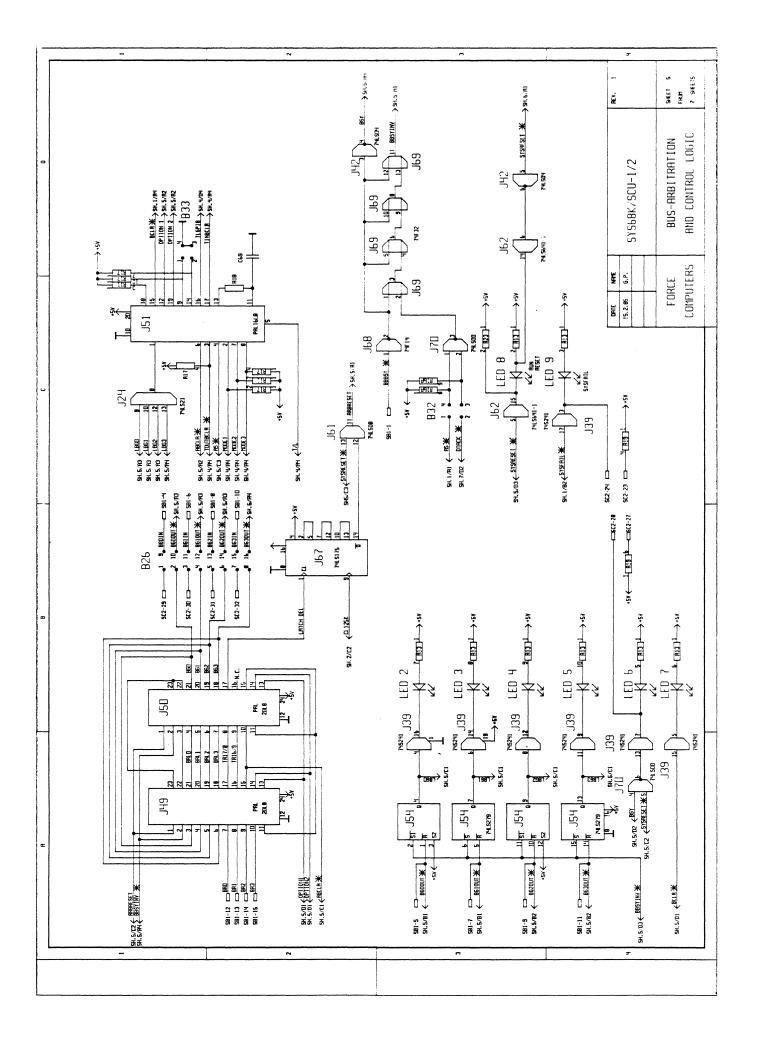

- E: Circuit Schematics

- F: Component Part List SYS68K/ASCU-1/2

- G: Glossary of VMEbus/PlØ14 Terms

| H: | Data Sheets | 68153  | BIM  |

|----|-------------|--------|------|

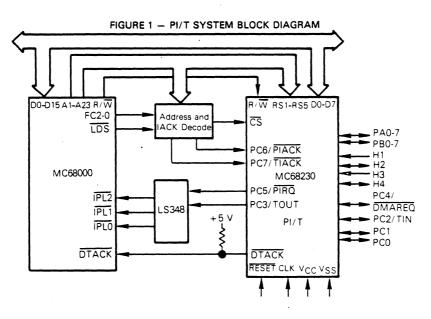

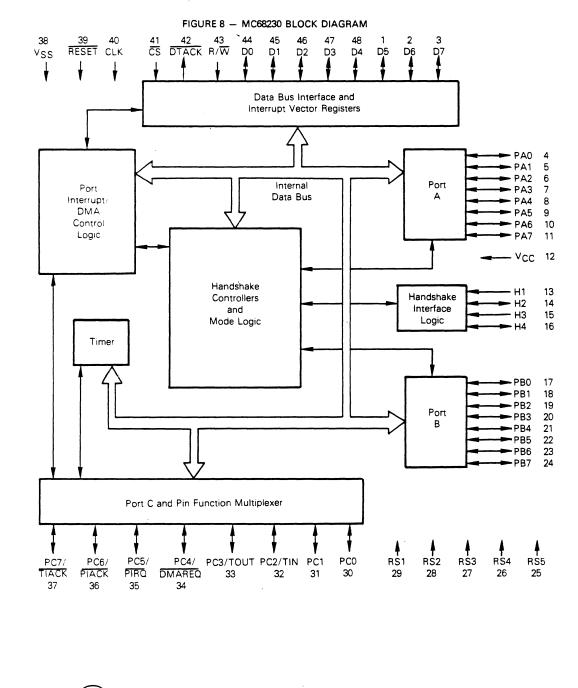

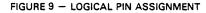

|    |             | 6823Ø  | PI/T |

|    |             | 68561  | MPCC |

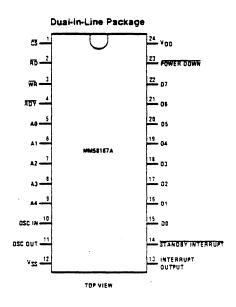

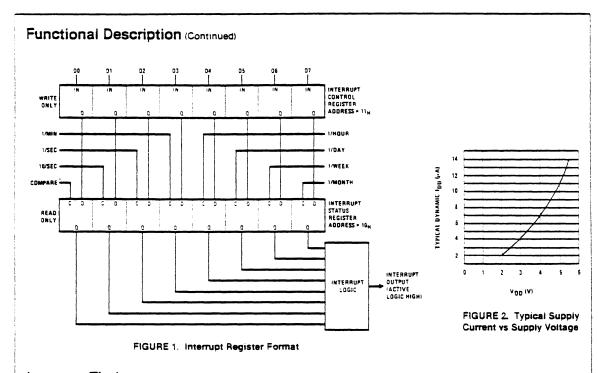

|    |             | 58167A | RTC  |

|    |             | 721Ø   | GPIB |

I: Product Error Report

## List of Figures

| Fig.# |                                                                                                       | Page |

|-------|-------------------------------------------------------------------------------------------------------|------|

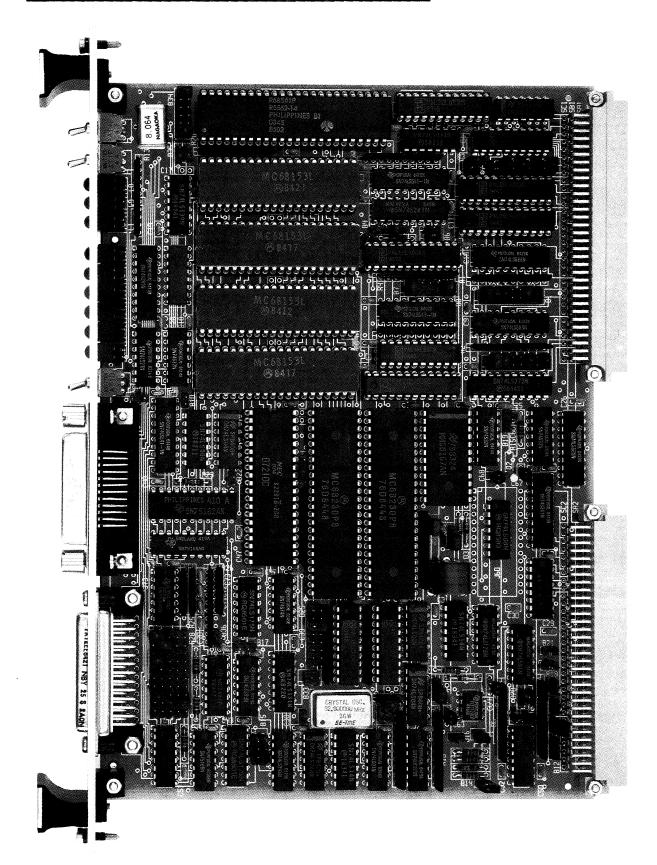

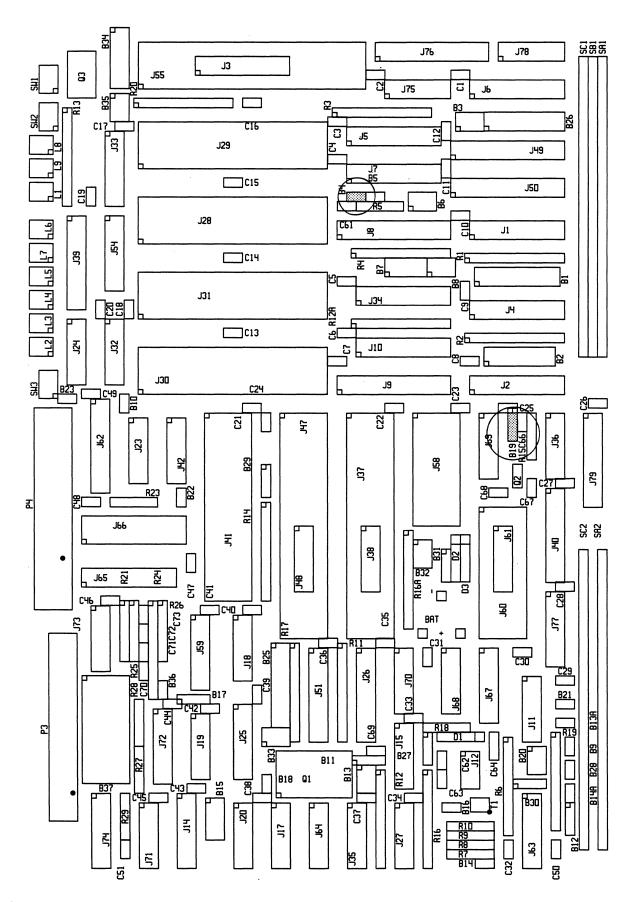

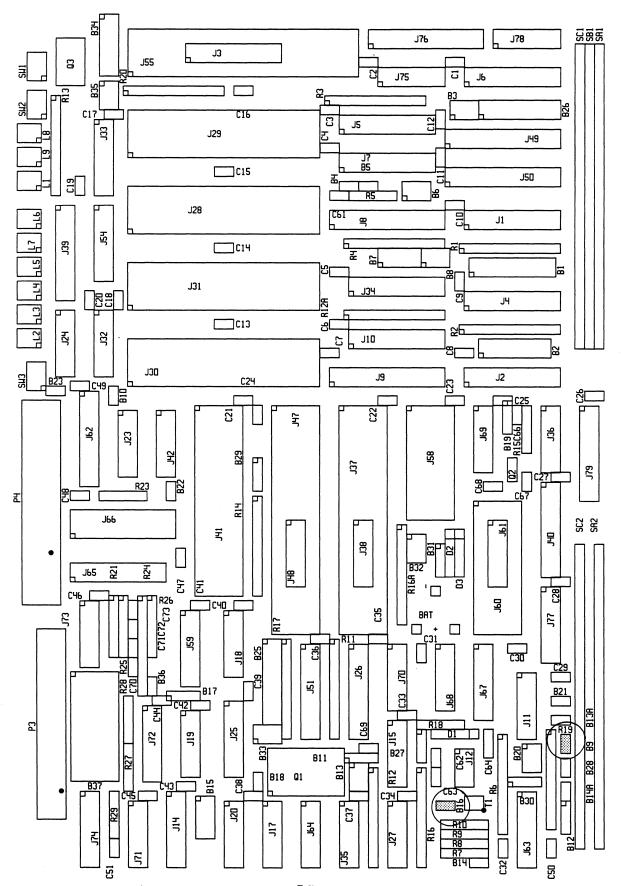

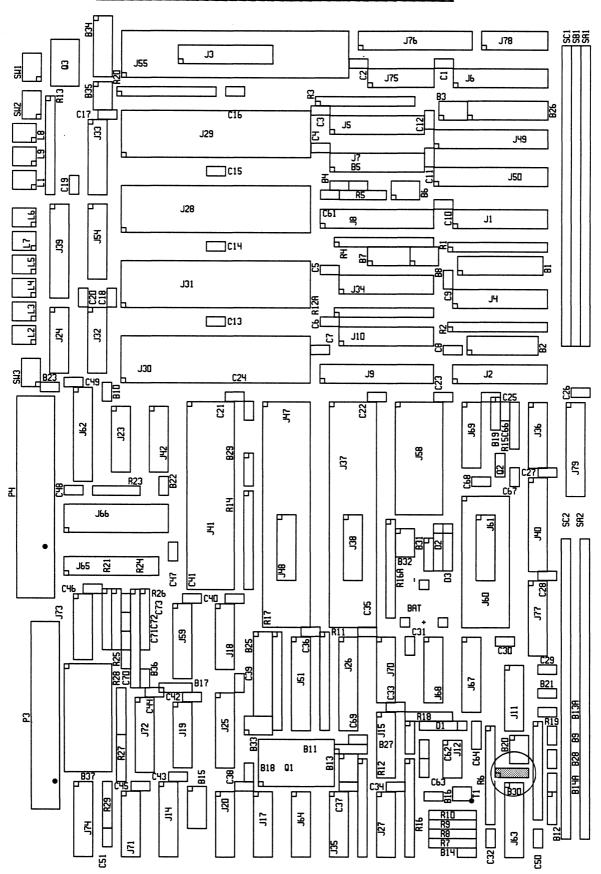

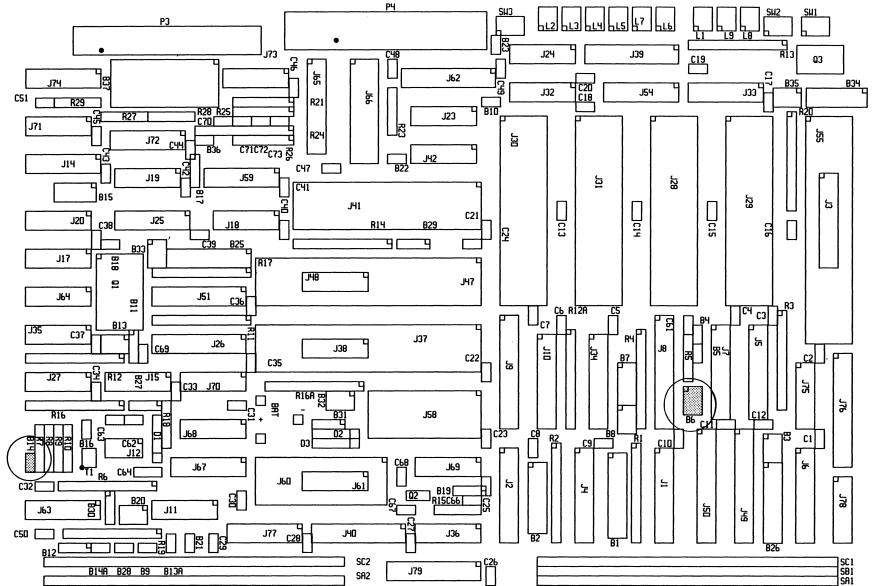

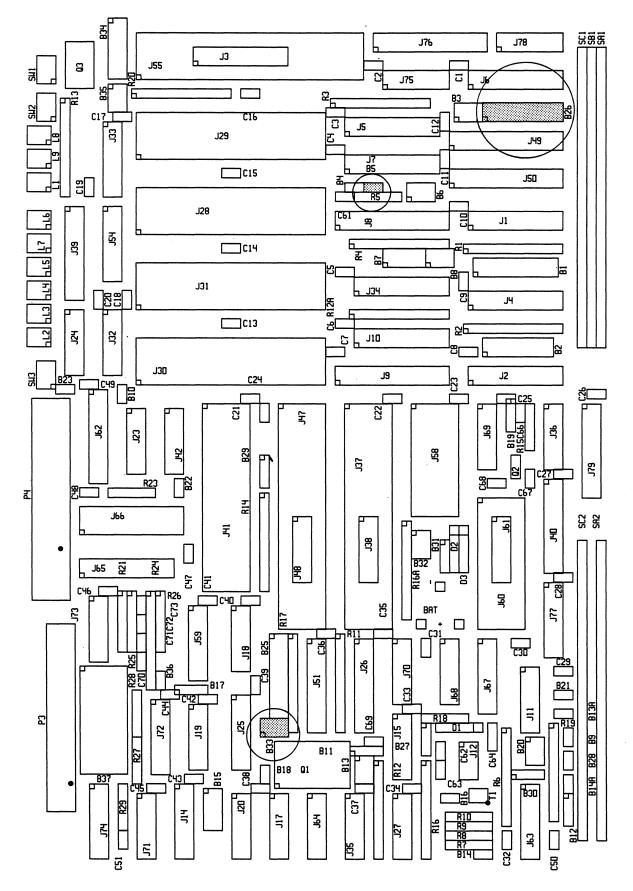

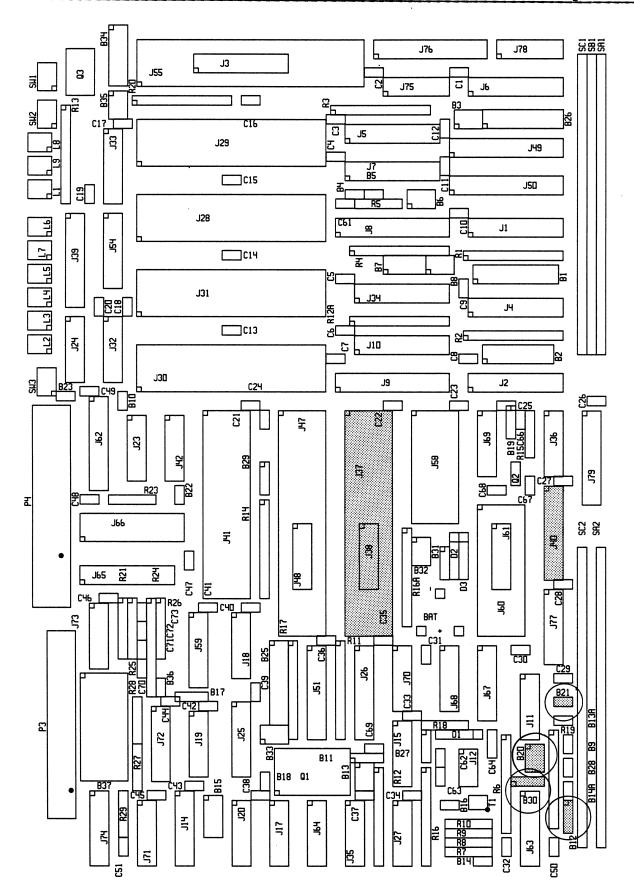

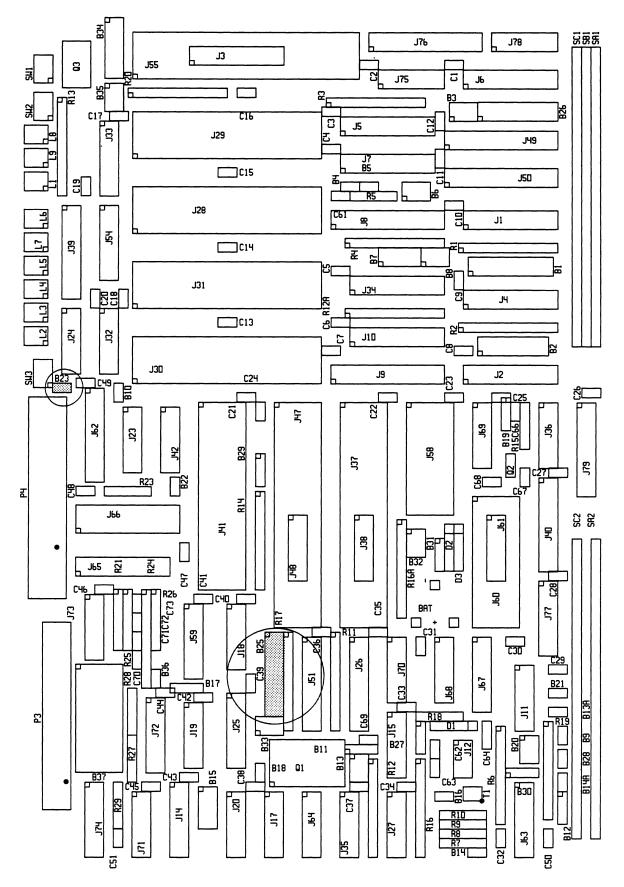

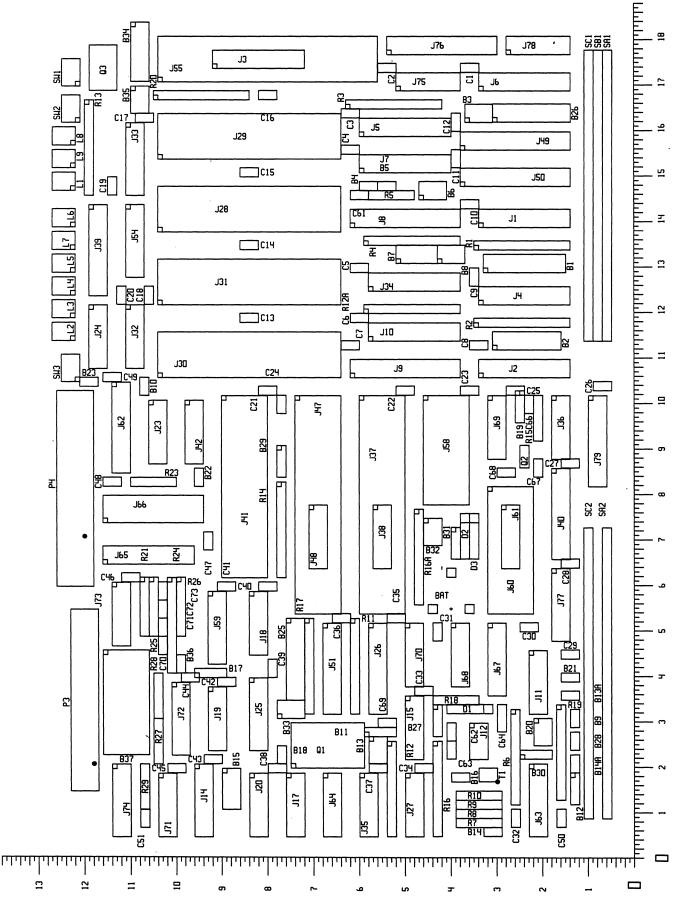

| 1     | Photo of the SYS68K/ASCU-1/2 Board                                                                    | 12   |

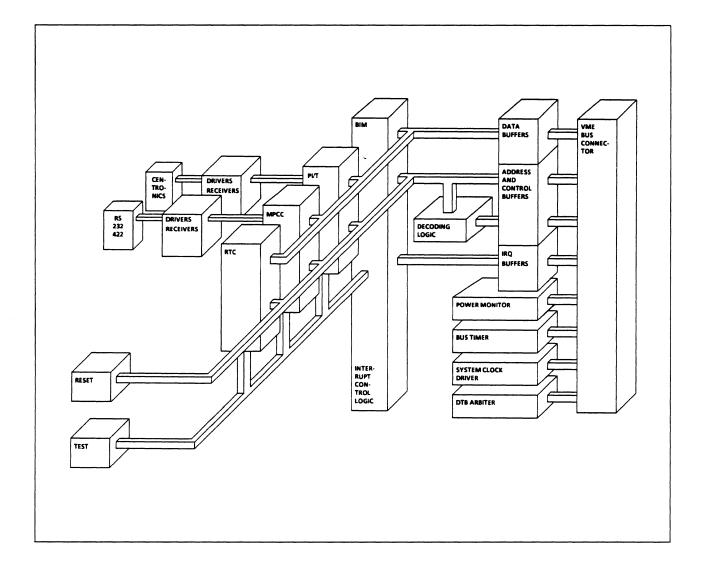

| 2     | Block Diagram of the SYS68K/ASCU-1                                                                    | 15   |

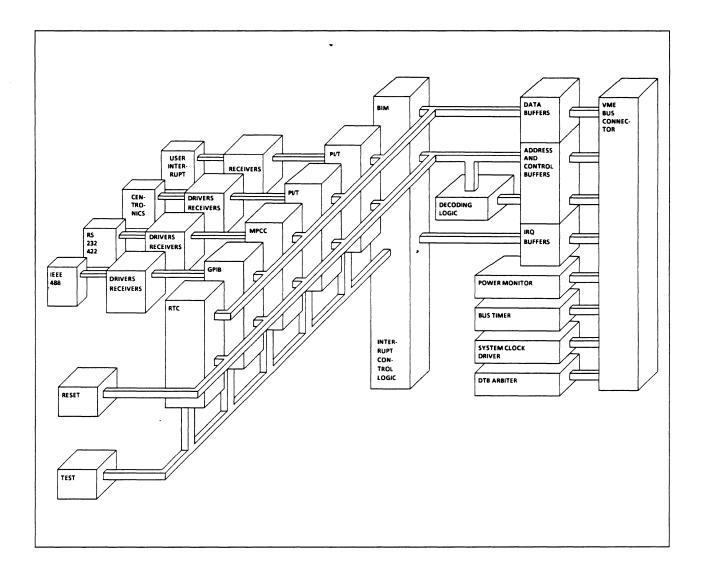

| 3     | Block Diagram of the SYS68K/ASCU-2                                                                    | 17   |

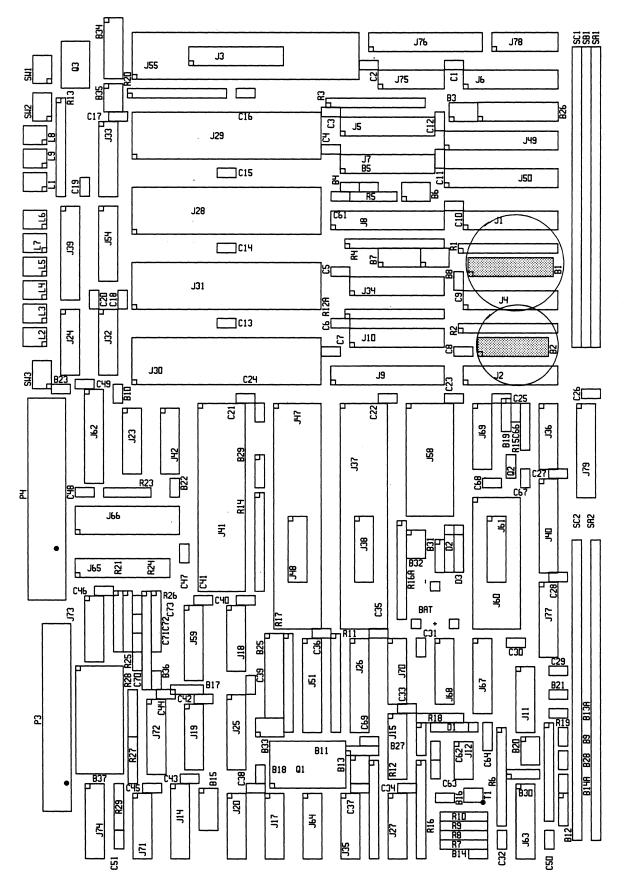

| 4     | Jumper Location Diagram for the Board Base Address<br>Selection                                       | 2Ø   |

| 5     | Board Base Address Selection                                                                          | 21   |

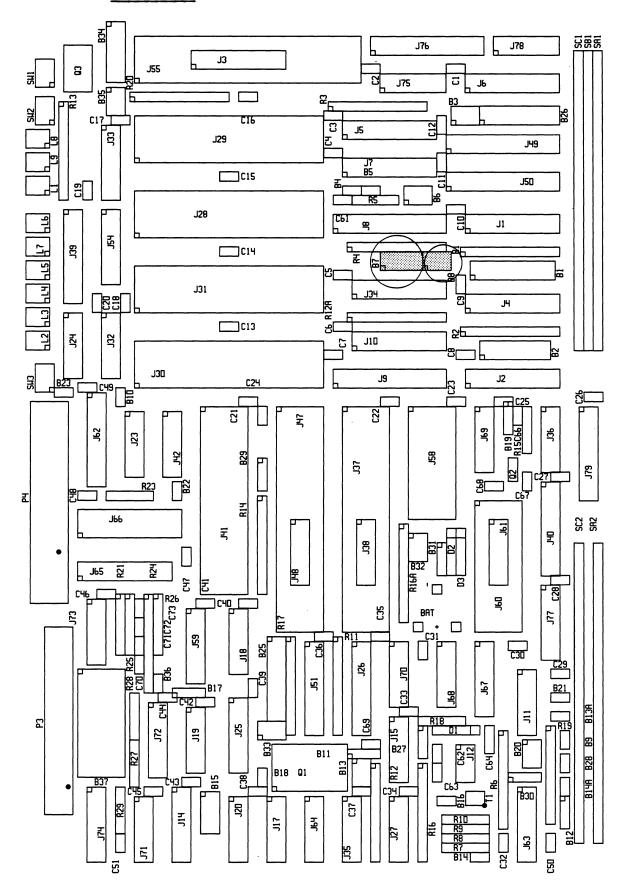

| 6     | Jumper Location Diagram for the Address Modifier<br>Code Selection                                    | 27   |

| 7     | Address Modifier Code Selection                                                                       | 28   |

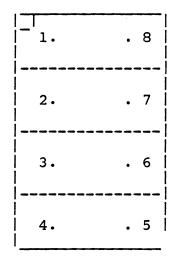

| 8     | The Front Panel of the SYS68K/ASCU-2                                                                  | 32   |

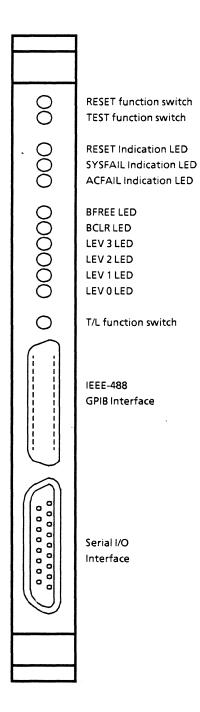

| 9     | Jumperfield Location Diagram of B4 and B19                                                            | 4Ø   |

| lØ    | The SYSRESET Jumperfield B16 and the Jumperfield B9<br>for the first External RESET Switch Connection | 5ø   |

| 11    | Jumperfield B3Ø for Selection of the Centronics<br>Interface / second Optional RESET Switch           | 52   |

| 12    | Jumper Locations of the ACFAIL* Signal Handling BlØ,<br>B12, B13 and B15                              | 59   |

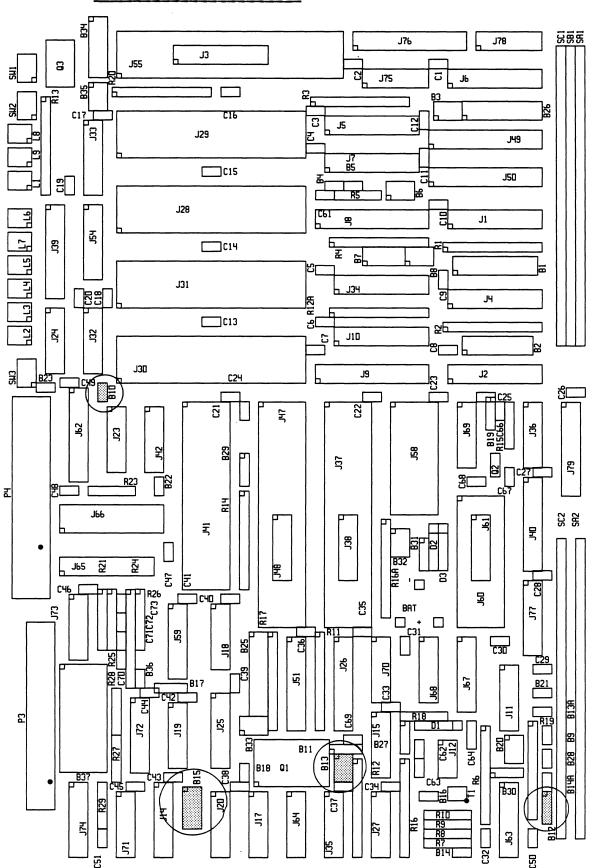

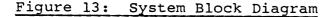

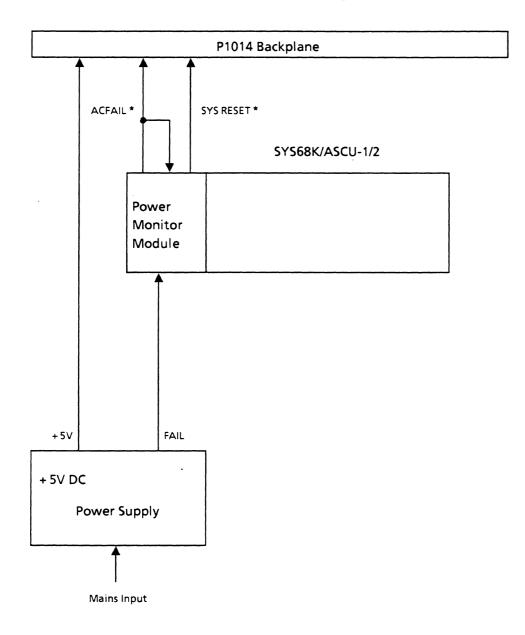

| 13    | System Block Diagram                                                                                  | 71   |

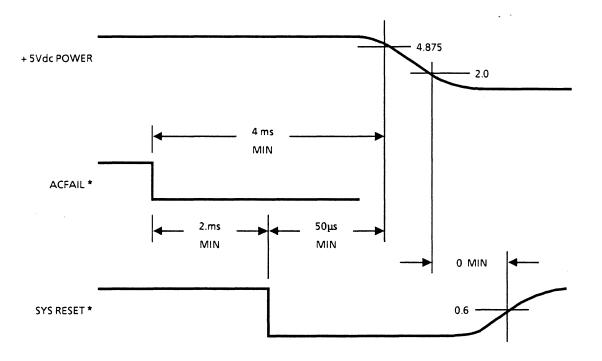

| 14    | Power Fail Timing Diagram                                                                             | 72   |

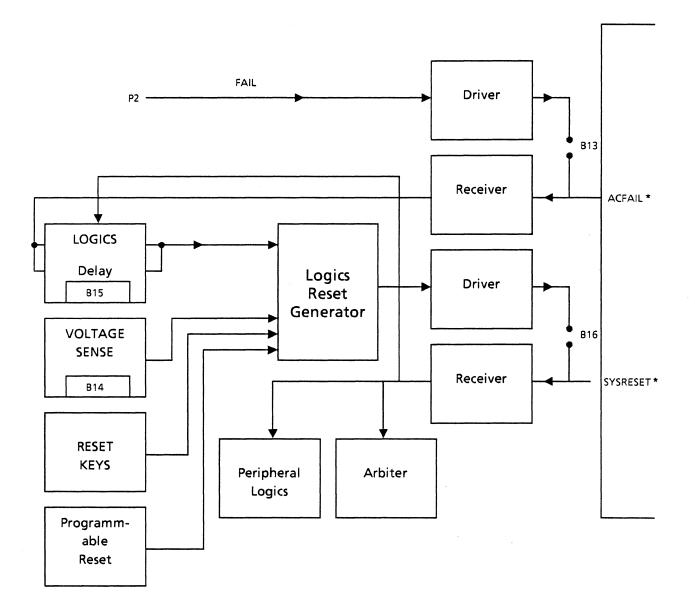

| 15    | Block Diagram of the RESET Structure                                                                  | 74   |

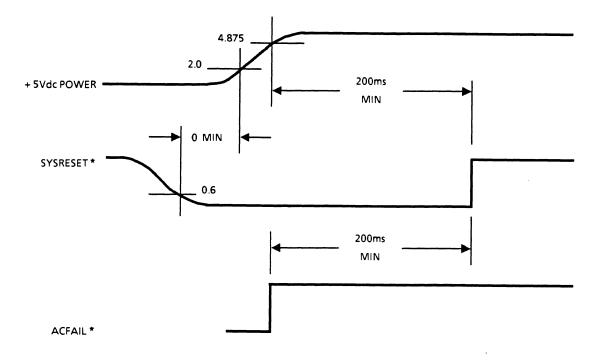

| 16    | Power Monitor System Restart Timing                                                                   | 75   |

| 17    | Location Diagram of Jumperfields Bl4 and B6                                                           | 76   |

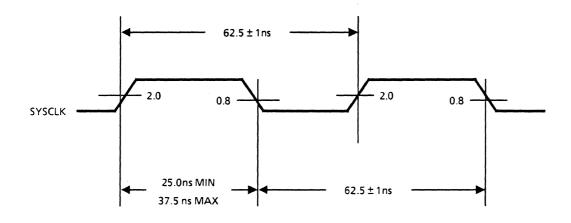

| 18    | SYSCLK Timing Diagram                                                                                 | 78   |

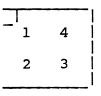

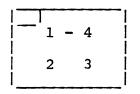

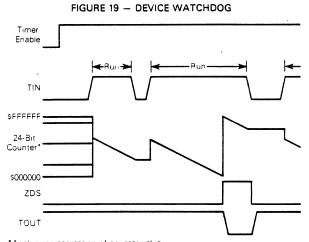

| 19    | Pin-Out of Jumperfield B26                                                                            | 8Ø   |

| 2Ø    | Location Diagram of the Arbiter Jumperfields                                                          | 82   |

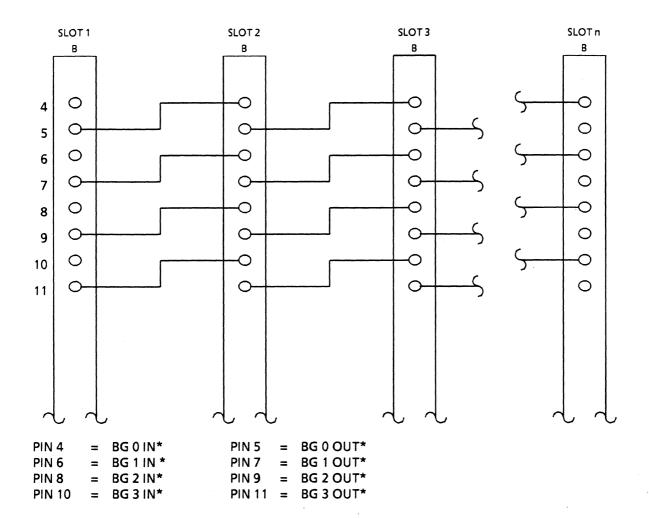

| 21    | The Bus Grant Daisy Chain                                                                             | 84   |

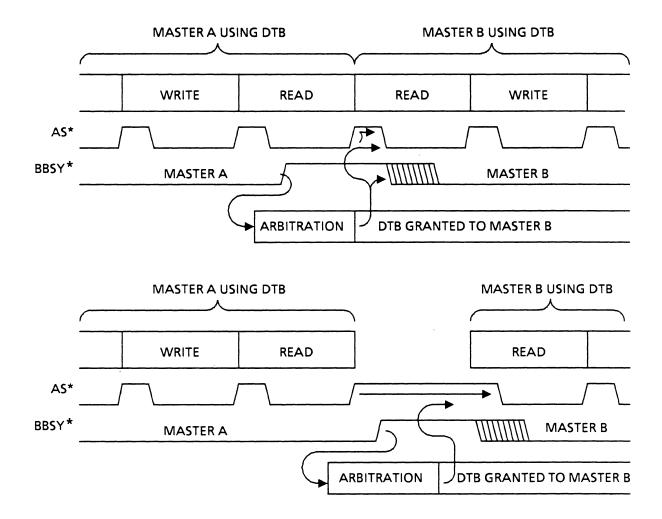

| 22    | Global DTB Arbitration Timing                                                                         | 85   |

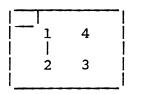

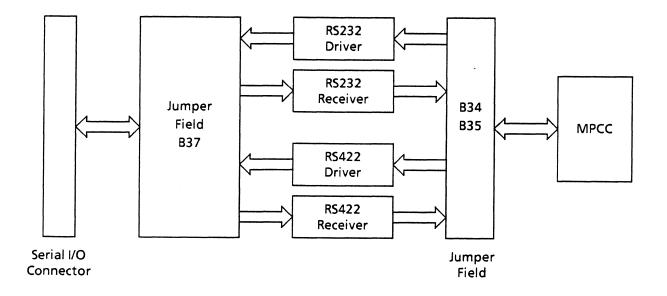

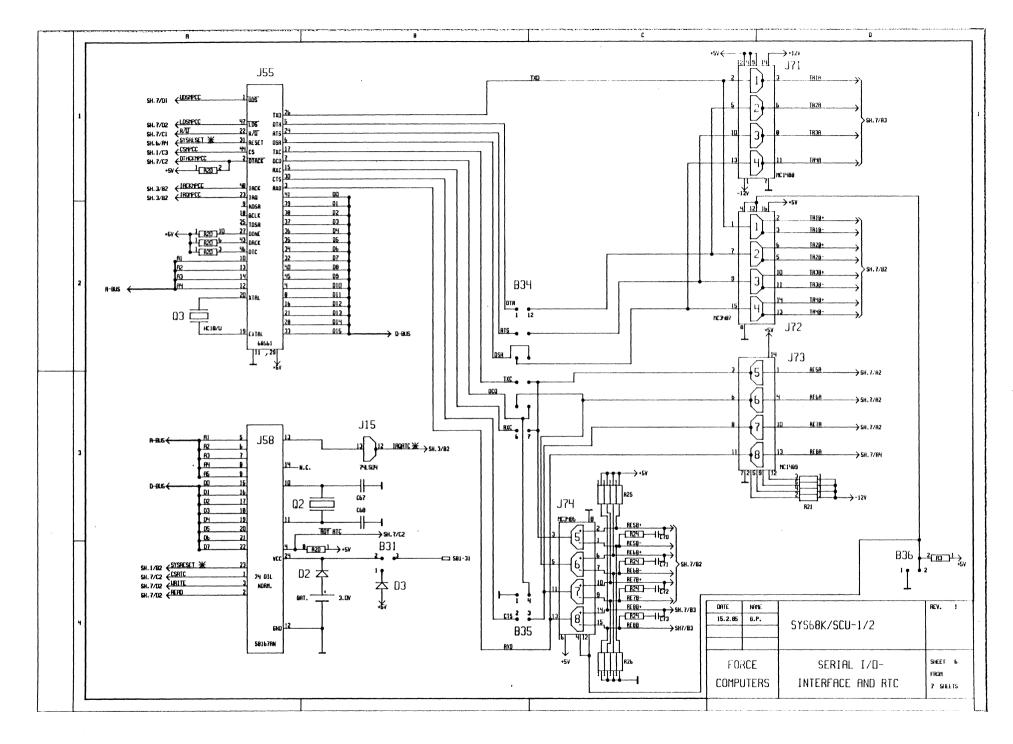

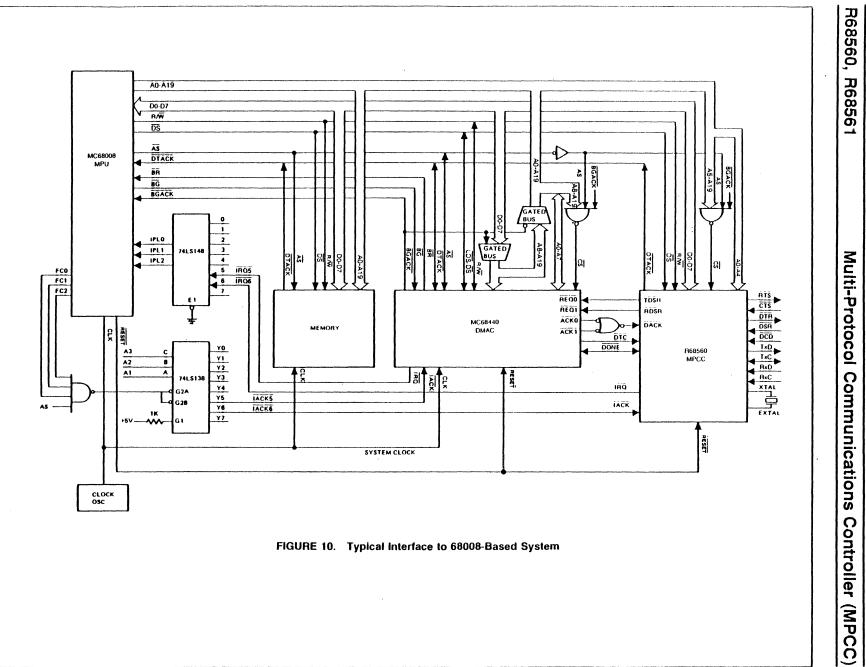

| 23    | Block Diagram of the Serial I/O Interface                                                             | 96   |

8

| Fig.# |                                                                     | Page |

|-------|---------------------------------------------------------------------|------|

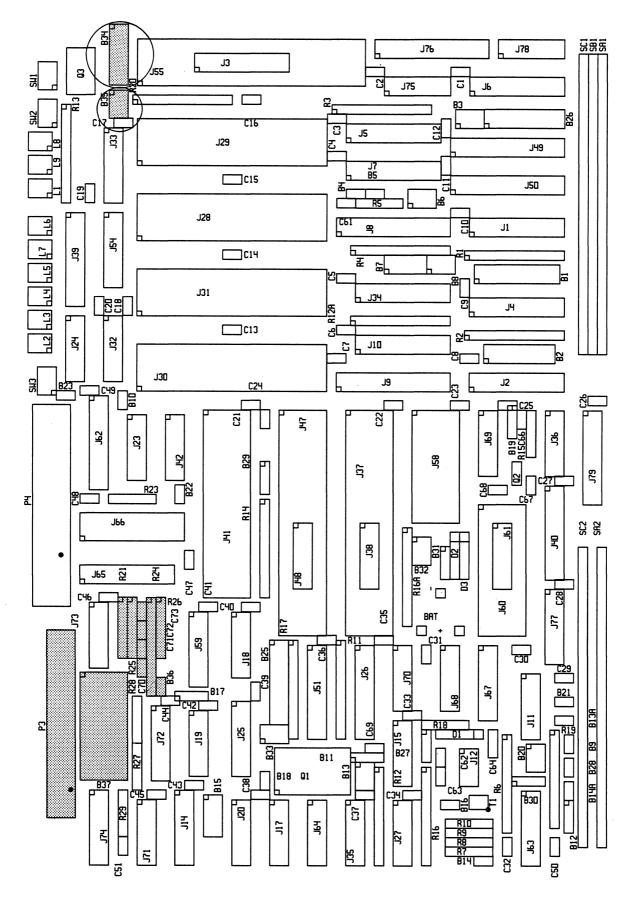

| 24    | Location Diagram of the Serial I/O Interface Parts                  | 98   |

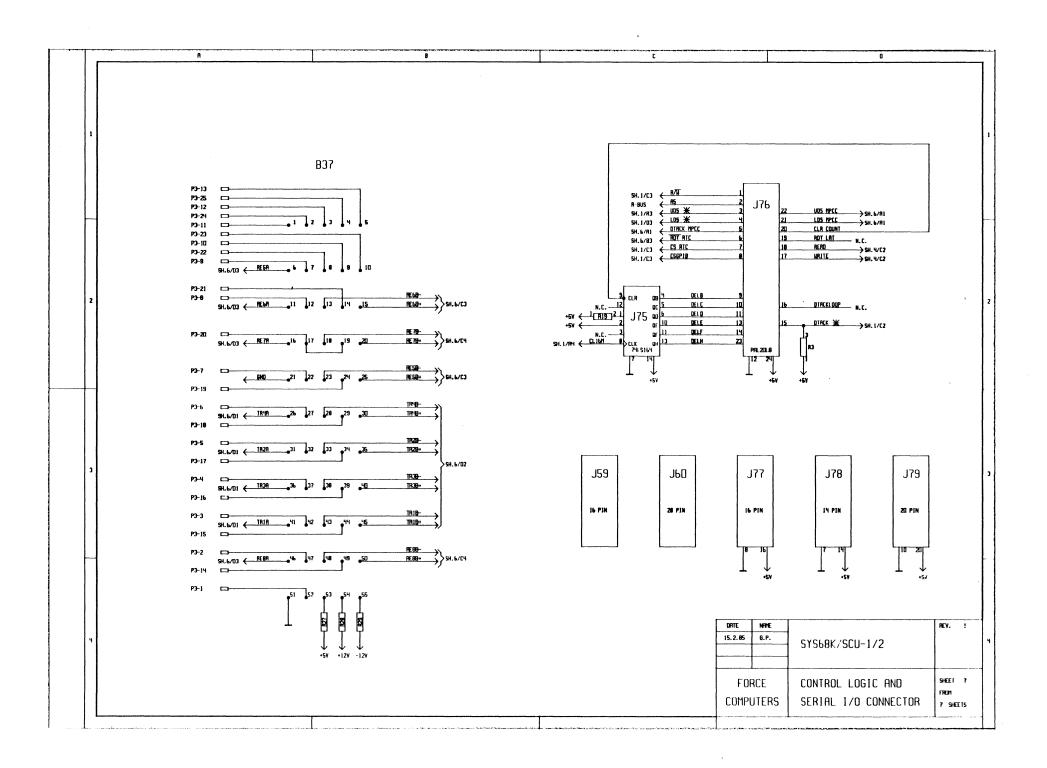

| 25    | Signal Assignment of Jumperfield B37                                | 100  |

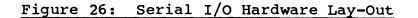

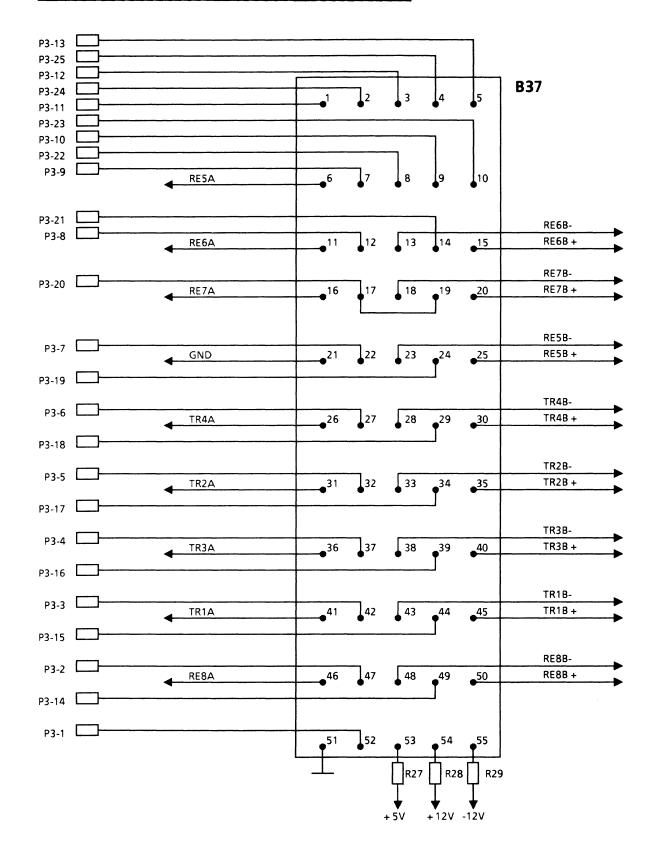

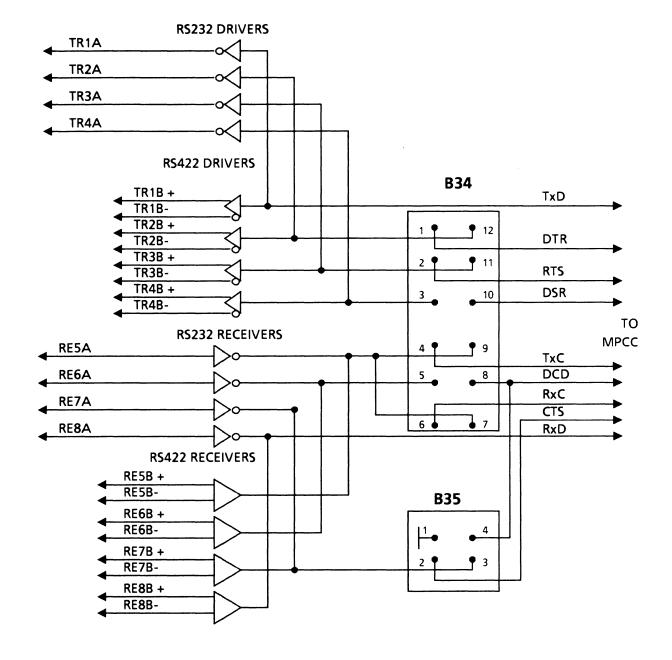

| 26    | Serial I/O Hardware Lay-out                                         | 1Ø1  |

| 27    | The Optional R/C Implementation                                     | 1Ø2  |

| 28    | Connection between the SYS68K/ASCU-1/2 Board and a<br>Terminal      | 1Ø4  |

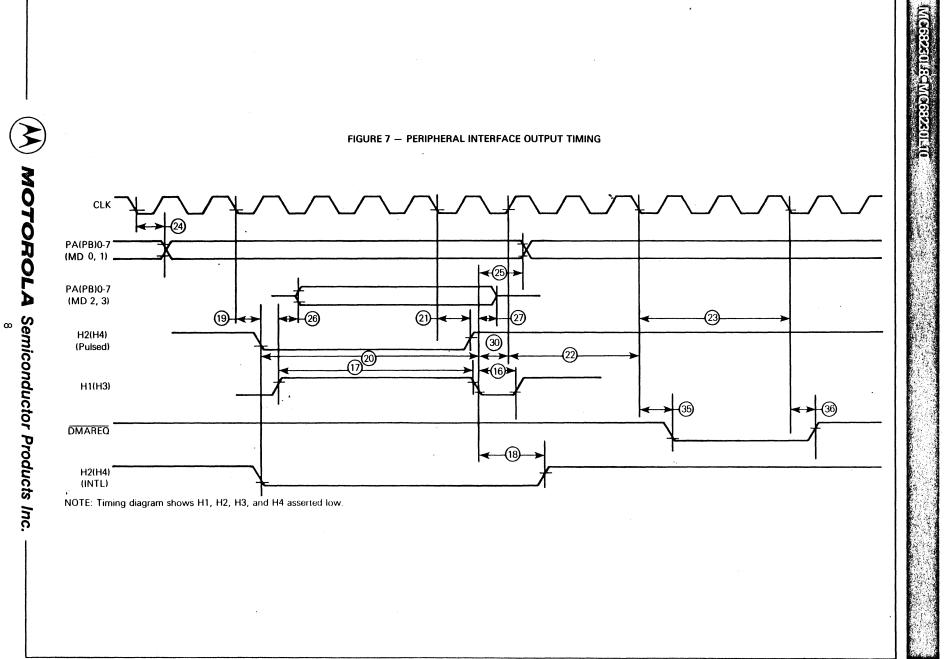

| 29    | Timing Diagram of the Centronics Parallel Interface                 | 11Ø  |

| 3Ø    | Hardware Realization of the Centronics Interface                    | 111  |

| 31    | Connection Example for the Centronics Interface                     | 113  |

| 32    | Location Diagram of the Centronics Interface<br>Components          | 114  |

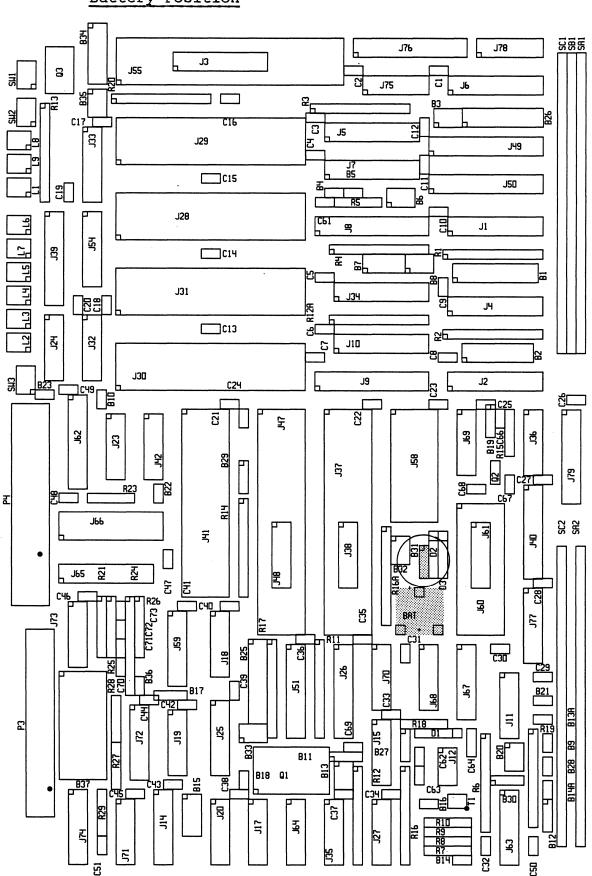

| 33    | Location Diagram of the Jumperfield B31 and the<br>Battery Position | 118  |

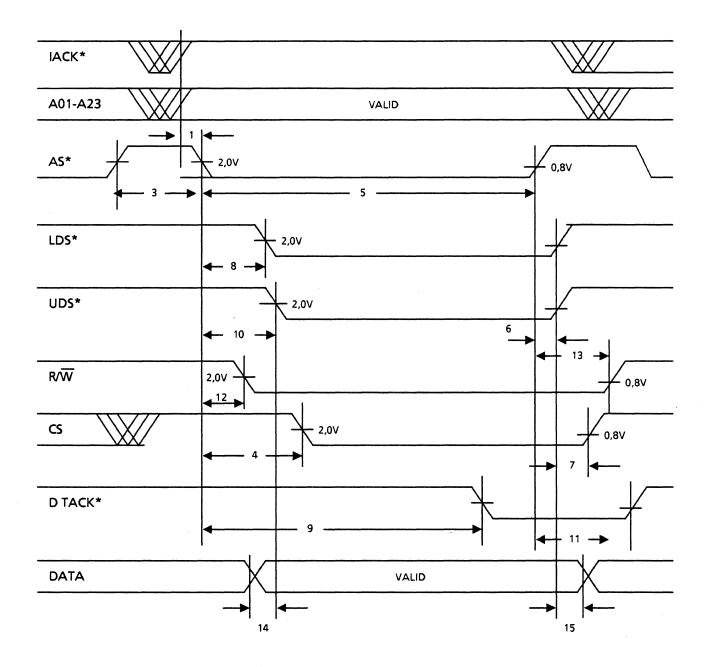

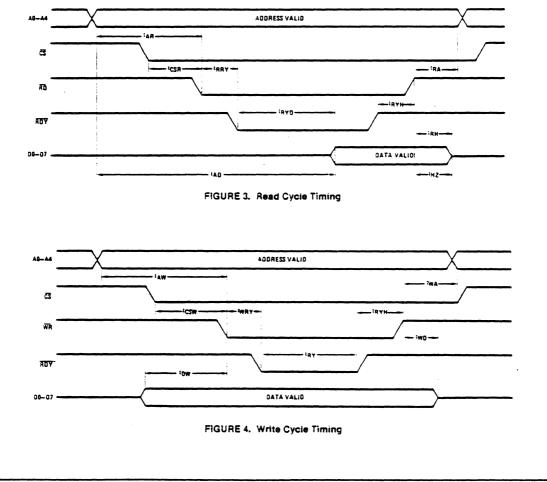

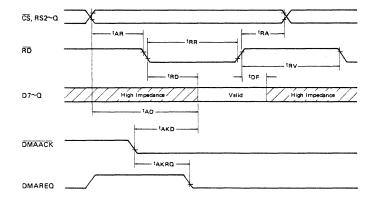

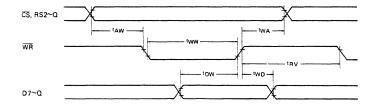

| 34    | RTC Write Cycle Timing Diagram                                      | 122  |

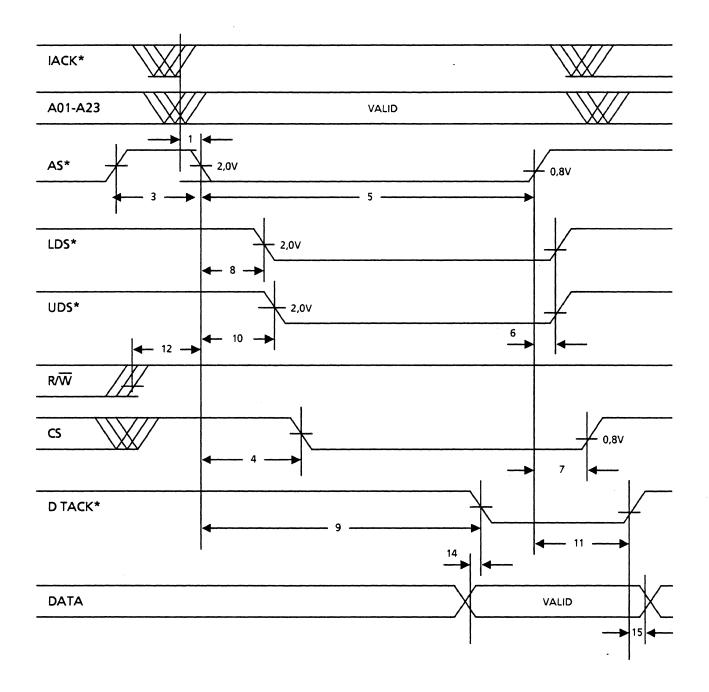

| 35    | RTC Read Cycle Timing Diagram                                       | 124  |

| 36    | Location Diagram of the TEST Interrupt Jumperfield                  | 127  |

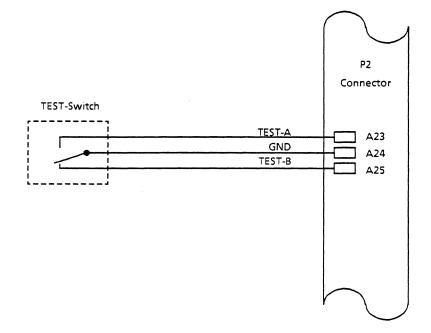

| 37    | Connection of an External TEST Switch                               | 128  |

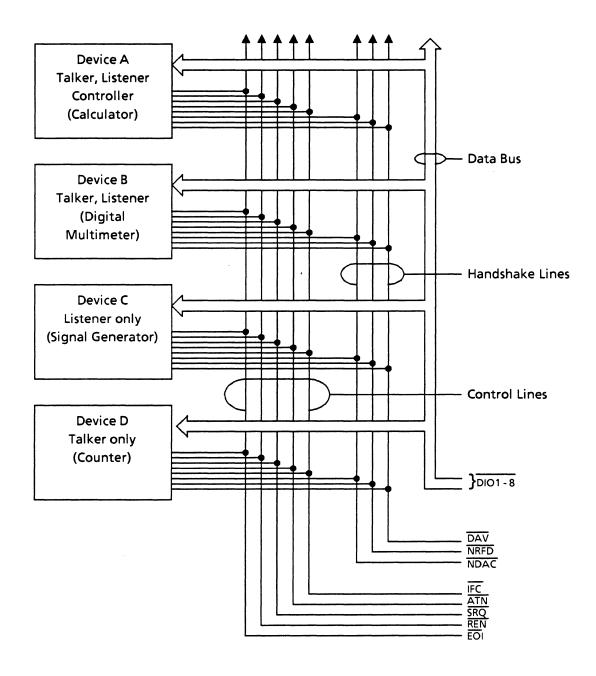

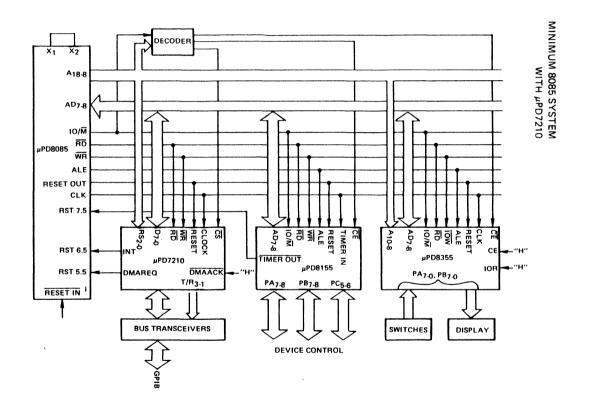

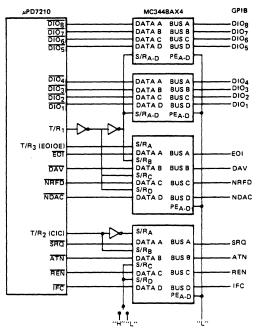

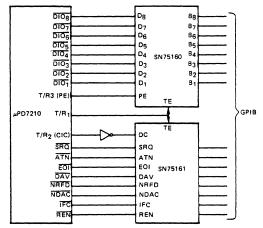

| 38    | GPIB Structure and Possible Bus Configurations                      | 133  |

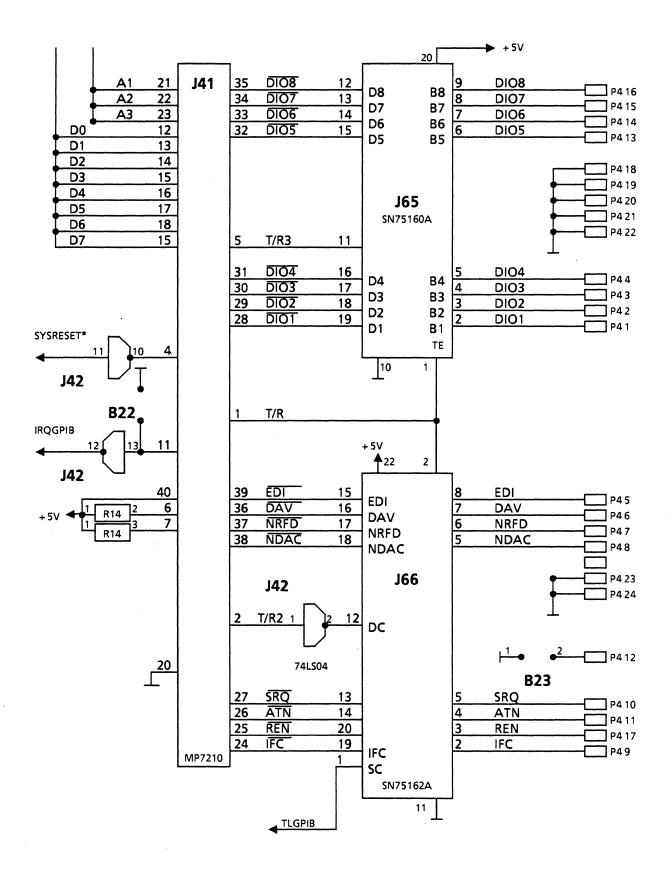

| 39    | Hardware Schematics of the GPIB Interface                           | 134  |

| 4Ø    | Pin-Out of the Jumperfield B25                                      | 138  |

| 41    | Location Diagram of the Jumperfields B23 and B25                    | 139  |

9

| Table | # List of Tables Page                                |     |

|-------|------------------------------------------------------|-----|

| 1     | Board Base Address Selection                         | 22  |

| 2     | Address Modifier Codes                               | 24  |

| 3     | Address Modifier Code Selection                      | 26  |

| 4     | IEEE 488 Connector Pin Assignment                    | 35  |

| 5     | Default I/O Signal Assignment to the D-Sub-Connector | 36  |

| 6     | Sequence of the On-Board IACK Daisy Chain            | 43  |

| 7     | Non-Vectorized Interrupt Sources                     | 45  |

| 8     | Vectorized Interrupt Source                          | 46  |

| 9     | Optional Vectorized Interrupt Source 1               | 47  |

| 10    | Optional Vectorized Interrupt Source 2               | 47  |

| 11    | RESET* on the ASCU-1/2                               | 48  |

| 12    | The Power Fail Signal Level                          | 56  |

| 13    | ACFAIL* Interrupt Channel Address Assignment         | 57  |

| 14    | Delay of the SYSRESET* Generation after ACFAIL*      | 58  |

| 15    | Functional Group Distribution                        | 63  |

| 16    | Software Control I/O Pins                            | 67  |

| 17    | Selection of the Arbitration Type                    | 79  |

| 18    | Jumper Selection for Enabled Bus Arbiter Function    | 8Ø  |

| 19    | Jumper Selection for Disabled Bus Arbiter Function   | 81  |

| 2Ø    | BCLR* Generation on the SYS68K/ASCU-1                | 83  |

| 21    | Bus Time-Out Values                                  | 89  |

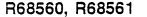

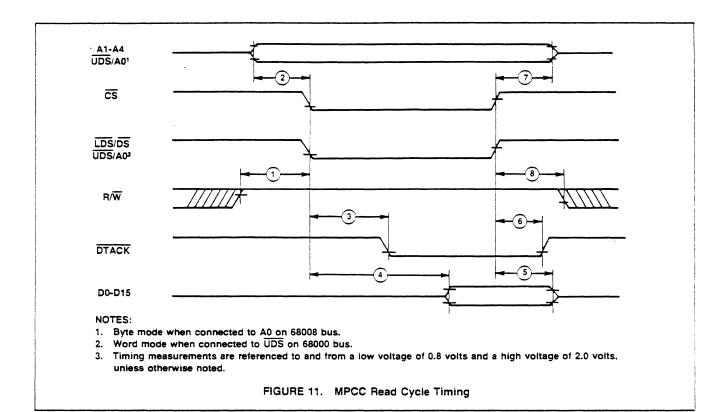

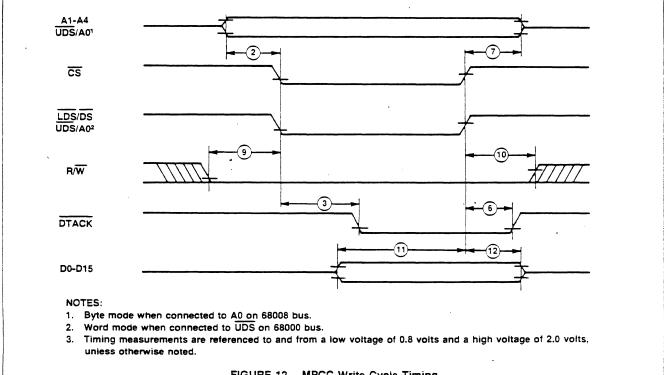

| 22    | The MPCC Address Map in the Byte Mode of Addressing  | 92  |

| 23    | The MPCC Address Map in the Word Mode of Addressing  | 93  |

| 24    | The Signal Assignments of the MPCC Serial Interface  | 97  |

| 25    | Default Jumper Settings for RS232 I/O Signals        | 1Ø3 |

| 25a   | MPCC Interrupt Channel Address Assignment            | 1Ø5 |

| 26    | Signal Assignment of Centronics Printer Interface    | 112 |

| 27    | Centronics Interrupt Assignment                      | 115 |

1Ø

,

| 28 | Power Connection for the RTC                         | 117 |

|----|------------------------------------------------------|-----|

| 29 | Register Table of the RTC                            | 120 |

| 3Ø | RTC Write Time Values                                | 121 |

| 31 | RTC Read Time Values                                 | 123 |

| 32 | RTC Interrupt Channel Address Assignment             | 125 |

| 33 | TEST Interrupt Channel Address Assignment            | 126 |

| 34 | TIMER Interrupt Channel Address Assignment           | 131 |

| 35 | GPIB Interface Capabilities                          | 135 |

| 36 | GPIB Address Selection                               | 138 |

| 37 | IEEE 488 Connector PIN Assignment                    | 14Ø |

| 38 | Register Table of the GPIB Controller                | 141 |

| 39 | GPIB Controller Interrupt Channel Address Assignment | 142 |

| 4Ø | GPIB Interrupt Events                                | 143 |

| 41 | The Software Programmable Interrupts of the ASCU-2   | 146 |

| 42 | BCLR* Generation Modes in the PRI Arbitration Type   | 15Ø |

| 43 | BCLR* Generation Modes in the RRS Arbitration Type   | 151 |

| 44 | BCLR* Generation Modes in the PRR Arbitration Type   | 152 |

| 45 | The MPCC Address Map in the Byte Mode of Addressing  | 155 |

| 46 | The MPCC Address Map in the Word Mode of Addressing  | 156 |

| 47 | The PI/T l Address Map                               | 158 |

| 48 | The PI/T 2 Address Map                               | 16Ø |

| 49 | The RTC Address Map                                  | 162 |

| 5Ø | The GPIB-Controller Address Map                      | 164 |

| 51 | The BIM 1 Register Table                             | 165 |

| 52 | The BIM 2 Register Table                             | 166 |

| 53 | The BIM 3 Register Table                             | 167 |

| 54 | The BIM 4 Register Table                             | 168 |

| 55 | Interrupt Channel Addressing                         | 169 |

|    |                                                      |     |

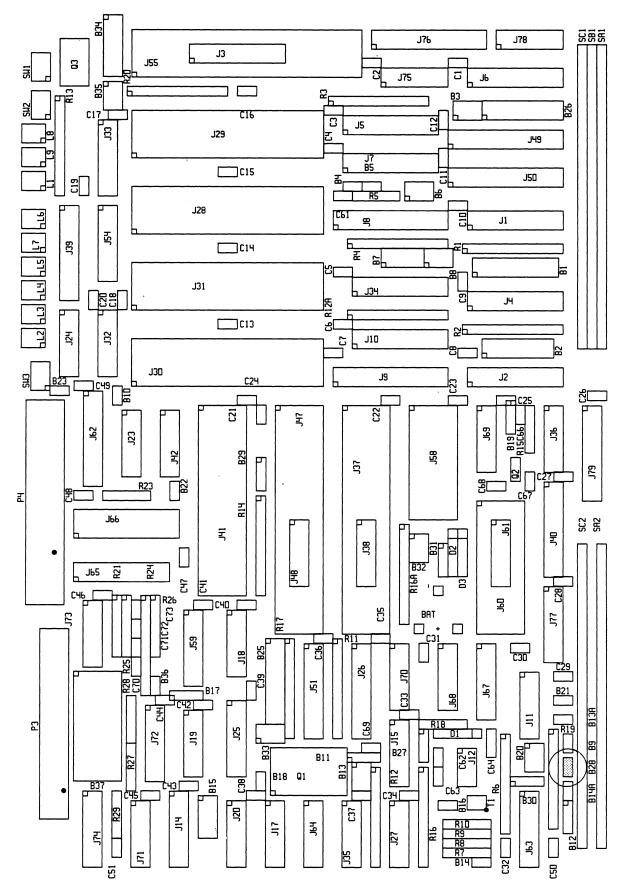

#### Figure 1: Photo of the SYS68K/ASCU-2 Board

#### 1. General Description SYS68K/ASCU-1/2

The SYS68K/ASCU-1 board is a high performance system controller which handles all exception signals on the VMEbus and contains powerful I/O devices such as a serial interface (RS232 and RS422 compatible), a centronics parallel interface, a real time clock with battery backup, and a 4 level bus arbiter.

The SYS68K/ASCU-2 board provides all the features of the ASCU-1 board as well as a IEEE 488 GPIB interface with Talker, Listener, and Controller functions and powerful interrupt capabilities for multiprocessor environments.

The two block diagrams show the different building blocks in detail.

#### 1.1 Features of the SYS68K/ASCU-1

- 4 level Bus ARBITER with prioritized, round robin, and prioritized round robin operating mode.

- LEDs show the current bus master level  $(\emptyset-3)$

- High speed serial I/O channel with 68561 Multi-Protocol Communications Controller, RS232 and RS422 driver/receiver circuitries.

- Centronics Parallel Interface for printer connection

- 58167A Real Time Clock with on-board battery back-up

- POWER MONITOR provides automatic power-up/power-down and ACFAIL/SYSRESET handling through power fail detection. A Reset function switch generates a SYSRESET to the VMEbus.

- SYSTEM CLOCK driver (16MHz)

- BUS TIMER with software selectable time-outs for Bus Error generation

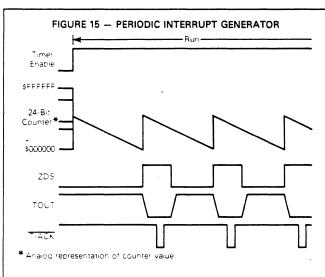

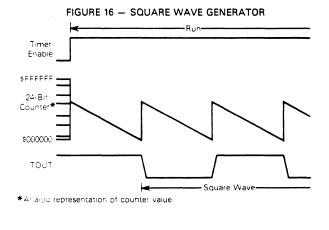

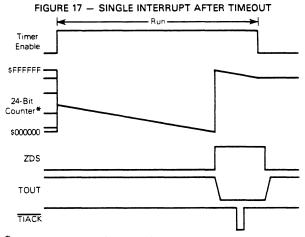

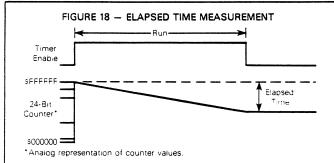

- Timer Interrupt can be used for time measurements or as a watch dog

- Software selectable option for generating an interrupt on ACFAIL detection

- TEST function switch generates an interrupt to the VMEbus on a software programmable level

- Every I/O device can be programmed to generate an interrupt on one of the 7 IRQ levels on the Priority Interrupt Bus

- Jumper selectable access address and address modifier code(s)

- DTB slave bus interface

.

### 1.2 Additional Features of the SYS68K/ASCU-2

- All of the features contained in the SYS68K/ASCU-1 description

- General Purpose Interface Bus (IEEE488) Talker, Listener, and Controller functions

. .

- 8 different fully software programmable interrupts to the VMEbus

- 5 user interrupts (buffered inputs through P2 connector)

- Software programmable time-out for bus mastership of the current bus master

•

,

#### 2. Access to the SYS68K/ASCU-1/2

The SYS68K/ASCU-1/2 is accessible under a user defined address and Address Modifier Code.

The decoding includes the Standard Decoding Mode, with an address range of 16Mbytes and short I/O range with 64 Kbytes address range.

To access the board, the jumper settings for the Board Base Address and the Address Modifier Code must match the valid address and Address Modifier Code on the VMEbus. The board is delivered with a default Board Base Address of \$B02000. The default jumper setting for the Address Modifier Code is the mode in which the SYS68K/ASCU-1/2 responds to any defined Address Modifier Code.

The SYS68K/ASCU-1/2 occupies an Address Range of 512 bytes, beginning at the Board Base Address. However, within this Address Range, not all locations can be accessed. An access to a non-specified location (no I/O device) will cause a bus trap error. For legal access, please refer to the ASCU-1/2 Device Address Assignment and the Register Map Table of the particular devices.

#### 2.1 Board Base Address Selection

The Base Address of the SYS68K/ASCU-1/2 is jumper selectable in the 16Mbyte address space, in steps of 512 bytes. To select the board, the address on the address lines A9-A23 must match the base address jumper settings at jumper fields B1 and B2.

Bl is the jumper field which defines the bit pattern of the address lines A23-A16. B2 is the jumper field for the address lines A15-A9.

Fig. 4 shows the location of the jumper fields B1 and B2 on the PC board.

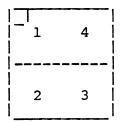

Fig. 5 shows the pinout of the jumper fields B1 and B2.

Table 1 points out the connection assignment:

- "IN" stands for a connection of the associated pins by a plugged-in jumper,

- "OUT" means that the pins are disconnected and the jumper is removed.

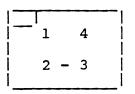

Jumper Field Pin-out:

| В                | 1         |

|------------------|-----------|

| - <sup>1</sup> . | .16       |

| 2.               | .15       |

| 3.               | .14       |

| 4.               | .13       |

| 5.               | •12  <br> |

| 6.               | .11       |

| 7.               | .1ø       |

| 8.               | . 9       |

.

| 1  | B2  |

|----|-----|

| 1. | .14 |

| 2. | .13 |

| 3. | .12 |

| 4. | .11 |

| 5. | .1Ø |

| 6. | . 9 |

| 7. | . 8 |

21

## Table 1: Board Base Address Selection

Default Base Address : \$B02000

.

| JUMP         | ER FIELI | D B 1                     |                                          |

|--------------|----------|---------------------------|------------------------------------------|

| Address Line |          | Default Jumper<br>Setting | Selection<br>Ø=Jumper IN, l=OUT          |

| A23          | 1 - 16   | OUT                       | 1                                        |

| A22          | 2 - 15   | IN                        | Ø                                        |

| A21          | 3 - 14   | OUT                       | 1                                        |

| A2Ø          | 4 - 13   | OUT                       | 1                                        |

| A19          | 5 - 12   | IN                        | Ø                                        |

| A18          | 6 - 11   | IN                        | Ø                                        |

| A17          | 7 - 10   | IN                        | Ø                                        |

| A16          | 8 - 9    | IN                        | ø                                        |

| JUMP         | ER FIELI | D B 2                     |                                          |

| A15          | 1 - 14   | IN                        | Ø                                        |

| A14          | 2 - 13   | IN                        | Ø                                        |

| A13          | 3 - 12   | OUT                       | 1                                        |

| A12          | 4 - 11   | IN                        | Ø                                        |

| A11          | 5 – 1Ø   | IN                        | Ø                                        |

| AlØ          | 6 - 9    | IN                        | ø                                        |

| A 9          | 7 – 8    | IN .                      | Ø                                        |

|              |          |                           | 19 100 100 100 100 100 100 100 100 100 1 |

22

.

#### 2.2 Address Modifier Decoding

The VMEbus has 6 signal lines (AMØ-AM5) carrying the Address Modifier Code which is generated by the bus master together with the address signals. The definition of the AM codes is given in table 2.

The SYS68K/ASCU-1/2 can be accessed with several AM codes, according to the jumper settings in the field B7 and B8. The following AM codes are decoded and selectable as described in table 3. At least one jumper must be inserted, and any combination is allowed. Therefore, the board is able to respond to several AM codes without changing the jumper settings.

Figure 6 outlines the jumper location diagram of the AM jumper field B7 and B8.

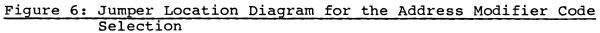

Figure 7 shows the pin numbering of B7 and B8.

The default setting in the AM jumper field during manufacturing is as shown in table 3, which causes the board to ignore the AM code.

When selecting the AM code Short Supervisory I/O Access (AM Code, \$2D) or Short Non-privileged I/O Access, the decoding is limited to the Address Lines Al - Al5.

Table 2: Address Modifier Codes

| HEX<br>Code                                  | •                                    |                  |                                 |                                           | er<br>Ø                              | Function                                                                                                                        |

|----------------------------------------------|--------------------------------------|------------------|---------------------------------|-------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                              |                                      | <br>             |                                 |                                           |                                      |                                                                                                                                 |

| 3F<br>3E<br>3D<br>3C<br>3B<br>3A<br>39<br>38 | H<br>H<br>H<br>H<br>H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>L<br>L<br>L                | H<br>L<br>L<br>H<br>L<br>L                | H                                    | Standard Non-Privileged Program Access                                                                                          |

| 37<br>36<br>35<br>34<br>33<br>32<br>31<br>3Ø | H<br>H<br>H<br>H<br>H<br>H<br>H      | L<br>L<br>L      | H<br>H<br>H<br>L<br>L<br>L<br>L | $\mathbf{L}$                              | Н                                    | Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved                                    |

| 2F<br>2E<br>2D<br>2C<br>2B<br>2A<br>29<br>28 | H<br>H<br>H<br>H<br>H<br>H<br>H      | H<br>H<br>H      | H<br>H<br>H<br>L<br>L<br>L<br>L | H<br>H<br>L<br>H<br>H<br>L<br>L           | H<br>L<br>H<br>L<br>H<br>L<br>H<br>L | Reserved<br>Reserved<br>Short Supervisory Access<br>Reserved<br>Reserved<br>Reserved<br>Short Non-Privileged Access<br>Reserved |

| 27<br>26<br>25<br>24<br>23<br>22<br>21<br>20 | H<br>H<br>H<br>H<br>H<br>H<br>H<br>H |                  | H<br>H<br>H<br>L<br>L<br>L<br>L | H<br>H<br>L<br>H<br>H<br>L<br>L<br>L<br>L | H<br>L<br>H<br>L<br>H<br>L<br>H<br>L | Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved                        |

L = low signal level H = high signal level

| Code       5       4       3       2       1       Ø         IF       L       H       H       H       H       User defined         IE       L       H       H       H       L       User defined         ID       L       H       H       H       L       User defined         IC       L       H       H       L       L       User defined         IC       L       H       H       L       L       User defined         IB       L       H       H       L       User defined         IA       L       H       H       L       User defined         I9       L       H       H       L       L       User defined         I8       L       H       H       L       L       User defined         I8       L       H       H       L       L       User defined         I7       L       H       L       H       H       User defined |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1E       L       H       H       H       L       User defined         1D       L       H       H       L       H       User defined         1C       L       H       H       L       L       User defined         1B       L       H       H       L       L       User defined         1A       L       H       H       L       User defined         19       L       H       H       L       L         18       L       H       H       L       L         18       L       H       H       L       L         18       L       H       H       L       L         17       L       H       L       H       User defined                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16       L       H       L       H       L       User defined         15       L       H       L       H       User defined         14       L       H       L       H       L       User defined         13       L       H       L       H       User defined         12       L       H       L       H       User defined         11       L       H       L       L       H         10       L       H       L       L       User defined                                                                                                                                                                                                                                                                                                                                                                                         |

| ØF       L       L       H       H       H       Extended Supervisory Block Transfer         ØE       L       L       H       H       L       Extended Supervisory Block Transfer         ØD       L       L       H       H       L       Extended Supervisory Block Transfer         ØC       L       L       H       H       L       Reserved         ØB       L       L       H       L       Reserved         ØA       L       L       H       L       Extended Non-Privileged Block Transfer         ØA       L       L       H       L       Extended Non-Privileged Data Access         Ø9       L       L       H       L       Reserved         Ø8       L       L       H       L       Reserved                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

•

L = low signal level H = high signal level

## Table 3: Address Modifier Code Selection

| AM Code<br>HEX | Function                                                                                                                                                                    | Jumper-<br>field | PINS | Decoded <br> Address <br>  Lines |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|----------------------------------|

| 3D             | Standard Supervisory Data<br>Access                                                                                                                                         | в7               | 1-8  | A1-A23                           |

| 39             | Standard Non-privileged<br>Data Access                                                                                                                                      | В7               | 2-7  | A1-A23                           |

| 2D             | Short Supervisory I/O Access                                                                                                                                                | в7               | 3-6  | A1-A15                           |

| 29             | Short Non-privileged I/O<br>Access                                                                                                                                          | в7               | 4-5  | <br>  Al-Al5<br>                 |

| XX *           | Ignore any code                                                                                                                                                             | в8               | 1-4  | A1-A23                           |

| 3F             | Standard Access Mode for CPU<br>boards which do not drive the<br>AM signal lines. This AM<br>code is not decoded in the<br>sense of the PlØl4 Block<br>Transfer Definition. | B8               | 2-3  | A1-A23                           |

|                |                                                                                                                                                                             |                  | <br> |                                  |

\* Default setting

26

Jumper Field Pin-out:

B7:

| -1. | . 4 |

|-----|-----|

| 2.  | • 3 |

#### 2.3 Application Examples

Example 1):

If the Board Base Address has to be changed to \$A57400 and the board should operate with the Standard Supervisory Data Access (AM Code: \$3D) as well as the Standard Non-Privileged Data Access (AM Code: \$39), then the following jumper settings have to be provided:

|              |             | Address<br>Line | Jumper<br>Setting | Selection |      |

|--------------|-------------|-----------------|-------------------|-----------|------|

| Jumper Field | B1:         | A23             | OUT               | 1         |      |

| -            |             | A22             | IN                | Ø         |      |

|              |             | A21             | OUT               | 1         |      |

|              |             | A2Ø             | IN                | Ø         |      |

|              |             | A19             | IN                | Ø         |      |

|              |             | A18             | OUT               | 1         |      |

|              |             | A17             | IN                | Ø         |      |

|              |             | A16             | OUT               | 1         |      |

| Jumper Field | B2:         | A15             | IN                | Ø         |      |

|              |             | A14             | OUT               | 1         |      |

|              |             | A13             | OUT               | 1         |      |

|              |             | A12             | OUT               | 1         |      |

|              |             | A11             | IN                | Ø         |      |

|              |             | AlØ             | OUT               | 1         |      |

|              |             | A 9             | IN                | Ø         |      |

| Jumper Field | в <b>7:</b> | AM-Code         | (HEX)             | Connected | PINs |

| 25 | 1 0 |

|----|-----|

| 3D | 1-8 |

| 39 | 2-7 |

Example 2):

In this example, the Short Board Base Address \$1600 with the AM-Code for Short Non-Privileged I/O access (\$29) is selected. It is irrelevant, in this case, which jumper settings are made in the field B1, because the address lines Al6-A23 will not be decoded.

The following jumper connections have to be installed:

|                  | Address<br>Line                               | Jumper<br>Setting                   | Selection                  |

|------------------|-----------------------------------------------|-------------------------------------|----------------------------|

| Jumper Field B2: | A15<br>A14<br>A13<br>A12<br>A19<br>A1Ø<br>A 9 | IN<br>IN<br>OUT<br>IN<br>OUT<br>OUT | Ø<br>Ø<br>1<br>Ø<br>1<br>1 |

| Jumper Field B7: | AM-Code                                       | (HEX)                               | Connected PINs             |

|                  | 29                                            |                                     | 4-5                        |

зø

#### 3. The Front Panel

#### 3.1 RESET Function Switch

The switch on the top of the SYS68K/ASCU-1/2 front panel is the RESET function switch. Pushing this switch can generate a SYSRESET\* signal to the VMEbus, and resets all devices on the SYS68K/ASCU-1/2. The SYSRESET\* signal is signaled by the red RESET LED on the front panel (Figure 8). For further information, please refer to chapter 8 - "Utility Signal Handling" and "Power Monitor Module".

#### 3.2 TEST Function Switch

The second switch on the front panel is the TEST function switch. It generates an interrupt request to the VMEbus. The interrupt level and vector is software programmable. The TEST function is inactive after the power-up procedure. For correct operation please refer to chapter 15 - "TEST Interrupt".

#### 3.3 The SYSFAIL LED

The red SYSFAIL LED signals the status of the corresponding Utility Bus Signal Line SYSFAIL\*.

This signal line is used to indicate that a local selftest of a board is in progress, or a system test has been started by an intelligent master board. During this test procedure the signal line is driven low.

The SYSFAIL\* line may be driven by any module in the system that is able to detect faults.

It may also be driven low at any time during normal operation to indicate that some kind of failure has occurred. Further details can be found in chapter 5.

#### 3.4 The ACFAIL LED

The red ACFAIL LED is built onto the SYS68K/ASCU-1/2 board as a visual indicator of power failures. The LED will signal a power failure when the ACFAIL\* signal line is asserted.

The signal handling of the ACFAIL\* signal is described in chapter 5 "Utility Signal Handling".

32

The SYS68K/ASCU-1/2 is equipped with six Bus Arbitration Status LEDs which show the activity of the Bus Arbiter and the bus load.

The LEDs are designated on the front panel as follows:

| BFREE | (green)  |

|-------|----------|

| BCLR  | (red)    |

| LEV 3 | (yellow) |

| LEV 2 | (yellow) |

| LEV 1 | (yellow) |

| LEV Ø | (yellow) |

The BUSFREE LED turns on after the power-up procedure is terminated, when the SYSRESET\* signal line has been cleared. Further on, the BUSFREE LED is controlled by the BBSY\* signal line.

This signal line is driven to a high level if no Bus Master has control of the Data Transfer Bus. On this condition, the BUSFREE LED will light up.

The asserted BBSY\* signal line indicates that a Bus Master has control of the Data Transfer Bus and the BUSFREE LED will turn off.

The BUSFREE LED will also turn off if the SYSRESET\* signal line is asserted.

The BCLR (Bus Clear) LED signals the asserted BCLR\* signal which is either generated by the on-board ARBITER or the BCLR-Timer. (The BCLR-Timer is installed only on the SYS68K/ASCU-2).

The red BCLR LED provides the visual information that the current Bus Master is requested to release the Data Transfer Bus. To monitor the level on which the current Bus Master is operating, the SYS68K/ASCU-1/2 provides four yellow LEDs, (LEV 3 to LEV  $\emptyset$ ).

These LEDs are attached to four daisy-chained Bus lines which are defined in the VMEbus and Pl $\emptyset$ l4\* specification as Bus Grant ( $\emptyset$ -3) OUT lines (BGx OUT).

The relation of the LEDs to the Bus Grant lines are as follows:

| LEV | 3 | -> | BG | 3 | OUT |

|-----|---|----|----|---|-----|

| LEV | 2 | -> | BG | 2 | OUT |

| LEV | 1 | -> | BG | 1 | OUT |

| LEV | Ø | -> | BG | Ø | OUT |

When the Arbiter grants the Data Transfer Bus to a requesting board by asserting the BGx OUT line, the LEV(x) LED will turn on (where x is a number  $\emptyset$ , 1, 2 or 3).

For a detailed description of the Bus Arbitration function, please refer to chapter 10 - "The 4-Level Bus ARBITER", and chapter 11 - "The BCLR-TIMER".

#### 3.6 The T/L Switch (included only on the ASCU-2)

The T/L toggle switch (only provided on the ASCU-2) provides a status signal, readable via the Port C of the second PI/T device.

\* PlØ14 - Bus Specification (VMEbus) of the IEEE Computer Society TC. The ASCU-2 provides a high performance IEEE-488 Interface (also called GPIB, HPIB, or IEC bus interface) with a 24 pin microribbon connector mounted on the front panel (see figure 8).

The mechanical construction and the mounting of the connector meets fully the IEEE-488 specification and allows stacked connection of interface cables.

The pin assignment of the connector is given in table 4.

| Contact | Signal Line | Contact | Signal Line |

|---------|-------------|---------|-------------|

| 1       | DIO 1       | 13      | DIO 5       |

|         |             |         | I           |

| 2       | DIO 2       | 14      | DIO 6       |

| 3       | DIO 3       | 15      | DIO 7       |

| 4       | DIO 4       | 16      | DIO 8       |

| 5       | EOI (24)    | 17      | REN (24)    |

| 6       | DAV         | 18      | Gnd,(6)     |

| 7       | NRFD        | 19      | Gnd,(7)     |

| 8       | NDAC        | 2Ø      | Gnd,(8)     |

| 9       | IFC         | 21      | Gnd,(9)     |

| 1Ø      | SRQ         | 22      | Gnd,(1Ø)    |

| 11      | ATN         | 23      | Gnd,(11)    |

| 12      | SHIELD      | 24      | Gnd,LOGIC   |

|         |             | <br>    |             |

#### Table 4: IEEE 488 Connector Pin Assignment

NOTE: Gnd,(n) refers to the signal ground return of the referenced contact. EOI and REN return on contact 24.

A comprehensive description of the interface is given in chapter 17 - "The IEEE-488 GPIB Interface".

#### 3.8 Serial Interface Connector

The 25-pin female D-sub connector is available on the front panel (see figure 8), and provides the connection to the RS232 and RS422-compatible Serial Interface.

The pin assignment to the connector of the two interfaces is completely jumper selectable.

The default pin assignment during manufacturing is given in table 5, using the RS232 interface.

This allows the connection of a standard terminal after initialization of the MPCC device.

For further information, please refer to chapter 12 - "The Serial I/O".

| Terminal Signal | D-Sub-Connector |

|-----------------|-----------------|

| DTR             | 20              |

| CTS             | 5               |

| RX DATA         | 3               |

| TX DATA         | 2               |

| GND             | 1               |

| GND             | 7               |

|                 |                 |

Table 5: The Default I/O Signal Assignment to the D-Sub-Connector

All other signals are not connected by default during manufacturing.

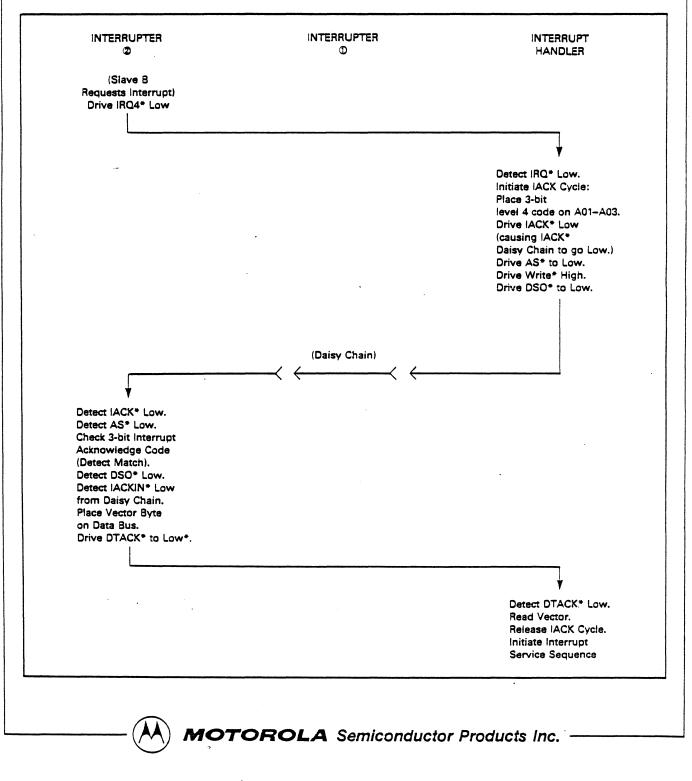

This chapter describes the Interrupt Structure of the SYS68K/ASCU-1/2.

A short description of the following terms is given in Appendix G (Glossary of PlØ14 Terms) at the end of this manual.

Terms:

- INTERRUPT HANDLER

- INTERRUPTER

- INTERRUPT BUS

- INTERRUPT ACKNOWLEDGE CYCLE

- DAISY CHAIN

For a detailed description please refer to the IEEE Pl014/VMEbus Specification.

Introduction:

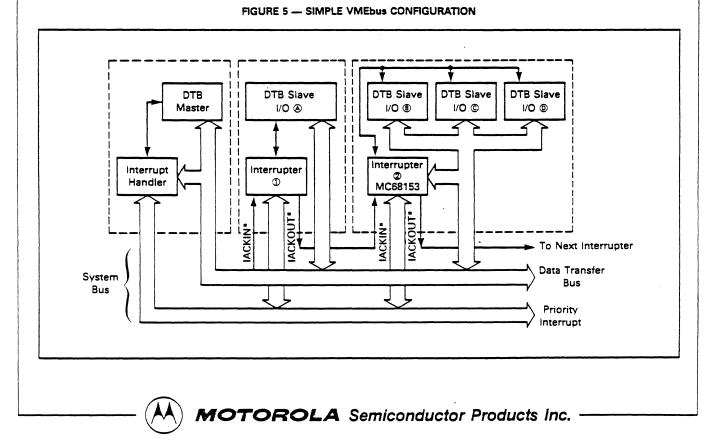

The PlØ14 Standard Specification defines a Priority Interrupt Bus with seven interrupt request lines (IRQ1-IRQ7). Each interrupt request line is assigned one interrupt level.

In a Single Handler System, where one Interrupt Handler services all interrupt requests, the signal line IRQ7 has the highest priority, and IRQ1 the lowest. Interrupters drive the interrupt request line low when requesting an interrupt. The Interrupt Handler honours the request by asserting the IACK\* line, putting the level code on the address lines AØ-A3, and driving AS\* low. The Interrupter then terminates the Interrupt Acknowledge Cycle providing the Interrupt Vector on the data bus lines DØ-D7 and drives DTACK\* low. More than one Interrupt Request Line can be driven simultaneously, and the same Interrupt Request Line can be asserted by several boards.

If more than one Interrupt Request Line is asserted at the same time, the Interrupt Handler prioritizes the requests and services them in order of priority.

If two or more Interrupter Modules request an interrupt at the same IRQ level, the Interrupter Modules themselves decide in which order the Interrupt Handler will acknowledge the interrupts.

To make sure that only one Interrupt responds to the interrupt acknowledge cycle, the VMEbus/Pl014 specification defines an Interrupt Acknowledge Daisy Chain structure with the Interrupt Acknowledge Daisy Chain line IACKIN\*/IACKOUT\*.

This line passes through each board on the system, whereby the IACKOUT\* pin of each Interrupter Module is connected to the IACKIN\* pin of the next Interrupter Module.

After leaving the board at slot n with the IACKOUT\* line, this line enters the next board at slot n+1 with the IACKIN\* line.

Each interrupter having a pending Interrupt Request only responds to the cycle when it receives a falling edge on the IACKIN\* daisy chain input. It puts the Interrupt Vector onto the data bus and drives the DTACK\* line low. This interrupter does not assert the IACKOUT\* pin, preventing other interrupters from responding to the interrupt acknowledge cycle.

An interrupter asserts its IACKOUT\* output when it has no Interrupt Request pending or when its pending Interrupt Request level differs from the one being acknowledged in the current cycle.

The Interrupt Acknowledge daisy chain operates from the left side to the right side of the backplane, giving priority to boards further left.

The IACKIN\* line starts at the first slot and has to be connected to the IACK\* bus line.

For this purpose the jumperfield B4 is provided on the board. An inserted jumper in this field connects the bus lines IACK\* with the IACKIN\* line of the board.

This jumper has to be inserted if the SYS68K/ASCU-1/2 is located at slot 1, but must be removed when the board is plugged into other slot positions. The default condition during manufacturing is a plugged-in jumper.

The jumper on jumperfield B19 connects the on-board Interrupt Acknowledge daisy chain line to the IACKOUT\* bus line. This jumper is not user selectable.

In the default condition on the SYS68K/ASCU-1 the jumper connects pins 2 and 3 of B19, and on the SYS68K/ASCU-2, pins 1 and 2 are connected.

Figure 9 outlines the location of the jumperfields B4 and B19.

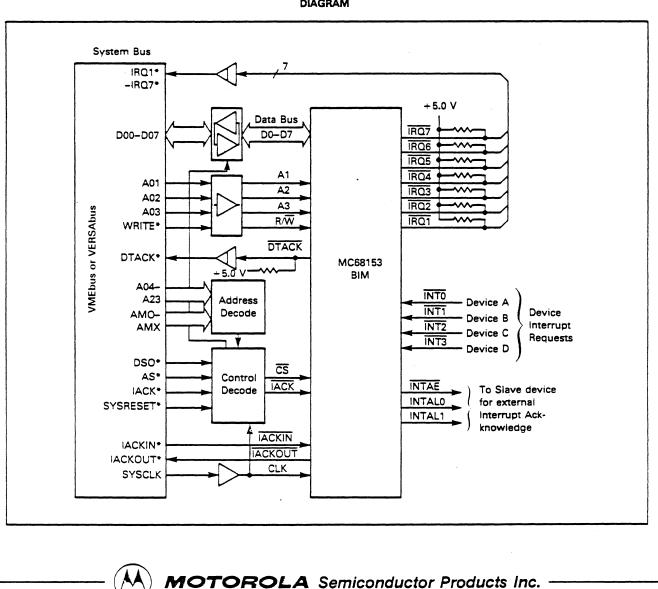

# 4.1 Programming of the BIM on the ASCU-1/2

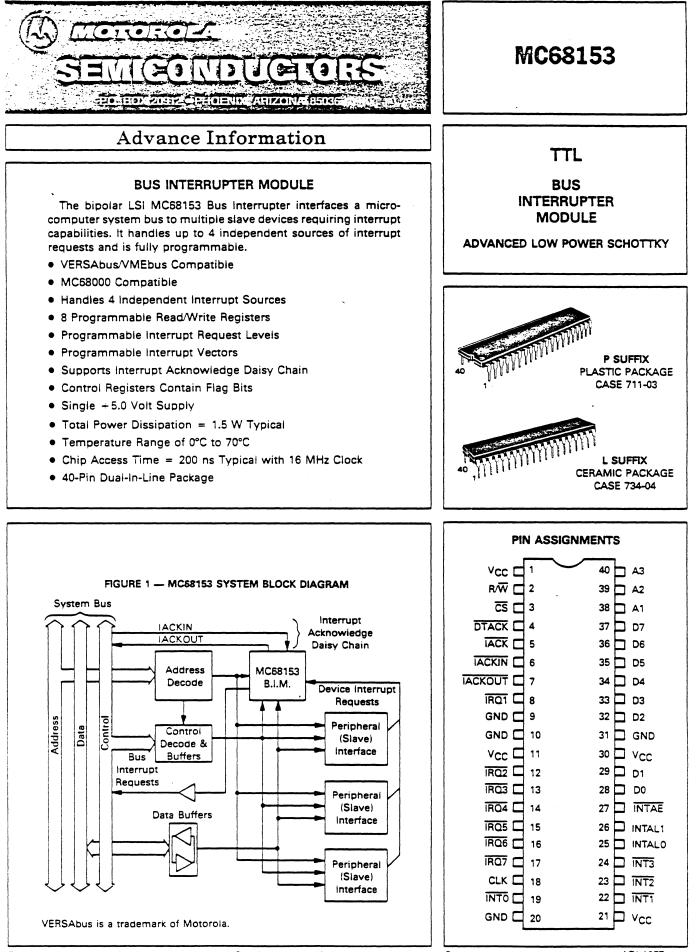

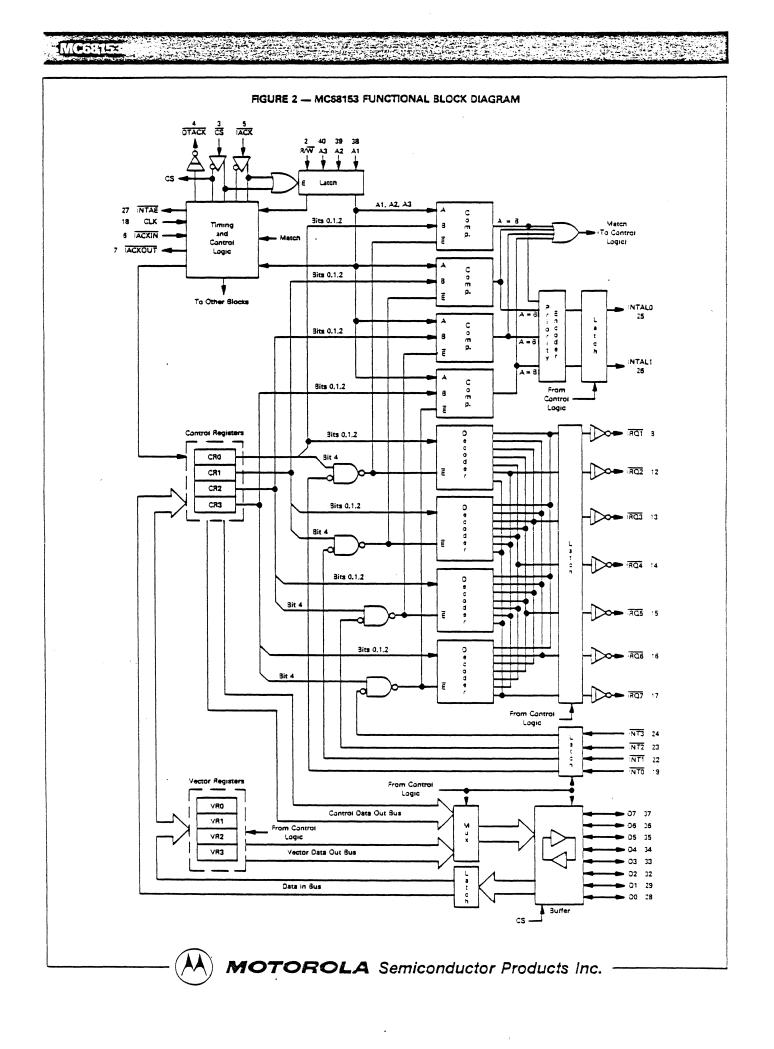

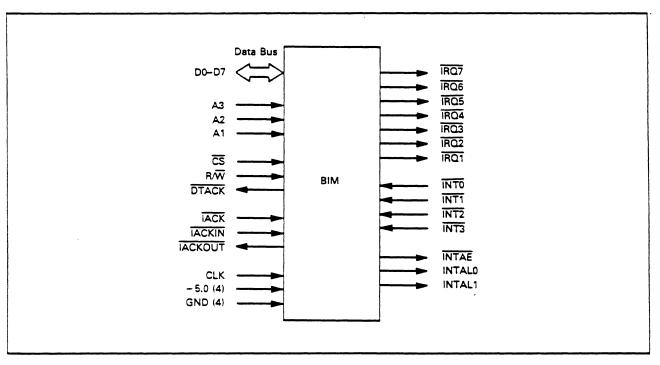

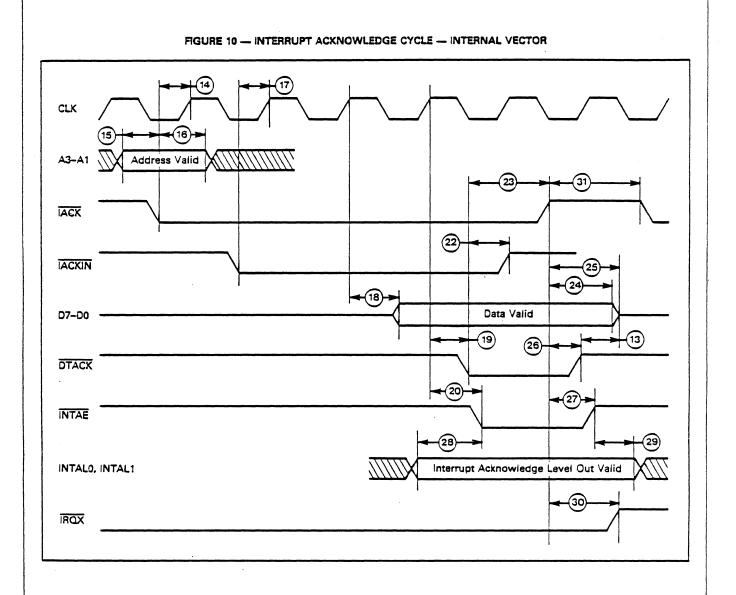

The SYS68K/ASCU-1/2 contains Bus Interrupter Modules (BIM 68153) to transmit the Interrupt Request Signals of peripheral devices (also called Interrupt Sources) to the VMEbus and the Interrupt Acknowledge Signal from the VMEbus to the interrupt sources. All interrupt sources are arbitrated by the BIMs.

The SYS68K/ASCU-1 has two BIMs on the board serving seven interrupt sources.

The SYS68K/ASCU-2 board is equipped with four BIM devices supporting sixteen interrupt sources.

Each Bus Interrupter Module has the capability to drive each Interrupt Request line on the VMEbus. It also provides a vector if the Interrupter does not support the vectored protocol. Both functions, the selection of the Interrupt Request Level as well as the supplied interrupt vector are fully under software control.

The BIM contains two types of registers: The Control Register, and the Vector Register.

Programming the Control Register allows the selection of the Interrupt Request Level as well as to enable or disable this function. If the interrupting source does not provide the interrupt vector, the Control Register can be programmed to give out the contents of the associated Vector Register as the required Interrupt Vector.

When the BIM device is reset, it prevents the interrupt generation from the board to the VMEbus.

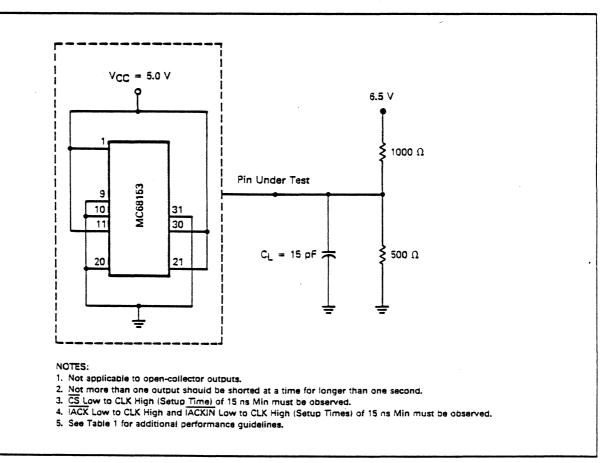

For detailed information, please refer to the data sheet of the BIM 68153 in Appendix H.

#### 4.2 Interrupt Sources and IACK Daisy Chain Structure

#### of the SYS68K/ASCU-1/2

For easier comprehension of the interrupt structure of the SYS68K/ASCU-1/2 it is helpful to consider all Bus Interrupter Modules on the board as a single device providing several interrupt channels.

Each interrupt source is assigned one interrupt channel. Every interrupt channel has an associated software programmable Control Register and Vector Register and can be programmed to generate an Interrupt Request on every IRQ-level of the VMEbus. It depends on the interrupting device, whether the Vector Register of the interrupt channel or the interrupt source by itself supplies the vector.

The following interrupt sources are provided on the SYS68K/ASCU-1/2. The list also shows the assigned interrupt channel number.

|                             |         | Interrupt Channel<br>Number | L |

|-----------------------------|---------|-----------------------------|---|

| - PORT INTERRUPT OF PI/T 1  |         | 1                           |   |

| - TIMER INTERRUPT OF PI/T 1 |         | 2                           |   |

| - ACFAIL                    |         | 3                           |   |

| - SYSFAIL                   |         | 4                           |   |

| - TEST INTERRUPT            |         | 5                           |   |

| - RTC                       |         | 6                           |   |

| - MPCC                      |         | 7                           |   |

| - GPIB CONTROLLER           | · ·     | 8                           | * |

| - 8 PROGRAMMABLE INTERRUPTS | BIM J30 | 9-12                        | * |

|                             | BIM J31 | 13-16                       | * |

\* available only on ASCU-2

The on-board daisy chain structure is hardware defined and operates in the order given in Table 6.

When all interrupt sources are working on the same IRQ-level, the SYSFAIL interrupt source has the highest priority. The lowest priority on the ASCU-1 has the TEST INTERRUPT source, on the ASCU-2 the PROGRAMMABLE INTERRUPT source with Interrupt Channel number 13.

.

| Interrupt Source        |     | Channel  | No. | Comment          |

|-------------------------|-----|----------|-----|------------------|

| SYSFAIL                 |     | 4        |     | highest priority |

| ACFAIL                  |     | 3        | l   |                  |

| TIMER INTERRUPT OF PI/T | 1   | 2        |     |                  |

| PORT INTERRUPT OF PI/T  |     | -<br>  1 | l   |                  |

|                         |     |          |     | decreasing       |

| GPIB CONTROLLER         |     | 8        |     | \/ priority      |

| MPCC                    |     | 7        |     |                  |

| RTC                     |     | 6        |     |                  |

| TEST INTERRUPT          |     | 5        |     |                  |

|                         |     |          |     |                  |

| PROGRAMMABLE INTERRUPT  | PA3 | 12       |     |                  |

|                         | PA2 | 11       |     |                  |

|                         | PAl | 10       |     |                  |

|                         | PAØ | 9        |     |                  |

|                         |     |          |     |                  |

| PROGRAMMABLE INTERRUPT  | PA7 | 16       |     |                  |

| •                       | PA6 | 15       |     |                  |

|                         | PA5 | 14       |     |                  |

|                         | PA4 | 13       |     | lowest priority  |

|                         |     | <br>=    |     |                  |

A summary of the interrupt sources and the assigned channel numbers and register addresses is shown in table 55 "Interrupt Channel Addressing".

#### 4.3 Interrupt Vector Structure

All interrupt sources on the SYS68K/ASCU-1/2 are arbitrated by the Bus Interrupter Modules which provide one interrupt vector for each interrupt source.

The BIM can be programmed to honour an Interrupt Acknowledge with the content of its vector register or to send the acknowledge signal to the interrupt source.

The SYS68K/ASCU-1/2 has three different groups of interrupt sources:

The first group are interrupt sources, which do not supply an interrupt vector.

This group must be supported by the BIM which must provide the interrupt vector. The BIM Control Register has to be programmed appropriately. Table 7 lists the affected interrupt sources with interrupt channel and BIM register address offset related to the Board Base Address.

# Table 7: Non-vectorized Interrupt Sources

| Interrupt<br>Source       | Interrupt<br>Channel<br>Number |       | Offset- Board<br>BIM Control<br>Register |       |   |

|---------------------------|--------------------------------|-------|------------------------------------------|-------|---|

| ACFAIL                    | 3                              | BIM 1 | \$105                                    | \$1ØD |   |

| SYSFAIL                   | 4                              | BIM 1 | \$107                                    | \$1ØF |   |

| <br>  TEST<br>  INTERRUPT | 5                              | BIM 2 | \$111                                    | \$119 |   |

| REAL TIME                 | 6                              | BIM 2 | \$113                                    | \$11B |   |

| GPIB<br>CONTROLLER        | 8                              | BIM 2 | \$117                                    | \$11F | * |

| PROGRAM.<br>INTERRUPT     | 9                              | BIM 3 | \$121                                    | \$129 | * |

| PROGRAM.<br>INTERRUPT     | 1Ø                             | BIM 3 | \$123                                    | \$12B | * |

| PROGRAM.<br>INTERRUPT     | 11                             | BIM 3 | \$125                                    | \$12D | * |

| PROGRAM.<br>INTERRUPT     | 12                             | BIM 3 | \$127                                    | \$12F | * |

| PROGRAM.<br>INTERRUPT     | 13                             | BIM 4 | \$131                                    | \$139 | * |

| PROGRAM.<br>INTERRUPT     | 14                             | BIM 4 | \$133                                    | \$13B | * |

| PROGRAM.<br>INTERRUPT     | 15                             | BIM 4 | \$135                                    | \$13D | * |

| PROGRAM.<br>INTERRUPT     | 16                             | BIM 4 | \$137                                    | \$13F | * |

\* ONLY INCLUDED ON THE ASCU-2

The second group is an Interrupt Source, which always supplies its own vector when it honours an Interrupt Acknowledge Cycle.

This interrupt source is the Multi Protocol Communication Controller (MPCC 68561).

The MPCC has three vector registers:

- Receiver Interrupt Vector Number Register (RIVNR)

- Transmitter Interrupt Vector Number Register (TIVNR)

- Serial Interrupt Vector Number Register (SIVNR)

As the MPCC always serves an interrupt acknowledge cycle with one of its own vectors, the BIM has to be programmed for an external interrupt acknowledge response.

The register address assignment of the MPCC interrupt source is shown in the table below:

| Table | ρ. | Vectorized | Interrunt | Source |

|-------|----|------------|-----------|--------|

| Table | 0: | Vectorized | Incertupe | Source |

| Interrupt<br>Source | Interrupt     Offset to Board Base Address       Channel     BIM 2     MPCC       Number |       |                    | s                          |                           |       |

|---------------------|------------------------------------------------------------------------------------------|-------|--------------------|----------------------------|---------------------------|-------|

|                     | NUMBEL                                                                                   |       | Vector<br>Register |                            | or Regi<br>Byte  <br>Mode | Word  |

| MPCC                | 7                                                                                        | \$115 | not used           | RIVNR:<br>TIVNR:<br>SIVNR: | \$ØØD                     | \$Ø2D |

The third group of interrupt sources can be enabled or disabled of providing the interrupt vector. The user can therefore choose whether the interrupt source or the BIM provides the vector.

The two independent interrupt sources belonging to this group reside in the Parallel Interface/Timer Module PI/T 1 (68230).

The timer has one interrupt vector available which is programmable in the 8-bit wide Timer Interrupt Vector Register of the PI/T 1 device. If the timer is enabled to support the vectored interrupt, the BIM must not provide the interrupt vector.

Table 9 shows the timer interrupt channel address assignment (offset to Board Base Address)

|                | <br> <br>                          | Offset to Board Base Address |             |                                                 |

|----------------|------------------------------------|------------------------------|-------------|-------------------------------------------------|

|                | Interrupt<br>  Channel<br>  Number |                              | Vector Reg. | PI/T 1<br> Timer Interrupt <br> Vector Register |

|                | 2                                  | \$1Ø3                        | \$1ØB       | not used                                        |

| TIMER<br> <br> | 2                                  | \$1Ø3                        | not used    | TIVR:\$Ø63                                      |

# Table 9: Optional Vectorized Interrupt Source 1

The Port Interrupt of the PI/T l device has one associated vector register, but it represents four consecutive vector numbers. As the BIM can only provide one vector for the Port Interrupt, it is recommendable to handle the BIM transparent, always selecting the external vector generation of the PI/T l device.

Table 10 shows the Port Interrupt channel address assignment (offsets to Board Base Address).

|                     |                                | Offset to Board Base Address                            |          |             |  |  |

|---------------------|--------------------------------|---------------------------------------------------------|----------|-------------|--|--|

| Interrupt<br>Source | Interrupt<br>Channel<br>Number | B I M l PI/T l<br>Control Reg. Vector Reg. Port Interru |          |             |  |  |

| PORT                | 1                              | \$1Ø1                                                   | \$109    | not used    |  |  |

| INTERRUPT           | 1                              | \$1Ø1                                                   | not used | PIVR: \$04B |  |  |

# Table 10: Optional Vectorized Interrupt Source 2

## 5. Utility Signal Handling

The SYS68K/ASCU-1/2 handles the utility signals SYSRESET\*, SYSFAIL\* and ACFAIL\* which are provided by the Utility Bus, and supply initialization and diagnostic capabilities for a VME/Pl014 standard system.

## 5.1 The SYSRESET\* Signal

The SYS68K/ASCU-1/2 board can be configured to drive the SYSRESET\* signal line or not to drive it. Figure 10 outlines the jumper location diagram B16 with which the function can be selected.

Jumper Bl6 inserted -> SYSRESET\* is driven to the VMEbus

removed -> SYSRESET\* is not driven to the VMEbus

The SYSRESET\* signal is driven to the VMEbus by default during manufacturing.

The SYSRESET\* Bus signal is always received by the board and resets each of the devices described in the following table.

#### Table 11: RESET on the ASCU-1/2

| P                                        | Abbreviation | Device  |

|------------------------------------------|--------------|---------|

| BUS INTERRUPTER MODULE 1                 | BIM 1        | 68153   |

| BUS INTERRUPTER MODULE 2                 | BIM 2        | 68153   |

| BUS INTERRUPTER MODULE 3                 | BIM 3        | 68153 * |

| BUS INTERRUPTER MODULE 4                 | BIM 4        | 68153 * |

| PARALLEL INTERFACE/TIMER MODULE 1        | PI/T 1       | 6823Ø   |

| PARALLEL INTERFACE/TIMER MODULE 2        | PI/T 2       | 6823Ø * |

| MULTI PROTOCOL COMMUNICATION CONTROLLER  | MPCC         | 68561   |

| GENERAL PURPOSE INTERFACE BUS CONTROLLER | GPIB         | 721Ø *  |

| REAL TIME CLOCK                          | RTC          | 58167A  |

\* included only on the SYS68K/ASCU-2.

The whole SYSRESET\* exception signal handling is performed by the POWER MONITOR MODULE. It generates a SYSRESET signal during power-up sequence, and monitors five reset sources. If any of the five sources becomes active, the Power Monitor Module asserts the SYSRESET\* signal line (providing that Jumper B16 is inserted).

The five reset sources are:

- 1) The RESET switch on the FRONT PANEL,

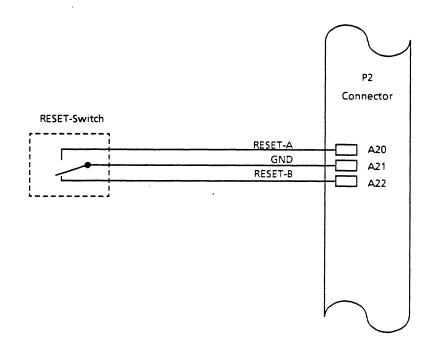

- 2) An optional switch connected to the P2 connector pins A2Ø, A21, A22. This switch should be connected in the following way:

To enable the function switch, the jumper B9 has to be removed. If there is no switch connected, the jumper must be plugged in. This is the default condition during manufacturing.

Figure 10 outlines the location diagram of the jumperfield B9 on the board.

for the External Reset Switch Connection

3) A second optional RESET switch can be connected to the P2 connector - PIN A2. This pin is a TTL-compatible input and generates a reset execution if the switch closes the pin to ground.

This pin is a double function pin also providing a signal ground for the Data 1 line of the CENTRONICS Interface, which is installed on the board. Therefore, selecting the function of the second optional RESET switch or the Centronics Interface, the jumper B30 has to be changed according to the following table.

Figure 11 shows the location diagram for Jumperfield B3Ø.

Jumperfield B3Ø

|                        | Jumperfield B3Ø<br>Connected Pins |

|------------------------|-----------------------------------|

| Centronics Interface * | 1 - 2                             |

| Optional Reset Switch  | 2 - 3                             |

<sup>\*</sup> default condition

Interface/second Optional RESET Switch

4) A software programmable SYSRESET\* execution is provided by the SYS68K/ASCU-1/2.

The function is directed by the signal PB7 of the PI/T l Parallel Interface, and can be activated if the PB7 signal is set to a logical  $\emptyset$  (low state).

This function becomes inactive after the SYS68K/ASCU-1/2 board has been reset.

If the board does not drive the SYSRESET\* signal to the VMEbus, the programmable reset function has no effect on the on-board devices.

More information about the programming of this function is available in chapter 7 "Software Control".

5) Reset after ACFAIL\* detection.

This function can be enabled or disabled by inserting or removing the jumper BlØ.

In default, the Reset after ACFAIL\* detection function is enabled with an inserted B1Ø jumper.

Figure 12 shows the location diagram of the jumper BlØ.

Detailed information about reset after ACFAIL\* detection is given in section 5.3, "ACFAIL\* Signal", and chapter 8, "Power Monitor Module".

# 5.2 The SYSFAIL\* Signal

The SYSFAIL\* signal line is monitored by the SYS68K/ASCU-1/2 and the status of the line is shown by the red SYSFAIL LED, mounted on the Front Panel. Additionally, a second LED can be connected to the P2 Connector Pin C23 and Pin C24.

Pin C24 provides the signal level for the second LED and Pin C23 sources the supply current. The LED is directly connectable without using an external resistor.

The SYSFAIL\* signal line is used for system diagnostics and may be driven by any system module able to detect faults.

The SYS68K/ASCU-1/2 provides an Interrupt Request generation to the VMEbus after the board has received the signal line at low-state.

The interrupt level and the vector is fully software programmable through the control register and the vector register of a Bus Interrupter Module (BIM).

The following table shows the offset of the two BIM registers to the Board Base Address.

| Interrupt<br>  Source   | Interrupt<br>  Channel<br>  Number | Device      | Offset to Boar<br>Control Reg. | rd Base Address<br>Vector Reg. |

|-------------------------|------------------------------------|-------------|--------------------------------|--------------------------------|

| <br> <br>  SYSFAIL*<br> | <br>  4<br>                        | <br>  BIM 1 | \$107                          | \$1ØF                          |

For the initialization of the registers, please refer to section 4.1 "Programming of the BIM on the ASCU-1/2" and section 4.3 "Interrupt Vector Structure".

## 5.3 The ACFAIL\* Signal

The SYS68K/ASCU-1/2 provides the connection of an external power fail signal on two pins of the P2 Connector. This power fail signal is typically driven by the System Power Supply to indicate AC power failure.

The board drives the power fail signal to the VMEbus ACFAIL\* line and receives the signal from this open collector bus line.

The ACFAIL\* line is always received by the ASCU-1/2 board, therefore, the line can also be driven by another board in the system.

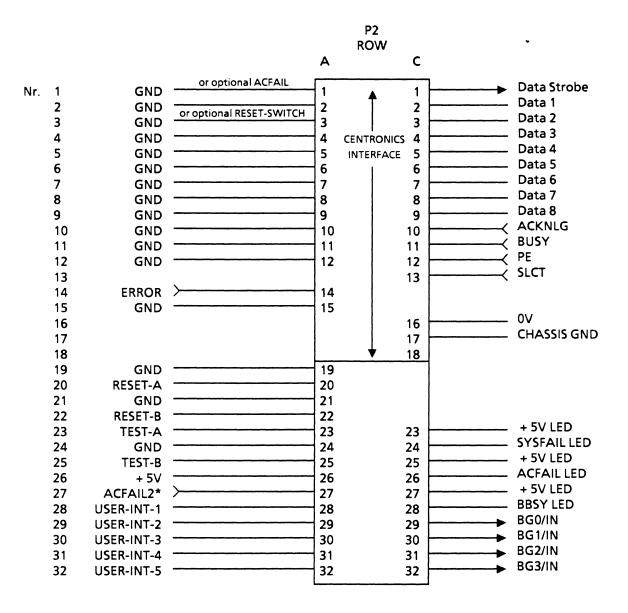

The external power fail signal can be connected to the ASCU-1/2 board at the following pins on Connector P2:

| Connecto | or P2 | - | Pin | Al  |

|----------|-------|---|-----|-----|

|          |       |   | Pin | A27 |

The Pin Al of the P2 Connector is a double function pin and also provides the signal ground for the DATA STROBE signal of the Centronics Interface.

A jumper on the Jumperfield B12 selects the Al pin either as a power fail input pin or a signal ground for the Centronics Interface Data Strobe line.

In the default jumper setting during manufacturing the Al pin functions as signal ground.

The following table lists the B12 jumper settings for these two functions.

|               | PIN Al Function                           | Jumperfield B12 <br> Connected PINs |

|---------------|-------------------------------------------|-------------------------------------|

| Connector P2> | Centronics I.F.<br>Data Strobe Signal GND | 2 - 3 *                             |

|               | Power Fail<br>Input-Pin                   | 1 - 2 .                             |

\* Default jumper setting.

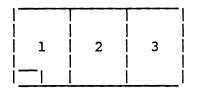

Pin-Out of Jumperfield B12

| 1 | 2 | 3 |

|---|---|---|

|   |   |   |

|   |   |   |

To adjust a Power Fail signal which is either true on low state  $(\emptyset)$  or on high state (1), jumperfield B13 is provided on the board. The possible jumper settings given in Table 12 determine the active level of the two power fail input pins at Connector P2 Pins Al and A27.

If there is no Power Fail signal attached to the board, the jumper settings on B13 has to be either the default one, or the jumper has to be removed. A removed jumper will hinder the board from reacting on the external Power Fail signal.

The location of B13 is shown in Figure 12.

Jumperfield B13 Power Fail Signal Active low 1 - 2 \* 2 - 3 Active high ļ Disabled function Jumper removed \* default jumper setting.

Table 12: The Power Fail Signal Level

Pin-Out of Jumperfield B13:

56

When the ASCU-1/2 board receives the ACFAIL\* line asserted, it will latch the signal and execute the following functions:

- turning on the red ACFAIL LED on the front panel

- requesting an interrupt to the VMEbus (if programmed)

- triggering a time-out counter which drives the SYSRESET\* line low after a selectable delay.

The latched ACFAIL\* signal is readable via the PB5 Port terminal of the Parallel Interface Timer Module 1/Port B (PI/T 1, location J37). The latch can be cleared if the PB6 terminal of the PI/T 1 device is programmed as a low status output, providing that the ACFAIL\* signal line is not still asserted.

This feature allows the system software to distinguish between occurring short AC-power drop-outs and longer power failure periods, which require an appropriate data saving reaction.

After the power-up sequence, both terminals PB6 and PB7 of the PI/T 1 are programmed as inputs and carry high level.

If the latched ACFAIL\* signal is cleared, the ACFAIL LED on the front panel will also turn off.

A second external LED for an ACFAIL display is connectable on the P2 connector Pin C26 and C25. Pin C26 provides the signal level and C25 the LED supply voltage. The circuitry includes a pre-register which supplies a source current of 50mA.

The Interrupt Request caused by the latched ACFAIL\* signal is handled by the BIM 1 device and has to be enabled by programming the appropriate Control and Vector register of the BIM (please refer to chapter 4.1 and the Data Sheet of the Bus Interrupter Module).

Table 13 outlines the offset of the corresponding BIM Register to the Board Base Address.

| Table | 13: | ACFAIL* | Interrupt | Channel | Address | Assignment |  |

|-------|-----|---------|-----------|---------|---------|------------|--|

|       |     |         |           |         |         |            |  |

|       |     |         |           |         |         |            |  |

| Interrupt<br>  Source<br> | Interrupt<br>  Channel<br>  Number |       |                 |       |  |  |

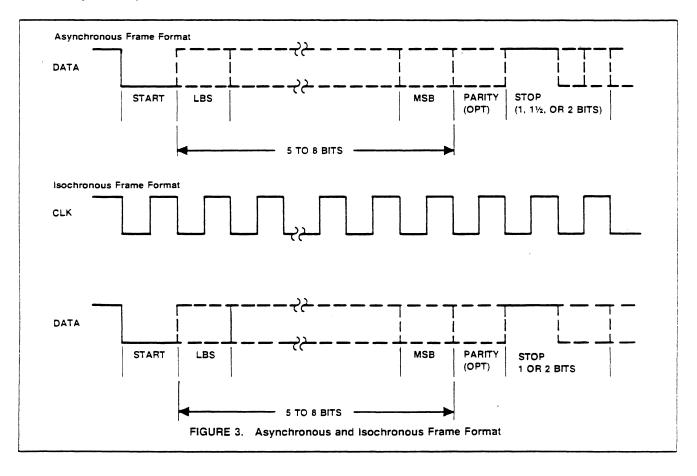

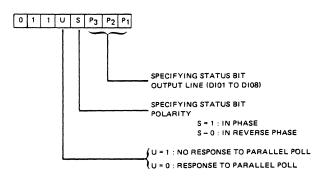

|---------------------------|------------------------------------|-------|-----------------|-------|--|--|