## 1 Introduction to the SYS68K/ISCSI-1

## 2 Installation

3 Hardware User's Manual

4 Appendix to the Hardware User's Manual

5 Copies of Data Sheets

6 Firmware User's Manual

7 Appendix to the Firmware User's Manual

8 User Notes 1

9 User Notes 2

10 Applications

11 Modifications

## **INTRODUCTION TO THE**

## SYS68K/ISCSI-1

First Edition October 1986 PART NO. 800114

FORCE COMPUTERS Inc./GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted. Copyright by FORCE Computers® The information in this document has been carefully checked and is believed to be entirely reliable. FORCE COMPUTERS makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors that may appear in this document. FORCE COMPUTERS reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance or design.

FORCE COMPUTERS assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of FORCE COMPUTERS GmbH/Inc.

FORCE COMPUTERS does not convey to the purchaser of the product described herein any license under the patent rights of FORCE COMPUTERS GmbH/Inc. nor the rights of others.

#### FORCE COMPUTERS Inc.

727 University Avenue Los Gatos, CA 95030 U.S.A.

Phone : (408) 354 34 10 Telex : 172465 FAX : (408) 395 77 18

#### FORCE COMPUTERS GmbH

Daimlerstrasse 9 D-8012 Ottobrunn/Munich West Germany

Phone : (089) 600 91-0 Telex : 524190 forc-d FAX : (089) 609 77 93

| FORCE COMPUTERS FRANCE Sarl<br>11, rue Casteja<br>92100 Boulogne<br>France | FORCE Computers UK Ltd.<br>No. 1 Holly Court<br>3 Tring Road<br>Wendover<br>Buckinghamshire HP22 6NR<br>England |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Phone : (1) 4620 37 37                                                     | Phone : (0296) 625456                                                                                           |

| Telex : 206 304 forc-f                                                     | Telex : 838033                                                                                                  |

| Fax : (1) 4621 35 19                                                       | Fax : (0296) 624027                                                                                             |

## Table of Contents

| 1.0 | Genera | l Informationl-1                           |

|-----|--------|--------------------------------------------|

|     | 1.1    | Hardware Features of the SYS68K/ISCSI-11-3 |

|     | 1.2    | The Hardware Functions1-4                  |

|     | 1.2.1  | The Local 68010 CPU1-4                     |

|     | 1.2.2  | The SCSIbus Interface1-5                   |

|     | 1.2.3  | The Floppy Disk Interface1-6               |

|     | 1.2.4  | The PI/T 682301-6                          |

|     | 1.2.5  | The Dual Ported RAM1-7                     |

|     | 1.2.6  | The VMEbus Interface1-8                    |

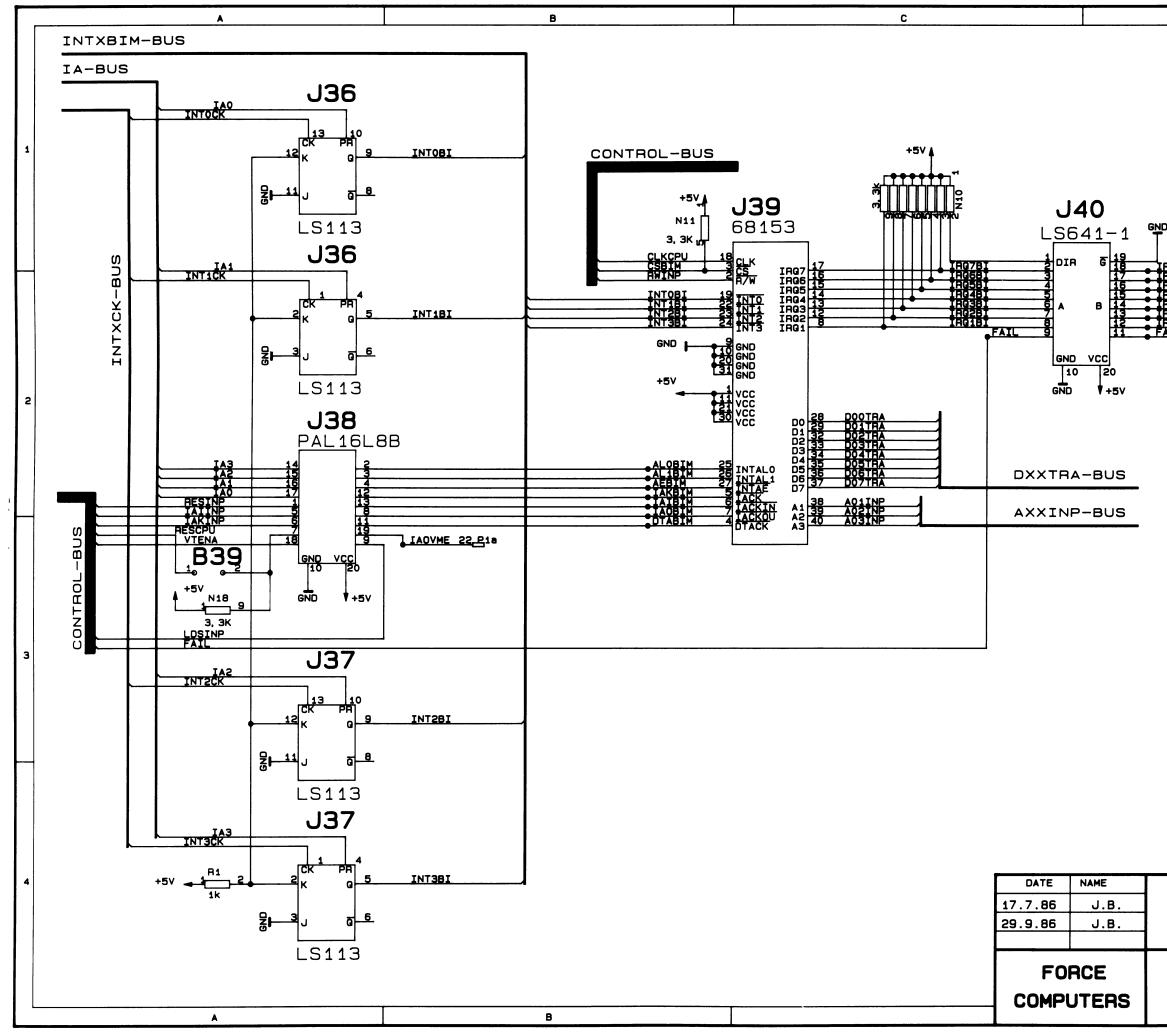

|     | 1.2.7  | The Bus Interrupter Module1-8              |

|     | 1.2.8  | The Optional Back Panel1-9                 |

| 2.Ø | Specif | ication of the SYS68K/ISCSI-12-1           |

| 3.0 | Orderi | ng Information                             |

### List of Figures

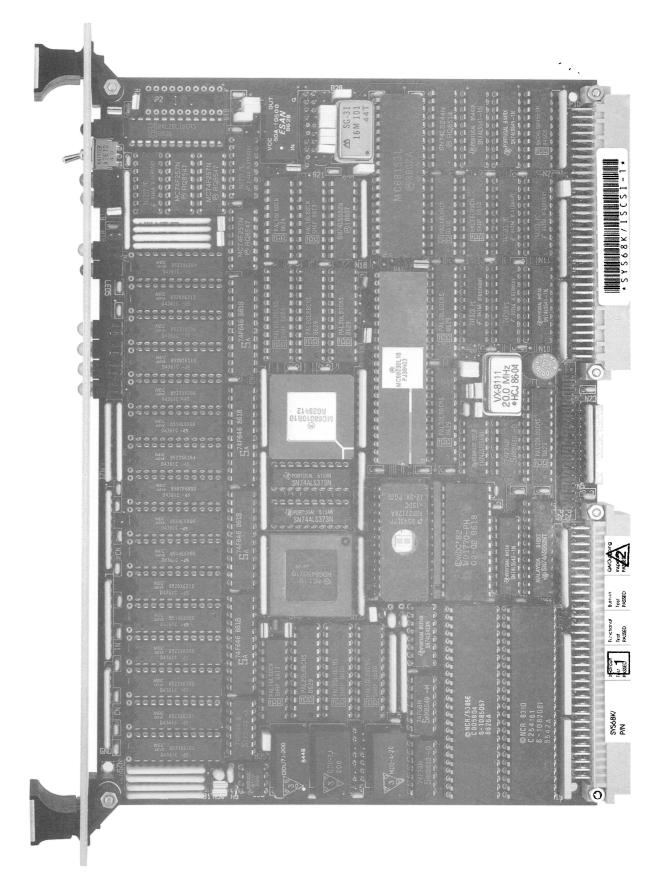

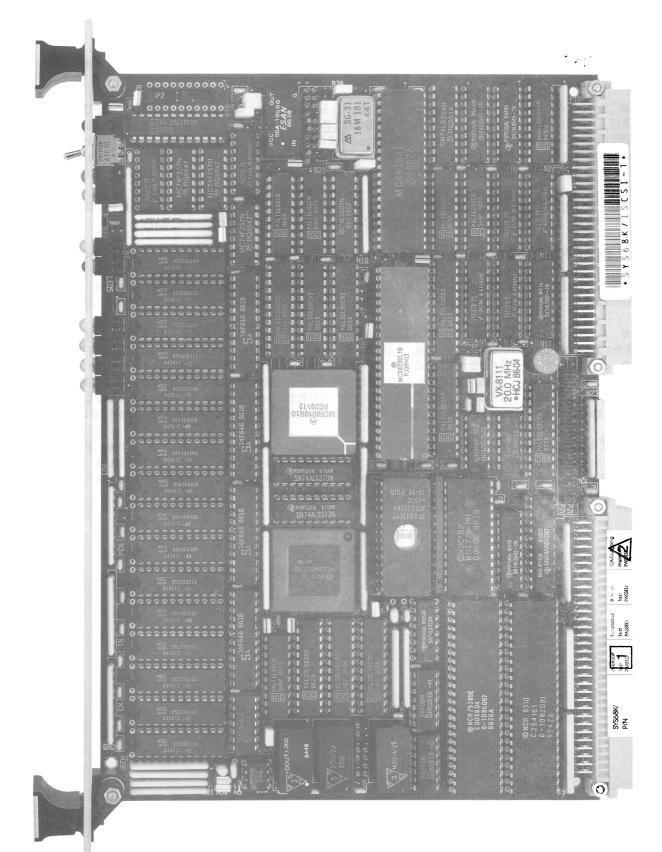

| Figure 1-1: | Photo of | the SYS68K/ISCSI-1 | .1-2 |

|-------------|----------|--------------------|------|

|-------------|----------|--------------------|------|

#### 1.0 General Information

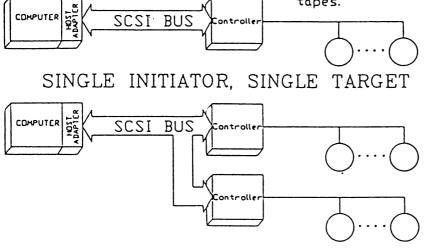

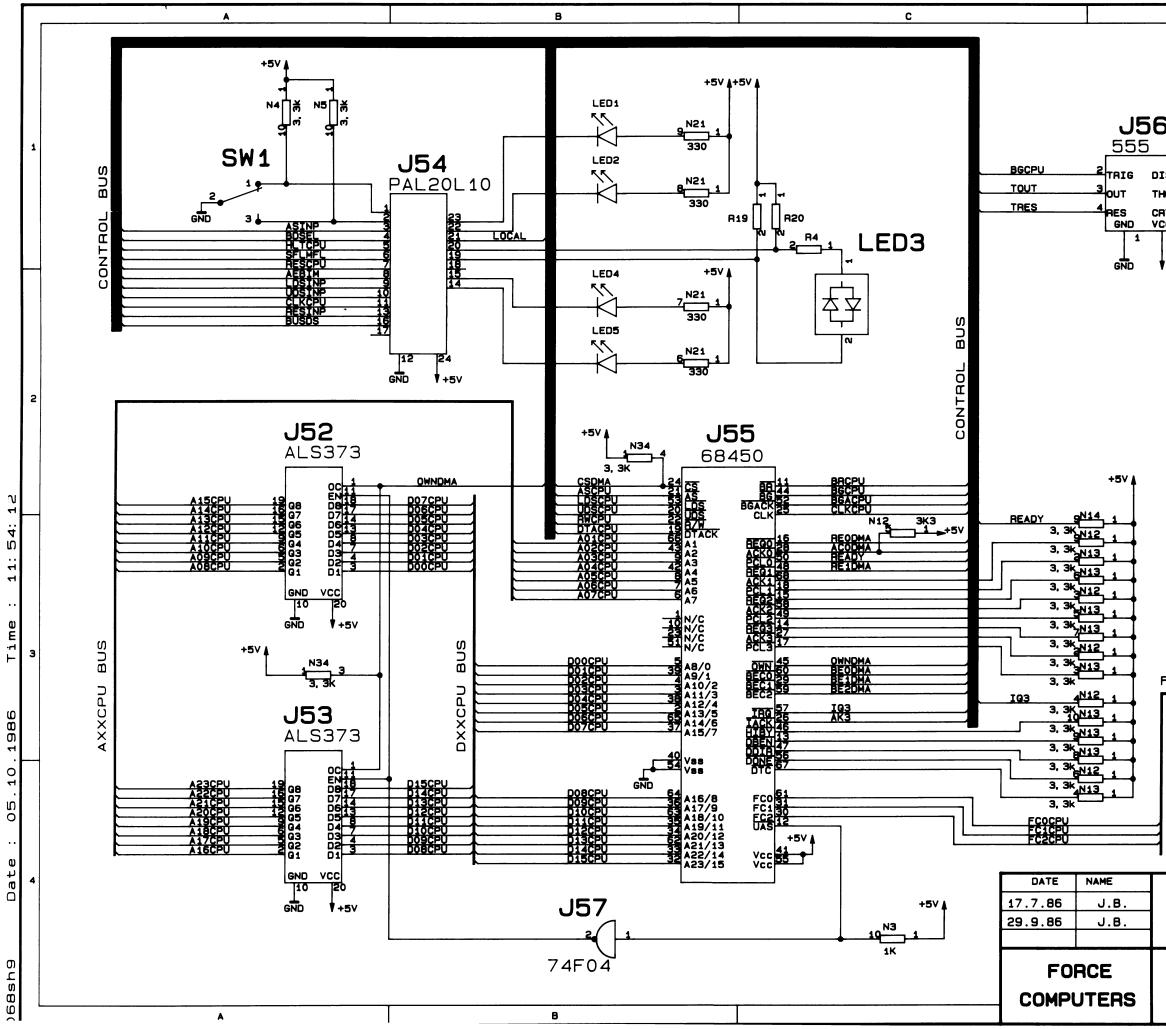

The SYS68K/ISCSI-1 board is a high performance intelligent SCSIbus controller board which fully supports the SCSI standard.

Up to four floppy drives can be controlled locally, without using the SCSIbus.

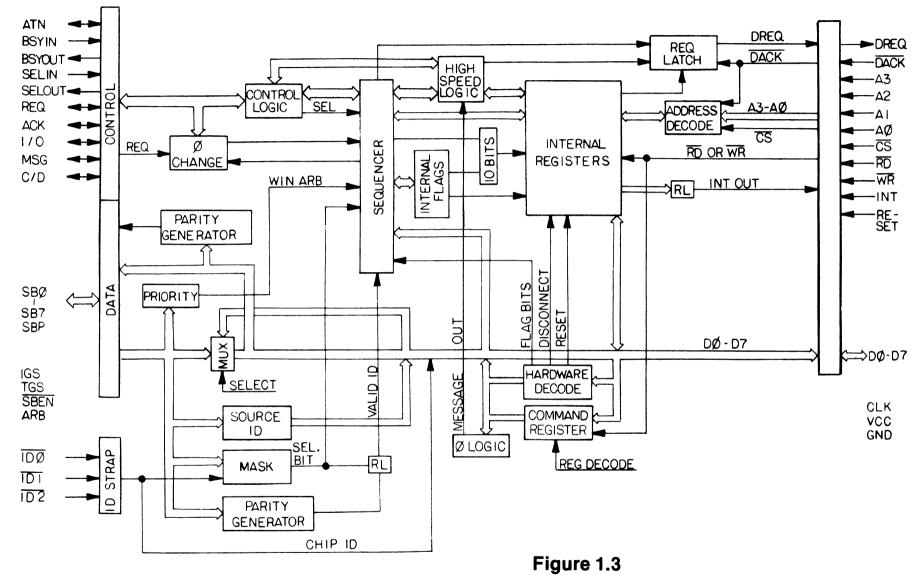

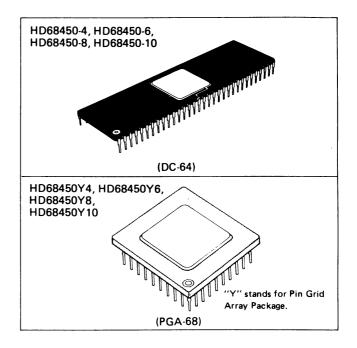

The board provides local intelligence with a 68010 CPU, 68450 DMAC, SCSI Bus Controller (SCSIBC) and Floppy Disk Controller (FDC). A 128Kbyte Dual Ported RAM (DPR) is used to store data and to interface the SYS68K/ISCSI-1 board. Highest throughput is guaranteed by using a 10MHz 68450 DMAC and the NCR 5386S SCSIBC.

On a single ended SCSIbus, the board works under the powerful firmware (128Kbyte EPROM area) as initiator or as target.

The SYS68K/ISCSI-1's own SCSIbus I.D. is software controlled. Four floppy drives are fully firmware supported, and can also be accessed via the SCSIbus in the target mode.

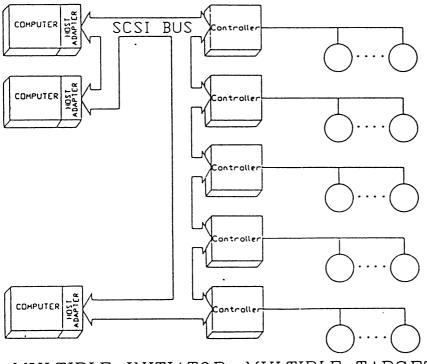

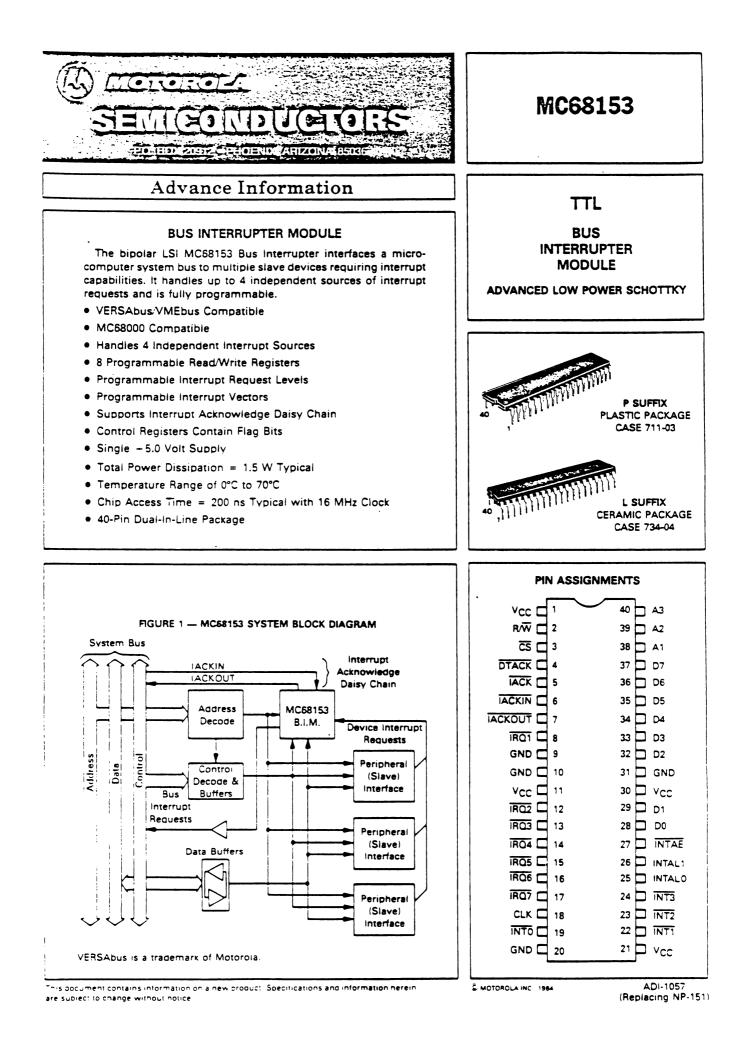

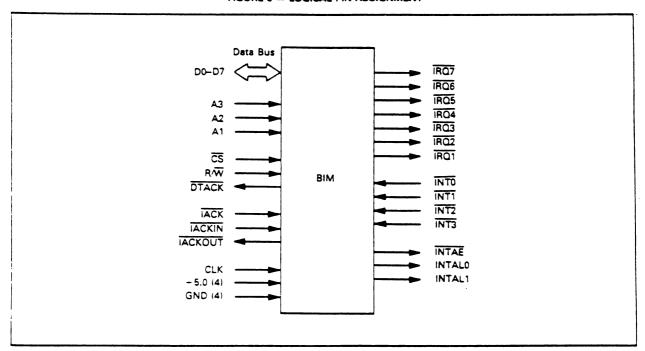

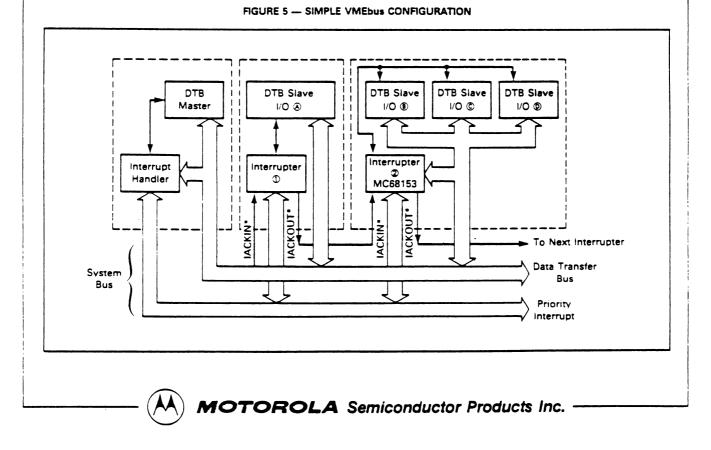

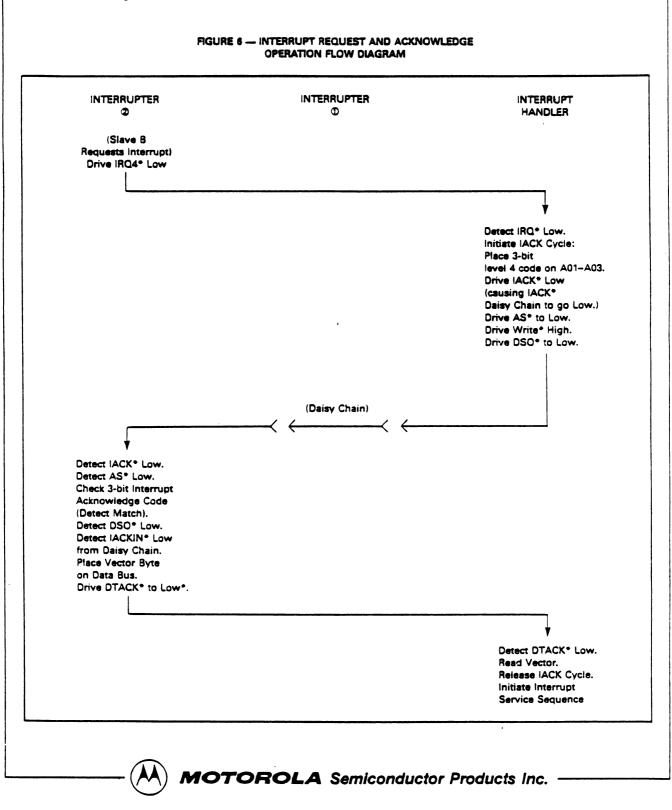

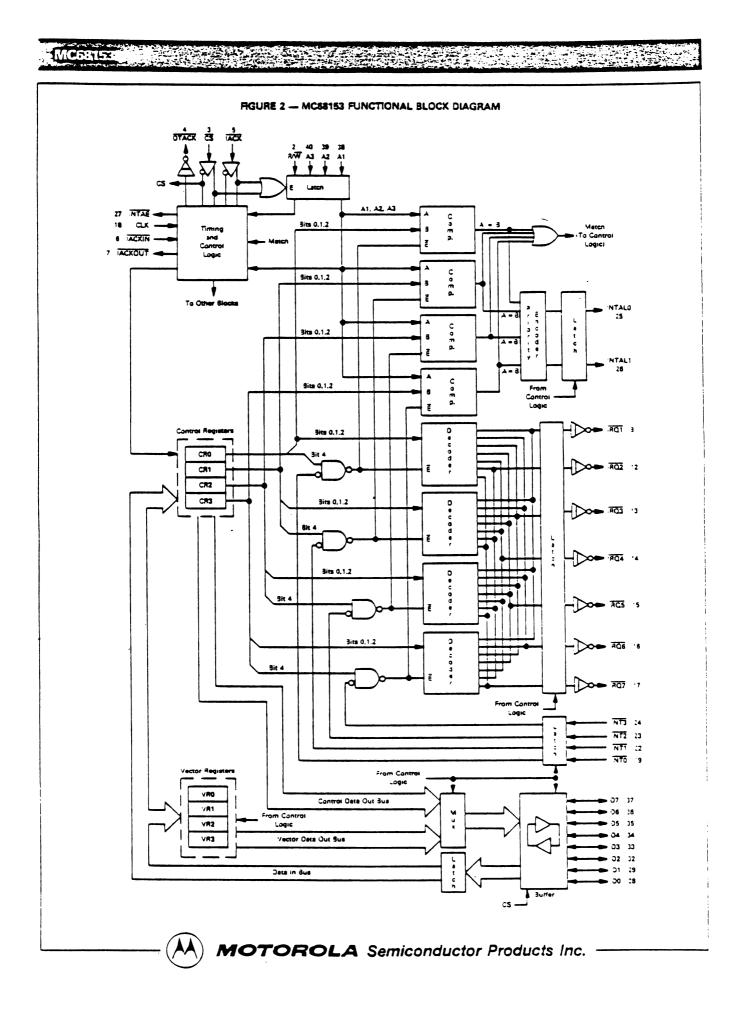

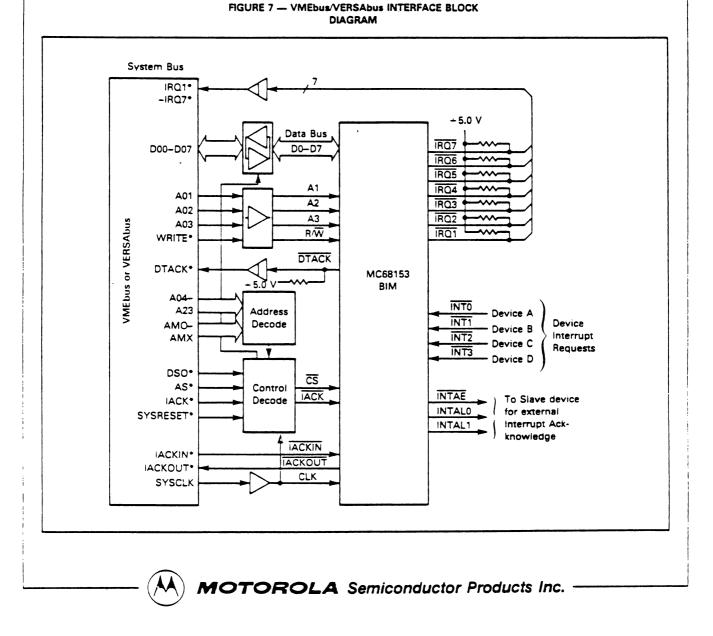

The SYS68K/ISCSI-1 contains a VMEbus Rev.C/IEEE Pl014 compatible interface to communicate to the host CPUs via its 128Kbyte DPR. The access address and the Address Modifier code are jumper selectable. A Bus Interrupter Module - BIM 68153 - is installed on the board to support fully asynchronous operation with the 4 different software programmable interrupt request channels.

The firmware of the SYS68K/ISCSI-1 described in the Firmware User's Manual handles all activities to/from the SCSIbus and the floppy interface. For special applications, the source code of the firmware is optionally available.

#### 1.1 Hardware Features of the SYS68K/ISCSI-1

- 68010 CPU for local control (10MHz)

- 68450 DMA Controller for local transfers (10MHz)

- Dual Ported 128Kbyte Ø wait state static RAM between the VMEbus and the local CPU

- SCSIbus interface built with the NCR 5386S SCSIbus controller.

Programmable as an initiator or target

- Transfer rate via the SCSIbus up to 1.5Mbyte/s

- SHUGART compatible floppy interface with the WD1772 FDC. Up to 4 floppy drives can be controlled independent of the SCSIbus

- All I/O signals available on P2 connector

- 4 different interrupt request signals to the VMEbus. Each channel contains a software programmable IRQ level (1 to 7) and vector

- Local parallel interface for controlling and monitoring board functions

- VMEbus Rev.C/IEEE Pl014 compatible interface A24:D16, D8

- Watchdog timer controlling correct functions of on-board hard and software

- Status and control LEDs for monitoring local activities

- High level handling firmware for communication, selftest, data caching/hashing and control

#### 1.2 The Hardware Functions

The local CPU reacts on the commands and initialisation parameters within the 128Kbyte DPR. Constant program run times are guaranteed through the special hardware logic providing zero wait state operation from the DPR, independent of the accesses from the VMEbus to the DPR.

The SYS68K/ISCSI-1 consists of self-test functions as well as a hardware watchdog timer which controls the activities of the 68010 CPU running with 10MHz.

User supplied programs can be loaded into the DPR and executed by the local CPU to adapt and extend board functionality.

The local CPU controls the SCSIbus and the floppy disk interface via local interrupts, and communicates to the host CPU via the DPR or via interrupt request to the VMEbus, generated by a Bus Interrupter Module.

The I/O signals to be supported through the NCR 5386S are terminated on the PC board. The terminators can be removed in order to be able to connect more than 3 SCSI devices.

#### 1.2.1 The Local 68010 CPU

A 10MHz 68010 CPU is installed on the SYS68K/ISCSI-1 to control the data traffic between the serial I/O channels and the VMEbus host CPU(s).

Two EPROMs with a maximum capacity of 128Kbyte are installed on the SYS68K/ISCSI-1 to hold the handling firmware. Constant zero wait state operation from the EPROM guarantees maximum CPU throughput and a fixed program run time.

The 128Kbyte Dual Ported RAM is also accessible without the insertion of wait states by using a CPU clock synchronized arbitration mechanism. The accesses from the CPU to the DPR are not delayed if a VMEbus access is pending or being executed.

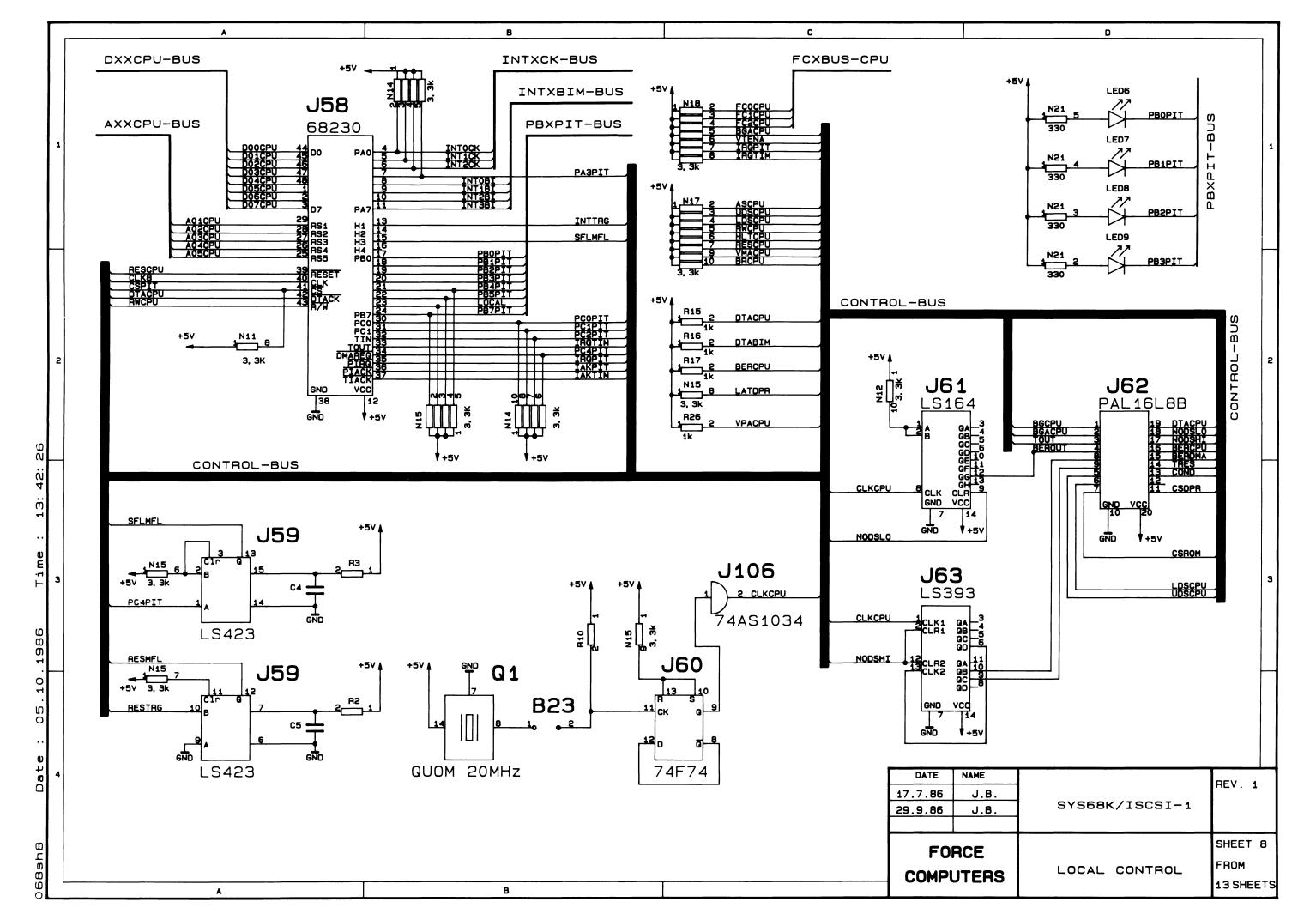

A local timer, included in the PI/T, is used to interrupt the CPU for task scheduling, command interpretation and execution.

The CPU and all I/O devices can be RESET through a SYSTEM reset via the SYSRESET signal of the VMEbus or by accessing a dedicated location within the DPR reserved for this function.

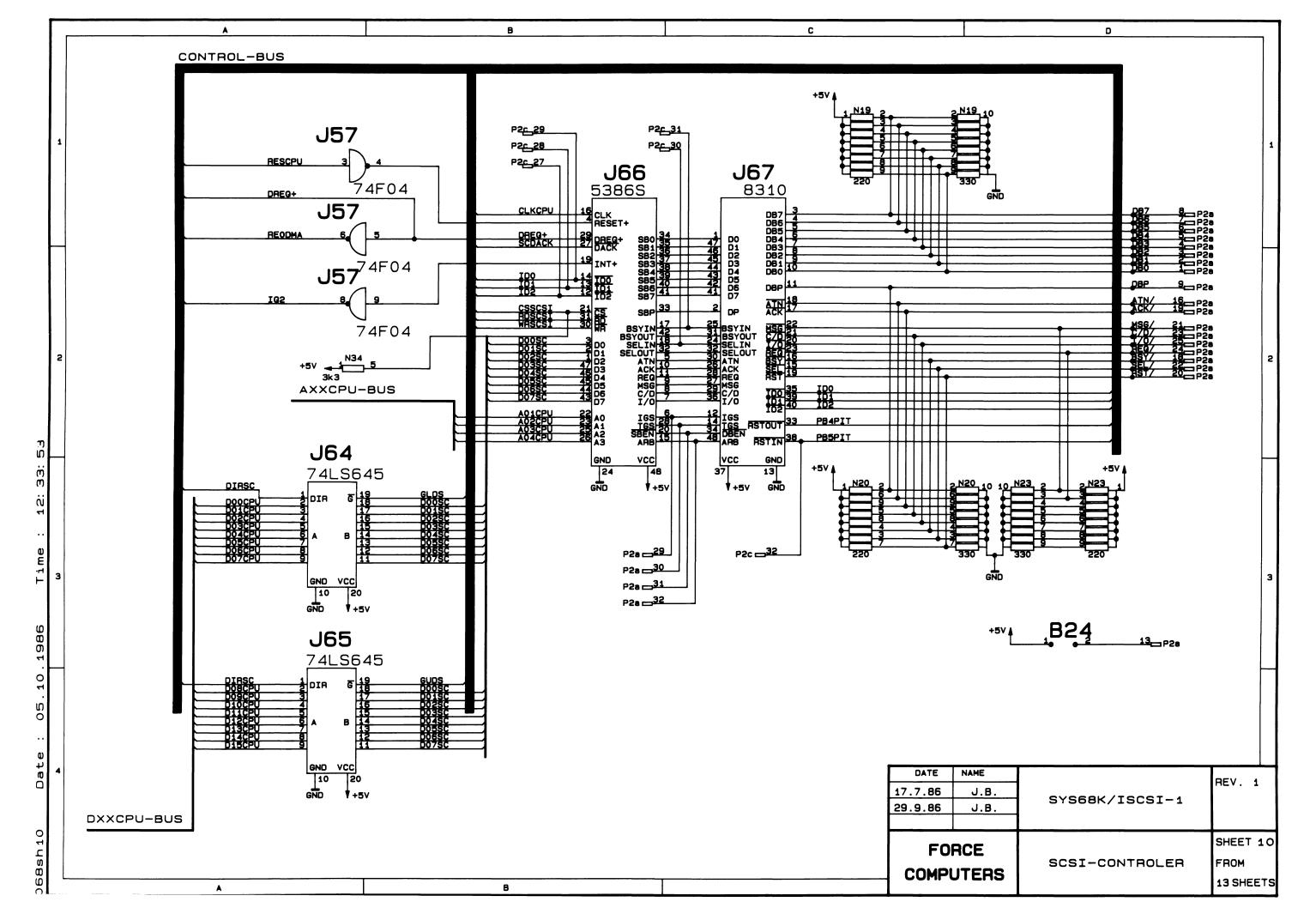

#### 1.2.2 The SCSIbus Interface

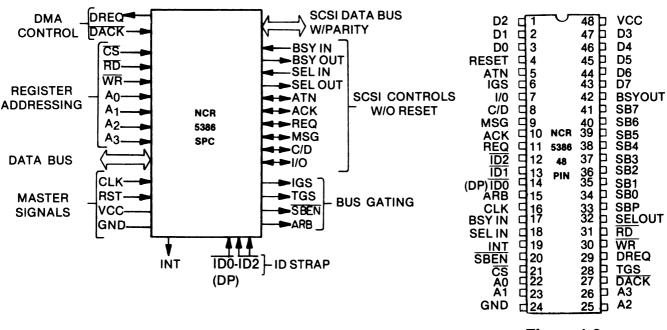

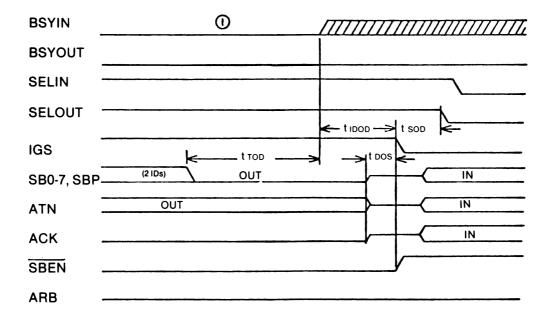

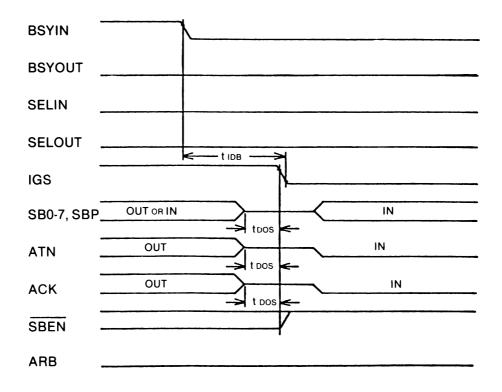

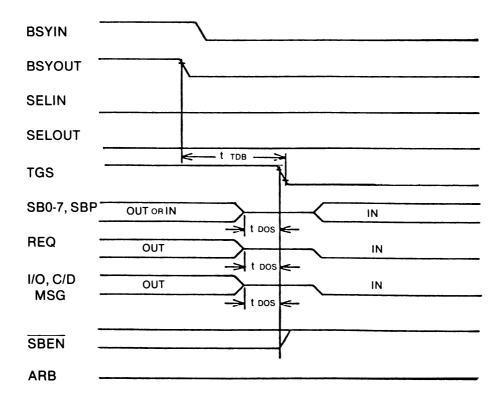

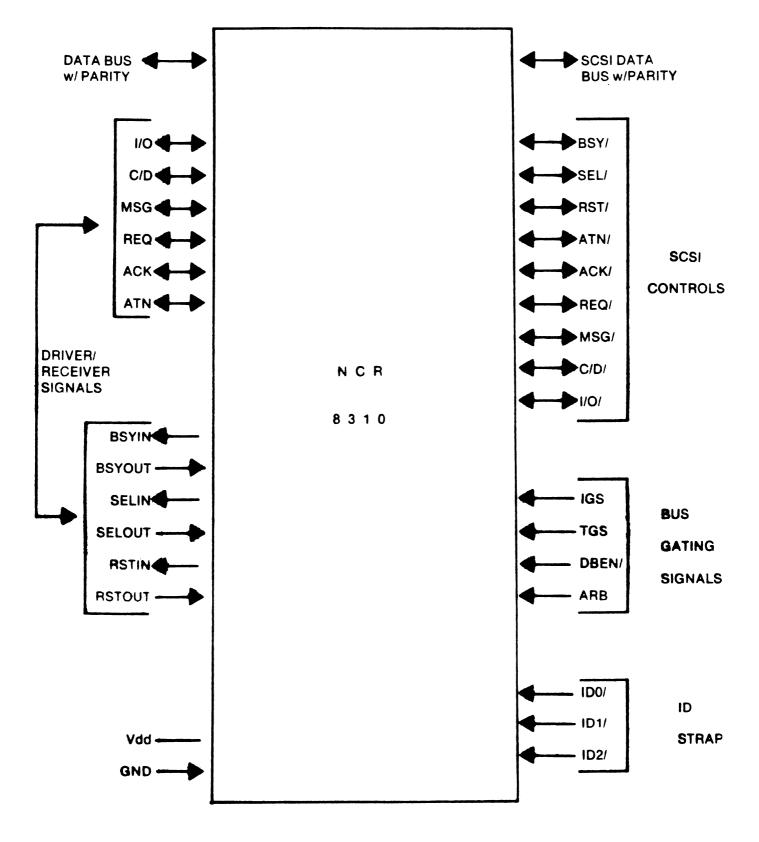

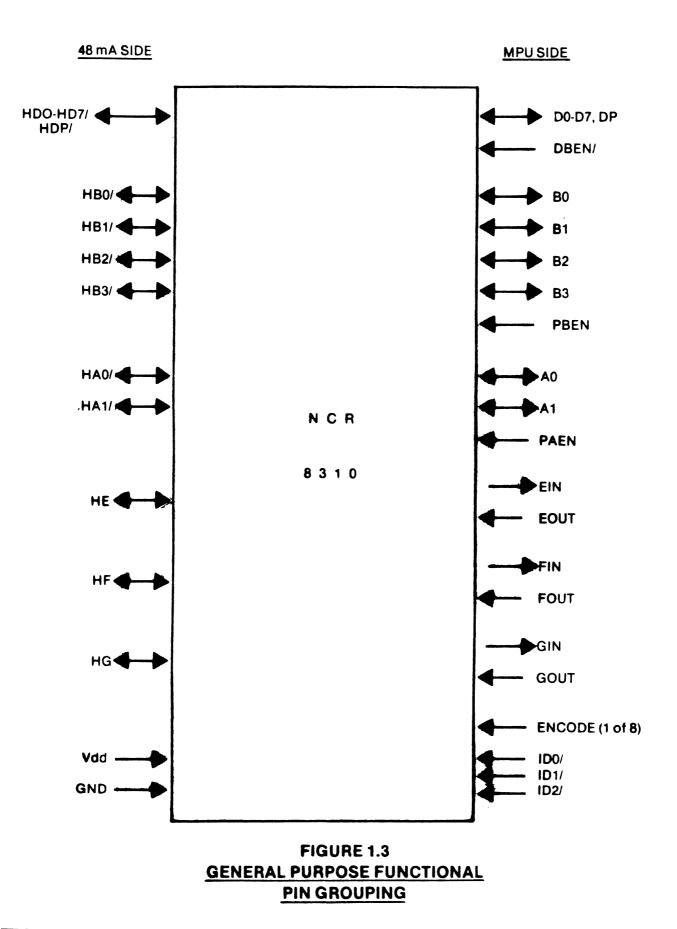

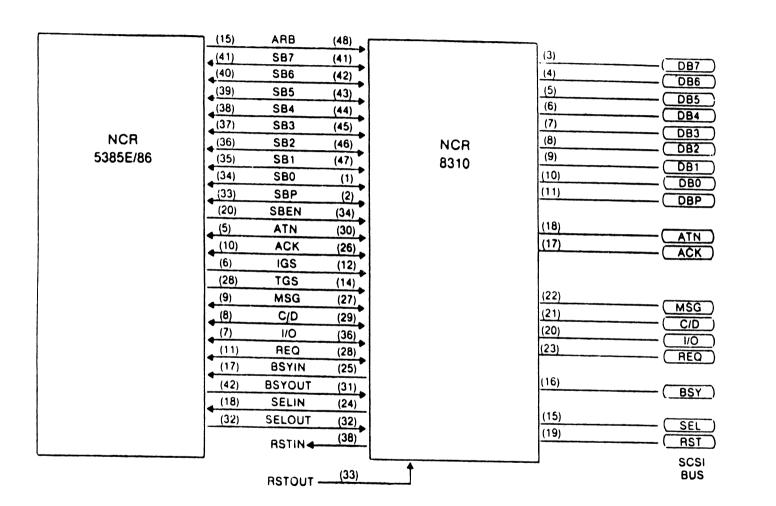

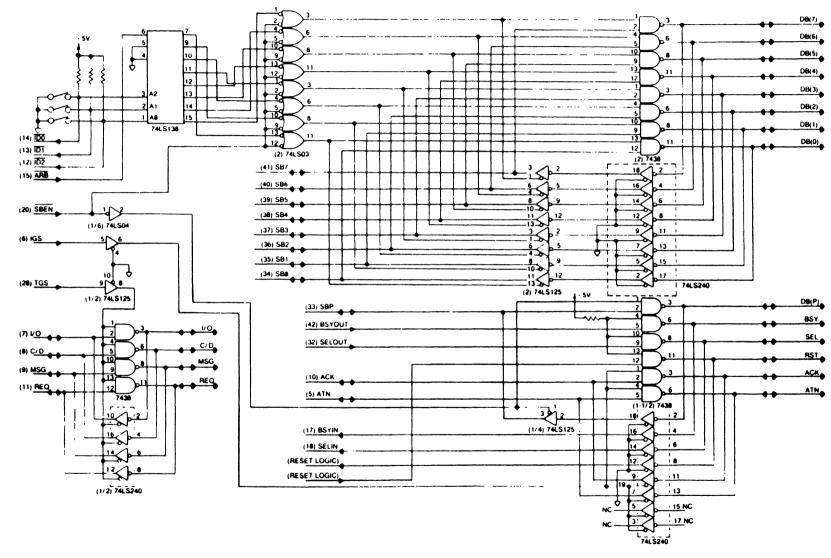

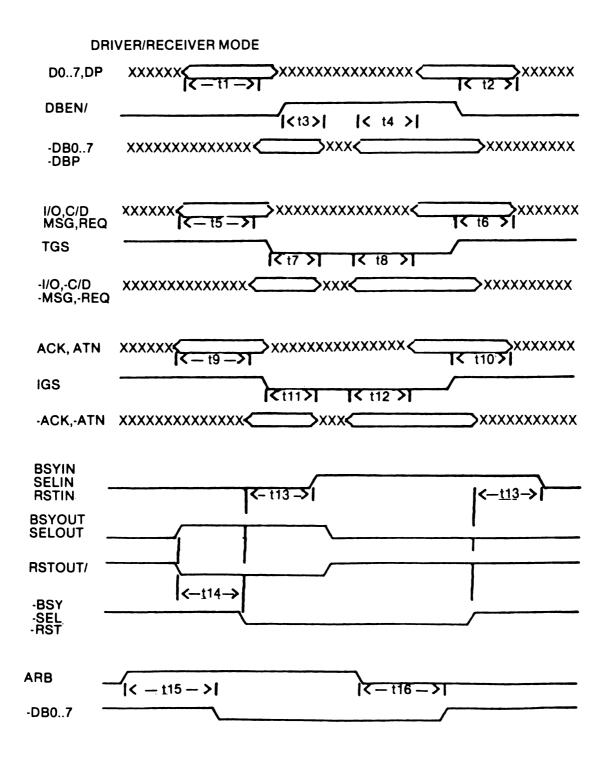

The SYS68K/ISCSI-1 contains an NCR 5386S SCSIbus controller and an NCR 8310 SCSIbus driver/transceiver. These chips provide the following features:

- Support of the ANSI X3T9.2 SCSI standard

- Asynchronous data transfer to 1.5Mbyte per second

- Support of both initiator and target modes

- Parity generation with optional checking

- Support of arbitration

- Control of all bus signals except RESET

- Doubly-buffered data register

- Versatile MPU bus interface

- Memory or I/O mapped MPU interface

- DMA or programmed I/O transfer

- 24-bit internal transfer counter

- Programmable (re)selection timeouts

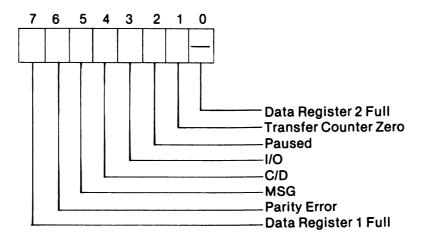

- Interrupt of MPU on all bus conditions requiring service

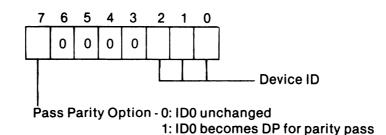

- SCSI pass parity optional with checking

- 48mA driver

The NCR 5386S SCSI Bus Controller communicates with the 68010 CPU and the 68450 DMAC as a peripheral device. The SCSI Bus Controller is controlled by reading and writing the internal registers which are addressed via the local address bus.

Since the SCSI Bus Controller interrupts the MPU when it detects an SCSIbus condition that requires servicing, the MPU is free from polling or controlling any of the SCSIbus signals.

For high speed data transfer, the SCSI Bus Controller communicates directly with the Dual Ported RAM via the DMA Controller. In this mode, the data transfer rate will be a maximum of 1.5Mbyte/s. The minimum guaranteed constant data throughput of the ISCSI-1 board is 1.3Mbyte/s, assuming an equivalent SCSI device data transfer rate.

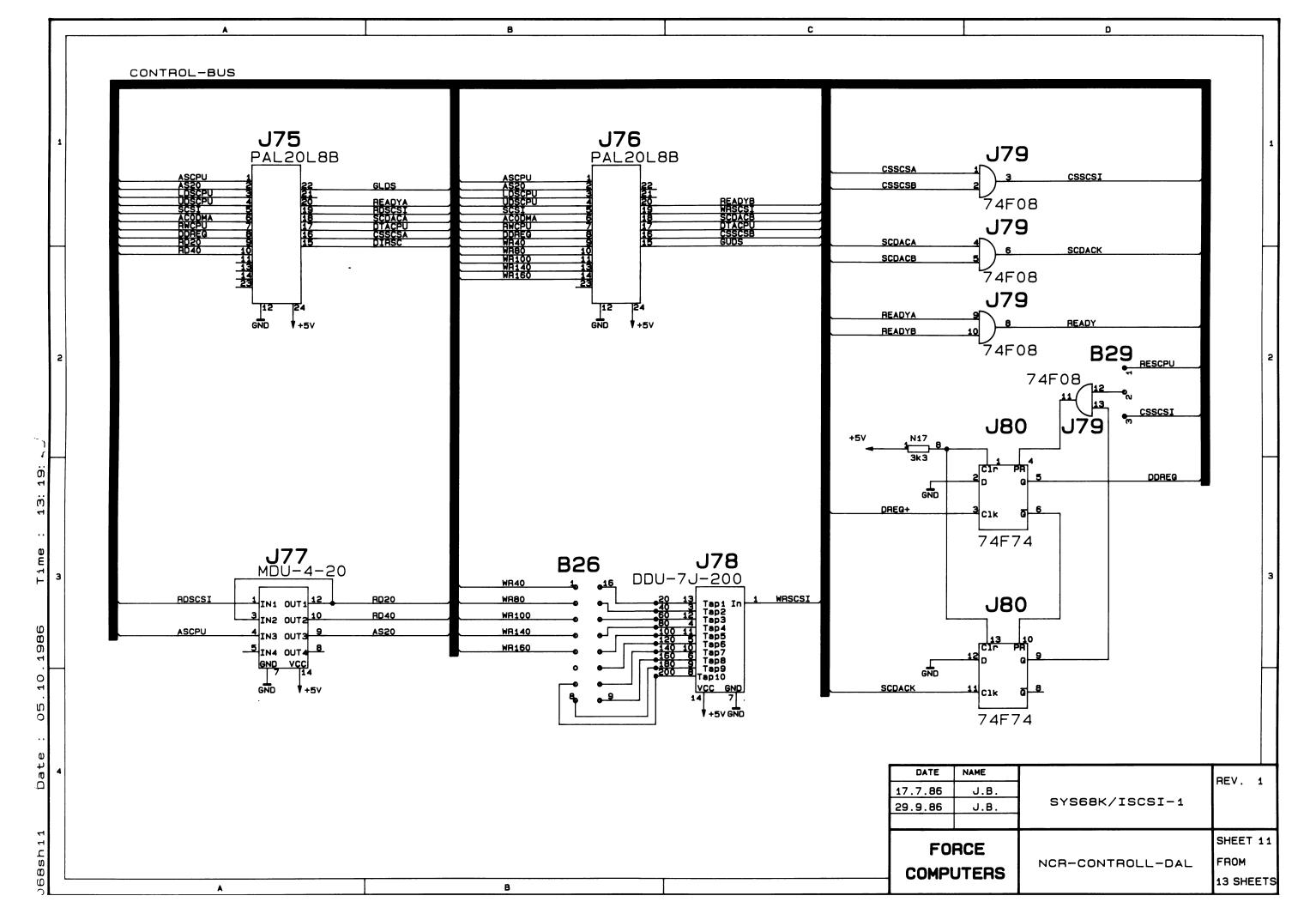

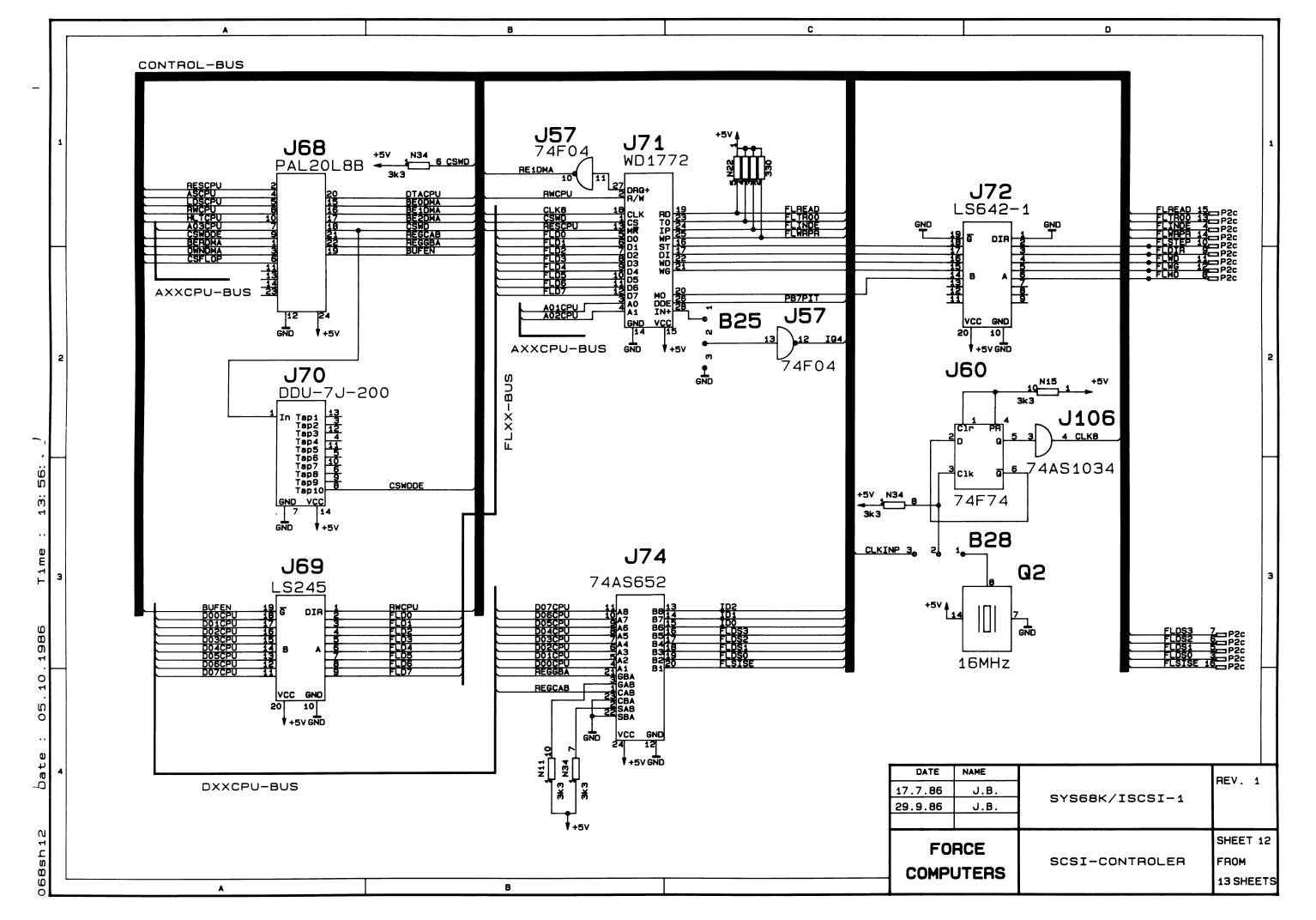

### 1.2.3 The Floppy Disk Interface

To provide easy connection from the ISCSI-1 board to floppy drives, the ISCSI-1 board includes a floppy disk interface.

The FDC WD1772 is able to control up to four floppy drives (3",  $3 \frac{1}{2}$ " and  $5 \frac{1}{4}$ ").

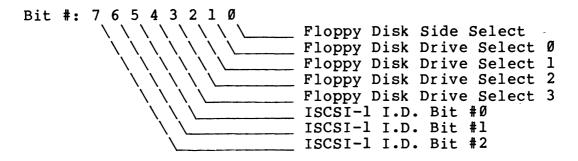

To allow the connection of all SHUGART-compatible floppy disk drives, the Drive Select signals  $\emptyset$  to 3, the Side Select signal and the single/double density signal are software programmable.

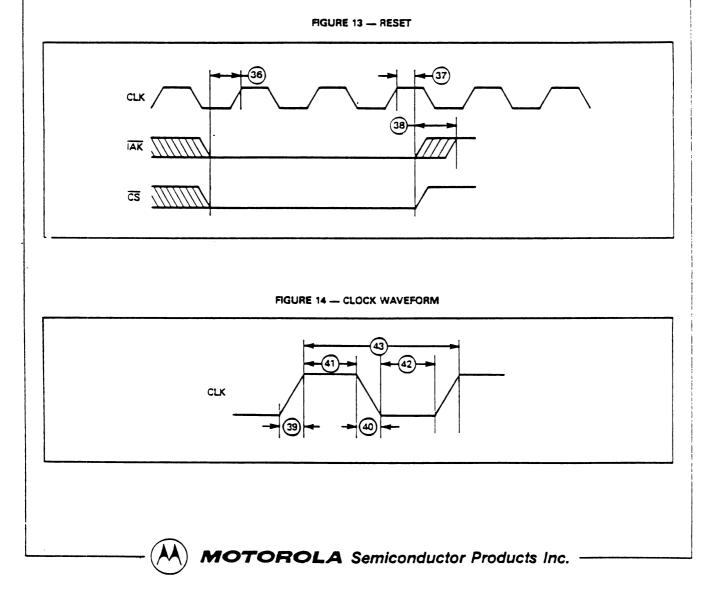

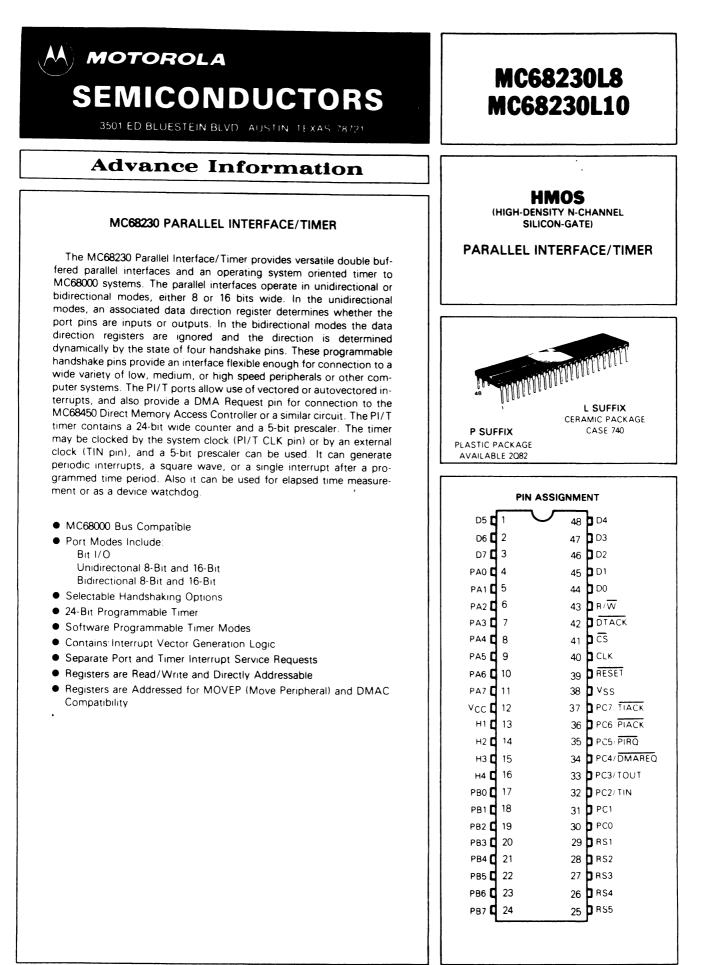

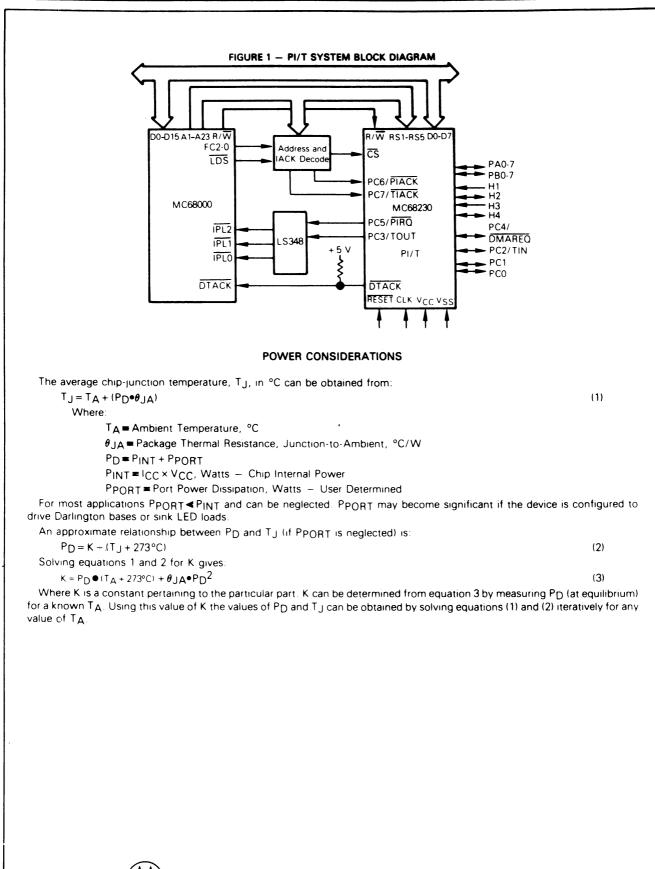

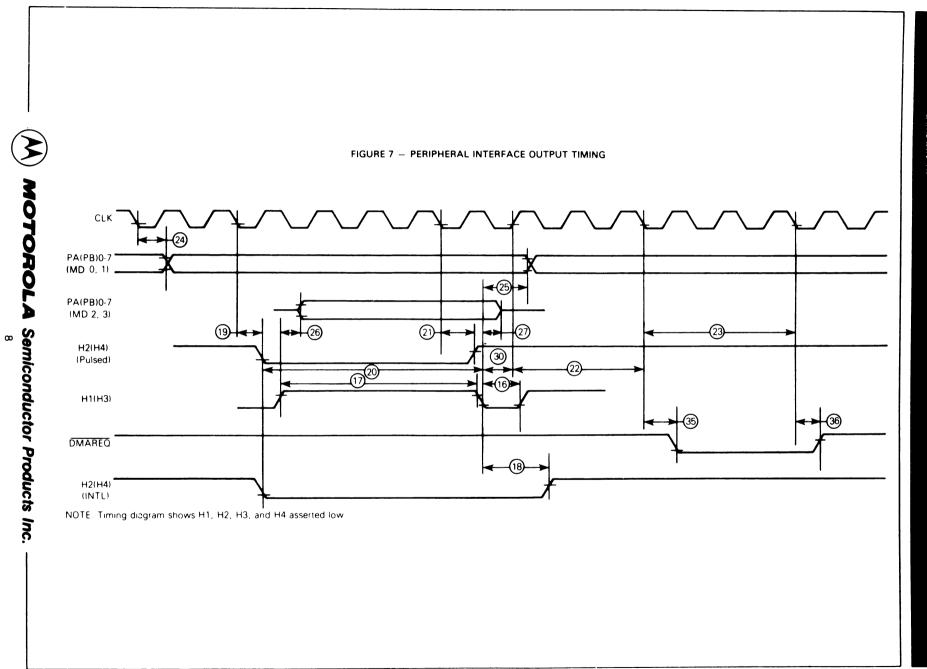

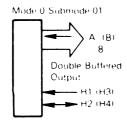

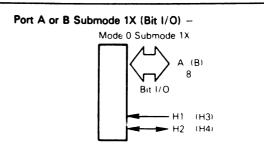

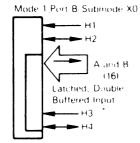

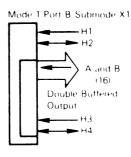

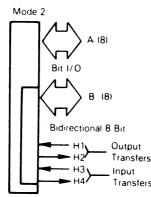

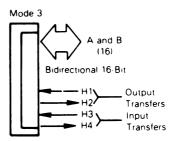

#### 1.2.4 The PI/T 68230

A 68230 Parallel Interface and Timer Chip is installed on the SYS68K/ISCSI-1 to control and display the status of all on-board activities. The PI/T is also used to force and monitor the interrupt request lines to the Bus Interrupter Module, which initiates the interrupts to the VMEbus (under control of the host CPU).

One handshake pin is used to interrupt the local CPU if the host CPU accesses a defined location within the DPR. One output signal is used to force the SYSFAIL signal of the VMEbus if an onboard error has been detected or if the board initializes the DPR after RESET or Power up.

The timer, also included in the PI/T, is the time base for the onboard handling firmware and the scheduler for the macro commands.

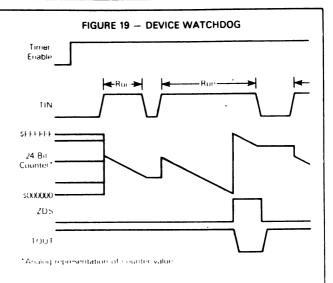

A watchdog timer, for processor control, is installed on the board to detect software or hardware errors independent from the onboard CPU. For this purpose, one output of the PI/T is used to retrigger the watchdog timer within defined time frames.

If the onboard CPU does not work properly, or if the hardware isn't working correctly, the timer will not be retriggered, and the SYSFAIL signal of the VMEbus will be activated. The host CPU then can initiate a software controlled RESET for the ISCSI, or start other maintenance activities.

The SCSIbus RESET is controlled by the PI/T. One input of the PI/T indicates the state of the SCSIbus RESET, and one output controls the SCSIbus RESET signal.

The FDC 1772 single/double density selection is made via one PI/T output.

#### 1.2.5 The Dual Ported RAM

128Kbyte of Dual Ported Static RAM with 45ns access time are installed on the SYS68K/ISCSI-1 to service all applications requiring fast operations and large amounts of data areas.

The local 68010 CPU runs without the insertion of wait states out of the DPR, because a CPU clock synchronised arbitration logic and a full buffered and latched VMEbus interface is installed on the SYS68K/ISCSI-1. Between two CPU access cycles, a VMEbus cycle is serviced and completed. On VMEbus Read cycles, the data pattern is latched, and the internal cycle of the DPR is aborted while the VMEbus cycle is decoupled.

A partition of the DPR is reserved for the local CPU for vector storage, the program counter, and temporary buffers. This partition is used from the VMEbus side for programming the BIM and initiating an interrupt, which will be handled from the onboard CPU, or driving a local RESET.

The access address and the Address Modifier code(s) are jumper selectable in 128Kbyte increments within the standard address range (A24:D16,D8). The access times of the DPR depend on the accesses made by the local CPU while the local 68010 has priority over VMEbus accesses.

#### 1.2.6 The VMEbus Interface

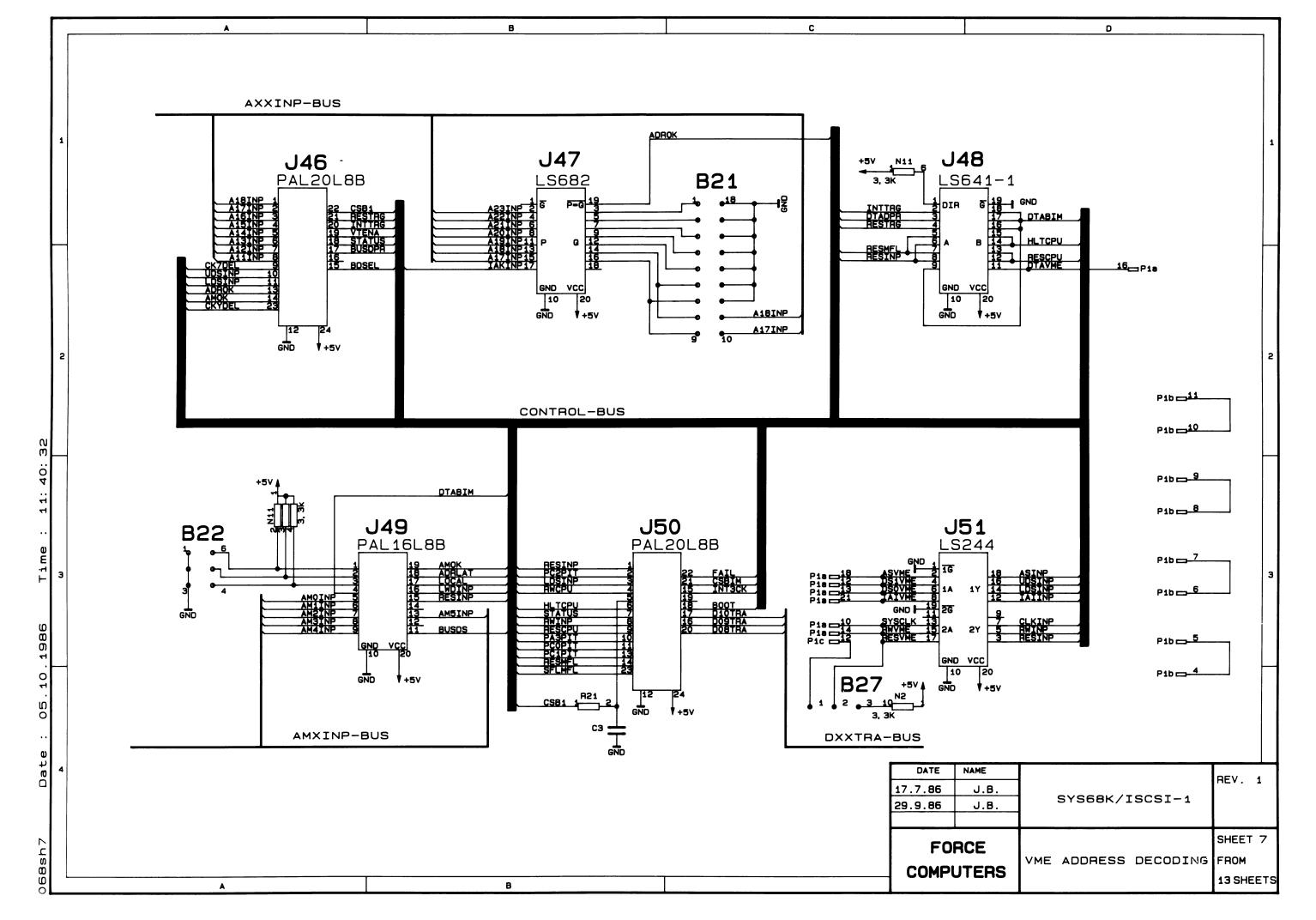

A full VMEbus Rev.C/IEEE Pl014 compatible interface is installed on the SYS68K/ISCSI-1 to allow an access to the DPR and the Bus Interrupter Module.

The 16-bit data width (D16,D8) of the DPR and the decoding of the standard address range (A24) allows easy installation in all VMEbus environments.

During Power-up and after a RESET has been executed from the local CPU, the SYS68K/ISCSI-1 drives the VMEbus signal SYSFAIL active to signal each board in the VMEbus environment that the board is not ready or has detected a malfunction.

A RESET for the local CPU can be initiated by accessing a dedicated address within the 128Kbyte boundary of the DPR. All local devices as well as the CPU will be reset through this access.

An interrupt to the local CPU can be forced by accessing another location within the DPR, signalling the on-board processor that a command has been given, or that an exception has to be taken.

The Dual Ported RAM can be accessed at least every 640ns because this is the worst case cycle time. The data transfer rate to/from the SYS68K/ISCSI-1 is 3 to 4Mbyte/s including the VMEbus protocol.

|            | Access Time | Cycle Time |

|------------|-------------|------------|

| best case  | 330         | 4ØØ        |

| average    | 43Ø         | 500        |

| worst case | 560         | 630        |

#### 1.2.7 The Bus Interrupter Module

To allow fully asynchronous operation, the SYS68K/ISCSI-1 contains a Bus Interrupter Module - BIM 68153 - providing 4 individually programmable interrupt channels. Each channel is able to force an interrupt request to the VMEbus. For each channel, the IRQ level (1 to 7) as well as the interrupt vector is fully software programmable.

The local CPU forces the requests to the BIM and the host CPU can program the interrupt vector and the level. This allows dynamic change of the interrupt level and vector in multi-processor environments.

#### 1.2.8 The Optional Back Panel

A back panel which can be plugged into the P2 connector of the SYS68K/ISCSI-1 board is optionally available. Included on this board is a 50-pin 2-row connector for the SCSIbus and a 34-pin 2-row connector for the floppy disk interface.

## 2.Ø Specification of the SYS68K/ISCSI-1

| Local CPU             | 68010 with 10MHz clock frequency                                                                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPROM                 | 128Kbyte maximum capacity<br>Ø Wait State operation                                                                                                                                                     |

| Dual Ported RAM       | 128Kbyte capacity using static RAMs<br>Ø Wait State operation from local CPU<br>330 ns best case VMEbus access time<br>430 ns average VMEbus access time<br>560 ns worst case VMEbus access time        |

| SCSIbus Interface     | NCR 53685 providing<br>initiator, target mode<br>asynchronous and synchronous modes<br>asynchronous data rate up to 1.5sbyte/s                                                                          |

| Floppy Disk Interface | SHUGART-compatible<br>Up to 4 drives (3", 3 1/2", 5 1/4")                                                                                                                                               |

| VMEbus Interface      | Full Rev. C and IEEE Pl014 compatible<br>A24:D16,D8 mode<br>4 IRQs with SW programmable level (1 to7)<br>and vector<br>Access Address jumper selectable<br>in 128Kbyte increments<br>SYSFAIL* supported |

| Handling Firmware     | in EPROM with macro commands for all I/O<br>channels installed                                                                                                                                          |

| Power Requirements    | +5V: 5.6 A (max) (Power Backplane or<br>+12V: 0.0 A (max) power connection<br>-12V: 0.0 A (max) on P2 necessary)                                                                                        |

| Operating Temperature | Ø to 50 Degrees C                                                                                                                                                                                       |

| Storage Temperature   | -50 to +85 Degrees C (non-operating)                                                                                                                                                                    |

| Relative Humidity     | Ø to 90% (non-condensing)                                                                                                                                                                               |

| Dimensions            | 233 x 160mm<br>9.2" x 6.3"                                                                                                                                                                              |

SYS68K/ISCSI-1Intelligent SCSIbus Controller<br/>board including firmware and<br/>documentation.

Back panel for the SYS68K/ISCSI-1 board providing SCSIbus connector

and floppy drive connector

SYS68K/ISCSI-1BPS

Part No. 300021

SYS68K/ISCSI-1/UM User's Manual for the SYS68K/ISCSI-1 Part No. 800114

SYS68K/ISCSI-1/SCSource Code of the SYS68K/ISCSI-1<br/>handling firmware, including<br/>documentation

# INSTALLATION

Please read the complete installation procedure before the board is installed in a VMEbus environment to avoid malfunctions and component damages.

### Table of Contents

| 1.0 | General Overviewl-1 |                                           |  |

|-----|---------------------|-------------------------------------------|--|

|     | 1.1                 | The Function Switch Positionsl-1          |  |

|     | 1.2                 | Connection of I/O Devices1-2              |  |

|     | 1.3                 | Base Address Selection and AM Decodingl-4 |  |

|     | 1.4                 | Interruptsl-4                             |  |

| 2.0 | Inst                | allation in the Rack2-1                   |  |

|     | 2.1                 | Power On                                  |  |

|     | 2.2                 | The SYS68K/ISCSI-1 On-Board Selftest2-2   |  |

## List of Tables

| Table 1-1 | The P2 Pin | Assignment | 1-2 |

|-----------|------------|------------|-----|

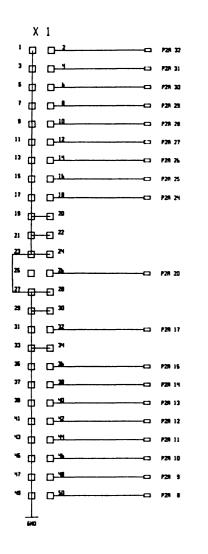

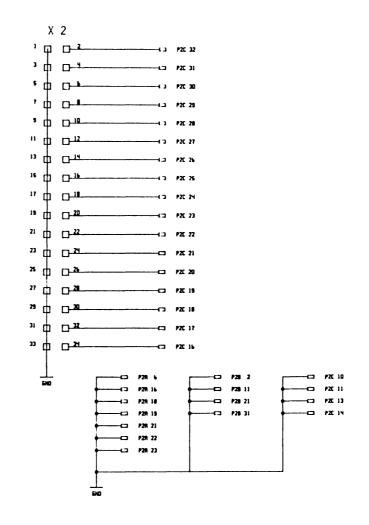

| Table 1-2 | The Xl Pin | Assignment | 1-3 |

| Table 1-3 | The X2 Pin | Assignment | 1-3 |

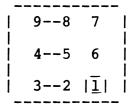

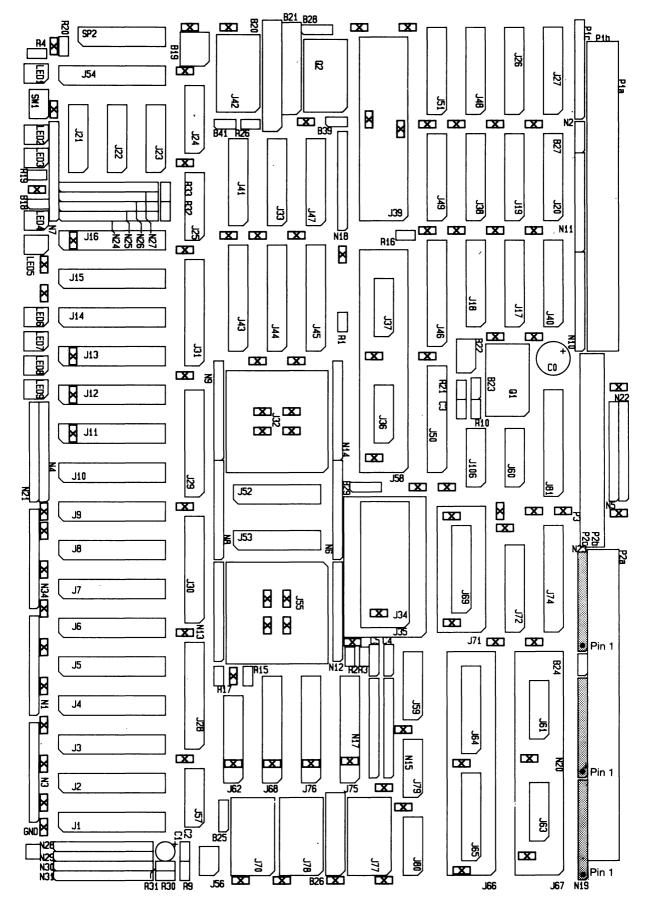

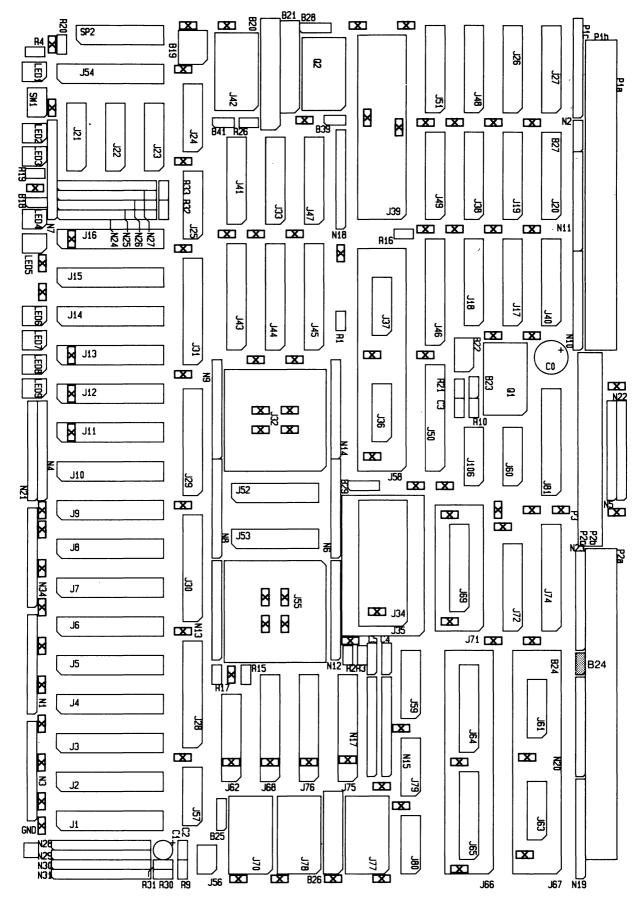

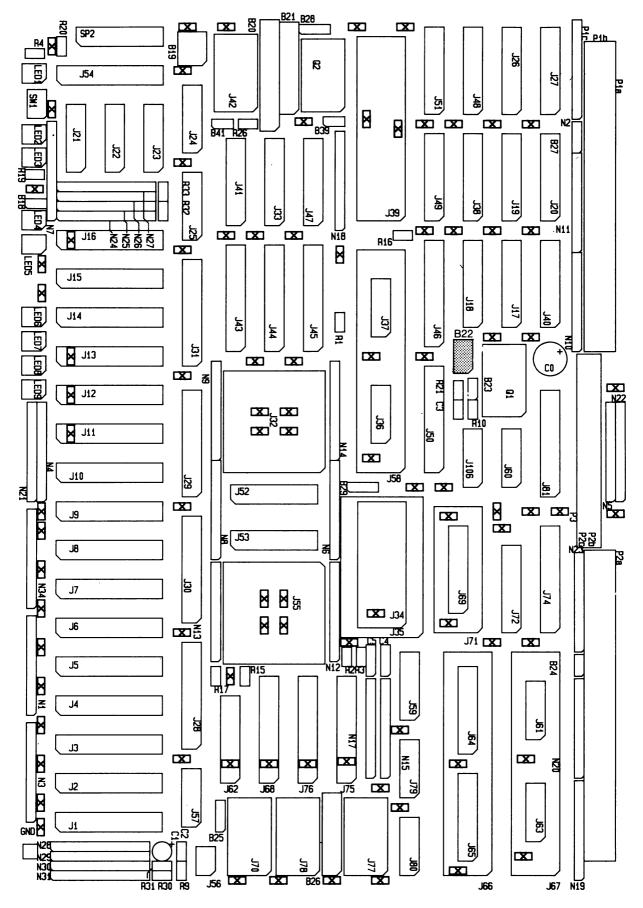

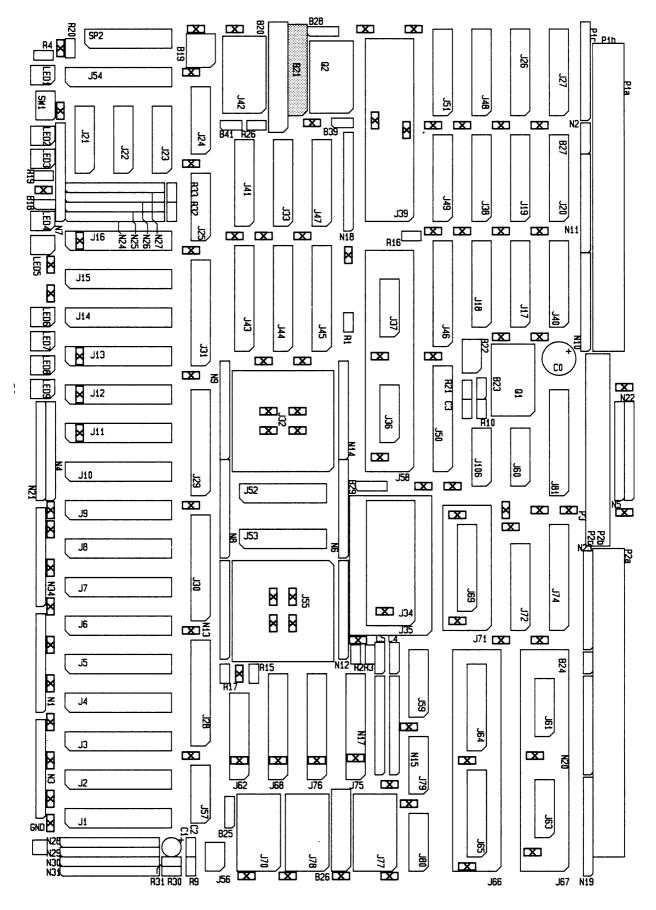

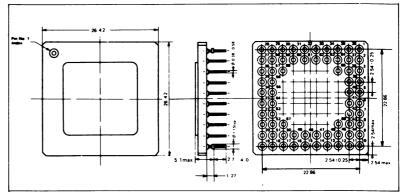

### Figure 1-1: Photo of the SYS68K/ISCSI-1

#### 1.0 General Overview

Easy installation of the SYS68K/ISCSI-1 is provided as the board is shipped in a ready-to-operate default configuration. A selftest is executed on reset by the firmware on the board.

Please read the complete installation procedure before mounting the board into a VMEbus backplane.

#### 1.1 The Function Switch Positions

There is a RUN/LOCAL (R/L) toggle switch installed on the front panel.

The two positions of the switch are defined as "UP" and "DOWN". The switch has to be set to "DOWN" for the first installation.

#### 1.2 Connection of I/O Devices

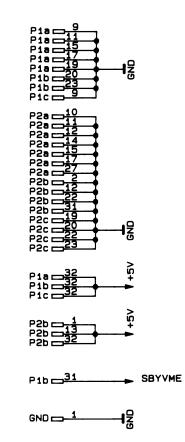

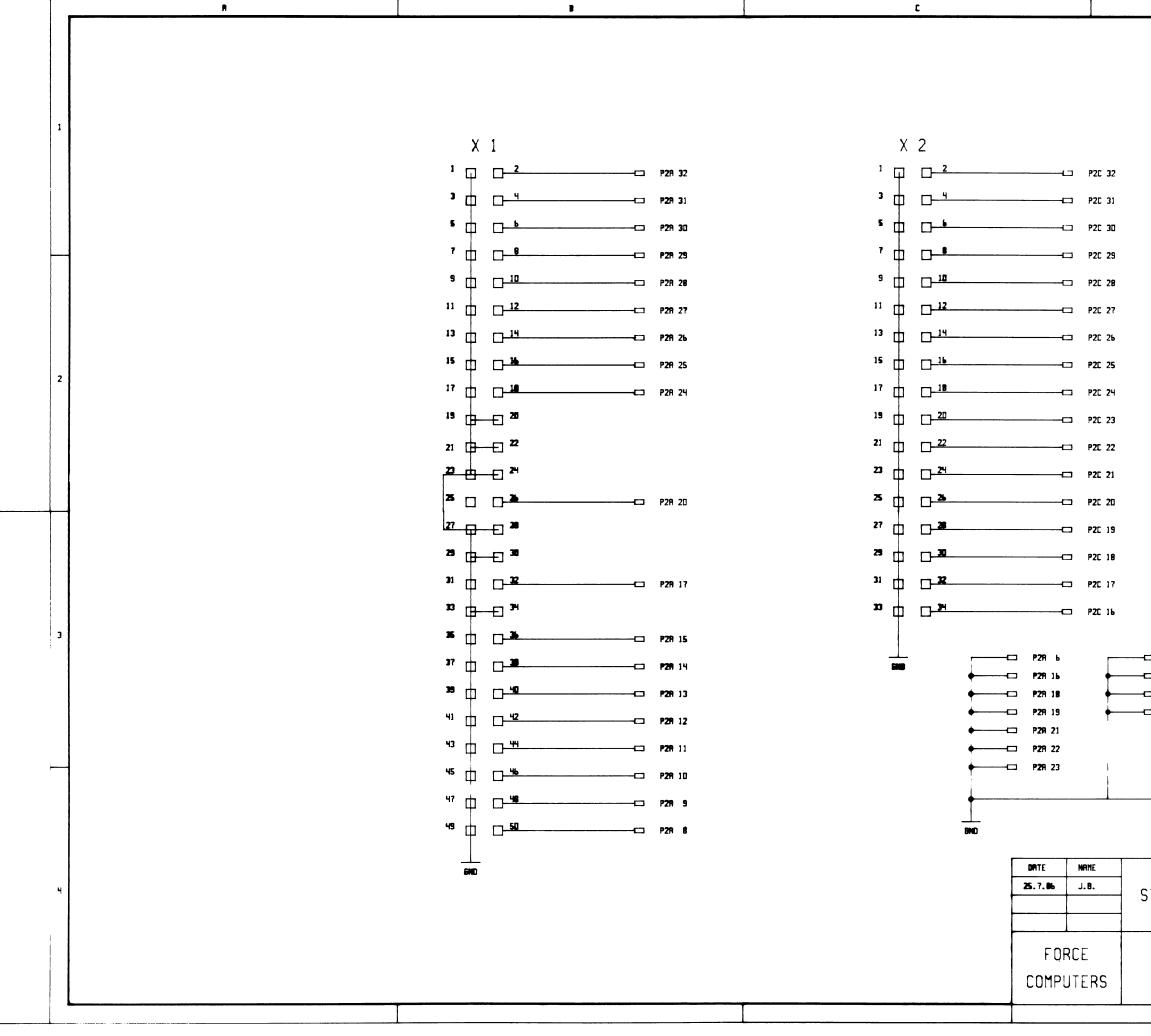

The SCSIbus signals and the floppy disk interface signals are routed to the P2 connector of the SYS68K/ISCSI-1 board. Table 1-1 shows the pin out of the P2 connector. For a detailed description, please refer the to Hardware User's Manual, Chapter 4.8.

If the optional SYS68K/ISCSI-1BPS is used, it must be connector to the P2 connector of the SYS68K/ISCSI-1 board. The pin out of the SCSIbus connector (X1) is listed in Table 1-2 and the pin out of the floppy disk interface connector (X2) is listed in Table 1-3.

| Pin         | Row A           | Row B           | Row C           |

|-------------|-----------------|-----------------|-----------------|

| Number      | Signal Mnemonic | Signal Mnemonic | Signal Mnemonic |

|             |                 |                 |                 |

|             | 6               |                 |                 |

| 1<br>2<br>3 | DB Ø            | VCC             | N.C.            |

| 2           | DB 1            | GND             | N.C.            |

| 3           | DB 2            | N.C.            | Drive Select Ø  |

| 4           | DB 3            | N.C.            | Index           |

| 5           | DB 4            | N.C.            | Drive Select 1  |

| 6           | DB 5            | N.C.            | Drive Select 2  |

| 7           | DB 6            | N.C.            | Drive Select 3  |

| 8           | DB 7            | N.C.            | Motor On        |

| 9           | DB P            | N.C.            | Direction In    |

| 10          | GND             | N.C.            | Step            |

| 11          | GND             | N.C.            | Write Data      |

| 12          | GND             | GND             | Write Gate      |

| 13          | TERMPWR         | VCC             | Track ØØØ       |

| 14          | GND             | N.C.            | Write Protect   |

| 15          | GND             | N.C.            | Read Data       |

| 16          | ATN             | N.C.            | Side Select     |

| 17          | GND             | N.C.            | N.C.            |

| 18          | BSY             | N.C.            | N.C.            |

| 19          | ACK             | N.C.            | GND             |

| 20          | RST             | N.C.            | GND             |

| 21          | MSG             | N.C.            | N.C.            |

| 22          | SEL             | GND             | GND             |

| 23          | C/D             | N.C.            | GND             |

| 24          | REQ             | N.C.            | N.C.            |

| 25          | 1/0             | N.C.            | N.C.            |

| 26          | N.C.            | N.C.            | N.C.            |

| 20          | GND             | N.C.            | RESERVED        |

| 28          | N.C.            | N.C.            | RESERVED        |

| 29          | RESERVED        | N.C.            | RESERVED        |

| 30          | RESERVED        | N.C.            | RESERVED        |

| 31          | RESERVED        | GND             | RESERVED        |

| 32          | RESERVED        | VCC             | RESERVED        |

| 22          | KESEKVED        | vcc             |                 |

|             | I I             |                 | I               |

Table 1-1: The P2 Pin Assignment

| Pin N | o.  Signal Mnemonic | Pin Number | Signal Mnemonic |

|-------|---------------------|------------|-----------------|

| 2     | DB Ø                | 1          | GND             |

| 4     | DB 1                | 3          | GND             |

| 6     | DB 2                | 5<br>7     | GND             |

| 8     | DB 3                | 7          | GND             |

| 10    | DB 4                | 9          | GND             |

| 12    | DB 5                | 11         | GND             |

| 14    | DB 6                | 13         | GND             |

| 16    | DB 7                | 15         | GND             |

| 18    | DB P                | 17         | GND             |

| 20    | GND                 | 19         | GND             |

| 22    | GND                 | 21         | GND             |

| 24    | GND                 | 23         | GND             |

| 26    | TERMPWR             | 25         | N.C.            |

| 28    | GND                 | 27         | GND             |

| 30    | GND                 | 29         | GND             |

| 32    | ATN                 | 31         | GND             |

| 34    | GND                 | 33         | GND             |

| 36    | BSY                 | 35         | GND             |

| 38    | ACK                 | 37         | GND             |

| 40    | RST                 | 39         | GND             |

| 42    | MSG                 | 41         | GND             |

| 44    | SEL                 | 43         | GND             |

| 46    | C/D                 | 45         | GND             |

| 48    | REQ                 | 47         | GND             |

| 50    | 1/0                 | 49         | GND             |

## Table 1-3: The X2 Pin Assignment

| Pin | No.  Signal Mnemonic | Pin Number | Signal Mnemonic |

|-----|----------------------|------------|-----------------|

| 2   | N.C.                 | 1          | GND             |

| 4   | N.C.                 | 3          | GND             |

| 6   | Drive Select Ø       | 5          | GND             |

| 8   | Index                | 7          | GND             |

| 10  | Drive Select l       | 9          | GND             |

| 12  | Drive Select 2       | 11         | GND             |

| 14  | Drive Select 3       | 13         | GND             |

| 16  | Motor On             | 15         | GND             |

| 18  | Direction In         | 17         | GND             |

| 20  | Step                 | 19         | GND             |

| 22  | Write Data           | 21         | GND             |

| 24  | Write Gate           | 23         | GND             |

| 26  | Track ØØØ            | 25         | GND             |

| 28  | Write Protect        | 27         | GND             |

| 30  | Read Data            | 29         | GND             |

| 32  | Side Select          | 31         | GND             |

| 34  | N.C.                 | 33         | GND             |

1-3

#### 1.3 Base Address Selection and AM Decoding

The default setup of the SYS68K/ISCSI-1 board is as follows:

Base Address \$A00000

End Address \$Alffff

Address Modifiers are set to accept privileged and nonprivileged standard data accesses (A24:D16,D8)

If a different setup is required, please refer to the Hardware User's Manual.

#### 1.4 Interrupts

All interrupt levels and vectors are software programmable on the SYS68K/ISCSI-1 so no hardware setup is required.

#### 2.0 Installation in the Rack

The board is configured to be mounted into a VMEbus rack at any one of the slots 2-21.

A reset generator has to be included in another slot.

- **Caution:** A) The VMEbus rack has to include a Jl and a J2 backplane.

- B) Switch power off before installing the board to avoid electrical damages to the components.

- C) The board has the be plugged in and the screws of the front panel must be turned on to guarantee proper installation.

- D) No connections are allowed on the P2 backplane on rows A and C (i.e. VMXbus or VSBbus connection).

#### 2.1 Power On

If the board is installed correctly, the following sequence will take place:

- 1) Green RUN LED lights up.

- 2) During SYSRESET, HALT LED is red.

- After SYSRESET goes inactive, the HALT LED turns green and the red SYSFAIL LED turns on. At this time the SYSFAIL signal on the VMEbus is also activated.

- 4) The onboard firmware starts execution of the onboard selftest, which takes about 30 seconds. The status information that is given on the front panel LEDs S1-S4 is described in Chapter 2.2.

- 5) When the selftest is complete and if no errors have occurred, the SYSFAIL LED turns off and the SYS68K/ISCSI-1 is ready for operation.

If any errors are detected during selftest, the LED S4 turns on and the LEDs S1-S3 show an error code. Please refer to the Software User's Manual for details.

#### 2.2 The SYS68K/ISCSI-1 On-Board Selftest

On power-up or reset, the SYS68K/ISCSI-1 selftest routine is executed in the following manner:

- Test of SCSI controller by write and read back several registers.

- Start SCSI controller self-diagnostic.

- Test the whole local and dual ported memory with read and write bytes, words and long words.

- DMA Controller test with high speed data transfer memory to memory.

- Test the floppy disk controller.

The control of the selftest state and results is provided via the front panel LEDs Sl to S4:

- LED Sl is turned on during the RAM test.

- LED S2 is turned on during the SCSIbus controller test.

- LED S3 is turned on during the floppy disk controller test.

- LED S4 is turned on during the DMA Controller test.

If any error has been found while selftest was active, the LED of the test phase which has generated the error will stay on. After the selftest has been successfully completed, all LEDs are turned off.

Example: After completion of the selftest routine, the LED S3 remains on. This state indicates a hardware error on the WD1772 Floppy Disk Controller.

## HARDWARE USER'S MANUAL

### Table of Contents

| 1.0 | General Informationl-1                  |

|-----|-----------------------------------------|

| 2.Ø | General Operation2-1                    |

| 3.Ø | Functional Groups of the SYS68K/ISCSI-1 |

| 4.0 | The Local CPU Hardware                  |

| 5.0 | The SCSIbus Description                 |

| 6.0 | The | VMEbus Interface Hardware6-1                  |

|-----|-----|-----------------------------------------------|

|     | 6.1 | VMEbus Access to the Board                    |

|     |     | 6.1.1 The Address Modifier Code Selection     |

|     |     | 6.1.2 The Board Base Address Selection        |

|     |     | 6.1.3 The Run/Local Switch                    |

|     |     | 6.1.4 The Access LED                          |

|     | 6.2 | The Address Map of the VME Address Range6-7   |

|     | 6.3 | The Dual Ported RAM (DPR) as VMEbus Memory6-8 |

|     | 6.4 | The Reset Trigger Call                        |

|     | 6.5 | The Interrupt Trigger Call                    |

|     | 6.6 | The Bus Interrupter Module                    |

|     | 6.7 | •                                             |

|     |     |                                               |

## List of Figures

| Figure 1-1                                           | Photo of the SYS68K/ISCSI-1 Board1-Ø                                                     |

|------------------------------------------------------|------------------------------------------------------------------------------------------|

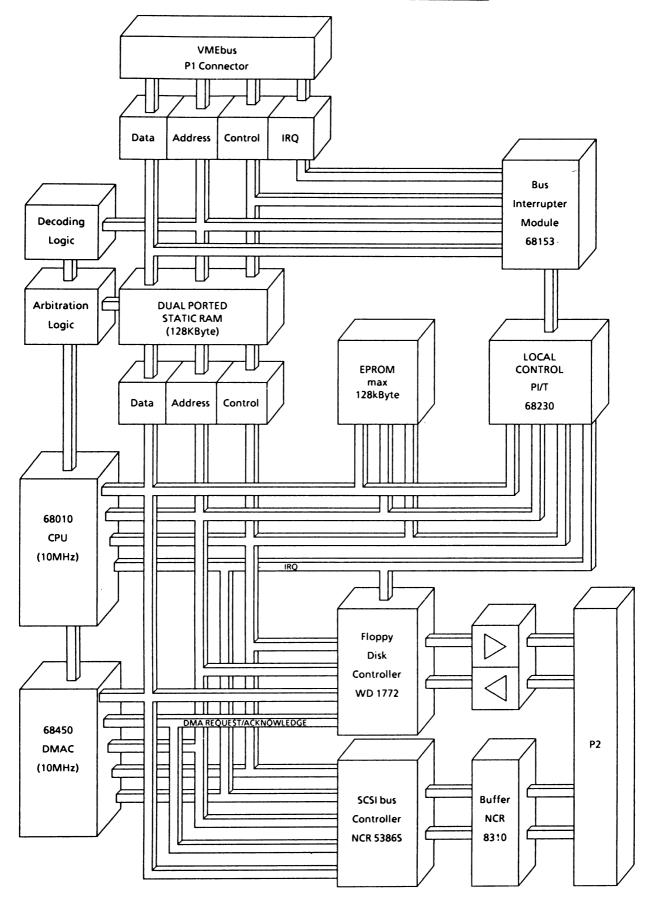

| Figure 2-1                                           | Block Diagram of the SYS68K/ISCSI-12-Ø                                                   |

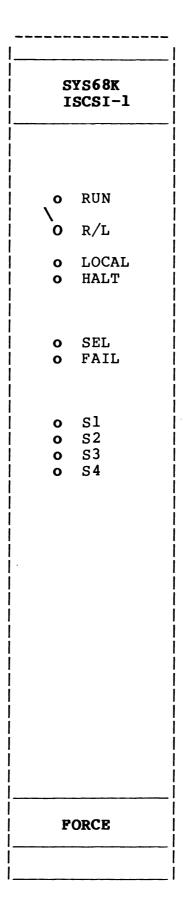

| Figure 3-1                                           | The Front Panel of the SYS68K/ISCSI-13-3                                                 |

| Figure 4-1<br>Figure 4-2                             |                                                                                          |

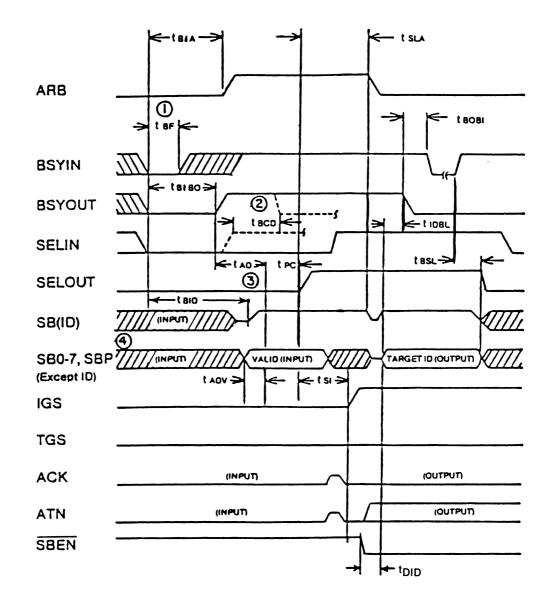

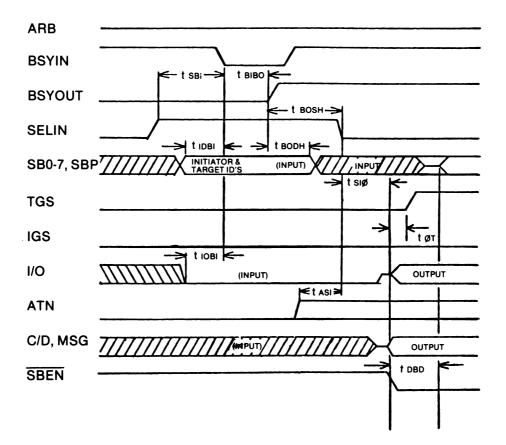

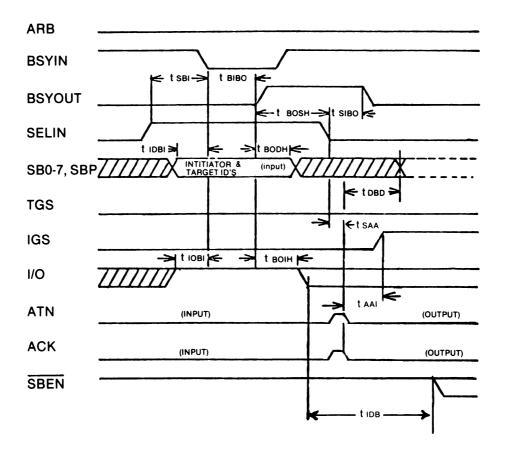

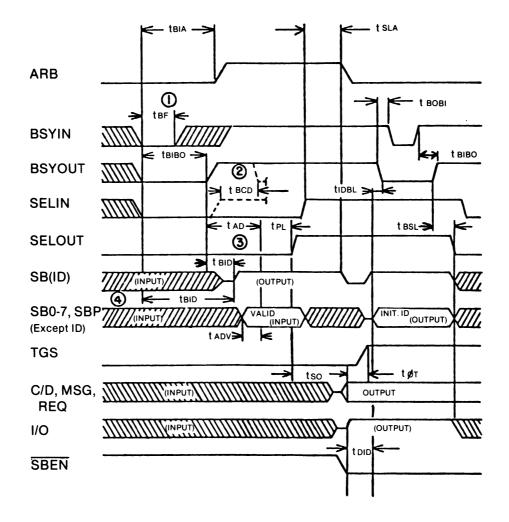

| Figure 5-1<br>Figure 5-2<br>Figure 5-3<br>Figure 5-4 | SCSI I.D. Bits                                                                           |

| Figure 6-1<br>Figure 6-2                             | Location Diagram of the Jumperfield B226-3<br>Location Diagram of the Jumperfield B216-5 |

## <u>List of Tables</u>

| Table 4-1 | The PI/T Address Map4-7                   |

|-----------|-------------------------------------------|

| Table 4-2 | Register Model of the DMAC4-14            |

| Table 4-3 | SCSIBC NCR 5386S Register Address Map4-20 |

| Table 4-4 | FDC WD 1772 Register Address Map          |

| Table 4-5 | The ISCSI-1 P2 Pin Assignment             |

| Table 4-6 | The ISCSI-1BPS X1 Pin Assignment          |

| Table 4-7 | The ISCSI-1BPS X2 Pin Assignment          |

|           | · -                                       |

#### 1.Ø General Information

The SYS68K/ISCSI-1 is a high performance intelligent SCSIbus controller board which fully supports the SCSI standard.

Up to 4 floppy drives can be controlled locally, without using the SCSIbus.

The board provides local intelligence with a 68010 CPU, 68450 DMAC, SCSIbus Controller (SCSIBC) and Floppy Disk Controller (FDC). A 128Kbyte Dual Ported RAM (DPR) is used to store data, and to interface the SYS68K/ISCSI-1 board. Highest throughput is guaranteed by using a 10MHz 68450 DMAC and the NCR 5386S SCSIBC.

On a single ended SCSIbus, the board works under the powerful firmware (128Kbyte EPROM area) as initiator or as target.

The SYS68K/SCSI-1's own SCSIbus I.D. is software controlled.

Four floppy drives are fully firmware supported and can also be accessed via the SCSIbus in the target mode.

The SYS68K/ISCSI-1 contains a VMEbus Rev.C/IEEE Pl014 compatible interface to communicate to the host CPUs via its 128Kbyte DPR. The access address and the Address Modifier code are jumper selectable. A Bus Interrupter Module (BIM 68153) is installed on the board to support fully asynchronous operation with the 4 different software programmable interrupt request channels.

The firmware of the SYS68K/ISCSI-l described in the Firmware User's Manual handles all activities to/from the SCSIbus and the floppy interface. For special applications, the source code of the firmware is optionally available.

### Figure 1-1: Photo of the SYS68K/ISCSI-1

2-Ø

#### 2.0 General Operation

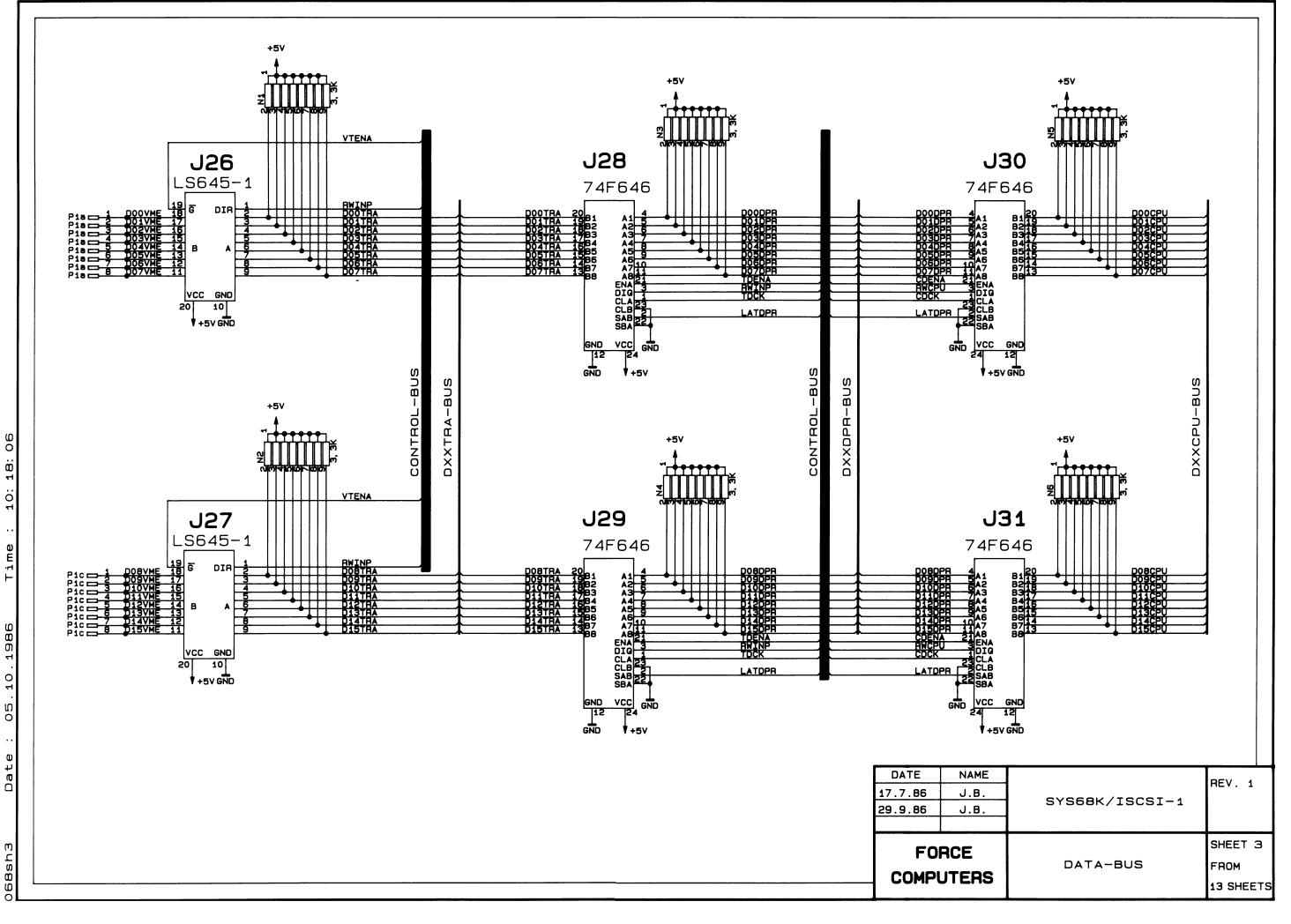

The SYS68K/ISCSI-1 is an intelligent VMEbus controller board providing an SCSIbus interface and a floppy disk interface.

The SYS68K/ISCSI-1 board includes 48mA drivers and receivers for the on-board terminated single ended SCSIbus and SHUGART compatible floppy interface. The buffered I/O signals are routed to the P2 backplane connector.

The NCR 5386S SCSIbus Controller supports the asynchronous and synchronous data transfer via the SCSIbus.

The WD 1772 floppy disk controller/formatter provides control of a maximum of four floppy disk drives (3", 3 1/2", 5 1/4").

The 68010 CPU chip, running at 10MHz, executes local software performing the intelligent I/O functions. The local I/O devices can be directly accessed by the CPU. A 68230 PI/T is installed for local control and timer functions.

The four channel 68450 Direct Memory Access Controller (DMAC) controls the high speed I/O data transfer.

The on-board SRAM is a Dual Ported RAM, which is accessible for the local CPU and DMAC and for the VMEbus master. The Dual Ported RAM (DPR) has 128Kbyte of wait-cycle-free memory space for the local CPU, as well as the medium of interface to the VMEbus master.

The SYS68K/ISCSI-1 board includes the function of an interrupter to the VMEbus. Up to four interrupts can be operated independent from each other.

The SYSFAIL\* signal of the VMEbus is supported, and status readout and a restart call are included in the hardware.

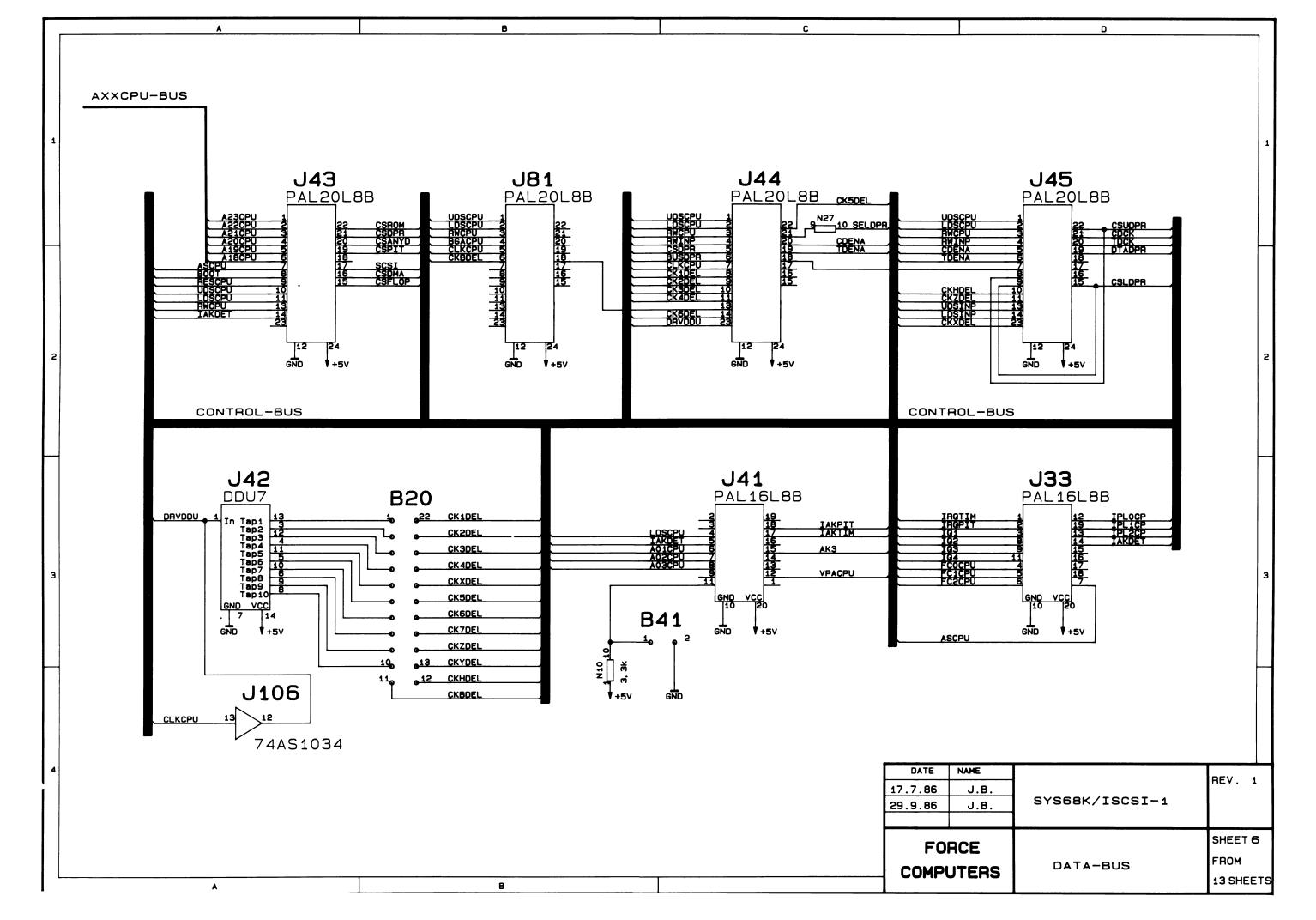

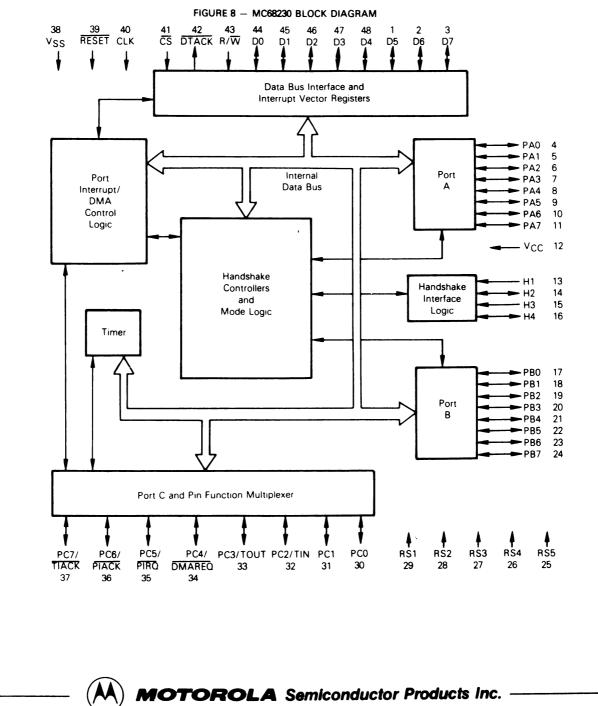

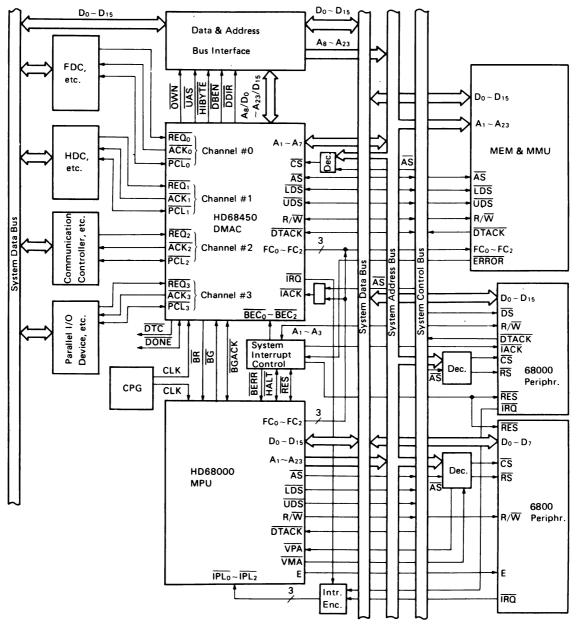

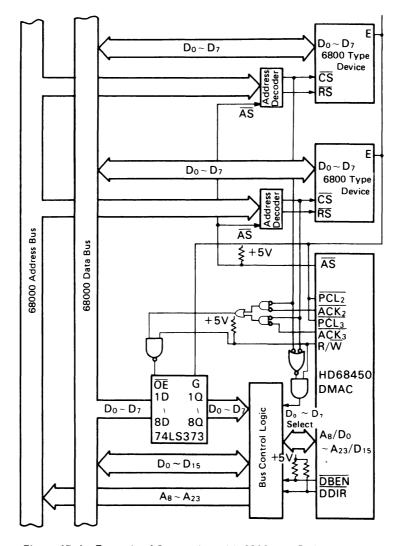

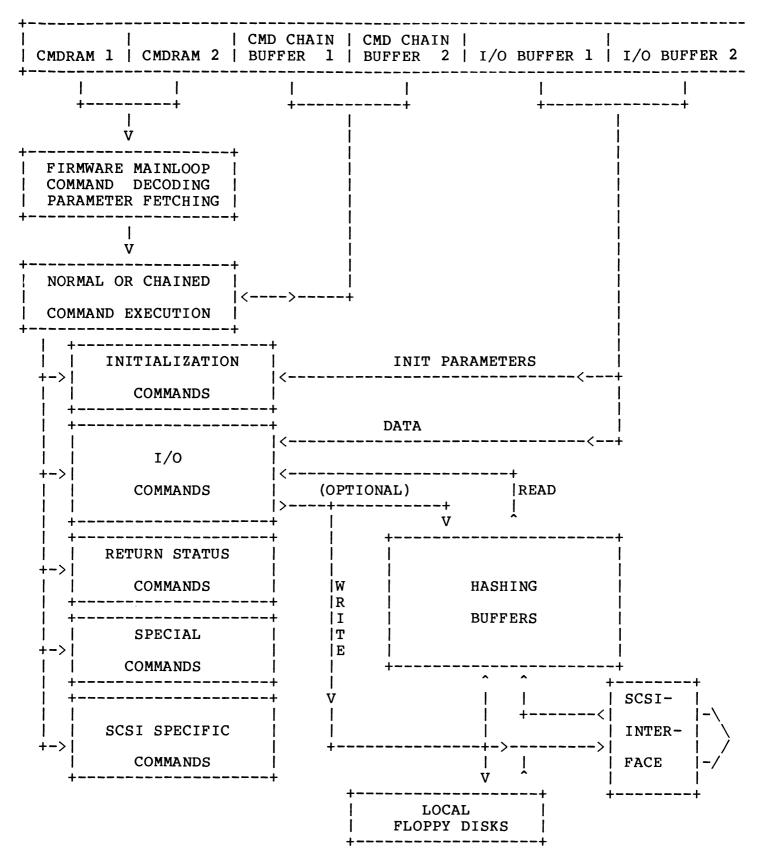

The general block diagram of the SYS68K/ISCSI-1 is shown in Figure 2-1.

#### 3.0 Functional Groups of the SYS68K/ISCSI-1

The SYS68K/ISCSI-1 consists of the following functional groups: The 68010 CPU with ROM The 68454 DMAC Local control and decoding The SCSIbus interface The floppy disk interface VMEbus interface and decoding Dual Ported RAM (DPR) Bus Interrupter Module with status register Reset and interrupt trigger call The watchdog timer Interrupt generator

The detailed description has been organised in two chapters: the local CPU hardware is described in Chapter 4 and the VMEbus interface is described in Chapter 5.

The description of the front panel and the P2 connector is as follows:

The SYS68K/ISCSI-1 is delivered with a front panel which also includes lever handles.

There is a RUN/LOCAL switch with LED indicators in the top position. When the switch is down, the board can be accessed on the VMEbus and the green RUN LED indicates this state. When the RUN/LOCAL switch is up, the board cannot be accessed from the VMEbus. In this situation the red LED, labelled LOCAL, lights up. The RUN and LOCAL LEDs can only light up one at a time.

The bi-colour LED with the label HALT will show a green light during the normal operation of the local CPU. It turns to red when the local CPU is in the HALT state and also during the RESET of the board.

The yellow LED, labelled SEL for select, lights up each time the SYS68K/ISCSI-l board is accessed from the VMEbus during data cycles and interrupt acknowledge cycles of the VMEbus.

The yellow FAIL indicator LED reflects the state of the on-board watch-dog timer and blinks during the high-speed DMAC SCSIbus transfers. If the FAIL LED lights up for more that 2 seconds, this means that the watch-dog timer has run out of time.

The yellow status LEDs labelled, S1 - S4, are controlled by the local PI/T device and are fully software controlled. These LEDs are all turned off at the RESET of the board.

Figure 3-1 shows the front panel of the SYS68K/ISCSI-1 with the switches and LEDs.

#### 3.2 The I/O Connector

The VMEbus definition of the Double Eurocard form factor includes two 96 pin bus connectors.

The Pl connector is the primary VMEbus interface. The P2 connector carries the extension bus signals and power supply connections via the b row. Rows a and c are for user I/O signals.

The SYS68K/ISCSI-1 board supplies buffered SCSI and floppy disk interface via the P2 connector. There are 25 pins providing the floppy disk I/O signals. 10 pins of the P2 connector are reserved for later applications.

The detailed pin-out is shown in section 4.8.

3-3

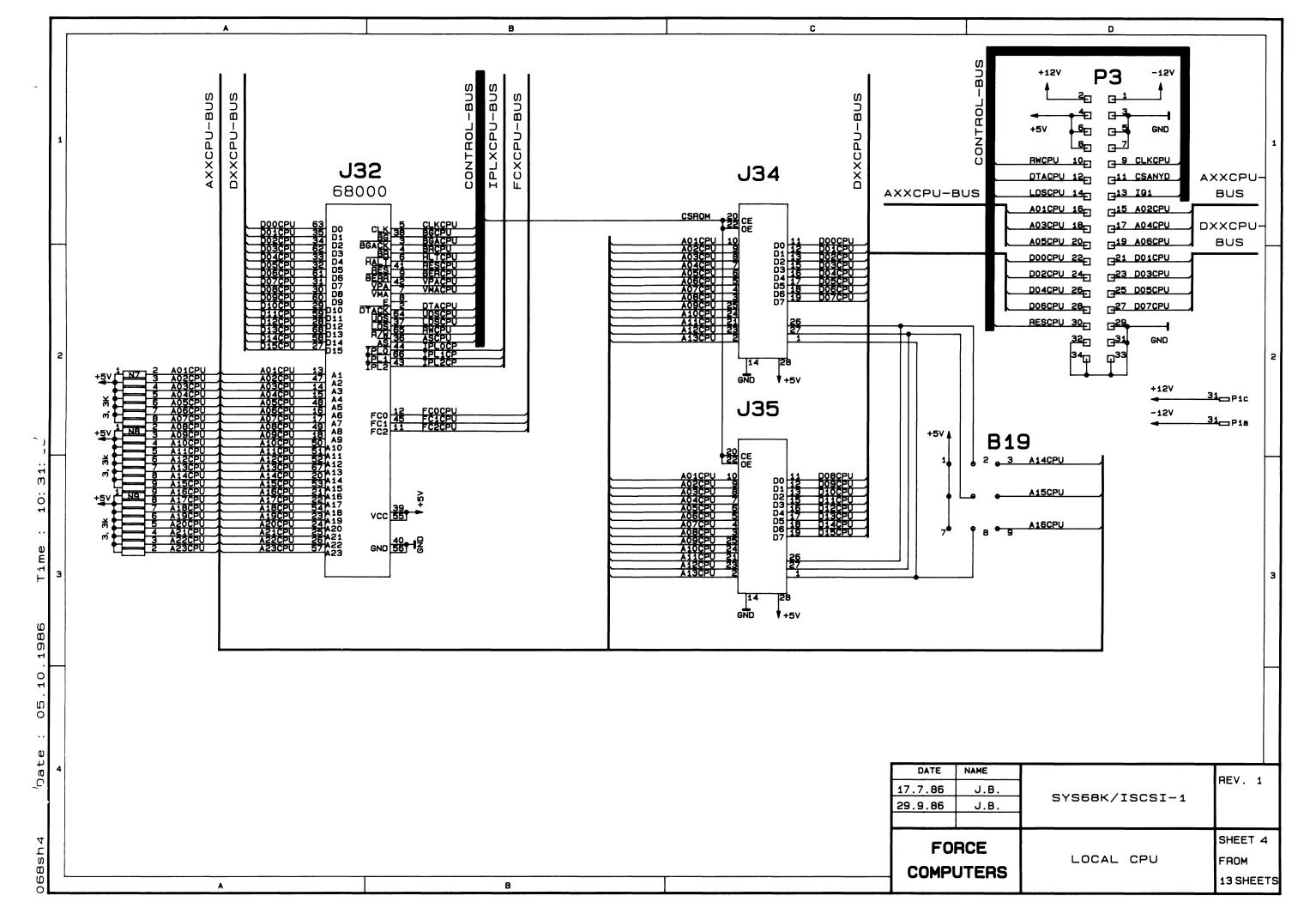

There is a 68010 microprocessor clocked at 10MHz working on the SYS68K/ISCSI-1.

The local CPU chip has an address and data bus totally independent of the VMEbus.

The local structure includes:

- Address decoding

- Reset driving

- Boot-up support

- Interrupt logic

- Bus error time-out control

- The DMAC (68450)

- The EPROMs

- The PI/T (68230)

- The SCSIbus Controller (5386S)

- The FDC (1772)

- The read back register for floppy disk control

- Access to the Dual Ported RAM

#### 4.1 Implementation of the Local Processor 68010

The local structure is built around the microprocessor 68010 which is fast enough to control the SCSIbus, the floppy disk interface and to handle data conversion and transport commands.

The 68010 works at a clock rate of 10MHz, therefore no wait cycles are needed if the Dual Ported RAM or the EPROM are accessed by the processor. This gives maximum yield of the processors power.

The following subchapters describe:

- Reset and bootup

- Decoding

- Interrupt structure

- Bus error

#### 4.1.1 Reset and Bootup of the Local CPU

The local CPU hardware can be reset in two different ways.

If the SYSRESET\* signal of the VMEbus is asserted, then the local CPU as well as the local peripheral devices and the VMEbus interface will be reset.

If a byte Read access is performed to the reset trigger address, then the local CPU and the local peripheral devices will be reset. The reset trigger address is \$1801 + board base address. Default is: A01801.

For boot-up, upon reset (or restart), the decoding logic is changed, so that the local EPROMs will be selected instead of the RAM. The first Write cycle of the local CPU introduces normal address decoding.

#### 4.1.2 Decoding of the Local Address Space

The local decoding structure is fixed. The address map is as follows: \$000000 -\$Ø1FFFF read/write Dual Ported RAM \$C40000 \$C4001F byte only SCSIbus controller -\$C80000 \$C8ØØFF read/write -DMAC \$CCØØØØ -\$CCØØØ7 odd byte only FDC \$CCØØØ9 -\$CCØØØ9 odd byte only Control register \$DØØØØØ \$DØØØ3F odd byte only PIT -\$EØØØØØ - \$E7FFFF read only EPROMs

### 4.1.3 The Local Interrupt Structure

| <br>  IRQ Level | <br>  IRQ Source    | Vector<br>if B41 inserted |                          |

|-----------------|---------------------|---------------------------|--------------------------|

| 1               | <br>  P3 Pin #13    | AV1 Autovector            | AV1 Autovector           |

| 2               | DMAC                | DMAC                      | AV2 Autovector           |

| 3               | SCSIBC              | AV3 Autovector            | AV3 Autovector           |

| 4               | FDC                 | AV4 Autovector            | AV4 Autovector           |

| 5               | <br>  PI/T Timer    | 1                         | PI/T Timer               |

| 6               |                     | Vector Reg.<br>           | Vector Reg.<br>          |

| 7               | <br>  PI/T Port<br> | PI/T Port<br>Vector Reg.  | PI/T Port<br>Vector Reg. |

The local interrupt structure is organized as follows:

Default configuration: B4l jumper removed.

The PI/T port interrupt can be used under software control to cause non-maskable (Level 7) interrupts if the watchdog timer elapses and/or if the VMEbus interrupt trigger call occurs.

### 4.1.4 The Local Bus Error Structure

There is a time-out counter installed to provide for bus error generation in the case of accessing non-decoded memory locations.

### 4.2 The EPROMs

The SYS68K/ISCSI-1 is delivered together with firmware, stored in two 27128 EPROMs. These EPROMs must have a maximum access time of 150ns. All EPROM access cycles are without wait states.

Other EPROM sizes are configurable by changes in the jumpering at B19.

The two EPROMs are stacked above each other, the lower byte (bits  $\emptyset$ -7) in the lower socket, the upper byte (bits 8-15) in the upper socket.

The base address of the EPROMs is \$E00000, and only read accesses are allowed.

The first two long locations in the EPROM pair must contain the boot-up information as follows:

E00 000 : Initial Supervisor Stack Pointer E00 004 : Initial Program Counter

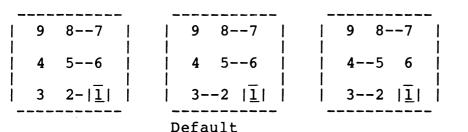

Configuration of the B19 jumper area:

2764

27128

27256

27512

Configuration

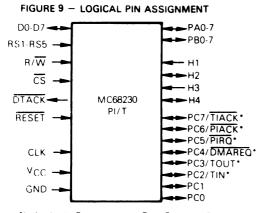

### 4.3 The Parallel Interface and Timer 68230 (PI/T)

There is a PI/T device installed for local control on the SYS68K/ISCSI-1.

The PI/T can be accessed only by the local CPU. The address range is D0001 to D0003F - odd byte only.

Table 4-1 gives the address map of the PI/T.

The following subchapters describe

- Control of the front panel LEDs

- Control of the SYSFAIL\* signal and the watchdog timer

- Control of the VMEbus interrupt requests

- The interrupt trigger input

- Reading the RUN/LOCAL switch

- Reading the B42 jumper selection

- The timer section of the PI/T

- The SCSIbus reset control

- The single or double floppy density selection

The PI/T port interrupt drives level 7 interrupts and the timer is connected to drive level 5 interrupts to the CPU. Both have to be configured (by software) to support interrupt vectors.

# Table 4-1: The PI/T Address Map

| Base Ad                              | ddress :             | \$D00000       |          |                                                       |

|--------------------------------------|----------------------|----------------|----------|-------------------------------------------------------|

| Address<br>HEX                       | Offset<br>           | Reset<br>Value | Label    | Description                                           |

| DØØØØ1                               | Ø1                   | 00             | PITPGCR  | Port General Control Register                         |

| DØØØØ3                               | 03                   | 00             | PITPSRR  | Port Service Request Register                         |

| DØØØØ5                               | Ø5                   | 00             | PITPADDR | Port A Data Direction Register                        |

| DØØØØ7                               | 07                   | 00             | PITPBDDR | Port B Data Direction Register                        |

| DØØØØ9                               | Ø9                   | 00             | PITPCDDR | Port C Data Direction Register                        |

| DØØØØB                               | ØB                   | ØF             | PITPIVR  | Port Interrupt Vector Register                        |

| DØØØØD                               | ØD                   | 00             | PITPACR  | Port A Control Register                               |

| DØØØØF                               | ØF                   | 00             | PITPBCR  | Port B Control Register                               |

| DØØØ11                               | 11                   |                | PITPADR  | Port A Data Register                                  |

| DØØØ13                               | 13                   |                | PITPBDR  | Port B Data Register                                  |

| DØØØ15                               | 15                   |                | PITPAAR  | Port A Alternate Register                             |

| DØØØ17                               | 17                   |                | PITPBAR  | Port B Alternate Register                             |

| DØØØ19                               | 19                   |                | PITPCDR  | Port C Data Register                                  |

| DØØØ1B                               | 1B                   |                | PITPSR   | Port Status Register                                  |

| DØØØ21                               | 21                   | 00             | PITTCR   | Timer Control Register                                |

| DØØØ23                               | 23                   | ØF             | PITTIVR  | Timer Interrupt Vector Reg.                           |

| DØØØ25<br>DØØØ27<br>DØØØ29<br>DØØØ2B | 25<br>27<br>29<br>28 | <br><br>       | PITCPR   | _<br>   Counter Preload Register<br>   <br>   <br>  _ |

| DØØØ2D<br>DØØØ2F<br>DØØØ31<br>DØØØ33 | 2D<br>2F<br>31<br>33 | <br><br><br>   | PITCNTR  | _<br>   Count Register<br>   <br>   <br> _            |

| DØØØ35                               | 35                   | 00             | PITTSR   | Timer Status Register                                 |

4-7

# 4.3.1 Control of the Front Panel LEDs S1-S4

There are four yellow LEDs, labelled Sl to S4, installed on the front panel of the SYS68K/ISCSI-1, that are driven by the PI/T device. These LEDs are fully under control of the local software which can write ls and Øs to the corresponding PI/T register bits.

| LED            | Controlled by                                |

|----------------|----------------------------------------------|

| S1<br>S2<br>S3 | Port B Bit Ø<br>Port B Bit 1<br>Port B Bit 2 |

| S4             | Port B Bit 3                                 |

For correct operation, Port B has to be programmed to operate in the bit I/O mode, and bits  $\emptyset$ , 1, 2 and 3 of the Port B data direction register have to be set (1).

When writing to the Port B data register, bits  $\emptyset$  to 3, a zero causes the light to turn on, and a one causes it to turn off.

#### 4.3.2 Control of the SYSFAIL\* Signal and the Watchdog Timer

There is a watchdog timer installed on the SYS68K/ISCSI-1. This is a retriggerable multivibrator with a nominal pulse duration of 20 milliseconds. This device is included to give information should a system breakdown occur.

The output state of the watchdog timer is available on the H3 terminal of the PI/T. The watchdog timer trigger input is connected to the PC4 pin of the PI/T. The high to low transition is the trigger.

If the watchdog is not triggered for more than 20 milliseconds, then its output becomes low (0). Triggering at a rate which is high enough (i.e. every 10 milliseconds), means that the output of the watchdog timer can be kept high (1). In case of a system breakdown, this retrigger does not occur any more, and the watchdog timer becomes low (0).

It is possible to use the H3 terminal of the PI/T not only to read, but also to use as an interrupt input (level 7 to the CPU). This gives an option for system recovery as long as the CPU does not go to HALT.

The SYSFAIL\* signal of the VMEbus can be used to broadcast the fact that a board is not functioning because of boot-up, selftest or failure. This signal will not be driven by the ISCSI-1 while SYSRESET\* is active. As soon as SYSRESET\* is released, SYSFAIL will be asserted (driven to low). This situation can only be changed by software controlled action of the local CPU.

Two output pins of the PI/T device control the SYSFAIL\* output: PCl and PC2. After RESET, both pins are driven high due to pullup resistors. The same is the case with both pins driven high (1) via software control.

If PCl is programmed to output low logic level ( $\emptyset$ ), then the SYSFAIL\* output to the VMEbus is released. With PCl = low, SYSFAIL\* is never active.

If PCl is high (1), and PC2 is programmed to output low ( $\emptyset$ ), then the SYSFAIL\* output will be asserted if the watchdog timer output is low ( $\emptyset$ ). This should be the runtime configuration. As long as the periodical toggle at the PI/T output pin PC4 occurs every 10 milliseconds, the watchdog timer output stays high (1), and SYSFAIL\* will not be asserted by ISCSI-1.

There is one more option:

The watchdog timer output can drive an interrupt request to the VMEbus via channel 3 of the BIM device. If pin PCØ of the PI/T is programmed to output low ( $\emptyset$ ), then the watchdog timer output is connected to set a flip-flop to drive an IRQ to channel 3 of the BIM. The flip-flop will be cleared by hardware during the interrupt acknowledge cycle. In this configuration, the PI/T output PA3 is not available for triggering this IRQ channel.

### 4.3.3 Control of the VMEbus Interrupt Requests

There is a Bus Interrupter Module 68153 (BIM) included in the SYS68K/ISCSI-1. This device is only accessible from the VMEbus (see chapter 6.6). So, the interrupt levels and vectors can only be programmed by VMEbus masters. The ISCSI-1 local software has no influence on this. The local software decides if and on which channel an interrupt request (IRQ) will be emitted. There are four channels to output an IRQ, while the BIM can distribute them to the seven IRQ level lines of the VMEbus.

The interrupt request signal must be released a very short time after it has been acknowledged. No software is fast enough to do that. Therefore, the IRQ outputs are handled in flip-flops that are asserted by software via a toggle from the flip-flop clock. The state of the four IRQ flip-flops can be read back by the local CPU. This is absolutely necessary, because a second IRQ can only be started to the same channel after the first has been acknowledged.

This affords some dynamic software handling by the local CPU. An IRQ asserted can only be cleared by the interrupt acknowledge cycle or by a SYSRESET\* from the VMEbus.

The four IRQ channels are associated and controlled by pins of the PI/T device as follows:

| BIM<br>Channel | Control  <br>  Reg  <br>  Address  <br> | Vector  <br>Reg  <br>Address  <br> | Toggle  <br>by  <br>PI/T  <br> | Readback of IRQ<br>Flip-Flop state<br>via PI/T |

|----------------|-----------------------------------------|------------------------------------|--------------------------------|------------------------------------------------|

| Ø              | <br>  \$A00001                          | <br>\$A00009                       | <br>PAØ                        | PA4                                            |

| 1              | <br>  \$A00003                          | \$A0000B                           | PA1                            | PA5                                            |

| 2              | <br>  \$A00005                          | \$A0000D                           | PA2                            | PA6                                            |

| 3              | <br>  \$A00007                          | <br>\$A0000F                       | PA3                            | PA7                                            |

VMEbus Default Address

The PI/T pins PAØ/PA3 have to be programmed to outputs, PA4/PA7 are inputs. Before writing to the Port A data direction register, \$FF has to be written to the Port A data register to avoid an unwanted output pulse.

### 4.3.4 The Interrupt Trigger Input

There is an option to trigger a level 7 interrupt to the local CPU from the VMEbus. To enable this option, the PI/T port interrupt (vectored) must be initialized by the local software.

The PI/T must be initialized so that a transition (low to high or high to low) on the Hl interrupt trigger input will cause an interrupt request. This interrupt request is of level 7, that is non-maskable. It must be the interrupt handler software that resets the interrupt. The VMEbus counterparts can be informed of the execution via the Dual Ported RAM or interrupt action via the BIM.

### 4.3.5 Reading the RUN/LOCAL Switch

The RUN/LOCAL switch controls whether or not the ISCSI-1 board can be accessed from the VMEbus. It would be of interest for the local software to distinguish this situation. The status of the RUN/LOCAL switch can be read by the local CPU via PI/T port PB6.

### 4.3.6 The Timer Section of the PI/T

The timer of the PI/T device is only of interest in the mode of a periodical interrupter. The timer interrupt has to be programmed so that the PI/T will support vectored interrupt acknowledge cycles.

The associated interrupt request level is level 5 of the CPU. This interrupt level is not subject to user configuration.

If the watchdog timer is used, it makes sense for the board to generate timer interrupts in the range of once every 5 to 10 milliseconds. The interrupt handler software should include some proof of correct system operation and finally the watchdog timer has to be triggered if the correct operation is stated.

The PI/T is clocked at a frequency of 8.0MHz.

### 4.3.7 The SCSIbus Reset Control

The SCSIbus reset is controlled via the PI/T port B bit #4 and #5. Bit #4 is programmed as an output, bit #5 as an input. To generate a reset on the SCSIbus it is necessary to clear (" $\emptyset$ ") bit #4 for at least 25 us and then set ("1") again. Bit #5 indicates the state of the SCSI reset.

### 4.3.8 The Single or Double Floppy Density Selection

The input of the floppy density selection, which selects either single (FM) or double (MFM) density is directly connected to port B bit #7 (programmed as an output). Bit #7 cleared ("0") selects double density, bit #7 set ("1") selects single density.

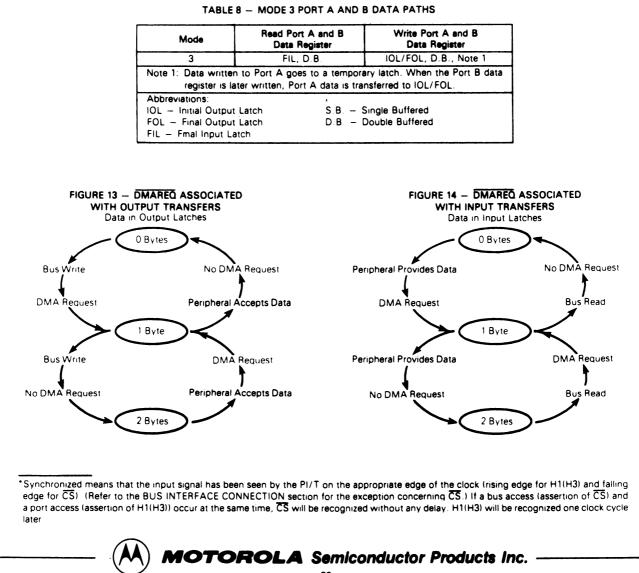

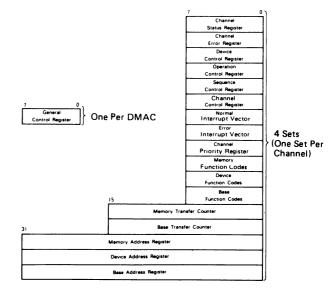

#### 4.4 The Direct Memory Access Controller 68450 (DMAC)

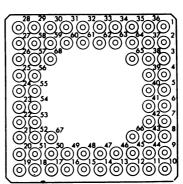

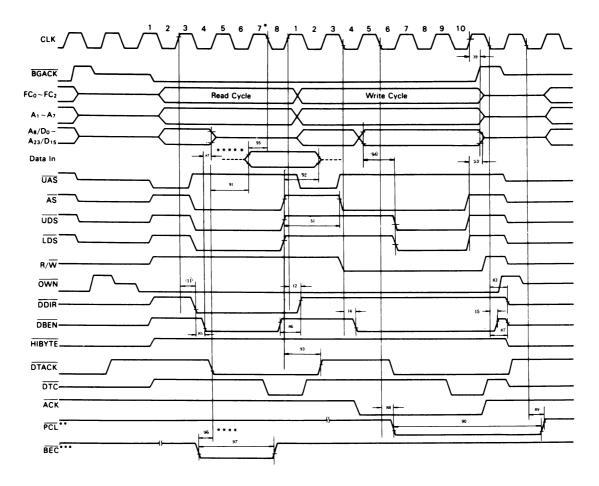

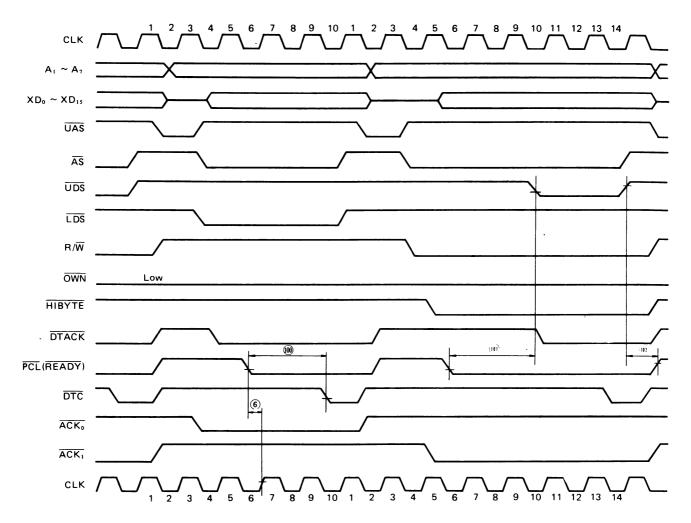

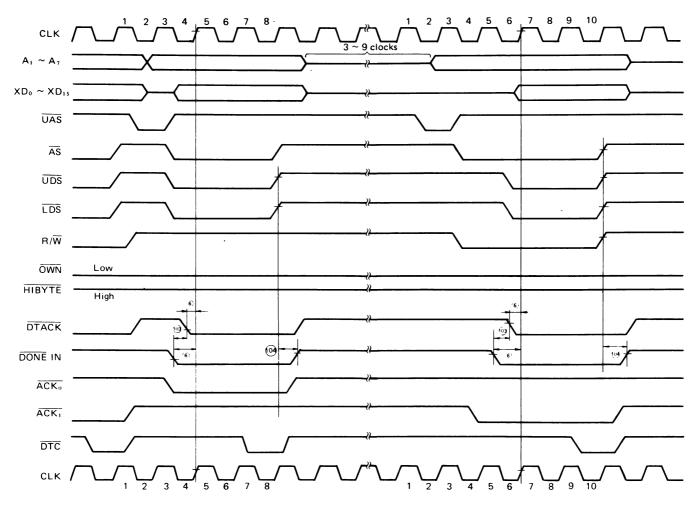

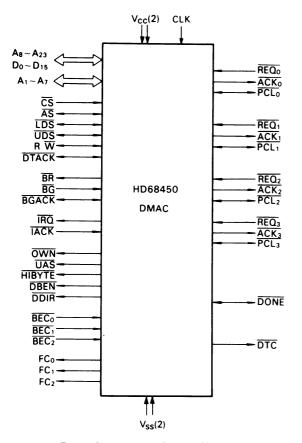

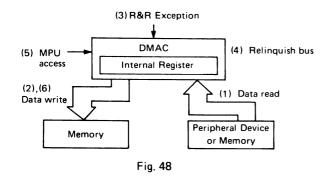

The SYS68K/ISCSI-1 board contains a 4-channel DMA Controller (68450) with a clock frequency of 10MHz. The 68450 offers a wide variety of programmable transfer options as described in the data sheet in Register 5, Chapter 5.

#### 4.4.1 The DMAC Implementation

The DMAC is an alternative bus master to the CPU, performing read/write cycles on-board.

The base address of the DMAC is \$C80000. Byte and word transfers are possible.

The DMAC can interrupt the CPU on IRQ level 2. If jumper B41 is inserted, the DMAC supports a vector which is the contents of one of the eight interrupt vector registers. If jumper B41 is removed, an autovector interrupt is generated. The autovector level is 2.

The DMAC, when master, can access all memory locations accessible to the CPU (except for the DMAC registers).

The DMAC can be requested by the SCSI controller or by the FDC. To provide high speed data transfer on the SCSIbus, the SCSI controller can also be accessed in the "Single Address Mode".

The data sheet of the 68450 DMAC is included in Register 5, Chapter 5.

### 4.4.2 Addressing of the DMAC

The DMAC can either be programmed in 8 or in 16-bit mode. The data bits DØ-D15 can be used for loading the DMAC.

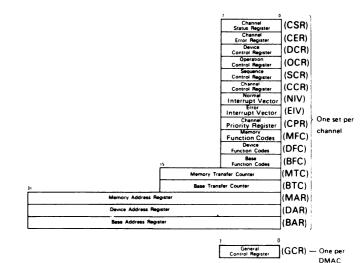

The register model of the DMAC is listed in Table 4-2.

| Base Address : \$C80000              |                      |                |                  |                                                                |  |  |  |

|--------------------------------------|----------------------|----------------|------------------|----------------------------------------------------------------|--|--|--|

| Address<br>HEX                       | Offset<br>           | Reset<br>Value | Label            | Description<br>                                                |  |  |  |

|                                      | CHANNEL Ø            |                |                  |                                                                |  |  |  |

| C80000<br>C80001                     | 00<br>01             | 01<br>00       | DMACSR<br>DMACER | Channel Status Register<br>  Channel Error Register (Read)<br> |  |  |  |

| C80004<br>C80005                     | Ø4<br>Ø5             | 00<br>00       | DMADCR<br>DMAOCR | Device Control Register<br>  Operation Control Register        |  |  |  |

| C80006<br>C80007                     | Ø6<br>Ø7             | 00<br>00       | DMASCR<br>DMACCR | <br>  Sequence Control Register<br>  Channel Control Register  |  |  |  |

| C8000A<br>C8000B                     | ØA<br>ØB             | <br>           | DMAMTC           | _<br>    Memory Transfer Counter<br> _                         |  |  |  |

| C8000C<br>C8000D<br>C8000E<br>C8000F | ØC<br>ØD<br>ØE<br>ØF | <br> <br> <br> | DMAMAR           | _<br>    Memory Address Register<br>   <br>                    |  |  |  |

| C80014<br>C80015<br>C80016<br>C80017 | 14<br>15<br>16<br>17 | <br><br>       | DMADAR           | _<br>    Device Address Register<br>   <br> _                  |  |  |  |

| C8001A<br>C8001B                     | lA<br>1B             |                | DMABTC           | _<br>    Base Transfer Counter<br> _                           |  |  |  |

| C8001C<br>C8001D<br>C8001E<br>C8001F | IC<br>ID<br>IE<br>IF | <br><br><br>   | DMABAR           | _<br>    Base Address Register<br>   <br> _                    |  |  |  |

| C80025                               | 25                   | ØF             | DMANIVR          | Normal Interrupt Vector                                        |  |  |  |

| C80027                               | 27                   | ØF             | DMAEIVR          | <br>  Error Interrupt Vector                                   |  |  |  |

| C80029                               | 29                   | Ø7             | DMAMFC           | Memory Function Codes                                          |  |  |  |

| C8002D                               | 2D                   | 00             | DMACPR           | <br>  Channel Priority Register                                |  |  |  |

| C80031                               | 31                   | Ø7             | DMADFC           | <br>  Device Function Codes                                    |  |  |  |

| C80039                               | 39                   | Ø7             | DMABFC           | <br>  Base Function Codes                                      |  |  |  |

# Table 4-2: Register Model of the DMAC

cont'd...

| Base Ad                              | ddress                           | \$C80000           |                    |                                                               |

|--------------------------------------|----------------------------------|--------------------|--------------------|---------------------------------------------------------------|

| Address<br>HEX                       | Offset<br>                       | Reset  <br>  Value | Label              | Description                                                   |

|                                      |                                  |                    |                    | CHANNEL 1                                                     |

| C80040<br>C80041                     | 40<br>  41                       | 01<br>00           | DMACSR1<br>DMACER1 | Channel Status Register<br>  Channel Error Register (Read)    |

| C80044<br>C80045                     | 44                               | 00<br>00           | DMADCR1<br>DMAOCR1 | Device Control Register<br>Operation Control Register         |

| C80046<br>C80047                     | 46<br>  47                       | 00<br>00           | DMASCR1<br>DMACCR1 | <br>  Sequence Control Register<br>  Channel Control Register |

| C8004A<br>C8004B                     | 4A<br>  4B                       |                    | DMAMTCl            | _<br>    Memory Transfer Counter<br> _                        |

| C8004C<br>C8004D<br>C8004E<br>C8004F | 4C<br>4D<br>4E<br>4F             | <br><br>           | DMAMAR1            | _<br>    Memory Address Register<br>   <br>                   |

| C80054<br>C80055<br>C30056<br>C80057 | <br>  54<br>  55<br>  56<br>  57 | <br><br><br>       | DMADAR1            | _ <br> _<br>    Device Address Register<br>   <br>            |

| C8005A<br>C8005B                     | <br>  5A<br>  5B                 |                    | DMABTC1            | _<br>    Base Transfer Counter<br> _                          |

| C8ØØ5C<br>C8ØØ5D<br>C8ØØ5E<br>C8ØØ5F | 5C<br>  5D<br>  5E<br>  5F       | <br><br>           | DMABAR1            | _<br>    Base Address Register<br>   <br> _                   |

| C80065                               | 65                               | ØF                 | DMANIVRl           | Normal Interrupt Vector                                       |

| C80067                               | 67                               | ØF                 | DMAEIVRl           | Error Interrupt Vector                                        |

| C80069                               | 69                               | Ø7                 | DMAMFC1            | Memory Function Codes                                         |

| C8006D                               | <br>  6D                         | ØØ                 | DMACPR1            | Channel Priority Register                                     |

| C80071                               | <br>  71                         | Ø7                 | DMADFC1            | Device Function Codes                                         |

| C8ØØ79                               | 79                               | 07                 | DMABFC1            | Base Function Codes                                           |

Table 4-2 cont'd 68450 DMAC Register Layout

cont'd...

| Base Address : \$C80000              |                            |                    |                    |                                                            |

|--------------------------------------|----------------------------|--------------------|--------------------|------------------------------------------------------------|

| Address<br>HEX                       | Offset<br>                 | Reset  <br>  Value | Label              | Description                                                |

|                                      |                            |                    |                    | CHANNEL 2                                                  |

| C80080<br>C80081                     | 8Ø<br>  81                 | 01<br>00           | DMACSR2<br>DMACER2 | Channel Status Register<br>  Channel Error Register (Read) |

| C80084<br>C80085                     | 84<br>85                   | 00<br>00           | DMADCR2<br>DMAOCR2 | Device Control Register<br>Operation Control Register      |

| C80086<br>C80087                     | 86<br>87                   | 00<br>00           | DMASCR2<br>DMACCR2 | Sequence Control Register<br>Channel Control Register      |

| C8008A<br>C8008B                     | 8A<br>8B                   |                    | DMAMTC2            | _<br>    Memory Transfer Counter<br> _                     |

| C8ØØ8C<br>C8ØØ8D<br>C8ØØ8E<br>C8ØØ8F | 8C<br>8D<br>8E<br>8F       | <br><br>           | DMAMAR2            | _<br>    Memory Address Register<br>   <br> _              |

| C80094<br>C80095<br>C&0096<br>C80097 | 94<br>  95<br>  96<br>  97 | <br><br>           | DMADAR2            | _<br>    Device Address Register<br>   <br> _              |

| C8009A<br>C8009B                     | 9A<br>9B                   |                    | DMABTC2            | _<br>    Base Transfer Counter<br> _                       |

| C8009C<br>C8009D<br>C8009E<br>C8009F | 9C<br>  9D<br>  9E<br>  9F | <br><br><br>       | DMABAR2            | _<br>    Base Address Register<br>   <br> _                |

| C800A5                               | A5                         | ØF                 | DMANIVR2           | Normal Interrupt Vector                                    |

| C800A7                               | A7                         | ØF                 | DMAEIVR2           | Error Interrupt Vector                                     |

| C800A9                               | <br>  A9                   | Ø7                 | DMAMFC2            | Memory Function Codes                                      |

| C800AD                               | AD                         | ØØ                 | DMACPR2            | <br>  Channel Priority Register                            |

| C800B1                               | <br>  Bl                   | 07                 | DMADFC2            | Device Function Codes                                      |

| С800в9                               | <br>  B9                   | 07                 | DMABFC2            | Base Function Codes                                        |

Table 4-2 cont'd 68450 DMAC Register Layout

cont'd...

| Base A                               | ddress                     | \$C80000         |                    |                                                               |

|--------------------------------------|----------------------------|------------------|--------------------|---------------------------------------------------------------|

| Address<br>HEX                       | Offset<br>                 | Reset  <br>Value | Label              | Description                                                   |

|                                      |                            |                  |                    | CHANNEL 3                                                     |

| C800C0<br>C800C1                     | CØ<br>  Cl                 | Ø1<br>  ØØ       | DMACSR3<br>DMACER3 | Channel Status Register<br>  Channel Error Register (Read)    |

| C800C4<br>C800C5                     | C4<br>C5                   | 00<br>00         | DMADCR3<br>DMAOCR3 | Device Control Register<br>  Operation Control Register       |

| C800C6<br>C800C7                     | C6<br>C7                   | 00<br>00         | DMASCR3<br>DMACCR3 | <br>  Sequence Control Register<br>  Channel Control Register |

| C800CA<br>C800CB                     | CA<br>CB                   | <br>             | DMAMTC3            | _<br>    Memory Transfer Counter<br> _                        |

| C800CC<br>C800CD<br>C800CE<br>C800CF | CC<br>CD<br>CE<br>CF       | <br><br>         | DMAMAR3            | _<br>    Memory Address Register<br>   <br> _                 |

| C800D4<br>C800D5<br>C800D6<br>C800D7 | D4<br>  D5<br>  D6<br>  D7 | <br><br>         | DMADAR3            | _<br>    Device Address Register<br>   <br> _                 |

| C800DA<br>C800DB                     | DA<br>DB                   |                  | DMABTC3            | _<br>    Base Transfer Counter<br> _                          |

| C800DC<br>C800DD<br>C800DE<br>C800DF | DC<br>DD<br>DE<br>DF       | <br><br>         | DMABAR3            | _<br>    Base Address Register<br>   <br> _                   |

| C800E5                               | E5                         | ØF               | DMANIVR3           | <br>  Normal Interrupt Vector                                 |

| C800E7                               | Е7                         | ØF               | DMAEIVR3           | <br>  Error Interrupt Vector                                  |

| C800E9                               | E9                         | Ø7               | DMAMFC3            | <br>  Memory Function Codes<br>                               |

| C800ED                               | ED                         | ØØ               | DMACPR3            | <br>  Channel Priority Register                               |

| C800F1                               | Fl                         | Ø7               | DMADFC3            | <br>  Device Function Codes<br>                               |

| C800F9                               | F9                         | 07               | DMABFC3            | <br>  Base Function Codes                                     |

|                                      |                            |                  |                    | GLOBAL DEVICE CONTROL                                         |

| C800FF                               | FF                         | ØØ               | DMAGCR             | DMAC General Control Register                                 |

4-17

# Table 4-2 cont'd 68450 DMAC Register Layout

### 4.4.3 The DMAC Interrupt Scheme

The DMA Controller contains 8 interrupt vector registers which will be read during an interrupt acknowledge cycle of the CPU if jumper B41 is inserted; otherwise, an auto vector is forced.

# 4.4.4 The DMAC Summary

| Default Base Address :   | \$C80000                        |

|--------------------------|---------------------------------|

| Default Access Address : | \$C80000 - \$C800FF             |

| Access Mode :            | Byte and Word<br>Read and Write |

| Usable Data Bits :       | DØ-D7, D8-D15                   |

| Interrupt Level :        | IQ2                             |

| Interrupt Vector :       | Auto vectors/non-autovector     |

### 4.5 The SCSIbus Controller NCR 5386S (SCSIBC)

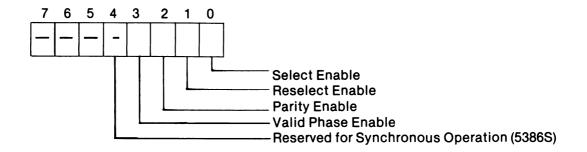

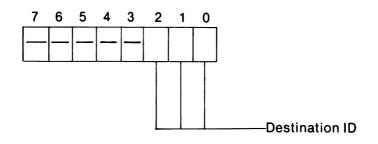

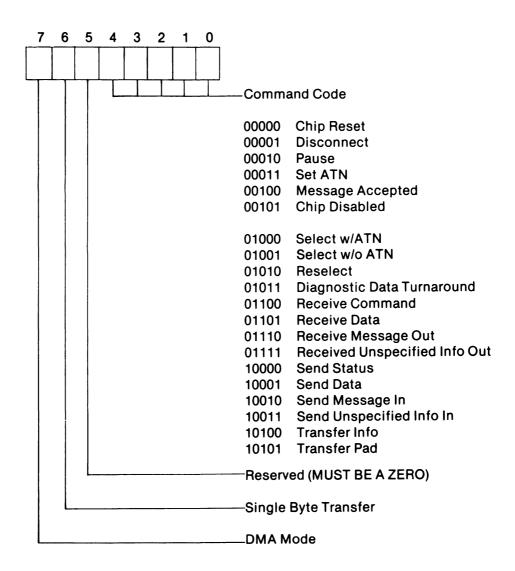

- The NCR 5386S SCSIbus Controller communicates with the 68010 CPU and the 68450 DMAC as a peripheral device. The SCSIBC is controlled by reading and writing several internal registers which are addressed via the local address bus.

- Since the SCSIBC interrupts the MPU when it detects a SCSIbus condition that requires servicing, the MPU is free from polling or controlling any of the SCSIbus signals.

- The SCSIBC will be programmed and controlled via the local CPU.

- The SCSIBC Interrupt is connected to the CPU interrupt level 3. The generated interrupt is always an auto vector interrupt.

- For high speed data transfer the SCSIBC communicate directly with the Dual Ported RAM under the DMAC control. In this mode the maximum data transfer rate will be 1.5Mbyte(s).

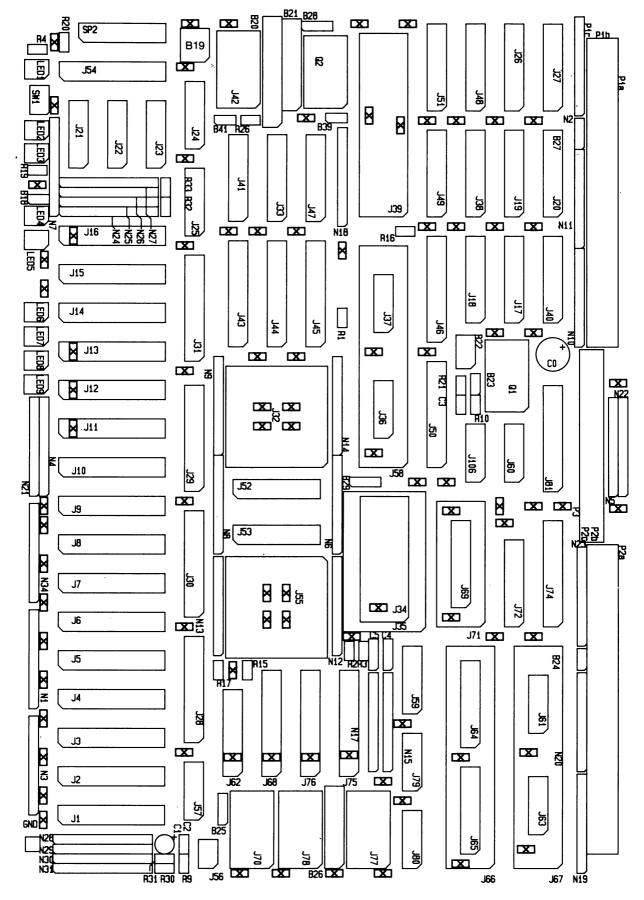

- The ISCSI-1's own SCSI I.D. is software programmable and is stored in the "Control Register" at the local address \$CC0009. For more information refer to section 4.7.

- The SCSIBC is connected to the SCSIbus via the SCSIbus driver/receiver chip NCR 8310.

- The data sheet of the SCSIBC is included in Register 5, Chapter 3.

|                                                                                                                      | Bas                                                                | e Addres                                   | s: \$C40                                                     | 000                                                                                                |                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                                                                                                              | Offset                                                             | Reset                                      | Mode                                                         | Label                                                                                              | Description                                                                                                                                                                                                                                                       |

| Hex                                                                                                                  |                                                                    | Value                                      |                                                              |                                                                                                    |                                                                                                                                                                                                                                                                   |

| \$C40001                                                                                                             | Ø1                                                                 |                                            | R/W                                                          | SDAT1                                                                                              | Data Register 1                                                                                                                                                                                                                                                   |

| \$C40003                                                                                                             | Ø3                                                                 |                                            | R/W                                                          | SCMDR                                                                                              | Command Register                                                                                                                                                                                                                                                  |

| \$C40005                                                                                                             | Ø5                                                                 |                                            | R/W                                                          | SCTRLR                                                                                             | Control Register                                                                                                                                                                                                                                                  |

| \$C40007                                                                                                             | Ø7                                                                 |                                            | R/W                                                          | SDID                                                                                               | Destination I.D.                                                                                                                                                                                                                                                  |