3,419,850

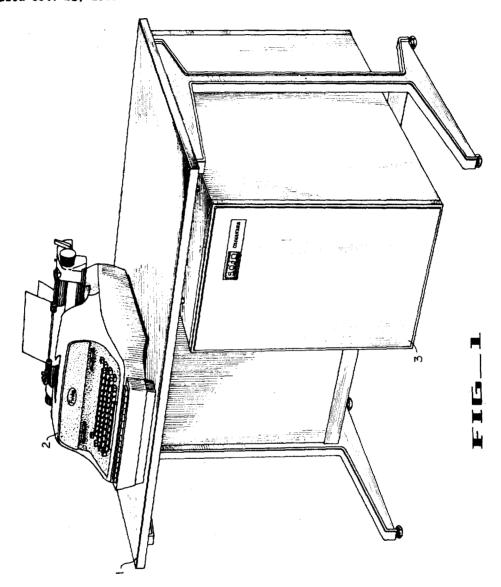

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

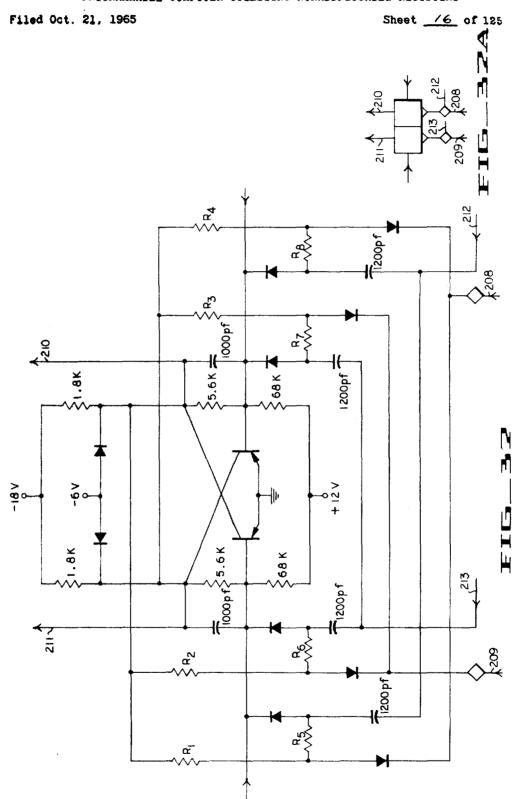

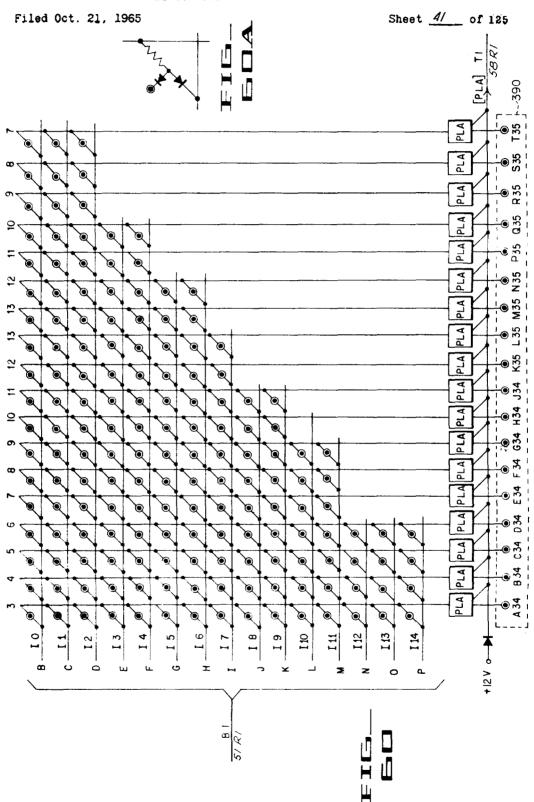

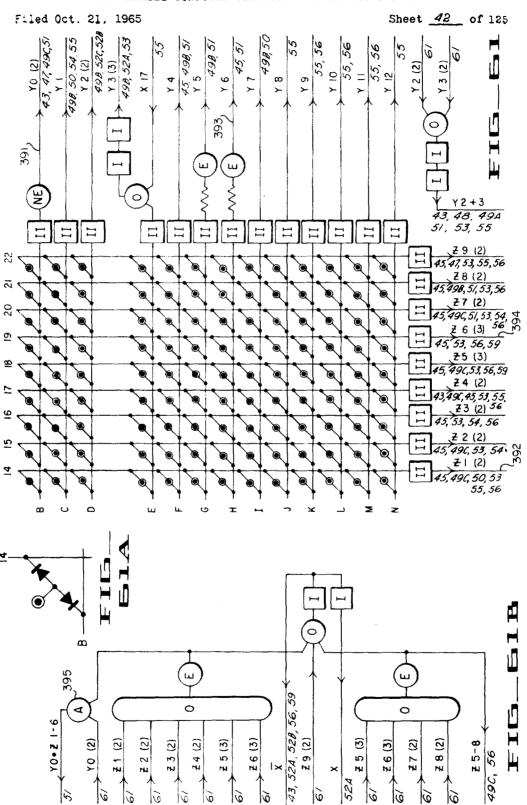

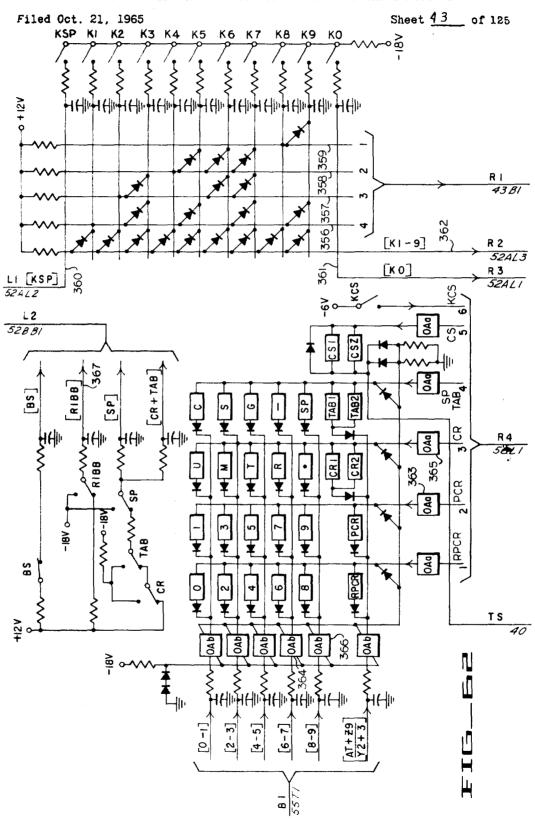

Filed Oct. 21, 1965

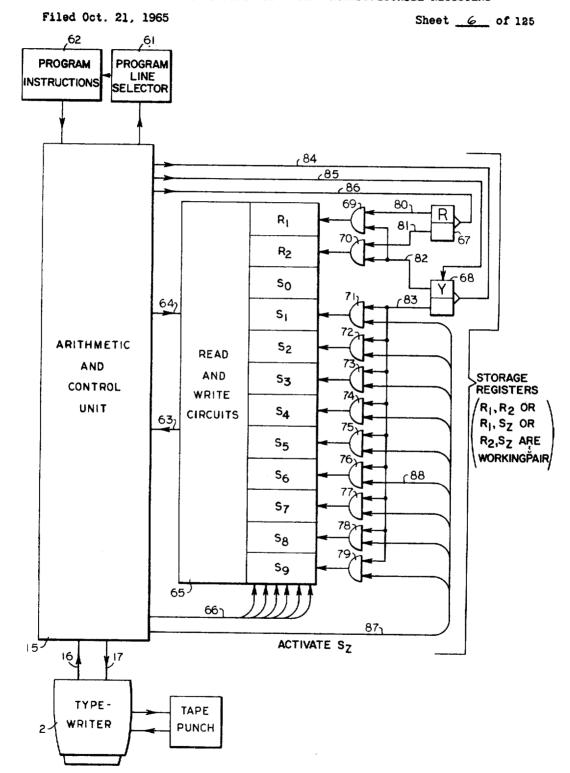

Sheet \_/\_ of 125

JAN KRAMMER INVENTOR

BY Charles R. Lepas ATTORNEY

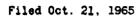

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>2</u> of 125

|                                           |                | NET COST    | 242.38                          | NET TOTAL<br>504.30                     |

|-------------------------------------------|----------------|-------------|---------------------------------|-----------------------------------------|

|                                           |                | DISCOUNT    | 9°%                             |                                         |

|                                           |                | GROSS AMT   | 287.82                          | GROSS TOTAL<br>542.97                   |

| RESHFIG MFG CO. SOLD TO: LANYTOWN LINGILM | SHIP TO: LSAME | DESCRIPTION | SCHTICK HOLDER<br>CARPETED BAGS |                                         |

|                                           |                | PRICE       | 5.67                            | 7 9 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 |

|                                           |                | QTY.        | 23<br>4 & &                     |                                         |

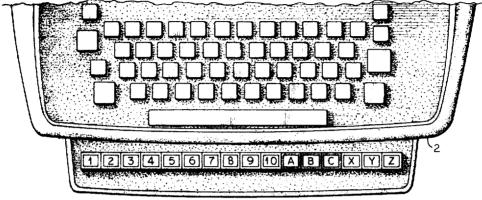

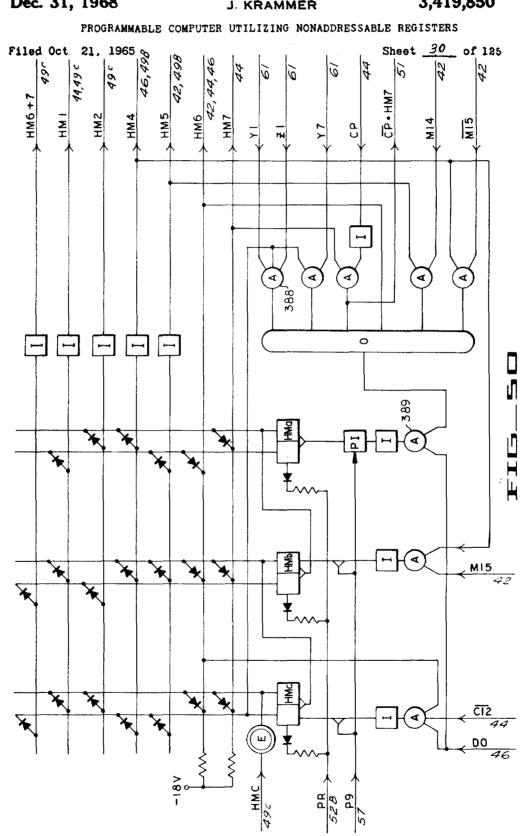

Dec. 31, 1968

J. KRAMMER

3,419,850

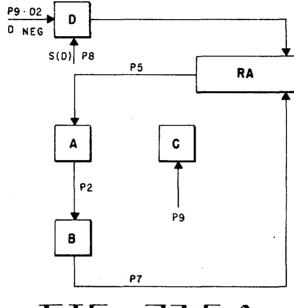

FIG.\_3

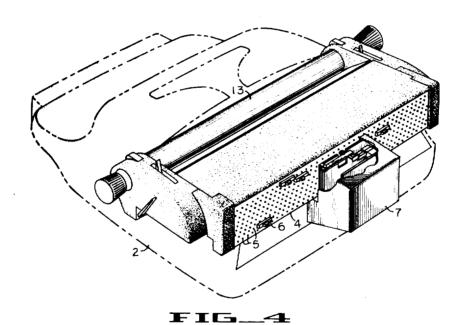

Filed Oct. 21, 1965

Sheet 4 of 125

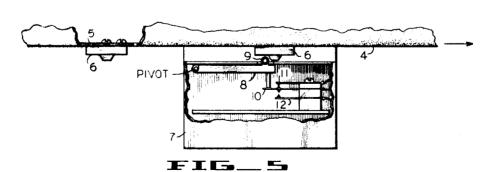

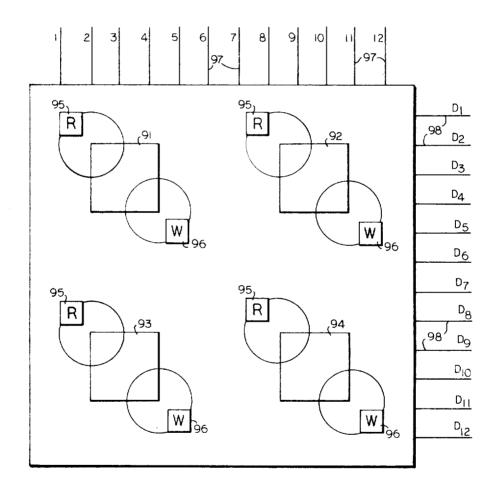

FIG\_6

Dec. 31, 1968

J. KRAMMER

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet \_ 5 of 125

3,419,850

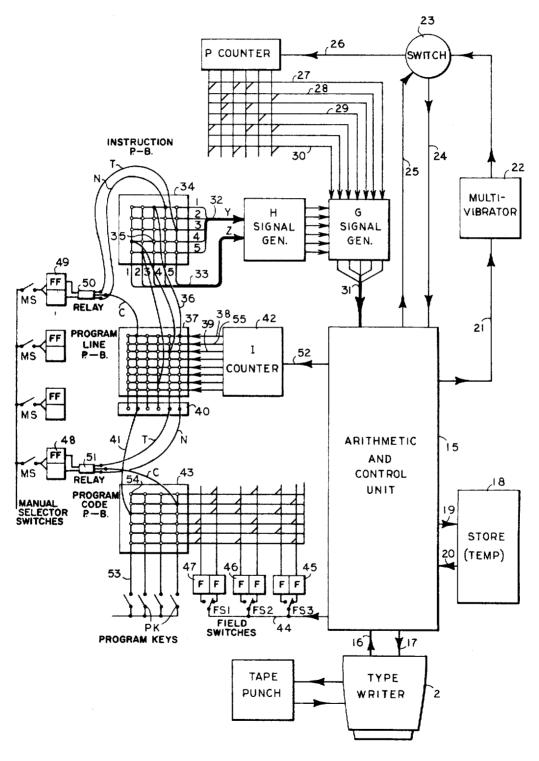

FIG\_A

Dec. 31, 1968

J. KRAMMER

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet \_7 of 125

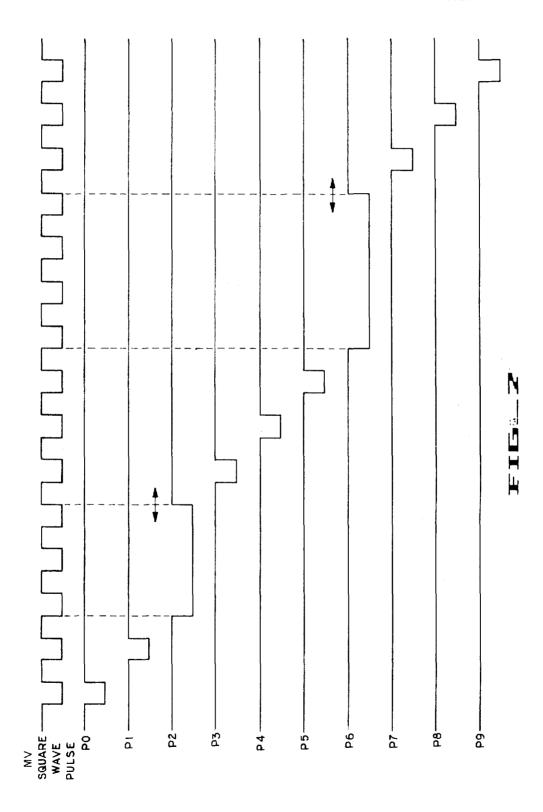

FIG\_9

Dec. 31, 1968

### J. KRAMMER

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>8</u> of 125

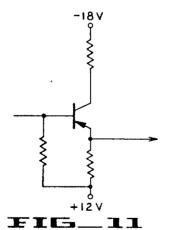

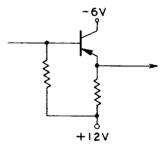

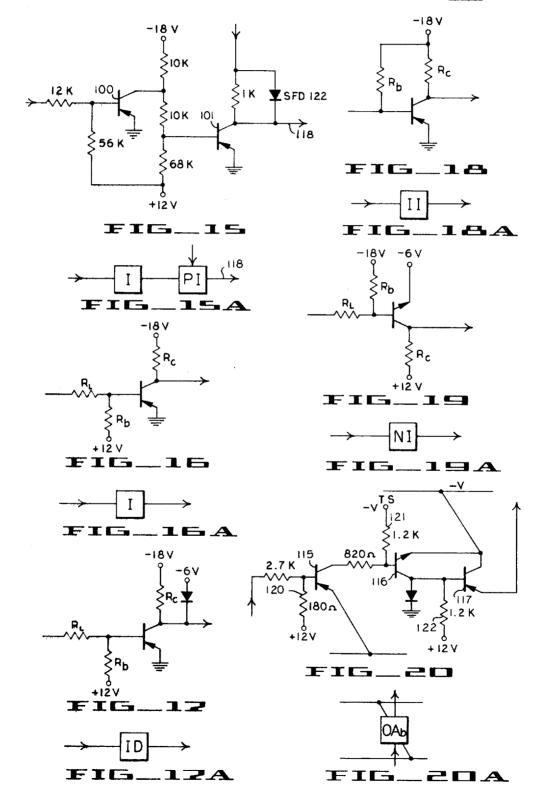

FIG\_12A

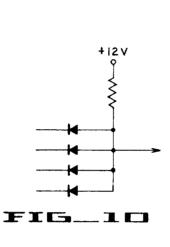

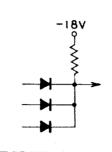

FIG\_10A

FIG\_13

FIG\_14

FIG\_11A

FIG\_14A

Filed Oct. 21, 1965

Sheet <u>9</u> of 125

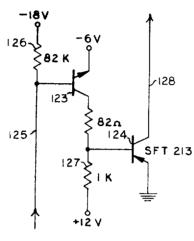

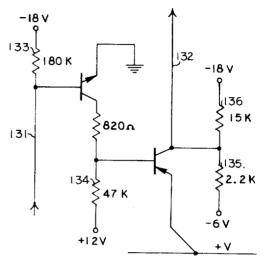

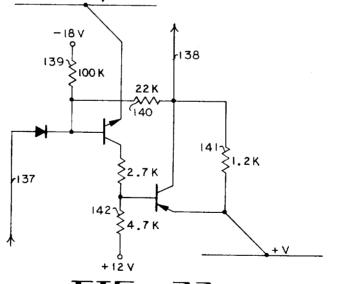

Filed Oct. 21, 1965

Sheet \_/O of 125

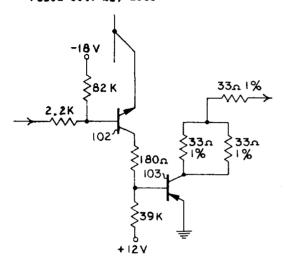

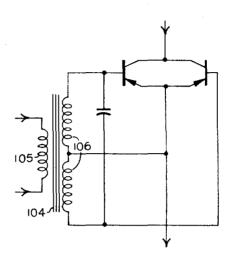

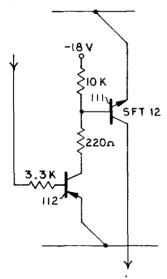

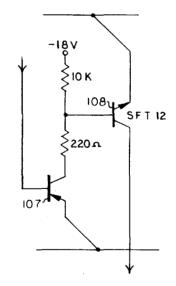

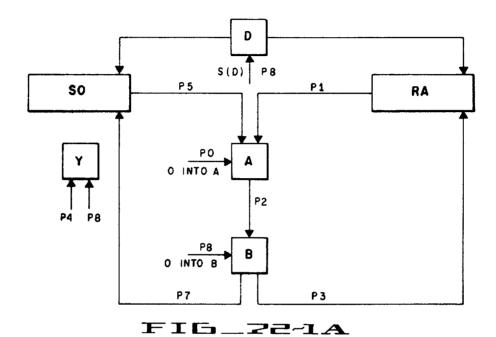

FIG\_\_21

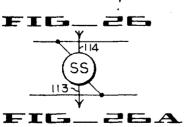

FIG\_22

ETE STA

FIG\_23A

Filed Oct. 21, 1965

Sheet \_// of 125

Dec. 31, 1968

### J. KRAMMER

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>/2</u> of 125

Filed Oct. 21, 1965

Sheet <u>/3</u> of 125

Dec. 31, 1968 J. KRAMMER

Filed Oct. 21, 1965

Sheet <u>/4</u> of 125

Filed Oct. 21, 1965

Sheet <u>/5</u> of 125

# J. KRAMMER

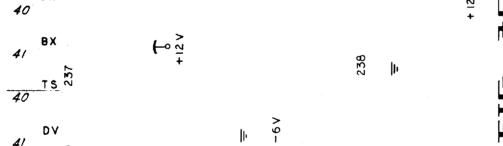

Filed Oct. 21, 1965

þ

Filed Oct. 21, 1965

Sheet <u>/8</u> of 125

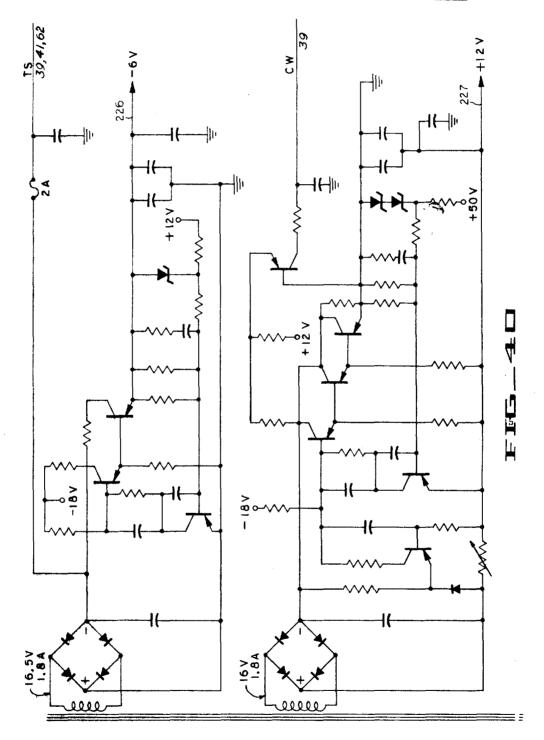

Filed Oct. 21, 1965

Sheet \_/9 of 125

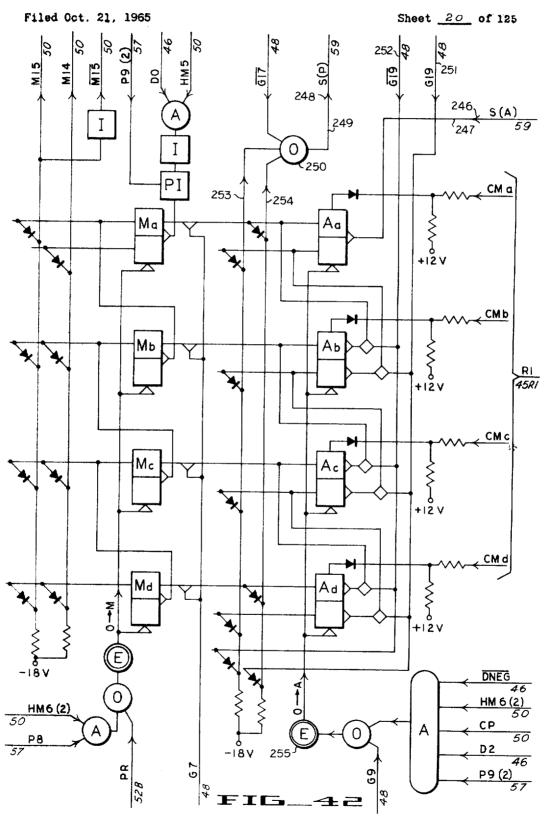

Filed Oct. 21, 1965

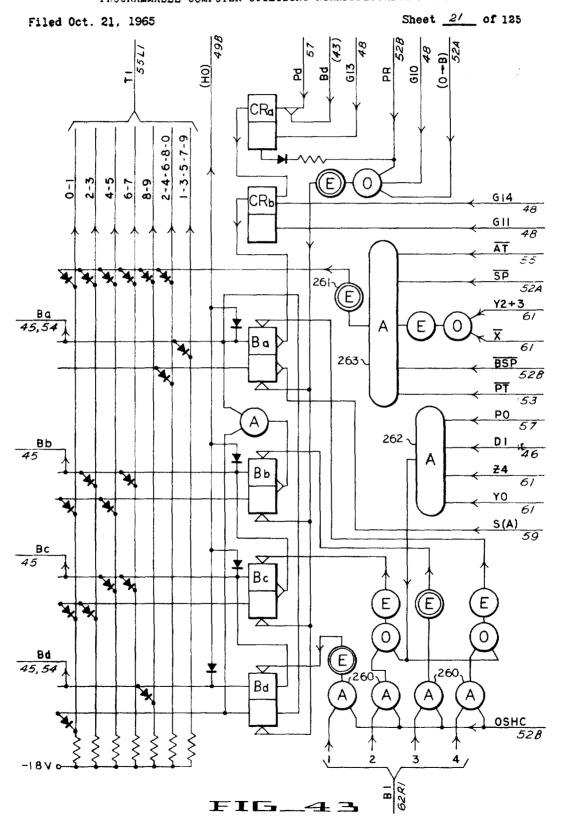

Sheet <u>22</u> of 125

FIG\_44

Dec. 31, 1968

#### J. KRAMMER

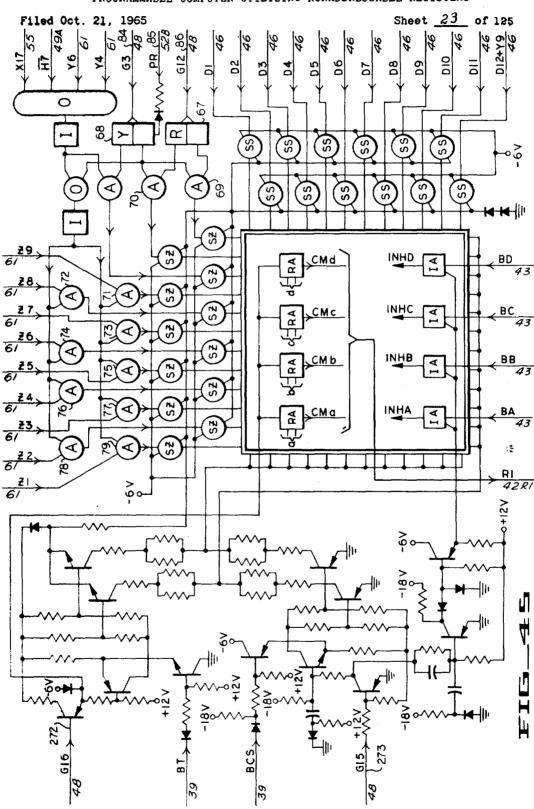

Filed Oct. 21, 1965 Sheet 25 of 125

Dec. 31, 1968

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965 Sheet <u>39</u> of 125 376 528 2×× 374 -18V LI [EPL·RPB] [PLA] RI F F C R 528 PS 528,54 -18Va 53 59 FIG

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

#### J. KRAMMER

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 44 of 125

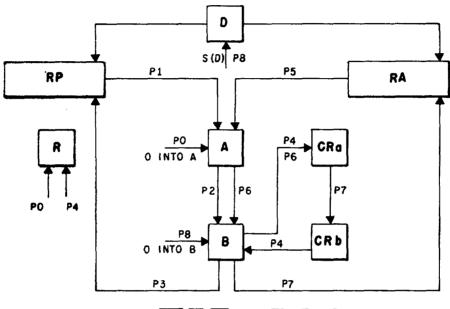

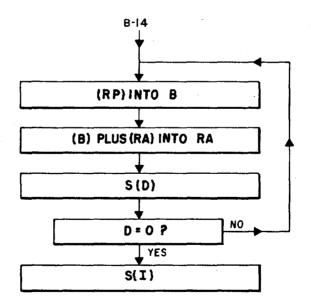

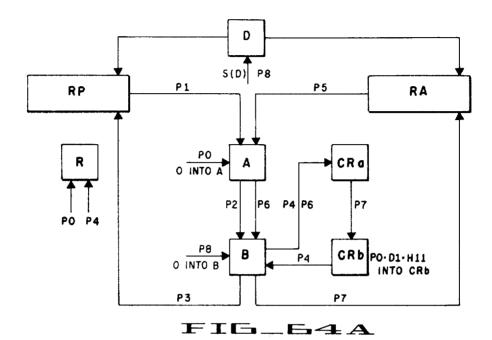

INSTRUCTION B14 RA PLUS RP INTO RA COMMAND LEVELS H9 H12 H14 H18 H19

```

FIG.

OPERATION

SIGNAL

61

PATCH

B14

B14

YO

B14

Zl

H9 H12 H18

H14 H19

YO

YO · Z1

PO · H19

G9

0 INTO A

G12

S(R)

G16

G9

PO•H12

45

48

G12

P1• H19

G16

READ

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN TO ZERO

COUNTS B UP TO An

45

G16

P2.H19

42

G17

29

59

0 INTO S(P)

S(A)

S(A)

43

48

P3•H19

G15

G15

WRITE

WRITE

G11

O INTO CRb

S(B)

1 INTO CRa

G12

S(R)

G16

P4.H14

G11

O INTO CRb

Bd BAR

P4•H12

G12

P5•H18

G16

G16

READ

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN TO ZERO

COUNTS B UP TO An

1 INTO CRA

G16

P6.H14

G17

O INTO S(P)

S(A)

S(A)

Bd BAR

P7•H18

G15

G15

P7•H14

WRITE

G13

C INTO CRa

1 INTO CRb

G13

CRa BAR

P8•H18

G10

P8•H9

G10

O INTO B

G2

S(D)

46 G2

REPEAT TILL D(C)

46

YC•Zì

Y0.21-6

F9.D0.Y0.Z1-6

S(I)

```

#### FIG....63

Filed Oct. 21, 1965

Sheet 45 of 125

FIG\_63A

FIG\_638

Filed Oct. 21, 1965

Sheet 46 of 125

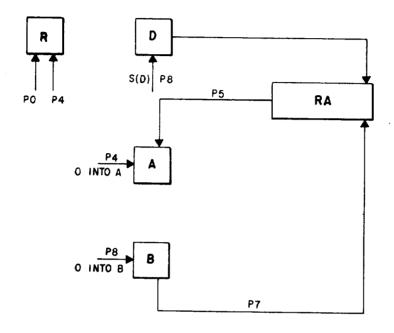

INSTRUCTION B15 RP MINUS RA INTO RA COMMAND LEVEL H9 H11 H12 H14 H18 H19

```

OPERATION PATCH

FIG.

SIGNAL

61

61

61

B15

Y0

Z2

B15

B15

Y0

49c

н9 н12 н18

49c

48

YO - Z2

H11 H14 H19

G9

O INTO A

42

48

09

PO+H11·D1

014

1 INTO CRB

G12

S(R)

G16

43

48

014

PO• H12

444445448

G12

P1. H19

G16

READ

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN TO ZERO

COUNTS B UP TO An

G15

P2.H19

G17

O INTO S(P)

S(A)

S(A)

P3-H19

45

G15

P4•H14

WRITE

GII

O INTO CRb

S(B)

I INTO CRa

GI2

43

43

43

43

48

G11

CRb BAR

Bd BAR

P4.H12

45

48

S(R)

G16

012

P5•H18

45

G16

P6•H11

G19

COUNT A UP TO 9 A NEG BAR

G17

ENABLES S(A) DISABLES T(P)

COUNTS A UP TO 9

COUNTS B UP TO AN COMPLEMENT

1 INTO CRA

G15

WRITE

G19

P6•H14

O INTO S(P)

S(A)

S(A)

48 54 43 48

S(A)

Bd BAR

F7•H18

G15

F7•H14

G13

CRA BAR

P8•H18

G13

O INTO CRa

1 INTO CRb

43 438

G10

43

G10

P8•H9

O INTO B

8(D)

46 G2 REPEAT TILL D(0)

Y0•Z2

P9•D0•Y0 • Z1-6

Y0.Z1-6

61

51

S(I)

```

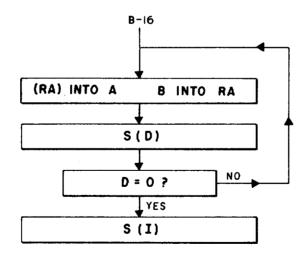

## FIG\_64

Filed Oct. 21, 1965

Sheet 47 of 125

1 INTO CRb (D=1)

(RP)INTO B

(9-RA) PLUS (B) INTO RA

S(D)

D=0 ?

YES

S(I)

F15\_54B

3,419,850

# PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>48</u> of 125

INSTRUCTION B16 O INTO RA COMMAND LEVEL H9 H12 H18

| F10<br>6198<br>448<br>448<br>448<br>448<br>448<br>448<br>448<br>448<br>448<br>4 | OPERATION PATCH B16 YO PO•H12 G12 P4•H18 G9 P4•H12 G12 P5•H18 G16 P7•H18 G15 P8•H18 G15 P8•H9 G2 TILL D(0) | SIGNAL B16 YO H9 H12 H18 G12 S(R) G9 O INTO A G12 S(R) G16 READ G15 WRITE G10 O INTO B G2 S(P) |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                                                                                 | 42                                                                                                         | S(D)                                                                                           |

| REPEAT                                                                          | TILL D(O)                                                                                                  | - ( - /                                                                                        |

| 61<br>51                                                                        | Y0•Z3<br>P9•D0•Y0•Z1-6                                                                                     | YO•Z1-6<br>S(I)                                                                                |

|                                                                                 |                                                                                                            |                                                                                                |

# FIG\_65

Dec. 31, 1968

J. KRAMMER

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>49</u> of 125

FIG\_65A

FIG\_65B

3,419,850

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet **50** of 125

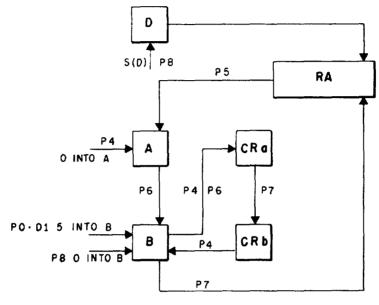

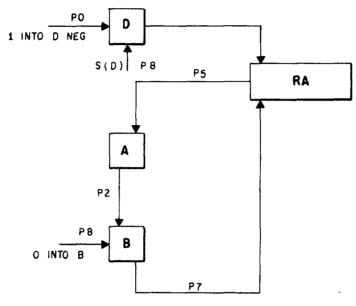

INSTRUCTION B17 LSD5 PLUS RA INTO RA COMMAND LEVEL H9 H12 H14 H18

```

FIG.

61

61

OPERATION

SIGNAL

PATCH

B17

B17

YO

61

B17

Z4

49c

YO

н9 н12 н18

YO•Z4

FO•YO•Z4•D1

FC•H12

49c

H14

H14

5 INTO B

G12

S(R)

G9

6 INTO A

G11

6 INTO CRb

S(B)

1 INTO CRa

G12

S(R)

43

48

45

48

G12

P4•H18

G9

P4•H14

) 28 3338 58 58 29 2338 58 338

Gil

CRb BAR

Bd BAR

P4•H12

S(R)

G16

G12

P5•H18

G16

P6•H14

READ

READ

G17

C INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN TO ZERO

COUNTS B UP TO An

1 INTO CRA

G15

WRITE

G13

P6•H14

G17

O INTO S(P)

S(A)

S(A)

Bd BAR

P7•H18

G15

P7•H14

G13

CRA BAR

P8•H18

G10

G13

C INTO CRa

1 INTO CRb

G10

43

48

G10

P8•H9

C INTO B

46

G2

S(D)

REPEAT TILL D(0)

Y0•Z4

Y0 • 21 - 6

P9.DO.YO.Z1-6

S(I)

```

#### FIG\_EE

Filed Oct. 21, 1965

Sheet <u>5/</u> of 125

FIG\_66A

FIG\_66B

3,419,850

# PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

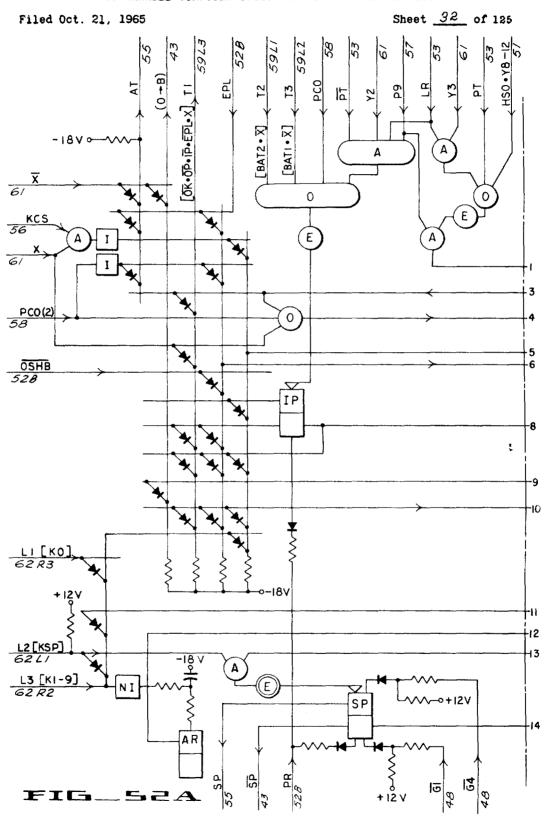

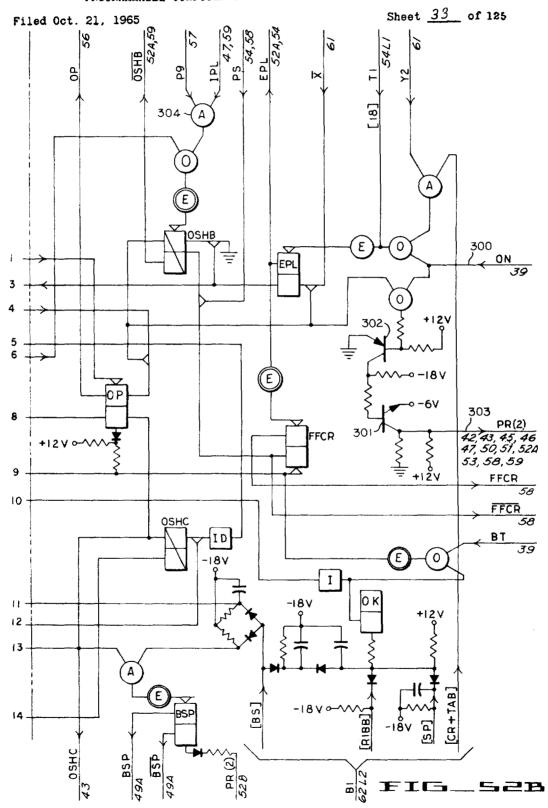

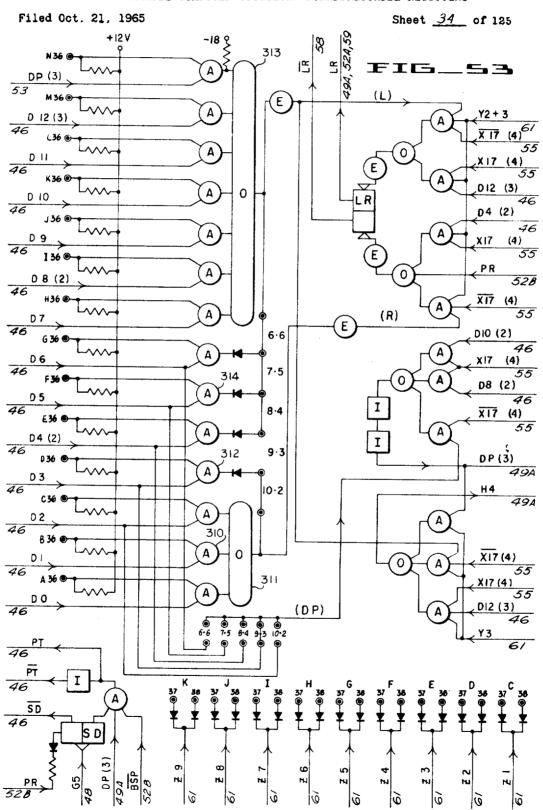

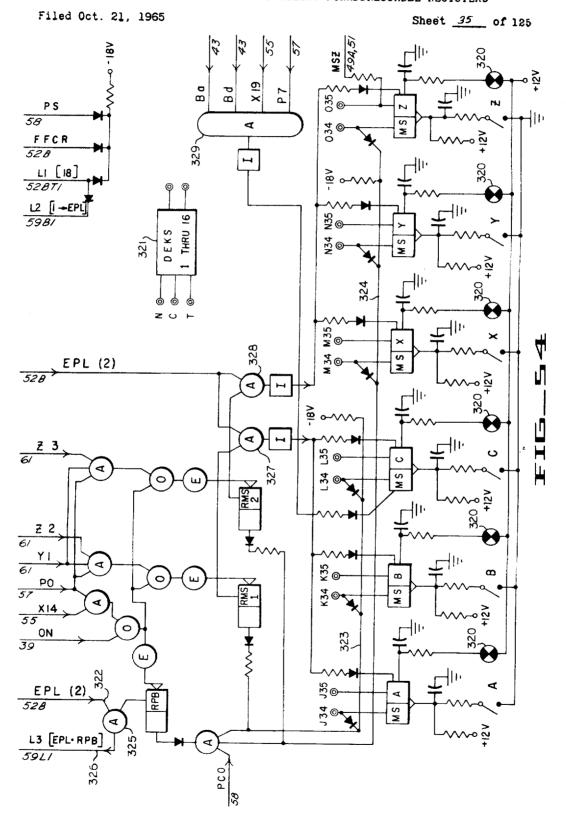

Sheet <u>52</u> of 125

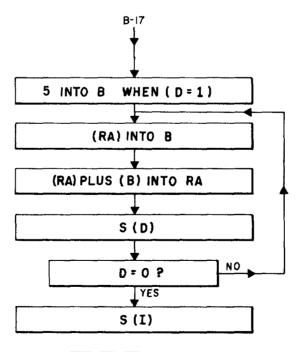

INSTRUCTION B18 .1 X RA INTO RA COMMAND LEVEL H6 H9 H12 H18 H17

```

FIG. 61 61 61 40c

OPERATION

SIGNAL

PATCH

B18

B18

YO

Z5

Z5-8

H9 H12 H18

H6

B18

B18

Z5

Y0

Y0•Z5

Y0•45-8

P0•H6

49c

484444445448

HO

H17

G6

1 INTO D NEG (COUNT DOWN)

G12

S(R)

<u>G6</u>

PO•H12

G12

P2•H17

G17

S(H)

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN TO ZERO

COUNTS B UP TO An

O INTO S(P)

S(A)

S(A)

P4•H12

G12

S(R)

45

G12

P5•H18

G16

P7•H18

G15

P8•H18

G16

READ

G15

WRITE

458 458 48

48

48

G10

G10

P8•H9

O INTO B

G2

S(D)

ro•H9

G2

REPEAT TILL D(0)

61 Y0•Z5

51 P9•D0•Y0

46

Y0•Z5

P9•D0•Y0•Z1-6

Y0.21-6

D NEG BAR (COUNT UP)

```

## FIG\_62

Filed Oct. 21, 1965

Sheet <u>53</u> of 125

FIG\_62A

FIG\_E2B

3,419,850

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>54</u> of 125

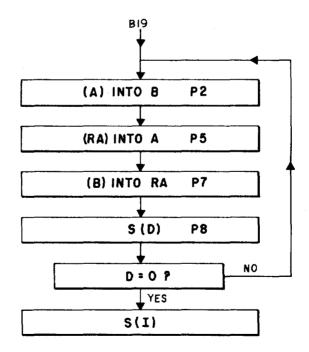

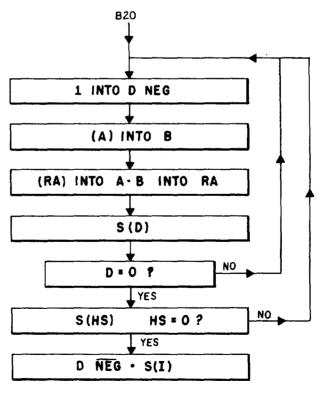

INSTRUCTION B19 10 X RA INTO RA (SL 1 X)

COMMAND LEVELS H9 H12 H18 H17

| FIG.                    | OPERATION             | SIGNAL                     |

|-------------------------|-----------------------|----------------------------|

| 61                      | PATCH                 | <b>B1</b> 9                |

| 61                      | <b>B</b> 19           | YO                         |

| 61                      | B19                   | z6                         |

| 61                      | <b>z</b> 6            | <b>25-8</b>                |

| 49 <b>c</b>             | YO                    | н9 н12 н18                 |

| 49.98<br>44.44<br>44.44 | <u>z</u> 5-8          | H17                        |

| 48                      | <u>PO</u> •H12        | gis                        |

| 45                      | G12                   | <u>s(</u> R)               |

| 40                      | P2•H17                | G17                        |

| į15                     | G17                   | O INTO S(P)                |

| 25<br>70                | O INTO S(P)           | ENABLES S(A) DISABLES T(P) |

| 12                      | S(A)<br>S(A)          | COUNTS A DOWN TO ZERO      |

| <u>1</u> 2              | P4•H12                | COUNTS B UP TO An<br>G12   |

| 45                      | G12                   | S(R)                       |

| 48                      | P5•H18                | G16                        |

| 45                      | G16                   | READ                       |

| 48                      | G16<br>P7•H18         | G15                        |

| 45                      | 015                   | WRITE                      |

| 5923858585858386        | <u>G1</u> 5<br>P8•H18 | <b>G</b> 10                |

| 43                      | <u>G1</u> 0<br>P8•H9  | O INTO B                   |

| 48                      | P8•H9                 | <b>G</b> 2                 |

|                         | 02                    | S(D)                       |

|                         | TILL D(O)             |                            |

| 61                      | Y0•Z6                 | Y0•Z1-6                    |

| 51                      | P9•D0•Y0•Z1-6         | S(I)                       |

|                         |                       |                            |

## FIG\_6A

Filed Oct. 21, 1965

Sheet <u>55</u> of 125

FIG\_68A

FIG\_68B

#### J. KRAMMER

3,419,850

# PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>56</u> of 125

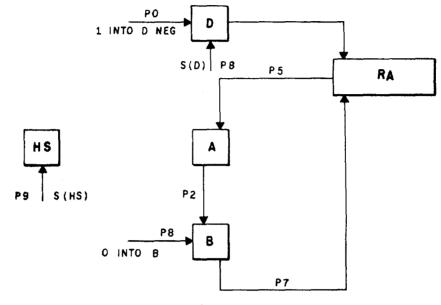

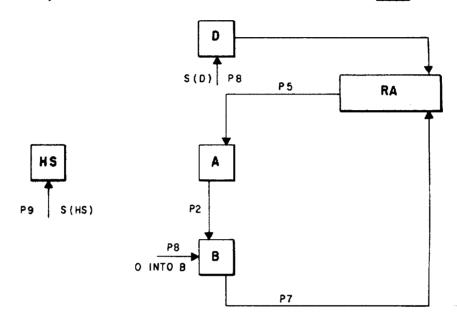

INSTRUCTION B20 .01 X RA INTO RA (SR 2X)

COMMAND LEVELS H6 H9 H12 H18

PHASE COUNTER HS

```

FIG.

61

61

61

OPERATION

PATCH

B20

SIGNAL

B20

YO

B20

Z7

Y0

Ž7

61

49c

Z5-8

H9 H12 H18

H6

Y0•Z5

Y0•Z5-8

P0•H6

49c

44868586

44844444

H17

G6

G6

1 INTO D NEG (COUNT DOWN)

G12

S(R)

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP

G12

<u>06</u>

PO•H12

G12

P2•H17

42

G17

C INTO S(P)

S(A)

S(A)

P4•H12

54444444444

G12

S(R)

G16

G12

P5•H18

48 P5•H18

45 G16

48 P7•H18

45 G15

48 P8•H18

43 G10

48 P8•H9

46 G2

REPEAT TILL D(0)

51 P9•Y0•D0•Z7

REPEAT TILL D(0)

51 P9•HS1•D0

46 P9•S(I)

READ

G15

WRITE

G10

OS B

S(D)

S(HS)

S(HS)

S(I)

D NEG BAR (COUNT UP)

```

## FIG\_69

Filed Oct. 21, 1965

Sheet <u>57</u> of 125

F16\_69A

FIG\_ESB

3,419,850

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

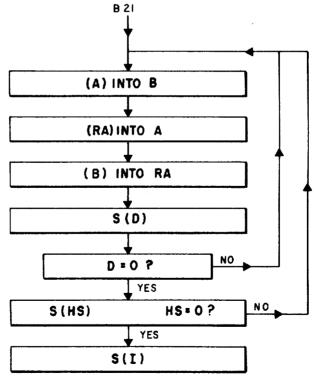

INSTRUCTION B21 100 X RA INTO RA (SL 2X)

COMMAND LEVELS H9 H12 H18

PHASE COUNTER HS

```

FIG.

OPERATION

SIGNAL

PATCH

B21

B21

B21

Z8

Y0

Z5-8

PO•H12

¥0

28

Z8

Z5-8

H9 H12 H18

H17

G12

S(R)

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP

G12

012

P2.H17

G17

0 INTO S(P)

S(A)

S(A)

P4•H12

G12

S(R)

G16

G12

P6•H18

G16

P7•H18

G15

P8•H18

READ

G15

WRITE

G10

O INTO B

G10

P8•H9

G2

S(D)

REPEAT TILL D(0)

S(HS)

51

51

S(HS)

S(I)

P9.HS1.DO

```

#### FIG\_20

Filed Oct. 21, 1965

Sheet <u>59</u> of 125

FIG\_20A

FIG\_208

3,419,850

Filed Oct. 21, 1965 Sheet <u>60</u> of 125

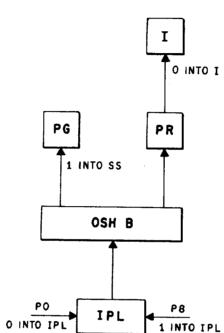

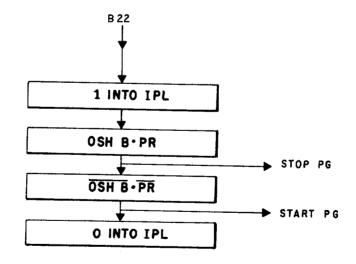

INSTRUCTION B22 O INTO I (ITERATE)

| 52b<br>59<br>52b | OPERATION PATCH B22 B22 P8•Y0•Z9 P9•IPL P9•IPL OSH B PR O INTO I                                                      | SIGNAL B22 YC Z9 1 INTO IPL 1 INTO OSH B 1 INTO SS (STOPS PG) 1 INTO PR 0 INTO I RESET INSTRUCTION COUNTER TO ZERO |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| NOTE:            | WHEN IN PROGRAM, PR AT O A 1 INTO FC, THEN WHEN IPL S STAY UNTIL THE FOLLOWING F THE INFORMATION IN THE FC DESTROYED. | SETS ON THE P8, IT WILL<br>PO. THIS INSURES THAT                                                                   |

| 52b<br>59<br>47  | OSH B TIMES OUT<br>OSH B<br>PO                                                                                        | O INTO PR<br>O INTO SS (STARTS PG)<br>O INTO IPL                                                                   |

# FIG\_21

Filed Oct. 21, 1965

Sheet 6/ of 125

FIG\_21B

#### Filed Oct. 21, 1965

Sheet <u>62</u> of 125

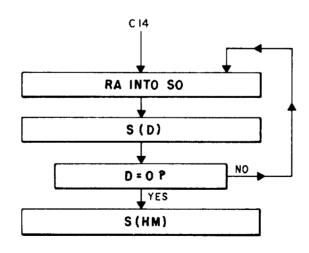

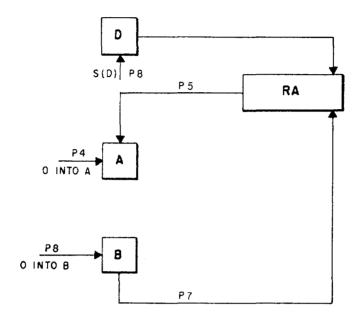

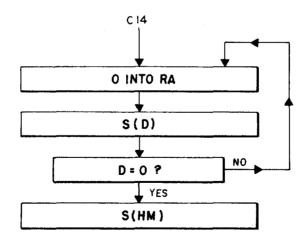

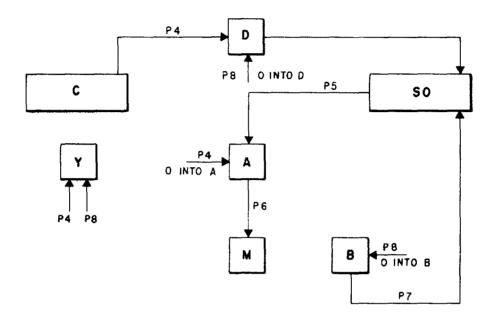

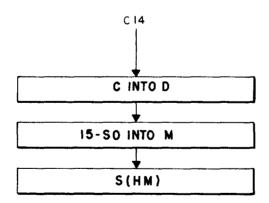

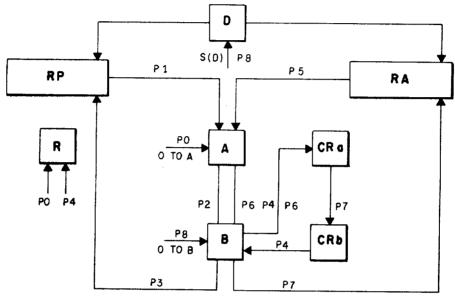

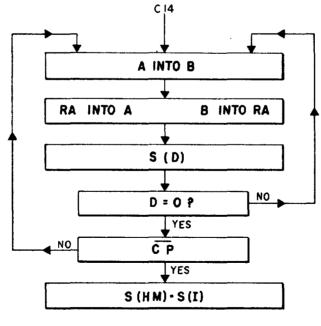

INSTRUCTION C14 MULTIPLICATION (RP)X(RA) INTO RA

COMMAND LEVELS Y1 Z1

PHASE COUNTER HM

FIG. OPERATION SIGNAL 61 61 C14 Y1 PATCH C14 61 50 C14 Zļ S(HM) HMO IS NOT USED.ON THE P9 THE HM IS STEPPED FROM ZERO TO 1. P9.D0.Y1.Z1.HMc HM1 H7 H9 H18 H19 1 INTO C Cd•Cc•Cb•Ca 50 49b 44 HMc • HMb • HMa HM1 PO•HM1 1 INTO C PO•H19 44 G9 C INTO A G16 G9 P1•H19 G16 READ (RA INTO A) P2•H19 017 **G17** GI/TO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An O INTO S(P) S(A) S(A) P3•H19 G15 P4•H7 G15 WRITE (B INTO RA) G3 S(Y) (LOOK AT SO) G3 P5•H18 GÌ6 G16 P7•H18 G15 P8•H18 G10 P8•H9 READ (SO INTO A) (CLEAR SO) G15 WRITE (B INTO SO) G10 O INTO B G2 G2 P8•H7 S(D) G3 S(Y) (LOOK AT RA) 45 G3

REPEAT TILL D(0)

50 P9•D0•Y1•Z1•HMc S(HM) TO 2

## FIG\_22~1

Filed Oct. 21, 1965

Sheet <u>63</u> of 125

FIG\_22-1B

Dec. 31, 1968

#### J. KRAMMER

3,419,850

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 64 of 125

MULTIPLICATION (CONTINUED)

HM2 O INTO RA

COMMAND LEVELS H9 H18

| FIG. OPERATION SIGNAL                                                                                                                                 |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 49b HM2 H9 H18                                                                                                                                        |        |

| 48 P4•H18 G9                                                                                                                                          |        |

| 42 <b>G</b> 9 O INTO A                                                                                                                                |        |

| 49b HM2 H9 H18  48 P4•H18 G9  42 G9 O INTO A  48 P5•H18 G16  45 G16 READ (RA INTO A) (CLEAN  48 P7•H18 G15  48 P8•H9 G2  48 P8•H18 G10  48 P8•H18 G10 |        |

| 45 G16 READ (RA INTO A) (CLEA                                                                                                                         | AR PA) |

| 48 P7•H18 G15                                                                                                                                         | ,      |

| 45 <u>G1</u> 5 WRÍTE (O INTO RA)<br>48 P8•H9 G2                                                                                                       |        |

| 48 P8•H9 g2                                                                                                                                           |        |

| 46 G2 S(D)                                                                                                                                            |        |

| 48 P8•H18 G10                                                                                                                                         |        |

| 43 GIO O INTO B                                                                                                                                       |        |

| REPEAT TILL D(O)                                                                                                                                      |        |

| 50 P9•DO•Y1•Z1•HMc S(HM) TC 3                                                                                                                         |        |

NOTE:

HM3 IS NOT USED. ON THE P9 THE HM WILL STEP FROM 3 TO 4.

## FIG\_22~2

Filed Oct. 21, 1965

Sheet <u>65</u> of 125

## FIG\_22~2A

FIG\_22~2B

Filed Oct. 21, 1965

Sheet 66 of 125

MULTIPLICATION (CONTINUED)

HM4 SO/C INTO M

COMMAND LEVELS H5 H7 H18

```

FIG.

OPERATION

SIGNAL

50

49b

HMC

H18

H5 H7

HM4

HMC

49b

48

HM4

P4.H18

G9

G9

O INTO A

G3

S(Y) (LOOK AT SO)

G8

C INTO D

SET C INTO D

428

48

45

48

G9

P4•H7

P4•H7

G3

P4•H5

C•G8

C INTO D

P5•H18

G16

44&46

46

48

45

48

G16

READ (SO INTO A)

P6•H5

G7

42

42

48

A (IF RESET)

G7

P7•H18

ENABLES M

SET 15 COMP OF A INTO M

G15

45

G15

P8•H7

WRITE (O INTO SO)

G3

S(Y) (LOOK AT RA)

48

FO...

45

G3

46

P8•HM4

P8•H18

O INTO B

IF THE M COUNTER RECEIVED A VALID NUMBER FROM A

DURING P6 TIME, M15 IS VALID.

50

P9•D0•HM4•M15

S(HM)

IF THE M COUNTER DID NOT RECEIVE A VALID NUMBER FROM A

DURING P6 TIME, M15 IS VALID.

50

HM4•M15

P9

RNABLE HMb

P9

1 INTO HMb (HM NOW

ENABLE HMb

1 INTO HMb (HM NOW AT 6)

```

#### FIG\_22~3

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 67 of 125

FIG\_22-3A

FIG\_22~3B

Filed Oct. 21, 1965

Sheet 68 of 125

MULTIPLICATION (CONTINUED)

HM5 (RP) PLUS (RA) INTO RA

COMMAND LEVELS H9 H12 H14 H18 H19

```

FIG.

OPERATION

SIGNAL

50

49b

49b

HMC

H18

нм6

HMC

HM5

HM5•Y1

PO•H19

н9 н14 н19

Hĺ2

G9

O INTO A

G12

S(R) (LOOK AT RP)

G9

PO•H12

G12

P1.H19

G16

READ (RP INTO A)

P2.H19

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

G17

G17

O INTO S(P)

S(A)

S(A)

P3•H19

G15

P4•H14

G15

WRITE (B INTO RP)

G11

O INTO CRb

S(B)

1 INTO CRa

G12

S(R) (LOOK AT RA)

G11

CRb BAR

Bd BAR

P4.H12

G12

P5•H18

G16

READ (RA INTO A)

45 48

G16

P6•H14

GIT

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

1 INTO CRA

GIT

GIT

FOR PLANS BA INTO EA

4544338458

454444444

G17

O INTO S(P)

S(A)

S(A)

Bd BAR

P7•H18

<u>G1</u>5

P7•H14

WRITE (RP PLUS RA INTO RA)

G13

43

43

46

46

G13

CRa BAR

P8•H9

G2

O INTO CRA

g(D)

REPEAT TILL D(0)

42 P9•DO•HM5

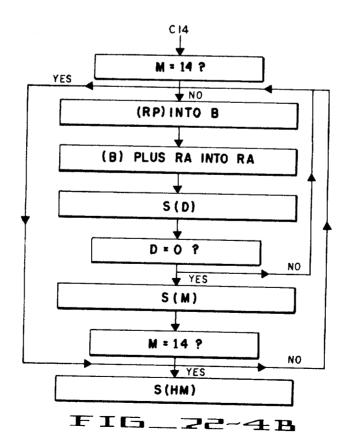

REPEAT TILL M=14

S(M)

P9.DO.HM5.M14

S(HM)

```

#### FIG\_22-4

Filed Oct. 21, 1965

Sheet 69 of 125

FIG\_22-4A

#### J. KRAMMER

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 70 of 125

MULTIPLICATION (CONTINUED)

HM6 SHIFT RIGHT 1X S(C)

COMMAND LEVELS H9 H17 H18

```

SIGNAL (HM6 OR 7)

FIG.

OPERATION

50000

50998

44

нм6

нм6+4+5+7

(HM6 OH 7)

HMC

H9 H17

H18

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

(HM6 OR 7)

P2*H17

P2*H17

G17

O INTO S(P)

S(A)

S(A)

P5*H18

42

4592438

438

G16

45

48

G16

P7•H18

READ (RA INTO A)

G15

WRITE (B INTO RA)

45

G15

P8•H18

G10

O INTO B

G2

O INTO M

S(D)

43

48

G10

P8•H9

P8•HM6

42

46

G2

REPEAT TILL D(2)

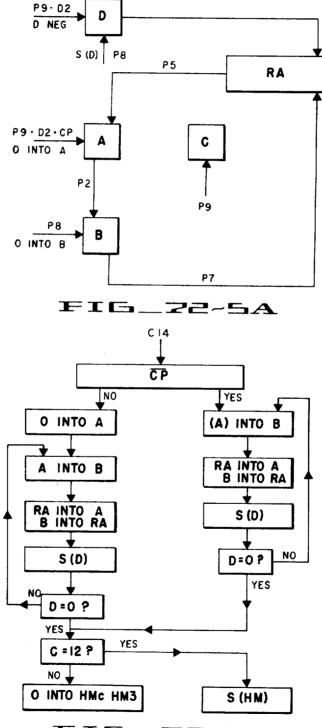

CP

0 INTO A

12 INTO D (1 INTO Dd) • (1 INTO Dc) •

(0 INTO Db) • (1 INTO Da)

D NEG (COUNT DOWN)

44

C1+2+3

P9•HM6•D2•D NEG•CP

P9•HM6 OR 7•D2•D NEG

42

46

46 P9•HM6 or 7•D2•D NEG REPEAT TILL D(0)

P9 • DO • HM6

P9 • DO • HM6

S(C)

S(HM) (TO7)

3 TO HM (C INTO HMe) HM=3

50

50

P9.DO.HM6.C12

BACK TO HM3 TILL C=12

46

P9.DO.HM6+7

D NEG

O INTO Cc

O INTO Cd (C=1)

S(HM) HM=7

ЫŁ

C13

44

Сс

Pd DO · HM6

50

```

#### FIG\_22~5

. .

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>7/</u> of 125

FIG\_22~5B

Filed Oct. 21, 1965

Sheet <u>72</u> of 125

MULTIPLICATION (CONTINUED)

HM7 SHIFT ROUND

COMMAND LEVELS H9 H17 H18

```

SIGNAL

HM6 OR 7

HMC

H9 H17

H18

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

FIG.

OPERATION

HM7

HM6+4+5+7

HM6 OR 7

HMC

554445448

P2.H17

G17

O INTO S(P)

S(A)

S(A)

P5.H18

G16

458 458

016

₱7•H18

READ (RA INTO A)

G15

WRITE (B INTO RA)

<u>Gi</u>5

Р8•н18

G10

O INTO B

G2

S(D)

D NEG

43846

G10

P8·H9

G2

46 G2

46 P9·HM6+7·DO

REPEAT TILL D(2)

46 P9·HM6 OR 7·D2·D NEG

12 INTO D (1 INTO Dd) (1 INTO Dc) (0 INTO Db) (1 INTO Da)

D NEG (COUNT DOWN)

46 P9·HM6 OR 7·D2·D NEG

44 P9·HM7·D2·D NEG

REPEAT TILL CP (C4)

S(C)

C4

CP•HM7

P9(CP•HM7) DO

PS (CP•HM7) DO

44

CF+HM7 SIGNAL

S(HM) (HM=0)

S(I)

50

50

```

## FIG\_ 22-6

Filed Oct. 21, 1965

Sheet <u>73</u> of 125

F16\_22~6A

FIG\_22/6B

### J. KRAMMER

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 74 of 125

# INSTRUCTION C12 1 INTO RMS1 COMMAND LEVELS Y1 Z2

| FIG.                        | OPERATION                | SIGNAL           |

|-----------------------------|--------------------------|------------------|

| 61                          | C12                      | Y1•Z2            |

| 54                          | PO•Y1•Z2                 | 1 INTO RMS1      |

| 54<br>56                    | <b>Zl·Y</b> l            | Zl·Yl SIGNAL     |

| 51                          | P9.D0.(Z1.Y1)            | S(I)             |

| AT THE                      | END OF THE PROGRAM LINE, | (ÈPL)            |

| 59                          | X.OSHB.OSHA.BAT 1.BAT2   | 1 INTO EPL       |

| 52b                         | 1 INTO EPL               | SET EPL FF.OSHB  |

| 54                          | OSHB                     | PR               |

| 52b<br>54<br>54<br>54<br>54 | EPL•RMS1                 | O INTO MSA, B, C |

| 54                          | O INTO MSA, B, C         | RESETS MSA, B, C |

| 54                          | MSA, B, C ŘESĚT          | RESETS RMS1      |

#### FIG\_23

# INSTRUCTION C13 1 INTO RMS2 COMMAND LEVELS Y1 Z3

| FIG.                  | OPERATION                | SIGNAL           |

|-----------------------|--------------------------|------------------|

| 61                    | C13                      | Y1• Z3           |

| 54                    | PO•Y1•Z3                 | 1 INTO RMS2      |

| 56                    | <b>Zī.</b> •Y1           | Zl·Yl SIGNAL     |

| 54<br>56<br>51        | P9.DO.(Z1.Y1)            | S(I)             |

| AT THE                | END OF THE PROGRAM LINE, | • •              |

| 59                    | X·OSHB·OSHA·BAT 1·BAT2   | 1 INTO EPL       |

| 52b                   | 1 INTO EPL               | SETS EPL FF.OSHB |

| 52b                   | OSHB                     | PR               |

| 54                    | EPL•RMS2                 | O INTO MSX, Y, Z |

| 54                    | O INTO MSX, Y, Z         | RESETS MSX, Y, Z |

| 52b<br>54<br>54<br>54 | MSX, Y, Z ŘESÉT          | RESETS RMS2      |

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>75</u> of 125

INSTRUCTION C17 RESTORE PROGRAM BANK (KEYS 1-10 MSA,B,C,X,Y,Z)

COMMAND LEVELS Y1 Z4

| FI <b>G.</b><br>61                     | OPERATION<br>PATCH       | SIGNAL<br>C17    |

|----------------------------------------|--------------------------|------------------|

| 61                                     | C17                      | Y1 Z4            |

| 55                                     | Y1.Z4                    | X14              |

| 55<br>54<br>54<br>55<br>55             | PO+X14                   | 1 INTO RMS1      |

| 54                                     | PO•X14                   | 1 INTO RMS2      |

| 54                                     | PO•X14                   | 1 INTO RPB       |

| 55                                     | Z1.Y1                    | Zl·Yl SIGNAL     |

| 51                                     | P9·D0·(21·Y1)            | S(I)             |

|                                        | END OF THE PROGRAM LINE, |                  |

| 59                                     | X.OSHA.OSHB.BAT 1.BAT 2  | 1 INTO EPL       |

| 52b                                    | 1 INTO EPL               | SETS EPL FF.OSHB |

| 52 <b>b</b>                            | OSHB                     | PR               |

| 54                                     | EPL•RMS1                 | O INTO MSA,B,C   |

| 54                                     | O INTO MSA,B,C           | RESET MSA,B,C    |

| 54                                     | EPL·RMS2                 | o into msx,y,z   |

| 54                                     | o into MSX, Y, Z         | RESET MSX,Y,Z    |

| 54                                     | EPL·RPB                  | 1 INTO EPL-RPB   |

| 5 <b>9</b>                             | EPL • RPB                | O INTO PCA       |

| 59                                     | O INTO PCA               | 1 INTO PCO       |

| 54                                     | PCO·MSA,B,C·MSX,Y,Z      | O INTO RPB       |

| 55555555555555555555555555555555555555 | MSA,B,C                  | o into RMS1      |

| 54                                     | MSX,Y,Z                  | o into RMS2      |

#### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 76 of 125

INSTRUCTION C18 1 INTO BAT 1 (BLOCK AUTOMATIC TAB)

COMMAND LEVELS Y1 25

| FIG.           | OPERATION         | SIGNAL                               |

|----------------|-------------------|--------------------------------------|

| 61             | PATCH             | C18                                  |

| 61             | C18               | Y1 25                                |

| 61             | Zī•Yl             | ZI•Yl SIGNAL                         |

| 59             | PO•Y1•Z5          | 1 INTO BAT 1                         |

| 59             | BAT 1             | O INTO EPL                           |

| 59<br>59<br>51 | P9.DO.(Z1.Y1)     | S(I)                                 |

| WITH E         | PL AT ZERÔ WE RÊM | AIN IN PROGRAM. WHEN THE CARRIAGE IS |

| MOVED A        | ACROSS A NUMBER 1 | 1 FIELD ACTUATOR, FS11 WILL OPERATE. |

| 59             | FS11              | RESETS BAT 1 FF                      |

#### FIG\_26

# INSTRUCTION C19 1 INTO BAT 2 (BLOCK AUTOMATIC TAB) COMMAND LEVEL Y1 Z6

| FΙ       | G. OPERATION           | SIGNAL                              |

|----------|------------------------|-------------------------------------|

| 61       | PATCH                  | C19                                 |

| 61       | <b>C</b> 19            | Y1 Z6                               |

| 61<br>61 | <b>2</b> 1∙Y1          | Zl•Yl SIGNAL                        |

| 59       | PO•Y1•Z6               | 1 INTO BAT 2                        |

| -59      | BAT 2                  | O INTO EPL                          |

| 51       | P9.DO.(Z1.Y1)          | S(I)                                |

| WI       | TH EPL AT ZERÔ WE RÉMA | IN IN PROGRAM. WHEN THE CARRIAGE IS |

| MO       | VED ACROSS A NUMBER 12 | FIELD ACTUATOR, FS12 WILL OPERATE.  |

| 59       |                        | RESETS BAT 2 FF                     |

Filed Oct. 21, 1965

Sheet <u>77</u> of 125

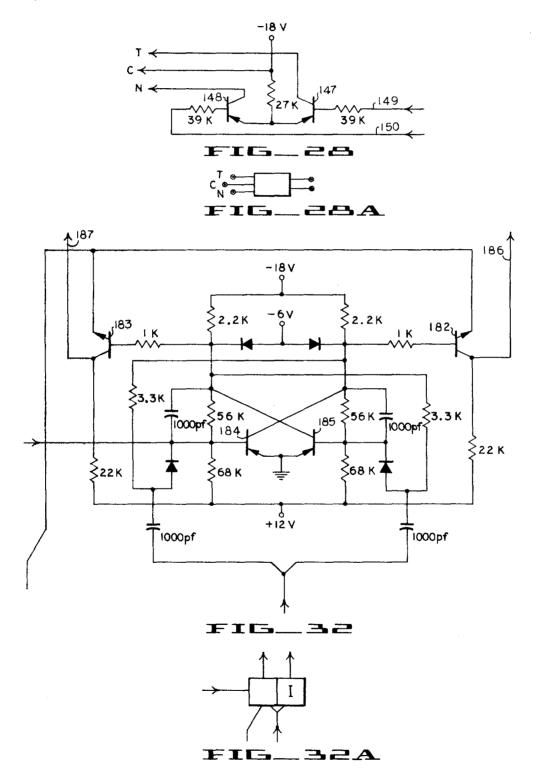

FIG\_28A

FIG\_ZAB

## Dec. 31, 1968

## J. KRAMMER

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 78 of 125

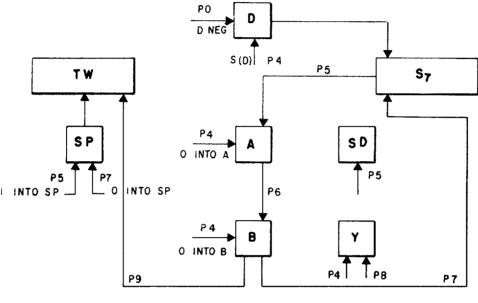

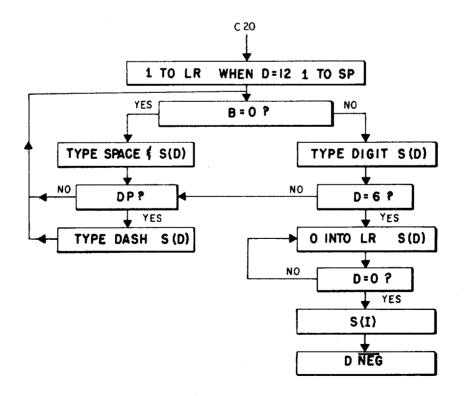

INSTRUCTION C20 TYPE AUTOMATIC DATE COMMAND LEVELS H6 H7 H16 H0 H2 H3 H4

| FIG.<br>61<br>61<br>55<br>61<br>61<br>49a<br>49a | OPERATION PATCH C20 Y1.27 X17 Y3 BSP.Y2 OR 3 X17 Y3 | SIGNAL<br>C2O<br>Y1 Z7<br>X17<br>Y3<br>Y2 OR 3<br>H6<br>H7<br>H16<br>PHASE 1 |

|--------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------|

| 48                                               | ₱ <b>0</b> • н6                                     | of                                                                           |

| 45<br>48                                         | <b>96</b>                                           | D NEG                                                                        |

|                                                  | P4•H16                                              | <b>G</b> 9                                                                   |

| 42<br>48                                         | <b>G</b> 9                                          | O INTO A                                                                     |

| 48<br>43                                         | P4•H16<br>G10                                       | G10<br>O INTO B                                                              |

| 49a -                                            | SD•Y2+3                                             | н3                                                                           |

| 48                                               | P4•H3                                               | G2                                                                           |

| 45                                               | G2                                                  | S(D)                                                                         |

| 45<br>48                                         | P4•H7                                               | G3                                                                           |

| 4538<br>54538<br>4538                            | G3                                                  | S(Y) (LOOK AT S7)                                                            |

| 53                                               | X17.D12.Y2 OR 3                                     | 1 INTO LR                                                                    |

| 48<br>46                                         | P5•H16<br>G16                                       | G16                                                                          |

| 45<br>63                                         | Y3•D12•X17                                          | READ (S7 INTO A)<br>H4                                                       |

| 148<br>148                                       | P5•H4                                               | G4                                                                           |

| 52a                                              | <b>ਰੋ</b> 4                                         | 1 INTO SP                                                                    |

| 48                                               | Рб•н16                                              | G17                                                                          |

| 42                                               | 017                                                 | o into s(p)                                                                  |

| 59<br>42                                         | O INTO S(P)                                         | ENABLES S(A) DISABLES T(P)                                                   |

| 42                                               | S(A)<br>S(A)                                        | COUNTS A DOWN                                                                |

| 43<br>48                                         | 5(A)<br>P7•H16                                      | COUNTS B UP TO An<br>G15                                                     |

| 45                                               | G15                                                 | WRITE (B INTO S7)                                                            |

| IF B NOW                                         | HAS A DIGIT THEN BO                                 | , , , , , , , , , , , , , , , , , , ,                                        |

| 43                                               | BO                                                  | НО                                                                           |

| 49a                                              | НО                                                  | НО                                                                           |

| 48                                               | P7•H0                                               | G1                                                                           |

| 52a<br>48                                        | <u>G1</u><br>P8•H7                                  | O INTO SP                                                                    |

| 45<br>45                                         | G3                                                  | S(Y) (LOOK AT RA)                                                            |

| 59                                               | P9•LR                                               | 1 INTO SS                                                                    |

| 52a                                              | P9.LR.Y3                                            | 1 INTO OP                                                                    |

| •                                                |                                                     |                                                                              |

## FIG\_\_\_ **78**~1

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>79</u> of 125

# TYPE AUTOMATIC DATE (CONTINUED) INSTRUCTIONS C20

| FIG. OPERATION                         | SIGNAL                  |

|----------------------------------------|-------------------------|

| SP FF NOT RESET ON P7                  |                         |

| 43 SP                                  | O INTO B (OUTPUT LINES) |

| 55 SP                                  | 1 INTO 8-9 LINES        |

| 55 OP·SP·CS·(YB-12 OR<br>BCS OR Z5-8)  | 1 INTO SP LINE          |

| 62 1 INTO 8-9-SP LINE                  | TYPE SPACE              |

| 62 SPACE BAR CONTACTS SP               | 1 INTO SP LINE          |

| 52b 1 INTO SP LINE                     | <u>ok</u>               |

| SP FF RESET ON P7 (NUMBER WILL BE A    | ONE)                    |

| 43 Ba                                  | 1 INTO 13579 LINE       |

| 43 Bd•Bc•Bb                            | 1 INTO O-1 LINE         |

| 44 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( |                         |

| CS (Y8-12 OR BCS OR                    | 1 INTO 1 LINE           |

| <del>25-</del> 8)                      |                         |

| 62 1 INTO 1.0-1 LINE                   | TYPE DIGIT 1            |

| 62 RIBBON CONTACTS CLOSE               | 1 INTO RIBBON LINE      |

| 52b 1 INTO RIBBON LINE                 | Ōĸ                      |

| 52b OK                                 | O INTO OP               |

| 52b OK TIMES OUT                       | OK                      |

| 52b OK•OF                              | o in <b>t</b> o ss      |

| REPEAT TILL D=11                       |                         |

|                                        |                         |

## FIG\_28-2

Filed Oct. 21, 1965

Sheet <u>80</u> of 125

INSTRUCTION C20 TYPE AUTOMATIC DATE (CONTINUED)

PHASE 2

```

OPERATION

FIG.

SIGNAL

48

PO•H6

06

46

D NEG

a6

48

P4.H16

a9

C9

P4.H16

C10

SD.Y2+3

P4.SD.H3

483986858

4444444444

O INTO A

G10

O INTO B

G2

S(D) D=10

G3

S(Y) (LOOK AT S7)

P4+H7

03

P5•H16

Gi6

016

READ (S7 INTO A)

D10 · X17

DP · LR · BSP

DP

H2

DP-LR-BSP

P5-H2

Q5

DP-Y3

SD-DP-BSP

P5-H4

Q4

G5

S(SD) (S(SD) PREVENTS S(D) NEXT TIME)

H4

PT

G4

1 INTO SP

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

P6.H16

017

O INTO S(P)

S(A)

S(A)

P7.H16

G15

WRITE (B INTO S7)

сі5

P8•н7

G3

S(Y) (LOOK AT RA)

1 INTO SS

1 INTO OP

G3

P9•LR

P9.LR.Y3

O INTO B OUTPUT LINES

PT

PT•X17

1 INTO SP OR DASH OR Pt

NOTE:

OUR EXAMPLE WILL USE DASH

I INTO DASH

OP DASH CS (Y8-12

OR BCS OR Z5-8)

RIBBON CONTACTS CLOSED

1 INTO RIBB

OR

1 INTO 6-7 LINE

1 INTO DASH LINE

55

55

55

INTO RIBB LINE

52b

Ōĸ

52b

52b

O INTO OP

OK

OK TIMES OUT OK. OF

52b

O INTO SS

```

#### FIG\_28-3

Filed Oct. 21, 1965

INSTRUCTIONS C20 TYPE AUTOMATIC DATE (CONTINUED)

PHASE 3

```

FIG.

OPERATION

SIGNAL

48

PO • H6

G6

D NEG

46

Œ6

P4.H16

48

G9

G9

P4•H16

G10

SD•Y2+3

P4•SD•H3

A OTMI O

42

48

G10

O INTO B

3986858

44444444

H3

S(D)

G2

P4 • H7

03

S(Y) (LOOK AT S7)

G3

P5 H2

G5

S(SD)

53

53

53

53

53

8

G16

READ (S7 INTO A)

Y17.D10

DP

H4

Y3 • DP

P5•H4

G4

52a

48

1 INTO SP

P6.H16

017

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

42

G17

O INTO S(P)

S(A)

S(A)

592

43

48

P7. H16

G15

WRÍTE (B INTO S7)

45

015

HAS A DIGIT THEN BO

IF B NOW

43

BO

(HO)

49c

(HO)

ĤΟ

48

₽7• HO

Gì

52a

48

G1

P8 H7

O INTO SP

G3

S(Y) (LOOK AT RA)

G3

P9•LR

45

59

1 INTO SS

52a

P9 • LR • Y3

INTO OP

SP

43

FF NOT RESET ON P7

SP

O INTO B (CUTPUT LINES)

1 INTO 8-9 LINE

1 INTO SP LINE

55

55

SP

OP•SP•CS•(<u>Y8-12</u> OR

BCS OR Z5-8)

1 INTO 8-9•SP LINE

62

TYPE SPACE

62 SPACE BAR CONTACTS SP 1 IN 52b 1 INTO SP LINE OR 5P RESET ON P7 (NUMBER WILL BE A ONE)

1 INTO SP LINE

Ba

Bd • Bc • Bb

1 INTO 13579 LINE

1 INTO 0-1 LINE

43

43

BG.BC.Bb

1 INTO 13579 LINE.OP.

CS (Y8-12 OR BCS OR

Z5-8)

1 INTO 1.0-1 LINE

RIBBON CONTACTS CLOSE

1 INTO RIBBON LINE

OK

43

1 INTO 1 LINE

62

TYPE DIGIT 1

\frac{1}{OK} INTO RIBBON LINE

62

52b

52b

52b

O INTO OP

OK TIMES OUT OK. OF

оĸ

52b

O INTO SS

REPEAT TILL D=8

```

## FIG\_28~4

#### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>82</u> of 125

INSTRUCTION C20 TYPE AUTOMATIC DATE (CONTINUED) PHASE  $^4$

```

OPERATION PO•H6

FIG.

SIGNAL

G6

46

48

06

D NEG

P4+H16

Œ9

09

P4•H16

O INTO A

G10

G10

SD•Y2+3

P4•SD•H3

43

O INTO B

H3

4444445398338

444444544554

G2

P4•H7

S(D) D=8

G3

S(Y) (LOOK ATS7)

03

P5•H16

G16

D8•X17

DP•LR•BSP

READ (S7 INTO A)

DP

Н2

P5•H2

G5

G5

S(SD) (S(SD) PREVENTS S(D) NEXT TIME)

DP • Y3

H4

P5•H4

G4

1 INTO SP

55445923858

544444444

SD.DP.BSP

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

P6•H16

G17

G17

O INTO S(P)

S(A)

S(A)

P7•H16

G15

P8•H7

COUNTS A DOWN

COUNTS B UP TO An

G15

WRITE (B INTO S7)

G3

S(Y) (LOOK AT RA)

1 INTO SS

1 INTO OP

0 INTO B OUTPUT LINES

1 INTO SP OR DASH OR Pt

G3

45

59

52a

P9.LR

P9.LR.Y3

43

PT • X17

NOTE:

OUR EXAMPLE WILL USE DASH

55

55

1 INTO 6-7 LINE

1 INTO DASH LINE

1 INTO DASH

OP DASH OF CS • (Y8-12 OR BCS OR 25-8)

RIBBON CONTACTS CLOSE

1 INTO RIBB

55

52b

52b

52b

INTO RIBB LINE

Ōĸ

O INTO OP

OK TIMES OUT OK. OP

O INTO SS

```

## FIG\_28-5

#### J. KRAMMER

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 83 of 125

INSTRUCTION C20 TYPE AUTOMATIC DATE (CONTINUED)

PHASE 5

```

OPERATION

PO•H6

SIGNAL

FIG.

48

Фб

46

q6

D NEG

48

P4-H16

a9

42

48

O INTO A

G9

P4.H16

G10

G10

SD•Y2+3

O INTO B

43

49a

48

H3

P4.H3

46

48

48

48

G2

P4•H7

S(D)

G3

S(Y) (LOOK AT S7)

G5

S(SD)

G3.

P5•H2

05

P5•H16

53

48

G16

45

53

53

48

G16

READ (S7 INTO A)

¥17 • D8

DP

Y3•DP

P5•H4

G4

H<sup>4</sup>

G4

52a

1 INTO SP

48

P6.H16

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

42

G17

59

42

O INTO S(P)

S(A)

S(A)

43

48

45

COUNTS B UP TO An

G15

WRITE (B INTO S7)

P7•H16

G15

B NOW HAS A DIGIT THEN BO

İF

43

(HC)

BO

49c

(HO)

ĤΟ

48

Р̂7•Но

G1

G1

O INTO SP

G3

S(Y) (LOCK AT RA)

INTO SP

P8•H7

45

G3

P9.LR

59

P9.LR.Y3

FF NOT RESET ON P7

INTO CP

SP OP.SP.CS.(Y8-12 OR BCS OR 1 IN

25-8)

62 1 INTO 8-9.SP LINE TYPE

62 SPACE BAR CONTACTS SP 1 IN

52b 1 INTO SP LINE OK

SP FF RESET ON P7 (NUMBER WILL BE A ONE)

43 Ba

43 Bd.Bc.Bb

43 1 INTO 13570

O INTO B (OUTPUT LINES)

1 INTO 8-9 LINE

1 INTO SP LINE

1 INTO SP LINE

OK

TYPE SPACE

1 INTO 13579 LINE

1 INTO 0-1 LINE

1 INTO 13579 LINE OP CS

(Y8-12 OR BCS OR Z5-8)

1 INTO 1 O-1 LINE

RIBBON CONTACTS CLOSE

1 INTOILINE

62

62

TYPE DIGIT 1

1 INTO RIBBON LINE

1 INTO RIBBON LINE

52b

52b

52b

O INTO CP

ŏκ.

OK TIMES OUT

O INTO SS

OK OP

52b

REPEAT TILL D=7

```

#### FIG\_28~6

## PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 84 of 125

# INSTRUCTION C20 TYPE AUTOMATIC DATE (CONTINUED) PHASE 6

## FIG\_28-2

### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 85 of 125

# INSTRUCTION C21 S(R) STEP R COMMAND LEVEL H13

| FIG.              | OPERATION     | SIGNAL       |

|-------------------|---------------|--------------|

| 61                | PATCH         | C21          |

| 61                | C21           | <u>Y1</u> Z8 |

| 49 <b>b</b><br>48 | <u>Y1•</u> Z8 | H13          |

|                   | PO•H13        | gj5′         |

| 45                | G12           | <u>S(</u> R) |

| 55                | Z1•Y1         | ZI•Ý1 SIGNAL |

| 51                | P9.DO.(Z1.Y1) | 3(1)         |

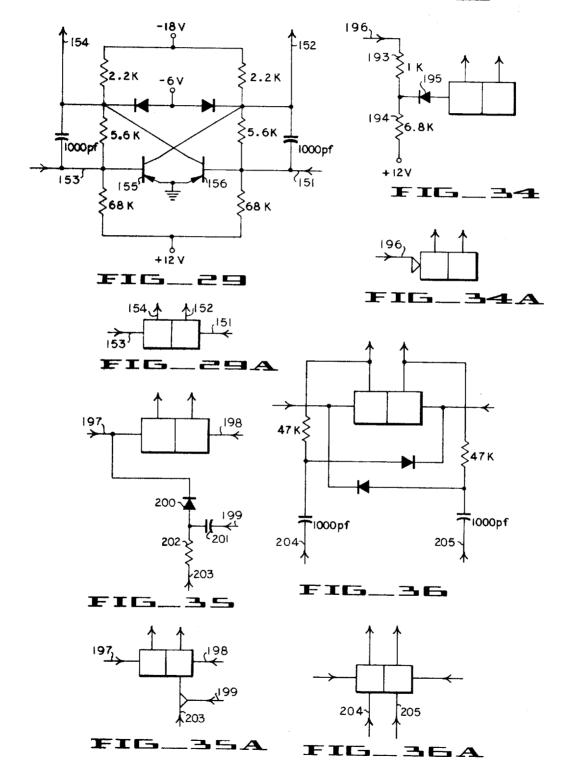

### FIG\_29

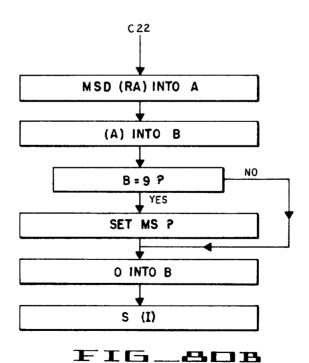

# INSTRUCTION C22 RA NEG 1 INTO MSC COMMAND LEVEL H19

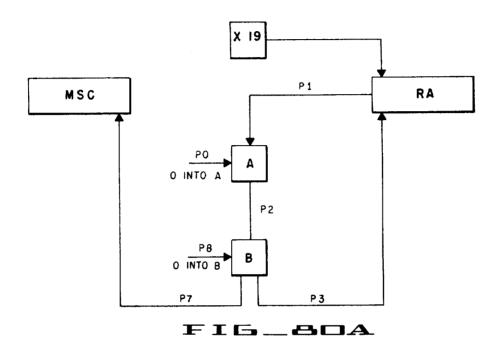

### FIG\_AD

Dec. 31, 1968

J. KRAMMER

3,419,850

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet <u>86</u> of 125

Filed Oct. 21, 1965

Sheet <u>87</u> of 125

Filed Oct. 21, 1965

Sheet <u>88</u> of 125

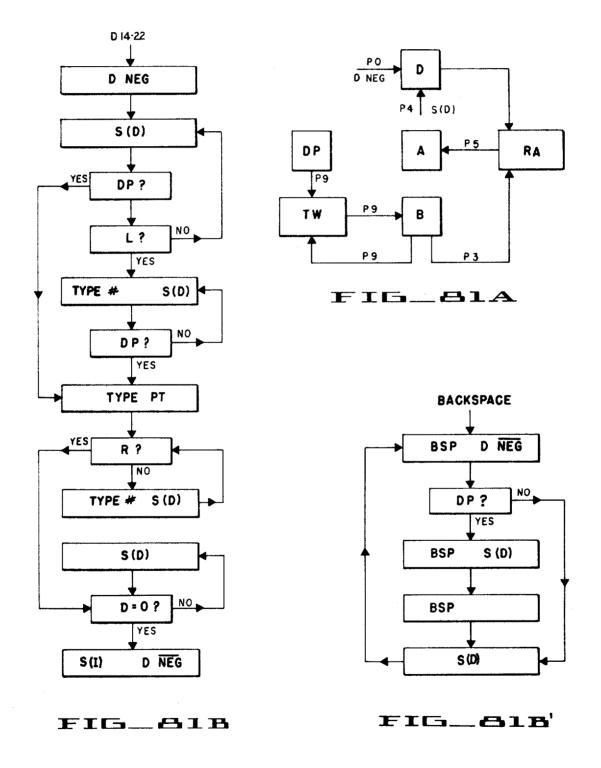

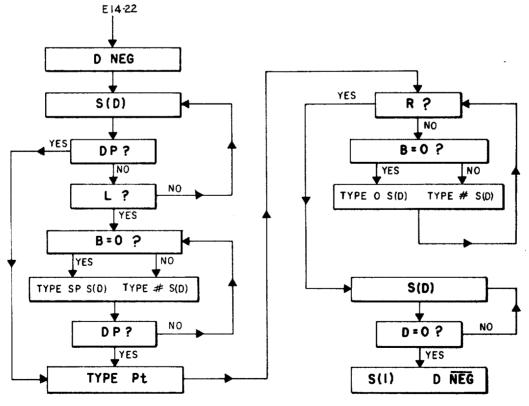

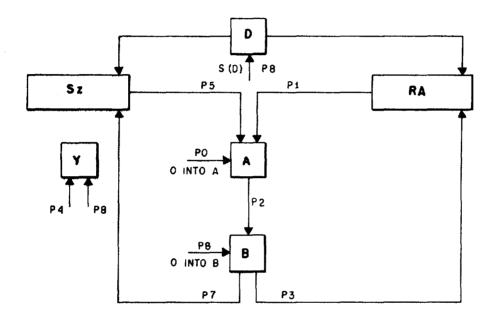

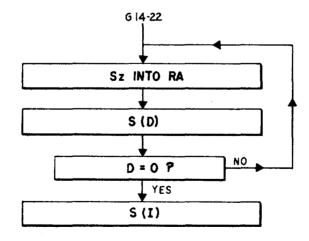

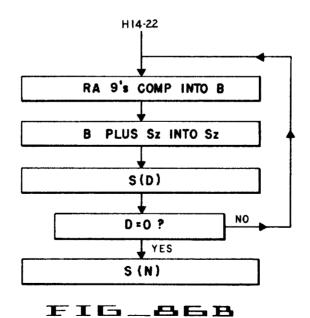

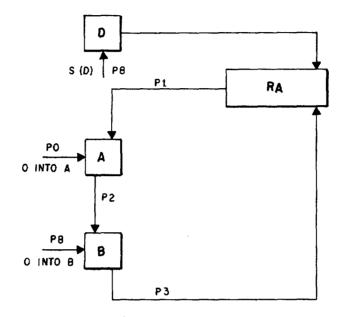

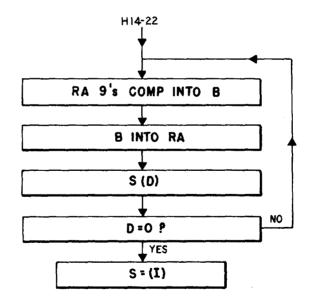

INSTRUCTION D14-22 TW INTO RA (LRD 1-9)

COMMAND LEVELS H15 LRD 2L.2R HC.H3.H6.H15

```

FIG.

OPERATION

SIGNAL

SIGNAL

D14

Y2

Y2 OR 3

Z1

H15

H13+H0

G12

S(R)

H6

61

61

61

PATCH

D14

Y2

D14

Y2

DO•Y2

PO·H13

G12

Y2 OR 3·BSP

PO·H6

G6

G6

46

48

D NEG (COUNT DOWN)

P3•H15

G15

G15

WRITE (B INTO RA)

45

48

P4.H15

G10

G10

SD•Y2 OR 3

O INTO B

H3

G2

S(D)

P4+H3

G2

48 P5•H15

45 G16

REPEAT TILL D=6

48 P4•H15

gì6

READ (RA INTO A)

P4•n15

G10

SD•Y2 OR 3

P4•H3

G10

43 a

4986 333338 592 a

4555544555

O INTO B

H3

G2

S(D) (D=5)

C37•38

F36

(L)

1 INTO LR

G16

G2

Z1

21

C37 PATCH

F36•D5

(L)•Y2 OR 3•X17

P5•H15

G16

READ (RA INTO A)

1 INTO SS (STOPS PG)

1 INTO IP

P9.LR

P9.LR.Y2.PT

TYPE SPACE

```

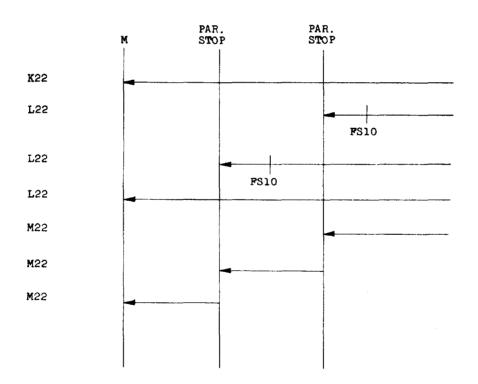

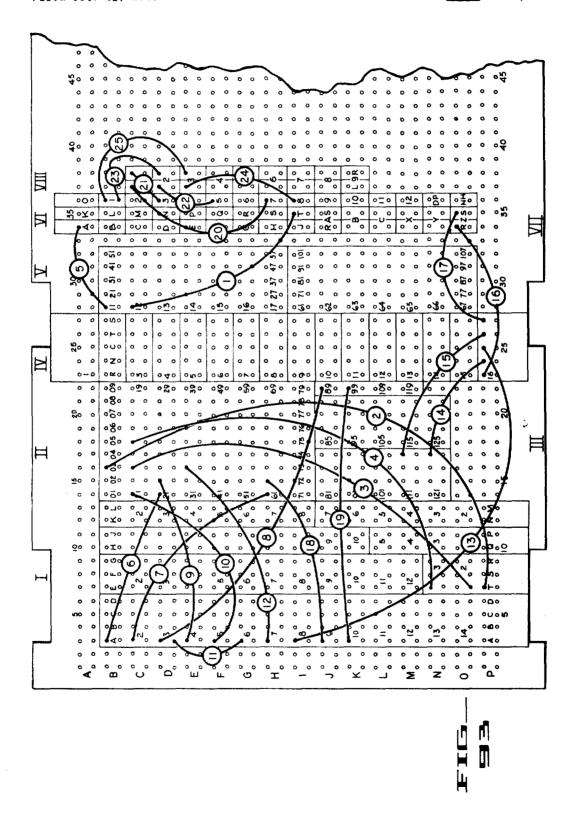

## FIG\_81-1

Filed Oct. 21, 1965

Sheet 89 of 125

#### INSTRUCTION D14-22 TW INTO RA (LRD 1-9)

```

OPERATION SPACE BAR

O INTO AR

52a

KSP

KSP+BS+KO+K1-9.0K.OP.

IP.(X-KCS)

AR

52a

ENABLE OSHC

FIRES OSHC

1 INTO SP FF

SP

52a

52a

52a

52a

52a

555

555

OBHC • KSP

SP FF

OSHC TIMES OUT

1 INTO OP O INTO IP

O INTO B OUTPUT LINES

1 INTO 8-9 LINE

SP

OP SP CS (Y8-12 OR BCS

OR Z5-8)

1 INTO 8-9 LINE

SPACE BAR CONTACTS

1 INTO SP LINE

OK

OK TIMES OUT

OK OP

P3 + H15

1 INTO SP LINE

TYPE SPACE

1 INTO SP LINE

52b

52b

O INTO OP

0 INTO SS (RESTARTS PG)

G15

52b

52b

48

P3•H15

G15

P4•H15

45

48

WRITE (B INTO RA)

G10

O INTO B

43

49a

48

<u>G</u>10

SD Y2 OR 3

H3

P4•H3

46

G2

S(D) (D=4)

48

P5.H15

G16

45

59

52

Q16

READ (RA INTO A)

1 INTO SS

1 INTO IP

P9.LR

P9.LR.Y2.PT

TYPE DIGIT 1

```

Filed Oct. 21, 1965

TYPE DIGIT

Sheet 90 of 125

INSTRUCTION D14-22 TW INTO RA (LRD 1-9) FIG. 62 62 OPERATION #1 KEY SIGNAL K1-9 K1-9 LINE K1-9 K1-9 LINE KSP+BS+KO+K1-9 • OK•OF•IP•(X•KCS) 52a O INTO AR 52a ENABLES OSHC FIRES OSHC.O INTO SP 1 INTO Ba 1 INTO OP O INTO IP 1 INTO 13579 LINE 1 INTO 0-1 LINE 52a AR 43 OSHC • K1 52a,b 43 43 43 OSHC TIMES OUT Ba · Bc · Bb 1 INTO 13579 LINE OP CS (Y8-12 OR BCS OR Z5-8)

1 INTO 1 O-1 LINE

RIBBON CONTACTS CLOSE

1 INTO RIBB LINE

OK TIMES OF THE 1 INTOILINE 62222222 6666228 TYPE DIGIT 1 1 INTO RIBB LINE

OK

O INTO OP

OK

O INTO SS (RESTARTS PG) OK TIMES OUT OK. OF P3.H15 G15 G15 P4•H15 WRÍTE (B INTO RA) **G1**0 O INTO B G10 SD-Y2 OR 3 P4.H3 G2 46 S(D) (D=3) (Dp) DP G2 53 53 49a 48 D3 (Dp)• <del>X17</del> DP•LR•BSP H2 P5.H2 05 S(SD) 53 53 49a 48 05 SD . DP . BSP Ρt DP • X17 HO P7.H0 Gl 52a Gi O INTO SP 59 52a P9.LR 1 INTO SS (STOPS PG) PG.Pt 43 55 Pt Pt•X17 O INTO B OUTPUT LINES 1 INTO 8-9 LINE OP•Pt•CS•(Y8-12 OR BCS OR Z5-8) RIBB CONTACTS CLOSED 55 1 INTO DECIMAL LINE 55 52**a** 52**a** 1 INTO RIBB LINE 1 INTO RIBB ΟK O INTO OP OK 52a 52a OK TIMES OUT OK. OP O INTO SS (RESTARTS PG) 48 P3.H15 G15 WRITE (B INTO RA) 45 **G**15 P4.H15 G10 43 G10 O INTO B 49a DP . LR . BSP H2 48 P5.H2 G5 S(SD) 53 59 52a G5 P9•LR P9•LR•Y2•PT 1 INTO SS (STOPS PG) 1 INTO IP

Filed Oct. 21, 1965

Sheet 9/ of 125

INSTRUCTION D14-22 TW INTO RA (LRD 1-9)

```

OPERATION

FIG.

SIGNAL

62

62

#1 KEY

K1-9

K1-9 LINE

K1-9

K1-9 LINE

KSP+BS+K0-K1-9+0K+OF+

(X+KCS)

AR

52a

O INTO AR

52a

ENABLES OSHC

52a

43

52a,b

43

43

FIRES OSHC

OSHC • K1

OSHC TIME OUT

1 INTO Ba

1 INTO OP•O INTO IP

1 INTO 13579 LINE

1 INTO 0-1 LINE

\frac{Ba}{Bd \cdot Bc \cdot Bb}

1 INTO 13579 LINE OP CS (VB-12 OR BCS OR Z5-8)

1 INTO 1 O-1 LINE

RIBBON CONTACTS CLOSE

1 INTO 1 LINE

6222228583a

448448

TYPE DIGIT 1

1 INTO RIBB LINE

1 INTO RIBB LINE

O INTO OP

OK TIMES OUT OK OF

ΟK

O INTO SS (RESTARTS PG)

P3.H15

G15

P4.H15

G10

SD.Y2 OR 3

WRITE (B INTO RA)

G10

O INTO B

H3

G2

S(D) (D=2)

G16

P4•H3

G2

P5.H15

READ (RA INTO A)

1 INTO SS (STOPS PG)

1 INTO IP

45

G16

P9.LR

P9.LR.Y2.PT

TYPE DIGIT

```

Filed Oct. 21, 1965

Sheet 92 of 125

INSTRUCTION D14-22 TW INTO RA (LRD 1-9)

```

FIG.

OPERATION

SIGNAL

62

62

K1-9

K1-9 LINE

#1 KEY

K1-9

K1-9 LINE

OK•OF•IP•(X•KCS)

O INTO AR

O INTO AR

ENABLES OSHC

FIRES OSHC

1 INTO Ba

1 INTO OP O INTO IP

1 INTO 13579 LINE

1 INTO 0-1 LINE

1 INTO 1 LINE

52a

52a

52a

52a

52a

52a

543

443

AR

OSHC·K1

OSHC TIMES OUT

Ba

Bd · Bc · Bb

Bd·Bc·Bb

1 INTO 13579 LINE·OP·CS·

(Y8-12 OR BCS OR Z5-8)

1 INTO 1·O-1 LINE

RIBBON CONTACTS CLOSE

1 INTO RIBB LINE

OK

OK TIMES OUT

OK·OP

222222285839863333385858398

TYPE DIGIT 1

1 INTO RIBB LINE

O INTO OP

OK

O INTO SS (RESTARTS PG)

Q15

WRITE (B INTO RA)

P3.H15

G15

P4.H15

G10

O INTO B

H3

G2

010

SD•Y2 OR 3

P4.H3

S(D) (D=1)

C37·C38

B36

G2

z_1

C38 PATCH

R

O INTO LR

B36 • D1

R•Y2 OR 3•X17

P5•H15

Q16

G16

READ (RA INTO A)

P3.H15

G15

P4.H15

G10

SD.Y2 OR 3

G15

WRITE (B INTO RA)

G10

O INTO B

H3

G2

S(D) (D=0)

S(I)

D NEG

P4.H3

G2

P9.D0.Y2 OR 3

P9.S(I)

51

46

```

Filed Oct. 21, 1965

Sheet <u>93</u> of 125

INSTRUCTION D1 $^4$ -22 TW INTO RA (LRD 1-9) BACK SPACE IN ENTRY FIELD AT ANY POINT OTHER THAN THE FIRST PLACE TO THE RIGHT OF THE DECIMAL.

| FIG.<br>42<br>52b<br>52a<br>52b<br>52b<br>52b<br>52b<br>52b<br>52b<br>52b | OSHC TIMES OUT  1 INTO BS LINE  OK  OK TIMES OUT  OK-OP  PO-B52-Y2 OR 3 | SIGNAL  1 INTO BS LINE AND BACK SPACE TW CARRIAGE O INTO AR FIRE OSHC 1 INTO BSP (DISABLE PT) 1 INTO OP O INTO IP OK O INTO OP OK O INTO SS (RESTART PG) G18 |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52b                                                                       | 1 INTO BS LINE                                                          | $\overline{O}\overline{K}$                                                                                                                                   |

|                                                                           |                                                                         |                                                                                                                                                              |

| 520<br>52h                                                                |                                                                         |                                                                                                                                                              |

| 48                                                                        |                                                                         |                                                                                                                                                              |

| 46                                                                        | G18                                                                     | D NEG                                                                                                                                                        |

| 48                                                                        | P3•H15                                                                  | 015                                                                                                                                                          |

| 45                                                                        | G15<br>SD•Y2 OR 3                                                       | WRITE                                                                                                                                                        |

| 49 <b>a</b><br>48<br>46                                                   |                                                                         | н3                                                                                                                                                           |

| 48                                                                        | P4•H3                                                                   | <b>G</b> 2                                                                                                                                                   |

| 46                                                                        | <b>G</b> 2                                                              | S(D) (UP)                                                                                                                                                    |

| 48<br>4 <b>3</b><br>48<br>45                                              | P4•H15                                                                  | <b>G1</b> 0                                                                                                                                                  |

| <sup>1</sup> 3                                                            | <b>G</b> 10                                                             | O INTO B                                                                                                                                                     |

| 48                                                                        | P5•H15                                                                  | <b>0</b> 16                                                                                                                                                  |

| 45                                                                        | <b>0</b> 16                                                             | READ (RA INTO A)                                                                                                                                             |

| 59                                                                        | P9•LR                                                                   | 1 INTO SS (STOP PG)                                                                                                                                          |

| 52 <b>a</b>                                                               | P9·LR·Y2·PT                                                             | 1 INTO IP                                                                                                                                                    |

| TYPE COR                                                                  | RECT DIGIT                                                              |                                                                                                                                                              |

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 99 of 125

INSTRUCTION D14-22 TW INTO RA (LRD 1-9)

BACK SPACE IN ENTRY FIELD AT THE FIRST PLACE TO THE RIGHT OF THE DECIMAL.

```

FIG.

OPERATION

SIGNAL

62

52b

BACK SPACE

1 INTO BS LINE

0 INTO AR

1 INTO BS LINE AND BACK SPACE TW CARRIAGE O INTO AR

52a

FIRE OSHC

1 INTO BSP (DISABLE PT)

1 INTO OP O INTO IP

1 INTO BS LINE OSHC

OSHC TIMES OUT

1 INTO BS LINE

OK

OK TIMES OUT

OK OP

52b

52b

52b

52b

O INTO OP

52b

52b

48

O INTO SS (RESTART PG)

PO.BSP.Y2 OR 3

G18

G18

BSP·DP

PO·H1

46

D NEG (D COUNTS UP)

49a

48

S(SD) (SET SD)

P3.H15

G15

P4.H15

Gis

45

48

WRITE

G10

O INTO B

43

G10

P5.H15

G16

45

016

READ (RA INTO A)

59 P9.LR

52a P9.LR.Y2.Pt

TYPE SECOND BACKSPACE

1 INTO SS (STOP PG)

1 INTO IP

DACKSPACE

BACK SPACE

1 INTO BS LINE

0 INTO AR

1 INTO BS LINE OSHC

OSHC TIMES OUT

1 INTO BS LINE

OK

62

1 INTO BS LINE AND BACK SPACE TW CARRIAGE

52b

O INTO AR

52a

52b

52b

52b

FIRE OSHC

1 INTO BSP (DISABLE PT)

1 INTO OP O INTO IP

OK

O INTO OP

OK

52b

52b

OK TIMES OUT

52b

48

OK. OP

PO. BSP. Y2 OR 3

O INTO SS (RESTART PG)

G18

BSP•DP

PO•H1

46

D NEG

49a

48

Hl

S(SD) (RESET SD)

48

P3.H15

015

SD•Y2 OR 3

45

WRITE

H3

49a

48

P4-H3

02

P4•H15

46

48

S(D) (UP)

gio

43

48

O INTO B

G10

P5•H15

016

016

45

59

READ (RA INTO A)

1 INTO SS (STOP PG)

1 INTO IP

P9.LR

P9.LR.Y2.PT

52a

TYPE CORRECT DIGIT

```

Filed Oct. 21, 1965

Sheet 95 of 125

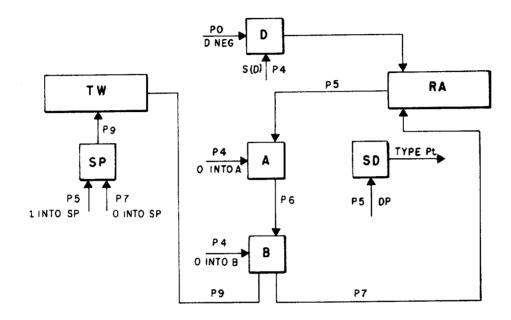

### FIG\_82A

FIG\_ACB

Filed Oct. 21, 1965

Sheet 96 of 125

# INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9) COMMAND LEVELS H6 H16 H0 H3

```

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

REPEAT TILL D=6

```

#### FIG\_82-1

#### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 97 of 125

INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9)

COMMAND LEVELS H6 H16 H3 H4

FIRST DIGIT=SPACE

```

FIG.

OPERATION

SIGNAL

G9

O INTO A

48

P4.H16

42

G9

48

P4•H16

G10

O INTO B

G10

SD•Y2 OR 3

P4•H3

43a

498

486

5533333

48

O INTO B

H3

G2

S(D) (D=5)

D37-38

(L)

L

LR

G2

Z2

D37 • D5

(L)

(L)•Y2 OR 3•\overline{Y17}

LR•\overline{X17}•Y3

H4

H4

H4

P5.H4

G4

52a

48

G4

1 INTO SP FF

P5•H16

G16

G16

4445444599a

5554555

READ (RA INTO A)

P6•H16

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

G17

G17

0 INTO S(P)

S(A)

P7.416

G15

P9.LR

P9.LR P9.LR

G15

WRITE (B INTO RA)

1 INTO SS

1 INTO OP

0 INTO B (OUTPUT LINES)

1 INTO 8-9 LINE

SP

OP SP CS (Y8-12 OR

BCS OR Z5-8)

1 INTO 8-9 LINE

SPACE BAR CONTACTS SP

1 INTO SP LINE

OK

1 INTO SP LINE

62

TYPE SPACE

1 INTO SP LINE

OK

O INTO OP

OK

62

52b

52b

52b

OK TIMES OUT

52b

O INTO SS

```

### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 98 of 125

INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9)

COMMAND LEVELS H6 H16 H3 H0

SECOND DIGIT = #1

```

FIG.

OPERATION P4.H16

SIGNAL

G9

O INTO A

09

P4•H16

42

48

G10

010

SD•Y2 OR 3

398685829238

4444444544

O INTO B

H3

G2

P4.H3

G2

S(D) (D=4)

G16

READ (RA INTO A)

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

02

P5•H16

Q16

P6.H16

G17

O INTO S(P)

S(A)

S(A)

P7•H16

45 G15

B NOW HAS A DIGIT THEN BO

43 BO

WRITE (B INTO RA)

(HO)

49c

48

(HO)

P7•HO

G1

ĤΟ

Gl

52a

59

52a

43

43

G1

O INTO SP

1 INTO SS

1 INTO OP

1 INTO 13579 LINE

1 INTO O-1 LINE

P9.LR

P9.LR.Y3

Ba

Bd•Bc•Bb

Bd-Bc-Bb

1 INTO 13579 LINE-OP-

CS-(Y8-12 OR BCS OR Z5-8)

1 INTO 1-O-1 LINE

RIBBON CONTACTS CLOSE

1 INTO RIBB LINE

OK

1 INTO 1 LINE

62

62

62

62

62

62

TYPE DIGIT 1

1 INTO RIBB LINE

O INTO OP

OK TIME OUT

OK

O INTO SS

```

Filed Oct. 21, 1965

Sheet 99 of 125

INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9)

COMMAND LEVELS H6 H16 HC H2 H3

TYPE DECIMAL

```

OPERATION

SIGNAL

48

P4.H16

G9

O INTO A

G10

42

G9

48

P4•H16

O INTO B

H3

G2

S(D) (D=3)

(Dp)

43

49a

48

G10

SD•Y2 OR 3

Р4•Н3

46

53398

45548

5548

G2

D3

(Dp)•X17

DF•LR•BSP

P5•H2

G5

ĎΡ

05

S(SD)

SD. DP. BSP

Ρt

P5•H16

G16

45

48

READ (RA INTO A)

COUNTS A DOWN

COUNTS B UP TO An

Р6•н16

G17

O INTO S(P)

S(A)

S(A)

P7. H16

42

5443845a

44548

G15

WRITE (B INTO RA)

P7•H16

G15

DP•X17

P7•H0

G1

P9•F

P9•LR

PT

PT•X17

но

G1

52a

52b

559

43

555

O INTO SP

1 INTO CP

1 INTO SS (STOPS PG)

C INTO B (CUTPUT LINES)

1 INTO 8-9 LINE

PI • X17

OP • PT • CS • (Y8-12 OR

BCS OR Z5-E)

RIBB CONTACTS CLOSE

1 INTO RIBB

OK

1 INTO DECIMAL LINE

55

52b

52b

52b

1 INTO RIBB LINE

OK

O INTO OP

OK

OK TIMES OUT OK OF

52b

O INTO SS (RESTARTS PG)

```

Filed Oct. 21, 1965

Sheet /00 of 125

INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9)

COMMAND LEVELS H6 H16

TYPE ZERO

```

FIG.

OPERATION

SIGNAL

G9

O INTO A

48

P4.H16

G9

P4•H16

28 3 98 38 58 2 9 2 38

24 4 4 4 5 4 4 4 4 5 4 4 4

G10

G10

O INTO P

DP•LR•BSP

P5•H2

G5

P5•H16

Н2

G5

S(SD) (DIGIT COUNTER MAY NOW BE STEPPED)

READ (RA INTO A)

@16

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

P6•H16

G17

0 INTO S(P)

S(A)

S(A)

P7.416

G15

G15

WRITE (B INTO RA)

45

B NOW CONTAINS A ZERO

NTAINS A ZERO

P9•LR

P9•LR•Y3

B AT O

B AT O

OP•24680 LINE•O-1

LINE•CS•(Y8-12 OR

BCS OR Z5-8)

1 INTO O LINE

RIBB CONTACTS CLOSE

1 INTO RIBB LINE

OK TIMES OUT

59

52a

43

43

55

1 INTO SS (STOPS PG)

1 INTO OP

1 INTO 24680 LINE

1 INTO 0-1 LINE

1 INTO 0 LINE

62

62

52b

52b

TYPE ZERO

1 INTO RIBB LINE

O INTO OP

OK TIMES OUT

oĸ.

52b

52b

O INTO SS

```

#### FIG\_82-5

#### J. KRAMMER

PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 20/ of 125

INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9)

COMMAND LEVELS H6 H16 H0 H3 H

TYPE DIGIT 1

```

FIG.

48

42

48

OPERATION

SIGNAL

P4•H16

09

0 INTO A

010

09

P4•H16

G10

SD•Y2 OR 3

43

49a

48

O INTO B

H3

P4+H3

46

G2

S(D) (D=2)

P5.H16

44454444

G16

READ (RA INTO A)

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

G15

WRITE (B INTO RA)

P6•H16

G17

O INTO S(P)

S(A)

S(A)

P7•H16

B NOW HAS A DIGIT THEN BO

43

(HO)

19c

48

(HO)

P7•HO

ĤΟ

G1

52a

592a

552a

43

43

Ġì

O INTO SP

P9.LR

1 INTO SS

1 INTO OP

1 INTO 13579 LINE

P9.LR.Y3

P9.LR.Y3

Ba

Bd.Bc.Bb

1 INTO 13579 LINE.OP.

CS.(Y8-12 OR BCS

OR 25-8)

1 INTO 1.0-1 LINE

RIBBON CONTACTS CLOSE

1 INTO RIBB LINE

OK

1 INTO 0-1 LINE

1 INTO 1 LINE

TYPE DIGIT 1

1 INTO RIBB LINE

OK

62

62

62

62

62

62

62

62

62

O INTO OP

OK

OK INTO SS

OK TIMES OUT OK OF

```

#### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 102 of 125

INSTRUCTION E14-22 OUTPUT RA INTO TW (LRD 1-9)

COMMAND LEVELS H6 H16 H3

```

FIG.

OPERATION

SIGNAL

48

42

48

G9

O INTO A

P4.H16

G9

P4•H16

010

O INTO B

G10

SD•Y2 OR 3

P4•H3

S(D) (D=1)

(R)

O INTO LR

G16

G2

D38•D1

X17•(R)•Y2 OR 3

P5•H16

G16

READ (RA INTO A)

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

P6.H16

G17

O INTO S(P)

S(A)

S(A)

P7•H16

G15

WRITE (B INTO RA)

G15

P4•H16

G9

O INTO A

G10

09

P4•H16

0 INTO B

H3

G2

S(D) (D=0)

G16

G10

SD•Y2 OR 3

P4 • H3

G2

P5•H16

45

48

G16

READ

READ

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

P6•H16

PO+HIO

G17

O INTO S(P)

S(A)

S(A)

P7+HIO

G15

P9+DO+Y2 OR 3

P9+S(I)

42

59

43

48

G15

WRITE

45

51

46

S(I)

D NEG

```

#### Filed Oct. 21, 1965

Sheet 103 of 125

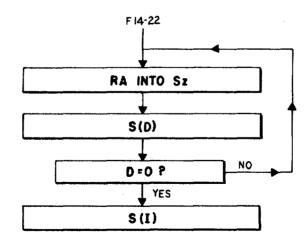

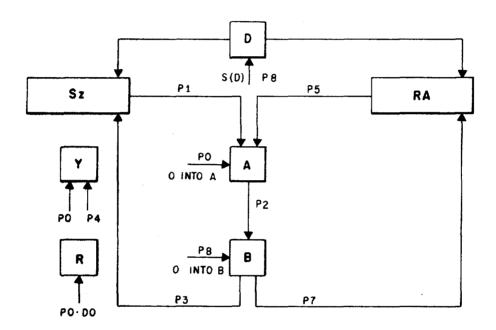

INSTRUCTION F14-22 STORE (RA INTO Sz) (RA INTO RA) Sz 1-9 COMMAND LEVELS H7 H9 H18 H19

```

FIG.

OPERATION

SIGNAL

¥4

PO•H19

н7 н9 н18 н19

09

P1•H19

G16

O INTO A

READ (RA INTO A)

P2.H19

G17

O INTO S(P)

S(A)

S(A)

G17

O INTO S(P)

ENABLES S(A) DISABLES T(P)

COUNTS A DOWN

COUNTS B UP TO An

P3•H19

G15

P4•H7

G15

WRITE (B INTO RA)

G3

S(Y) (LOOK AT Sz)

G16

READ (Sz INTC A) (CLEAR Sz)

P5•H18

G16

P7•H18

G15

P8•H18

G15

WRITE (B INTO Sz)

G10

G10

P8•H9

O INTO B

G2

S(D)

46 G2

48 PE•H7

45 G3

REPEAT TILL D(0)

51 P9•Y4•D0

G3 S(Y) (LOCK AT RA)

S(I)

```

#### FIG\_A3

Filed Oct. 21, 1965

Sheet 104 of 125

F16\_83A

FIG\_83B

#### J. KRAMMER

### PROGRAMMABLE COMPUTER UTILIZING NONADDRESSABLE REGISTERS

Filed Oct. 21, 1965

Sheet 105 of 125

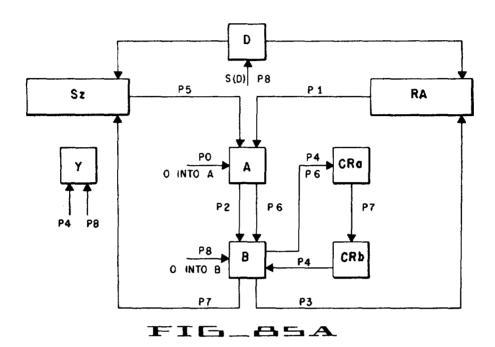

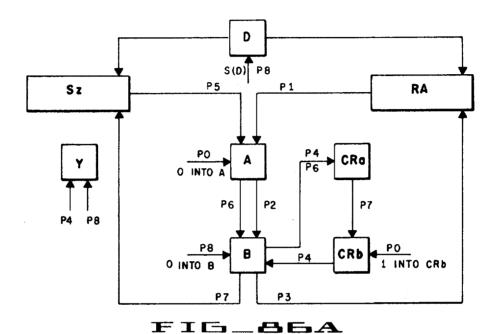

INSTRUCTION G14-22 RETRIEVE (Sz INTO RA) (Sz INTO Sz)\$1-9

COMMAND LEVELS H8 H9 H13 H18 H19

```

OPERATION

SIGNAL

G14

Y5 Z1

H13

H8 H9 H18 H19

G12

PATCH

G14

Y5•D0

Y5

PO•H13

G12

PO•H19

S(R)

09

0 INTO A