# FUJITSU

### SCIENTIFIC & TECHNICAL JOURNAL

# Summer 1993 VOL. 29, NO. 2

The Issue's Cover :

盛花 (Flowering)

FUJITSU Scientific & Technical Journal is published quarterly by FUJITSU LIMITED of Japan to report the results of research conducted by FUJITSU LIMITED, FUJITSU LABORATORIES LTD., and their associated companies in communications, electronics, and related fields. It is the publisher's intent that FSTJ will promote the international exchange of such information, and we encourage the distribution of FSTJ on an exchange basis. All correspondence concerning the exchange of periodicals should be addressed to the editor.

FSTJ can be purchased through KINOKUNIYA COMPANY LTD., 38-1, Sakuragaoka 5-Chome, Setagaya-ku, Tokyo 156, Japan, (Telephone : +81-3-3439-0162, Facsimile : +81-3-3706-7479).

The price is US\$7.00 per copy, excluding postage.

FUJITSU LIMITED reserves all rights concerning the republication and publication after translation into other languages of articles appearing herein.

Permission to publish these articles may be obtained by contacting the editor.

| FUJITSU LIMITED           | Tadashi Sekizawa, President |

|---------------------------|-----------------------------|

| FUJITSU LABORATORIES LTD. | Mikio Ohtsuki, President    |

| Editorial Board                |       |                |       |                 |

|--------------------------------|-------|----------------|-------|-----------------|

| Editor                         | Shig  | eru Sato       |       |                 |

| Associated Editors             | Hajir | me Ishikawa    | Hideo | Takahashi       |

| <b>Editorial Representativ</b> | es    |                |       |                 |

| Sadao Fujii                    |       | Tetsuya Isayar | ma    | Yoshihiko Kaiju |

| Masasuke Matsun                | noto  | Yoshimasa Mi   | ura   | Makoto Mukai    |

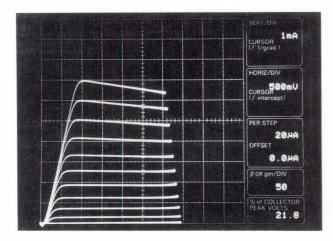

| Junzo Nakajima                 |       | Yasushi Nakaj  | ima   | Koichi Niwa     |

| Hajime Nonogaki                |       | Juro Ohga      |       | Shinji Ohkawa   |

| Shinya Okuda                   |       | Teruo Sakurai  |       | Yoshio Tago     |

| Shozo Taguchi                  |       | Kunihiro Tanig | lawa  | Makoto Saito    |

| Takaki Shimura                 |       | Mitsuhiko Tod  | а     | Takao Uehara    |

| Akira Yoshida                  |       |                |       |                 |

### **Editorial Coordinator**

Editorial Roard

#### Yukichi Iwasaki

FUJITSU LIMITED 1015 Kamikodanaka, Nakahara-ku, Kawasaki 211, Japan Cable Address : FUJITSULIMITED KAWASAKI Telephone : +81-44-777-1111 Facsimile : +81-44-754-3562

Printed by MIZUNO PRITECH Co., Ltd. in Japan © 1993 FUJITSU LIMITED (June 15, 1993)

# FUjitsu

SCIENTIFIC & TECHNICAL JOURNAL Summer 1993 VOL. 29, NO. 2

### CONTENTS

### Papers

| 119 | · · · · · · · · · · · · · · · · · · · | sor Systems<br>Mayumi Kamiko               | ● Takashi Chikayama           |

|-----|---------------------------------------|--------------------------------------------|-------------------------------|

| 128 |                                       | uted Grammer<br>Hiroshi Saijo              | ● Chikao Shioya               |

| 137 | · · · · · · · · · · · · · · · · · · · | lulti-Level Logic Mini<br>Yusuke Matsunaga | mization                      |

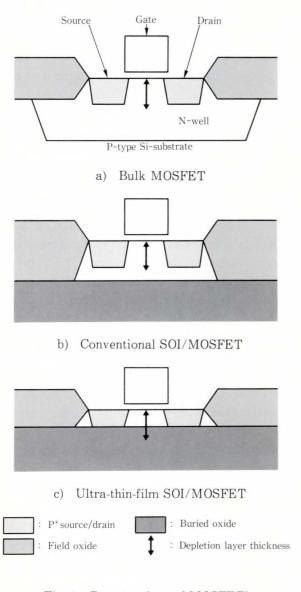

| 146 |                                       | Im SOI/pMOSFET's a<br>Seiichiro Kawamura   | at 90-300 K                   |

| 154 | · · · · · · · · · · · · · · · · · · · | endent Dielectric Br<br>Sadahiro Kishii    | eakdown<br>●Akira Ohsawa      |

| 161 |                                       | ons Systems<br>Yoshiharu Tozawa            | ● Toshio Kawasaki             |

| 169 |                                       | T Applications<br>Hideyasu Ando            | ●Adarsh Sandhu                |

| 180 |                                       | Oriented Specificatio<br>Moo Wan Kim       | on Language<br>● Hideo Yunoki |

| 189 |                                       | <b>ks</b><br>Kazuyuki Watanabe             |                               |

# ParaGraph: A Graphical Tuning Tool for Multiprocessor Systems

Seiichi Aikawa

Mayumi Kamiko

Takashi Chikayama

Takashi Chikayama (Manuscript received November 30, 1992)

Distributing computational load to many processors is a critical issue for efficient program execution on multiprocessor systems. Finding a good load distribution algorithm is one of the most important research topics for parallel processing. Tools for evaluating load distribution algorithms are very useful for this kind of research. This paper describes a system called ParaGraph that gathers periodical statistics of the computational and communication load of each processor during program execution, in both the higher level of programming language and lower level of implementation, and presents them graphically to the user.

### 1. Introduction

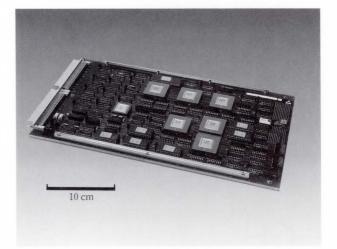

In the Japanese Fifth Generation Computer Systems Project, parallel inference systems have been developed for promoting parallel software research and development. The system adopts a concurrent logic programming language KL1<sup>1)</sup> as the kernel and consists of a parallel inference machine, PIM<sup>2)</sup> and its operating system, PIMOS<sup>3)</sup>.

For efficient program execution, the computational load must be appropriately distributed to each processor. On scalable loosely-coupled multiprocessor systems, load balancing and minimization of communication overhead are essential, but become more difficult compared to tightly-coupled systems as communication costs increase. Although many load distribution algorithms have been developed<sup>4). 5)</sup>, none have been sufficient to execute every program effectively. Finding a good load distribution algorithm is one of the most important research topics for parallel processing.

Tools for evaluating load distribution algorithms are very useful for this kind of research. The objective of the ParaGraph system is to help programmers design and evaluate load distribution algorithms on loosely-coupled multiprocessor systems. ParaGraph gathers profiling information during program execution on the parallel inference machine, PIM, and displays it graphically based on the X window system<sup>6)</sup>.

Many performance displays have been devised for utilization, communication, and task information<sup>7), 8)</sup>. For example, graphical meters<sup>7)</sup> represent processor-utilization and graphical animation on a processor configuration map<sup>8)</sup> represents interprocessor-communication of message-passing programs. Such specialized views provide an intuitive feeling for dynamic behavior, but it is difficult to determine where the performance bottlenecks are. Because the execution of parallel programs often raise complex phenomena, simple observation of each phenomena can not provide full information needed to detect performance bottlenecks. For example, suppose that when tasks are not mutually independent and must communicate with each other closely. The program is less efficient because of communication overhead. But graphical meters may show processors work hard, although most of processing time must have been consumed on message-handling. In this case, it is useful to compare the activity of processors with frequencies of sending and receiving messages along execution time. Thus, bottlenecks are often determined by comparing S. Aikawa et al.: ParaGraph: A Graphical Tuning Tool for Multiprocessor Systems

with some pieces of profiling information each other. In ParaGraph system, every kind of profiling information can be displayed based on three common axes to be easy to compare. Because such profiling information can be viewed as having three axes: what, when, and where.

In chapter 2, how load distribution can be described in KL1 on PIM are described. Chapter 3 describes the implementation of the ParaGraph system and graphical representation of program execution, and chapter 4 discusses how useful graphical displays are to detect performance bottlenecks with examples of various programs.

The contents of this paper partially overlap the subject of a previous paper<sup>9)</sup>.

### 2. Load distribution algorithms

### 2.1 Load distribution in KL1

The parallel inference machine runs a concurrent logic programming language called KL1<sup>(1, 3), 10)</sup>. A KL1 program consists of a collection of guarded Horn clauses of the form:

$H:-G_1,...,G_m \mid B_1,...,B_n \ (m, n \ge 1),$ where  $H, G_i$ , and  $B_i$  are atomic formulas. H is called the head,  $G_i$ , the guard goals, and  $B_i$  the body goals. The guard part consists of the head and the guard goals and the body consists of body goals. They are separated by the commitment operator " $\mid$ ". A collection of guarded Horn clauses whose heads have the same predicate symbol P and the same arity N, define a procedure P with arity N. This is denoted as P/N.

The guard goals wait for instantiations to variables (synchronization) and test them. When the guard part of one or more clauses succeed, one of those clauses is selected and its body goals are called. These body goals communicate with each other through their common variables. If variables are not ready for testing in the guard part because the value has not been computed yet, testing is suspended.

In addition to the above basic mechanism, there is a mapping facility which includes load distribution specification. The programmer can annotate the program by attaching pragmas to the body goals to specify a processor {specified

| :- J>0, D=0             |

|-------------------------|

|                         |

| processor specification |

| +                       |

| BL2) @node (Proc),      |

| R1,D,BL1).              |

|                         |

by Goal@node (Proc)}. The programmer must tell the KL1 implementation which goals to execute on which processors.

Figure 1 shows a part of a KL1 program. If the goal next\_queen/7 is committed to this clause, its body goals are called. The goal try\_ext/7 has a processor specification, and it is to be executed on processor number "Proc". This processor number can be dynamically computed.

### 2.2 Design issues

Load balancing derives maximum performance by efficiently utilizing the processing power of the entire system. This is done by partitioning a program into mutually independent or almost independent tasks, and distributing tasks to processors. Many load balancing studies have been devised, but they are tightly coupled to particular applications. Therefore, programmers have to build load distribution algorithms for their own applications.

To distribute the computational load efficiently, the programmer should keep in mind the following points. Since load distribution is implemented by using goals, the programmer should understand the execution behavior of each goal. When goals are executed on a loosely-coupled multiprocessor, the programmer should investigate the load on individual processors and the communication overhead between processors.

For evaluating load distribution algorithms, tools must provide many graphic displays for the programmer to understand the computational and communication load of each processor in both the higher program and lower implementation levels. No single display and no single profiling level can provide the full information needed to detect performance bottlenecks.

### 3. System overview

### 3.1 Gathering information

To statistically profile large-scale program execution, KL1 implementation provides information gathering facilities, low-level profiling and higher-level profiling. KL1 implementation provides these facilities as language primitives, to minimize the undesirable influence to the execution behavior of programs. These facilities have been implemented at the firmware level. The profiling facilities are summarized as follows.

1) Low-level profiling

Profiles the low-level behavior of the processor, such as how much CPU time went to the various basic operations required for program execution.

2) Higher-level profiling

Profiles the higher-level behavior of the processor, such as how many times each piece of the program was executed.

To minimize the perturbation, the gathered profiling information resides in each processor's local memory during program execution, and after execution, ParaGraph collects this information and converts into some standard form. Since profiling information is automatically produced by the KL1 implementation, programmers do not have to modify the application programs.

### 3.1.1 Low-level profiling

The basic low-level activities can be categorized into computation, communication, garbage collection, and idling. Computation means normal program execution such as goals' reductions and suspensions, communication means sending and receiving inter-processor messages, garbage collection means itself, and finally, idling means doing nothing.

The processor profiling facility measures how much time went to each category for each processor. Such information can be periodically gathered to show gradual changes of behavior. The profiling facility can also measure frequencies of sending and receiving various kinds of interprocessor messages<sup>(1), 12)</sup>.

- 1) A *throw\_goal* message transfers a KL1 goal with a throw goal pragma to a specified processor.

- 2) A *read* message requests for some value from the remote processor when a clause selection condition requires it.

- An answer\_value message replies to a read message when the request value becomes available.

- A unify message requests body unification (giving a value to a variable).

### 3.1.2 Higher-level profiling

KL1 provides a mechanism for grouping goals and controlling their execution in a meta-level. This mechanism can be considered to be an interpreter for the KL1 language. It also provides profiling facility at a higher level than processor profiling. Low-level profiling gathers a number of important statistics from many aspects that help analyzing performance bottlenecks, but it provides no information on where in the program is the root of such a behavior.

To correlate execution behavior with a portion of the program, higher-level profiling measures how many times goals associated with each predicate are reduced or suspended (due to unavailability of data required for reduction). Transition of behavior can be observed by periodically gathering the information.

### 3.2 Graphic displays

The profiling information can be viewed as having three axes: what, when, and where. In sequential execution, "where" is a constant and the "when" aspect is not important, since the execution order is strictly designated. Therefore, simple tools like gprof provided with UNIX<sup>Note)</sup> suffice. However, all three axes are important when parallel execution is concerned.

If such massive information is not presented carefully, the user might be more confused than informed. Therefore, ParaGraph provides graphic displays based on three axes. We named each representation using the terms "What,"

Note: The UNIX operating system was developed and is licensed by UNIX System Labiratories, Inc.

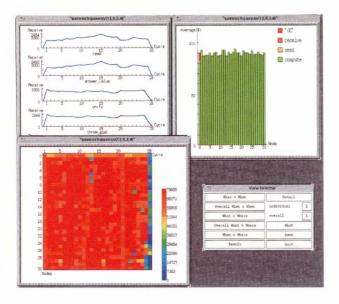

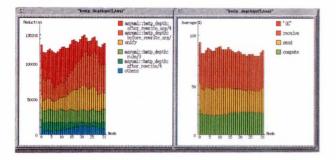

Fig. 2-Examples of graphic displays: a What × When view (top-left), an overall What × Where view (top-right), and a When × Where view (bottom-left) and a menuoriented user interface (bottom-left).

"When," and "Where." The term "What" is the visualization target corresponding to the type of profiling information such as low-level processor behavior, higher-level processor behavior, and interprocessor message frequencies. The term "When" and "Where" indicate time expressed by a cycle number and the processor number respectively.

Figure 2 shows the graphic displays of ParaGraph. These displays are execution behavior of all solution search program of N queen problem.

Every type of profiling information can be easily displayed with the views described below with a menu-oriented user interface such as the bottom-right window in Fig. 2. If the window size is too small to display everything in detail, coarser display aggregating several cycles or several processors together is possible to see the overall behavior at a glance. Scrolling on the vertical and horizontal directions are also possible if details are to be examined. It is also possible to display only selected "What" items.

### 3.2.1 A What $\times$ When view

There are two kinds of views in terms of "What" and "When" items. One is a What  $\times$  When view which shows the behavior of each

"What" item during execution. A graph is displayed of a "What" item in order of the total volume. The x axis is the cycle numbers, and the y axis is the rate of processor utilization, the number of messages, and the number of reductions or suspensions corresponding to the type of profiling information. Since every graph is drawn with the same scale on the vertical axis, it is easy to compare with "What" items.

The other is an overall What  $\times$  When view which shows the behavior of all "What" items during execution. Each "What" item is stacked in the same graph and displayed by a line. The y axis represents the average rate of processor utilization, the total number of messages, and the total number of reductions and suspensions corresponding to the type of profiling information.

These views are helpful for example, if a program has sequential bottlenecks such as tight synchronization. In this case, the number of goal reductions will be down at some portion during program execution. Such a problem will be detected easily by observing program execution.

The top-left window in Fig. 2 shows received message frequencies on all processors with What  $\times$  When view. In this window, four kinds of receiving message frequencies are displayed on each graph. These messages are displayed in order of the total number of received messages. The other messages are displayed by scrolling vertically.

From this, we know that each received message frequency on all processors is less than 2 500 times/an interval (an interval is 2 second). As this program is divided mutually independent subtasks, communication message frequency is very low.

### $3.2.2 \text{ A When} \times \text{Where view}$

A When  $\times$  Where view shows the behaviors of all "What" items on each processor. Each processor is displayed with various color patterns that indicate volume. The relationship between color patterns and volume are shown in the bottom right corner. The brighter the pattern, the busier the processor. Volume means the rate of processor utilization, the number of messages, and the number of reductions or suspensions that correspond to the type of profiling information. It's also possible to display only selected "What" items instead of all of them.

The bottom-left window in Fig. 2 is a When  $\times$  Where view. The x axis is the cycle number, and the y axis is the processor number. This view displays the execution behavior of all goals on a 32-processor machine. The color patterns indicate the number of reductions. The relationship between the number of reductions and color pattern is displayed on the bottom right corner.

From this, we know that the work load on each processor was well balanced, and this program was executed about 70 000 reductions/an interval on each processor at each moment in time.

### 3.2.3 A What $\times$ Where view

There are two kinds of views in terms of "What" and "Where" items. One is a What  $\times$  Where view which shows the load balance of each "What" item on each processor. A bar chart is displayed of a "What" item in order of total volume. The x axis represents the processor numbers, the y axis represents the rate of processor utilization, the number of messages, and the number of reductions or suspensions that correspond to the type of the profiling information. All bar charts are drawn with the same scale on the vertical axis, so it is easy to compare with the volume of each "What" item.

The other is an overall What  $\times$  Where view which shows the load balances of all "What" items on each processor. Each "What" item is stacked in the same bar chart and displayed by a certain color pattern. The y axis represents the average rate of processor utilization, the total number of messages, and the number of total reductions or suspensions that correspond to the type of profiling information. The relationship between each category and color pattern is displayed on the top-right corner.

The top-right window in Fig. 2 shows the low-level behavior of the processor with an overall What  $\times$  Where view. In this window, each categories of low-level behavior is displayed with several color pattern.

From this, the average of computation took

more than 80 % of total execution time, and the average of communication on processor No. 0 was about 10 %, and the others were less than 5%. Since processor No. 0 collected answer values from the others, it took higher average. Thus, this view shows most of the processors run fully, and this example program was executed very efficiently on each processor.

### 4. Examples

This chapter discusses which views to use to view various performance bottlenecks. For efficient program execution on multiprocessor systems, the following phases are usually repeated until a solution is reached:

- 1) a program is partitioned into subtasks,

- 2) the subtask is mapped to each processor dynamically, and

- each processor runs subtasks while communicating with each other.

Various problems are often encountered when executing a program on multiprocessor systems. We will show how graphic displays in both the higher program and lower implementation levels are helpful with performance problems.

### 4.1 Uneven partitioning

When the granularity between subtasks is very different, it is useful to observe the lowlevel processor behavior with a When  $\times$  Where view and the higher-level processor behavior with a What  $\times$  Where view. From the When  $\times$ Where view, we will find which processors run fully and which are idle. From the What  $\times$  Where view, we will determine which goals caused the load imbalances.

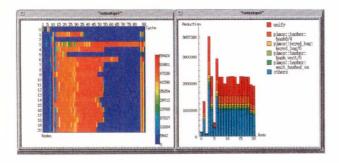

The left window in Fig. 3 shows the lowlevel behaviors on each processor with a When  $\times$  Where view, while the right window in Fig. 3 shows the higher-level behaviors of the same processors with a What  $\times$  Where view on a 21-processor machine. An example program is a logic design expert system which generates a circuit based on a behavior specification. The strategy of parallel execution is that first, the system divides a behavior specification into sub-specifications, next designs subcircuits based S. Aikawa et al.: ParaGraph: A Graphical Tuning Tool for Multiprocessor Systems

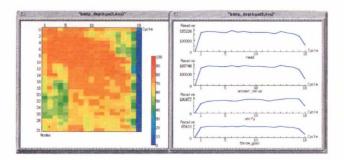

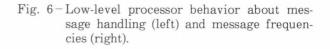

Fig. 3- The low-level processor behavior (left) and execution behavior of goals (right).

on the sub-specifications on each processor, and finally gathers partial results together and combines them. The When  $\times$  Where view suggests that most of processors run almost equally, but processors No. 3 and No. 6 run fully, and processors No. 0, No. 2, and No. 5 were idle. The What  $\times$  Where indicates the which goals were executed on each processor.

From this, we know that processors No. 3 and No. 6 were allocated very complicated tasks, and processors No. 0, No. 2, and No. 5 were allocated very tiny tasks, that is, uneven partitioning of behavior specification must cause a bottleneck in performance.

### 4.2 Load imbalance

If a mapping algorithm has problems such as allocating subtasks to the same processor, it is useful to observe low-level behavior of the processor with a When  $\times$  Where view and higher-level behavior with a What  $\times$  Where view. From the When  $\times$  Where view, we see which processors run fully or which are idle, and from the What  $\times$  Where view, we see the load balance of each goal. Using both views, we can determine how to distribute the goals that are imbalanced to each processor.

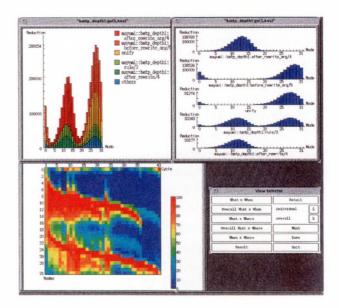

The bottom-left window of Fig. 4 shows low-level behavior of the processor with a When  $\times$  Where view, the top-left window and the top-right window show the higher-level behavior of the processor with an overall What  $\times$  Where view, a What  $\times$  Where view respectively. An example program is a part of the theorem prover which evaluates whether an input formula is a tautology. The strategy consists of 2

Fig. 4-Low-level processor behavior (bottom-left), the load balances of all goals (top-left), and the load of each goal (top-right).

steps:

- 1) convert an input formula to clause form (i.e. conjunctive normal form),

- 2) evaluate its clause form and determine whether it is a tautology.

The step 1 is executed in parallel as follows. First, main task partitions an input formula into subformulas. Second, it generates subtasks to convert subclause forms, and finally, distributes subtasks to many processors dynamically. These steps are repeated recursively until subformulas are converted to subclause forms. The step 2 is executed in sequential on processor No. 0.

The When  $\times$  Where view of the bottom-left window suggests that only certain processors (processor No. 6-15 and No. 23-31) run fully and that the others were mostly idle. The overall When  $\times$  Where view of the top-left window also suggests most of the goals were executed on the same processors, especially the number of reductions of top five goals were higher than the other goals.

We can check the load of each goal on each processor from the What  $\times$  Where view of the top-right window. These goals were executed on certain processors and were the cause of the load imbalances. From this, we have to change its mapping algorithm to be flatten the shape, to S. Aikawa et al.: ParaGraph: A Graphical Tuning Tool for Multiprocessor Systems

Fig. 5-The load balances of goals (left) and low-level processor behavior (right).

use all processors efficiently.

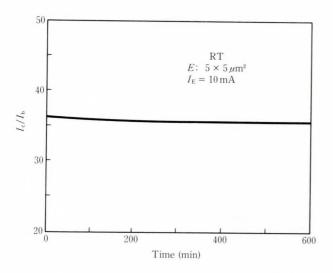

### 4.3 Large communication overhead

When subtasks are not mutually independent and must communicate with each other closely, the program is less efficient because of communication overhead. In this case, the low-level behavior of the processor with an overall What  $\times$  Where view and frequencies of sending and receiving messages with a What  $\times$ Where view are helpful. From the overall What  $\times$  Where view, we will learn how much time has been consumed on message handling for each processor, while the What  $\times$  Where view shows us what kind of messages each processor has sent or received.

Figure 5 displays an execution behavior of an improved version of the program described in section 4.2. The left window shows the load balances of all goals on a 32-processor machine with an overall What  $\times$  When view. This view shows that the work load on each processor was balanced in overall execution, but was not efficient because of large communication overhead. It will be proved from low-level behavior of the processor with an overall What  $\times$  Where view shown in the right window.

Figure 6 shows the same program execution as Fig. 5. The left window shows the receiving and sending message handling time rate with What  $\times$  Where view, the right window shows the frequencies of four received inter-processor messages with a What  $\times$  When view. The right window of Fig. 5 suggests the load average on each processor was about 80-85 %, but the average of computation on each processor was about 20 %.

Most of the processing power was consumed sending and receiving message handling time more than 60 % of total execution time.

The left window of Fig. 6 shows the message handling time on each processor at each moment in time was almost equally. The right window in Fig. 6 shows that the read message was received about 185 000 times, answer\_value message was about 170 000 times, unify message was 100 000 times, and throw\_goal message was about 66 000 times per interval on all processors. The tasks generated in this program communicated with each other closely among processors as compared with the result of N queen's message frequencies (see the top-left window of Fig. 2).

From this, we know that as work loads are distributed more and more, it becomes easier to balance work loads on each processor, but communication overhead also increases and performance is thus lowered. As a result, we have to redesign or improve how to divide into subtasks. Because the generated subtasks that were not mutually independent caused such a problem we mentioned above.

### 5. Conclusion

We developed the ParaGraph system on parallel inference machines to provide graphic displays of processor utilization, interprocessor communication, and execution behavior of parallel programs. Experiments with various programs have indicated that graphic displays are helpful in dividing work loads evenly and determining where the bottlenecks are on multiprocessor systems.

We released a version last year as a tuning tool of PIMOS, but have experienced some problems. In the future, we will improve the system considering the following points. First, real-time performance visualization tools are needed. Although displaying execution behavior in real-time perturbs the program being monitored, it is useful not only in early tuning but also in debugging such as detecting deadlock status and infinite loops. To develop such a tool, low overhead instrumentation techniques and new displays that are easy to understand for programmers appearing in real-time must be devised.

Second, tools which can visualize the portion of the performance bottlenecks directly are needed. Massively parallel machines that have thousands of processors and programs for long runs produce a large amount of profiling information, but it is difficult to process or display for simple expansion of our system because of a vast quantity of information. To solve such problems, analysis techniques indicating bottlenecks directly will be needed. We will study automatic analysis techniques and graphical displays of its result (we call this bottleneck visualization). One such approach is critical path analysis<sup>13)</sup>, which identifies the path through the program that consumed the most time.

### 6. Acknowledgment

The work described in this paper was done under Institute for New Generation Computer Technology (ICOT) contract as a part of the R&D of the Fifth Generation Computer Systems Project. We thank all researchers of ICOT and other companies who tested our tool. We also thank K. Nakao and H. Kubo who helped us to develop this tool.

### References

- Ueda, K., and Chikayama, T.: Design of the Kernel Language for the Parallel Inference Machine. *The Computer Journal*, **33**, 6, pp. 494-500 (1990).

- 2) Goto, A., Sato, M., Nakajima, K., Taki, K., and

Matsumoto, A.: Overview of the Parallel Inference Machine (PIM) Architecture. Proc. Fifth Generation Computer Systems 1988, 1, Tokyo, pp. 208-229.

- Chikayama, T., Sato, H., and Miyazaki, T.: Overview of the Parallel Inference Machine Operating System (PIMOS). Proc. Fifth Generation Computer Systems 1988, 1, Tokyo, pp. 230-251.

- Furuichi, M., Taki, K., and Ichiyoshi, N.: "A Multi-Level Load Balancing Scheme for OR-Parallel Exhaustive Search Program on the Multi-PSI". ICOT TR-526, Tokyo, ICOT Research Center, 1989.

- Kimura, K., and Ichiyoshi, N.: Probabilistic Analysis of the Optimal Efficiency of the Multi-Level Dynamic Load Balancing Scheme. Proc. Sixth Distributed Memory Comput. Conf., 1989.

- Scheifler, R. W., and Gettys, J.: The X Window system. ACM Trans. Graphics, 5, 2, pp. 79-109 (1986).

- Malony, A. D., Reed, D. A., and Rudolph, D. C.: "Integrating Performance Data Collection, Analysis, and Visualization". Performance Instrumentation and Visualization, 1st ed., N.Y., ACM Press, 1990, pp. 73-97.

- Heath, M. T., and Etheridge, J. A.: Visualizing the Performance of Parallel Programs. *IEEE* Software, 8, 5, pp. 29-39, (1991).

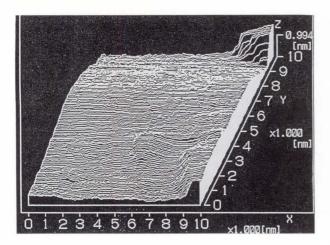

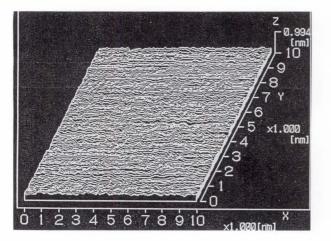

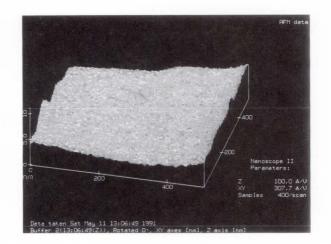

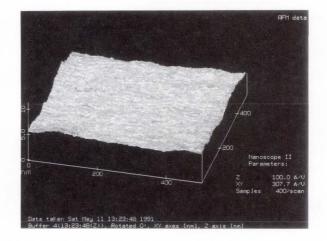

- Aikawa, S., Kamiko, M., Kubo, H., Matsuzawa, F., and Chikayama, T.: ParaGraph: A Graphical Tuning Tool for Multiprocessor Systems. Proc. Fifth Generation Computer Systems 1992, 1, Tokyo, pp. 286-293.

- Ichiyoshi, N.: "Research Issues in Parallel Knowledge Information Processing". ICOT TM-0822, Tokyo, ICOT Research Center, 1989.

- Nakajima, K., Inamura, Y., Ichiyoshi, N., Chikayama, T., and Nakashima, H.: Distributed Implementation of KL1 on the Multi-PSI/V2". Proc. Sixth Int. Conf. Logic Prgmg. 1989.

- 12) Nakajima, K., and Ichiyoshi, N.: "Evaluation of Inter-processor Communication in the KL1 Implementation on the Multi-PSI". ICOT TR-531, Tokyo, ICOT Research Center, 1990.

- Miller, B. P., Clark, M., Hollingsworth, J., Kierstead, S., Lim, S., and Torzewski, T.: IPS-2:

The Second Generation of a Parallel Program Measurement System. *IEEE Trans. Par. Distr. Syst.*,

1, 2, pp. 206-217 (1990).

Seiichi Aikawa received the B.S. degree in electronics from Gunma University, Gunma, Japan, in 1985. He joined Fujitsu Laboratories Ltd., Kawasaki, in 1985 and has been engaged in reseach and development of programming environment in the Fifth Generation Computer Systems project.

He is a member of Information Processing Society of Japan.

Takashi Chikayama received his bachelor degree in mathematical engineering in 1977 and his doctoral degree in information engineering in 1982, both from the University of Tokyo.

He joined Fujitsu Laboratories Ltd., and then Institute for New Generation Computer Technology (ICOT) in 1982. He has been conducting research and development in the Fifth Generation

Computer Systems project since, mainly in programing language and operating systems area.

Mayumi Kamiko received the B.S. degree in Information Eng. from Shinshu University, Nagano, Japan, in 1987.

She joined Fujitsu Laboratories Ltd., Kawasaki, in 1987 and has been engaged in reseach and development of operating system and programming environment in the Fifth Generation Computer Systems project.

She is a member of Information Processing Society of Japan.

### A Practical Test Program Generator Based on Attributed Grammer

● Hiroshi Kawata ● Hiroshi Saijo ● Chikao Shioya

(Manuscript received December 1, 1992)

This paper presents a test program generator called TPGEN, which is based on attributed grammar. TPGEN generates a wide variety of test programs mainly for programming language processors. The generated test programs are executable and have self-checking code for validating execution results. The generated test programs are assured that they have specific testing covevage.

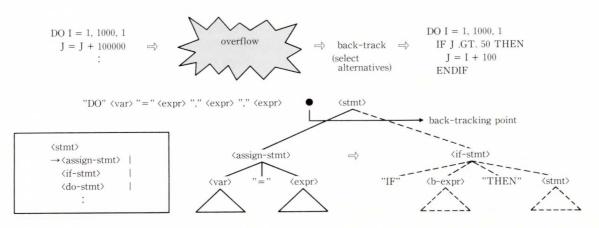

TPGEN simulates the execution of a test program being generated and if an abnormal event such as zero divide or infinite loop is detected, TPGEN back-tracks to the specified position and selects an alternative production rule to avoid such abnormal execution. Introduction of this mechanism has succeeded in generating a wide variety of programs with complex structures.

### 1. Introduction

In the past, the formal definition of programming languages has been of interest mainly for the automatic generation of language processors such as compilers, interpreters and syntax-directed editors<sup>11</sup>. There have also been studies on its application to automatic generation of test cases or test programs<sup>21</sup>. Automatic generation of test programs typically defines test grammar in a formal way, such as BNF, and generates test programs from this description. It is a relatively simple task to randomly generate test programs according to a syntax description of the language, but the generation of practical executable programs requires solutions to several problems.

The first problem is to resolve contextual dependencies when generating correct programs. Duncan<sup>3)</sup> has resolved this problem using attributed grammar and has developed a test program generator using a parser generator technique. But in our experience, the use of a general parser generator technique requires the description of all the information regarding attributes and the passing of attributes and thus results in a large and unwieldly description.

The second problem is in the generation of

test programs with self-checking code. Confirmation of test results requiring a large amount of manpower reduces the benefit of automatic generation. Reports<sup>3)-5)</sup> show how to describe the semantics of language elements and give predicted execution results, but include no mechanism for automatic checking of execution results. D. L. Bird and C. U. Munoz<sup>6)</sup> have described the automatic generation of test programs which are as executable and self-checkable as possible, although there are some restrictions on generated program structures.

The third problem concerns functional coverage. To assure adequate coverage we must be able to generate executable programs with complex structures such as loops. The reports that have been published so far describe relatively simple cases<sup>3-8</sup>.

Other reports<sup>9), 10)</sup> have pointed out that PROLOG is very useful when prototyping a test case or test data generator. We implemented TPGEN in LISP because of LISP's facilities such as manipulation of pointer variables and complex data structures which were necessary to make our tool more practical.

Our test program generator, TPGEN, has been in use for software product inspection for more than three years. In this paper, we present how TPGEN generates executable test programs with self-checking code, how it assures testing coverage, and how it improves the quality of generated programs and some empirical results obtained in comparison with conventional methods.

### 2. Outline of generation principle of TPGEN

In a syntax-directed definition, each production rule  $A \rightarrow \alpha$  has associated with it a set of semantic rules of the form  $b := f(c_1, c_2, \dots, c_k)$ , where f is a function, b is a synthesized attribute of A or an inherited attribute of one of the grammar symbols on the right side of the production, and  $c_1, c_2, \dots c_k$  are attributes belonging to the grammar symbols of the production. Functions in semantic rules are often written as expressions. Occasionally, the only purpose of a semantic rule in a syntax-directed definition is to create a side-effect. Such semantic rules are written as procedure calls or program segments. They can be thought of as rules defining the values of dummy production<sup>1)</sup>. An attribute grammar is a syntax-directed definition in which the functions in semantic rules cannot have a side-effect.

The semantic definition of TPGEN consists of two descriptions: one resolves context-dependency to generate grammatically correct programs and the other simulates execution of generated programs. In generating a proper expression, for example, its type is passed to the production rule of an expression as an inherited attribute. The value attribute is introduced to each non-terminal so that the generated program can be simulated. Introduction of such attributes is not enough to complete the semantic definition of TPGEN, which will be explained later.

We will now explain how TPGEN generates test programs from the language definition. Figure 1 shows a simplified definition of a small subset of FORTRAN (see the appendix for more details). In this figure, symbols enclosed by < and > mean non-terminals and symbols surrounded by " and " mean terminals.

If we select production rules in Fig. 1 in the order of (1), (2-2), (4), (6-1), (7-1), ..., then parts (a)

| <program></program>         | > <stmt> &amp;</stmt>                            | $\cdots$ (1)                          |

|-----------------------------|--------------------------------------------------|---------------------------------------|

| <stmt></stmt>               | > <assign-stmt> !</assign-stmt>                  | $\cdots$ (2-1)                        |

|                             | <if-stmt> &amp;</if-stmt>                        | $\cdots$ (2-2)                        |

| <assign-stmt></assign-stmt> | > <var> "=" <expr< td=""><td></td></expr<></var> |                                       |

|                             | (insert-checking-                                | routine) & ··· (3-1)                  |

| <if-stmt></if-stmt>         | > "IF (" <b-expr> "]</b-expr>                    | ) THEN" <stmt></stmt>                 |

|                             | "ELSE" <stmt> "E</stmt>                          |                                       |

| <expr></expr>               | > <primary></primary>                            | ! (5-1)                               |

|                             | <primary> "+" <pri></pri></primary>              | primary> ! $\cdots$ (5-2)             |

|                             | <primary> "-" &lt;</primary>                     | primary> & · · · (5-3)                |

| <b-expr></b-expr>           | > <primary> ".GT."</primary>                     | <primary> ! · · · (6-1)</primary>     |

|                             | <primary> ".LT."</primary>                       | <primary> ! (6-2)</primary>           |

|                             | <primary> ".EQ."</primary>                       | <primary> &amp; · · · (6-3)</primary> |

| <primary></primary>         | > <ref-var> !</ref-var>                          | (7-1)                                 |

|                             | <const> &amp;</const>                            | (7-2)                                 |

Fig. 1-A simplified example of language definition (syntax only).

| IJK1 = 150                                  | · · · (c)                                                                          |

|---------------------------------------------|------------------------------------------------------------------------------------|

| IF (IJK1 .GT. 100) THEN<br>IJK1 = IJK1 - 60 | $\cdots$ (a)                                                                       |

| CALL CHECK(1, 90, IJK1, 'ASSIGN STM         | MT INVALID')···(b)                                                                 |

| ELSE I JK2 = 30                             | $\cdots$ (a)<br>$\cdots$ (a)                                                       |

| CALL CHECK(2,30,IJK2,'ASSIGN STM<br>ENDIF   | $\begin{array}{c} \text{MT INVALID'} & \cdots & (b) \\ & \cdots & (a) \end{array}$ |

| STOP<br>END                                 |                                                                                    |

a) Example (1)

| IJK1 = 150                                                 | · · · (c)    |

|------------------------------------------------------------|--------------|

| IF (IJK1 .GT. 100) THEN                                    | $\cdots$ (a) |

| IJK1 = IJK1 - 60                                           | $\cdots$ (a) |

| ELSE                                                       | $\cdots$ (a) |

| IJK2 = 30                                                  | $\cdots$ (a) |

| ENDIF                                                      | $\cdots$ (a) |

| CALL CHECK(1,90,IJK1,'ASSIGN STMT INVALID')<br>STOP<br>END | · · · (b)    |

b) Example (2)

Fig. 2-Examples of generated text.

and (b) of Fig. 2a) will be generated. Part (b) of Fig. 2a) is generated based on the description of 'insert-checking-routine', and part (c) is an initialization statement which is generated with a declarative statement.

The procedure adopted by TPGEN to generate executable test programs with selfchecking code is as follows:

TPGEN selects production rules randomly or considering functional coverage, if specified, starting from <program> and generates source text. Usually, we define a <program> so that it includes several executable statements with several declarative statements and initialization statements. Number of statements included in a <program> is determined randomly within specified minimum and maximum integers.

- 2) TPGEN generates source text based on the selected production rules, and each time a production rule is applied, generated text is simulated. If an abnormal event such as an overflow is detected, some alternative is selected. If all alternatives result in abnormal execution, TPGEN back-tracks to the parent production rule of the current production rule and continues processing. Confirmation of execution results is done by generating self-checking code according to the 'insert-checking-routine'.

- 3) A source text for a <program> is generated by the above procedure. If a generated program includes a complex program structure such as a loop, there are several problems to be resolved, which will be explained later.

### 2.1 Resolving context-dependency

If a test program is generated by selecting production rules completely at random, variables or functions defined in the declaration portion will not coincide with those used in the execution portion. In order to resolve such context-dependency, information concerning declared variables must be easily retrieved. In TPGEN, system functions are available which make it easy to store and retrieve information concerning declared variables.

Such information is considered to belong to a specific non-terminal (\$PROGRAM in the appendix). For example, if a variable is declared in a declarative statement, its name, data type and other information is registered to that non-terminal using a system function. If a variable is assigned a value by an assignment statement, the value of that variable is updated using another system function.

In generating an expression, the specific data type is passed to the production rule of an

expression as an inherited attribute. In generating a subscript expression, its range or expected value is passed to the rule of an expression and if the value of the generated expression is not appropriate, we usually specify generation for a fixed period of time until it is appropriate. A back-tracking mechanism is very useful in such a situation. This will be explained later.

The production rule of subroutines is invoked from the semantic definition of the "CALL" statement, receives the necessary information (subroutine name and parameters) from it, and generates an appropriate subroutine. Normal execution of that subroutine is assured for the current "CALL" statement by simulating its execution at the time of generation.

The production rule of the "CALL" statement includes two alternatives. One is to generate a "CALL" statement for already generated subroutines, and the other is for a new subroutine. When a new subroutine is generated, to generate it must be stored with its name in a global variable so that other "CALL" statements for it can be generated later.

The generation of a subroutine at the time of generating a "CALL" statement, however, requires placing that subroutine at an appropriate point inside the generated test program. This problem is resolved by separating text generation and its arrangement. Syntax definition of such a production rule simply states the arrangement of generated text (syntax elements), and the generation of text is done by semantic definition (see the appendix).

### 2.2 Self-checking code

Automatic checking of execution results is very important in the inspection and testing of our software. We have been using checking routines for many years, before TPGEN was introduced. We have checking routines for each type of variable and for each target language. The checking routines themselves are coded in each target language. In Fig. 2, they receive, as parameters, a sequential number to identify erroneous text, a simulated value of the variable to be checked, the variable to be checked, and error message text.

A test program generated by TPGEN is executable once it is link-edited with the above checking routines.

Although TPGEN understands values of all variables, users of TPGEN must specify the position where the self-checking code should be inserted, and the way it should be inserted. One reason is that TPGEN does not understand the structure of the target language. For example, if the "THEN" clause of an "IF" statement consists of one assignment statement, insertion of the self-checking code inside the "THEN" clause may require, in some languages, grouping of these statements. But the current TPGEN does not understand the target language to that extent.

Insertion of a self-checking routine is done for specified variables based on the definition of the 'insert-checking-routine' as shown in Fig. 1 or CHECK, which is described in the appendix. Figure 1 specifies the self-checking code to be inserted at the end of each assignment statement. In Fig. 2a), such code is inserted in the "THEN" clause and "ELSE" clauses. The "ELSE" clause is not executed in this example, but such an insertion is done assuming the "ELSE" clause will be executed. Another test program designer may specify the insertion of checking routines at the end of the "IF" statement for all variables whose values are changed during the execution of the "IF" statement. In this case, he should know the variables whose values change according to the difference between the value of variables on entrance to the "IF" statement and the value of variables on exit from the "IF" statement and a program described in Fig. 2b) is generated.

If the assignment statements in Fig. 2a) are included in a loop, the definition of CHECK in the appendix is not enough to generate a correct self-checking code. Insertion of a self-checking code inside a loop requires to identify repetition in addition to the value of the variable at that repetition and this information must be included in the definition of 'insert-checking-routine'.

Validation of the contents of external files is done by validation of variables when they retrieve a record from that file.

Test programs generated by TPGEN thus have self-checking code, and if a test program is executed correctly, such a program is discarded and only the information concerning what kind of functional test was done is stored in the database.

### 3. Characteristics of TPGEN

TPGEN generates test programs as described above. However, we also added the following features in order to make the quality of generated test programs closer to that of those generated manually.

### 3.1 Preventing abnormal execution by backtracking

In TPGEN, an expression is evaluated each time a production rule is applied, and if an abnormal event is detected, TPGEN randomly

Fig. 3 – An example of back-tracking caused by a loop.

selects an alternative rule, excluding already selected rules. If an abnormal event is detected for all such selections, TPGEN back-tracks to its parent production rule, and text generation and its simulation continue. But this approach has some problems. One problem is that even if some selection, for example, (5-2) of Fig. 1 results in abnormal execution, it may be executed normally if it is selected more than twice, because a different < primary > will be selected.

A similar problem exists when such an expression is included inside a loop. In a loop (see Fig. 3), an assignment statement is generated so that no abnormal execution will occur for the first repetition. But the "DO" statement may cause abnormal execution for that assignment statement, at a later repetition. If it does, TPGEN considers that the "DO" statement, not the assignment statement, is executed abnormally. So, if the back-tracking point is specified inside the production rule of the "DO" statement, as in Fig. 3, the generation environment is resumed to the specified point, and the "DO" statement (body of the "DO" statement) is generated and simulated for a fixed number of times until it is executed normally. If a back-tracking point is specified at the top of the "DO" statement, generation of the "DO" statement itself is repeated for a fixed number of times until it is executed normally. If no back-tracking point is specified for the "DO" statement, some statement other than the "DO" statement will be selected as an alternative to the current "DO" statement.

To specify back-tracking points is delicate work. Users must make the scope of backtracking as narrow as possible so that a wide variety of programs will be generated, and they must at the same time, reduce the frequency of back-tracking to improve generation efficiency.

Detection of infinite loops is done by counting repetition numbers. Since the introduction of "GOTO" statements makes it difficult to design test programs with no infinite loops, we usually design test programs which include "GOTO" statements separately.

### 3.2 Assuring functional coverage of generated programs

The combinations of selecting production rules can become enormous, even infinite, because of the nested or recursive structure of the target language. Thus, generation of test programs based on a random selection of production rules cannot answer such questions as; "are the generated test programs enough to cover the functionality of the target language?".

In addition to random selection of production rules, TPGEN tries to assure the following coverage of generated programs:

Condition-2 (2 level combination): For each alternative of each production rule, TPGEN tries to assure generation of all combinations of all alternatives of non-terminals which are included in that rule. For example, consider the <if-stmt> in Fig. 1. Each <b-expr> and <stmt> of the "THEN" clause, and the <stmt> of the "ELSE" clause consists of three alternatives, so twenty seven combinations should be selected for <if-stmt>.

This metric is based on syntax definition only, and it is usually not possible to generate test programs so that they satisfy condition-2 for all production rules. We adopted condition-2 for the following reasons:

- As we cannot do complete functional testing, the second best approach is to make clear what kinds of functional tests are done by the generated programs.

- 2) Condition-2 above is, in a sense, close to the method which is actually used in designing test cases manually<sup>11), 12</sup>. Thus, we can expect that the quality of test programs generated by TPGEN is close to that of those made manually.

### 3.3 Other features

The following additional features have been introduced to make TPGEN more practical.

1) Weights

A facility to control weights or relative frequency of each of the possible alternatives is introduced in the reports<sup>5), 6)</sup>. If one particular type of statement has a high weight, it will appear densely in the generated text. In TPGEN, weights are introduced in the following way:

### < stmt> -> W1 < assign-stmt>

### W2 < if- stmt > &

where W1/ $\Sigma$ Wi is the probability of selecting <assign-stmt>.

Here, W1 and W2, may be expressions, and may be changed dynamically:

<stmt> -> 200 <assign-stmt> |

(E : SELECT : INIT 100 : IF – SELECTED (-30)) < if-stmt > &

The weight of <if-stmt> is read as follows: the relative frequency is set to 100 initially, then it is decreased by 30, each time <if-stmt> is selected. This enables us to change the selection frequency of <if-stmt> to zero at the time the nesting level of the IF statement reaches the maximum allowed by the target language processor.

2) Special terminals for formatting control

In FORTRAN, each line must start at column 7. We usually use indentation for nested IF statements. To cope with these matters, TPGEN has special terminals for controlling the position of generated text. This also improves the readability of generated text.

### 4. Evaluation of TPGEN

TPGEN has been used for more than 3 years in our quality assurance department for several language processors, including FORTRAN, C, LISP, PROLOG, AI-oriented shell, sort-merge, and COBOL-embedded SQL. At the time of their functional enhancement, these products were inspected partially, using TPGEN with about 2 800 production rules and more than 20 million LOCs (line of codes) of generated programs.

1) Applicable range of TPGEN

TPGEN is effective for generating test programs which execute normally. In the case of FORTRAN, about 80 % of the normal functional testing can be done using TPGEN. TPGEN is not effective for functional testing of special functions such as  $\Gamma$  function and special files such as VSAM files.

In the case of SQL, most of the functional testing for data manipulation language (DML) could actually be done using TPGEN, but TPGEN is not effective for data definition language (DDL). In the case of DML, the test program is designed based on a database whose structure is predetermined by a test case designer, but testing of DDL requires making a variety of databases, and it is difficult in our current environment to make simple few selfchecking routines for such a varying data structure.

2) Quality of generated test programs

The functional coverage of TPGEN is basically the same as our conventional method, but we found that test programs generated by TPGEN have better bug-detection characteristics. The main reason, we think, is the complexity of generated programs. We analyzed test programs generated by TPGEN against those made by conventional methods for SQL test programs and found that the number of tokens included in a single SQL statement is about 3.5 times more than those made by conventional means. We also found that the number of phases, predicates, and the depth of nested expressions also increased.

In designing test cases manually, we often specify that some testing factor may be optional, because we think such a factor is not important for such a test case. But this is potentially a big problem, and bugs often exist in places where we think there are no problems. TPGEN generates test programs randomly without any preconceived ideas. This is the key point of a random testing tool.

3) Efforts required to make test programs using TPGEN

Our experience shows that making test programs using TPGEN is five times easier than conventional methods. Using TPGEN, most of our labors is devoted to designing test cases. The simple tedious work of coding the test programs is left to TPGEN, and our time can be spent on other work such as inspecting the ease of use and performance.

### 4) Performance

TPGEN requires a fair amount of CPU time and memory. It takes two or three seconds of CPU time on Fujitsu's large computer M-780 to generate test programs of about 1 kilo LOCs for a programming language which has no loops

|        | *1*2*3*4*5*6*7                                                       |

|--------|----------------------------------------------------------------------|

| 000001 | \$PROGRAM ->                                                         |

| 000002 | STMT "aRNL"                                                          |

| 000003 | "STOP" "aRNL"                                                        |

| 000004 | "END" #%                                                             |

| 000005 |                                                                      |

|        | (E:EXP-R STMT :IN-TERM "@RNL") &                                     |

| 000006 | STMT ->                                                              |

| 000007 | 200 ASSIGN-STMT !                                                    |

| 000008 | 100 IF-STMT &                                                        |

| 000009 | ASSIGN-STMT ->                                                       |

| 000010 | VAR "=" EXPR "@RNL"                                                  |

| 000011 | CHECK #X                                                             |

| 000012 | (E:EXPL VAR)                                                         |

| 000013 | (E:EXPL EXPR)                                                        |

| 000014 | (M:SEM (F:VAR-SET VAR.V EXPR.V))                                     |

| 000015 | (E:EXPL CHECK VAR.V "ASSIGN STMT INVALID") &                         |

| 000016 | IF-STMT ->                                                           |

| 000017 | "IF (" B-EXPR ") THEN" "@TAB+"                                       |

| 000018 | STMT#1 "@TAB-"                                                       |

| 000019 | "ELSE" "@TAB+"                                                       |

| 000020 | STMT#2 "@TAB-"                                                       |

| 000021 | "ENDIF" #2                                                           |

| 000022 | (E:EXPL B-EXPR)                                                      |

| 000023 |                                                                      |

| 000024 | (IF (NOT B-EXPR.V) (F:EFFECT-PART-CUT))                              |

| 000025 | (E:EXPL STMT#1)                                                      |

| 000026 | (IF B-EXPR.V (F:EFFECT-PART-CUT))                                    |

| 000027 | (E:EXPL STMT#2) &                                                    |

|        | EXPR ->                                                              |

| 000028 | PRIMARY                                                              |

| 000029 | PRIMARY#1 "+" PRIMARY#2 % (F:V-SET (+ PRIMARY#1.V PRIMARY#2.V))      |

| 000030 | PRIMARY#1 "-" PRIMARY#2 % (F:V-SET (- PRIMARY#1.V PRIMARY#2.V)) &    |

| 000031 | B-EXPR ->                                                            |

| 000032 | PRIMARY#1 ".GT." PRIMARY#2 % (F:V-SET (> PRIMARY#1.V PRIMARY#2.V)) ! |

| 000033 | PRIMARY#1 ".LT." PRIMARY#2 % (F:V-SFT (< PRIMARY#1 V PRIMARY#2 V)) 1 |

| 000034 | PRIMARY#1 ".EQ." PRIMARY#2 % (F:V-SET (= PRIMARY#1.V PRIMARY#2 V)) & |

| 000035 | PRIMARY ->                                                           |

| 000036 | REF-VAR X (F:V-SET (F:VARV REF-VAR)) !                               |

| 000037 | CONST &                                                              |

| 000038 | CHECK(VAR COMMENT) ->                                                |

| 000039 | "CALL CHECK(" ITEM-NO "," A "," B "," C ")" #X                       |

| 000040 | (E:EXPL ITEM-NO)                                                     |

| 000041 | (E:PN A (F:VARV VAR))                                                |

| 000042 | (E:PN B VAR)                                                         |

| 000043 | (E:PN C COMMENT) &                                                   |

| 000044 | VAR ->                                                               |

| 000045 | #P (CAR (F:RANDOM-SELECT (F:ALL-DECL-VAR))) !                        |

| 000046 | #P (GENSYM "IJK") (F:DECL PO.V #'INTEGERP) &                         |

| 000047 | REF-VAR -> #P (CAR (F:RANDOM-SELECT (F:ALL-VAR))) &                  |

| 000048 | CONST -> #P (F:RANDOM 1 200) &                                       |

| 000049 | ITEM-NO ->                                                           |

| 000050 | A #2                                                                 |

| 000051 | (IF (NOT ITN) (SETQ ITN 1))                                          |

| 000052 | (E:PN A ITN)                                                         |

| 000053 | (SETQ ITN (1+ ITN)) &                                                |

| 000054 | (SETQ *CVS* '(ITN))                                                  |

|        |                                                                      |

Fig. 4 – Test program specification written in TPGEN for a small subset of FORTRAN.

such as SQL, and about 10 seconds for a programming language such as FORTRAN, where we need heavy testing of loops which often require back-tracking for selecting alternative production rules.

### 5. Conclusion

The test program generator TPGEN, which is based on attributed grammar, has succeeded in generating test programs which assure a specific testing coverage and have testing quality as good as or better than manually produced ones.

....\*

Additional merits of TPGEN in our practical work is important. In our quality assurance work, we sometime find that a software product has poor quality. We request the development group to take drastic measure to correct it. Later, when we receive the revised softwave product, we inspect it again. The same test set loses some capabilities for quality assurance in this case. With TPGEN, however, we can generate another test set. Thus we can easily check the quality of the new product.

Testing using TPGEN is so-called 'black box' testing. We usually need to employ many kinds of tests including 'white box' testing, for software products testing. We have not evaluated TPGEN from the point of view of 'white box' testing. And simple definition of syntax and semantics of programming language is not enough as input to TPGEN, and the current TPGEN requires descriptions such as the insertion of checking routines and the specification of back-tracking positions.

Authors are grateful to Dr. Tokuda of Tokyo Institute of Technology for his helpful comments and suggestions on an earlier version of this paper.

### 6. Appendix

A detailed definition of a small subset of FORTRAN is shown in Fig. 4. The following is an explanation of this figure.

- 1) The data declaration and its related initialization are omitted.

- 2) The syntax definition is on the left side of "%" or "#%" and the semantic definition is on the right side of "%" or "#%". The numbers at the top of the syntax definition (see the definition of STMT) define the relative selection frequency of that rule (default is 100).

- 3) "@RNL" specifies the column where the generated text is placed. "@TAB+" and "@TAB-" indicate a carriage return and a shift of output position by a specified number of columns (default is 2) to the right or left, respectively.

- 4) In the case of "%", text is generated according to the syntax definition, and then the semantic definition is evaluated. The semantic definition of EXPR (line 29) means that the value attribute of the non-terminal EXPR should be set to the sum of the value attribute of PRIMARY#1 and that of PRIMARY#2. "F : V-SET" is a system function which evaluates the value of its argument and registers it as a value attribute of left side non-terminal. The "#n"

is a sequential number to identify some non-terminal which appears more than twice in one syntax definition. If no semantic definition is described, as in line 28, the value attribute of the left side non-terminal is set to that of right side non-terminal.

- 5) In the case of "#%", the semantic definition is evaluated first, and then the text is arranged according to the syntax definition using text which is generated in the course of the evaluation of the semantic definition. Such semantic definition includes descriptions which control expansion of production rules. For example, semantic definition of \$PROGRAM specifies to expand STMT randomly more than once (each STMT is separated by "@RNL").

- 6) In our actual implementation, semantic definition which specifies to simulate execution of the generated text must be explicitly stated by writing the "M : SEM" function as described in line 14, because such a definition may be executed more than once if the generated program includes a loop. But such description is omitted in this example except line 14.

- Semantic definition of IF-STMT is a little 7)bit complicated, because it contains a clause which is not executed. Simulation of such a not-executed clause is done in the same way as an executed clause, but the simulation environment (values of generated variables) must be resumed, on exit from such a not-executed clause, to those which is on entrance to the not-executed clause. Saving and restoring such simulation environment is specified by "F : EFFECT - PART - CUT". Line 23 means that if the value of B-EXPRis false, then save current simulation environment and restore simulation environment after having evaluated line 24.

- 8) In the definition of the assignment statement, the value attribute of the left side non-terminal (VAR) is name of some variable and the value attribute of expression (EXPR) is the value of that expression. On line 14, "F : VAR-SET" is a system function which retrieves the spe-

H. Kawata et al.: A Practical Test Program Generator Based on Attributed Grammer

cified variable (VAR . V) among the information which is stored to \$PROGRAM and sets its value field by the second argument (EXPR . V). Line 15 expands CHECK by passing two parameters (value attribute of VAR and string constant "ASSIGN STMT INVALID").

9) The definition of CHECK is read as follows: the CALL statement is expanded according to the syntax definition after evaluation of the semantic definition, which expands ITEM-NO (a sequential number that identifies the self-checking code), then A is set by the simulated value of VAR, B is set by VAR, and C is set by COMMENT.

### References

- Aho, A. V., Sethi, R., and Ullman, J. D.: Compilers-Principles, Techniques, and Tools. Addison-Wesley, 1986, pp. 279-289.

- Ince, D. C.: The Automatic Generation of Test Data. Computer Journal, 30, 1, pp. 63-69 (1987).

- Duncan, A. G., and Hutchison, J. S.: Using Attributed Grammars to Test Designs and Implementation. Proc. 5 th ICSE, 1981, pp. 170-178.

- 4) Bauer, J. A., and Finger, A. B.: Test Plan

Generation using Formal Grammars. Proc. 4th ICSE, Munich, 1979.

- Mauer, P. M.: Generating Test Data with Enhanced Context-free Grammars. *IEEE Soft*ware, 7, pp. 50-55 (1990).

- Bird, D. L., and Munoz, C. U.: Automatic generation of random self-checking test cases. *IBM Syst. J.*, 22, 3, pp. 229-245 (1983).

- Bazzichi, F., and Spadafora, I.: An Automatic Generator for Compiler Testing. *IEEE Trans. Software Eng.* SE-8, 4, pp. 343-353 (1982).

- Seaman, R. P.: Testing high level language compilers. Proc. IEEE Comput. Syst. and Tech. Conf., 1974, pp. 366-375.

- Pesh, H., Schnupp, P., Schaller, H., and Spirk, A. P.: Test Case generation Using PROLOG. Proc. 8th ICSE, 1985, pp. 252-258.

- Boug, L., Choquet, N., Fribourg, L., and Gaudel, M. C.: Application of PROLOG to Test Sets Generations. *Lect. Notes Comput. Sci.*, 186, pp. 261-275 (1985).

- Tatsumi, K.: Test Case Design Support System. Proc. Int. Conf. Quality Control (ICQC '87), JUSE, 1987, pp. 615-620.

- 12) Tatsumi, K.: Conceptual Support for Test Case Design. Proc. COMPSAC87, 1987, pp. 285-290.

Hiroshi Kawata received the B.E. degree in electrical engineering from Kyushu Institute of Technology, Fukuoka, Japan, in 1964 and Dr. degree in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1970.

He joined Fujitsu Ltd., Kawasaki, in 1970 and has been engaged in development of compiler, database system, and various software tools.

He is a member of Information Processing Society of Japan.

**Hiroshi Saijo** received the B.E. in physical engineering and the M.E. degree in thformation engineering from Tohoku University, Sendai, Japan, in 1977 and 1980. He joined Fujitsu Ltd., Kawasaki, in 1980 and has been working on quality

He is a member of Information Processing Society of Japan.

Chikao Shioya received the B.E. degree in electrical engineering from Keio University, Yokohama, Japan, in 1985.

He joined Fujitsu Ltd., in 1985 and has been working on quality assurence of software products. His Interest includes artificial intelligence.

He is a member of Information Processing Society of Japan.

### Variable Ordering of Binary Decision Diagrams for Multi-Level Logic Minimization

Masahiro Fujita

Yusuke Matsunaga

(Manuscript received November 27, 1992)

Binary Decision Diagram (BDD) is now widely used in CAD fields, especially in formal verification and logic synthesis. In this paper, variable ordering methods of BDD for the application of multi-level logic minimization are presented. The variable ordering algorithm for sum-of-products representation is based on cover patterns and selects most binate variables first, and the one for multi-level logic representation is based on depth first traversal of circuits. In both cases, the obtained variable orderings are optimized by exchanging a variable with its neighbor in the ordering. Experimental results show the effectiveness of our methods.

### 1. Introduction

In logic synthesis, multi-level logic minimization plays a very important role in order to increase the quality of synthesized circuits in terms of area and testability. There have been many efforts in developing effective and efficient multi-level logic minimization methods, and several logic synthesis systems which include multi-level logic minimization have been developed 1)-6). In all of them, the key point of multi-level minimization is the use of don't care sets; i.e., people have been paying lots of attention to how to effectively use don't care sets and how to keep the size of don't care sets manageable. We have developed a multi-level logic minimization program<sup>5)</sup> based on the transduction method<sup>4)</sup> using Binary Decision Diagram (BDD)<sup>7)</sup> as an internal representation of logic functions. BDD is a canonical representation of logic functions. BDD has obtained much attention, since it can represent practical logic functions like the ones used in ALUs much more compactly than other representations, such as sum-of-products representation. Much larger circuits can be minimized using BDD compared with the original transduction method<sup>4)</sup> which

uses truth tables to represent logic and permissible functions. We also developed a Boolean resubstitution algorithm with permissible functions<sup>6</sup>, which can be considered as an extension of the transduction method. Permissible functions are defined on each gate and express don't care sets which do not change the values of primary outputs. We used BDD to represent permissible functions compactly and get equal or superior performance compared with other multilevel logic minimization programs, such as MIS and BOLD, especially for large circuits.

The performance of our synthesis method, however, highly depends on sizes of BDDs. Sizes of BDDs greatly depend on the variable orderings used, especially for large circuits. In this paper, we present methods to find good variable orderings for BDDs with application to logic synthesis in mind. The problem of finding the best variable ordering is NP-hard<sup>8)</sup>, and a couple of heuristics for *good* variable ordering were proposed <sup>7), 9), 10)</sup>. In Refs. 9 and 10 variable ordering methods based on network topology were developed. Here we use the approach that we first generate an initial variable ordering and then try to optimize it.

Initial variable orderings are generated in two different ways; if the synthesis program receives circuit descriptions in sum-of-products representation, the variable orderings are generated by analyzing cover patterns, and if the synthesis program receives circuit descriptions in multi-level logic representation, the variable orderings are generated by traversing the circuits in depth-first way as shown in Ref. 9. Both these situations can happen in logic synthesis. In some cases, specification for a circuit is in a truth table format, and in other cases, designers want to specify circuits with many intermediate variables which are actually multi-level logic representation. Sometimes designers want to optimize their circuit designs using multi-level logic minimization methods, in which case the input to logic synthesis systems is also in multi-level logic representation.

The initial orderings are optimized in the following way: First we construct BDDs for logic functions using the initial orderings, and then minimize sizes of BDDs by exchanging a variable with its neighbor in the ordering. The resulting orderings are used to calculate permissible functions for multi-level minimizations.

Since sizes of BDD highly depend on variable orderings, minimization time are also drastically influenced by the variable ordering used, although the quality of minimization results does not change. The required time for generation of initial orderings and optimization of them is much less than that for multi-level minimization. We present experimental results and show that we can get large speed-up by the presented methods.

In chapter 2, we briefly review permissible functions expressed in BDDs. In chapter 3, we present the method for initial ordering generation. In chapter 4, we present the method of BDD minimization after constructing BDDs for logic functions. Chapter 5 shows experimental results, and finally chapter 6 gives concluding remarks.

### 2. Boolean resubstitution with permissible functions and BDD

In this chapter, we briefly review the two key issues used in our multi-level logic minimiza-

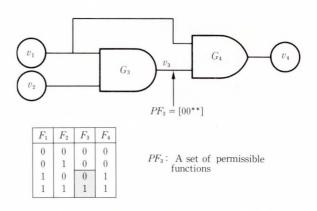

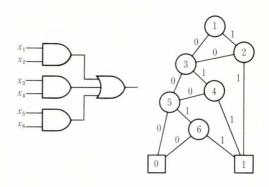

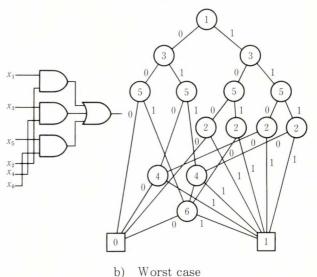

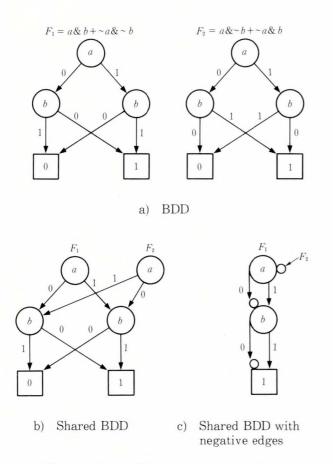

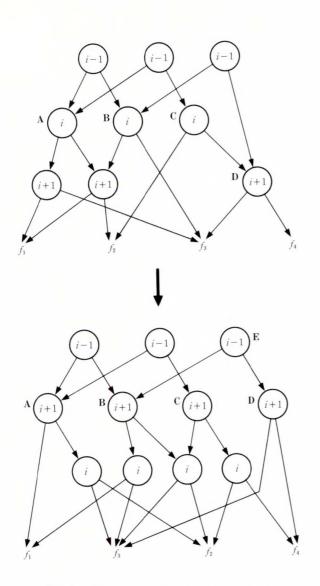

Fig. 1 – An example of permissible functions.

tion methods: permissible functions and BDD. As for the details, please see Refs. 5-7.

### 2.1 Permissible functions

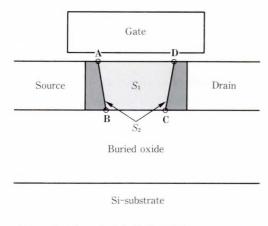

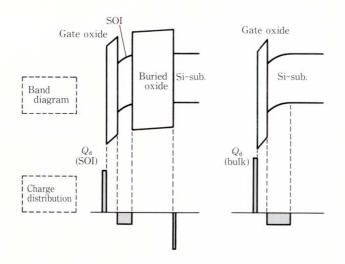

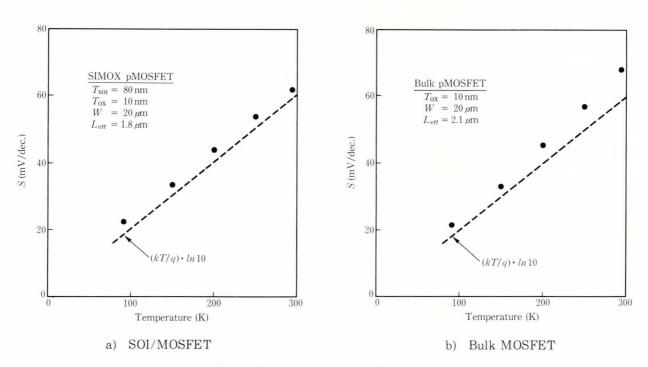

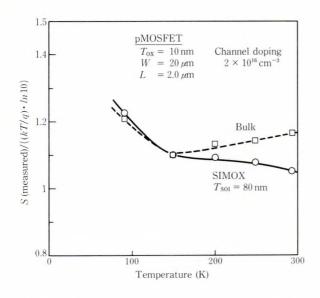

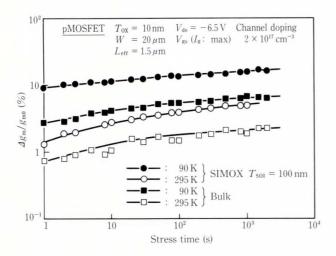

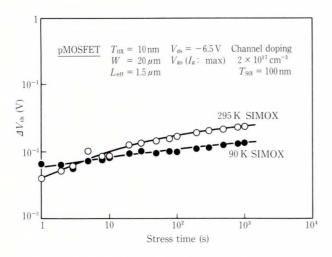

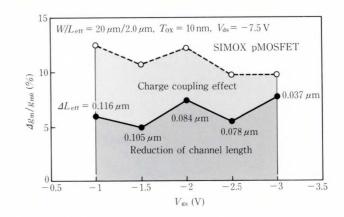

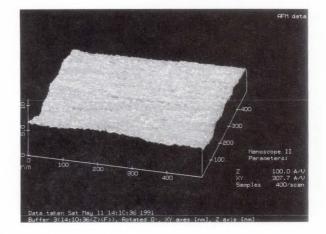

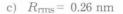

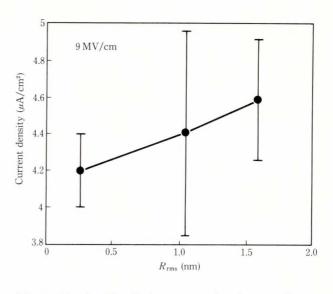

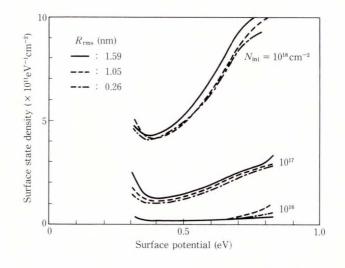

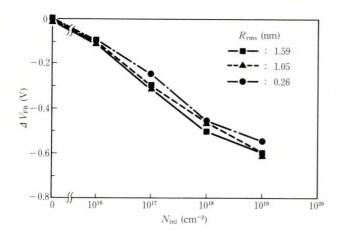

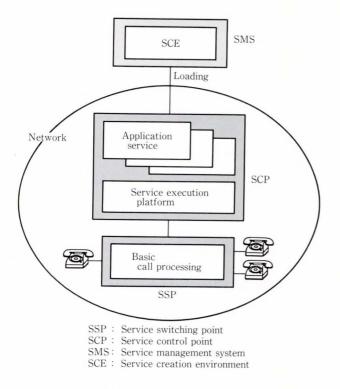

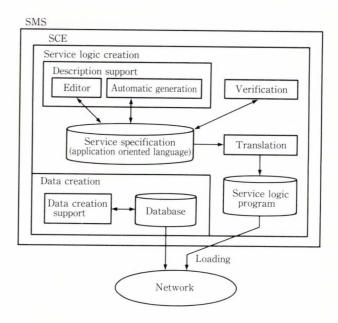

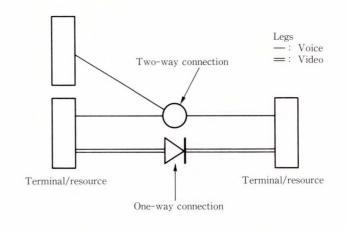

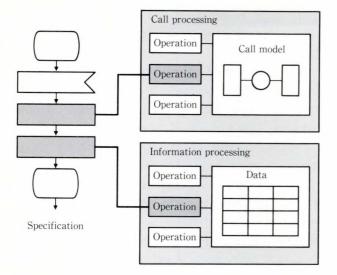

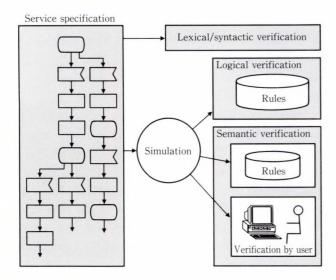

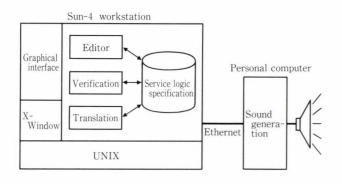

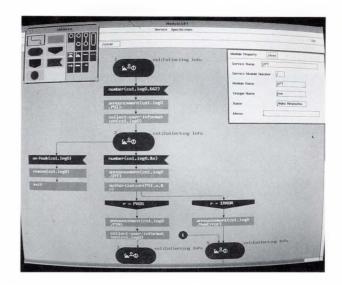

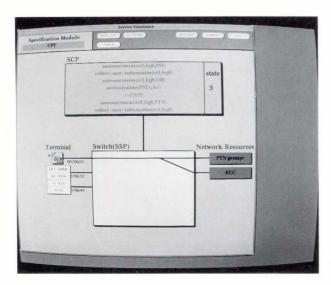

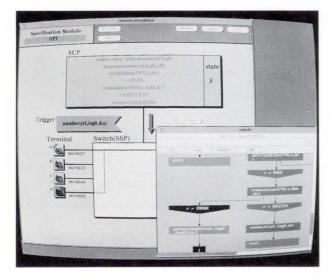

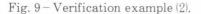

The key concept of permissible functions is that each node in a circuit is an incompletelyspecified logic function of the primary inputs due to the don't care sets obtained from network topologies, and permissible functions represent possible implementations at such nodes<sup>4)</sup>. Permissible functions are defined on each node (a primary input, a gate, or a primary output) in the circuit. They are defined as follows. Assume  $v_i$  is an intermediate node in a network. The logic function of any output variable in the network may not change even when the logic function  $F_i$  of node  $v_i$  is replaced with another logic function  $PF_i$ . Then the logic function  $PF_i$ is called a permissible function of node  $v_i$ .