# M2382K

# Micro-Disk Drives Customer Engineering Manual

|         |                | REVISION RECORD              |

|---------|----------------|------------------------------|

| Edition | Date published | Revised contents             |

| 01      | March, 1988    |                              |

| 01A     | May, 1988      | Editing                      |

| 01B     | October, 1988  | Editing                      |

| 01C     | June, 1989     | Editing                      |

|         |                |                              |

|         |                |                              |

|         |                |                              |

|         |                |                              |

|         |                |                              |

|         |                |                              |

|         |                |                              |

|         |                |                              |

|         |                | Specification No.: 41FH6826E |

Comments concerning this manual should be addressed to one of the following addresses:

FB04517

FUJITSU LIMITED

International Marketing

Marunouchi 1-6-1, Chiyoda-ku, Tokyo 100 JAPAN

TEL: 03-216-3211

FAX: 03-213-7174, 03-216-9353

TLX: J22833

Cable: "FUJITSU LIMITED TOKYO"

FUJITSU AMERICA INC.

3055 Orchard Drive, San Jose, California 95134-2017, U.S.A.

TEL: (1-408) 432-1300

FAX: 408-432-1318, 1319

TLX: 230-176207

TWX: 910-338-2193

FUJITSU CANADA INC.

6280 Northwest Drive, Mississauga, Toronto, Ontario, CANADA

TEL: (1-416) 673-8666 FAX: 416-673-8677

TLX: 968132

FUJITSU EUROPE LIMITED 2, Longwalk Road, Stockly Park,

West Drayton, Middlesex UB11 1AB, ENGLAND

TEL: (44-1) 573-4444 FAX: 1-573-2643 TLX: 263871FEL SP G

FUJITSU DEUTSCHLAND GmbH

Rosenheimerstraße 145, D-8000 München 80, F.R. GERMANY

TEL: (49-89) 413010 FAX: 89-41301100 TLX: 897106 FDG D FUJITSU NORDIC AB

Torggatan 8, 171 54, Solna, SWEDEN

TEL: (46) 8-764-76-90 FAX: 8-28-03-45 TLX: 13411 FNAB S

FUJITSU ITALIA S.p.A.

Via Melchiorre Gioia, 8, 20124 Milano, ITALY

TEL: (39-2) 6572741 FAX: 2-6572257 TLX: 350142 FJITLY I

FUJITSU AUSTRALIA LIMITED

475 Victoria Avenue, Chatswood, N.S.W. 2067, AUSTRALIA

TEL: (61-2) 410-4555 FAX: 2-411-8603, 8362

TLX: 25233

FUJITSU HONG KONG LIMITED

R.M. 1831, Sun Hung Kai Centre, 30 Harbour Road,

HONG KONG

TEL: (852-5) 8915780

FAX: 5-742917

TLX: 62667

The contents of this manual are subject to

change without prior notice.

All Rights Reserved,

FAI Copyright ©1988 FUJITSU LIMITED.

#### **LIST OF EFFECTIVE PAGES**

| PAGE  | REV | PAGE  | REV | PAGE | REV | ] | PAGE | REV |   | PAGE  | REV |   | PAGE            | REV |

|-------|-----|-------|-----|------|-----|---|------|-----|---|-------|-----|---|-----------------|-----|

| Cover | 01C | 2-2   | 01C | 3-13 | 01  |   | 4-44 | 01B |   | 4-95  | 01B |   | 5-26            | 01  |

| Blank | _   | 2-3   | 01  | 3-14 | 01  |   | 4-45 | 01  |   | 4-96  | 01B |   | 5-27            | 01  |

| i     | 01C | 2-4   | 01  | 3-15 | 01  |   | 4-46 | 01  |   | 4-97  | 01B | ĺ | 5-28            | 01  |

| Blank | _   | 2-5   | 01  | 3-16 | 01C | 1 | 4-47 | 01B |   | 4-98  | 01B |   | 5-29            | 01  |

| iii   | 01C | 2-6   | 01  | 3-17 | 01  | İ | 4-48 | 01  |   | 4-99  | 01B | Ī | 5-30            | 01  |

| Blank | _   | 2-7   | 01  | 3-18 | 01A |   | 4-49 | 01B |   | 4-100 | 01B |   | 5-31            | 01  |

| v     | 01A | 2-8   | 01  | 3-19 | 01  |   | 4-50 | 01B |   | 4-101 | 01B |   | 5-32            | 01  |

| vi    | 01A | 2-9   | 01  | 3-20 | 01C |   | 4-51 | 01B |   | 4-102 | 01B |   | 5-33            | 01  |

| vii   | 01B | 2-10  | 01A | 4-1  | 01A |   | 4-52 | 01B |   | 4-103 | 01B |   | 5-34            | 01  |

| viii  | 01A | 2-11  | 01  | 4-2  | 01A |   | 4-53 | 01B |   | 4-104 | 01B |   | 5-35            | 01  |

| ix    | 01  | 2-12  | 01  | 4-3  | 01  |   | 4-54 | 01B |   | 4-105 | 01B | İ | 5-36            | 01  |

| x     | 01A | 2-13  | 01A | 4-4  | 01  |   | 4-55 | 01B |   | 4-106 | 01B |   | 5-37            | 01  |

| хi    | 01B | 2-14  | 01A | 4-5  | 01  |   | 4-56 | 01B |   | 4-107 | 01B |   | 5-38            | 01  |

| xii   | 01B | 2-15  | 01  | 4-6  | 01  |   | 4-57 | 01B |   | 4-108 | 01B |   | 5-39            | 01  |

| xiii  | 01A | 2-16  | 01  | 4-7  | 01  |   | 4-58 | 01B |   | 4-109 | 01B |   | 5-40            | 01  |

| Blank | _   | 2-17  | 01  | 4-8  | 01  | İ | 4-59 | 01B | İ | 4-110 | 01B |   | 5-41            | 01  |

| xv    | 01A | 2-18  | 01  | 4-9  | 01  |   | 4-60 | 01B |   | 4-111 | 01B |   | 5-42            | 01  |

| xvi   | 01  | 2-19  | 01  | 4-10 | 01A |   | 4-61 | 01B |   | 4-112 | 01B |   | 6-1             | 01A |

| 1-1   | 01A | 2-20  | 01  | 4-11 | 01  |   | 4-62 | 01B |   | 4-113 | 01B |   | 6-2             | 01  |

| 1-2   | 01A | 2-21  | 01  | 4-12 | 01  |   | 4-63 | 01B |   | 4-114 | 01B |   | 6-3             | 01  |

| 1-3   | 01A | 2-22  | 01  | 4-13 | 01  |   | 4-64 | 01B |   | 4-115 | 01B |   | 6-4             | 01  |

| 1-4   | 01  | 2-23  | 01A | 4-14 | 01  |   | 4-65 | 01B |   | 4-116 | 01B |   | 6-5             | 01  |

| 1-5   | 01A | 2-24  | 01  | 4-15 | 01A |   | 4-66 | 01B |   | 4-117 | 01B |   | 6-6             | 01  |

| 1-6   | 01  | 2-25  | 01  | 4-16 | 01  |   | 4-67 | 01B |   | 4-118 | 01A |   | 6-7             | 01  |

| 1-7   | 01  | 2-26  | 01A | 4-17 | 01C |   | 4-68 | 01B |   | 4-119 | 01B |   | 6-8             | 01  |

| 1-8   | 01A | 2-27  | 01  | 4-18 | 01  |   | 4-69 | 01B |   | 4-120 | 01B |   | 6-9             | 01  |

| 1-9   | 01A | 2-28  | 01  | 4-19 | 01  |   | 4-70 | 01B |   | 5-1   | 01  |   | 6-10            | 01  |

| 1-10  | 01A | 2-29  | 01A | 4-20 | 01  |   | 4-71 | 01B |   | 5-2   | 01  |   | 6-11            | 01  |

| 1-11  | 01A | 2-30  | 01A | 4-21 | 01  |   | 4-72 | 01B |   | 5-3   | 01A |   | 6-12            | 01  |

| 1-12  | 01  | 2-31  | 01  | 4-22 | 01A |   | 4-73 | 01B |   | 5-4   | 01  |   | 6-13            | 01  |

| 1-13  | 01  | 2-32  | 01  | 4-23 | 01  |   | 4-74 | 01B |   | 5-5   | 01  |   | 6-14            | 01A |

| 1-14  | 01  | 2-33  | 01  | 4-24 | 01  |   | 4-75 | 01B |   | 5-6   | 01  |   | 6-15            | 01  |

| 1-15  | 01  | 2-34  | 01  | 4-25 | 01  | Ì | 4-76 | 01B |   | 5-7   | 01  |   | 6-16            | 01  |

| 1-16  | 01C | 2-35  | 01A | 4-26 | 01  |   | 4-77 | 01B |   | 5-8   | 01  |   | 6-17            | 01  |

| 1-17  | 01C | 2-36  | 01B | 4-27 | 01A |   | 4-78 | 01B |   | 5-9   | 01  |   | 6-18            | 01A |

| 1-18  | 01  | 2-37  | 01A | 4-28 | 01  |   | 4-79 | 01B |   | 5-10  | 01  |   | 6-19            | 01  |

| 1-19  | 01  | 2-38  | 01  | 4-29 | 01  |   | 4-80 | 01B |   | 5-11  | 01  |   | Blank           | _   |

| 1-20  | 01  | 2-39  | 01  | 4-30 | 01  |   | 4-81 | 01B |   | 5-12  | 01  |   | 7-1             | 01  |

| 1-21  | 01  | Blank | -   | 4-31 | 01  |   | 4-82 | 01B |   | 5-13  | 01  |   | Blank           | _   |

| 1-22  | 01A | 3-1   | 01  | 4-32 | 01B |   | 4-83 | 01B |   | 5-14  | 01  |   | Reader          |     |

| 1-23  | 01  | 3-2   | 01  | 4-33 | 01C |   | 4-84 | 01B |   | 5-15  | 01  |   | Comment<br>Card | _   |

| 1-24  | 01  | 3-3   | 01  | 4-34 | 01B |   | 4-85 | 01B |   | 5-16  | 01  |   | Blank           | _   |

| 1-25  | 01  | 3-4   | 01  | 4-35 | 01B |   | 4-86 | 01B |   | 5-17  | 01  |   | Cover           | 01C |

| 1-26  | 01  | 3-5   | 01  | 4-36 | 01B |   | 4-87 | 01B |   | 5-18  | 01  |   |                 |     |

| 1-27  | 01  | 3-6   | 01  | 4-37 | 01B |   | 4-88 | 01B |   | 5-19  | 01  |   |                 |     |

| 1-28  | 01  | 3-7   | 01  | 4-38 | 01B |   | 4-89 | 01B |   | 5-20  | 01  |   |                 |     |

| 1-29  | 01A | 3-8   | 01  | 4-39 | 01C |   | 4-90 | 01B |   | 5-21  | 01  |   |                 |     |

| 1-30  | 01A | 3-9   | 01  | 4-40 | 01B |   | 4-91 | 01B |   | 5-22  | 01  |   |                 |     |

| 1-31  | 01  | 3-10  | 01  | 4-41 | 01  |   | 4-92 | 01B |   | 5-23  | 01  |   |                 |     |

| 1-32  | 01  | 3-11  | 01  | 4-42 | 01B |   | 4-93 | 01  |   | 5-24  | 01  |   |                 |     |

| 2-1   | 01  | 3-12  | 01  | 4-43 | 01B |   | 4-94 | 01B |   | 5-25  | 01  |   |                 |     |

# **CONTENTS**

|       |                                    | Page |

|-------|------------------------------------|------|

| СНАР  | TER 1 GENERAL                      | 1-1  |

| 1.1   | General Description                | 1-1  |

| 1.1.1 | Introduction                       | 1-1  |

| 1.1.2 | Features                           | 1-1  |

| 1.2   | Specification                      | 1-3  |

| 1.2.1 | Functional specifications          | 1-3  |

| 1.2.2 | Physical specifications            |      |

| 1.2.3 | DC power requirements              | 1-5  |

| 1.2.4 | High frequency noise specification | 1-7  |

| 1.2.5 | Reliability                        | 1-9  |

| 1.2.6 | Error rate                         | 1-10 |

| 1.2.7 | Media defects                      | 1-10 |

| 1.3   | Configuration                      | 1-13 |

| 1.3.1 | Fundamental configuration          | 1-13 |

| 1.3.2 | Options                            | 1-15 |

| СНАР  | TER 2 INSTALLATION                 | 2-1  |

| 2.1   | Unpacking                          | 2-1  |

| 2.2   | Visual Inspection                  | 2-1  |

| 2.3   | Installation                       | 2-2  |

| 2.3.1 | Mounting dimensions                | 2-2  |

| 2.3.2 | Service area                       | 2-5  |

| 2.3.3 | Shock/Vibration stopper            | 2-6  |

| 2.3.4 | Cooling                            | 2-7  |

| 2.4   | Mounting of Options                | 2-10 |

| 2.4.1 | Mounting fan unit                  | 2-10 |

| 2.4.2 | Mounting panel unit                | 2-11 |

| 2.4.3 | Mounting diagnostic panel unit     | 2-12 |

| 2.4.4 | Installation mounting tray         | 2-14 |

| 2.5   | Cabling                            | 2-22 |

| 2.5.1 | Connectors on drive side           | 2-22 |

| 2.5.2  | Power cable connection                     | 2-22 |

|--------|--------------------------------------------|------|

| 2.5.3  | Interface cabling                          | 2-24 |

| 2.5.4  | System grounding                           | 2-27 |

| 2.6    | Mode Select Settings                       | 2-27 |

| 2.6.1  | Disk addressing                            | 2-28 |

| 2.6.2  | Tag 4/5 enable                             | 2-29 |

| 2.6.3  | File protect                               | 2-29 |

| 2.6.4  | Device type (optional)                     | 2-30 |

| 2.6.5  | Sector mode                                | 2-30 |

| 2.6.6  | Sector counting                            | 2-31 |

| 2.6.7  | Calibration seek                           | 2-35 |

| 2.6.8  | ON-Side switch (for vertical mount)        | 2-35 |

| 2.6.9  | Spindle start delay switch                 | 2-36 |

| 2.6.10 | Disable channel A or B                     | 2-37 |

| 2.6.11 | Release timer                              | 2-37 |

| 2.6.12 | Remote/Local                               | 2-38 |

| 2.6.13 | Inhibit switch of Index and Sector signals | 2-38 |

| 2.7    | Shipping                                   | 2-39 |

| 2.8    | Storage and Repacking                      | 2-39 |

| СНАР   | TER 3 OPERATION                            | 3-1  |

| 3.1    | Power ON/OFF                               | 3_1  |

| 3.2    | Panel Unit                                 |      |

| 3.3    | Diagnostic Panel Unit                      |      |

| 3.3.1  | LEDs and switches                          |      |

|        | Function modes                             |      |

| 3.3.3  | Function mode setting                      |      |

| 3.3.4  | Flowchart and seven-segment display        |      |

| 3.3.5  | Error codes                                |      |

| 3.4    | Main PCA                                   |      |

| 3.5    | Power Supply                               |      |

|        |                                            |      |

|        | TER 4 THEORY OF OPERATION                  |      |

| 4.1    | Mechanical Assemblies                      |      |

| 4.2    | Heads and Recording Media                  |      |

| 4.2.1  | Heads                                      | 4-2  |

|        |                                            |      |

| 4.2.3   | Servo track format                        |

|---------|-------------------------------------------|

| 4.2.4   | Data surface format                       |

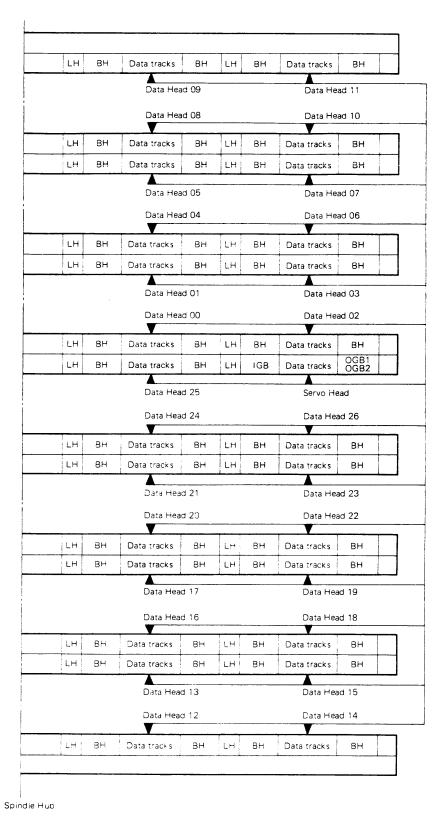

| 4.2.5   | Head and surface configuration            |

| 4.3     | Interface                                 |

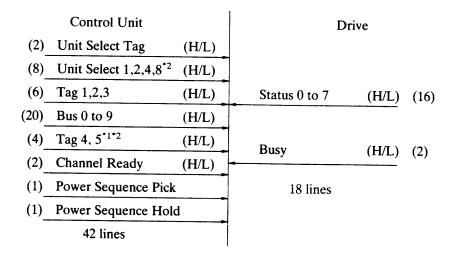

| 4.3.1   | Signal lines                              |

| 4.3.2   | Description of Signal Lines               |

| 4.3.3   | Timing                                    |

| 4.3.3.1 | Format                                    |

| 4.3.3.2 | Fixed Sector format                       |

| 4.3.3.3 | Variable Sector format                    |

| 4.3.3.4 | Format Timing Specification               |

| 4.3.4   | Signal transmission driver/receiver       |

| 4.3.5   | Connector pin assignment                  |

| 4.4     | Electrical Circuit Functions              |

| 4.4.1   | Power-up sequence control                 |

| 4.4.2   | DC motor control                          |

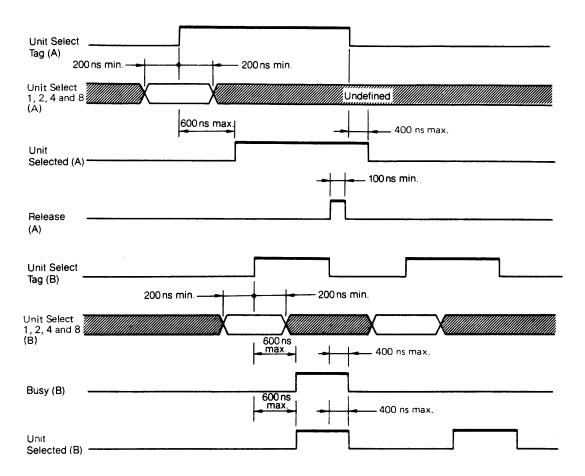

| 4.4.3   | Unit selection                            |

| 4.4.4   | Seek control logic function               |

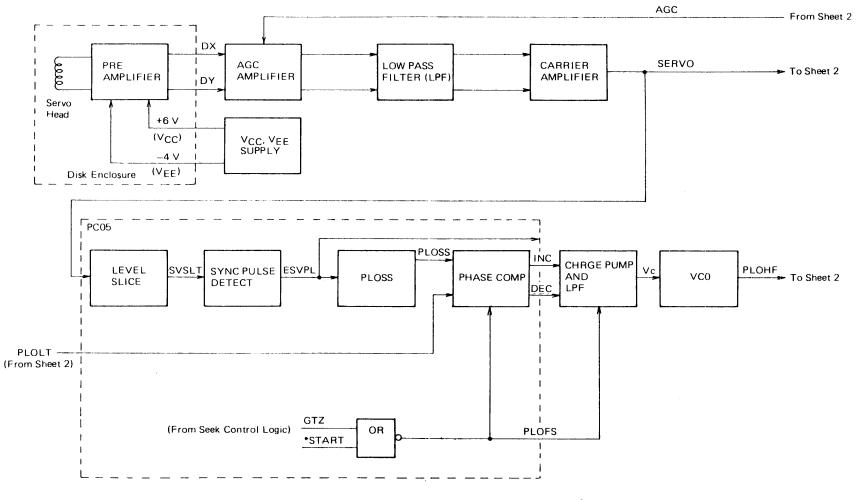

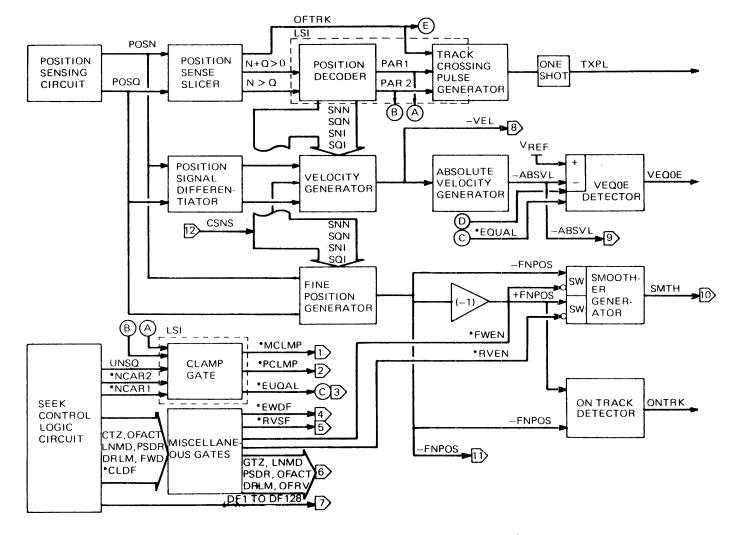

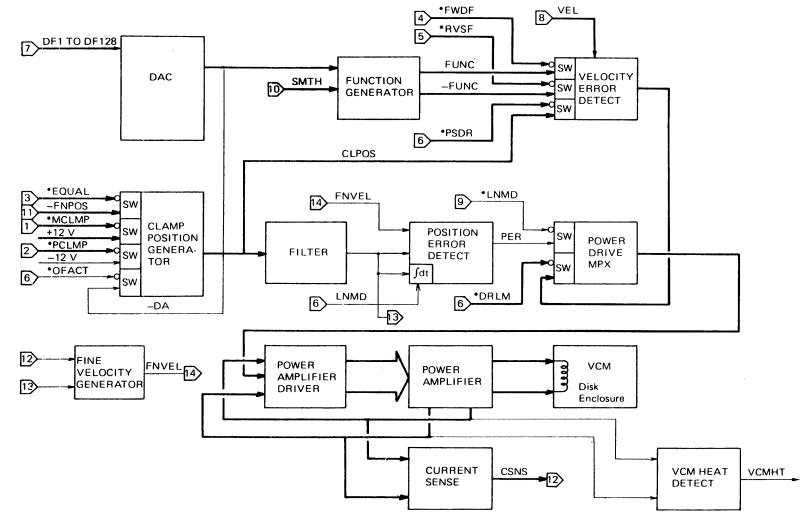

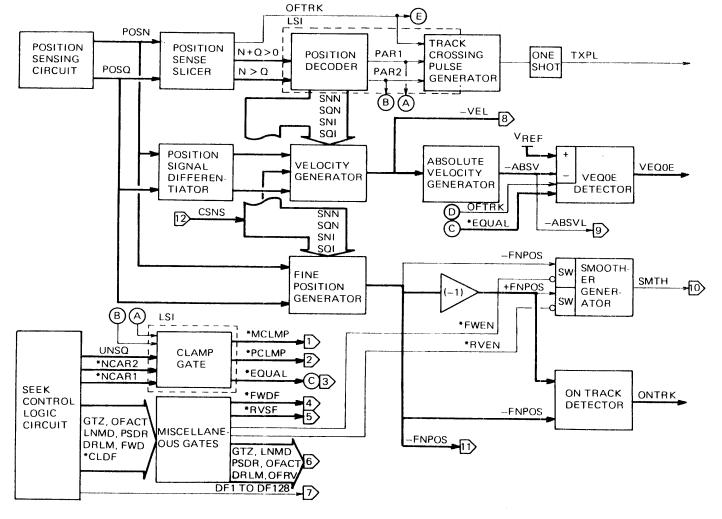

| 4.4.5   | Servo circuit function                    |

| 4.4.6   | Index/Sector/Guard Band generate function |

| 4.4.7   | Head selection                            |

| 4.4.8   | Read/Write function                       |

| 4.4.9   | VFO 4-116                                 |

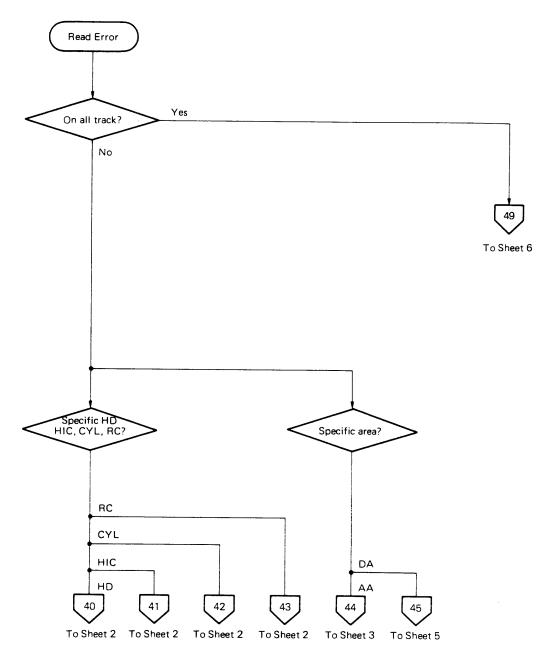

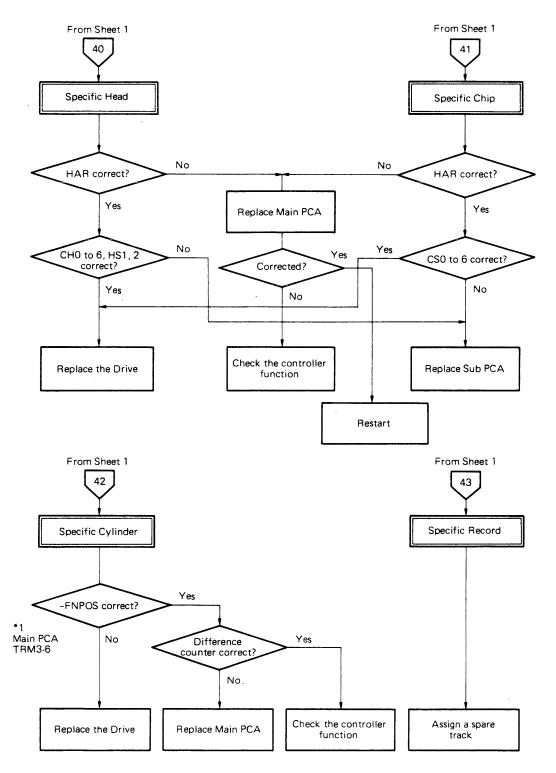

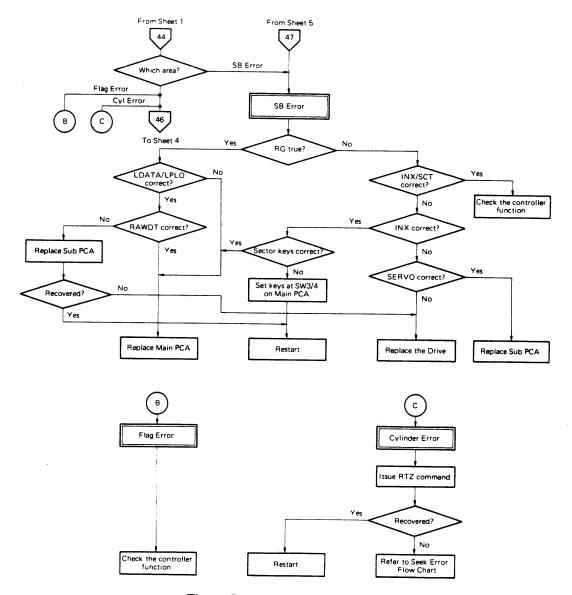

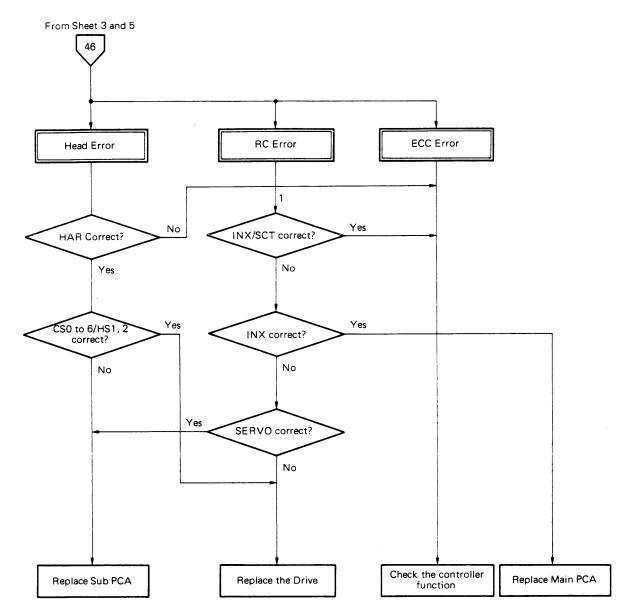

| CHAPI   | TER 5 TROUBLESHOOTING GUIDE               |

| 5.1     | Introduction                              |

| 5.2     | Error Status                              |

| 5.3     | Fault Isolation List                      |

| 5.4     | Troubleshooting Symbol                    |

| 5.5     | Troubleshooting Flowchart                 |

| СНАРТ   | TER 6 MAINTENANCE 6-1                     |

| 6.1     | Introduction                              |

| 6.2     | General Precautions                       |

| 6.2.1   | Power on/off                              |

| 6.2.2   | Parts replacement                         |

| 6.2.3   | Others 6-1                                |

| 6.3   | Maintenance Tools and Equipments 6-1     |

|-------|------------------------------------------|

| 6.4   | Preventive Maintenance                   |

| 6.5   | PCA Replacement 6-2                      |

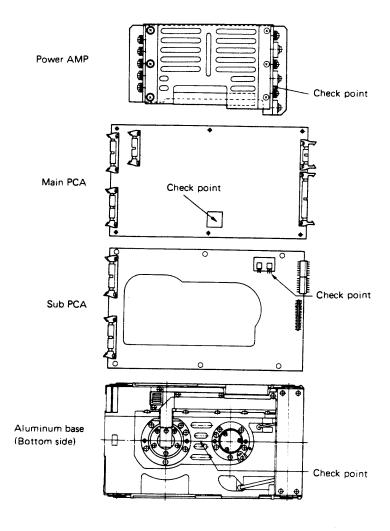

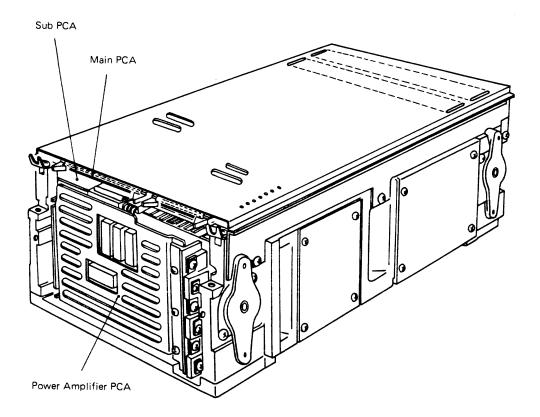

| 6.5.1 | PCA arrangement                          |

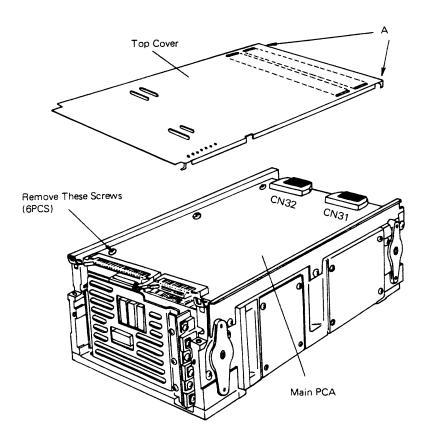

| 6.5.2 | Main PCA replacement procedure 6-3       |

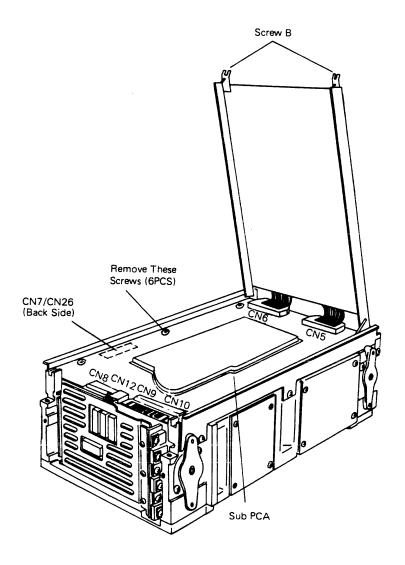

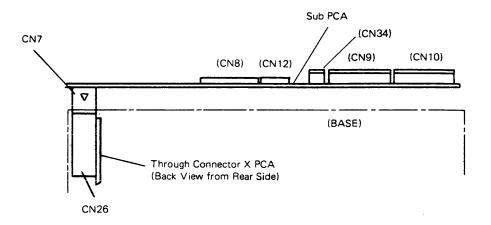

| 6.5.3 | Sub PCA replacement procedure 6-4        |

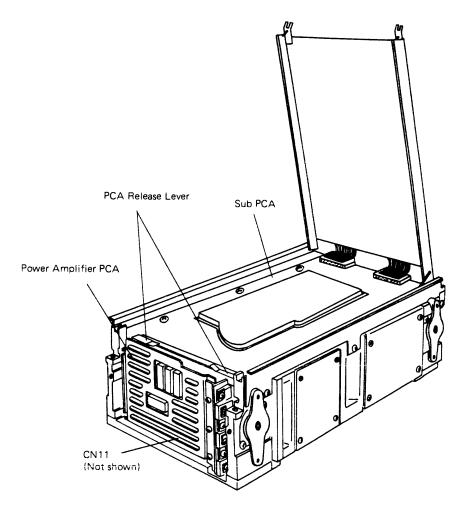

| 6.5.4 | Power Amplifier PCA replacement 6-6      |

| 6.6   | PCA Check and Adjustment 6-7             |

| 6.6.1 | Test point arrangement on PCA 6-7        |

| 6.6.2 | PCA selection after PCA replacement 6-14 |

| 6.6.3 | Electrical measurement 6-15              |

| 6.6.4 | Electrical check and adjustment 6-16     |

| СНАРТ | TER 7 SPARE PARTS 7-1                    |

| 7.1   | Spare Parts                              |

# **FIGURES**

|      | Page                                                       |

|------|------------------------------------------------------------|

| 1.1  | Positioning time profile                                   |

| 1.2  | +24 V DC load current on power up sequence                 |

| 1.3  | Total +24 V DC load current (Ready)                        |

| 1.4  | High frequency noise                                       |

| 1.5  | Measurement procedure                                      |

| 1.6  | Media defect format 1                                      |

| 1.7  | Skip displaced format 2 and 3                              |

| 1.8  | Fundamental configuration 1-13                             |

| 1.9  | Block diagram                                              |

| 1.10 | Fan unit: B03B-4880-E011A                                  |

| 1.11 | Optional fan unit alarm                                    |

| 1.12 | Power supply unit: B14L-5105-0244A                         |

| 1.13 | Power supply unit: B14L-5105-0247A#A1                      |

| 1.14 | 19-inch rack mount installation                            |

| 1.15 | Mounting tray                                              |

| 1.16 | A-cables for daisy-chain (non-shield type)                 |

| 1.17 | A-cables for daisy-chain (shield type)                     |

| 1.18 | Power cable: B660-0625-T453A                               |

| 1.19 | Power cable: B660-0625-T454A 1-27                          |

| 1.20 | Power cable: B660-0620-T455A 1-27                          |

| 1.21 | Power cable: B660-0620-T456A 1-28                          |

| 1.22 | Cable: B660-1995-T003A (E501A Panel unit-Drive connecting) |

| 1.23 | Cable: B660-2560-T004A (Diagnostic panel-drive)            |

| 1.24 | Panel unit: B03B-4880-E501A                                |

| 1.25 | Mounting panel unit                                        |

| 1.26 | Diagnostic panel unit                                      |

| 2.1  | External view of carton 2-2                                |

| 2.2  | Acceptable mounting positions                              |

| 2.3  | Mounting dimensions                                        |

| 2.4  | Maintenance access                                         |

| 2.5  | Shock/Vibration stopper2-6                                 |

| 2.6  | Recommended air flow pattern                  |    |

|------|-----------------------------------------------|----|

| 2.7  | Thermal check point location                  |    |

| 2.8  | Examples of installation cooling              |    |

| 2.9  | Mounting fan unit                             | 0  |

| 2.10 | Mounting panel unit                           | 1  |

| 2.11 | Mounting diagnostic panel unit                | 2  |

| 2.12 | 19-inch rack mount installation               | 4  |

| 2.13 | Bracket assembly                              | 5  |

| 2.14 | Bracket assembly mounting on the 19-inch rack | 6  |

| 2.15 | Mounting tray to the outer rails              | 7  |

| 2.16 | Bracket mounting                              | 8  |

| 2.17 | Mounting drive                                | 9  |

| 2.18 | Mounting the panel unit                       | 0  |

| 2.19 | Power supply unit installation                | 1  |

| 2.20 | Mounting positions of connectors              | 2  |

| 2.21 | System interface cabling                      | 4  |

| 2.22 | Interface cabling                             | 5  |

| 2.23 | Cable termination                             | 6  |

| 2.24 | Mode Select switch location                   | 7  |

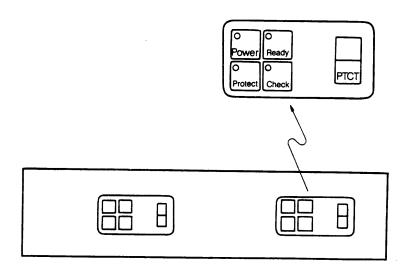

| 3.1  | Optional panel unit                           |    |

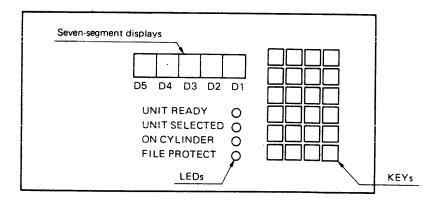

| 3.2  | Diagnostic panel unit                         |    |

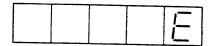

| 3.3  | Error display                                 |    |

| 3.4  | Fault display location on main PCA            | 6  |

| 3.5  | Front view of power supply unit               | 0  |

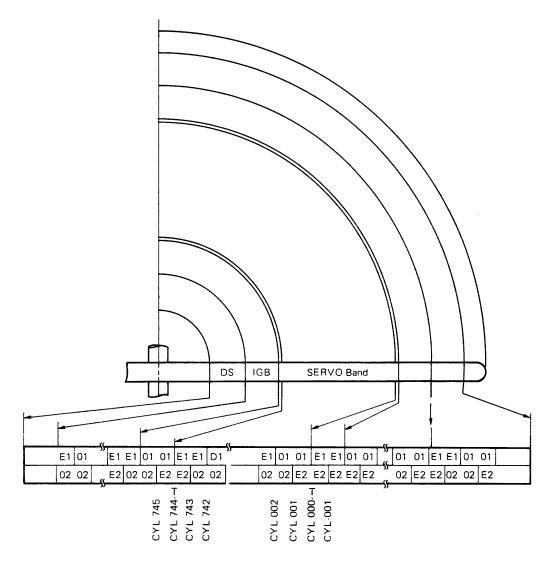

| 4.1  | Servo track configuration                     |    |

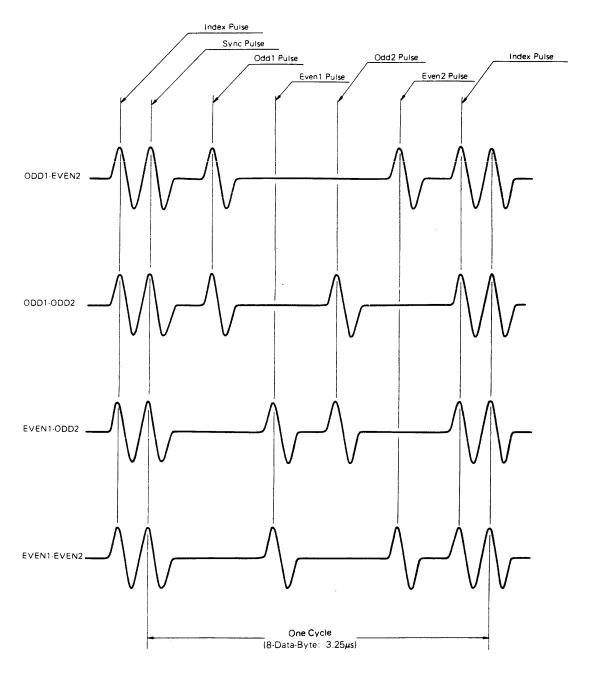

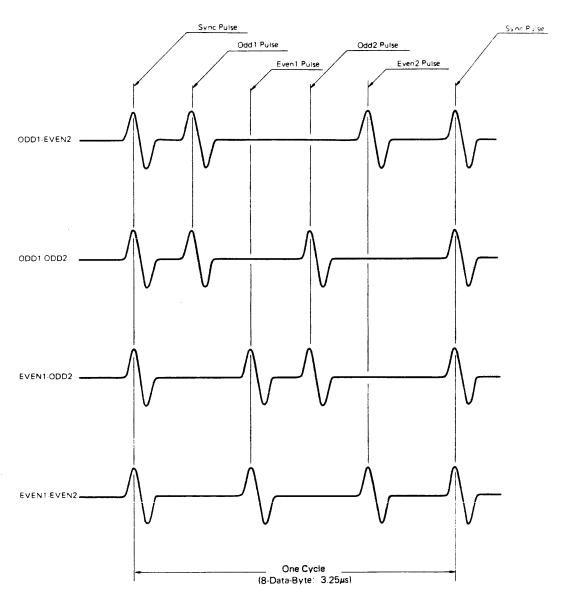

| 4.2  | Normal bit pattern                            |    |

| 4.3  | Index bit pattern 4-6                         |    |

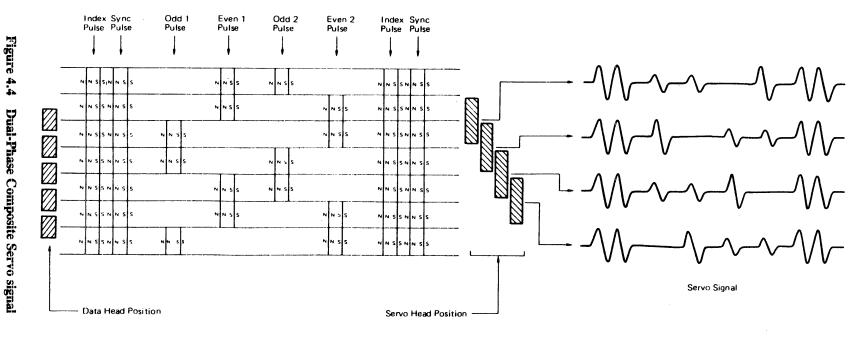

| 4.4  | Dual-Phase Composite Servo signal             |    |

| 4.6  | M2382K surface configuration                  | 1  |

| 4.7  | A-cable signals4-1                            | 2  |

| 4.8  | B-cable signals4-1                            | 3  |

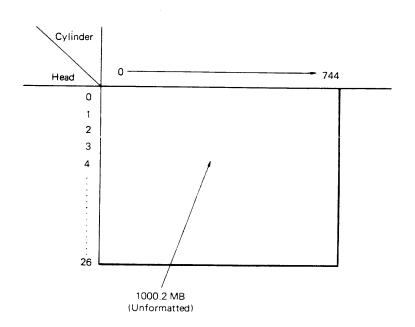

| 4.10 | M2382K cylinder/head addressing               | 5  |

| 4.11 | Unit Select timing                            | 4  |

| 4.12 | Priority Select timing                        | :5 |

| 4.13 | Seek timing4-                                  | 26 |

|------|------------------------------------------------|----|

| 4.14 | Same Cylinder Address                          | 26 |

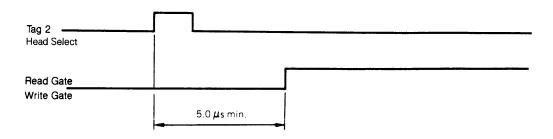

| 4.15 | Tag 1/Tag 2 timing                             | 27 |

| 4.16 | Tag 2 Read/Write timing4-                      | 27 |

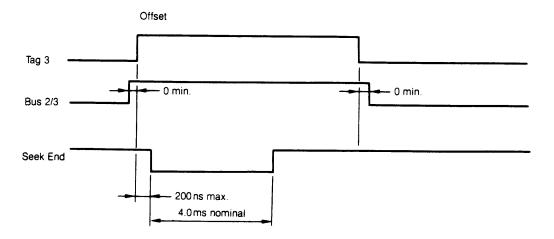

| 4.17 | Offset timing4-                                | 27 |

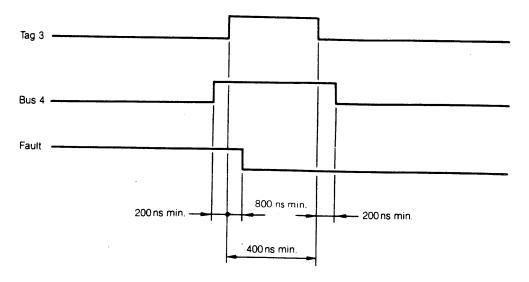

| 4.18 | Fault clear timing 4-                          | 28 |

| 4.19 | RTZ timing 4-                                  | 28 |

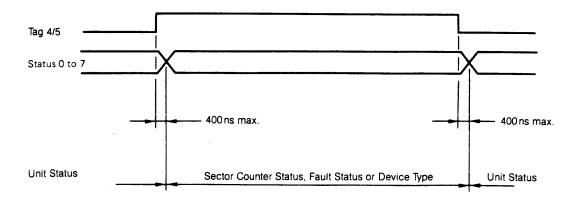

| 4.20 | Tag 4/5 and Status lines                       | 29 |

| 4.21 | Index/Sector timing 4-                         | 29 |

| 4.22 | 1F Write Clock, Write Clock/Write Data 4-      | 30 |

| 4.23 | Read Clock/Read Data timing4-                  | 31 |

| 4.24 | Channel Ready timing 4-                        | 31 |

| 4.25 | Format Write timing 4-                         | 36 |

| 4.26 | Data Write timing 4-                           | 36 |

| 4.27 | Data Read timing4-                             | 37 |

| 4.28 | 1F Write Clock in reading4-                    | 38 |

| 4.29 | Write-to-Read transient4-                      | 39 |

| 4.30 | AM Write timing 4-                             | 39 |

| 4.31 | AM Read timing 4                               | 40 |

| 4.32 | *A-cable Driver/Receiver                       | 42 |

| 4.33 | B-cable Driver/Receiver                        | 43 |

| 4.34 | Clock/Data Driver/Receiver                     | 44 |

| 4.35 | Power up sequence control block diagram        | 49 |

| 4.36 | Power up sequence flowchart4-:                 | 50 |

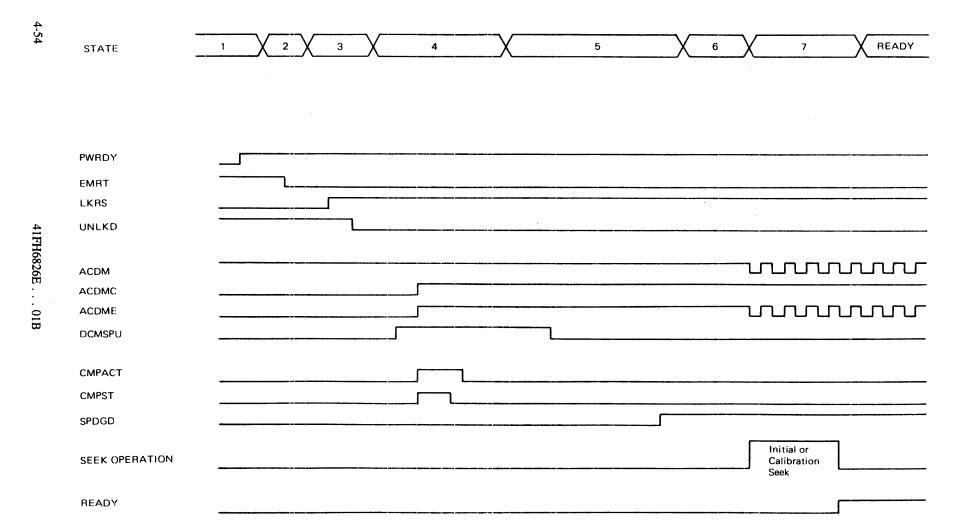

| 4.37 | Power up sequence control timing chart         | 54 |

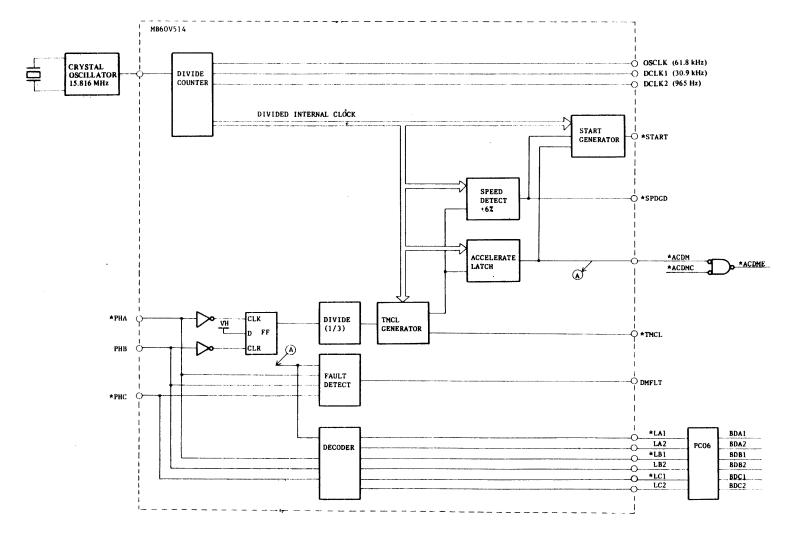

| 4.38 | DC motor control block diagram4-:              | 56 |

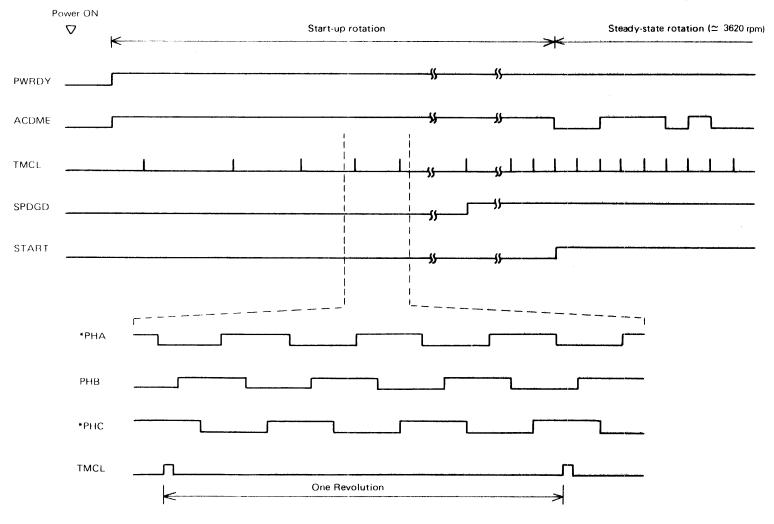

| 4.39 | DC motor control timing chart4-:               | 57 |

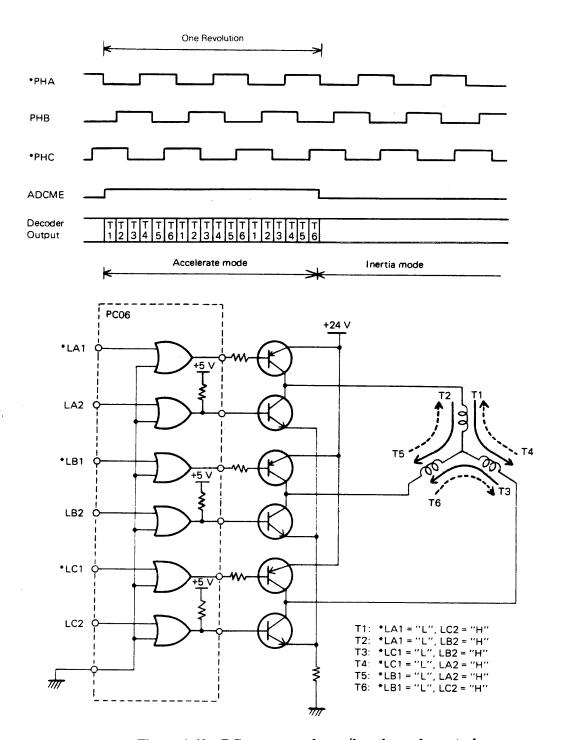

| 4.40 | DC motor accelerate/inertia mode control       | 58 |

| 4.41 | Functional block diagram of select/reserve 4-6 | 50 |

| 4.42 | Select/Reserve timing chart 4-6                | 51 |

| 4.43 | Seek control logic block diagram 4-6           | 53 |

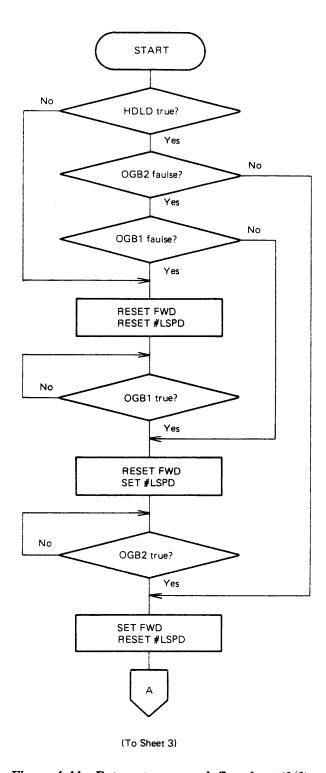

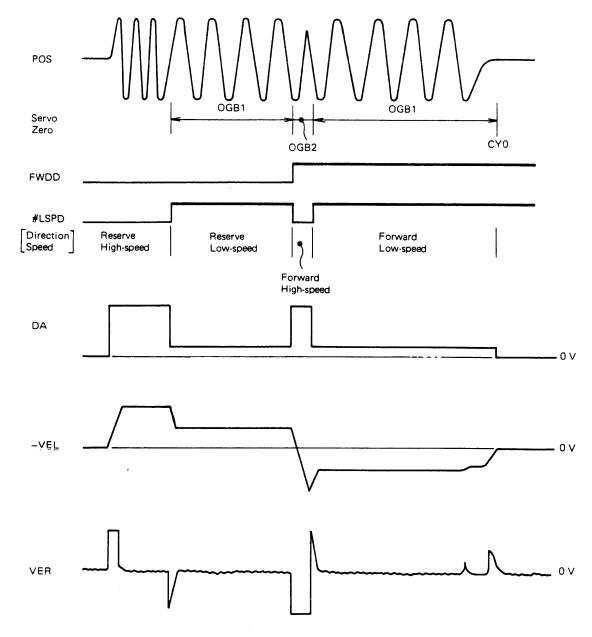

| 4.44 | Return to zero seek flowchart 4-6              | 55 |

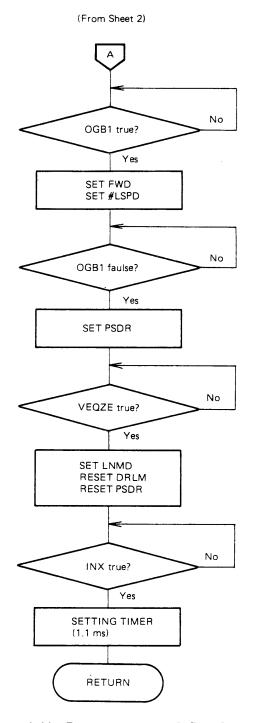

| 4.45 | Return to zero seek timing chart 4-6           | 58 |

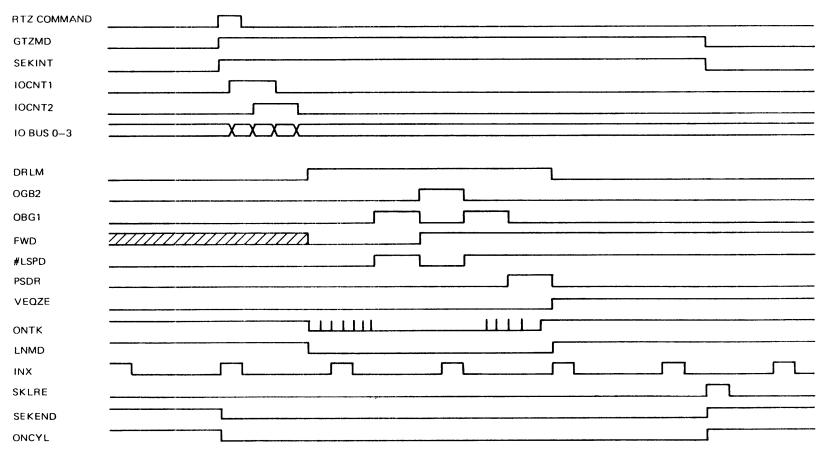

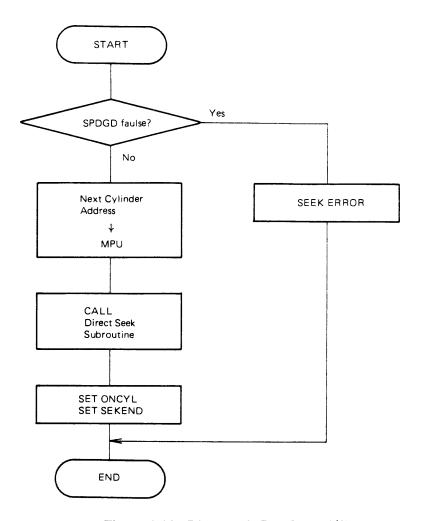

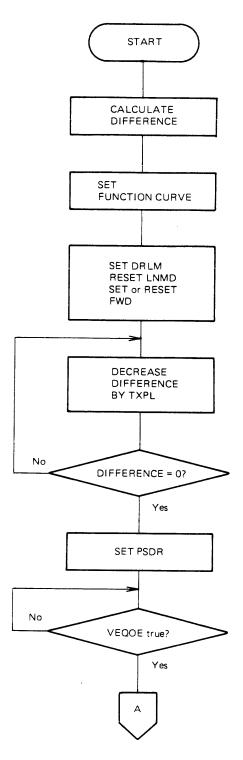

| 4.46 | Direct seek flowchart                          | 70 |

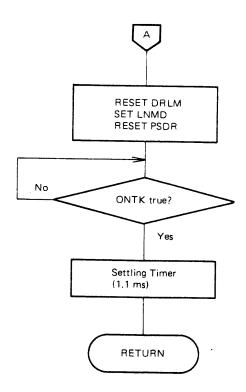

| 4.47 | Direct seek timing chart 4-7                   | 73 |

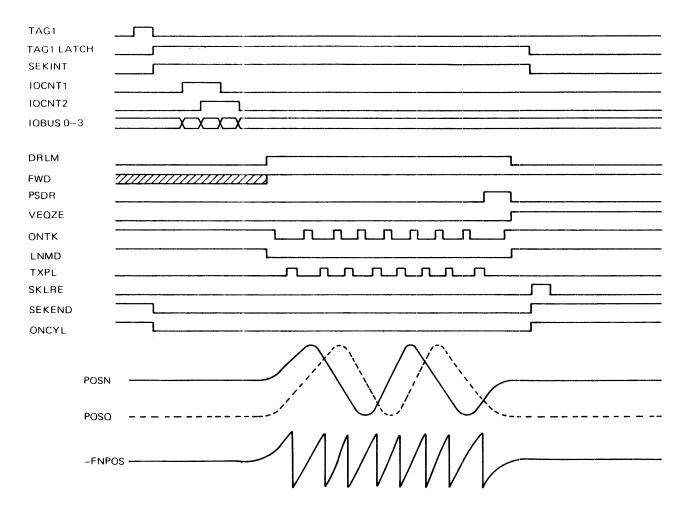

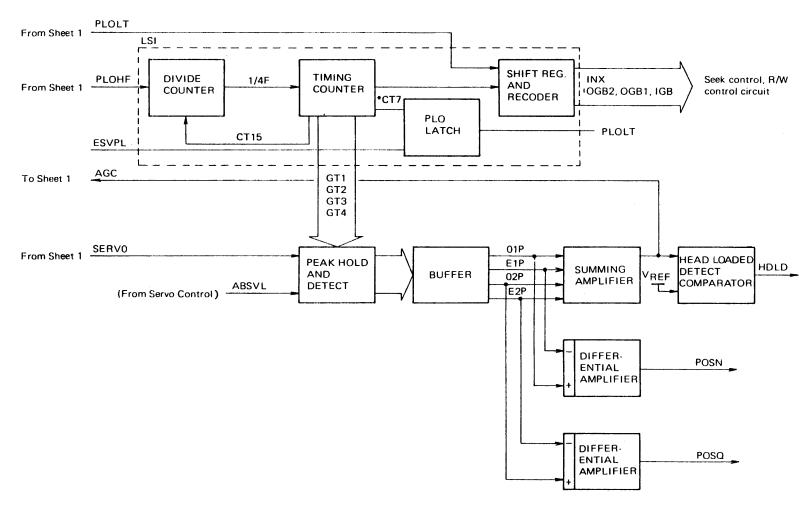

| 4.48 | Position sensing block diagram                 |    |

| 4.49 | PLO and peak hold timing chart                 | 4-78  |

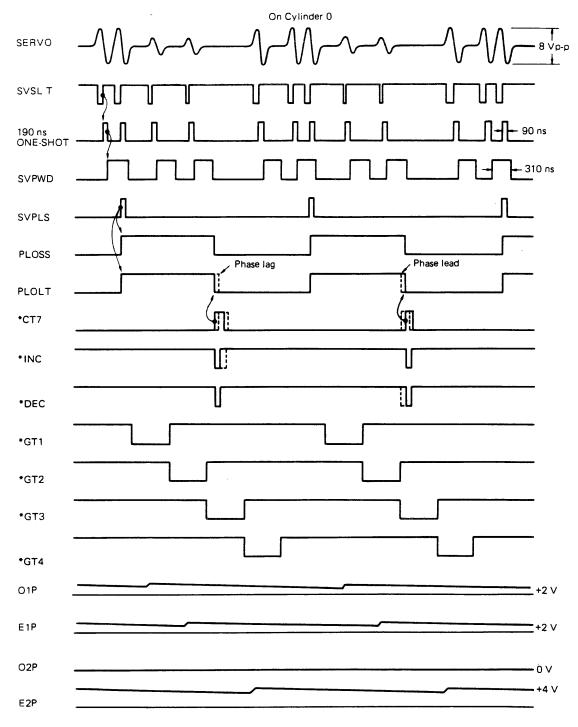

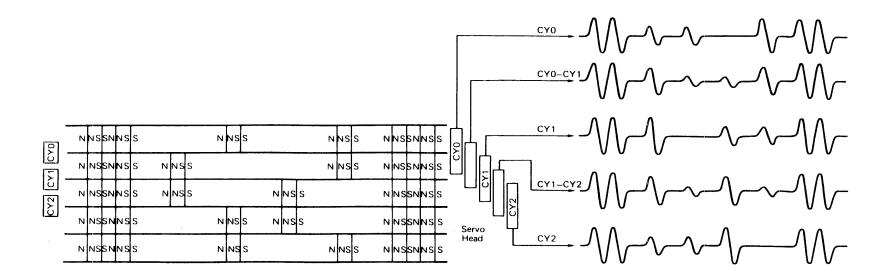

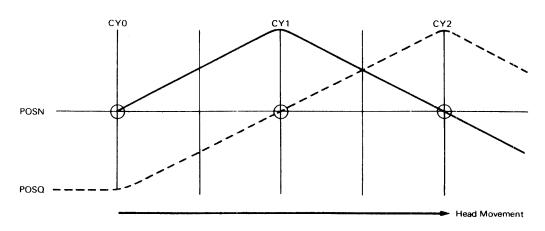

|------|------------------------------------------------|-------|

| 4.50 | Servo signal to Position signal conversion     | 4-79  |

| 4.51 | Servo control block diagram                    | 4-81  |

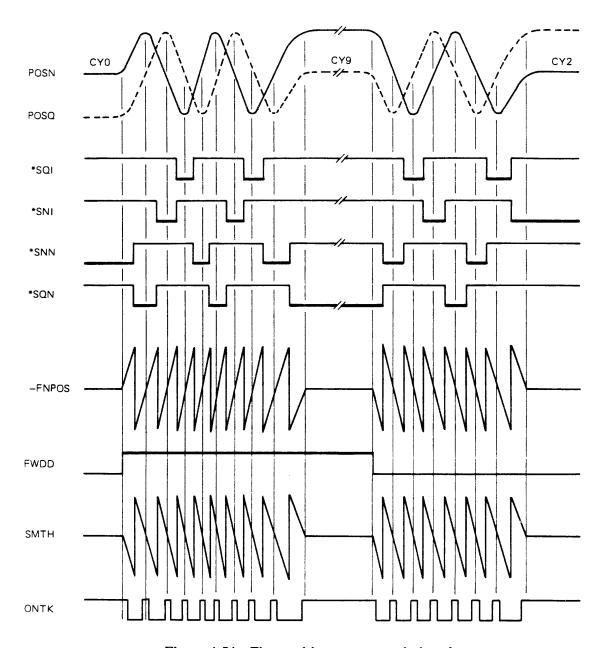

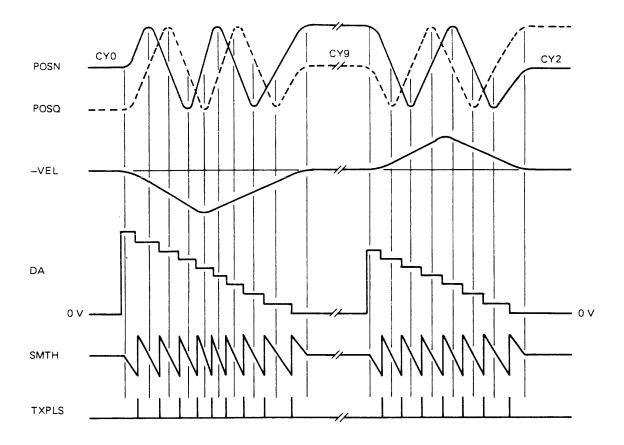

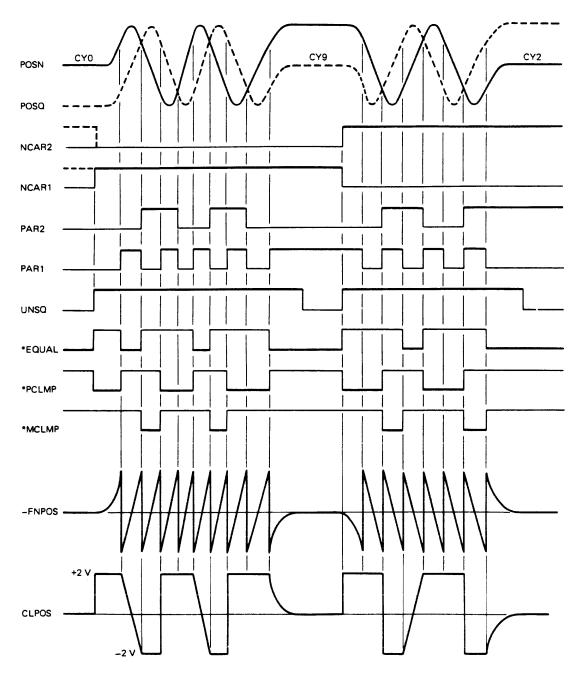

| 4.52 | Position detect timing chart                   | 4-83  |

| 4.53 | Velocity generator timing chart                | 4-85  |

| 4.54 | Fine position generator timing chart           | 4-87  |

| 4.55 | Direct Seek target velocity generator          | 4-89  |

| 4.56 | GTZ target velocity generator                  | 4-90  |

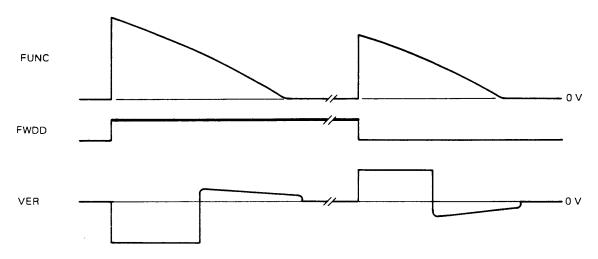

| 4.57 | Clamp Position timing chart                    | 4-92  |

| 4.58 | Direct Seek signal flowchart                   | 4-95  |

| 4.59 | GTZ signal flowchart                           | 4-97  |

| 4.60 | Linear Mode signal flowchart                   | 4-99  |

| 4.61 | Index/Guard Band patterns detect block diagram | 4-102 |

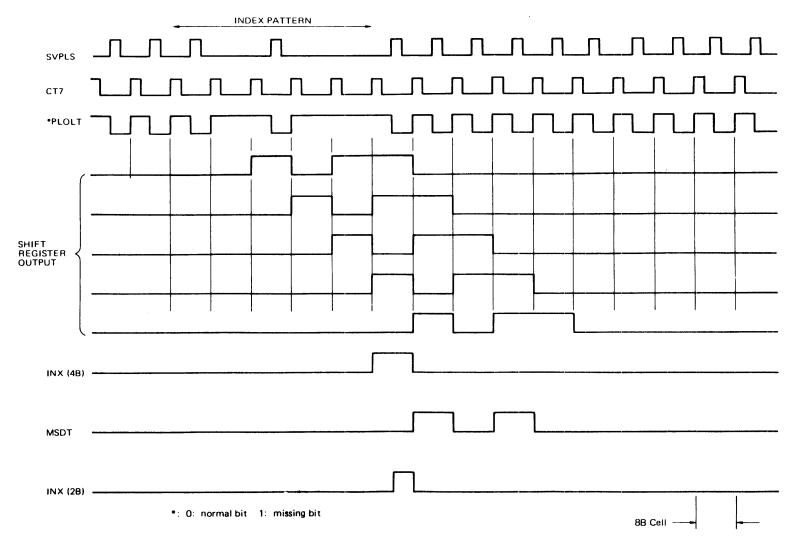

| 4.62 | Index detect timing chart                      | 4-103 |

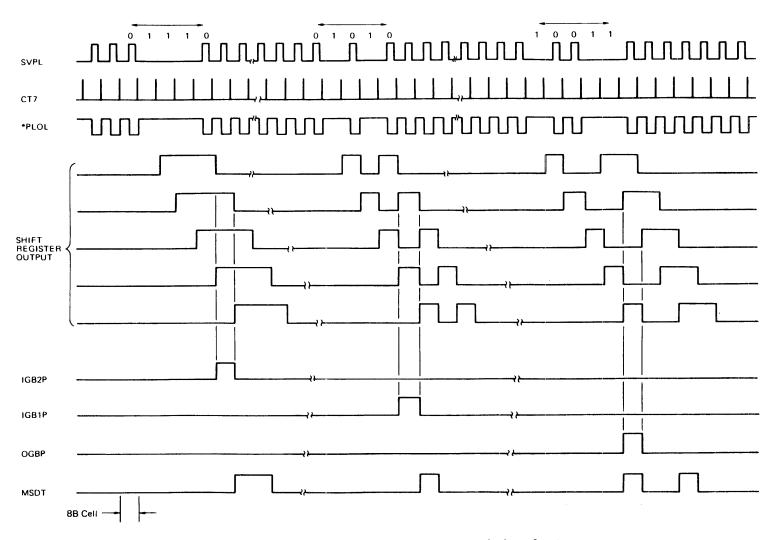

| 4.63 | Guard Band pulse detect timing chart           | 4-105 |

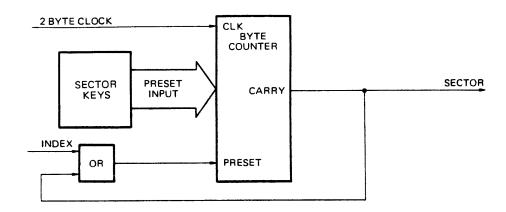

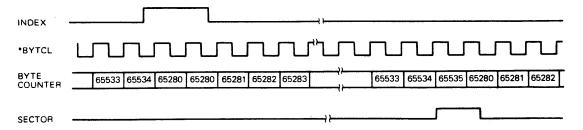

| 4.64 | Sector generator block diagram                 | 4-106 |

| 4.65 | Sector generator timing chart                  | 4-106 |

| 4.66 | Head selection block diagram                   | 4-108 |

| 4.67 | Data write                                     | 4-109 |

| 4.68 | Data read                                      | 4-110 |

| 4.69 | 1-7 coding                                     | 4-110 |

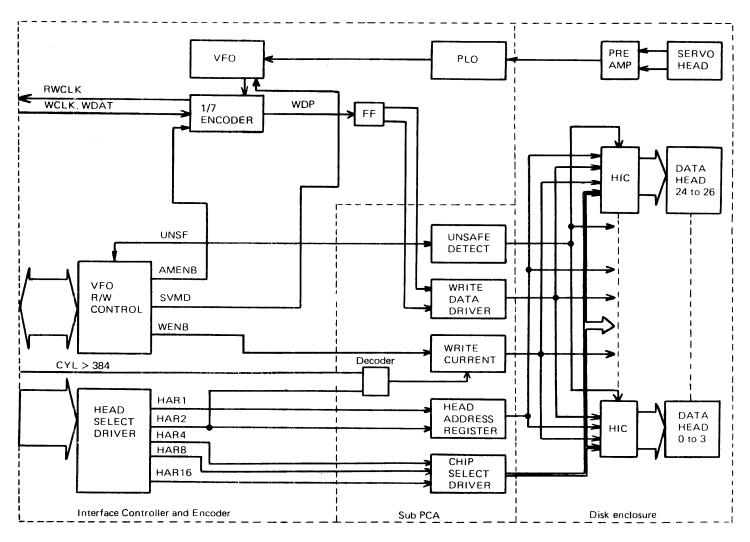

| 4.70 | Write operations block diagram                 | 4-112 |

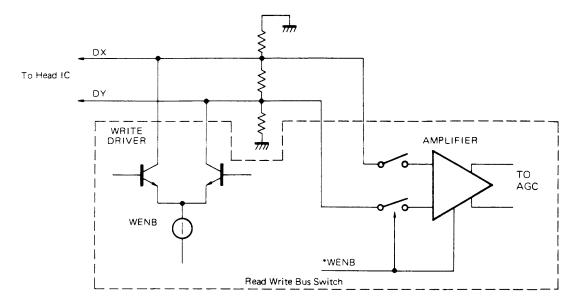

| 4.71 | Read write bus switch                          | 4-113 |

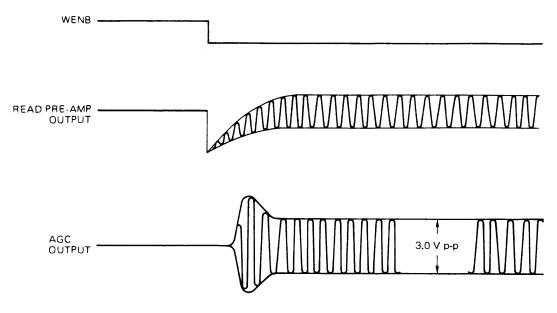

| 4.72 | AGC squelch function                           | 4-114 |

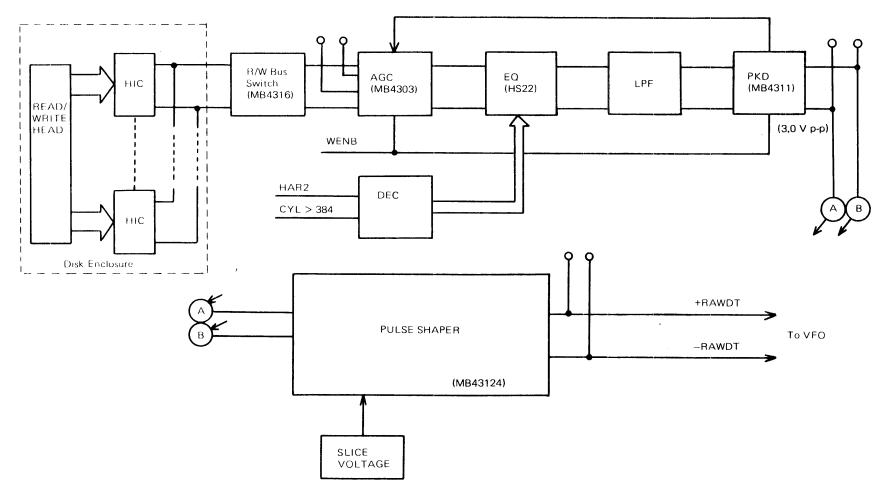

| 4.73 | Read operation block diagram                   | 4-115 |

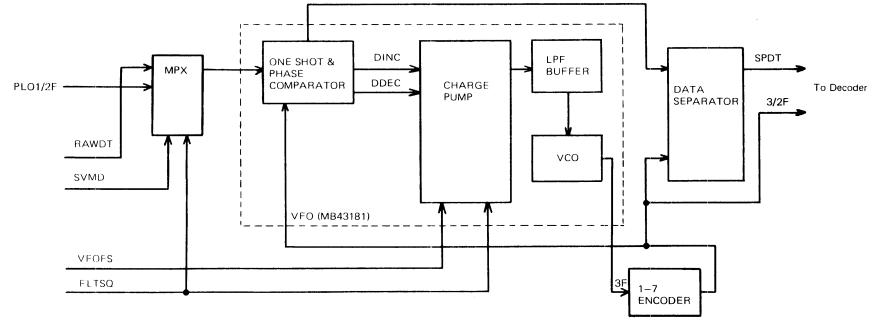

| 4.74 | VFO block diagram                              | 4-117 |

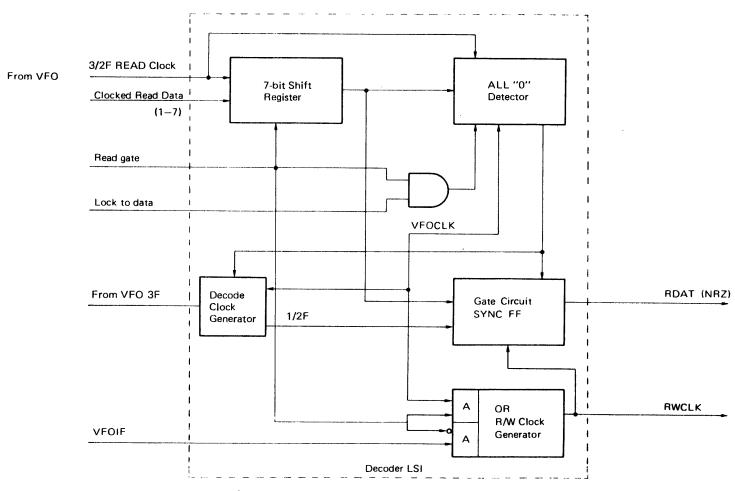

| 4.75 | 1-7 decoder block diagram                      | 4-120 |

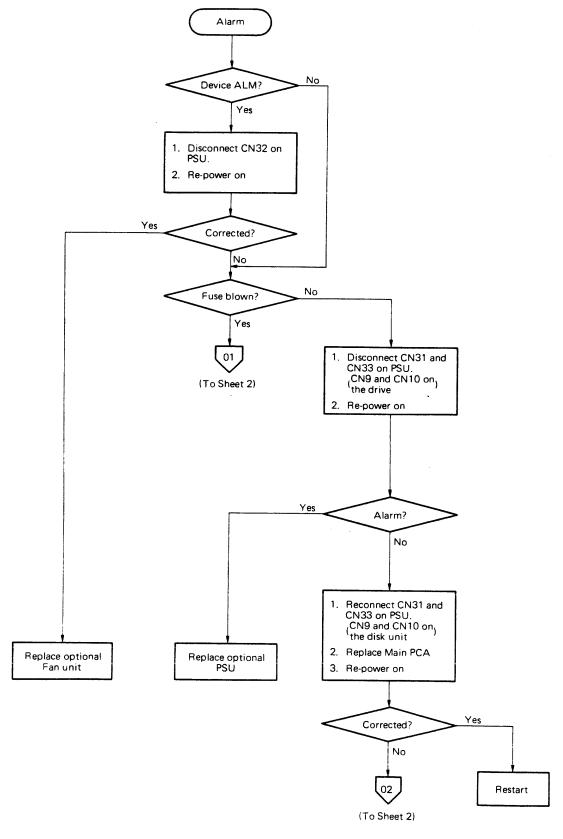

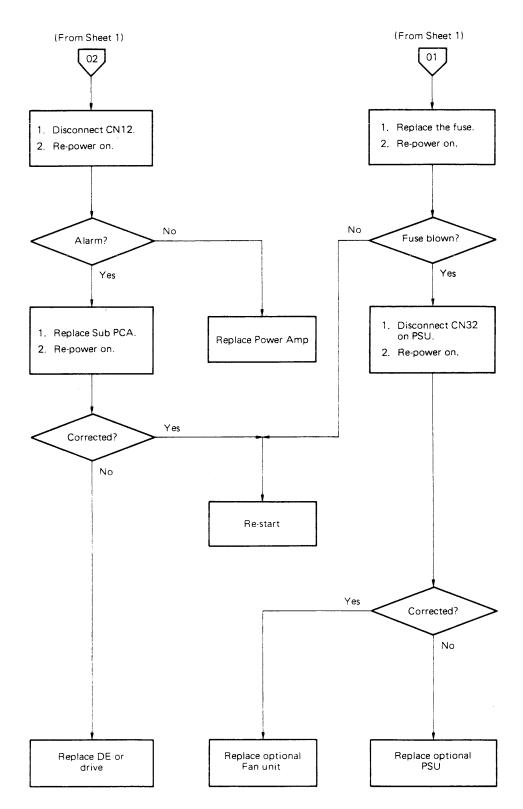

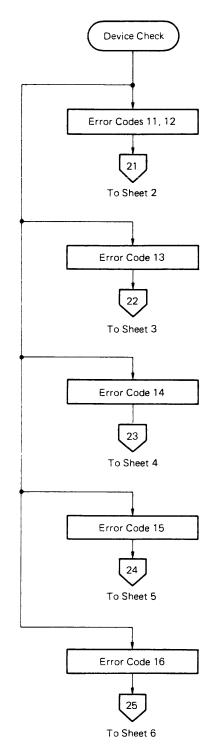

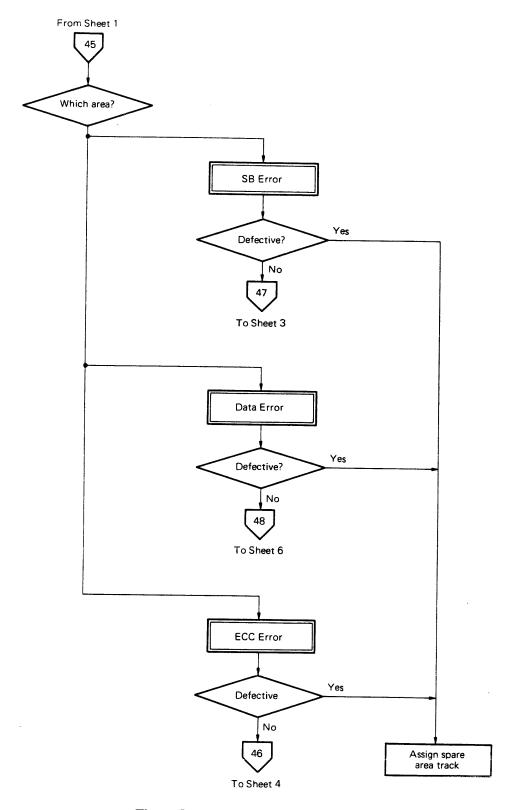

| 5.1  | Alarm flowchart                                | 5-10  |

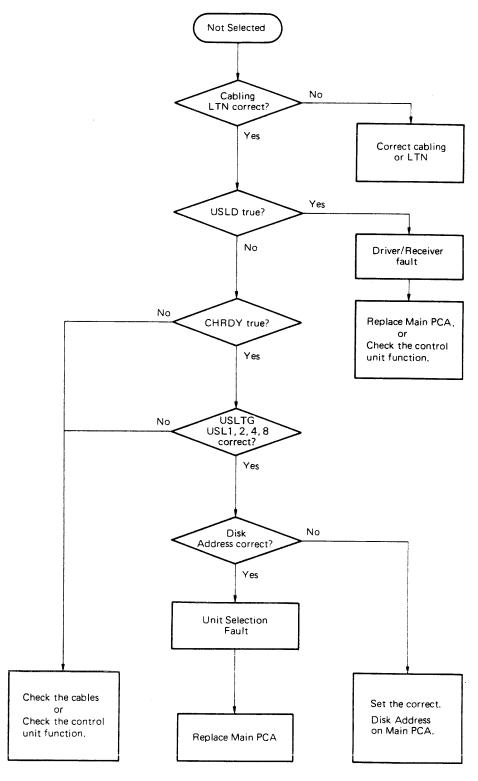

| 5.2  | Not Selected flowchart                         | 5-12  |

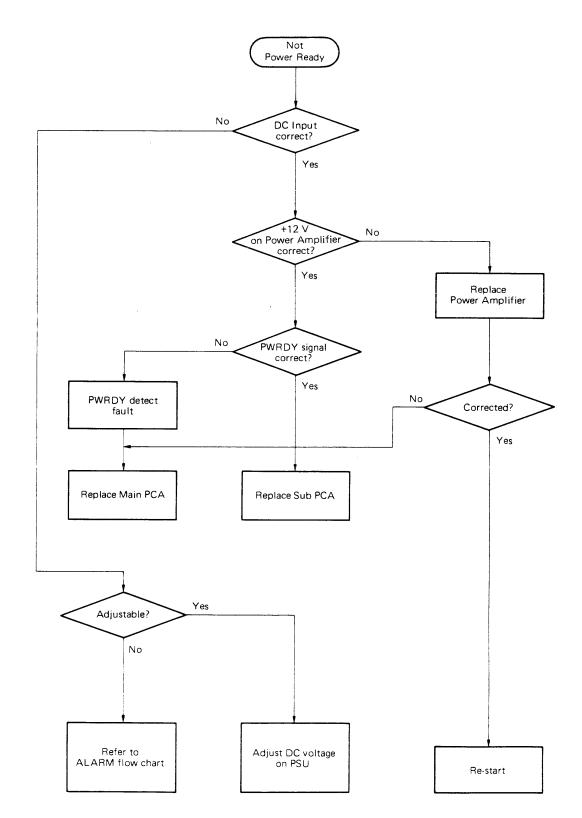

| 5.3  | Not Power Ready flowchart                      | 5-13  |

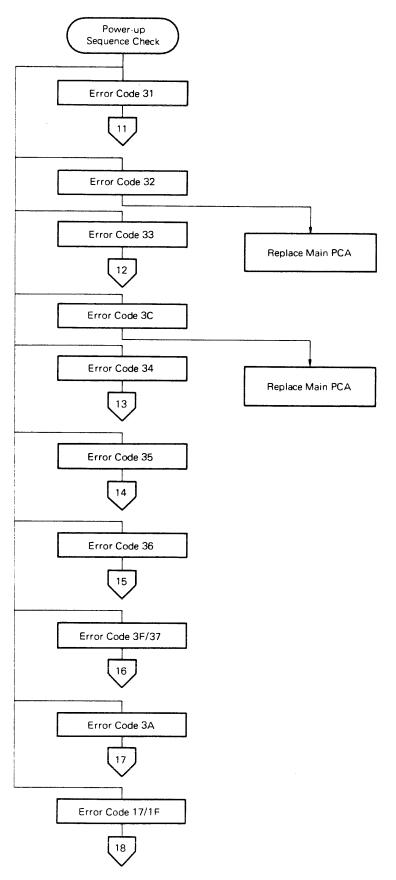

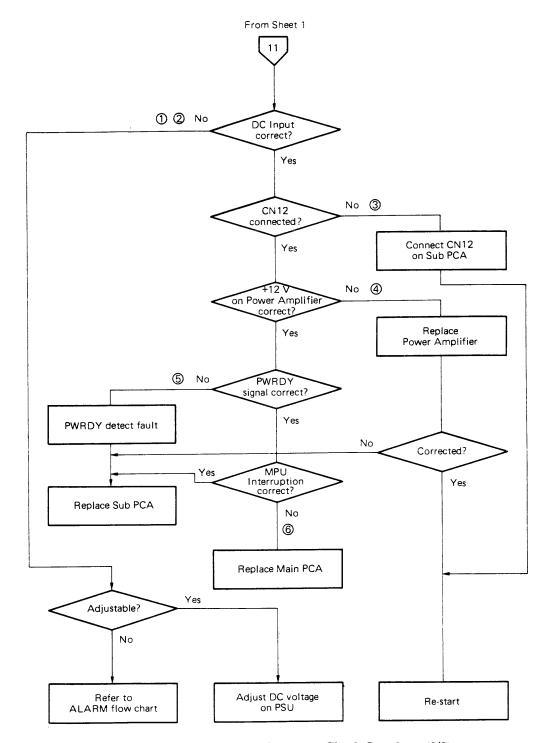

| 5.4  | Power-up Sequence Check flowchart              | 5-14  |

| 5.5  | Device Check flowchart                         | 5-23  |

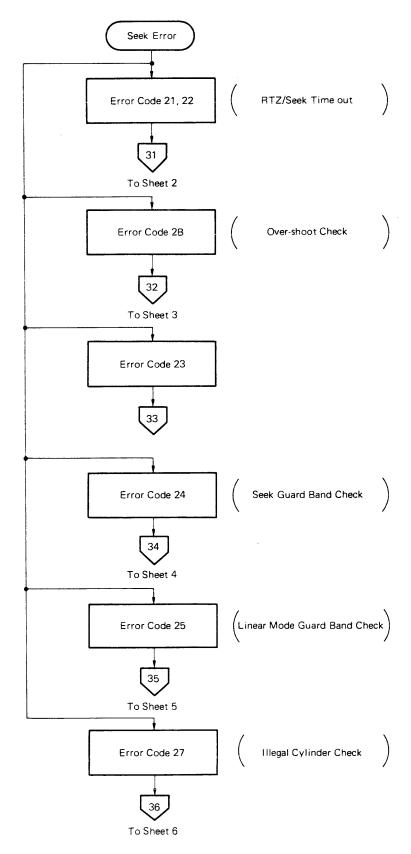

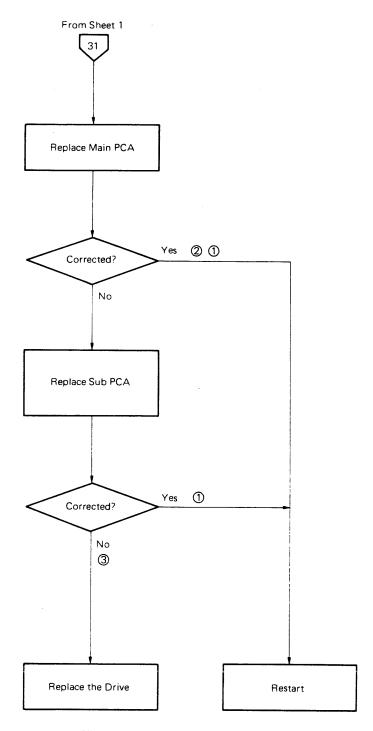

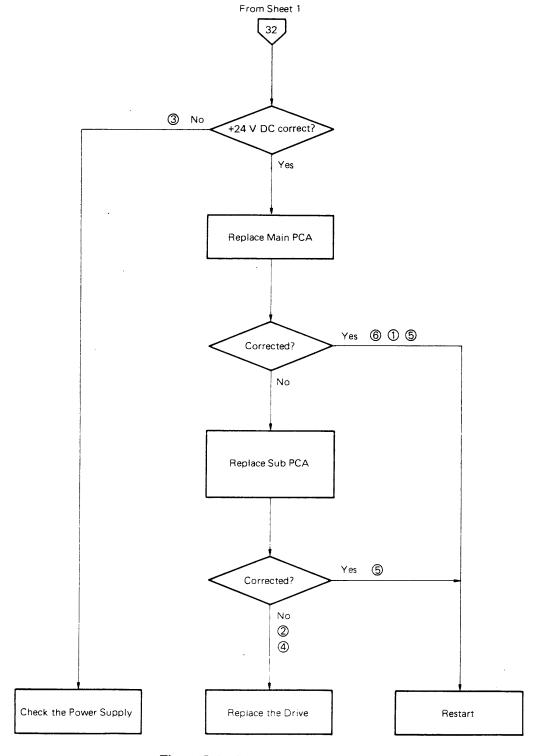

| 5.6  | Seek Error flowchart                           | 5-29  |

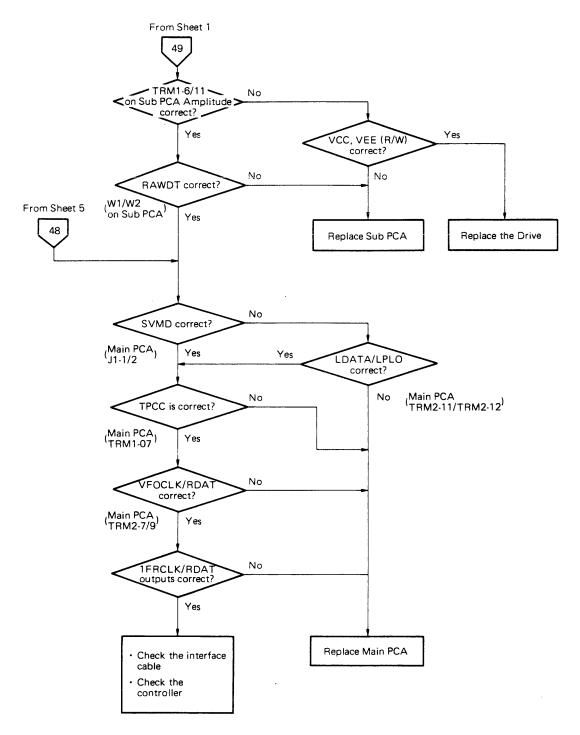

| 5.7  | Read Error flowchart                           | 5-36  |

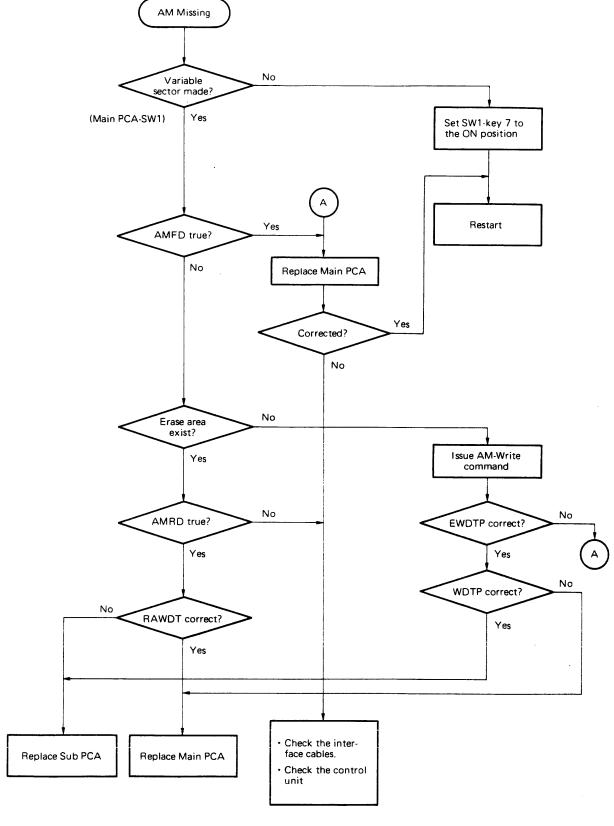

| 5.8  | AM Missing flowchart                           | 5-42  |

| 6.1  | PCA arrangement                                | 6-2   |

| 6.2  | Main PCA replacement              | 6-3  |

|------|-----------------------------------|------|

| 6.3  | Sub PCA replacement               | 6-4  |

| 6.4  | Through connector PCA connection  | 6-5  |

| 6.5  | Power Amplifier PCA replacement   | 6-6  |

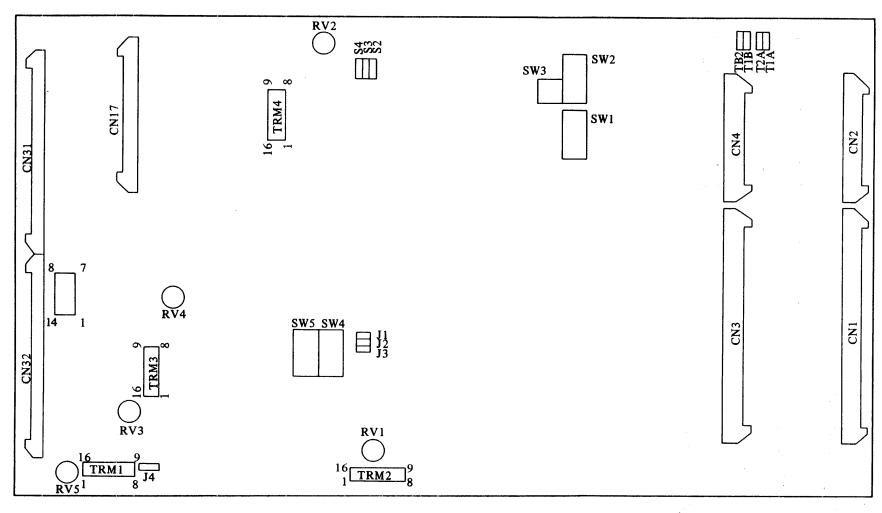

| 6.6  | Main PCA test points arrangement  | 6-8  |

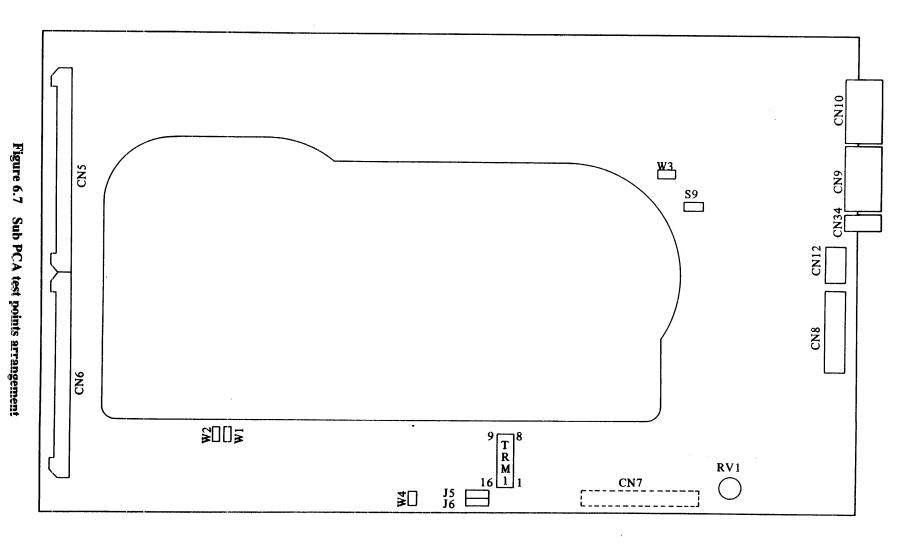

| 6.7  | Sub PCA test points arrangement   | 6-12 |

| 6.8  | Read output measurement           | 6-15 |

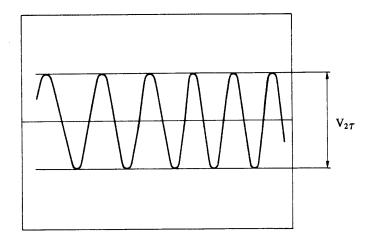

| 6.9  | PLO Free-run frequency adjustment | 6-17 |

| 6.10 | Data separator phase adjustment   | 6-18 |

# **TABLES**

|     |                                       | Page  |

|-----|---------------------------------------|-------|

| 1.1 | Functional specifications             | 1-3   |

| 1.2 | Physical specifications               | 1-4   |

| 1.3 | DC power requirements                 | 1-5   |

| 1.4 | Options                               | 1-15  |

| 2.1 | Thermal check point                   | 2-7   |

| 2.2 | Disk addressing                       | 2-28  |

| 2.3 | Tag 4/5 enable                        | 2-29  |

| 2.4 | File protect                          | 2-29  |

| 2.5 | Device type                           | 2-30  |

| 2.6 | Sector mode                           | 2-30  |

| 2.7 | Sector counting keys                  | 2-31  |

| 2.8 | Sector selection                      | 2-33  |

| 2.9 | Spindle start delay setting           | 2-36  |

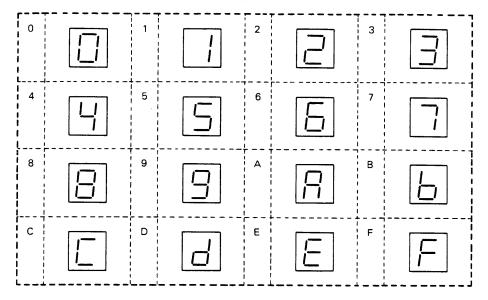

| 3.1 | Display characters                    | 3-4   |

| 3.2 | Function modes                        | 3-6   |

| 3.3 | Seek test modes                       | 3-8   |

| 3.4 | Code table                            | 3-15  |

| 3.5 | Status LED                            | 3-17  |

| 4.1 | Index, OGB2, OGB1, and IGB Patterns   | 4-9   |

| 4.2 | Tag/Bus lines                         | 4-14  |

| 4.3 | Status lines determined by Tag 4/5    | 4-18  |

| 4.4 | Fault/Seek error status               | 4-21  |

| 4.5 | Device type                           | 4-22  |

| 4.6 | A-cable pin assignment                | 4-45  |

| 4.7 | B-cable pin assignment (26 pos.)      | 4-46  |

| 4.8 | Seek malfunctions                     | 4-74  |

| 4.9 | Translation between NRZ and 1-7 codes | 4-111 |

| 5.1 | Error status                          | 5-2   |

| 5.2 | Fault indicator definition            | 5-3   |

| 5.3 | Fault isolation list                  | 5-5   |

| 5.4 | Symbol of flowchart                   | 5-9   |

| 0.1 | Maintenance tools and equipments | 6-1  |

|-----|----------------------------------|------|

| 6.2 | Main PCA check terminals         | 6-9  |

| 6.3 | Main PCA potentiometer functions | 6-11 |

| 6.4 | Main PCA switch functions        | 6-11 |

| 6.5 | Sub PCA check terminals          | 6-13 |

| 6.6 | Sub PCA potentiometer function   | 6-13 |

| 6.7 | Selection after PCA replacement  | 6-14 |

| 7.1 | Spare parts list                 | 7-1  |

#### CHAPTER 1 GENERAL

#### 1.1 General Description

#### 1.1.1 Introduction

This manual describes Fujitsu 8-inch rigid disk drive models, M2382K. The drive contains non-removable disks in a sealed module. A rotary actuator using a closed loop servo performs head positioning.

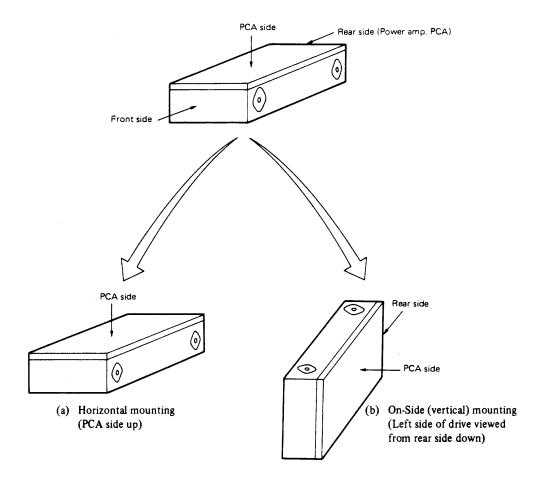

The drives can be mounted horizontally two drives wide in a 19-inch rack (with 3 pitch) or mounted vertically in a system cabinet.

The drive uses conventional Winchester contact start/stop (CSS) type heads and oxide media. Features of this technology are high performance, high reliability and low price.

The maximum unformatted storage capacities of the M2382K drive is 1000.2 MB.

The drive utilizes a modified high speed version of the industry standard SMD interface, referred to as ESMD, 3.0 MB/s transfer rate and originally equipped with cross-call function within the drive.

Development time for controllers and software will be substantially reduced for systems standardizing on the ESMD interface. Sector size is user selectable from 1 to 128 sectors per track.

Only DC voltages of +24 V, +5 V, -5.2 V and -12 V are required, providing international versatility. Total power consumption is approximately 120 W including cross-call function.

#### 1.1.2 Features

#### (1) High reliability

- (a) Well proven Winchester-type technology contact-start/stop (CSS) heads and media are used. The heads are returned to landing zone during spindle start and stop functions.

- (b) Each head arm has an LSI circuit to amplify the small signal read from the disk, thereby reducing read errors by increasing the signal to noise ratio.

- (c) The heads, media and positioning mechanism are provided with a closed-loop air filtration system in a sealed disk enclosure (DE).

- (d) The electrical components located in the DE are minimized to provide increased reliability and repairability.

#### (2) Maintenance free

No scheduled maintenance is required.

The use of a built-in DC spindle motor (no belt), completely sealed DE, plus highly reliable PCAs eliminate the necessity for scheduled maintenance.

Additionally, no adjustment is required after exchanging PCAs. A "calibration seek" operation is required after PCA exchange. To facilitate maintenance, an optional "Diagnostic Panel Unit" is available, providing the functions of seek exerciser, unit status monitor and seek error logging.

#### (3) Compact

This drive can be mounted two drives wide in a standard 19-inch rack. The weight of the drive is approximately 39 pounds (17.7 kg).

#### (4) Versatile mounting

These drives may be mounted horizontally, or vertically (On-side).

#### (5) Quiet

Low acoustical noise level and low vibration make these drives attractive for an office environment.

#### (6) Universal

Since this drive requires only DC voltages, only one model is required for domestic and foreign applications.

## 1.2 Specification

# 1.2.1 Functional specifications

Table 1.1 Functional specifications

| Model                                           | M2382K                                                  |

|-------------------------------------------------|---------------------------------------------------------|

| Item                                            | W12302K                                                 |

| Storage Capacity (Unformatted)                  | 1000.2 MB                                               |

| Number of Cylinders                             | 745                                                     |

| Tracks of Cylinder                              | 27                                                      |

| Cylinder Capacity                               | 1,342,656 bytes                                         |

| Track Capacity                                  | 49,728 bytes                                            |

| Number of Sectors                               | 1 to 128                                                |

| Average Rotational Latency                      | 8.3 ms                                                  |

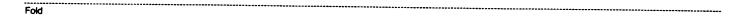

| Positioning Time Track to Track Average Maximum | 4 ms<br>16 ms<br>33 ms                                  |

| Rotational speed                                | $3,620 \text{ rpm } \pm 1 \%$                           |

| Transfer Rate                                   | 3.0 MB/s                                                |

| Encoding method                                 | RLL (1/7)                                               |

| Interface Data                                  | NRZ                                                     |

| Recording Density                               | 25,211 BPI                                              |

| Track Density<br>(Inner zone/Outer zone)        | 1,046/1,193 TPI                                         |

| Start/Stop time                                 | < 50 / < 50  sec.                                       |

| Interface                                       | SMD (modified)                                          |

| Dimension<br>Width×height×depth                 | 8.5 in. (216 mm)×5.0 in. (127 mm)<br>×15.0 in. (380 mm) |

| Weight                                          | Approx. 39 lbs. (17.7 kg)                               |

| Mounting axis                                   | Horizontal or vertical                                  |

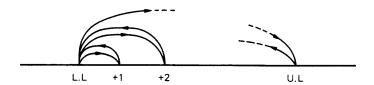

Figure 1.1 Positioning time profile

## 1.2.2 Physical specifications

**Table 1.2 Physical specifications**

| Operating             |                                                                                     |

|-----------------------|-------------------------------------------------------------------------------------|

| Temperature           | 41°F to 104°F (5°C to 40°C)                                                         |

| Relative Humidity     | 20 % to 80 % (no condensation)                                                      |

| Temperature Variation | <27°F/hr (15°C/hr) (no condensation)                                                |

| Altitute              | 10,000 feet (3,000 m)                                                               |

| Vibration             | 0.2G sinvsoidal max. 3 Hz to 60 Hz to 3 Hz Sweep, 2 minutes/sweep, 30 sweeps        |

| Shock                 | 2.0G, 10 ms, half-sine pulse                                                        |

| Non-operating         |                                                                                     |

| Temperature           | -40°F to 140°F (-40°C to 60°C)                                                      |

| Relative Humidity     | 5 % to 95 % (no condensation)                                                       |

| Altitute              | 40,000 feet (12,000 m)                                                              |

| Vibration             | 0.4G sinusoidal max.<br>3 Hz to 60 Hz to 3 Hz<br>Sweep, 2 minutes/sweep, 30 sweeps. |

| Shock                 | 15G, 10 ms—in storage or during transportation                                      |

#### 1.2.3 DC power requirements

This drive requires +5 V, -5.2 V, -12 V and +24 V DC voltage from the optional power supply or system power supply. Each load current required by the drive is shown in Table 1.3.

Table 1.3 DC power requirements

| DC Voltage  | Load Current (Basic)                                                                    |

|-------------|-----------------------------------------------------------------------------------------|

| +5 V ±5 %   | 3.5 A                                                                                   |

| -12 V ±5 %  | 1.5 A                                                                                   |

| -5.2 V ±5 % | 3.5 A                                                                                   |

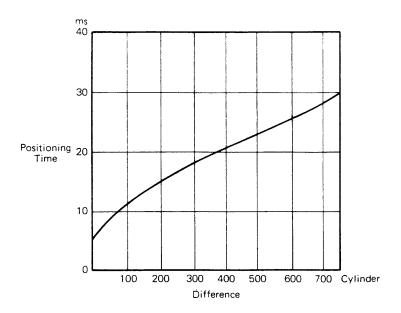

| +24 V ±10 % | 4.5 Arms (Effective, typical) 9.0 Ao-p (Maximum) 5.5 Arms (POWER ON; Effective typical) |

The load currents of +5 V, -5.2 V and -12 V DC will be stable regardless of operation performed within the drive, however, the load current of +24 V DC will be varied through a power up sequence, DC motor acceleration and/or seek operation.

DC voltages must be maintained within their tolerance during operation.

#### Note:

All DC return lines must be made electrically common at the power supply when using a power supply other than the unit supplied by Fujitsu. Failure to commonize the returns will result in premature failure of the motor circuit.

The +24 V DC load current profile during power up sequence is shown in Figure 1.2.

#### Note:

Start up timing is delayed according to the setting of SW5 on the main PCA. See Subsection 4.4.1 for details.

Figure 1.2 +24 V DC load current on power up sequence

The +24 V DC load current profile during the repeated acceleration/inertia modes of DC motor and/or seek operation after Ready status is shown in Figure 1.3.

Figure 1.3 Total +24 V DC load current (Ready)

#### 1.2.4 High frequency noise specification

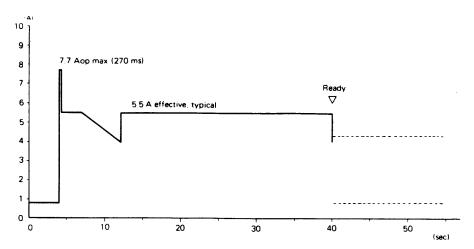

When DC power is supplied to the drive from a customer power supply with switching type regulation, the high frequency noise caused by switching regulator should be specified as follows.

#### (1) High frequency noise definition

It is defined that the high frequency noise is caused by a switching transient on basic voltage within the switching type regulator on the power supply unit as shown in Figure 1.4.

Note:

A noise is defined as the higher spike,  $V_{1p-p}$  and  $V_{2p-p}$

Figure 1.4 High frequency noise

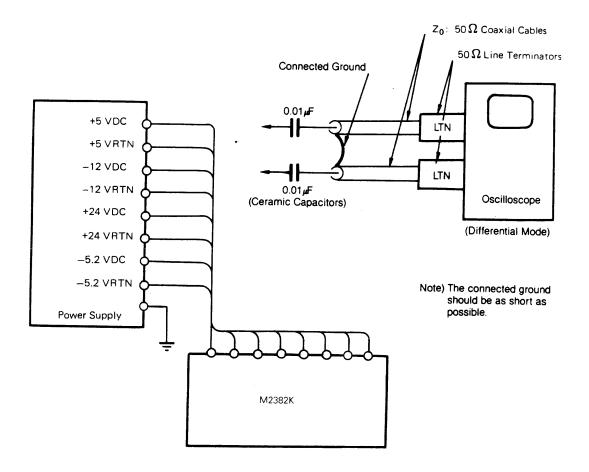

#### (2) Measurement procedure

A noise level should be measured on terminals of the power supply as shown in Figure 1.5.

Figure 1.5 Measurement procedure

#### (3) Noise specification

a. Noise between each DC output and return terminals.

$V_{N1}$ : 0.1  $V_{p-p}$  max.

b. Noise between each terminal (DC output and return) and Frame Ground (FG).

$V_{N2}$ : 1.0 V max.

c. This specification is not applied on an external line noise definition.

#### 1.2.5 Reliability

#### (1) MTBF

The MTBF is defined as follows:

The MTBF shall exceed 35,000 hours when estimated by drives each having statistically significant operating hours (more than 6,000 hours). Operating hours means total power-on hours without any maintenance time. Equipment Failures are defined as any stoppage or substandard performance of the equipment which necessitates repairs, replacements or re-adjustments on an unscheduled basis, excluding those caused by operator error, cable failure or other malfunction not caused by the equipment.

#### (2) MTTR

MTTR is the average time a well-trained service mechanic should take to diagnose and repair the trouble. This drive is designed for an MTTR of 30 minutes or less.

#### (3) Preventive maintenance time

No scheduled maintenance is required.

#### (4) Service life

This drive is designed to provide a useful life of at least five (5) years before factory refurbishment is required.

#### (5) Data security

Data integrity is assured in the event of a power failure except on sectors when a write operation was being performed.

#### 1.2.6 Error rate

The following error rates assume that this drive is being operated within specification. Errors caused by known media defects or equipment failures are excluded.

#### (1) Read errors

Prior to determination of a read error rate, the data shall have been verified as written correctly and all media defects flagged.

#### (a) Recoverable error rate

A recoverable read error is one which can be read correctly within sixteen retries when reading on track, and should not exceed ten per 10<sup>11</sup> bits transferred.

#### (b) Unrecoverable error rate

An unrecoverable read error is one which cannot be read correctly within sixteen retries and should not exceed ten per  $10^{14}$  bits transferred.

#### (2) Positioning error rate

The positioning error which can be corrected within one retry should not exceed ten per  $10^8$  seeks.

#### 1.2.7 Media defects

A media defect is defined as a repeative read error that occurs on a properly adjusted drive within specific operating conditions.

#### (1) Media defect characteristics

#### (a) The maximum number of defects:

M2382K 1000.1 MB: 1000

(b) The maximum number of defective tracks per drive is as follows:

M2382K 1000.2 MB: 65

A defective track is defined as a track having any of following:

- (1) Two to four defects

- 2 Defective logging area

#### Note:

No track shall have more than four defects.

- (2) Media defect free areas are defined as follows:

- 1) Cylinder 0, Head 0 through 2

- 2 Any error in logging area to extent defined in the Media Defect List

- (3) Media defect information

The drive will have a media defect list which will list the following information.

- (1) Cylinder Address

- (2) Head Address

- (3) Position (bytes from Index  $\pm 1$  byte)

- (4) Length (bits ±1 bit)

The above information will be listed by hexadecimal code. The maximum media defect length at a defect is 64 bytes (512 bits).

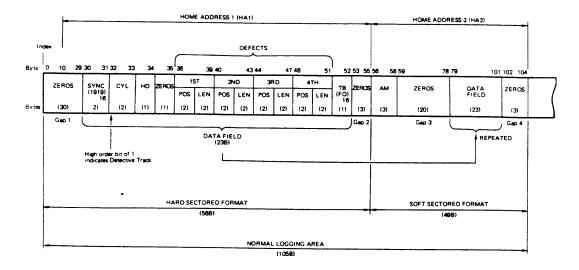

#### (4) Media defect format

The drive will be formatted at the factory with a standard Media Defect Format. The format is a hard-sectored format and is included in the first 56 bytes following Index signal, as shown in Figure 1.6 Format 1. The format rules are as follows:

- ① A track which has more than one defect is defined and flagged as a defective track. The first four media defects are logged.

- 2 If the beginning of a defect is located between Byte 10 to Byte 55 (HA1) after Index, 60 bytes of zeros are added to gap 1 (90 bytes total). In this case, if any part of a defect is located between Byte 60 and Byte 115 (HA1), the track is flagged as defective. Refer to Figure 1.7 Format 2.

- ③ If the track is defined as a defective track according to above-mentioned Rules ① or ②, the high order bit of the first cylinder address byte is set to 1. Remaining information may or may not be valid.

#### **Notes:**

- 1. Position (POS) of defect is in bytes after Index  $\pm 1$  byte.

- 2. Length (LEN) of defect is in bits  $\pm 1$  bit.

- 3. Unused defect locations are all zeros.

Figure 1.6 Media defect format 1

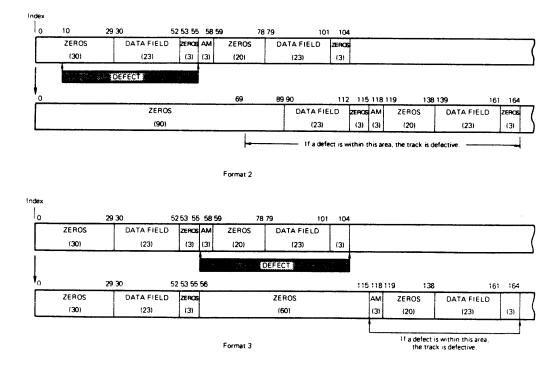

Figure 1.7 Skip displaced format 2 and 3

#### 1.3 Configuration

#### 1.3.1 Fundamental configuration

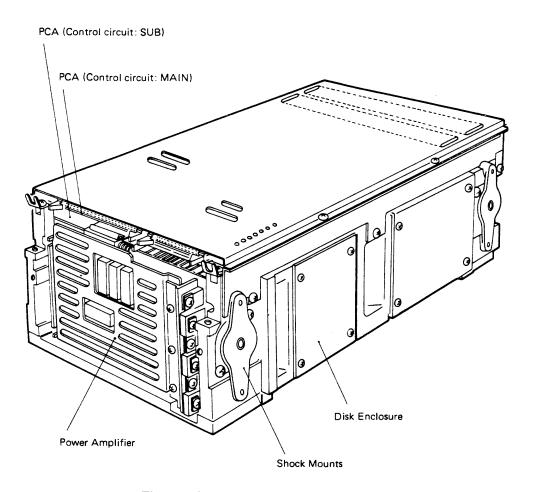

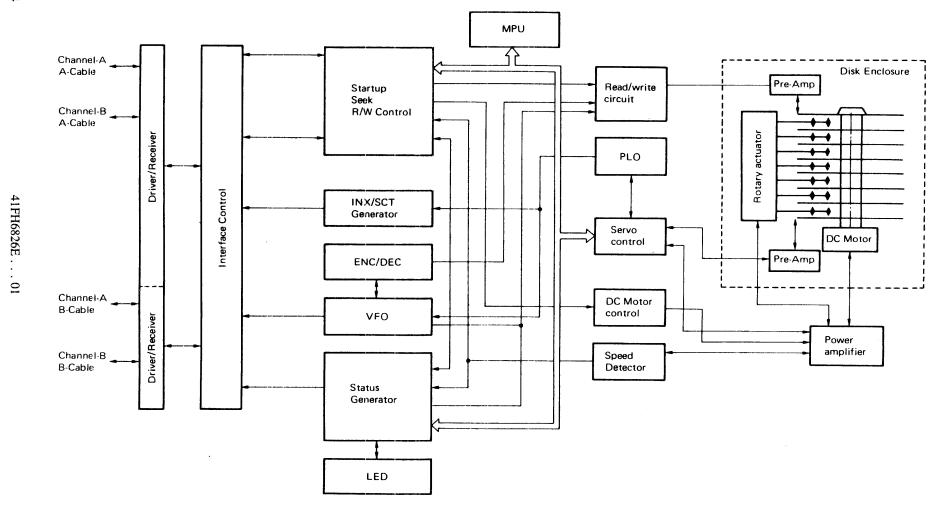

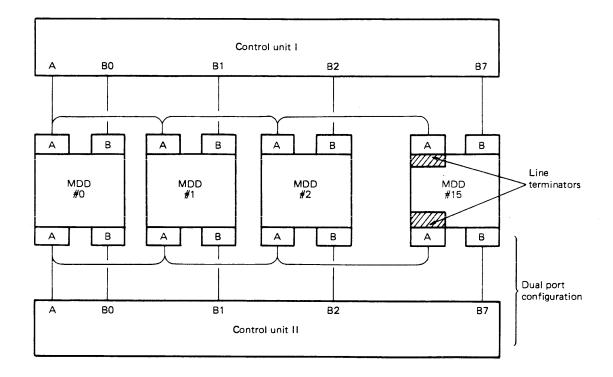

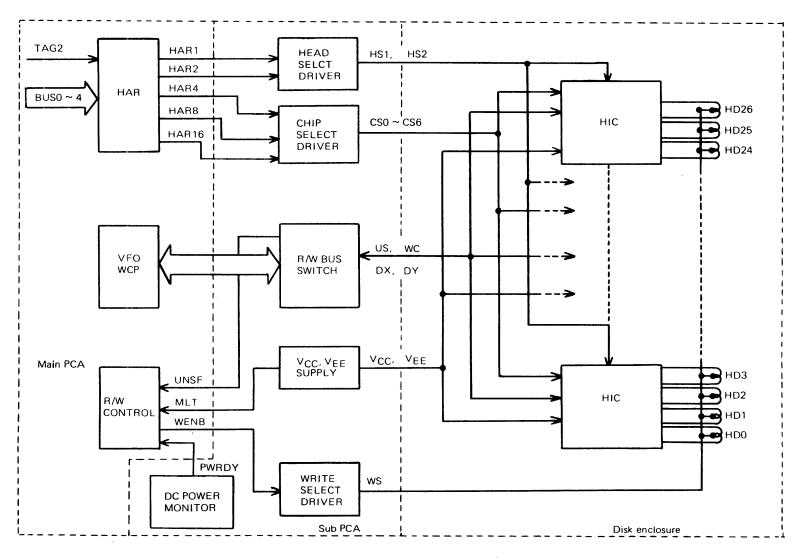

Figure 1.8 shows the fundamental configuration of the drive; Figure 1.9 shows the block diagram.

Figure 1.8 Fundamental configuration

Figure 1.9 Block diagram

# 1.3.2 Options

**Table 1.4 Options (1/2)**

| Item No. | Component name       | Specification<br>(Part Number) | Remarks                                                                                                                                                     |

|----------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

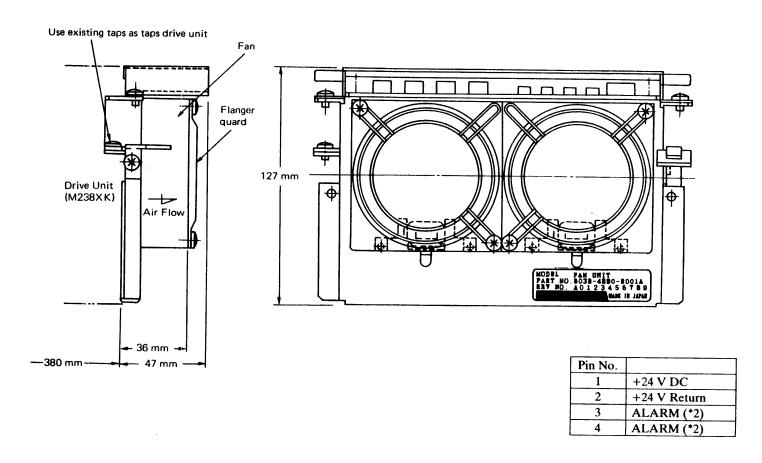

| 1-1      | Fan unit             | B03B-4880-E011A                | +24 V DC, 0.5 A 127 mm (H) standard                                                                                                                         |

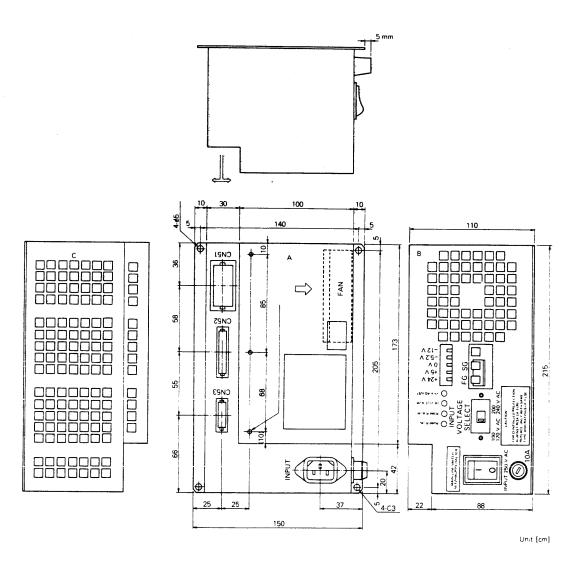

| 2-1      | Power supply unit    | B14L-5105-0244A                | <ul> <li>for 1 drive</li> <li>100/115/120/200/220/240 VAC</li> <li>With connectors for feeding power to fan units and dual channel option</li> </ul>        |

| 2-2      | Power supply unit    | B14L-5105-0247A<br>#A1         | <ul> <li>for 2 drives</li> <li>100/115/120/1200/220/240 VAC</li> <li>With connectors for feeding power to fan units and dual dual channel option</li> </ul> |

| 3-1      | Cable (Non-shielded) | B660-1065-T006A                | Interface cable (A) 60P flat cable                                                                                                                          |

| 3-2      | Cable (Non-shielded) | B660-1065-T008A                | Interface cable (B)<br>26P flat cable                                                                                                                       |

| 3-3      | Cable (Non-shielded) | B660-1865-T020A                | Interface cable (A) for 2 drives daisy chain                                                                                                                |

| 3-4      | Cable (Non-shielded) | B660-1865-T030A                | Interface cable (A) for 3 drives daisy chain                                                                                                                |

| 3-5      | Cable (Non-shielded) | B660-1865-T040A                | Interface cable (A) for 4 drives daisy chain                                                                                                                |

| 3-6      | Cable (Non-shielded) | B660-1865-T050A                | Interface cable (A) for 5 drives daisy chain                                                                                                                |

| 3-7      | Cable (Non-shielded) | B660-1865-T060A                | Interface cable (A) for 6 drives daisy chain                                                                                                                |

| 3-8      | Cable (Non-shielded) | B660-1865-T070A                | Interface cable (A) for 7 drives daisy chain                                                                                                                |

| 3-9      | Cable (Non-shielded) | B660-1865-T080A                | Interface cable (A) for 8 drives daisy chain                                                                                                                |

| 3-10     | Cable (Shielded)     | B660-0620-T438A                | interface cable (A)<br>60P flat cable                                                                                                                       |

| 3-11     | Cable (Shielded)     | B660-0620-T436A                | Interface cable (B) 26P flat cable                                                                                                                          |

| 3-12     | Cable (Shielded)     | B660-0620-T439A                | Interface cable (A) for 2 drives daisy chain                                                                                                                |

| 3-13     | Cable (Shielded)     | B660-0620-T440A                | Interface cable (A) for 3 drives daisy chain                                                                                                                |

**Table 1.4 Options (2/2)**

| Item No. | Component name                        | Specification<br>(Part Number) | Remarks                                                                         |

|----------|---------------------------------------|--------------------------------|---------------------------------------------------------------------------------|

| 3-14     | Cable (Shielded)                      | B660-0620-T441A                | Interface cable (A) for 4 drives daisy chain                                    |

| 3-15     | Cable (Shielded)                      | B660-0620-T442A                | Interface cable (A) for 5 drives daisy chain                                    |

| 3-16     | Cable (Shielded)                      | B660-0620-T443A                | Interface cable (A) for 6 drives daisy chain                                    |

| 3-17     | Cable (Shielded)                      | B660-0620-T444A                | Interface cable (A) for 7 drives daisy chain                                    |

| 3-18     | Cable (Shielded)                      | B660-0620-T445A                | Interface cable (A) for 8 drives daisy chain                                    |

| 3-19     | Cables<br>(Shielded/<br>non-Shielded) | T.B.D.                         | Interface cables for "B" channel                                                |

| 4-1      | Panel unit                            | B03B-4880-E501A                | Flat key type control panel board                                               |

| 4-2      | Diagnostic panel                      | B03B-4880-E550A                | Maintenance panel  Seek exerciser/bus status monitor/error logging monitor      |

| 5-1      | Mounting tray                         | B21L-1810-0001A                | For mounting two drive in 19-inch rack with 3 pitches (tray and slide guide)    |

| 5-2      | Mounting tray                         | B21L-1810-0002A                | For mounting two drives in 19-inch rack with 3 pitches with optional panel unit |

| 7-1      | Power cable<br>(Non-Shielded)         | B660-0625-T453A                | Drive-optional power supply                                                     |

| 7-2      | Power cable (Non-shielded)            | B660-0625-T454A                | Drive and DC (+24) fan unit<br>-optional power supply                           |

| 7-3      | Power cable<br>(Shielded)             | B660-0620-T455A                | Drive-optional power supply                                                     |

| 7-4      | (Power cable)<br>(Shielded)           | B660-0620-T456A                | Drive and DC fan unit -optional power supply                                    |

| 8-1      | Cable                                 | B660-1995-T003A                | Optional panel unit (B03B-4880-<br>E501A)-drive.                                |

| 8-2      | Cable                                 | B660-2560-T004A                | Diagnostic panel option (B03B-4880-E550A)-drive                                 |

#### Note:

Items in the table above are optional and not fundamental components of this drive. These items must be ordered separately.

#### (1) Fan unit

This drive requires some means of cooling, since there is no internal blower motor. For this purpose, optional fan units are available in the event that adequate cooling is not provided within the mounting cabinet. This optional fan unit uses dual fans and mounts directly mountable onto the rear of the drive, and may be mounted in the field by using the existing taps and attached screws.

In the case of using fan unit with optional power supply, the power cable shall be designated as B660-0625-T454A, B660-0620-T456A.

Figure 1.10 shows the mounting of the fan unit.

Figure 1.10 Fan unit: B03B-4880-E011A

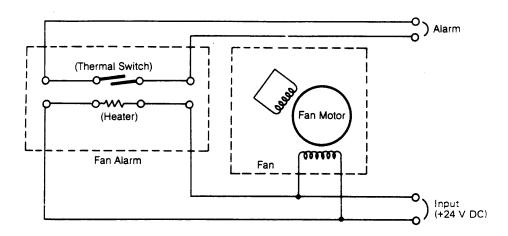

#### \*2: Fan alarm specification

Type of contact point : Normal open

Contact capacity : 0.5 A DC Max.

200 V DC Max. \*However:  $i(A) \times E(V) \le 10 \text{ W DC}$

Rated power (Heater): 4.2 W (+24 V DC)

Response time : 5 - 300 sec.

Circuit : as follows

Figure 1.11 Optional fan unit alarm

#### \*3: Fan unit connector part number

Connector : Amp 1-480702-0(UL94V-2) or 350779-1(UL94V-0)

Contact : Amp 350550-1

## (2) Power supply unit

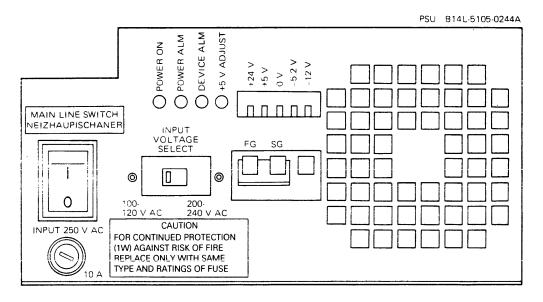

A power supply unit may either be mounted horizontally behind the drive or may be mounted vertically. Figures 1.12 and 1.13 show the details of I/O terminals and the external dimensions of the power supply units.

Figure 1.12 Power supply unit: B14L-5105-0244A

Figure 1.13 Power supply unit: B14L-5105-0247A#A1

# (3) 19-inch rack mount kit

A mounting tray and brackets are available to facilitate the installation of two drives, side by side in a 19-inch rack, in three pitche. The tray can also accommodate the optional fan unit and power supply unit(s) for each of the two drives.

Figure 1.14 19-inch rack mount installation

The mounting tray (inner frame) guided by brackets (outer frame) can be drawin out forward. (Travel distance is approximately 24 inches).

The 19-inch rack mounting method is illustrated in Figure 1.14. Figure 1.15 shows the drives mounted in the mounting tray and brackets.

## Note:

Mounting tray (0001A) cannot accommodate the optional panel unit; In that case, 0002A-type must be specified.

Figure 1.15 Mounting tray

#### (4) Cables

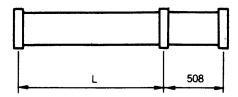

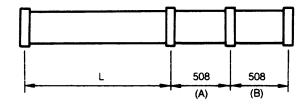

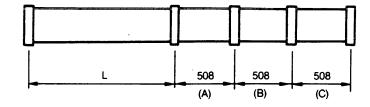

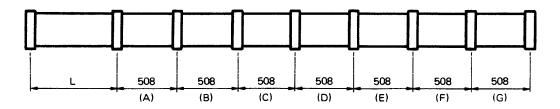

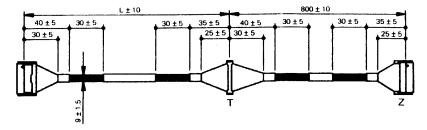

The interface cable (A) may be up to 30 m (1181 inches) long (to the drive at the final step in case of daisy-chain mode). The length of the cable can be specified in 508 mm (20 inches) increments.

The interface cable (B) may be up to 15 m long. The length of this cable can be specified in 500 mm increment.

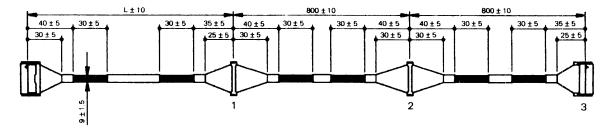

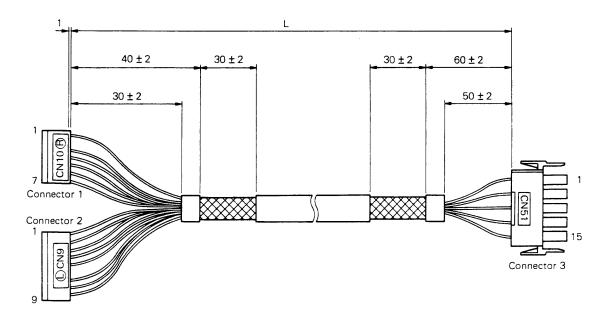

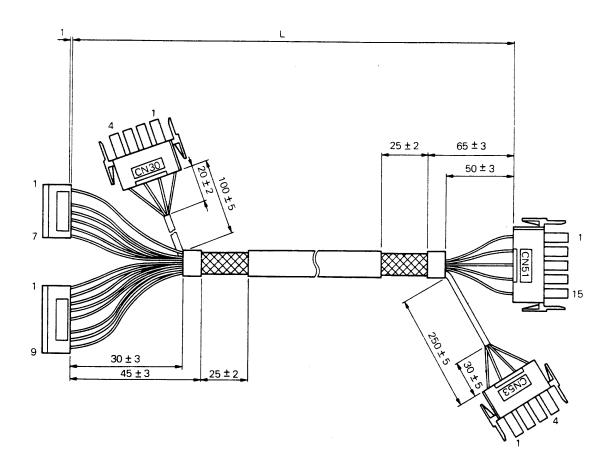

The (A) cables for daisy-chain connection shown at items 3-3 to 3-9 and 3-12 to 3-18 in Table 1-4 are as shown in Figures 1-16 and 1-17. Cable length "L" (specifiable by "#L") refers to the corresponding sections of the following drawings:

#### • For B660-1865-T020A

#### • For B660-1865-T030A

#### • For B660-1865-T040A

#### • For B660-1865-T080A

The connectors at both ends are of close-end, while the intermediate connectors are of through-end.

Figure 1.16 A-cables for daisy-chain (non-shield type)

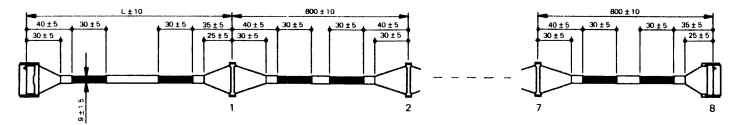

#### • For B660-0620-T439A

# • For B660-0620-T440A

# • For B660-0620-T445A

\* The connectors at both ends are of close-end, while the intermediate connectors are of through-end.

Figure 1.17 A-cables for daisy-chain (shield type)

How to specify cable lengths

(For 3.5 m: Example 1)

B660-1065-T008A

#L3R503

Cable specification

$$3.5 \times 10^3 \text{ (mm)}$$

(For 50 cm: Example 2)

B660-0625-T327A

#L500R0

Cable specification

$$500 \times 10^{0}$$

(mm)

The lengths of cables at Items 7, 8 and 9 in Table 1-4 must also be specified.

Figure 1.18 Power cable: B660-0625-T453A

Figure 1.19 Power cable: B660-0625-T454A

Figure 1.20 Power cable: B660-0620-T455A

Figure 1.21 Power cable: B660-0620-T456A

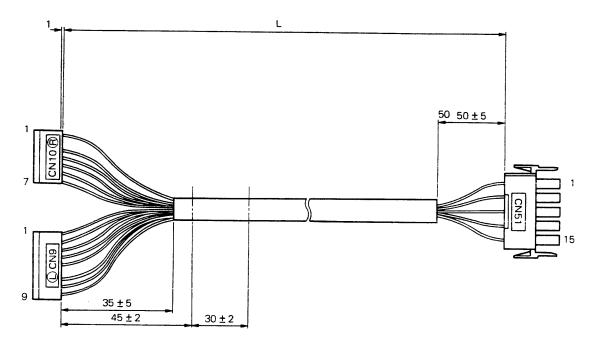

Figure 1.22 Cable: B660-1995-T003A (E501A Panel unit-Drive connecting)

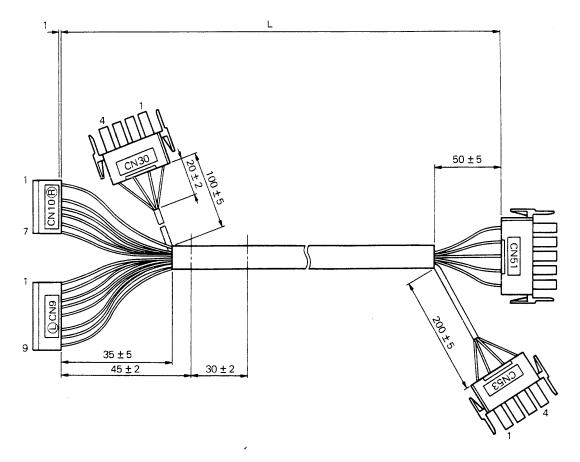

Figure 1.23 Signal Crossover Cable: B660-2560-T004A (Diagnostic panel-drive)

## Signal Crossover Cable Diagram

#### (a) Connector

#### A Cable connector (60 pos.)

Header specification FCN-702P060-AU/M (Wire wrapping)

FCN-704P060-AU/M (Straight) FCN-705P060-AU/M (Right Angle)

Socket specification FCN-707J060-AU/B (Closed End)

FCN-707J060-AU/O (Through End)

## B Cable connector (26 pos.)

Header specification FCN-703P026-AU/M (Wire wrapping)

FCN-704P026-AU/M (Straight) FCN-705P026-AU/M (Right Angle)

Socket specification FCN-707J026-AU/B (Closed End)

FCN-707J026-AU/O (Through End)

#### (b) Cable

#### A Cable

Specification 455-248-60 Spectra Strip

Zo= $100 \Omega \pm 10 \Omega$ 28 AWG, 7 strands

**B** Cable

Specification 174-26 Ansley/3476-26 3M

$Zo=100 \Omega \pm 10 \Omega/Zo=130 \Omega \pm 15 \Omega$

28 AWG, 7 strands

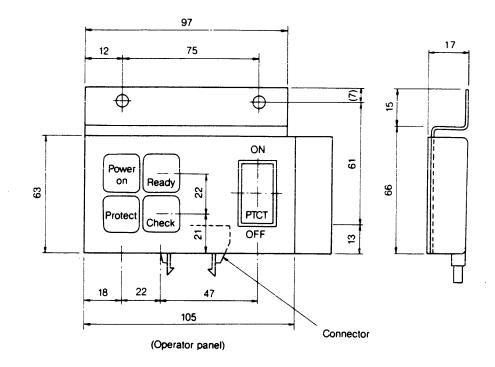

#### (5) Panel unit

The optional panel unit includes function lights which indicate power on, ready, write protect, check, and a write protect and check clear switches.

Figure 1.24 shows the mounting dimensions and mounting status of panel unit B03B-4880-E501A. This panel unit will mount directly on the drive.

Figure 1.24 Panel unit: B03B-4880-E501A

When the panel unit is used with the mounting tray (B21L-1810-0002A), this panel unit (B03B-4880-E501A) is mounted as shown in Figure 1.25.

Figure 1.25 Mounting panel unit

## Operator panel connection

The main control circuit PCA allows for connection of an optional control panel. At location B30 on this PCA, there is a 14 pin DIP socket for the control panel connection. Following is the pin-out for this DIP socket.

| PIN NUMBER | SIGNAL MNEMONIC | DEFINITION          |

|------------|-----------------|---------------------|

| 1          | +5 V            | +5 Volt             |

| 2          | *FPTK           | File Protect Switch |

| 3          | *CKCLR          | Check Clear Switch  |

| 4          | *LRDY           | Ready LED           |

| 5          | ov              | Signal Ground       |

| 6          | *LUSLD          | Unit Selected LED   |

| 7          | OV              | Signal Ground       |

| 8          | ov              | Signal Ground       |

| 9          | *PWRDY          | Power Ready LED     |

| 10         | *LFPT           | File Protect LED    |

| 11         | *LDVCK          | Device Check LED    |

| 12         | ov              | Signal Ground       |

| 13         | OV              | Signal Ground       |

| 14         | +5 V            | +5 Volt             |

<sup>&</sup>quot;\*" indicates a low active signal.

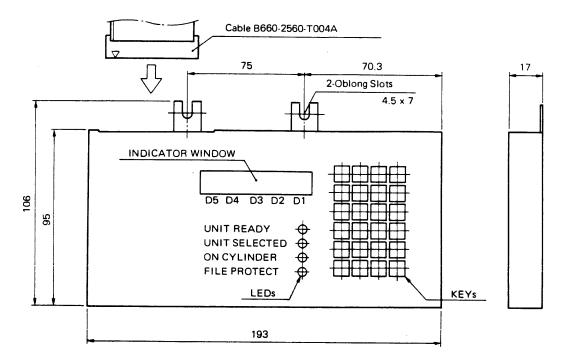

# (6) Diagnostic panel unit

The optional diagnostic panel is available for maintenance facility. The dimensions are given in Figure 1.26.

For detailed description of functions, refer to Section 3.3.

Figure 1.26 Diagnostic panel unit

# **CHAPTER 2 INSTALLATION**

This chapter describes unpacking, installation, and cabling of this drive when shipped separately, and shipping precautions when the drive is delivered as a system.

#### 2.1 Unpacking

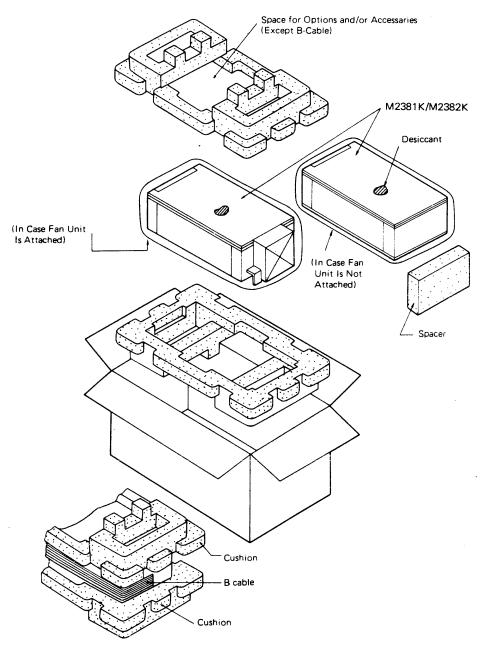

This drive is wrapped in a polyethylene bag, surrounded by cushions, and packed in a carton. An exterior view of the carton is shown in Figure 2.1.

(1) Store and open the carton on a flat surface. Ensure that the top of the box, indicated by a "This Side Up" signs, is oriented correctly, and take out options.

#### Note:

Don't store on the drive in the upside-down position.

- (2) Take out the top cushion.

- (3) Pull the drive out of the box by grasping its base.

Move the drive slowly and carefully, to prevent unnecessary shock.

(4) Store packing material for possible future use.

#### Note:

When the difference in the storage (or shipping) environment and the unpacking environment exceeds 20°C (36°F), the carton should be allowed to stand at the unpacking site for more than 3 hours prior to unpacking to avoid condensation.

#### Caution:

When unpacking, don't place the drive on a bare floor directly to avoid handling damage due to shocks. Place it on a suitable cushioning material.

#### 2.2 Visual Inspection

After unpacking, check the following.

- (1) There should be no cracks, rust or other damage that mars appearance and integrity.

- (2) All parts should be firmly fixed, there should be no loose screws, etc.

- (3) The attachments and options should be as ordered.

## 2.3 Installation

This drive may be mounted in a 19-inch rack or built into a system cabinet. If mounting the drive in a standard 19-inch rack, the mounting tray and its brackets are provided (as options). When the drive is built into a system cabinet, it can be mounted horizontally or vertically (Refer to Figure 2.2)

## 2.3.1 Mounting dimensions

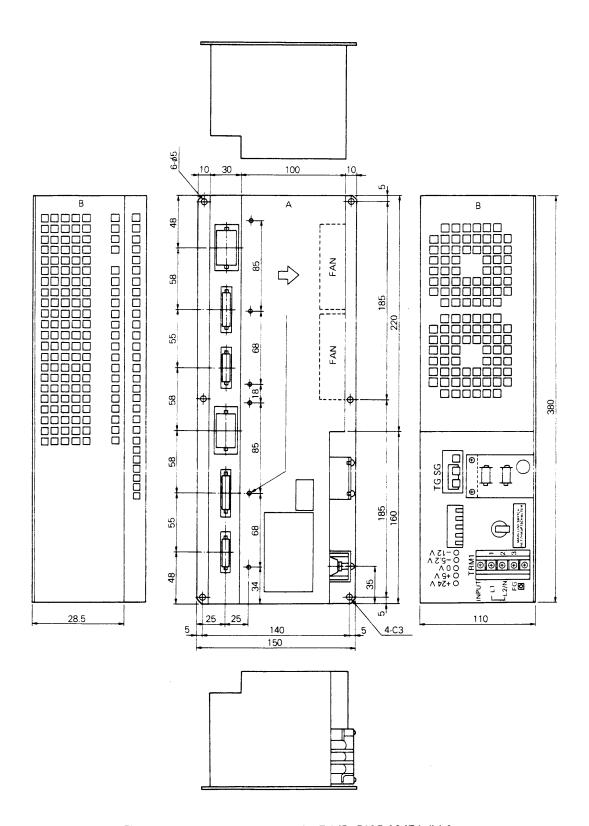

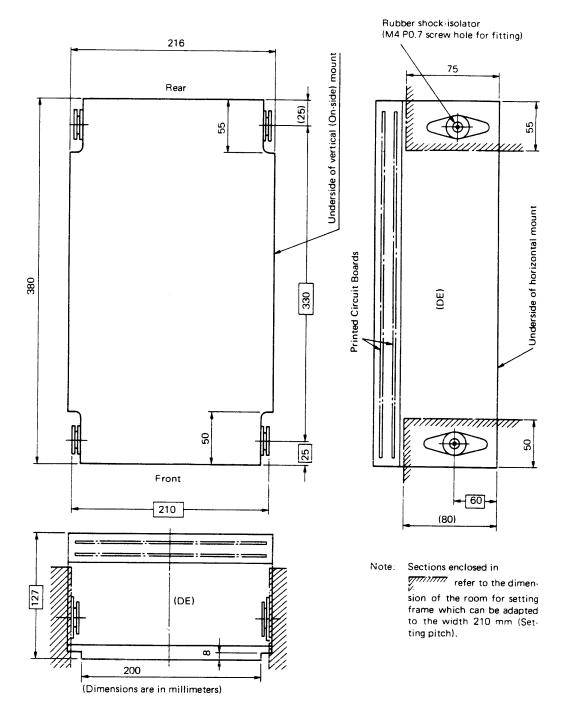

Figure 2.3 shows the drive's dimensions and the structure of its frame.

Figure 2.1 External view of carton

# Note:

Any mounting other than above is not acceptable.

Figure 2.2 Acceptable mounting positions

Figure 2.3 Mounting dimensions

## 2.3.2 Service area

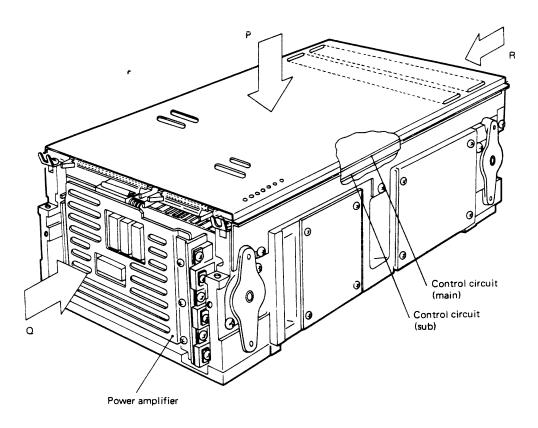

In the case of maintenance or cable connection, the drive is accessed as shown below.

When determining the service area and where to install, make sure that there is enough room for maintenance work.

P side: Maintenance operation on PCAs (main/sub control circuit)

Q side: Maintenance operation on PCA (power amplifier)

R side: Operating the optional panel unit

Figure 2.4 Maintenance access

# 2.3.3 Shock/Vibration stopper

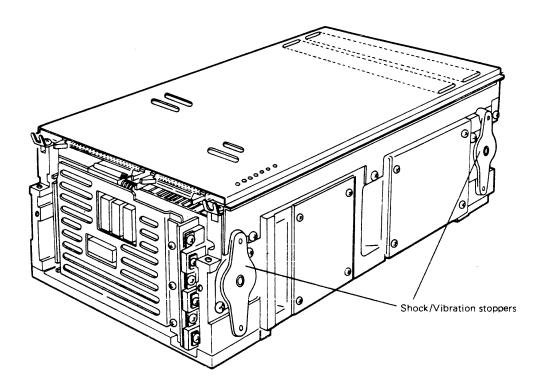

The rubber shock isolators of the drive have integrated stoppers on both ends of each isolator fitting. These limit the amplitude within 3 mm in each direction when the drive is subjected to the specified shock or vibration.

The stoppers act as snubbers after the drive is installed in the system cabinet, and they are effective while in the operating and non-operating modes. There is no necessity of securing the drive to the system cabinet or other countermeasures for system transportation. Figure 2.5 shows the shock/vibration stoppers.

Figure 2.5 Shock/Vibration stopper

#### 2.3.4 Cooling

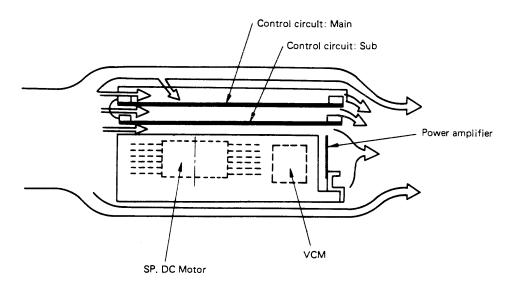

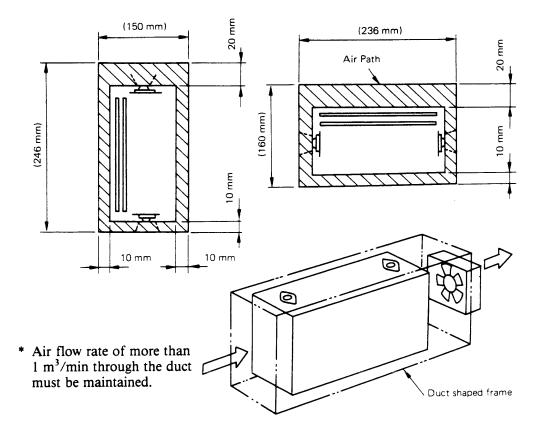

The drive requires some means of cooling\*, since there is no internal blower motor. Figure 2.6 shows the recommended air flow pattern.

Figure 2.6 Recommended air flow pattern

\* For this purpose, an optional fan unit is available. This fan unit will remove the generated heat effectively. (Refer to Subsection 1.3.2.)

The cooling effectiveness shall be confirmed by taking the surface temperatures of specified ICs and heat sinks.

The temperatures must be maintained below those listed in Table 2.1 regardless of ambient temperature.

Maximum surface Part No. On Board Temperature (Tc) Heat sink Power AMP 70°C (for Power Tr) M80 (MB121011) Main PCA 80°C Heat sink Sub PCA 70°C Aluminum base DE 62°C (Bottom side)

Table 2.1 Thermal check point

- \* Random seeking

- \* Even at max. environment temperature (40°C)

Check point location is shown below.

Figure 2.7 Thermal check point location

# • Using optional fan unit

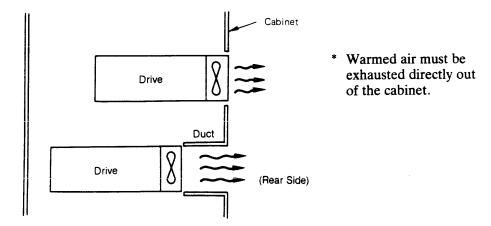

• Without optional fan unit

We recommend that the installation frame be shaped like a duct and the cooling air flow path as illustrated in Figure 2.8.

\* Air flow rate of more than 1 m<sup>3</sup>/min through the duct must be maintained.

Figure 2.8 Examples of installation cooling

# 2.4 Mounting of Options

# 2.4.1 Mounting fan unit

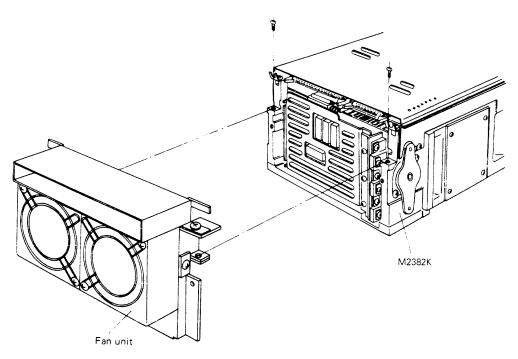

The optional fan unit can be mounted or replaced in the filed. See item (1) in subsection 1.3.2 for the specifications, shape, and connector pin assignments of the fan unit. The mounting procedures of an optional fan are as follows:

- 1) Mount the fan unit and attach it with the screws. Refer to Figure 2.9.

- 2) Connect the power supply cable to the fan unit.

Figure 2.9 Mounting fan unit

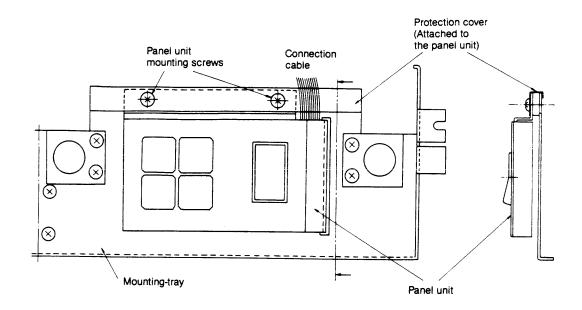

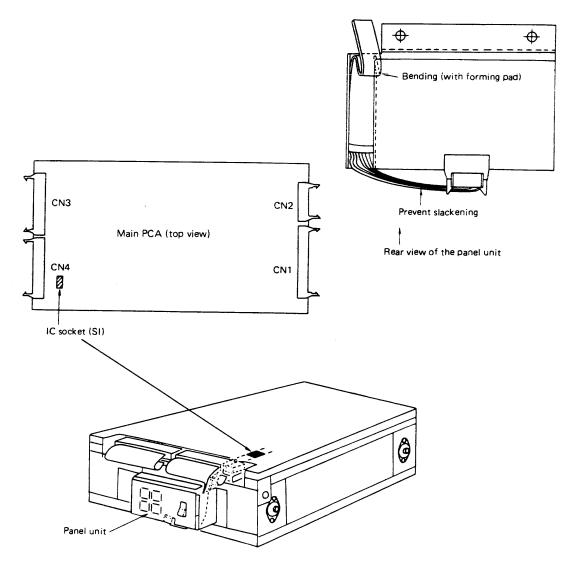

## 2.4.2 Mounting panel unit

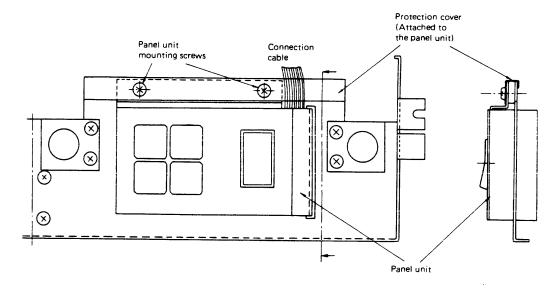

Figure 2.10 shows panel unit mounting diagrams.

# Note:

To prevent the connection cable from slackening under the panel unit or on the drive top (PCA), bend the cable at the rear of the panel unit as shown in the figure above.

Figure 2.10 Mounting panel unit

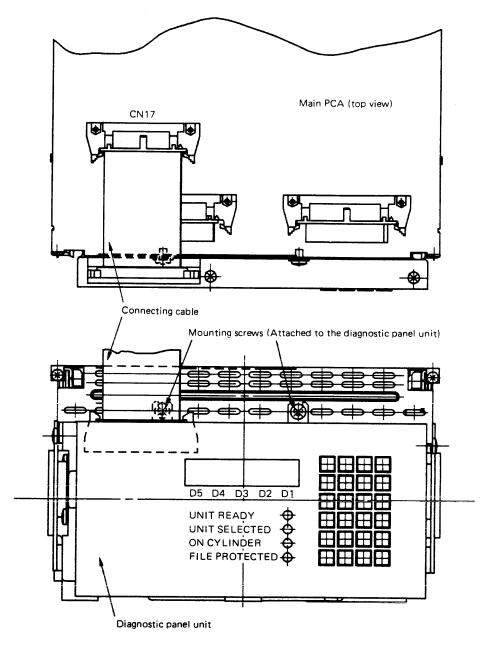

# 2.4.3 Mounting diagnostic panel unit

Figure 2.11 shows diagnostic panel unit mounting diagram.

- 1) Mount the diagnostic panel unit and attach it with the screws.

- 2 Connect the cable to CN17 on the main PCA.

Figure 2.11 Mounting diagnostic panel unit

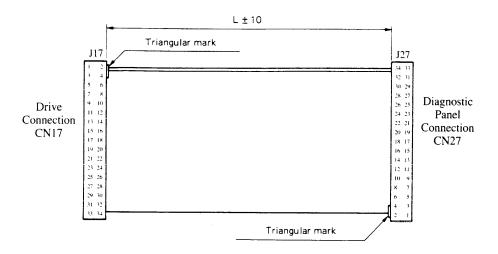

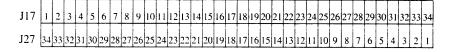

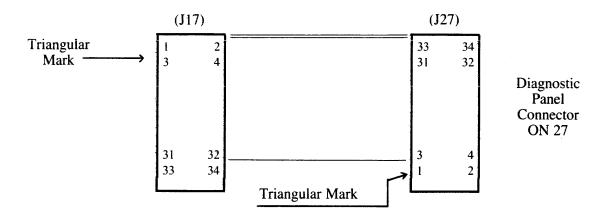

## DIAGNOSTIC PANEL: CROSSOVER CABLE

# **CAUTION**

The cable connecting the diagnostic panel to the M2344K, M2372K, and the M2382K is a crossover cable.

The following diagram explains what makes up a crossover cable.

SIGNAL CROSSOVER CABLE: B660-2560-T004A (Diagnostic Panel Cable)

Signal Crossover Cable Diagram

|     |   |   |   |     |   |   | //   |    |    |    |    |    |    |

|-----|---|---|---|-----|---|---|------|----|----|----|----|----|----|

| _1_ | 2 | 3 | 4 | _ 5 | 6 | 7 | 8 // | 29 | 30 | 31 | 32 | 33 | 34 |

| 34  |   |   |   |     |   |   | 27   |    |    |    |    |    |    |

**NOTE: DO NOT** replace this cable with a standard cable connecting pin '1' on one connector to pin '1' on the other connector. Using a cable other than the crossover cable could result in a blown EEPROM memory chip on the drive.

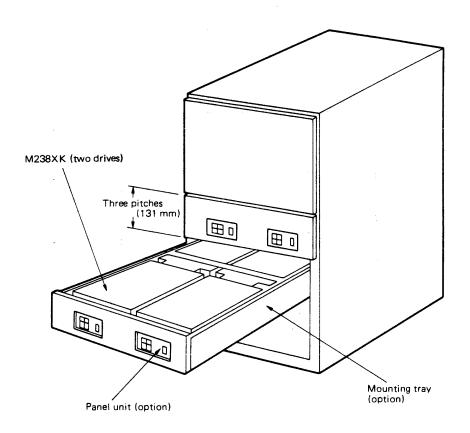

# 2.4.4 Installation mounting tray

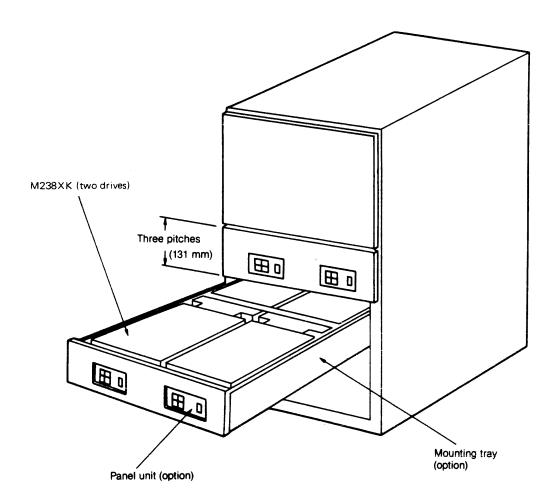

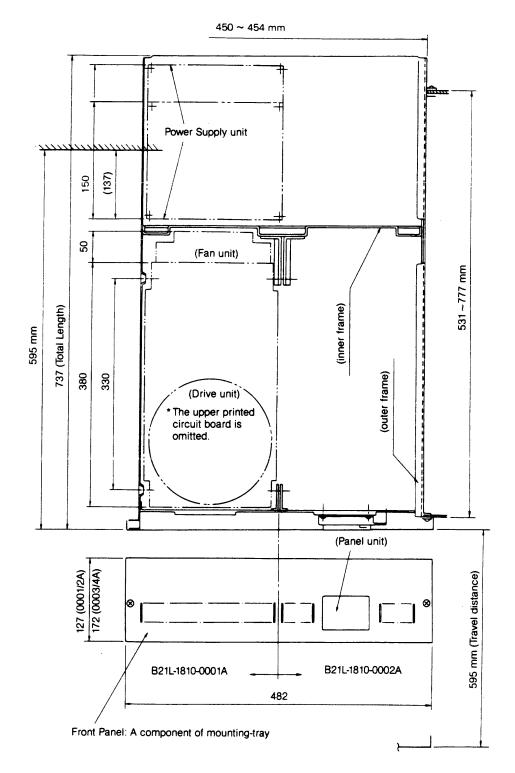

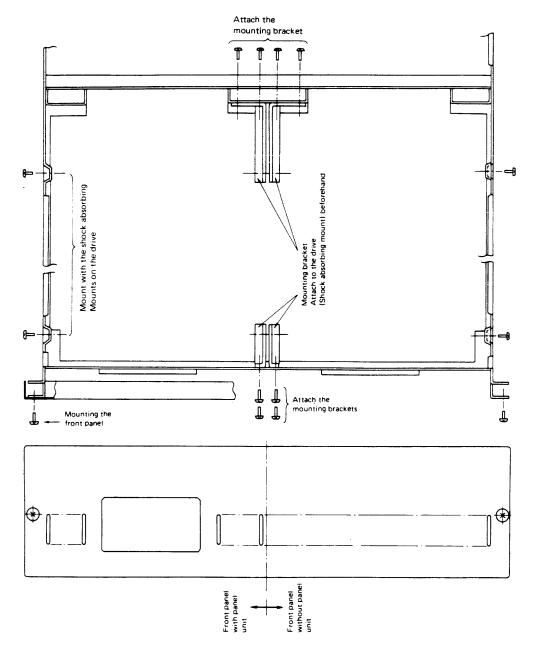

Two drives can be installed side by side, in 3 pitches (131 mm) of height, in a 19-inch rack using the optional mounting tray as shown in Figure 2.12

Figure 2.12 19-inch rack mount installation

# (1) Installation mounting tray in the 19-inch rack

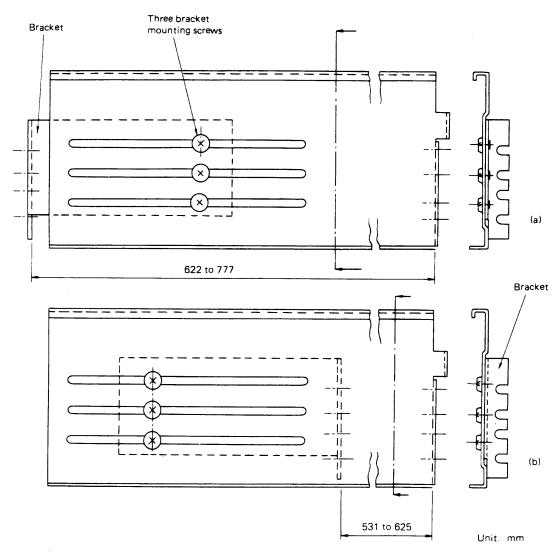

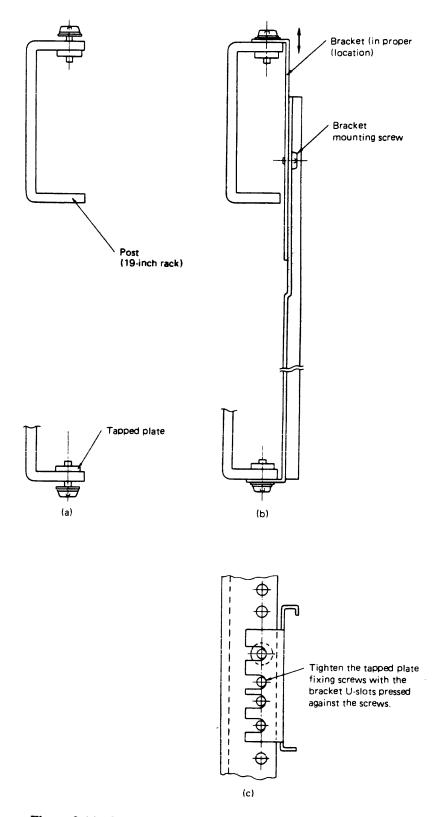

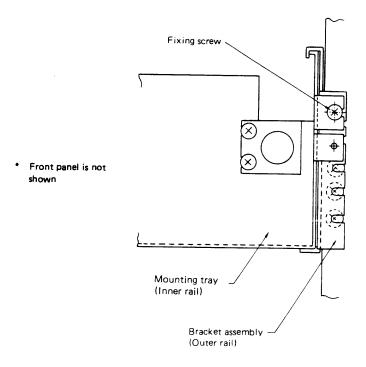

First, mount the bracket assembly on the 19-inch rack as follows. The bracket assembly consists of a pair of right and left slide guides (outer rails).

1) Loosen 3 screws which hold the bracket in the back, so that it moves back and forth. (See Figure 2.13)

The installation frame can be mounted in the 19-inch rack with a depth of mounting pitch ranging from 531 mm to 777 mm by adjusting the brackets. When mounting the installation frame in the rack with a depth of 622 mm to 777 mm, secure the brackets as shown in Figure 2.13, (a).

For racks other than the above, secure the brackets as shown in Figure 2.13, (b). The brackets are symmetrical, so a pair can be used for either (a) or (b).

- 2 Remove tapped plates and hold them on the 19-inch rack post as shown in Figure 2.14, (a).

- 3 Install left and right outer rails (bracket assembly) in the 19-inch rack. Tighten the bracket mounting screws after adjusting bracket location to fit it to the depth of the mounting pitch. (See Figure 2.14, (b).)

- 4 Mount the outer rails using tapped plates with the bracket U-slots (in the back and front) pressed against the tapped plate fixing screws. (See Figure 2.14, (c).)

#### Note:

The above Figure ((a) and (b)) shows only the right slide guide (see from the front). The brackets in (a) and (b) are symmetrical to each other.

Figure 2.13 Bracket assembly

Figure 2.14 Bracket assembly mounting on the 19-inch rack

(5) Insert the mounting tray (inner rail) and check its movement. If it does not slide freely, loosen the tapped plate holding screws and adjust outer rail locations for their relative width.

Confirm that the inner rail stops against the stopper when it is pulled out. (The installation frame can be pulled out approximately 595 mm.)

- 6 Insert the mounting tray and fix it to the outer rails at the front left and right. (See Figure 2.15).

- 7 Mount the front panel.

Figure 2.15 Mounting tray to the outer rails

- (2) Each drive installation on the mounting tray

- (a) Fan unit installation

Drives installed on the mounting tray must have a fan unit. Refer to subsection 2.4.1.

- (b) Drive (with fan) installation

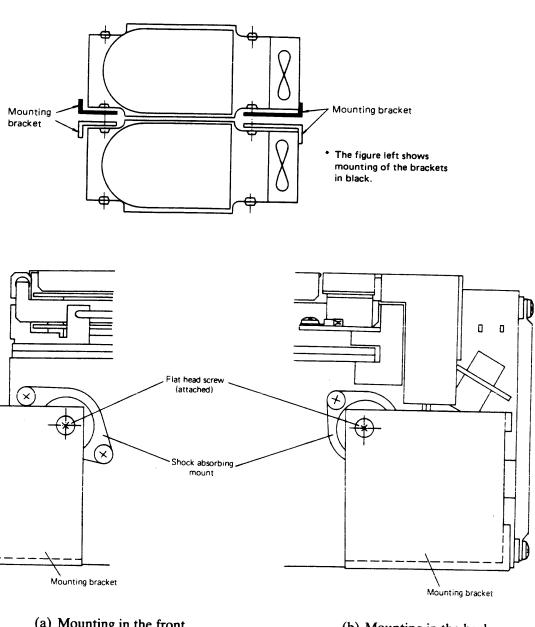

- 1 Attach the mounting brackets using taps (M4) for shock absorbing mounts after setting the mounting brackets to drive location. Note that the front and back brackets are different. Refer to Figure 2.16.

- 2 Set the drive on the mounting tray. The drive can temporarily ride on the front and back beams of the installation frame (inner rail) without manual support using the mounting brackets and 4 cushion supports in the front and back. (See Figure 2.17.) Therefore, even one person can install the drive unit on the mounting tray either removed or on the rack (pulled-out).

- 3) If the panel unit is required, mount it. See item (c).

- 4 Mount the front panel

(a) Mounting in the front of the drive

(b) Mounting in the back of the drive

Figure 2.16 Bracket mounting

Figure 2.17 Mounting drive

# (c) Mounting the panel unit

The panel unit (optional) is mounted as shown in subsection 2.4.2. When the panel unit is used in the mounting tray, mount it as shown in the following figure 2.18.

When the panel unit is mounted, use the mounting tray as the inner rail. (Refer to item (3) in subsection 1.3.2.) This type of mounting tray has a blank panel on one side. When installing 2 drives, this blank panel is not used. When installing 1 drive, mount this blank panel in the unused window.

#### Notes:

- 1. The protection cover on the installation frame edge protects cables from damage. Mount it together with the panel unit as shown in the following figure.

- 2. For cable forming, see Figure 2.10.

Figure 2.18 Mounting the panel unit

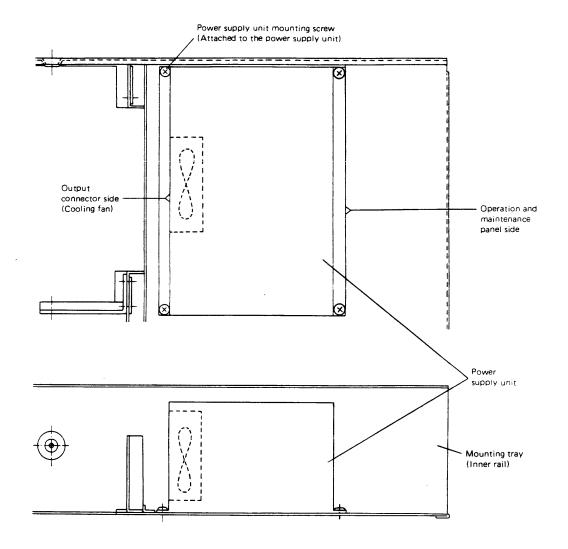

#### (d) Power supply unit installation

The power supply unit is mounted at the back of the mounting tray (inner rail) using 4 screws. (See Figure 2.19) Even after the inner rail is mounted on the 19-inch rack, the power supply unit can be installed if sufficient space is left.

# Note:

Refer to item (4) in subsection 1.3.2 for optimum cable lengths when the optional power supply unit is installed.

Figure 2.19 Power supply unit installation

## 2.5 Cabling

#### 2.5.1 Connectors on drive side

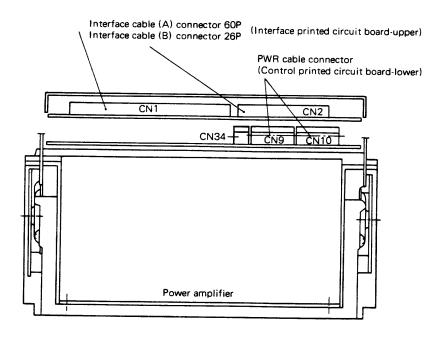

Figure 2.20 shows the mounting positions of connectors on the drive side.

Figure 2.20 Mounting positions of connectors

Cables connected to this drive include interface cable (A) 60P, interface cable (B) 26P, and power cable.

\* The connectors for the power cable consist of two 7P and 2P connectors, while the cable side also requires two 7P and 9P connectors. See subsection 2.5.2.

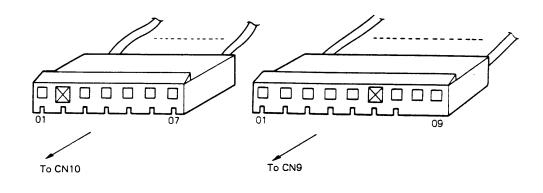

#### 2.5.2 Power cable connection

This drive requires only a DC power source. The following shows the recommended connector specification for the power cable, and correspondence between pin assignment and voltages.

## Power connector specification (on the unit PCA)

Header (7P): MOLEX 2420-07A-G Header (9P): MOLEX 2420-09A-G

# Recommended connector specifications (for power cable)

• Housing (7P) : MOLEX 5239-07

(9P) : MOLEX 5239-09

• Contact : MOLEX 2478-GS

(14 units)

• Key : MOLEX 2560-1

## Pin assignment and voltages

| (CN10)   |              | (CN9)    |             |

|----------|--------------|----------|-------------|

| ìov      | (-12  V RTN) | ì +5 V   |             |

| 2 (Key)  | ,            | 2 + 5 V  |             |

| 3 0 V    | (-12  V RTN) | 3 -5.2 V |             |

| 4 - 12 V | •            | 4 −5.2 V |             |

| 5 -12 V  |              | 5 0 V    | (+24 V RTN) |

| 6 0 V    | (+5 V RTN)   | 6 (Key)  | ,           |

| 7 0 V    | (+5 V RTN)   | 7 0 V    | (+24 V RTN) |

|          |              | 8 + 24 V | ,           |

|          |              | 9 + 24 V |             |

#### Notes:

- 1. Use AWG 18 cable.

- 2. The cable length must be less than 1.5 m.

- 3. Two types of optional power cable are available in combination with optional power supply. See Subsection 1.3.2 for details.

### 2.5.3 Interface cabling

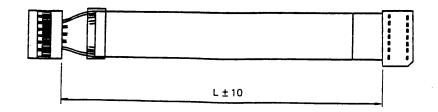

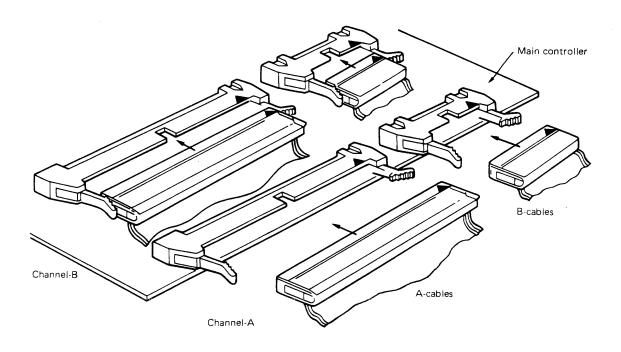

Interface cables include A-cable (60P) for control signals and B-cable (26P) for data signals.

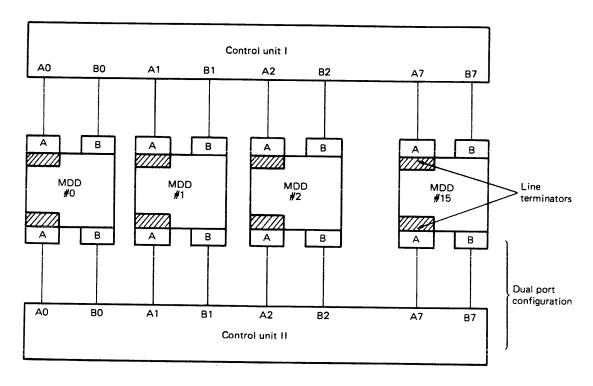

#### (1) Cabling

Interface cables may be connected to the system in the star-chain mode or the daisy-chain mode, as shown in Figure 2.21. For the star-chain mode, the line terminator resistor packs for A-cable are necessary for each drive to be connected. For the daisy-chain mode, only the last drive requires the line terminator.

The connectors of A-cable and B-cable do not have polarizing keys. They should be inserted in accordance with the triangular marks (pin-1 indication) as shown in Figure 2.22.

See Subsection 1.3.2 for details of optional interface cables.

## (1) Star-chain cabling (radial)

Figure 2.21 System interface cabling (1/2)

(2) Daisy-chain cabling

Figure 2.21 System interface cabling (2/2)

Figure 2.22 Interface cabling

#### (2) Cable termination

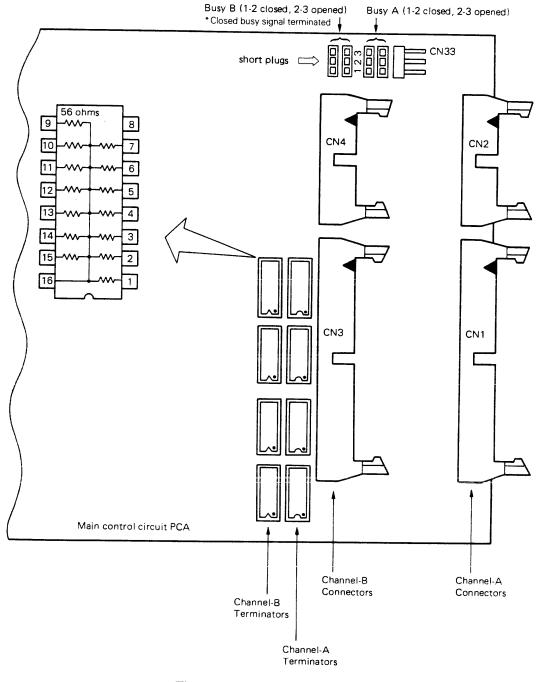

All the drives are shipped with eight terminator module-resistors attached on the main PCA. In the case of daisy-chain configuration, the resistors should be removed from the drives on which line-termination is not necessary when installed in the system. When the Busy A or Busy B signals are used in dual port configuration, these signals termination should be set by 2 or 4 short plugs. Figure 2.23 shows the allocation of the module resistors and short plugs on the main PCA.

Figure 2.23 Cable termination

### 2.5.4 System grounding

(1) This drive is uniformly grounded to signal ground (SG).

Four SG screw holes are prepared at both ends of the front and rear surface of the DE casting for the case where SG/FG connection is required by the system (M4  $P0.7\times6$  mm).

(2) On the optional power supply unit, both SG and FG terminals are provided for connection or disconnection between SG and FG determined by system grounding requirements (refer to Figure 1.12 and 1.13).

#### 2.6 Mode Select Settings

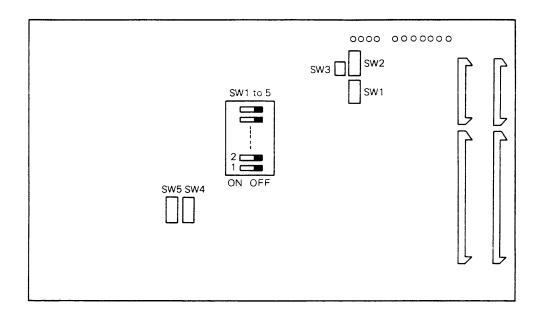

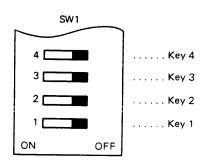

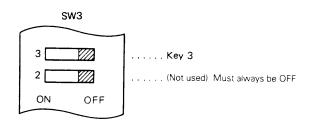

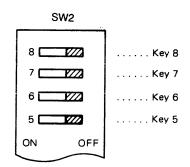

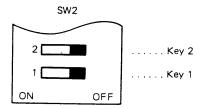

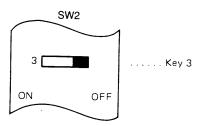

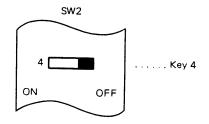

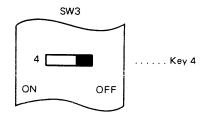

When the drive is installed in the system, the Customer must set switch 1 through 5 according to system requirements; these switches determine, Disk Logical Unit Number, Sector Mode, Tag 4/5 Enable, File Protect, Sector Counting, Device type, and On-Side. Switch 1 through Switch 5 are located on the main PCA, as shown in Figure 2.24.

#### Note:

SW1 and SW2 have 8 keys, and SW4 and SW5 have 7 keys, and SW3 has 4 keys.

Figure 2.24 Mode Select switch location

### 2.6.1 Disk addressing

Disk Logical Unit Number 0 to 15 is selected by SW1 on the main PCA. Set the desired disk address with the three keys on SW1 using the binary code as shown in Table 2.2.

Table 2.2 Disk addressing

| Disk Address | Key 4 | Key 3          | Key 2 | Key 1 |

|--------------|-------|----------------|-------|-------|

| Disk Address | 23    | 2 <sup>2</sup> | 21    | 20    |

| 0            | OFF   | OFF            | OFF   | OFF   |

| 1            | OFF   | OFF            | OFF   | ON    |

| 2            | OFF   | OFF            | ON    | OFF   |

| 3            | OFF   | OFF            | ON    | ON    |

| 4            | OFF   | ON             | OFF   | OFF   |

| 5            | OFF   | ON             | OFF   | ON    |

| 6            | OFF   | ON             | ON    | OFF   |

| 7            | OFF   | ON             | ON    | ON    |

| 8            | ON    | OFF            | OFF   | OFF   |

| 9            | ON    | OFF            | OFF   | ON    |

| 10           | ON    | OFF            | ON    | OFF   |

| 11           | ON    | OFF            | ON    | ON    |

| 12           | ON    | ON             | OFF   | OFF   |

| 13           | ON    | ON             | OFF   | ON    |

| 14           | ON    | ON             | ON    | OFF   |

| 15           | ON    | ON             | ON    | ON    |

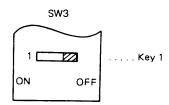

### 2.6.2 Tag 4/5 enable

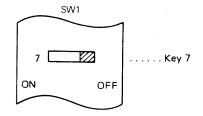

This drive provides optional Tag 4 and Tag 5 functions. The customer may enable or disable these optional functions using Key 7 on SW1 on the main PCA. Refer to Table 2.3.

Disabling the Tag 4 and Tag 5 functions inhibits the receivers of Tag 4 and Tag 5 on the interface. If Tag 4 and Tag 5 are not supported, Key 7 must be in 'OFF' position.

Table 2.3 Tag 4/5 enable

| Tag 4/5 | Key 7 |

|---------|-------|

| Enable  | ON    |

| Disable | OFF   |

### 2.6.3 File protect

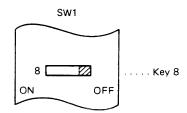

When the customer desires to inhibit the write operation, the File Protect key may be set to the On position (Key 8 on SW1). Refer to Table 2.4.

**Table 2.4** File protect

| File Protect    | Key 8 |

|-----------------|-------|

| Enable writing  | OFF   |

| Disable writing | ON    |

### 2.6.4 Device type (optional)

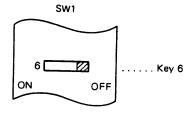

The device type, M2382K, can be setted by Key 6 on SW1 (See Table 2.5).

#### Note:

Tag 4/5 feature must be enabled to obtain device type status.

Table 2.5 Device type

| Device type | Key 6 |

|-------------|-------|

| M2382K      | OFF   |

Key 6 always OFF

#### 2.6.5 Sector mode

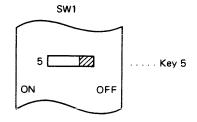

The customer can select Hard Sector mode or Variable Soft Sector mode, using Key 5 on SW1 according to Table 2.6.

In the case of Hard Sector, the customer must set the number of sectors per disk revolution as described in Subsection 2.6.6. Setting the number of sectors per revolution is also available in the Variable Soft Sector mode.

Table 2.6 Sector mode

| Sector Mode          | Key 5 |

|----------------------|-------|

| Hard Sector          | OFF   |

| Variable Soft Sector | ON    |

### 2.6.6 Sector counting

Sector count configuration switches SW4 and SW5 are located on the main PCA. Each key of SW4 and SW5 represents the binary powers of the 2-Bytes Clock as shown in Table 2.7.

SW 4 Kev No. Value SW 5 Key No. Value

Table 2.7 Sector counting keys

#### Note:

The value 1 byte is always set by hardware.

SW4 and SW5 keys must be set according to the desired number of bytes per sector. Knowing that the number of bytes possible on a track equals 49,728, any sectoring requirement (sectors per track) can be configured using the following formulas:

### (1) Calculation based on Sectors/Track

Example: 9 Sectors/Track

$$\frac{\text{1}}{\text{Number of sectors}} = \frac{\text{Number of Bytes}}{\text{per sector}} = \frac{49,728}{9} = 5,525.3333$$

② If the above calculation results in a remainder, truncate the remainder and add one to the integer portion of "number of bytes per sector".

$$5,525 + 1 = 5,526$$

3 Configure SW4 and SW5 to "number of bytes per sector" less one to allow for Sector Counter Reset Clock.

$$5,526 - 1 = 5,525$$

$$5,525 = 4,096 + 1024 + 256 + 128 + 16 + 4 + 1$$

Keys must be "ON": keys # 5 3 1 7 4 2 See above note.

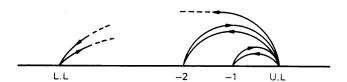

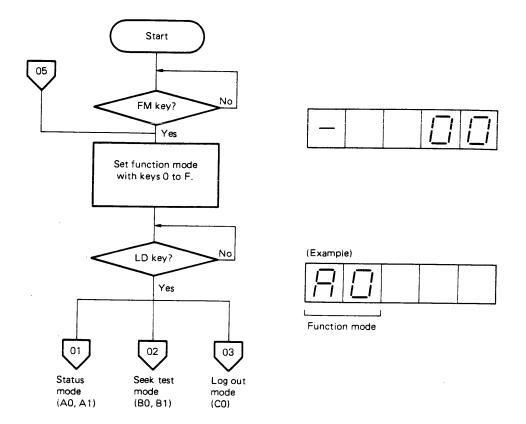

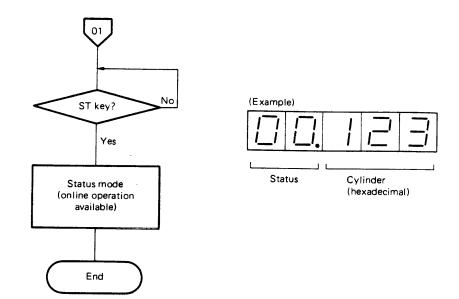

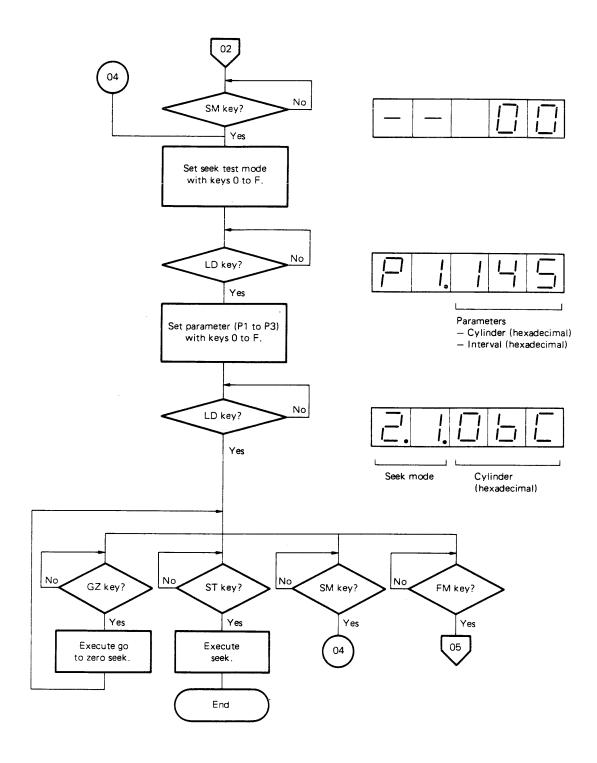

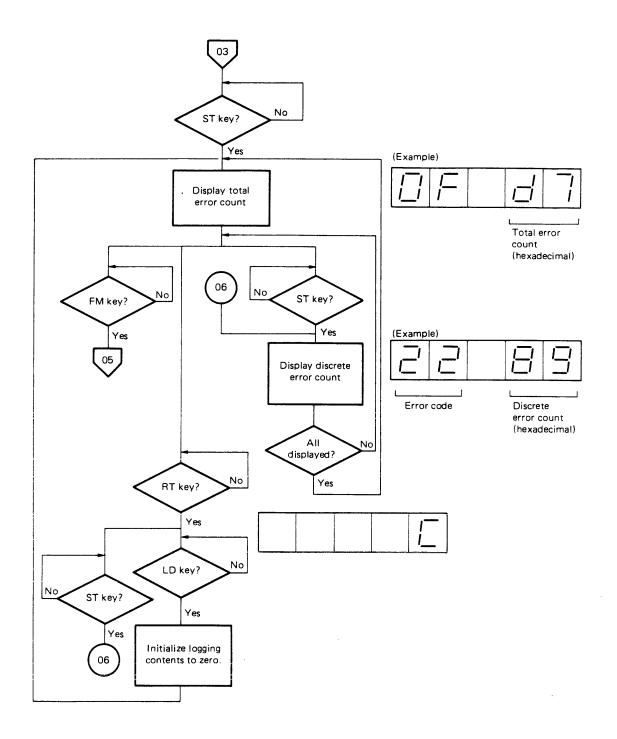

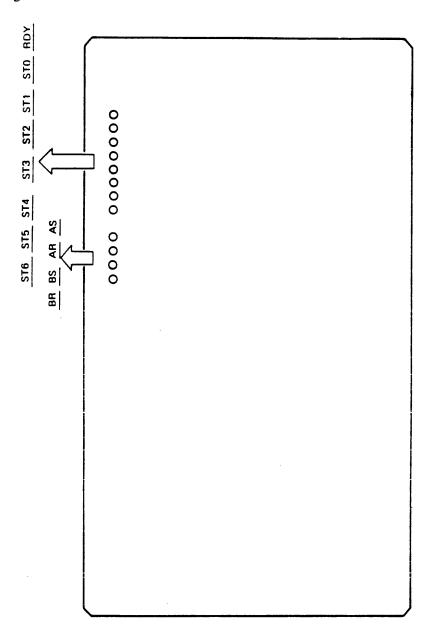

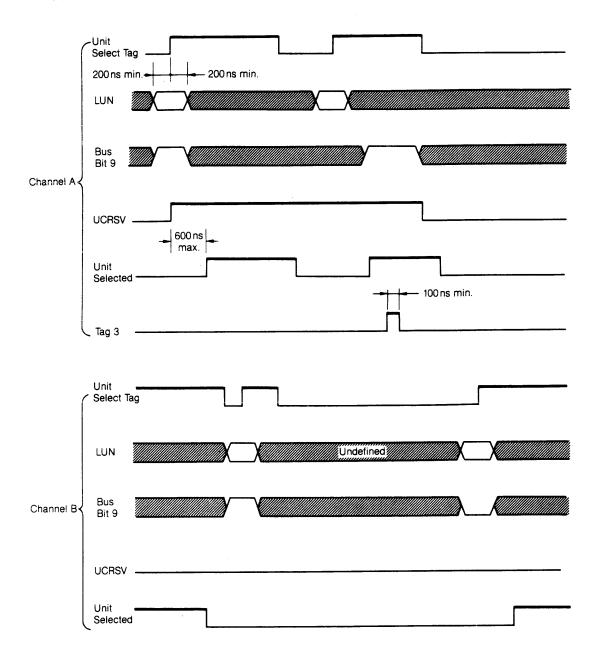

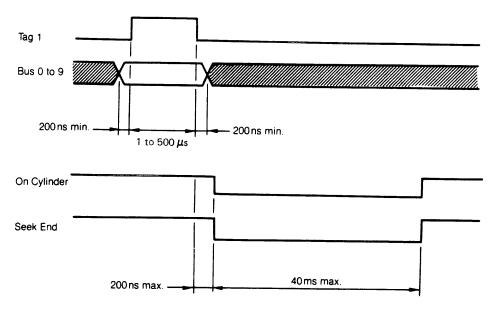

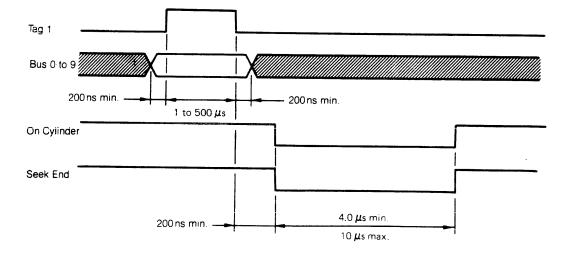

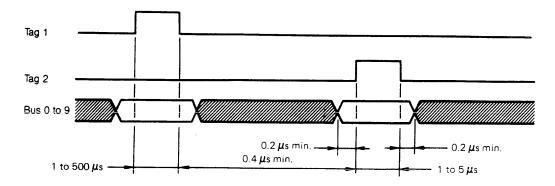

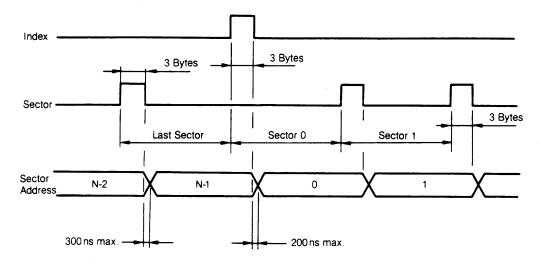

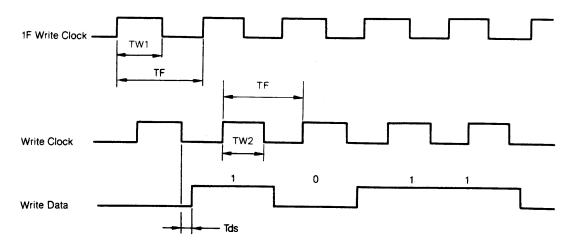

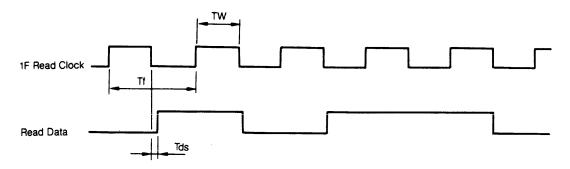

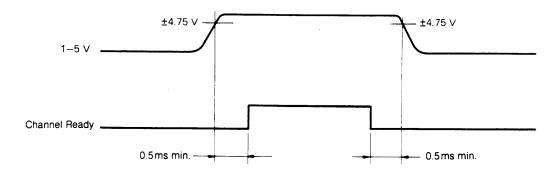

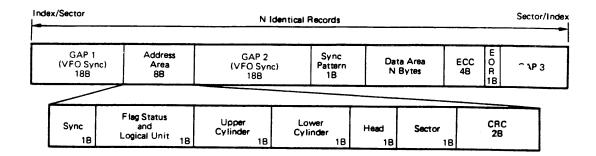

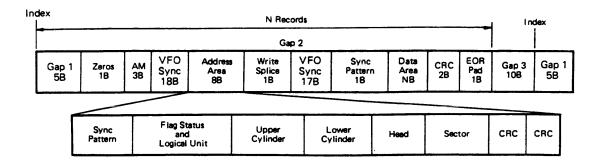

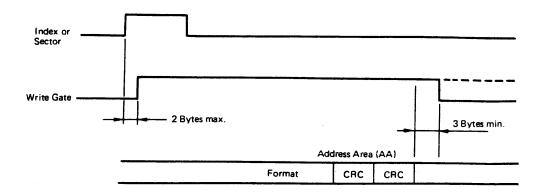

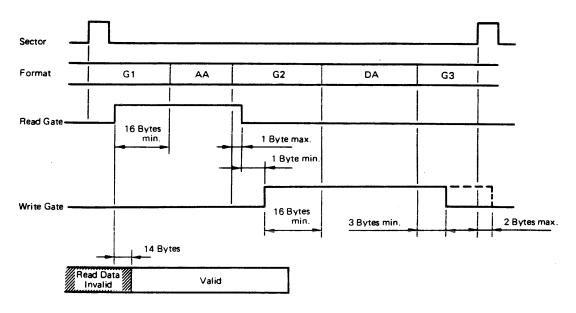

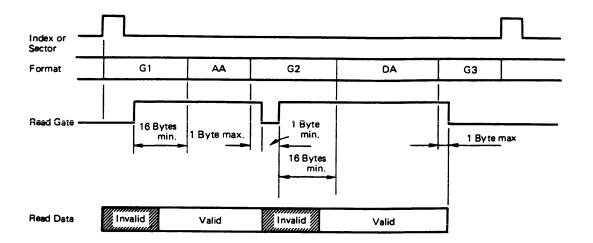

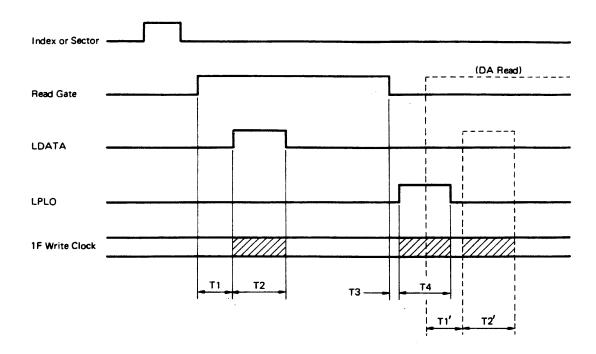

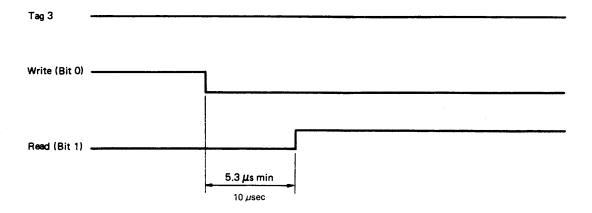

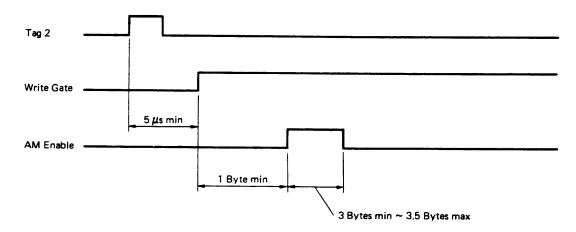

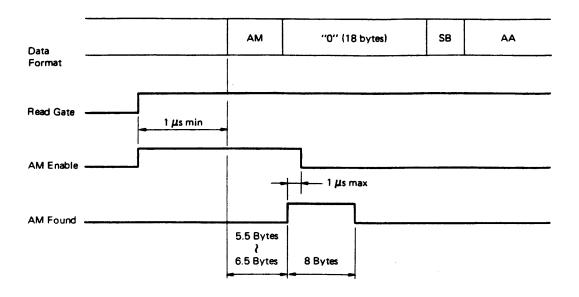

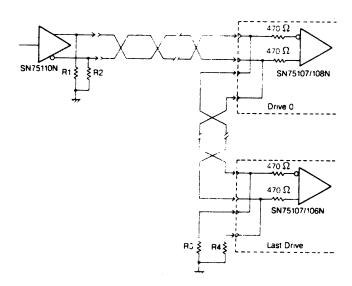

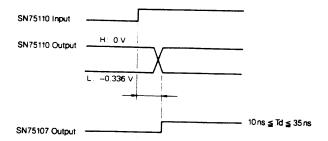

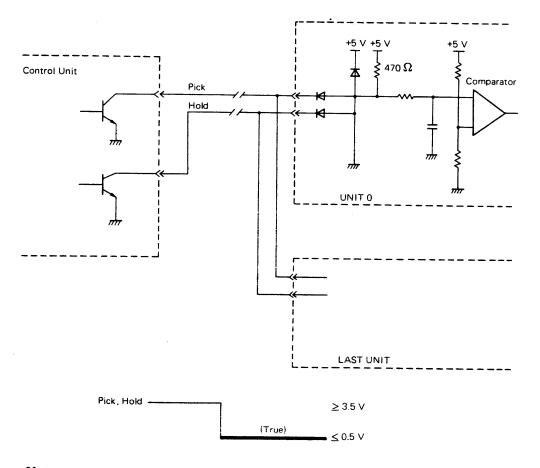

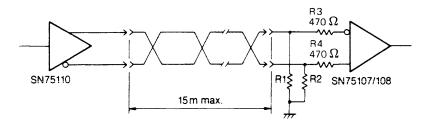

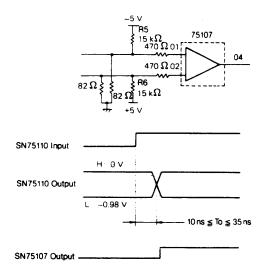

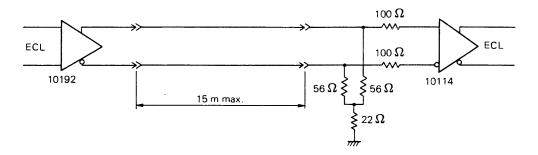

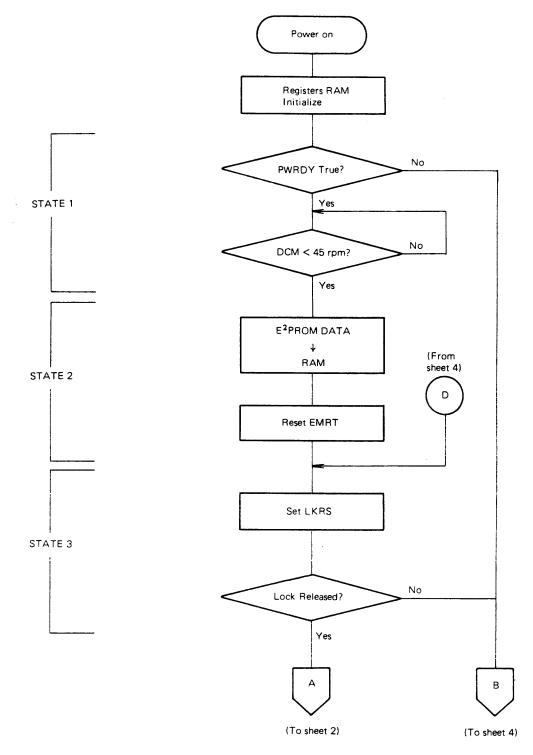

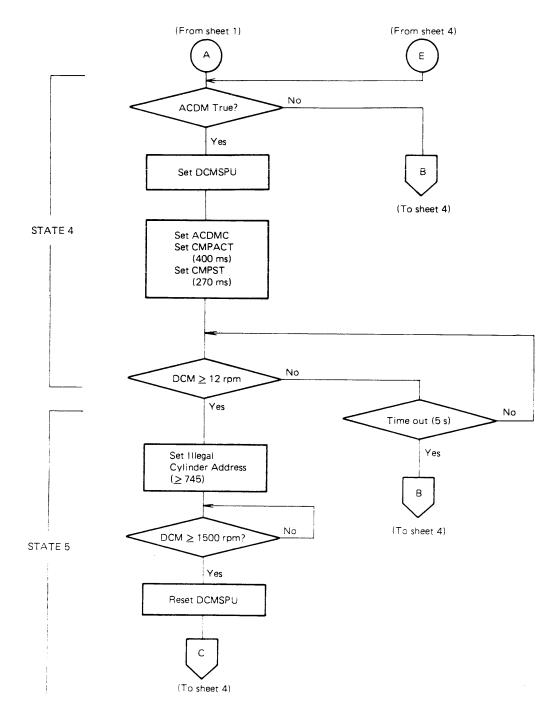

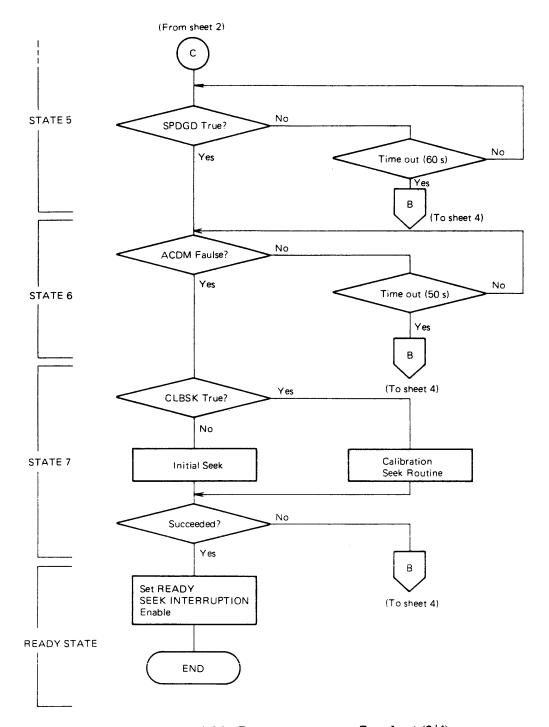

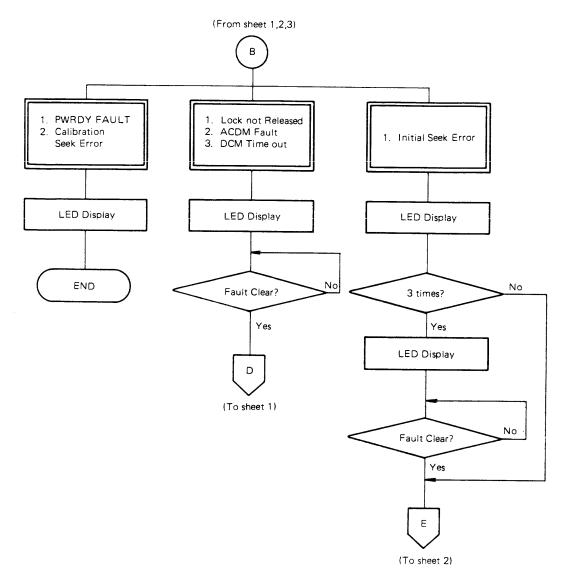

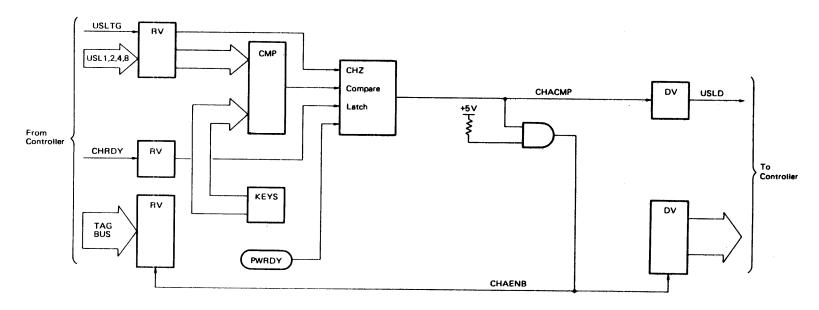

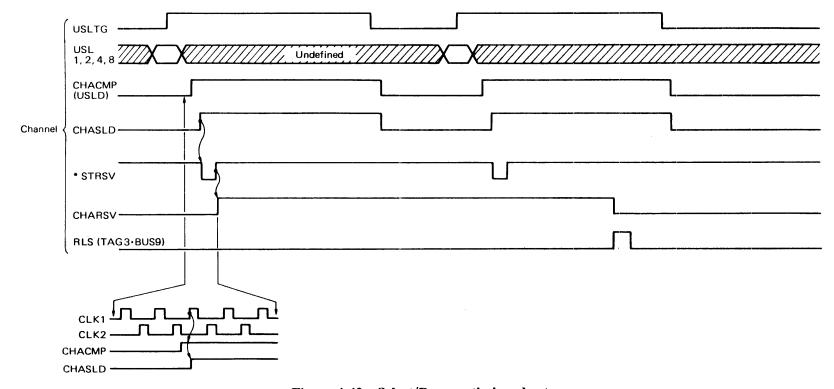

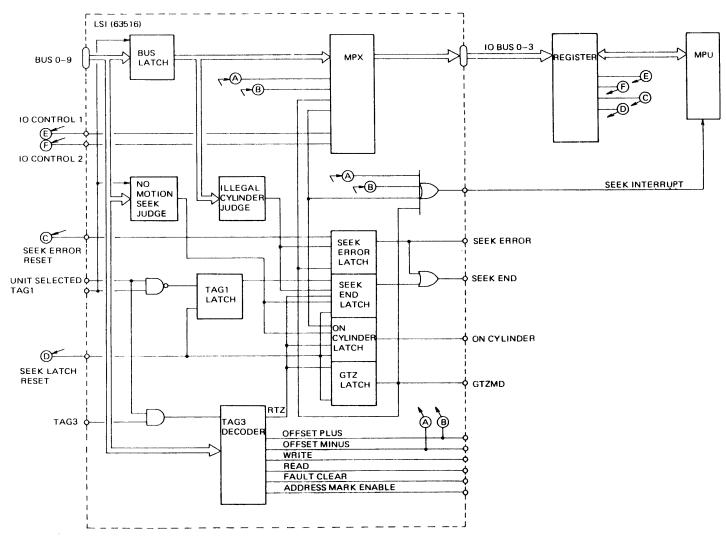

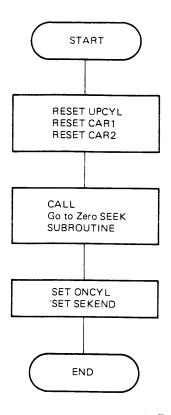

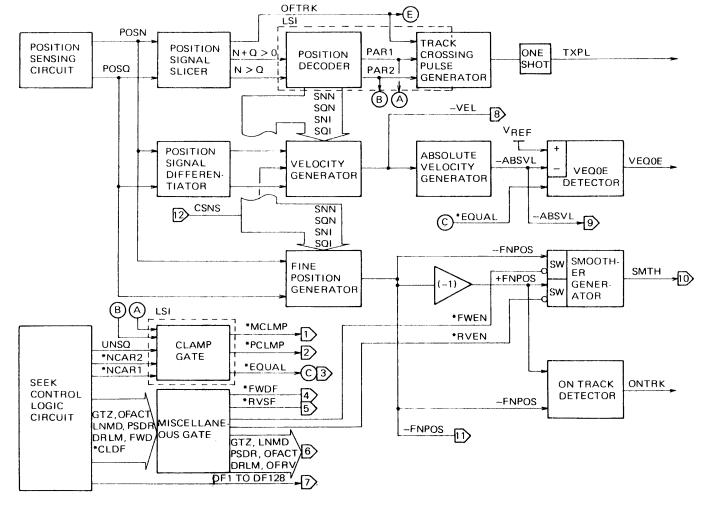

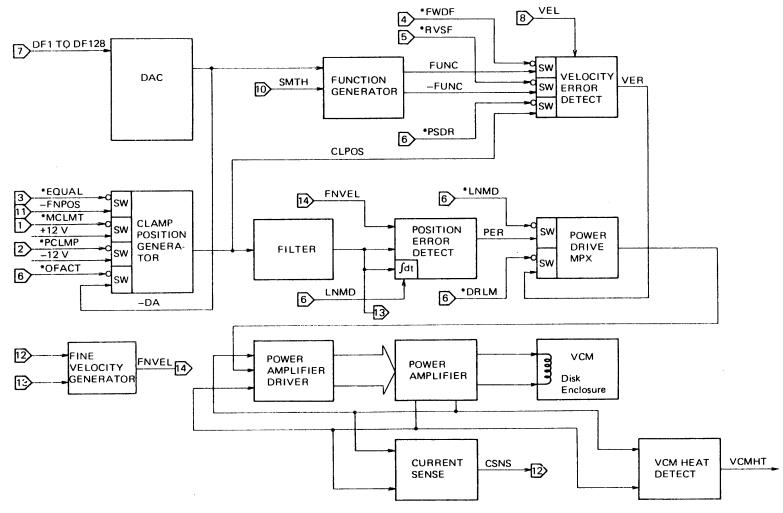

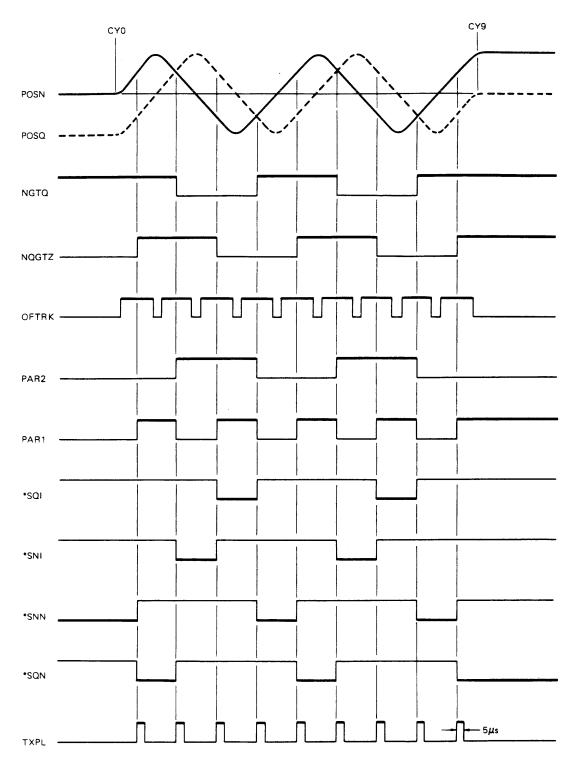

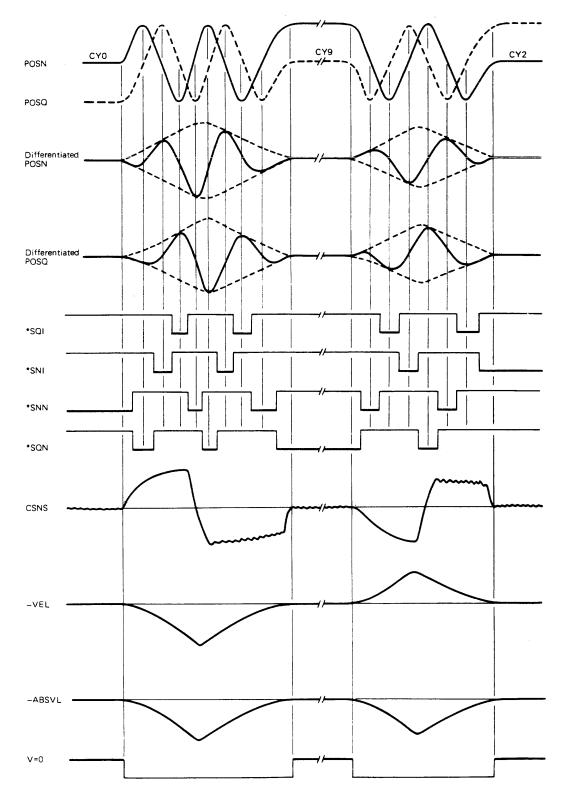

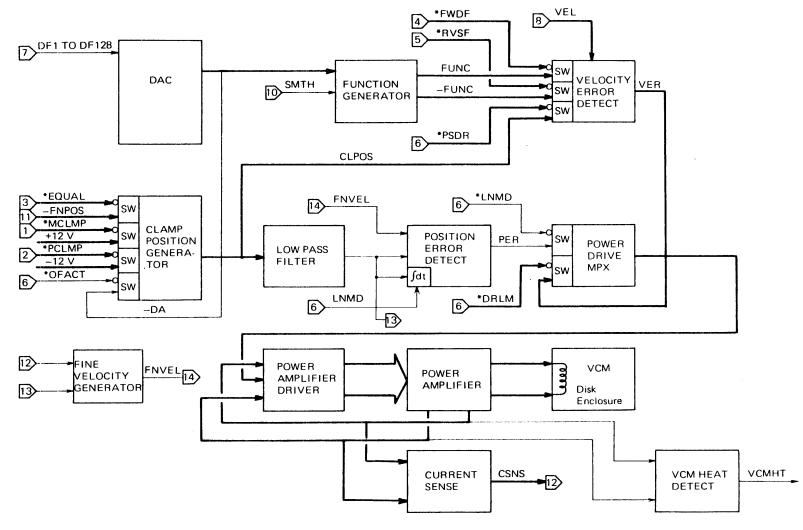

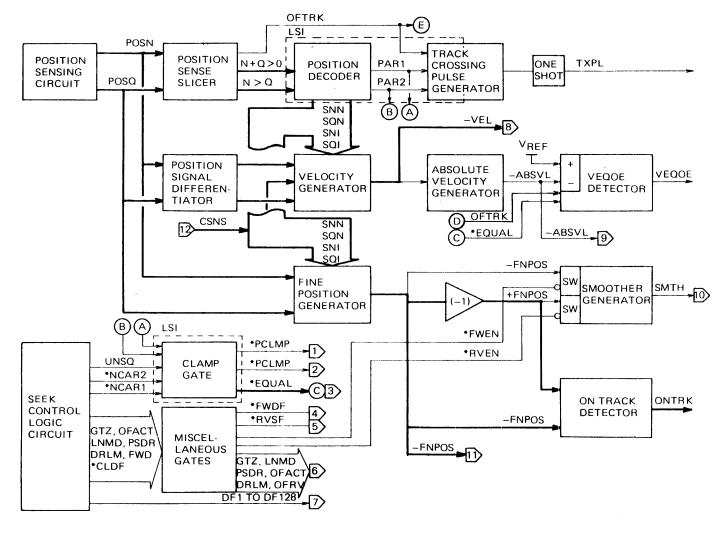

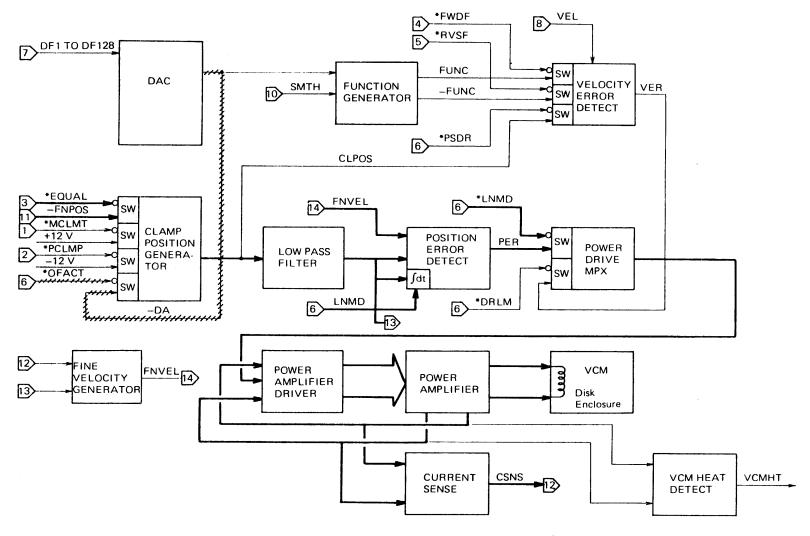

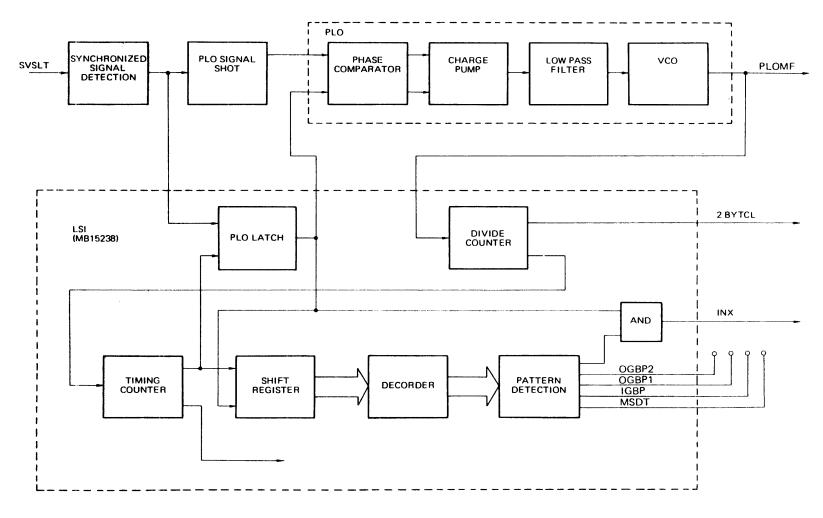

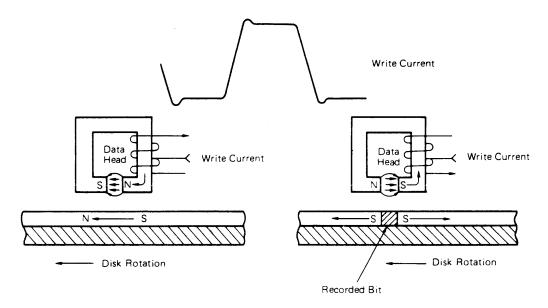

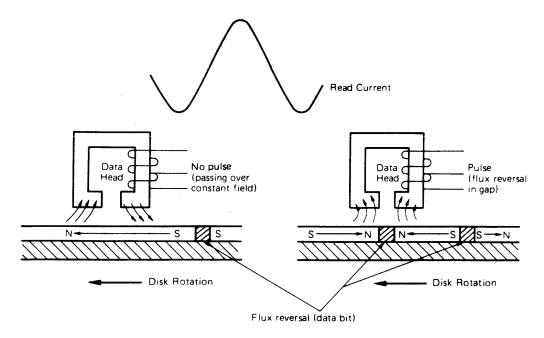

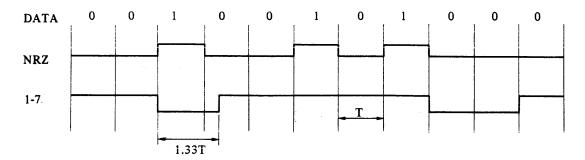

SW5 SW4