4

# PROGRAMMERS REFERENCE MANUAL

## L-3055 DATA PROCESSING SYSTEM

## CO GENERAL DECISION

INFORMATION SYSTEMS GROUP 808 WESTERN AVE • GLENDALE 1, CALIFORNIA

#### **PROGRAMMER'S REFERENCE MANUAL**

### FOR AN

## L-3055 DATA PROCESSING SYSTEM

USED AS THE

AN/FYQ-11 DATA PROCESSOR SET

15 September 1963

General Precision, Inc. Information Systems Group Librascope Division 808 Western Avenue Glendale 1, California

#### LIST OF EFFECTIVE PAGES

Total number of pages in this publication is 318 consisting of the following:

| Page No.                                                                                                                                                                                                          | Issue                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page No.<br>Title<br>A<br>iii thru xvii<br>1-0 thru 1-10<br>2-1 thru 2-14<br>3-1 thru 3-10<br>4-1 thru 4-57<br>5-1 thru 5-6<br>6-1 thru 6-29<br>7-1 thru 7-9<br>8-1 thru 8-37<br>9-1 thru 9-25<br>10-1 thru 10-15 | Issue<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original |

| 11-1 thru 11-18<br>12-1 thru 12-21<br>13-1 thru 13-24<br>14-1<br>15-1 thru 15-5<br>A-1 thru A-3<br>B-1 thru B-4<br>C-1 thru C-6<br>D-1 thru D-3<br>E-1 thru E-3                                                   | Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original                                                          |

| $\mathbf{L} = \mathbf{i}  (\mathbf{III} \mathbf{u}  \mathbf{L} = \mathbf{j})$                                                                                                                                     | Original                                                                                                                                                                      |

\* The asterisk indicates pages changed, added or deleted by current change

А

### TABLE OF CONTENTS

| Section | I INTRODUCTION |                                  | Page  |

|---------|----------------|----------------------------------|-------|

| 1.1     | SYSTE          | M FUNCTIONS                      | 1 - 1 |

| 1.2     | SYSTE          | M FEATURES                       | 1-5   |

| 1.3     | CENTF          | RAL PROCESSOR                    | 1-6   |

| 1.4     |                | MEMORY                           | 1-6   |

| 1.5     |                | 1EMORY                           | 1-7   |

| 1.6     | REAL-          | TIME COMMUNICATION               | 1-7   |

| 1.7     |                | ECORD FACILITIES                 | 1-8   |

| 1.8     | CHECF          | ING FEATURES                     | 1-8   |

| 1.9     |                | CXING                            | 1-9   |

| 1.10    |                | RAM INTERRUPTS                   | 1-9   |

| Section | II             | CORE MEMORY AND WORK FORMAT      |       |

| 2.1     | MEMO           | RY REGISTERS                     | 2 - 1 |

|         | 2.1.1          | Memory Address Register          | 2-1   |

|         | 2.1.2          | Memory Access Register (M)       | 2 - 1 |

| 2.2     | SPECIA         | AL FEATURES                      | 2-2   |

|         | 2.2.1          | Cycle Demand Priority            | 2 - 2 |

|         | 2.2.2          | Individual Memory Trunkline      | 2-2   |

|         | 2.2.3          | Shared Memory Trunkline          | 2 - 2 |

|         | 2.2.4          | Module Address Patchboard        | 2-3   |

|         | 2.2.5          | Core Memory Twinning             | 2-5   |

| 2.3     | INFOR          | MATION FORMAT                    | 2-5   |

|         | 2.3.1          | Word                             | 2-5   |

|         | 2.3.2          | Character                        | 2-6   |

|         | 2.3.3          | Bit                              | 2-6   |

|         | 2.3.4          | Alphanumeric Data Word           | 2-7   |

|         | 2.3.5          | Floating-Point Data Word         | 2-8   |

| 2.4     | INSTRU         | JCTION WORD FORMAT               | 2-9   |

|         | 2.4.1          | Command Character (C)            | 2-10  |

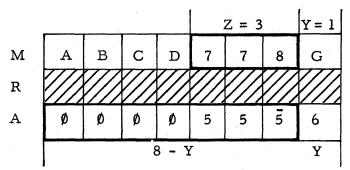

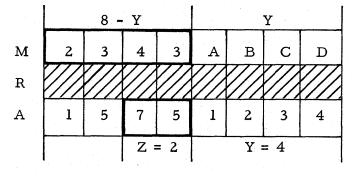

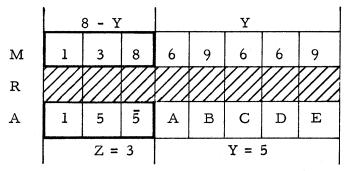

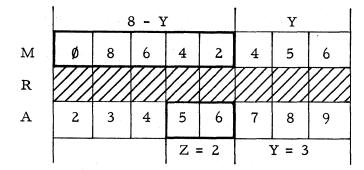

|         | 2.4.2          | Select Characters (ZY)           | 2-10  |

|         | 2.4.3          | Index Character (X)              | 2-11  |

|         | 2.4.4          | Memory Address Characters (MMMM) | 2-12  |

| Section                                     | II (Cont' | d)                                   | Page         |

|---------------------------------------------|-----------|--------------------------------------|--------------|

|                                             | 2.4.5     | Zone Bit Options                     | 2-12         |

| Section                                     | III       | CENTRAL PROCESSOR                    |              |

| 3.1                                         | ARITHN    | METIC SECTION                        | 3-1          |

|                                             | 3.1.1     | R Register                           | 3 <b>-</b> 1 |

|                                             | 3.1.2     | A Register                           | 3-1          |

|                                             | 3.1.3     | Q Register                           | 3-2          |

|                                             | 3.1.4     | Toggles                              | 3-2          |

|                                             | 3.1.5     | Adder                                | 3-2          |

| 3.2                                         | PROGR     | AM CONTROL SECTION                   | 3-2          |

|                                             | 3.2.1     | Instruction Address Register (Ia)    | 3-3          |

|                                             | 3.2.2     | Operand Address Register (Oa)        | 3-3          |

|                                             | 3.2.3     | Index Holder (Xh)                    | 3-4          |

| -                                           | 3.2.4     | Command Holder (C)                   | 3-4          |

|                                             | 3.2.5     | Z Holder (Z)                         | 3-4          |

|                                             | 3.2.6     | Y Holder (Y)                         | 3-5          |

|                                             | 3.2.7     | X Counter (X) $\ldots$               | 3-5          |

|                                             | 3.2.8     | Index Modify Register (B)            | 3 <b>-</b> 5 |

| а. — С. С.<br>С. — С. — С. — С. — С. — С. — | 3.2.9     | Index Registers (Xrl-Xrl7)           | 3-5          |

|                                             | 3.2.10    | Toggles and Switches                 | 3-6          |

| 3.3                                         | PROGR     | AM CONTROL SECTION OPERATION         | 3-6          |

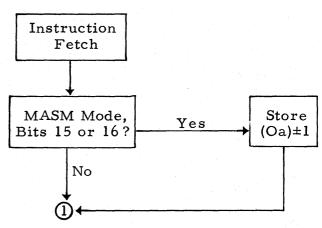

|                                             | 3.3.1     | MASM Operand Address Store           | 3-6          |

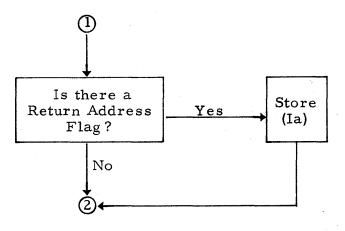

|                                             | 3.3.2     | Flagged Return Address               | 3-7          |

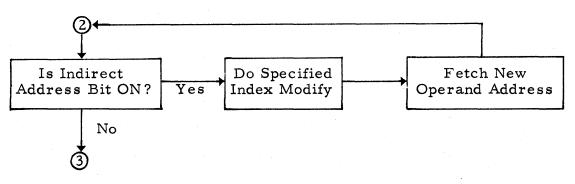

|                                             | 3.3.3     | Indirect Address                     | 3-7          |

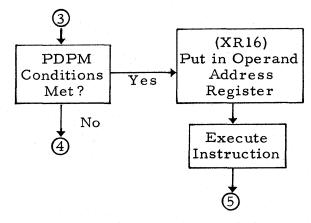

|                                             | 3.3.4     | PDPM Operation                       | 3-7          |

|                                             | 3.3.5     | Index Modify                         | 3-8          |

| 3.4                                         | PUSH-I    | DOWN POP-UP MEMORY MODE (PDPM)       | 3-8          |

| 3.5                                         | MULTI     | -ADDRESS STACKING MEMORY MODE (MASM) | 3-9          |

| Section                                     | IV        | INSTRUCTIONS                         |              |

| 4.1                                         | ARITHM    | METIC INSTRUCTIONS                   | 4-2          |

|                                             | 4.1.1     | Add                                  | 4-4          |

|                                             | 4.1.2     | Subtract                             | 4-6          |

Section IV (Cont'd)

|     | 4.1.3  | Add A to M, Place in R         | 4-7  |

|-----|--------|--------------------------------|------|

|     | 4.1.4  | Subtract A from M, Place in R  | 4-9  |

|     | 4.1.5  | Multiply Long                  | 4-11 |

|     | 4.1.6  | Multiply Short                 | 4-12 |

|     | 4.1.7  | Divide Long                    | 4-13 |

|     | 4.1.8  | Divide Short                   | 4-14 |

| 4.2 | DATA N | AOVE INSTRUCTIONS              | 4-16 |

|     | 4.2.1  | Bring M to A                   | 4-17 |

|     | 4.2.2  | Combine M with A               | 4-18 |

|     | 4.2.3  | Hold A to M                    | 4-19 |

|     | 4.2.4  | Jerk M to R                    | 4-19 |

|     | 4.2.5  | Keep R to M                    | 4-20 |

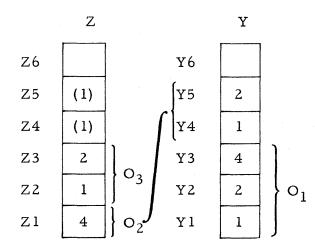

|     | 4.2.6  | Load M in ZY                   | 4-21 |

|     | 4.2.7  | Save ZY in M                   | 4-22 |

|     | 4.2.8  | Copy Z to Y                    | 4-23 |

|     | 4.2.9  | Left Shift                     | 4-25 |

|     | 4.2.10 | Right Shift                    | 4-26 |

| 4.3 | COMPA  | RE INSTRUCTIONS                | 4-28 |

|     | 4.3.1  | Alphabetic Compare             | 4-30 |

|     | 4.3.2  | Numeric Compare                | 4-31 |

|     | 4.3.3  | Field Compare, Automatic Shift | 4-32 |

|     | 4.3.4  | Index Register Compare         | 4-33 |

| 4.4 | SET-CO | NVERT INSTRUCTIONS             | 4-33 |

|     | 4.4.1  | Set-Reset Toggle               | 4-34 |

|     | 4.4.2  | Set-Reset Bit                  | 4-35 |

|     | 4.4.3  | Logical OR                     | 4-35 |

|     | 4.4.4  | Logical AND                    | 4-36 |

|     | 4.4.5  | Convert                        | 4-36 |

| 4.5 | PROGRA | AM CONTROL INSTRUCTIONS        | 4-37 |

|     | 4.5.1  | No Operation                   | 4-38 |

|     | 4.5.2  | Unconditional Transfer         | 4-38 |

v

| Section | IV (Cont'd)                                           | Page          |

|---------|-------------------------------------------------------|---------------|

|         | 4.5.3 Test                                            | 4-38          |

|         | 4.5.4 Bit Compare                                     | 4-39          |

|         | 4.5.5 Execute                                         | 4-40          |

|         | 4.5.6 Modify Index Register                           | 4-40          |

|         | 4.5.7 Halt                                            | 4-41          |

| 4.6     | FLOATING-POINT INSTRUCTIONS                           | 4-41          |

|         | 4.6.1 Floating-Point Add                              | 4-43          |

|         | 4.6.2 Floating-Point Subtract                         | 4-45          |

|         | 4.6.3 Floating-Point Add A to M and place in R        | 4-48          |

|         | 4.6.4 Floating-Point Subtract A from M and Place in R | 4 <b>-</b> 50 |

|         | 4.6.5 Floating-Point Multiply Long                    | 4 <b>-</b> 53 |

|         | 4.6.6 Floating-Point Divide Long                      | 4 <b>-</b> 55 |

|         | 4.6.7 Floating-Point Numeric Compare                  | 4 <b>-</b> 56 |

| Section | V I/O INTERFACE                                       |               |

| 5.1     | I/O BUFFER REGISTER                                   | 5-1           |

| 5.2     | CHARACTER HOLDER                                      | 5-1           |

| 5.3     | SCANNER                                               | 5-1           |

| 5.4     | I/O INSTRUCTION REGISTER                              | 5-2           |

| 5.5     | I/O INSTRUCTION LOCATION REGISTER                     | 5-2           |

| 5.6     | OUTPUT OPERATION                                      | 5-2           |

| 5.7     | INPUT OPERATION                                       | 5-3           |

| 5.8     | ERROR CONSIDERATION                                   | 5-4           |

| 5.9     | STATUS INDICATORS AND DEVICE ADDRESSES                | 5 <b>-</b> 5  |

| 5.10    | I/O INTERFACE INSTRUCTION FORMAT                      | 5-6           |

|         | 5.10.1 Input                                          | 5-6           |

|         | 5.10.2 Output                                         | 5 <b>-</b> 6  |

| Section | VI BUFFER PROCESSOR                                   |               |

| 6.1     | BUFFER PROCESSOR CONFIGURATION                        | 6-1           |

| 6.2     | INPUT MESSAGE TRANSFER                                | 6-1           |

| e       | 6.2.1 Data Link to Receiving L-119                    | 6-1           |

|         | 6.2.2 Receiving L-119 to Central Processor            | 6-4           |

| Section | VI (Cont'd)                                 | Page |

|---------|---------------------------------------------|------|

| 6.3     | OUTPUT MESSAGE TRANSFER                     | 6-7  |

|         | 6.3.1 Central Processor to Sending L-119    | 6-7  |

|         | 6.3.2 Sending L-119 to Data Link            | 6-10 |

| 6.4     | MESSAGE STORAGE                             | 6-11 |

| 6.5     | L-119 MODULE DESCRIPTION                    | 6-11 |

|         | 6.5.1 Input/Output Interface                | 6-11 |

|         | 6.5.2 Disc Memory                           | 6-13 |

|         | 6.5.3 Major Logical Elements                | 6-14 |

|         | 6.5.4 Buffer Processor Words                | 6-16 |

| *.      | 6.5.5 Memory Addresses                      | 6-16 |

|         | 6.5.6 Memo Assignments                      | 6-17 |

| 6.6     | BUFFER PROCESSOR INSTRUCTIONS               | 6-19 |

| 6.7     | INSTRUCTION SEQUENCING                      | 6-21 |

|         | 6.7.1 Instruction Retrieval                 | 6-21 |

|         | 6.7.2 Normal Instruction Timing             | 6-21 |

|         | 6.7.3 Message Track Instruction Timing      | 6-22 |

|         | 6.7.4 Input Message Sequence                | 6-22 |

|         | 6.7.5 Output Message                        | 6-23 |

| 6.8     | BUFFER PROCESSOR OPERATION                  | 6-24 |

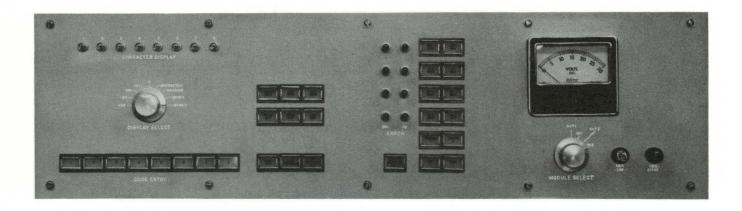

|         | 6.8.1 Controls and Indicators               | 6-24 |

|         | 6.8.2 Buffer Processor Operating Procedures | 6-27 |

| Section | VII UNI-RECORD INTERFACE                    |      |

| 7.1     | UNI-RECORD BUFFER REGISTER                  | 7-1  |

| 7.2     | CHARACTER HOLDER                            | 7-1  |

| 7.3     | WORD COUNTER                                | 7-1  |

| 7.4     | UNI-RECORD INSTRUCTION REGISTER             | 7-2  |

| 7.5     | UNI-RECORD INSTRUCTION LOCATION REGISTER    | 7-2  |

| 7.6     | STATUS AND ERROR TOGGLES                    | 7-2  |

| 7.7     | UNI-RECORD DEVICE ADDRESSING                | 7-5  |

| 7.8     | UNI-RECORD INTERFACE INSTRUCTIONS           | 7-5  |

|         | 7.8.1 Input                                 | 7-6  |

|         | 7.8.2 Output                                | 7-7  |

| Section | VII (Co | nt'd)                                | Page   |

|---------|---------|--------------------------------------|--------|

|         | 7.8.3   | Test                                 | 7-8    |

| 7.9     | TAPE    | TRANSPORT CONTROL INSTRUCTIONS       | 7-8    |

|         | 7.9.1   | Backspace Tape -(                    | 7-8    |

|         | 7.9.2   | Forward-Space Tape -)                | 7-8    |

|         | 7.9.3   | Rewind Tape $-\Box$                  | 7-9    |

|         | 7.9.4   | Write File Mark – – ,                | 7-9    |

| Section | VIII    | UNI-RECORD CONSOLES                  |        |

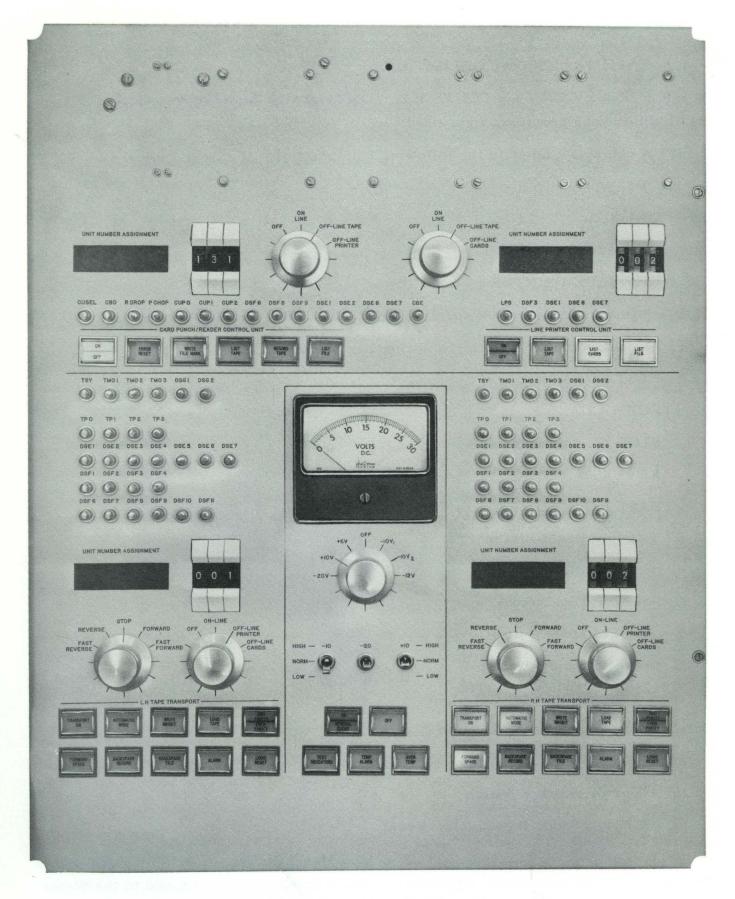

| 8.1     | TAPE    | TRANSPORTS                           | 8-2    |

|         | 8.1.1   | Tape Transport On-Line Read          | 8-3    |

|         | 8.1.2   | Tape Transport On-Line Write         | 8-5    |

|         | 8.1.3   | Tape Transport Mode Change Operation | 8-6    |

|         | 8.1.4   | Tape Transport Control Operations    | 8 - 7  |

|         | 8.1.5   | Tape Transport Off-Line Operations   | 8-8    |

|         | 8.1.6   | Tape Transport Operation             | 8-9    |

|         | 8.1.7   | Tape Transport Operating Procedures  | 8-12   |

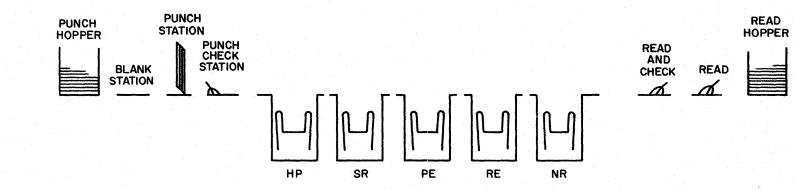

| 8.2     | CARD    | READER/PUNCH                         | 8-16   |

|         | 8.2.1   | Console Description                  | 8-16   |

|         | 8.2.2   | Card Reader                          | 8 -1 7 |

|         | 8.2.3   | Card Punch                           | 8-24   |

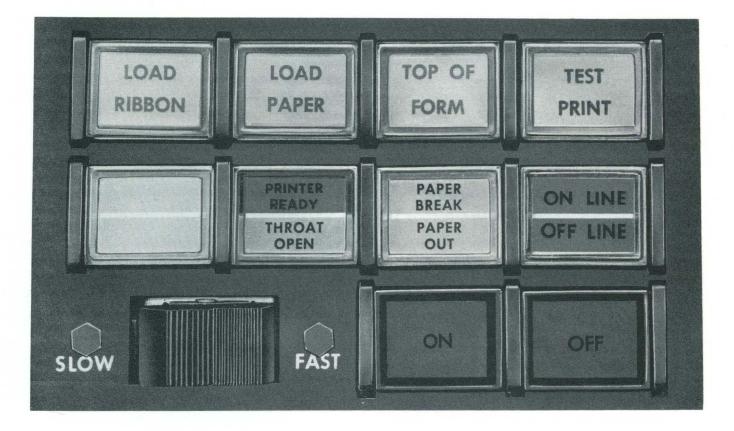

| 8.3     | LINE I  | PRINTER                              | 8-29   |

|         | 8.3.1   | Line Printer On-Line                 | 8-30   |

|         | 8.3.2   | Line Printer Off-Line                | 8-34   |

| Section | IX      | DISC MEMORY                          |        |

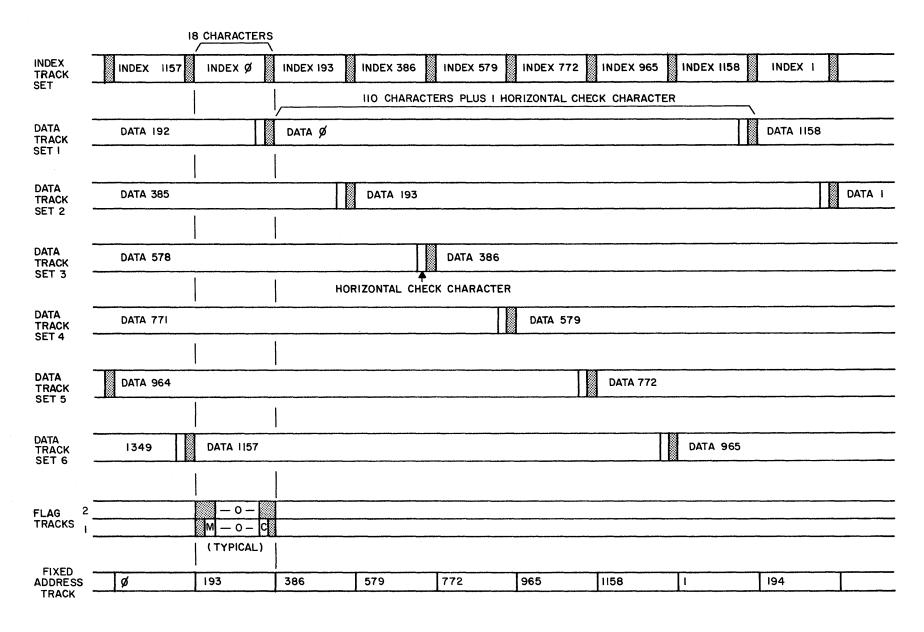

| 9.1     | ORGA    | NIZATION OF DATA                     | 9-2    |

|         | 9.1.1   | Character                            | 9-2    |

|         | 9.1.2   | Block                                | 9-2    |

|         | 9.1.3   | Data-Band                            | 9-2    |

|         | 9.1.4   | Twin                                 | 9-4    |

|         | 9.1.5   | Flag Tracks                          | 9-4    |

| Se | ction | IX (Con | ut'd)                                             | Page |

|----|-------|---------|---------------------------------------------------|------|

|    | 9.2   | DISC 1  | MEMORY INSTRUCTION FORMAT                         | 9-5  |

|    |       | 9.2.1   | The Interface Construction Word                   | 9-5  |

|    |       | 9.2.2   | Disc Memory Operation Word                        | 9-6  |

|    |       | 9.2.3   | Key/Data Address and Mask-Control Address<br>Word | 9-6  |

|    |       | 9.2.4   | Key Format                                        | 9-7  |

|    |       | 9.2.5   | Mask and Control Format                           | 9-8  |

|    | 9.3   | DISC I  | MEMORY COMPONENTS                                 | 9-9  |

|    |       | 9.3.1   | Disc Storage                                      | 9-9  |

|    |       | 9.3.2   | Core Buffer and Search Registers                  | 9-9  |

|    |       | 9.3.3   | Disc Memory Operation Register                    | 9-9  |

|    |       | 9.3.4   | MC Buffer Store                                   | 9-10 |

|    |       | 9.3.5   | CP Buffer Store                                   | 9-11 |

|    | 9.4   | DISC 1  | MEMORY INTERFACE                                  | 9-11 |

|    |       | 9.4.1   | Interface Instruction Register                    | 9-12 |

|    |       | 9.4.2   | Interface Instruction Location Register           | 9-12 |

|    |       | 9.4.3   | Interface Address Processing Register             | 9-12 |

|    |       | 9.4.4   | Disc Memory Interface Operation                   | 9-12 |

|    | 9.5   | DISC 1  | MEMORY OPERATION                                  | 9-13 |

|    |       | 9.5.1   | Write Function                                    | 9-14 |

|    |       | 9.5.2   | Read Function                                     | 9-14 |

|    |       | 9.5.3   | Obsolete Function                                 | 9-15 |

|    |       | 9.5.4   | Count Function                                    | 9-15 |

|    |       | 9.5.5   | Fixed Address Access                              | 9-15 |

|    |       | 9.5.6   | Obsolete Access                                   | 9-16 |

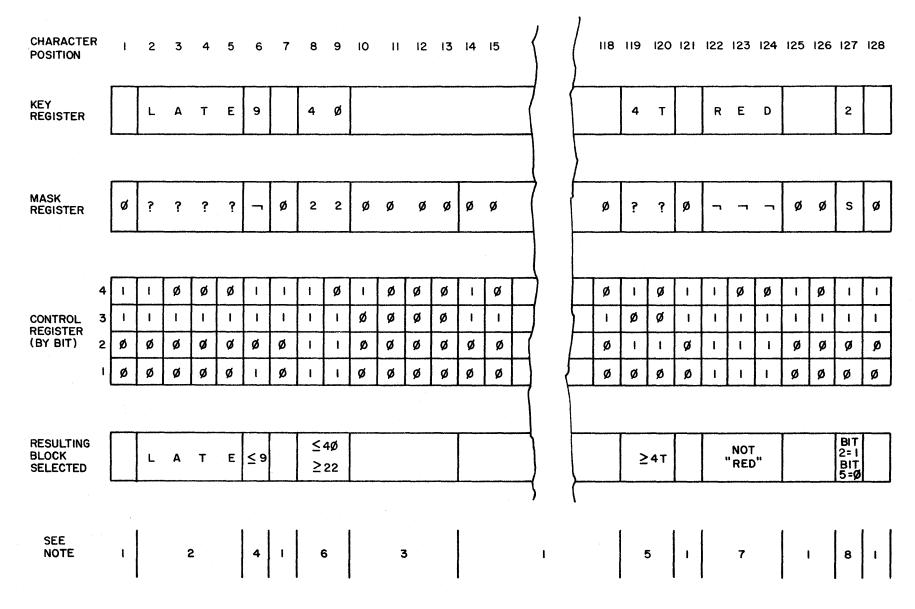

|    |       | 9.5.7   | Content Access                                    | 9-16 |

|    |       | 9.5.8   | Compare Flag Access                               | 9-20 |

|    |       | 9.5.9   | Multi-Block, First Qualify Access                 | 9-20 |

|    | 9.6   | TWIN    | MODE                                              | 9-22 |

|    | 9.7   | STAT    | US TOGGLES                                        | 9-22 |

|    |       |         | Overload                                          | 9-22 |

|    |       | 9.7.2   | Twin Compare (ZY=/S)                              | 9-22 |

| Section | IX (Cont' | d)                                            | Page    |

|---------|-----------|-----------------------------------------------|---------|

|         | 9.7.3     | Operative (ZY=/U)                             | 9-23    |

|         | 9.7.4     | Display Backup (ZY=34)                        | 9-23    |

|         | 9.7.5     | Interface Busy $(ZY=3#)$                      | 9-23    |

|         | 9.7.6     | Disc Memory Unit Busy (ZY=37)                 | 9-23    |

| 9.8     | WRITE     | INHIBIT SWITCHES                              | 9-25    |

| Section | Х         | DISC MEMORY OPERATIONS                        |         |

| 10.1    | FIXED A   | ADDRESS OPERATIONS                            | 10-2    |

|         | 10.1.1    | Fixed Address Read                            | 10-2    |

|         | 10.1.2    | Fixed Address Obsolete                        | 10-3    |

|         | 10.1.3    | Fixed Address Read and Obsolete               | 10-3    |

|         | 10.1.4    | Fixed Address Write                           | 10-4    |

| 10.2    |           | XED ADDRESS INDIVIDUAL BLOCK<br>FIONS         | 10-4    |

|         | 10.2.1    | Content Access Read                           | 10-4    |

|         | 10.2.2    | Content Access Read and Obsolete              | 10-5    |

|         | 10.2.3    | Content Access Obsolete and Count             | 10-5    |

|         | 10.2.4    | Content Access Count                          | 10-6    |

|         | 10.2.5    | Compare Flag Read                             | 10-6    |

|         | 10.2.6    | Compare Flag Read and Obsolete                | 10-7    |

|         | 10.2.7    | Obsolete Flag Write                           | 10-7    |

| 10.3    |           | XED ADDRESS MULTI-BLOCK<br>TIONS              | . 10-8  |

|         | 10.3.1    | Content Access Read Multi-Block               | 10-8    |

|         | 10.3.2    | Content Access Obsolete Multi-Block           | . 10-8  |

|         | 10.3.3    | Content Access Read and Obsolete Multi-Block. | 10-9    |

|         | 10.3.4    | Compare Flag Read Multi-Block                 | . 10-9  |

|         | 10.3.5    | Compare Flag Read and Obsolete Multi-Block .  | . 10-9  |

|         | 10.3.6    | Obsolete Flag Write Multi-Block               | . 10-10 |

| 10.4    | DISPLA    | Y BUFFER WRITE OPERATIONS                     | . 10-10 |

|         | 10 4 1    | MC Buffer Write                               | 10-10   |

| Section | X (Cont'd | 1)                                                   | Page          |

|---------|-----------|------------------------------------------------------|---------------|

|         | 10.4.2    | CP Buffer Write                                      | 10-11         |

| 10.5    | PREPA     | RE OPERATIONS                                        | 10-11         |

|         | 10.5.1    | Select Disc Memory Module                            | 10-11         |

|         | 10.5.2    | Load Key, Mask and Control                           | 10-12         |

| 10.6    | RETURI    | N OPERATIONS                                         | 10-12         |

|         | 10.6.1    | Return Disc Memory Operation                         | 10-12         |

|         | 10.6.2    | Return Key, Mask and Control Information             | 10-13         |

|         | 10.6.3    | Return Display Buffer Status                         | <b>10-1</b> 3 |

| Section | XI        | PROGRAM INTERRUPTS                                   |               |

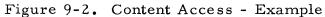

| 11.1    | INTERR    | UPT HIERARCHY                                        | 11-1          |

| 11.2    | IGNORE    | INTERRUPT TOGGLES                                    | 11-2          |

| 11.3    | INTERR    | UPT OPERATION                                        | 11-2          |

| 11.4    | INTERR    | UPT PROGRAM SELECTION                                | 11-3          |

| 11.5    | INTERR    | UPT PROGRAM EXIT                                     | 11-4          |

| 11.6    | FLAGGI    | ED RETURN ADDRESSES                                  | 11-4          |

| 11.7    | INTERR    | UPT CLASS: I/O INTERFACE (ZY=42)                     | 11-4          |

|         | 11.7.1    | Detail: Interface Not Busy (ZY=39)                   | 11-4          |

|         | 11.7.2    | Detail: L-119 Message Available (ZY=2,)              | 11-5          |

|         | 11.7.3    | Detail: Display Console Message<br>Available (ZY=2#) | 11-5          |

|         | 11.7.4    | Detail: Sending L-119 Available (ZY=2()              | 11-5          |

| 11.8    | INTERR    | UPT CLASS: REAL-TIME (ZY=43)                         | 11-5          |

|         | 11.8.1    | Detail: Real-Time Clock (ZY=3()                      | 11-5          |

|         | 11.8.2    | Detail: Interval Timer (ZY=3,)                       | 11-5          |

| 11.9    |           | UPT CLASS (AND DETAIL): OTHER<br>SSOR (ZY=44)        | 11-5          |

| 11.10   |           | UPT CLASS: DISC MEMORY INTERFACE                     | 11-5          |

|         | 11.10.1   | Detail: Interface Not Busy (ZY=2Y)                   | 11-6          |

|         |           | Detail: Disc Memory Unit Not Busy (ZY=2Z)            | 11-6          |

|         | 11.10.3   | Detail: Display (ZY=35)                              | 11-6          |

| Section | XI (Cont'd)                                                                                      | Page  |

|---------|--------------------------------------------------------------------------------------------------|-------|

| 11.11   | INTERRUPT CLASS: UNI-RECORD INTERFACE<br>(ZY=3W)                                                 | 11-6  |

|         | 11.11.1 Detail: Interface Not Busy (ZY=3Y)                                                       | 11-6  |

|         | 11.11.2 Detail: Operator (ZY=3Z)                                                                 | 11-6  |

| 11.12   | INTERRUPT CLASS: ERROR (ZY=41) -(COMPUTER,<br>DATA TRANSFER)                                     | 11-6  |

|         | 11.12.1 Detail: M Register Parity Error:<br>(ZY=V1)                                              | 11-7  |

|         | 11.12.2 Detail: R Register (ZY=V2)                                                               | 11-7  |

|         | 11.12.3 Detail: A Register (ZY=V3)                                                               | 11-7  |

|         | 11.12.4 Detail: Q Register (ZY=V4)                                                               | 11-7  |

|         | 11.12.5 Detail: Arithmetic (ZY=V5)                                                               | 11-7  |

|         | 11.12.6 Detail: R Repeater (ZY=V6)                                                               | 11-7  |

| 11.13   | INTERRUPT CLASS: ERROR (ZY=41) - (COMPUTER,<br>ARITHMETIC) · · · · · · · · · · · · · · · · · · · | 11-7  |

|         | 11.13.1 Detail: Overflow (ZY=W1)                                                                 | 11-8  |

|         | 11.13.2 Detail: F. P. Overflow (ZY=W2)                                                           | 11-8  |

|         | 11.13.3 Detail: Numerical (ZY=W3)                                                                | 11-8  |

|         | 11.13.4 Detail: Convert Overflow (ZY=W4)                                                         | 11-8  |

| 11.14   | INTERRUPT CLASS: ERROR (ZY=41) - (COMPUTER, PROGRAM)                                             | 11-8  |

|         | 11.14.1 Detail: Instruction (ZY=X1)                                                              | 11-8  |

|         | 11.14.2 Detail: Illegal Address (ZY=X2)                                                          | 11-9  |

|         | 11.14.3 Detail: End of Memory (ZY=X3)                                                            | 11-9  |

| 11.15   | INTERRUPT CLASS: Error (ZY=41) - INTERFACE,<br>DISC MEMORY)                                      | 11-9  |

|         | 11.15.1 Detail: Vertical Parity Interval<br>(ZY=/1)                                              | 11-9  |

|         | 11.15.2 Detail: Horizontal Check Interval<br>(ZY=/2)                                             | 11-10 |

|         | 11.15.3 Detail: Flag Parity (ZY=/3)                                                              | 11-10 |

|         | 11.15.4 Detail: Fixed Address $(ZY=/4)$                                                          | 11-12 |

|         | 11.15.5 Detail: M Register (ZY=/5)                                                               | 11-12 |

|         | 11.15.6 Detail: Write (ZY=/6)                                                                    | 11-12 |

Section XI (Cont'd)

| Section XI (Cont'd)                                               | Page           |

|-------------------------------------------------------------------|----------------|

| 11.15.7 Detail: Instruction (ZY=/7)                               | 11-13          |

| 11.15.8 Detail: Hang Up (ZY=/8)                                   | 11-14          |

| 11.15.9 Detail: Transmission Parity (ZY=/9)                       | 11-14          |

| 11.15.10 Detail: Out of Temperature (ZY=/=)                       | 11-15          |

| 11.15.11 Detail: Slow Down (ZY=/')                                | 11-15          |

| 11.15.12 Detail: Operand Address $(ZY=/>)$                        | 11-15          |

| 11.15.13 Detail: Count (ZY=36)                                    | 11-15          |

| 11.16 INTERRUPT CLASS: ERROR (ZY=41) -<br>(INTERFACE, I/O)        | 11 <b>-</b> 15 |

| 11.16.1 Detail: Parity (ZY=S1)                                    | 11-15          |

| 11.16.2 Detail: M Register (ZY=S2)                                | 11-16          |

| 11.16.3 Detail: Hang Up (ZY=S3)                                   |                |

| 11.16.4 Detail: Operand Address (ZY=S4)                           | 11-16          |

| 11.17 INTERRUPT CLASS: ERROR (ZY=41) - (INTERFACE,<br>UNI-RECORD) | 11-16          |

| 11.17.1 Detail: On Line Data (ZY=T1)                              | 11-16          |

| 11.17.2 Detail: On Line Evesdrop (ZY=T2)                          | 11-16          |

| 11.17.3 Detail: On Line Mechanical (ZY=T3)                        | 11-17          |

| 11.17.4 Detail: M Register Parity Error (ZY=T4)                   | 11-17          |

| 11.17.5 Detail: Horizontal Check (ZY=T5)                          | 11-17          |

| 11.17.6 Detail: Instruction (ZY=T6)                               | 11-17          |

| 11.17.7 Detail: Overload (ZY=T7)                                  | 11-17          |

| 11.17.8 Detail: Real World Parity (ZY=T8)                         | 11-17          |

| 11.17.9 Detail: Real World Mechanical (ZY=T9)                     | 11-17          |

| 11.17.10 Detail: Device Unavailable ( $ZY=T^>$ )                  | 11-17          |

| 11.17.11 Detail: Operand Address ( $ZY=T<$ )                      | 11-18          |

| Section XII DUPLEXING                                             |                |

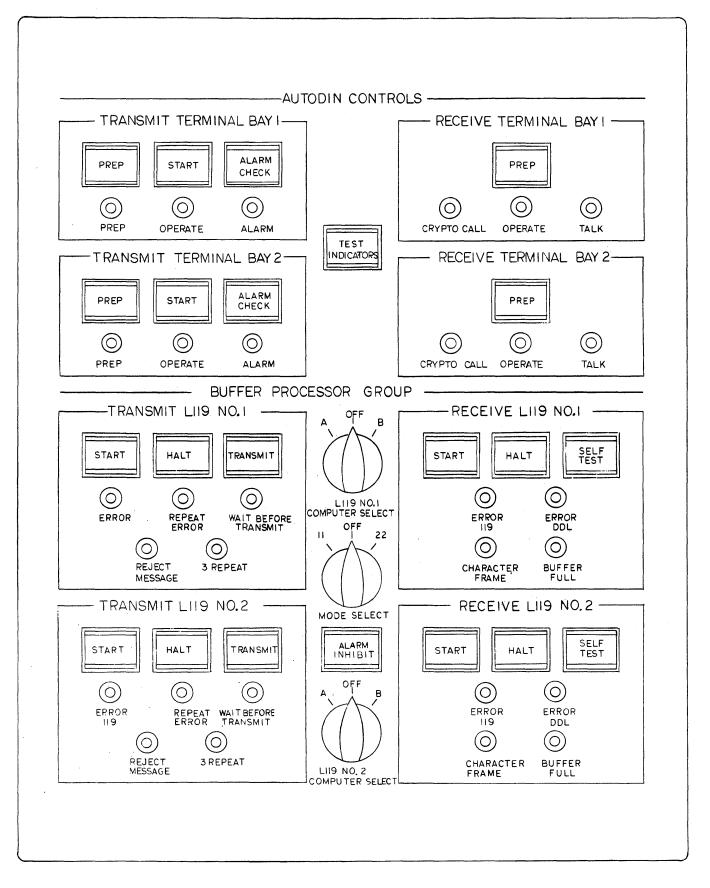

| 12.1 BUFFER PROCESSOR SWITCHING                                   | 12-1           |

| 12.1.1 Receiving L-119 Module Controls                            | 12-1           |

| 12.1.2 Sending L-119 Module Controls                              | 12-4           |

| 12.1.3 L-119 Module Pair Controls                                 | 12-4           |

| Section | XII (Cont | 'd)                                                          | Page          |

|---------|-----------|--------------------------------------------------------------|---------------|

|         | 12.1.4    | Receiving L-119 Module Indicators                            | 12-5          |

|         | 12.1.5    | Sending L-119 Module Indicators                              | 12-6          |

|         | 12.1.6    | Testable L-119 Module Control Switches                       | 12-7          |

|         | 12.1.7    | L-119 Module Operation from the Central<br>Switching Console | 12-8          |

|         | 12.1.8    | Audible Alarm                                                | 12-9          |

|         | 12.1.9    | Test Indicators Button                                       | 12-10         |

| 12.2    | AUTOD     | IN REMOTE CONTROLS                                           | 12-10         |

|         | 12.2.1    | Sending Crypto Controls                                      | 12-10         |

|         | 12.2.2    | Receiving Crypto Controls                                    | 12-11         |

|         | 12.2.3    | Control Switch and Indicator Power                           | 12-11         |

|         | 12.2.4    | Operation of Autodin Controls                                | 12-11         |

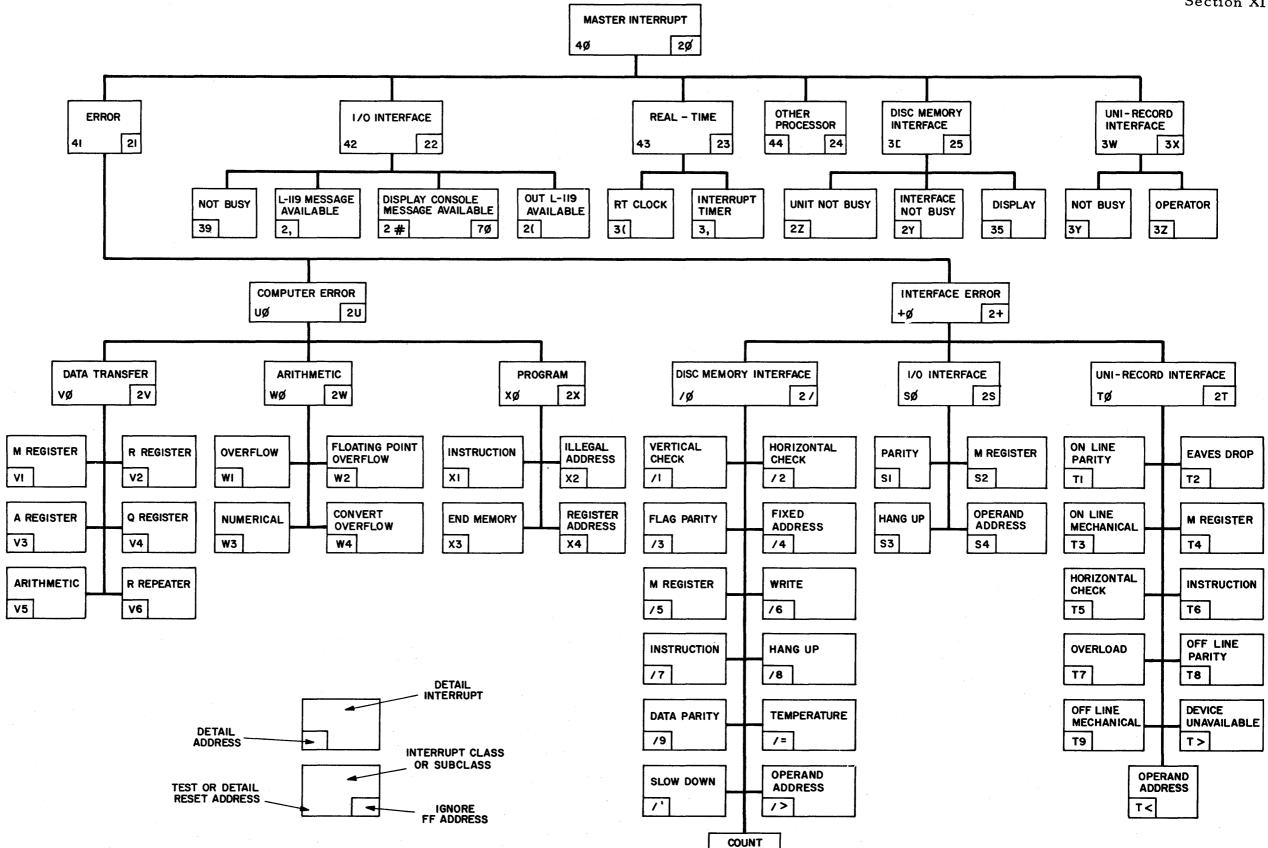

| 12.3    | INTEGR    | RATED CONSOLE SWITCHING                                      | <b>12-1</b> 3 |

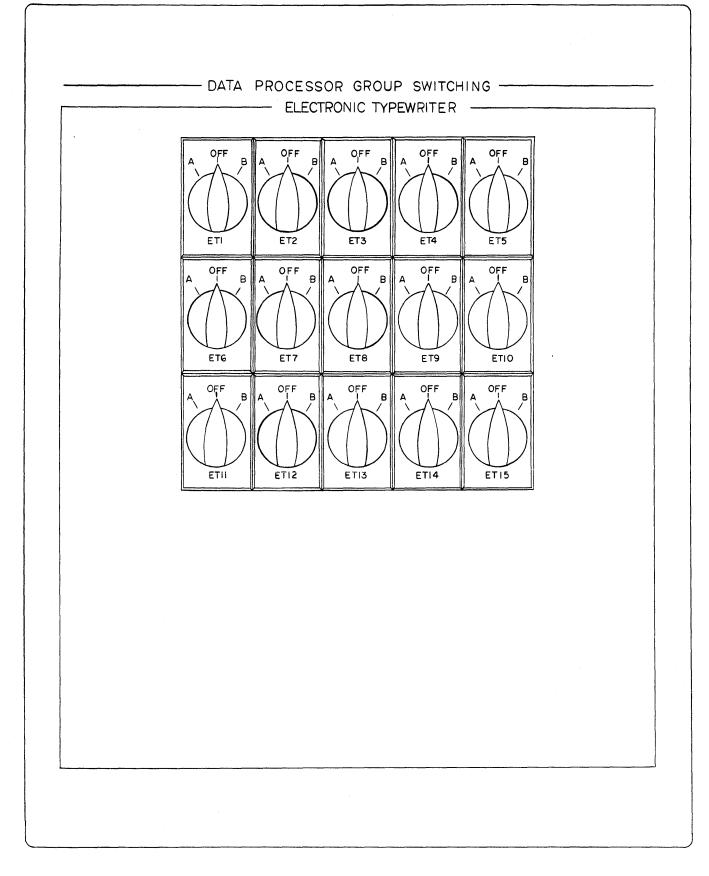

|         | 12.3.1    | Electronic Typewriter Switching                              | <b>12-1</b> 3 |

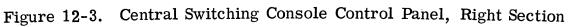

|         | 12.3.2    | Display and Console Printer Switching                        | 12-14         |

| 12.4    | DISC M    | EMORY TRUNKLINE                                              | 12-20         |

|         | 12.4.1    | Control Status Toggle                                        | 12-20         |

|         | 12.4.2    | Disc Memory Trunkline Coupling<br>Mode Toggle                | 12-20         |

|         | 12.4.3    | Other Disc Memory Busy                                       | 12-20         |

| Section | XIII      | CONTROL CONSOLE AND CENTRAL<br>PROCESSOR CONTROL PANEL       |               |

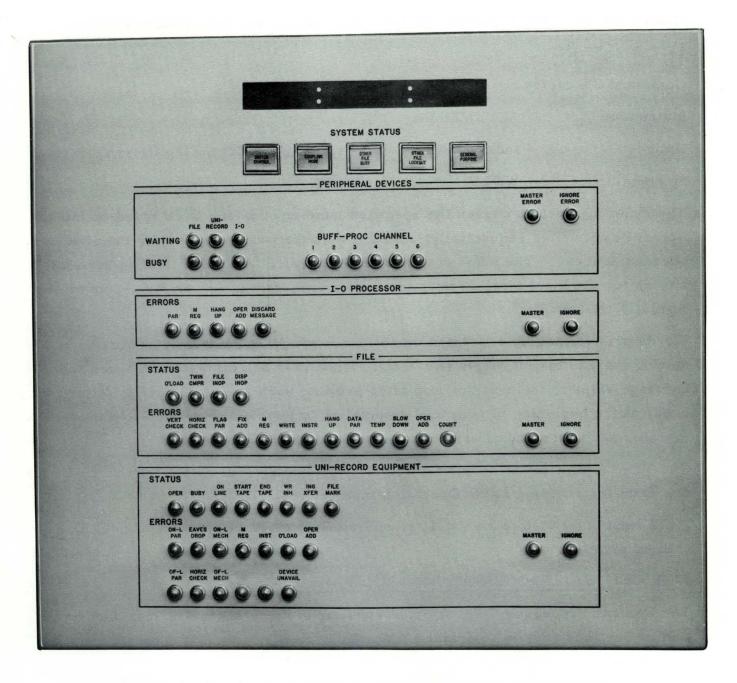

| 13.1    | CONTRO    | OL CONSOLE CONTROL PANEL                                     | 13-1          |

| 13.2    | CONTRO    | OL TYPEWRITER                                                | 13-6          |

|         | 13.2.1    | Manual Input                                                 | 13-6          |

|         | 13.2.2    | Typewriter Instructions                                      | 13-6          |

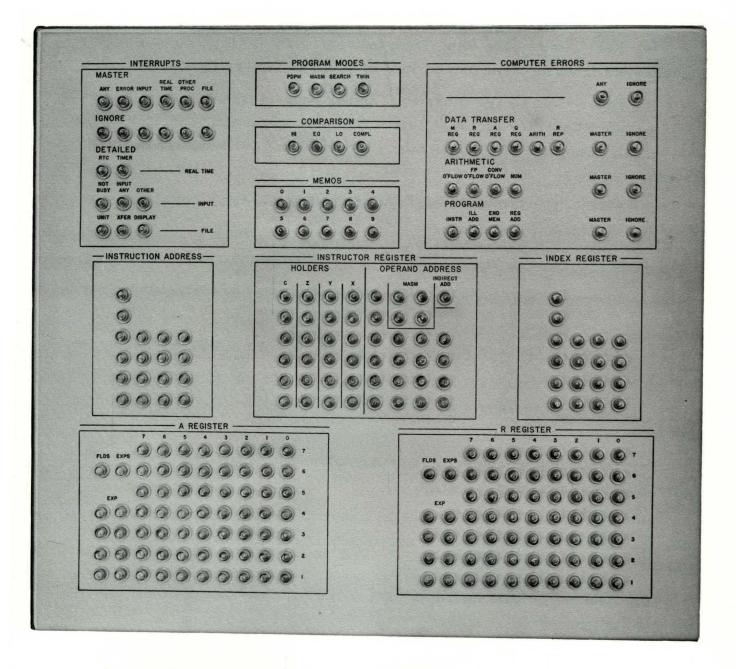

| 13.3    | CENTRA    | AL PROCESSOR CONTROL PANEL                                   | 13-7          |

|         | 13.3.1    | Left Section Indicators                                      | 13-7          |

|         | 13.3.2    | Center Section Indicators                                    | 13-14         |

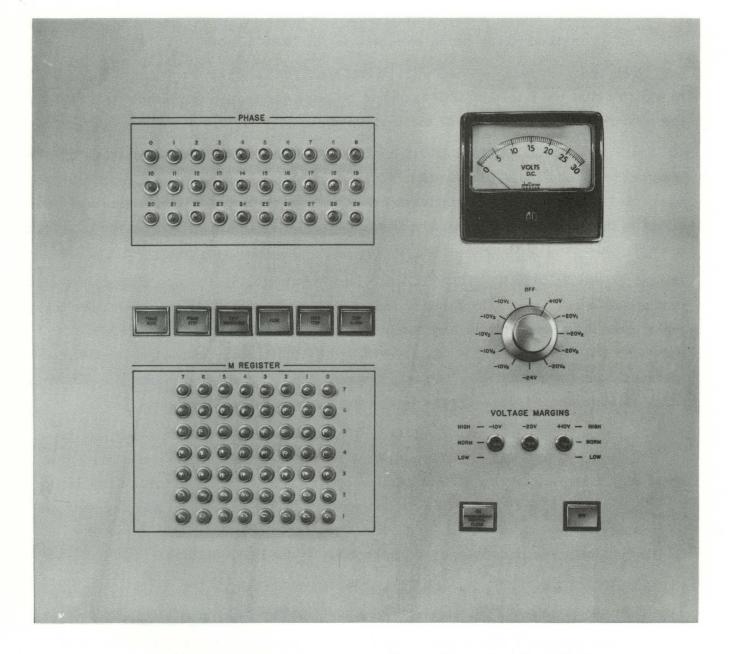

|         | 13.3.3    | Right Section Controls and Indicators                        | 13-21         |

| Section X | IV REAL-DASH TIME CLOCK AND<br>INTERVAL TIMER | Page          |

|-----------|-----------------------------------------------|---------------|

|           | REAL-DASH TIME CLOCK                          | 14-1          |

| 14.2      | INTERVAL TIMER                                | 14-1          |

| Section X | DISPLAY CONSOLES                              |               |

| 15.1      | ELECTRONIC TYPEWRITER ET                      | 15-2          |

|           | 15.1.1 Input Messages                         | 15-2          |

|           | 15.1.2 Output Messages                        | <b>15-</b> 3  |

| 15.2      | LOGIC KEYBOARD ASSEMBLY LKB                   | 15-4          |

| 15.3      | MULTI COLOR DISPLAY MC                        | 15-4          |

| 15.4      | CONSOLE PRINTER CP                            | 15-5          |

| 15.5      | HARDCOPY ASSEMBLY HC                          | 15 <b>-</b> 5 |

## ILLUSTRATIONS

| Figure |                                                           | Page  |

|--------|-----------------------------------------------------------|-------|

| 1-1    | Data Processor Set AN/FYQ-11                              | 1 - 0 |

| 1-2    | AN/FYQ-11 Data Flow and Switching Control Diagram         | 1-3   |

| 2-1    | Memory Address Selection Patchboard                       | 2-4   |

| 2-2    | Information Word Format                                   | 2-6   |

| 2-3    | Instruction Word Format                                   | 2-10  |

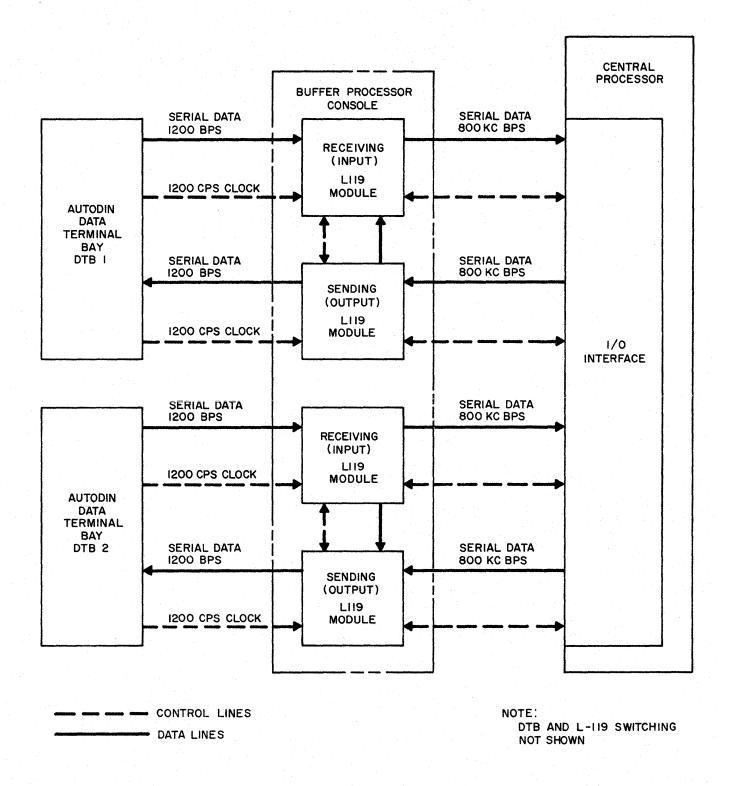

| 6 - 1  | Buffer Processor Console Functional Configuration         | 6-2   |

| 6-2    | C or T Select Message Format                              | 6-3   |

| 6-3    | Single Block Input Message Format                         | 6-5   |

| 6-4    | Multi-Block Input Message Format                          | 6-6   |

| 6-5    | Single Block Output Message Format                        | 6-8   |

| 6-6    | Multi-Block Output Message Format                         | 6-9   |

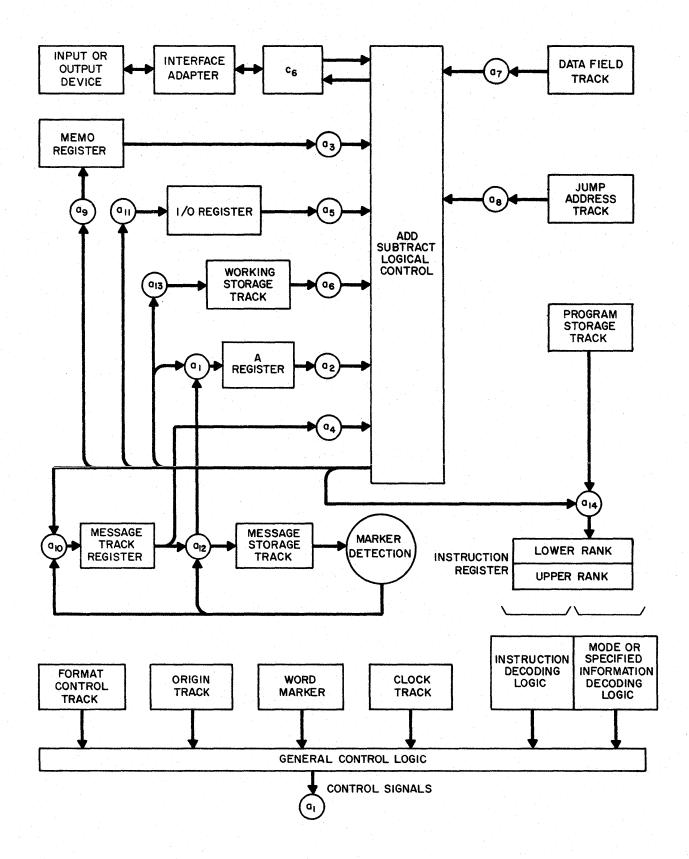

| 6-7    | L-119 Block Diagram                                       | 6-12  |

| 6-8    | Buffer Processor Maintenance Panel                        | 6-26  |

| 7 - 1  | Uni-Record Device ZY Addresses                            | 7-5   |

| 8 - 1  | Magnetic Tape Console Control Panel                       | 8-10  |

| 8-2    | Card Flow Diagram                                         | 8-18  |

| 8-3    | Card Reader/Punch Control Panel                           | 8-25  |

| 8-4    | Line Printer Control Panel                                | 8-35  |

| 9-1    | Index-Data-Fixed Address-Flag Format                      | 9-3   |

| 9-2    | Content Access - Example                                  | 9-21  |

| 10-1   | Display Buffer Status Word                                | 10-15 |

| 11-1   | Interrupt Hierarchy                                       | 11-19 |

| 12-1   | System Switching Configuration                            | 12-2  |

| 12-2   | Central Switching Console Control Panel, Center Section . | 12-3  |

## ILLUSTRATIONS - Continued

| Figure | Page                                                         |

|--------|--------------------------------------------------------------|

| 12-3   | Central Switching Console Control Panel, Right Section 12-16 |

| 12-4   | Central Switching Console Control Panel, Left Section 12-17  |

| 12-5   | Switching Status Work (ZY17)                                 |

| 13-1   | Control Console Control Panel                                |

| 13-2   | Central Processor Control Panel, Left Section 13-8           |

| 13-3   | Central Processor Control Panel, Center Section 13-15        |

| 13-4   | Central Processor Control Panel, Right Section 13-22         |

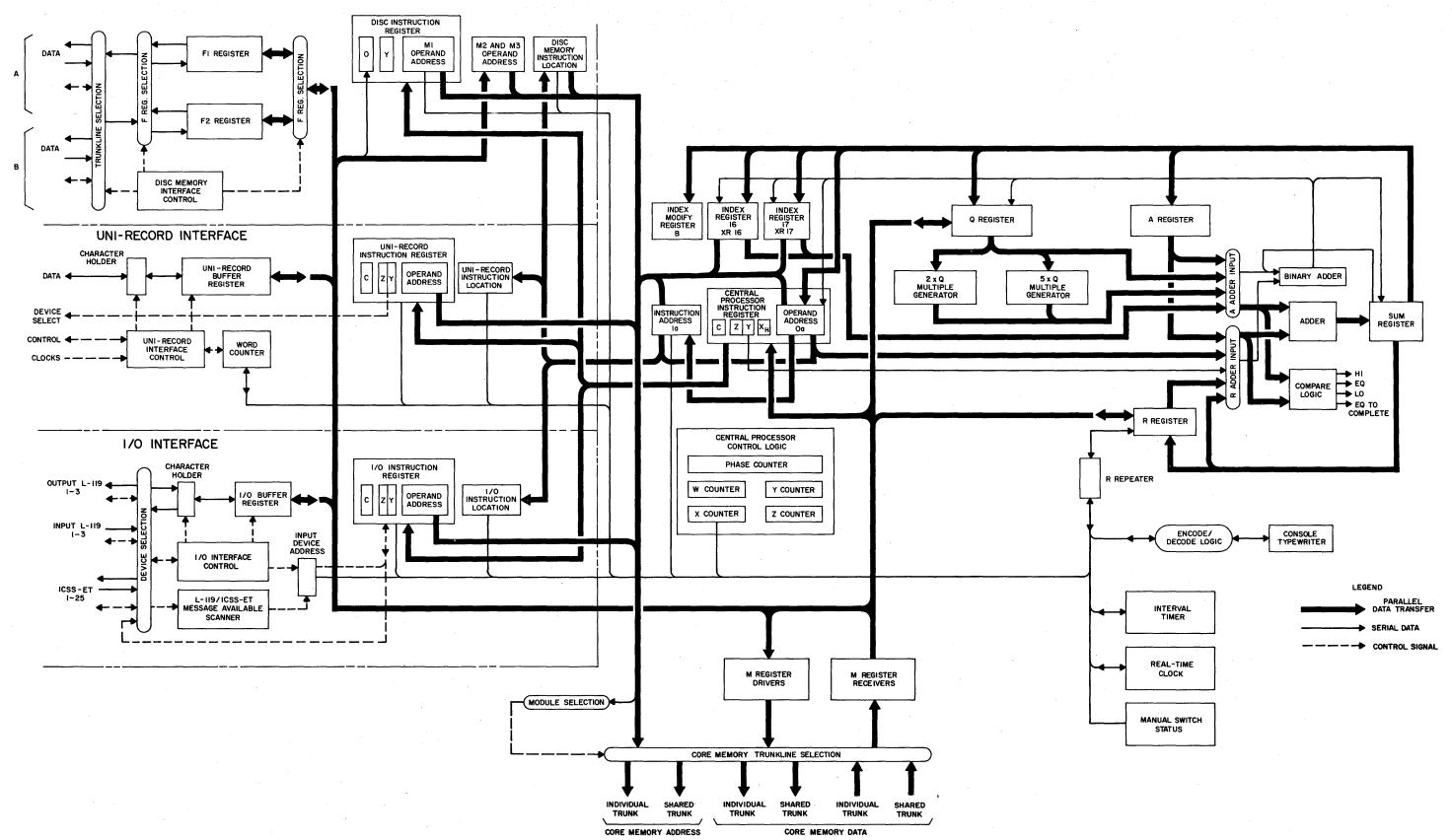

| E-1    | Central Processor Functional Block Diagram E-3               |

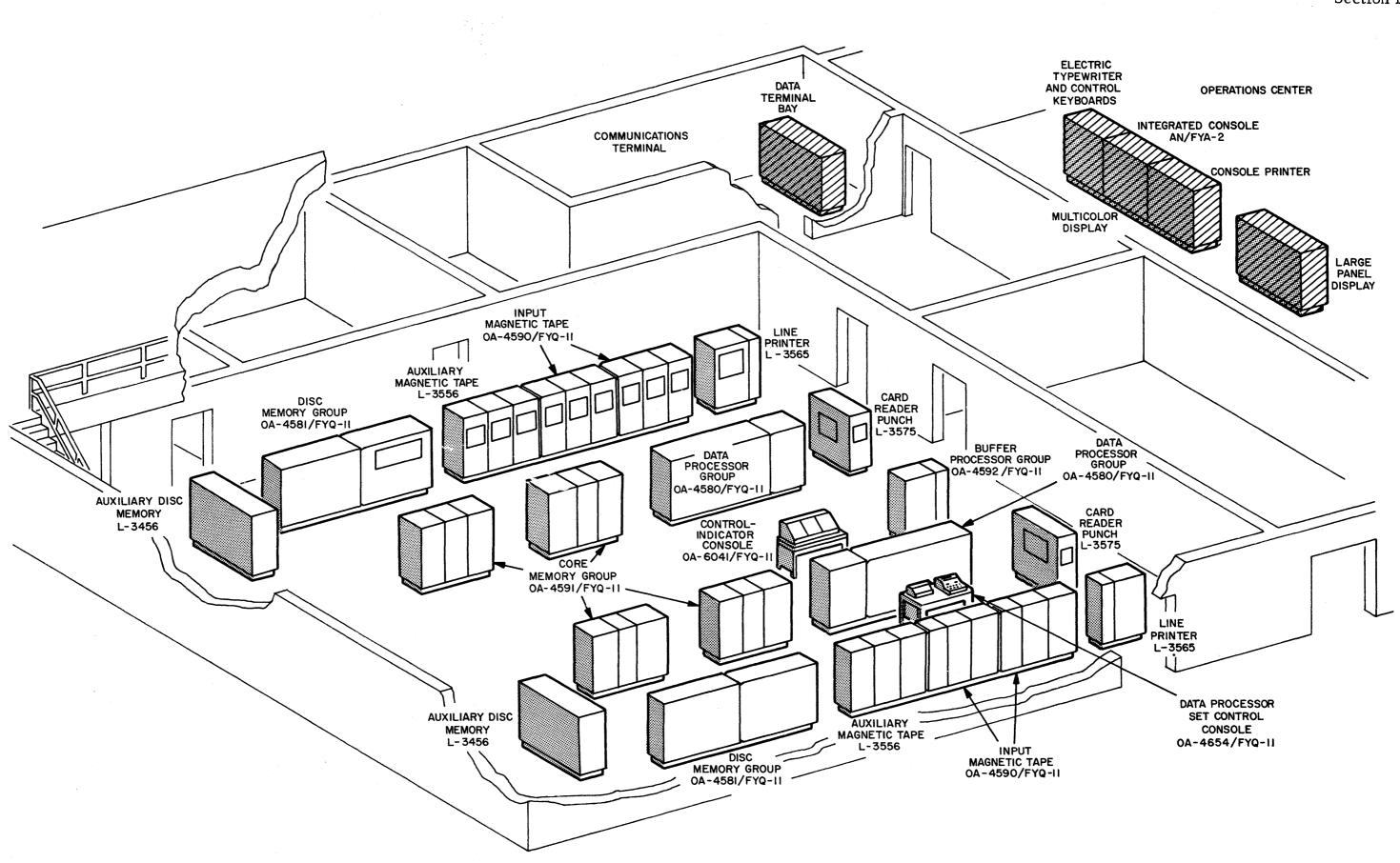

Figure 1-1. Data Processor Set AN/FYQ-11

#### SECTION I

#### INTRODUCTION

This publication is the Programmers Reference Manual for an L-3055 Data Processing System used as the Data Processor Set AN/FYQ-11, figure 1-1, a subsystem of the 473L Command and Control System. Content of the manual is orientated around system functional information that is needed for programming. This manual consists of 15 sections that are bound in one volume.

The system described is the Complete Operating Capability (COC) for Data Processor Set AN/FYQ-11. The Data Processing System operates with the Integrated Console Subsystem, Large Panel Display Subsystem and Data Communications Subsystem (AUTODIN) to provide large scale automatic processing, display and transmission of information. On-line and off-line magnetic tape, card reader/ punch, and line printer operations are provided by the system.

#### 1.1 SYSTEM FUNCTIONS.

The Data Processing System consists of on-line, real-time general purpose alphanumeric data processing equipment that performs arithmetic, logical, storage, control, and retrieval operations on various inputs and stored data to produce outputs under program, operator, and automatic control. This data processing equipment maintains control of data by acquisition, filing, distribution, transmission, and monitoring.

The Data Processing System provides for inputs through digital data links, integrated console typewriters, a control console, a card reader, and magnetic tapes. Outputs are provided through integrated console typewriters, integrated console printer, integrated console displays, large panel displays, line printer, control console typewriter, card punch, magnetic tapes, and digital data links.

The basic functions of input-output, data processing and storage are performed by the four major elements of the system:

a. Central Processor, Control Console, and Core Memory.

b. Buffer Processors for real-time inputs from digital data links, and outputs to digital data links.

Section I Paragraph 1.1

c. Uni-Record devices consisting of Magnetic Tape Consoles, Card Reader/ Punch, and Line Printer.

d. Disc Memory for fixed address or content-access operations and integrated console buffer storage.

Equipment items of the Data Processing System are listed in table 1-1.

#### Table 1-1. L-3055 Data Processing Equipment Used as Data Processor Set AN/FYQ-11

| IOC      | COC | NOMENCLATURE                                                                            |

|----------|-----|-----------------------------------------------------------------------------------------|

| <b>1</b> | 2   | Data Processor Group OA-4580/FYQ-11 (Central<br>Processor L-3155)                       |

| 1        | 2   | Disc Memory Group OA-4581/FYQ-11 (Disc Memory<br>L-3455)                                |

| 1        | 1   | Buffer Processor Group OA-4592/FYQ-11 (Buffer<br>Processor Console, four L-119 Modules) |

| 2        | 4   | Input Magnetic Tape OA-4590/FYQ-11 (Magnetic Tape<br>Console L-3555)                    |

| <b>1</b> | 4   | Core Memory Group OA-4591/FYQ-11 (Core Memory<br>L-3755)                                |

| 1        | 2   | Console, Data Processor Set Control OA-4654/FYQ-11<br>(Control Console L-3855)          |

| 0        | 1   | Console, Control-Indicator OA-6041/FYQ-11 (Central Switching Console L-3655)            |

| 1        | 2   | Card Reader/Punch L-3575                                                                |

| 1        | 2   | Line Printer L-3565                                                                     |

| 1        | 2   | Auxiliary Disc Memory L-3456                                                            |

| 1        | 2   | Auxiliary Magnetic Tape L-3556                                                          |

|          |     |                                                                                         |

Data furnished by Digital Data Links is available for computation, retrieval, and display under automatic control of stored programs and upon manual request. The system performs computations on the data, arranges the format, updates stored data, and presents the result to Integrated Consoles, Large Panel Displays, or

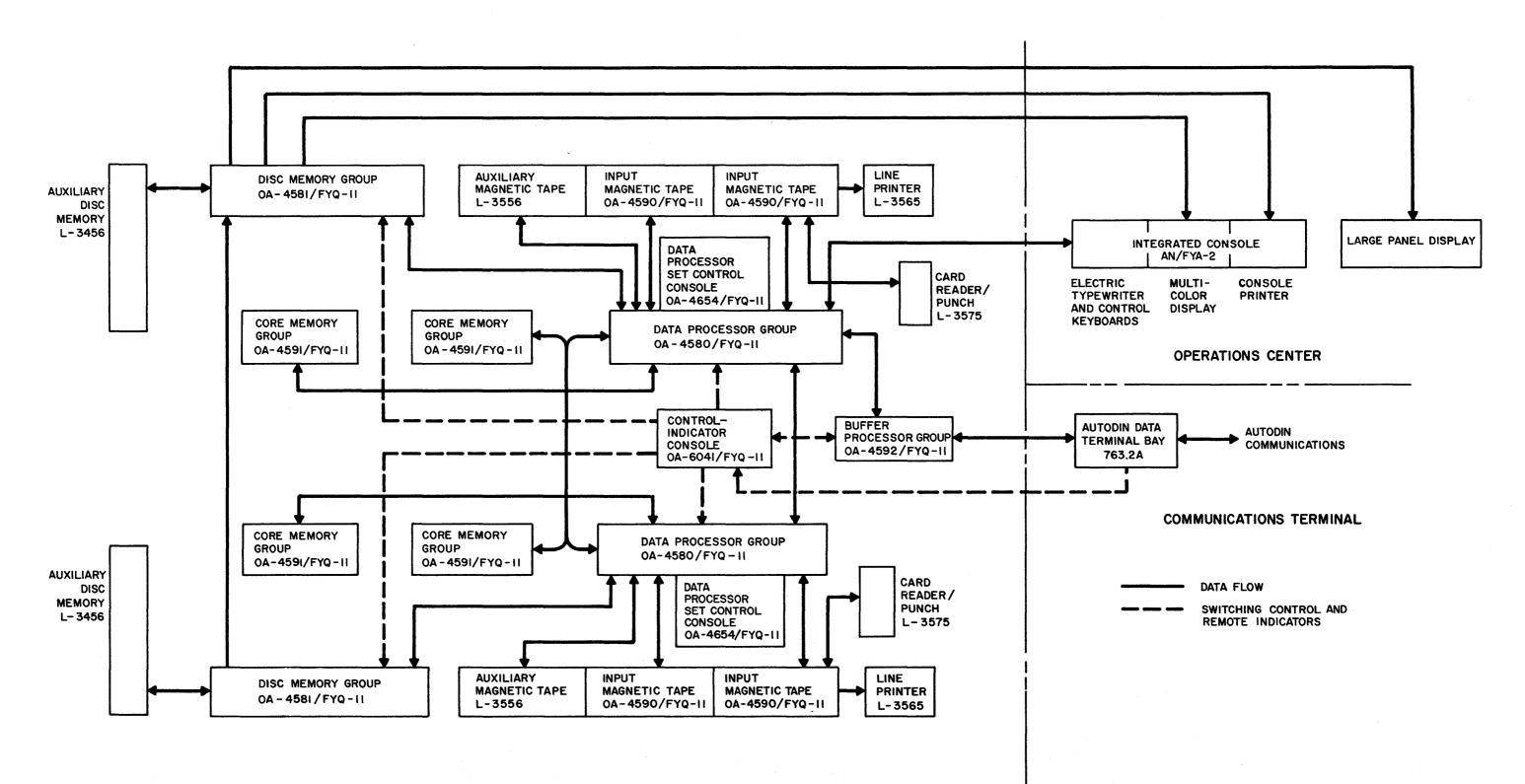

Figure 1-2. AN/FYQ-11 Data Flow and Switching Control Diagram

1-3/1-4

Digital Data Links. Programs control the execution of the functions required for the operational tasks. A control program supervises the reception of messages which are to be decoded and processed for transmission or display.

Rapid processing and retrieval of a wide variety of information as well as the execution of specific programs requires close interaction between manpower and the system. Considerable scheduling and system control is necessary to establish priorities, eliminate unnecessary delays, and perform the processing operations on a dynamic real-time basis. Characteristics of the units, the data peripheral devices, and programming must be understood by personnel responsible for the programming and operation.

The Data Processing System communicates electronically with units of the system and peripheral equipment by means of trunklines, buffers, and interfaces, figure 1-2. The Disc Memory Trunkline provides for communication between the Central Processor and Disc Memory. The Uni-Record Trunkline provides for data transfer and control between the Central Processor and the Magnetic Tape Console. The Tape Transports, Line Printer, Card Punch, and the Card Reader are the Uni-Record devices which are addressed by appropriate input or output instructions. The I/O Interface provides for data transfer between the Buffer Processor or an Integrated Console Electronic Typewriter, and the Central Processor. The I/O Interface in the Central Processor selects the particular Buffer Processor Module or Integrated Console Typewriter, and designates the operation to be performed.

#### 1.2 SYSTEM FEATURES.

The Central Processor operates in parallel on words of eight alphanumeric characters. The magnetic Core Memory is modularly expandable up to 64,000 words. The Disc Memory, utilizing large discs, offers both fixed address and content access. The real-time interface provides time shared memory operation, as well as buffering, and separately programmed data-link operation. A Uni-Record Trunkline handles magnetic tapes, punched card equipment and a line printer.

All data transfers are parity checked, with provision for programmed error recovery. Multiplexing of all major system elements permits maintenance with reduction, but not loss, of capability.

The program interrupt feature gives the necessary response to real-time data transfer demands. Data transfers, both input/output and with Disc Memory, have their completion signaled to the program by an interrupt.

Section I Paragraphs 1.3 to 1.4

The entire Data Processing System has been organized to provide ease of programming, speed of operation, reliability, and general purpose flexibility.

#### 1.3 CENTRAL PROCESSOR.

The Central Processor has an alphanumeric character organization with decimal memory addressing. The computer word of eight characters provides variable field flexibility with fixed word simplicity. Single address instructions specify a required field within any memory or register word for most operations.

There are 43 basic commands, including input and output. Control characters and flags within the instruction word extend the range of program operations. Automatic index modification is provided with all commands that specify an operand or next-instruction address. Two Index registers are static and 15 more are in the Core Memory. Indirect addressing and indirect instruction execution, with index modification, is provided.

The Central Processor may use the Core Memory in either of two special modes, PDPM (Push-Down, Pop-Up Memory), and MASM (Multi-Address Stacking Mode). Programmed memory comparisons may range over regions of Core Memory word by word, or on a character field basis, independent of word boundaries.

The Central Processor operates at a clock frequency of 1.5 megacycles. Data transfers with the Core Memory are full-word parallel, while most other operations between registers (including addition) are in half-word parallel. Typical operation times including instruction and operand access are: addition (non-indexed) 10.5 microseconds; full word multiplication 25.0 microseconds; indexing, an additional 2.0 microseconds (static); 5.0 microseconds (from core).

#### 1.4 CORE MEMORY.

The five-microsecond cycle time magnetic Core Memory is provided in modules of 4000 words of 56 bits each. Module addresses are patched in the Central Processor. Each Central Processor may address 64,000 words of memory, of which 32,000 words can be shared between two Central Processors.

A special twinning feature allows duplicate writing in a pair of individual (nonshared) memory modules.

Transfers to and from the Core Memory are word parallel, and are parity checked. The memory is time shared within the Central Processor by the real-time, Disc Memory, Uni-Record interfaces and the program control, permitting continued program execution while interface operations are in progress.

A special feature allows partial overlap of core memory cycles in separate modules, reducing the effective cycle time.

#### 1.5 DISC MEMORY.

Disc storage is provided by central Disc Memory modules and by Auxiliary Disc Memory modules. Each disc module contains a storage capacity of about 20 million alphanumeric characters, organized into blocks of 128 characters (16 Data Processor words). Large discs rotate at approximately 14 revolutions per second, and utilize a full complement of fixed heads rather than moving heads. The access time is, therefore, a direct function of the revolution rate.

A Central Processor can be switched to one of two Disc Memory trunklines, and a trunkline can service up to seven central Disc Memory modules. Each module provides a Control Section and a fast buffer for transfers to and from the Central Processor. A Disc Memory module may, in turn, control up to seven Auxiliary Disc Memory modules, each of which also contains 20 million characters of storage but provide no Control Section or buffer storage. There may be a total of seven Central Modules and 49 Auxiliary Modules of disc storage with each Data Processor, permitting over 1 billion characters of file storage.

The Disc Memory Control Section has the important capability of accessing data by content, in addition to the standard fixed address read and write operations. A search may be specified on any combination of bit, character, and field positions in each block. Once started, the search operation continues without Central Processor intervention, and up to 1350 blocks can be compared per disc revolution. Also the Disc Memory can tag specified blocks as obsolete, and new data may then be loaded into the first available obsolete spaces, thereby reducing store access time. These blocks can be retrieved with a search by content, which, under program option, can also provide the fixed address locations.

#### 1.6 REAL-TIME COMMUNICATION.

Buffer Processors are provided to maintain communication with a Data Terminal Bay, and to buffer, code-convert, and format check data. These communicate with the Central Processor through an I/O Interface, which also handles data transfers to and from Display Console Electronic Typewriters.

#### Section I Paragraphs 1.7 to 1.8

The Buffer Processors execute their own internally stored programs. One, with appropriate program, is needed for incoming data, and another for outgoing data. Programs and data are stored on a 8000 revolution per minute magnetic disc.

The Display Consoles also have a sizeable buffer storage area as part of the Disc Memory for outgoing data.

The Central Processor I/O Interface has a control section that executes operations in parallel with program execution. This I/O Interface scans input devices, Buffer Processors and Display Consoles, signaling the Central Processor with an interrupt when a message is available.

Data transfers are bit serial at a rate (over 700, 000 bits per second) set by the communicating devices, and are character parity checked.

#### 1.7 UNI-RECORD FACILITIES.

The Central Processor has a Uni-Record Interface which has a character-serial trunkline. This trunkline handles magnetic tape transports, punched card readers and punches, and line printers. The Uni-Record Interface has its own control section which can execute operations, once started, in parallel with program execution. Data transfers are character parity checked.

The Uni-Record Trunkline has the capability of off-line operations, namely, tapeto-card, card-to-tape, tape-to-line printer and card-to-line printer, under manual control.

#### 1.8 CHECKING FEATURES.

Reliability has been a primary aim in the data processing system design. When errors occur, they are caught by the character parity check that accompanies every data transfer by the Central Processor. Where possible, illegal characters are regarded as errors, such as in arithmetic operations and in memory addresses.

As part of the Disc Memory, I/O, and Uni-Record Interface operations, the Central Processor program receives an interrupt signal upon remote detection of parity error in data transfers either way. Under program control, an override of the automatic termination of data transfers upon error detection is provided as an aid in error corrections.

Blocks, as stored in the Disc Memory, have the character parity bits stripped from them, but longitudinal parity bits substituted, for reasons of speed and economy. Character parity is regenerated during transfer to the Central Processor. A basic protection of stored data is provided by using the duplexed system to duplicate operations and stored data. This concept is carried to a finer level by the feature called "twinning", available both in Core Memory and Disc Memory. Information is simultaneously stored in duplicate when in twin mode. In event of failure of one read operation, the second copy is still available.

The normal result of a sensed error is a program interrupt, unless this interrupt is ignored. The interrupt program can test for the detailed source of the error to take remedial action.

#### 1.9 DUPLEXING.

In a duplexed or multiplexed system, system functioning can be maintained by a single Central Processor. Program controlled cross connections are provided between Central Processors and Disc Memory Trunklines.

Each Display Console can be switched manually to either side of a duplex system. Similarly, Buffer Processors may be switched, and have duplicate standby equipment available.

Each Central Processor is able to test by program the state of each switch. In addition, special communication is available between Central Processors for programmed switching.

#### 1.10 PROGRAM INTERRUPTS.

The Central Processor has an elaborate set of program interrupts. These provide a transfer of control to special programs which determine and deal with the causes of the interrupts and then resume normal program execution.

There are six classes of interrupts, each with an independent special program starting point. These classes are: Error, Disc Memory, Input, Real Time, Uni-Record, and Other Processor. Within each class are several detail interrupt sources which are program testable.

The Error class of interrupts has two divisions, Computer Error, which includes data transfer, arithmetic and program errors, and Interface Error, which includes Disc Memory, I/O Interface, and Uni-Record Interface errors.

The other classes of interrupts contain signals generated when specific action is to be taken as, for instance, when an interface finishes a data transfer operation.

All detail interrupt requests are stored in toggles which are reset by program individually or by class, and which can also be set by program.

Section I Paragraph 1.10

Other toggles, under program control, permit ignoring interrupt requests by class, subclass, or totally, but without losing the interrupt requests which remain program testable.

#### SECTION II

#### CORE MEMORY AND WORD FORMAT

Core Memory for the Data Processing System is provided in modules of 4000 words. These modules may be assigned to a Central Processor on an individual basis, or may be connected to two Central Processors via a shared memory trunkline. The assignment of module addresses is by a patchboard, which has the additional facility of pairing modules in the Twin mode.

#### 2.1 MEMORY REGISTERS.

#### 2. 1. 1 MEMORY ADDRESS REGISTER.

Words in each Core Memory module have decimal addresses of  $\emptyset \emptyset \emptyset \emptyset$  through 3999. Each module has an address register which is loaded in parallel via the trunk from the Central Processor, while the high order bits of the high order character of the address perform module selection through the patchboard. (In some units, two modules share a common address register.) The Memory Address register appears to the Central Processor as a single register. The Memory Address register receives word addresses in parallel from the Program Control Section and the Disc Memory, Uni-Record and I/O Interfaces. Parity is not checked, but an error is indicated when a non-existing memory module is addressed.

#### 2.1.2 MEMORY ACCESS REGISTER (M).

Each Core Memory module has an eight-character (full word) M register. (In some units, two modules share a common M register.) Transfers to or from Core Memory are full word parallel, via the trunkline which appears to the Central Processor as a single Memory Access Register, which is displayed on the Central Processor Control Panel. All transfers are character parity checked.

Memory cycle time is 5 microseconds, and data is on the trunkline 2.5 microseconds after the start of the cycle. For some operations Core Memory is half cycled for read only or write only. For instance, a half cycle write is performed when an address of four characters is to be stored into a word of memory, leaving the rest of the word unchanged. The effect is a saving of time where, otherwise, two full memory cycles would be needed; a read-restore, and a clear-write. The sequence is half cycle read, modify, half cycle write. Half cycling is under tight logical control so that, even under error conditions, no information will ever be lost. Other than effects on timing, programming is not involved in half cycling by any possibilities of over-writing or inadvertently clearing portions of memory.

A special feature allows overlap of memory cycles in different Core Memory modules. The overlap gives an effective cycle time of about 4 microseconds. This cycle overlap is particularly effective in unrelated operations, such as the memory cycles requested by interfaces and their effect on normal program execution.

#### 2.2 SPECIAL FEATURES.

#### 2.2.1 CYCLE DEMAND PRIORITY.

The Disc Memory, I/O, and Uni-Record Interfaces operate independently of, and simultaneously with, the Program Control Section. Any or all may be requesting a memory cycle. A precedence occurs at logic level giving priorities as follows:

- a. I/O Interface.

- b. Disc Memory Interface.

- c. Uni-Record Interface.

- d. Program Control Section.

Central Processor program instruction execution can wait the most easily, and is given the lowest priority.

#### 2.2.2 INDIVIDUAL MEMORY TRUNKLINE.

Each Central Processor has an individual Memory Trunkline which can service up to eight memory modules. The assignment of a module to a Trunkline is done physically by attaching cables.

Memory modules are contained in cabinets that hold up to four modules and two sets of Trunkline Drivers. Each Trunkline Driver can connect one Trunkline with up to three memory modules. Pairs of modules which share common Address and M registers cannot be connected to separate Trunklines.

2.2.3 SHARED MEMORY TRUNKLINE.

Each Central Processor has a Shared Memory Trunkline. A single Central Processor can service up to eight additional memory modules via this Trunkline. Two such Trunklines from two Central Processors can be connected together through a Shared Memory Switch built into the memory cabinet, and a total of up to eight

memory modules can be distributed on either side of the switch. When the Shared Memory Switch is closed, a single Shared Memory Trunkline is formed, servicing all of the memory modules on either side of the switch, and only one Central Processor has preemptive use of the Trunkline. That Central Processor also has exclusive program control of the switch. When the switch is open, each Central Processor can independently access the memory modules on its side of the switch.

Either Central Processor can control the Shared Memory Switch, and have access to all of the Shared Memory, and that Central Processor has Control Status. Control Status is indicated to each Central Processor by its Control Status toggle, which can be program tested (ZY = 59) and reset, but not set. The Control Status toggles in the two Central Processors are cross connected so that, when one is reset by program, the other is set, which transfers Control Status. Control Status also has an effect on the control of Disc Memory Duplexing, (Section XII).

Each Central Processor has a program testable, settable, and resettable toggle (ZY = 31) that requests opening and closing of the Shared Memory Switch. Only the Request Memory Switch toggle in the Central Processor that has Control Status, affects the Shared Memory Switch. The Shared Memory Switch status is separately testable (ZY = 32). Switching will follow within 10 microseconds after changing the Request toggle.

When one Central Processor is shut down, the other has full use of Shared Memory and the Shared Memory Switch remains closed. The Memory Switch Status will test closed (true). These conditions will persist until after power is reapplied to the shut down Central Processor.

#### 2.2.4 MODULE ADDRESS PATCHBOARD.

Each Central Processor has a small Patchboard, figure 2-1, with which its memory module addresses are established. Each of the sixteen groups of 4000 addresses ( $\emptyset\emptyset\emptyset\emptyset\emptyset$  through 63999) is presented as a selection signal that can be patched (connected) to any memory module, including all of those on the Shared Memory Trunkline. Memory modules are numbered  $\emptyset$  through 7 on the Individual Memory Trunkline and 8 through 15 on the Shared Memory Trunkline.

Shared Memory modules can be assigned module addresses independently by the Patchboards in the two Central Processors. That is, a given module may or may not have the same address patched to it in the two Central Processors. Section II

|                        |            | · · · · |                |        |                                                                                                                |  |

|------------------------|------------|---------|----------------|--------|----------------------------------------------------------------------------------------------------------------|--|

| STRAIGHT ADDRESS       |            | MEMORY  |                |        |                                                                                                                |  |

| 00000 - 03999 GSOD     | GISPO (    | C       | )              |        | ADDRESS<br>GSTOD<br>P3                                                                                         |  |

| 04000-07999 🔵 GSI      |            |         |                |        |                                                                                                                |  |

| 08000-11999 OS20       | GISP2      |         |                |        |                                                                                                                |  |

| 12000 - 15999 🔘 GS30   | GISP3□ (   | C       |                | GISPT3 | GST3D                                                                                                          |  |

| 16000 - 19999 🔘 654 P  | GISP4      |         | $) \bigcirc$   | GISPT4 | GST4 🗆 🔿                                                                                                       |  |

| 20000 - 23999 GS50     | GISP5□ (   |         |                |        | GST5 🗆 🔿                                                                                                       |  |

| 24000 - 27999          | GISP6□ (   | C       |                |        | GSTE 🗆 🔿                                                                                                       |  |

| 28000 - 31999 🔘 GS70   | GISP7□ (   |         |                |        |                                                                                                                |  |

| 32000 - 35999 ◯ GS8□   | GISP8□ (   | С       | )              |        | GST8 🗆 🔿                                                                                                       |  |

| 36000 - 39999 🔿 659 🗆  |            |         | )              |        | GST9 🗆 🔿                                                                                                       |  |

| 40000 - 43999 () GSIO□ | GISPIO 🗆 🤇 | С       | ) <sup>1</sup> |        |                                                                                                                |  |

| 44000 - 47999 ◯ GSII⊡  |            |         | )              |        |                                                                                                                |  |

| 48000 - 51999          | GISPI2 [   | C       | )              |        | GSTI2                                                                                                          |  |

| 52000 - 55999 🔵 GSI30  | GISPI3 🗆 ( | C       | )              |        |                                                                                                                |  |

| 56000 - 59999 🔵 GSI40  | GISPI4□ (  | C       | )              |        |                                                                                                                |  |

| 60000 - 63999 🔘 6SI5🗆  | GISPI5 🗆 ( |         | )              |        | GSTI5 🗆 🔿                                                                                                      |  |

|                        |            |         |                |        |                                                                                                                |  |

|                        |            |         |                |        | the second s |  |

PI, P2, P3: EXAMPLES OF PATCHES

Figure 2-1. Memory Address Selection Patch Board

2-4

#### 2.2.5 CORE MEMORY TWINNING.

The Patchboard in each Central Processor which assigns module addresses has an additional capability of providing simultaneous write operations in pairs of memory modules on the individual Trunkline. Pairs which share common address and M registers cannot be twinned. For example, if memory module B is patched to module A, write operations addressed to A will also write in B (in corresponding words). However, write operations addressed to B will not affect A, unless a second patch of A to B is made. In any case, read operations are not affected by the twinning.

Twinning is under control of a toggle (ZY = 53) that can be program tested, set, or reset. When the Twin Mode toggle is reset, duplicate writing will not take place.

Operations in which there is a write half cycle in Twin mode will always have a corresponding full clear and write cycle in the twin module. The clear occurs at the time of the read half cycle that preceded the write half cycle. No time is lost, but the information preserving properties of Twin mode are lost in half-cycle operations.

Figure 2-1 shows how the Patchboard can be used for module address selection. Patch wire P1 establishes addresses  $\emptyset\emptyset\emptyset\emptyset\emptyset$  to  $\emptyset3999$  for Core Memory module 2. Patch wire P2 establishes addresses  $2\emptyset\emptyset\emptyset\emptyset$  to 23999 for Core Memory module 4. Patch wire P3 establishes twin addresses  $\emptyset\emptyset\emptyset\emptyset\emptyset$  to  $\emptyset3999$  in Core Memory module 4. When the Twin Mode toggle is ON, write operations addressed to locations  $\emptyset\emptyset\emptyset\emptyset\emptyset$  to  $\emptyset3999$  in module 2 will write also in corresponding locations  $2\emptyset\emptyset\emptyset\emptyset$  to 23999 in module 4. Read operations addressed  $\emptyset\emptyset\emptyset\emptyset\emptyset$  to  $\emptyset3999$  will read only from module 2 and, similarly, read operations addressed  $2\emptyset\emptyset\emptyset\emptyset$  to 23999 will read only from module 4. Write operations addressed  $2\emptyset\emptyset\emptyset\emptyset$  to 23999 will write only in module 4 and will not affect module 2. Modules 2 and 4 do not share common address and M registers.

#### 2.3 INFORMATION FORMAT.

#### 2.3.1 WORD.

The basic storage element is the Central Processor word, which may be assigned specific Core Memory addresses. A word consists of eight 7-bit characters, figure 2-2, and may contain either an instruction, alphanumeric data, or a floatingpoint number. The characters in a word are numbered zero through seven, beginning with the least significant character position. Section II Paragraphs 2. 3. 2 to 2. 3. 3

#### 2.3.2 CHARACTER.

A character contains seven bits. These bits are numbered 1 through 7, beginning with the least significant bit position. Bits 1 through 4 are designated the numeric bits, bits 5 and 6 are the zone bits, and bit 7 is an odd parity check bit. The following diagram presents the character and bit assignment for a Central Processor word.

| C <sub>7</sub> | C <sub>6</sub> | С5       | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | Сø |   |

|----------------|----------------|----------|----------------|----------------|----------------|----------------|----|---|

|                |                | 0        | DD PAI         | RITY BI        |                | Ø7             | 7  |   |

|                |                |          |                | BITS           | 1              |                | Ø6 | 6 |

|                |                |          | ZONE           |                |                |                | Ø5 | 5 |

|                |                |          |                |                |                |                | Ø4 | 4 |

|                |                |          |                |                |                |                | Ø3 | 3 |

|                |                | <u>1</u> | NUMER<br>      |                |                |                | Ø2 | 2 |

| 71             | 61             | 51       | 41             | 31             | 21             | 11             | Ø1 | 1 |

Character Number

Bit Number

$c_7$  most significant  $C_{\emptyset}$  least significant

Figure 2-2. Information Word Format

A short two-digit notation will sometimes be used in this manual to designate a bit position in the Central Processor word. The first digit will provide the character number, and the second digit will specify the bit number within that character. Bit 75, for example, designates bit number 5 for the most significant character position. 2.3.3 BIT.

A bit may have a binary value of 1 or  $\emptyset$ , in accordance with the position of a toggle, or the direction of magnetization of a single core in Core Memory or of an area on either magnetic disc or magnetic tape. These bits may be transferred from Core Memory to the Program Control, Disc Memory Control, or Arithmetic Sections, where the binary value is recognized and used to access instructions, transfer data, and perform computation. The 1 status of a toggle is also sometimes considered its Set, ON, or True state, while a  $\emptyset$  status is the Reset, OFF, or False state. The four numeric bits plus the two zone bits are sufficient to permit 64 alphanumeric character code combinations. Refer to Appendix A for a list of Central Processor, Typewriter/Printer and Punched Card character codes. A seventh bit has been added to each 6-bit character code to provide an odd number of 1 bits. This odd parity status is checked on every data transfer to or from Core Memory, Arithmetic Section registers, Disc Memory, Uni-Record Trunkline devices, and other input-output units. In the event of a parity error, an interrupt request is generated and the Central Processor will enter an interrupt program (unless errors are being ignored under program control).

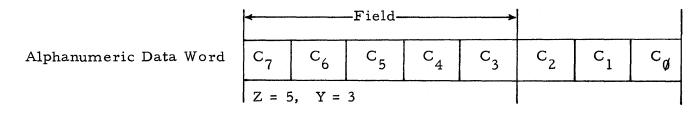

#### 2.3.4 ALPHANUMERIC DATA WORD.

An alphanumeric data word may contain several fields of data, each containing fixed-point numeric, alphabetic, or alphanumeric (any combination of symbols, alphabetic, and fixed-point numeric) information. A field consists of any consecutive number of characters within the word, and may be specified by many Central Processor instructions. Floating-point instructions, however, process only fullword operands.

The following example presents a Gross Pay field, containing \$110.25, and a Rate of Pay field, specifying \$2.25 per hour, within an alphanumeric data word. EXAMPLE:

| C <sub>7</sub>  | C <sub>6</sub> | с <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | С <sub>Ø</sub> |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1               | 1              | Ø              | 2              | 5              | 2              | 2              | 5              |

| Gross Pay field |                |                |                |                | Rate/F         | Pay Field      |                |

The programmer must locate the decimal point of numeric fields for fixed-point operations. The sign of each fixed-point field within the word is carried in the sixth bit of the least significant character position. A positive sign is indicated by a  $\emptyset$  in bit position six, while a negative sign is provided by a l. The fifth bit of the least significant character of the field, as well as the zone bits of the other numeric characters, are normally  $\emptyset$ . Alphabetic characters and special symbols contain combinations of 1 and  $\emptyset$  in the zone bit positions.

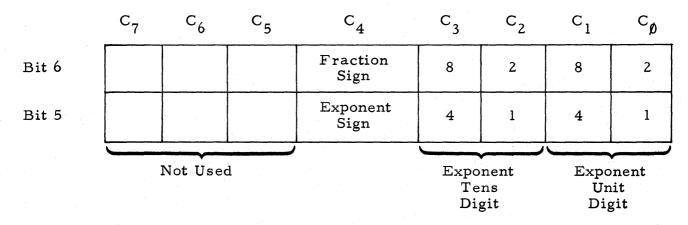

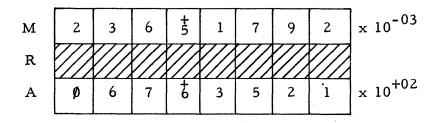

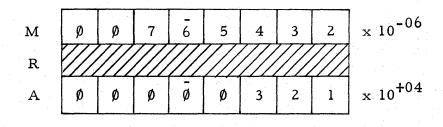

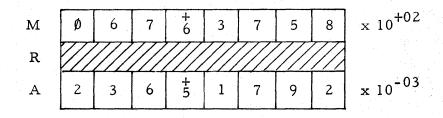

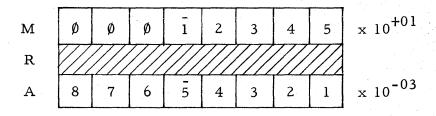

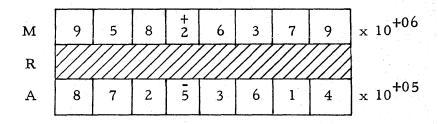

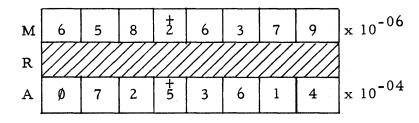

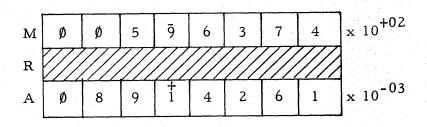

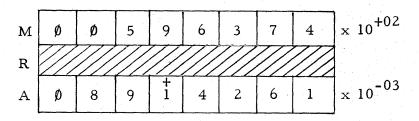

# 2.3.5 FLOATING-POINT DATA WORD.

Floating-point execution may be specified as an option by all full-word arithmetic instructions and by a numeric compare instruction, paragraph 2.4.5. This option is provided to extend the range of the operands that participate in these operations. Floating-point numbers carry and automatically process the decimal point position. A floating-point data word presents the number as a signed decimal fraction times a signed integral power of ten. The sign of the fraction and the exponent with its sign are carried in the zone bits of characters  $C_4$  through  $C_{\emptyset}$  in the following format. A l bit in a sign position indicates a minus.

The exponent is carried as two binary-coded decimal digits in the zone bits of the four least significant characters of the data word.

Floating-point numbers can range from  $. ppppppp x 10^{-99}$  (equals zero) to  $.99999999 \times 10^{99}$ . There is no minus zero in either the mantissa or exponent.

The following example presents the bit configuration for the floating-point operand,  $+.0162 \ge 10^{-14}$ , which could be represented in the computer word and in the example as the normalized quantity,  $+.16200000 \ge 10^{-15}$ . A floating-point number is said to be normalized when it is positioned so that the machine decimal point is to the left of the most significant (non-zero) digit of the fraction.

# Section II Paragraph 2.4

# EXAMPLE:

|                                   | C <sub>7</sub> | с <sub>6</sub> | С5 | с4   | C <sub>3</sub> | C2 | C1 | Сø |                |

|-----------------------------------|----------------|----------------|----|------|----------------|----|----|----|----------------|

| Floating-Point                    | Ø              | 1              | Ø  | Ø    | 1              | ø  | Ø  | Ø  | в <sub>7</sub> |

| Data Word<br>(as it would         | ø              | Ø              | Ø  | Ø(+) | Ø              | ø  | Ø  | ø  | в <sub>6</sub> |

| appear in a<br>register)          | ø              | ø              | Ø  | 1(-) | Ø              | 1  | 1  | 1  | в <sub>5</sub> |

|                                   | ø              | ø              | Ø  | Ø    | Ø              | Ø  | Ø  | Ø  | в4             |

|                                   | ø              | 1              | Ø  | Ø    | Ø              | ø  | Ø  | Ø  | B <sub>3</sub> |

|                                   | ø              | 1              | 1  | Ø    | Ø              | Ø  | ø  | Ø  | в2             |

|                                   | 1              | Ø              | Ø  | ø    | Ø              | ø  | Ø  | Ø  | в              |

| Quantity: +                       | . 1            | 6              | 2  | Ø    | Ø              | ø  | ø  | Ø  | x 10-15        |

| Printout<br>on Line<br>Printer or |                |                |    |      |                |    |    |    |                |

| Typewriter:                       | 1              | 6              | 2  | +    | Ø              | +  | +  | +  |                |

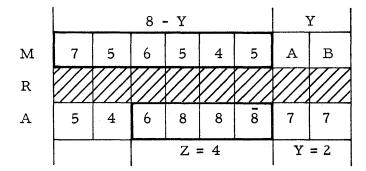

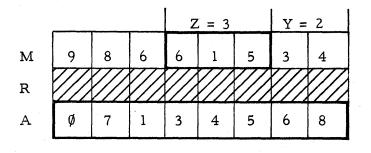

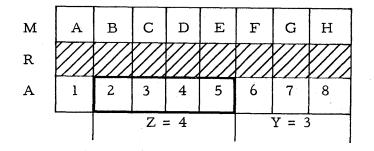

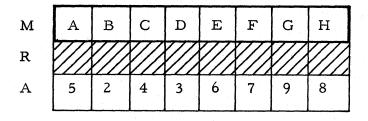

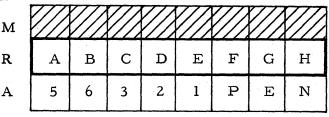

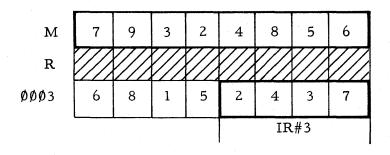

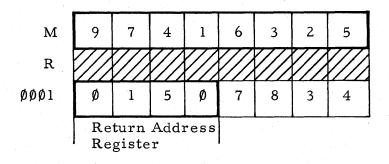

## 2.4 INSTRUCTION WORD FORMAT.