# HONEYWELL INTEROFFICE CORRESPONDENCE

PHOENIX OPERATIONS - HONEYWELL INFORMATION SYSTEMS

|      | - | - | 4 | 2 | 4 | <b>^</b> |

|------|---|---|---|---|---|----------|

| DATE | 7 | 1 | 1 | 2 |   | 2        |

|      |   |   |   |   |   |          |

PHONE

MAIL ZONE

COPIES

\_\_\_\_\_\_ Specification File

A service of the second s

C. Bjerke FROM

COMPONENT LADC

SF section: 14.4 doc # : 0257A-0 page : 1

SUBJECT I/O Design Specification

This specification has incorporated changes to the original design specification suggested by the I/O Design Review Committee and as such represents the design to be implemented.

| SF section: | : | 14.4    |

|-------------|---|---------|

| doc #       | : | 0257A-0 |

| date :      | : | 771212  |

| page :      | : | 2       |

# Design Specifications for a New I/O System

# 1. INTRODUCTION

The interim I/O System consists of two parts: IOQ and IOS. IOQ contains the caller and user interfaces; IOS, which was adapted from GCOS IOS, contains the I/O scheduling, interrupt, and error recovery routines.

In order to meet several requirements of the CP-6 I/O System, The interim IOS will be replaced with a new set of I/O processing routines ("the new IOS"). Although some internal changes to IOQ will be necessary, the interfaces to IOQ for routines outside of the I/O System will remain essentially unchanged.

# 1.1 REQUIREMENTS

The New I/O System for CP-6 will provide the following features:

- o It will be written mostly in PL6 for easy maintenance.

- Each handler will be an independent set of routines. Common code will be primarily subroutines.

- Table searches will be minimized by using queue structures where applicable.

- o It will be designed for a multi-processor environment.

- o It will be designed so that a wide variety of device handlers may be accomodated, including those specifically mentioned herein.

- o Disk I/O will be scheduled so as to minimize arm positioning delays and rotational latency.

# 1.2 Conventions

# 1.2.1 Module and Entry Point Names

All module and entry point names will have the following prefixes:

| SF section | <b>1:</b> | 14.4    |

|------------|-----------|---------|

| doc #      | :         | 0257A-0 |

| date       | :         | 771212  |

| page       | :         | 3       |

# Prefix Module

| NIC\$ | Console Handler                         |

|-------|-----------------------------------------|

| NID\$ | Disk Handler                            |

| NIL\$ | Line Printer Handler                    |

| NIO\$ | IOQ                                     |

| NIP\$ | Card Punch Handler                      |

| NIQ\$ | Packet Allocator                        |

| NIR\$ | Card Reader Handler                     |

| NIS\$ | Driver and Interrupt Distributor (BMAP) |

| NIT\$ | Magnetic Tape Handler                   |

| NIU\$ | Utility Subroutines (PL6)               |

# 1.2.2 External Symbol Names

All external symbol names defined in the above modules will have the prefix: NI\_.

### 1.2.3 Calling Sequences

All calling sequences will be PL-6 calling sequences, which are described in AF sect. 6.3, #0137.

# 1.3 Scope

,

This document describes the new IOS. Section 2 discusses those aspects of the hardware which must be taken into consideration when designing the I/O System. Section 3 contains an overview. Section 4 describes the data structures. Section 5 describes the procedures. Section 6 describes the changes to IOQ and entry points of IOQ which are used by IOS.

This document does not describe the individual device handlers, other than indicating the general modus operandi thereof.

# 1.4 References

This design specification is based on information contained in the following documents:

| 58001190  | E PS – 1 | 4 Megaword System Controller                |

|-----------|----------|---------------------------------------------|

| 43A239854 | EPS-1    | 6000B Input/Output Multiplexer (IOM) Centre |

| 43A177880 | EPS-1    | 6000 IOM Peripheral Subsystem Interface Ad  |

| 43A177879 | EPS-1    | MPC - PSI Link Adapter                      |

| 58001108  | EPS-1    | Unit Record MPC Controller/Subsystem        |

| 58008518  | EPS-1    | MTP601 Tape Controller                      |

| 43A232230 | EPS-1    | DSC181/DSC190 Controller _                  |

| SF section: | 14.4    |

|-------------|---------|

| doc#:       | 0257A-0 |

| date :      | 771212  |

| page :      | 4       |

# 2. HARDWARE CONSIDERATIONS

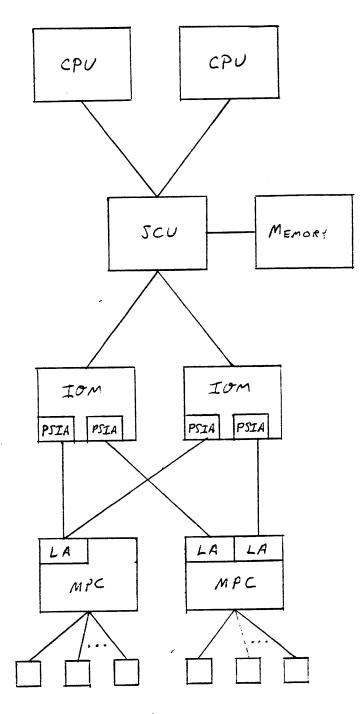

The general configuration of the L66 I/O hardware is shown in Fig. 2.1. There may be up to four CPUs. By the use of mask registers, I/O interrupts can be selectively directed to different CPUs. However, in order to maintain the current concept utilized in the Job Scheduler, all I/O interrupts will be sent to one CPU. There may be more than one System Controller (SCU), but if all of the CPUs and IOMs are to have the same address space, the only purpose for more SCUs is to provide more than 4 megawords of memory. There may be up to four Input/Output Multiplexors (IOMs), but each IOM is controlled independently and identically. Multiple IOMs can be used to provide greater I/O bandwidth and/or more I/O channels.

A Micro-Programmed Controller (MPC) may have one or two Link Adapters, each of which is capable of performing one data transfer operation at a time. Thus, two Link Adapters allow two simultaneous data transfer operations on dual-access tape and disk subsystems. Each Link Adapter may be connected to one or two Peripheral Subsystem Interface Adapters (PSIAs). The only purpose for having two PSIAs attached to one Link Adapter is to provide redundant paths to the MPC. Typically, the two PSIAs would be connected to different IOMs. Each PSIA may control up to eight I/O channels. The latter are usually called logical channels, to distinguish them from physical channels, which connect PSIAs to Link Adapters. The use of multiple logical channels on a PSIA depends on the type of peripheral subsystem.

A unit record MPC can control up to eight peripherals such as card readers, line printers, and card punches. Each device is assigned the same logical channel number on all of the PSIAs connected to the MPC. Thus, there may be up to four paths to each device (2 Link Adapters X 2 PSIAs). However, since unit record data transfers are always buffered in the MPC and the data transfer time is much less than the device cycle time, more than one Link Adapter or PSIA only provide redundant paths to the MPC. Thus, a unit record peripheral would usually be accessed by the same channel. Any contention between the devices for logical channels would be resolved by the MPC and thus would be transparent to the I/O software in the CPU.

A magnetic tape MPC can control up to 16 tape drives via a 1 X N or a 2 X N switch. Thus, with two Link Adapters, two tape drives may be doing simultaneous data transfers. Keeping a Link Adapter busy requires only two logical channels on the PSIA: one for the current request being processed, and one to hold a request which can be started immediately when the current request is finished. If there are more than two logical channels, a request issued to the lowest priority channel may never be started because enough requests are issued on higher priority channels to keep the Link Adapter busy. Thus, I/O scheduling for a tape subsystem must resolve

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 5       |

contention for the channels and, for maximum throughput, should keep both Link Adapters (if there are two) busy.

A disk subsystem may have one or two MPCs, each of which may have one or two Link Adapters, thus a maximum disk subsystem may perform four simultaneous data transfers. On a disk subsystem, the multiple logical channels of the PSIA are used to implement seek overlap. When a request is issued to a disk channel, the MPC initiates the seek phase of the request, then releases the logical channel so that other logical channels may be processed. In this manner, several disk drives may all be seeking simultaneously. When one of them arrives at the requested sector, the MPC restarts the corresponding logical channel, and performs the data transfer operation. If a disk arrives at the requested sector while a data transfer is in progress, the on-sector interrupt from the drive will be ignored and will occur again on the next revolution. However, if maximum performance is to be obtained from the disk subsystem, the disk I/O software must still schedule disk operations so as to minimize arm positioning delays and rotational latency. Thus, I/O scheduling for a disk subsystem must resolve contention for the channels, it should keep all of the Link Adapters busy, and it should schedule the requests for a drive so as to minimize seek delays.

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 6       |

# 3. OVERVIEW

The new IOS will consist of the Driver, the Interrupt Distributor, the Lost Interrupt Poller, and several device handlers, one for each type of supported device. The Driver will set up the connect and payload channel mailboxes and issue the Connect I/O Channel (CIOC) instruction to initiate the I/O operation. The Interrupt Distributor will be entered whenever an interrupt occurs. It will determine the channel which caused the interrupt and call the Poster of the device handler for that channel. The Lost Interrupt Poller is called periodically to check for lost interrupts. In addition, there will be some common subroutines, such as an interface to KEYIN.

Each handler will consist of a Scheduler and a Poster. The Scheduler is called by IOQ or the Poster to schedule the device for the I/O operation. The Poster is called by the Interrupt Distributor when an interrupt occurs to start the next request on the interrupting channel, analyze the completed request, perform any necessary error recovery, and return the completed request to IOQ for end-action processing.

SF section: 14.4 doc # : 0257A-0 date : 771212 page : 7

#### 3.1 Table and Queue Structure

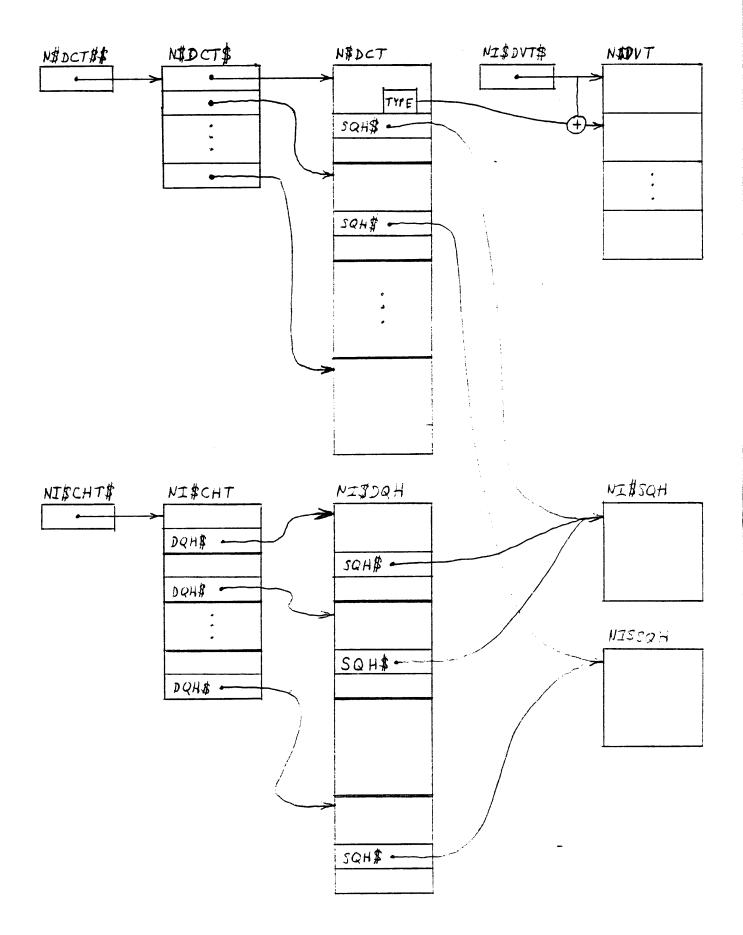

The static table structure for the New I/O System is shown in Fig. 3.1. The dynamic table and queue structure is shown in Fig. 3.2.

3.1.1 Tables

All of the I/O tables will be constructed at startup or recovery time from configuration information stored on disk. Each table will have a pointer in the New I/O System's static storage; this pointer will be set up when the table is constructed.

o Device Control Table (N\$DCT)

The Device Control Table contains scheduling information for all local and remote devices.

o Channel Table (NI\$CHT)

The Channel Table points to the Driver Queue Header and Poster for each channel.

o Driver Queue Header (NI\$DQH)

The Driver Queue Header contains scheduling data for a channel.

o Subsystem Queue Header (NI\$SQH)

The Subsystem Queue Header contains scheduling data for a subsystem.

### 3.1.2 Queues

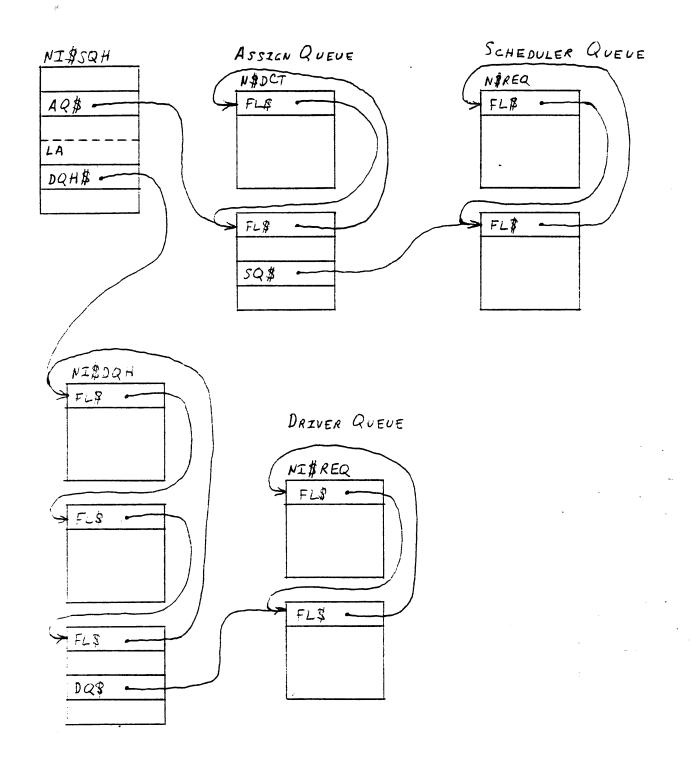

All FIFO queues will be linked circularly, where each entry points to its successor; and the last entry points to the first. The queue header, <u>i.e.</u>, the pointer to the queue, then points to the last entry in the queue. This saves space, in that the queue header needs only one pointer, yet allows easy enqueuing at either end of the queue and easy dequeuing at the head of the queue.

o Scheduler Queue

Each device has a queue of outstanding requests called the Scheduler Queue. For most devices, this will be a FIFO queue, but for disk, the requests will be ordered according to arm position, so as to minimize arm positioning delays. The header of each Scheduler Queue is in the Device Control Table entry. As requests are received, IOQ enqueues them on the requested device's Scheduler Queue. When a channel has been assigned to

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 8       |

this device, the device Scheduler will move those requests which can be processed as a group to the Driver Queue.

### o Assign Queue

Each subsystem will have a Assign Queue, which is a FIFO queue of devices waiting for channels to become available. The Assign Queue header is in the Subsystem Queue Header. The device Scheduler will put an idle device on the Assign Queue when there are requests on that device's Scheduler Queue. When a channel is assigned to the device, the device will be removed from the Assign Queue.

### o Driver Queue

Each channel will have a Driver Queue, which is a queue of requests that are ready to be started. This queue will be FIFO for most devices, but for disk, it will be ordered according to sector position within a track, so as to minimize rotational latency. At any moment in time, a Driver Queue will contain requests for only one device. For a disk channel, the Driver Queue will contain requests for only a single cylinder of a disk pack. The device Scheduler enqueues requests on the Driver Queue when a channel has been assigned. The device Poster removes a request from the Driver Queue when it terminates.

This two-level queuing structure (Scheduler Queue and Driver Queue) is designed to maximize disk throughput. Basically, the Scheduler Queue is a queue of cylinders to be accessed, and the Driver Queue is a queue of requests for the current cylinder.

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 9       |

#### 3.2 I/O Request Processing

In the New I/O System, IOQ is called for both local and remote peripheral requests. On receiving a request, IOQ enqueues the request on the Scheduler Queue for the device. Then, if this request is for a remote device, IOQ calls the Front End Interface to process the request. If this request is for a local device, IOQ allocates an IOS Request Packet and links it to the IOQ Request Packet. From the information in the IOQ Request Packet, IOQ then sets up the PCW, LPWX, and DCW list in the IOS Request Packet and calls the device Scheduler for the requested device.

If the device is idle, the device Scheduler enqueues the device on the Assign Queue for that subsystem. It then processes the Assign Queue, assigning a channel to each device thereon, until there are no more channels available or the Assign Queue is empty.

When a channel is assigned to a device (see section 3.4), the device is removed from the Assign Queue, and one or more requests, depending on the device, are moved from the device's Scheduler Queue to the channel's Driver Queue. The Driver is then called to start the first request on the channel's Driver Queue.

The Driver sets up the connect and payload channel mailboxes and issues the CIOC instruction to start the I/O operation.

When the interrupt occurs, the Interrupt Distributor determines the channel number and calls the device Poster for that channel. If no errors occurred, the Poster calls the Driver to start the next request on this channel. If there were no errors or the errors were unrecoverable, the completed request is returned to IOQ for end-action processing. If the channel is now idle, the Poster calls the device Scheduler to restart If an error occurred that must be retried, the the channel. request is rescheduled to be processed next. If repositioning is required before the retry, reserved IOS Request Packets are used to effect the repositioning and are scheduled ahead of the request packet. This rescheduling may be done in either of two ways, depending on the device. For sequential devices, i.e., devices other than disk, it requeues the IOS packet on the Driver Queue and calls the Driver to process the request. For disk devices, it requeues the IOS packet on the Scheduler Queue and calls the device Scheduler to process the request. If an error occurred which requires operator intervention, a message is sent to the operator's console, and the request and the contents of the channel's Driver Queue are moved back to the beginning of the device's Scheduler Queue. The device Scheduler is then called to restart the channel (with requests for another device). The completion of the operator intervention may be signaled either by a special interrupt or an operator keyin. In the former case, the Interrupt

SF section: 14.4 doc # : 0257A-0 date : 771212 page : 10

Distributor will post the special interrupt to the device Poster. In the latter case, IOS' interface to KEYIN will post the keyin to the Poster. When the operator intervention is complete, the device will be inserted at the beginning of the Assign Queue, and the device Scheduler will be called to restart the device.

r

.

ì

2

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 11      |

### 3.3 Channel Assignment

The multiplicity of channels which may access a subsystem requires that channels be assigned dynamically to devices as they are needed. For unit record subsystems, this channel assignment amounts only to selecting an available one from those configured. For tape and disk subsystems, Link Adapters and channels are assigned in a round-robin fashion. When there is a device to be assigned to a channel, the next Link Adapter with an available channel is found, and the device is assigned to the next available channel on that Link Adapter.

# 3.4 Direct Channel I/O

An entry point to the Driver will be provided for issuing a connect to a direct channel. The Front End Handler will have an Poster of its own for handling interrupts from the direct channel.

### 3.5 Lost Interrupts

Occasionally, the hardware may fail in such a manner that no interrupts are returned from an I/O operation. For this reason, we need a Lost Interrupt Poller, <u>i.e.</u>, a routine which is called periodically, say, every 5-10 seconds, to poll all of the active channels to see if a channel has been active for an unreasonably long time. If this is so, <u>i.e.</u>, a lost interrupt has occurred, the device Poster is called with a unique interrupt level. The latter will then take the appropriate error recovery action.

# 3.6 Error Statistics and Error Logging

All I/O errors will be logged in the system error log. Presumably there will be a ghost job that will monitor the error log and warn the operator if the error rate on a device exceeds an acceptable level (thresholding). The error log entry will include a time stamp, the external device identification, the IOM and channel numbers, the hardware status words, and any extended status that may be available. In the case of a memory error during I/O, memory mapping information will also be included.

#### 3.7 Test and Diagnostics

The New I/O System will provide options in the IOQ Request Packet for specifying T&D I/O. This will take the form of a unique logical function code, which will indicate that the DCW list is already set up (in the job's virtual memory), and that no error recovery or logging are to be performed on this

| SF section: | 14.4    |

|-------------|---------|

| doc#:       | 0257A-0 |

| date :      | 771212  |

| page :      | 12      |

.

,

request. The I/O System tables will have provision for reserving a device for T&D.

r

ĩ

.

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 13      |

# 4. DATA STRUCTURES

The following packets and tables will be used by the New I/O System:

4.1 IOQ Request Packet (N\$REQ)

The IOQ Request Packet is used for all I/O requests for both local and remote devices. It contains the information which must be provided by the caller and space for information to be returned to the caller on completion.

| %MAC | N\$REQ(NAME=N\$REQ,                     | <pre>STCLASS=BASED);</pre>       | (* <b>*</b> (0                                                |                         | DAG                                            |                                    | ¥ /                          |            |          |   |     |

|------|-----------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------|------------------------------------------------|------------------------------------|------------------------------|------------|----------|---|-----|

| DCL  | 1 NAME STCLASS ALI<br>0 1 2 3 4 5 6 7 8 | 0 1 2 3 4 5 6 7 8                | 0 1 2                                                         | 3 4 5 6                 | 7 8                                            | 0 1                                | */<br>2                      | 3 1        | 5        | 6 | 7 { |

| 0    | FL\$                                    |                                  |                                                               |                         |                                                |                                    |                              |            |          |   |     |

| 1    |                                         | DRELAD                           | פתר                                                           |                         |                                                | •                                  |                              |            | ,        |   |     |

|      | BUFSIZE                                 |                                  | *                                                             | FC                      |                                                | O PF                               | LG                           |            | I ¦ B    |   | R   |

| 3    | BIIF¢                                   |                                  | •                                                             |                         |                                                | ,                                  |                              |            |          |   |     |

| 4    | PTP                                     |                                  | # # #                                                         | ####                    | ##                                             | ;<br># #                           | #                            | # #        | ;<br>; # | # | #   |

|      | DCB\$                                   |                                  |                                                               |                         |                                                |                                    |                              |            |          |   |     |

| 6    | FAENTRY                                 |                                  |                                                               |                         |                                                |                                    |                              |            |          |   |     |

| 7    | FAINEO                                  |                                  | •                                                             |                         |                                                | •                                  |                              |            |          |   |     |

| 10   |                                         |                                  | •                                                             |                         |                                                | •                                  |                              |            |          |   |     |

| 11   | ARSIZE                                  |                                  | <b>*</b>  <br>                                                | CC<br>ERR ¦A<br>I¦P¦I¦E | BN                                             | USE                                | R∦                           |            |          |   |     |

| 12   | ARCT                                    |                                  |                                                               |                         |                                                |                                    |                              |            |          |   |     |

|      | RCT                                     |                                  | •                                                             |                         |                                                | •                                  |                              |            |          |   |     |

|      |                                         | 5) UNAL,<br>N(21) UNAL,<br>UNAL, | /* LINK<br>/* DEVI<br>/* DEVI<br>/* DEVI<br>/* SET<br>/* PACK |                         | T PĀ<br>CAL A<br>E INI<br>TIVE<br>ADDI<br>IDEX | CKET<br>ADDR<br>DEX<br>ADD<br>RESS | IN<br>ESS<br>*/<br>RES<br>*/ | QU<br>; *, |          |   |     |

SF section: 14.4 doc # : 0257A-0 date page : 771212 : 14

2 BUFSIZE UBIN(20) UNAL, /\* BUFFER SIZE (BYTES) \*/ 2 \* BIT(1). 3 \* BIT(5),3 BASE UBIN(18) UNAL, 3 BYTE UBIN(3) UNAL, 3 \* BIT(10),2 BUFREAL REDEF BUF\$, 3 EXTA UBIN(6) UNAL, 3 ADR UBIN(18) UNAL, 3 BYTE UBIN(2) UNAL, 2 \* BIT(1), 2 CC, 3 ERR, 4 IO BIT(1), /\* I/O ERROR \*/ 4 PE BIT(1), /\* PARITY ERROR \*/ 4 INVD BIT(1), /\* INVALID OPERATION \*/ 3 ABN, 3 ABN,<br/>4 EOF BIT(1),<br/>4 EOT BIT(1),<br/>4 BOT BIT(1),/\* END-OF-FILE \*/<br/>/\* END-OF-TAPE \*/<br/>/\* BEGINNING-OF-TAPE \*/<br/>/\* BEGINNING-OF-TAPE \*/<br/>/\* USER ID \*/<br/>2 ARCT SBIN WORD,<br/>2 RCT SBIN WORD;/\* END-OF-FILE \*/<br/>/\* END-OF-TAPE \*/<br/>/\* BEGINNING-OF-TAPE \*/<br/>/\* ACTUAL RECORD COUNT \*/<br/>\* RECORD COUNT \*/

2 \* BIT(1), 2 FC UBIN(6) UNAL, 3 USER BIT(1), 3 ARS BIT(1), 3 EVNT BIT(1), 3 EVNT BIT(1), 3 EA BIT(1), 4 EA BIT(1), 3 EA BIT(1), 3 EA BIT(1), 4 EA BIT(1), 5 EA BIT(1), 5 EA BIT(1), 7 EALL END-ACTION ROUTINE \*/ 7 EALL /\* REAL BUFFER ADDRESS IF PTP=0 \*/ > \* BII(10), 2 PTP UBIN(18) UNAL, 2 DCB\$ PTR, 2 EAENTRY EPTR, 2 EAINFO UBIN(36), 2 EVNTINFO UBIN(36), 2 END-ACTION PROCEDURE \*/ 2 EVNTINFO UBIN(36), 2 EVNTINFO UBIN(36), 2 ARSIZE UBIN(20) UNAL, 2 \* BIT(1)

/\* BPF=0: PAGE TABLE POINTER (0=REA! /\* -> USER'S DCB \*/ /\* END-ACTION PROCEDURE \*/ /\* END-ACTION PARAMETER \*/ /\* ACTUAL RECORD SIZE \*/ /\* LOGICAL COMPLETION CODE (0=OK) \*

%MEND:

| SF section | : | 14.4    |

|------------|---|---------|

| doc #      | : | 0257A-0 |

| date       | : | 771212  |

| page       | : | 15      |

# 4.2 IOS Request Packet (NI\$REQ)

•

The IOS Request Packet is allocated by IOQ for a local device I/O request. It resides in real memory and contains information specific to a local device I/O operation.

| %MAC<br>DCL | NI\$REQ(NA<br>1 NAME STC<br>0 1 2 3 4 | ME=NI\$RI<br>LASS DAI<br>5 6 7 8 | EQ,STO<br>LIGNEI<br>0 1 2 | CLAS<br>D,<br>2 3 | 3S =<br>4 | BAS<br>5 ( | SED<br>5 <b>7</b> | ;;<br>8 | /*<br>0 | I/0<br>1 2 | REC<br>3 L | QUE<br>4 5 | ST<br>6 | Р <i>І</i><br>7 | A CH<br>8 | CET<br>0    | */<br>1 2   | ,<br>2 3 | 4      | 5 | 6 | 7 | 8        |

|-------------|---------------------------------------|----------------------------------|---------------------------|-------------------|-----------|------------|-------------------|---------|---------|------------|------------|------------|---------|-----------------|-----------|-------------|-------------|----------|--------|---|---|---|----------|

| 0           | FL\$                                  |                                  | ;<br>,                    |                   |           |            |                   |         | i — —   |            |            |            |         |                 |           | ; ·<br>,    |             |          |        |   |   |   |          |

| 1           | IOQ\$                                 |                                  |                           |                   |           |            |                   |         | ı — —   |            |            |            |         |                 |           | , <b></b>   |             |          |        | • |   |   | • -      |

| 2           | DCT\$                                 |                                  | !                         |                   |           |            |                   |         | !       |            |            |            |         |                 |           |             |             |          |        |   |   |   |          |

| 3           | ERRCT                                 | LPWCO                            | NT<br>!                   | ;#                | #         | # #        | <br>              | #       | #<br>!  | # #        | # 1        | ¥ #        | #       | #               | #         | # 1         | =   <br>  = | ŧ #      | #      | # | # | # | #        |

|             | PCW<br>*                              |                                  | !                         | <b> </b> A        | EX        |            |                   |         | ID      | CW         | M '        | ŧ          |         |                 |           | !           |             |          |        |   |   |   |          |

| 5           | CHANNEL                               |                                  | PTP                       |                   |           |            |                   |         | '       |            |            |            |         |                 |           | FL/         | AGS         | 5        |        |   |   |   |          |

|             | L PWX<br>BASE                         |                                  | 1                         |                   |           |            |                   |         | ¦SI     | ZE         |            |            |         |                 |           | , — — ·     |             |          |        |   |   |   |          |

|             | DCW<br>FWA                            |                                  |                           |                   |           |            |                   |         | IC      | P          | TYF        | ΡĒ         |         | ALI             | LY        | , <b></b> - |             |          |        |   |   |   |          |

|             | DCW<br>FWA                            |                                  | i                         |                   |           |            |                   |         |         | P          | TYI:       | PE         | <br> T  | AL              |           | i — — ·     |             | •        |        |   |   |   | <b>.</b> |

|             | DCW<br>FWA                            |                                  | 1                         |                   |           |            |                   |         | ; IC    | P          | TYF        | ΡE         | T       | ALI             | LY        | · ·         |             |          |        |   |   |   | _        |

|             | DCW<br>FWA                            |                                  | 1                         |                   | /<br>/    |            |                   |         | IC      | P          | T Y I      | PE         | T       | AL              | LY        | ·           |             |          |        |   |   |   | -        |

|             | DCW<br>FWA                            |                                  |                           |                   |           |            |                   |         |         | P          | TYF        | PE         | T       | ALI             | LY        | ·           |             |          |        |   |   |   | _        |

|             | SEEK<br>SCL                           |                                  | 1                         | S                 | sz        |            | ¦S                | EC      | TOR     |            |            |            |         |                 |           | , — — ·     |             |          |        |   |   |   | -        |

|             | CL\$                                  |                                  | ;                         |                   |           |            |                   |         | ;       |            |            |            |         |                 |           | i ·         |             |          |        |   |   |   | •        |

|             | STATUS<br>P   P   MAJOR               | MINOR                            | <b></b>                   | 10                | M         | *          | <br> 1            | <br> *  | I CH    | AN         | 101        | 1          | <br>  * |                 |           | ·           |             | R        | <br>CR |   |   |   | -        |

| 17          | NW A                                  |                                  |                           |                   |           |            |                   |         | NC      | P          | R          | ¥<br>      | T       |                 | LYI<br>   | R<br>       |             | ~        |        |   | • |   | -        |

| SF sectio | n: | 14.4    |

|-----------|----|---------|

| doc #     | :  | 0257A-0 |

| date      | :  | 771212  |

| page      | :  | 16      |

3 \* BIT(2),3 ININT BIT(1),

3 CHAN BIT(3),

/\* CHANNEL STATUS \*/

3 IOM BIT(3),

/\* IOM STATUS \*/

3 \* BIT(6)

/\* IOM STATUS \*/

3 \* BIT(6),3 \* BIT(2),3 TALLYR UBIN(12) UNAL; /\* TALLY RESIDUE \*/

2 FL\$ PTR, 2 IOQS PTR, 2 DCT\$ PTR, 2 ERRCT UBIN(6) UNAL, 2 ERRCT UBIN(6) UNAL, 3 # BIT(12), 3 AEX UBIN(6) UNAL, 3 # BIT(14), 3 \* BIT(18) UNAL, 3 FLAGS BIT(9), 4 \* CHANNEL NUMBER \*/ 5 \* CHANNEL NUMAL, 5 \* CH /\* INITIATION INTERRUPT \*/ 3 \* BIT(6), 3 RCR UBIN(6) UNAL, 3 NWA UBIN(18) UNAL, 3 NCP UBIN(3) UNAL, 3 READFLG BIT(1), 3 \* BIT(2). 4 RECORD COUNT RESIDUE \*/ NEXT WORD ADDRESS \*/ /\* NEXT WORD ADDRESS \*/ /\* NEXT CHAR POSITION \*/ /\* READ/WRITE FLAG \*/

SF section: 14.4 doc # : 0257A-0 date : 771212 page : 17

# 4.3 Device Control Table (N\$DCT)

The Device Control Table contains scheduling information for both local and remote devices. It is accessed by a parallel table of pointers, called N\$DCT\$; the index into this table of pointers is the Device Control Table Index (DCTX). The pointer table will be pointed to by the pointer, N\$DCT\$\$. Thus, a reference to a field in the Device Control Table would appear as:

N\$DCT\$\$->N\$DCT\$(DCTX)->N\$DCT.field.

This pointer-table structure allows DCT entries to be of different sizes and allows dynamic allocation of packets for remote devices.

%MAC N\$DCT(NAME=N\$DCT,STCLASS=BASED); /\* DCT ENTRY \*/ DCL 1 NAME STCLASS ALIGNED, 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 0 | F L \$ -----1 DEVNM | - - - - - - - -- -- - - - - -21 ----DFLG TYPE 3 DCTX **DVN** I |0 | \* |0 |L |0 | 1 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ . 4 \SO\$ !----5 SPEC 6 SPECINFO 7 |SQH\$ -----10 | DOH\$ -----11 STATE 12 | ERROR 13 DISK SETL\$ 14! | **\*** \*\*\*\*\*\* 151 \* # # # # # # # # # # # # # # # # #

SF section: 14.4 doc # : 0257A-0 date : 771212 page : 18 /\* FORWARD LINK FOR ASSIGN QUEUE \*/ 2 FL\$ PTR, 2 DEVNM CHAR(8) ALIGNED, /\* DEVICE NAME E.G. LPO2 \*/ /\* DCT INDEX \*/ 2 DCTX UBIN(18) UNAL, /\* DEVICE FLAGS \*/ 2 DFLG. 3 INPUT BIT(1), 3 OUTPUT BIT(1), 3 \* BIT(1), 3 \* BIT(1), 3 OCK BIT(1), /\* OPERATOR'S CONSOLE \*/ /\* LOCAL DEVICE \*/ 3 LCL BIT(1), 3 OLDSC BIT(1), 3 OLDSC BIT(1), 2 TYPE UBIN(6) UNAL, 2 DVN UBIN(6) UNAL, 2 SQ\$ PTR, 2 SPEC EPTR, 2 SPEC EPTR, 2 SPECINFO UBIN(36), 2 SQH\$ PTR, 2 SQH\$ PTR, 2 DQH\$ PTR, 2 DQH\$ PTR, 2 STATE UBIN(6) UNAL, 2 STATE UBIN(6) UNAL, 2 STATE UBIN(6) UNAL, 3 SETL\$ PTR, 3 \* BIT(54). 3 OLDSC BIT(1), 2 TYPE UBIN(6) UNAL, 3 TYPE UBIN(6) UNAL, 3 SETL\$ PTR, 3 \* BIT(54). 4 DEVICE TYPE \*/ 4 DEVICE TYPE \*/ 4 DEVICE NUMBER \*/ 4 DEVICE NUMBER \*/ 4 DEVICE NUMBER \*/ 4 SCHEDULER QUEUE \*/ 4 DEVICE STATUS QUEUE HEADER \*/ 4 CURRENTLY ASSIGNED DRIVER QUEUE \*/ 4 DEVICE STATUS (UP, DOWN, T&D) \*/ 4 DEVICE STATUS (UP, DOWN, T&D) \*/ 4 DEVICE STATUS (UP, DOWN, T&D) \*/ 4 DISK-SPECIFIC DATA \*/ 4 LINK TO NEXT PACK IN SET \*/ 4 DISK-SPECIFIC DATA \*/ 4 DISK-SPECIFIC DA 3 \* BIT(54), 2 PRINTER REDEF DISK, 3 VFC\$ PTR, 3 CHAIN\$ PTR, 3 VFCL UBIN(9) UNAL, 3 CHAINL UBIN(9) UNAL; 4 PRINTER-SPECIFIC DATA \*/ /\* -> VFC IMAGE \*/ /\* -> CHAIN IMAGE \*/ /\* VFC IMAGE LENGTH \*/ /\* CHAIN IMAGE LENGTH \*/

| SF section: |   | 14.4    |

|-------------|---|---------|

| doc #       | : | 0257A-0 |

| date :      | : | 771212  |

| page :      | : | 19      |

# 4.4 Device Table (NI\$DVT)

1 T 1 T 1

- 5

. . . . . . . . .

The Device Table contains static information for each type of local device in the system. The index into this table is the device type, which is contained in each local entry of the Device Control Table. This table will be pointed to by the pointer, NI\$DVT\$.

%MAC NI\$DVT(NAME=NI\$DVT,STCLASS="(0:0) BASED(NI\$DVT\$)"); DCL 1 NAME STCLASS ALIGNED,

| 0         | 0 1 2 3 4 5 6 7 8                                                                                                                            | 0 1 2 3 4 5 6 7 8 | 012345678                                                                                                                                                                                                  | 012345678                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0 D       | )OT\$                                                                                                                                        |                   | ;;                                                                                                                                                                                                         |                                                                                                                       |

| 1   S     | SCHED                                                                                                                                        |                   |                                                                                                                                                                                                            |                                                                                                                       |

| 2   P     | POST                                                                                                                                         |                   |                                                                                                                                                                                                            |                                                                                                                       |

| 3 0       | CYLINDERS                                                                                                                                    | SURFACES          | CYLSIZE                                                                                                                                                                                                    | SECTORS  P #                                                                                                          |

|           | IODEL                                                                                                                                        | 1                 | ; ;                                                                                                                                                                                                        |                                                                                                                       |

| 5         |                                                                                                                                              |                   |                                                                                                                                                                                                            |                                                                                                                       |

| 4 M G N D | 2 DOT\$ PTR,<br>2 SCHED EPTR,<br>2 POST EPTR,<br>2 CYLINDERS UBI<br>2 SURFACES UBIN(<br>2 SECTORS UBIN(<br>2 PSIA BIT(1),<br>2 MODEL CHAR(8) |                   | /* PRE-HANDLER ENTR<br>/* -> DEVICE SCHEDU<br>/* POST-HANDLER ENT<br>/* (DISK) NUMBER OF<br>/* DEVICE ATTACHED | RY */<br>JLER */<br>TRY */<br>F CYLINDERS */<br>F SURFACES */<br>F SECTORS/CYLINDE<br>F SECTORS/TRACK *<br>TO PSIA */ |

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 20      |

# 4.5 Channel Table (NI\$CHT)

The Channel Table is indexed by the IOM number and the channel number and contains an entry for each possible channel (overhead and payload) in the system. The entry for each configured channel contains a pointer to the Driver Queue Header and an entry pointer to the Poster for that channel. This table will be pointed to by the pointer, NI\$CHT\$.

2 DQH\$ PTR, 2 POSTER EPTR; /\* -> DRIVER QUEUE HEADER \*/

/\* POSTER \*/

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 21      |

# 4.6 Driver Queue Header (NI\$DQH)

The Driver Queue Header contains configuration and scheduling information for a particular channel. For multi-device subsystems, the Driver Queue Headers are grouped by Link Adapter; for unit record subsystems, the Driver Queue Headers are grouped by device.

# %MAC NI\$DQH(NAME=NI\$DQH,STCLASS=BASED); DCL 1 NAME STCLASS ALIGNED.

| DCL | 1 NAME STCLASS ALIGNE<br>0 1 2 3 4 5 6 7 8 0 1                                                                     | ED,<br>12345678              | 3 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 {<br>                                                                                                                                                                                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | FL\$                                                                                                               |                              | ·                                                                                                                                                                                                                                                                                                                      |

| 1 ! | GATE                                                                                                               |                              |                                                                                                                                                                                                                                                                                                                        |

| 2   | IOCHAN<br>IOM ¦CHANNEL                                                                                             | STATUS<br>                   | LA STATE LOSTINT                                                                                                                                                                                                                                                                                                       |

| 2   | \$0H\$                                                                                                             |                              | -                                                                                                                                                                                                                                                                                                                      |

| 4   | DQ\$                                                                                                               |                              | -                                                                                                                                                                                                                                                                                                                      |

| 5   | ERROR                                                                                                              |                              | -                                                                                                                                                                                                                                                                                                                      |

|     | 2 FL\$ PTR,<br>2 GATE SBIN ALIGNEI<br>2 IOCHAN,<br>3 IOM UBIN(6) UN<br>3 CHANNEL UBIN(6) UN<br>2 STATUS UBIN(6) UN | D,<br>AL,<br>) UNAL,<br>NAL, | <pre>/* LINK TO NEXT CHANNEL ON LINK ADA /* GATE ON DRIVER QUEUE */ /* IOM NUMBER */ /* CHANNEL NUMBER */ /* CHANNEL STATUS (UP,DOWN,T&amp;D) */ /* LINK ADAPTER NUMBER */ /* SCHEDULING STATE */ /* LOST INTERRUPT FLAG */ /* -&gt; SUBSYSTEM QUEUE HEADER */ /* HEAD OF DRIVER QUEUE */ /* ERROR STATISTICS */</pre> |

# %MEND;

٠,

**n** .

| SF section | : | 14.4    |

|------------|---|---------|

| doc #      | : | 0257A-0 |

| date       | : | 771212  |

| page       | : | 22      |

### 4.7 Subsystem Queue Header (NI\$SQH)

For each configured peripheral subsystem, there is a Subsystem Queue Header. It contains configuration and scheduling information for that subsystem. Each Subsystem Table entry consists of two sections: the first is global data, and the second is a table of data for each Link Adapter on the subsystem.

# %MAC NI\$SQH(NAME=NI\$SQH, STCLASS=BASED);

DCL 1 NAME STCLASS ALIGNED, 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 0 1 2 3 4 5 6 7 8 OGATE 1 DCT\$ -----3 | A Q \$ \_\_\_\_\_ ----4 | L A 51 DQH\$ 61 ERROR LEVEL 2 ARRAY: 4 (' 4'O) ENTRIES TOTAL. 2 GATE SBIN ALIGNED, /\* GATE ON SCHEDULING TABLES \*/ 2 DCT\$ PTR, /\* -> FIRST DCT ENTRY \*/ /\* NUMBER OF DEVICES \*/ 2 NDCT UBIN(6) UNAL, /\* NUMBER OF LINK ADAPTERS \*/ /\* NEXT LINK ADAPTER INDEX \*/ /\* HEAD OF ASSIGN QUEUE \*/ 2 NLA UBIN(3) UNAL, 2 LAX UBIN(3) UNAL, 2 AQ\$ PTR, /\* LINK ADAPTER TABLE: \*/ 2 LA(0:3), 3 NCHAN UBIN(6) UNAL, 3 NACT UBIN(6) UNAL, /\* NUMBER OF CONFIGURED CHANNELS \*/ /\* NUMBER OF ACTIVE CHANNELS \*/

- 3 STATUS UBIN(2) UNAL, /\* LINK ADAPTER STATUS (UP, DOWN, T&D 3 DQH\$ PTR, /\* -> NEXT CHANNEL'S DRIVER QUEUE H

- /\* ERROR STATISTICS \*/

%MEND:

3 ERROR UBIN(36):

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 23      |

# 4.8 IOM Table

A 5

The IOM table contains data needed to manage the overhead channels of an IOM. There is a table of pointers to the IOM table packets; this pointer table is indexed by the IOM number.

|   | NI\$IOM(NAME<br>1 NAME STCLA                                                                                              | SS ALI                                                             | GNE                             | D.                   |     |     |    |   |                          |     |                                              |                              |                                             |                             |                                 | _                           |                                   |                  |              |                  |   | _  |      | _   |

|---|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------|----------------------|-----|-----|----|---|--------------------------|-----|----------------------------------------------|------------------------------|---------------------------------------------|-----------------------------|---------------------------------|-----------------------------|-----------------------------------|------------------|--------------|------------------|---|----|------|-----|

| 1 | 0 1 2 3 4 5                                                                                                               | 678                                                                | 0 1                             | 2                    | 3   | 4 5 | 56 | 7 | 8 0                      | 1   | 2                                            | 3                            | 4 5                                         | 56                          | 7                               | 8                           | 01                                | 2                | 3            | 4                | 5 | 6  | 7    | 8   |

| 0 | GATE                                                                                                                      | •                                                                  |                                 |                      |     |     |    |   | •                        |     |                                              |                              |                                             |                             |                                 |                             | •                                 |                  |              |                  |   |    |      | . – |

| 1 | MBX\$                                                                                                                     |                                                                    |                                 |                      |     |     |    |   |                          |     |                                              |                              |                                             |                             |                                 |                             |                                   |                  |              |                  |   |    |      |     |

| 2 | IOM#                                                                                                                      | LASTCO                                                             | N N                             |                      | NE  | XTF |    |   | - i -<br>I N             | EXT | ſS                                           |                              |                                             | M                           | AX                              | 5                           | i<br>I                            |                  | ¦ *          |                  |   | AD | DR   | E   |

| 3 | FLTBUF                                                                                                                    |                                                                    |                                 |                      |     |     |    |   | IS                       | PE  | CBU                                          | F                            |                                             |                             |                                 |                             | <br>                              |                  |              |                  |   |    |      |     |

|   | 2 GATE SBI<br>2 MBX\$ PTF<br>2 IOM# UBJ<br>2 LASTCON<br>2 NEXTF UE<br>2 NEXTS UE<br>2 MAXS UBJ<br>2 * BIT(3)<br>2 ADDRESS | IN ALIG<br>,<br>IN(6) U<br>UBIN(6)<br>BIN(6)<br>BIN(6) U<br>N(6) U | NED<br>NAL<br>) U<br>UNA<br>UNA | ,<br>NAL<br>L,<br>L, | • 9 |     |    |   | / * * * *<br>/ / * * * * |     | ATE<br>> M<br>OM<br>AST<br>NDE<br>NDE<br>ORS | O<br>AI<br>NU<br>C<br>X<br>T | N C<br>LBC<br>MBE<br>ONN<br>TO<br>TO<br>CAS | ON<br>XE<br>IEC<br>NE<br>NE | NE<br>S<br>TE<br>XT<br>XT<br>NE | CT<br>*/<br>D(<br>W(<br>XT: | CHA<br>CHAN<br>DRD<br>DRD<br>S */ | INE<br>INE<br>IN | EL<br>F<br>S | */<br>AUI<br>PE( |   | BU | न न। | 71  |

2 FLTBUF UBIN(18) UNAL, /\* LOC. OF FAULT BUFFER (IN REAL) \* 2 SPECBUF UBIN(18) UNAL; /\* LOC. OF SPECIAL INTERRUPT BUFFER

| SF section | : | 14.4    |

|------------|---|---------|

| doc #      | : | 0257A-0 |

| date       | : | 771212  |

| page       | : | 24      |

# 5. PROCEDURES

#### 5.1 Driver (NIS\$DRIVER)

The Driver starts the I/O operation for the first request on a given Driver Queue.

# Calling Sequence

CALL NIS\$DRIVER(DQH\$);

where: DQH\$ points to a Driver Queue Header.

#### Entry Conditions

Interrupts must be disabled. The Driver Queue must not be locked. The channel must not be busy.

# Exit Conditions

The I/O is started. The Driver Queue is not locked.

#### Description

The PCW (Peripheral Control Word) is set up from the PCW and PTP fields of the request packet and the channel number of the Driver Queue Header. The payload channel mailbox is set up to point to the DCW list and status doubleword of the request packet. The CIOC is then issued with the connect channel mailbox pointing to the PCW. Since the Driver may be called by the device Scheduler or the device Poster, it must be able to run with interrupts enabled or disabled. The Driver does not remove the first request from the Driver Queue; it is removed by the device Poster.

| SF section | : | 14.4    |

|------------|---|---------|

| doc #      | : | 0257A-0 |

| date       | : | 771212  |

| page       | : | 25      |

# 5.2 Interrupt Distributor (NIS\$INTDIS)

The Interrupt Distributor determines the interrupting channel and calls the associated Poster.

# Calling Sequence

The Interrupt Distributor is called by the wired-in CLIMB instruction to the entry descriptor at location 30(octal). This entry descriptor must be type 11 and must specify the Monitor's Linkage Segment, the Monitor's privileged Instruction Segment, and WSR (Working Space Register) number 0.

# Description

The Interrupt Distributor determines the interrupt level and the interrupting channel number from the Interrupt Cell number in the Safe-Store Frame and the corresponding IMW (Interrupt Mask Word). If the interrupt was from the system fault channel or the special status channel, the fault word or special status word, respectively, is examined to determine the associated payload channel number. The fault word or special status word is altered to look like a peripheral status word by inserting a major status code of 17(octal) for a fault interrupt or 16(octal) for a special interrupt. The fault word or special status word is passed to the device Poster along with the Driver Queue Header of the interrupting payload channel and the interrupt level. The device Poster for the payload channel is then called to process the interrupt. On return from the device Poster, the Interrupt Distributor loops back to process any other interrupts that were indicated in the current IMW. When all of them have been processed, the Interrupt Distributor returns to the interrupted routine.

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 26      |

# 5.3 Lost Interrupt Poller (NIS\$LOSTINT)

The Lost Interrupt Poller is called periodically to check for lost interrupts.

# Calling Sequence

CALL NIS\$LOSTINT;

#### Entry Conditions

Interrupts must be enabled. No driver queues may be locked.

#### Exit Conditions

Interrupts will be enabled. No driver queues will be locked.

# Description

The Lost Interrupt Poller is called periodically, say, every 5-10 seconds. Each time it is called, it scans all of the channels' Driver Queue Headers. For each channel, if the Lost Interrupt Flag is not set and the channel is active, the Lost Interrupt Flag is set. If the Lost Interrupt Flag is already set, a lost interrupt condition has occurred, since the channel has been active since the previous polling cycle. (The Lost Interrupt Flag is cleared by the Driver when starting a request and by the Interrupt Distributor when a termination interrupt occurs.) The lost interrupt is reported to the device handler by calling the device Poster with a unique interrupt level. Interrupts are disabled while each channel is being processed.

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 27      |

# 5.4 Lock Gate Routine (NIS\$LOCK)

The Lock Gate routine is a fast assembly-language routine for locking a gate.

# Calling Sequence

CALL NIS\$LOCK(GATE);

where: GATE is the gate to be locked.

#### Entry Conditions

GATE must be a word-aligned 36-bit field.

#### Exit Conditions

The gate is locked.

#### Description

A gate is used to synchronize code sequences running in two or more CPUs. The gate is locked when its value is zero. When a gate has been locked by one CPU, it cannot be locked by any other CPU. This routine locks a gate by using a Load Accumulator and Clear (LDAC) instruction. If the gate is already locked, NIS\$LOCK loops on the LDAC until it is unlocked. If the gate is locked for an excessive length of time (more than 16 ms.), the system will crash with a lockup fault. The gate may be unlocked merely by storing a non-zero value into it.

SF section: 14.4 doc # : 0257A-0 date : 771212 page : 28

### 5.5 Queue Handling Macros

These PL-6 macros are provided for enqueuing and dequeuing packets from FIFO queues.

Calling Sequences

To enqueue a packet at the tail of a queue:

%ENQUEUE(P#=P\$,Q#=Q\$);

To enqueue a packet at the head of a queue:

%REQUEUE(P#=P\$,Q#=Q\$);

To dequeue a packet from the head of a queue:

%DEQUEUE(P#=P\$,Q#=Q\$);

where:

P\$ points to the packet to be queued, or, on return, points to the packet dequeued.

Q\$ points to the queue header.

Entry Conditions

None

Exit Conditions

ENQUEUE REQUEUE

The specified packet has been linked into the queue.

DEQUEUE

The first packet on the specified queue has been removed from the queue and returned in P\$. If the queue is empty, P\$=ADDR(NIL) is returned.

#### Description

If the queue is empty, ENQUEUE and REQUEUE set the queue header to point to the new packet, and set the link field of the packet to point to itself. If the queue is not empty, ENQUEUE inserts the new packet after the packet pointed to by the queue header, then sets the queue header to point to the new packet. REQUEUE inserts the new packet after the packet pointed to by the queue header but does not change the queue header.

If the queue is empty, DEQUEUE returns P\$=ADDR(NIL). If not, it unlinks the packet following the packet pointed to by the

| SF section | n: | 14.4    |

|------------|----|---------|

| doc #      | :  | 0257A-0 |

| date       | :  | 771212  |

| page       | :  | 29      |

|            |    |         |

.

queue header and returns it to the caller. If this is the last packet on the queue, the queue header is set to ADDR(NIL).

| SF section | <b>n</b> : | 14.4    |

|------------|------------|---------|

| doc #      | :          | 0257A-0 |

| date       | :          | 771212  |

| page       | :          | 30      |

# 5.6 Device Scheduler (NIx\$SCHED)

The device Scheduler enqueues the device on the Assign Queue, assigns a channel to the device, and schedules a list of requests to be executed.

# Calling Sequence

CALL NIx\$SCHED(DCT\$);

where:

DCT\$ points to the Device Control Entry for the device.

#### Entry Conditions

Interrupts are enabled. The Subsystem Tables and Driver Queue are not locked.

### Exit Conditions

If a channel was available, I/O has been started. Interrupts are enabled. The Subsystem Tables and Driver Queue are not locked.

#### Description

On entry to the device Scheduler, if there are requests on the device's Scheduler Queue and the device is not busy, it is enqueued on the Assign Queue. Then, if there is an available channel, the first device on the Assign Queue is removed and assigned to the next available channel, and requests from the device's Scheduler Queue are moved to the channel's Driver Queue. For most devices, only one list of requests will be moved to the Driver Queue at a time. However, in order to minimize disk rotational latency, all of the disk requests for a cylinder will be moved to the Driver Queue as a group. The Driver is then called to start the first request. On return from the Driver, the device Scheduler loops back to process another channel. When there are no more available channels or no entries on the Assign Queue, the Device Scheduler is done.

SF section: 14.4 doc # : 0257A-0 date : 771212 page : 31

# 5.7 <u>Device Poster (NIx\$POSTER)</u>

The device Poster analyzes interrupts, calls the Driver to restart the channel, performs error recovery, and returns completed requests to IOQ for end-action processing.

#### Calling Sequence

CALL NIx\$POSTER(DQH\$,LEVEL,STATUS);

#### where:

٤°

DQH\$ points to the Driver Queue Header of the interrupting payload channel.

LEVEL is the interrupt level:

| 0 | overhead    |

|---|-------------|

| 1 | termination |

| 2 | marker      |

| 3 | special     |

STATUS is the fault word or special status word.

# Entry Conditions

Interrupts are disabled. The Driver Queue is not locked.

#### Exit Conditions

Interrupts are disabled. The Driver Queue is not locked. 1

# Description

The device Poster is called by the Interrupt Distributor to process the interrupt. If this is a termination interrupt, the current request is removed from the Driver Queue. If there were no errors, the Driver is called to start the next request on the Driver Queue. Marker interrupts are ignored; this interrupt level is included for the Front End (Direct Channel) Handler. If this is a special interrupt, <u>i.e.</u>, an asynchronous interrupt, it may be used by error recovery routines; otherwise it will be passed to IOQ for a possible caller of special interrupt control. If this is a fault interrupt, the fault word is stored in the second status word of the current

If there were no errors or the errors were unrecoverable, the completed request is returned to IOQ for end-action processing. If a recoverable error occurred, the appropriate error recovery technique is applied. To retry the operation, the device Scheduler is called. If repositioning is required, reserved request packets are used to effect the repositioning.

| SF section: | 14.4    |

|-------------|---------|

| doc # :     | 0257A-0 |

| date :      | 771212  |

| page :      | 32      |

# 6. IOQ INTERFACES FOR IOS

The following entry points to IOQ are used only by IOS.

# 6.1 I/O Completion Routine (NIO\$COMP)

NIO\$COMP performs all caller- and user-related actions related to I/O completion.

# Calling Sequence

CALL NIO\$COMP(Q\$);

where: Q\$ points to the request.

#### Entry Conditions

Interrupts are enabled. No gates are locked.

#### Exit Conditions

The request packet has been either returned to the caller, requeued for a new operation, or released.

#### Description

From the hardware status words, NIO\$COMP sets the completion code, actual record size, and actual record count fields of the IOQ Request Packet and releases the IOS Request Packet. Then, depending on the setting of bits in the request's OPFLG field, NIO\$COMP may do one or more of the following:

- o Set completion information in the user's DCB.

- o Report an "I/O Completion" event to the Job Scheduler.

- Call an end-action routine. (Note: an end-action routine may not request any resources, such as request packets.)

- o Requeue the IOQ Request Packet for a New I/O operation.

- o Release the packet.

| SF section: | 14.4    |

|-------------|---------|

| doc# :      | 0257A-0 |

| date :      | 771212  |

| page :      | 33      |

# 6.2 Special Interrupt Completion Routine (NIO\$SPCOMP)

If a caller has requested special interrupt control, NIO\$SPCOMP calls his end-action routine.

# Calling Sequence

CALL NIO\$SPCOMP(DCTX, STATUS);

where:

DCTX is the Device Table Index of the interrupting device. STATUS is the special interrupt hardware status word.

#### Entry Conditions

Interrupts are enabled. No gates are locked.

# Exit Conditions

If this special enterrupt has been requested, the caller's end-action routine has been called.

#### Description

NIO\$SPCOMP is called for every special interrupt that is not used by the device Poster. It checks the Device Table to see if this special interrupt has been requested. If so, the requestor's end-action routine is called with the hardware status word. (Note: an end-action routine may not request any resources, such as request packets.)

٤.,

PERIPHERAL DEVICES

FIG. 2.1

FIG. 3.1

FIG. 3.2