# Honeywell

# SERIES 6000 SUMMARY DESCRIPTION

# SERIES 6000 SUMMARY DESCRIPTION

# Table of Contents

| ı  | SERIES 6000 OVERVIEW 1                      | l  | Integrated Data Store (I-D-S) 19             |

|----|---------------------------------------------|----|----------------------------------------------|

|    | Growth and Flexibility 1                    | 1  | I-D-S Concurrent Access 20                   |

|    | The Models 1                                |    | I-D-S Data Query 20                          |

|    | Additional Benefits 1                       |    | Indexed-Sequential Processor (ISP) 20        |

|    | GECOS 6000 2                                |    | System Software 20                           |

|    | Common File System 2                        |    | Loader 21                                    |

|    | Batch Processing 2                          |    | File and Record Control 21                   |

|    | Remote Processing 2                         |    | Bulk Media Conversion (BMC) 21               |

|    | Transaction Processing 2                    |    | System Editor 21                             |

|    |                                             |    | Utility 21                                   |

|    | Time Sharing 3                              |    |                                              |

|    | Total On-Line Testing System (TOLTS) 3      | 1  | Time-Sharing System 21                       |

|    | HADDWADE OVEDVIEW A                         |    | Programming Languages 21                     |

| H  | HARDWARE OVERVIEW 4                         |    | Time-Sharing Batch 21                        |

|    | Functional Modularity 4                     |    | File Editing, Inspection, and Maintenance 22 |

|    | Memory Module 5                             |    | Time-Sharing System Extension and            |

|    | Processor Module 5                          |    | Maintenance 22                               |

|    | Input/Output Multiplexer (IOM) 6            | i  | Time-Sharing Library 22                      |

|    | Communications Processors 6                 |    | Applications Software 23                     |

|    | Series 6000 Characteristics 7               |    | Linear Programming System (LP 6000) 23       |

|    |                                             |    | Automatically Programmed Tools (APT) 23      |

| Ш  | GENERAL COMPREHENSIVE OPERATING             |    | PERT/TIME 24                                 |

|    | SUPERVISOR (GECOS) 6000 9                   |    | PERT/COST 24                                 |

|    | Features of GECOS 9                         |    | SIMSCRIPT 24                                 |

|    | Batch Processing 9                          |    | Time Series Forecasting 24                   |

|    | Job/Activity Definition 9                   |    | Civil Engineering Package (CEP) 24           |

|    | Job Flow 10                                 |    | Biomedical Statistical Programs (BMD) 25     |

|    | Job Input 10                                |    | MATHPAC 25                                   |

|    | System Scheduler 10                         |    | Generalized Parts Explosion System           |

|    | Allocator Queue 10                          |    | (GEPEXS) 25                                  |

|    | Activity Allocation 10                      |    |                                              |

|    | Activity Anocation 10 Activity Execution 11 | İ  | Generalized Inventory Management System      |

|    |                                             |    | (GEIMS) 25                                   |

|    | Activity/Job Termination 12                 | 1  | dataBASIC System 25                          |

|    | Job Output 12                               | ., | MEMORY MORIUS - AC                           |

|    | Multiprocessing 12                          | V  | MEMORY MODULE 26                             |

|    | Remote Processing 13                        |    | System Controller Characteristics 26         |

|    | Remote Batch 13                             |    | Model 6030/6040 System Controller and        |

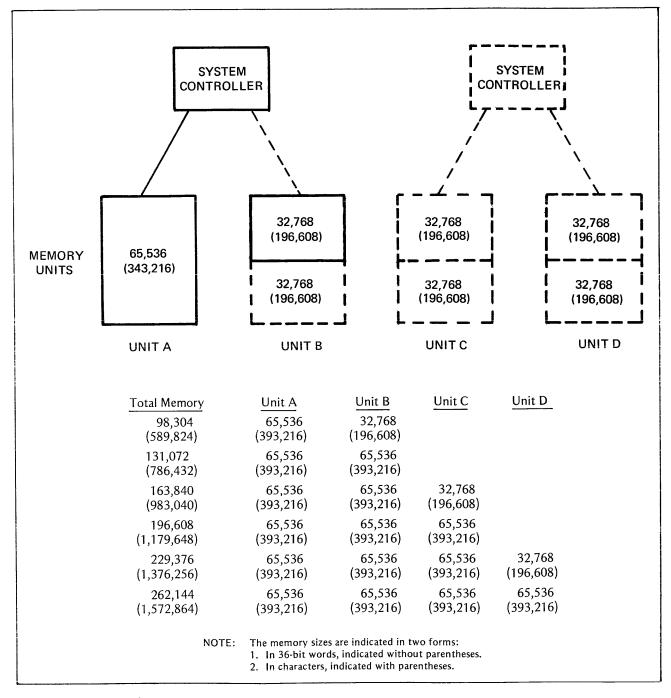

|    | Remote Access 13                            | 1  | Memory 27                                    |

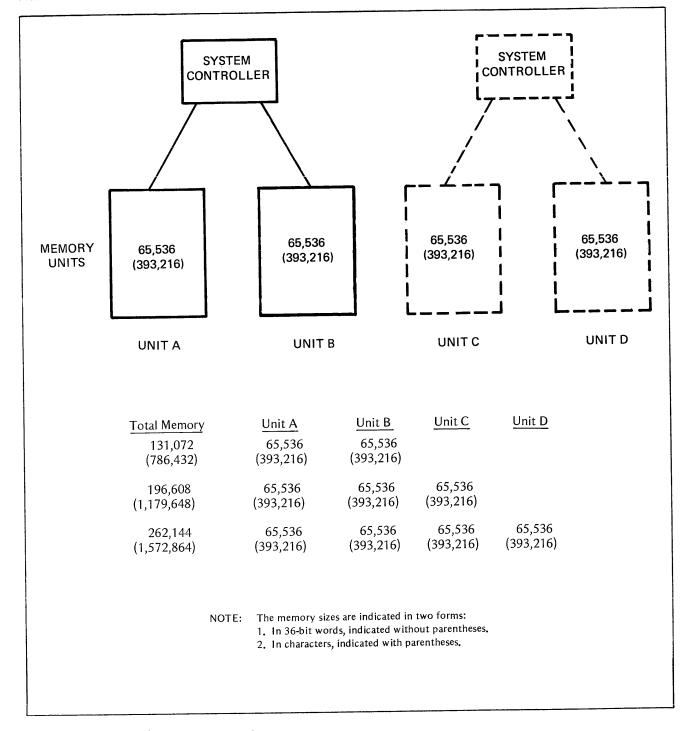

|    | Transaction Processing 13                   | 1  | Model 6050/6060 System Controller and        |

|    | Time Sharing 13                             |    | Memory 28                                    |

|    | Communications/Mass Store Link 14           |    | Model 6070/6080 System Controller and        |

|    | File System 15                              |    | Memory 29                                    |

|    | Total On-Line Testing System (TOLTS) 16     |    | System Controller Ports 30                   |

|    | Peripheral On-Line Testing System 16        |    | Memory Addressing 30                         |

|    | Communications On-Line Testing System 16    | İ  | Memory Interleaving 30                       |

|    | Main Frame On-Line Testing System 16        |    | Interrupt Orientation 30                     |

|    | Remote On-Line Testing System 17            |    |                                              |

|    | Off-Line Test and Diagnostic System 17      | VI | PROCESSOR 31                                 |

|    | ,                                           |    | Extended Instruction Set (EIS) 31            |

| IV | SOFTWARE OVERVIEW 18                        |    | Salient Features of the EIS 31               |

|    | Language Processors 18                      |    | System Configuration Flexibility 32          |

|    | Macro Assembler 18                          | ĺ  | Register Descriptions 32                     |

|    | Fortran Compiler 18                         |    | EIS Register Descriptions 32                 |

|    | COBOL Compiler 18                           |    | Word Formats 33                              |

|    | ALGOL Compiler 19                           | 1  | Fixed-Point Data 33                          |

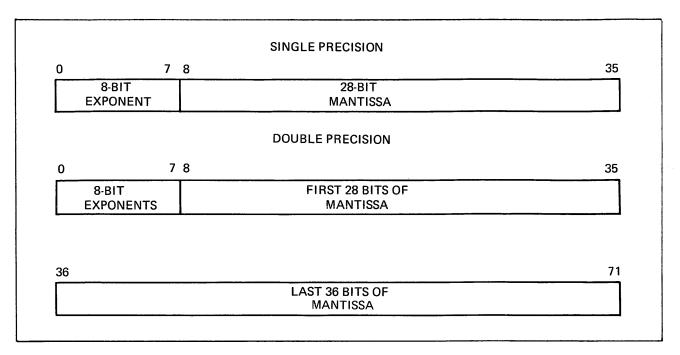

|    | JOVIAL Compiler 19                          | 1  | Floating-Point Binary Data 33                |

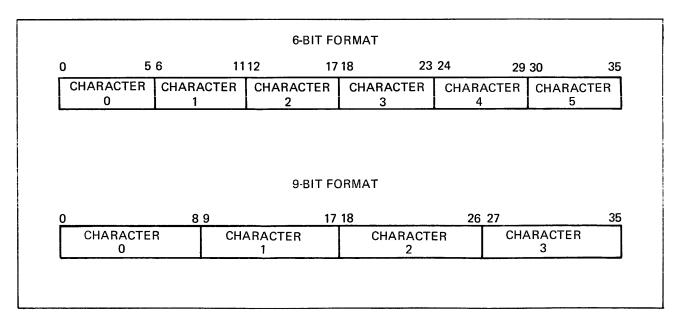

|    | Sort/Merge 19                               |    | Alphanumeric Data 33                         |

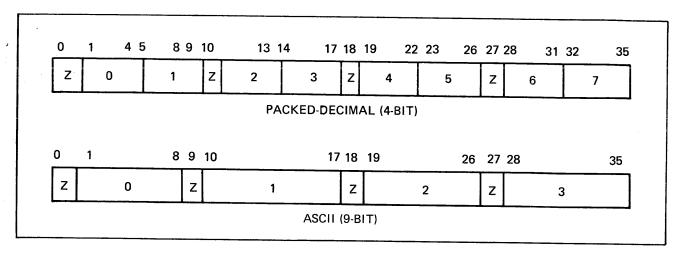

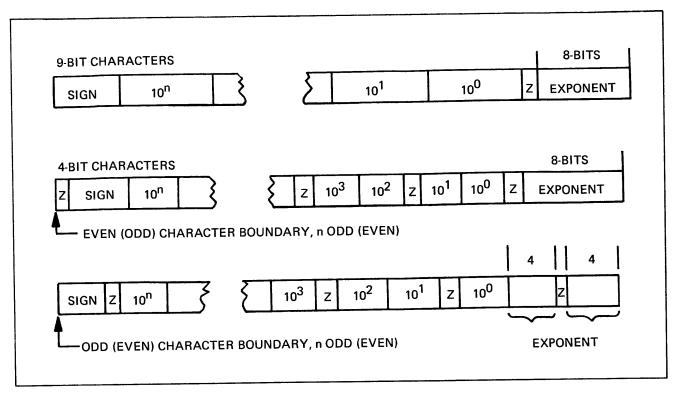

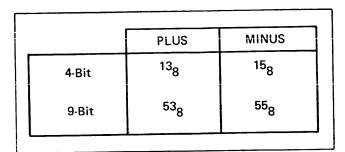

|       | Packed Decimal Data 34                                                                | N                                                                 | lagnetic Tape Subsystems 59                                           |  |  |

|-------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

|       | Floating-Point Decimal Data 35                                                        |                                                                   | RT300 Printer and Control 61                                          |  |  |

|       | Instruction Format 36                                                                 | j .                                                               | RT201 Printer and Control 61                                          |  |  |

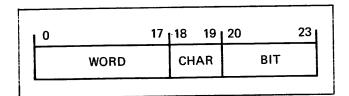

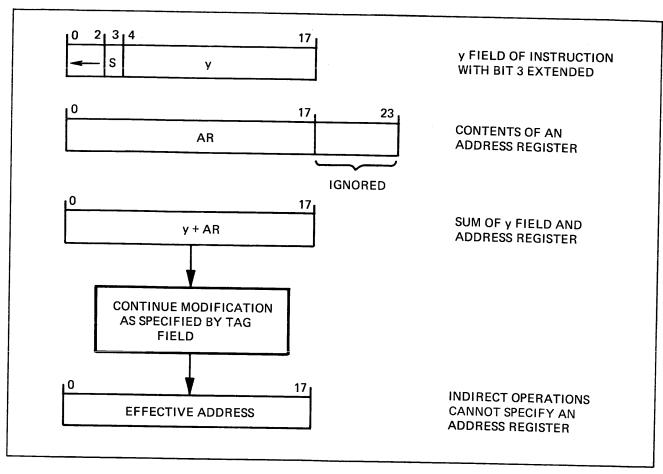

|       | Address Modification 37                                                               |                                                                   | RZ201 Card Reader and Control 62                                      |  |  |

|       | Modification Types 37                                                                 | <u> </u>                                                          | PZ201 Card Punch and Control 62                                       |  |  |

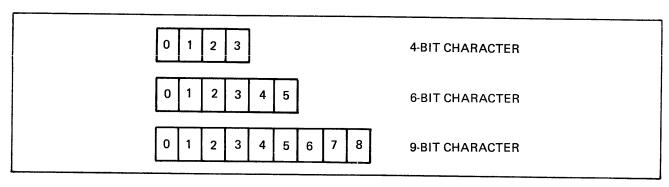

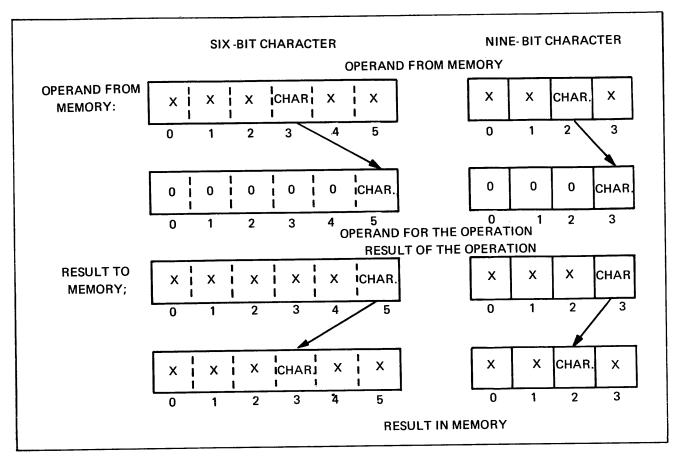

|       | Character Operations 37                                                               |                                                                   | . 2201 2414 1 511011 4114 2011(10)                                    |  |  |

|       | EIS Address Modification 37                                                           | Appendix A                                                        | Instruction Execution Times 63                                        |  |  |

|       | Instruction Repertoire 38                                                             | Appendix B                                                        | Preliminary Timing Formulas for EIS Processors 69                     |  |  |

|       | Data Movement 39                                                                      | Appendix C                                                        | Complete List of EIS Instructions 80                                  |  |  |

|       | Fixed-Point Arithmetic (Binary) 39                                                    | Appendix D                                                        | Complete List of Micro Operations 82                                  |  |  |

|       | Boolean Operations 40                                                                 | Appendix E                                                        | Series 6000 Six-bit BCD Character Set 83                              |  |  |

|       | Comparison 40                                                                         | Appendix E Appendix F                                             | American Standard Code for Information Interchange                    |  |  |

|       | Floating-Point Arithmetic (Binary) 40                                                 | Appendix                                                          | (ASCII) 84                                                            |  |  |

|       | Transfer of Control 40                                                                |                                                                   | (ASCII) 64                                                            |  |  |

|       | Execute Instructions 41                                                               |                                                                   |                                                                       |  |  |

|       | Code Conversion Instructions 41                                                       |                                                                   |                                                                       |  |  |

|       |                                                                                       | l ist of                                                          | Illustrations                                                         |  |  |

|       | Gating Instructions 41                                                                | LISTO                                                             | แนรแสแบบร                                                             |  |  |

|       | Master Mode Instructions 41 EIS Processor Instructions 41                             | Figure 1 M                                                        | odel 6030 – Entry into the Series 6000                                |  |  |

|       |                                                                                       | Figure I - M                                                      |                                                                       |  |  |

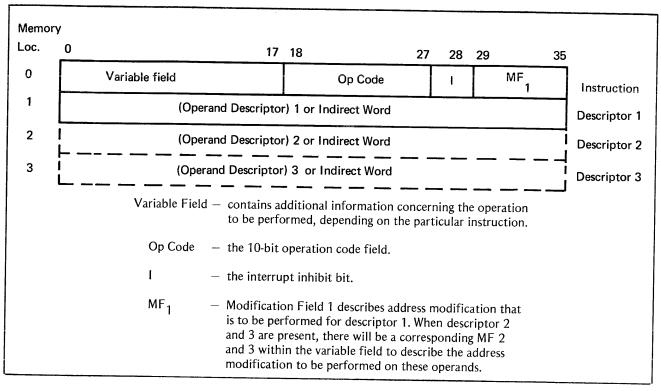

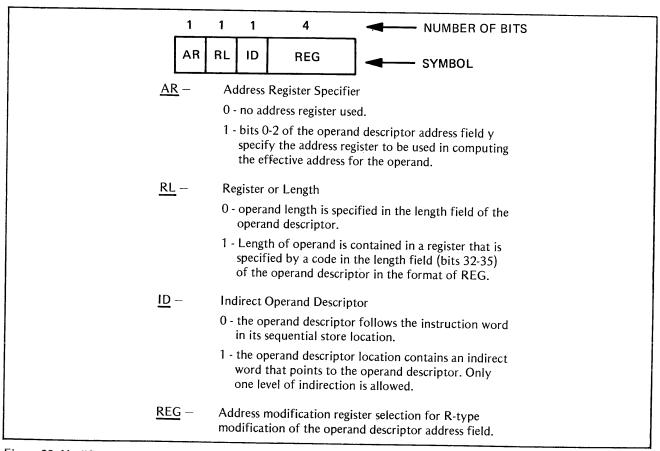

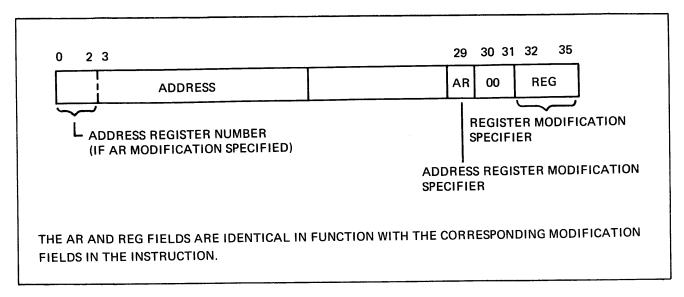

|       | EIS Multiword Instruction Format 41                                                   | Eiguro 2 M                                                        | Family 1                                                              |  |  |

|       | EIS Multiword Instruction Repertoire 45                                               | Figure 2 – Model 6080 – Top Model of the Series 6000<br>Family 2  |                                                                       |  |  |

|       | EIS Single-Word Instruction Repertoire 45                                             | Eiguro 2 E                                                        |                                                                       |  |  |

|       | EIS Edited Move Micro Operations 46                                                   | Figure 3 — Functional-Modularity 4<br>  Figure 4 — Basic System 7 |                                                                       |  |  |

| \/II  | INDUTION THE MULTIPLE VED (IOM) 47                                                    |                                                                   | ultidimensional System 8                                              |  |  |

| VII   | INPUT/OUTPUT MULTIPLEXER (IOM) 47                                                     |                                                                   | ultiprocessor System 8                                                |  |  |

|       | IOM Description 47                                                                    |                                                                   | ommunications/Mass Store Link 14                                      |  |  |

|       | Data Channels 47                                                                      | , -                                                               |                                                                       |  |  |

|       | Common Peripheral Channels 47                                                         |                                                                   | ile System Structure 15<br>PT Remote Program Flow Chart 23            |  |  |

|       | Peripheral Subsystem Interface Channels 47                                            |                                                                   | Time Series Forecasting and Analysis Graph 24                         |  |  |

|       | Special Channels 47                                                                   |                                                                   |                                                                       |  |  |

|       | Bootload Channel 48                                                                   |                                                                   | Sample Response Surface for MATHPAC Analysis 25                       |  |  |

|       | Connect Channel 48                                                                    |                                                                   | Model 6030/6040 Memory Configuration 27                               |  |  |

|       | System Fault Channel 48                                                               |                                                                   | Model 6050/6060 Memory Configuration 28                               |  |  |

|       | Wraparound Channel 48                                                                 |                                                                   | Model 6070/6080 Memory Configuration 29                               |  |  |

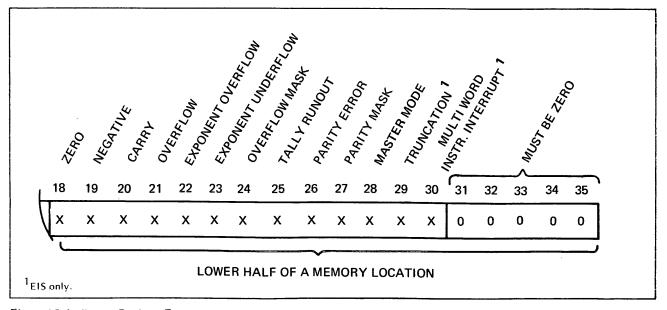

|       | Snapshot Channel 48                                                                   |                                                                   | ndicator Register Format 32                                           |  |  |

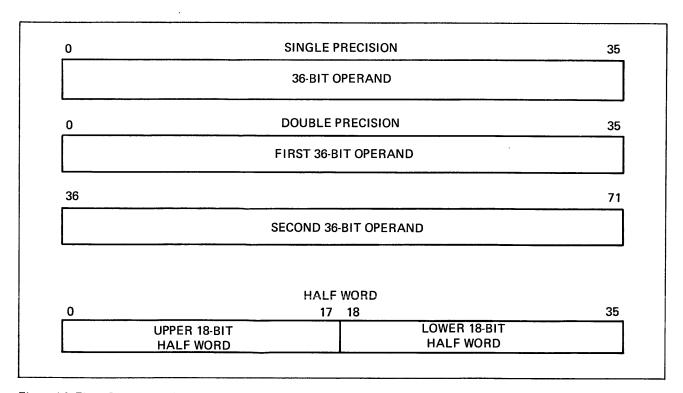

|       | Scratchpad Access Channel 48                                                          |                                                                   | Fixed-Point Data Formats 33                                           |  |  |

|       | Data Communications Interface 48                                                      |                                                                   | Floating-Point Data Formats 34                                        |  |  |

|       | Scatter-Gather Capability 48                                                          | Figure 18 – 3                                                     | Six-Bit and Nine-Bit Alphanumeric Data                                |  |  |

|       | IOM Memory Protection 48                                                              | F: 10                                                             | Formats 34                                                            |  |  |

|       | IOM Program Interrupts 48                                                             |                                                                   | Decimal Formats for EIS 35                                            |  |  |

| 1/111 | DEMOTE INDUT/OUTDUT OPERATIONS 40                                                     |                                                                   | Bit Positions for EIS Bit String Mode 35                              |  |  |

| VIII  | REMOTE INPUT/OUTPUT OPERATIONS 49 Remote Processing Capabilities 49                   |                                                                   | Floating-Point Decimal Formats 36                                     |  |  |

|       | DATANET 355 Processor 49                                                              |                                                                   | Decimal Sign Position Formats 36<br>General Instruction Format 36     |  |  |

|       |                                                                                       | 1 ~                                                               |                                                                       |  |  |

|       | Communications Subsystem 49 High-Speed Line Adapter (HSLA) 50                         |                                                                   | Typical Character Operations 38<br>Address Register Format 38         |  |  |

|       |                                                                                       |                                                                   |                                                                       |  |  |

|       | Low-Speed Line Adapter (LSLA) 50<br>System Organization 50                            | Figure 20 -                                                       | Address Modification of a Single-Word Instruc-                        |  |  |

|       | DATANET 30 Processor 50                                                               | Eiguro 27                                                         | tion with the Use of an Address Register 39 Fixed-Point Comparison 40 |  |  |

|       | Features 50                                                                           |                                                                   | Extended Instruction Format 42                                        |  |  |

|       |                                                                                       |                                                                   |                                                                       |  |  |

|       | System Configurations 50 DATANET 305 Processor 50                                     |                                                                   | Modification Field Format 42                                          |  |  |

|       |                                                                                       |                                                                   | Operand Descriptor 43 Operand Descriptors by Type 43                  |  |  |

|       | System Configurations 50                                                              |                                                                   | Micro Operation Format 46                                             |  |  |

| IV    | DEDIBLED AL CLIDOVOTEMO 52                                                            |                                                                   | DATANET 355 Communications Subsystem 51                               |  |  |

| IX    | PERIPHERAL SUBSYSTEMS 52 Control Console 52                                           |                                                                   | Control Console 52                                                    |  |  |

|       |                                                                                       |                                                                   | DSS180 Basic Configuration 53                                         |  |  |

|       | DSS180 Removable Disk Storage Subsystem 52 DSS190 Removable Disk Storage Subsystem 53 |                                                                   | DSS180 Maximum Configuration 53                                       |  |  |

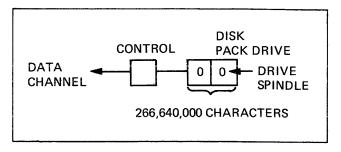

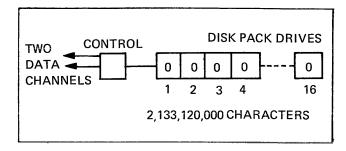

|       | DSS270 Disk Storage Subsystem 54                                                      |                                                                   | DSS180 Maximum Configuration 53 DSS190 Minimum Configuration 54       |  |  |

|       | DSS167 Removable Disk Storage Subsystem 56                                            |                                                                   |                                                                       |  |  |

|       | DSS170 Removable Disk Storage Subsystem 57                                            |                                                                   |                                                                       |  |  |

|       | TO INDIAVACIO DISTURBIO DI STOLICIO DI LOCA                                           | IEUI U JJ — 1                                                     | レンンとさい プロス きいいきと きいいくさいけい ブサ                                          |  |  |

VII

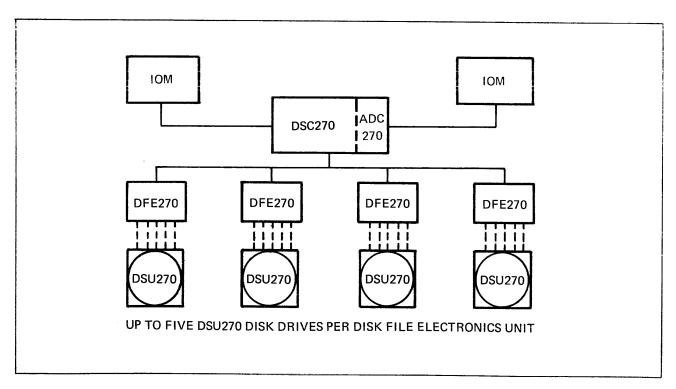

| Figure 40 — DSS270 Maximum Configuration 55           |

|-------------------------------------------------------|

| Figure 41 — DSS167 Disk Storage Subsystem 56          |

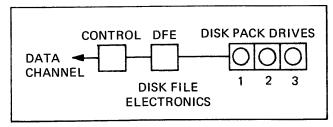

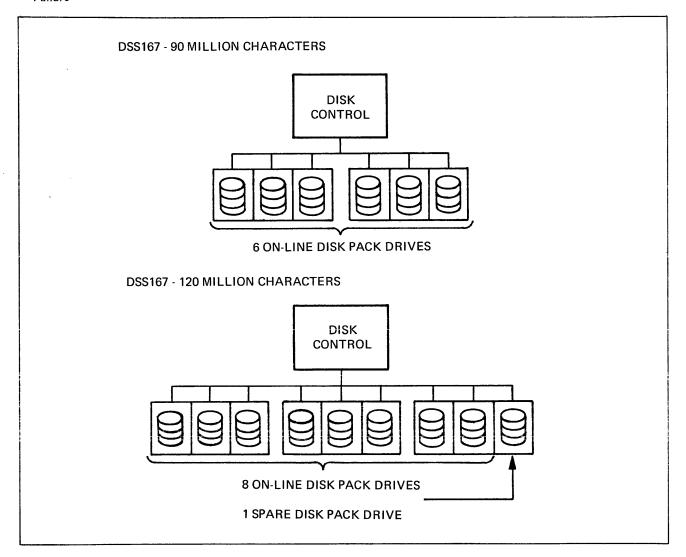

| Figure 42 – DSS167 Subsystem Configurations 57        |

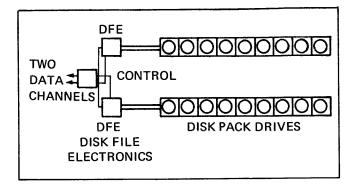

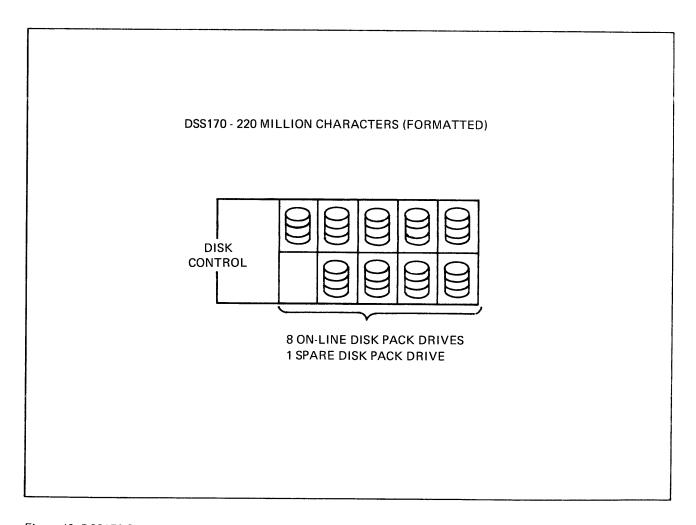

| Figure 43 – DSS170 Subsystem Configuration 58         |

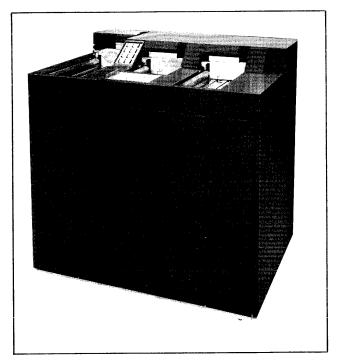

| Figure 44 — Magnetic Tape Unit 59                     |

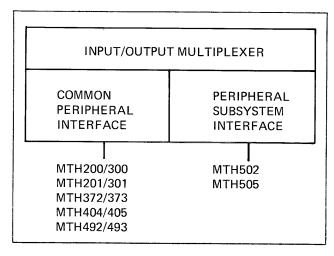

| Figure 45 — Magnetic Tape Interface 60                |

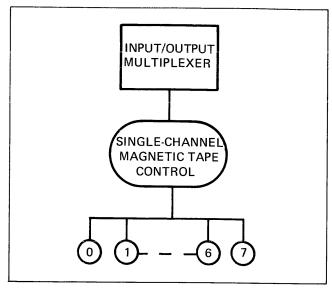

| Figure 46 — Single-Channel Magnetic Tape Subsystem 60 |

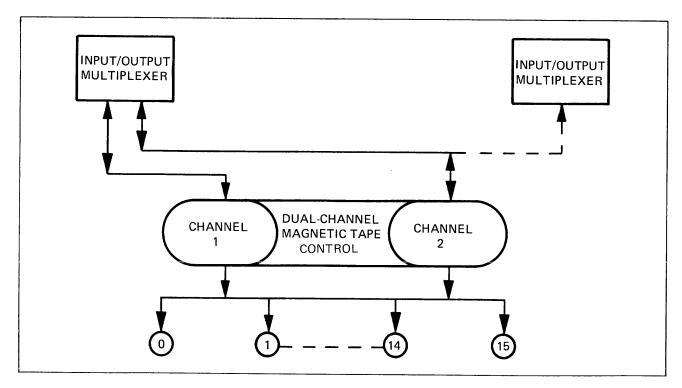

| Figure 47 — Dual-Channel Magnetic Tape Subsystem 60   |

| Figure 48 – PRT300 Printer 61                         |

| Figure 49 - PRT201 Printer 61                         |

| Figure 50 – CRZ201 Card Reader 62                     |

| Figure 51 — CPZ201 Card Punch 62                      |

|                                                       |

# List of Tables

# Section I

# Series 6000 Overview

The Honeywell Series 6000 is a family of large-scale, multidimensional information systems featuring high throughput, optimum use of system resources, and a wide spectrum of user-oriented capabilities.

The Series 6000 achieves an exceptionally high level of performance by operating in a total multiprogramming and multiprocessing environment. The system optimizes the use of its resources through concurrent processing in all dimensions — local and remote batch, remote access, transaction processing, and time sharing — all utilizing a common data base.

# **GROWTH AND FLEXIBILITY**

Each member of the Series 6000 family is an optimum blend of powerful, state-of-the-art hardware and time-tested software.

- The functional modularity of the hardware provides an orderly, natural path of growth as the needs of a company's business grow. Multiple processors can be added, or more memory, or more data communications.

- Through it all, the user's programming investment is safe. The GECOS time-proven operating system is in control of all systems, from the smallest to the largest. No reprogramming is necessary, no matter what new combination of Series 6000 hardware best fits the growth needs of a business. GECOS operates in all Series 6000 models and all hardware configurations. All the capabilities of GECOS are available at each and every hardware level.

### THE MODELS

Three models of the new family — Models 6030, 6050, and 6070 — are particularly well suited to mixed scientific, engineering, and business work loads. Price/performance in mixed-work load environments is outstanding. A few of the key features of these models are:

- Series 6000 Fortran with the highest compile speed in the industry.

- Efficiency the same fast Fortran compiler is used in both batch and time sharing.

- Data Base Management a common file system is accessible in all dimensions local and remote batch, remote access, time sharing, and transaction processing.

Three more members of the Series 6000 family — Models 6040, 6060 and 6080 — are specifically designed for heavy COBOL users. These models feature well over 100 new business-oriented instructions which provide powerful character string and decimal arithmetic capabilities. This extended instruction set closely correlates with the business source languages and significantly reduces program size (hence memory requirements). The result is faster and more economical processing of business oriented jobs.

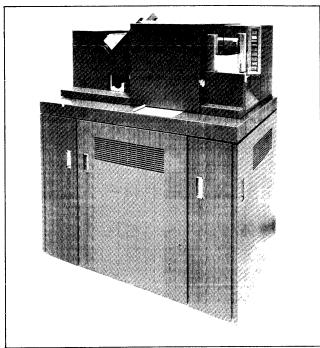

Figure 1. Model 6030 - Entry into the Series 6000 Family

The totally user-oriented features include:

- Full ANSI COBOL compiler

- Integrated Data Store (I-D-S), a powerful data base structuring technique

- Indexed-Sequential File Processing

- Unique Transaction Processing Executive

# ADDITIONAL BENEFITS

Bundled The Series 6000 systems come bundled —

basic support services, an extensive software library, several language compilers, education and training, and applications packages are

included in the basic system price.

**Applications** Some of the application tools available are:

Inventory Management System

Parts Explosion System

Automatically Programmed Tools (APT)

Linear Programming (LP 6000) PERT/TIME and PERT/COST SIMSCRIPT Simulation Language

Times Series Forecasting MATHPAC Subroutine Library

Languages Language capabilities include ANSI COBOL,

Fortran, ALGOL, JOVIAL, and a powerful macro-assembly language (GMAP), plus several problem-oriented languages and time-

sharing languages.

Maximum Series 6000 systems are built for maximum Up-Time Up-time. With the latest in integrated circuit

technology, improved packaging results in more compact and easily maintained hardware. Circuit testers and maintenance panels expedite system diagnosis and help to isolate malfunctions quickly. The total on-line testing and diagnostic routines in GECOS allow temporary deallocation of central system modules, peripherals, or communication subsystems for automatic checkout while normal processing continues in other system elements.

Figure 2. Model 6080 -Top Model of the Series 6000 Family

#### **GECOS 6000**

GECOS 6000 maintains the status of all system resources (peripherals, memory, and processors) and all user jobs in the system. Using the System Scheduler, the allocator queue accommodates a virtually unlimited number of jobs; these jobs can be entered into the system through multiple central and remote devices concurrent with the execution of jobs in the system. The jobs are dispensed to the system according to priorities and resource requirements. GECOS allocates system resources to jobs in the allocator queue in accordance with the priority of the job, and supervises the concurrent and simultaneous execution of as many programs (up to 63) as the configuration can accommodate. GECOS also controls the concurrent printing/punching of output from completed jobs. High-priority programs can be expedited by swapping out programs in execution.

GECOS also provides the programmer with a complete

logical approach to problem solution. There are no constraints or unusual programming considerations imposed on the programmer because of the multiprogramming or multiprocessing environment in which his program will be executed. File processing is performed sequentially or randomly at the logical file level; the programmer need not be concerned with the physical characteristics and constraints of the peripheral device used nor with the organization of the file system.

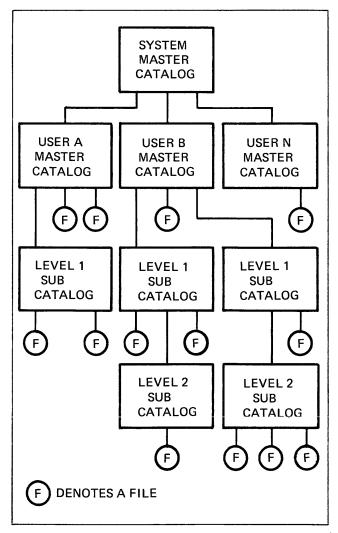

#### COMMON FILE SYSTEM

The "heart" of a Series 6000 Multidimensional Information System is a centralized file system of hierarchical, tree-structured design, accessible by programs operating in any of the dimensions. Catalogs and files are secured by passwords. File access is controlled by GECOS. Several programs can read and/or can update a file concurrently. A unique design feature of the file system allows maintenance (repacking) routines to be "cleaning up" a portion of the file system while production routines in concurrent operation are accessing other portions of the system.

# **BATCH PROCESSING**

GECOS 6000 provides a flexible, high-throughput batch processing environment. Up to 63 programs can be in concurrent execution. Incoming jobs are classified into a number of separately defined job streams, permitting each user to control his own priorities. Roll-out, roll-in capabilities allow for fast response to high-priority jobs or transactions. Batch jobs may be submitted from any local input device or remote terminal at any time, without operator intervention.

#### REMOTE PROCESSING

Concurrent remote processing capabilities can be added to Series 6000 systems by including one or more DATANET 30, DATANET 305, or DATANET 355 Communications Processors in the configuration. Each communications processor permits a variety of terminal, transmission rate, and processing options. Remote processing capabilities include remote batch, remote access, transaction processing, and time sharing. GECOS remote access uses a reactive terminal interface which provides direct terminal access (through the communications processor) to the information system and to the common file system, facilitating the development of "on-line" terminal applications.

# TRANSACTION PROCESSING

The Transaction Processing Executive opens the door to on-line, real-time data processing. Transactions (messages representing events in the user's business) can be entered via remote terminals. The Transaction Processing Executive interprets the transaction code contained in the message and calls the necessary application programs into execution to process the message. The output or acknowledgement will be returned to the designated terminal.

<sup>&</sup>lt;sup>1</sup>Trademark.

# TIME SHARING

A Time Sharing Executive, which utilizes the reactive terminal interface, provides Series 6000 installations with concurrent time sharing, featuring Fortran and BASIC, an easy to use, problem-solving language; and a powerful text-editing package to create, update, and obtain formatted printouts of textual data. Full upper/lower case ASCII character handling is provided.

Catalog structuring, file protection, file sharing, access control, and source/object file storage capabilities are provided through the file system.

The time-sharing batch capability permits time-sharing users to create and initiate batch mode programs and to scan or receive the batch output — all from a time-sharing terminal.

In addition, the structure of the Time Sharing Executive and the integration of time-sharing files in the file system facilitate user extension of the time-sharing system to provide further remote processing capabilities.

# TOTAL ON-LINE TESTING SYSTEM (TOLTS)

The Total On-Line Testing System is composed of four major subsystems for peripheral, communications, main frame, and remote processing. This on-line testing system is part of a total maintenance and recovery concept. Eight concurrent diagnostic programs can operate with user programs under GECOS.

# Section II

# Hardware Overview

Honeywell Series 6000 systems provide processing and input/output capabilities across a wide performance range. Systems are tailored to the specific work load and processing environment of an installation through the selection of the appropriate system model and by the configuration of central system modules and peripheral devices. System models are differentiated by the speed of the central system components.

With a system model, further performance flexibility is possible through "functional modularity," or the selection of central system modules to match the work load needs of the installation.

The Comprehensive Operating Supervisor, GECOS, is the same for all models and configurations and provides multidimensional processing capabilities from the smallest to the largest system.

# **FUNCTIONAL MODULARITY**

Series 6000 multidimensional systems employ a unique, new-design concept which provides complete flexibility in configuring the precise blend of processing, memory,

input/output, and communications resources to perform efficiently any given scientific/data processing work load mix. This concept also facilitates major system extension without reprogramming or conversion.

The major system functions of processing, memory, input/output, and communications control have been separated into the following discrete functional modules:

- Memory Modules to provide the required amount of core storage.

- Processor Modules to provide the required amount of computational capability.

- Input/Output Modules to control the required level of data input/output between memory and the peripheral and communications subsystems.

- Communications Processor Modules to control data communications functions and provide service to remote users.

Multiple modules of each type may be configured on an information system to match the processing, memory size, memory access, and data input/output requirements of an

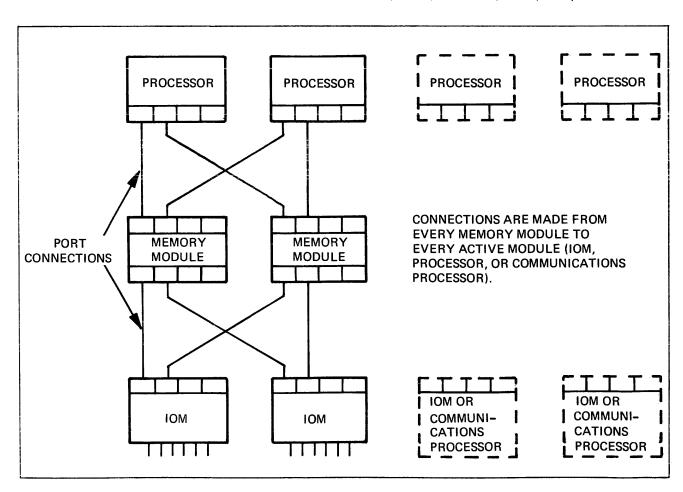

Figure 3. Functional Modularity

installation work load. This modular construction results in configurations that are tailored to the precise needs of an installation. System growth is readily accomplished by adding the appropriate modules as they are needed. Added reliability is a by-product of system extension, since all modules of a given type are identical and can provide back-up for each other.

The operating system (GECOS) automatically adapts itself to control any standard equipment configuration.

Figure 3 illustrates the way the central system modules are interconnected to provide a high degree of functional modularity and backup capability. The solid-line figures represent a configuration consisting of two processor modules, two memory modules, and two input/output multiplexer (IOM) modules. Every processor and IOM connects through ports to each memory module; these connections permit access to the full range of processors, memory, and peripherals. The broken lines represent expansion capabilities. The system grows by adding more processors, memory, input/output multiplexer modules, or communications processors.

#### MEMORY MODULE

Each memory module is composed of a system controller and associated memory units. Series 6000 systems are "memory-oriented," permitting processor and IOM functions to execute asynchronously and simultaneously.

The memory module has neither program execution nor arithmetic capability, but acts as a passive system component. It serves the processor and I/O multiplexer modules which call upon the memory module to save or retrieve information or to communicate with other system components.

Each word in the memory module is composed of 36 bits plus a parity bit. For purposes of memory protection in multiprogramming, the memory is organized into blocks of 1024 words each. Each memory module may contain up to 131,072 words (128 blocks). Additional memory modules permit a maximum of 262,144 words per system.

The system controller has up to eight ports for connection to active modules and also contains 32 program interrupt cells. The eight ports have "wired-in" positional priority in the order of their numbers  $(0\ldots7)$ ; thus, simultaneous requests are serviced in a predetermined manner.

Increased system throughput is achieved by operating the memory module and associated memory units on a 72-bit parallel basis. This corresponds to two instructions, two data words, or one double-precision fixed or floating-point number.

Systems with more than one system controller provide additional effective information rate, since each system controller operates independently and its functions can be overlapped with those of other system controllers.

Additional overlap is provided by the address interleaving feature of the Series 6000 systems. Address interleaving considerably reduces the possibility of the same memory unit being accessed in succession. Furthermore, the processor and system controller are especially designed to utilize memory accesses of two memory units in rapid succession. These two factors contribute to the higher access rates and effective memory cycle times of the Series 6000 systems. For example, Models 6070 and 6080 can have each of four memory units provide a complete memory cycle (read/write) of two full 36-bit words within a single basic cycle time of 500 nanoseconds — an effective rate of 62.5 nanoseconds per 36-bit word.

# PROCESSOR MODULE

Series 6000 systems are highly modular, allowing the system configuration to be matched to the work load mix. The Extended Instruction Set (EIS) processor is particularly well suited for a heavy business load, while the other models handle mixed work loads of business and scientific jobs.

Each processor module has full program execution capability and conducts all actual computational processing (data movement, arithmetic, logic, comparison, and control operations) within the information system. The processor, which communicates only with the system controller(s) and associated memory, consists of an operations unit and a control unit. The operations unit executes arithmetic and logical operations; the control unit performs instruction fetching, address preparation, memory protection, and data fetching/storing. Both units operate with relative independence and maximum overlap to provide the highest possible rate of instruction execution on the faster models.

The processors contain several special features that make significant contributions to the exceptional multiprogramming, high throughput, and rapid turnaround capabilities of the information systems.

These features are under the control of GECOS, which maintains automatic supervision and complete control of the multiprogramming/multiprocessing environment.

These features are:

**Dual-Mode Operation.** The processor has two modes of operation — master and slave.

- Master mode, reserved for GECOS, allows unrestricted access to all of memory, permits initiation of data input/output operations through the IOM(s), and permits the setting of control registers.

- Slave mode, used for the execution of all user programs, is also used by GECOS when appropriate. Slave mode operation restricts memory references to assigned program boundaries and causes all memory references to be relative to a base address register (BAR). Program execution time is strictly limited by a timer register. Also, program execution is limited to a subset of the instruction repertoire control operations (such as input/output operations or setting the BAR and timer registers) cannot be executed in slave mode.

Dual-mode operation effectively restricts operating control of the information system's multiprogramming environment to GECOS.

Base Address Register (BAR). Each processor contains a base address register, which performs both address translation and memory protection functions in slave mode operation. (The BAR is not used in master mode processing.)

The BAR is set by GECOS prior to transferring control to a slave program. It contains the beginning address of the program (absolute) in memory and the number of 1024-word blocks assigned to the program. Program memory is logically and physically contiguous.

During slave mode execution, all memory addresses developed by a program are checked to ensure that the address is within the area of memory assigned to the program. If the developed address is within the program's area, the address is added to the beginning address value in the BAR to develop the true address, and the memory access is performed. If the address developed by the program is outside the area of memory assigned to the program, control automatically reverts to GECOS for appropriate action.

An important attribute of the BAR is the ability to move user programs in memory without address relocation merely by establishing a new BAR setting. This feature is used for program swapping and memory compaction.

Timer Register. Each processor contains a timer register, which initiates a program interrupt at the end of a preestablished interval of time. The interval is set by GECOS prior to giving control to a slave program. (The timer register can be set in master mode only.)

The timer register is used by GECOS to time programs for automatic termination, to prevent programs from monopolizing a processor, and to provide detailed accounting information on processor and peripheral use time.

Processor Faults. Sixteen special processing status conditions, termed "faults," cause interruption of sequential instruction exceution and transfer of control to one of 16 discrete fault vector locations for appropriate action by GECOS. Faults provide program control (e.g., arithmetic overflow), system control (e.g., timer runout or an attempt to reference outside of memory limits), and communication control (e.g., master mode entry).

Extended Instruction Set (EIS). The EIS models have processor instructions well suited for work loads with a predominance of business over scientific work. The EIS processor has all of the instructions of the other models plus many business-oriented features including: decimal arithmetic, powerful editing, mixed-mode operations, address registers, and extended instruction format (multiword instruction) with two or three addresses. For example, a single COBOL statement can be performed by a single instruction on the EIS processor but would require several instructions on a conventional processor. This not only reduces the memory required but also the execution time.

# INPUT/OUTPUT MULTIPLEXER (IOM)

Each IOM module operates essentially as a stored-program device controlled by, and sharing memory accesses with, the processor modules. Data transfer operations are initiated by GECOS in master mode. (Data transfer operations cannot be initiated by a program in the slave mode.) Peripheral device operations are controlled by processor-prepared control word lists stored in the communications region in memory (referred to as "IOM mailboxes"). Data transfer operations are performed asynchronously with program processing.

Each IOM module in any configuration is directly coupled to each memory module, providing direct access to all of memory. Data transfer operations are controlled by lists of Data Control Words (DCW) which specify the areas of memory to/from which data is to be transferred. These DCW lists allow data to be gathered from, or distributed to, noncontiguous locations in memory.

Memory protection of data transfers is performed in much the same manner as in the processor. The BAR setting of the program requesting the I/O is inserted as part of the required instructions in the IOM mailboxes. Each DCW processed by an IOM is checked for address limits. If an out-of-bounds address is detected, the transfer is not performed and an appropriate interrupt is generated to the control processor. IOM communication with the processor is effected through the IOM mailboxes and through four discrete types of interrupts to one of 32 present interrupt vector locations. All data transfer and peripheral status conditions of interest are signaled to the control processor via the interrupt mechanism to maximize peripheral utilization and program throughput.

# **COMMUNICATIONS PROCESSORS**

Communications capabilities are an integral part of the Series 6000 systems. Three data communications processors are available to provide the front-end processing functions — DATANET 355, DATANET 30, and DATANET 305.

The DATANET 355 Communications Processor is capable of servicing up to 200 remote terminals simultaneously. It is configured primarily on larger Series 6000 systems that have large communications requirements. Multiple DATANET 355s may be connected to a single system to permit even larger networks. The DATANET 355 connects directly to the system controller within each memory module. The communications link to mass storage for remote batch input/output functions is provided only by the DATANET 355 processor.

The DATANET 30 Communications Processor holds a long-time success record, fulfilling a variety of communications needs in the data processing industry. The DATANET 30 is currently available as a front-end communications processor for the Series 6000 systems to meet the needs of medium-size communications requirements. The DATANET 30 connects to a common peripheral channel of the Series 6000 Input/Output Multiplexer.

The DATANET 305 Communications Processor answers the need for small-to-medium communications requirements on a Series 6000 system. The DATANET 305 enables time-sharing functions for up to 12 teletypewriter users and remote batch processing for two users. The DATANET 305 permits growth compatibility to either the DATANET 30 or DATANET 355 when the communications requirements exceed those of the DATANET 305.

All three communications processors receive and process information from a variety of remote terminals for direct input to the System Scheduler, the Transaction Processing Executive, or time sharing or user application programs, and transmit output and control information to these terminals over common carrier communications facilities. As stored-program processors, all three communication

processors provide the front-end processing benefits of more effective line handling discipline, greater terminal capacity and flexibility, less central processor overhead, standard system interface for remote input/output functions, and increased system availability to the remote terminal user. The division of the work load between the central processor and the front-end processor provides greater total system throughput.

# **SERIES 6000 CHARACTERISTICS**

Table 1 gives the general characteristics of the various Series 6000 models. Section 1 points out that Models 6040, 6060, and 6080 have the Extended Instruction Set (EIS) processors, while Models 6030, 6050, and 6070, which are lower priced, do not.

|                                         | Model<br>6030/6040 | Model<br>6050/6060 | Model<br>6070/6080 |

|-----------------------------------------|--------------------|--------------------|--------------------|

| Max. Memory Size in words (36-bit word) | 131,072            | 262,144            | 262,144            |

| Cycle Time (microseconds per two words) | 1.2                | 1.2                | 0.5                |

| No. of Data Channels                    | 16                 | 24                 | 24                 |

| Max. Transfer Rate Per IOM (chars/sec.) | 1.3M               | 3.7M               | 6.0M               |

| Peripheral Capacity (subsystems)        | 16                 | 24                 | 24                 |

| I/O Compute Simultaneity                | 16                 | 24                 | 24                 |

| Programmable Registers                  | 49/57              | 49/57              | 49/57              |

| Floating Point                          | Yes                | Yes                | Yes                |

| Memory Protect                          | Yes                | Yes                | Yes                |

| Hardware Radix Conversion               | Yes                | Yes                | Yes                |

| Interleaving                            | No                 | 2&4-way            | 2&4-way            |

| Instruction Overlapping                 | No                 | Yes                | Yes                |

| Instructions per Second (max.)          | 340,000            | 550,000            | 1,400,000          |

**TABLE 1. SERIES 6000 CHARACTERISTICS**

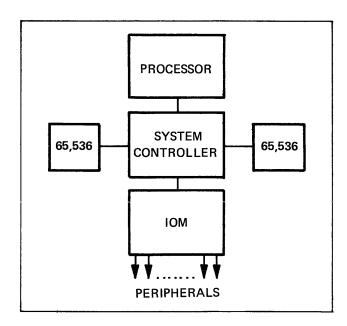

Figure 4. Basic System

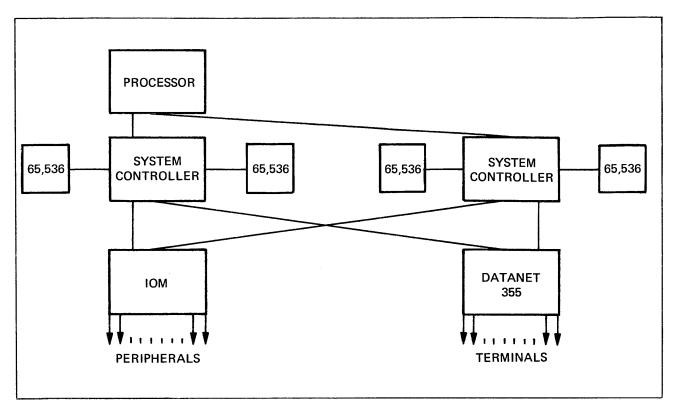

Figure 5 shows the typical central modules for a multidimensional system. A basic batch-only system (see Figure 4) contains a single processor, a single system controller, and a single IOM with its peripherals, while the multidimensional system requires more memory, possibly two system controllers, and a DATANET communications processor. The communications processor is essential for all dimensions of the systems except local batch.

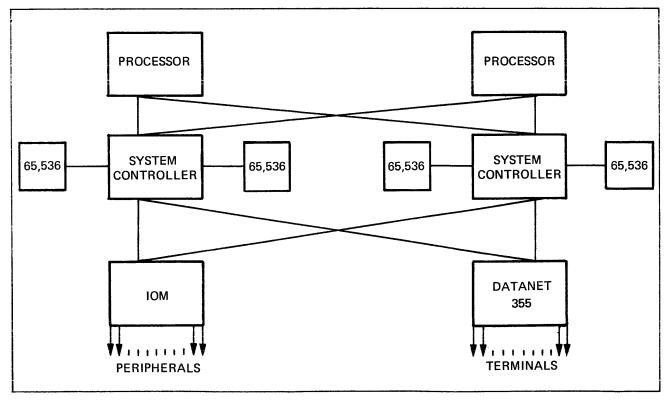

Figure 6 illustrates the central configuration of a multiprocessor system. Fundamental to Series 6000 operation is the fact that all active modules (processors, IOMs, and DATANET 355s) connect to all system controllers and thus have common access to memory and to the common data base. These connections permit GECOS to assign work to the available resources.

Although Figure 6 shows only two processors, one IOM, and one DATANET 355, the system allows as many as four processors, four IOMs, and three DATANET 355s,

subject to the additional theoretical restriction of eight total active modules. It is unlikely that eight or more active modules would be required to perform the work load of a system.

Along with the functional modularity of the hardware configuration, there is complete program compatibility such that any program that is capable of running on one configuration can run on any other configuration (except for EIS programs, which must run on an EIS system).

Figure 5. Multidimensional System

Figure 6. Multiprocessor System

# Section III

# General Comprehensive Operating Supervisor (GECOS) 6000

The General Comprehensive Operating Supervisor (GECOS) 6000 is the most versatile and proven executive system in the industry today. The Honeywell Series 6000 Information Processing Systems, with GECOS, incorporate all of the proven multiprogramming, multiprocessing, local and remote batch processing capabilities of its predecessors, plus the latest concepts of file system design, communications, and time sharing.

Under GECOS, the dimensions of batch processing, remoteaccess processing, transaction processing, and time sharing are integrated, thus creating a level of computational effectiveness and flexibility not attainable with multiplesystem installations. This merging of processing dimensions in concurrent operation on a single system provides increased effectiveness and flexibility in two significant respects:

- The respective amounts of batch processing, transaction processing, and time sharing can be tailored to individual installation requirements and can be dynamically variable throughout the processing day.

- 2. The file system (in which files from all processing dimensions are stored in a common file structure and which provides access to any file in the file system from any processing dimension) provides increased opportunities for data base effectiveness. The overhead of duplicate data bases and of transferring files between systems has been designed out of existence. Even more important, the centralized data storage provided by the file system is the necessary first step toward providing management with timely information upon which to base management decisions.

# **FEATURES OF GECOS**

GECOS provides the user with a large number of benefits The major functional characteristics include the following:

- Resource Management. GECOS maintains current status of all system resources (processors, memory, and peripherals), allocating available resources to jobs with proven allocation algorithms for optimum resource utilization.

- Job Scheduling. GECOS, via the System Scheduler, accepts a virtually unlimited number of user jobs from multiple local and remote input devices simultaneously. Up to 63 jobs can execute concurrently or simultaneously (system resources permitting). GECOS also performs automatic output media conversion for completed jobs. GECOS utilizes the most advanced multiprogramming and multiprocessing techniques to maximize job throughput, minimize turnaround time, and optimize resource utilization.

- Priority Allocation. GECOS contains an effective job priority structure that allows "hot" jobs to be expedited. Priority jobs receive first consideration in resource allocation, which can cause the temporary suspension and removal from memory (swapout) of programs in execution to make room for a high-priority program.

- Ease of Use. GECOS provides the development programmer with a complete, logical interface to his program and file structuring. All physical system and peripheral device constraints and programming considerations are handled by GECOS. Remote locations interface directly with the central system without preestablished operator assistance or coordination. Concurrent time sharing places the full power of the information system at the fingertips of the engineer, the programmer, or the manager.

- Data Base Management. The file system provides a permanent on-line repository with millisecond access for data files from all modes of processing. Full user cataloging, password protection, access control, and file sharing capabilities are provided. Multiple programs in multiprogramming execution can read a file concurrently. I-D-S (Integrated Data Store, a Honeywell data management system) files can occupy space in the file system.

- Security Control. GECOS positively prevents all programs within the system from accessing unauthorized memory areas or data files. Programs in memory execute within firm boundaries. Data files are protected by passwords and positive checking of all data transfer operations. Remote users must be validated before they can access the system.

- On-Line System Development. The file system and the reactive terminal interface upon which GECOS Time Sharing is implemented provide a powerful, yet easily adaptable, base for the development of on-line terminal applications for management information systems (MIS) or information storage and retrieval.

# **BATCH PROCESSING**

# Job/Activity Definition

As a preface to describing the general flow of user jobs through GECOS, some definitions of terms are given below.

Multiprogramming. The concurrent processing of many programs residing in core memory to maintain the highest possible amount of simultaneous input/output and to maximize processor utilization

- Multiprocessing. Two or more processors simultaneously executing programs in memory to gain greater throughput.

- Activity. A single program (such as a Fortran compilation or an object program execution).

- Job. A set of related activities that together constitute a logical computer application, and that must execute sequentially because of their logical relationship.

# Job Flow

Local batch jobs, remote batch jobs, and transaction processor slaves are processed in the same manner by GECOS. Remote jobs differ only in the input and output routines that interface with the communications processor.

Batch jobs flow through five phases of GECOS in the course of processing:

- Job Input (Input Media Conversion)

- Activity Allocation

- Activity Execution

- Activity/Job Termination

- Job Output (Output Media Conversion)

The major functions of each phase are outlined below.

# Job Input

User jobs enter the system simultaneously from multiple central and remote peripherals. Incoming jobs are placed in temporary files in the file system. These jobs can be entered directly to the allocator queue or via the System Scheduler.

# System Scheduler

At the user's option, the jobs can enter the system via the System Scheduler rather than directly into the allocator queue. The System Scheduler is a powerful feature that enables various job priorities to be established and utilized in organizing the work load for the central system. The Scheduler can have a significant impact on job turnaround time. This effect is most pronounced if the higher-priority activities are relatively short in comparison to activities of lesser priority. This disparity is often encountered in practice; for example, transaction processing is usually more time-critical than batch processing.

Two main features are provided by the System Scheduler:

- 1. A virtually unlimited number of jobs can be entered in the system at one time.

- 2. An arbitrary number of job streams can be established in relation to user organizations served by the installation. Each organization can then establish priorities in the job streams to which it is assigned.

Two special scheduling streams are provided to facilitate "express" jobs and "hold" jobs. A "hold" job can have a "hold until" date and time associated with it; this is the

date and time the job will be entered into its actual scheduling stream. "Express" jobs are those jobs that require a limited amount of system resources. The number of express jobs that can be run at any one time is determined by the user, as are the criteria for determining an "express" classification.

Jobs are scheduled using the following criteria. Scheduling streams are queued for an eligible job on a rotational basis. The highest priority job is selected from the queued stream; jobs of equal priority are selected on a first-in, first-out basis.

#### Allocator Queue

As the job sequence number card is detected for each job in the temporary file space, it is assigned an internal program number (1-63) and placed in the allocator queue according to its relative priority. All of the time-sharing jobs are considered as a single job of the 63 programs in the queue. Jobs entering the system may carry an initial priority established by the System Scheduler or the Transaction Processing Executive; if not, GECOS will calculate a priority for the job based on its resource requirements.

The major features of allocator-queue processing are:

- Multiple job input streams from a combination of central system and remote sources.

- The job image in the file system is preserved intact throughout job processing. A job or an activity within a job can be restarted when necessary.

- Each job entering the system is scanned for gross resource (peripheral and memory) requirements to ensure that the currently operational system configuration can accommodate the job. A single job that exceeds configuration capabilities is immediately deleted from the system with appropriate operator notification.

- Jobs entering the system are also screened for the estimated amounts of system resources required; these are compared to limits established by operations. Jobs exceeding these limits are run only with operator approval. These limits, changeable during processing, allow emphasis on small jobs.

# **Activity Allocation**

The allocation phase of GECOS is activated (1) when a new job is placed in the queue by the job input phase and is a candidate for allocation, and (2) when resources are released that can be assigned to a new activity.

Allocation of system resources is performed in two subphases:

- 1. Peripheral Allocation

- 2. Memory Allocation

Peripheral Allocation Subphase. The queue is ordered according to job priority. Peripheral allocation routines examine each job in sequence, allocating peripherals to the current activity of a job.

Peripherals are not allocated to an activity until the activity's total peripheral requirements are available. Instead, the job is bypassed until the next allocation cycle in favor of lower-priority jobs whose requirements can be satisfied. If the job proves difficult to allocate, provision is made to block allocation of lower-priority jobs until sufficient resources become available for the job.

Special features of peripheral allocation are:

- Balanced Peripheral Allocation. File allocation on peripherals of a given type is balanced across all channels to which that type of peripheral is connected. On multidevice channels, file allocation is also balanced across all devices on that channel. This technique maximizes device and channel utilization and minimizes multiprogramming interference.

- Hold Status for Demounted Files. When a job requiring demounted files (e.g., magnetic tape) enters the system, GECOS notifies the operator of the files required. The job is not a candidate for allocation until the operator indicates that the files have been retrieved from the library.

- Demounted File Request-by-Name. The file system provides for cataloging demounted files. When a job in allocation requests such a file by name, GECOS retrieves the current reel number from the file system and notifies the operator that it is needed. This feature provides security for demounted files in that (1) the files can be protected by passwords, and (2) the correlation between file name and physical reel number is stored in the file system.

- Named Device Request. Programmers may request that a specific device be allocated to a job (instead of the normal method of specifying only the type of device needed). This feature is useful when a device with a special option is required (such as a printer with a special character set).

- Dynamic Allocation of Implicit Files. The implicit files used by software (such as the files used to hold user jobs or those used as intermediate files during compilation) are allocated dynamically. This technique handles variable-length files with effective storage utilization.

An activity is a candidate for memory allocation only after peripheral allocation is complete and the activity is ready for execution.

Memory Allocation Subphase. As defined previously, the concept of multiprogramming is based on the concurrent execution of multiple programs resident in memory. Those programs ready for execution utilize the processor, while others await the completion of input/output operations.

Effective multiprogramming demands full memory utilization, which in turn demands efficient handling of variable-length programs GECOS allocates memory in 1024-word blocks. A user activity may request any number of blocks, up to the full size of slave memory (total memory less the

amount occupied by the resident portion of GECOS). The blocks allocated to an activity are contiguous. When an activity terminates, its blocks are made available for reallocation. When required, GECOS compacts the activities in memory (moves them together) to make multiple noncontiguous areas contiguous. With this technique, all available memory can be effectively utilized.

GECOS features a 3-level memory allocation algorithm based on job priority. An activity of a job with normal priority will be allocated memory only if a contiguous area of memory large enough to accommodate the activity is available. At a higher level of priority, the activities of other jobs in memory will be compacted, making noncontiguous areas contiguous so that the activity in allocation may be allocated. At the highest level of priority, activities of other jobs in execution will be temporarily removed from memory (swapped) to make room for the activity in allocation. Each time a job is thus bypassed for memory allocation, its priority is increased.

When memory allocation is successful, the activity is placed on the Dispatcher queue (a queue of all activities in memory that are ready for execution).

# **Activity Execution**

During execution, each activity is executed under the supervision and control of the Dispatcher. The Dispatcher keeps as many system components as possible in simultaneous use. It accomplishes this by selecting the highest-priority activity that can make effective use of the processor and peripheral subsystems and transferring control to it.

This Dispatcher queue is dynamic. Activities are in the queue only if they are ready to execute. The queue is sequenced according to the priority of the activities for execution; the highest priority is at the top of the queue. Dispatching is, therefore, a very simple and straightforward mechanism of picking the top entry from the queue and dispatching to it. To maintain high utilization of physical resources, the Dispatcher maintains a list of user programs that require very little processor time, only enough to keep peripherals in full operation. The Dispatcher will select one of these for execution (a "courtesy call") if the user program at the top of the queue was not in a courtesy call. When dispatching to a user program, the Dispatcher sets the base address register (BAR) and the time register and sets slave mode in the process of transfer.

In multiprocessor systems, the Dispatcher selects activities from the same queue for each processor. All processors can execute both GECOS and user programs; however, only the control processor will respond to the peripheral interrupts. GECOS redispatches at the completion of interrupt processing. Since the Dispatcher queue may be modified in the course of interrupt processing, the priority of job execution is truly interrupt-oriented. This feature facilitates the development of responsive, event-oriented systems.

Swapping may occur as a normal function of activity execution, if the priority of a job in the input queue is sufficiently high to demand this service. GECOS performs

a great many service functions for activities in execution that (1) the activities cannot perform directly from slave mode (e.g., input/output operation) or (2) that relieve the user programmer from detailed knowledge of system operation (e.g., calling in of overlays).

Centralized Input/Output. Input/Output (I/O) operations proceed simultaneously and asynchronously with processing under the control of the input/output multiplexer (IOM) module(s). I/O operations are initiated solely by GECOS in master mode. The hardware prohibits initiation of I/O operations from slave mode. The IOM modules execute I/O operations in accordance with control words prepared by GECOS and stored in an IOM "mailbox" area in memory.

In combination with the File and Record Control routines, GECOS provides a complete logical interface for file processing. All I/O requests are checked to ensure that the device or file is allocated to the requesting activity and that the data buffer is within the requesting program's memory allocation.

I/O requests are processed to the extent possible when received and are queued for each peripheral subsystem. These techniques allow interrupt processing to be reduced to a minimum and new I/O operations to be initiated quickly. GECOS I/O routines provide for device interchange. When an allocated peripheral device (e.g., card reader, printer, card punch, or magnetic tape) is operating at an error rate above a predetermined threshold the operator can request that a new device be allocated for the file being processed. The operator can then move the file to the new device and continue processing. GECOS keeps track of the number of files and the number of records within a file that have been read or written on magnetic tape and uses this information to reposition a magnetic tape after interchange.

GECOS provides a method of processing on disk that simulates the serial mode of processing normally peculiar to magnetic tape. This mode of processing not only provides for device independence but also allows the opportunity to reduce program setup time by eliminating the use of magnetic tape for some files.

# Activity/Job Termination

An activity in execution may terminate normally or abnormally. The processing of each type is different.

■ Normal Termination. Normal termination processing first looks ahead to the next activity (if there is one). If it is a compilation activity of the same type as that terminating, the new activity is merged with the present activity (initiated immediately) using the same resources used by the present activity. If the next activity is not the same, the operator is notified of files that require demounting. If a file in an activity is to be used in subsequent activities, a notation is made in the file system to save the file. An accounting record is written on the System Output (SYSOUT) file, itemizing the system resources used by the activity. The allocation phase of GECOS is notified that the resources used by the activity are available for reuse and that the next activity is a candidate for allocation.

If end-of-job, the job is removed from the job stack.

GECOS runs successive compilation activities of the same type as a single activity, thus avoiding the deallocation of resources at the end of a compilation only to reallocate the same type and amount of resources to the following activity.

■ Abnormal Termination. Abnormal termination (abort) processing may be initiated by the activity, or by GECOS, when the activity tries to execute an illegal operation (e.g., an attempt to access memory outside its boundary).

The aborting activity can at its option have a dump of its allocated memory written on the output collector (SYSOUT). The programmer may also define abort subactivities (useful for dumping data files) that are executed only when an abort occurs.

As with normal termination, the resources used by the aborting activity are released for reallocation. Compilation activities following an aborted activity are executed. Whether subsequent object program execution activities are executed is a programmer option.

# Job Output

GECOS includes a system output phase (SYSOUT) which consists of an output collection function and an output dispersing function.

Multiple output files (for printing and punching) from all activities in execution are collected in the file system, along with those generated by GECOS in the course of job processing (e.g., accounting reports and abort memory dumps). This mechanism avoids the necessity of dedicating peripheral devices to small-volume print or punch files.

The output-dispersing routines read the data collected in the file system and batch the output from many jobs on multiple printers and card punches. This provides a more effective utilization of peripherals.

Output printing and punching is automatically performed concurrently with the execution of other jobs in the system and the entry of still more jobs into the input stack.

# MULTIPROCESSING

The effectiveness of multiprocessor systems is largely a combination of three factors:

- A sufficiently large number of activities in memory and ready for execution (as opposed to those waiting for I/O) to keep the processors busy in the average mix of jobs in the system.

- A sufficient number of memory accesses available to each processor to allow it to execute without delay.

- An operating system design that does not serialize processing each time a supervisory or service function is performed for an activity in execution.

The design of GECOS is especially effective in multiprocessor configurations. The following specific points are worthy of special mention:

- The organization and memory utilization of GECOS distributes user programs, tables, buffers, and service subroutines throughout memory, minimizing multiprocessor interference for memory accesses.

- A minimum of multiprocessor "gating" is required. (A "gate" is a software switch that prevents multiple processors from accessing a common table or entering a common routine if it would be harmful to do so.)

- Where interference would be likely, most major program service functions are performed in parallel by providing individual copies of the service subroutines to each program requiring the function.

# REMOTE PROCESSING

Remote processing is available in a Series 6000 system by including one or more communications processors in the configuration. GECOS controls multiple communications processors, integrating remote processing with central-site processing in concurrent operation. Remote processing capabilities include remote batch, remote access, transaction processing, and time sharing.

# Remote Batch

The full capabilities of the Series 6000 Multidimensional Information System are available to the remote batch user. Any job that can be entered directly at the central system can be entered remotely from a remote batch computer. A remote batch job differs from a local batch job only in the GECOS job input/output routines that interface with the communications processor. Once inside the central system, local batch and remote batch processing are identical.

Remote batch jobs have several options available for the output files they generate. These options are selected by control cards as follows:

- Return to sending terminal.

- Enter into the file system.

- Output at central site.

- Hold until terminal calls back.

- Send to another terminal.

#### Remote Access

The remote access capabilities satisfy the requirements for data base inquiry, remote data base management, data collection, or other "on-line" applications.

Remote access provides direct terminal access to a program in execution. The program, written in any batch programming language (Fortran, COBOL, GMAP, etc.) can be submitted as a job via local batch, remote batch, or time-sharing batch.

The terminal in remote access effectively becomes an online peripheral to the activity in process. The activity can send output to, and receive input from, the terminal or terminals.

# **Transaction Processing**

The Transaction Processing Executive controls the concurrent execution of application programs in the GECOS multidimensional environment, providing on-line, real-time capability. Transactions are related to events in the user's business, such as order entry or customer file update. Some characteristics of transaction processing are:

- Transactions are submitted by the *end user* of the system (e.g., bank teller, stock clerk, sales manager) with no need for specialized knowledge of the information processing system or its operation.

- The transaction is initiated by the user. Subsequent actions are implicit to the transaction itself. No specific command language is required by the user.

- The scheduling of tasks to be performed is not the responsibility of the transaction submitter.

- The Transaction Processing Executive does not use system resources when the transaction system is not activated.

The executive operates as a privileged slave in the directaccess mode and will generally be in execution. Control over the execution status of the executive is from the operator's console. The application programs will not generally be in execution, but will be activated by the executive selectively upon receipt of transactions.

The transaction processing application programs are normal user application programs and may be written in any of the Series 6000 languages including the data base managers. The powerful resource management and service functions of GECOS are available to maximize throughput.

# Time Sharing

GECOS Time Sharing is designed for installations that want to provide time-sharing service to their users without disruption of their batch processing commitments. The portion of the Honeywell Series 6000 system dedicated to time-sharing processing options is variable throughout the processing day.

All of the catalog structuring, source/object file storage, file protection, file sharing, and access control capabilities of the file system are available to the time-sharing programmer. A special catalog/file maintenance routine is provided to perform user catalog and file maintenance functions from a time-sharing terminal.

The Time Sharing Executive performs the functions of selecting, allocating, dispatching, and swapping time-sharing user programs. The executive is structured as a single privileged slave program operating under the control of GECOS. It, in turn, suballocates memory and subdispatches the processor to individual time-sharing user programs. In the process of subdispatching, the Time Sharing Executive establishes a new BAR setting around the user program to be executed, ensuring the integrity of other user programs in memory.

The Time Sharing Executive also performs various services for individual programs, including file system I/O, terminal I/O, and creation and modification of

files, catalogs, and their security definitions. It also accounts for resources used by the individual timesharing users.

Time-sharing user memory is allocated to individual user programs for execution. Several programs can occupy portions of this area. A program can be swapped to allow another user of higher priority to be allocated memory space.

GECOS Time Sharing provides standard time-sharing capabilities (BASIC, Fortran, and Text Editor); and, in addition, offers time-sharing batch and the capability of generating time-sharing systems through the load and execute subsystems.

GECOS Time Sharing is designed to encourage development of terminal applications, in keeping with the present batch mode philosophy in which the manufacturer supplies the operating system, the commonly used compilers, and utility routines, while the user develops the specific applications required for his business.

The structure of GECOS Time Sharing and the integration of time-sharing files in the file system facilitate user extension. Users can add primitives, commands, or subsystems to GECOS Time Sharing, or they can replace the Time Sharing Executive with an executive that satisfies their particular terminal application requirements.

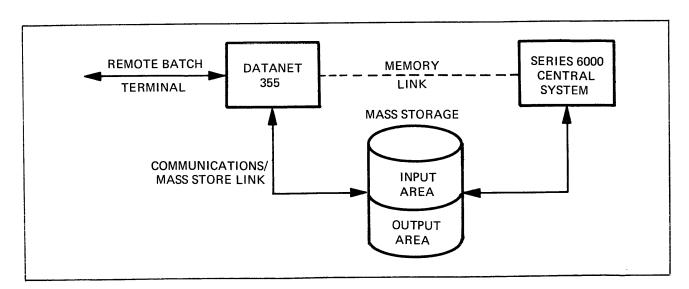

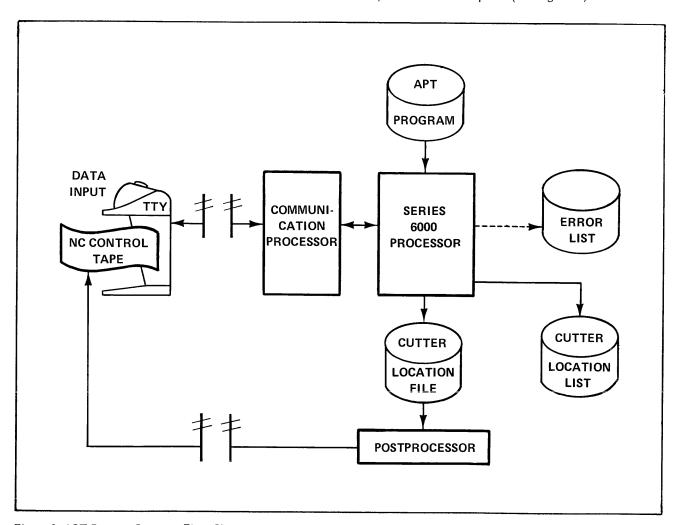

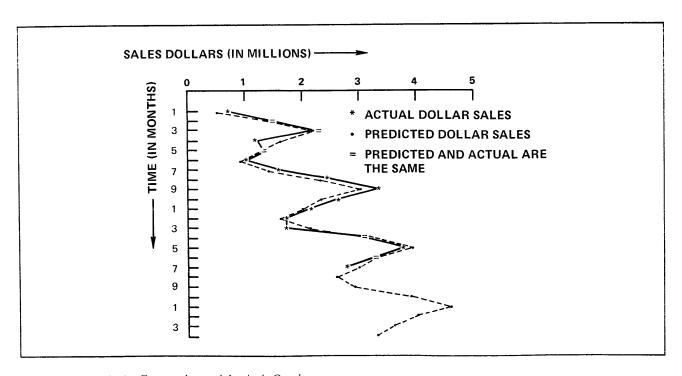

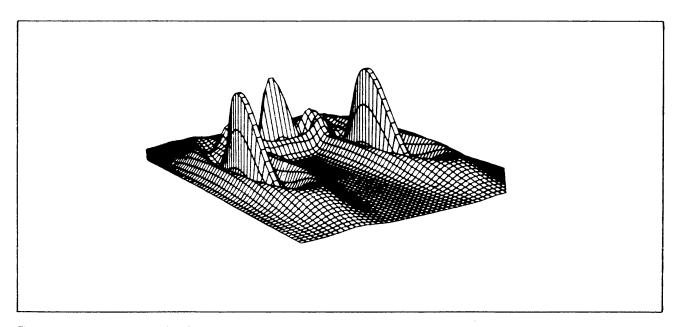

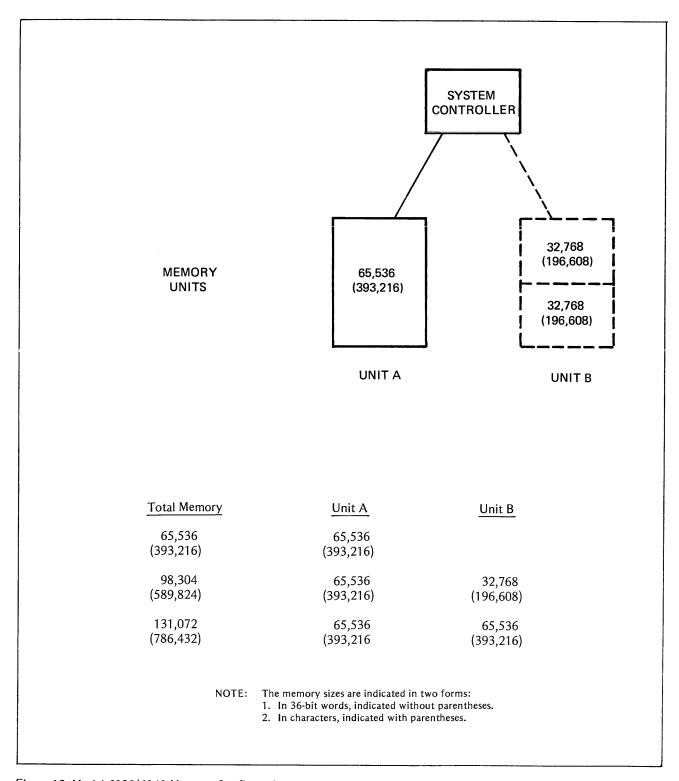

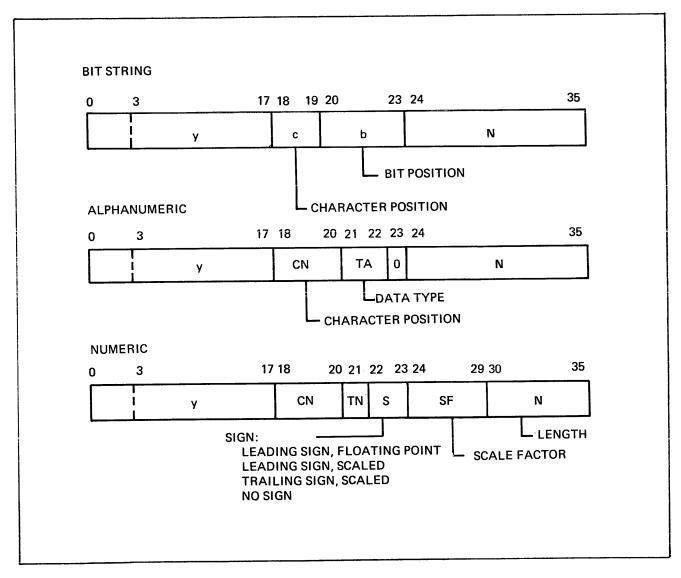

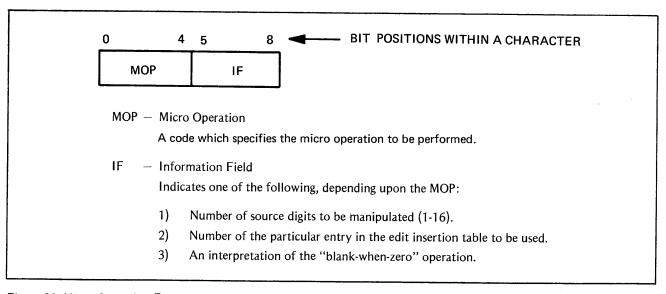

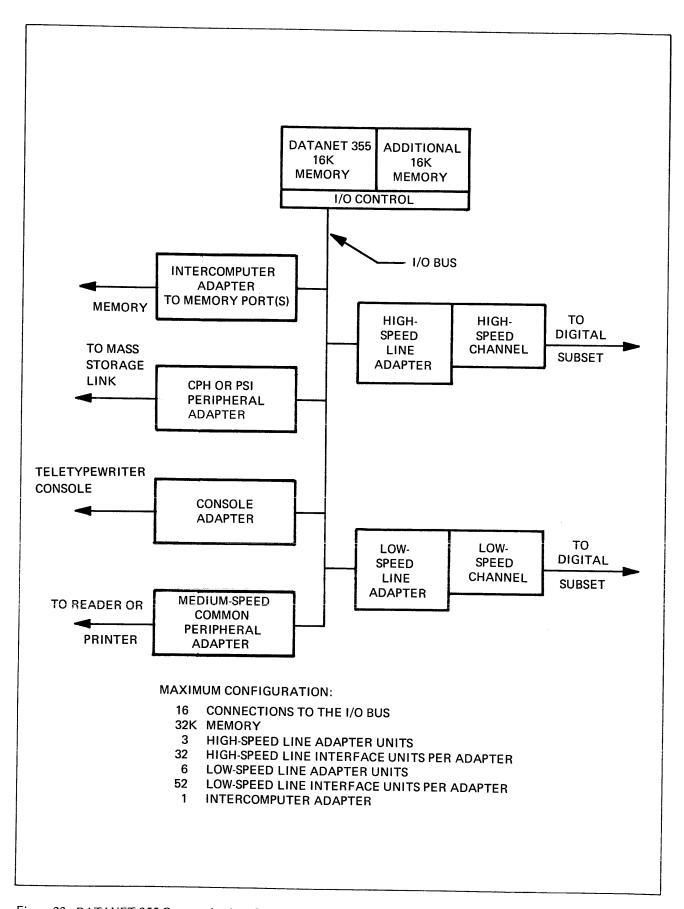

# COMMUNICATIONS/MASS STORE LINK