Spec set 1

| Honeywell<br>Honeywell Information systems                                             |                                            | SPEC. NO.<br>60149766 |            | SHEET | rev.<br>H |

|----------------------------------------------------------------------------------------|--------------------------------------------|-----------------------|------------|-------|-----------|

| Billerica, MA<br>U.S.A.                                                                |                                            |                       | CODE<br>C6 | 1C    |           |

| PREPARED BY DATE TITL<br>A.C. Hirtle 5/20/83<br>APPROVED BY DATE<br>See Approval Sheet | Engineering Product<br>Local Area Controll | •-                    |            | 1     |           |

|                                                                                        | •••••                                      | •                     |            |       |           |

#### REVISION RECORD

| REV. | AUTHORITY | DATE      | SIGNATURE | SHEETS AFFECTED |

|------|-----------|-----------|-----------|-----------------|

| A    | BLCDD7588 | 5/20/83   | act       | All             |

| В    |           | 8/11/83   | act       | All             |

| С    |           | 11/4/83   | and       | As marked       |

| D    |           | 1/12/84   | acia      | As marked       |

| E、   |           | 4/18/84 - | act       | As marked       |

| F    | BLCDE7775 | 10/4/84   | acA       | As marked       |

| G    | BLCDF7256 | 3/31/85   | act       | As marked       |

| Н    | BLCDG7319 | 4/30/86   | add       | As marked       |

## NOTE

This EPS-1, if not revised within one year, should be considered obsolete and therefore reference should be made to the appropriate product manual.

his document and the information contained herein are confidential to and the property of Honeywell Information Systems Inc. and are made available only to Honeywell employees for the sole purpose of conducting Honeywell's business. This document, any copy thereof and the informetion contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager; and shall not be disclosed or distributed (a) to persons who are not Honeywell employees, or (b) to Honeywell employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this focument no longer has need for the document for the authorized Honeywell purpose, this document and any copies thereof shall be returned to the employee's manager. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsibile doneweil Vice President.

| 14.<br>1 |   |                   | ,                            | General III III III III III IIII IIII IIII I                             | -<br>- |

|----------|---|-------------------|------------------------------|--------------------------------------------------------------------------|--------|

|          |   |                   |                              | ÷                                                                        |        |

|          |   | i je<br>Grada se  | te mit <u>et</u> ti<br>Norma | ng ng<br>ng ng n                        |        |

|          | ; | n got e<br>gil er | • .                          | 198                                                                      |        |

| •        |   | <u>*</u> .•       |                              |                                                                          |        |

|          |   | * • •<br>*        |                              | an ann an Anna Anna Anna Anna Anna Anna                                  |        |

|          |   | -10               |                              | 27.28 · C 1                                                              |        |

|          |   | 4 4.              |                              | 1. E. S.                                                                 |        |

|          |   | 10 - 10           |                              | · · · · ·                                                                |        |

|          |   |                   |                              | the second states and the                                                |        |

|          |   |                   |                              | 14                                                                       | ¥<br>F |

|          |   |                   |                              | ie Traisle                                                               |        |

|          |   |                   | ~                            | ాత సంభిష్ రెడి                                                           |        |

|          |   |                   | ;                            |                                                                          |        |

|          |   |                   |                              | امر میں در دور میں میں<br>این اور اور میں اور<br>اور اور اور اور میں اور |        |

|          |   |                   |                              | ವಾರ್ಟೆಗಳ ಸಂಗ್ರಹವಾಗಿ<br>ಸಂಗ್ರಹವಾಗಿ ಇವರ<br>ಸಂಗ್ರಹವಾಗಿ ಸಂಗ್ರಹವಾಗಿ           |        |

|          |   |                   |                              | an dan sana sana sana sana sana sana san                                 |        |

|          |   |                   |                              |                                                                          |        |

•

1. Sec. 1. Sec.

| HONEYWELL                       | SPEC. NO.<br>60149766 | SHEET<br>  1.1 | REV. |

|---------------------------------|-----------------------|----------------|------|

| Author:  <br>  A. C. Hirtle     |                       | Code           |      |

| First Draft Date  <br>  5/20/83 |                       | <br>  C61C     |      |

|                                                 | HONEYWELL INFORMATION SYSTEMS<br>SYSTEMS ENGINEERING - BOSTON               |

|-------------------------------------------------|-----------------------------------------------------------------------------|

| ENGINEERING<br>PRODUCT                          | LOCAL AREA CONTROLLER<br>TITLE: <u>SUBSYSTEM (LACS)</u>                     |

| SPECIFICATION<br>( EPS - 1 )<br>SUBSYSTEM LEVEL | VERSION: <u>APPROVED</u> DATE: <u>4/30/86</u><br>PRODUCT CALENDAR REFERENCE |

#### NOTE

This EPS-1, if not revised within one year, should be considered obsolete and therefore reference should be made to the appropriate product manual.

This document and the information contained herein are confidential to and the property of Honeywell Information Systems Inc., and are made available only to Honeywell employees for the sole purpose of conducting Honeywell's business. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager; and shall not be disclosed or distributed (a) to persons who are not Honeywell employees, or (b) to Honeywell employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this document no longer has need for the document for the authorized Honeywell purpose, this document and any copies thereof shall be returned to the employee's manager. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsible Honeywell Vice President.

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    | -                                       |                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|-----------------------------------------------|

| nen ↔ · | <ul> <li>We can get a set of the set of</li></ul> | 1                  | -m k '<br>4                             |                                               |

|         | , γ το το γ αφοριζός. «Νασ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    | 986-0-148                               |                                               |

|         | 4,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | `. <del>≱</del> u. | s i                                     | a V. C. a K. j                                |

|         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 p y              | - 5                                     | араны — л<br>40 марыны — ласан<br>6 араны — л |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                         | 4 ) A 4 <b>8</b> 4 ' ' '                      |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                         | na transformation<br>s transformation         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | φ κ.<br>1. 2       | ал қ.<br>•<br>К.•                       |                                               |

|         | <ul> <li>F</li> <li>F</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                         |                                               |

|         | ेर हु <sup>€</sup><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |                                         | να (α <sub>μα</sub> )<br>του β (με) του σ     |

|         | 1999 -<br>2016 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1. e . e . e       |                                         | 1911 ·                                        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | n ne P             | an a s<br>an suis<br>an suis<br>an suis |                                               |

· · ·

.

| HONEYWELL | SPEC. NO. | 1 | SHEET | REV. | 1 |

|-----------|-----------|---|-------|------|---|

| l         | 60149766  | 1 | 2.0   | H    | 1 |

( )

# CONTENTS

|        |           | CONTENTS                                 | DACE   |

|--------|-----------|------------------------------------------|--------|

|        |           |                                          | PAGE   |

| SECTIO | N 1       | INTRODUCTION                             | 3      |

| 1.1    | Documer   | nt Definition                            | 3      |

| 1.2    |           | nce Documents                            | 3<br>3 |

| 1.3    |           | iations/Definition                       | 4      |

|        |           |                                          | _      |

| SECTIO | )N 2      | ARCHITECTURE                             | 6      |

| 2.1    | Overvi    | ew                                       | 6      |

| 2.2    | Securi    | ty                                       | 10     |

| 2.3    | Multip    | rocessor Support                         | 10     |

| 2.4    | Local     | Area Controller (LAC)                    | 11     |

| 2.5    | LAC Blo   | ock Diagram                              | 12     |

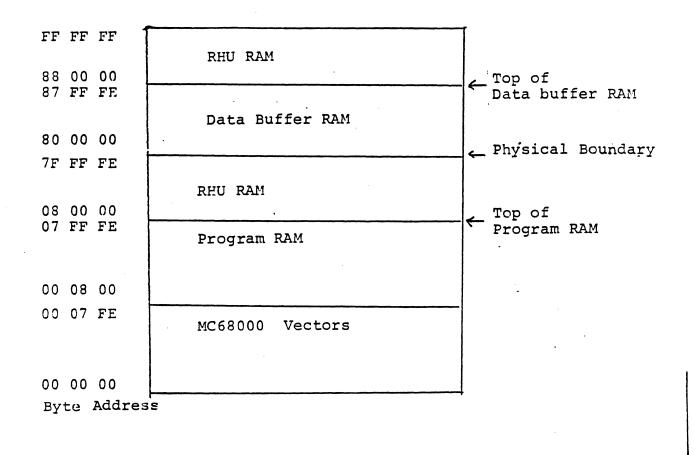

| 2.6    | Memory    | Layout                                   | 14     |

| 2.7    |           | mory Management                          | 16     |

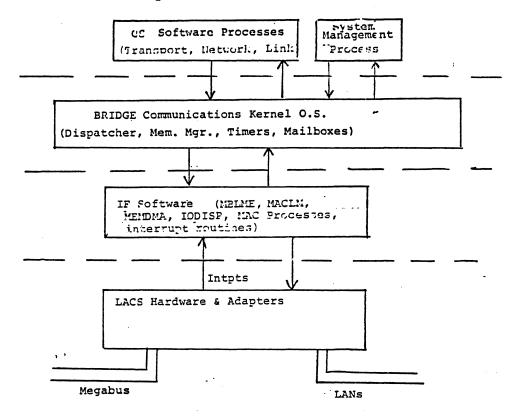

| 2.8    | LAC So    | ftware-Firmware-Hardware Structure       | 17     |

|        | 2.8.1     | General                                  | 17     |

|        | 2.8.2     | Interprocess Communications              | 18     |

|        | 2.8.3     |                                          | 18     |

|        | 2 • U • J | Relative Flocess Florities               | TO     |

| 2.9    | Mailbo    | xes and Mailbox Message Queues           | 20     |

|        |           |                                          |        |

|        | 2.9.1     | Mailboxes Associated with IF Software    | 20     |

|        | 2.9.2     | Mailbox Message Priorities               | 21     |

| 2.10   | LAN CO    | ntrol Block                              | 21     |

| 2.11   |           | ftware Interface to the Megabus          | 21     |

| 2.12   |           | ftware Interface with Adapters           | 21     |

| 2.13   | Softwar   | re Interface Between Level 6 and LACS    | 22     |

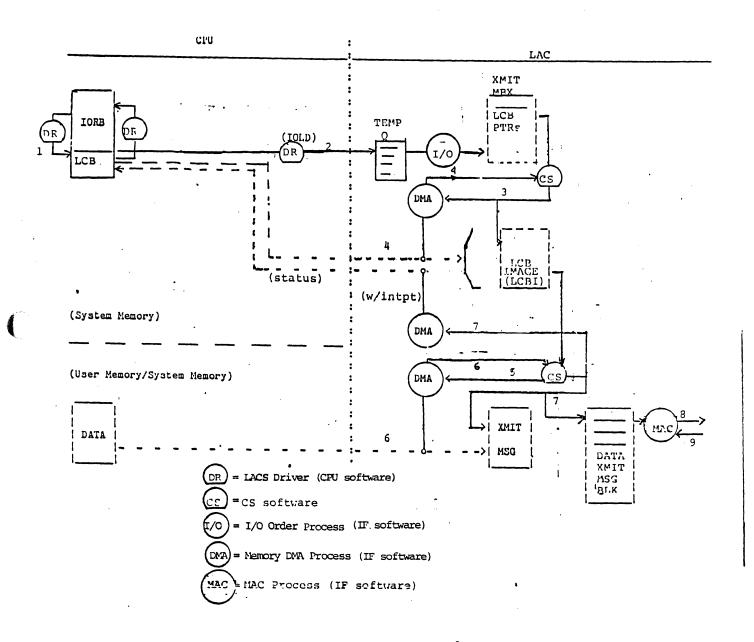

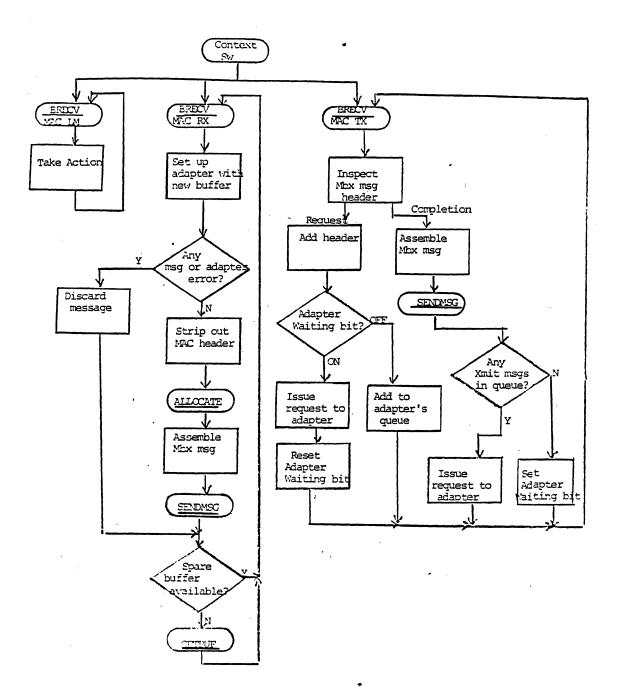

|        |           | Transmit Data Operation Flow             | 22     |

|        |           | Receive Data Operation Flow              | 27     |

|        |           | Control Operations                       | 31     |

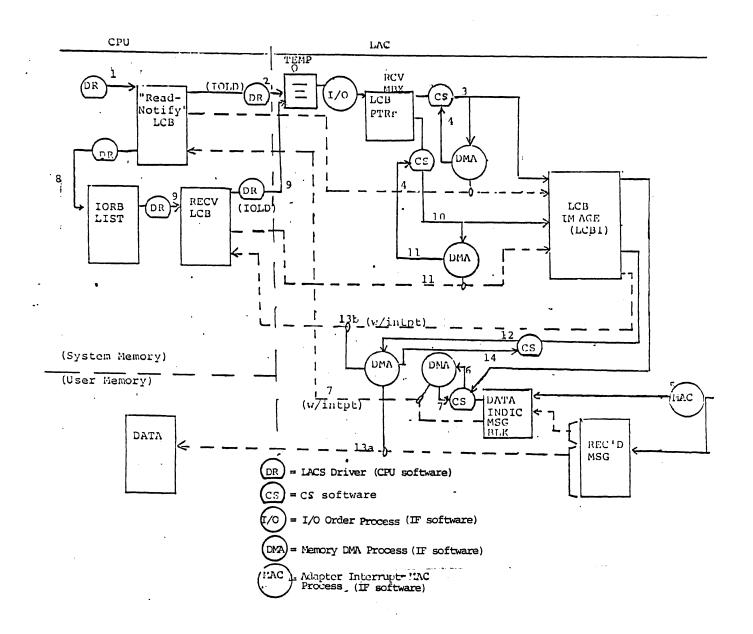

| 2.14   |           | tware & IF Software Functional Diagrams. | 33     |

| 2.15   |           | upts to Level 6                          | 37     |

| 2.16   |           |                                          | 38     |

| 2.17   |           | tartup                                   | 39     |

| 2.18   |           |                                          | 41     |

| 2.10   |           | ng of Software Error Conditions          | 41     |

| 2.19   | nanut I   | ng of software Error conditions          | 41     |

| SECTIO | ON 3      | FUNCTIONAL DESCRIPTION (LAC)             | 44     |

| 3.1    |           | Functions                                | 44     |

| 3.2    | I/0 Or    | ders                                     | 45     |

|        | 3.2.1     | List of I/O Orders                       | 45     |

|        | 3.2.2     | Output Order Definitions                 | 45     |

|        | 3.2.3     | Input Order Definition                   | 47     |

|        | 3.2.4     | WAIT, NAK and ACK Responses              | 47     |

|        | 3.2.5     |                                          | 48     |

| HONEYWELL<br>                             |                                  | SPEC. NO.<br>  60149766                                                                 | SHEET<br>  2.1 | REV.     |   |

|-------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|----------------|----------|---|

| 19 20 20 20 20 20 20 20 20 20 20 20 20 20 | CONJ                             | TENTS (CONTINUED)                                                                       |                |          |   |

|                                           | ے الجا میں ا                     |                                                                                         |                | PAGE     |   |

| 3.3 Chan                                  | nel Numbers                      |                                                                                         |                | 52       |   |

| 3.4 Devi                                  | ce Identification                | Number                                                                                  |                | 52       |   |

|                                           | Transfers within                 |                                                                                         |                | 53       |   |

|                                           | ructions                         |                                                                                         |                | 53       |   |

|                                           | Firmware                         |                                                                                         |                | 53       |   |

|                                           | oftware                          |                                                                                         |                | 54       |   |

| 3.8.                                      | 1 IF Software Pro                | ocesses                                                                                 |                | 54       |   |

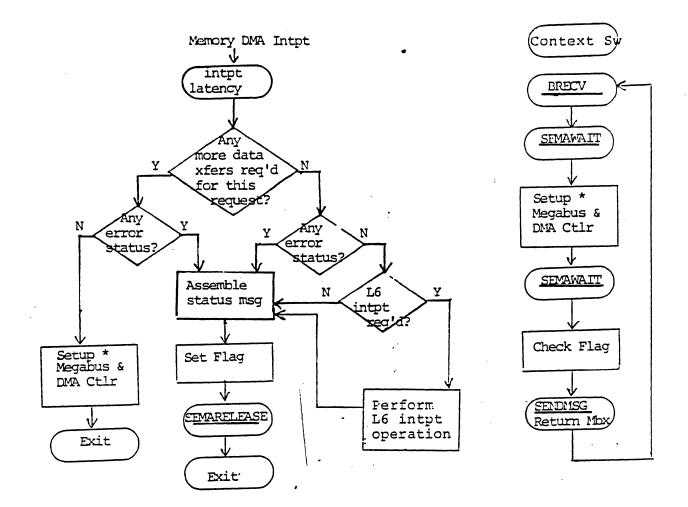

|                                           | 3.8.1.1 Memor                    | y DMA Request (MEI                                                                      | MDMA)          | 54       |   |

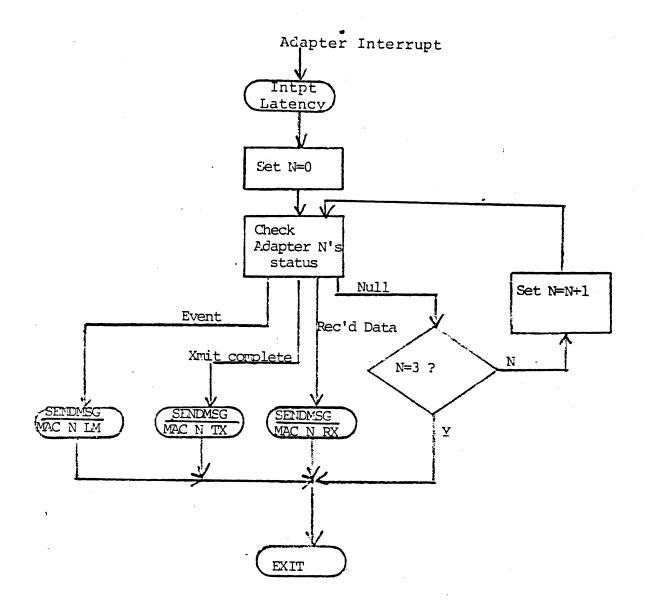

|                                           | 3.8.1.2 MAC                      |                                                                                         |                | 64       |   |

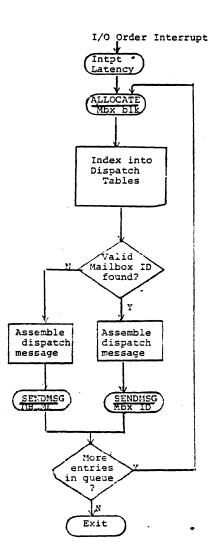

|                                           | 3813 $1/0$ 0                     | rder Dispatch (IO                                                                       | ופסזר          | 66       |   |

|                                           | 3 8 1 4 Mogabi                   | rder Dispatch (IOI<br>us Layer Managemen                                                | 5101/<br>o+    | 72       |   |

| •                                         |                                  | ayer Management                                                                         |                | 72       |   |

| ».                                        |                                  |                                                                                         |                | 12       |   |

| 3.8.                                      | 2 IF Software Int                | terrupt Routines                                                                        |                | 74       |   |

|                                           | 3.8.2.1 Inter                    | rupt Retry                                                                              |                | 74       |   |

| na kata<br>Contra an                      | 3.8.2.2 I/O D                    | ispatch                                                                                 |                | 75       |   |

| <i>I</i> *                                | 3.8.2.3 DMA Co                   | ontroller                                                                               |                | 76       |   |

| s4, €                                     | 3.8.2.4 Megab                    | us DMA Register Ex                                                                      | xhaust         | 77       |   |

| · *,                                      | 3.8.2.5 Adapt                    | er Interrupt                                                                            |                | 77       |   |

| 1. A.                                     | 3.8.2.6 RAM Pa                   | rupt Retry<br>ispatch<br>ontroller<br>us DMA Register E:<br>er Interrupt<br>arity Error |                | 77       |   |

| 3.9 Hand                                  | ling of Hardware E               |                                                                                         |                | 80       |   |

| SECTION 4                                 | INTERFACES                       |                                                                                         |                | 81       | ( |

| 4.1 Leve                                  | 1 6 Interface with               | LACS                                                                                    |                | 81       |   |

| 4.2 LAC                                   | Interface with the               | Megabus                                                                                 |                | 81       |   |

| 4.3 LAC                                   | Interface with Ada               | nters                                                                                   |                | 82       |   |

| 4.4 Test                                  | Connector Interface              | Ce                                                                                      |                | 83       |   |

| SECTION 5                                 | PERFORMANCE                      |                                                                                         |                | 84       |   |

| 5.1 LAN                                   | Data Rate                        |                                                                                         | χ.             | 84       |   |

|                                           | Throughput                       |                                                                                         |                |          |   |

| 5.3 LAC                                   | Infougnput<br>Thetamation Mining |                                                                                         |                | 84       |   |

|                                           | Instruction Timing               |                                                                                         |                | 84       |   |

|                                           | rity Position of L               |                                                                                         |                | 84       |   |

| 5.5 Prio                                  | rity Position of A               | dapters                                                                                 |                | 84       |   |

| SECTION 6                                 | PHYSICAL STRUC                   | TURE                                                                                    |                | 85       |   |

|                                           | aging                            |                                                                                         |                | 85       |   |

| 6.2 Powe                                  |                                  |                                                                                         |                | 85       |   |

|                                           | ronment                          |                                                                                         |                | 85       |   |

| 6.3 Envi                                  |                                  | •                                                                                       |                | 85       |   |

|                                           | LY                               |                                                                                         |                | 0.1      |   |

| 6.4 Safe                                  |                                  |                                                                                         |                |          |   |

| 6.4 Safe<br>6.5 Stan                      | dards<br>ability                 |                                                                                         |                | 85<br>85 |   |

# HONEYWELL CONFIDENTIAL & PROPRIETARY

٩

| HONE                 | YWELL                                              | SPEC. NO.<br>    60149766                                                                                                                                                                                     |   | REV.<br>H                                                      |

|----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------------|

|                      |                                                    | CONTENTS (CONTINUED)                                                                                                                                                                                          |   | PAGE                                                           |

| SECTI(<br>7.1<br>7.2 | General                                            | RELIABILITY AND MAINTAINABILIT<br>Requirements<br>ance Features                                                                                                                                               | Y | 86<br>86<br>86                                                 |

|                      | 7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8 | Error Checking and Reporting<br>Internal Loopback<br>Statistic Gathering<br>LAC RAM Load/Dump<br>FCS Checking<br>Adapter RAM Access<br>Remote Loopback<br>MAC Internal Status<br>Remote Station Inquiry (XID) |   | 86<br>86<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87<br>87 |

| 7.3<br>7.4           |                                                    | nability<br>d Address Space Assignments                                                                                                                                                                       | : | 88<br>89                                                       |

|                      |                                                    | Overall Maps<br>Dedicated RAM Area Layouts                                                                                                                                                                    |   | 89<br>91                                                       |

| APPENI               | DIX A                                              | TOKEN BUS ADAPTER                                                                                                                                                                                             |   | 93                                                             |

| A.1                  | General                                            | Description                                                                                                                                                                                                   | • | 96                                                             |

| APPENI               | DIX B                                              | CSMA/CD (ETHERNET) ADAPTER                                                                                                                                                                                    |   | 96                                                             |

| B.1                  | General                                            | Description                                                                                                                                                                                                   |   | 98                                                             |

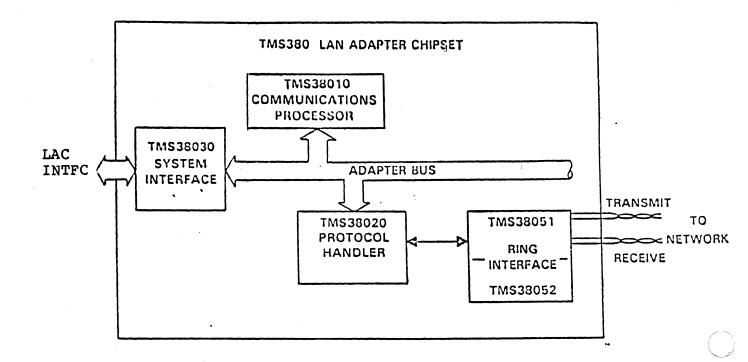

| APPENI               | DIX C                                              | TOKEN RING ADAPTER                                                                                                                                                                                            |   | 98                                                             |

| C.1                  | General                                            | Description                                                                                                                                                                                                   |   | 98                                                             |

|                      |                                                    |                                                                                                                                                                                                               |   |                                                                |

# HONEYWELL CONFIDENTIAL & PROPRIETARY

C

| HONEYWELL |     | SPEC. NO. | 1 | SHEET | REV. | 1 |

|-----------|-----|-----------|---|-------|------|---|

|           | i i | 60149766  | I | 2.3   | i H  | I |

# ILLUSTRATIONS

| FIGURE                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                               | PAGE                                                                       |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

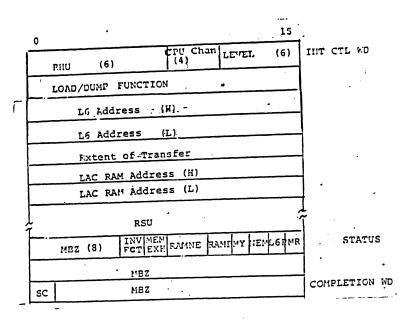

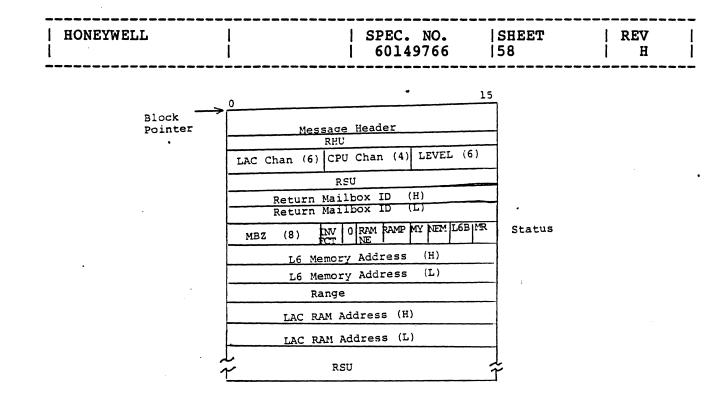

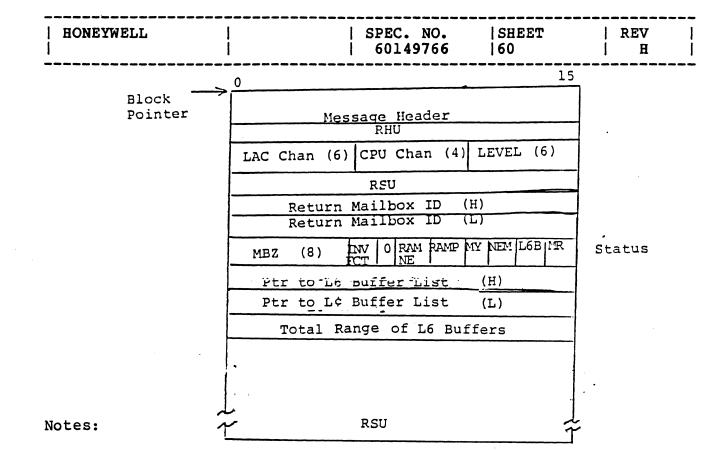

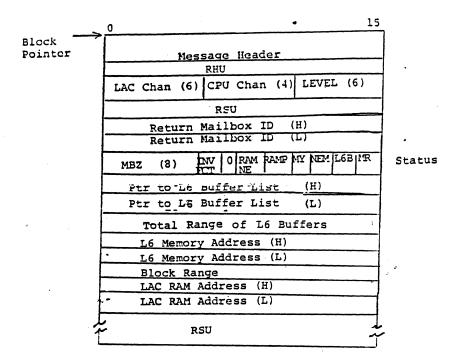

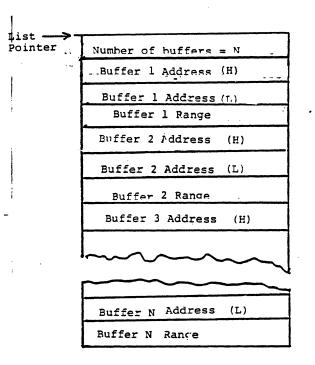

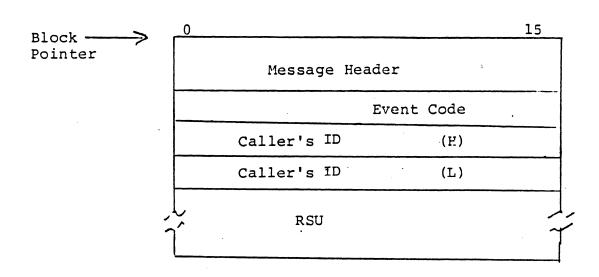

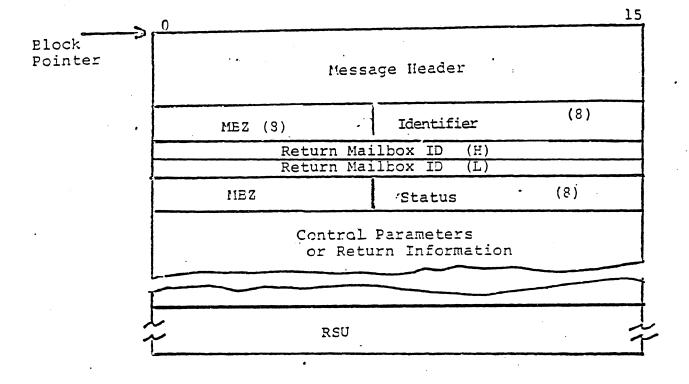

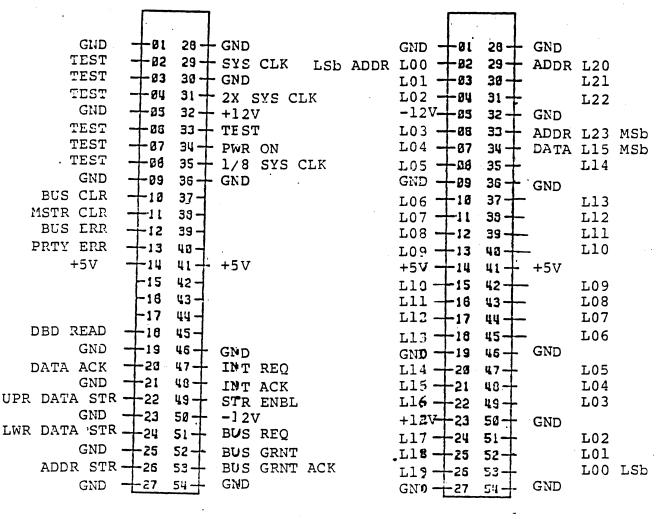

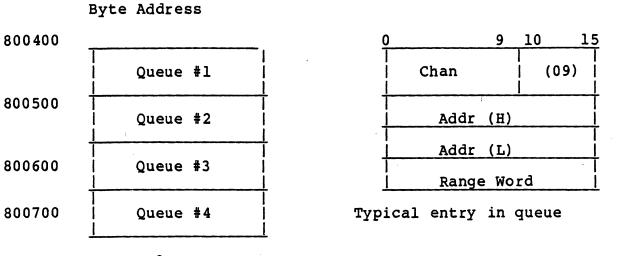

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11                                     | LACS Applications to Local Area Networks<br>LACS Applications<br>LAC Block Diagram<br>LAC RAM Memory Map<br>LAC Operating Structure<br>LLC Transmit Flow<br>LLC Receive Flow<br>I/O Dispatch Process<br>Memory DMA Process<br>Adapter Interrupt<br>Adapter-Specific MAC Processes                                                                                                                                                             | 8<br>9<br>12<br>14<br>19<br>26<br>28<br>33<br>34<br>35<br>36               |

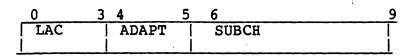

| <br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15 | LCB Format for Load/Dump<br>LCB Format for Start I/O<br>DMA Request/Confirm<br>DMA Request/Confirm<br>DMA Request/Confirm<br>DMA Request/Confirm<br>Retry Dispatch Table Request/Confirm<br>L6 Buffer List<br>Data Transmit/Fault Indicate<br>Fault Indicate Status From Data Transmit<br>Event Indicate Message Block<br>IODISP Dispatch Table Setup<br>IOLD Information Message Block<br>Data Indicate Message Block<br>LMI Request/Confirm | 50<br>51<br>58<br>59<br>60<br>61<br>62<br>63<br>66<br>71<br>76<br>78<br>79 |

| 4-1<br>4-2                                                                                                      | LAC-Adapter Bus<br>Test Connector                                                                                                                                                                                                                                                                                                                                                                                                             | 82<br>83                                                                   |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5                                                                                 | Address Space Layout During QLT<br>Address Space Layout During Normal Operation<br>I/O Order Temporary Queue<br>Configuration Information Area<br>LAC Error Status                                                                                                                                                                                                                                                                            | 89<br>90<br>91<br>92<br>92                                                 |

| A-1                                                                                                             | Token Bus Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                       | 94                                                                         |

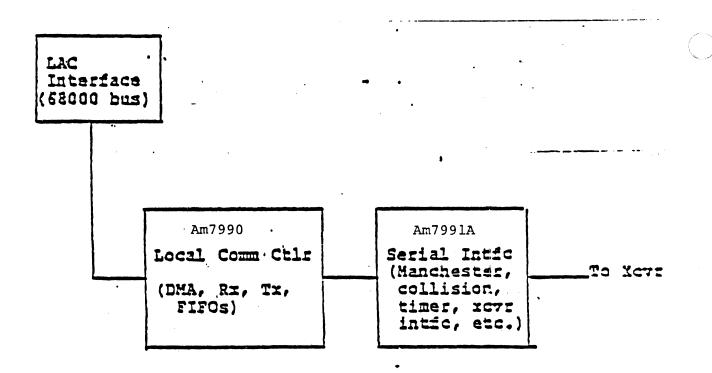

| B-1                                                                                                             | CSMA/CD (ETHERNET) Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                              | 97                                                                         |

| C-1                                                                                                             | Token Ring Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                      | 99                                                                         |

|                                                                                                                 | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| 2-1 | Software | Event | Notification | Codes |

|-----|----------|-------|--------------|-------|

|     |          |       |              |       |

# HONEYWELL CONFIDENTIAL & PROPRIETARY

43

| HONEYWELL | 1 | SPEC. NO. | SHEET | REV | 1 |

|-----------|---|-----------|-------|-----|---|

| 1         | 1 | 60149766  | 3     | Н   | 1 |

|           |   |           |       |     |   |

SECTION 1

INTRODUCTION

# 1.1 DOCUMENT DEFINITION

This document defines the functional characteristics and program-visible architecture of the Local Area Controller Subsystem (LACS).

# 1.2 <u>REFERENCE DOCUMENTS</u>

| 1.     | 60149824   | DPS6 Local Area Network Controller PFS                                                                            |

|--------|------------|-------------------------------------------------------------------------------------------------------------------|

| 2.     | 58088015   | Local Area Networks Global Functional Spec.                                                                       |

| 3.     | CC71       | Level 6 Minicomputer Handbook                                                                                     |

| 4.     | DSA-41     | Local Area Networks                                                                                               |

| 5.     | IEEE 802.1 | Local Area Network Overview, Rev. B, June<br>1983                                                                 |

| 6.     | ISO 7498   | Open System Interconnection Ref. Model                                                                            |

| 7.     | IEEE 802.2 | Local Area Network Logical Link Control,<br>Draft E, March 1984                                                   |

| 8.     | IEEE 802.3 | Local Area Network CSMA/CD Access, July 1983                                                                      |

| 9.     | IEEE 802.4 | Local Area Network Token Bus Access, Draft E,<br>July 1983                                                        |

| 10.IEE | E 802.5    | Local Area Network Token Ring Access, Draft<br>9/23/83                                                            |

| 11.    |            | Ethernet Specification, Version 2.0<br>(Digital Equipment Corp., Intel Corp.,<br>Xerox Corp.)                     |

| 12.    | B01.08     | HIS Standard, Operating Environment                                                                               |

| 13.    |            | HIS Standard, Equipment Safety                                                                                    |

| 14.    | D.002.01   |                                                                                                                   |

| 15.    |            | MRX Megabus EPS-1                                                                                                 |

| 16.    | MTG2       | PWA Test Documentation Requirements                                                                               |

| 17.    | MTG3       | PWA Test Documentation Requirements<br>PWA Microdiagnostic Creation                                               |

| 18.    | MTG5       | QLT Creation                                                                                                      |

|        |            | T&V Creation                                                                                                      |

| 20.    | 58035052   | Worldwide Maintenance Requirements                                                                                |

| 21.    |            | MC68000 User's Manual (Motorola                                                                                   |

|        | (AD2)      | Semi-conductor Products, Inc.)                                                                                    |

| 22.    | 60126298   | Level 6 Bus (Megabus) EPS-1                                                                                       |

|        | 03860507   | Purchase Specification for RF Modem                                                                               |

| 24.    |            | 82586 Reference Manual (INTEL Corp.)                                                                              |

| 25.    | 09-0016-00 | ESPL Software Technical Reference Manual,<br>Vol. 1, Kernel and Support Software (Bridge<br>Communications, Inc.) |

| 26.    | 60149817   | LAN Software EPS-1                                                                                                |

|        |            |                                                                                                                   |

HONEYWELL CONFIDENTIAL & PROPRIETARY

٩

| HON<br> | IEYWELL |            |                         | SPEC. NO.<br>60149766 |             | REV<br>  H | <br> <br>(* |

|---------|---------|------------|-------------------------|-----------------------|-------------|------------|-------------|

| 1.3     | ABBREVI | ATION      | S/DEFINITIONS           |                       |             |            | No.         |

|         | ACK     | -          | Positive Ackn<br>EPS-1) | owledgement           | (as defined | by the L6  | Bus         |

|         | СМ      | -          | Controller Ma           | nagement (So          | oftware)    |            |             |

|         | CRC     |            | Cyclic Redund           |                       |             |            |             |

|         | CPU     | -          | Central Proce           |                       |             |            |             |

|         | CS      | -          | Communication           |                       | oftware)    |            |             |

|         | CSMA/CD | -          | Carrier Sense           |                       |             | ion Detect |             |

|         | DMA     | -          | Direct Memory           | Access                | •           |            |             |

|         | DA      | -          | Destination A           |                       |             |            |             |

|         | DSAP    | -          | Destination S           |                       | ss Point    |            |             |

|         | FC      | -          | Function Code           |                       |             |            |             |

|         | FIFO    | -          | First-In-Firs           |                       | ;           |            |             |

|         | GA      | -          | Group Address           |                       |             |            |             |

|         | ICW     | -          | Interrupt Con           |                       |             |            |             |

|         | IORB    |            | Input/Output            |                       | ck          |            |             |

|         | ID      | <b>-</b> . | Identificatio           |                       |             |            |             |

|         | IF      |            | Interface (So           | ftware)               |             |            |             |

|         | I/O     | -          | Input/Output            | -                     |             |            |             |

|         | IOLD    |            | Input/Output            | Load                  |             | •          |             |

|         | LAC     | -          |                         |                       |             | • •        |             |

|         | LACS    |            | Local Area Co           | ntroller Sul          | bsystem     |            |             |

|         | LAN     | -          | Local Area Ne           | twork                 |             |            |             |

|         | LCB     |            | LAN Control B           | lock                  |             |            | (           |

|         | LCBI    | -          | LAN Control B           | lock Image            |             |            | 6           |

|         | LLC     | -          | Link Layer Co           | ntrol                 |             |            |             |

|         | LME     | -          | Layer Managem           | ent Entity            | •           |            |             |

|         | LMI     | -          | Layer Managem           | ent Interfa           | ce          |            |             |

|         | LSAP    | -          | Link Service            | Access Point          | t           |            |             |

|         | LSI     |            | Large Scale I           | ntegration            |             | •          |             |

|         | MAC     | -          | Media Access            | Controller            |             |            |             |

|         | MBZ     | -          | Must be Zero            |                       |             |            |             |

|         | MSB     | -          | Most Signific           | ant Byte              |             |            |             |

|         | MSb     | -          | Most Signific           |                       |             |            |             |

|         | MTBF    | -          | Mean Time Bet           |                       | es          |            |             |

|         | MTTR    |            | Mean Time To            |                       |             |            |             |

|         | NAK     | -          | Negative Ackn<br>EPS-1) |                       | (defined by | the L6 Bu  | 5           |

|         | ORU     |            | Optimum Repla           | ceable Unit           |             |            |             |

|         | OS      | -          | Operating Sys           | tem                   |             |            |             |

|         | OSI     |            | Open Systems            |                       | tion        |            |             |

|           |  |           |       |     | - |

|-----------|--|-----------|-------|-----|---|

| HONEYWELL |  | SPEC. NO. | SHEET | REV |   |

| 1         |  | 60149766  | 5     | Н   | I |

1.3 <u>ABBREVIATIONS/DEFINITIONS</u> (Continued)

| PC    |            | Personal Computer                         |

|-------|------------|-------------------------------------------|

| PIO   | -          | Physical Input/Output                     |

| PROM  | -          | Programmable Read-Only Memory             |

| PDU   | -          | Protocol Data Unit                        |

| QLT   | -          | Quality Logic Test                        |

| RAM   | -          | Random Access Memory                      |

| RFU   | -          | Reserved for Future Use                   |

| RHU   | -          | Reserved for Hardware Use                 |

| RSU   | -          | Reserved for Software Use                 |

| SA    | -          | Source Address/Station Address            |

| SC    | -          | Service Call                              |

| SMDSI | -          | Systems Management Data Service Interface |

| SSAP  | -          | Source Service Access Point               |

| TBD   | <b>-</b> . | To Be Defined                             |

| TC    | -          | Trunk Coupler                             |

| T&V   | -          | Test and Verification                     |

| WS    | -          | Work Station                              |

| HONEYWELL | SPEC. NO. | SHEET | REV | ł |

|-----------|-----------|-------|-----|---|

|           | 60149766  | 6     | Н   | 1 |

|           |           |       |     |   |

SECTION 2 ARCHITECTURE

#### 2.1 OVERVIEW

The Local Area Controller Subsystem (LACS) is a programmable communications subsystem that connects to the Level 6 Megabus. LACS comprises the following set of communications components:

- o Local Area Controller (LAC) Motherboard

- o Media Access Controller (MAC) & Physical Layer Adapters

- o Trunk Couplers (TCs)

- o RF Modems

This specification is concerned with the definition and description of the first two items above (i.e., the LAC and the adapters).

With suitable software loads and hardware/ adapter selection, the LACS is intended to be capable of supporting any of the IEEE 802 Local Area Network Standards.

The design of the LACS minimizes the interactions required over the Level 6/LACS interface and isolates the LACS on-board communications software from the specific hardware characteristics of the Level 6 and LAN adapter interfaces via supporting interface software.

A communications kernel based on one by Bridge Communications Inc., is used as the O.S. within the LAC. In this specification "CS Software" (Communication Service) refers to LAC-resident software which implements the OSI Link, Network, and Transport layers; "SM Software" (System Management layer instance) refers to LAC-resident software which supports IEEE802 System Management functions. CS and SM software will be written in "C" language by Honeywell Software Development and is the subject of a separate EPS-1.

"IF Software" (InterFace) refers to LAC-resident software which provides interfacing support between the CS and SM software and the LACS hardware. IF software will be written in "C" and assembly language by Honeywell Hardware Development and its functionality and interfaces are described in this specification. The Term "LAC Software" refers to all LAC-resident software (O.S. Kernel, CS SM and IF).

| HONEYWELL | SPEC. NO. | SHEET | I REV |   |  |  |

|-----------|-----------|-------|-------|---|--|--|

|           | 60149766  | 7     | H     | 1 |  |  |

|           |           |       |       |   |  |  |

Although the IEEE 802 Standard goes no higher than a standard data link control interface (Layer 3/Layer 2), the Level 6-to-LACS interface that is provided is so heavily software-defined and flexible as to be readily adaptable to support of higher (e.g. Session/Transport) layer interfaces (with suitable Level 6 and CS software).

The LACS, used for all Local Area Network (LAN) applications, is mounted in a standard Level 6 chassis and requires one slot on the Megabus; it will support the 32-bit address bus of the larger Level 6 systems. The LAN adapters provide an interface from the LAC to the LAN. The adapter (a daughterboard) includes a Media Access Controller (MAC). The LAC provides for the attachment of up to four adapter daughterboards.

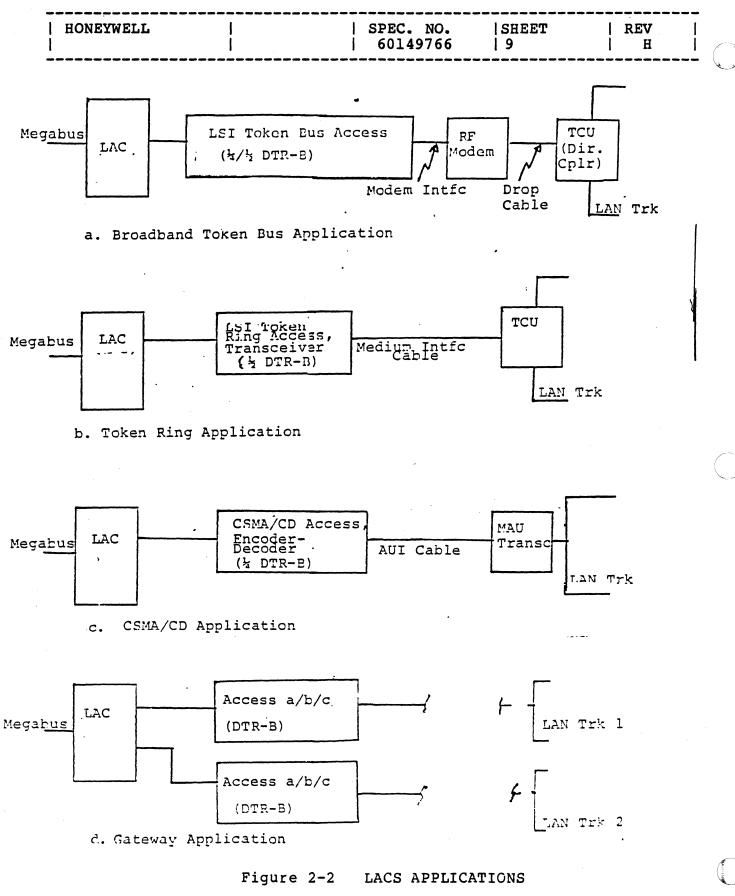

The adapters are of several types (e.g., Token Bus MAC, CSMA/CD MAC, etc.).

The TCs are of several types (for example, broadband directional coupler, token ring TCU, Ethernet transceiver) and are packaged as separate units. The RF modem, used for broadband applications, is also separately packaged.

Because of its ability to support adapters of similar or dissimilar types, the LACS (with appropriate LAC software) can be used not only for 802 LAN connection with a Level 6 but also in future as a gateway between 802 LANS, or, in the case of broadband LANs, as a bridge between broadband channels. Other applications for the LACS could be as LAN traffic monitor/journalizer and network control. The CS and SM software would, of course be tailored for each application; it is expected that the IF software and O.S. Kernel will be used in all applications.

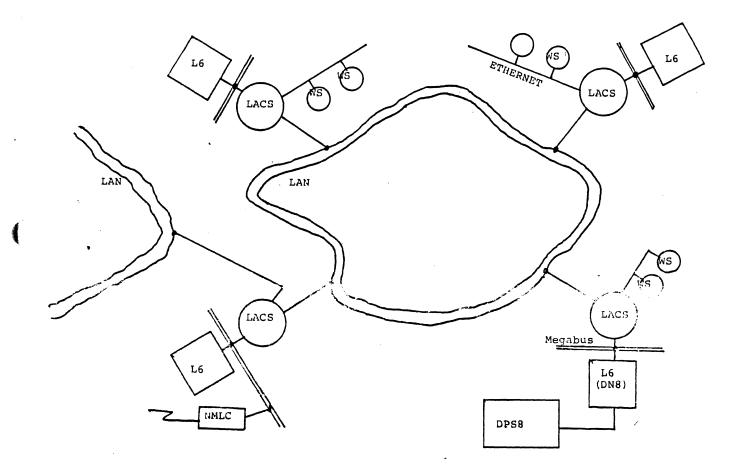

Figure 2-1 shows a Local Area Network with LACS providing connections for Level 6 systems, for workstation LAN access, and for Gateway between LANs; Figure 2-2 shows various configurations of the LACS. A maximum of two ports are shown in use.

| HONEYWELL | <br>I | SPEC. NO. | SHEET | REV |   |

|-----------|-------|-----------|-------|-----|---|

| 1         | 1     | 60149766  | 8     | I H | 1 |

|           |       |           |       |     |   |

Figure 2-1 LACS APPLICATIONS TO LOCAL AREA NETWORKS

HONEYWELL CONFIDENTIAL & PROPRIETARY

٥

| HONEYWELL |   | SPEC. NO. | SHEET | REV | 1 |

|-----------|---|-----------|-------|-----|---|

| 1         | 1 | 60149766  | 10    | H   | 1 |

# 2.2 SECURITY

No encryption/decryption functionality is defined for the LACS for the following reasons:

- 1. The IEEE 802 Standards do not specify any link layer or station encryption technique.

- 2. For a LAN, the use of the National Bureau of Standards Data Encryption Standard (DES) would be better applied at the Session or Presentation layer.

- 3. Key management on a LAN at the link layer presents many logistical problems with a DES technique. It would seem there is a good possibility that if an encryption technique is defined for LAN use, it will be based on some kind of Public Key scheme applied by the station.

- 4. Standards for Public Key systems do not exist at present.

### 2.3 MULTIPROCESSOR SUPPORT

The LAC provides for multiprocessor central systems (having up to 16 processors) in its I/O interface. Each I/O command block (LCB) issued to the LACS will contain fields which indicate the channel number of the CPU which is to be interrupted on completion of the function called for and the interrupt LEVEL to use. The LAC Software retains this information while carrying out the operation.

LAC hardware provides an interlock mechanism to handle the problem of two or more CPUs attempting to issue IOLDs (with Function Code 09/OD) simultaneously to the LAC. Further details are in subsection 3.2.2.

LAC hardware provides the specific capabilities required for connection to the multiprocessor type Megabus as well as to a monoprocessor type Megabus. Further details are in subsection 4.1.

| HONEYWELL | 1 | SPEC. NO. | SHEET | REV | 1 |

|-----------|---|-----------|-------|-----|---|

| 1         | l | 60149766  | 11    | Н   | 1 |

### 2.4 LOCAL AREA CONTROLLER (LAC)

The LAC, via hardware, software-generated parameters and CS software, provides OSI layer functions such as sequencing of outgoing frames, error control and retransmission, sequence checking of incoming frames and statistics gathering.

There are three software-visible interfaces associated with the LACS which are described in this specification: the CS/SM Software - IF Software interface in operations with the CPU and main memory; the CS/SM Software- IF Software interface in operations with the attached adapter(s) and the LACS I/O Order interface as seen by the LACS Driver in the CPU.

The operations of the three interfaces listed above and a brief description of the physical organization of the LAC are covered in the remainder of this Section. Further details of the physical organization of the LACS and its physical interfaces are covered in Section 4, 6, and 7 and in the appendices.

| HONEYWELL | 1 | SPEC. NO. | SHEET | REV | 1 |

|-----------|---|-----------|-------|-----|---|

| 1         | l | 60149766  | 112   | H   | 1 |

|           |   |           |       |     |   |

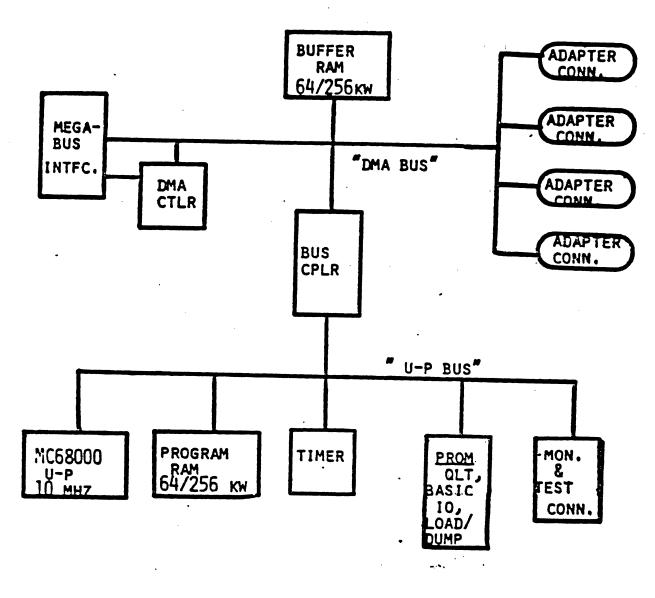

## 2.5 LAC BLOCK DIAGRAM

A block diagram of the LAC is shown in Figure 2-3.

The LAC uses a commercially popular microprocessor (MC68000) and presents that microprocessor's bus to the adapters.

Figure 2-3 LAC BLOCK DIAGRAM

HONEYWELL CONFIDENTIAL & PROPRIETARY

۵

| HONEYWELL | I | SPEC. NO. | SHEET | REV | 1 |

|-----------|---|-----------|-------|-----|---|

|           | l | 60149766  | 13    | H   | 1 |

|           |   |           |       |     |   |

The RAM is physically separated into two sections: a data buffer RAM and program RAM. The intent of the separation is to allow for simultaneous DMA of data in the data buffer RAM with the Level 6 memory or with the LAN adapters along with software execution in the program RAM. The Bus Coupler allows for simultaneous independent operation of the MC68000 busses on each side, yet permits the microprocessor to perform accesses to any location in the total RAM.

The DMA controller is a two-channel device; one channel is used by the microprocessor to perform the DMA movement of data between main memory and the data buffer RAM. The other channel is used to accept I/O order information from the Megabus and deliver it to a temporary queue in the data buffer RAM for further analysis and disposition by firmware or IF software.

The timer device provides the basic clock tick for the LAC operating system to use in providing timer functions for LAC software .

DMA functionality for the adapters is provided by hardware located on the adapters themselves. Adapter DMA is always into or out of the data buffer RAM.