# HONEYWELL

# HARDWARE

## DPS 6 & LEVEL 6 COMMUNICATIONS HANDBOOK

#### SUBJECT

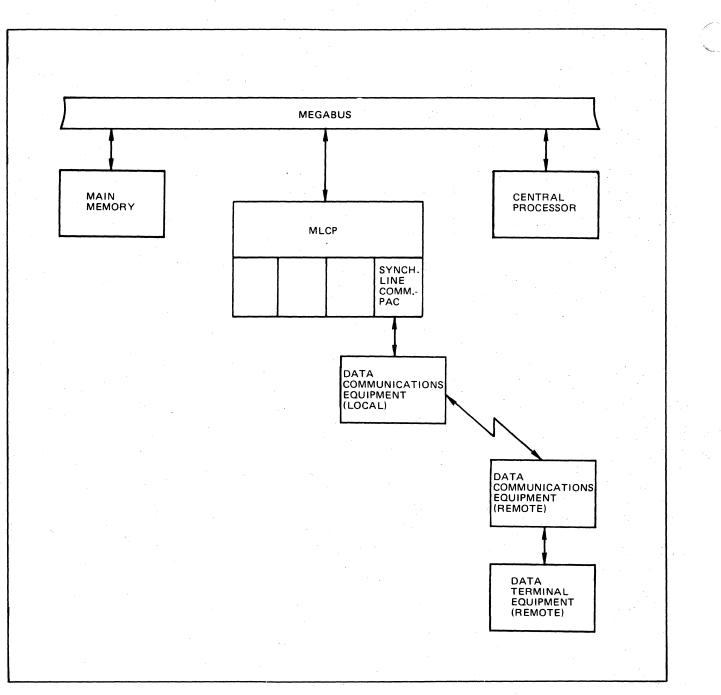

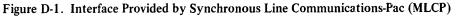

Multiline Communications Processor (MLCP) and Dual Line Communications Processor (DLCP), Related Line Interfaces, and Reference Information for Programmer Developing Communications Applications

#### SPECIAL INSTRUCTIONS

This edition of the manual completely supersedes Revision 1 dated May 1977, and Addendum A dated September 1977. Due to the extent of the revision, change bars and asterisks (denoting deletions) have not been used. Refer to the Preface for a summary of the major new items added since the last revision.

.

ORDER NUMBER AT97-02

October 1978

### **Preface**

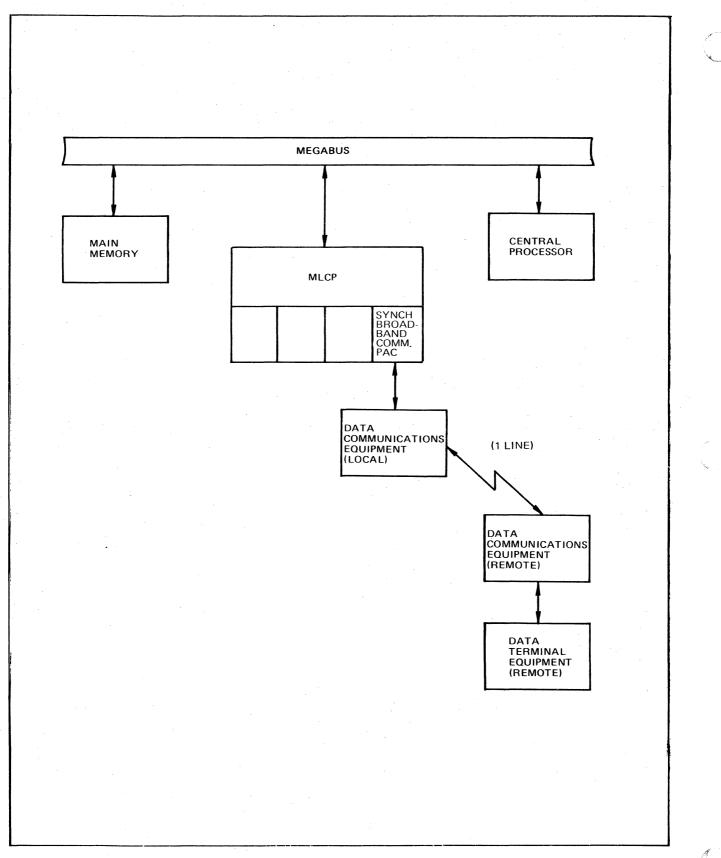

This manual is intended for computer programmers who are already experienced in creating communications applications. The purpose of this manual is to assist these experienced communications programmers in creating applications for a Honeywell Series 60 (Level 6) hardware environment that includes a Multiline Communications Processor (MLCP) or a Dual Line Communications Processor (DLCP), and one or more line interfaces (adapters, Communications-Pacs).

The presentation is limited to a discussion of these communications processors and their associated line interfaces; the reader's knowledge of data communications equipment, communications line conventions, and data terminal equipment is expected to be based on additional sources such as those listed at the end of this Preface.

This reference handbook is intended for use in conjunction with appropriate Honeywell documentation for the Level 6 operating systems referenced in the list that immediately follows the new and changed information below.

New and changed information since the last edition of the manual includes the following:

- o All information concerning the Dual Line Communications Processor (DLCP) is new. Timings for DLCP instructions are based on firmware revision 4.

- o Appendices on the following line interfaces:

- 1. Synchronous Broadband Communications-Pac (Appendix E)

- 2. DCM9110 Communications-Pac, Autocall Feature (Appendix F) o Reorganized:

- 1. Table Look-up example for MLCP, originally contained in Section 4, may now be referenced in Appendix A.

- 2. MLCP-specific LCT firmware-use-only diagrams, originally found in Section 5, may now be referenced in Appendix A.

- 3. LCT diagrams for MLCP and DLCP collectively are contained in Section 5.

- NOTE: Throughout this manual, the MLCP and DLCP are referred to collectively as the "Processor." The word "adapter" is used to reference the line interface, which in the case of the DLCP is present on the same physical board as the DLCP and which in the case of the MLCP is separately packaged (Communications-Pac). The function of the two is identical in either instance.

Main memory (i.e., the Level 6 central processor) programs are referenced as such or are abbreviated as MMP.

Individual references to MLCP and DLCP have been retained where appropriate.

Honeywell disclaims the implied warranties of merchantability and fitness for a particular purpose and makes no express warranties except as may be stated in its written agreement with and for its customer.

In no event is Honeywell liable to anyone for any indirect, special or consequential damages. The information and specifications in this document are subject to change without notice.

© Honeywell Information Systems Inc., 1978

File No.: 1R03, 1S03

#### **RELATED HONEYWELL LITERATURE**

| Order<br>Number | Manual Title                                  |

|-----------------|-----------------------------------------------|

| CB20            | GCOS 6 MOD 400 System Concepts                |

| CB21            | GCOS 6 MOD 400 Program Execution and Checkout |

| CB22            | GCOS 6 MOD 400 Programmer's Guide             |

| CB23            | GCOS 6 MOD 400 System Building                |

| CB24            | GCOS 6 MOD 400 Operator's Guide               |

| CB01            | GCOS 6 Program Preparation                    |

| CB02            | GCOS 6 Commands                               |

| CB07            | GCOS 6 Assembly Language Reference            |

#### REFERENCE LITERATURE FOR DATA COMMUNICATIONS EQUIPMENT

The following non-Honeywell publications should be referenced as appropriate.

- o EIA (Electronic Industries Association) Standard RS-232-C

- o CCITT (International Consultive Committee for Telephony and Telegraphy) White Book, Volume VIII

- Data Set 103A Interface Specification February 1967 (Bell System Technical Reference, PUB41101)

- Data Set 103A3/103E/103G/103H Interface Specification October 1973 (Bell System Technical Reference, PUB41102)

- o Data Set 103F Interface Specification May 1964 (Bell System Technical Reference, PUB41103)

- Data Set 113A Interface Specification August 1973 (Bell System Technical Reference, PUB41104)

- o 113-Type Data Station Interface Specification October 1971 (Bell System Technical Reference, PUB41105)

- o Data Sets 201A & B August 1969 (Bell System Technical Reference, PUB41201)

- o Data Set 201C Interface Specification April 1973 (Bell System Technical Reference, PUB41210)

- Data Sets 202C & D Interface Specification May 1964 (Bell System Technical Reference, PUB41202)

- o Data Sets 202S & T Interface Specification August 1974 (Bell System Technical Reference, PUB41212)

- o Data Set 203-Type Revised April 1974 (Bell System Technical Reference, PUB41204)

- o Data Set 208A Interface Specification November 1973 (Bell System Technical Reference, PUB41209)

- Data Set 208B Interface Specification August 1973 (Bell System Technical Reference, PUB41211)

- Data Set 301B Interface Specification March 1967 (Bell System Technical Reference, PUB41301)

- o Wideband Data Station 303 Type December 1974 (Bell System Technical Reference, PUB41302)

- Digital Data System Data Service Unit Interface Specification March 1973 (Bell System Technical Reference, PUB41450)

- o Interface Between Data Terminal Equipment and Automatic Calling Equipment for Data Communication – August 1969 (Electronic Industries Association, RS-366)

# **Contents**

| n | - |                    |

|---|---|--------------------|

| м | υ | $\boldsymbol{\nu}$ |

|   |   |                    |

| Section 1. Introduction to Level 6                 |            |

|----------------------------------------------------|------------|

| Communications                                     | 1-1        |

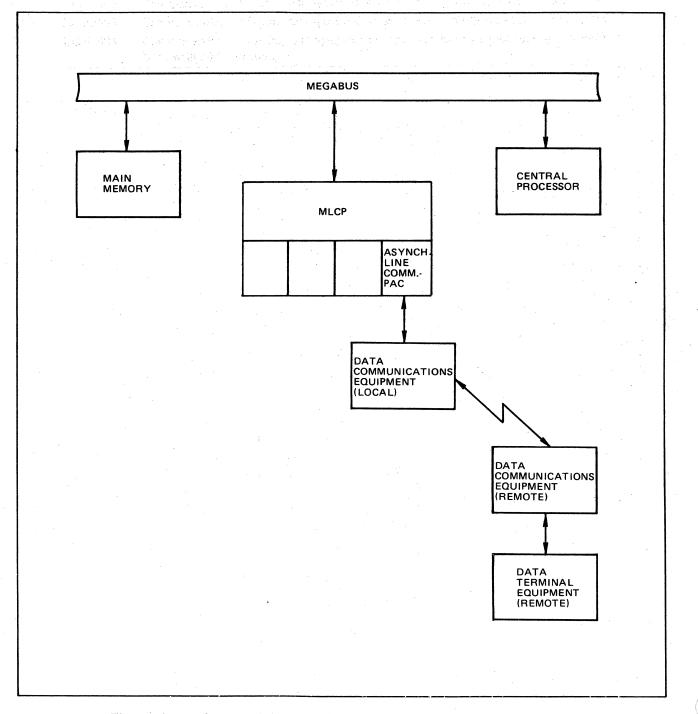

| Hardware Overview                                  | 1-1        |

| MLCP                                               |            |

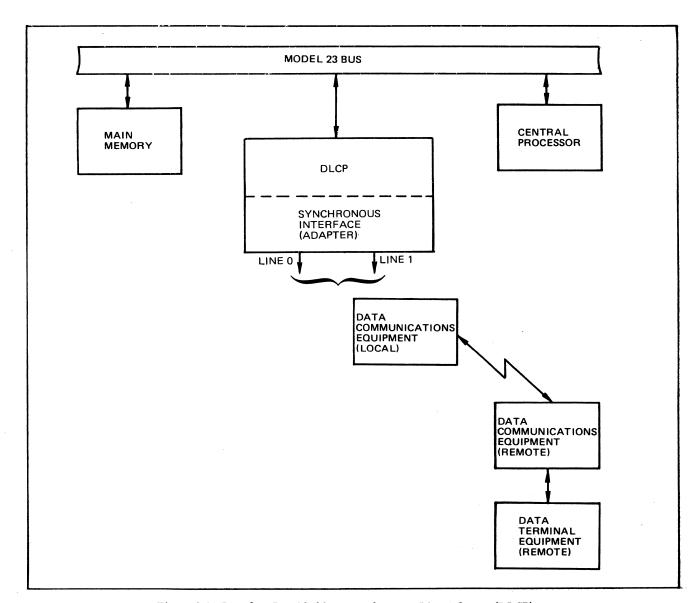

| DLCP                                               | 1-1        |

| Operation                                          | 1-2        |

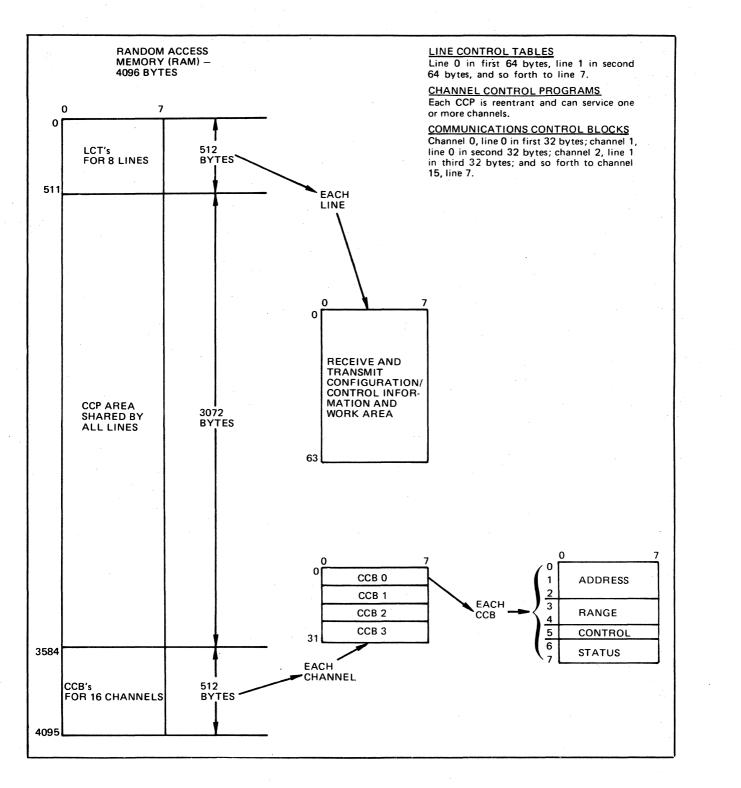

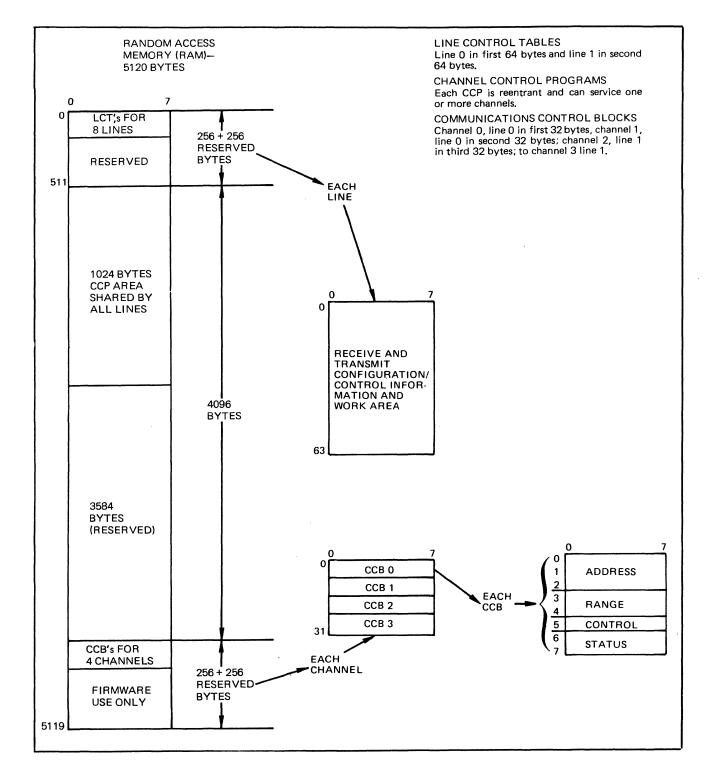

| RAM Layout                                         | 1-3        |

| Message Delimiting                                 | 1-3        |

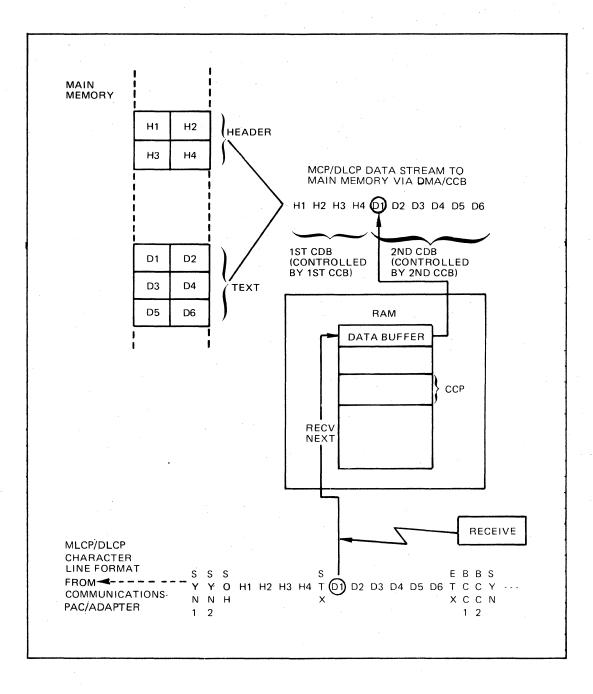

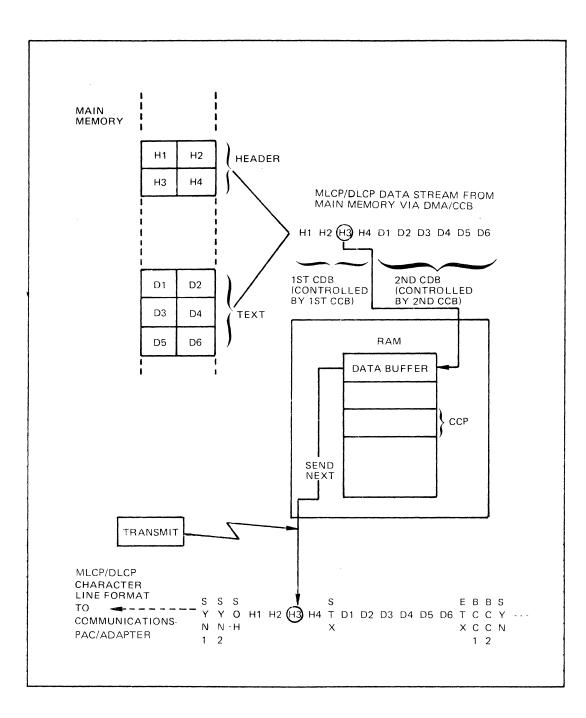

| Transmit and Receive                               | 1-8        |

| Summary of Major Features                          | 1-8        |

| Processing Priorities                              | 1-8        |

| Servicing Main Memory Program                      |            |

| Input/Output Instructions                          | 1-8        |

| Servicing Communications-Pac/Adapter               |            |

| Channel Request Interrupts                         | 1-8        |

| Background Firmware Scanning                       | 1-11       |

| Programming Overview                               | 1-11       |

| Main Memory Program                                | 1-12       |

| Communications Control Blocks                      | 1-12       |

| Channel Control Program                            | 1-12       |

| Line Control Tables                                | 1-13       |

| Setting Up the Processor; Receiving                |            |

| and Transmitting Data                              | 1-13       |

|                                                    |            |

| Section 2. Main Memory Program                     | 2-1        |

| Summary of Main Memory Program                     |            |

| Input/Output Instructions Related                  | ~ ~        |

| to Processor                                       | 2-1        |

| Control of Communications                          | ~ ~        |

| Data Blocks                                        | 2-3        |

| Control of Communications Control                  | <b>~</b> ~ |

| Blocks                                             | 2-3        |

| Control of Channel Control                         | <b>~</b> 2 |

| Programs<br>Detection of Errors and Status Changes | 2-3        |

| Related to Data Communications                     |            |

| Equipment and Data Terminal                        |            |

| Equipment                                          | 2.2        |

| Detailed Description of Main Memory                | 2-3        |

| Program Input/Output Instructions                  |            |

| Related to Processor                               | 2-4        |

| IO (Input CCB Range) Instruction                   |            |

| IO (Input CCB Status) Instruction                  |            |

| IO (Input Data Set Status)                         | 2-5        |

| Instruction                                        | 2-5        |

| IO (Input Device Identification                    | 23         |

| Number) Instruction                                | 2-5        |

| IO (Input LCT Byte) Instruction                    |            |

| IO (Input Der Dyte) Instruction                    | - 0        |

| Instruction                                        | 2-6        |

| IO (Input Extended Identification                  |            |

| Number) Instruction                                | 2-6        |

| IOLD (Output CCB Address and Range)                |            |

| Instruction                                        |            |

|                                               | 1 480  |

|-----------------------------------------------|--------|

| IO (Output CCB Control)                       |        |

| Instruction                                   | . 2-7  |

| IO (Output Channel Control)                   |        |

| Instruction                                   | . 2-8  |

| IO (Output Interrupt Control)                 |        |

| Instruction<br>IO (Output LCT Byte)           | . 2-10 |

| IO (Output LCT Byte)                          |        |

| Instruction                                   | . 2-10 |

| IO (Output MLCP/DLCP Control)                 |        |

| Instruction                                   |        |

| Soft Initialize                               | . 2-11 |

|                                               |        |

| Section 3. Communications Control             |        |

| Blocks                                        |        |

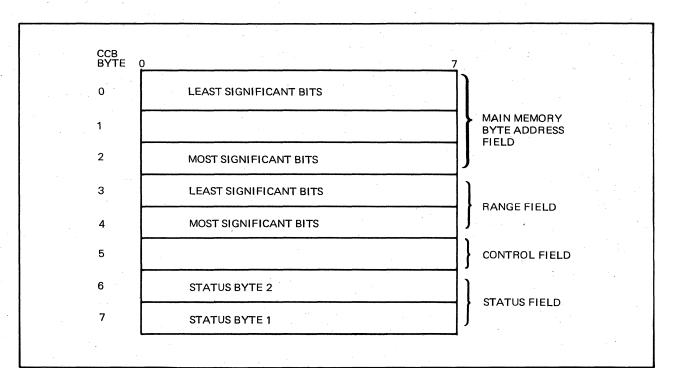

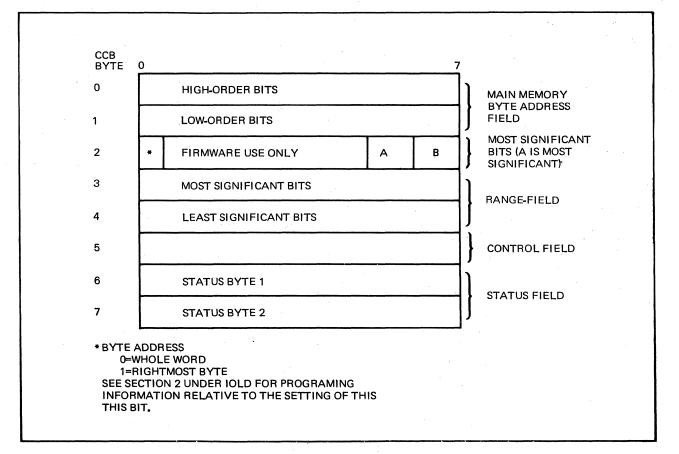

| CCB Format                                    |        |

| CCB Address Field                             |        |

| MLCP                                          |        |

| DLCP                                          |        |

| CCB Range Field                               |        |

| CCB Control Field                             |        |

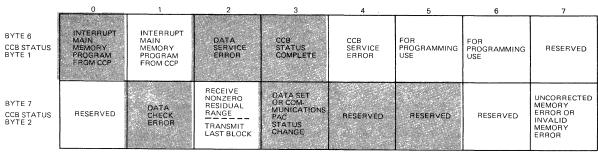

| CCB Status Field                              |        |

| Writing a CCB                                 |        |

| CCB Descriptions of a CDB                     |        |

| MLCP                                          |        |

| DLCP                                          | . 3-9  |

| Processing of an "Active" CCB                 | . 3-10 |

| Completion of a CCB                           | . 3-10 |

|                                               |        |

| Section 4. Channel Control Program            |        |

| CCP Structure and Components                  |        |

| CCP Setup                                     |        |

| Starting CCP                                  | . 4-1  |

| MLCP CCP Execution                            |        |

| DLCP CCP Execution                            | . 4-2  |

| MLCP Registers and Program                    | 4.2    |

| Indicators Used by CCP                        | . 4-3  |

| DLCP Registers and Program                    | 4.0    |

| Indicators used by CCP                        | . 4-3  |

| Using CCP Generation Control                  |        |

| Statements and Executable                     | 4 4    |

| Instructions                                  |        |

| Program Development Tools                     |        |

| Programming Rules                             | . 4-4  |

| Macro Preprocessor and Assembly               | 4 5    |

| Operation                                     |        |

| Internal Formats                              |        |

| MLCP Loader<br>CCP Generation Control         | . 4-5  |

|                                               | 4 5    |

| Statements                                    |        |

| LOC Statement                                 |        |

| ORG Statement                                 |        |

| MORG Statement                                |        |

| DATA Statement<br>CCP Executable Instructions | . 4-/  |

|                                               |        |

| Branch Instructions                           |        |

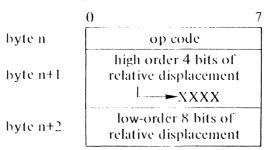

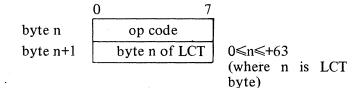

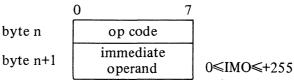

| Short Displacement Instructions               | . 4-10 |

Page

| Page |

|------|

|------|

|                                                                            | 0                                            |

|----------------------------------------------------------------------------|----------------------------------------------|

| Long Displacement Instruction4<br>Double Operand Instructions4<br>Format 1 | 1-20<br>1-20<br>1-21<br>1-23<br>1-24<br>1-25 |

|                                                                            |                                              |

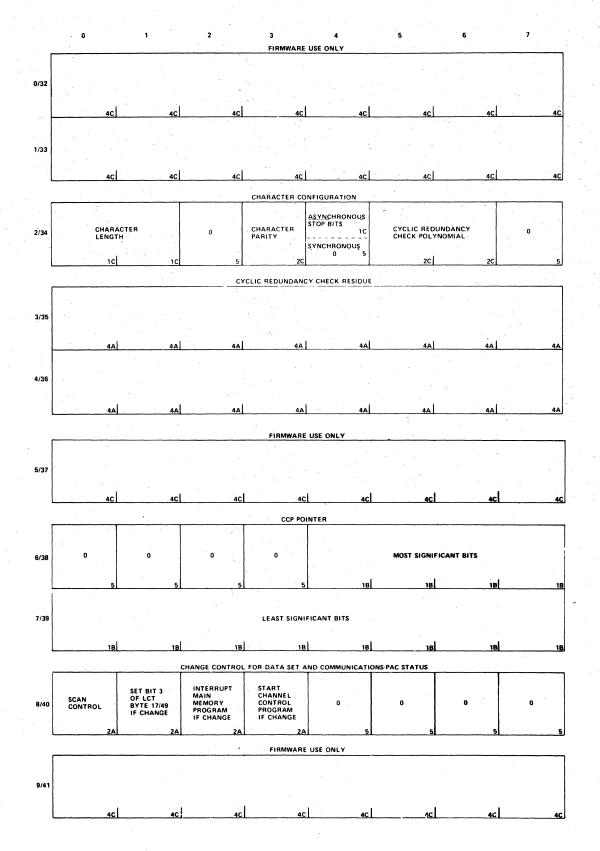

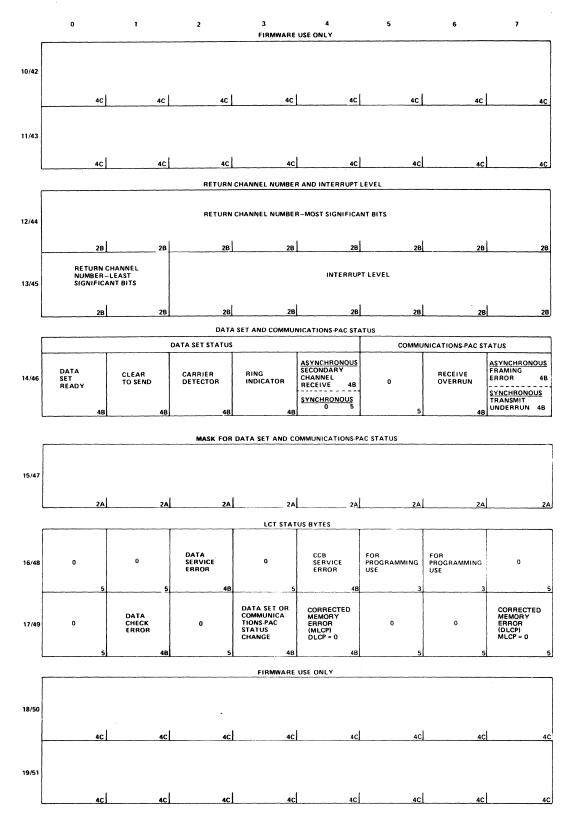

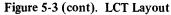

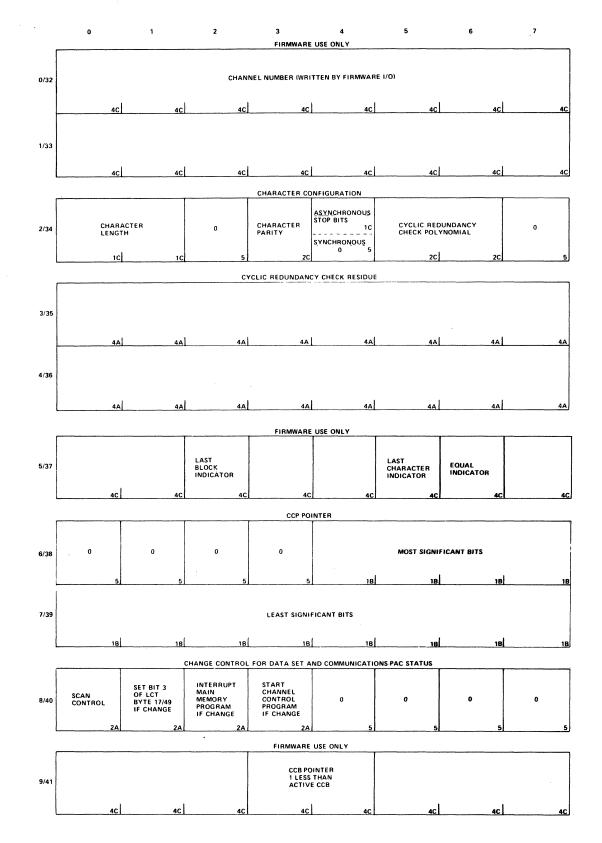

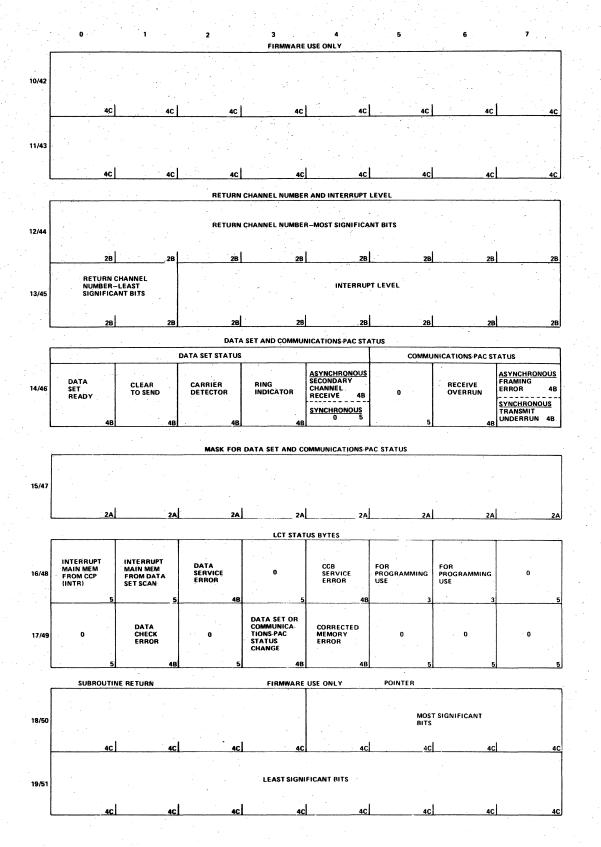

| Section 5. Line Control Tables                                             | 5-1                                          |

| LCT Byte 2/34 – Character                                                  | : >                                          |

| Configuration                                                              | -3                                           |

| Redundancy Check Residue                                                   | 5-4                                          |

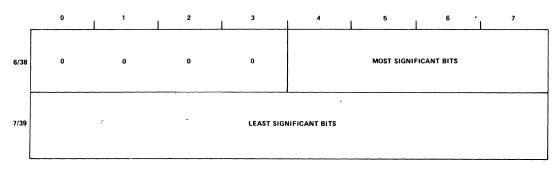

| LCT Bytes $6/38$ and $7/39 - CCP$                                          | , .                                          |

| Pointer 5                                                                  | 5-5                                          |

| LCT Byte 8/40 – Change Control for                                         |                                              |

| Data Set and Adapter Status                                                | -6                                           |

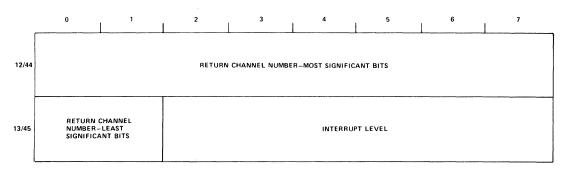

| LCT Bytes 12/44 and 13/45 – Return<br>Channel Number and Interrupt         |                                              |

| Level                                                                      | . 7                                          |

| LCT Byte $14/46$ – Data Set and                                            | - /                                          |

| Adapter Status                                                             | -7                                           |

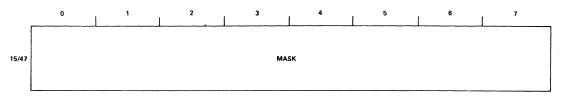

| LCT Byte 15/47 – Mask for Data Set                                         |                                              |

| and Adapter Status                                                         | -9                                           |

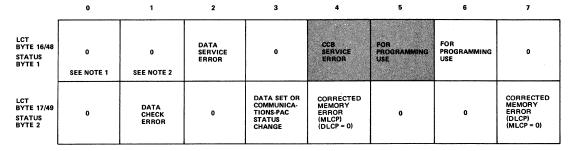

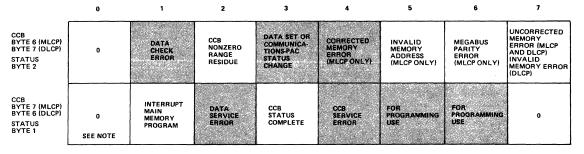

| LCT Bytes 16/48 and 17/49 –                                                | 10                                           |

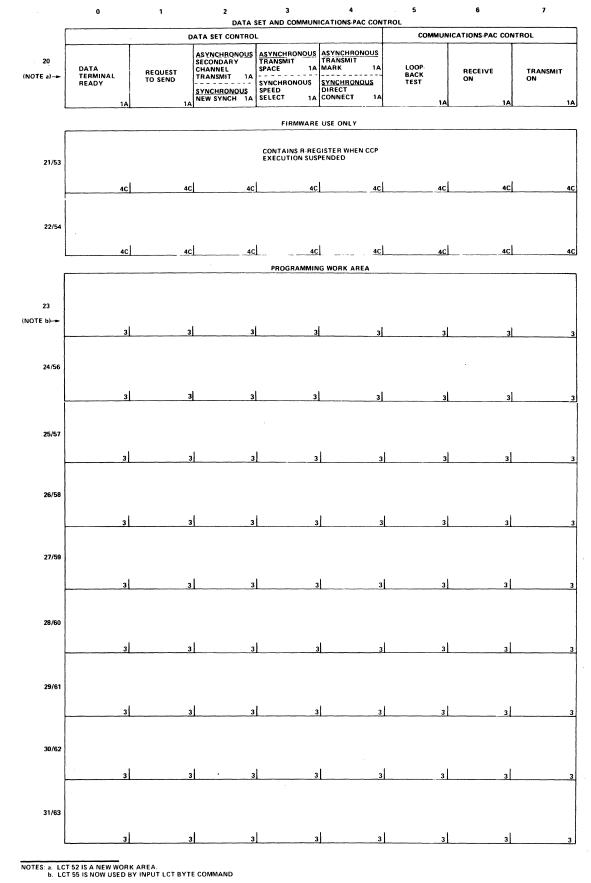

| LCT Status5<br>LCT Byte 20 – Data Set and Adapter                          | -10                                          |

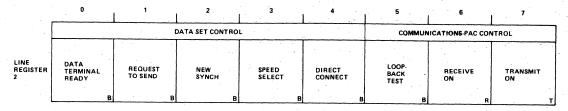

| Control                                                                    | -12                                          |

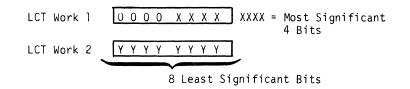

| Programming Work Area                                                      | -12                                          |

| Layout of LCT Bytes                                                        | -14                                          |

|                                                                            |                                              |

| Section 6. Processor Interfaces                                            | -1                                           |

| Processor Channel Number                                                   |                                              |

| Addressing from Main Memory Program6                                       | 1                                            |

| Processor Interrupts to Main                                               | -1                                           |

| Memory Program                                                             | -1                                           |

| Processor Control of Data Sets and                                         | •                                            |

| Line Adapters 6                                                            | -3                                           |

| Processor Monitoring of Data Set                                           |                                              |

| and Adapter Status                                                         | -3                                           |

| Processor Parity Checking and                                              | 4                                            |

| Generation                                                                 | -4                                           |

| Checking                                                                   | -5                                           |

| Data Transfer Datas for Drasses                                            |                                              |

| Communications Lines                                                       | -6                                           |

| Section 7. Program Preparation and                                         |                                              |

| Loading                                                                    |                                              |

| MLCP Loader7                                                               |                                              |

| Load Control Block                                                         |                                              |

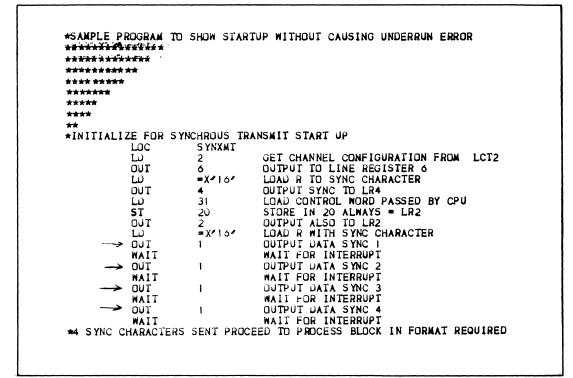

| Sample Program                                                             |                                              |

| Block Mode Write                                                           | -4                                           |

|                                                                            | -5                                           |

|                                                                            |                                              |

| CCB Status Field After<br>Block Mode Write                   |   |

|--------------------------------------------------------------|---|

| Appendix A. Programming Guidelines for<br>Selected MLCP/DLCP |   |

| Features                                                     |   |

| Initialization                                               |   |

| Adapter SetupA-2                                             |   |

| Access to Line Registers                                     |   |

| CCP Instructions                                             |   |

| SEND Instruction                                             |   |

| RECV Instruction                                             |   |

| OUT LR1 Instruction                                          |   |

| IN LR1 Instruction                                           |   |

| SFS Instruction                                              |   |

| BLBT, BLBF Instructions                                      |   |

| LD Instruction                                               |   |

| WAIT Instruction                                             |   |

|                                                              |   |

| BLCT, BLCF Instructions                                      |   |

| INTR Instruction (MLCP Only)A-5                              |   |

| Table Look-Up Instruction                                    |   |

| Programming ExampleA-5                                       |   |

| Valid CCBsA-9                                                |   |

| Data Set ScanA-1                                             | C |

| CPU Interrupts                                               | 1 |

| CCBs as Cause of CPU InterruptsA-1                           | 1 |

| Data Set Scan as Source of                                   |   |

| CPU InterruptsA-1                                            | 1 |

| Combination of CCP Interrupts and                            |   |

| INTR in Debug                                                | 2 |

| Deferred Interrupt Queue                                     |   |

| Forbidden Operations                                         |   |

| Undefined Op Codes                                           |   |

| Undefined Function Codes                                     |   |

|                                                              |   |

| Unprotected MLCP/DLCP Memory A-1<br>Timeouts                 |   |

|                                                              | 5 |

| Addressing Limits                                            | 5 |

| CCB Area Only Implicitly Accessible                          | 3 |

| Inability of One Line to Access                              | ~ |

| Another                                                      | 3 |

| Need for Pad Characters                                      |   |

| Two-Way Alternate Operation                                  |   |

| Error HandlingA-1                                            | 5 |

| Conditions Under Which Processor Will                        |   |

| Issue a NAKA-1                                               | 5 |

| LCT Status BytesA-1                                          | 5 |

| CCB Status Bytes                                             | 6 |

| Block Mode ReadA-1                                           |   |

| Abnormal CCP Termination                                     |   |

| MLCP LCT Bytes Used by                                       |   |

| Firmware                                                     | 7 |

| Worksheet for MLCP Only                                      | 2 |

|                                                              |   |

| Appendix B. Communications-Pacs                              |   |

| endix B. | Communications-Pacs     |  |

|----------|-------------------------|--|

|          | and Adapters Attachable |  |

|          | to MLCP/DLCPB-1         |  |

v

| Appendix C. Asynchronous Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Communications-Pacs/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                            |

| Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . C-1                                                                                                                                                      |

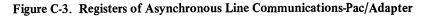

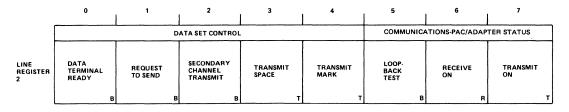

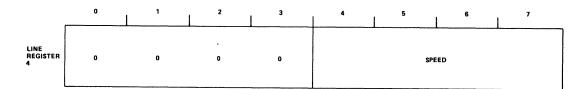

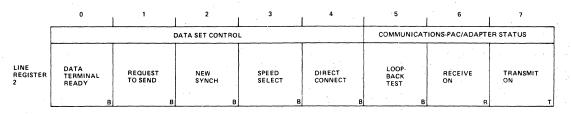

| Line Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . C-1                                                                                                                                                      |

| Line Registers for Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~ -                                                                                                                                                        |

| Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . C-5                                                                                                                                                      |

| Line Registers for Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ~ -                                                                                                                                                        |

| Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                            |

| Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

| Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                            |

| Channel Request Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

| Transmit Space/Mark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            |

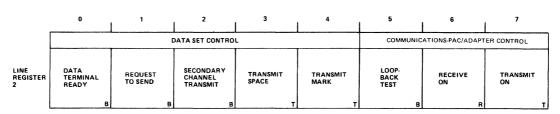

| "Loop-Back" Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

| Receive/Transmit On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                            |

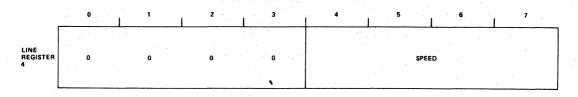

| Line Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

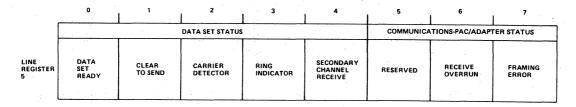

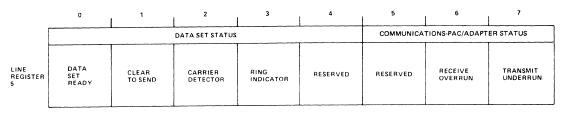

| Clear to Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

| Receive Overrun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |

| Framing Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

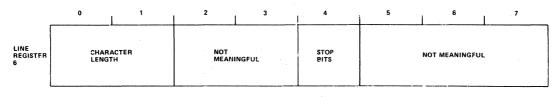

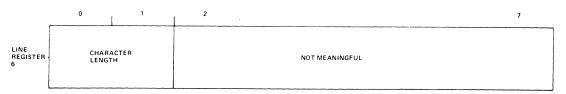

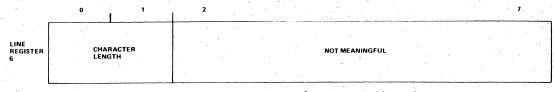

| Character Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

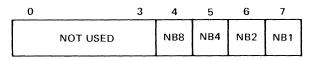

| Parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                            |

| Stop Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| Cyclic Redundancy Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                            |

| Master Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                            |

| Line/Channel Number Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                            |

| Device Identification Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . C-14                                                                                                                                                     |

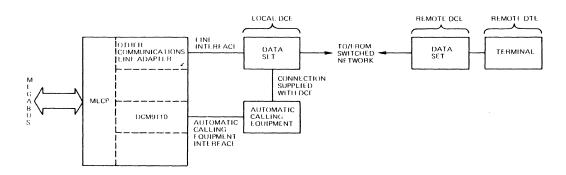

| Physical Interface to Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

| Communications Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>C</b> 1 4                                                                                                                                               |

| and Data Terminal Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .C-14                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |

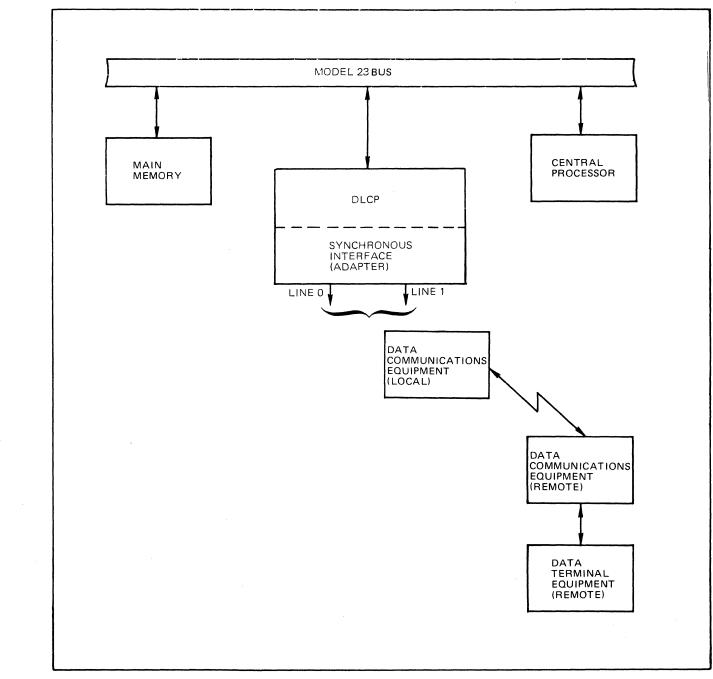

| Annendix D. Synchronous Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                            |

| Appendix D. Synchronous Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                            |

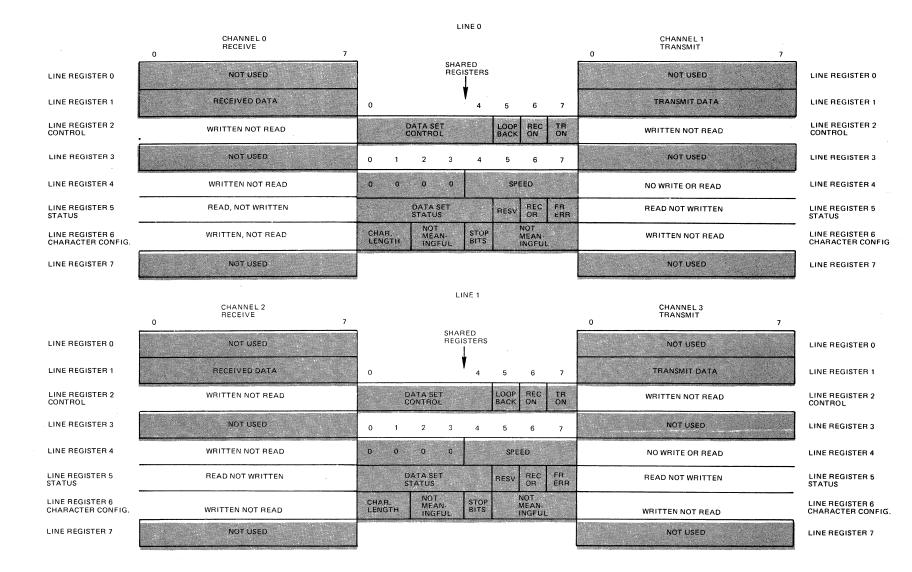

| Communications-Pacs/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D-1                                                                                                                                                        |

| Communications-Pacs/<br>Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

| Communications-Pacs/<br>Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

| Communications-Pacs/<br>Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .D-1                                                                                                                                                       |

| Communications-Pacs/<br>Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .D-1                                                                                                                                                       |

| Communications-Pacs/<br>Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .D-1<br>.D-5                                                                                                                                               |

| Communications-Pacs/<br>Adapters         Line Registers         Line Registers for Receive<br>Channel         Line Registers for Transmit<br>Channel                                                                                                                                                                                                                                                                                                                                                   | .D-1<br>.D-5<br>.D-7                                                                                                                                       |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelChannelProgramming Considerations                                                                                                                                                                                                                                                                                                                                             | .D-1<br>.D-5<br>.D-7<br>.D-9                                                                                                                               |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData Transfers                                                                                                                                                                                                                                                                                                                                      | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9                                                                                                                       |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request Interrupts                                                                                                                                                                                                                                                                                                            | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10                                                                                                              |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed Selection                                                                                                                                                                                                                                                                                             | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10                                                                                                     |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect                                                                                                                                                                                                                                                                               | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10                                                                                            |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" Test                                                                                                                                                                                                                                                               | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11                                                                                   |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit On                                                                                                                                                                                                                                            | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11                                                                          |

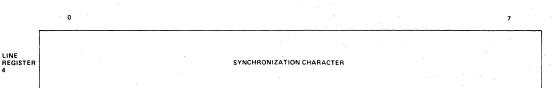

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive Character Synchronization                                                                                                                                                                                                                              | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11                                                                 |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelData Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit OnReceive Character SynchronizationClear to Send                                                                                                                                                        | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12                                                        |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit OnReceive Character SynchronizationClear to SendReceive Overrun                                                                                                                                         | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12                                                       |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive Character SynchronizationClear to SendReceive OverrunTransmit Underrun                                                                                                                                           | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12                                              |

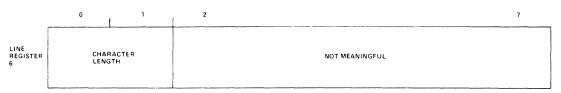

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelData Registers for Transmit<br>Channel Request InterruptsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter Length                                                                                                                                  | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13                                     |

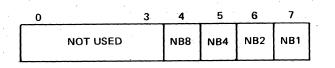

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParity                                                                                                                                                           | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-13                            |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParityData Transfer Clocks                                                                                                 | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-13<br>.D-14                   |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit OnReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParityData Transfer ClocksMaster Clear                                                                  | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-13<br>.D-14<br>.D-14  |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit OnReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParityData Transfer ClocksMaster ClearLine/Channel Number Assignment                                    | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-14<br>.D-14<br>.D-14  |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit OnReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParityData Transfer ClocksMaster Clear                                                                  | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-14<br>.D-14<br>.D-14  |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive/Transmit OnReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParityData Transfer ClocksMaster ClearLine/Channel Number AssignmentDevice Identification Number        | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-14<br>.D-14<br>.D-14  |

| Communications-Pacs/<br>AdaptersLine RegistersLine Registers for Receive<br>ChannelLine Registers for Transmit<br>ChannelLine Registers for Transmit<br>ChannelProgramming ConsiderationsData TransfersChannel Request InterruptsSpeed SelectionDirect Connect"Loop-Back" TestReceive Character SynchronizationClear to SendReceive OverrunTransmit UnderrunCharacter LengthParityData Transfer ClocksMaster ClearLine/Channel Number AssignmentDevice Identification NumberPhysical Interface to Data | .D-1<br>.D-5<br>.D-7<br>.D-9<br>.D-10<br>.D-10<br>.D-10<br>.D-11<br>.D-11<br>.D-11<br>.D-12<br>.D-12<br>.D-12<br>.D-13<br>.D-13<br>.D-14<br>.D-14<br>.D-14 |

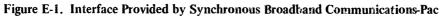

| Appendix E. Synchronous Broadband<br>Communications-Pacs E-1                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line Registers E-1                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Line Registers for Receive                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Line Registers for Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Receive/Transmit ON                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

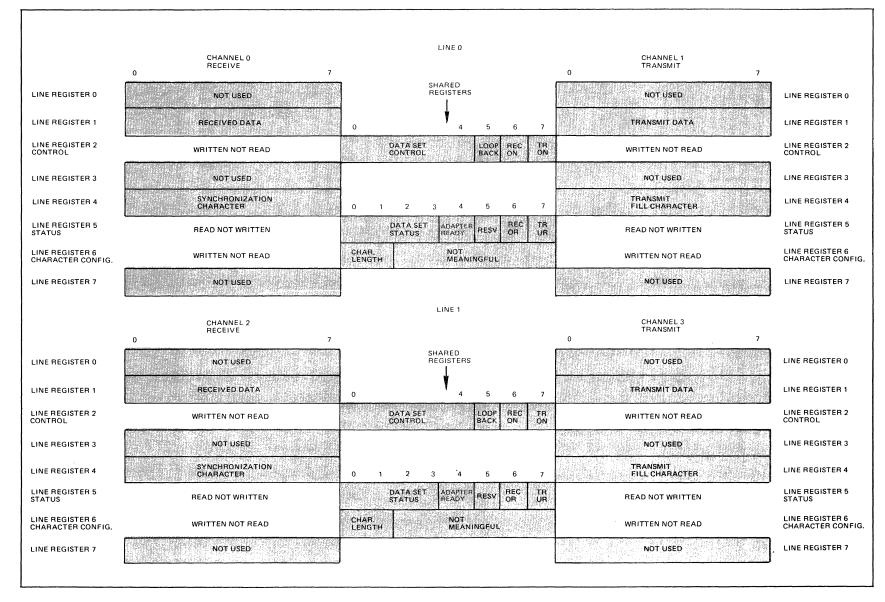

| Programming for Effective Use                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

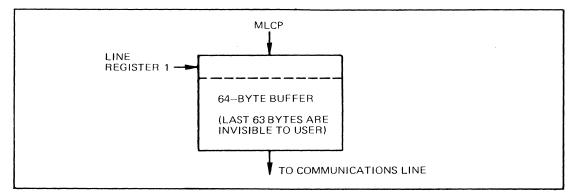

| of the 64-Byte Buffer E-10                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data Transfers: Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Data Transfers: Receive                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Preloading the Transmit BufferE-12                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Direct Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| "Loop-Back" Test E-13                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Receive Character Synchronization E-13                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Clear to Send E-13                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Receive Overrun                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Transmit Underrun E-14                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Character Length E-14                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Parity                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cyclic Redundancy Check                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Data Transfer Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Master Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Line/Channel Number Assignment E-15                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Device Identification Number                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Physical Interface to Data                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Communications Equipment and Data                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Terminal Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Appendix F. DCM9110 Communications-Pac.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Appendix F. DCM9110 Communications-Pac,<br>Automatic Calling                                                                                                                                                                                                                                                                                                                                                                                                         |

| Automatic Calling                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Automatic Calling<br>Feature                                                                                                                                                                                                                                                                                                                                                                                                                                         |

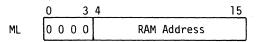

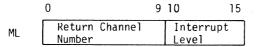

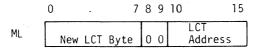

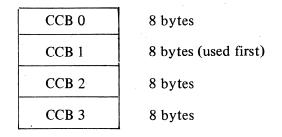

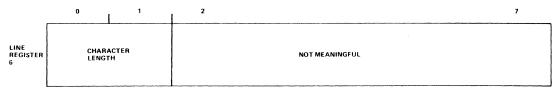

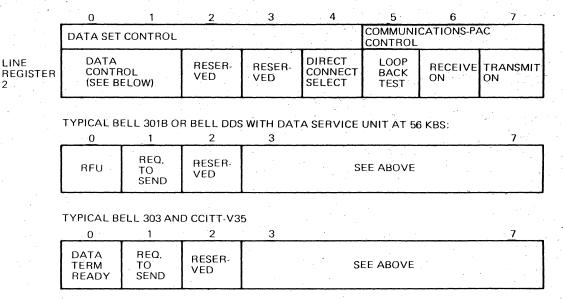

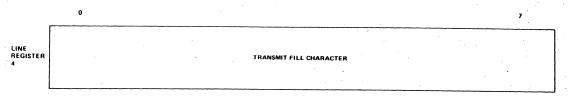

| Automatic Calling<br>FeatureFeatureConfiguration InformationDCM9110 ConfigurationDCM9110 Channel Number<br>AssignmentsAssignmentsSignmentsContinue InterpreterContinue InterpreterAssignmentsF-1Device Identification NumberF-2                                                                                                                                                                                                                                      |