## SERIES 60 (LEVEL 6) COMMUNICATIONS HANDBOOK ADDENDUM B

## SUBJECT

Corrections and Changes to the Handbook, and a New Appendix, Covering the Synchronous Broadband HDLC Communications-Pac

## SPECIAL INSTRUCTIONS

This is the second addendum to Revision 2, dated October 1978. Bars in the margins indicate technical changes and additions; asterisks denote deletions. Appendix H, being entirely new, does not contain change bars or asterisks. Note:

Insert this cover after the manual cover to indicate the updating of the document with Addendum B.

## **ORDER NUMBER**

AT97B, Rev. 2

August 1979

## Honeywell

## **COLLATING INSTRUCTIONS**

Remove

To update this manual, remove old pages and insert new pages as follows:

vii, viii 2-11, blank 3-5 through 3-8 4-13 through 4-16 4-23, 4-24 5-5, 5-6 D-1, D-2

vii through x 2-11, blank 3-5 through 3-8 4-13 through 4-16 4-23, 4-24 5-5, 5-6 D-1, D-2 H-1 through H-65

Insert

Honeywell disclaims the implied warranties of merchantability and fitness for a particular purpose and makes no express warranties except as may be stated in its written agreement with and for its customer.

In no event is Honeywell liable to anyone for any indirect, special or consequential damages. The information and specifications in this document are subject to change without notice.

© Honeywell Information Systems Inc., 1979

8/79 AT97B

**Checking Status Before**

Appendix H.

vii

Each RECV ..... G-20

| Avoiding Possible Race                                    |               |

|-----------------------------------------------------------|---------------|

| Condition During Call Abort<br>Physical Interface to Data | . 1 - 1 1     |

| Communications Equipment and                              |               |

| Data Terminal Equipment                                   | E 12          |

| Data reminai Equipment                                    | ند ۲۰۱ .<br>د |

| Appendix G. DCM9106 Synchronous HDL0                      | -             |

| Communications-Pac                                        |               |

| (Medium-Speed Lines)                                      | G-1           |

| HDLC Frame Structure                                      | G-1           |

| Frame Format                                              | G-2           |

| Flag Sequence                                             | G-2           |

| Address Field                                             | G-2           |

| Control Field                                             | G-2           |

| Information Field                                         | G-3           |

| Frame Check Sequence                                      | G-3           |

| Abort                                                     | G-3           |

| Transparency                                              | G-3           |

| Inter-Frame Time Fill                                     | G-3           |

| Intra-Frame Time Fill                                     | G-3           |

| Receive Idle Link State                                   | G-3           |

| Line Registers                                            | G-3           |

| Line Register 1                                           | G-4           |

| Line Register 1 Output Data                               | G-4           |

| Line Register 1 Input Data                                |               |

| Line Register 2, Output Line                              |               |

| Control                                                   | G-5           |

| Line Register 5, Status                                   |               |

| Line Register 6 Character                                 |               |

| Control                                                   | G-12          |

| Initialization and Startup                                |               |

| General Guidelines                                        | G-15          |

| Master Clear                                              | G-15          |

| Possible Race Condition at                                |               |

| Startup                                                   | G-15          |

| Channel Number Assignment                                 | G-15          |

| Device ID Assignment                                      | G-16          |

| Firmware Revision Level                                   | G-16          |

| Data Transfer Clocks                                      | G-16          |

| Transmit Operations                                       | G-16          |

| Startup and Interframe                                    |               |

| Considerations                                            | G-16          |

| Data Transfer                                             | G-17          |

| Checking Status before                                    |               |

| Each SEND                                                 | G-17          |

| End of Frame                                              | G-17          |

| Byte Size Switching.                                      | G-18          |

| FCS Handling                                              | G-18          |

| Underrun Handling                                         | G-18          |

| Transmit Data Buffering                                   | G-19          |

| Transmitter On/Off Timing                                 | G-19          |

| Receive Operations                                        | G-19          |

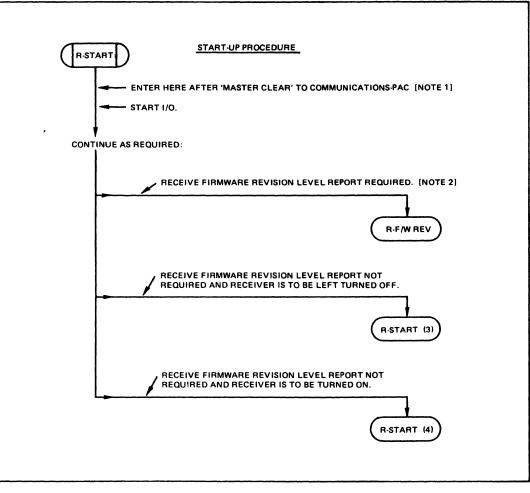

| Startup                                                   | G-19          |

| Between Frames                                            | G-20          |

| Start of Frame                                            | G-20          |

| Data Transfer and Receive                                 |               |

| Overrun                                                   | G-20          |

| End of Frame                                                | G-20   |

|-------------------------------------------------------------|--------|

| Byte Size Switching                                         | .G-21  |

| FCS Handling                                                | G-21   |

| Receiver On/Off Functionality                               |        |

| and Resynchronization                                       | G-22   |

| Data Set Control and Status                                 | G-22   |

| Timing                                                      | G-22   |

| Physical Interface to Data                                  |        |

| Communications Equipment and Data                           |        |

| Terminal Equipment                                          | G-43   |

| ppendix H. Synchronous Broadband HDL                        | С      |

| Communications-Pac                                          | H-1    |

| Introduction                                                | H-1    |

| HDLC Frame Structure                                        | H-1    |

| Flag Sequence                                               | H-3    |

| Address Field                                               | H-3    |

| Control Field.                                              | H-3    |

| Information Field                                           | H-4    |

| Logical Control Field                                       | H-4    |

|                                                             | H-5    |

| Text Field                                                  | H-5    |

| Frame Check Sequence                                        |        |

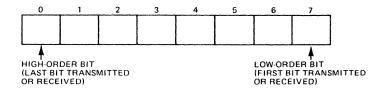

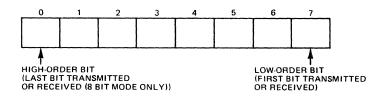

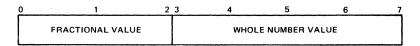

| Order of Bit Transmission                                   | H-5    |

| Abort                                                       | H-5    |

| Transparency.                                               | H-6    |

| Interframe Time Fill                                        | H-6    |

| Intraframe Time Fill                                        | H-6    |

| Idle Link State                                             | H-6    |

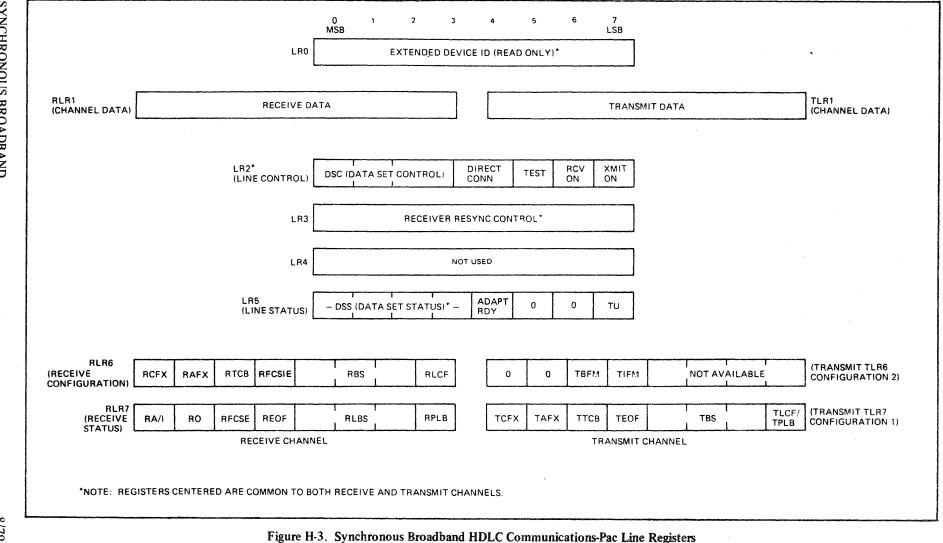

| Line Registers                                              | H-6    |

| Shared Line Registers                                       | H-9    |

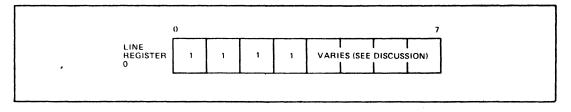

| Line Register Zero-Extended Device                          | 11.0   |

| Identification Number.                                      | H-9    |

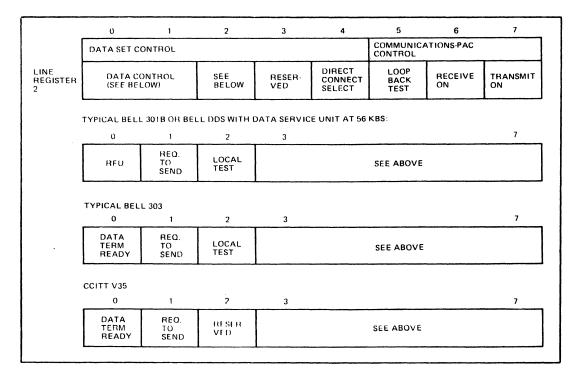

| Line Register 2 - Line Control                              | H-9    |

| Line Register 3 Receive                                     | 11.10  |

| Resynchronization                                           | H-10   |

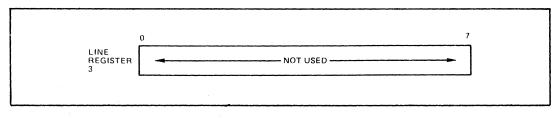

| Line Register 4 Not Used                                    |        |

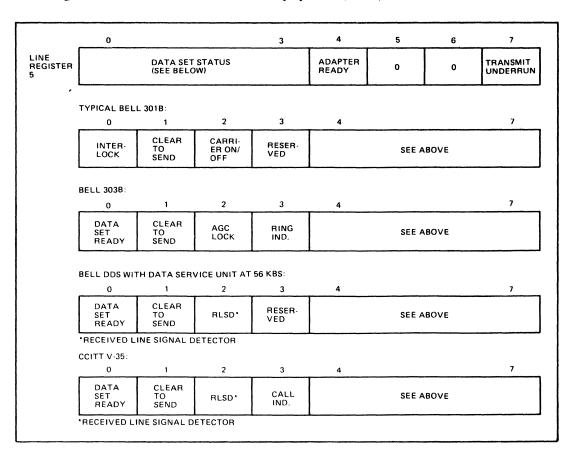

| Line Register 5 – Data Communicati                          | ons    |

| Equipment (DCE) Status.                                     | H-II   |

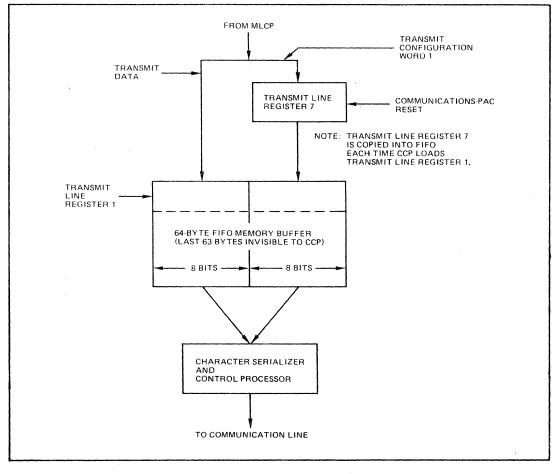

| Transmit Line Registers.                                    | H-12   |

| Transmit Line Register 1 – Output                           |        |

| Data Transmit Channel                                       |        |

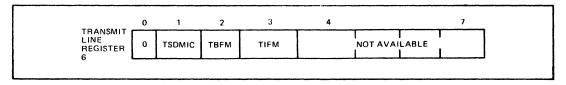

| Transmit Line Register 6 – Transmit                         |        |

| Configuration Word 2                                        | H-13   |

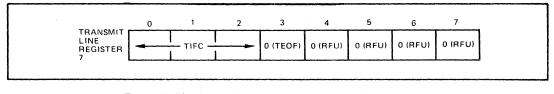

| Transmit Line Register 7 – Transmit<br>Configuration Word 1 | 11 1 4 |

| Interframe Format                                           | H-14   |

| (Format T7-1)                                               | LI 11  |

| Start-of-Frame Format                                       | H-14   |

| (Format T7-2)                                               | H-15   |

| End-of-Frame Format                                         | 11-13  |

| (Format T7-3)                                               | H-16   |

| Initialization Format                                       | 1110   |

| (Format T7-4)                                               | H-17   |

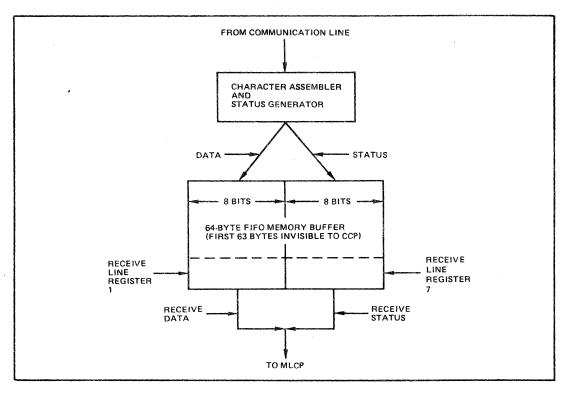

| Receive Line Registers.                                     | H-18   |

|                                                             |        |

| F | ig | U | re | 8 |

|---|----|---|----|---|

|---|----|---|----|---|

.

| Receive Line Register 1 – Input Data       |

|--------------------------------------------|

| Receive Channel                            |

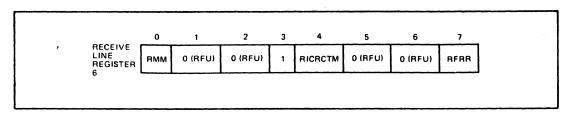

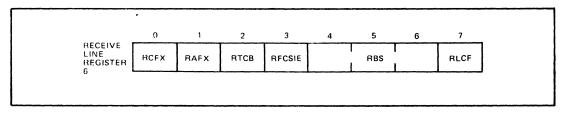

| Receive Line Register 6 – Receive          |

| Configuration H-19                         |

| Initialization Format                      |

| (Format R6-1)                              |

| Frame Format (Format R6-2) H-19            |

| Receive Line Register 7 –                  |

| Receive Status                             |

| Transmit and Receive Data Formats H-22     |

| Address, Control, and Logical              |

| Control Fields H-22                        |

| Text Field                                 |

| Normal (Non-Bit Stream) Mode H-22          |

| Bit Stream Mode                            |

| Byte Size Control                          |

| Transmit Byte Size                         |

| Receive Byte Size                          |

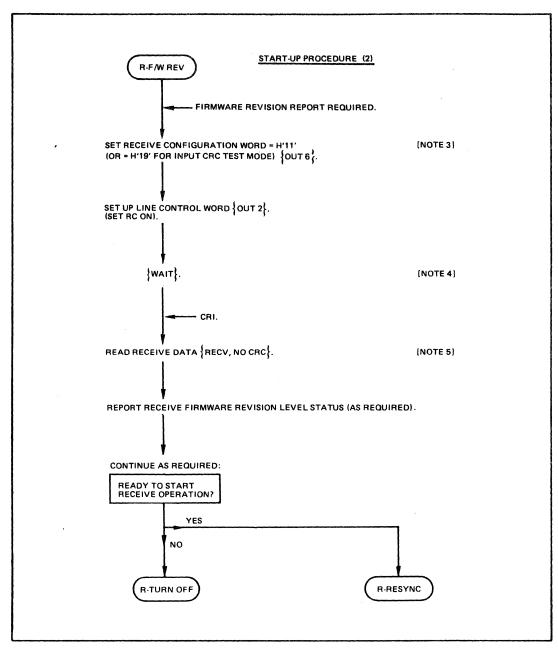

| Initialization and Startup                 |

| General Guidelines                         |

| Master Clear                               |

| Channel Number Assignment H-26             |

|                                            |

| Device ID Assignment                       |

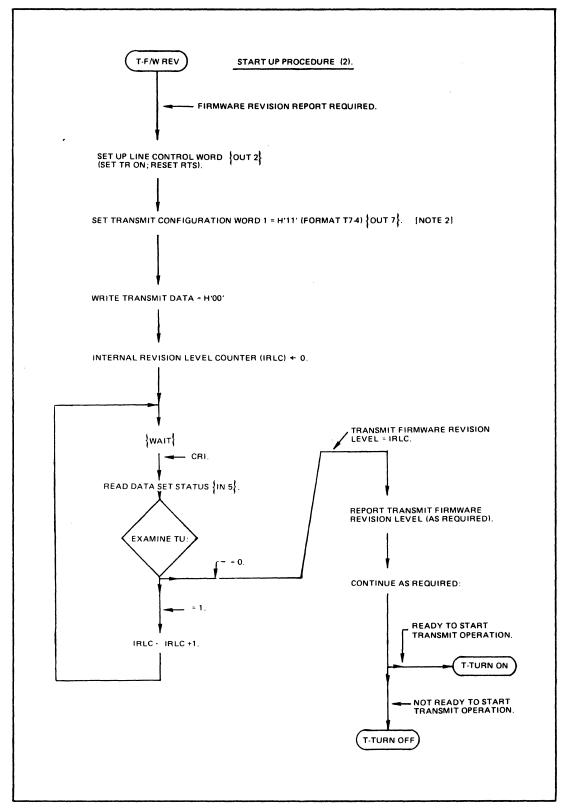

| Firmware Revision Level                    |

| Data Transfer Clocks                       |

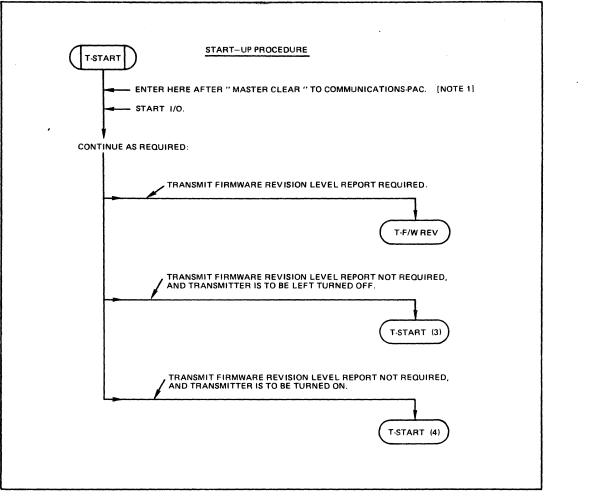

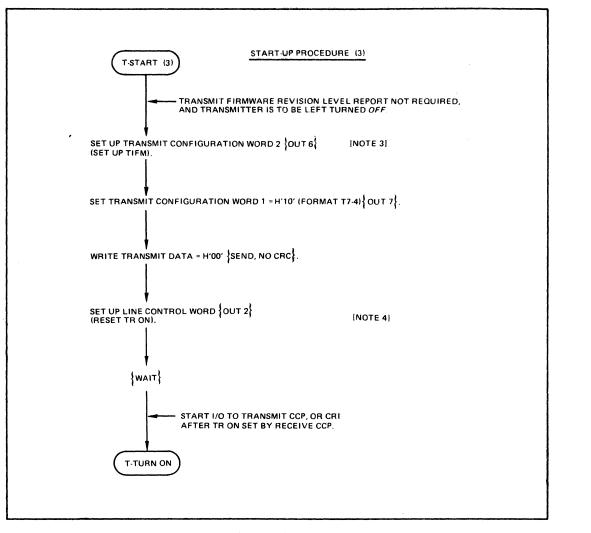

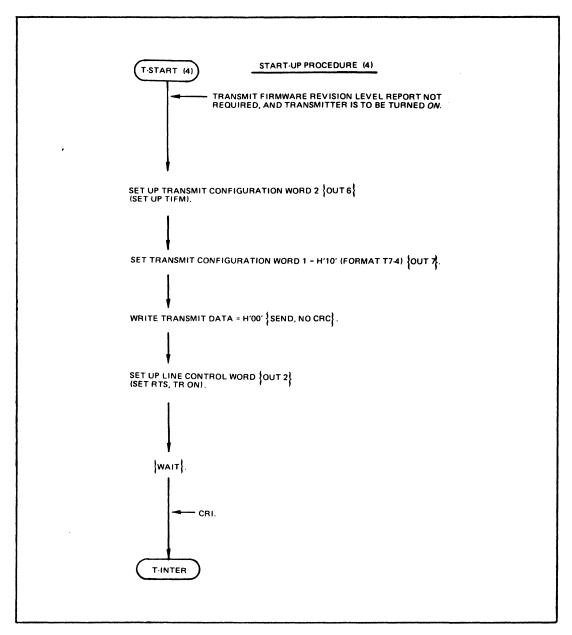

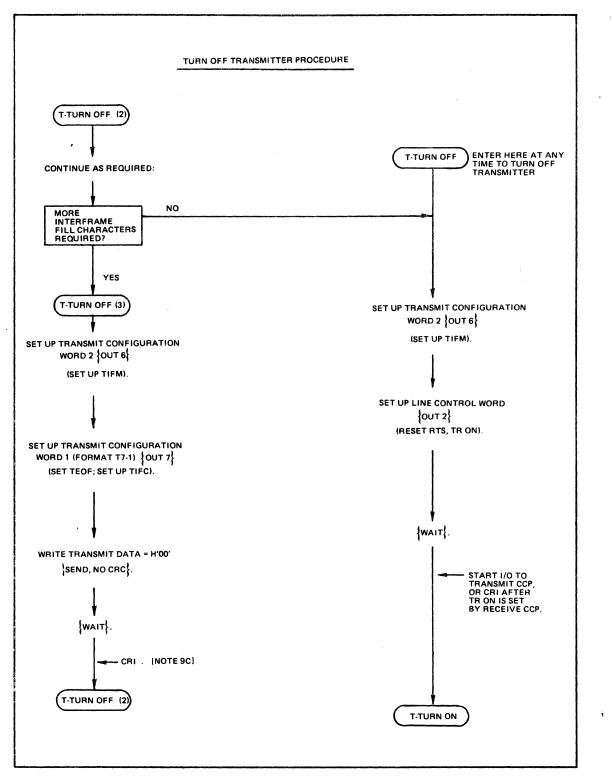

| Transmit Operations                        |

| Startup and Interframe                     |

| Considerations                             |

| Data Transfer During Frame                 |

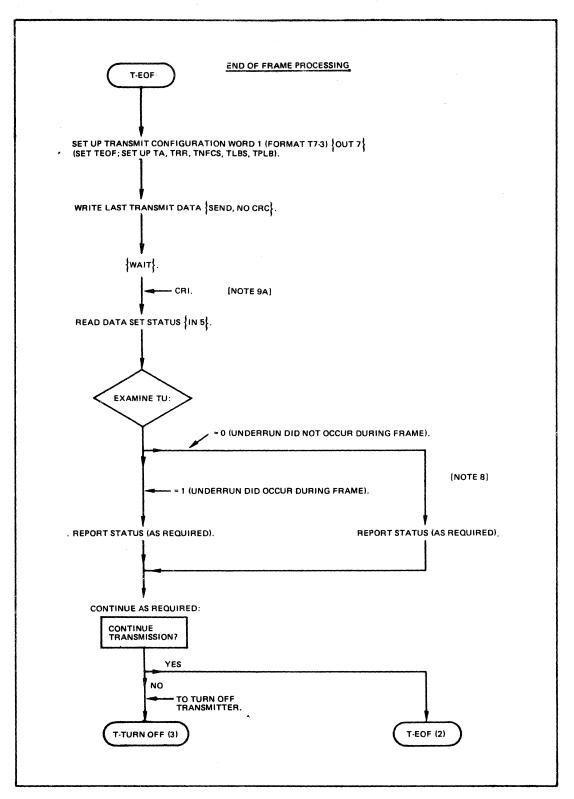

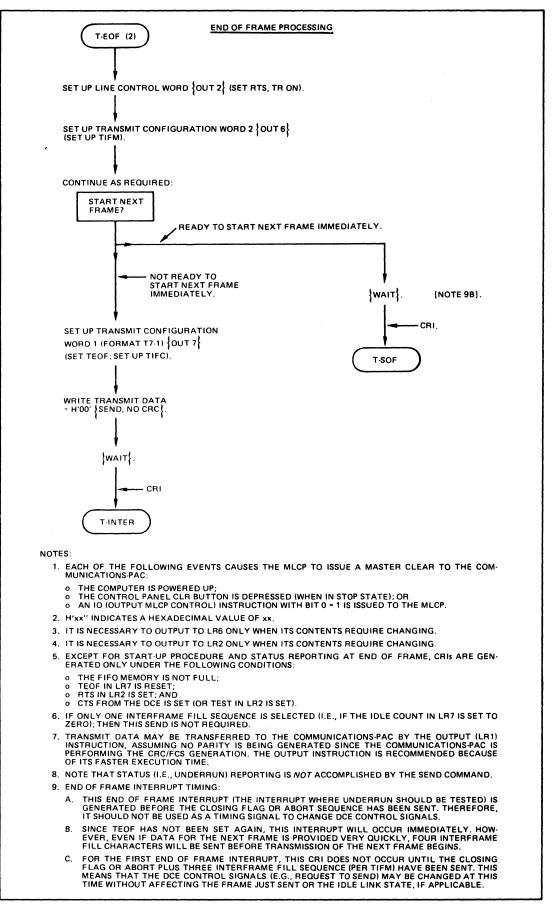

| End of Frame                               |

| Byte Size Switching and FCS Handling. H-29 |

| Underrun Processing                        |

| Preloading the Transmit Buffer to          |

| Prevent Underrun                           |

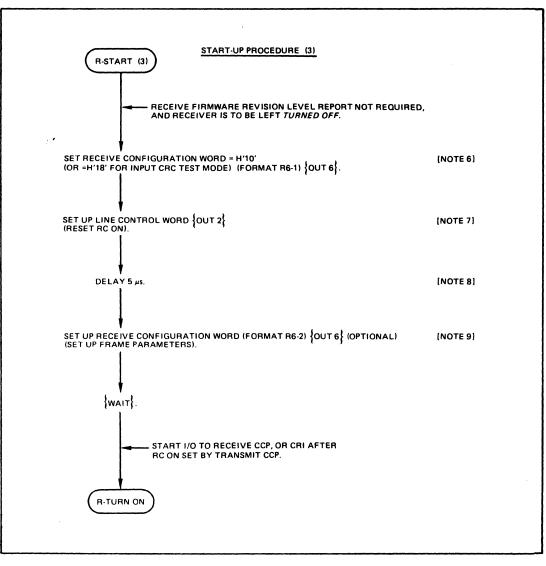

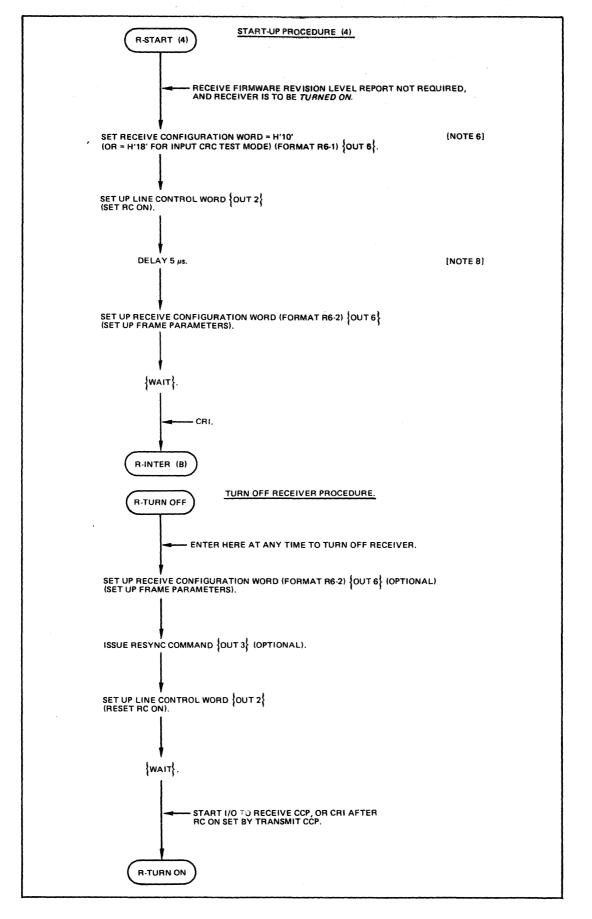

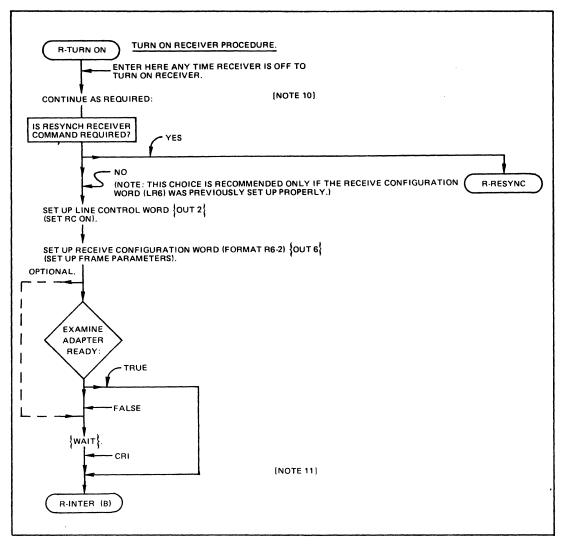

| Receive Operations                         |

| Startup and Interframe                     |

| Considerations                             |

| Data Transfers H-30                        |

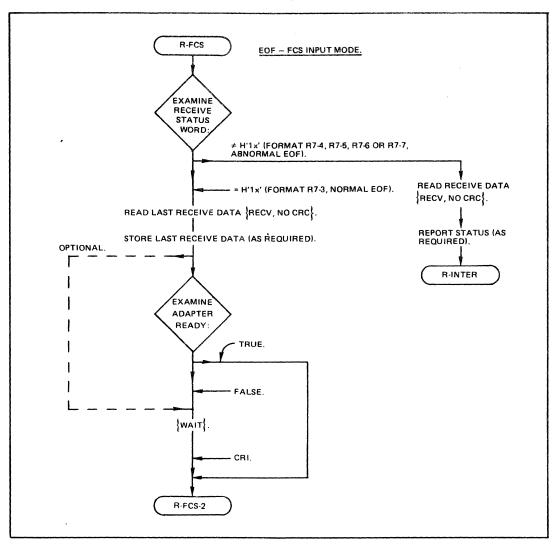

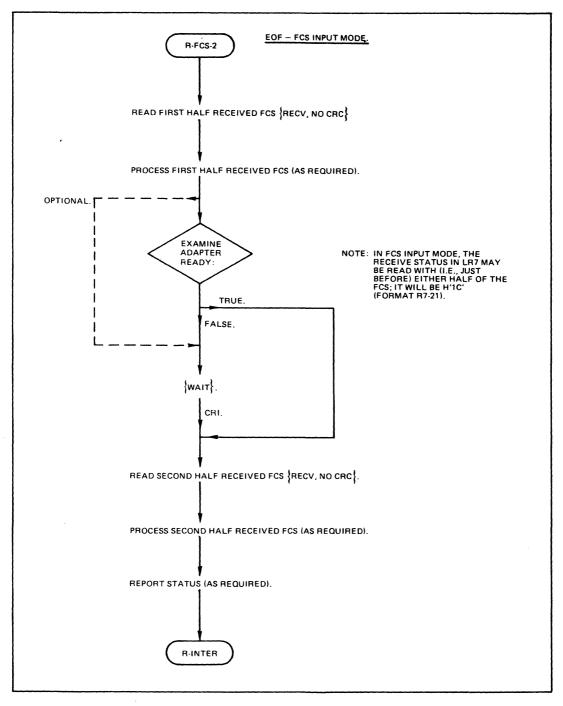

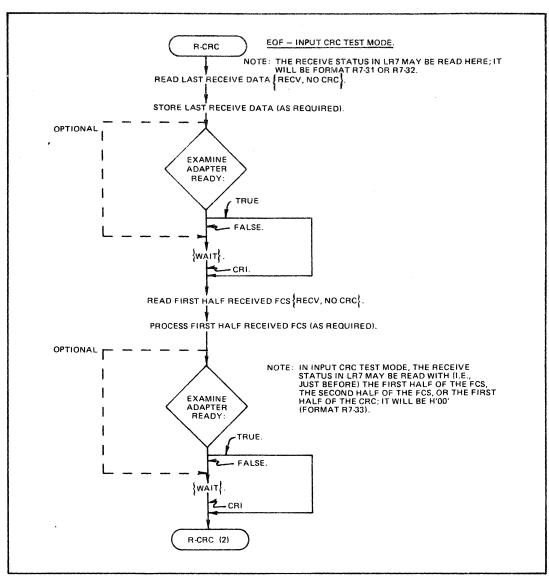

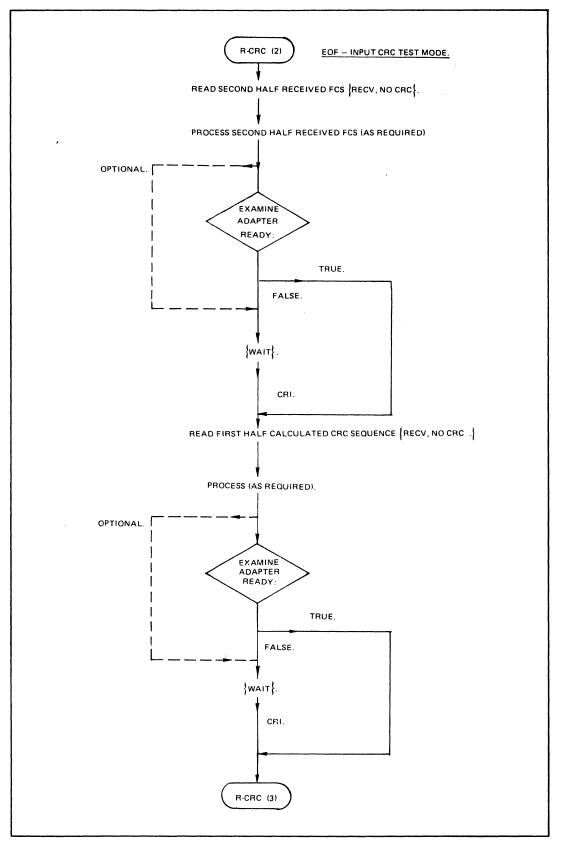

| End of Frame H-30                          |

| Receive Overrun H-31                       |

| Missed Frame Condition H-31                |

| Idle Link State H-31                       |

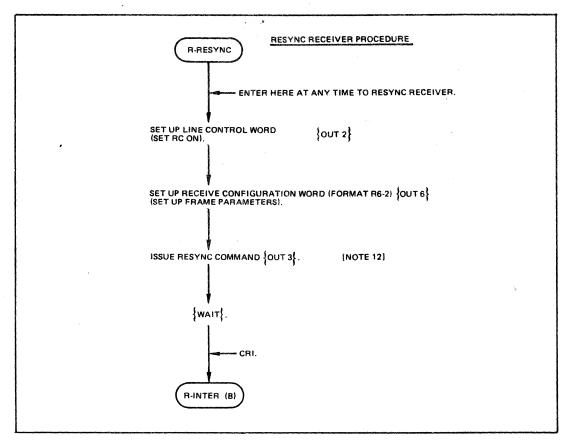

| Receiver Resynchronization Control H-31    |

| Data Set Control and Status H-31           |

| Timing                                     |

| Physical Interface to Data Communications  |

| Equipment and Data Terminal                |

| Equipment H-62                             |

| DCM9112 H-62                               |

| DCM9113 H-63                               |

| DCM9121 H-65                               |

| · · · · · · · · · · · · · · · · · · ·      |

| Fig | ure |

|-----|-----|

|     |     |

| Figure      | Page                                   |

|-------------|----------------------------------------|

| 1-1.        | MLCP Attachment to Megabus 1-2         |

| 1-2.        | DLCP Attachment to Level 6             |

|             | Model 23 Bus 1-3                       |

| 1-3.        | MLCP Memory Map 1-4                    |

| 1-4.        | DLCP Memory Map 1-5                    |

| 1-5.        | Receive                                |

| 1-6.        | Transmit                               |

| 1-7.        | Setting Up the MLCP/DLCP 1-14          |

| 1-8.        | Receiving Data                         |

| 1-9.        | Transmitting Data                      |

| 3-1.        | Format of a CCB for MLCP 3-4           |

| 3-2.        | Format of a CCB for DLCP 3-4           |

| 3-3.        | MLCP CCB Status Bytes 1 and 2 3-7      |

| 3-4.        | DLCP CCB Status Bytes 1 and 2 3-7      |

| 5-1.        | LCT Status Bytes 1 and 2 (MLCP) 5-10   |

| 5-2.        | LCT Status Bytes 1 and 2 (MLCT) 5-11   |

| 5-3.        | LCT Layout                             |

| 7-1.        | Format of CCB for Block Mode Write     |

| /-1.        | (MLCP)                                 |

| 7-2.        | Format of CCB for Block Mode Write     |

| /           | (DLCP)                                 |

| A-1.        | Sample Table Look-Up                   |

| /1-1.       | Program (MLCP Only)A-7                 |

| A-2.        | MLCP LCT Locations                     |

| A-3.        | MLCP LCT Worksheet                     |

| C-1.        | Interface Provided by Asynchronous     |

| <b>、</b> 1. | Line Communications-Pac (MLCP). C-2    |

| C-2.        | Interface Provided by Asynchronous     |

|             | Line Adapter (DLCP)                    |

| C-3.        | Registers of Asynchronous Line         |

|             | Communications-Pac/AdapterC-4          |

| C-4.        | Sample Program for Receive On          |

|             | Asynchronous Line Adapter              |

|             | (MLCP and DLCP)                        |

| D-1.        | Interface Provided by Synchronous Line |

|             | Communications-Pac (MLCP) D-2          |

| D-2.        | Interface Provided by Synchronous Line |

|             | Adapter (DLCP)                         |

| D-3.        | Registers of Synchronous Line          |

|             | Communications-Pac/Adapter D-4         |

| D-4.        | Sample Program Showing Startup         |

|             | Without Causing Underrun Error         |

|             | (MLCP and DLCP)                        |

| E-1.        | Interface Provided by Synchronous      |

|             | Broadband Communications-Pac E-2       |

| E-2.        | Registers of Synchronous               |

|             | Broadband Communications-Pac E-3       |

| E-3.        | Line Register 1 for                    |

|             | Receive Channel E-4                    |

|             |                                        |

## Figure

.

(

Page

| 1 igure   |                                   | Tuge    |

|-----------|-----------------------------------|---------|

| E-4.      | Line Register 2 for               |         |

|           | Receive Channel                   | . E-5   |

| E-5.      | Line Register 4 for               |         |

|           | Receive Channel                   | . E-5   |

| E-6.      | Line Register 5 for               |         |

|           | Receive Channel                   | . E-6   |

| E-7.      | Line Register 6 for               |         |

|           | Receive Channel                   | . E-7   |

| E-8.      | Line Register 1 for               | • • •   |

| • • • • • | Transmit Channel                  | F-7     |

| E-9.      | Line Register 2 for               | • • • / |

| • • • •   | Transmit Channel                  | F-8     |

| E-10.     | Line Register 4 for               |         |

| •/ ••••   | Transmit Channel                  | F-8     |

| E-11.     | Line Register 5 for               | 0       |

| • / • • • | Transmit Channel                  | F-0     |

| E-12.     | Line Register 6 for               | • • • • |

| • • • • • | Transmit Channel                  | F-10    |

| E-13.     | Transmit Loop                     |         |

| E-14.     | Receive Loop                      |         |

| E-15.     | Preloading the Transmit Buffer    | F-17    |

| F-1.      | DCM9110 Environment               |         |

| F-2.      | Line Register 1 Output Data       |         |

| F-3.      | Line Register 1 Input Data        | F-4     |

| F-4.      | Line Register 2 Output Control    | . F-4   |

| F-5.      | Line Register 5                   |         |

|           | Input Status One                  | . F-6   |

| F-6.      | Line Register 7 Input             |         |

|           | Status 2                          | . F-7   |

| F-7.      | Typical Automatic Calling         |         |

|           | Equipment/DCM9110/MLCP            |         |

|           | Timing Sequence                   | . F-8   |

| G-1.      | HDLC Frame                        | G-2     |

| G-2.      | Line Registers                    |         |

| G-3.      | Line Register 1                   |         |

| G-4.      | Line Register 2                   | G-5     |

| G-5.      | Line Register 5                   |         |

| G-6.      | Line Register 6                   | G-12    |

| G-7.      | Transmit Flowchart                | G-24    |

| G-8.      | Receive Flowchart                 | G-34    |

| H-1.      | Interface Provided by Synchronous |         |

|           | Broadband HDLC                    |         |

|           | Communications-Pac.               | H-2     |

| H-2.      | HDLC Frame                        |         |

| H-3.      | Synchronous Broadband HDLC        |         |

|           | Communications-Pac                |         |

|           | Line Registers                    | H-8     |

| H-4.      | Line Register Zero                | H-9     |

| H-5.      | Line Register 2                   |         |

| H-6.      | Line Register 3                   | H-10    |

| H-7.      | Line Register 5                   | H-11    |

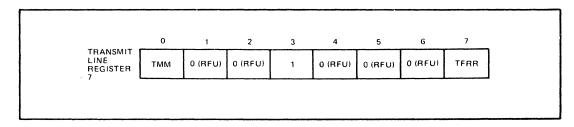

| H-8.      | Transmit Line Registers 1 and 7   |         |

|           | and FIFO Memory                   | H-12    |

| H-9.      | Transmit Line Register 6,         |         |

| ** / •    | Transmit Ente Register 0,         |         |

## Figure

| Figure |                                                    | Page         |

|--------|----------------------------------------------------|--------------|

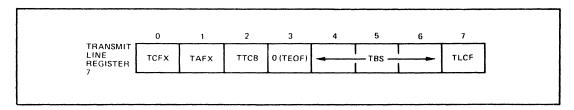

| H-10.  | Transmit Line Register 7,<br>Interframe Format     | H-14         |

| H-11.  | Transmit Line Register 7,<br>Start-of-Frame Format | H-15         |

| H-12.  | Transmit Line Register 7,<br>End-of-Frame Format   | H-16         |

| H-13.  | Transmit Line Register 7,<br>Initialization Format |              |

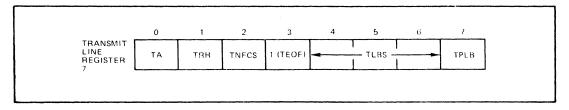

| H-14.  | Receive Line Registers 1 and 7<br>and FIFO Memory  |              |

| H-15.  | Receive Line Register 6,<br>Initialization Format  |              |

| H-16.  | Receive Line Register 6,<br>Frame Format           |              |

| H-17.  | Receive Line Register 7,                           |              |

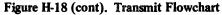

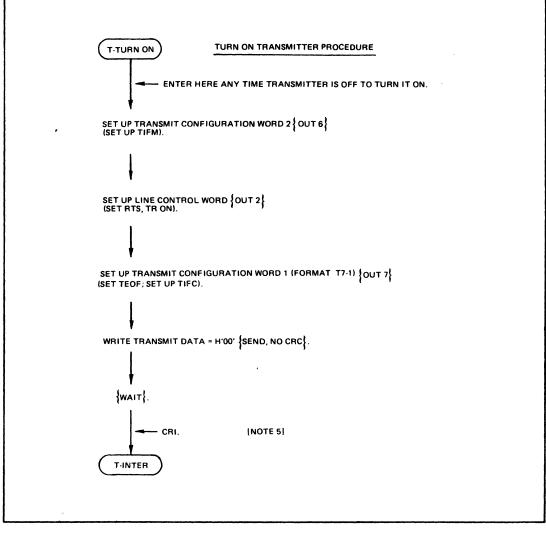

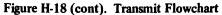

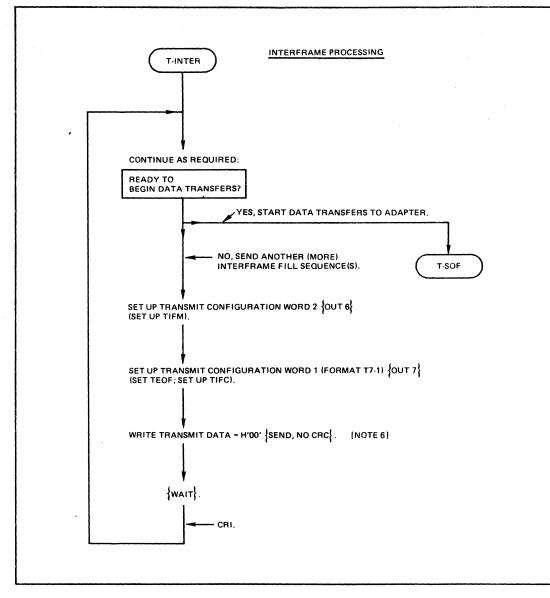

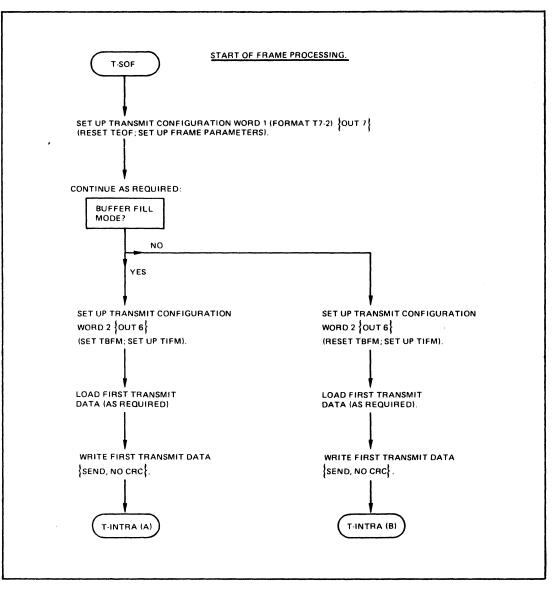

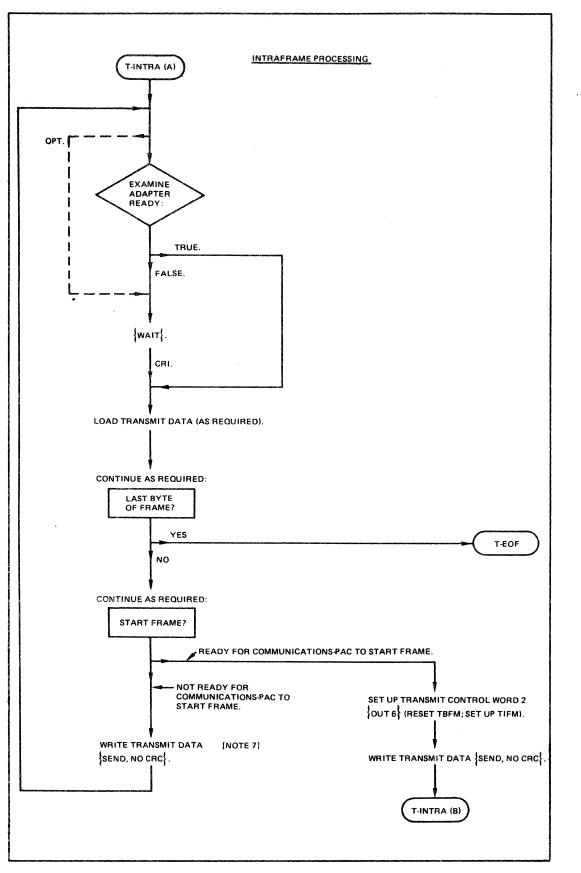

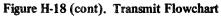

| H-18.  | Receive Status<br>Transmit Flowchart               | H-21<br>H-34 |

| H-19.  | Transmit Loop                                      | H-46         |

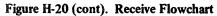

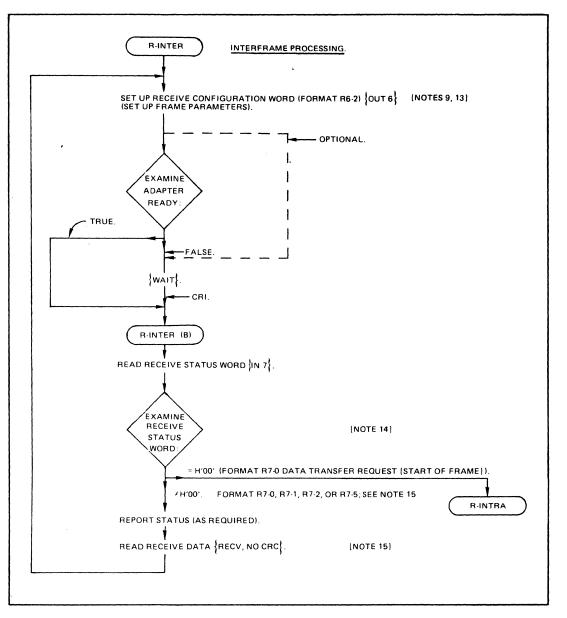

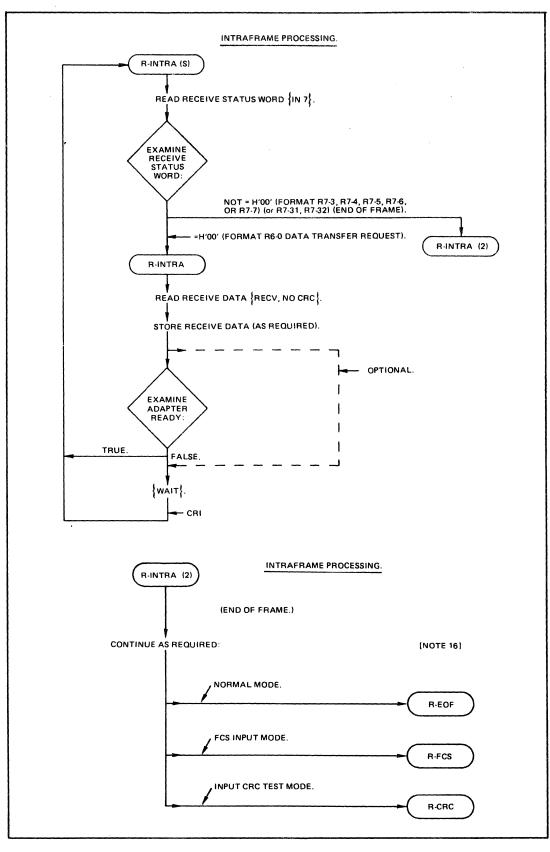

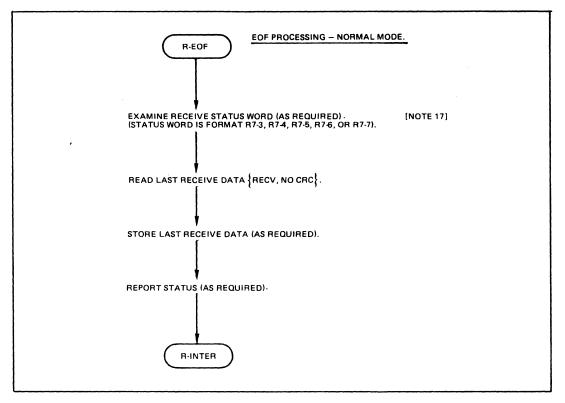

| H-20.  | Receive Flowchart.                                 | H-47         |

| H-21.  | Receive Loop                                       | H-61         |

## **Tables**

Page

## Table

| 1-1. | Hardware Summary                      |

|------|---------------------------------------|

| 1-2. | Priorities for Servicing Adapter      |

|      | Channel Request Interrupts            |

|      | DLCP 1-10                             |

| 1-3. | Priorities for Serving                |

|      | Communications-Pac Channel            |

|      | Request Interrupts MLCP 1-11          |

| 2-1. | Summary of Main Memory Program        |

|      | Input/Output Instructions             |

|      | Related to Processor                  |

| 3-1. | CCB Completion Conditions 3-11        |

| 4-1. | Format of Macro Calls for CCP         |

|      | Generation Control Statements 4-5     |

| 4-2. | CCP Executable Instructions 4-8       |

| 4.3. | Format of Macro Calls for CCP         |

|      | Executable Instructions               |

| 4.4. | Timings for Branch Instructions 4-11  |

| 4-5. | Timings for Double Operand            |

|      | Instructions 4-11                     |

| 4-6. | Timings for Input/Output              |

|      | Instructions 4-12                     |

| 4-7. | Timings for Send/Receive              |

|      | Instructions                          |

| 4-8. | Timings for Generic Instructions 4-13 |

| 4-9. | MLCP Bit Map of CCP Executable        |

|      | Instructions' Op Code Words           |

|      | Receive Mode                          |

|      |                                       |

| Table | Page                                                          |

|-------|---------------------------------------------------------------|

| 4-10. | MLCP Bit Map of CCP Executable<br>Instructions' Op Code Words |

|       | Transmit Mode                                                 |

| 5-1.  | Summary of Line Control                                       |

|       | Table Bytes                                                   |

| 6-1.  | MLCP Channel Number Addressing 6-2                            |

| 6-2.  | DLCP Channel Number Addressing 6-2                            |

| 6-3.  | Cyclic Redundancy Check                                       |

|       | Information 6-5                                               |

| 6-4.  | Data Transfer Related to Adapter                              |

| _     | Type and Operation Mode 6-7                                   |

| 6-5.  | Possible Settings for MLCP's                                  |

|       | Fixed-Rate Clock 6-7                                          |

| 7-1.  | Format of Load Control Block 7-3                              |

| B-1.  | Communications-Pac                                            |

|       | Attachable to MLCP B-1                                        |

| B-2.  | DLCP Adapters B-2                                             |

| C-1.  | Configuration Speeds for                                      |

|       | Asynchronous Line                                             |

|       | Communications-Pac/Adapter C-6                                |

| C-2.  | Physical Interface of                                         |

|       | Asynchronous Line                                             |

|       | Communications-Pac/Adapter C-15                               |

| D-1.  | Physical Interface of                                         |

|       | Synchronous Line                                              |

|       | Communications-Pac/Adapter D-15                               |

| E-1.  | Bell 301, 303                                                 |

|       | Compatible Interface E-16                                     |

| E-2.  | CCITT-V35 Interface                                           |

|       | (Including Bell DDS                                           |

|       | at 56 KB\$) E-17                                              |

| F-1.  | Digital Signal Character Set F-4                              |

| F-2.  | Automatic Calling Equipment/                                  |

|       | DCM9110 Interface Signals F-12                                |

х

.

| G-1.  | Line Register 5 Transmit Status   | G-8    |

|-------|-----------------------------------|--------|

| G-2.  | Line Register 5 Receive Status,   |        |

|       | Between Frames and At Start and   |        |

|       | Middle of Frame                   | G-9    |

| G-3.  | Line Register 5 Receive Status,   |        |

|       | Error Frame                       | G-9    |

| G-4.  | Line Register 5 Receive Status,   |        |

|       | Normal Frame                      | G-10   |

| G-5.  | Line Register 5 Receive Status,   |        |

|       | Partial Byte                      | G-11   |

| G-6.  | Transmit Line Register 6          | 011    |

|       | Transmit Control                  | G-13   |

| G-7.  | Receive Line Register 6           | () 1./ |

|       | Receive Control                   | G-14   |

| G-8.  | Key to Flowcharts                 | () 11  |

|       | (Figures G-7 and G-8)             | G-23   |

| G-9.  | Physical Interface of Synchronous |        |

|       | HDLC Communications-Pac           | G-43   |

| H-1.  | Text Control Byte                 |        |

| H-2.  | Text Field Byte Size              | H-24   |

| H-3.  | TBS Encoding                      |        |

| H-4.  | TLBS Encoding.                    |        |

| H-5.  | TCB Encoding.                     |        |

| H-6.  | Key to Abbreviations and          |        |

| 11-0. | Configuration Formats Used in     |        |

|       | Text and Flowcharts               | H_37   |

| H-7.  | Bell 301, 303-Compatible          | 11-52  |

| 11-/. | Interface                         | H.62   |

| H-8.  | CCITT-V35 Interface (Including    | 11-02  |

| 11-0. | Bell DDS At 56 KBS)               | Н 64   |

| шо    |                                   |        |

| H-9.  | MIL188-C Interface (DCM9121)      | п-өэ   |

8/79 AT97B

## **IO (Output MLCP/DLCP Control) Instruction**

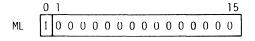

This instruction (function code: 01) transfers, from ML, a control word to the Processor. All Processor channels are affected by this control word. Any channel can be specified in CF, provided that channel is serviced by an adapter.

The format of ML is shown below.

If I is set to 1, MLCP initialization will be performed; otherwise, no action is taken. DLCP initialization will occur unconditionally (i.e., the value of I may be 1 or 0). Initialization comprises the following actions:

- o The Processor executes its basic logic test.

- o Each line register 2 of each adapter is reset to zero; channel request interrupts are thus inhibited.

- o All of RAM is reset to zero.

- o LCT byte 1 of channel 0 contains the hexadecimal number of the firmware revision.

- o All channels are initialized. (This operation is described under the "IO (Output Channel Control) Instruction," earlier in this section.)

- o The Processor is placed in a quiescent state; no interrupts or data transfers can occur.

- o Clears the adapters.

#### Soft Initialize

The pressing of the Clear (CLR) push button on the central processor control panel causes the Processor to perform a "soft initialize" which does the following:

- o Clears the adapters.

- o Clears LCT bytes 8, 9, 40 and 41 of each channel.

- o Clears the Processor internal registers.

The soft initialize differs from the hard initialize caused by the command Output Processor Control (code: 01) in that the hard initialize, in addition to performing the soft initialize functions defined above, also clears the RAM (software-visible).

When in a software debug mode, it is preferable that the RAM not be cleared so that meaningful dumps can be taken to indicate the Processor condition. ł

\*

The contents of the address field are increased as data characters are physically transferred between the CDB and the MLCP based on the CCP's execution of format 1 LD (Load) or ST (Store) instructions.

The address field value is increased by l each time execution of a format 1 LD (Load) or ST (Store) instruction causes *one* data character to be physically transferred between the CDB and the MLCP. This case applies only upon execution of the first (or last) LD or ST instruction pertaining to a CDB that begins (or ends) at an odd byte boundary.

The address field value is increased by 2 each time execution of a format 1 LD (Load) or ST (Store) instruction causes *two* data characters to be physically transferred between the CDB and the MLCP. This case applies upon execution of the *first* of two LD instructions or upon execution of the *second* of two ST instructions. (Execution of the *second* LD instruction or of the *first* ST instruction does not cause a physical data transfer between the CDB and the MLCP; hence the address field value is not increased as either of these instructions is executed.)

## DLCP

The *address* field occupies bytes 0, 1, and 2 of the CCB. This field is written from the main memory program by an IOLD (Output CCB Address and Range) instruction. When first written, the address field contains the starting *word* address of a CDB in the main memory program; the low-order end of the starting byte address is contained in byte 1 of the CCB. Bits 6 and 7 of byte 2 contain the two most significant bits (refer to Figure 3-2) of the address with bit 6 the high-order bit.

The address field value is increased by one every *second* time a format 1 LD or ST instruction is issued, which action causes a word to be physically transferred between a CDB and the DLCP.

NOTE: The format 1 LD or ST is a byte transfer and therefore two uses are required to transfer a word.

An exception to this occurs at an odd byte boundary, in which instance the address field value is increased by one when the *first* format 1 LD or ST causes the first *byte* to be physically transferred between a CDB and the DLCP. (An odd byte boundary would normally occur only on the very first format 1 LD or ST.)

#### **CCB** Range Field

The *range* field occupies bytes 3 and 4 of the CCB. This field is written from the main memory program by an IOLD (Output CCB Address and Range) instruction. When first written, the range field indicates the number of bytes in the CDB. The low-order end of the range value is contained in byte 3 of the CCB for the MLCP and in byte 4 for the DLCP.

The contents of the range field are decreased by 1 each time a format 1 LD (Load) or ST (Store) instruction is executed in the CCP (regardless of whether that instruction causes a physical data transfer between the CDB and the Processor).

## **CCB** Control Field

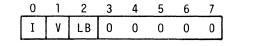

The *control* field occupies byte 5 of the CCB. The control field is written from the main memory program by an IO (Output CCB Control) instruction. The format and significance of this field are shown below.

I – Interrupt V – Valid LB – Last Block

## Bit 0 – interrupt control

- 0 No action.

- 1 Interrupt the main memory program when this CCB is marked as completed (CCB byte 7, bit 3 for MLCP; CCB byte 6 bit 3 for DLCP). The interrupt will occur at the interrupt level assigned to this channel. If no interrupt level has been assigned, no interrupt will occur.

- Bit 1 "valid" CCB

- 0 This is not a "valid" CCB; it cannot be used as an "active" CCB. This condition exists before this bit is set to 1 by an IO (Output CCB Control) instruction. This bit is reset to 0 by firmware when this CCB is marked as completed (bit 3 of CCB byte 7 (MLCP), byte 6 (DLCP) after it has been used during processing of a CDB.

- 1 --- This is a "valid" CCB; it is usable as an "active" CCB. This bit must be set to 1 complete setup of the CCB.

- Bit 2 last CDB

- 0 No action.

- 1 This CCB pertains to the last CDB in a message. This is a flag that can be used by the CCP for special processing of the last CDB in a message. If this bit is set to 1, the Processor's LB-indicator will be set to 1 when this CCB is "active." The CCP can test the LB-indicator by means of BLBT (Branch if Last Block True) and BLBF (Branch if Last Block False) instructions.

### **CCB Status Field**

The *status* field comprises bytes 6 and 7 of the CCB. The CCB status field is reset to zero as setup of the CCB is completed by execution of an IO (Output CCB Control) instruction. Later, as processing ends relative to a CCB, its status field is updated by firmware and the CCB status complete bit (CCB byte 7, bit 3 for MLCP and byte 6, bit 3 for DLCP) is set to 1. (Table 3-1 indicates the conditions under which processing relative to a CCB can end.)

The CCB status field is updated with information from the two LCT status bytes combined with other information. The LCT status bytes are bytes 16 and 17 for a receive channel and bytes 48 and 49 for a transmit channel. Once the status field of the CCB has been updated, the CCB's status is said to be "meaningful."

The status bytes of the "status" CCB can be read from the main memory program, whenever appropriate, by an IO (Input CCB Status) instruction. An IO (Input Next CCB Status) instruction moves the "status" CCB pointer to the following CCB (which then becomes the "status" CCB) and reads the status field of this new "status" CCB.

The format of the two bytes of CCB status field is shown on the following page. The entire word is passed from the LCT status bytes. Note that, in the CCB status field, status byte 1 is stored *above* status byte 2; this order is the opposite of the order of the status bytes in the LCT.

Status Byte 1

(CCB Byte 7, MLCP) (CCB Byte 6, DLCP)

Bit 0 interrupt main memory program from CCP

- 0 No action.

- 1 The main memory program has been interrupted due to execution of an INTR instruction in the CCP.

|                                | . 0                                                | 1                                                  | 2                                                                               | 3                                                      | 4                            | 5                            | 6                          | 7                              |

|--------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|------------------------------|----------------------------|--------------------------------|

| BYTE 6<br>CCB STATUS<br>BYTE 2 | RESERVED                                           | DATA<br>CHECK<br>ERROR                             | RECEIVE<br>NONZERO<br>RESIDUAL<br>RANGE<br>TRANSMIT<br>LAST BLOCK<br>(SEE NOTE) | DATA SET OR<br>COMMUNICA<br>TIONS-PAC<br>STATUS CHANGE | CORRECTED<br>MEMORY<br>ERROR | INVALID<br>MEMORY<br>ADDRESS | MEGABUS<br>PARITY<br>ERROR | UNCORRECTED<br>MEMORY<br>ERROR |

| BYTE 7<br>CCB STATUS<br>BYTE 1 | INTERRUPT<br>MAIN<br>MEMORY<br>PROGRAM<br>FROM CCP | INTERRUPT<br>MAIN<br>MEMORY<br>PROGRAM<br>FROM CCB | DATA<br>SERVICE<br>ERROR                                                        | CCB<br>STATUS<br>COMPLETE                              | CCB<br>SERVICE<br>ERROR      | FOR<br>PROGRAMMING<br>USE    | FOR<br>PROGRAMMING<br>USE  | RESERVED                       |

NOTE: For transmit, bit 2 equals last CCB block.

Figure 3-3. MLCP CCB Status Bytes 1 and 2

|                                | 0                                                  | 1                                                  | 2                                                                 | 3                                                             | 4.                      | 5                         | 6                         | • 7                                                             |

|--------------------------------|----------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|-------------------------|---------------------------|---------------------------|-----------------------------------------------------------------|

| BYTE 6<br>CCB STATUS<br>BYTE 1 | INTERRUPT<br>MAIN<br>MEMORY<br>PROGRAM<br>FROM CCP | INTERRUPT<br>MAIN<br>MEMORY<br>PROGRAM<br>FROM CCP | DATA<br>SERVICE<br>FRROR                                          | CCB<br>STATUS<br>COMPLETE                                     | CCB<br>SERVICE<br>ERROR | FOR<br>PROGRAMMING<br>USE | FOR<br>PROGRAMMING<br>USE | RESERVED                                                        |

| BYTE 7<br>CCB STATUS<br>BYTE 2 | RESERVED                                           | DATA<br>CHECK<br>ERROR                             | RECEIVE<br>NONZERO<br>RESIDUAL<br>RANGE<br>TRANSMIT<br>LAST BLOCK | DATA SET<br>OR COM-<br>MUNICATIONS<br>PAC<br>STATUS<br>CHANGE | RESERVED                | RESERVED                  | RESERVED                  | UNCORRECTED<br>MEMORY<br>ERROR OR<br>INVALID<br>MEMORY<br>ERROR |

NOTE: FOR TRANSMIT, BIT 2 EQUALS LAST CCB BLOCK.

## Figure 3-4. DLCP CCB Status Bytes 1 and 2

- Bit 1 interrupt main memory program

- 0 No action.

- 1 The main memory program has been interrupted when processing ends relative to this CCB. This bit is set to 1 in either of two cases: (1) if bit 0 of CCB byte 5 has been set to 1 by an IO (Output CCB Control) instruction in the main memory program or (2) if bits 0 and 2 of LCT byte 8/40 have been set to 1 and a data set or adapter status change has been recorded in LCT byte 14/46 (Data Set Scan).

- Bit 2 data service error

- 0 No data service error has occurred.

- 1 A data "timing window" has been missed. On receive, the adapter has detected a receive overrun (see bit 6 of LCT byte 14/46 in Section 5). On transmit, the adapter has detected a transmit underrun (see bit 7 of LCT byte 14/46 in Section 5).

- Bit 3 CCB status complete

This bit is always set to 1 as the CCB status field is written by Processor firmware. This setting indicates that processing relative to this CCB has ended and the contents of its status field are meaningful. Table 3-1 indicates the conditions under which processing relative to a CCB can end.

- Bit 4 CCB service error

- 0 No CCB service error has occurred.

- 1 This bit setting pertains to an error that occurred before this CCB became "valid."

COMMUNICATIONS CONTROL BLOCKS On receive, a format 1 ST (Store) instruction was attempted when there was no "valid" CCB. The instruction was not executed; instead, Processor firmware set this bit to 1 (in LCT status byte 1) and proceeded to the next sequential instruction in the CCP.

On transmit, a format 1 LD (Load) instruction was attempted when there was no "valid" CCB. The instruction was not executed; instead, Processor firmware set this bit to 1 (in LCT status byte 1), returned the CCP pointer to the address of this LD instruction, and executed a WAIT (Wait) instruction. At the next channel request interrupt for this channel, this instruction was attempted again.

See the description of bit 4 of LCT byte 16/48 in Section 5.

Bits 5 and 6 - for programming use

Within LCT status byte 1, these two bits can be used by the CCP for applicationspecific purposes. Later, when the contents of the LCT status bytes are transferred to the CCB status field, these two bit positions become available for scrutiny by the main memory program as it issues an IO (Input CCB Status) or IO (Input Next CCB Status) instruction. Thus, these two bit positions can be used as a means for the CCP to pass application-specific status information to the main memory program.

#### Status Byte 2

(CCB Byte 6, MLCP) (CCB Byte 7, DLCP)

- Bit 1 data check error

- 0 No data check error has occurred.

- 1 A data parity error has been detected by firmware, or the CCP has set this bit after detecting a cyclic redundancy check error. (In both cases, this bit setting is relevant only to receive operations.)

- Bit 2 CCB nonzero range residue for receive only (see "NOTE" on previous page 'under diagram)

- 0 No CCB range residue exists.

- 1 The CCB has been terminated before its range field value decreased to 0.

- Bit 2 last block for transmit only

- 0 Not last block

- 1 Last block

- Bit 3 data set or adapter status change

- 0 No data set or adapter status change has been recorded.

- 1 Bits 0 and 1 of LCT byte 8/40 were set to 1 and a data set or adapter status change was recorded in LCT byte 14/46.

- Bit 4 corrected memory error (MLCP only; bit not used in DLCP)

- 0 No corrected memory error has occurred.

- 1 One or more hardware-corrected memory errors occurred in the CDB related to this CCB.

- Bit 5 invalid memory address (MLCP only; bit not used in DLCP)

- 0 No invalid memory address has occurred.

- 1 A reference to a CDB has resulted in an invalid memory address on the Megabus; main memory has issued a NAK. This condition has caused the CCB to be terminated.

- Bit 6 Megabus parity error (MLCP only; bit not used in DLCP)

- 0 No Megabus parity error has occurred.

- 1 Incorrect parity existed on the Megabus as a data character was transferred to the MLCP. This condition has caused the CCB to be terminated.

| Instruction | MLCP<br>(μs)  | DLCP<br>(µs)  |  |  |

|-------------|---------------|---------------|--|--|

| NOP         | 1.7           | 2             |  |  |

| WAIT        | 15.0 (Note 1) | 41.0 (Note 3) |  |  |

| GNB         | n (Note 2)    | n (Note 4)    |  |  |

| SFS         | 5.6           | 21-71         |  |  |

| ССН         | 8.4           | Note 5        |  |  |

| DEC         | 2.0           | 2             |  |  |

| RET         | 4.9           | 8             |  |  |

| SR          | 2.4           | 2             |  |  |

| INTR        | 11.0          | 125-154       |  |  |

| INZ'        | 200.00        | 650           |  |  |

## **TABLE 4-8. TIMINGS FOR GENERIC INSTRUCTIONS**

### NOTES: 1. (MLCP)

This figure includes the time necessary to perform a context swap from the currently running CCP to the next CCP (approximately 8  $\mu$ s).

## 2. (MLCP)

GNB-receive mode and previously active CCB causes interrupt to central processor: 32.2  $\mu s$

GNB-receive mode without interrupt: 25.2  $\mu$ s

GNB-transmit mode with interrupt:  $28.8 \ \mu s$

GNB-transmit mode without interrupt: 21.8  $\mu$ s

3. (DLCP)

養養

This figure includes the time only to suspend the currently executing CCP.

### 4. (DLCP)

GNB-receive mode and previously active CCB causes interrupt to central processor: 239  $\mu s$

GNB-receive mode without interrupt:  $120 \ \mu s$ GNB-transmit mode with interrupt:  $314 \ \mu s$ GNB-transmit mode without interrupt:  $195 \ \mu s$

## 5. (DLCP)

Timings for CCH are as follows: 49 µs for LRC 73 µs for CRC 16 73 µs for CRC ITT 82 µs for CRC 12

|                                                 | Bits<br>0-3     |                                                  | В                          | its 4-7 (Bi                   | t 7 = LS                                      | B)   |      |      |      |          |     |   |   |   |   |   |         |

|-------------------------------------------------|-----------------|--------------------------------------------------|----------------------------|-------------------------------|-----------------------------------------------|------|------|------|------|----------|-----|---|---|---|---|---|---------|

| Instruction<br>Type/Format                      | (Bit 0=<br>MSB) | 0                                                | 1                          | 2                             | 3                                             | 4    | 5    | 6    | 7    | 8        | 9   | A | В | С | D | E | F       |

| Generic                                         | 0               | NOP                                              | WAIT                       | GNB                           | SFS                                           | CCH  | DEC  | RET  | SR   | INTR     | INZ |   |   |   |   |   |         |

| Double Operand –<br>Reference to CDB            | 1               |                                                  | ST                         |                               |                                               |      |      |      |      |          |     |   |   |   |   |   | Γ       |

| Input Output INa                                | 2               | LR0                                              | LR1                        | LR2                           | LR3                                           | LR4  | LR5  | LRG  | LR7  | 1        |     |   | 1 |   |   |   |         |

| Input Output OUTa                               | 3               | LR0                                              | LR1                        | LR2                           | LR3                                           | LR4  | LR5  | LR6  | LR7  |          |     |   | T | Τ |   | Ι |         |

| Reserved                                        | 4               | [                                                | <u> </u>                   | 1                             | <u>†                                     </u> | 1    | 1    | 1    | 1    | <b> </b> |     |   | 1 | 1 |   | 1 |         |

| Double Operand –<br>Reference to LCT<br>]Byte n | 5               | LD                                               | ST                         | C                             | AND                                           | OR   | XOR  | TLU  |      |          |     |   |   |   |   |   |         |

| Reserved for transmit channel <sup>e</sup>      | 6               |                                                  |                            |                               |                                               |      |      |      |      |          |     |   |   |   |   |   |         |

| Reserved                                        | 7.8             |                                                  |                            |                               |                                               |      |      |      |      |          |     |   |   |   |   |   |         |

| Double Operand-<br>Reference to IMO             | 9               | LD                                               |                            | C                             | AND                                           | OR   | XOR  |      |      |          |     |   |   |   |   |   |         |

| Send Receive RECV                               |                 | RECV 0<br>No<br>Parity<br>or<br>CRC <sup>b</sup> | RECV 1<br>CRC <sup>b</sup> | RECV 2<br>Parity <sup>b</sup> | RECV3<br>Parity<br>and<br>CRC <sup>b</sup>    |      |      |      |      |          |     |   |   |   | - |   |         |

| Reserved                                        | B.C.D           |                                                  |                            |                               |                                               |      |      |      |      |          |     |   |   |   |   |   |         |

| Branch –<br>Branch True                         | E               | В                                                | BET                        | BZT                           | BLCT                                          | BLBT | BART | JUMP | BVBT |          |     |   |   |   |   |   |         |

| Branch<br>Branch False                          | F               | BS                                               | BEF                        | BZF                           | BLCF                                          | BLBF | BART |      | BVBF |          |     |   |   |   |   |   | ******* |

## TABLE 4-9. MLCP BIT MAP OF CCP EXECUTABLE INSTRUCTIONS' OP CODE WORDS - RECEIVE MODE

<sup>a</sup>Existence of line register is dependent on type of Communications-Pac being used. If a nonexistent line register is used in the IN or OUT statement, the statement will be treated as a no-op.

<sup>b</sup>Indicates whether the parity check and/or cyclic redundancy check information in LCT byte 2 applies to the data character being transferred to the MLCP's R-register from the receive channel's line register 1 in the Communications-Pac.

<sup>c</sup>Do not use.

CHANNEL CONTROL PROGRAM

## TABLE 4-10. MLCP BIT MAP OF CCP EXECUTABLE INSTRUCTIONS' OP CODE WORDS - TRANSMIT MODE

16 in 160.

|                                               | Bits<br>0-3     |                                                 |                           | Bits 4                       | -7 (Bit 7                                  | = LSB) |                  |      |      |      |     |   |   |   |   |   |   |

|-----------------------------------------------|-----------------|-------------------------------------------------|---------------------------|------------------------------|--------------------------------------------|--------|------------------|------|------|------|-----|---|---|---|---|---|---|

| Instruction<br>Type/Format                    | (Bit 0=<br>MSB) | 0                                               | 1                         | 2                            | 3                                          | 4      | 5                | 6    | 7    | 8    | 9   | A | В | с | D | E | F |

| Generic                                       | 0               | NOP                                             | WAIT                      | GNB                          | SFS                                        | ССН    | DEC              | RET  | SR   | INTR | INZ |   |   |   |   |   |   |

| Double Operand-<br>Reference to CDB           | 1               | LD                                              |                           |                              |                                            |        |                  |      |      |      |     |   |   |   |   |   |   |

| Input/Output – IN <sup>a</sup>                | 2               | LR0                                             | LR1                       | LR2                          | LR3                                        | LR4    | LR5 <sup>a</sup> | LR6  | LR7  |      |     |   |   |   |   |   |   |

| Input/Output – OUT <sup>a</sup>               | 3               | LR0                                             | LR1                       | LR2                          | LR3                                        | LR4    | LR5              | LR6  | LR7  |      |     |   |   |   |   |   |   |

| Reserved                                      | 4               |                                                 |                           |                              |                                            |        |                  |      |      |      |     |   |   |   |   |   |   |

| Double Operand-<br>Reference to LCT<br>Byte n | 5               | LD                                              | ST                        | C                            | AND                                        | OR     | XOR              | TLU  |      |      |     |   |   |   |   |   |   |

| Send/Receive—SEND                             | 6               | SEND0<br>No<br>Parity<br>or<br>CRC <sup>b</sup> | SEND1<br>CRC <sup>b</sup> | SEND2<br>Parity <sup>b</sup> | SEND3<br>Parity<br>and<br>CRC <sup>b</sup> |        |                  |      |      |      |     |   |   |   |   |   |   |

| Reserved                                      | 7,8             |                                                 |                           |                              |                                            |        |                  |      |      |      |     |   |   |   |   |   |   |

| Double Operand—<br>Reference to IMO           | 9               | LD                                              |                           | С                            | AND                                        | OR     | XOR              |      |      |      |     |   |   |   |   |   |   |

| Reserved for<br>Receive Channel <sup>C</sup>  |                 |                                                 |                           |                              |                                            |        |                  |      |      |      |     |   |   |   |   |   |   |

| Reserved                                      | B,C,D           |                                                 |                           |                              |                                            |        |                  |      |      |      |     |   |   |   |   |   |   |

| Branch–<br>Branch True                        | E               | В                                               | BET                       | BZT                          | BLCT                                       | BLBT   | BART             | JUMP | BVBT |      |     |   |   |   |   |   |   |

| Branch–<br>Branch False                       | F               | BS                                              | BEF                       | BZF                          | BLCF                                       | BLBF   | BARF             |      | BVBF |      |     |   |   |   |   |   |   |

<sup>a</sup>Existence of a line register is dependent on type of Communications-Pac being used. If a nonexistent line register is used in the IN or OUT statement, the statement will be treated as a no-op.

<sup>b</sup>Indicates whether the parity generation and/or cyclic redundancy check information LCT byte 34 applies to the data character being transferred from the MLCP's R-register to the transmit channel's line register 1 of the Communications-Pac. The parity generation is done before the CRC operation (i.e., the parity bit is included in the CRC calculation).

<sup>c</sup>Do not use.

8/79 AT97B

## **Branch Instructions**

Fifteen (MLCP) or thirteen (DLCP) branch instructions are available to the CCP. The BART and BARF branch instructions are not available to the DLCP.

In the discussion that follows, differences between the MLCP and DLCP are noted with respect to displacement and internal instruction format. The expanded formats shown for DLCP should be understood in terms of the number of bytes for the expansion. The contents of these bytes are for DLCP firmware and microprocessor use only and are not visible to the user.

## Short Displacement Instructions

Format of Short Displacement Macro Call:

macro-name operand (comments)

macro-name

B BS BET BEF BZT BZF BLCT BLCF BLBT BLBF BVBT BVBF (MLCP and DLCP)

BART BARF (MLCP only)

operand

An internal value expression that identifies the target of the branch instruction.

MLCP: The displacement d is between the current byte address and the target byte address and must be in the following range:

-128≤d≤+127

The displacement is from P (the current value of the MLCP P-register, which is pointing to the byte that contains the displacement).

DLCP: The displacement d is from the byte address of the next op code to the target byte address and must be in the following range:

-128≤d≤+127

The displacement is from P+1 (P is the current value of the DLCP P-register).

Internal Format of Instructions:

...

MLCP: All short displacement branch instructions for the MLCP have the same internal format as follows. Recall that displacement is from the current byte address.

|          | 0 7          |             |

|----------|--------------|-------------|

| byte n   | op code      |             |

| byte n+1 | displacement | -128≪d≪+127 |

DLCP: The internal formats are shown in the diagrams that follow. The actual byte contents are not visible to the user. Recall that displacement is from the byte address of the next op code.

1 (D)

| Instruction:     | Branch (B) |   |              |             |

|------------------|------------|---|--------------|-------------|

| Internal Format: |            | 0 | ,            | 7           |

|                  | byte n     |   | op code      | ]           |

|                  | byte n+1   |   | displacement | -128≪d≪+127 |

CHANNEL CONTROL PROGRAM

AT97

XOR (Exclusive OR) – Perform an exclusive OR operation on the contents of the R-register and the contents of byte n of the LCT for this channel. Store the results of this operation in the R-register.

TLU (Table Look-Up) – This instruction permits the contents of a "table location" in RAM to be evaluated so as to produce either a "translation" of the contents of that location or a branch to another location in the CCP. Appendix A provides a sample use of the TLU instruction.

Examples: LD 31 LD WORK LD WORK+2

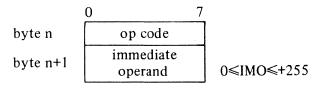

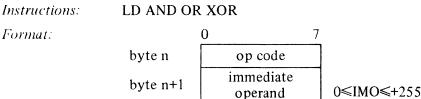

Format 3

Double operand instructions in this format refer to the R-register and an immediate operand.

All of the double operand instructions usable in this format are valid in either transmit or receive mode.

Format of Macro Call:

macro-name=operand(comments)

macro-name

LD C AND OR XOR

operand

An internal value expression that, when resolved, is an integer value from 0 to 255, inclusive. This integer value is an immediate operand, which is stored directly after the byte that contains the op code. Note that the internal value expression must be preceded by an equals sign (in the macro call).

Internal Format of Instructions:

Format:

MLCP:

DLCP:

Instruction: Compare (C)

Format:

|          | 0 7                  |    |

|----------|----------------------|----|

| byte n   | op code              |    |

| byte n+l | immediate<br>operand |    |

| byte n+2 | op code              |    |

| byte n+3 | op code              |    |

| byte n+4 | constant             | 0≮ |

0≤IMO≤+255

## Description of Instructions

LD (Load) - Load the immediate operand into the R-register.

C (Compare) – Compare the immediate operand with the contents of the R-Register. If the comparison is equal, set the E-indicator to 1; otherwise, reset it to 0.

AND (Logical AND) Perform a logical AND operation on the immediate operand and the contents of the R-register. Store the results of this operation in the R-register.

OR (*Inclusive OR*) — Perform an inclusive OR operation on the immediate operand and the contents of the R-register. Store the results of this operation in the R-register.

*XOR (Exclusive OR)* Perform an exclusive OR operation on the immediate operand and the contents of the R-register. Store the results of this operation in the R-register.

Examples: LD =X'02' LD =STX NOTE: Format must conform to the macro preprocessor. LD =VAL+2

#### Input/Output Instructions

These instructions are used to transfer control, synchronization, transmit fill, status, and character configuration information between the Processor R-register and the appropriate line registers of a line adapter. The input/output instructions can also be used to transfer data characters between the Processor and line register 1 of an adapter; however, input/output instructions do not provide parity checking or generation, cyclic redundancy checking, or receive overrun or transmit underrun checking and notification.<sup>3</sup>

Format of Macro Call:

macro-name operand (comments)

macro-name IN,OUT

operand

An internal value expression that, when resolved, is an integer value from 0 to 7, inclusive. This integer is the number of an adapter line register that will be read or written.

NOTE: The line register must be legitimate for the connected adapter. If the register does not exist and the instruction is in the CCP, the IN or OUT will be treated as no-op. The IN will cause the R-register to be altered.

<sup>&</sup>lt;sup>3</sup> Send/receive instructions, described in the following subsection, offer these capabilities.

execution of SEND (Send) and RECV (Receive) instructions whose operand values are 1 or 3. The resultant cyclic redundancy check residue in LCT bytes 3/35 and 4/36 may be examined from the CCP. These bytes must be initialized by the CCP or the main memory program whenever a block CRC calculation is restarted. LRC is in bytes 3/35; and LCT 4/36 is zeros.

The appropriate initial value for LCT byte 3/35 and 4/36 is all 1s for a CRC polynomial code equal to 01 (HLDC) (MLCP only). For the other CRC polynomial codes (CRC 16, LRC, CRC 12), the appropriate initial value is all zeros (MLCP and DLCP). The program, typically the CCP, must ensure that these initial values are provided.

#### Byte Layout:

The format of these bytes is governed by which cyclic redundancy check polynomial is used; see Section 6.

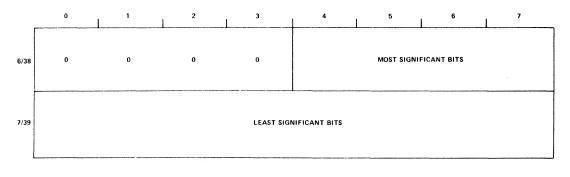

## LCT BYTES 6/38 AND 7/39 – CCP POINTER

## Description:

These bytes store the 12-bit RAM address at which the CCP will begin execution when it is started again. When the Processor services this CCP, this RAM address will be loaded into the P-register (program counter).

### Programming Considerations:

The initial starting address of the CCP must be written into these bytes from the main memory program.

During processing, Processor firmware uses these bytes to store the contents of the P-register whenever the CCP executes a WAIT (Wait) instruction or whenever a firmware pause occurs (MLCP only) or the executing CCP is swapped out (DLCP). When the CCP resumes, firmware restores the contents of these bytes to the P-register, thereby allowing the CCP to begin at its next sequential instruction.

The contents of these bytes may be modified from the main memory program, if you wish to have the CCP resume at an address other than the one stored here. IO (Output LCT Byte) instructions can be used for this purpose. However, the CCP must not be running at the time or the results are unspecified.

When LCT byte 6/38 is written, bits 0 through 3 must always be reset to zero.

These bytes must not be modified by the CCP.

Byte Layout:

# LCT BYTE 8/40 – CHANGE CONTROL FOR DATA SET AND ADAPTER STATUS

#### Description:

This byte may be written from the CCP to control (1) whether the Processor firmware will scan for changes in data set status and line adapter (Communications-Pac) status, recording these changes in LCT byte 14/46 and (2) what action(s) will be taken when a status change is recorded. (A mask in LCT byte 15/47 governs exactly which types of status change will cause LCT byte 14/46 to be updated with the contents of adapter line register 5.)

#### **Programming** Considerations:

This byte may be initially written from the main memory program or from the CCP. It may subsequently be changed by either program - at points in time appropriate to the communications application.

Whenever this byte is written, bits 4 through 7 must always be reset to zero. If bits 2 and 3 are both set to 1, only bit 2 (terminate the active CCB and interrupt the main memory program) will be acted upon when a data set or adapter status change is recorded in LCT byte 14/46.

Refer also to the programming guidelines in Appendix A.

Byte Layout:

|      | 0               | 1                                              | 2                                                   | 3                                                   | 4 | 5 | 6 | 7 |  |

|------|-----------------|------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|---|---|---|---|--|

| 8/40 | SCAN<br>CONTROL | SET BIT 3<br>OF LCT<br>BYTE 17/49<br>IF CHANGE | INTERRUPT<br>MAIN<br>MEMORY<br>PROGRAM<br>IF CHANGE | START<br>CHANNEL<br>CONTROL<br>PROGRAM<br>IF CHANGE | 0 | 0 | 0 | 0 |  |

## Bit 0 - scan control

- 0 The Processor firmware will not scan adapter line register 5 for changes in data set status and adapter status.

- 1 The Processor firmware will scan adapter line register 5 for changes in data set status and adapter status. Firmware will write the entire contents of line register 5 into LCT byte 14/46 whenever it detects a difference between the contents of a bit position in line register 5 and the contents of the same bit position in LCT byte 14/46 (provided there is a 1 in the corresponding bit position of the mask contained in LCT byte 15/47). Next, the action(s) specified in bits 1, 2, and 3 of LCT byte 8/40 will be taken.

- Bit 1 set bit 3 of LCT byte 17/49 if change

- 0 No action.

- 1 When a data set or adapter status change is recorded in LCT byte 14/46, set to 1 bit 3 of LCT byte 17/49 (LCT status byte 2).

- Bit 2- interrupt main memory program if change (refer also to LCT status byte 16/48)

- 0 No action.

- 1 When a data set or adapter status change is recorded in LCT byte 14/46, terminate the active CCB and interrupt the main memory program at the interrupt level established for this channel. (Ignore the setting of bit 3 of this byte and set bit 1 of LCT status byte 16/48.)

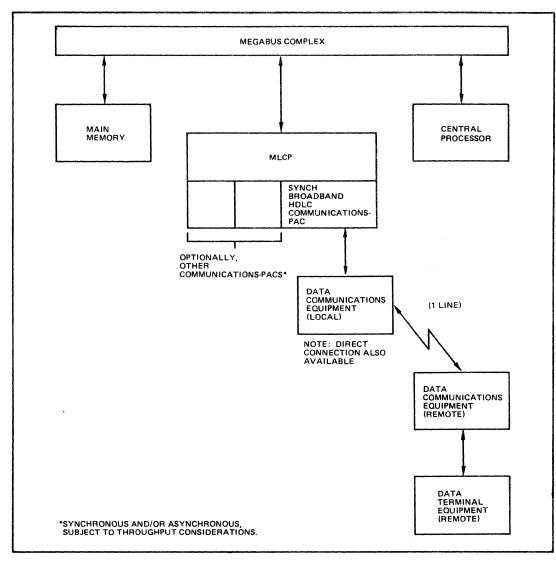

## Appendix D

## Synchronous Line Communications-Pacs/Adapters

A Synchronous Line Communications-Pac/Adapter (Type DCM9103 or DCM9104 (MLCP) and Type DCM9302 or DCM9303 (DLCP)) provides an interface between the MLCP or DLCP respectively, and one or two completely independent synchronous communications lines.<sup>1</sup> For each line, the synchronous line adapter provides the following services:

- o Serial/parallel data conversion for synchronous bit-serial data transfers

- o Character synchronization by use of a synchronization character such as the ASCII SYN

- o Control of data sets

- o Monitoring of data set status

Each communications line comprises a receive channel and a transmit channel and is thus capable of half-duplex or full-duplex data communications operations. Each line has a clocked, independently configurable speed (up to 20,000 bits per second for MLCP or up to 9600 bits per second for DLCP)<sup>2</sup> and an independently configurable data character size (from five to eight bits—including parity, if used); each channel of a line uses the configured line speed and data character size. The synchronous line adapter supports BSC, Basic Mode ASCII, and similarly formatted control procedures.

The following data communications equipment and data terminal equipment is supported through an EIA RS-232-C interface:

- o Bell System 201A, B, C, or equivalent

- o Bell System 203A, B, or equivalent

- o Bell System 208A, B, or equivalent

- o Bell System 209 or equivalent

Figure D-1 illustrates the Synchronous Line Communications-Pac's interface position between the MLCP and synchronous communications lines. (Note that the MLCP can connect any combination of Synchronous Line Communications-Pacs and Asynchronous Line Communications-Pacs up to a total of four.) Figure D-2 illustrates the DLCP interface.

#### LINE REGISTERS

The programming interface to the synchronous line adapter is achieved through its line registers. These line registers are illustrated in Figure D-3.

<sup>&</sup>lt;sup>1</sup>Throughout this appendix, descriptions are based on a Synchronous Line Communications-Pac/Adapter that services *two* lines. The *single*-line version of the synchronous line adapter is identical except for the number of lines it services.

<sup>&</sup>lt;sup>2</sup> Each line's speed is governed by the associated data set, or by either the MLCP's fixed-rate clock, or the DLCP clock settable for each line. Details appear under "Data Transfer Clocks," later in this appendix.

Figure D-1. Interface Provided by Synchronous Line Communications-Pac (MLCP)

SYNCHRONOUS LINE COMMUNICATIONS-PACS/ADAPTERS

D-2

AT97

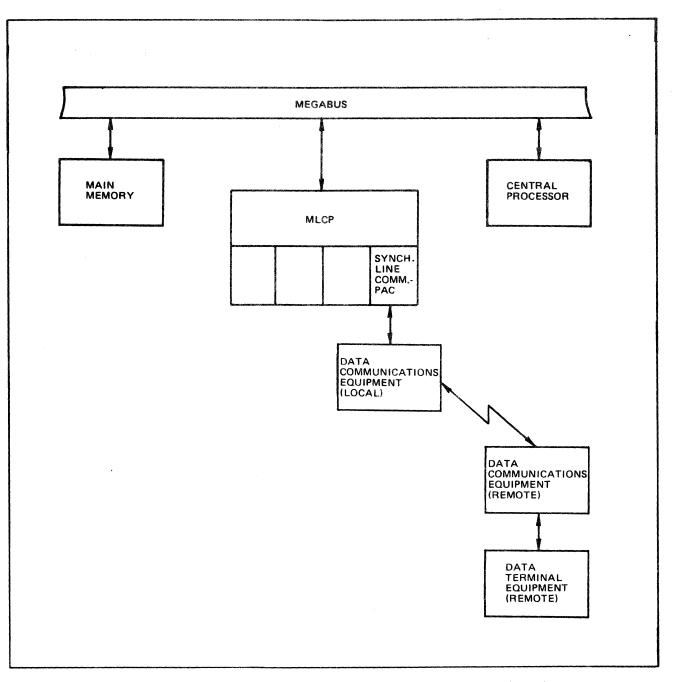

## Appendix H

# Synchronous Broadband HDLC Communications-Pac

## **INTRODUCTION**

The Synchronous Broadband HDLC (high-level data link control) Communications-Pac (Types DCM9112, 9113, and 9121) provides an interface between the MLCP and one broadband synchronous communications line (72,000 bps maximum). The Synchronous Broadband HDLC Communications-Pac provides for the application of the following control procedures (protocols):

- o American National Standard for Advanced Data Communication Control Procedure (ADCCP), Draft 7, BSR X3.66, 14 December 1977.

- o ISO HDLC (Draft No. ISO/TC 97/SC 6N 1339, dated February 1973)

- o Honeywell HDLC procedure

The communications line comprises a receive channel and a transmit channel, and is capable of either full- or half-duplex operation. Operation of the two channels is completely independent except that they share the same modem and a change in data set control signal will affect both channels.

The Synchronous Broadband HDLC Communications-Pac supports the following interfaces:

- DCM9112 Bell 303-compatible interface, supporting the following connections: Bell System 301B modem or equivalent Bell System 303 modem or equivalent Direct connect, 303-compatible

- DCM9113 -- CCITT V35 interface supporting the following connections: Data communications equipment using V35 Bell System Digital Data Service (DDS) using Data Service Units at 56kbs

- DCM9121 -- MIL188C, supporting the following connections: Modems or equivalent supporting a MIL-STD-188C interface

In addition, the Communications-Pac may be used in direct connect arrangements where the MLCP supplies the clock. The direct connect cable is identified by specifying W18-0001C.

Figure H-1 illustrates the Synchronous Broadband HDLC Communications-Pac's interface position between the MLCP and a synchronous broadband communications line. Note that a single broadband line can be intermixed with other line types on a single MLCP, subject to overall throughput considerations, but one broadband line per MLCP is a limit.

## HDLC FRAME STRUCTURE

The HDLC frame structure, illustrated in Figure H-2, eliminates the need for control characters of other protocols (such as bisynchronous) and maximizes the ratio of information (data) to control in bits. It offers field transparency and code independence facilitating the sending of binary information (i.e., the frame structure is bit-oriented). In addition, the HDLC frame structure has the potential for handling very high speed lines to accommodate growth in networking or other data communications applications.

Specifications may change as improvements and modifications are introduced.

The elements of the HDLC procedure supported by the Communications-Pac are zerobit insertion and deletion, character assembly/disassembly, and the handling of flag, abort, idle and partial byte.

The Cyclic Redundancy Check (CRC) Frame Check Sequence (FCS) is calculated and checked automatically by the Communications-Pac. Extended address field, extended control field, logical control field, and byte size switching are supported.

Figure H-1. Interface Provided by Synchronous Broadband HDLC Communications-Pac

| FLAG<br>01111110 | ADDRESS<br>8 BITS<br>(OR MULTIPLE OF<br>8 BITS) | CONTROL<br>8 BITS<br>OR<br>16 BITS | INFORMATION          | FCS<br>16 BITS   | FLAG<br>01111110 |

|------------------|-------------------------------------------------|------------------------------------|----------------------|------------------|------------------|

| * A N 1 I N      | SPECIFIED NUMBER OF                             | BITS WHICH MAY                     | IN SOME CASES BE A M | ULTIPLE OF A PAF | TICULAR          |

|                  | ACTER SIZE, E.G., OCTE                          | rs.                                |                      |                  |                  |

Figure H-2. HDLC Frame

SYNCHRONOUS BROADBAND HDLC COMMUNICATIONS-PAC 8/79 AT97B .

In HDLC, all transmissions are in "frames" and each frame conforms to the structure of Figure H-2. In this section, an eight-bit string is called an "octet." (Frames containing only supervisory control sequences constitute a special case in which the information field is omitted. This is protocol-dependent.) The fields of the frame are defined in the paragraphs that follow.

## **Flag Sequence**

All frames start and end with the flag sequence. This sequence is a zero-bit followed by six one-bits followed by a zero-bit (01111110). All stations attached to the data link continuously hunt, on a bit-by-bit basis, for this sequence. A transmitter must send only complete flag bit sequence; however, the sequence of 011111101111110 at the receiver is two flag sequences. The flag is used for frame synchronization. Flag detection is performed by the Communications-Pac under programmer control.

In order to achieve transparency, the flag sequence is prohibited from occurring in the Address, Control, information and FCS fields via a "zero-bit insertion" procedure performed by the Communications-Pac. (See the paragraph entitled "Transparency" later in this section.)

The flag sequence which closes a frame may also be the opening flag sequence for the next frame. Any number of complete flags may be used between frames.

## **Address Field**

The *address field* contains the link level address of a secondary station or stations. The length of this field is normally one octet.

For extended addressing, this field may optionally contain multiple octets. Field extension is accomplished by the use of the least significant bit of each address field octet as a continuation bit. In this case all octets in the field (except the last) will have a zero in their continuation bit position.

Whether or not extended mode applies is under program control and must be determined by prior agreement between the transmitter and receiver. In the Synchronous Broadband HDLC Communications-Pac, the mode is indicated to the Communications-Pac via a bit in the appropriate configuration register of the Communications-Pac (transmit line register 7 and receive line register 6).

Normally, transmitted address field bytes must be program generated and transferred like data to the MLCP-Communications-Pac for transmission. Similarly, received address field bytes are normally input to the main memory program (MMP) as part of the data block.

#### **Control Field**

The *control field* contains a command or response and may contain sequence numbers. The control field is used by the transmitting (primary) station to instruct the addressed secondary station what operation it is to perform. It is also used by the secondary station(s) to respond to the remote primary station(s). The length of the control field is one octet in the case of the basic control field. It is two octets in length in the case of the extended control field.

The first bit of the octet (i.e., the low order bit, bit 7 - first octet if in extended mode) provides information about the format of the remainder of the frame. When a zero, it indicates the frame is in Information Transfer format and byte size of the text field is specified in the "Logical Control field"<sup>1</sup> or the appropriate configuration register of the Communications-Pac. When a one, it indicates the frame is in supervisory format or non-sequenced format and all data for the remainder of the frame is in 8-bit bytes.

The specification as to whether or not extended mode applies is under program control and must be determined by prior agreement between the transmitter and receiver. In the Synchronous Broadband HDLC Communications-Pac, the mode is indicated to the Communications-Pac via a bit in the appropriate configuration register of the Communications-Pac (transmit line register 7 and receive line register 6).

<sup>&</sup>lt;sup>1</sup> Refer to the paragraph entitled "Information Field," and to the discussion on the Logical Control Field.

Output Control field bytes must be program generated and transferred as data to the MLCP-Communications-Pac for transmission. Similarly, received Control bytes are input to the MMP as part of the data block.

## **Information Field**