# Honeywell

THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN IS PROPRIETARY TO AND THE EXCLUSIVE PROPERTY OF HONEYWELL INFORMATION SYSTEMS INC. THIS DOCUMENT AND THE INFORMA-TION CONTAINED THEREIN IS FOR THE USE OF HONEYWELL AUTHO-RIZED RECIPIENTS ONLY FOR THE MAINTENANCE AND OPERATION OF HONEYWELL PRODUCTS AND MUST BE MAINTAINED IN STRICTEST CONFIDENCE. IT MUST NOT BE REPRODUCED IN WHOLE OR IN PART. THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN SHALL NOT BE DISCLOSED TO ANY OTHER PARTY WITHOUT THE PRIOR WRIT-TEN CONSENT OF HONEYWELL.

SERIES 60 LEVEL 6

# TYPE DCM9103 DUAL SYNCHRONOUS COMMUNICATIONS LINE ADAPTER MANUAL

Doc. No. 71010231-200 Order No. FL49, Rev. 1

# Honeywell

THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN IS PROPRIETARY TO AND THE EXCLUSIVE PROPERTY OF HONEYWELL INFORMATION SYSTEMS INC. THIS DOCUMENT AND THE INFORMA-TION CONTAINED THEREIN IS FOR THE USE OF HONEYWELL AUTHO-RIZED RECIPIENTS ONLY FOR THE MAINTENANCE AND OPERATION OF HONEYWELL PRODUCTS AND MUST BE MAINTAINED IN STRICTEST CONFIDENCE. IT MUST NOT BE REPRODUCED IN WHOLE OR IN PART. THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN SHALL NOT BE DISCLOSED TO ANY OTHER PARTY WITHOUT THE PRIOR WRIT-TEN CONSENT OF HONEYWELL.

SERIES 60 LEVEL 6

# TYPE DCM9103 DUAL SYNCHRONOUS COMMUNICATIONS LINE ADAPTER MANUAL

Doc. No. 71010231-200 Order No. FL49, Rev. 1

| REVISION     | DATE                               | AUTHORITY                                  | AFFECTED PAGES    |

|--------------|------------------------------------|--------------------------------------------|-------------------|

| -100<br>-200 | May 1976<br>Oct. 1976<br>Oct. 1976 | Original Issue<br>BLCO 60216<br>BLCO 60736 | 2-8<br>2-16, 2-17 |

|              |                                    |                                            |                   |

|              |                                    | CEO-B. Billerica                           |                   |

RECORD OF REVISIONS

Publications Department, CEO-B, Billerica, MA 01821 Printed in the United States of America All rights reserved

# CONTENTS

| Section  |                      |                                                                                   |                                                                                                                                                                                                         | Page                                                                                   |

|----------|----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| I        | 1.4                  | General D<br>Interface<br>Physical<br>Options                                     | Characteristics                                                                                                                                                                                         | 1-1<br>1-1<br>1-3<br>1-3<br>1-3<br>1-3                                                 |

| II       | THEORY<br>2.1<br>2.2 | Fundament<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8 | gram Description<br>al Hardware Description<br>Interconnections<br>Subchannel Identification Code<br>Lines<br>SCLA Control<br>Data Set Control<br>Data Output<br>Data Input<br>Input Status Multiplexer | 2-1<br>2-4<br>2-4<br>2-8<br>2-8<br>2-9<br>2-15<br>2-18<br>2-21<br>2-21<br>2-21<br>2-25 |

| III      | THEORY               | OF OPERAT                                                                         | ION - CYCLE FLOW                                                                                                                                                                                        | 3-1                                                                                    |

| Appendix | k A Wra              | paround T                                                                         | est                                                                                                                                                                                                     | A-1                                                                                    |

| Appendix | k B Cak              | oling                                                                             |                                                                                                                                                                                                         | B-1                                                                                    |

# ILLUSTRATIONS

|                                                                        | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

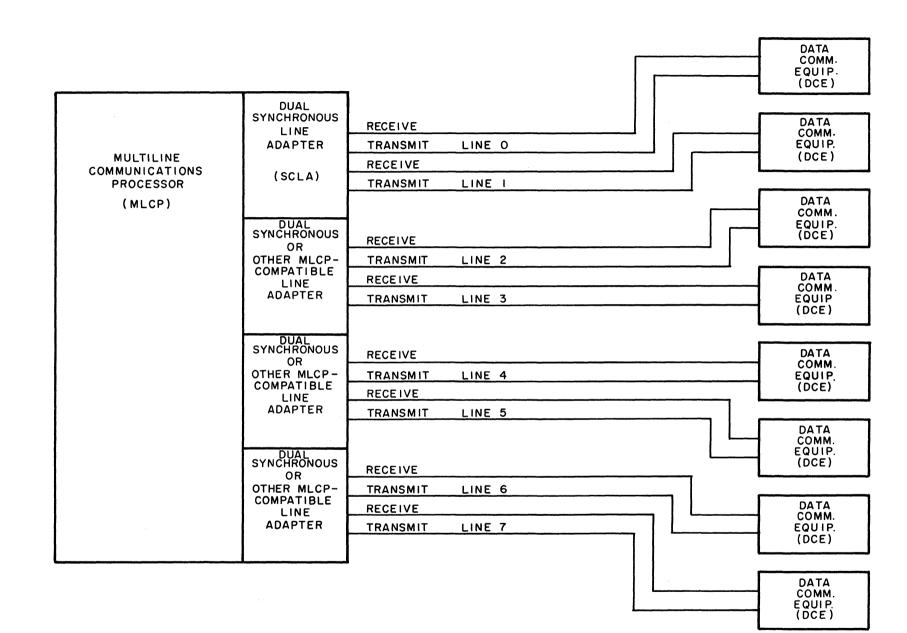

| Configuration Diagram, Dual Synchronous<br>Communications Line Adapter | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

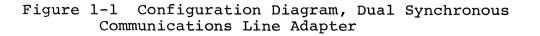

| Dual SCLA Layout and Dimensions                                        | 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dual Synchronous Communications Line Adapter<br>Block Diagram          | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5                                                                      | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interconnections Between Dual SCLA and Lines                           | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dual SCLA Control, Address and Control Line                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Decoding                                                               | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dual SCLA Line Registers                                               | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data Set Control Logic                                                 | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Character Transmission                                                 | 2-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data Output to Data Communications Equipment                           | 2-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data Input to MLCP from Data Communications                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Equipment                                                              | 2-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Input Status Multiplexer Logic                                         | 2-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Test Multiplexer Logic                                                 | 2-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Direct Connect Logic                                                   | 2-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

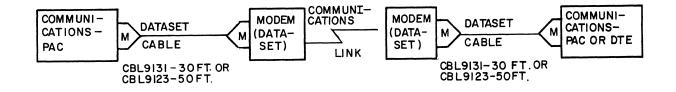

| Typical Modem Configuration                                            | B-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

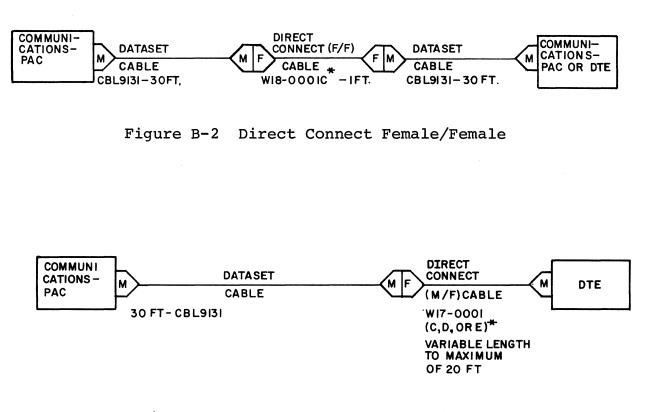

| Direct Connect Female/Female                                           | в-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Direct Connect Male/Female                                             | в-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                        | Communications Line Adapter<br>Dual SCLA Layout and Dimensions<br>Dual Synchronous Communications Line Adapter<br>Block Diagram<br>Interconnections Between MLCP and Dual SCLA<br>Interconnections Between Dual SCLA and Lines<br>Dual SCLA Control, Address and Control Line<br>Decoding<br>Dual SCLA Line Registers<br>Data Set Control Logic<br>Character Transmission<br>Data Output to Data Communications Equipment<br>Data Input to MLCP from Data Communications<br>Equipment<br>Input Status Multiplexer Logic<br>Test Multiplexer Logic<br>Direct Connect Logic<br>Typical Modem Configuration<br>Direct Connect Female/Female |

# TABLES

| Table |                                              | Page |

|-------|----------------------------------------------|------|

| 2-1   | Interconnections-SCLA To/From MLCP           | 2-5  |

| 2-2   | Interconnections-SCLA To/From Lines          | 2-7  |

| 2-3   | SCLA ID Code Generation                      | 2-8  |

| 2-4   | Address and Control Lines - General Decoding | 2-11 |

| 2-5   | Decoding-Control and Address Lines           | 2-12 |

| 2-6   | Transmitter/Receiver Word Size Configuration | 2-18 |

| 2-7   | Inputs to Input Status Multiplexer           | 2-24 |

| A-1   | EIA Connector Jumpers for DCMT1 Loop Test    | A-1  |

.

iv

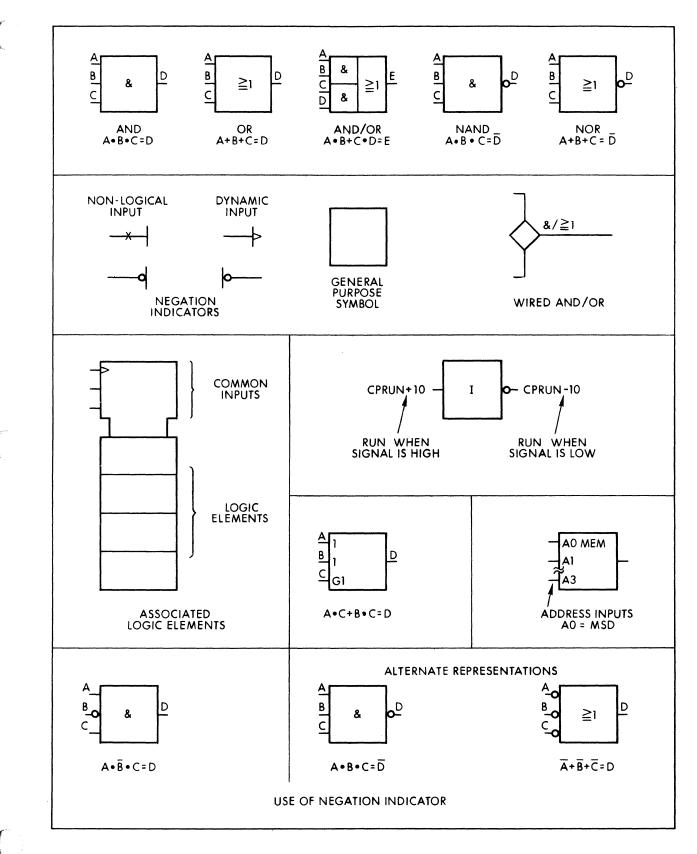

LOGIC SYMBOLOGY

v/vi

$\sim$

# I INTRODUCTION

### 1.1 GENERAL DESCRIPTION

The Type DCM9103 Dual Synchronous Communications Line Adapter is one of a series of solid-state Communications-Pacs used with the Multiline Communications Processor (MLCP) of the Honeywell Series 60 Level 6 computer. As shown in Figure 1-1, up to four compatible line adapters can be used with an MLCP, and from one to four of these adapters can be a dual SCLA. Each dual SCLA can support two full-duplex lines, and each direction (receive and transmit) of a line is a separate channel into the MLCP. (Note that in this manual, SCLA refers to a dual Synchronous Communications Line Adapter.)

An SCLA contains the logic for data handling, control and interface between the MLCP and Data Communications Equipment (DCE). Essentially, the SCLA contains a group of line registers which the MLCP continually sets to effect required operational functions. Note that all formatted control procedures used in communicating with the DCE are performed in the MLCP.

The SCLA can be used with, but is not restricted to, the following DCE:

- Dataphone Data Set 201 or equivalent, or direct connect

- Dataphone Data Set 203 or equivalent, or direct connect

- Dataphone Data Set 208 or equivalent, or direct connect.

.

HONEYWELL PROPRIETARY AND CONFIDENTIAL

## 1.2 INTERFACE

The data interface between the SCLA and the DCE is full-duplex for each line. All input and output data information is in a serial stream consisting of communication-type characters. Either 5-, 6-, 7-, or 8-bit characters are used, depending upon software instructions.

In addition to the data interface between the SCLA and the DCE, there are also ten control line interconnections between the SCLA and DCE for each line. See Table 2-2 for an explanation of the use of these lines.

All transmission between the SCLA and the DCE is at a level specified by Specification RS232C of the Electronic Industries Association (EIA). To conform with this specification, 0V and 5V signals generated in the SCLA are changed to +12V and -12V respectively if they are transmitted to the DCE. Conversely, +3 to +25V and -3 to -25V levels generated in the DCE are changed to 0V and 5V respectively when they are received in the SCLA.

The interface between the SCLA and MLCP is half duplex. All input data, output data, and control signals are carried on lines which use connectors on the bottom of the SCLA to connect to the MLCP. All data is transferred in parallel (byte form) between the SCLA and MLCP.

The transmission rate between the SCLA and the DCE is determined by either the transmit clock or receive clock signal generated in the DCE and sent into the SCLA.

# 1.3 PHYSICAL CHARACTERISTICS

The SCLA (BD2LAS) can be attached to any Communications-Pac position on the MLCP (BF4MLC). The physical dimensions of the MLCP and the Communications-Pacs are shown in Figure 1-2.

The BD2LAS board has two 25-pin connectors (Z01 and Z02) which are used for the physical and electrical connection of the Communications-Pac to the MLCP. A 28-pin connector, Y01, is used to connect the DCE cable to the BD2LAS board.

For information pertaining to cabling, refer to Appendix B.

#### 1.4 OPTIONS

The Synchronous Communications Line Adapter (SCLA) can be used in a direct connect application. This application allows the MLCP to interface with another computer without the use of Data Communications Equipment (DCE). Details on the direct connect option are covered in subsection 2.2.9.

## **1.5** REFERENCE DOCUMENTS

The following documents supplement the information contained in this manual.

| Title                                                             | Document No. | Order No. |

|-------------------------------------------------------------------|--------------|-----------|

| Model 34/36 Systems<br>Manual                                     | 71010200-200 | FL35      |

| Type MLC9103 Multiline<br>Communications Proces-<br>sor Manual    | 71010230-200 | FL48      |

| Type DCM9103 Communi-<br>cations Line Adapter<br>Reference Manual | 71010381-200 | FL52      |

| Level 6 Minicomputer<br>Handbook                                  |              | AS22      |

| MLCP Programmer's<br>Reference Manual                             |              | AT97      |

| Level 6 System Checkout<br>and Operator's Guide                   |              | AW94      |

Figure 1-2 Dual SCLA Layout and Dimensions

🦉 📐 14 - 2

1-4

# II THEORY OF OPERATION

# 2.1 BLOCK DIAGRAM DESCRIPTION

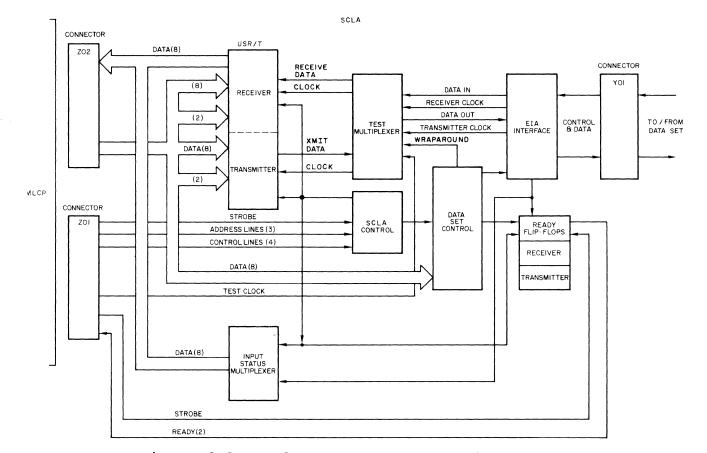

The Synchronous Communications Line Adapter (SCLA) provides the Multiline Communications Processor (MLCP) with two independent interfaces with standard synchronous communications lines. Figure 2-1 is a block diagram of the logic used in interface A (between the MLCP and line 0). Interface B (between the MLCP and line 1), which has similar logic, is not shown. Note, however, that the line adapter control block and the test multiplexer shown in Figure 2-1 are common to interface A and interface B.

The basic function of the SCLA is to control the data flow between the MLCP and the lines. Data bytes received in parallel from the MLCP are transformed into standard communication-type characters and transferred to the lines in a serial stream. Communication-type characters received from the lines in a serial stream are converted to data bytes and sent to the MLCP in parallel-byte form. A secondary function of the SCLA is to interchange control information between the MLCP and the DCE.

All interconnections between the adapter and the MLCP are via hardware connectors on the bottom of the SCLA. There are four control lines and three address lines between the MLCP and the SCLA. The line adapter control logic uses these lines to generate signals for control of the SCLA hardware. (See subsection 2.2.3 for details on the decoding of the control and address lines and the use of the generated control signals.) The eight data input lines are used to transfer either data bytes from the receiver or an input byte from the input status multiplexer into the MLCP. The data output lines are used to transfer;

- Configuration bytes to the transmitter/receiver (XMTR/RCVR) configuration register.

- 2. Sync configuration bytes to the receiver.

- 3. Sync configuration bytes to the transmitter.

- 4. Configuration information to the data set control register.

- 5. Data bytes to the transmitter.

Prior to receiving data from the line, the MLCP channel program loads three SCLA registers. First, the XMTR/RCVR configuration register is loaded to handle 5-, 6-, 7-, or 8-bit characters. Next, a sync character is loaded into the XMTR/RCVR sync character register. Finally, the MLCP loads the data set control register to control the operation of the SCLA lines. Note that parity checking of received characters is not accomplished in the SCLA. Then the sync character is used to make a bit-by-bit comparison of the data stream received from the DCE. When a sync character is detected in the incoming stream, the receiver changes from the bit-by-bit mode into a byte mode of operation and notifies the MLCP via the ready flip-flop. In the byte mode, the sync character and all the following characters in the input message are transferred to the MLCP from the DCE. (See subsection 2.2.6 for more details on an input operation.) If the receiver has two characters ready for transfer to the MLCP before one is taken, the receiver generates an overrun error signal.

Prior to transmitting data to the line, the MLCP channel program loads three SCLA registers. First, the XMTR/RCVR configuration register is loaded to handle 5-, 6-, 7-, or 8-bit characters. Next, a transmit fill character is loaded into the XMTR/RCVR transmit fill character register. Finally the MLCP loads the data set control register to control the operation of the SCLA lines. Note that no parity bit generation is accomplished by the transmitter. The configured transmit fill character is sent out to the line during an output operation whenever the MLCP fails to maintain required data output rate. The transmitter also generates an underrun error signal when this condition develops. (See subsection 2.2.5 for more details on a transmit operation.)

The input status multiplexer inputs SCLA error and line status information into the MLCP from either interface A or interface B as selected. (See subsection 2.2.7 for specific information carried by the input signals.)

The test multiplexer provides a wraparound mode for use by diagnostic software. This wraparound mode allows the serial data stream out of the transmitter to be sent directly back to the MLCP via the receiver in data-byte form. The test multiplexer also shifts the source of the clock signal to the MLCP when the wraparound mode is being used. The diagnostic software checks the operation of the SCLA in the wraparound mode by comparing transmitted to received characters. (See subsection 2.2.8 and Appendix A for further details.)

The data set control logic consists of an 8-bit register which stores control information from the MLCP. This information is then used by the SCLA for controlling the interface with its associated DCE. (See subsection 2.2.4 for details on the use of the stored information.)

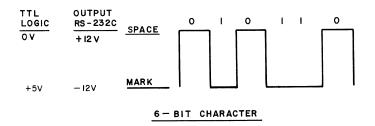

The EIA interface logic enables the SCLA to use transmitters and receivers designed to specification RS-232C of the Electronic Industries Association (EIA). This interface changes the level of the signals out of the SCLA from the TTL 0V and +5V to +12V and -12V respectively for use by the DCE. Conversely, the EIA interface logic changes signals received at +3 to +25V and -3 to -25V levels from the DCE to 0V and +5V respectively for use by the SCLA. (See Figure 2-7.)

The ready flip-flops which are used in a receive or transmit operation are discussed in detail in subsections 2.2.5 and 2.2.6.

Figure 2-1 Dual Synchronous Communications Line Adapter (SCLA), Block Diagram

# 2.2 FUNDAMENTAL HARDWARE DESCRIPTION

#### 2.2.1 Interconnections

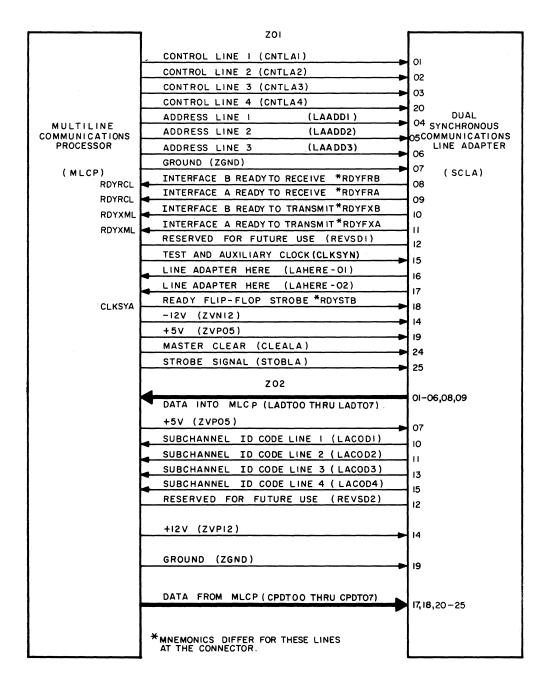

Figure 2-2 shows the interconnections between the Multiline Communications Processor (MLCP) and the SCLA. Table 2-1 describes the function of the signals carried by these interconnections.

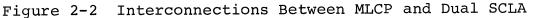

Figure 2-3 shows the interconnections between the SCLA and the lines. Table 2-2 describes the function of the signals carried by these interconnections.

2-4

| MNEMONIC                 | NAME OF LINE                     | FUNCTION                                                                                                                                                                         |

|--------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLEALA                   | Master Clear                     | Clears hardware in the SCLA when ordered by the MLCP.                                                                                                                            |

| CLKSYN                   | Test and Auxiliary<br>Clock      | Clock signal from MLCP used in<br>the test mode and direct con-<br>nect mode.                                                                                                    |

| CNTLAl<br>thru<br>CNTLA4 | Control                          | Selects functions to be per-<br>formed by SCLA hardware.                                                                                                                         |

| CPDT00<br>thru<br>CPDT07 | Data Output Byte                 | Data output byte from the<br>MLCP. Used to transfer both<br>data and control information.                                                                                        |

| LAADD1<br>thru<br>LAADD3 | Address                          | Selects line and channel to be serviced.                                                                                                                                         |

| LACOD1<br>thru<br>LACOD4 | Subchannel ID Code               | Lines by which the MLCP iden-<br>tifies the specific type of<br>SCLA attached to it.                                                                                             |

| LADTOO<br>thru<br>LADTO7 | Input Byte                       | Data input byte into the MLCP.<br>Depending upon the operating<br>condition of the SCLA, this<br>byte can be either data or<br>status from either interface A<br>or interface B. |

| LAHERE-01<br>LAHERE-02   | SCLA Here                        | Notifies the MLCP that a SCLA is installed.                                                                                                                                      |

| RDYFRA                   | Interface A Ready<br>to Receive  | Indicates that interface A is<br>ready to transfer a data char-<br>acter into the MLCP.                                                                                          |

| RDYFRB                   | Interface B Ready<br>to Receive  | Indicates that interface B is<br>ready to transfer a data char-<br>acter into the MLCP.                                                                                          |

| RDYFXA                   | Interface A Ready<br>to Transmit | Indicates that interface A is<br>ready to receive a new data<br>character from the MLCP for<br>transmission to the line.                                                         |

| RDYFXB                   | Interface B Ready<br>to Transmit | Indicates that interface B is<br>ready to receive a new char-<br>acter from the MLCP for trans-<br>mission to the line.                                                          |

| RDYSTB                   | Ready Flip-Flop<br>Strobe        | Used to synchronize the ready<br>flip-flops in interface A and<br>B (of the SCLA) with the MLCP.                                                                                 |

| STOBLA                   | Strobe Signal                    | Strobe from the MLCP to the<br>SCLA for generating various<br>control signals. Indicates<br>that data from MLCP is valid.                                                        |

| REVSD1<br>REVSD2         | Reserved                         | Reserved for future use.                                                                                                                                                         |

| ZGND                     | Ground                           | Ground                                                                                                                                                                           |

| ZVP05                    | +5V                              | +5V                                                                                                                                                                              |

| ZVN12                    | -12V                             | -12V                                                                                                                                                                             |

| ZVP12                    | +12V                             | +12V                                                                                                                                                                             |

Table 2-1 Interconnections-SCLA To/From MLCP

2-5

(

Figure 2-3 Interconnections Between Dual SCLA and Lines

2-6

Table 2-2 Interconnections-SCLA To/From Lines

| MNEMONIC | NAME                    | FUNCTION                                                                                                                                                                                                 |

|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                         | NOTE                                                                                                                                                                                                     |

| an       |                         | for line 0. Line l has<br>gnals, but the last letter<br>nstead of A.                                                                                                                                     |

| CLKRDA   | Receive Clock           | Clock signal from the DCE to the<br>SCLA while it is receiving data<br>from the DCE.                                                                                                                     |

| CLKXDA   | Transmit Clock          | Clock signal from the DCE to the<br>SCLA when it is transmitting data<br>to the DCE.                                                                                                                     |

| CLSDDA   | Clear to Send           | A response by the DCE to a Request<br>to Send signal from the SCLA.                                                                                                                                      |

| CRONDA   | Carrier Detect          | Indicates to the SCLA that the<br>basic carrier frequency of the<br>communication is present.                                                                                                            |

| DATRDA   | Receive Data            | The serial data line from the DCE to the SCLA.                                                                                                                                                           |

| DATXDA   | Transmit Data           | The serial data line from the SCLA to the DCE.                                                                                                                                                           |

| NSYNDA   | New Sync<br>(Clock)     | A request from the SCLA to the DCE<br>for a new sync signal. In a Di-<br>rect Connect application this sig-<br>nal is used as a clock for the re-<br>ceiver. See subsection 2.2.9.                       |

| RDYDSA   | Data Set Ready          | A signal from the DCE to the SCLA indicating it is ready to operate.                                                                                                                                     |

| RINGDA   | Ring Indicator          | Indicates that the line is in the<br>ringing condition and is trying to<br>get the attention of the SCLA.                                                                                                |

| RQSDDA   | Request to Send         | A request to transmit from the SCLA to the DCE.                                                                                                                                                          |

| SPSLDA   | Speed Select<br>(Clock) | A signal from the SCLA to the DCE<br>modem to select a specified rate<br>of transfer. In a Direct Connect<br>application this signal is used as<br>a clock for the transmitter. See<br>subsection 2.2.9. |

| TRDYDA   | Terminal Ready          | A signal from the SCLA to the DCE<br>indicating that the SCLA is ready<br>for operation.                                                                                                                 |

| ZGND     | Ground                  | Ground.                                                                                                                                                                                                  |

# 2.2.2 Subchannel Identification Code Lines

The subchannel identification code lines (see Figure 2-2) are used by the MLCP to identify the type of SCLA attached. The MLCP then uses this information to form a software identification word. The specific word assigned to the SCLA is hexadecimal 2158.

The SCLA utilizes interface lines LACOD1 through LACOD4 to input its portion of the subchannel identification code to the MLCP. Table 2-3 identifies the MLCP data bus bit positions to which the SCLA ID code is eventually transferred, the binary and hexadecimal configuration of the subchannel ID code, and the voltage levels to which the LACODx lines are hardwired in the SCLA to produce its portion of the ID (i.e., xx58). The 21xx is generated in the MLCP, and the entire ID word (2158) is transferred to the Megabus\* network when requested by software.

| MLCP Data Bus                             | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9   | 10  | 11  | 12  | 13 | 14 | 15 |

|-------------------------------------------|---|---|---|---|---|---|---|---|---|-----|-----|-----|-----|----|----|----|

| SCLA ID (LACOD1-4)                        |   |   |   |   |   |   |   |   |   | 1   | 2   | 3   | 4   |    |    |    |

| ID Word (Binary)                          | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1   | 0   | 1   | 1   | 0  | 0  | 0  |

| ID Word (Hex)                             |   | 2 | 2 |   |   |   | L |   |   |     | 5   |     |     |    | 8  |    |

| LACOD1-4 Hardwired<br>Connections In SCLA |   |   |   |   |   |   |   |   |   | +5V | GND | +5V | +5V |    |    |    |

Table 2-3 SCLA ID Code Generation

# 2.2.3 SCLA Control

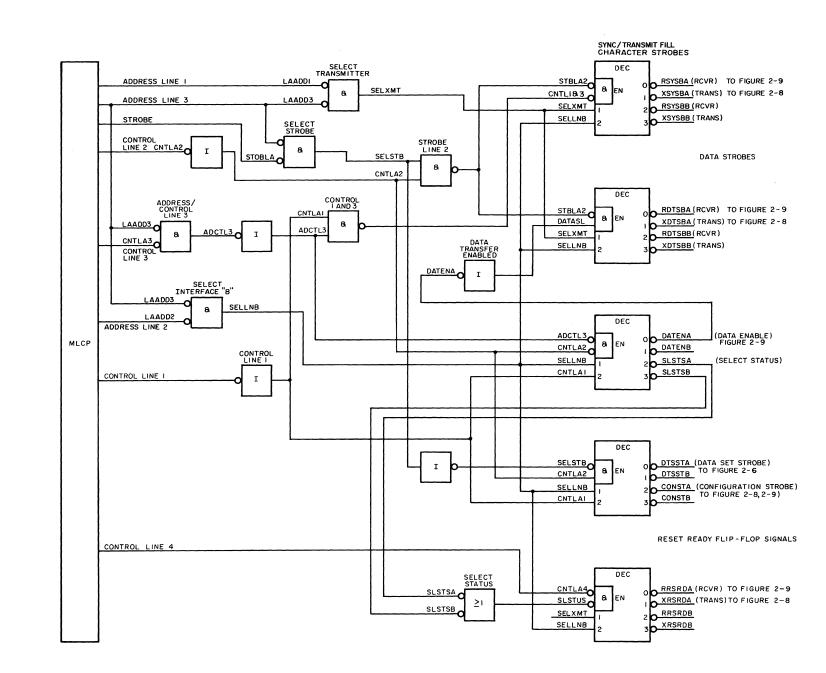

As shown in Figure 2-4, the SCLA control logic consists of five 2-line to 4-line decoders and numerous gates and inverters. The function of this logic is to develop control signals for performing operations in the hardware of the SCLA. All of these control signals are developed from the three address lines, four control lines, and the strobe signal sent out by the MLCP.

Table 2-4 is a quick reference table showing the general decoding of the address and control lines from the MLCP. Table 2-5 lists the specific use of the address and control information received from the MLCP in developing SCLA control signals.

\*Trademark of Honeywell Information Systems Inc.

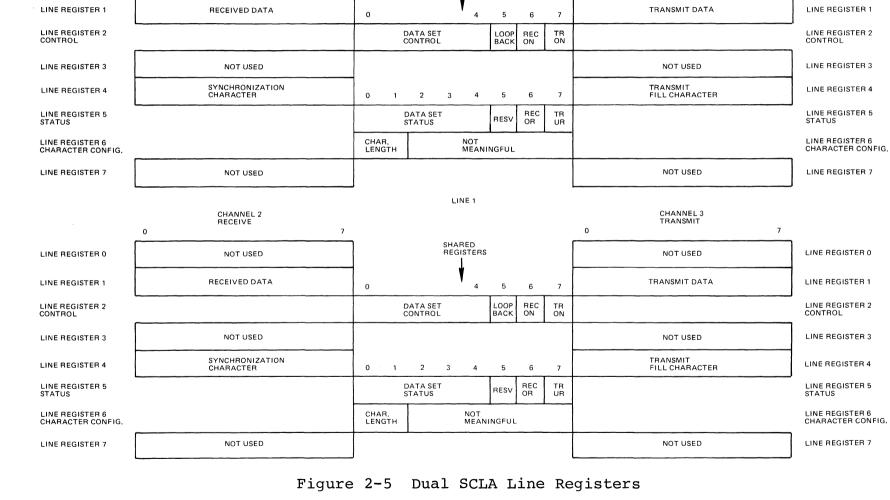

The programming interface to the SCLA is achieved through line registers located in the SCLA. These registers are illustrated in Figure 2-5.

Each communications line is serviced by a different set of line registers. Each channel (transmit or receive) of a line has a dedicated set of registers and also shares three registers with the other channel of the same line.

As shown in Figure 2-5, line registers 0, 3, and 7 are not used. Line registers 1, 4, and 6 are located in the Universal Synchronous Transmitter/Receiver (Figures 2-8 and 2-9) and are accessed through the specified input gates. Line register 2 contains data set control information and is shown in Figure 2-6. Line register 5 is the status register and is shown in Figure 2-10.

For a detailed description of the line register contents, refer to the MLCP Programmer's Reference Manual (Order Number AT97).

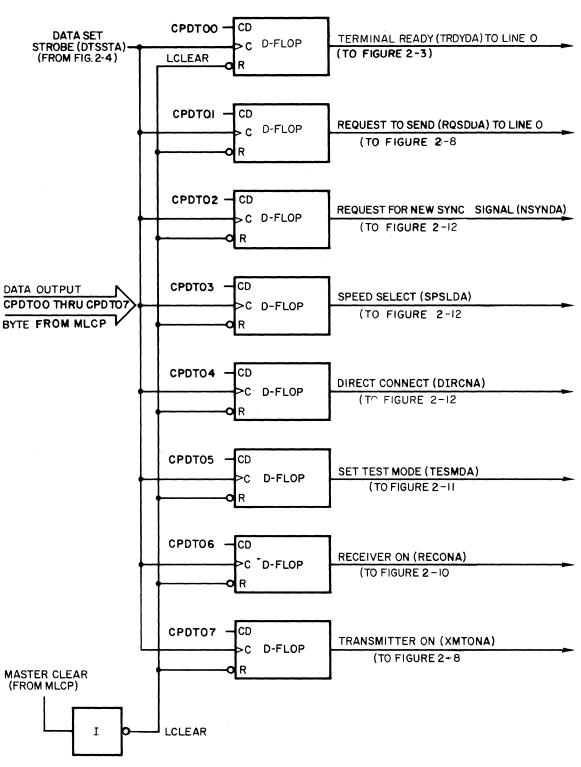

#### 2.2.4 Data Set Control

As shown in Figure 2-6 the data set control logic primarily consists of the data set control register, which is comprised of eight D-type flip-flops. The flip-flops are loaded by the data set strobe with information conveyed by the data information lines from the MLCP. Figure 2-6 shows the destination and the general usage of the output of each flip-flop. The NSYNDA and SPSLDA outputs have different functions in a normal line interface than in a direct connect interface, which is discussed in subsection 2.2.9. The function of the output signal from each flip-flop is as follows.

- 1. TRDYDA SCLA ready to the DCE. This is commonly called Terminal Ready in communications systems.

- 2. RQSDDA Request to send from the SCLA to the DCE.

- 3. NSYNDA When used with a line connector, this signal from the SCLA to the DCE requests a new sync signal from the DCE. When used in a direct connect application, this signal is used for the receiver clock. (See subsection 2.2.9.)

- 4. SPSLDA Sends a signal from the SCLA to the modem to select a specified rate of transfer. In a direct connect application, this signal is used for the transmitter clock. (See subsection 2.2.9.)

- 5. DIRCNA This signal is used to set the direct connect operational mode (See subsection 2.2.9.)

- 6. TESMDA Set test mode in the SCLA. (See subsection 2.2.8 for details.) Although interface B does not generate this signal, interface B is placed in the test mode by the hard-ware of interface A.

- 7. RECONA Enables the receiver in the SCLA. (See subsection 2.2.6 for details on use.)

- 8. XMTONA Enables the transmitter in the SCLA. (See subsection 2.2.5 for details on use.)

Figure 2-4 Dual SCLA Control, Address and Control Line Decoding

2-10

HONEYWELL PROPRIETARY AND CONFIDENTIAL

4

٠

(

.

.

Table 2-4 Address and Control Lines - General Decoding

|        | RESS                                                 |                |                                     |                                                                                                                                                                          |                                              |                                                   |                                                                                                                                                                                                                                                                |  |  |  |  |  |

|--------|------------------------------------------------------|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1      | 2                                                    | 3              |                                     |                                                                                                                                                                          |                                              | GENER                                             | AL FUNCTION AND COMMENT                                                                                                                                                                                                                                        |  |  |  |  |  |

| 1<br>0 | 0<br>0                                               | 1<br>1         |                                     | Select transmitter<br>Select receiver                                                                                                                                    |                                              |                                                   |                                                                                                                                                                                                                                                                |  |  |  |  |  |

| X<br>X | 1<br>0                                               | 1<br>1         |                                     | Select interface B<br>Select interface A                                                                                                                                 |                                              |                                                   |                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Х      | Х                                                    | 1              |                                     | Indicates to the SCLA that is has been selected<br>by the MLCP. The MLCP can control up to four<br>SCLAs but enables only the SCLA with address<br>line 3 set.           |                                              |                                                   |                                                                                                                                                                                                                                                                |  |  |  |  |  |

| х      | Х                                                    | <sub>0</sub> ) |                                     | Ine 3 set.<br>Indicates to the SCLA that it has not been<br>selected by the MLCP. Address line decoding is<br>not performed by the SCLA when address line 3<br>is reset. |                                              |                                                   |                                                                                                                                                                                                                                                                |  |  |  |  |  |

|        |                                                      |                |                                     |                                                                                                                                                                          |                                              |                                                   | fected by status of this                                                                                                                                                                                                                                       |  |  |  |  |  |

|        | b<br>LINE                                            | it wh          | nen d                               | eterm                                                                                                                                                                    | ining                                        | indi                                              | fected by status of this cated control function.                                                                                                                                                                                                               |  |  |  |  |  |

|        | b                                                    | oit wh         | nen d                               |                                                                                                                                                                          | ining                                        | indi                                              |                                                                                                                                                                                                                                                                |  |  |  |  |  |

|        | b<br>LINE<br>EGIST                                   | oit wh         | nen d<br>C                          | eterm<br>ONTRO                                                                                                                                                           | İning<br>L LIN                               | indi<br>E                                         | cated control function.                                                                                                                                                                                                                                        |  |  |  |  |  |

|        | b<br>LINE<br>EGIST<br>SELEC                          | oit wh         | nen d<br>C<br>1                     | eterm<br>ONTRO<br>2                                                                                                                                                      | ining<br>L LIN                               | indi<br>E<br>4                                    | cated control function.<br>GENERAL FUNCTION AND COMMENT                                                                                                                                                                                                        |  |  |  |  |  |

|        | b<br>LINE<br>REGIST<br>SELEC<br>4                    | oit wh         | nen d<br>C<br>1                     | eterm<br>ONTRO<br>2<br>0                                                                                                                                                 | ining<br>L LIN<br>3<br>0                     | indi<br>E<br>4<br>X                               | cated control function.<br>GENERAL FUNCTION AND COMMENT<br>Load sync character                                                                                                                                                                                 |  |  |  |  |  |

|        | b<br>LINE<br>EGIST<br>SELEC<br>4<br>2                | oit wh         | nen d<br>C<br>1<br>1<br>0           | eterm<br>ONTRO<br>2<br>0<br>1                                                                                                                                            | ining<br>L LIN<br>3<br>0<br>0                | indi<br>E<br>4<br>X<br>X                          | Cated control function.<br>GENERAL FUNCTION AND COMMENT<br>Load sync character<br>Load data set register<br>Load receiver/transmitter with                                                                                                                     |  |  |  |  |  |

|        | b<br>LINE<br>EGIST<br>SELEC<br>4<br>2<br>6           | oit wh         | nen d<br>C<br>1<br>0<br>1           | eterm<br>ONTRO<br>2<br>0<br>1<br>1                                                                                                                                       | ining<br>L LIN<br>3<br>0<br>0<br>0           | indi<br>E<br>4<br>X<br>X<br>X<br>X                | GENERAL FUNCTION AND COMMENT<br>Load sync character<br>Load data set register<br>Load receiver/transmitter with<br>configuration information<br>Output/input data to/from                                                                                      |  |  |  |  |  |

|        | b<br>LINE<br>EGIST<br>SELEC<br>4<br>2<br>6<br>1      | oit wh         | nen d<br>C<br>1<br>0<br>1<br>0      | eterm<br>ONTRO<br>2<br>0<br>1<br>1<br>0                                                                                                                                  | L LIN<br>3<br>0<br>0<br>0<br>1               | indi<br>E<br>4<br>X<br>X<br>X<br>X<br>X           | GENERAL FUNCTION AND COMMENT<br>Load sync character<br>Load data set register<br>Load receiver/transmitter with<br>configuration information<br>Output/input data to/from<br>transmitter or receiver                                                           |  |  |  |  |  |

|        | b<br>LINE<br>EGIST<br>SELEC<br>4<br>2<br>6<br>1<br>5 | oit wh         | nen d<br>C<br>1<br>0<br>1<br>0<br>1 | eterm<br>ONTRO<br>2<br>0<br>1<br>1<br>0<br>0                                                                                                                             | ining<br>L LIN<br>3<br>0<br>0<br>0<br>1<br>1 | indi<br>E<br>4<br>X<br>X<br>X<br>X<br>X<br>X<br>X | GENERAL FUNCTION AND COMMENT<br>Load sync character<br>Load data set register<br>Load receiver/transmitter with<br>configuration information<br>Output/input data to/from<br>transmitter or receiver<br>Input status<br>Reset data request ready flip-<br>flop |  |  |  |  |  |

2-11

0

|                    | CONTROL | ADDRESS |                      |                      |                                                                  |

|--------------------|---------|---------|----------------------|----------------------|------------------------------------------------------------------|

| LINE               | LINES   | LINES   |                      |                      | TUNCTION OF DECODED                                              |

| REGISTER<br>SELECT | 1234    | 123     | OUTPUT OF<br>DECODER | ADAPTER<br>INTERFACE | FUNCTION OF DECODED<br>CONTROL SIGNAL                            |

| 6                  | 1 1 0 X | X 0 1   | CONSTA               | A                    | Load/receiver/transmitter<br>with configuration infor-<br>mation |

| 6                  | 1 1 0 X | X 1 1   | CONSTB               | В                    | Load/receiver/transmitter<br>with configuration infor-<br>mation |

| 1                  | 0 0 1 X | 101     | XDTSBA               | А                    | Load transmitter data<br>buffer                                  |

|                    | 0 0 1 X | 111     | XDTSBB               | В                    | Load transmitter data<br>buffer                                  |

|                    | 0 0 1 X | 001     | DATENA               | A                    | Enable input from re-<br>ceiver to MLCP                          |

|                    | 0 0 1 X | 001     | RDTSBA               | А                    | Input receiver data to<br>MLCP                                   |

|                    | 0 0 1 X | 011     | DATENB               | В                    | Enable input from re-<br>ceiver to MLCP                          |

| i                  | 0 0 1 X | 0 1 1   | RDTSBB               | В                    | Input receiver data to<br>MLCP                                   |

| 4                  | 100X    | 001     | RSYSBA               | A                    | Load receiver sync char-<br>acter                                |

| 4                  | 100X    | 011     | RSYSBB               | В                    | Load receiver sync char-<br>acter                                |

| 2                  | 0 1 0 X | X 0 1   | DTSSTA               | A                    | Load data set control<br>register                                |

| 2                  | 0 1 0 X | X 1 1   | DTSSTB               | В                    | Load data set control<br>register                                |

| 5                  | 101X    | X 0 1   | SLSTSA               | A                    | Enable and select status<br>multiplexer for this in-<br>terface  |

|                    | 101X    | X 1 1   | SLSTSB               | В                    | Enable and select status<br>multiplexer for this in-<br>terface  |

|                    | 1011    | 001     | RRSRDA               | A                    | Reset receiver ready<br>flip-flop                                |

|                    | 1011    | 101     | XRSRDA               | A                    | Reset transmitter ready flip-flop                                |

|                    | 1011    | 0 1 1   | RRSRDB               | В                    | Reset receiver ready<br>flip-flop                                |

| 5                  | 1011    | 111     | XRSRDB               | В                    | Reset transmitter ready flip-flop                                |

| 4                  | 1 0 0 X | 101     | XSYSBA               | A                    | Load transmitter fill character                                  |

| 4                  | 1 0 0 X | 111     | XSYSBB               | В                    | Load transmitter fill character                                  |

Table 2-5 Decoding-Control and Address Lines

LINE 0

SHARED REGISTERS CHANNEL 1

NOT USED

7

LINE REGISTER 0

TRANSMIT

0

CHANNEL 0

NOT USED

7

RECEIVE

0

LINE REGISTER 0

DATA SET CONTROL REGISTER

Figure 2-6 Data Set Control Logic

2-14

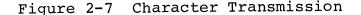

#### 2.2.5 Data Output

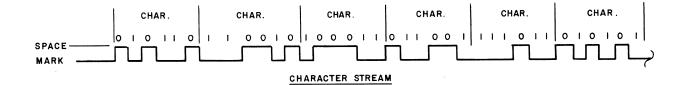

The SCLA sends out information to the DCE in a stream of 5-, 6-, 7-, or 8-bit communication-type characters in a continuous block. (See Figure 2-7 for an example of a stream of 6-bit characters.) A character in the stream can be a transmit fill character or a data character. Transmit fill characters are primarily used to notify the receiving equipment of the start of a block of data characters. Transmit fill characters are also used to maintain a continuous stream when data characters are not available during the output operation. Parity generation is inhibited in the SCLA transmitter, but transmitted characters may include a parity bit which is embedded in the byte received from the MLCP.

As shown in Figure 2-8, when the MLCP starts an output operation, it first configures the XMTR/RCVR configuration register to handle either 5-, 6-, 7-, or 8-bit characters. To effect the desired configuration, CPDT00 and CPDT01 are set as shown in Table 2-6 and then strobed into the XMTR/RCVR configuration register by signal CONSTA (see Table 2-5 and Figure 2-4). Note that a 5V input inhibits parity generation by the transmitter.

Next, a transmit fill configuration character must be entered into the transmitter. This is accomplished by the channel program when it sets data lines CPDT00 through CPDT07 with the designated transmit fill character and strobes it into the transmitter with signal XSYSBA (see Table 2-5 and Figure 2-4).

After the configuration information and the configuration transmit fill character are entered into the transmitter, an output operation is started when the channel program turns on the transmitter (XMTONA) and sets Request to Send (RQSDDA). This allows serial data to be sent out to the line as shown in Figure 2-7. The transmitter then requests a data byte to load its data register (RDYXMA). Then if both the Clear to Send and Request to Send are true, the CJ input to the transmitter ready flip-flop is enabled. Then at the next ready flip-flop strobe from the MLCP, the flip-flop sets and sends a ready for a Transmit Data Byte (RDYFXA) to the MLCP. The MLCP then responds by an output or send instruction which strobes a data byte into the transmitter data register (XDTSBA) and resets the transmitter Request (RDYXMA). If the transmitter does not receive a byte from the MLCP in time to maintain the continuous output data stream, it sends out a transmit fill character. An underrun error signal is also generated at this time which is sent to the input multiplexer as a status input (see subsection 2.2.7). When the MLCP has completed its channel program (Wait instruction), it causes an XRSRDA signal to be issued, which resets the transmitter ready flip-flop (RDYFXA).

The voltage level of the bits between the SCLA transmitter and the DCE interface is changed from the TTL level of 0V and +5V to +12V and -12V by the EIA logic. (See Figure 2-7.)

During an output operation with a line, the clock signal (CLKXMA) required to operate the transmitter is received directly from the DCE. However, in the test mode or when using the direct connect feature, the required clock signal originates in the MLCP. The data line to the DCE is placed in a marking condition when in the test mode.

When the channel program in the MLCP desires to conclude the operation, it turns the transmitter off (XMTONA). This causes the data line to the DCE to go into the Mark state (see Figure 2-7).

2-16

Figure 2-8 Data Output to Data Communications Equipment

| Set    | ting   | Word Size |

|--------|--------|-----------|

| CPDT00 | CPDT01 | (Bits)    |

| 0      | 0      | 5         |

| 0      | 1      | 6         |

| 1      | 0      | 7         |

| 1      | 1      | 8         |

# Table 2-6 Transmitter/Receiver Word Size Configuration

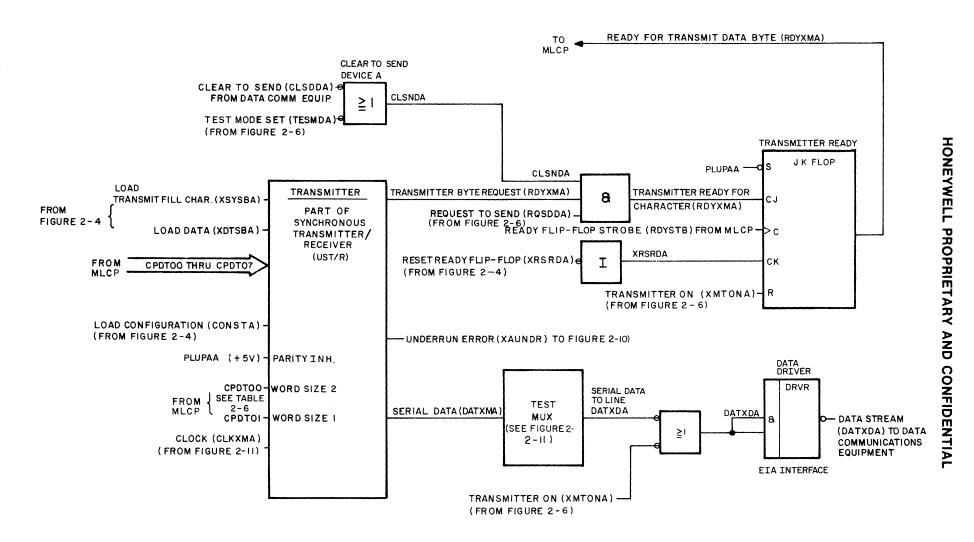

### 2.2.6 Data Input

The adapter receives information from the DCE in a stream of 5-, 6-, 7-, or 8-bit communication-type characters in a continuous stream. (See Figure 2-7 for an example of a stream of 6-bit characters.) The stream may consist of sync characters or data characters. After the receiver in the SCLA recognizes a sync character in an incoming message, it treats that character and all the following characters in the message as data characters. The receiver makes no parity checks on incoming information; however, characters may have parity bits which are transparent to the receiver but are checked in the MLCP. The receiver generates an error (overrun) signal if it has two data bytes ready before one is transferred into the MLCP.

As shown in Figure 2-9, when the channel program starts an input operation it first configures the XMTR/RCVR configuration register to handle either 5-, 6-, 7-, or 8-bit characters in the incoming message. To effect the desired configuration, CPDT00 and CPDT01 are set as shown in Table 2-6 and strobed into the XMTR/RCVR configuration register by CONSTA. (See Table 2-5 and Figure 2-4.) Note that a +5V input always inhibits parity checking by the receiver.

2-18

Next, a sync character must be entered into the transmitter/receiver. This is accomplished by the channel program when it sets data lines CPDT00 through CPDT07 with the designated sync character and strobes it into the receiver with signal RSYSBA. (See Table 2-5 and Figure 2-4.)

After the configuration information and the sync character are entered into the receiver, an input operation is started when the MLCP turns on the receiver (RECONA). This sets the receiver in a search mode. In this mode the incoming data bit stream is examined bit by bit until a sync character is found. When the sync character is found, the receiver sends the sync character to a data-holding register within the transmitter/receiver for transfer to the MLCP. At this time the receiver also enables the CJ input to the receiver ready flip-flop (RDYRCA). Then at the next ready flip-flop strobe (RDYSTB) from the MLCP, signal RDYFRA notifies the MLCP that the receiver has a byte ready for transfer. When the receiver identifies the first sync character in the data stream, it sets the receiver in the character mode. In this mode the bits of the incoming data stream are assembled into characters, of the size specified by the configuration register, and sent to the MLCP.

To input a byte from the receiver, the MLCP first connects the data-holding register of the receiver to the MLCP by causing a data enable (DATENA) signal to be issued (see Figure 2-4 and Table 2-5). Then the MLCP transfers the byte with a Received Data Strobe (RDTSBA), input or receive instruction which resets Receiver Request (RDYRCA). Then the receiver ready flip-flop is reset by the MLCP (Wait instruction), causing an RRSRDA signal to be issued. Successive bytes are then transferred as described above from the DCE to the MLCP until the input operation is completed.

During a data input operation, if the receiver has two bytes ready for transfer before one is taken by the MLCP, an overrun (RAOVRN) signal is generated. This error signal is sent to the input status multiplexer and remains on until the next character is received from the DCE.

Between the DCE interface and the SCLA receiver, the level of the bits in the data stream is changed from the EIA level of +3 to +25V, and -3 to -25 to the adapter level of 0V to +5V by the EIA logic.

The channel program stops an input operation by resetting the receiver on (RECONA) signal. This holds the receiver ready flip-flop reset. Note that during an input operation with a line, the clock signal (CLKREA) required to operate the receiver is received directly from the DCE. However, in the test mode or when using the direct connect feature, the required clock signal originates in the MLCP.

Figure 2-9 Data Input to MLCP from Data Communications Equipment

HONEYWELL PROPRIETARY AND CONFIDENTIAL

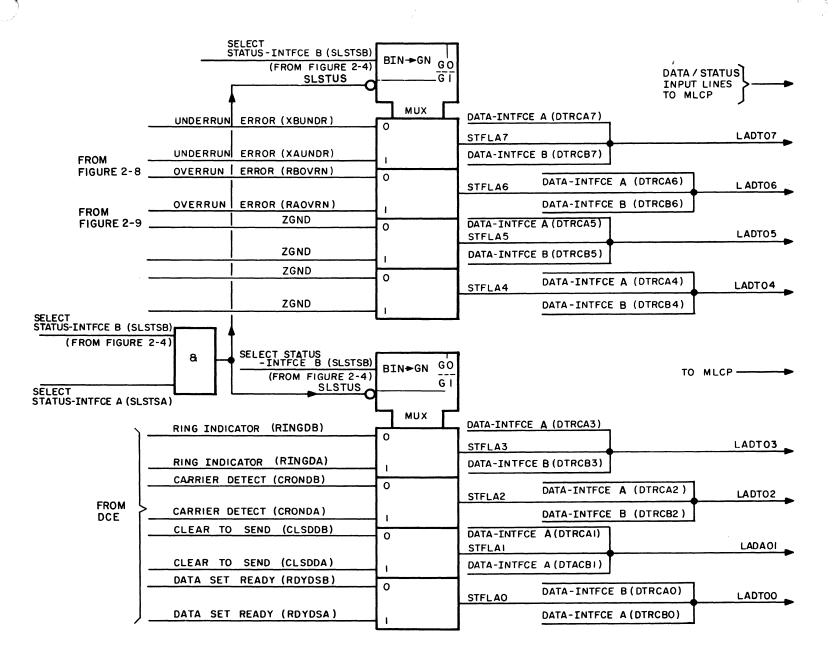

#### 2.2.7 Input Status Multiplexer

The input status multiplexer (Figure 2-10) provides a means of sending both error status in the SCLA and status and control information from the DCE to the MLCP. The information sent from the multiplexer to the MLCP may originate in either interface A or interface B or in their respective DCE, depending upon the decoding of the control and address lines from the MLCP. When interface B has not been selected (SLSTSB), the multiplexer assumes that interface A and its associated DCE has been selected.

The multiplexer requires an enable signal because it is a tristate device. When not enabled, all the outputs of the multiplexer are at infinite impedance (floating), thereby disconnecting all logical inputs from the multiplexer into the MLCP. As shown in Figure 2-10, the multiplexer is enabled when the Select Status signal for interface A or B is true.

Each output bit of the multiplexer is hard-wired to the corresponding data input bit from both interface A and interface B prior to being sent to the MLCP. All data input and status bytes are sent to the MLCP via the LADT00 through LADT07 connections. Table 2-7 lists the source and function of all inputs into the status input multiplexer.

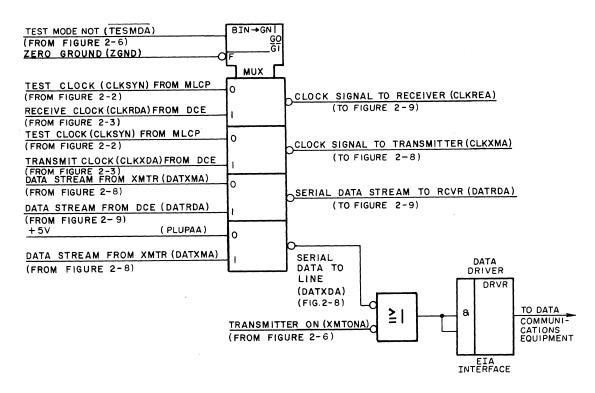

### 2.2.8 Test Multiplexer

A test multiplexer (Figure 2-11) in each interface provides the interface of the SCLA with a wraparound feature. This feature allows serial data out of the transmitter to be sent directly back to the receiver. Diagnostic software uses the wraparound feature to check the operation of the transmitter and receiver by comparing a data byte sent out by the MLCP to the byte received back. Operation with the DCE is precluded when the wraparound logic is enabled. Refer to Appendix A for supplemental information pertaining to wraparound.

As shown in Figure 2-11, a Zero (ground) is placed on the enabling input of the multiplexer. This, in effect, negates the tristate feature of the multiplexer so that the outputs are always logically connected to either the selected Zero or One input. (Note that Figure 2-11 shows the multiplexer for interface A. The multiplexer for interface B is connected in a similar manner, but the Set Test Mode signal (TESMDA) is generated in the logic of interface A only.)

When operating on-line (test mode not set), the logic One inputs to the multiplexer are connected to the corresponding output. This makes the following normal operating connections within the multiplexers.

| INPUT                                                                                                | OUTPUT                                                                                                               |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| MULTIPLE                                                                                             | XER – INTERFACE A                                                                                                    |

| Receive clock from DCE<br>Transmit clock from DCE<br>Line - Interface A<br>Transmitter - Interface A | Clock signal to Rcvr - Interface A<br>Clock signal to Xmtr - Interface A<br>Rcvr - Interface A<br>Line - Interface A |

| MULTIPLE                                                                                             | XER – INTERFACE B                                                                                                    |

| Receive clock from DCE<br>Transmit clock from DCE<br>Line - Interface B<br>Transmitter - Interface B | Clock signal to Rcvr - Interface B<br>Clock signal to Xmtr - Interface B<br>Rcvr - Interface B<br>Line - Interface B |

When the test mode is set, the Zero inputs to the multiplexers are connected to the corresponding output. This makes the following connections within the multiplexers.

| INPUT                                                                                               | OUTPUT                                                                                                                              |  |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| MULTIPLEXER - INTERFACE A                                                                           |                                                                                                                                     |  |

| Test clock from MLCP<br>Test clock from MLCP<br>Data stream from Xmtr - Interface A<br>PLUPPA (+5V) | Clock signal to Rcvr - Interface A<br>Clock signal to Xmtr - Interface A<br>Data stream to Rcvr - Interface A<br>Line - Interface A |  |

| MULTIPLEXER - INTERFACE B                                                                           |                                                                                                                                     |  |

| Test clock from MLCP<br>Test clock from MLCP<br>Data stream from Xmtr - Interface B<br>PLUPPA (+5V) | Clock signal to Rcvr - Interface B<br>Clock signal to Xmtr - Interface B<br>Data stream to Rcvr - Interface B<br>Line - Interface B |  |

As shown in Figure 2-11, a Mark <u>signal</u> is always sent out to the line if the transmitter is not on (XMTONA) or the test mode is set. In the test mode the PLUPPA (+5V) input to the multiplexer causes DATXDA to go low, which in turn causes a low (Mark) signal to go out to the DCE.

Figure 2-10 Input Status Multiplexer Logic

HONEYWELL PROPRIETARY AND CONFIDENTIAL

C

| INPUT<br>SIGNAL  | SOURCE                                                             | COMMENT                                                                                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XBUNDR<br>XAUNDR | Adapter transmitter-interface B<br>Adapter transmitter-interface A | Indicates that the transmitter<br>has not received data bytes<br>from the MLCP fast enough to<br>maintain data stream (underrun<br>error). The transmitter has<br>sent a transmit fill character<br>to maintain the data output<br>stream. |

| RBOVRN<br>RAOVRN | Adapter receiver-interface B<br>Adapter receiver-interface A       | Indicates that the receiver<br>had two data bytes ready be-<br>fore one was transferred to<br>the MLCP (overrun error).                                                                                                                    |

| RINGDB<br>RINGDA | DCE of interface B<br>DCE of interface A                           | The associated line is ringing<br>and is trying to get the at-<br>tention of the MLCP.                                                                                                                                                     |

| CRONDB<br>CRONDA | DCE of interface B<br>DCE of interface A                           | Indicates that the basic<br>carrier frequency of the as-<br>sociated communication line is<br>present.                                                                                                                                     |

| CLSDDB<br>CLSDDA | DCE of interface B<br>DCE of interface A                           | A response by the associated<br>DCE to a request-to-send sig-<br>nal from the SCLA.                                                                                                                                                        |

| RDYDSB<br>RDYDSA | DCE of interface B<br>DCE of interface A                           | A signal from the associated<br>DCE indicating that it is<br>ready to operate.                                                                                                                                                             |

Table 2-7 Inputs to Input Status Multiplexer

Figure 2-11 Test Multiplexer Logic

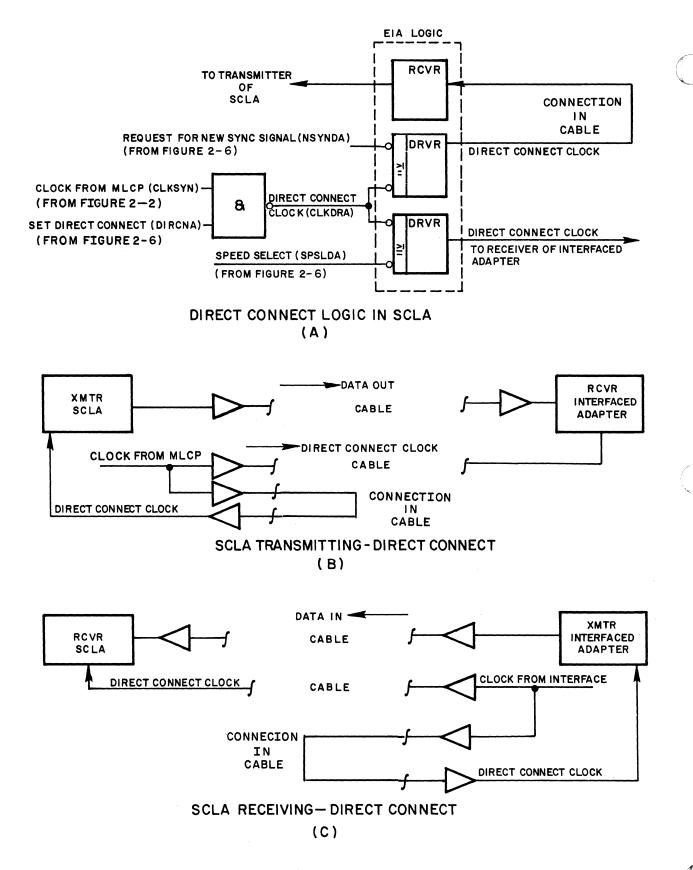

### 2.2.9 Direct Connect Logic

The additional logic associated with the direct connect feature is shown in Figure 2-12 (A). This logic is installed in both interface A and interface B of the SCLA at the time of delivery. However, a different cable out of the SCLA is required when using a direct connection rather than a line connection.