# Honeywell

THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN IS PROPRIETARY TO AND THE EXCLUSIVE PROPERTY OF HONEYWELL INFORMATION SYSTEMS INC. THIS DOCUMENT AND THE INFORMA-TION CONTAINED THEREIN IS FOR THE USE OF HONEYWELL AUTHO-RIZED RECIPIENTS ONLY FOR THE MAINTENANCE AND OPERATION OF HONEYWELL PRODUCTS AND MUST BE MAINTAINED IN STRICTEST CONFIDENCE. IT MUST NOT BE REPRODUCED IN WHOLE OR IN PART. THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN SHALL NOT BE DISCLOSED TO ANY OTHER PARTY WITHOUT THE PRIOR WRIT-TEN CONSENT OF HONEYWELL.

## SERIES 60 (LEVEL 6)

## TYPE DCM9106 HIGH-LEVEL DATA LINK CONTROL ADAPTER MANUAL

## Honeywell

THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN IS PROPRIETARY TO AND THE EXCLUSIVE PROPERTY OF HONEYWELL INFORMATION SYSTEMS INC. THIS DOCUMENT AND THE INFORMA-TION CONTAINED THEREIN IS FOR THE USE OF HONEYWELL AUTHO-RIZED RECIPIENTS ONLY FOR THE MAINTENANCE AND OPERATION OF HONEYWELL PRODUCTS AND MUST BE MAINTAINED IN STRICTEST CONFIDENCE. IT MUST NOT BE REPRODUCED IN WHOLE OR IN PART. THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN SHALL NOT BE DISCLOSED TO ANY OTHER PARTY WITHOUT THE PRIOR WRIT-TEN CONSENT OF HONEYWELL.

SERIES 60 (LEVEL 6)

## TYPE DCM9106 HIGH-LEVEL DATA LINK CONTROL ADAPTER MANUAL

Doc. No. 71010977-200 Order No. FN12, Rev. 1

| REVISION    | DATE         | AUTHORITY              | AFFECTED PAGES     |

|-------------|--------------|------------------------|--------------------|

| -100        | Jan. 1977    | Interim Issue          |                    |

| -200        | June 1977    | BLC061762<br>BLC061866 | Entire Manual      |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        | · .                |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

|             |              |                        |                    |

| ardware Pub | Lications. M | TO, Billerica, MA      | 01821 File No.: 45 |

RECORD OF REVISIONS

Printed in the United States of America All rights reserved

977/FN12

đ

#### CONTENTS

.

| Section |                                       |           |                                | Page   |  |  |  |

|---------|---------------------------------------|-----------|--------------------------------|--------|--|--|--|

| I       | INTROD                                | UCTION    |                                | 1-1    |  |  |  |

|         | 1.1 Scope and Purpose of the Document |           |                                |        |  |  |  |

|         | 1.2                                   |           | General Description            | 1-1    |  |  |  |

|         | 1.3                                   | Functiona | al Description                 | 1-3    |  |  |  |

|         |                                       | 1.3.1     | Multiline Communications       |        |  |  |  |

|         |                                       |           | Controller                     | 1-3    |  |  |  |

|         |                                       | 1.3.2     | HDLC Adapter                   | 1-3    |  |  |  |

|         |                                       | 1.3.3     | Attachable Communication       |        |  |  |  |

|         |                                       |           | Equipment                      | 1-4    |  |  |  |

|         | 1.4                                   | Operation | nal Summary                    | 1-5    |  |  |  |

|         | 1.5                                   | Reference | e Documents                    | 1-6    |  |  |  |

| II      | THEORY                                | OF OPERA  | FION                           | 2-1    |  |  |  |

|         | 2.1                                   | Software  |                                | 2-1    |  |  |  |

|         | 2.2                                   | Firmware  |                                | 2-3    |  |  |  |

|         | 2.3                                   | Hardware  |                                | 2-3    |  |  |  |

|         |                                       | 2.3.1     | HDLC/MLC Interface             | 2-4    |  |  |  |

|         |                                       | 2.3.2     | HDLC/DCE Interface             | 2-4    |  |  |  |

|         |                                       | 2.3.3     | MLC Control Logic              | 2-8    |  |  |  |

|         |                                       | 2.3.4     | Trans it Data/Control Path     | 2-9    |  |  |  |

|         |                                       | 2.3.5     | Receive Data/Control Path      | 2-11   |  |  |  |

|         |                                       | 2.3.6     | Microprogram Control Memory    |        |  |  |  |

|         |                                       |           | Logic                          | 2-12   |  |  |  |

|         |                                       | 2.3.7     | Microprocessor                 | 2-14   |  |  |  |

|         | 2.4                                   |           | cucture/Operational            |        |  |  |  |

|         |                                       |           | cistics/Operations             | 2-15   |  |  |  |

|         |                                       | 2.4.1     | Frame Structure                | 2-15   |  |  |  |

|         |                                       | 2.4.2     | Operational Characteristics    | 2-17   |  |  |  |

|         |                                       | 2.4.3     | Operations                     | 2-19   |  |  |  |

|         | 2.5                                   |           | late Hardware Description      | 2-25   |  |  |  |

|         |                                       | 2.5.1     | Microprocessor Logic           | 2-25   |  |  |  |

|         |                                       | 2.5.2     | MLC Command Decode and Control |        |  |  |  |

|         |                                       |           | Logic                          | 2-30   |  |  |  |

|         |                                       | 2.5.3     | Microprogram Control Memory    |        |  |  |  |

|         |                                       |           | Logic                          | 2-33   |  |  |  |

|         |                                       | 2.5.4     | Transmit_Logic                 | · 2-35 |  |  |  |

|         |                                       | 2.5.5     | Receive Logic                  | 2-38   |  |  |  |

| III     |                                       |           | FION - CYCLE FLOW              | 3-1    |  |  |  |

|         | 3.1                                   | Adapter H |                                | 3-1    |  |  |  |

|         | 3.2                                   | Internal  |                                | 3-1    |  |  |  |

|         | 3.3                                   | External  | RAM                            | 3-5    |  |  |  |

## iii

## CONTENTS

| Section |     |            |                                                                                                                  |                                  | Page  |

|---------|-----|------------|------------------------------------------------------------------------------------------------------------------|----------------------------------|-------|

|         | 3.4 | Firmware   | Commands ar                                                                                                      | nd Microinstructions             | 3-8   |

|         |     | 3.4.1      | Subcommand                                                                                                       |                                  | 3-8   |

|         |     | 3.4.2      |                                                                                                                  | rnal RAM Command                 | 3-8   |

|         |     | 3.4.3      |                                                                                                                  | it Buffer Command                | 3-8   |

|         |     | 3.4.4      |                                                                                                                  | odify Next Command               | 3-8   |

|         | •   | 3.4.5      |                                                                                                                  | coprocessor Command              | 3-11  |

|         |     | 3.4.6      |                                                                                                                  | Buffer Command                   | 3-11  |

|         |     | 3.4.7      |                                                                                                                  | nal RAM Command                  | 3-12  |

|         |     | 3.4.8      | Branch Com                                                                                                       |                                  | 3-12  |

|         |     | 3.4.9      | and the second | Subcommand Command               | 3-12  |

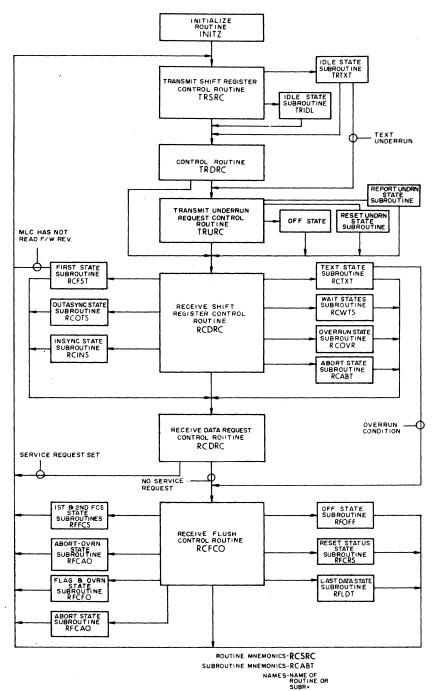

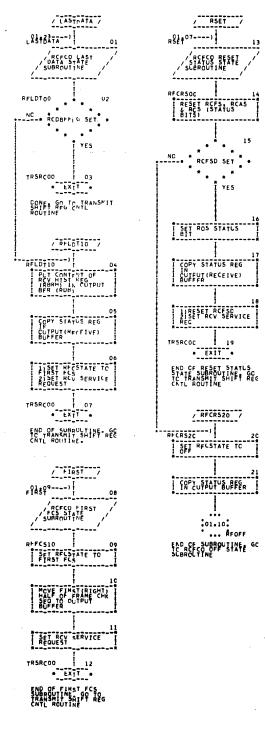

|         | 3.5 |            | Cycle Flow                                                                                                       |                                  | 3-16  |

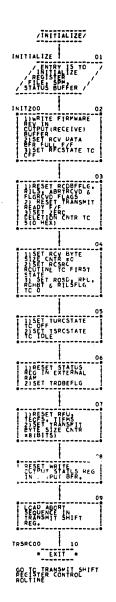

|         |     | 3.5.1      | Initialize                                                                                                       | Routine                          | 3-18  |

|         |     | 3.5.2      |                                                                                                                  | nift Register Control            | 5 10  |

|         |     | 3.3.2      | Routine                                                                                                          | tte vedigeret geweret            | 3-20  |

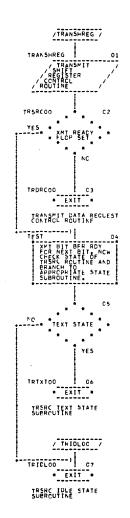

|         |     |            | 3.5.2.1                                                                                                          | TRSRC Enter Sequence             | 3-20  |

|         |     |            | 3.5.2.2                                                                                                          | TRSRC IDLE State                 | 5 20  |

|         |     |            |                                                                                                                  | Subroutine                       | 3-20  |

|         |     |            | 3.5.2.3                                                                                                          | TRSRC TEXT State                 | J~20  |

|         |     |            | J. J. Z. J                                                                                                       | Subroutine                       | 3-21  |

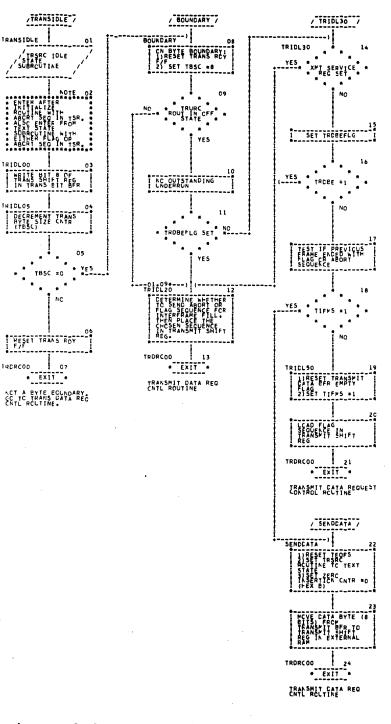

|         |     | 3.5.3      | Tranemit Da                                                                                                      | ata Request Control              | J-71  |

|         |     | 2.3.2      | Routine                                                                                                          | ita Request control              | 3-22  |

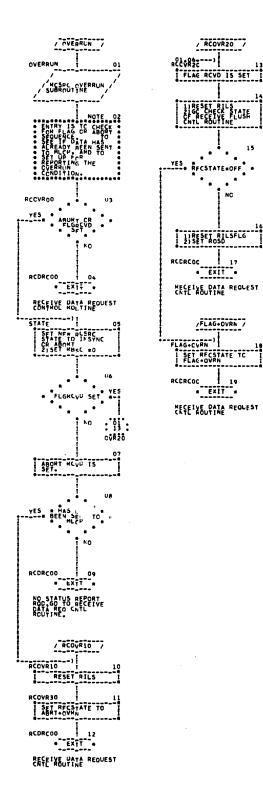

|         |     | 3.5.4      |                                                                                                                  | nderrun Report Control           | 5-22  |

|         |     | 7.7.4      | Routine                                                                                                          | iderian vebore concrot           | 3-22  |

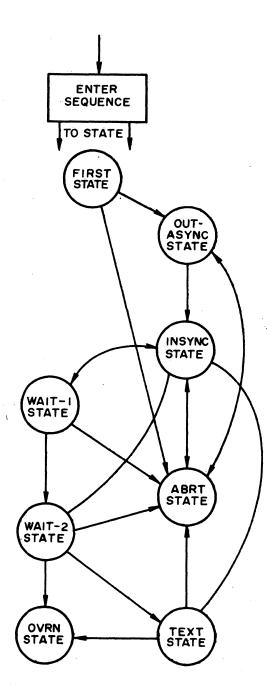

|         |     | 3.5.5      |                                                                                                                  | ift Register Control             | J 2 2 |

|         |     | 2.5.5.5    | Routine                                                                                                          | tit Register control             | 3-23  |

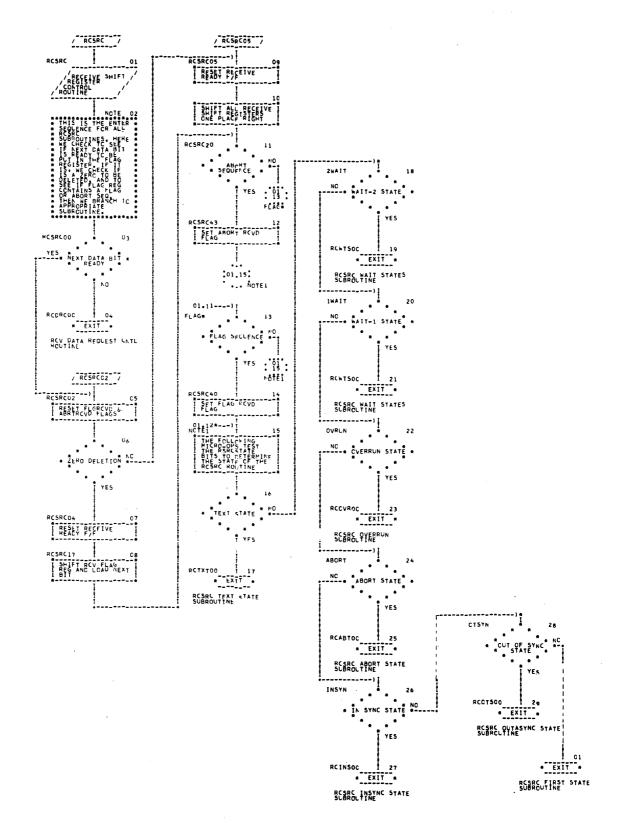

|         |     |            | 3.5.5.1                                                                                                          | RCSRC Routine Enter              | 3-23  |

|         |     |            | 2.2.2.I                                                                                                          |                                  | 3-25  |

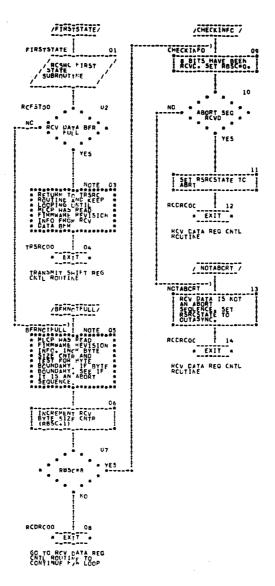

|         |     |            | 3.5.5.2                                                                                                          | Sequence<br>RCSRC FIRST State    | 3-23  |

|         |     |            | 3.3.3.2                                                                                                          | Subroutine                       | 3-25  |

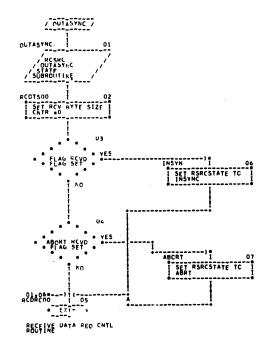

|         |     |            | 3.5.5.3                                                                                                          | RCSRC OUTASYNC State             | 3-23  |

|         |     |            | 2.2.2.2                                                                                                          | Subroutine                       | 3-26  |

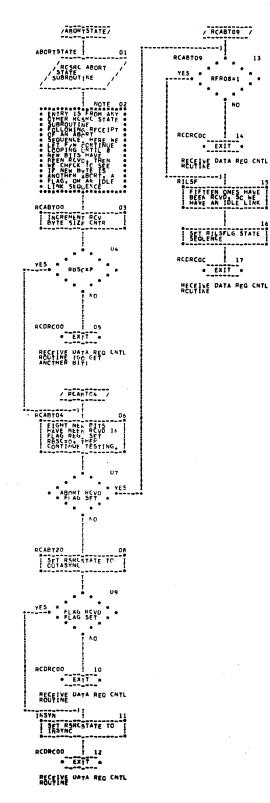

|         |     |            | 3.5.5.4                                                                                                          | RCSRC ABRT State                 | 5-20  |

|         |     |            | 2.2.2.4                                                                                                          | Subroutine                       | 3-26  |

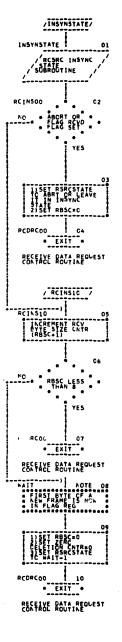

|         |     |            | 3.5.5.5                                                                                                          | RCSRC INSYNC State               | 5-20  |

|         |     |            | 3.5.5.5                                                                                                          |                                  | 3-27  |

|         |     |            | 3.5.5.6                                                                                                          | Subroutine<br>RCSRC WAIT-1 State | 5-27  |

|         |     |            | 2.2.2.0                                                                                                          | Subroutine                       | 3-27  |

|         |     |            | 3.5.5.7                                                                                                          | RCSRC WAIT-2 State               | 5-21  |

|         |     |            | J. J. J. J.                                                                                                      | Subroutine                       | 3-28  |

|         |     |            | 3.5.5.8                                                                                                          | RCSRC TEXT State                 | 5-20  |

|         |     |            | 3.5.5.0                                                                                                          | Subroutine                       | 3-29  |

|         |     |            | 3.5.5.9                                                                                                          | RCSRC OVRN State                 | 5-29  |

|         |     |            | 2.2.2.2                                                                                                          | Subroutine                       | 3-30  |

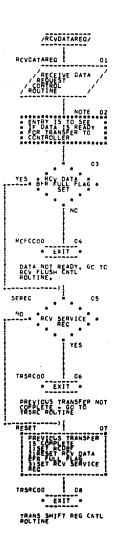

|         |     | 3.5.6      | Bogoivo Dat                                                                                                      | a Request Control                | 2-20  |

|         |     | J. J. J. D | · · · · · · · · · · · · · · · · · · ·                                                                            | La request control               | 3-31  |

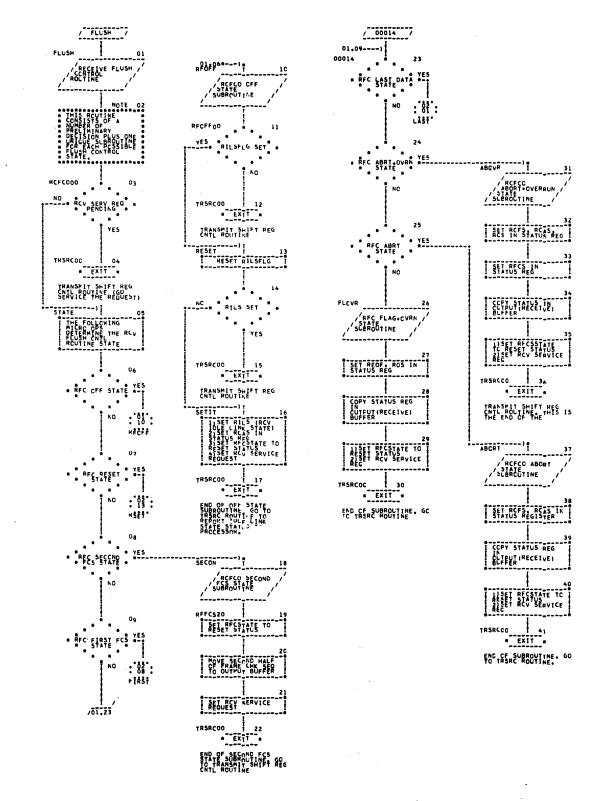

|         |     | 2 5 7      | Routine<br>Roceine Eli                                                                                           | ab Control Ponting               | 3-31  |

|         |     | 3.5.7      |                                                                                                                  | ish Control Routine              | 3-31  |

|         |     |            | 3.5.7.1                                                                                                          | RCFCO Enter Sequence             | 3-31  |

| :       |     |            | 3.5.7.2                                                                                                          | RCFCO OFF State Sequence         | 2-2T  |

|         |     |            | 3.5.7.3                                                                                                          | RCFCO Last Data State            | 3-32  |

|         |     |            |                                                                                                                  | Subroutine                       | 3-34  |

## HONEYWELL PROPRIETARY AND CONFIDENTIAL

iv

## CONTENTS

Section

| Section    |                        |                                      | Page |

|------------|------------------------|--------------------------------------|------|

| •          | 3.5.7.4                | RCFCO First FCS State<br>Subroutine  | 3-32 |

|            | 3.5.7.5                | RCFCO Second FCS State<br>Subroutine | 3-33 |

|            | 3.5.7.6                | RCFCO Reset Status                   |      |

|            |                        | State Subroutine                     | 3-33 |

|            | 3.5.7.7                | RCFCO ABRT&OVRN State                |      |

|            |                        | Subroutine                           | 3-34 |

|            | 3.5.7.8                | RCFCO FLG&OVRN State                 |      |

|            |                        | Subroutine                           | 3-34 |

|            | 3.5.7.9                | RCFCO Abort State                    |      |

|            |                        | Subroutine                           | 3-34 |

| Appendix A | TYPE 2901 MICROPROCESS | OR CHIP STRUCTURE                    | A-1  |

| Appendix B | INSTALLATION           |                                      | B-1  |

| Appendix C | T&V WRAPAROUND TESTS   |                                      | C-1  |

#### HONEYWELL PROPRIETARY AND CONFIDENTIAL

v

ILLUSTRATIONS

| 1-1HDLC System Block Diagram1-21-2MLC/HDLC Adapter/DCE Interfaces1-42-1HDLC Major Block Diagram2-22-2HDLC Adapter Intermediate Block Diagram2-52-3HDLC/DCE Interface2-62-4HDLC/DCE Interface2-62-5Transmit Buffer Topology and Byte Definition2-102-6Receive Buffer Topology and Byte Definition2-122-7Frame Format2-162-8Logical Transmit Data Flow2-232-9Logical Receive Data Flow2-242-10Microprocessor Functional Block Diagram2-272-11MLC Command Decode And Control Signal Generation2-322-12UPCM/UPCM Command Decode/Test Multiplexer2-342-13Transmit Data and Control Paths2-403-11Internal RAM Register Assignment3-23-2External RAM Register Assignment3-23-3HDLC Firmware Overview3-183-4Firmware Revision Level in Output (Receive) Buffer3-193-5RCSRC State Subroutine3-363-6TRSRC Enter Sequence3-403-11TRDRC Routine3-383-10TRDRC Routine3-433-11TRURC Routine3-443-12RCSRC OTASYNC State Subroutine3-443-14RCSRC COTASYNC State Subroutine3-443-15RCSRC ARET State Subroutine3-443-16RCSRC TEXT State Subroutine3-443-11TRURC Routine              | Figure                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-2HDLC Adapter Intermediate Block Diagram2-52-3HDLC/MLC Interface2-62.4HDLC/DCE Interface2-62.5Transmit Buffer Topology and Byte Definition2-102-6Receive Buffer Topology and Byte Definition2-112-7Frame Format2-162-8Logical Transmit Data Flow2-232-9Logical Receive Data Flow2-242-10Microprocessor Functional Block Diagram2-272-11MLC Command Decode and Control Signal Generation2-322-12UPCM/UPCM Command Decode/Test Multiplexer2-342-13Transmit Data and Control Paths2-403-1Internal RAM Register Assignment3-23-2External RAM Register Assignment3-53-3HDLC Firmware Overview3-183-4Firmware Revision Level in Output (Receive) Buffer3-193-5RCSRC State Subroutine Relationships3-243-6Initialize Routine3-363-7TRSRC Enter Sequence3-363-8TRSRC Idle State Subroutine3-393-11TRURC Routine3-443-12RCSRC OUTASYNC State Subroutine3-433-13TRURC Routine3-433-14RCSRC OUTASYNC State Subroutine3-443-15RCSRC MART State Subroutine3-443-16RCSRC INSYNC State Subroutine3-443-17RCSRC OUTASYNC State Subroutine3-443-18RCSRC TEXT State Subroutine3-44 | 1-1                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

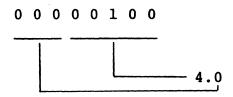

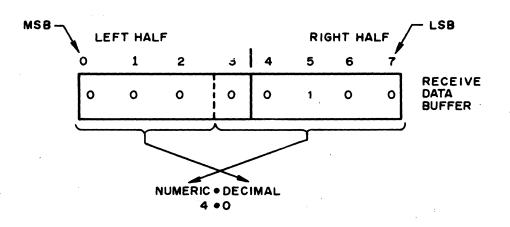

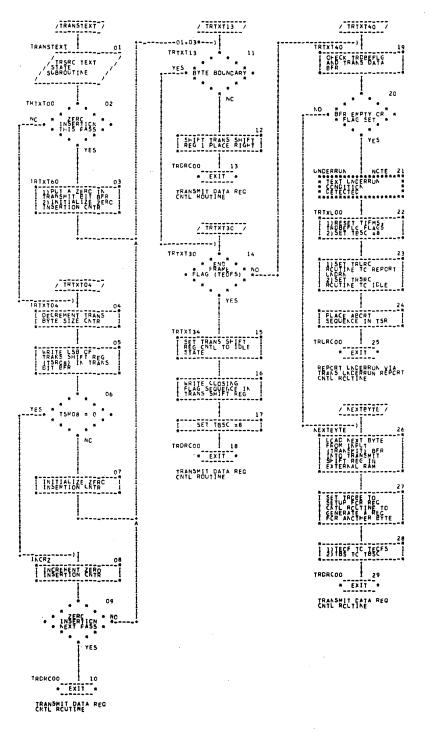

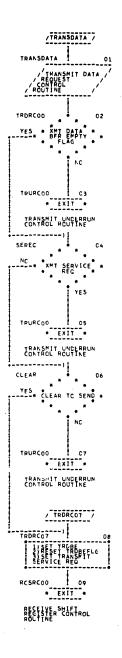

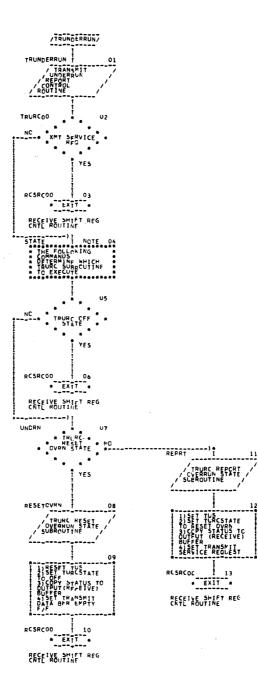

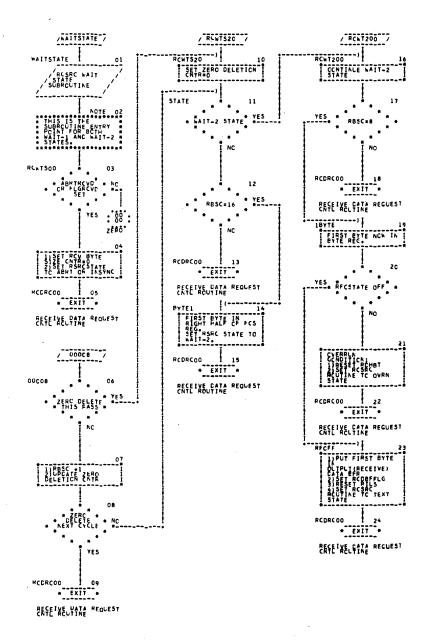

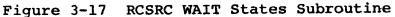

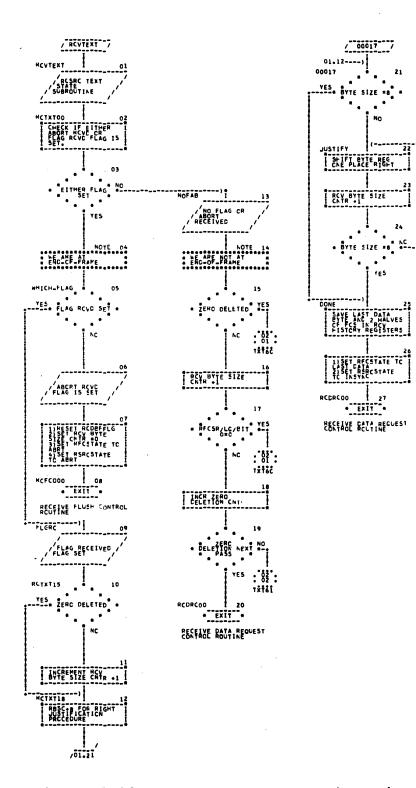

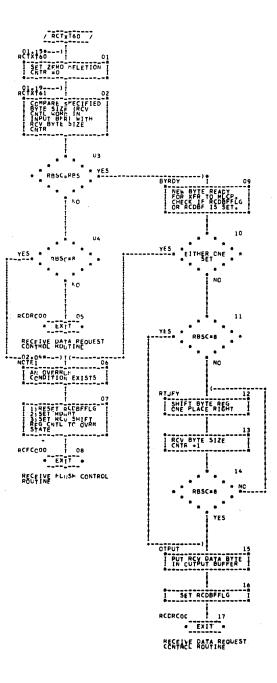

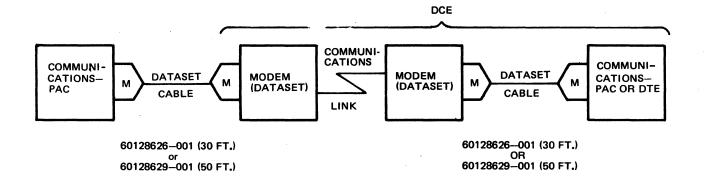

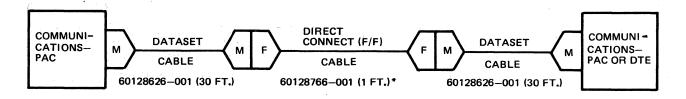

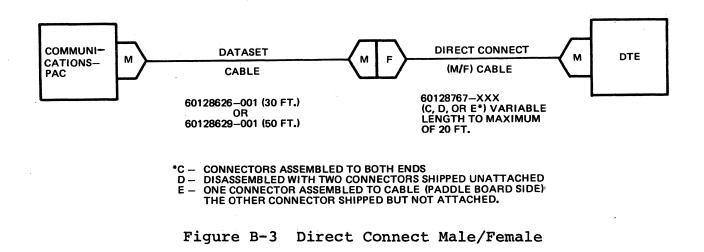

| 3-2External RAM Register Assignment3-53-3HDLC Firmware Overview3-183-4Firmware Revision Level in Output (Receive) Buffer3-193-5RCSRC State Subroutine Relationships3-243-6Initialize Routine3-353-7TRSRC Enter Sequence3-363-8TRSRC Idle State Subroutine3-373-9TRSRC TEXT State Subroutine3-383-10TRDRC Routine3-393-11TRURC Routine3-403-12RCSRC FIRST State Subroutine3-413-13RCSRC FIRST State Subroutine3-423-14RCSRC OUTASYNC State Subroutine3-433-15RCSRC ABRT State Subroutine3-443-16RCSRC INSYNC State Subroutine3-453-17RCSRC WAIT State Subroutine3-453-17RCSRC OVRN State Subroutine3-463-18RCSRC TEXT State Subroutine3-473-19RCSRC OVRN State Subroutine3-473-20RCDRC Routine3-503-21RCFCO Routine3-51B-1Typical Modern ConfigurationB-1B-2Direct Connect Female/FemaleB-2                                                                                                                                                                                                                                                                         | 2-2<br>2-3<br>2.4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13                                                         | HDLC Adapter Intermediate Block Diagram<br>HDLC/MLC Interface<br>HDLC/DCE Interface<br>Transmit Buffer Topology and Byte Definition<br>Receive Buffer Topology and Byte Definition<br>Frame Format<br>Logical Transmit Data Flow<br>Logical Receive Data Flow<br>Microprocessor Functional Block Diagram<br>MLC Command Decode and Control Signal Generation<br>UPCM/UPCM Command Decode/Test Multiplexer<br>Transmit Data and Control Paths                                                                                                                                                                                                                                                                                                                                                       | 2-5<br>2-6<br>2-10<br>2-12<br>2-16<br>2-23<br>2-24<br>2-27<br>2-32<br>2-34<br>2-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B-2 Direct Connect Female/Female B-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20 | External RAM Register Assignment<br>HDLC Firmware Overview<br>Firmware Revision Level in Output (Receive) Buffer<br>RCSRC State Subroutine Relationships<br>Initialize Routine<br>TRSRC Enter Sequence<br>TRSRC Idle State Subroutine<br>TRSRC TEXT State Subroutine<br>TRDRC Routine<br>RCSRC Routine Enter Sequence<br>RCSRC FIRST State Subroutine<br>RCSRC OUTASYNC State Subroutine<br>RCSRC ABRT State Subroutine<br>RCSRC INSYNC State Subroutine<br>RCSRC INSYNC State Subroutine<br>RCSRC WAIT States Subroutine<br>RCSRC TEXT State Subroutine<br>RCSRC TEXT State Subroutine<br>RCSRC VAIT State Subroutine<br>RCSRC TEXT State Subroutine<br>RCSRC TEXT State Subroutine<br>RCSRC TEXT State Subroutine<br>RCSRC OVRN State Subroutine<br>RCSRC OVRN State Subroutine<br>RCDRC Routine | 3-5<br>3-18<br>3-24<br>3-35<br>3-36<br>3-37<br>3-38<br>3-39<br>3-40<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-41<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-42<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-45<br>3-50 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | B-2                                                                                                                                          | Direct Connect Female/Female                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | в-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

.

#### TABLES

| Table |                                     | Page |

|-------|-------------------------------------|------|

| 2-1   | HLIC/DCE Status Reporting Format    | 2-4  |

| 2-2   | HDLC/PCE Interface                  | 2-7  |

| 2-3   | MLC Address and Control Line Decode | 2-9  |

vi

#### TABLES

| Table                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 2-5 UPCM Te                                                                                                                                                                                                                                                                                                               | ubcommand Decode<br>est Conditions<br>rocessor ALU Destination Control Field                                                                                                                                                                                                                                                                                                            | 2-13<br>2-14                                                  |

| Decode<br>2-7 Microp                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                         | 2-29<br>2-29<br>2-30                                          |

| 3-2       Externa         3-3       Microin         3-4       Subcomm         3-5       Test and         3-6       Scratch         3-7       Microph         3-8       ALU Son         3-9       ALU Fun         3-10       Received         3-11       Transmin         3-12       ALU Deg         3-13       Generation | al RAM Register File Assignments<br>al RAM Register Assignments<br>nstruction Formats<br>mand Selection<br>nd Modify Next Selection<br>h Pad Register Selection<br>rocessor Register File Selection<br>urce Operand Control<br>nction Control<br>e Buffer Register Selection<br>it Buffer Register Selection<br>stination Control<br>tion of Fill Character in TRSRC IDLE<br>Subroutine | 3-3 3-6 3-9 3-10 3-12 3-13 3-13 3-14 3-14 3-14 3-15 3-15 3-16 |

| C-1 EIA Cor                                                                                                                                                                                                                                                                                                               | nnector Jumpers for DCMS2-Mode C Loop Test                                                                                                                                                                                                                                                                                                                                              | C-1                                                           |

vii

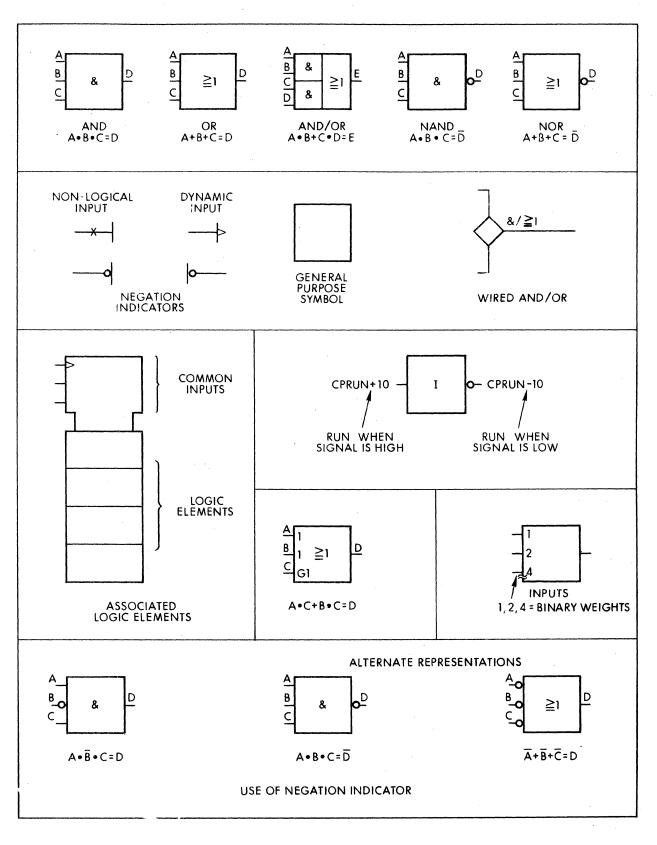

LOGIC SYMBOLOGY

viii

## I INTRODUCTION

#### 1.1 SCOPE AND PURPOSE OF THE DOCUMENT

This product manual describes the hardware and firmware of the Type DCM9106 High-Level Data Link Control (HDLC) Adapter.

The theory of operation for the HDLC, presented in Section II, provides a description of the functional hardware elements and their application and analyzon the operation of these elements at the detailed level presented in the logic block diagrams. These are found in the Type DCM9106 HDLC Adapter Reference Manual, Order No. FN13. Programming and medium information is presented to aid in understanding the HDLC adapter hardware description. To obtain programming details, refer to the Level 6 Minicomputer Handbook, Order No. AS22 or the Peripherals Handbook, Order No. AT04.

A description of the HDLC adapter firmware is presented in Section III; a description of and flow charts for the HDLC adapter are also included in Section III of this manual.

#### 1.2 ADAPTER GENERAL DESCRIPTION

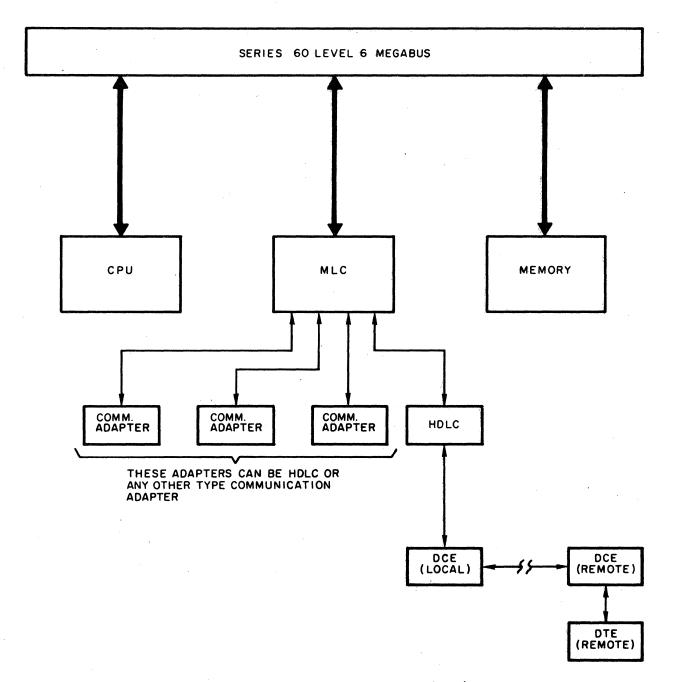

The Type DCM9106 High-Level Data Link Control (HDLC) Adapter, one of a series of Communications-Pacs, is a solid-state module used with a Multiline Communications Controller (MLC) to control a single communication line in the Model 6/34, 6/36, or 6/43 configuration of the Series 60 Level 6 computer system. The HDLC subsystem, whose attachment configuration is illustrated in Figure 1-1, can transmit to or receive data from a remote piece of Data Terminal Equipment (DTE).

The HDLC adapter consists of Dual In-Line Packages (DIPs) mounted on a single-size Series 60 Level 6 board (BD2DLC) utilizing printed wiring assembly (PWA) techniques. The HDLC adapter is mounted on the MLC package using its two 25-pin in-line connectors.

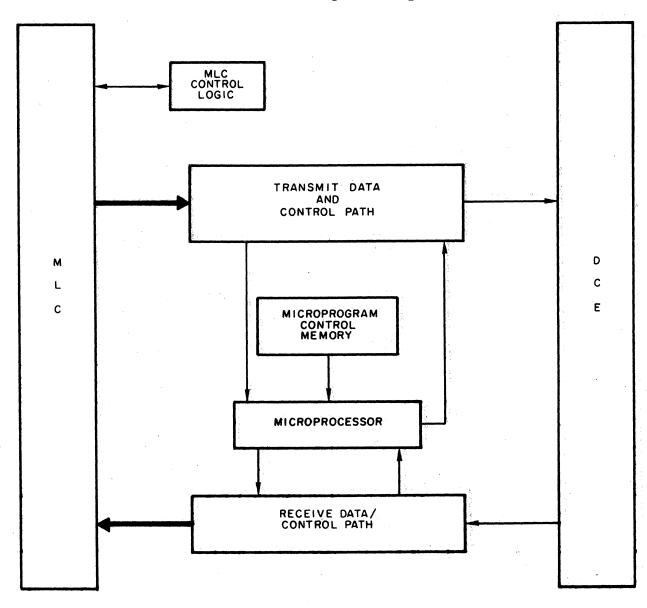

Figure 1-1 HDLC System Block Diagram

### 1.3 FUNCTIONAL DESCRIPTION

The HDLC adapter contains the communication-line-specific hardware and firmware for control of a single synchronous clocked data communication line. The HDLC provides for independent transmit and receive of data, with individual transmit and receive character sizes and either half-duplex or full-duplex operation. Data characters of five bits through eight bits can be transmitted or received, and this byte size is dynamically controlled by the Channel Control Programs (CCPs) stored in the MLC random access memory (refer to subsection 2.1). The format of the data for transmit and receive operations is in frames and is discussed in subsection 2.4.1 of this manual.

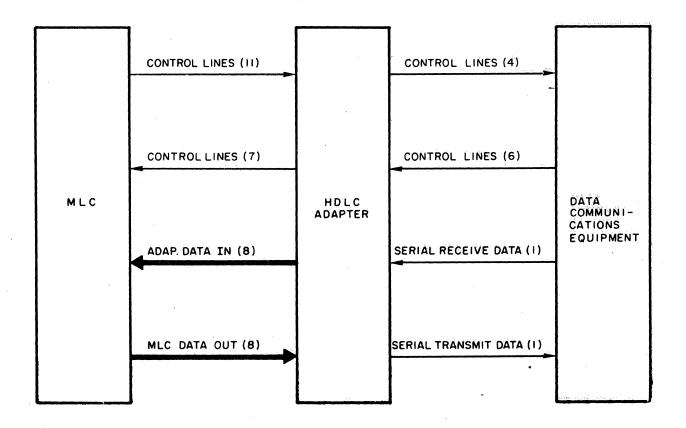

The HDLC adapter hardware is configured to handle a four-bit data structure rather than the nominal eight-bit data structure. The only area in which the HDLC is required to deal with eightbit data structures is at the HDLC/MLC data line interface (see Figure 1-2). During discussions of the HDLC adapter hardware, any four-bit data structure is referred to as a "byte," and any eight-bit data structure (at the interface level) is called a "word".

#### 1.3.1 Multiline Communications Controller (MLC)

The MLC is a microprogrammed communication line control unit which supports via the HDLC adapter a synchronous clocked data communication line. The majority of the firmware portion of the MLC is generalized to facilitate its application as a control element for various types of communication line adapters. The MLC performs the following general purpose control functions:

- Execution of Series 60 Level 6 Megabus\* network sequences

- Command decoding

- Status and control register storage

- Data information multiplexing to adapters

- Execution of CCPs to accomplish transmit or receive operations

- Generation of data verification information

- Checking of data verification information.

#### 1.3.2 HDLC Adapter

The HDLC adapter supports a single synchronous clocked data communication line through the application of the firmware and hardware located on the adapter. The HDLC adapter performs the following communication-line-specific functions:

- Controls communication line interface dialogues

- Generates various types of control sequences for transmission

\*Trademark of Honeywell Information Systems Inc.

- Recognizes various types of control sequences on receive

- Supplies and deletes zeros as necessary to provide data field transparency (refer to subsection 2.4.1)

- Supplies data and status information to the MLC

- Provides for data to be wrapped from the MLC to the communication line interface and back to the MLC for test purposes.

#### 1.3.3 Attachable Communication Equipment

The type of communication equipment which can be attached to the HDLC must be able to receive and transmit data across an interface (see Figure 1-2) in a bit serial manner in the format illustrated in Figure 2-7. The communication equipment must also supply the timing required for both transmit and receive operations and the necessary control signals for HDLC operation.

Figure 1-2 MLC/HDLC Adapter/DCE Interfaces

HONEYWELL PROPRIETARY AND CONFIDENTIAL

#### 1.4 OPERATIONAL SUMMARY

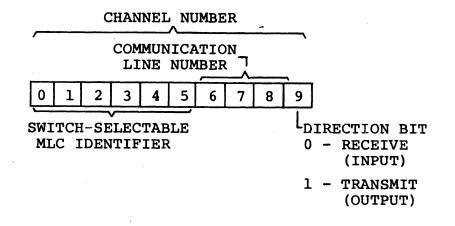

Each communication line attached to the MLC by way of the HDLC adapter (or other communication adapters) is addressable by software via channel numbers. A line has two channel numbers assigned, differing only in the low-order bit position (called the direction bit). When an I/O Load instruction for a line is accepted, the direction bit of the channel number specifies if this is an input (receive) or output (transmit) data transfer. The following indicates the composition of a channel number, where bits 0 through 5 are assigned at system installation.

Software usability of the communication lines attached to the MLC is such that the channels are, in general, independent of one another. For example, a transmit operation of the HDLC communication line is not dependent on the activity of the other HDLC channel (receive channel) except that the MLC can possibly stall the initiation of a command sequence to one channel while the MLC is busy servicing another channel.

The MLC contains a set of software-loadable random access memory locations in which the Channel Control Programs (CCPs), for controlling the transmit or receive operation on each line, are stored. Commands addressed to a nonbusy HDLC channel are always accepted by the MLC and the CCP stored in the random access memory for that channel is executed under control of the MLC firmware. The CCP is responsible for setting HDLC control information, transferring data to or from the HDLC, and examining adapter status prior to each data transfer. Upon completion of the operation, adapter status is used to update the MLC status for the channel, and the software is informed of the results of the operation.

#### 1-5

## 1.5 REFERENCE DOCUMENTS

The information contained in the following documents will facilitate an understanding of the HDLC adapter and the system of which it is a part.

| TITLE                                         | PART NO.     | ORDER NO. |

|-----------------------------------------------|--------------|-----------|

| Model 34/36 System Manual                     | 71010200-200 | FL35      |

| Type MLC9101 MLC Manual                       | 71010230-100 | FL48      |

| Type DCM9106 HDLC Adapter<br>Reference Manual | 71010405-100 | FN87      |

| Circuits Description<br>Reference Manual      | 71010206-200 | FL47      |

| Power System Manual                           | 71010290-200 | FL34      |

| Series 60 Level 6<br>Peripherals Manual       | N/A          | AT04      |

| Series 60 level 6<br>Minicomputer Handbook    | N/A          | AS22      |

| Level 6 Checkout and<br>T&V Manual            | N/A          | AW94      |

## II THEORY OF OPERATION

The High Level Data Link Control Adapter (HDLC), in conjunction with the MLC, is a software- and firmware-controlled communication line peripheral device adapter. The HDLC, when attached to the MLC, controls input and output (transmit and receive) operations.

The HDLC adapter contains all the communication-line-specific hardware as well as storage for the firmware which is necessary for the functional implementation of data transfer or control sequences of which the Data Communication Equipment (DCE) is capable. The HDLC adapter hardware is divided into five major logic components: MLC control logic, transmit data and control path, microprogram control memory, microprocessor, and receive data and control path (see Figure 2-1), which provides the path for data transfer and allows the control of efficient communication line operations.

#### 2.1 SOFTWARE

Two levels of software are associated with HDLC performance: central processor software operations and Channel Control Program (CCP) software executions.

The central processor software, through the application of the function codes listed in subsection 2.2.1 of the MLC Product Manual, loads the channel control program into the MLC scratch pad memory (refer to Section IV in the MLC product manual listed in Section I). Also utilizing function code capabilities, it is the

initiating factor for communication line operations. Actual performance of the communications line operation starts once the central processor software completes loading the necessary control parameters into the MLC Scratch Pad Memory (SPM). Control of the operation will then result from the execution of the CCP software located in the MLC SPM.

1

The CCPs are the MLC resident software which allows flexibility in the execution of communication line operations. Information pertaining to CCP instruction type and CCP location is found in Section IV of the MLC Product Manual. Examples of typical CCPs for a transmit and a receive operation are presented in Appendix B and Appendix C, respectively.

Figure 2-1 HDLC Major Block Diagram

HONEYWELL PROPRIETARY AND CONFIDENTIAL

#### 2.2 FIRMWARE

As in the case of the software, there are two levels of firmware associated with HDLC functionality: the generalized firmware and the HDLC-specific firmware. The generalized firmware is an integral part of the MLC microprogram control store and maintains control of the HDLC/MLC interface and also performs execution of CCP instructions. Intermediate flow charts of this firmware and a description of the data control information and firmware utilization are found in Section IV, Theory of Operations-Cycle Flow, of the MLC Product Manual listed in Section I. The HDLCspecific firmware is located in a microprogram control memory on the adapter. It interprets internal events or conditions pertaining to the HDLC and reacts in a prescribed manner (i.e., setting or resetting of hardware functions). Efficient data transfer is also the result of firmware control of hardware elements in the data path. Section III, Theory of Operation-Cycle Flow, of this manual supplies intermediate flow charts of the HDLC-specific firmware routines and descriptions of the control data, routine application, and firmware word structure.

#### 2.3 HARDWARE

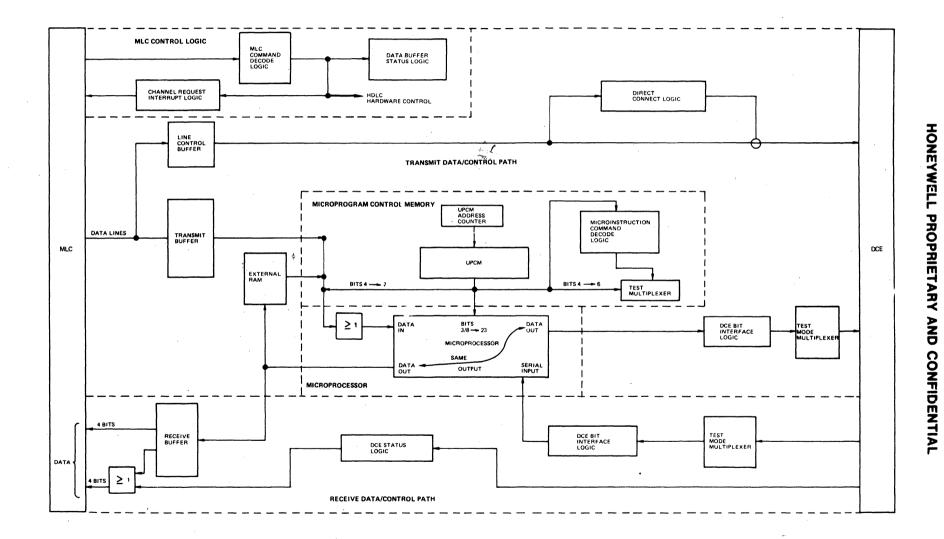

As shown in Figure 2-1, the HDLC hardware is organized into five fundamental logic areas. Figure 2-2, an intermediate block diagram of the HDLC adapter, depicts the logical components comprising each of these areas and shows the interconnections with the MLC and the DCE. Although the primary function of the HDLC is to establish efficient data flow between the MLC and the communication line, the adapter performs the following secondary functions of:

- Assisting the MLC in formatting data transmitted to the communication line

- Developing timing and control signals for the communication line

- Generating operational error indicators for MLC interrogation

- Generating transmit and receive channel request interrupts and sending them to the MLC

- Generating status information for sending to the MLC (refer to Table 2-1)

- Reporting DCE status information to the MLC (refer to Table 2-1)

- Serializing data from the MLC for transfer to the communication line

- Deserializing data from the communication line for transfer to the MLC.

The HDLC hardware is configured to handle a four-bit data structure rather than the nominal eight-bit data structure. The only area that the adapter is required to deal with eight-bit data structures is at the HDLC/MLC data line interface. During discussions of the adapter hardware, any four-bit data structure is referred to as a "byte," and any eight-bit data structure (at interface level) is called a "word".

The descriptions in the following subsections are of an overview nature and all pertain to the interfaces and logic blocks depicted in Figure 2-2.

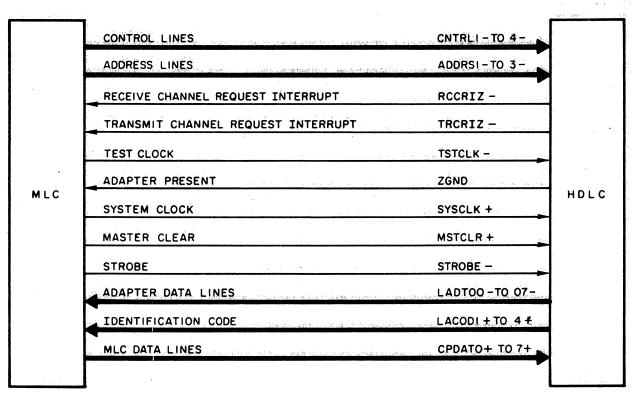

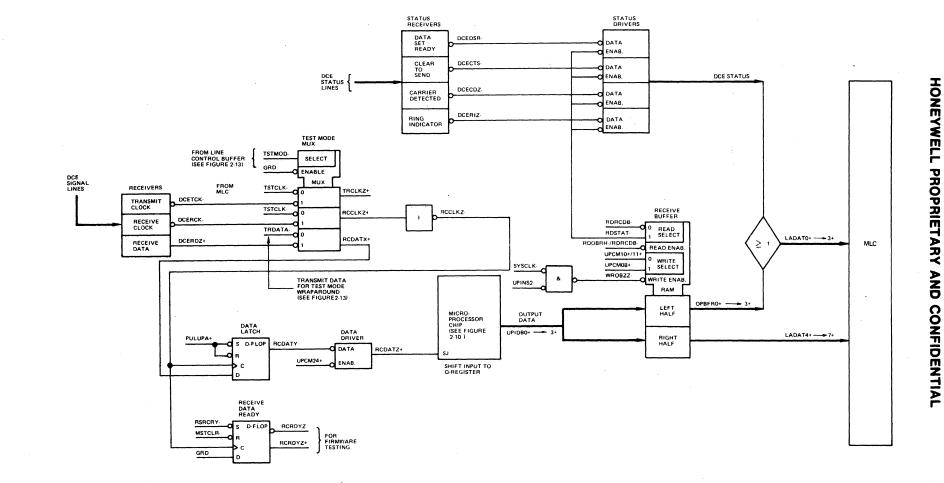

#### 2.3.1 HDLC/MLC Interface

The interface signal lines between the HDLC adapter and the MLC are shown in Figure 2-3. A description of the application of these lines is provided in the MLC Product Manual (see list in Section I). Signal line mnemonics are shown as they are designated by the adapter (certain lines may be assigned different mnemonics within the MLC).

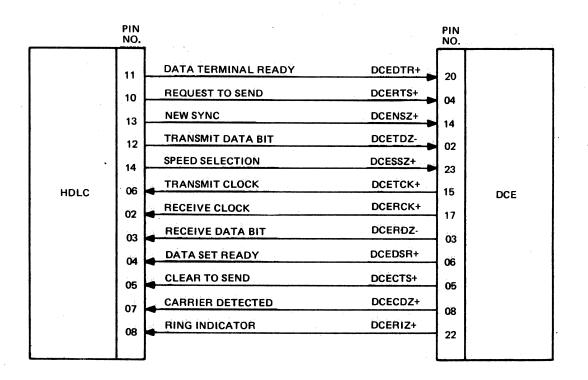

#### 2.3.2 HDLC/DCE Interface

A diagram of the HDLC/DCE interface interconnections is shown in Figure 2-4. This figure identifies the interface lines, their direction, mnemonics, and applications. It represents the lines as seen by the HDLC and not the DCE, where many of the lines have different mnemonics. For a more detailed description concerning the implementation of each signal line, refer to Table 2-2.

This interface provides a link with the DCE and allows the HDLC hardware and firmware the capability of performing the central processor software designated operations. It provides the path necessary to supply the DCE with data, control, and timing pulses; it also supplies the HDLC with timing, data, and status from the DCE.

| SOURCE        | MNEMONIC | MLC INTERFACE<br>DATA BIT | DESCRIPTION                      |

|---------------|----------|---------------------------|----------------------------------|

| DCE           | DSRZZZ+  | LADAT0+                   | Data Set Ready                   |

| DCE           | CTSZZZ+  | LADAT1+                   | Clear to Send                    |

| DCE           | CDZZZZ+  | LADAT2+                   | Carrier Detected                 |

| DCE           | RIZZZZ+  | LADAT3+                   | Ring Indicator                   |

| HDLC Firmware | RCF      | LADAT4+                   | Receive End of Frame             |

| HDLC Firmware | RCAS     | LADAT5+                   | Receive Abort/Idle<br>Link State |

| HDLC Firmware | RO       | LADAT6+                   | Receive Overrun                  |

| HDLC Firmware | TU       | LADAT7+                   | Transmit Underrun                |

Table 2-1 HDLC/DCE Status Reporting Format

Figure 2-2 HDLC Adapter Intermediate Block Diagram

HONEYWELL PROPRIETARY AND CONFIDENTIAL

Figure 2-3 HDLC/MLC Interface

Figure 2-4 HDLC/DCE Interface

HONEYWELL PROPRIETARY AND CONFIDENTIAL

Table 2-2 HDLC/DCE Interface (Sheet 1 of 2)

| TERM/MNEMONIC                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | OUTPUT LINES                                                                                                                                                                                                                                                                                                                                                                                                |

| Data Terminal Ready<br>(DCEDTR+) | This signal occurs when bit 0 of the<br>line control buffer (see Figure 2-13) is<br>set or reset. This signal indicates to<br>the DCE that the HDLC is ready to<br>transmit or receive.                                                                                                                                                                                                                     |

| Request to Send<br>(DCERTS+)     | This signal occurs when bit 1 of the<br>line control buffer (see Figure 2-13) is<br>set or reset. This signal indicates to<br>the DCE that the HDLC is ready to<br>transmit.                                                                                                                                                                                                                                |

| New Sync<br>(DCENSZ+)            | This signal occurs when bit 2 of the<br>line control buffer (see Figure 2-13) is<br>set or reset and indicates a request<br>from the HDLC to the DCE for a new sync<br>signal during normal operation. In the<br>direct connect mode, this signal is the<br>result of bit 4 of the line control<br>buffer and the test clock. It is then<br>used as a clock signal.                                         |

| Transmit Data<br>(DCETDZ-)       | This line is the serial data line from the HDLC to the DCE.                                                                                                                                                                                                                                                                                                                                                 |

| Speed Select<br>(DCESSZ+)        | During normal operation, this signal<br>occurs when bit 3 of the line control<br>buffer (see Figure 2-13) is set or reset<br>and indicate to the DCE for it to<br>select a specified rate of transfer<br>during normal operation. In the direct<br>connect mode, this signal is the result<br>of bit 4 of the line control buffer and<br>the test clock. It is then used as a<br>clock for the transmitter. |

|                                  | INPUT LINES                                                                                                                                                                                                                                                                                                                                                                                                 |

| Transmit Clock<br>(DCETCK+)      | This signa! (provided from the DCE)<br>supplies the HDLC with the timing<br>element necessary to perform transmit<br>operations.                                                                                                                                                                                                                                                                            |

| Receive Clock<br>(DCERCK+)       | This signal (provided from the DCE)<br>supplies the HDLC with the timing<br>element necessary to perform receive<br>operations.                                                                                                                                                                                                                                                                             |

| Receive Data<br>(DCERDE-)        | This line is the serial data line from the DCE to the HDLC.                                                                                                                                                                                                                                                                                                                                                 |

(

Table 2-2 HDLC/DCE Interface (Sheet 2 of 2)

| TERM/MNEMONIC                 | DESCRIPTION                                                                                                                                                    |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                               | INPUT LINES                                                                                                                                                    |  |  |  |

| Data Set Ready<br>(DCEDSR+)   | This signal (from the DCE to the HDLC)<br>indicates that the DCE is connected and<br>available for operation.                                                  |  |  |  |

| Clear to Send<br>(DCECTS+)    | This signal is a response by the DCE<br>resulting from the HDLC's request to<br>send, if the DCE can accommodate the<br>requested transmit operation.          |  |  |  |

| Carrier Detected<br>(DCECDZ+) | This signal (from the DCE to the HDLC)<br>indicates that the basic carrier<br>frequency of the communications line is<br>present.                              |  |  |  |

| Ring Indicator<br>(DCERIZ+)   | This signal (from the DCE) indicates to<br>the HDLC that a ringing condition is<br>being received on the communications<br>line which is directed to the HDLC. |  |  |  |

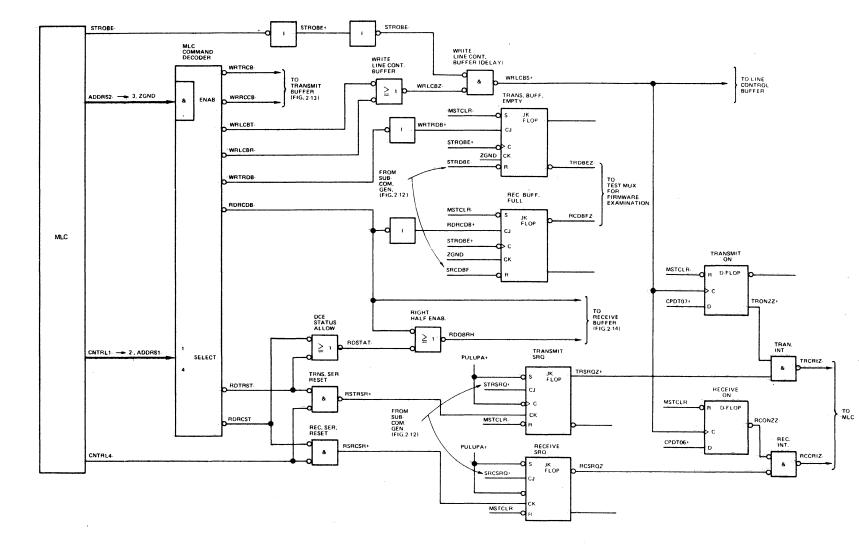

#### 2.3.3 MLC Control Logic

All data, control, configuration, and status information is transferred between the HDLC and the MLC via the interface data in and data out lines. This process is accomplished under control of the MLC, by the MLC Command Decoder which generates control signals as the result of the MLC strobe, address, and control lines (refer to Table 2-3). The outputs of this command decoder, within the MCL control logic, are distributed to the

Data Buffer Status logic and to the Channel Request Interrupt logic. External to the MLC control logic, the outputs allow the reading, writing, and resetting of various hardware elements.

The Data Buffer Status logic portion of the MLC control logic is enabled as the result of the HDLC firmware command decoding and supplies signals to the firmware for interrogation. These signals indicate whether the transmit and receive data buffers are full or empty and are reset by the appropriate decode from the MLC command decode logic.

From a functional standpoint, the Channel Request Interrupt logic is also considered part of the MLC control logic. The requests are enabled as the result of HDLC firmware command decoding and when the HDLC requires servicing, and are sent to the MLC. When the MLC responds with the appropriate command, the requests are reset by outputs of the MLC command decode logic.

|    | DRES<br>INES | -            |    | CONT         |    |    |        |          | ,                                                                  |

|----|--------------|--------------|----|--------------|----|----|--------|----------|--------------------------------------------------------------------|

| 1- | 2-           | 3-           | 1- | 2-           | 3- | 4- | STROBE | MNEMONIC | COMMAND DESCRIPTION                                                |

| L  | Н            | L            | L  | L            | Х  | Х  | Y      | WRTRCB-  | Write Transmit Control Byte                                        |

| L  | н            | L            | Н  | $\mathbf{L}$ | х  | х  | Y      | WRLCBT-  | Write Transmit Line Control Buffer                                 |

| н  | Ĥ            | L            | н  | L            | х  | х  | Ŷ      | WRLCBR-  | Write Receive Line Control Buffer                                  |

| Ħ  | н            | L            | L  | $\mathbf{L}$ | х  | х  | Y      | WRRCCB-  | Write Receive Control Byte                                         |

| L  | Н            | L            | н  | Н            | Х  | х  | Y .    | WRTRDB-  | Write Transmit Data Buffer - Reset<br>Data Buffer Empty (TRDBEZ-)  |

| L  | н            | · L          | L  | H            | х  | н  | х      | RDTRST-  | Read Transmit Status                                               |

| н  | н            | $\mathbf{L}$ | L  | Н            | Х  | Н  | х      | RDRCST-  | Read Receive status                                                |

| L  | Н            | L            | L  | Н            | Х  | L  | х      | RDTRST-  | Read Transmit Status - Reset<br>Transmit Service Request (TRSRQZ+) |

| н  | Н            | L            | L  | Н            | X  | L  | х      | RDRCST-  | Read Receive Status - Reset<br>Receive Service Request (RRCSRQ-)   |

| н  | н            | L            | н  | н            | х  | х  | N      | RDRCDB-  | Read Receive Data Buffer                                           |

| н  | H            | L            | н  | Н            | х  | х  | Y      | RDRCDB-  | Read Receive Data Buffer - Reset<br>Data Buffer Full (RCDBFZ-)     |

|    | т —          | Low          | ·  |              |    |    |        |          |                                                                    |

Table 2-3 MLC Address and Control Line Decode

L = Low

H = High

X = No effect

Y = Yes

N = NO

#### 2.3.4 Transmit Data/Control Path

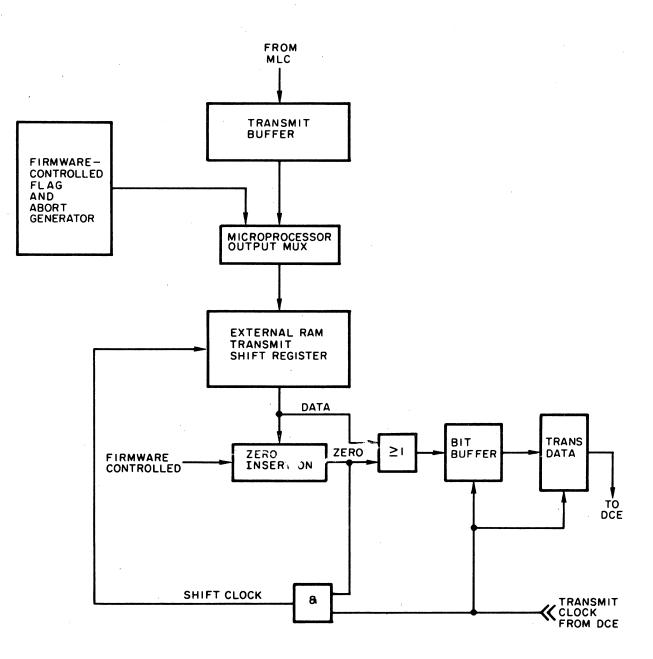

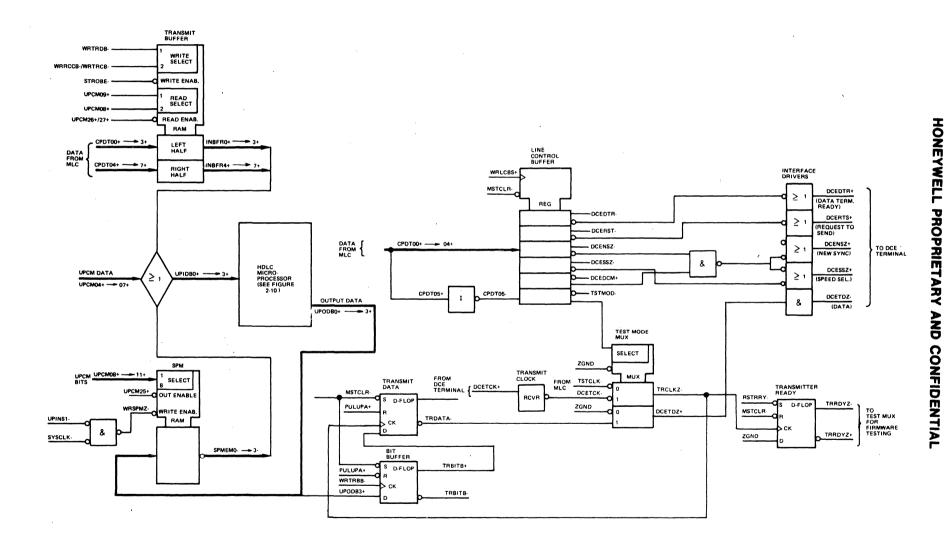

The transmit data/control path is a composite of six basic fundamental logic areas; the Transmit Buffer, the Line Control Buffer, the External Random Access Memory (RAM), the Direct Connect Logic, a portion of the DCE Bit Interface Logic, and a portion of the Test Mode Multiplexer.

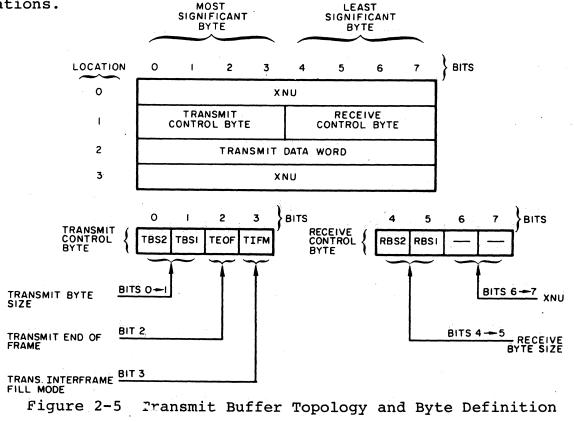

The transmit buffer (see Figure 2-5) has four word-size (8bit) locations which provide storage for the transmit control byte, the receive control byte, and the transmit data word. Only two locations are employed for storage of this information, leaving two other locations unused at this time. Information is written into the transmit buffer from the MLC data lines by the decode of the appropriate MLC command. The four-bit wide output is enabled when the firmware executes the proper microinstructions.

The Line Control Buffer (LCB) is eight bits wide and is loaded from the MLC data lines when a write line control buffer command is decoded from the MLC. Four outputs of the LCB are sent directly to the DCE interface as control signals, two outputs indicate the mode of operation (direct connect or test mode), and the remaining two specify transmit and receive on or off.

The sixteen byte size location external RAM serves as an extension to the internal RAM located in the microprocessor (refer to subsection 2.3.7 and 2.5.1). The external RAM (see Figure 3-2 for topology) is controlled by the HDLC firmware, and information read from it or written into it from the microprocessor is the result of a firmware command decode.

The direct connect logic uses the direct connect output of the line control buffer in conjunction with the test clock supplied by the MLC to develop a direct connect mode clock. This direct connect mode clock is sent to the DCE on the new sync and speed select interface lines.

The DCE bit interface logic portion of the transmit data/ control path consists of the logic required to transfer the least significant bit of the microprocessor data output to the test mode multiplexer, an action controlled by the HDLC firmware and the transmit clock logic. The DCE bit interface logic also includes a transmit data ready indicator, for firmware testing, which is set at the same clock time that new data is being supplied to the test mode multiplexer.

The transmit portion of the test mode multiplexer supplies data to the DCE interface and transmit clock timing to the DCE bit interface logic. The multiplexer selects one of two inputs for the transmit data, the data from the DCE bit interface logic or a ground level if the HDLC is in test mode. To supply the transmit clock for the DCE bit interface logic, the test mode multiplexer selects the transmit clock supplied by the DCE under normal operations or the test clock from the MLC during test mode operations.

2-10

#### 2.3.5 Receive Data/Control Path

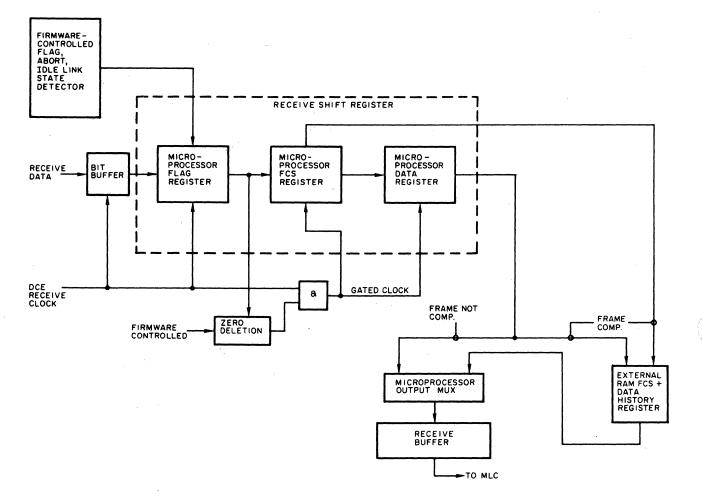

Four basic hardware logic elements are implemented to create the receive data/control path: a portion of the Test Mode Multiplexer, a portion of the DCE Interface logic, the DCE Status logic, and the Receive Buffer.

The receive portion of the test mode multiplexer supplies the DCE bit interface logic with receive clock timing and data. The receive timing supplied by the test mode multiplexer is either the result of the receive clock from the DCE during normal operation or the test clock sent by the MLC while in test mode. To provide data for the DCE bit interface logic, the test mode multiplexer selects one of two inputs: the data from the DCE or the transmit data from the transmit portion of the test mode multiplexer if the HDLC is in test mode.

The receive portion of the DCE bit interface logic within the receive data/control path consists of the logic necessary to transfer the receive data bit from the test mode multiplexer to the serial input of the microprocessor (refer to subsections 2.3.7 and 2.5.1). This action is accomplished under control of the HDLC firmware and the receive clock supplied by the test mode multiplexer. The DCE bit interface also consists of a receive data bit ready indicator, which is set at the same time the new receive data is being supplied to the microprocessor input, and is used for firmware examination.

The DCE status logic passes four bits of DCE status for transfer to the MLC. When a read status command is decoded in the MLC control logic, the four status signals (refer to Table 2-1) from the DCE are provided on bits 0 to 3 of the MLC/HDLC interface data lines.

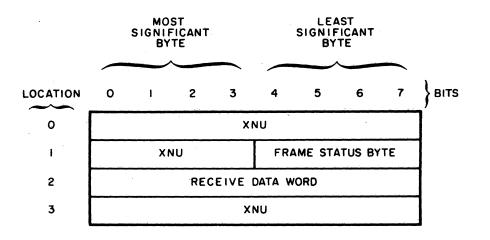

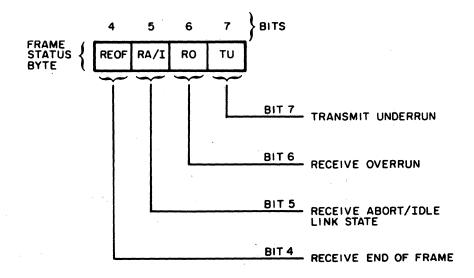

The receive data/control path receives buffer (see Figure 2-6) is four word size (8 bit) is ations which provide storage for the receive data word and the firmware generated frame status byte (refer to Table 2-1). Only one and one-half locations are utilized for storage of this information, leaving two and onehalf locations unused at this time. Bytes of information are written into the receive buffer from the four-bit wide data output of the microprocessor when the appropriate HDLC firmware The output of the receive buffer is enabled command is executed. onto the HDLC/MLC interface lines when the correct MLC command is decoded by the MLC control logic (refer to Table 2-3). When a read receive data buffer command is received, the complete data word is reflected on the interface lines, whereas, in the case of a read status command, interface data lines 4 to 7 will reflect the receive buffer status byte, and lines 0 to 3 will contain the status from the DCE status logic (refer to Table 2-1).

Figure 2-6 Receive Buffer Topology and Byte Definition

## 2.3.6 Microprogram Control Memory Logic

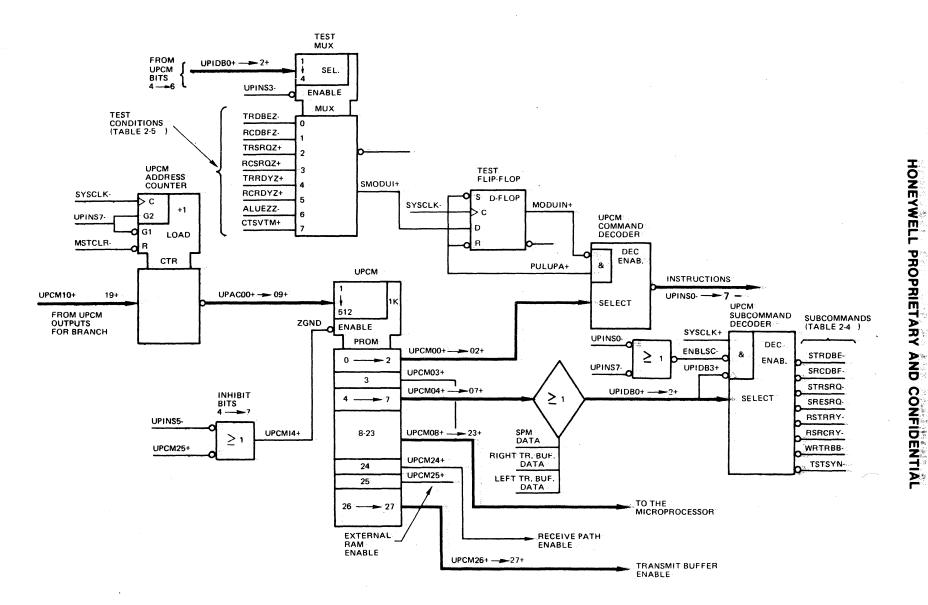

The Microprogram Control Memory Address Counter, the Microprogram Control Memory (UPCM), the Microinstruction Command Decode logic, and the Test Multiplexer are the four functional areas involved in making up the Microprogram Control Memory logic.

The ten-bit UPCM address counter specifies the location within the UPCM that contains the firmware command (refer to Section III of this manual for specific command information) presently being executed. The address counter increments at the start of each MLC clock cycle or is parallel loaded with ten of the outputs of the UPCM firmware command for a branch operation decode from the microinstruction command decode logic.

2-12

The firmware, sequences of microinstructions, for the HDLC is stored in the UPCM, which is arranged into 1024 twenty-eight bit locations. The address of the UPCM is provided by the UPCM address counter and the outputs of the addressed location are always read with the exception of bits 04 to 07. These four outputs are the firmware data inputs to the microprocessor and must be inhibited for certain types of firmware commands (Write External RAM, Read Transmit Buffer, and Read External RAM).

The microinstruction command decode logic is comprised of two major areas, the UPCM command decoder and the UPCM subcommand decoder. The UPCM command decoder evaluates bits 0 to 2 of the UPCM outputs to determine which of the eight possible instruction types the firmware is performing (see Section IV). When the command decoder detects an op code of either 0 (Subcommand instruction) or 7 (Branch and Subcommand instruction), the subcommand decoder is enabled (when bit 7 is Zero). The subcommand decoder then generates one of the eight available strobes (refer to Table 2-4), depending upon the decode of bits 4, 5, and 6 of the firmware command.

The test multiplexer portion of the UPCM logic provides the firmware with the capability of testing various hardware or operational conditions throughout the HDLC. When an op code of 3 (Test and Modify Next Instruction) is detected by the command decoder, the test multiplexer is enabled. Bits 4, 5, and 6 of the firmware command are then analyzed to select the test condition (refer to Table 2-5) and if the condition is true, the next firmware command is bypassed.

| UPCM BITS |              |              | S            |          |                                |

|-----------|--------------|--------------|--------------|----------|--------------------------------|

| 4+        | 5+           | 6+           | 7+           | MNEMONIC | SUBCOMMAND DESCRIPTION         |

| L         | L            | L            | L            | STRDBE-  | Set Transmit Data Buffer Empty |

| L         | L            | н            | L            | SRCDBF-  | Set Receive Data Buffer Full   |

| L         | Н            | $\mathbf{L}$ | L            | STRSRQ-  | Set Transmit Service Request   |

| L         | H            | н            | L            | SRCSRQ-  | Set Receive Service Request    |

| н         | $\mathbf{L}$ | L,           | L            | RSTRRY-  | Reset Transmitter Ready        |

| н         | L            | Н            | L            | RSRCRY-  | Reset Receiver Ready           |

| н         | н            | L            | $\mathbf{L}$ | WRTRBB-  | Write Transmit Bit Buffer      |

| н         | H            | H            | L            | TSTSYN-  | Test SYNC                      |

| Table 2-4 U | UPCM | Subcommand | Decode |

|-------------|------|------------|--------|

|-------------|------|------------|--------|

H = High

L = Low

| UPCM BITS |              |    |          |                                        |

|-----------|--------------|----|----------|----------------------------------------|

| 4+        | 5+,          | 6+ | MNEMONIC | TEST DESCRIPTION                       |

| L         | L            | L  | TRDBEZ-  | Transmit Data Buffer Empty             |

| L         | $\mathbf{L}$ | H  | RCDBFZ-  | Receive Data Buffer Full               |

| L         | н            | L  | TRSRQZ+  | Transmit Service Request               |

| L         | н            | н  | RCSRQZ+  | Receive Service Request                |

| Ĥ         | L            | L  | TRRDYZ+  | Transmitter Ready                      |

| н         | L            | Н  | RCRDYZ+  | Receiver Ready                         |

| н         | н            | L  | ALUEZZ-  | ALU Result Equal Zero                  |

| н         | н            | н  | CTSVTH+  | An "OR" of Clear to Send and Test Mode |

Table 2-5 UPCM Test Conditions

H = High

L = Low

#### 2.3.7 Microprocessor

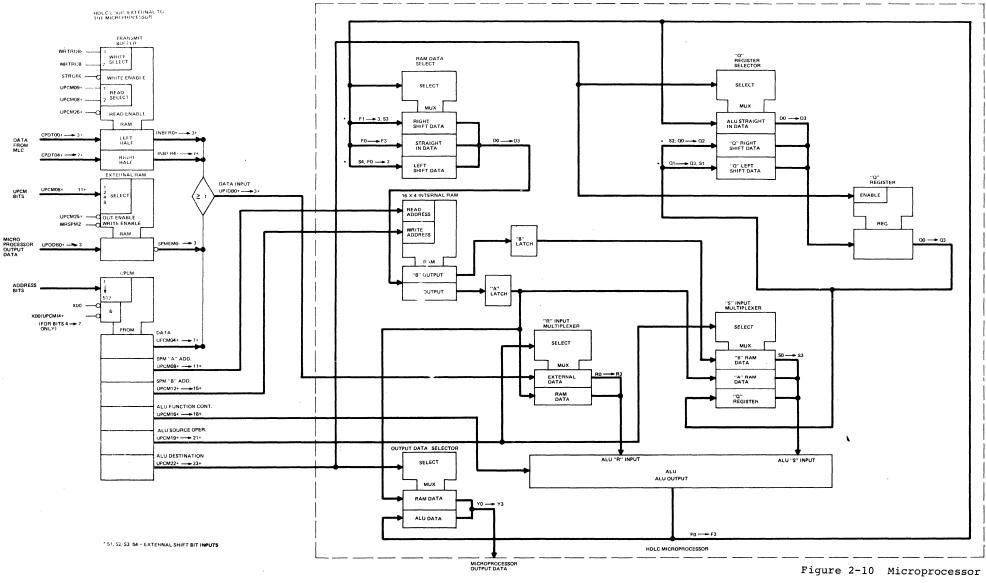

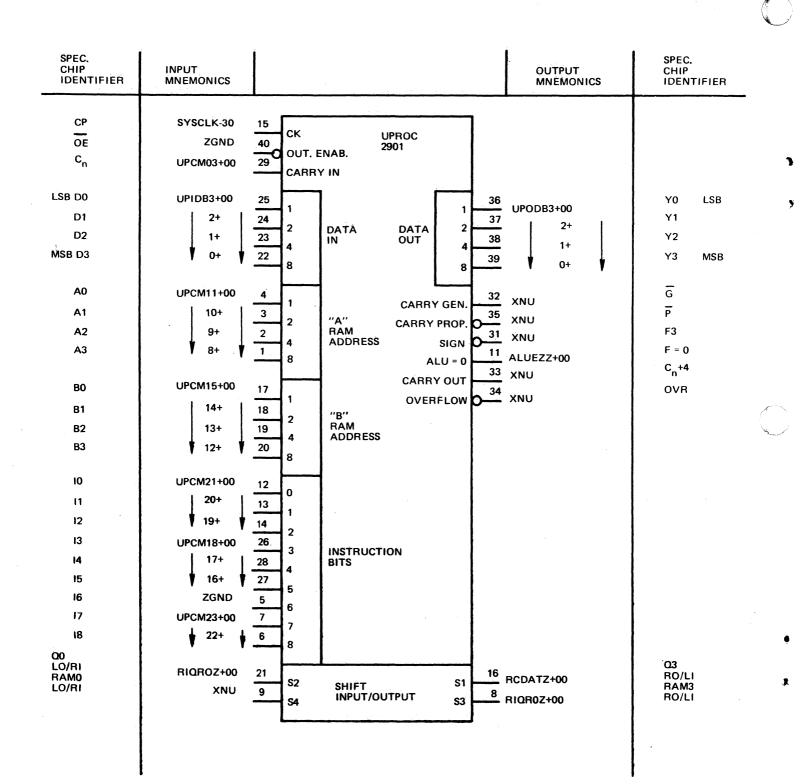

All activity within the HDLC centers around the processing capabilities of the firmware-controlled microprocessor. The microprocessor supplies the HDLC with a sixteen location byte wide internal RAM, a byte wide shift register, and a byte wide ALU. The addressing within the microprocessor of its various components and the internal data paths supplied (see Figure 2-10) for data transfer allows the HDLC to serialize and deserialize data, store operational information, and perform logical operations on data and information bytes.

Data provided to the microprocessor can come from the UPCM (bits 4 to 7), from either byte of the transmit buffer (see Figure 2-5), or from the external RAM.

The firmware control of the microprocessor is a result of bits 8 to 23 of the firmware command. These bits determine the internal RAM read or write address, the function the ALU is to perform, the source of the ALU operands, and the destination of the ALU result.

2-14

#### 2.4 FRAME STRUCTURE/OPERATIONAL CHARACTERISTICS/OPERATIONS

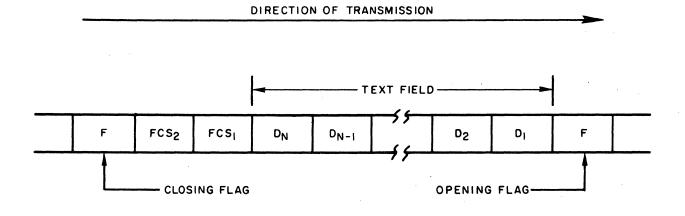

#### 2.4.1 Frame Structure