# THE CUSTOM PROCESSOR SERIES

ſ

C

Ĵ

(, **[**]

TECHNICAL DESCRIPTION OF THE 32-BIT CUSTOM CENTRAL PROCESSOR

## TABLE OF CONTENTS

This document and the information contained herein are confidential to and the joint property of Honeywell Corporation and the Ultimate Corporation for the sole purpose of conducting their business. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager, and shall not be disclosed or distributed (a) to persons who are not Honeywell or Ultimate employees, or (b) to Honeywell or Ultimate employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this document no longer has need for the document for the authorized Honeywell or Ultimate purpose, this document and any copies thereof shall be returned to the employee's manager. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsible Honeywell or Ultimate Vice President.

Throughout the text of this document, the term "custom processor" shall be interchangeble with the term "Ultimate Processor".

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

T

•

₹.

TABLE OF CONTENTS

| SECTION I                         | •     |

|-----------------------------------|-------|

| 1.0 SCOPE AND PURPOSE             | 1-1   |

| 1.1 Disclainer                    | 1-1   |

| - 1.2 References                  | 1 - 1 |

| SECTION II                        |       |

| 2.0 OPERATIONAL OVERVIEW          | 2-1   |

| 2.1 System environment            | 2-1   |

| 2.2 Introductory description      | 2-4   |

| 2.2.1 the ralu                    | 2-4   |

| 2.2.2 the aram                    | 2-5   |

| 2.2.3 the dbus                    | 2-5   |

| 2.2.4 the abus                    | 2-5   |

| 2.2.5 the zbus                    | 2-5   |

| 2.2.6 the local bus               | 2-5   |

| 2.2.7 flags                       | 2-6   |

| 2.2.8 the shifter                 | 2-6   |

| 2.2.9 indicators                  | 2-6   |

| 2.2.10 op registers               | 2-6   |

| 2.2.11 other registers            | 2-6   |

| 2.2.12 the clock                  | 2-7   |

| 2.2.13 the stack                  | 2-7   |

| 2.2.14 the next address generator | 2-7   |

| 2.2.15 availability               | 2-7   |

## CUSTOM PROCESSOR TECHNICAL DESCRIPTION PAGE 1-2

۰.

Γ

I

ſ

## TABLE OF CONTENTS

SECTION III 3.0 HARDWARE DESCRIPTION 3-1 3.1 Register file and alu 3-2 3.1.1 the 2901's 3-2 3.1.2 ralu addressing and control 3-2 3.1.3 ralu support logic 3-3 3.2 Auxiliary Random Access Memory 3-3 3.2.1 aram read or write 3-3 3.2.2 aram addressing 3-4 3.3 The D Bus 3-4 3.3.1 dbus byte w 3-5 5.3.2 dbus byte x 3-5 3.3.3 dbus byte y 3-6 3.3.4 dbus byte z 3-7 3.4 The S Bus 3-8 5.4.1 sbus byte w 3-8 5.4.2 sbus byte x, y, z 3-9 3.4.3 sbus enables 3-10 3.5 The Z Bus 3-10 5.5.1 zbus sources 3-11 5.5.2 zbus enables 3-11

•

.

Y

Ţ

Ч

| 3.6 The Local Bus                           | 3-12 |

|---------------------------------------------|------|

| <b>5.6.1</b> local bus addressing           | 3-12 |

| <b>3.6.2 local bus data storage</b>         | 3-12 |

| 5.6.3 local bus procedure storage           | 3-13 |

| 3.6.4 local bus control circuitry           | 3-13 |

| 3.7 Temporary, Permanent and Control Flags  | 3-15 |

| 3.7.1 temporary flags                       | 3-15 |

| 3.7.2 permanent flags                       | 3-16 |

| 3.7.3 control flags                         | 3-16 |

| 3.8 Nibble Shifter                          | 3-16 |

| <b>3.8.1 shifter data flow</b>              | 3-17 |

| <b>3.8.2 shifter control</b>                | 3-17 |

| 3.9 Arithmetic and Miscellaneous Indicators | 3-17 |

| 3.9.1 arithmetic indicators                 | 3-17 |

| 5.9.2 miscellaneous indicators              | 3-18 |

| 3.9.2.1 scram indicator                     | 3-19 |

| <b>3.9.2.2</b> difbuf indicator             | 5.19 |

| 3.9.2.3 hashit indicator                    | 3.19 |

| 3.9.2.4 illadd indicator                    | 3.19 |

| 3.9.2.5 leading zero detector               | 3.19 |

| 3.10 The OP Register                        | 3.19 |

| 5.10.1 the sbus multiplexor                 | 3.19 |

| 5.10.2 the op multiplexor                   | 3.20 |

| 3.10.3 the op registers                     | 3.20 |

| 3.10.4 the type register                    | 3.20 |

I

I

ſ

TABLE OF CONTENTS

| 3.11 Loading Various Registers                  | 3-20 |

|-------------------------------------------------|------|

| 3.11.1 loading the H register                   | 3-20 |

| <b>3.11.2</b> loading the output register       | 3-21 |

| 3.11.3 loading the V register                   | 3-21 |

| 3.11.4 changing adra, adrb, and adrp            | 3-21 |

| 3.11.5 changing grbr                            | 3-21 |

| 3.11.6 changing bsbr                            | 3-22 |

| 3.11.7 chasnging bsar                           | 3-22 |

| 3.11.8 loading the accounting timer             | 3-22 |

| 3.12 The Four Speed Clock                       | 3-22 |

| 3.12.1 the basic clock                          | 3-23 |

| 3.12.2 the gear shifter                         | 3-23 |

| 3.12.3 clock stalls                             | 3-24 |

| 3.13 The Return Stack                           | 3-26 |

| 3.13.1 the 16 location return memory            | 3-26 |

| 3.13.2 the 4 bit return memory address register | 3-26 |

| 3.13.3 the return memory local register         | 3-27 |

| 3.13.4 the relative push local register         | 3-27 |

| 3.13.5 the absolute push local register         | 3-27 |

| 3.13.6 the hardware interrupt register          | 3-27 |

| 3.13.7 the return address bus                   | 3-28 |

| 3.13.8 the stack overflow/underflow detector    | 3-28 |

| •                                               |      |

-

E

•

-

| 3.14 The Next Address Generator          | 3-28 |

|------------------------------------------|------|

| 5.14.1 bank selection                    | 3.29 |

| 3.14.2 else next bank address generation | 3.29 |

| 3.14.3 if bank next address generation   | 3.30 |

| 3.14.3.1 if bank address bits 01-05      | 3.30 |

| 3.14.3.2 if bank address bits 06-09      | 3.31 |

| 5.14.3.3 if bank address bits 10-13      | 3.31 |

| 3.15 Availability Circuits               | 3.33 |

| 3.15.1 error detection circuits          | 3.33 |

| 3.15.1.1 procedure parity                | 3.33 |

| 3.15.1.2 data parity                     | 3.34 |

| 3.15.1.3 procedure red                   | 3.34 |

| 3.15.1.4 data red                        | 3.34 |

| 3.15.1.5 procedure uar                   | 3.34 |

| 3.15.1.6 data uar                        | 3.34 |

| 3.15.1.7 stack overflow or underflow     | 3.35 |

| 3.15.1.8 control store parity            | 3.35 |

| 3.15.2 parity generation circuits        | 3.36 |

| 3.15.3 verifying the integrity circuits  | 3.36 |

| 3.15.4 branch to zero                    | 3.36 |

| SECTION IV                               |      |

| 4.0 FIRMWARE DESCRIPTION                 | 4-1  |

| 4.1 2901 Control                         | 4-3  |

| 4.2 Aram Control                         | 4-6  |

### CUSTOM PROCESSOR TECHNICAL DESCRIPTION

PAGE 1-6

٠.

[.

I

ſ

I

I

.

TABLE OF CONTENTS

| 4.3 D Bus Control                       | 4-7   |

|-----------------------------------------|-------|

| 4.3.1 DG=literal                        | 4-7   |

| 4.3.2 DG=broadside                      | 4-7 ' |

| 4.3.3 DG=mix                            | 4-8   |

| 4.3.4 DG=sign extend                    | 4-8   |

| 4.4 S Bus Control                       | 4-9   |

| 4.4 Z Bus Control                       | 4-10  |

| 4.6 Local Bus Control                   | 4-10  |

| 4.7 Flag Control                        | 4-14  |

| 4.7.1 permanent flags                   | 4-14  |

| 4.7.2 control flags                     | 4-15  |

| 4.7.3 temporary flags                   | 4-15  |

| 4.8 Nibble Shifter Control              | 4-15  |

| 4.9 Indicator Control                   | 4-15  |

| 4.9.1 arithmetic indicators             | 4-16  |

| 4.9.2 miscellaneous indicators          | 4-16  |

| 4.10 OP Register Control                | 4-17  |

| 4.10.1 pbus to OP                       | 4-18  |

| 4.10.2 sbus to OP                       | 4-19  |

| 4.10.3 OP increment/decrement           | 4-20  |

| 4.11 Load Controls                      | 4-20  |

| 4.11.1 loading adra, adrb, or adrp/pctr | 4-21  |

| 4.11.2 loading outr, v, or h            | 4-21  |

| 4.11.3 changing rbr                     | 4-22  |

| 4.11.4 changing rar                     | 4-22  |

| 4.11.4.1 loading all of rar             | 4-22  |

| 4.11.4.2 changing rarh                  | 4-23  |

| 4.11.4.3 changing rarl                  | 4-23  |

|                                         | · -   |

, **I**

I

| 4.12 Clock Control        | 4-23 |

|---------------------------|------|

| 4.13 Stack Control        | 4-24 |

| 4.14 Next Address Control | 4-24 |

| 4.15 Availability         | 4-30 |

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

INTRODUCTION

## INTRODUCTION

The thirty-two-bit custom processor is a ten megahertz, thirty-two-bit wide, microprogramable firmware engine driven by a one-hundred and twenty-eight bit wide control store word and having a blank identity.

1.1 PURPOSE

This tchnical description imparts information which is necessary for any who wish to provide the custom processor with a new incarnation. Those who attempt personalization of the custom processor need be capable of writing and testing microcode. For testing microcode, Custom and Special Products offers a Firmware Development Facility which greatly simplifies the task (see appendix  $\lambda$ ).

1.2 SCOPE

This document is intended for the prospective microprogrammer. It describes the operation of the 32-bit custom processor at the level of an experienced coder. Others, such as test technicians, might also find the information in section three useful.

In addition to this section, this document contains four other sections and three appendices.

Section II describes the system environment, an exposure of the custom processor capabilities and a brief discussion of each of its major areas.

Section III is a detailed description of each of the fifteen hardware areas.

Section IV is a detailed description of each of the fifteen firmware areas.

Section V is a discussion of internal speed considerations.

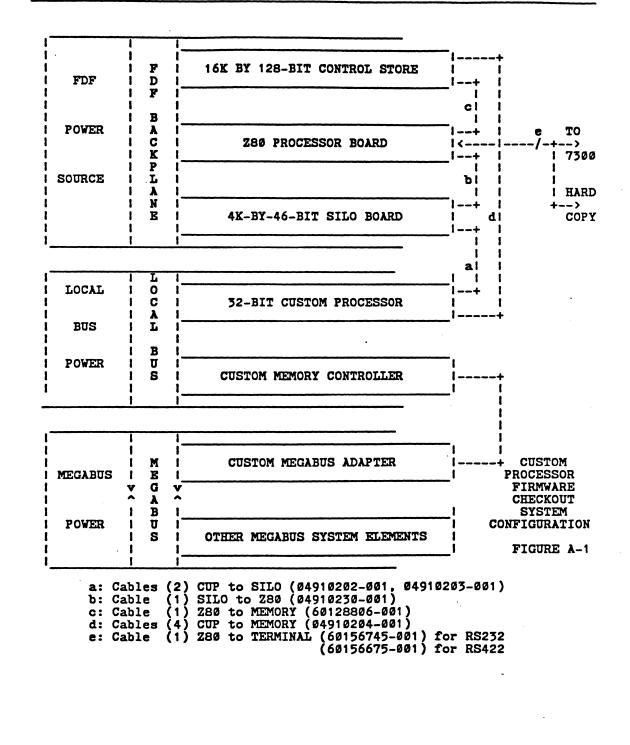

Appendix  $\lambda$  contains a description of the Firmware Development Facility which is available for the checkout of firmware written for the Custom Processor.

Appendix B contains a description of the Quality Logic Test firmware which is available for linking into the custom firmware load and is recommended as a means of verifying the integrity of the Custom Processor at every system initialization.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

Appendix C is a description of the Test and Verification routine available with every incarnation of the Custom Processor.

1.3 DISCLAIMER

The firmware dictionary serves as the specification for the custom processor. The firmware dictionary shall govern in any disagreement between it and this technical description.

1.4 REFERENCES

.

In order to code firmware to execute on the CUP32, the following additional documents may prove useful:

CUP32 dictionary

CUP32 logic block diagrams

for the mother board ...60160259

for the daughter board 60160249

RTL6 assembly language manual

document

#LDA-021

### CUSTOM PROCESSOR TECHNICAL DESCRIPTION

## OPERATIONAL OVERVIEW

This section describes the system environment into which the 32-bit Custom Processor may be connected. The section also gives a first-level description of the Custom Processor's inner workings.

2.1 SYSTEM ENVIRONMENT

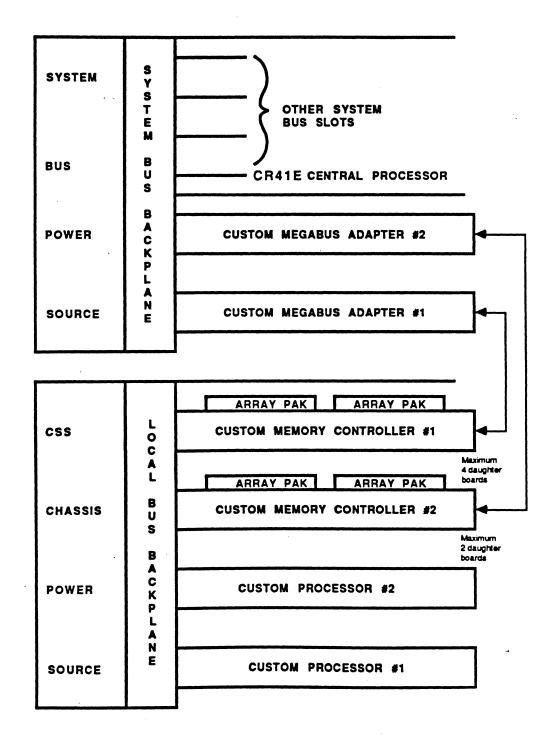

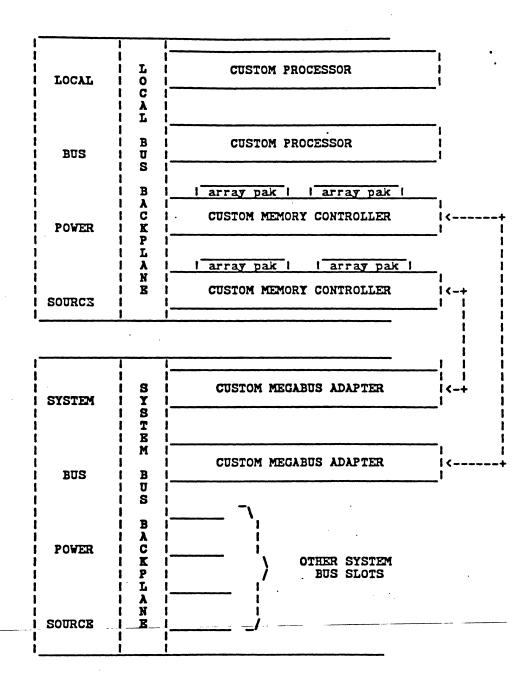

The 32 bit Custom Processor is housed in a central subsystem chassis (see figure 2-1). This chassis contains an interconnect backplane called the Local Bus which allows communication among elements within the central subsystem chassis. A minimum of two elements must be installed into the central subsystem chassis: namely, a 52-bit Custom Processor and a triport memory. One port of the tri-port memory connects to a Custom Processor on the Local Bus, another port connects via a Custom MEGABUS Adapter board to a 32-bit MEGABUS System Bus, and a third port is available to connect to a second Custom Processor on the Local Bus. The Custom MEGABUS Adapter board physically plugs into the 32-bit System Bus and a set of cables connect it to the tri-port memory. The central subsystem chassis is designed to accommodate a total of two 32-bit Custom Processors and two tri-port memories. In configurations where two tri-port memories are installed, each tri-port memory is connected via cables to its dedicated Custom Processor access to System Bus elements including peripheral controllers, communication controllers, central memories, and other processing elements (e.g., a Series 6 CPU).

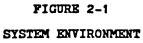

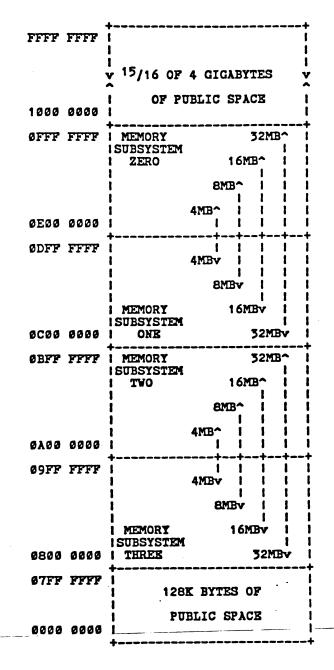

Each tri-port memory may be configured to contain either two-megabytes or four-megabytes of memory. When more than one tri-port memory is installed, the total address space is contiguous. Figure 2-2 illustrates possible memory configurations which are supported. Note that it is possible to connect another complete central subsystem chassis to the System Bus for a maximum of four 32-bit Custom Processors and four tri-port memories.

The configuration should include at least one Level 6 processor, if for no other reason than to allow test software to be loaded and executed. This is the most effective way of allowing the user to verify the integrity of all device and communication controllers.

Architecturally, the system is strategized to minimize System\_Bus memory\_traffic\_in support of a processor's instruction stream. In these systems memory traffic on the System Bus will service direct memory access(DMA) almost exclusively. The only other System Bus traffic will be that programmed I/O dialogue required to institute and control DMA and that interprocessor mailbox dialogue necessary for sharing system resources.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

## HONEYWELL CONFIDENTIAL AND PROPRIETARY

## ULTIMATE

CONFIGURATION

### SYSTEM ENVIRONMENT

## HONEYWELL CONFIDENTIAL AND PROPRIETARY

10-1-5

OPERATIONAL OVERVIEW

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

### OPERATIONAL OVERVIEW

### FIGURE 2-2A

MEMORY CONFIGURATIONS FOR THE 24-BIT ADDRESS SPACE

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

.

Ξ.

OPERATIONAL OVERVIEW

MEMORY ADDRESS ALLOCATION FOR 32-BIT ADDRESS SPACE

### CUSTOM PROCESSOR TECHNICAL DESCRIPTION

.

#### OPERATIONAL OVERVIEW

#### 2.2 INTRODUCTORY DESCRIPTION

The major block diagram of figure 2-3 is a representation of the Custom Processor. This section is divided into fifteen paragraphs each of which discusses the topic at a first level. The discussions in sections three and four are similarly subdivided allowing the reader quick reference to greater hardware detail (section three) or greater firmware detail (section four). The fifteen sections are listed below, each with their associated block diagram identifier:

- I. the ralu

- II. the aram

III. the d bus

- IV. the s bus

- V. the z bus

- VI. the Local Bus

- VII. flags

VIII. shifter

- IX. indicators

- X. op code registers

- XI. other registers

- XII. the clock

- XIII. the stack

- XIV. the next address generator

- IV. availability

2.2.1 the ralu (see block diagram identifier I)

The register file and alu is comprised of eight 2901 bit slice chips constituting a thirty-two-bit alu, a sixteen-location dual-ported random- access memory and a bit shifter (32 or 64 bits wide). Operations inside the alu occur at nearly a ten megahertz rate. The ralu receives external thirty-two-bit data from the dbus and transmits thirty-two-bit results to the zbus.

2.2.2 the aram (see block diagram identifier II)

The auxiliary random access memory is a single-ported 4096-location memory. Each location contains thirty-two bits. The memory may be addressed in any one of seven different ways. Its data is read onto the sbus. Data written into the aram is taken from the sbus. Writing of the aram is byte partitioned; that is, any combination of 1, 2, 3, or 4 bytes may be "copied" from the sbus into the addressed aram location.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

2.2.3 the dbus (see block diagram identifier III)

The dbus is the place where all roads lead. It is a thirty-two bit bus which receives data from the sbus, the zbus, the pbus and numerous other secondary sources. It may deliver its wealth to the ralu, the output register, and to the zbus. It has byte partitioning capabilities; e.g., it may take a byte of the aram for its upper eight bits, an h register byte for its next eight bits, a literal for its next eight bits, and a bunch of zeros for its last eight bits.

2.2.4 the sbus (see block diagram identifier IV)

The sbus receives and provides aram data. It receives and provides data for the three Local Bus address registers. It has the unique capability of receiving and reflecting two of its sources during the same firmware step by virtue of a time-multiplexing mechanism.

2.2.5 the zbus (see block diagram identifier V)

If the dbus is where all roads lead and the sbus is hermaphroditic, the zbus is totally colorless. Indeed, it is a journeyperson bus, capable of receiving data from the outside world (the memory subsystem), receiving ralu revelations and sending all this to the v register, and/or to the dbus, and/or to the sbus via the nibble shifter.

2.2.6 the Local Bus (see block diagram identifier VI)

The Local Bus is the area of the processor responsible for communicating with the memory subsystem and through it, via the System Bus, to all other system elements; e.g., a Series 6 processor or a Series 6 controller. The Local Bus area contains, along with the interface circuits required to carry on a dialogue upon the Local Bus, an eight-byte lock-ahead procedure buffer and two four-byte data buffers. The two data buffers receive information from memory to be deposited onto the zbus. The lock-ahead procedure buffer is organized to supply one or two bytes to the op register and/or the dbus and automatically replentish the prefectch buffer as bytes are consumed.

2.2.7 flags (see block diagram identifier VII)

The Custom Processor contains twenty-four firmware settable and testable flops. Some have hardware dedicated functions (e.g., processor off-line); others have more sophisticated firmware sequence control characteristics (e.g., they may participate in sixteen-way "splatters").

2.2.8 shifter (see block diagram identifier VIII)

2.2.9 indicators (see block diagram identifier IX)

Indicators are storage elements which remember some property of the results obtained in one firmware step so that they may affect the firmware sequence later on. There are arithmetic indicators like "zero" and "carry" which are provided at any byte partition and there are more specialized indicators like the leading-zero detector. Many have the ability to participate in "splatters" which permits up to 17-way firmware branches.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

2.2.10 op registers (see block diagram identifier X)

The op registers permit capturing interesting nibbles of the procedure stream for future reference. The storage mechanisms involved may also receive nibbles from the sbus; they contribute to aram addressing, they may be incremented or decremented, they may be tested for crossing the zero boundary, and they may participate in 17 way branches.

2.2.11 other registers (see block diagram identifier XI)

Many other registers provide strategically located storage for information. Address registers for data and procedure fetches, which can be incremented or decremented, are loaded from the sbus and communicate their content to the memory subsystem. The output data register is loaded from the dbus and communicates its content to the memory subsytem. The v register is connected bidirectionally to the zbus and is a convenient stopover for zbus data. The h register, one of the byte partitionable sources to the dbus, and the accounting timer are also loaded from the sbus.

2.2.12 clock (see block diagram identifier XII)

The clock has a maximum frequency of nearly ten megahertz. It is an asynchronous mechanism whose speed for each step is selected by the firmware assembler. The clock is structured to wait before starting the next step (stall) if the coder wishes, implicitly or explicitly, to postpone its start until an external event occurs (such as receiving previously requested memory subsystem data).

2.2.13 the stack (see block diagram identifier XIII)

The return stack is a mechanism which simplifies the use of subroutines. It contains seventeen levels. Absolute or relative addresses may be "pushed" onto the stack. Unconditional, conditional and masked returns are provided.

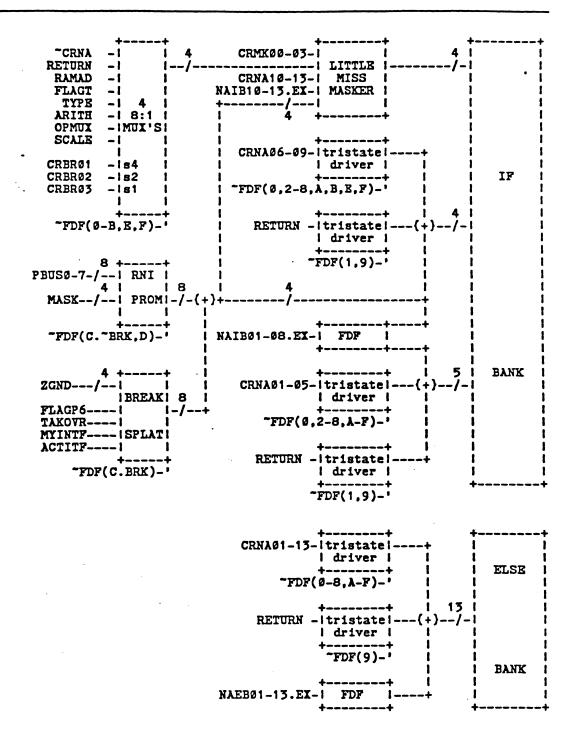

2.2.14 the next address generator (see block diagram identifier XIV)

The next address generator is a particularly flexible element in that it eliminates the need for numeric sequentiality in the execution of firmware steps. The next address may be any one of the 16384 locations provided. The destination may be specified as a "go-to" or it may be chosen from a pair of addresses dependent upon one of seventy-two test conditions. It may instead be chosen among sixteen locations dependent upon some group of four indicators (six groups are provided) or the destination may be a seventeenth location dependent upon one of the seventy-two test conditions. Then again, it may be chosen among one of 256 locations dependent upon a byte of the procedure stream via a table look-up mechanism containing sixteen look-up tables. Or, it may be a subroutine return. Three types of returns are provided: an unconditional return or one which returns depending on one of the seventy-two test conditions or one which returns to an alternate return location as a function of subroutine processing discoveries.

2.2.15 availability

The Custom Processor is possessed of data parity checking circuits, data uncorrectable memory edac error detectors, and firmware parity error detectors. It can also detect references to unavailable system resources, and inappropriate return stack references. Parity bits accompany data sent from the Custom Processor to other system elements allowing them the opportunity of verifying the integrity of the received information.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

....

All Custom Processors include an imbedded comprehensive self-test firmware routine called the quality logic test (QLT) which, at every system initialization, exercises all processor and memory subsystem hardware elements verifying their specified operation. This firmware routine includes a thorough memory array test.

major block diagram goes here

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

HARDWARE DESCRIPTION

## HARDWARE DESCRIPTION

This section describes hardware entities at a level of detail sufficient for comprehension if the reader has a set of custom processor schematics (LBD's) and if the reader has experience in the interpretation of logic diagrams. LBD page references are suffixed with m for mother board or d for daughter board. Reference is also made to the block diagram of 2-3.

The hardware discussion will be subdivided into fifteen zones. Each of these zones is a separable entity that has one or more firmware fields dedicated to its control as shall be seen in section iv.

The fifteen sections and the block diagram identifier are:

- I. Register file and alu (2901's)

- II. Auxiliary random access memory ( $\lambda$ RAM)

- III. D bus

- IV. S bus

- V. Z bus

- VI. Local bus

- VII. Temporary, permanent and control flags

- VIII. Nibble shifter

- IX. Arithmetic and miscellaneous indicators

- X. OP register and OP register multiplexers

- XI. Load of H, V and other registers

- XII. Four-speed clock

- XIII. Return stack

- XIV. Next address generation

- IV. Availability

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

In the text which follows, capitalization is used sparingly so that all signal names and micro names may stand out. Signal name polarities are avoided wherever possible: instead the terms "on" and "off" are used. When, for instance, REQNOW is "on", REQNOW+ is high and REQNOW- is low. This applies even when the signal exists in only one polarity (e.g., "MCX000 is on" means MCX000- is low and would also mean MCX000+ is high were there such a signal. A neutral polarity indicator "." is used for those signal names which achieve uniqueness only in their eighth and ninth . characters (e.g., NAEB13.EX).

3.1 Register file and alu (block diagram identifier I)

The ralu is the resource which performs thirty-two-bit arithmetic and logic operations. It resides between the dbus, from which it receives operands, and the zbus to which it delivers results.

3.1.1 The 2901's (see page 13d)

The ralu is comprised of eight 2901's. These eight chips constitute:

1. a dual-ported 16-location by 32-bit register file

- 2. a 32-bit arithmetic and logic unit

- 5. a 32-bit q register

- 4. a shifting element capable of shifting the alu output one bit left or right.

- 5. a shifting element capable of shifting the concatenation of the alu output and the q register one bit left or right.

- 6. a zero detector, an overflow detector, a sign detector and a carry detector.

3.1.2 Ralu addressing and control (see 1bd pages 3d, 4d and 5d)

The raw control register provides the 2901's almost all of their control inputs:

| <b>A</b> port address | CRAA(00-03) |

|-----------------------|-------------|

| B port address        | CRAB(00-03) |

| source select         | CRAS(00-02) |

| function select       | CRAF(00-02) |

| destination select    | CRAD(00-02) |

#### CUSTOM PROCESSOR TECHNICAL DESCRIPTION

a

1

1

**.** .

3.1.3 Ralu support logic (see page 12d)

The carry look-ahead network is comprised of 74S182's connected in a somewhat unconventional manner. First, the carry into the least significant 2901 (AUCO32) is derived by decoding bits three and four of the AF field to produce four cases:

- AF3 AF4 AUCØ32

- **0 0** cause a carry into alu unconditionally

- 1 cause a carry into the alu if the carry indicator is off

- 6 cause a carry into the alu if the carry indicator is on

- 1 do not cause a carry into the alu

Next, the carry into the second 2901 is from the first's ripple carry. Then the 74S182's take over, providing input carries for the most significant six 2901's. Last, the carry out of the most significant stage ( $\lambda$ UCO00) is derived by combining the G and P outputs of the most significant 74S182 chip using a couple of inverters and a 74S51.

The zero detector of the 2901 is an open-collector output requiring pullup. Eight resistors are required since the leading-zero indicators must examine each individual nibble even though the zero arithmetic indicator is partitioned only to the byte.

The signal ALUTOZ is derived as shown (predecoded) in order to enable/disable the 2901's to the zbus in a timely manner (see 5.0).

5.2 AUXILIARY RANDOM ACCESS MEMORY - ARAM (block diagram indentifier II)

The auxiliary random access memory is comprised of eight 1421-45's. Each chip contains 4096 locations of four bit wide static ram. The aram receives a twelve-bit address from an eight-way selector called rmad. The aram may be read/written to/from the sbus.

3.2.1 Aram read or write (see 1bd pages 17d and 19d-26d)

When written, the aram is byte partitioned. When read, 32 bits of data are placed upon the sbus for normal reads. The signals RAMWCE, RAMICE, RAMYCE, and RAMZCE are the four chip enables. They are structured simply to provide the split cycle sbus capability having a gate for first half cycle, a gate for second half cycle and a gate to "bridge" the early and late gates when the ARAM is the sbus source for the full cycle. The four signals ARMØWR, ARMIWR, ARM2WR, and ARM3WR provide the write enable for the w byte, the x byte, the y byte, and the z byte, respectively. 3.2.2 Aram addressing (see pages 18d and 29d)

#### CUSTOM PROCESSOR TECHNICAL DESCRIPTION

.

• •

The three-bit firmware field RM provides control for an eight-to-one selection of aram addressing sources. Twelve  $74\lambda$ S151's perform the selection resulting in RMAD(00-11). The table below shows what address results from each selection:

| select<br>code | RMAD(00-03)   | RMAD(04-07) | RMADØ8-15)   |

|----------------|---------------|-------------|--------------|

| Ø              | zeros         | GRBR(00-03) | OPRGA(Ø-3)   |

| 1              | zeros         | GRBR(00-03) | . OPRGB(0-3) |

| 2              | zeros         | GRBR(00-03) | OPRGC(Ø-3)   |

| 3              | zeros         | GRBR(00-03) | OPRGD(Ø-3)   |

| 4              | CRFT(01-04)   | CRDK(00-03) | CRDK(04-07)  |

| 5              | s p           | a r         | e            |

| 6              | BSBR(00-03)   | BSAR(00-03) | BSAR(04-07)  |

| 7              | 1,ZBUS(19-21) | ZBUS(22-25) | ZBUS(26-29)  |

grbr is a four bit "general bank" register which permits the sixteen aram locations accessible by opa, b, c, and d to be any block of sixteen in the first 256 aram locations (see 5.11). bsar and bsbr are a four and an eight-bit register which together provide an independent aram addressing mechanism (see 5.11). crft together with crdk provide the "literal" address where crdk is part of the dbus control (see 3.3) and crft normally controls the temporary flags (see 5.7). The last selection has a rather specialized use. It allows 2048 locations of the aram to become a cache of control structures where a field of the zbus is used to access one of the 2048 locations and data in the accessed location can be used to determines hit or miss at the discretion of the microcoder (see 5.9.2.3).

#### 3.3 THE D BUS (block diagram identifier III)

The dbus is a major node in the 32-bit custom processor. It is one of three 32-bit buses but it is the most prolific. Data may be deposited upon it from a wide variety of sources. Such data may then be made available for computation in the ralu, or placed into the output register, or transmitted to the zbus. The dbus is structured as four eight-bit buses, allowing up to four dbus sources to be combined (see section 4.3 for a complete list of the combinations and permutations).

3.3.1 dbus byte w - bits 00-07 (see 1bd pages 17d, 19d and 20d)

Byte w may receive from six mutually exclusive sources which are listed below along with the signal, emanating from a pal, that enables each source:

| source                                | enable signal |

|---------------------------------------|---------------|

| 1. the sbus to dbus latch (LTCH00-07) | LTCHWE        |

| 2. the h register (HREG00-07)         | HREGWE        |

| 5. the zbus (BUS200-07)               | BZTOBD        |

| 4. a fill byte (SGNEXT)               | FILLWE        |

| 5. the 8 bit "j" literal (CRDJ00-07)  | CRDJWE        |

| 6. the 8 bit "k" literal (CRDK00-07)  | CRDKWE        |

|                                       |               |

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

PAGE 3-4

٩.,

There is more discussion of source #1 in 3.4.

At the firmware level, the normal fill bit is CRDF00 which becomes an input to an eight-to-one multiplexer along with three sbus bits in order to provide three types of sbus sign extension as a function of certain dbus control bits (CRDJ02, CRDJ04, and CRDTRE). The output of the multiplexer is replicated 8, 16, 24 or 32 times providing the required fill or sign extension.

3.3.2 dbus byte x = bits 08-15 (see 1bd pages 17d, 21d and 22d)

Byte x may receive from six mutually exclusive sources which are listed below along with the signal, emanating from a pal, that enables each source:

| source                                 | enable signal |

|----------------------------------------|---------------|

| 1. the sbus to dbus latch (LTCH08-15)  | LTCHXE        |

| 2. the h register (HREGØ8-15)          | HREGIE        |

| 3. the shure (MUSZ08-15)               | BZTOBD        |

| 4. a fill byte (SGNEXT)                | FULLXE        |

| 5. pctr/p history (PHST08-15) register | PCTREN        |

| 6. the 8 bit "k" literal               | CRDKIE        |

By examination of the last two characters of the enable signal, one may determine if the source is partitionable or if it is a "broadside" source. In the six sources above, the latch, the h register, the fill, and the k literal are particular sources whereas the zbus and the pctr/p history are not.

3.3.3 dbus byte y (bits 16-23) see 1bd pages 17d, 23d and 24d

Byte y may receive from eleven mutually exclusive sources which are listed below along with the signal, emanating from a pal, that enables each source:

| 80           | urce                                                                   | enable signal          |

|--------------|------------------------------------------------------------------------|------------------------|

| 1.           | the sbus to dbus latch (LTCH16-23)                                     | LTCHYE                 |

| 2.           | the h register (HREG16-23)                                             | HREGYE                 |

| 3.           | the zbus (BUSZ16-23)                                                   | BITODD                 |

| 4.           | a fill nibble (SGNEIT)<br>a fill nibble (SGNEXT)                       | Fillye.03<br>Fillye.47 |

| 5.           | the "j" 8 bit literal (CRDJ00-07)                                      | CRDJYE                 |

| 6.           | the "k" 4 bit literal (CRDK00-03)<br>the "k" 4 bit literal (CRDK04-07) | CRDKYE.03<br>CRDKYE.47 |

| 7.           | the pctr/p history register (PEST16-23)                                | PCTREN                 |

| 8.           | the hex decoder (HEXD00-07)                                            | HEXDEN                 |

| 9.           | the opath registers (OPEGAØ-3, OPEGBØ-3)                               | OPRGYS                 |

| 10.          | the "procedure" mux (PTOD16-23)                                        | Picyen                 |

| <b>f</b> † . | the aram bank registers (GRBR00-03)<br>(BSHR00-03)                     | ASBREN                 |

| •            |                                                                        | DA DA CE 3-5           |

×.,

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

PAGE 3-5

•

Sources #4 and #6 are partitioned at the nibble level in order to support the micro D:RAMAD-X8 (see 4.3).

Source #8 is one byte of the hex decoder, a mechanism which decodes, with a couple of 74S138's, the least significant four bits of the aram address (RMAD08-11) and emits a one in a field of fifteen zeros.

Source #9 allows the op register to be placed upon the dbus.

Source #10 for this byte deposits the output of a 2:1 mux onto the .\_dbus. The two sources on the input of the mux are:

a. the most significant byte of the pbus (BUSP00-07)

b. seven fill bits (CRDFØØ) and the most significant bit of opc(OPRGCØ) which, with the help of the corresponinput on byte z, yields opc/d shifted left one place for the micros D:OPCD-X2 and D:OPCD-X2'1.

Source #11 provides access to the independent aram addressing mechanism.

3.3.4 dbus byte z = bits 24-31 (see lbd pages 17d, 25d and 26d)

Byte z may receive from eleven mutually exclusive sources which are listed below along with the signal, emanating from a pal, that enables each source:

| source                                    | enable signal |

|-------------------------------------------|---------------|

| 1. the sbus to dbus latch (LTCH24-31)     | LTCHZE        |

| 2. the h register (HREG24-31)             | HREGZB        |

| 5. the zbus (BZUS24-31)                   | BZTOBD        |

| 4. a fill byte (SGNEXT)                   | FILLZE        |

| 5. the rmad times 8 mechanism             | PCBREN        |

| 6. the 8 bit "k" literal (CRDK00-07)      | CRDKZE        |

| 7. the pctr/p history register (PHST24-31 | ) PCTREN      |

| 8. the hex decoder (HEXD08-15)            | HEXDEN        |

| 9. the opc&d registers (OPRGCØ-3,OPRGDØ-3 | ) OPRGZE      |

| 10. the "procedure" mux (PTOD24-31)       | PTOYEN        |

| 11. an aram address register (BSAR00-07)  | ASBREN        |

Source #5 implements the least significant eight bits of the micro D:RAMAD-X8 placing onto this byte the high order k literal bit CRDK00, RMAD(08-11), and the next three k literal bits (CRDK01-03).

Source #10 for this byte deposits the output of a 4:1 mux onto the dbus. The four sources on the input of the mux are:

- a. the eight least-significant bits of the pbus (BUSP08-15)

b. the three least significant bits of opc (OPRGC1-3), opd (OPRGDØ-3), and the fill bit (CRDFØØ).

This input along with the corresponding input on byte y allows the dbus to receive opc/d doubled (CRDFØØ=0) or dibbled (CRDFØØ=1) for micros D:OPCD-X2 or D:OPCD-X2'1.

-----

#### HARDWARE DESCRIPTION

c. the most significant eight bits of the pbus (BUSP00-07)

d. registers opc/d shifted right three bits for the micro D:OP-BIT-AD

3.4 THE S BUS (block diagram identifier IV)

The sbus is a very special kind of 32-bit bus. Although it has a limited number of sources and few destinations, it is unique because, in the same step, two different 32-bit sources may be placed upon it. The justification for this construction is that data from the aram must be read, modified and written in the same step (the 1421's share input/output data pins). Thus the sbus is a split-cycle mechanism capable of having data from one source in the early phase of a step (e.g., the aram) and another source during the late phase (e.g., the zbus-shifter). Another unique property of the sbus is its ability to send either the early data or the late data (but not both) to the dbus. This is accomplished via transparent latches which, on a byte-partioned basis, either go blind at mid-cycle (thus capturing the early sbus data) or remain transparent throughout the cycle (thus delivering to the dbus the late sbus data). "Byte partioned" means that micros are provided which permit each dbus byte independent choice of the early sbus information, the late sbus information, or other sources as described in 5.5.

3.4.1 sbus bytes w, x, y, and z (see lbd pages 14d, 15d, 21d, 22d, 17m, 21m, and 33m)

Bytes x, y, and z may receive from eight mutually exclusive sources which are listed below along with the signal which enables each source. These thirty-two bits of the sbus appear on both the mother and daughter boards. Three of the eight sources are on the daughter board and five are on the mother board.

enchie etempi

| source                                                                                                               | enable signal                        |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| <ol> <li>the aram byte v (λRλM00-03)<br/>byte x (λRλM08-15)<br/>byte y (λRλM16-23)<br/>byte z (λRλM24-31)</li> </ol> | Ramwce<br>Ramyce<br>Ramyce<br>Ramzce |

| 2. the shifter a output (SHFT08-31)                                                                                  | SFT1 EN                              |

| 5. the shifter b output (SHFT08-31)                                                                                  | SFT2EN                               |

| 4. the stack top (KTOP06-13) and<br>the accounting timer (ACTM00-15)                                                 | ACTN2S                               |

| 5. the syndrome register (SYND08-31)                                                                                 | SYND2S                               |

| 6. address register a (ADRA08-31)                                                                                    | ADRA2S                               |

| <br>7. address register b (ADRB08-31)                                                                                | ADRB2S                               |

| 8. address register p (ADRP08-31)                                                                                    | ADRP2S                               |

Regarding source #1, the enable circuitry has been discussed in 3.2 but one should note that when writing the aram, both the chip enable (RAMWCE) and the write enable (ARMØWR) must be on. This condition causes the 1421 rams' output circuitry to go to the high impedance state. This arrangement allows the sbus to receive data from any other source while the aram is writing.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

Sources #2 and #3 are listed separately because of the configuration of shifter chips (25510's) used. Sixteen chips, each with four output pins, are connected in a parallel structure such that, as a function of the high order bit of the shift distance (CRSD00), either one or the other group of eight chips is enabled to the sbus (see 3.8).

Source #4 is, at the full sbus level, a collection of two sources which total less than 33 bits. The upper 16 bits "read" the stack top (the firmware address which the next RETURN micro will utilize) and the lower 16 bits "read" the accounting timer (see 3.11.8).

Source #5, the syndrome register, is a mechanism which captures subsystem configuration information, the most recent error event or reason code. The path to the sbus merely allows the coder to view this reason code (for more about errors, see 3.15).

Sources #6, #7, and #8 allow reading adra, adrb, and adrp respectively. For more about these registers, see 5.11.

3.4.2 Sbus enables (see 1bd pages 17d, 10m and 17m)

The sbus control field (CRSS00-02) allows one of six types of sbus cycles in any step. The table shown below summarizes the six cases:

| CRSS00-02 | early           | data i | from            | la         | ate data from |

|-----------|-----------------|--------|-----------------|------------|---------------|

| Ø         | <b>೩</b> ರೆ:    | ra/b/p |                 |            | adra/b/p      |

| 1         | adra/b/p        |        |                 | zbus       |               |

| 2         | synd/actm.stack |        | synd/actm.stack |            |               |

| 3         | <b>z</b> 1      | bus    |                 |            | zbus          |

| 4         | 8               | P      | a               | r          | e .           |

| 5         | 8               | P      | a               | . <b>r</b> | e             |

| 6         | a               | ram    |                 |            | aram          |

| 7         | 8               | ram    |                 |            | zbus          |

The aram split cycle controls are discussed in 5.2. The general technique for the shifter and the address registers is the same; namely, there is an input on each enable circuit for the early half of the cycle and another for the late half.

The shifter enable circuits receive an input from a flop (CRSSE3) which predecodes the control store word looking for the only code which requires the zbus to the sbus during the early phase (i.e., code 3). The late input is decoded in a pal.

The early gate on the address register enable circuits (ADRA2S, ADRB2S, and ADRP2S) is timed with MCLOCK whereas the late inputs are essentially untimed. Notice that the choice among adra/b/p is the responsibility of the BS field and not of the SS field. The 74S139 which decodes two bits of BS for this purpose is enabled for codes 0, 1, 4, and 5, but 4 and 5 are not used and 0 and 1 are the codes which deposit adra/b/p to the sbus.

3.5 THE Z BUS (block diagram identifier V)

The zbus is a place where the ralu may deposit its computations, is the bus upon which external data arrives (from inra/b) and is the bus which feeds the nibble shifter.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

PAGE 3-8

٠.

-• • • HARDWARE DESCRIPTION

3.5.1 zbus sources (see 1bd pages 16d, 29d, 32d, 33d, and 34d)

The zbus is thirty-two bits wide and receives from six thirty-two-bitwide sources. Along with the ralu and the input data registers, the zbus may receive from the v register, the dbus, and from an external connection (i.e., the firmware development facility). The six sources are listed below along with their respective enable signals:

| source                               | • . | enable signal |

|--------------------------------------|-----|---------------|

| 1. inra (INRA00-31)                  | ۴   | CRIA2Z        |

| 2. inrb (INRB00-31)                  |     | CRIB2Z        |

| <pre>5. v register (VREG00-31)</pre> |     | VREGEN        |

| 4. ralu (λLUY00-31)                  |     | ALUTOZ        |

| 5. the dbus (BUSD00-31)              |     | DBTPZB        |

| 6. the fdf (BUSZ00-31.EX)            |     | CRTB2Z        |

3.5.2 zbus enables (see 1bd pages 12d, and 32d)

The ZB field controls the zbus sources as shown below:

| crzb(00-02) | source | enable signal |

|-------------|--------|---------------|

| 0           | ralu   | ALUTOZ        |

| 1           | fdf    | CRTB2Z        |

| 2           | inra   | CRIA2Z        |

| 3           | inrb   | CRIB2Z        |

| 4           | dbus   | DBTOZB        |

| 5           | vreg   | VIRHEN        |

| 6           | inra   | CRIA2Z        |

| 7           | inrb   | CRIB2Z        |

All six enables emanate from a pal which decodes crzb. Codes Ø through 5 produce results previously discussed. When inra or inrb is placed upon the zbus as a result of code two or three a parity check is performed on all four bytes. When inra or inrb is placed upon the zbus as a result of code six or seven, a parity check is performed on only the two most significant bytes.

3.6 THE LOCAL BUS (see block diagram identifier VI)

The local-bus hardware can be divided into four sections:

An addressing mechanism

A data storage mechanism

A procedure storage mechanism and

Local-bus control circuitry

The BS field is responsible for managing the resources represented by the above list which contains three address registers, 64 bits of procedure stream storage, and 64 bits of data storage.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

3.6.1 Local bus addressing (see lbd pages 18m, 19m, and 20m)

Addresses from the processor to the memory subsystem(s) may emanate from one of three sources: adra, adrb, or adrp. A three-to-one mux is formed using 74S241's selected by ADRAEN, ADRBEN, and ADRPEN. Once the selection has been made, the address is latched via another group of 74S241's connected as a batlatch. (A batlatch is used to eliminate propagation delay. Batlatches require delicate timing.) Thirty nanoseconds into a firmware step which has made a local bus request, the flop ABATEN comes on, enabling the batlatch which connects its input to its output. About thirty nanoseconds later, ADRSOF comes on, disabling the multiplexer. The batlatch thereby swallows its tail.

3.6.2 Local bus data storage (see 1bd pages 32d, 33d, 34d and 34m)

Data from the local bus is captured off the local bus with a transparent latch (i.e., four 74S373's). The behavior of the signal LBLOOK is that it puts the latch in transparent mode sometime after the request to memory has been made; as soon as the memory signals that valid data is present on the interface (DCNNUS), the latch is closed. The data may now be safely transferred to either inra, or inrb dependent upon which was requested.

The signals DALOOK and DBLOOK perform the transfer of data from the local-bus latch to inra or inrb. During the step in which the request was initiated, both these 'looks' clear. At the beginning of the step immediately following the request, the appropriate look activates causing the latched data to flood into inra or inrb. The look signal remains on until the next local-bus request occurs.

3.6.3 Local-bus procedure storage (see 1bd pages 15m, 16m, 28m, 30m, 34m

The mother board captures local-bus data in the same manner as the daughter board, using a duplicate set of 74S373 transparent latches. From the local bus latch, the information moves into the procedure "prefetch" buffer. This buffer receives procedure 32 bits at a time and dispenses procedure either eight or sixteen bits at a time. In order to allow for enough look-ahead, the procedure buffer can remember eight bytes (64 bits). Thus the destination for each 32-bit delivery from the local-bus latch alternates; the first 32 bits are placed in the procedure buffer at bytes a, b, c, and d; the second 32 bits are placed in the procedure buffer at bytes e, f, g, and h; the third 32 bits are placed in a, b, c, and d again etc. The alternation results from the look signals (PALOOK and PELOOK) taking turns, because pareqt and pereqt take turns because FRELOD complements each time a procedure request is made.

In order to dispense one byte at a time, eight 74S373 chips form this 64-bit storage register with their outputs connected together to form an eight bit bus. The output of this network is called BUSP00-07. A three bit counter, called the take counter, keeps track of which byte is next for delivery onto BUSP00-07. When PTAKE4/2/1=0, the first latch chip \*(INRPA0-7) is enabled onto BUSP00-07, when PTAKE4/2/1=1 then INRPB0-7 is enabled onto BUSP00-07 ... and when PTAKE4/2/1=7, then INRPH0-7 is enabled onto BUSP00-07.

In order to dispense two bytes of procedure at a time, eight more 74S373's form a completely duplicate 64 bit storage register also with their outputs connected together to form an eight-bit bus, but this bus is called BUSP08-15 and the network differs from the one previously described only in enabling. Above, when PTAKE4/2/1=1, BUSP00-07 received from INRPB0-7; in that instance, the secondary buffer enables INRPC0-7 to BUSP08-15. Thus whatever byte the take counter sends to BUSP08-15 from the primary procedure buffer, the next byte in line is sent to BUSP08-15 from the secondary buffer.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

Decoding the take counter is accomplished with a 745138. The take counter itself is comprised of three 745112 j/k flops which, with the help of a pal, increment by zero, one, or two each firmware step, recording the removal of procedure bytes.

3.6.4 Local-bus control circuitry (see lbd pages 9m, 11m, 28m and 33m)

Sometime during the middle of each firmware step, the address of the next firmware step is determined by mechanisms described in 3.14. Sometime near the end of each firmware step, the output of the control-store array "(the next firmware word) becomes valid. The BS field emanates from the control-store array at bits 120-127 (CSBSC0-7) and is captured in eight control register flops (CRBUS0-7). Processor timing is such that CSBSC0-7 are valid 20ns before the end of each step allowing certain decisions to be made before the next step actually begins. Two decisions are made which are related:

- 1. Does the action in the upcoming step require that a request

- to a memory subsystem be intiated?

- 2. Does the action in the upcoming step require that the present step be delayed in terminating?

If, for any reason, a transaction between the processor and a memory subsystem is in process, the signal REQNOW is on. As an illustration of the two decisions above, suppose a firmware sequence is encountered which calls for two memory writes in two consecutive firmware steps. As the first step nears completion, CSBSC0-7 alerts the request logic (REQTEN, REQUST, and the flop USREQT) that the next step will initiate (another) transaction but, since only one transaction may proceed at a time and since the first memory write is still in process, this step must be delayed in terminating (stalled). Thus, REQNOW and CSBSC0-5 have a significant impact upon the clock logic (see 5.12). USREQT gets a chance at the beginning of every step and is, of course, structured to assume that whatever stall was required, has occurred and has been released.

A summary of the control sequence is as follows:

- 1. USREQT comes on at the beginning of any step which initiates a memory-subsystem transaction.

- 2. An array of PALs determines whether the request is to be sent to Memory Subsystem #1 (or Memory Subsystem #0)

- a. M1REQT is clocked by USREQT and activates if the tri-state request collector M1RQTD.00 is true

- b. M1RQTD.01-03 are active in 32-bit address systems ( $\lambda$ DDR32=1) if M1PRZT (M1 present) is true

- c. M1RQTD.-04,05 are active in 24-bit address systems ( $\lambda$ DDR32=0) if M1PRZT (M1 present) is true

- d. M1RQTD.04 is active to disengage the network if M1 is not present

- e. MØREQT is also clocked by USREQT and activates for all cases where M1REQT does not:

Memory Subsystem #1 not present

A lock/unlock memory reference

- A memory reference not in M1 space

- A non-memory reference

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

- 2. immediately, REQNOW comes on.

- 3. the memory subsystem "grants" the processor. (If the memory subsystem was not busy, the grant arrives in about 50ns; but if it was busy, who knows.)

- 4. about 50ns after the grant is received, USREQT goes off.

- 5. now REQNOW is in charge and will remain on until the transaction completes:

- a. for memory reads, when data arrives from memory (DCNNUS signals the arrival and OUTREN is off)

- b. for i/o reads, when the data arrives from the MEGABUS (second-half bus cycle) via the memory subsystem (DCNNUS signals the arrival and OUTREN is off)

- c. for 1/o reads where no data arrives, when grant (RQGTUS) goes off.

- d. for all writes, when grant goes off.

Once the request is initiated, the firmware sequence is permitted to go on its merry way, ignoring the local-bus interface until such time as a resynchronization point is encountered (e.g., a data stall, a new local bus transaction initiation). During this interval, the transaction is remembered in three storage elements:

1. the thirty-two-bit address is in the batlatch of 3.6.1

2. the data to be written (if any) is in outr

3. the control information is in the "fred" register Item #3 above is comprised of two registered pals. One pal monitors eight inputs and creates six local-bus control signals. Notice that the pal is allowed to change its output values only on the leading edge of each new memory subsystem request, snapshotting its other seven inputs to decide whether this transaction is:

- 1. a write? (FWRITE)

- 2. a doubleword read/write? (FRDBLW)

- 3. a lock/unlock? (FRLOCK)

- 4. a memory reference? (FRMREF, two copies)

- 5. to use adra, adrb or abrp? (FRBUS2/3)

- 6. to capture the ACK/NAK indicator (ACKREN)

A second pal (16R6B) monitors four inputs and generates three outputs deciding whether this transaction is:

- 1. to send a response notification? (LBSHBC)

- 2. to write only eight bits of the first sixteen (LBWCT1) Note: other system elements refer to this signal as xxBYTE

- 3. to write all sixteen bits of the second sixteen (LEWCT2) Note: other system elements refer to this signal as xxDBPL

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

HARDWARE DESCRIPTION

.

A third pal (16R6b) monitors ten inputs and creates four local-bus related outputs which determine whether this step is:

1. one which initiates a local bus request (CRREQT)

2. one which performs a local bus "wrap" test (CRWRAP)

3. one which will consume (one or two bytes of) procedure

4. one which will change the procedure steerage mechanism (FRELOD). If FRELOD=0, arriving prefetched procedure is captured by procedure buffers  $\lambda$ , B, C, and D. If FRELOD=1, arriving prefetched procedure is captured by procedure buffers B, F, G, and H.

3.7 TEMPORARY, PERMANENT AND CONTROL FLAGS (block diagram identifier VII)

There are twenty-four flags organized as three groups of eight. Sixteen of the twenty-four are controlled by one firmware field while the other eight have their own.

3.7.1 temporary flags (see 1bd pages 9m, 24m and 29m)

The temporary flags are controlled by the FT field (CRFT00-04). Seventeen of the thirty-two possible codes are devoted to the temporary flags; one to clear them all, eight to set one of them at a time and eight to clear one of them at a time. The flops themselves are a 74LS259. One pal output (CLRTFL) determines when a broadside clear occurs, and another (FLGTEN) determines when a one-bit change occurs. The polarity of the change is determined by the data input CRFT00. Which flop is to change is determined by the select inputs CRFT02-04. The eight outputs are synchronized by a 74S374 and sent to eight test-condition inputs (see 5.14). FLGT6E, temporary flag 6 before synchronization, is the data bit written into the stop code ram (see 5.9.2.1). 3.7.2 permanent flags (see 1bd pages 15m, 28m and 29m)

The permanent flags are controlled by the BS field (CRBUS0-7). Sixteen of the possible 256 codes are devoted to the permanent flags; eight to set one of them at a time, and eight to clear one of them at a time. The flops themselves are a 74S259. A broadside clear occurs at master clear. A pal output (FLGPEN) determines when a one bit change occurs. The polarity of the change is determined by CRBUS3. Which flop is to change is determined by the select inputs CRBUS5-7. The eight outputs are synchronized by a 74S374 and sent to eight test conditions (see 3.14). Permanent flag #7 (FLAGP7) is one of the "break" stimuli.

3.7.3 control flags (see 1bd pages 24m, 27m, 29m and 33m)

The control flags are controlled by the BS field (CRBUS0-7). Sixteen of the possible 256 codes are devote to the control flags; eight to set one of them at a time, and eight to clear one of them at a time. The flops themselves are a 74LS259. A broadside clear occurs at master clear. A pal output (FLGCEN) determines when a one-bit change occurs. The polarity of the change is determined by CRBUS3. Which flop is to change is determined by the select inputs CRBUS5-7. The eight outputs are sychronized by a 74S374 and sent to eight test conditions (see 5.14). Some of the control flops have side-effects:

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

....

| FLAGCO  | off line                                        |

|---------|-------------------------------------------------|

| FLAGC1  | qlt failed (if flagc0 is off)                   |

| FLAGC2  | generate even parity to outr (if flagc0 is off) |

| FLAGC 3 | enable the accounting timer                     |

| FLAGC4  | undedicated                                     |

| FLAGC5  | inhibit disaster                                |

| FLAGC6  | undedicated                                     |

| FLAGC7  | stack error detection enable                    |

3.8 NIBBLE SHIFTER (see block diagram identifier VIII)

The nibble shifter is the only connection between the zbus and the sbus and is therefore in a critical path. The shifter is really an eight nibble rotator; there is no distinction for instance between, shifting three nibbles left and shifting five nibbles right. 5.8.1 shifter data flow (see lbd pages 11d, 14d and 15d)

The shifter is implemented with sixteen 25510's connected as two parallel groups of eight. The first group is enabled when the shift distance prescribed by the SD field (CRSD00-02) is either zero, one, two or three, and the second group is enabled when the shift distance is either four, five, six, or seven.

The 25S10 whose output names are SHFT00.SA, SHFT04.SA, SHFT08.SA and SHFT12.SA reveals first that this chip is enabled for shift distances of 0, 1, 2, or 5 and that for a distance of zero, the chip internally connects its four outputs to its lowest four inputs; for a shift distance of one, the four outputs are connected to the next higher four inputs; for a shift distance of two, to the next higher four inputs; and for a shift distance of three, to the top four data inputs.

The second group of eight shifter chips operates like the first, but are enabled for shift distances of four or more and thus their data inputs are wired bias by sixteen bit positions.

5.8.2 Shifter control (see 1bd pages 10m, 11d, 14d, 15d and 17d)

Since the shifter deposits its result onto a split-cycle bus, the enable requires early/late timing. For SS (CRSS00-2) code three only, the shifter is enabled to the sbus during the early phase; a pal generating signals S1LATE and S2LATE determines what circumstances allow the shifter to the sbus during the late phase.

3.9 ARITHMETIC AND MISCELLANEOUS INDICATORS (block diagram identifier IX)

There are six arithmetic indicators and eight miscellaneous indicators. The intent of these indicators is to allow the coder to remember some characteristic(s) of some data for the purpose of affecting the addressing sequence of a subsequent firmware routine.

3.9.1 arithmetic indicators (see 1bd pages 5d, 12d, 13d, 27d and 28d)

Five of the six arithmetic indicators derive their inputs from the output of the alu. The sixth samples the least-significant bit of the zbus (BUSZ31). In addition to storage for the indicators, four 4:1 muxes are employed. Three of the muxes are halves of 74S153's and one is a 74S64.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

· · -

#### HARDWARE DESCRIPTION

The overflow mux (OVFMUX) selects one of four 2901 overflow signals as a function of the ID code (CRID00,01) as follows:

| CRID00,01 | overflow source                                               |

|-----------|---------------------------------------------------------------|

| 00        | carry into alu bit 24 not equal to carry<br>out of alu bit 24 |

| 01        | carry into alu bit 16 not equal to carry<br>out of alu bit 16 |

| 10        | carry into alu bit 08 not equal to carry<br>out of alu bit 08 |

| 11        | carry into alu bit 00 not equal to carry<br>out of alu bit 00 |

The carry mux (CRYMUX) samples one of four alu carries as a function of the ID field as follows:

| CRID00,01 | carry source            |

|-----------|-------------------------|

| 00        | carry out of alu bit 24 |

| 01        | carry out of alu bit 16 |

| 19        | carry out of alu bit Ø8 |

| 11        | carry out of alu bit 00 |

The sign mux (SGNMUX) samples one of four alu "signs" as a function of the ID field as follows:

| CRID00,01 | sign source       |

|-----------|-------------------|

| 00        | alu output bit 24 |

| 01        | alu output bit 16 |

| 19        | alu output bit 08 |

| . 11      | alu output bit 00 |

The zero mux (SZRMUX) samples four groupings of bits as a function of the ID field as follows:

| CRID00,01 | zero source                            |

|-----------|----------------------------------------|

| 00        | if alu output bits 24-31 are all zeros |

| 01        | if alu output bits 16-31 are all zeros |

| 10        | if alu output bits 08-31 are all zeros |

| 11        | if alu output bits 00-31 are all zeros |

These four mux outputs are stored into the overflow indicator (OVFIND), the carry indicator (CRYIND), the sign indicator (SGNIND), and the zero indicator (SZRIND) at the behest of a pal output (AINDEN). Also captured are the double zero indicator (DZRIND) and the odd indicator (ODDIND). A code emanating from the FT field causes the arithmetic indicators to "clear" such that four indicators are off and the zero and double-zero indicators are on.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

3.9.2 miscellaneous indicators (see lbd page 27d)

The eight miscellaneous indicators can be divided into one group of four and four groups of one. A pal output (BINDEN) determines when the miscellaneous indicators sample their inputs. 3.9.2.1 SCRAM indicator

The stop code ram is a 256-location by one-bit-wide memory addressed from byte y of the dbus. It is written from FLGT6E under command of a pal output (WRSCRM) modulated with appropriate timing. Its data output is captured along with the other seven miscellaneous indicators when the pal output BINDEN occurs.

#### 3.9.2.2 DIFBUF indicator

This mechanism compares eight bits of the dbus with eight bits of the zbus utilizing a 74F521.

3.9.2.3 HASHIT indicator

This mechanism compares thirteen bits of the zbus with thirteen bits of the sbus utilizing two 25LS2521's.

#### 3.9.2.4 ILLADD indicator

This mechanism uses a 16L8A pal to decide whether the rightmost byte of an operand is in the same 512-byte buffer as a specified base address. The pal assumes that the base address and the displacement locating the leftmost byte of an operand are being added in the alu, that one of these values is on the dbus, and that the type register contains the operandlength information (1, 2, 4 or 6 byte operand). The pal would prefer a carry signal out of alu bit 23 but one is not available so the pal derives it from the input carry to alu bit 25 (AUCO24), the dbus bit 23 (BUSD23) and the sum bit 23 (BUSZ23).

3.9.2.5 leading zero detector

This mechanism, utilizing a 16L8A pal, determines the number of leading zeros present in the value from the alu. The pal receives the zero detector from each of the eight 2901's. The outputs from the pal (AUP208, AUP204, AUP202, and AUP201) are captured in the miscellaneous indicators. The four indicators (P28IND, P24IND, P22IND, and P21IND) are coded such that: 0000 means no leading-zero nibbles were detected, 0101 means that five leading-zero nibbles were detected and 1000 means the entire alu output was zero.

**5.10** THE OP REGISTER (block diagram identifier I)

Certain bytes and/or nibbles of the procedure stream must be stored for future reference. The four 4-bit wide registers opa, opb, opc and opd provide said storage. These four registers can also be loaded from the sbus, can be incremented or decremented, and have the ability to address the aram. The seven bit field OP controls the entire op area.

3.10.1 the sbus multiplexer (see 1bd pages 10d and 31d)

When the op register(s) are to be loaded from the sbus, the sbus multiplexer (SMUI00-15) is required to narrow the 32-bit sbus to a width of 16 bits, matching the width of the op muxtiplexer. CROP02 decides which half of the sbus is chosen.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

3.10.2 the op multiplexer (see lbd pages 10d and 31d)

The op multiplexer (OPMI00-15) is comprised of four 16L8A pals. Each pal has four data outputs, nine data and four control inputs. At the first level, the choice is between the pous data inputs and the sbus data inputs. At the next level, a choice of which nibble of the selected bus is to be directed to the output (sort of a rotate). And at the last level, a choice as to whether the four bit literal inputs (CRFT01-04) should be presented to the outputs. All this is controlled by the inputs CROP00-03.

3.10.3 The op registers (see 1bd page 312)

There is a 74 $\lambda$ S169 for each of  $\neg$ pa (OPRGAØ-3), opb (OPRGBØ-3), opc (OPRGCØ-3), and opd (OPRGDØ-3). Loading, incrementing or decrementing is controlled by a pal which emits, for each register, one load signal and one count signal. For opa, the load signal is OPALOD and the count signal is OPAPAT. When the count signal is on, the appropriate op register increments if cropØ2 is on and decrements otherwise. OPATOP, OPBTOP, OPCTOP, and OPDTOP are provided to detect when the counter in question is "wrapping" (in the firmware verna- cular) i.e., incrementing from F to zero or decrementing from zero to F.

3.10.4 the type register (see lbd page 5:d)

The type register stores two bits in a 74S169. The input to the type register is the same as the two most significant inputs of opa. The unused two stages of the 74S169 are wired so that when the type is 11 (three), the "carry" output of the chip (TYPIS3) will be on. A signal from the FT field (CLRTFL) clears the type register and a load signal (TYPELD), also from an FT pal, performs the load honors.

3.11 LOADING VARIOUS REGISTERS (block dizgram identifier XI)

Many firmware fields have no other purpose but to control the loading of various registers. These fields are H, LA, LO, and LV. Other fields have a secondary justification for existence by providing the load controls to certain registers in need. These fields are BS and FT.

3.11.1 loading the H register (see 1bd pages 10d, 17d, 20d, 22d, 22d, 26d)

The H register is loaded at the behest of a dedicated control store bit (CSH056) with its attendant control-register flop (CRH000) pulse-formed in HREGLD.

5.11.2 loading the output register (see 1bd pages 11d and 35d)

The output register (OUTR00-31) is loaded at the behest of a dedicated control store bit (CSLOA0) with its attendant control-register flop (CRLO00) pulse-formed in outrck. Note that 36 bits are captured with this load stimulus; namely, the 32 bits of the dbus and four byte-parity bits in flops OUTR0P, OUTR1P, OUTR2P, and OUTR3P. These four parity bits are generated by four 82s62 parity generator/checker—chips called MYDP00, MYDP08, MYDP16, and MYDP24. See section 3.15 for more about checking.

3.11.3 loading the v register (see 1bd pages 11d and 34d)

The v register (VREG00-31) is loaded at the behest of a dedicated control-store bit (CSLV96) with its attendant control register flop (CRLV00) pulse-formed in vregid.

CUSTOM PROCESSOR TECHNICAL DESCRIPTION

Ξ.

5.11.4 changing adra, adrb, and adrp/pctr (see lbd pages 10m, 26m 17d, 21d, 23d and 26d)

Four control-store bits (CSLAB6-9) and four cr flops (CRLA00-03) are provided to control the changing of the three address registers. Each address register is thirty-two bits long and is comprised of four 74AS869 chips. Address registers adra (ADRA00-31) and adrb (ADRB00-31) may be loaded from the shus, or may be incremented by four, or may be decremented by four. The address register adrp (ADRP00-31) may be fully loaded from the shus or may have only its nine least significant bits copied from the sbus or may have its twenty-three-most-significant bits copied from the sbus. Note that adrp is implicitly incremented by four whenever four procedure bytes are requested from the memory subsystem.

The pal which controls all this generates two mode bits ( $\lambda DR\lambda MØ,1$ ) and a carry-in ( $\lambda DRACI$ ) for adra, and two mode bits ( $\lambda DRBM0,1$ ) and a carry-in ( $\lambda DRBCI$ ) for adrb. When  $\lambda DRA/BMØ=0$  and  $\lambda DRA/BM1=1$ , the register decrements; when mØ=1 and m1=0, the register increments; and when mØ=1 and m1=1, the register loads from the sbus.

For adrp, the pal generates two load signals (PULOAD, PLLOAD) for copying twenty-three or nine sbus bits into adrp. Because of the particular and the necessity to increment by four, a thirty-third flop is required to store  $\lambda$ DRP30.

The register PCTR(08-30) mimics adrp for loading actions. Its bit justification in the three 74 $\lambda$ S869 chips permit incrementing by one or two when procedure bytes are removed from the prefetch buffer. When pctr is delivered to the dbus, the least-significant bit of the take counter (PTAKE1) becomes the units position of pctr.

5.11.5 changing grbr (see lbd page 30d)

The four-bit register GRBR( $\emptyset\emptyset-\emptyset3$ ) is used in combination with opa,b,c, and d to address the aram. The OP field controls grbr. A 16R8A pal receives the seven control-store bits of the OP field and generates control signals for the 74AS169 chip which houses grbr. The pal output GRBRLD causes GRBR( $\emptyset\emptyset-\emptyset3$ ) to load from the four most significant bits of the opmux (OPMI00-03). The pal output GRBRPT causes GRBR( $\emptyset\emptyset-\emptyset3$ ) to increment by one or decrement by one as a function of CROP02. If CROP02 is on, grbr increments; if CROP02 is off, grbr decrements. The firmware name for grbr is rbr.

3.11.6 changing bsbr (see lbd page 30d)

### CUSTOM PROCESSOR TECHNICAL DESCRIPTION

PAGE 3-18

7.

The four-bit register BSBR(00-03) is used in combination with BSAR(00-07) to address the aram. The OP field controls bsbr. A 16R8A pal receives the seven control-store bits of the OP field and generates control signals for the 74AS169 chip which houses bsbr. The pal output BSBRLD causes BSBR(00-03) to load from opmux bits 4-7 (OPMX04-07). The pal output BSBRPT causes BSBR(00-03) to increment by one or decrement by one as a function of CROP02. If CROP02 is on, bsbr increments; if CROP02 is off, bsbr decrements. The firmware name for bsbr is rarh.

3.11.7 changing bsar (see lbd page 30d)

The eight-bit register BSAR(00-07) is used in combination with bsbr to address the aram. The OP field controls bsar. A 16R8A pal receives the seven control-store bits of the OP field and generates control signals for the two 74AS169 chips which house bsar. The pal output BSARLD causes BSAR(00-07) to load from the eight-least significant bits of the opmux (OPMI0815). The pal output BSARPT causes BSAR(00-07) to increment by one or decrement by one as a function of CROP02. If CROP02 is on, bsar increments; if CROP02 is off, bsar decrements. The firmware name for bsar is rarl.

3.11.8 loading the accounting timer (see 1bd pages 24m and 33m)

The accounting timer is a mechanism which provides real time information for job accounting and other purposes. The accounting timer is constructed from two 74 $\lambda$ S869 counter chips wired to either load or increment. The timer ( $\lambda$ CTM00-15) has a 100 microsecond period (i.e., it is incremented at a 10khz rate when enabled by FLAGC3). It is loaded by an FT-field micro decoded by a 16L8A pal ( $\lambda$ CTMLD) which invokes an implicit clock stall (see5.13) whose purpose is to insure that an accounting timer clock (MHZ001) occurs while the data to be loaded from the sbus is valid at the inputs of the 74 $\lambda$ S869 chips. Note that when the accounting timer increments from 65,535, an accounting timer interrupt ( $\lambda$ CTINT) is stored. This interrupt (synchronized through  $\lambda$ CTITF) asserts the break stimulus and thereby causes a "derail" at the next sample of break by the RNI macro.

3.12 THE FOUR SPEED CLOCK (block diagram identifier XII)

The custom processor resides in an asynchronous world. The custom processor clock is an asynchronous mechanism. The clock has two orthogonal properties:

1. the clock allows the duration of each firmware step to be any one of four lengths as a function of the combination of micros coded in that step.

2. the clock allows each firmware step to delay its completion until some external event occurs.

3.12.1 the basic clock (see lbd pages 3m and 4m)

The basic clock has three delay lines, three delay-line drivers, one one 74S64 and two switch banks for adjustment purposes. Two of the three delay lines are connected in parallel. When MCI000 occurs because all of its inputs are high (take it on faith), a positive to negative edge travels down the 100ns delay line MCI010 through MCI100. At about the same time, MCI010 creates an edge of the opposite polarity (negative to positive) traveling down the delay line MCPW05 through MCPW50. The outputs of this latter delay line are switch selected to create the width of MCLOCK. This is accomplished by connecting the output of the switch bank (MCKPWA) through a 74S64 (MCSTLA) to the original delay line driver (MCI000) making one of its inputs low which achieves a pulse width of about 70ns. Having established that a "negative" seventy-nanosecond pulse is wending its way down the MCI010-100 delay line, it is now appropriate to pursue what happens to cause the cycle to complete (and start over). In

CUSTOM PROCESSOR TECHNICAL DESCRIPTION