| HONEYWELL BULL                 | SPECIFICATION NUMBER          | DISTRIBUTION | SHEETS | REV |

|--------------------------------|-------------------------------|--------------|--------|-----|

| BILLERICA                      | 60165905                      | CODE C40C    | 1/xx   | 1   |

| CUSTOM AND<br>SPECIAL PRODUCTS | TITLE:                        |              |        |     |

| PREPARED BY                    | PRODUCT TECHNICAL DESCRIPTION |              |        |     |

| R Lemay                        | 16-BIT CUSTOM PROCESSOR       |              |        |     |

| APPROVED BY                    | 1                             |              |        |     |

ha

| REVISION | AUTHORITY | DATE    | SIGNATURE | SHEETS AFFECTED |  |

|----------|-----------|---------|-----------|-----------------|--|

| Α        | Draft     | 01JUL82 | R. Lemay  | all             |  |

| 0        | Ultimate  | 01JUL83 |           | all             |  |

| 1        | Ultimate  | 01JAN88 |           | all             |  |

This revision is issued to reflect changes attendant in the redesign of, the Custom Processor. The new functionality is summarized in Appendix A.

## TABLE OF CONTENTS

This document and the information contained herein are confidential to and the joint property of the Ultimate Corporation and of Honeywell Bull Corporation printed for the sole purpose of conducting their businesses. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager, and shall not be disclosed or distributed (a) to persons who are not Honeywell Bull or Ultimate employees, or (b) to Honeywell Bull or Ultimate employees for whom such information is not necessary in connection with the execution of their assigned duties. Upon request, or when the employee in possession of this document no longer has need for the document for authorized Honeywell Bull or Ultimate purposes, this document and any copies thereof shall be returned to the employee's manager. Deviation from this policy may only be authorized by a Honeywell Bull or Ultimate Vice President.

PAGE i-1

TABLE OF CONTENTS

## TABLE OF CONTENTS

## SECTION ONE

| 1.0     | INTR | ODUCTION                                                                                                                                                                                                                                                                                                                                                    | 1.                   | -1               |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|

|         | 1.1  | Purpose                                                                                                                                                                                                                                                                                                                                                     | 1.                   | -1               |

|         | 1.2  | Scope                                                                                                                                                                                                                                                                                                                                                       | 1.                   | -1               |

|         | 1.3  | Disclaimer                                                                                                                                                                                                                                                                                                                                                  | 1-                   | -1               |

|         | 1.4  | References                                                                                                                                                                                                                                                                                                                                                  | 1-                   | -2               |

| SECTION | TWO  |                                                                                                                                                                                                                                                                                                                                                             |                      |                  |

| 2.0     | OPER | ATIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                            | 2-                   | -1               |

|         | 2.1  | System environment                                                                                                                                                                                                                                                                                                                                          | 2-                   | -1               |

|         | 2.2  | Introductory description                                                                                                                                                                                                                                                                                                                                    | 2-                   | -3               |

|         |      | <pre>2.2.1 the ralu<br/>2.2.2 the aram<br/>2.2.3 the dbus<br/>2.2.4 the address bus<br/>2.2.5 the zbus<br/>2.2.6 the system bus<br/>2.2.7 flags<br/>2.2.8 the shifter<br/>2.2.9 indicators<br/>2.2.10 op registers<br/>2.2.11 other registers<br/>2.2.12 the clock<br/>2.2.13 the stack<br/>2.2.14 the next address generator<br/>2.2.15 availability</pre> | 2-<br>2-<br>2-<br>2- | 3334444444555555 |

| SECTION | THRE | E                                                                                                                                                                                                                                                                                                                                                           |                      |                  |

| 3.0     | HARD | NARE DESCRIPTION                                                                                                                                                                                                                                                                                                                                            | 3-                   | -1               |

|         | 3.1  | Register file and alu                                                                                                                                                                                                                                                                                                                                       | 3-                   | -2               |

|         |      | 3.1.1 the 2901's<br>3.1.2 ralu addressing and control<br>3.1.3 ralu support logic                                                                                                                                                                                                                                                                           | 3-<br>3-<br>3-       | -2<br>-2<br>-2   |

|         | 3.2  | Auxiliary Random Access Memory                                                                                                                                                                                                                                                                                                                              | 3-                   | -3               |

|         |      | 3.2.1 aram read or write<br>3.2.2 aram addressing                                                                                                                                                                                                                                                                                                           | 3-<br>3-             | -3<br>-3         |

|         | 3.3  | The D Bus                                                                                                                                                                                                                                                                                                                                                   | 3-                   | -4               |

|         |      | 3.3.1 dbus byte x<br>3.3.2 dbus byte y<br>3.3.3 dbus byte z                                                                                                                                                                                                                                                                                                 | 3-<br>3-<br>3-       | -4<br>-5<br>-6   |

PAGE i-2

| 3.4 The Address Bus                                                                                                                 | 3-6                          |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 3.4.1 address bus data flow<br>3.4.2 address bus enables                                                                            | 3-7<br>3-7                   |

| 3.5 The Z Bus                                                                                                                       | 3-8                          |

| 3.5.1 zbus sources<br>3.5.2 zbus enables                                                                                            | 3-8<br>3-8                   |

| 3.6 The System Bus                                                                                                                  | 3-9                          |

| 3.6.1 megabus cache addressing<br>3.6.2 megabus cache data storage<br>3.6.3 megabus cache procedure storage                         | 3-9<br>3-9<br>3-9            |

| 3.6.3.1 the procedure bus 3.6.3.2 the procedure bus latches                                                                         | 3-10<br>3-10                 |

| 3.6.4 megabus control circuitry                                                                                                     | 3-10                         |

| 3.6.4.1 writes<br>3.6.4.2 reads<br>3.6.4.3 reads                                                                                    | 3-11<br>3-12<br>3-10         |

| 3.6.4.3.1 cache/local memory reads<br>3.6.4.3.2 MEGABUS reads                                                                       | 3-12<br>3-12                 |

| 3.6.5 megabus response circuits                                                                                                     | 3-13                         |

| 3.7 Temporary and Permanent Flags                                                                                                   | 3-14                         |

| 3.7.1 temporary flags<br>3.7.2 permanent flags                                                                                      | 3-14<br>3-15                 |

| 3.8 Nibble Shifter                                                                                                                  | 3-15                         |

| 3.8.1 shifter data flow<br>3.8.2 shifter control                                                                                    | 3-16<br>3-16                 |

| 3.9 Arithmetic and Miscellaneous Indicators                                                                                         | 3-16                         |

| 3.9.1 arithmetic indicators<br>3.9.2 miscellaneous indicators                                                                       | 3-16<br>3-17                 |

| 3.9.2.1 scram indicator<br>3.9.2.2 difbuf indicator                                                                                 | 3-17<br>3.17                 |

| 3.10 The OP Register                                                                                                                | 3.17                         |

| 3.10.1 the abcd registers<br>3.10.2 the opcod register                                                                              | $3.17 \\ 3.13$               |

| 3.11 Loading Various Registers                                                                                                      | 3-17                         |

| 3.11.1 loading the H register<br>3.11.2 loading the output register<br>3.11.3 loading adra and adrb<br>3.11.4 loading adrp and pctr | 3-18<br>3-18<br>3-18<br>3-19 |

| 3.12 The Four Speed Clock                                                                                                           | 3-20                         |

| 3.12.1 the basic clock<br>3.12.2 the gear shifter<br>3.12.3 clock stalls                                                            | 3-20<br>3-20<br>3-21         |

PAGE i-3

TABLE OF CONTENTS

JR TECHNICAL DESCRIPTION (60165905

3.13 The Return Stack 3 - 233 - 233 - 233.13.1 the return registers 3.13.2 the stack pointer 3-23 3.14 The Next Address Generator 3.14.1 bank selection 3.14.2 else-bank-next-address generation 3.14.3 if-bank-next-address generation 3-24 3 - 253 - 253.14.3.1 if bank address bits 01-09 3.14.3.2 if bank address bits 10-13  $3-25 \\ 3-26$ 3-27 3.15 Availability Circuits 3.15.1 error detection circuits 3 - 273-28 3-28 3-28 3-28 3-28 3-29 3-29 3-29 3-29 3.15.1.1 procedure parity 3.15.1.2 data parity 3.15.1.3 procedure red 3.15.1.4 data red 3.15.1.5 procedure and data uar 3.15.1.6 procedure page cross detection 3.15.1.7 control store parity 3.15.2 parity generation circuits 3.15.3 verifying the integrity circuits 3.15.4 branch to zero 3-29 3-30 3-30 3.16 Alterable Firmware Array 3-30 3.16.1 loading the alterable firmware array 3.16.2 enabling the alterable firmware array 3 - 303 - 31SECTION FOUR 4.0 FIRMWARE DESCRIPTION 4-1 4.1 2901 Control 4 - 34 - 64.2 Aram Control 4.2.1 rm 4.2.2 rw 4-6  $\bar{4} - 6$ 4.3 D Bus Control 4 - 64.3.1 full literal 4.3.2 broadside 4.3.3 mixes 4-6 4-6 **4**-7 4.4 Address Bus Control 4 - 74.5 Z Bus Control 4 - 74 - 84.6 Megabus/Cache Control 4.7 Flag Control 4 - 104.7.1 permanent flags 4.7.2 temporary flags 4-11 4-11 4.8 Nibble Shifter Control 4-11

PAGE i-4

| 4.9 Indicator Control                                                      | 4-11                 |

|----------------------------------------------------------------------------|----------------------|

| 4.9.1 arithmetic indicators<br>4.9.2 miscellaneous indicators              | 4-11<br>4-12         |

| 4.10 ABCD and OP Control                                                   | 4-12                 |

| 4.11 Load Controls                                                         | 4-12                 |

| 4.11.1 loading adra, adrb, or adrp/pctr<br>4.11.2 loading outr and/or shrg | 4-13<br>4-13         |

| 4.12 Clock Control                                                         | 4-13                 |

| 4.13 Stack Control<br>4.14 Next Address Control<br>4.15 Availability       | 4-13<br>4-14<br>4-17 |

| SECTION FIVE                                                               |                      |

| 5.0 THE NANOSECONDS                                                        | 5-1                  |

| 5.1 The Symbology                                                          | 5-1                  |

| 5.2 The Choices                                                            | 5-2                  |

| 5.3 Putting It Together                                                    | 5-2                  |

| APPENDIX A                                                                 |                      |

| Enhancements                                                               | A-1                  |

|                                                                            |                      |

PAGE i-5

## LIST OF FIGURES

.

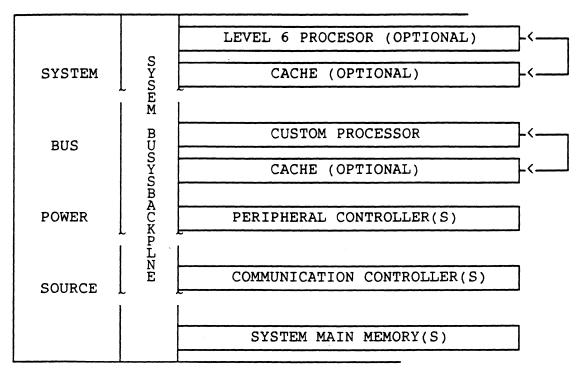

| FIGURE | 2-1A | SYSTEM ENVIRONMENT WITH CACHE       | 2-2  |

|--------|------|-------------------------------------|------|

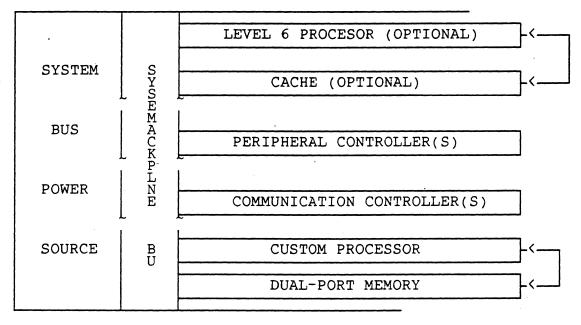

| FIGURE | 2-1B | SYSTEM ENVIRONMENT WITHOUT CACHE    | 2-2  |

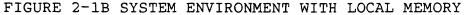

| FIGURE | 2-2  | PROCESSOR BLOCK DIAGRAM             | 2-6  |

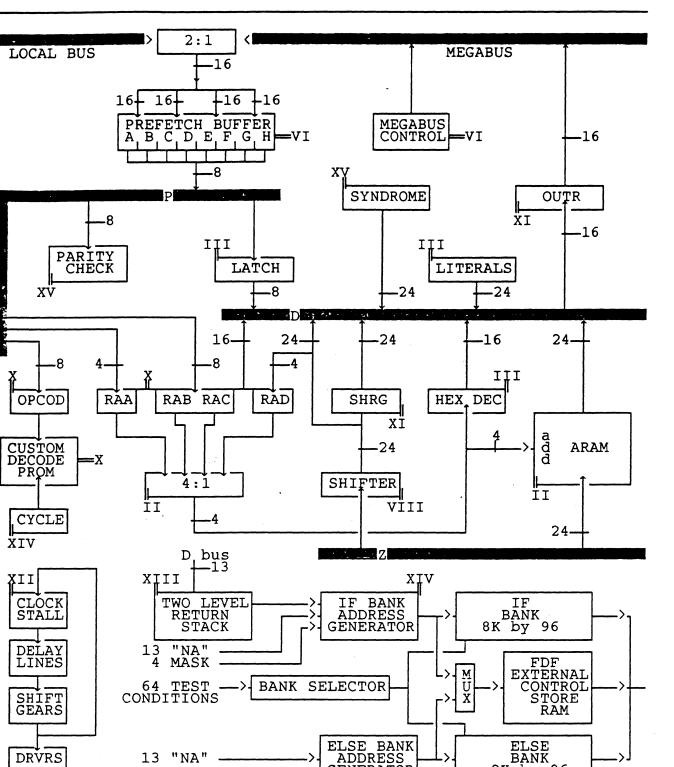

| FIGURE | 3-1  | IF AND ELSE BANK ADDRESS GENERATORS | 3-20 |

| FIGURE | 4-1  | FIRMWARE WORD FORMAT                | 4-2  |

| FIGURE | 5-1  | PERT CHART                          | 5-4  |

LIST OF TABLES

| TABLE | 3-1  | RALU CARRY NETWORK                  | 3-2  |

|-------|------|-------------------------------------|------|

| TABLE | 3-2  | ARAM ADDRESS SELECTOR               | 3-3  |

| TABLE | 3-3  | DBUS BYTE X                         | 3-4  |

| TABLE | 3-4  | DBUS BYTE Y                         | 3-5  |

| TABLE | 3-5  | DBUS BYTE Z                         | 3-6  |

| TABLE | 3-6  | ADDRESS BUS                         | 3-7  |

| TABLE | 3-7  | ADDRESS REGISTER ENABLES            | 3-7  |

| TABLE | 3-8  | ZBUS SOURCES                        | 3-8  |

| TABLE | 3-9  | ZBUS ENABLES                        | 3-8  |

| TABLE | 3-10 | SIDE-EFFECTS OF TEMPORARY FLAGS     | 3-15 |

| TABLE | 3-11 | SIDE-EFFECTS OF PERMANENT FLAGS     | 3-15 |

| TABLE | 3-12 | CONFIGURATION REGISTER INPUTS       | 3-19 |

| TABLE | 3-13 | CONFIGURATION REGISTER OUTPUTS      | 3-19 |

| TABLE | 3-14 | CLOCK SPEEDS                        | 3-20 |

| TABLE | 3-15 | STALL CONDITIONS                    | 3-22 |

| TABLE | 3-16 | ELSE BANK SOURCES                   | 3-25 |

| TABLE | 3-17 | IF BANK SOURCES                     | 3-25 |

| TABLE | 3-18 | IF BANK ADDRES BITS 01-09           | 3-26 |

| TABLE | 3-19 | IF BANK ADDRESS BITS 10-13 (PART 1) | 3-26 |

| TABLE | 3-19 | IF BANK ADDRESS BITS 10-13 (PART 2) | 3-27 |

| TABLE | 3-20 | CYCLE MODULATION OF FWLOAD          | 3-31 |

PAGE i-6

## LIST OF TABLES (continued)

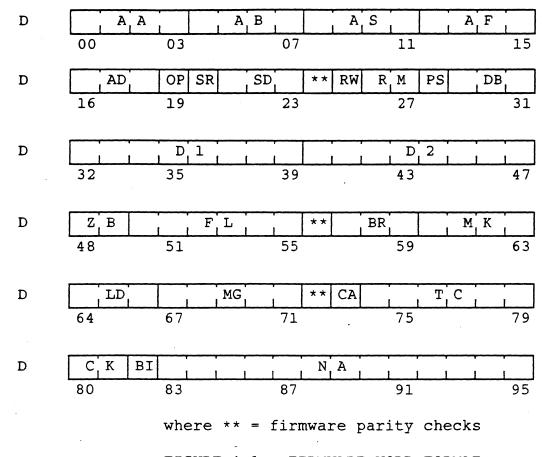

| TABLE 4-1  | THE FOURTEEN FIRMWARE ZONES              | 4-1  |

|------------|------------------------------------------|------|

| TABLE 4-2  | 2901 CONTROL FIELDS (PART 1)             | 4-3  |

| TABLE 4-2  | 2901 CONTROL FIELDS (PART 2)             | 4-4  |

| TABLE 4-2  | 2901 CONTROL FIELDS (PART 3)             | 4-5  |

| TABLE 4-2  | 2901 CONTROL FIELDS (PART 4)             | 4-6  |

| TABLE 4-3  | DBUS LITERALS                            | 4-7  |

| TABLE 4-4  | DBUS BROADSIDES                          | 4-7  |

| TABLE 4-5  | DBUS MIXES                               | 4-7  |

| TABLE 4-6  | ZBUS MICROS                              | 4-8  |

| TABLE 4-7  | MEGABUS AND CACHE/LOCAL MEMORY (PART 1)  | 4-9  |

| TABLE 4-7  | MEGABUS AND CACHE/LOCAL MEMORY (PART 2)  | 4-10 |

| TABLE 4-7  | MEGABUS AND CACHE/LOCAL MEMORY (PART 3)  | 4-10 |

| TABLE 4-7  | MEGABUS AND CACHE/LOCAL MEMORY (PART 4)  | 4-11 |

| TABLE 4-7  | MEGABUS AND CACHE/LOCAL MEMORY (PART 5)  | 4-11 |

| TABLE 4-7  | MEGABUS AND CACHE/LOCAL MEMORY (PART 6)  | 4-12 |

| TABLE 4-8  | ARITHMETIC INDICATORS (PART 1)           | 4-13 |

| TABLE 4-8  | ARITHMETIC INDICATORS (PART 2)           | 4-14 |

| TABLE 4-9  | ABCD and OP MICROS                       | 4-14 |

| TABLE 4-10 | LOAD MICROS (PART 1) ADDRESS REGISTERS   | 4-15 |

| TABLE 4-10 | LOAD MICROS (PART 2) OUTR SHRG and TIMER | 4-15 |

| TABLE 4-10 | LOAD MICROS (PART 3) CNFG                | 4-15 |

| TABLE 4-11 | CONFIGURATION REGISTER                   | 4-16 |

| TABLE 4-12 | CLOCK SPEED MICROS                       | 4-16 |

| TABLE 4-13 | PUSH MICRO                               | 4-17 |

| TABLE 4-14 | NEXT ADDRESS CONTROL FIELDS (PART 1)     | 4-17 |

| TABLE 4-14 | NEXT ADDRESS CONTROL FIELDS (PART 2)     | 4-18 |

| TABLE 4-15 | NEXT ADDRESS MECHANISMS (PART 1)         | 4-18 |

| TABLE 4-15 | NEXT ADDRESS MECHANISMS (PART 2)         | 4-19 |

| TABLE 4-15 | NEXT ADDRESS MECHANISMS (PART 3)         | 4-20 |

| TABLE 4-16 | FRAMIT ACTIONS                           | 4-22 |

PAGE i-7

## INTRODUCTION

The "sixteen-bit" Custom Processor is a nine megahertz, twentyfour-bit wide, microprogrammable MEGABUS connected firmware engine driven by a ninety-six-bit wide control store word and having a blank identity.

1.1 PURPOSE

This technical description may be useful to those who wish to provide the Custom Processor with a new incarnation but it is specifically directed toward the test technician who needs to understand its inner workings. Those who attempt personalization of the Custom Processor are referred to the Specification of the 16-bit Custom Processor. For board testing or firmware checkout, Custom and Special Products offers a Firmware Development Facility which greatly simplifies the task.

## 1.2 SCOPE

This document is intended for the test technician. It (particularly section 3) describes the operation of the sixteen-bit Custom Processor at the level sufficient to perform component level fault isolation.

In addition to this section, this document contains four other sections.

Section two describes the system environment, an exposure of the Custom Processor capabilities and a brief discussion of each of its major areas.

Section three is a detailed description of each of the fifteen hardware areas.

Section four is a detailed description of each of the fifteen firmware areas.

Section five is a discussion of internal speed considerations.

#### 1.3 DISCLAIMER

The firmware dictionary serves as the specification for the Custom Processor. The firmware dictionary shall govern in any disagreement between it and this technical description.

PAGE 1-1

INTRODUCTION

## 1.4 REFERENCES

PAGE 1-2

INTRODUCTION

## OPERATIONAL OVERVIEW

This section describes the system environment into which the sixteen-bit Custom Processor may be connected. The section also gives a broad-brush description of the Custom Processor's inner workings.

## 2.1 System Environment

The sixteen-bit Custom Processor is comprised of a mother/daughter board pair which connects to the MEGABUS backplane (see figure 2-1). The MEGABUS backplane is a means of interconnecting system elements including peripheral controllers, communication controllers, processors, and memories. Dialogue among system elements is transacted on the MEGABUS backplane. Many kinds of transactions are allowed but two major categories are of interest, "writes" which transpire in one MEGABUS cycle, and "reads" which transpire in two MEGABUS cycles. The circuitry which supports the MEGABUS backplane is evenly distributed among all system elements such that each element performs its share of the priority resolution (tie-breaking); each element is responsible for determining that it is the intended recepient of a transaction; each element is responsible for remembering the identity of the requestor of a read type operation so that the response may be sent to its proper destination.

The Custom Processor is a system element which possesses a sixteen-bit-wide MEGABUS data interface but possesses a twenty-four-bit-wide MEGABUS address interface and internally contains a nine megahertz, twenty-four-bit-wide microprocessor driven by a ninety-six-bit-wide firmware word. Memory and I/O dialogue may emanate from the Custom Processor. Controllers may be directed to treat the Custom Processor as the recepient of their interrupts. By virtue of the 24-bit internal structure and the 24-bit MEGABUS address interface, the Custom Processor has access to all 16 megabytes of main memory. This allows the Custom Processors.

An optional Cache or Local Memory may be connected to the Custom Processor in order to minimize MEGABUS traffic generated by the CUP16's voracious appetite. Applications which include the CUP16 are mostly configurations of cooperating heterogeonous system elements each dedicated to a specific function (e.g., the CUP16 is assigned to process the application, the Level-6 cpu is assigned to manage the data base.

The system configuration should include at least one Level 6 processor, if for no other reason than to allow test software to be loaded and executed. This is the most effective way of allowing the user to verify the integrity of all device and communication controllers.

PAGE 2-1

HONEYWELL BULL CONFIDENTIAL & PROPRIETARY

FIGURE 2-1A SYSTEM ENVIRONMENT WITH CACHE

PAGE 2-2

## 2.2 INTRODUCTORY DESCRIPTION

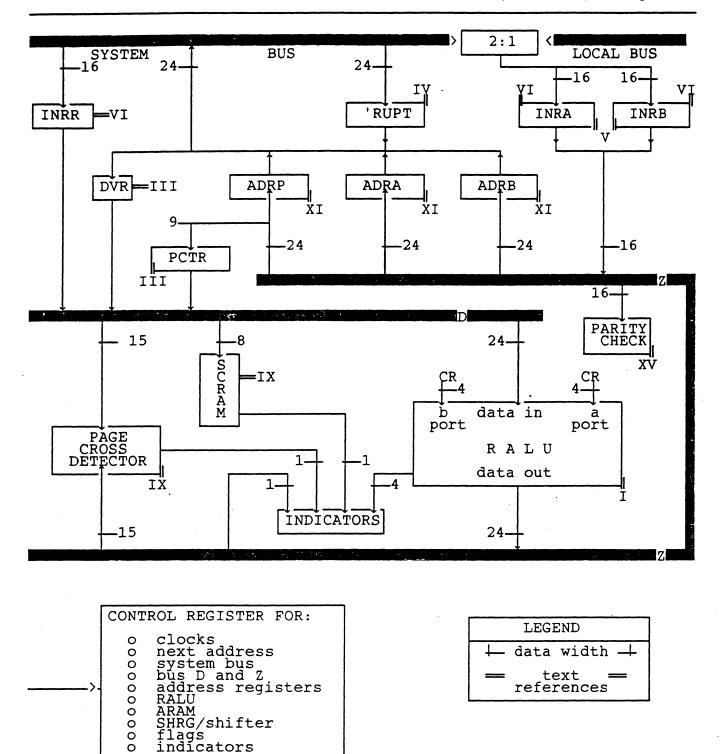

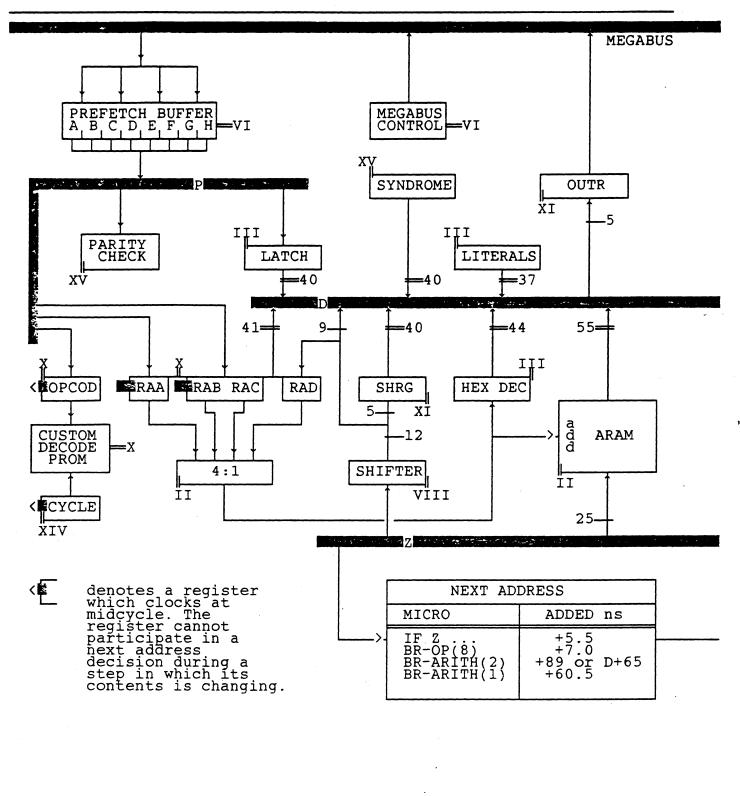

The major block diagram of figure 2-2 is a representation of the Custom Processor. This section is divided into fifteen paragraphs each of which discusses the topic at a first level. The discussions in sections three and four are similarly subdivided allowing the reader quick reference to greater hardware detail (section three) or greater firmware detail (section four). The fifteen sections are listed below, each with its associated block diagram identifier:

- I. the ralu

- II. the aram

- III. the d bus

- IV. the address bus

- V. the z bus

- VI. the system bus

- VII. flags

- VIII. shifter

- IX. indicators

- X. op code registers

- XI. other registers

- XII. the clock

- XIII. the stack

- XIV. the next address generator

- XV. availability

## 2.2.1 the ralu (see block diagram identifier I)

The register file and alu is comprised of six 2901 bit slice chips constituting a twenty-four-bit alu, a sixteen-location dual-ported random- access memory and a bit shifter (24 or 48 bits wide). Operations inside the alu occur at nearly a nine megahertz rate. The ralu receives external twenty-four-bit data from the dbus and transmits twenty-four-bit results to the zbus.

2.2.2 the aram (see block diagram identifier II)

The auxiliary random access memory is a single-ported 16-location memory. Each location contains twenty-four bits. The memory may be addressed in any one of four ways. Its data is read onto the dbus. Data written into the aram is taken from the zbus.

2.2.3 the dbus (see block diagram identifier III)

The dbus is the place where all roads lead. It is a twenty-four bit bus which receives literal data, or data from the address bus or the pbus or numerous other secondary sources. It may deliver its wealth to the ralu or to the output register. It has byte partitioning capabilities; i.e., it may take combinations of literal byte(s), SHRG byte(s) and shifted zbus byte(s). As an example, the dbus may receive an all one's literal for its eight most significant bits, the middle byte of SHRG for its eight middle bits, and any byte of the zbus for its eight least significant bits.

PAGE 2-3

## 2.2.4 the address bus (see block diagram identifier IV)

The address bus provides addresses sent to the system bus. It receives data from four sources; the three local bus address registers (ADRA, ADRB, and ADRP), and a register which captures the output of the MEGABUS address receivers (RUPT). It may deliver the content of any one of these four address registers to the dbus.

### 2.2.5 the zbus (see block diagram identifier V)

If the dbus is where all roads lead, the zbus is quite uninspiring. Indeed, it is a journeyperson bus, capable of receiving data from the outside world (ie, the memory subsystem) and receiving ralu revelations and sending all this to the dbus via the nibble shifter and/or to the ARAM and/or to any one of the address registers.

#### 2.2.6 the system bus (see block diagram identifier VI)

The system bus is the area of the processor responsible for communicating with non-memory system elements; e.g., a level-6 processor or a level-6 controller and with locally connected or MEGABUS connected memories. The system bus area contains, along with the interface circuits required to carry on a dialogue with other system elements, an eight-byte look-ahead procedure buffer and two two-byte data buffers. The two data buffers receive information from the system bus (memory or I/O data) to be deposited onto the zbus. The look-ahead procedure buffer is organized to supply one byte to the op register and/or the dbus and to replenish itself automatically as bytes are consumed.

## 2.2.7 flags (see block diagram identifier VII)

The Custom Processor contains sixteen firmware settable and testable flops. Some have hardware dedicated functions (e.g., processor off-line); others have more sophisticated firmware sequence control characteristics (e.g., they may participate in sixteen-way "splatters").

## 2.2.8 shifter (see block diagram identifier VIII)

The shifter is a nibble rotator connected between the zbus and the dbus. The H register (SHRG) also receives the shifter output. All six possible 4-bit shift distances are supported; e.g., shift left four nibbles, shift right two nibbles are two equal operations.

## 2.2.9 indicators (see block diagram identifier IX)

Indicators are storage elements which remember some property of the results obtained in one firmware step so that they may affect the firmware sequence later on. There are arithmetic indicators like "zero", "carry" and "overflow"; there are more specialized indicators like the frame bound detector. Many have the ability to participate in "splatters" which permit up to 17-way firmware branches.

## 2.2.10 op registers (see block diagram identifier X)

The op registers permit capturing interesting nibbles of the procedure stream for future reference. The storage mechanisms involved are a register called OPCOD, and four registers called RAA, RAB, RAC, and RAD. OP captures eight bits of the procedure for sixteen-way "splatters". RAA, RAB, and RAC each capture four bits of the procedure bus, while RAD is an incrementing register which is loaded from the nibble shifter.

PAGE 2-4

**OPERATIONAL OVERVIEW**

## 2.2.11 other registers (see block diagram identifier XI)

Other registers provide strategically located information storage. Address registers for procedure and data fetches are loaded from the zbus and communicate their content to the system bus. A register (PCTR) is provided to keep track of the address of the next procedure byte. The output data register is loaded from the dbus and communicates its content to the system bus. The H register, one of the byte partitionable sources to the dbus, captures the output of the nibble shifter.

## 2.2.12 clock (see block diagram identifier XII)

The clock has a maximum frequency of nine megahertz. It is an asynchronous mechanism whose speed for each step is selected by the firmware assembler. The clock is structured to wait before starting the next step (stall) if the coder wishes, implicitly or explicitly, to postpone its start until an external event occurs (such as receiving previously requested memory subsystem data).

#### 2.2.13 the stack (see block diagram identifier XIII)

The return stack is a mechanism which simplifies the use of subroutines. It contains two levels. Absolute addresses are "pushed" onto the stack. Unconditional, conditional and alternate (masked) returns are provided.

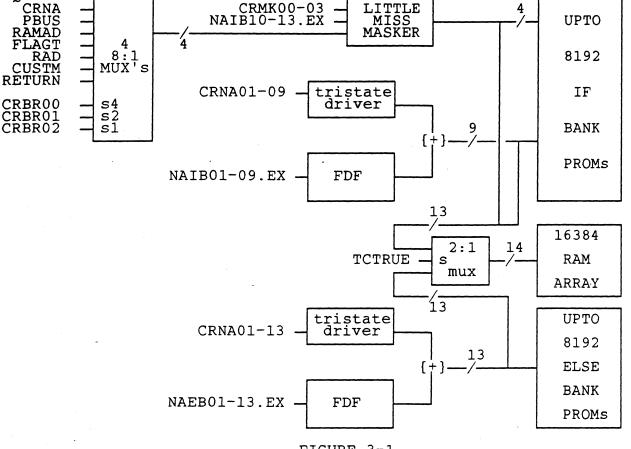

## 2.2.14 the next address generator (see block diagram identifier XIV)

The next address generator is a particularly flexible element in that it eliminates the need for numeric sequentiality in the execution of firmware steps. The next address may be any one of the 16384 locations provided. The destination may be specified as a GO-TO or it may be chosen from a pair of addresses dependent upon one of sixty-four test conditions. It may instead be chosen among sixteen locations dependent upon some group of four indicators (five groups are provided) or the destination may be a seventeenth location dependent upon one of the sixty-four test conditions. Then again, it may be chosen from among one of 16 locations dependent upon a byte of the procedure stream (OP) via a table look-up mechanism containing eight look-up tables. Or, it may be a subroutine return. Four types of returns are provided: an unconditional return, or one which returns if a specified one of the sixty-four test conditions is true, or one which returns to an alternate return location as a function of subroutine processing discoveries, or one which conditionally performs an alternate return. subroutine processing disperforms an alternate return.

#### 2.2.15 availability

The Custom Processor is possessed of data parity checking circuits, data uncorrectable memory edac error detectors, firmware parity error detectors, and detectors for references to unavailable system resources. Parity bits accompany data sent from the Custom Processor to other system elements allowing them the opportunity of verifying the integrity of the received information.

All Custom Processors include an imbedded comprehensive self-test firmware routine called the quality logic test (QLT) which, at every system initialization, exercises all processor hardware elements verifying their specified operation. This firmware routine may optionally include a thorough memory array test.

PAGE 2-5

..

16-BIT CUSTOM PROCESSOR TECHNICAL DESCRIPTION

## (60165905) Page 2-6

PAGE 2-6

11AUG 87

**`**..

OPERATIONAL OVERVIEW

BLOCK DIAGRAM OF THE

8K by 96

HONEYWELL BULL CONFIDENTIAL & PROPRIETARY

GENERATOR

XIV

FIGURE 2-2

## 16-BIT CUSTOM PROCESSOR

0 0

PAGE 2-7

## HARDWARE DESCRIPTION

This section describes hardware entities at a level of detail sufficient for comprehension if the reader has a set of Custom Processor logic block diagrams (lbd) and if the reader has experience in the interpretation of logic diagrams. Lbd page references are suffixed with m for mother board or d for daughter board. Reference is also made to the block diagram of 2-2.

The hardware discussion is subdivided into sixteen zones. Each of these zones is a separable entity that has one or more firmware fields dedicated to its control as shall be seen in section four.

The fifteen sections and the block diagram identifier are:

| I.<br>II.<br>IV. | Register file and alu (2901`s)<br>Auxiliary random access memory (ARAM)<br>D bus<br>Address bus |

|------------------|-------------------------------------------------------------------------------------------------|

| V:               | Z bus                                                                                           |

| VI:              | System bus                                                                                      |

| VII:             | Temporary and permanent flags                                                                   |

| VII:             | Nibble shifter                                                                                  |

| IX.              | Arithmetic and miscellaneous indicators                                                         |

| X:               | OP registers                                                                                    |

| XI.              | Loading of H and other registers                                                                |

| XII.             | Four-speed clock                                                                                |

| XIII.            | Return stack                                                                                    |

| XIV.             | Next address generation                                                                         |

| XV.              | Availability                                                                                    |

| XVI.             | Alterable Firmware Array                                                                        |

NOTE: In the logic descriptions that follow, formal signal names are capitalized and take one of three forms:

- o six characters; e.g., OLDMTY

- nine characters with a neutral polarity indicator; e.g., NAIB06.EX

- o concatenations; e.g., BUSP00-07 (the pbus) PTAKE4/2/1 (the take counter)

PAGE 3-1

#### HARDWARE DESCRIPTION

Polarity indicators are avoided. If a description claims signal ABCDEF to be on, left unstated is that ABCDEF+ (if any) is "high" and ABCDEF- (if any) is "low".

3.1 Register file and alu (block diagram identifier I)

The ralu is the resource which performs twenty-four-bit arithmetic and logic operations. It resides between the dbus, from which it receives operands, and the zbus to which it delivers results.

3.1.1 The 2901's (see page 12d)

...

The ralu is comprised of six 2901's. These six chips constitute:

- 1. a dual-ported 16-location by 24-bit register file

- 2. a 24-bit arithmetic and logic unit

- 3. a 24-bit q register

- 4. a shifting element capable of shifting the alu output one bit left or right.

- 5. a shifting element capable of shifting the concatenation of the alu output and the q register one bit left or right.

- 6. a zero detector, an overflow detector, a sign detector and a carry detector.

3.1.2 Ralu addressing and control (see lbd pages 3d, 4d and 5d)

The raw control register provides the 2901's almost all of their control inputs:

| A port address     | CRAA(00-03) |

|--------------------|-------------|

| B port address     | CRAB(00-03) |

| source select      | CRAS(00-02) |

| function select    | CRAF(00-02) |

| destination select | CRAD(00-02) |

|                    |             |

3.1.3 Ralu support logic (see lbd page 12d)

The carry look-ahead network is comprised of two 74S182 carry look-ahead chips connected in a conventional manner. First, the carry into the least significant 2901 (AUCO32) is derived by decoding bits three and four of the AF field to produce four cases as shown in Table 31-1.

| CRAF03 | CRAF04 | AUC032                                                   |

|--------|--------|----------------------------------------------------------|

| 0      | 0      | cause a carry into alu unconditionally                   |

| 0      | 1      | cause a carry into the alu if the carry indicator is off |

| 1      | 0      | cause a carry into the alu if the carry indicator is on  |

| 1      | 1      | do not cause a carry into the alu                        |

TABLE 3-1 RALU CARRY NETWORK

PAGE 3-2

### HARDWARE DESCRIPTION

Next, the carry into the second, third and fourth 2901's (AUCO28, AUCO24, and AUCO20) is from the first 74S182. Last, the carry into the fifth (AUCO16) and sixth (AUCO12) 2901's (the most significant stages) are generated by the second 74S182 which receives inputs from the original carry-in, the propagate/generate outputs of the most significant two 2901's and the propagate/generate outputs of the other 74S182 carry look-ahead chip.

The zero detector of the 2901 is an open-collector output. Six 2901 zero-detect outputs are connected together in an open-collector network "terminated" by a 430-ohm resistor.

The bit-shift pins of the 2901's are connected in a conventional manner, where AUSR07 allows the value of temp flag 1 to be injected into all right shifts and AUSQ31 allows the value of temp flag 1 to be injected into q register left shifts.

3.2 Auxiliary Random Access Memory - ARAM (block diagram indentifier II)

The Auxiliary Random Access Memory is comprised of six 74S189's. Each chip contains 16 locations of four-bit-wide static ram. The ARAM receives a four-bit address from a four-way selector called RAMAD. In any step, the ARAM may be read onto the dbus or written from the zbus but not both.

#### 3.2.1 ARAM read or write (see lbd page 16d)

when written, the ARAM captures 24 bits from the zbus into the addressed location. When read, 24 bits of data are placed upon the dbus. ARAMEN is the chip enable. It comes on when reading the ARAM (CRRMRD) or when writing the ARAM (ARAMWR). The d input of the flop CRRMRD is a predecode of the output of the control store array, so that CRRMRD can be valid as early in the cycle as possible, affording the fastest access of the ARAM onto the dbus. ARAMWR is timed to occur during the second half of a step creating a "write pulse" which copies the zbus data into the addressed ARAM location through the end of the step. By the time the copying ends, the zbus has settled into validity.

#### 3.2.2 ARAM addressing (see page 15d)

The two-bit firmware field RM provides control for a four-to-one selection of ARAM addressing sources. Two 74S153's perform the selection resulting in RAMAD(0-3). Table 3-2 shows what address results from each selection.

| ARAM ADDRESS SELECTOR |            |  |  |

|-----------------------|------------|--|--|

| CRRM(00,01)           | RAMAD(0-3) |  |  |

| 0                     | RAA00(0-3) |  |  |

| 1                     | RAB00(0-3) |  |  |

| 2                     | RAC00(0-3) |  |  |

| 3                     | RAD00(0-3) |  |  |

## TABLE 3-2 ARAM ADDRESS SELECTOR

CRRM(00,01) are the control register flops which store the two-bit firmware field specified to control the ARAM addressing source. RAMAD(0-3) is the four-bit ARAM address. RAA00(0-3), RAB00(0-3), RAC00(0-3), and RAD00(0-3) are the four OP registers. A, B, and C store appropriate procedure nibbles and D stores a non-procedural nibble from the four least-significant bits of the nibble shifter.

PAGE 3-3

٠,

#### HARDWARE DESCRIPTION

3.3 The D Bus (block diagram identifier III)

The dbus is a major node in the 16-bit Custom Processor. It is one of the 24-bit buses and is the most prolific. Data may be deposited upon it from a wide variety of sources. Such data may then be made available for computation in the ralu, or placed into the output register, or used to address the stop code ram. The dbus is structured as three eight-bit buses, allowing up to three dbus sources to be combined (see section 4.3 for a complete list of the combinations and permutations).

3.3.1 dbus byte x - bits 08-15 (see lbd pages 13d, 16d, 17d, 31m, and 35m)

Byte x may receive from six mutually exclusive sources which are listed in Table 3-3 along with the signal that enables each source.

| source                               | enable signal |

|--------------------------------------|---------------|

| 1. the address bus (ADRS08-15)       | ADRS2D        |

| 2. the h register (SHRG08-15)        | SRLF2D        |

| 3. the nibble shifter (SHFT08-15)    | SHLF2D        |

| 4. the ARAM (ARAM08-15)              | ARAMEN        |

| 5. literal data (8*CRDB02)           | LVLF2D        |

| 6. the syndrome register (SYND08-15) | SYND2D        |

TABLE 3-3 DBUS BYTE X

Source #1 is a collector of four sources, three of which store 24-bit addresses for MEGABUS references, and the other stores the MEGABUS address receivers when the CUP16 is the recipient of an unsolicited MEGABUS transaction (i.e., interrupt).

Source #2 is the register which is parked between the nibble shifter and the dbus i.e., it receives the output of the nibble shifter and can place the captured value onto the dbus in some subsequent step.

Source #3 is the nibble shifter capable of rotating the zbus value into the H register, onto the dbus, or both.

Source #4 is the ARAM placing its 24-bit "readout" of the addressed location onto the dbus.

Source #5 provides the dbus with 16-bit literals and a byte of "fill" (eight one's or eight zeros).

Source #6 deposits the syndrome register onto the dbus. The syndrome register captures the reason code for any hardware detected error.

Three of the sources are partitioned on byte boundaries; the shifter, the H register, or the literal may be selected for each dbus byte independently.

PAGE 3-4

HARDWARE DESCRIPTION

3.3.2 dbus byte y - bits 16-23 see 1bd pages 13d, 15d, 18d, 19d 31m, and 35m)

Byte y may receive from ten mutually exclusive sources which are listed in Table 3-4 along with the signal that enables each source.

| so  | urce                                    | enable signal |

|-----|-----------------------------------------|---------------|

| 1.  | the address bus (ADRS16-23)             | ADRS2D        |

| 2.  | the h register (SHRG16-23)              | SRMD2D        |

| 3.  | the nibble shifter (SHFT16-23)          | SHMD2D        |

| 4.  | the ARAM (ARAM16-23)                    | ARAMEN        |

| 5.  | literal data (CRDC16-23)                | CRDB00        |

| 6.  | the syndrome register (SYND16-23)       | SYND2D.03     |

| 7.  | the ABCD register (RAA, RAB for byte y) | ABCD2D        |

| 8.  | the hex decoder (HEXD00-07)             | HEXD2D        |

| 9.  | the interrupt register (INRR16-23)      | INRR2D        |

| 10. | the procedure counter (PCTR16-23)       | PCTR2D        |

TABLE 3-4 DBUS BYTE Y

Sources #1 through #6 are equivalent to the six sources on byte x.

Source #7 allows access to the sixteen bits of the ABCD register.

Source #8 is one byte of the hex decoder, a mechanism which decodes, with a couple of 74S138's, the four bits of the ARAM address (RAMAD0-3) and emits (in conjunction with the z byte) a one in a field of fifteen zeros.

Source #9 allows the interrupt data register to be placed upon the dbus. The interrupt data register captures the MEGABUS data receivers when an interrupt is accepted by the Custom Processor.

Source #10 for this byte deposits seven zeroes and the most significant bit of the procedure counter, a register which tracks the address of the procedure byte next to be "taken" from the prefetch buffer. PCTR is accurate modulo 512.

PAGE 3-5

HARDWARE DESCRIPTION

3.3.3 dbus byte z - bits 24-31 (see lbd pages 13d, 15d, 20d, 21d 31m, and 35m)

Byte z may receive from eleven mutually exclusive sources which are listed in Table 3-5 along with the signal that enables each source.

| DB05 BITE 2                                |               |

|--------------------------------------------|---------------|

| source                                     | enable signal |

| 1. the address bus (ADRS24-31)             | ADRS2D        |

| 2. the h register (SHRG24-31)              | SRRT2D        |

| 3. the nibble shifter (SHFT24-31)          | SHRT2D        |

| 4. the ARAM (ARAM24-31)                    | ARAMEN        |

| 5. literal data (CRDC24-31)                | CRDB01        |

| 6. the syndrome register (SYND24-31)       | SYND2D        |

| 7. the ABCD register (RAC, RAD for byte z) | ABCD2D        |

| 8. the hex decoder (HEXD08-15)             | HEXD2D        |

| 9. the interrupt register (INRR24-31)      | INRR2D        |

| 10. the procedure counter (PCTR24-31)      | PCTR2D        |

| 11. the pbus (BUSP00-07)                   | PBUS2D        |

TABLE 3-5 DBUS BYTE Z

Sources #1 through #10 are equivalent to those on byte y.

Source #11 allows access to bytes of the procedure stream for computational purposes. Bytes and/or nibbles of the procedure stream are also accessible to the register ABCD and to the eight-bit register OPCOD.

## 3.4 The Address Bus (block diagram identifier IV)

The address bus is a collector of address sources. Its primary purpose is to supply twenty-four bit byte addresses to the MEGABUS system bus or to the Cache/Local Memory interfaces. A secondary purpose is to deliver the address bus's selected source to the dbus and another purpose is to deliver to the dbus the function code from an interrupting MEGABUS channel. Registers ADRA, ADRB, and ADRP contain addresses. The mechanism is optimized for memory references in that ADRA and ADRB access data whereas ADRP accesses procedure. Memory references may be either single or double pull, may read "lock" or "unlock", may write word or byte, or may write "unlock". ADRA and ADRB may also be loaded with channel-number/function-code information so that they may be used to communicate with other system elements. The CUP16 may, for instance, interrupt another processor, read a disk controller's status, or instruct a communication controller to perform a DMA transfer.

PAGE 3-6

HARDWARE DESCRIPTION

3.4.1 address bus data flow (ADRS08-31) (see 1bd pages 29m and 30m)

The address bus may receive from four mutually exclusive sources which are listed in Table 3-6 along with the signal which enables each source.

TABLE 3-6 ADDRESS BUS

| source                                | enable signal |

|---------------------------------------|---------------|

| 1. address register A (ADRA08-31)     | ADRAEN        |

| 2. address register B (ADRB08-31)     | ADRBEN        |

| 3. address register P (ADRP08-31)     | ADRPEN        |

| 4. the interrupt register (RUPT08-31) | RUPTEN        |

Regarding sources #1, #2, and #3, each address register is loaded from the zbus and may participate in a read/write transaction by supplying the twenty-four address bits.

Source #4 captures the CUP16's channel number and the function code when another MEGABUS system element directs an unsolicited MEGABUS transaction toward the CUP16. By virtue of this data path (which allows the dbus to receive this information via the address bus) and the MEGABUS data lines from INRR, the microcoder may determine the nature of the message that the interruptor is attempting to transmit (by examining RUPT for the function and INRR for the accompanying data).

3.4.2 address bus enables (see 1bd pages 18m, 29m and 33m)

Two bits of the "MEGABUS" control field (CSMG68,69) determine which of the four address-bus sources will be chosen. These two control store array bits are predecoded by a 74S139 forming the four select signals for the next firmware step. Before these signals are used, they must pass another test; as they arrive on the input of a 74AS1843 latch, the latch's gate input (MYDCNP) decides, based upon the current state of the MEGABUS interface, whether to pass these select signals through or ignore them. If either interface is currently "busy", then these select signals are ignored; if both interfaces are not busy, then these select signals proceed to their destination and cause the address bus to receive the appropriate address register. This mechanism guards against changing the address value presented to the MEGABUS or Cache/Local Memory address drivers while the MEGABUS transaction is still in process. The two-bit field results in one of four selections as listed in Table 3-7.

| CSMG68-69 | predecode | "FR"input | select signal |

|-----------|-----------|-----------|---------------|

| 00        | CERPTE    | CRRPTE    | RUPTEN        |

| 01        | CEADPE    | CRADPE    | ADRPEN        |

| 10        | CEADAE    | CRADAE    | ADRAEN        |

| 11        | CEADBE    | CRADBE    | ADRBEN        |

TABLE 3-7 ADDRESS REGISTER ENABLES

PAGE 3-7

### HARDWARE DESCRIPTION

## 3.5 The Z Bus (block diagram identifier V)

The zbus is the bus where the ralu may deposit its computations, is the bus upon which external data arrives (from inra/b) and is the bus which feeds the nibble shifter.

3.5.1 zbus sources (see lbd pages 16d-21d, and 22m)

The zbus is twenty-four bits wide and receives data from two twenty-four-bit-wide sources and two sixteen-bit-wide sources. Along with the ralu (24 bits) and the input data registers (16 bits), the zbus may also receive from an external 24-bit-wide connection (1.e., the firmware development facility). The four sources are listed in Table 3-8 along with their respective enable signals.

| source                                          | enable signal    |

|-------------------------------------------------|------------------|

| 1. the inra (INRA16-31)                         | CRIA2Z           |

| 2. the inrb (INRB16-31)                         | CRIB2Z           |

| 3. the ralu (ALUY08-15)<br>the ralu (ALUY16-31) | CRTB2Z<br>CRAY2Z |

| 4. the fdf (BUSZ08-31.ex)                       | CRTB2Z           |

TABLE 3-8 ZBUS SOURCES

## 3.5.2 zbus enables (see 1bd page 9d)

To achieve the earliest zbus "valid", the two control store array bits of the ZB field are predecoded by a 74S139 into four early enable signals which are then captured in four control register flops. The two-bit ZB field (CSZB48,49), the zbus source, the early enable and the final enable are shown in Table 3-9.

TABLE 3-9 ZBUS ENABLES

| CSZB(48,49) | source | early enable | final enable |

|-------------|--------|--------------|--------------|

| 00          | ralu   | CEAY2Z       | CRAY2Z       |

| 01          | fdf    | CETB2Z       | CRTB2Z       |

| 10          | inra   | CEIA2Z       | CRIA2Z       |

| · 11        | inrb   | CEIB2Z       | CRIB2Z       |

When the sixteen bits of inra or inrb are placed upon the zbus as a result of code two or three, they are accompanied by eight bits of the alu. Also in codes two or three, a parity check is performed to verify the integrity of the data received from the Cache/Local Memory or MEGABUS receivers (see 3.15).

PAGE 3-8

HARDWARE DESCRIPTION

# 3.6 The System Bus and Local Bus Interfaces (block diagram identifier VI)

This interface hardware can be divided into four sections:

- o An addressing mechanism

- o A data storage mechanism

- A procedure storage mechanism and

- o Control circuitry

The MG field is responsible for managing the resources represented by the above list which contains three address registers, 64 bits of procedure stream storage, and 32 bits of data storage.

3.6.1 MEGABUS and Cache/Local Memory addressing (see lbd pages 29m and 30m

Addresses from the processor to the MEGABUS (or Cache/Local Memory) may emanate from one of four sources: adra, adrb, adrp or rupt. Three of the four registers are comprised of 74F374's whose outputs are tied together to form the address bus in conjunction with a set of 74F241 drivers allowing the fourth register (adrp) to join in. This forms a four-to-one mux selected by ADRAEN, ADRBEN, ADRPEN and RUPTEN. The resultant address bus is connected to the address transmitters (26S10's) providing the address for all MEGABUS transactions including the non-memory-reference variety. This address is also sent to the Cache/Local Memory. This same resultant address bus is connected to the dbus by 74F241 drivers enabled by the signal ADRS2D.

3.6.2 MEGABUS and Cache/Local Memory data storage (see 1bd pages 1m and 22m)

Data from the MEGABUS or from the Cache/Local Memory is captured in either inra or inrb. A group of four 74F257's select between Cache/Local Memory and MEGABUS data as a function of CADONG. Cache/Local Memory data is selected only if the outstanding data reference is being processed by the Cache/Local Memory. The data on the output of the selector is captured by inra if the MEGABUS or Cache/Local Memory reference in process was requested for inra as signified by INRACK making a "leading edge". If INRBCK makes a leading edge, then the data is destined for inrb. Both inra and inrb deliver their data to the zbus as described in 3.5.

3.6.3 MEGABUS and Cache/Local Memory procedure storage (see 1bd pages 26m and 27m)

Procedure arrives in sixteen-bit waves in the same manner as data arrives; namely, a selection of Cache/Local Memory versus MEGABUS is performed by four 74F257's controlled by CADONG. The selector output (DATA00-15) is directed into the sixty-four-bit procedure buffer as a function of a two-bit counter (PRASKO,PRASK1) which is responsible for remembering where the next sixteen-bits of procedure are to be placed. In the beginning, PRASKO and PRASK1 are off. When the first sixteen bits arrive, PRASK1 sets, clocking DATA(00-07) into INRPA(0-7) and DATA(08-15) into INRPB(0-7). When the next sixteen bits of procedure arrive, PRASK0 sets, clocking DATA(00-07) into INRPC(0-7) and DATA(08-15) into INRPD(0-7). When the third sixteen bits of procedure arrive, PRASK1 goes off, clocking DATA(00-07) into INRPE(0-7) and DATA(08-15) into INRPD(0-7). When the third sixteen bits of procedure arrive, PRASK1 goes off, clocking DATA(00-07) into INRPE(0-7) and DATA(08-15) into INRPD(0-7). When the third sixteen bits of procedure arrive, PRASK1 goes off, clocking DATA(00-07) into INRPE(0-7) and DATA(08-15) into INRPF(0-7). When the fourth sixteen-bit procedure word arrives, PRASK0 goes off, clocking DATA(00-07) into INRPG(0-7) and DATA(08-15) into INRPF(0-7). Now

PAGE 3-9

HARDWARE DESCRIPTION

PRASKO and PRASK1 are back to their original state (both off) such that when the fifth sixteen-bit word arrives, INRPA and INRPB each receive a new byte of procedure. As long as procedure continues to be fetched from consecutive memory locations, the eight-byte buffer is treated as a circular storage mechanism.

## 3.6.3.1 The procedure bus

In order to dispense one byte at a time, the eight 74F374 chips which form this eight-byte storage register have their outputs connected together to form an eight-bit bus. The output of this network is called BUSP00-07. A three-bit counter, called the take counter, keeps track of which byte is next for delivery onto BUSP00-07. When PTAKE4/2/1=0, the first 74S374 chip (INRPA0-7) is enabled onto BUSP00-07, when PTAKE4/2/1=1, then INRPB0-7 is enabled onto BUSP00-07,..., and when PTAKE4/2/1=7, then INRPH0-7 is enabled onto BUSP00-07.

Decoding the take counter is accomplished with a 74F138. The take counter itself is comprised of a 74S163 counter chip which, with the help of CDPTAK, increments by zero or one each firmware step, recording the removal of procedure bytes. Each time the PTAKE counter increments, it signifies the removal of a procedure byte and therefore a one-byte vacancy.

## 3.6.3.2 The procedure bus latches (see lbd pages 20d and 36m)

The procedure bus generally heads in four directions: the dbus, the OP registers (RAA, RAB, and RAC), the OPCOD register, and a next-address splatter input. The dbus and the splatter input require the pbus information to be valid until the end of the firmware step. Each has a latch dedicated to that purpose. The pbus to dbus latch is BUSPD(0-7) and the splatter latch is BUSPS(0-3).

3.6.4 Interface control circuitry (see lbd pages 9m, 12m, 18m, and 33m)

Sometime during the middle of each firmware step, the address of the next firmware step is determined by mechanisms described in 3.14. Sometime near the end of each firmware step, the output of the control-store array (the next firmware word) becomes valid. The MG field emanates from the control-store array at bits 67-71 (CSMG67-71) and is captured in five control-register flops (CRMG00-04). Processor timing is such that CSMG67-71 are valid at least 15ns before the end of each step allowing certain decisions to be made before the next step actually begins. Two decisions are made which are related:

- 1. Does the action in the upcoming step require that a request to the MEGABUS or Cache/Local Memory be intiated?

- 2. Does the action in the upcoming step require that the present step be delayed in terminating?

If, for any reason, a transaction between the processor and an external system element is in process, the signal MGBUSY is on. As an illustration of the two decisions above, suppose a firmware sequence is encountered which calls for two memory writes in two consecutive firmware steps. As the first step nears completion, CSMG67-71 alerts the request logic contained in the PAL (BUSNOW, LOCNOW) that the next step will initiate (another) transaction but, since only one transaction may proceed at a time and since the first memory write is still in process, this step must be delayed in terminating (stalled). Thus, MGBUSY and CSMG67,68 will stall the clock until the first write is complete (see 3.12 for more details about clock stalls). MYASKK/CAHREQ get a chance at the beginning of every step and are, of

PAGE 3-10

HARDWARE DESCRIPTION

course, structured to assume that whatever stall was required, has occurred and has been released. When a Local Memory is connected to the local port (rather than a Cache), writes may be directed to it rather than the MEGABUS. When the first write was sent to the Local Memory, MGBUSY remains true until CAHREO relaxes whereas if the first write was directed at the MEGABUS, MGBUSY remains true until MYASKK relaxes.

### 3.6.4.1 Writes via the MEGABUS

When performing a memory write or an I/O "output", the sequence is as follows:

- 1. MYASKK comes on at the beginning of any step which initiates a memory write.

- 2. as soon as the MEGABUS tie-breaker becomes not busy (BSBUSY), MYREQT comes on.

- 3. the CUP16 will now participate in the next tie-break. Typically, about 75ns are required to "fetch" the bus. If the tie-break was triggered by a lower priority MEGABUS element, the CUP16 could win in 24ns! Because the CUP16 is designed for the typical case, its address and data (and parity) signals are not ready before the 70ns point in the initiating step. When MEGABUS access is granted to the CUP16, all of the inputs to MYDCNS will be satisfied save one (MYDCNP) which will activate only when the internal information is valid.

- 4. MYDCNN sets enabling the (26S10) address and data transmitters.

- 5. The MEGABUS element to which this transaction is directed, signals BSACKR, ackowledging the responsibility for completing the request (e.g., writing the memory location).

- 6. BSACKR clears MYASKK (MYDCNN and MYREOT as well) which causes MGBUSY to go off, releasing a stall which may have been waiting for the termination of the write.

Note the distinction among REQNOW, MYASKK/MYREQT. REQNOW is synchronized to the CUP clock and is on during MEGABUS (and Cache/Local Memory initiation steps) only. MYASKK and MYREQT are synchronized to the MEGABUS timing; MYASKK clears at the trailing edge of the MYDCNN which clears MYREQT signifying that the transaction has been accepted by the other party.

Once any request is initiated, the firmware sequence is permitted to go on its merry way, ignoring the MEGABUS and Cache/Local Memory interfaces until such time as a resynchronization point is encountered (e.g., a data stall, a new MEGABUS or Cache/Local Memory transaction initiation). During this interval, the transaction is remembered in three storage elements:

- 1. the control information is in the "fred" register (FRSHBC, FRLOCK, FRMREF, FRWRIT and FRDBPL).

- 2. the twenty-four-bit address is "frozen" on the address bus by ADRPEN, ADRAEN, ADRBEN, and RUPTEN.

- 3. the data to be written (if any) is in outr (OUTR00-15).

PAGE 3-11

HARDWARE DESCRIPTION

## 3.6.4.2 Writes to the Local Memory

When performing a memory write to the Local Memory, the sequence is as follows:

- 1. LOCNOW signifies that a Cache/Local Memory operation is to be initiated (i.e., the Local Memory is connected and On-line) and FWRITE signifies that the operation is to be a write.

- 2. CAHREQ signals the request to the Local Memory. FRBDWR sends OUTR to the Local Memory's data lines.

- 3. The Local Memory captures the entire transaction at its first idle moment and signals CYCADN which clears CAHREO signifying the completion of the write operation.

### 3.6.4.3 Reads

Reads are also complicated by the existence of the Cache/Local Memory. If the Cache/Local Memory is not present or is off-line (CACHON is off), all reads are directed to the MEGABUS. If the Cache/Local Memory is present and on-line, then memory reads which do not attempt a "lock" (FRLOCK) are directed through the Cache/Local Memory. All other reads (locks or I/O) are directed through the MEGABUS path. For any read, REQNOW causes SETDCP which, with the help of a PAL decoding the MG and FL fields, emits five control signals captured by the "fred" register and emits three signals which signify what kind of information is being read. CPDUES means procedure is being requested, CDDUES means that data is being requested and CADUES means that the data being requested is to be placed into inra (when it arrives). The arrival of information from either source is signalled by MYSHRP for procedure and MYSHRD for data.

#### 3.6.4.3.1 Cache/Local Memory reads

LOCNOW emanates from a PAL and with proper timing, causes CAHREO. Implied by LOCNOW are both the firmware bit signifying a Cache/Local Memory request (CSMG73) and the Cache/Local Memory On-Line signal. The Cache/Local Memory request is not allowed to be true for read/lock or I/O read operations. When the Cache/Local Memory receives CAHREO, it accesses the location specified by the address bus and returns sixteen bits (CADP00-15) and a data strobe (CYCADN). The Cache/Local Memory does not "double-pull" (FRDBPL is ignored), does not participate in lock transactions (FRLOCK and FRSHBC are off), and only performs memory references (FRMREF is on).

#### 3.6.4.3.2 MEGABUS reads

BUSNOW emanates from a PAL, sets MYASKK which causes MYREQT and later, after MYDCNP has waited for the dust to settle, provides MYDCNN; the appropriate "due" flop is set; all as previously described.

When a double-pull procedure read is requested, the memory may or may not send two transfers; if BSDBPL accompanies the first sixteen-bits, the memory promises to send another sixteen-bits. PRCDUE clears at the arrival of the last sixteen-bits.

When a double-pull data read is requested, DATDUE clears similarly when the last sixteen-bits arrive distinguishing the two cases as above. Note that when DATDUE is on and FRADUE is off, it means that sixteen bits are due for delivery into inrb.

**PAGE 3-12**

HARDWARE DESCRIPTION

If the reference does not succeed, either because it encountered a time-out or because the reference was nak'ed (BSNAKR), the due flops are cleared by DUECLR.

### 3.6.5 MEGABUS response circuits (see lbd page 8m)

٠.

When MEGABUS cycles are directed to the CUP, channel recognition logic activates the response circuitry. The response circuitry generates MYACKR or MYNAKR and sends the response to the MEGABUS element which initiated the transaction. The response circuitry also creates timing signals which allow the capturing of information pertinent to the transaction. A PAL receives information about the MEGABUS cycle as described below and creates signals captured in flops "at the middle of the MEGABUS cycle:

- 1. The channel recognition logic comprises a 74F521 (MYCHAN.0A) eight-bit comparator, two 74S86's (MYCHAN.0B,0C) one-bit comparators, and a 74S260 (MYCHAN.00) which makes the total determination that the channel number associated with a MEGABUS cycle matches the channel-number switches (MYCH00-09).

- 2. Integrity information (BSAPOK and BSDPOK) which, with the help of 74AS280 parity checkers signify that the MEGABUS address, data and command leads agree with the transmitted parity bits.

- 3. "State Machine" information indicating whether "Second-Half data is expected (PRCDUE, DATDUE, FRADUE), whether the CUP is now processing an interrupt (RPSYNC), whether the CUP is fully ON-LINE (P6SYNC) and whether the CUP is operating in "Force-Error" mode (FRCERR).

- 4. A stimulus which indicates that the Function-Code 01 feature is enabled and that a function code 01 bus cycle addressed to the CUP is now occurring having a "one" in its most-significant data bit (BSDT00).

**PAGE 3-13**

#### HARDWARE DESCRIPTION

The eight outputs of this PAL provide the D input to flops each of which is responsible for an aspect of either providing a proper MEGABUS response or of capuring data into an appropriate storage register:

- MBSHRP activates MYSHRP when procedure is arriving via the MEGABUS (LMSHRP activates MYSHRP when procedure is arriving from the Local Memory)

- MBSHRD activates MYSHRD when data is arriving via the MEGABUS (LMSHRD activates MYSHRD when data is arriving from the Local Memory)

- MBINRA activates INRACK clocking 16 data bits into INRA when that data is arriving via the MEGABUS (LMINRA activates INRACK when the data is arriving from the Local Memory)

- MBINRB activates INRBCK clocking 16 data bits into INRB when that data is arriving via the MEGABUS (LMINRB activates INRBCK when the data is arriving from the Local Memory)

- MBACKR activates MYACKR when the CUP acknowledges a MEGABUS cycle whether receiving requested data or receiving an (unsolicited) interrupt cycle

- MBNAKR activates MYNAKR when the CUP refuses an interrupt MEGABUS cycle (because it is already processing one). TONAKR activates MYNAKR when the CUP is Channel zero and a bus cycle has not otherwise receive a response for 5 microseconds.

- MBINTR activates MYINTR when the CUP accepts an interrupt bus cycle. MBINTR captures into ADRx the MEGABUS address leads associated with the interrupt cycle and captures into INRX the data lead associated with the interrupt cycle.

- MBINIT activates INITFF when a function-code 01 is accepted. INITFF causes the CUP to enter its QLT firmware sequence.

3.7 Temporary and Permanent Flags (block diagram identifier VII)

There are sixteen flags organized as two groups of eight. All sixteen are controlled by the FL firmware field.

3.7.1 temporary flags (see lbd page 15d)

The temporary flags are controlled by the FL field (CRFL00-05). Seventeen of the sixty-four possible codes are devoted to the temporary flags; one to clear them all (and perform other functions), eight to set one of them at a time and eight to clear one of them at a time. The flops themselves are a 74LS259. One 74S138 output (GPINIT) determines when a broadside clear occurs, and a 74S10 (FLGTCK) determines when a one-bit change occurs. The polarity of the change is determined by the data input CRFL02. Which flop is to change is determined by the select inputs CRFL03-05. The eight outputs are synchronized by a 74S374 and sent to eight test-condition inputs (see 3.14).

PAGE 3-14

### HARDWARE DESCRIPTION

Some temporary flags have side-effects as shown in Table 3-10.

| TA           | BLE | 3-10      |       |

|--------------|-----|-----------|-------|

| SIDE-EFFECTS | OF  | TEMPORARY | FLAGS |

| FLAGT0 | 16-way splatter (see 3.14)                   |

|--------|----------------------------------------------|

| FLAGT1 | 16-way splatter and shift-end-effect control |

| FLAGT2 | 16-way splatter                              |

| FLAGT3 | 16-way splatter                              |

| FLAGT4 | undedicated                                  |

| FLAGT5 | undedicated                                  |

| FLAGT6 | data input to SCRAM                          |

| FLAGT7 | undedicated                                  |

## 3.7.2 permanent flags (see 1bd page 23m)

The permanent flags are also controlled by the FL field (CRFL00-05). Sixteen of the possible sixty-four codes are devoted to the permanent flags; eight to set one of them at a time, and eight to clear one of them at a time. A broadside clear occurs at master clear. The flops themselves are a 74S259. A 74S10 (FLGPCK) determines when a one-bit change occurs. The polarity of the change is determined mostly by CRFL02 overridden by the general error detector SYRCLK. Which flop is to change is determined by the select inputs CRFL03-05. The eight outputs are synchronized by a 74S374 and sent to eight test conditions (see 3.14). Permanent flag #5 controls how the CUP reacts to hardware detected errors; if FLGEP5 is off, the error reason code is captured in the syndrome and an unscheduled branch to firmware location zero occurs; if FLGEP5 is on, only the reason code is captured. Permanent flag #7 (FLAGP7) is one of the "break" (COFEBK) stimuli.Other permanent flags also have side-effects as shown in Table 3-11.

| ТА           | BLE | 3-11      |       |

|--------------|-----|-----------|-------|

| SIDE-EFFECTS | OF  | PERMANENT | FLAGS |

| FLAGP0 | on line                                        |

|--------|------------------------------------------------|

| FLAGP1 | QLT failed (if FLAGP0=0)                       |

| FLAGP2 | generate even parity to OUTR etc (if FLAGP0=0) |

| FLAGP3 | undedicated                                    |

| FLAGP4 | undedicated                                    |

| FLAGP5 | inhibit disaster                               |

| FLAGP6 | accept MEGABUS interrupts                      |

| FLAGP7 | firmware "interrupter"                         |

## 3.8 Nibble Shifter (block diagram identifier VIII)

The nibble shifter is the only connection between the zbus and the dbus and is therefore in a critical path. The shifter is really a six-nibble rotator; there is no distinction, for instance between shifting one nibble left and shifting five nibbles right.

PAGE 3-15

#### HARDWARE DESCRIPTION

#### 3.8.1 shifter data flow (see lbd pages 13d and 14d)

11

The shifter is implemented with twelve 25S10's connected as three parallel groups of four. The first group is enabled when the shift distance prescribed by the SD field (CRSD00-02) is either zero, one, two, or three; the second group is enabled when the shift distance is either zero, one, four, or five; and the third group is enabled when the shift distance is the shift distance is two, three, four, or five. In each step, two of the three groups are enabled, producing twenty-four outputs.

The 25S10 chips whose output names are SHFT00.SA, SHFT04.SA, SHFT08.SA and SHFT12.SA reveals first that these chips are enabled for shift distances of 0, 1, 2, or 3 and that, for a distance of zero, each chip internally connects its four outputs to its lowest four inputs; for a shift distance of one, the four outputs are connected to the next higher four inputs; for a shift distance of two, to the next higher four inputs; and for a shift distance of three, to the top four data inputs.

The second group of four shifter chips (SHFTxx.SB) operates like the first, but is enabled for shift distances of zero, one, four, or five and thus their data inputs are biased eight bit positions.

The third group of four shifter chips operates like the other two, but is enabled for shift distances of two, three, four, or five and thus their data inputs are biased sixteen bit positions.

3.8.2 shifter control (see lbd pages 5d and 13d)

The three control register flops CRSD(00-02) are decoded by SHGCEN to enable the third group of shifter chips. The first and second group enables require no decoding.

3.9 Arithmetic and Miscellaneous Indicators (block diagram identifier IX)

There are six arithmetic indicators and two miscellaneous indicators. The intent of these indicators is to allow the coder to remember some characteristic(s) of some data for the purpose of affecting the addressing sequence of a subsequent firmware routine.

3.9.1 arithmetic indicators (see lbd pages 11d and 12d)

Five of the six arithmetic indicators derive their inputs from the output of the alu. The sixth samples the least-significant bit of the zbus (BUSZ31).

The overflow indicator (INOVFL) captures whether the carry into alu bit 08 was not equal to the carry out of alu bit 08 (AUOVFL).

The carry indicator (INCARY) captures whether a carry occurred out of alu bit 08 (AUCO08).

The sign indicator (INSIGN) captures whether the alu's most-significant bit was on (AUSIGN).

The zero indicator (INZERO) captures whether the alu output was zero (AUZERO).

Double zero (INZRDB) is derived from the alu being zero in this step and the zero indicator being previously on.

The indicators are captured at the behest of the FL field where either of two 74S138 outputs (IIBCLD or INDLD1) loads the six arithmetic indicators.

PAGE 3-16

HARDWARE DESCRIPTION

#### 3.9.2 miscellaneous indicators (see lbd pages 11d and 15d)

There are two miscellaneous indicators. They are captured in a 74S174 by INCLK2 derived from a 74S138 output with pulse shaping.

## 3.9.2.1 scram indicator

The stop code ram is a 256-location by one-bit-wide memory, addressed from byte y of the dbus. It is written from FLAGT6 under command of CRAMIT, a write pulse created from another output of the 74S138 properly timed by MCLKVL. The output data from the scram is exclusive-ored with FLAGT6 forming STOPCD, which is routed to the indicator INSCRM.

## 3.9.2.2 difbuf indicator

This mechanism compares fifteen bits of the dbus with fifteen bits of the zbus, utilizing fifteen 74S86 exclusive-or circuits, three 74S260 circuits, and one 74S10.

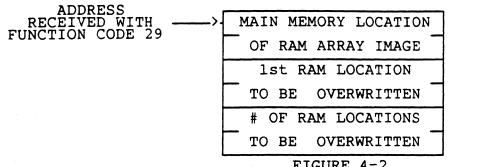

## 3.10 The OP Register (block diagram identifier X)