| Honeywell HONEYWELL INFORMATION SYSTEMS                          | •                                            | SPEC. NO.<br>60149777 |      | SHEET<br>1/81 | REV. |

|------------------------------------------------------------------|----------------------------------------------|-----------------------|------|---------------|------|

| Billerica, MA                                                    |                                              | PROJECTION -          | CODE |               |      |

| PREPARED BY DATE  K. Kowal  APPROVED BY DATE  See Approval Sheet | Engineering Products<br>Wren Device Controll |                       | Part | 1             |      |

## REVISION RECORD

| REV. | AUTHORITY | DATE    | SIGNATURE | SHEETS AFFECTED                                  |

|------|-----------|---------|-----------|--------------------------------------------------|

| A    | BLDCD7729 | 6/27/83 | KIK       | 1/87, 1.1, 2.0 throug through 2.4, 3 through 86F |

| В    | BLCE7139  | 2/14/84 | 14 A.K    | 1/81, 1.1, 2.0 through 2.4, 3 through 83F        |

#### NOTE

This EPS-1, if not revised within one year, should be considered obsolete and therefore reference should be made to the appropriate product manual.

This document and the information contained herein are confidential to and the property of Honeywell Information Systems Inc. and are made available only to Honeywell employees for the sole purpose of conducting Honeywell's business. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager; and shall not be disclosed or distributed (a) to persons who are not Honeywell employees, or (b) to Honeywell employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this pocument no longer has need for the document for the authorized Honeywell purpose, this document and any copies thereof shall be returned to honeywell Vice President.

| Monoravall                    | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 1.1   | В    |

| HONEYWELL INFORMATION SYSTEMS | 001-13777 | T • T |      |

HONEYWELL INFORMATION SYSTEMS SYSTEMS ENGINEERING - BOSTON

ENGINEERING

PRODUCT

SPECIFICATION

( EPS - 1 )

SUBSYSTEM LEVEL

VERSION: Approval DATE: 2/14/84

PRODUCT CALENDAR REFERENCE:\_\_\_\_\_

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| and ney wen                   | 60149777  | 2.0   | В    |

| HONEYWELL INFORMATION SYSTEMS | 33117     |       |      |

| Secti        | on      |                                | * , .                                   | Pag  |

|--------------|---------|--------------------------------|-----------------------------------------|------|

| SECTI        | ON 1 IN | TRODUCTION                     | • • • • • • • • • • • •                 | 3    |

| 1.1          | Scope   | •••••                          | • • • • • • • • • •                     | 3    |

| 1.2          | Objecti | ves                            |                                         | 3    |

| 1.3          | Documer | tation                         |                                         | 14   |

|              | 1.3.1   | Related Documents              | • • • • • • • • • •                     | 4    |

|              | 1.3.2   |                                |                                         | 4    |

| 1.4          | Definit | ions                           | •••••                                   | 5    |

|              |         | 7                              | <u>.</u>                                |      |

| SECTI        | ON 2 AF | CHITECTURE                     | • • • • • • • • • • • • • • • • • • • • | 7    |

| 2.1          | Oromii  |                                |                                         | 7    |

| 2.2          |         | omponents                      |                                         | 7    |

| 2.2          | 2.2.1   | Wren Device Controller         |                                         | 7    |

|              | 2.2.2   | Wren Disk Drive                |                                         | 9    |

|              | 2.2.3   | WDD Power Supply               |                                         | 9    |

|              | 2.2.3   | MDD Lower, Subbit              | • • • • • • • • • • • •                 | 9    |

| SECTI        | ON 3 FU | NCTIONAL REQUIREMENTS          | • • • • • • • • • •                     | 11   |

| 3.1          | Basic F | unctions                       |                                         | - 11 |

| <b>J</b> • · | 3.1.1   | Configuration and Simultaneity |                                         | 11   |

|              | 3.1.2   | WDC Control                    |                                         | 13   |

|              | 30.02   | 3.1.2.1 Command Transfer       |                                         | 13   |

|              |         | 3.1.2.2 Interrupts             |                                         | 13   |

|              |         | 3.1.2.3 Data Transfer          |                                         | 14   |

|              | 3.1.3   | Overview of WDC Access         |                                         | 15   |

|              |         |                                |                                         |      |

| SECTI        | ON 4 DE | VICE INTERFACE                 | • • • • • • • • • • • • • • • • • • • • | 17   |

| 4.1          | User In | iterfaces                      |                                         | 17   |

| 4.2          | Externa | l Interfaces                   |                                         | 17   |

|              | 4.2.1   | Controller-IOP Interface       |                                         | 17   |

|              | 4.2.2   | Wren Device Interface          |                                         | 17   |

| 4.3          | Control | ler Output Lines               |                                         | 19   |

| •            | 4.3.1   | Drive Select                   |                                         | 19   |

|              | 4.3.2   | Direction                      |                                         | 20   |

|              | 4.3.3   | Step                           |                                         | 21   |

|              | 4.3.4   | Head Select                    |                                         | 21   |

|              | 4.3.5   | Return to Zero                 |                                         | 22   |

| Secti | on      |               | •            |       |     |                   |                                         | Page |

|-------|---------|---------------|--------------|-------|-----|-------------------|-----------------------------------------|------|

|       | 11 7 6  | Deed Emek     | 1            |       |     |                   | • • • • • • • • • • •                   | . 22 |

|       | 4.3.6   |               |              |       |     |                   |                                         |      |

|       | 4.3.7   |               |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 4.3.8   | •             |              |       |     |                   | • • • • • • • • • • • • • • • • • • • • |      |

| •     | 4.3.9   |               |              |       |     |                   | • • • • • • • • • • • •                 | _    |

| ••    | 4.3.10  |               |              |       |     |                   | • • • • • • • • • • •                   |      |

| •     | 4.3.11  |               |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 4.3.12  |               |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 4.3.13  |               |              |       |     |                   | • • • • • • • • • • •                   |      |

| 4.4   |         | •             | • •          |       |     |                   | • • • • • • • • • • • •                 |      |

|       | 4.4.1   |               | •            |       |     |                   | • • • • • • • • • • •                   |      |

| •     | 4.4.2   |               |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 4.4.3   | •             |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 4.4.4   |               |              |       |     |                   | • • • • • • • • • • •                   | -    |

|       | 4.4.5   |               |              |       |     |                   |                                         |      |

|       | 4.4.6   |               |              |       |     |                   | · · · · · · · · · · · · ·               |      |

| •     | 4.4.7   | Read Data     | "+" and "-"  | ·     |     |                   |                                         | . 27 |

| 4.5   | Data Fo | rmat          |              |       |     | · • • • • • • • • | • • • • • • • • • • •                   | . 27 |

|       | 4.5.1   | Format De     | finition     | ••••• |     |                   | • • • • • • • • • • •                   | . 27 |

|       | 4.5.2   | Intersect     | or Gap, ISG. |       |     | • • • • • • • •   | • • • • • • • • • • •                   | . 29 |

|       | 4.5.3   | Address A     | rea          |       |     |                   | • • • • • • • • • •                     | . 29 |

|       | 4.5.4   | Data Area     |              |       |     |                   | • • • • • • • • • •                     | 30   |

|       |         |               |              |       |     | 7-                |                                         |      |

| SECTI | ON 5 IN | STRUCTIONS    |              |       |     |                   | • • • • • • • • • • •                   | 31   |

|       |         |               |              |       | ur. | 7 t,              |                                         |      |

| 5.1   | General |               |              |       |     |                   |                                         | _    |

|       | 5.1.1   | I/O Comma     | nds          |       |     |                   | • • • • • • • • • • •                   | • 33 |

| 5.2   | Instruc | tions         |              |       |     |                   | • • • • • • • • • • •                   | 36   |

|       | 5.2.1   | IOLD          |              |       |     |                   |                                         | . 36 |

|       |         | 5.2.1.1       | Output Addr  | ess   |     |                   | • • • • • • • • • • •                   | 37   |

|       |         | 5.2.1.2       | Output Rang  | e     |     |                   | • • • • • • • • • • •                   | . 37 |

|       | 5.2.2   | Output Co     |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 5.2.3   |               |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 5.2.4   | •             | -            |       |     |                   | • • • • • • • • • • •                   | _    |

|       | 5.2.5   |               |              |       |     |                   | • • • • • • • • • • •                   |      |

|       | 5.2.6   | -             | ~            |       |     |                   | • • • • • • • • • • •                   |      |

|       | 30200   | -             |              |       |     |                   |                                         |      |

|       |         | 5.2.6.2       |              |       |     |                   | • • • • • • • • • • •                   |      |

|       |         | 5.2.6.3       |              |       |     |                   | •••••                                   |      |

|       |         | 5.2.6.4       |              |       |     |                   | • • • • • • • • • • •                   |      |

|       |         | 5.2.6.5       |              |       |     |                   | • • • • • • • • • • • •                 | _    |

|       |         | 5.2.6.6       |              |       |     |                   | • • • • • • • • • • • • •               | _    |

|       |         | 5.2.6.7       |              |       |     |                   | • • • • • • • • • • • • •               |      |

|       |         | 5.2.6.8       |              |       |     |                   | • • • • • • • • • • • •                 |      |

|       |         | 5.2.6.9       |              |       |     |                   | • • • • • • • • • • • • •               |      |

|       |         |               |              |       |     |                   |                                         |      |

|       |         | / a a U a I U |              |       |     | _, ~ ~ , .        |                                         |      |

| Hamarayall                    | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 601H9777  | 2.2   | B    |

| HONEYWELL INFORMATION SYSTEMS |           | 2.2   | -    |

| Secti | on,                                     |                                           | Page       |

|-------|-----------------------------------------|-------------------------------------------|------------|

| •     | 5.2.7                                   | Output Control Word                       | 46         |

|       | • • • • • • • • • • • • • • • • • • • • | 5.2.7.1 Initialize                        | 46         |

| •     |                                         | 5.2.7.2 Stop I/0                          | 46         |

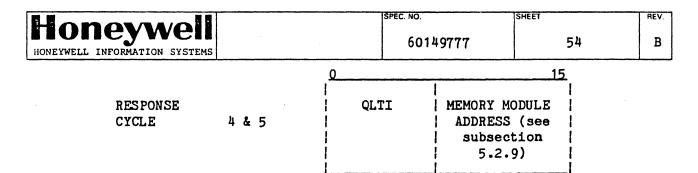

|       | 5.2.8                                   | Input Memory Byte Address                 | 47         |

|       | 5.2.9                                   | Input Memory Module Address               | 47         |

|       | 5.2.10                                  | Input Range                               | 47         |

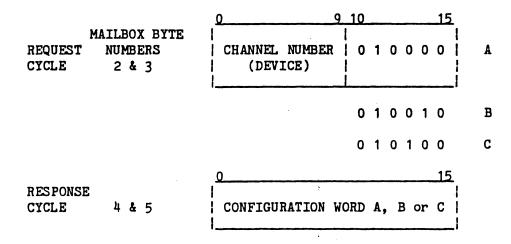

|       | 5.2.11                                  | Input Configuration Word A, B, or C       | 48         |

|       | 5.2.12                                  | Input Interrupt Control                   | 48         |

|       | 5.2.13                                  | Input Identification Code                 | 49         |

|       | 5.2.14                                  | Input Task Word                           | 49         |

|       | 5.2.15                                  | Input Status Word 1                       | 50         |

|       |                                         | 5.2.15.1° Device Ready                    | 50         |

|       | •                                       | 5.2.15.2 Attention                        | 51         |

|       | •                                       | 5.2.15.3 Device Fault                     | 51         |

|       |                                         | 5.2.15.4 Read Error                       | 51         |

|       | •                                       | 5.2.15.5 Program Error                    | 51         |

|       |                                         | 5.2.15.6 QLT Fault                        | 51         |

|       | f                                       | 5.2.15.7 Unsuccessful Search/Format Error | 52         |

|       |                                         | 5.2.15.8 Error Log Overflow               | 52         |

|       |                                         | 5.2.15.9 Successful Recovery              | 52         |

|       |                                         | 5.2.15.10 WDC Timeout                     | 52         |

|       |                                         | 5.2.15.11 RFU-MBZ                         | 52         |

|       | 46                                      | 5.2.15.12 Non-Existent Resource           | 52         |

|       | 5.2.16                                  | Input Status Word 2                       | 52         |

|       |                                         | 5.2.16.1 Corrected Read Error             | 53         |

|       |                                         | 5.2.16.2 Successful Retry                 | 53         |

|       |                                         | 5.2.16.3 Read/Write Fault                 | 53         |

|       | F 0 4F                                  | 5.2.16.4 Seek Error                       | 53<br>53   |

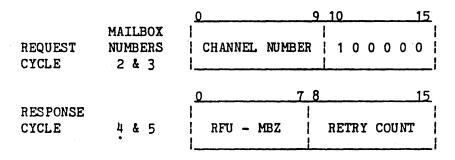

|       | 5.2.17                                  | Input Quick Logic Test Indicators         | 53<br>54   |

|       | 5.2.18                                  | Input Firmware Revision                   | 54<br>54   |

|       | 5.2.19                                  |                                           | 54         |

|       | 5.2.20                                  | Input Retry Count                         | 55<br>55   |

| 5.3   | 5.2.21<br>IOP-WDC                       |                                           | 56         |

| 2.3   | 5.3.1                                   | Command Sequence                          | 56         |

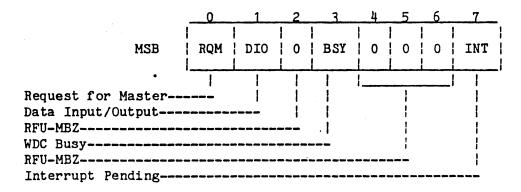

|       | 5.3.2                                   | Main Status Register                      | 56         |

|       | . 5.5.2                                 | 5.3.2.1 Request for Master - RQM          | 57         |

|       |                                         | 5.3.2.2 Data Imput/Output - DIO           | 5 <b>7</b> |

|       |                                         | 5.3.2.3 FDC Busy - BSY                    | 57         |

|       |                                         | 5.3.2.4 Interupt Pending - INT            | 57         |

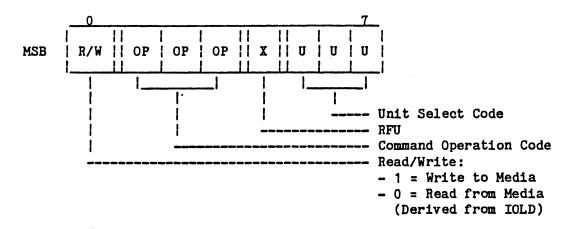

|       | 5.3.3                                   | Command Phase                             | 58         |

|       | 2.2.3                                   | 5.3.3.1 Command Header Byte               | 58         |

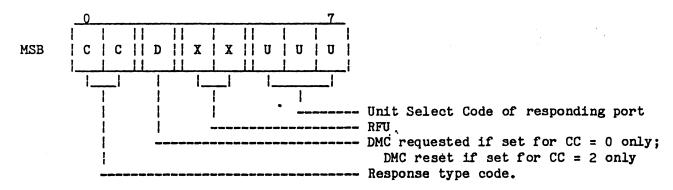

|       |                                         | 5.3.3.2 Initial Response                  | 58         |

|       | 5.3.4                                   | Execution Phase                           | 60         |

|       | 5.3.5                                   | Result Phase                              | 60         |

|       |                                         |                                           |            |

| Honoravoll                    | SPEC. NO.  | SHEET | REV. |

|-------------------------------|------------|-------|------|

| Honeywell                     | 60149777   | 2.3   | В    |

| HONEYWELL INFORMATION SYSTEMS | 1 00143111 | 2.5   | -    |

| Secti               | on                         |                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                           |

|---------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 5.4                 | Defect 1 5.4.1 5.4.2 5.4.3 | Management  EDAC Functionality  Read Error Retry  Media Defect Handling  5.4.3.1 Error Logging Procedure  5.4.3.2 Sector Reallocation                                                                                                                                                                                                                                                                                 | 60<br>62<br>62<br>63<br>64                                     |

| SECTI               | ON 6 PH                    | YSICAL AND LOGICAL STRUCTURES                                                                                                                                                                                                                                                                                                                                                                                         | 69                                                             |

| 6.1                 | Physical 6.1.1             | Physical Specifications - WDC.  6.1.1.1 Mechanical.  6.1.1.2 Environmental.  6.1.1.3 Electrical.  Physical Specifications - Wren Disk Drive.  6.1.2.1 Mechanical.  6.1.2.2 Environmental.  6.1.2.3 Electrical.                                                                                                                                                                                                        | 69<br>69<br>70<br>70<br>70<br>70<br>70                         |

| SECTI               | ON 7 PE                    | RFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                             | 73                                                             |

| 7.1<br>7.2<br>SECTI | Perform                    | ance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                  | 73<br>73<br>75                                                 |

| 8.1 8.2             | Maintai<br>8.2.1<br>8.2.2  | ty nability Maintainability Requirements 8.2.1.1 Mean Time to Repair 8.2.1.2 Mean Time Between Preventive Maintenance 8.2.1.3 Diagnostic Facility Localization Effectiveness Maintenance Strategy 8.2.2.1 Maintainability Features 8.2.2.2 Installation lity Product Life Mean Time Between Failures. Transient Error Rate. Recoverable Error Rate. Unrecoverable Error Rate. Recoverable Seek Error Rate Requirement | 75<br>75<br>75<br>76<br>76<br>76<br>77<br>78<br>78<br>79<br>79 |

| SECTI<br>9.1<br>9.2 | General                    | NFIGURABILITYvice Subsystem                                                                                                                                                                                                                                                                                                                                                                                           | 81<br>81<br>81                                                 |

## LIST OF ILLUSTRATIONS

| Figur                                                                       | e ·                                                                                                                                                                                                                                                                                                                         | Page                                                           |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2-1                                                                         | Disk Subsystem                                                                                                                                                                                                                                                                                                              | 8                                                              |

| 3-1<br>3-2<br>3-3<br>3-4                                                    | Channel Numbers  Hercules I/O Mailbox Map  Hercules Interrupt Mail Box  Hercules Register Mail Box                                                                                                                                                                                                                          | 12<br>12<br>13<br>14                                           |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11 | Wren Device Controller Interface Cables  Power Turn On and Drive Select  Track Access Timing.  Head Select Timing.  Offset Plus/Minus Timing.  Early/Late Strobe Enable Timing.  Offset Plus/Minus, Early/Late Strobe Timing.  NRZ Data and Clock Timing.  Index and Byte Clock Relationship.  Read Timing.  Sector Format. | 18<br>20<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>28<br>29 |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5                                             | Command Flow Chart                                                                                                                                                                                                                                                                                                          | 34<br>55<br>61<br>64<br>66                                     |

| LIST                                                                        | OF TABLES                                                                                                                                                                                                                                                                                                                   |                                                                |

| Table                                                                       |                                                                                                                                                                                                                                                                                                                             | Page                                                           |

| 5 <b>-</b> 1<br>5 <b>-</b> 2                                                | Instructions  Data Transfer Commands                                                                                                                                                                                                                                                                                        | 36<br>42                                                       |

| 7-1                                                                         | Operational Characteristics Summary                                                                                                                                                                                                                                                                                         | 73                                                             |

77

|                               | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 3     | В    |

| HONEYWELL INFORMATION SYSTEMS |           |       | 1 1  |

SECTION 1 INTRODUCTION

#### 1.1 SCOPE

This Engineering Product Specification defines the Wren Device Controller (WDC), which is a Hercules bus-mounted printed circuit board with logic providing control over the Wren Device Interface (WDI) and, connected, up to two Wren Disk Devices (WDDs). Functionally, the WDC emulates the command structure designed for Storage Module Drives (SMDs) and Cartridge Module Drives (CMDs) with a unique feature of providing a fixed media storage only on two or three platters. The WDC also performs medium defect reallocation for the complete volume with the same software visibility of sector 1 as on Lark.

The WDC is coresident on the same printed circuit assembly with the Sentinel streamer tape controller (STC, EPS-1 60149737) and shares some of the IOP logic with the STC. There is only one level of simultaneity for both WDDs and one STC.

## 1.2 OBJECTIVES

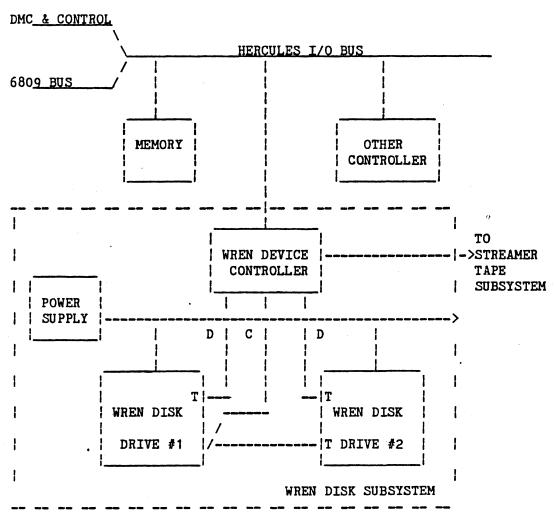

Four major components comprise the Wren Disk Subsystem (WDS):

- o Wren Device Controller

- o Up to two Wren Disk Drives with interface cables

- o Dc power cables to the power supply

- o Power supply.

| Homorowall                    | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 14    | В    |

| HONEYWELL INFORMATION SYSTEMS | 007.3111  | ,     | -    |

Only the WDC functionality is described in this EPS-1. The FDI utilizes two cables: a command cable and a data cable. The command (C) cable is a daisy-chain command/status cable. The data (D) cable is a radial cable for the data and clocks plus some control. The third cable is for the dc power only delivered from the separate power supply.

RESPONSIBILITY

TITLE

#### 1.3 DOCUMENTATION

NUMBER

## 1.3.1 Related Documents

|    | 60126298           | EPS-1 Level 6 Bus (Megabus)                                                     | Systems Engineering |

|----|--------------------|---------------------------------------------------------------------------------|---------------------|

|    | 60144453           | EPS-1 Hercules                                                                  | Systems Engineering |

|    | 60149661           | PFS 8" Fixed Disk Subsystem - Hercules/Helios-0                                 | Product Planning    |

|    | 60149674           | Finch Device Controller - Hercules                                              | Peripheral Systems  |

|    | MTG1               | PWA Test Equipment Connection Requirements                                      | AMDXT-TE            |

|    | MTG3               | PWA Microdiagnostic Creation                                                    | AMDXT-TE.           |

| 1. | 3.2 Refere         | nce Documents                                                                   |                     |

|    | 60129949           | Application Rules for Minicomputer and Terminals Products                       | Circuit Design      |

|    | Q4.1               | PWA/PWB Testability Design Rules                                                | PAE-TEE             |

|    | MG1                | Component Availability                                                          | AMDXT-TE            |

|    | MTG2               | PWA Test Documentation Requirements                                             | AMDXT-TE            |

|    | MTG4               | PWA Test Monitor/Test Box Design                                                | AMDXT-TE            |

|    | MTG5               | PWA Quality Logic Test Creation                                                 | AMDXT-TE            |

|    | MTG6               | PWA Test and Verification Program Creation                                      | AMDXT-TE            |

|    | MTG7               | PWA IC Socket Utilization                                                       | AMDXT-TE            |

|    | MTG8               | Design for Producibility, Installability, Main-<br>tainability & Replaceability | AMDXT-TE            |

|    | MPTG1              | PWB/PWA Producibility Guidelines                                                | AMDXT-TE            |

|    | 58035052           | Worldwide Maintenance Requirements                                              | FED                 |

|    | 77653332<br>Rev. B | Product Specification for Finch Disk Drive - Model 9410-3F                      | MPI. OKC.           |

|          | eywell ormation systems                                                    | 60149777    | SHEET  | 5/6  | REV. |

|----------|----------------------------------------------------------------------------|-------------|--------|------|------|

| 77653374 | Application Notes - Diagnostics for Finch Disk Drive                       | Model 9410  | MPI. C | OKC. |      |

| 77653461 | Application Notes - Interfacing a 9<br>Disk Drive with a 9410 Finch Disk D |             | MPI. C | OKC. |      |

| 77711078 | Product Specification for Wren Disk 9415-3                                 | Drive Model | MPI. C | OKC. |      |

| 77711098 | Specification for Finch Device Inte                                        | rface       | MPI. C | OKC. |      |

## 1.4 DEFINITIONS

CMD - Cartridge Module Drive

CRC - Cyclic Redundancy Check

CPU - Central Processor Unit, LSI-6

DMC - Direct Multiplex Control

DS - Disk Subsystem

EDAC - Error Detection and Correction

EOT - End of Track (Record)

FDI - Finch Device Interface

IOP - Input/Output Processor (6809)

IOPB - IOP Bus

LED - Light Emitting Diode

MBZ - Must Be Zero

ORU - Optimum Replaceable Unit

PWA - Printed Wire Assembly

PWB - Printed Wire Board

QLT - Quick Logic Test

RFU - Reserved for Future Use

RPS - Rotational Position Sensing

SMD - Storage Module Drive

T&V - Test and Verification

WDD - Wren Disk Drive.

WDS - Wren Disk Subsystem

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

|                               | 60149777  | 7     | В    |

| HONEYWELL INFORMATION SYSTEMS |           | •     |      |

SECTION 2 ARCHITECTURE

#### 2.1 OVERVIEW

The Disk Subsystem (DS) provides the Hercules computer systems with facility to store and retrieve data from mass storage media mounted on a disk device. Up to two WDDs can be cabled up to one WDC which can process simultaneously a single data transfer and one Seek command; all Hercules commands are accepted by the WDC in its nonbusy state. The WDC interfaces with other Hercules systems via the 6809 bus which can be Communications Adapter, Memory, IOP, etc. All controllers on the 6809 bus can function independently and concurrently utilizing the 6809 bus asynchronously.

## 2.2 MAJOR COMPONENTS

#### 2.2.1 Wren Device Controller

The WDC is a microprogrammed peripheral control unit which can interface with up to two WDDs (see Figure 2-1) cabled via connectors mounted on the device printed circuit board. The microprocessor portion of the WDC is generalized to facilitate its application as a control element for higher capacity devices. In addition to providing the IOP Bus command protocol supervision for three independent channels' combinatorial logic, the WDC interfaces with the IOP Bus as well as with the WDD connectors. The WDC performs the following functions:

- o Execution of IOP Bus sequences

- o Status and control register storage in dedicated, per channel, random access memory

| Llomoravoll                   | SPEC. NO.   | SHEET | REV. |

|-------------------------------|-------------|-------|------|

| Honeywell                     | 60149777    | 8     | В    |

| HONEYWELL INFORMATION SYSTEMS | 1 331.13111 | · ·   |      |

- o DMC data transfers

- o FDI dialog control with serial-parallel and parallel-serial data conversion and associated error detection and correction

- o Medium defect handling using the prerecorded error logs in the highest numbered cylinder.

D = Data Cable

C = Command Cable

T = Terminators

Wren Device Configuration

Figure 2-1 Disk Subsystem

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| I I OHICY WELL                | 60149777  | 9/10  | В    |

| HONEYWELL INFORMATION SYSTEMS |           |       | 1    |

#### 2.2.2 Wren Disk Drive

The WDD is a small, random access, rotating 5.25-inch disk, mass memory device with fixed disk media storage. It employs rigid disk technology with a servo surface and low mass flying read/write heads attached to a rotary voice coil positioner. The unformatted storage capacity of the WDD is:

## WDD Configuration 9415-32-3

- o 35 Mbytes five surfaces of three disks

- o One servo control surface.

Basic components of the WDD are base casting and spindle, spindle drive motor, spindle and disk assembly, rotary voice coil actuator assembly with read/write heads, base Printed Wire Assembly (PWA) with LSI circuitry, motor control PWA, and read/write preamp PWA.

The WDD interface with the WDC comprises two cables: one radial D (data) cable and one daisy-chainable C (command) cable.

#### 2.2.3 WDD Power Supply

The WDD power provides dc voltages required to operate the WDD. The voltages are +5 V and +12 vdc.

| Honeywell                     | SPE      | EC. NO.  | SHEET | REV. |

|-------------------------------|----------|----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS |          | 60149777 | 11    | В    |

| HONEIWELL INFORMATION SISTEMS | <u> </u> |          |       |      |

SECTION 3 FUNCTIONAL REQUIREMENTS

### 3.1 BASIC FUNCTIONS

## 3.1.1 Configuration and Simultaneity

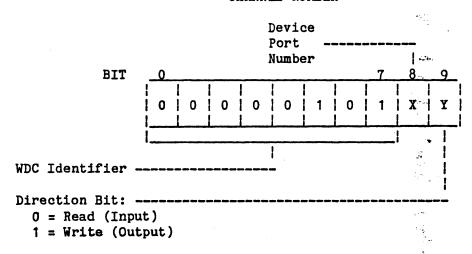

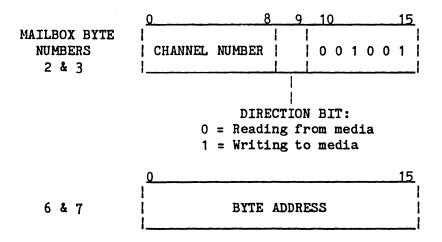

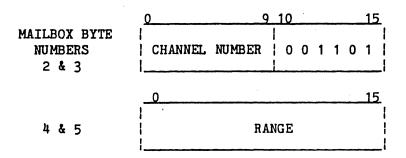

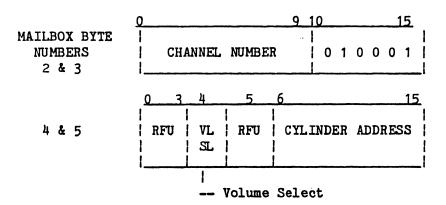

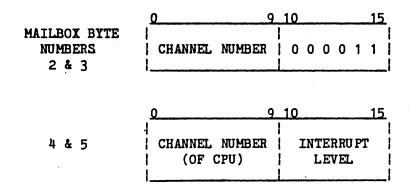

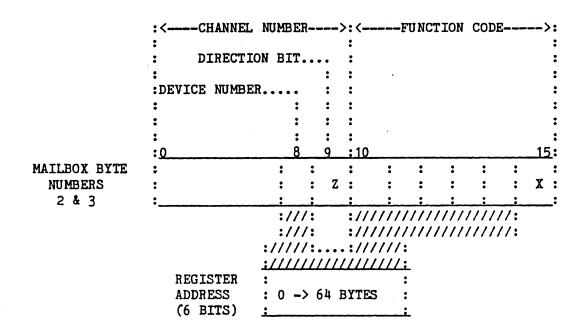

Devices attached to the WDC are software addressable via a channel number. Each device has two channel numbers assigned, differing from each other only in the low-order bit position (the direction bit). When an IOLD instruction is issued to an WDC, the direction bit of the output address channel number specifies whether this is an input or an output data transfer. For all other commands, the direction bit is ignored by the hardware. Figure 3-1 outlines the composition of the channel number. Bits 0 through 9 are assigned at system installation and must conform to constraints defined in the L6 Bus EPS-1. Software visibility of the devices attached to the WDC is such that the device is, in general, independent of all others on the bus.

The WDC and the IOP provide a single level of simultaneity (only one data transfer can be active in the subsystem consisting of two WDC channels and one streamer channel) and supports the following:

- o A nonbusy device must accept all instructions directed to it, (i.e., IOLD, Configuration Words A and B, Task Word, etc.) even though a data transfer may be active over another device. An instruction may be "waited" for a period not exceeding 350 microseconds (Ref. 5.3.2.3).

- o Following completion of a data transfer operation, any Seek orders received should be initiated prior to the start of any data transfer operations.

| Hopovy                        | SPEC. NO. | SHEET | REV. | 1 |

|-------------------------------|-----------|-------|------|---|

| Honeywell                     | 60149777  | 12    | В    |   |

| HONEYWELL INFORMATION SYSTEMS | 00113111  | , ,=  | _    | ı |

- o The Channel Number for the Wren Disk Drive in the Hercules CPU/IOP is fixed as 0500<sub>16</sub>.

- o Channel Numbers for the Wren Disk Drives are 500<sub>16</sub> for device #1 and 580<sub>16</sub> for device #2.

- o WDD ID Number is assigned  $333X_{16}(X = 1, 3, 5 \text{ or } F; \text{ see subsection 5.2.13}).$

#### CHANNEL NUMBER

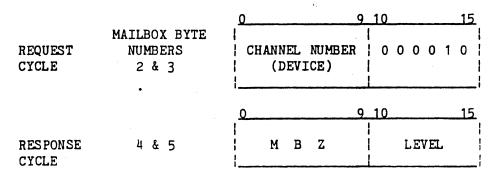

Figure 3-1 Channel Numbers (see Figure 3-2)

NOTE

The four highest order address bits are passed to the IOP through a hardware register.

Figure 3-2 Hercules I/O Mailbox Map

HONEYWELL CONFIDENTIAL & PROPRIETARY

| Honeywell                     | SPEC. NO.  | SHEET | REV. |

|-------------------------------|------------|-------|------|

| I I O I I E Y WE II           | 60149777   | 13    | В    |

| HONEYWELL INFORMATION SYSTEMS | 1 301.3111 | .5    |      |

## 3.1.2 WDC Control

## 3.1.2.1 COMMAND TRANSFER

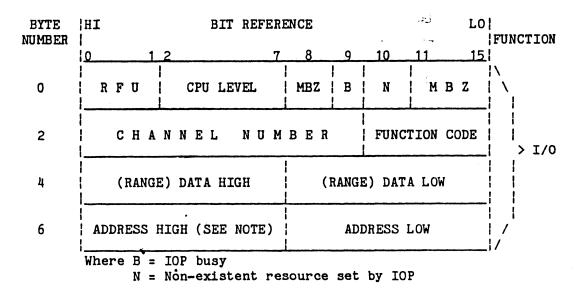

The IOP recognizes a command transfer request when the 6809 (IOP) recognizes a Non-maskable Interrupt (NMI) from the LSI-6 (CPU) and the content of the IOP's Mail Box is ready for interrogation. The IOP firmware is then invoked to process the information. For the not-busy case, the IOP completes the transaction by issuing an ACK (B=0) to the CPU. If, however, the IOP is busy executing a previously received command, the IOP interface hardware completes the transaction by issuing a NAK (B=1) to the CPU. When complete, the IOP resets the interrupt flop.

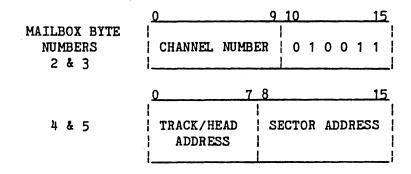

On receipt of a command, the IOP stores it in an appropriate table corresponding to the device Channel Number (bits 0 through 9) and depending on the Function Code (bits 10 through 15) of that command, either stores it in a queue to wait for a Task command or executes it immediately (i.e., Read Status command, etc.).

When an input from the IOP is requested by the CPU, the IOP responds to the NMI from the LSI-6 which now can read the data word contained in bytes 4 and 5. The NMI flip-flop is reset by the IOP when this is accomplished.

The address and data bus configurations of the CPU for the various commands are detailed in subsection 5.2.

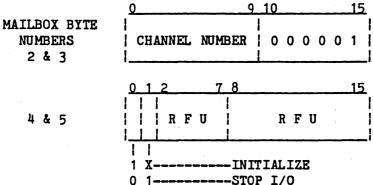

#### 3.1.2.2 INTERRUPTS

The current CPU Interrupt Level (byte 0, bits 2 through 7) is maintained by the CPU firmware. If the CPU Interrupt Level is lower than or equal to that of the interrupting channel, no interrupt from the IOP to the CPU is attempted, and, as long as this is true, the channel shall continue requesting an interrupt until it is accepted or the condition causing the interrupt is reset.

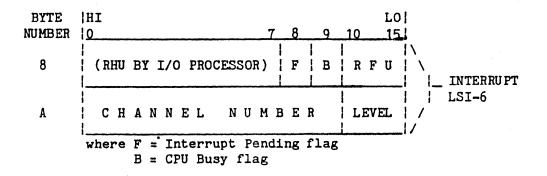

When an interrupt is serviced, the IOP loads the interrupt Mail Box (see Figure 3-3) bytes A and B and sets bit 8 (F) of byte 9 to a One then interrupt the LSI-6. The CPU reads both bytes A and B, clears the F bit and either sets bit B (bit 9 of byte (9) to a One if the interrupt is not accepted (NAKed) or a Zero if the interrupt is accepted.

Figure 3-3 Hercules Interrupt Mail Box

| Hopovyoll                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 14    | В    |

| HONEYWELL INFORMATION SYSTEMS | 337.77    |       |      |

#### 3.1.2.3 DATA TRANSFER

All data transfers associated with the WDC are executed in the Direct Multiplex Control (DMC) mode and in the byte format on the IOP bus.

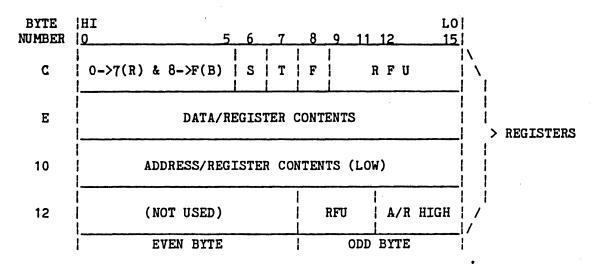

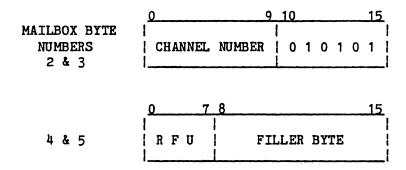

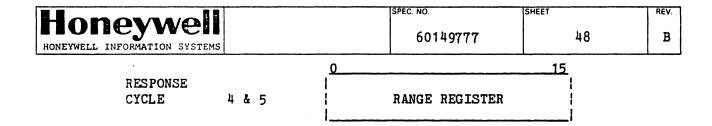

Data transfer procedure is initiated by the CPU loading the IOP with the set up commands, i.e., Configuration Word A, etc., through the I/O Mail Box (see Figure 3-2) and then issuing the Task command which triggers the IOP sequence. The IOP loads the address and range data into the Hercules Register Mail Box (Figure 3-4) for subssequent transfer to the CPU for DMC operation. Standard L6 disk commands are translated by the IOP into the IOP Protocol format (see subsection 5.3) which are then sent to the WDC. When the WDC is ready for data transfer, it makes a DMC request (an interrupt to the CPU) and the data proceeds to the CPU memory without the IOP's direct involvement. The CPU (under DMC control) provides the memory address and the WDC supplies the data to the main CPU memory for each byte of data.

This exchange continues until the end-of-range is indicated by the DMC to the WDC on the last byte of transfer.

where Byte C, bits 0 trough 3:

value 0 to 7 - CPU R register transfer in bytes E and F

value 8 to F - CPU B register transfer in bytes 10, 11, and 13

S = Direction flag:

0 is into the mail box

1 is into the CPU

T = Information type flag for bytes E through 11 and 13:

0 is DMC

. 1 is Register

F = Register operation in progress when set.

Figure 3-4 Hercules Register Mail Box

| Honeywell                     | SPEC. NO. | SHEET  | REV. |

|-------------------------------|-----------|--------|------|

| andincy well                  | 60149777  | 15/16  | В    |

| HONEYWELL INFORMATION SYSTEMS | 337.19111 | .5, .0 | -    |

#### 3.1.3 Overview of WDC Access

The WDC interface to the 6809 IOP bus emulates a general purpose bi-directional 8-bit wide bus using command and status protocol for communicating with peripheral controllers. Associated with a controller is a set of two registers which can be accessed by the IOP: a Status Register and a Data Register. The 8-bit Main Status Register contains the status information of the WDC and may be accessed at any time. The 8-bit Data Register (which actually consists of several bytes in a stack with only one byte presented to the IOP bus at a time) stores data, commands, parameters and WDC status information. Data bytes are read out of or written into the Data Register in order to program or obtain the results after a particular command. The main Status Register may only be read and is used to facilitate the transfer of data.

Commands are initiated by a multi-byte transfer from the IOP, and the result after execution of that command may also be a multi- byte transfer back to the IOP. Each command, therefore, consists of three phases:

- o Command Phase The WDC receives all pertinent information to execute a command

- o Execution Phase The WDC performs the required task.

- o Result Phase After completion of the operation, status and other house-keeping information are made available to the IOP.

| Honeywell                     | SPEC. NO. | SHEET    | REV. |

|-------------------------------|-----------|----------|------|

| HONEYWELL INFORMATION SYSTEMS | 1 001     | 49777 17 | В    |

SECTION 4 DEVICE INTERFACE

#### 4.1 USER INTERFACES

No specific user action is required to load or initialize the WDC other than those required during subsystem installation for the identification of subsystem configuration. User actions required to load and unload devices are described in appropriate operating guidelines.

#### 4.2 EXTERNAL INTERFACES

## 4.2.1 Controller-IOP Interface

The WDC attaches to the IOP bus as a standard Hercules controller. See the Hercules EPS-1 (60144453) subsection 4.6 for more details or refer to section 5.3 of this EPS-1 for specific information.

#### 4.2.2 Wren Device Interface

The appropriate drive specification should be referenced for information more detailed than that presented in this subsection. The drive specification also represents the governing document in terms of drive functionality (see subsection 1.3.2).

The WDD requires two separate cables for attachment to the WDC. The C-cable and the D-cable provide a radial connection from the drive to the WDC. Figure 4-1 outlines the signals on each cable. Address and control functions are transferred on C-cable lines. The significance of the information on these lines is indicated by the description that follows.

| <br>       |                                   |      | GROUND PIN NO. |

|------------|-----------------------------------|------|----------------|

|            | HEAD SELECT 2 <sup>2</sup> >      | 6    | 1              |

|            | READ ENABLE>                      | 2    | 3              |

|            | HEAD SELECT 2 <sup>1</sup> >      | 4    | 5<br>7         |

|            |                                   |      | 9<br>11        |

|            | HEAD SELECT 2 <sup>0</sup> > <br> | 32   | 13<br>15       |

| WREN       | RETURN TO ZERO>                   | 34   | 17             |

| DEVICE     | < INDEX                           | 8    | 19             |

| CONTROLLER | < DRIVE READY                     | 26   | 21             |

| C-CABLE    | < BYTE CLOCK                      | 30   | 23             |

| CONNECTOR  | DRIVE SELECT 1>                   | 10   | 25             |

| 1          | DRIVE SELECT 2>                   | .12  | 2 <b>7</b>     |

| 1          | DRIVE SELECT 3>                   | 14   | 29             |

|            | <b> </b>                          |      | 31             |

| 1          | DIRECTION>                        | 18   | 33             |

| 1          | STEP>                             | 20   |                |

| 1          | OFFSET STROBE>                    | 22   |                |

| 1          | WRITE ENABLE>                     | 24   |                |

| 1          | <pre> &lt; WRITE FAULT </pre>     | 28   |                |

|            | RESERVED                          | 16   |                |

| 1          |                                   | WREN | COMMAND        |

| 1          |                                   | CONN | ECTOR#         |

|            | <b>l</b>                          |      |                |

EDGE CONNECTOR

\*All signals in the Command cable are single-ended.

a. Command C-Cable (34-pin connector).

Figure 4-1 Wren Device Controller Interface Cables (Sheet 1 of 2)

|                                 |         | PIN#                                                                                                  | TYPE*                                                           |

|---------------------------------|---------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| DEVICE<br>CONTROLLER<br>D-CABLE | <-INDEX | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | TYPE*  SE  SE  SE  SE  DIFF  DIFF  DIFF  DIFF  DIFF  DIFF  DIFF |

|                                 | GROUND  | 20<br>WREN                                                                                            |                                                                 |

|                                 |         | CONN                                                                                                  | ECTOR                                                           |

3M CONNECTOR

\*SE = Single-ended signal; DIFF = Differential signal.

(D-Cable = Data Cable)

Figure 4-1 Wren Device Controller Interface Cables (Sheet 2 of 2)

## 4.3 CONTROLLER OUTPUT LINES

## 4.3.1 Drive Select (1. 2 & 3)

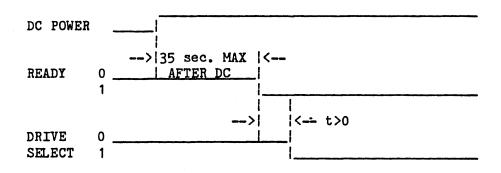

Since only two devices are interfaced to the WDC, Drive Select 1 & 2 are used and the remaining one line can be left unpowered. These input lines are used to gate all command lines to the WDD.

The Unit Select plug located on the base board assembly of the WDD must be set to 1 for drive 1 and 2 for drive two.

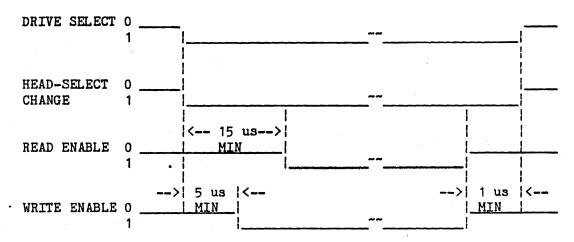

Figure 4-2 shows the drive selection timing.

| Honeywell                     | NO.      | SHEET | REV. |

|-------------------------------|----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS | 60149777 | 20    | В    |

Figure 4-2 Power Turn On and Drive Select

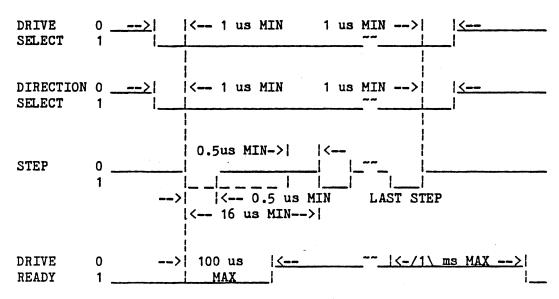

### 4.3.2 Direction

Direction determines the source of movement of the head-carriage: a logical 1 signifies head-carriage movement toward the higher-numbered cylinders; a logical 0 signifies head-carriage movement toward the low-numbered cylinders (see Figure 4-3).

/1\ - 10 ms for a single track seek (i.e., 1 Step pulse. dependent on Step rate input.

Figure 4-3 Track Access Timing

| Honovavoll                    | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 21    | B    |

| HONEYWELL INFORMATION SYSTEMS | 00113111  |       | -    |

## 4.3.3 Step

Step is used with Direction to cause head-carriage movement. Each pulse on the Step line causes the head-carriage to be moved one cylinder in the direction determined by the state of the Direction line.

The rate of head movement is determined by the rate of the in-coming Step pulses; however, the Step pulse rate may exceed the head movement rate. The Drive Ready false indication signifies that a seek is in progress (see Figure 4-3).

# 4.3.4 Head Select: $2^0$ , $2^1 \times 2^2$

These lines are used to select the media and head for data transfer.

| HEA          | D SELEC                     | CT  | - HEAD FUNCTION MEDI |             |                                    |  | MEDTA |

|--------------|-----------------------------|-----|----------------------|-------------|------------------------------------|--|-------|

| 22           | 21                          | 20  |                      | Concilon    | MEDIA                              |  |       |

| 0            | 0                           | . 0 | 0                    | Top Head    | 1st Disk nearest<br>  deck casting |  |       |

| 0            | 0                           | 1 ` | 1                    | Bottom Head | 2nd                                |  |       |

| 0            | 1                           | 0   | 2                    | Top Head    | 2nd                                |  |       |

| 0            | 1                           | 1   | 3*                   | Bottom Head | 3rd                                |  |       |

| 1 1 1        | 0                           | 0   | ;<br>1 7t#           | Top Head    | 3rd                                |  |       |

| <br> Remaini | Remaining Codes are Illegal |     |                      |             |                                    |  |       |

<sup>\*</sup>Invalid for two disk devices.

Drive head line is not affected by any head change (see Figure 4-4).

Figure 4-4 Head Select Timing

| Honeywell                     | SPEC. NO. | SHEET   | REV. |

|-------------------------------|-----------|---------|------|

| a roney wen                   | 60149777  | 22      | B    |

| HONEYWELL INFORMATION SYSTEMS | 00143111  | <b></b> |      |

## 4.3.5 Return To Zero

RTZ causes the actuator to return to Zero and resets the "Write Fault" lach. This seek is significantly longer than a seek to track 0 and should only be used for recalibration.

## 4.3.6 Read Enable

This signal enables the Read Data and Real Clock on the Read/ Servo clock lines.

## 4.3.7 Write Enable

This signal enables the write drive and initiates recording of the contents of the Write Data lines onto the media (see Figure 4-5 for timing).

Only one signal line may be inactivated at a time.

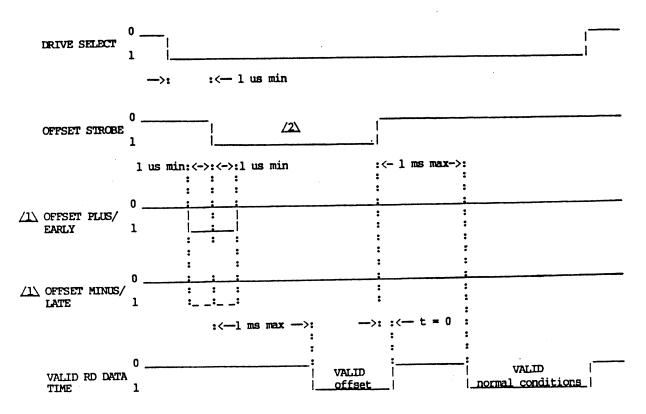

/2\ Offset strobe not sllowed during Seek, RTZ or write.

Figure 4-5 Offset Plus/Minus Timing

|                               | ISPEC. NO. | SHEET | REV.  |

|-------------------------------|------------|-------|-------|

|                               |            |       | 1     |

| Honeywell                     |            |       | 1 1   |

|                               | 60149777   | ) 23  | В     |

| HONEYWELL INFORMATION SYSTEMS | 1 11(1100  | -5    | 1 - 1 |

| HONETWEED IN CHARTION SISIEMS | j          | 1     | 1 1   |

### 4.3.8 Early Data Strobe Enable/Offset Plus

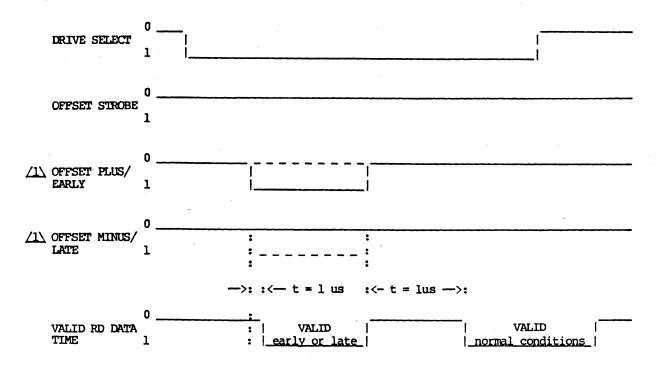

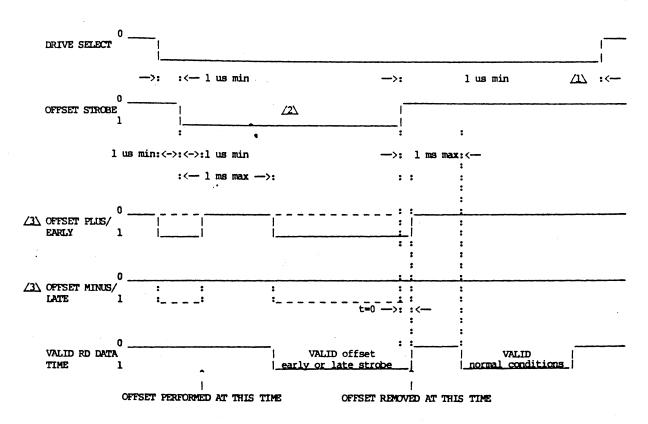

This line, when used in conjunction with the Offset Strobe Signal, can be used to obtain three combinations of Plus Offset, Early Data Strobe Enable or both during a Read operation (see Figures 4-5, 4-6 and 4-7).

## 4.3.9 Late Data Strobe Enable/Offset Minus

This line, when used in conjunction with the Offset Strobe Signal can be used to obtain three combinations of the Minus Offset, Late Data Strobe or both during a Read operation (see Figures 4-5, 4-6 and 4-7).

1 Only one signal line may be inactivated at a time.

Figure 4-6 Early/Late Strobe Enable Timing

△1\( \) Offset strobe must be deactivated 1 us prior to selection.

∠2\ Offset strobe not allowed during Seek, RTZ or Write.

(3) Only one signal line can be activated at a time.

Figure 4-7 Offset Plus/Minus, Early/Late Strobe Timing

# 4.3.10 Write Data "+" and "-"

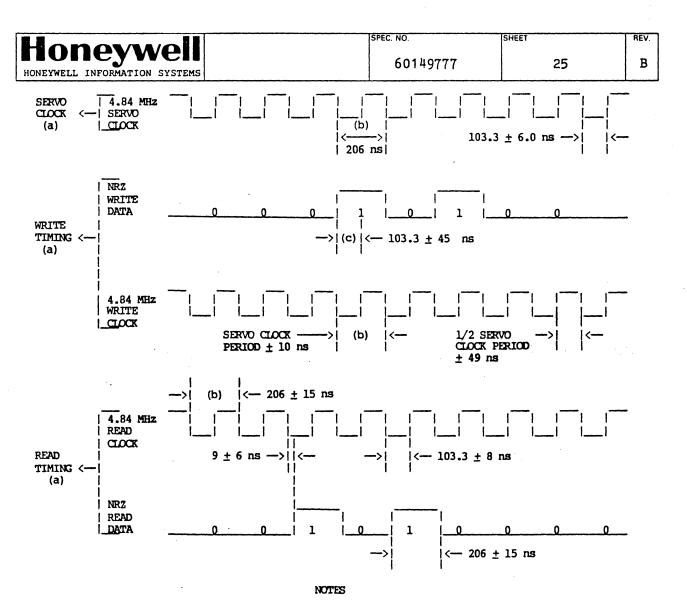

These lines carry the balanced differential data to be recorded on the media. The NRZ data is in phase synchronization with the Write Clock signal (see Figure 4-8).

# 4.3.11 Write Clock "+" and "-"

These lines carry the balanced differential Write Clock signal. The Write Clock is the Servo Clock retransmitted to the drive by the WDC during a write operation (see Figure 4-8).

- (a) All times in nanoseconds measured at drive I/O connector.

- (b) Similar period symmetry shall be  $\pm$  3 ns between any two adjacent cycles during reading or writing.

- (c) This time (103.3  $\pm$  45 ns) is measured from the activation (or deactivation) of NRZ write data line and rising edge of the write clock line.

All clocks are nominal. A combined spindle speed and clock circuit timing tolerance not exceeding 3% must be taken into account.

Servo clocks are valid when not reading. Other timing is applicable during reading or writing.

Figure 4-8 NRZ Data and Clock Timing

| Hopovyoll                     | SPEC. NO | O. SHEET | REV. |

|-------------------------------|----------|----------|------|

| Honeywell                     | 6        | 0149777  | 26 B |

| HONEYWELL INFORMATION SYSTEMS |          | 0145/11  |      |

#### 4.3.12 Offset Strobe

This line is used to indicate an actuator offset for the nominal On Cylinder position. The Offset function is intended to be used to aid in the recovery of marginal data that has been previously recorded on the disk media and should only be utilized after rereads without actuator offset have been attempted. This line is available on the 34-pin interface only.

#### 4.3.13 Reserved

This is not used by the Wren Disk Drive.

#### 4.4 CONTROLLER INPUT LINES

## 4.4.1 Drive Ready

When true, this line indicates that the disk is up-to-speed and the actuator is on cylinder and not executing a seek or an RTZ function. This line is generated with Drive Select and it also is available as Unit Ready on the D-cable where it is not gated with Drive Select.

## 4.4.2 Index

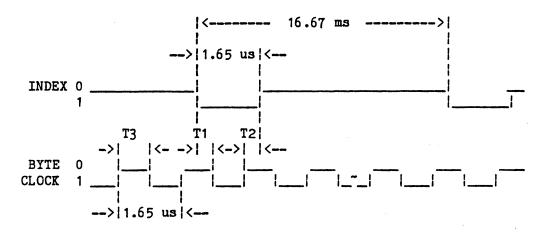

Index, which occurs once per revolution, indicates the physical beginning of a cylinder (see Figure 4-8).

This signal is contained in the C-cable gated with Drive Select; it is also available in the D-cable not gated with Drive Select. The relationship of Index and Byte Clock timing is shown in Figure 4-9.

where T1 = 0.2 microsecond to 0.41 microsecond

T2 = 0.41 microsecond to 0.53 microsecond

T3 = 0.83 microsecond

Figure 4-9 Index and Byte Clock Relationship

|                               | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 27    | В    |

| HONEYWELL INFORMATION SYSTEMS |           | _,    |      |

#### 4.4.3 Byte Clock

Byte Clock occurs once per eight Servo Colck periods. There are 10,080 byte clocks per disk revolution at a minimal rate of 605 KHz. Interrelationship of Index and Byte Clock are shown in Figure 4-9.

## 4.4.4 Write Fault

Write Fault conditions detected by the Wren disk drive activate the Write Fault signal. It remains active until it is deactivated by either the Fault Reset signal or by power sequencing of the drive.

The Write Fault condition occurs when:

- o Write current is absent

- o Write data is absent

- o The disk is not ready

- o Invalid head or internal multiple heads are selected

- o Read Enable is true

- o Offset Strobe is true.

#### 4.4.5 Unit Ready

This signal is the same as Drive Ready but without being gated by Drive Select.

## 4.4.6 Servo/Read Clock "+" and "-"

These balanced differential lines contain the device-generated Read Clocks if the Read Enable signal is true; or, the drive generated Servo Clocks, when the Read Enable is false. These lines are not gated with the Drive Select signal.

#### 4.4.7 Read Data "+" and "-"

These balanced differential lines transmit the recovered data from the media in the NRZ form from the FDD to the FDC. This data is in frequency and pulse synchronization with the Read Clock as specified in Figures 4-8 and 4-10.

#### 4.5 DATA FORMAT

#### 4.5.1 Format Definition

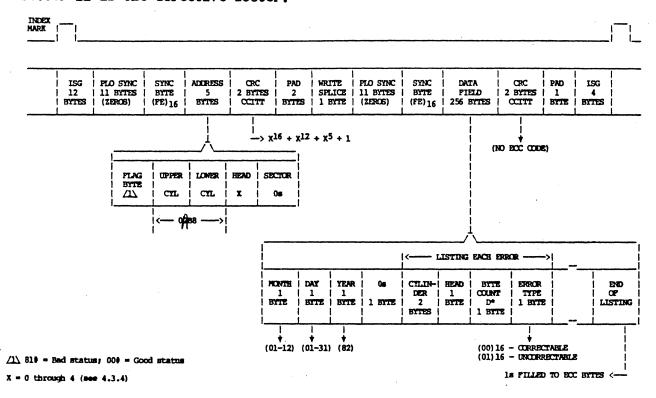

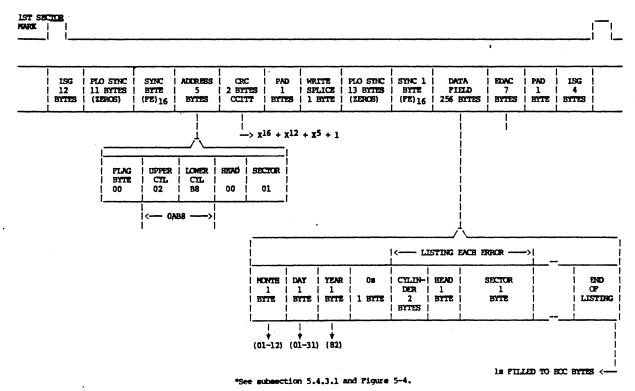

The record format on the disk is under control of the control- ler. The Index pulse and byte clocks are available for use by the controller to indicate the beginning of a track and to allow the controller to define the beginning of a sector. A suggested format for fixed-length data records is shown in Figure 4-11.

The format presented in Figure 4-11 consists of three functional areas: Intersector Gap, Address and Data. The Data area is used to record the system's data files. The Address area is used to locate and verify the track and sector location on the disk where the Data areas are to be recorded. This section refers to a Sector pulse which is generated internally to the controller from the Byte clock to ease the format description.

| WRITE SPLICE                | ·        |

|-----------------------------|----------|

| >   < 1                     | BIT MIN. |

| READ ENABLE                 |          |

| PLO SYNC                    |          |

|                             | <>       |

| READ CLOCKS VALID           | 1/////   |

| READ DATA VALID (INTERFACE) | 1/////   |

NOTE

Read Enable must be deactivated prior to the Write Splice. Read Enable may be reinitiated at least one bit after the Write Splice and with at least 11 bytes of PLO SYNC remaining in the sync field.

Figure 4-10 Read Timing

|                               | SPEC | C. NO.   | SHEET | REV. |

|-------------------------------|------|----------|-------|------|

| Honeywell                     | ·    | 60149777 | 20    | ъ.   |

| HONEYWELL INFORMATION SYSTEMS |      | וועדוטט  | 43    | ם    |

#### DATA PIELD LENGTH USING 32 SECTORS

DATA FIELD = TOTAL BYTES/TRACK = (SYNC FIELDS, TOLERANCE GAPS, AND ADDRESSES

DATA FIELD = 10080 = 315

DATA FIELD = 10080 32 = 31

DATA = 256 BYTES/SECTOR

EFFICIENCY = 256 x 32 = 811

\*Byte Sync pattern = FE

Figure 4-11 Sector Format

#### 4.5.2 Intersector Gap. ISG

The Intersector Gap is 16 bytes long for the WDD, and is oriented to begin before Index (Sector) pulse and end after Index (Sector) pulse (see Figure 4-11).

### 4.5.3 Address Area

The Address area is used to provide positive indication of the track and sector locations. The Address area is normally read by the controller and the address field bytes verified prior to a data area read or write. The Address area is normally only written by the controller during a format function, and thereafter only read to provide a positive indication of the sector location and establish the boundaries of the data area. The Address area consists of the following bytes:

- PLO Sync (11 bytes minimum) These 11 bytes of Zeros are required by the drive to allow the drive's read-data-phase- locked oscillator to become phase and frequency synchronized with the data bits recorded on the media.

- Byte Sync Pattern (1 byte) Standard format FE; it indi- cates to the controller the beginning of the address field information, and it establishes byte synchronization (ability to partition serial bit stream into meaningful groupings, such as bytes).

| Honovyoll                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 30    | В    |

| HONEYWELL INFORMATION SYSTEMS |           |       | 1    |

- 3. Address Field These bytes are as shown and interpreted by the controller. The format consists of five bytes, which allows one byte to define flag status bits or logical unit number, two bytes to define the cylinder address, one byte to define the head address, and one byte to define the sector address.

- 4. ADR CRC (Address Field Check Codes) Selection of an appropriate errordetection mechanism, such as a cyclic redundancy check (CRC) code, is made

by the hardware and applied to the address for file integrity purposes.

These codes are generated by the controller and written on the media when

the address is written. Data integrity is maintained by the controller

recalculating and verifying the address field check codes when the address

field is read.

- 5. <u>ADR Pad</u> (Address Field Pad) The Address Field Pad bytes must be written by the controller and are required by the drive to ensure proper recording and recovery of the last bits of the address field check codes.

## 4.5.4 Data Area

The data area is used to record the data fields. The contents of the data fields within the data area are specified by the CPU, DMC and memory. The remaining parets of the data area are specified and interpreted by the controller to recover the data fields and ensure their integrity. The data area consists of the following:

- 1. <u>Write Splice</u> (one byte) This byte area is required by the drive to allow time for the write drivers to turn on and reach a recording amplitude sufficient to ensure data recovery. This byte should be allowed for in the format.

- 2. <u>PLO Sync</u> (13 bytes) These 13 bytes of Zeros are required when reading to allow the drive's phase-locked oscillator to become phase and frequency synchronized with the data bits recorded on the media.

- 3. <u>Byte Sync Pattern</u> (one byte) Standard format FE. This byte indicates to the controller the beginning of the data field bytes and establishes byte synchronization for the data field.

- 4. Data Field The data field contains the 256 bytes of CPU defined data.

- 5. <u>Data EDAC</u> (Data-Field Check Codes) These codes are generated by the controller and written on the mdeia with the data field. The controller maintains data integrity by recalculating and verifying the data field check codes when the data field is read.

- 6. <u>Data Pad</u> (Data Field Pad) The Data Field Pad bytes must be written by the controller and are required by the drive to ensure proper recodring and recovery of the last bits of data field check codes.

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| and neg wen                   | 6014977   | 7 31  | В    |

| HONEYWELL INFORMATION SYSTEMS | 301.311   | '     |      |

SECTION 5 INSTRUCTIONS

### 5.1 GENERAL

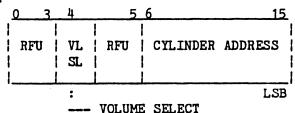

Two configuration words are required to define data access on a disk device. Configuration words A and B contain the image of the ID field of the sector on which a particular operation is initiated. Data access is defined via four hierarchical elements split between the two configuration words. In order to provide for the potential growth of WDD disk type devices, the following guidelines are established for the distribution of the four hierarchical elements in the two configuration words.

- 1. Bits 0 through 5 of configuration word A are reserved for use as a magazine address. Magazine selection applies to a device which has more than one physically identifiable media. For example, a cartridge disk device may have a fixed media and a removable media.

- 2. Bits 6 through 15 of configuration word A are reserved for use as a cylinder address.

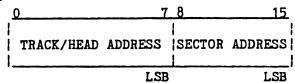

- 3. Bits 0 through 7 of configuration word B are reserved for use as a track/head address.

- 4. Bits 8 through 15 of configuration word B are reserved for use as a sector address.

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| I TOTICY WELL                 | 60149777  | 32    | В    |

| HONEYWELL INFORMATION SYSTEMS | 333111    | 3_    |      |

Configuration Word A:

Configuration Word B:

In multisector data transfer operations (Read or Write), the controller enables an automatic track and cylinder function. Track switching occurs whenever the last logical sector on the track has been completed and the range has not expired. Note that track switching is not associated with index mark but with equality with the last sector number. When the last track of the cylinder has been completed and track switching is attempted, the WDC initiates a seek to the next consecutive cylinder number, selects track number Zero, and initiates a search for sector number Zero.

## Additional considerations are:

- o Data transfer continues until the DMC range expires, an error is encountered, an unsuccessful search occurs, or the end of the last cylinder is detected (setting bit 5 of the status word).

- o Automatic track switching does not occur for any format operation or any unsuccessful search (detection of two index marks without a successful compare).

- o When track completion is detected without an error and the range has not expired, the configuration words are modified to reflect the next consecutive track and sector Zero. In addition, if cylinder completion is also detected, the configuration words are modified to reflect the next consecutive cylinder, and track and sector Zero. Note that this update occurs only if the EOT sector number has been reached and end of range has not been reached.

- o An attempt to automatically switch off the last track of the last cylinder results in status bit 5 being set (except in the case where the range has been decremented to Zero).

- o Both track and cylinder switching occurs within the fixed disks selected by the configuration words.

The functionality described above enables software to access records in sequential order without having to reload the sector ID argument for every operation on a particular track or cylinder.

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS | 60149777  | 33    | В    |

| HONETHELL INFORMATION SISTEMS |           | 1     | 1    |

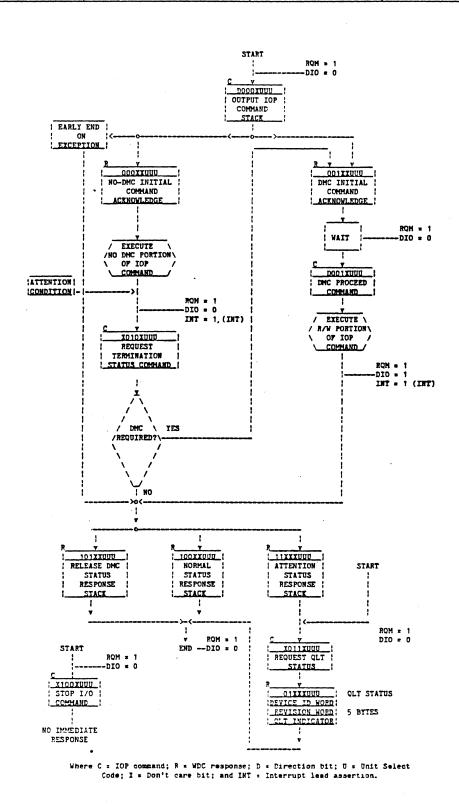

## 5.1.1 I/O Commands

All I/O commands are addressed by the CPU into the IOP I/O Mail- box (see Figure 3-2) which are shown in subsection 5.2 for each in- struction.

The IOP communicates with the WDG by means of a protocol de- scribed in subsection 5.3.

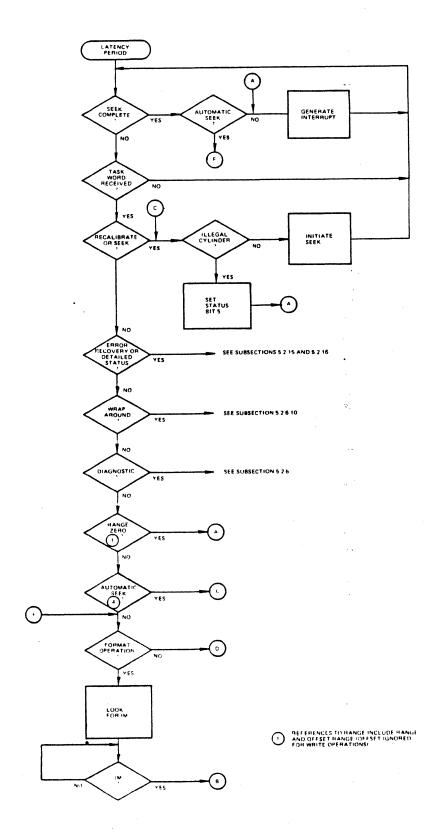

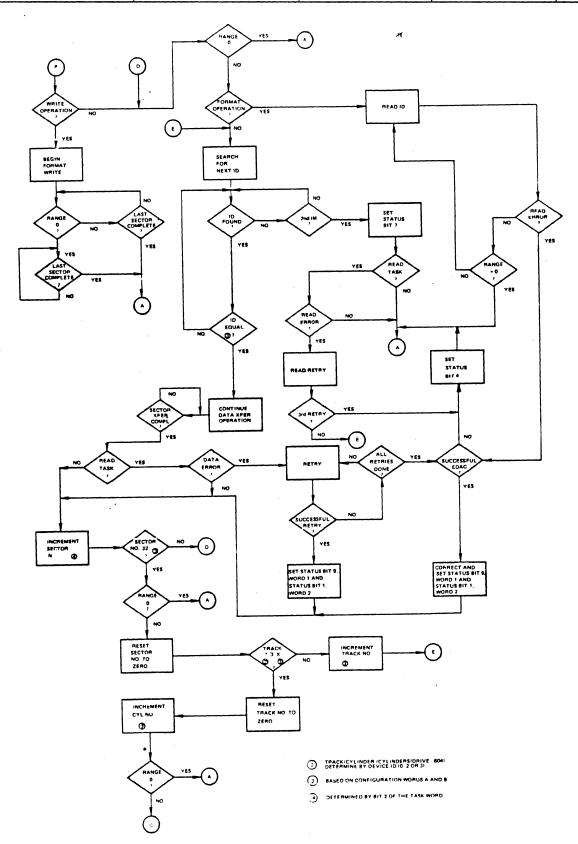

Figure 5-1 is a representation of a command flow chart.

Figure 5-1 Command Flow Chart (Sheet 1 of 2)

Figure 5-1 Command Flow Chart (Sheet 2 of 2)

| Honoravall                    | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| Honeywell                     | 60149777  | 36    | В    |

| HONEYWELL INFORMATION SYSTEMS | 00113111  | ]     |      |

# 5.2 INSTRUCTIONS

The Level 6 instructions supported by the IOP are listed in Table 5-1 with detailed instruction description following.

Table 5-1 Instructions

| TYPE      |          | FUNCTION ODE (HEX)* | :          | INSTRUCTION              |          | UBSECTIO<br>EFERENCE                    |

|-----------|----------|---------------------|------------|--------------------------|----------|-----------------------------------------|

| Output    | - :<br>: | 09                  | -:·<br>:   | IOLD                     | -:-<br>: | 5.2.1                                   |

| •         | :        |                     | :          | Address (09)             | :        | • • • • • • • • • • • • • • • • • • • • |

|           | :        |                     | :          | Range (OD)               | :        |                                         |

|           | :        | 11                  | :          | Configuration Word A     | :        | 5.2.2                                   |

|           | :        | 13                  | :          | Configuration Word B     | :        | 5.2.3                                   |

|           | :        | 15                  | :          | Configuration Word C     |          | 5.2.4                                   |

|           | :        | 03                  | :          | Interrupt Control        | :        | 5.2.5                                   |

|           | :        | 07                  | :          | Task Word                | :        | 5.2.6                                   |

|           | :        | 01                  | :          | Control Word             | :        | 5.2.7                                   |

| Input     | :        | 08                  | - : ·<br>: | Memory Byte Address      | -;-<br>: | 5.2.8                                   |

|           | :        | OA                  | :          | Memory Module Address    | :        | 5.2 9                                   |

|           | :        | OC                  | :          | Range                    | :        | 5.2.10                                  |

|           | :        | 10                  | :          | Configuration Word A     | :        | 5.2.11                                  |

|           | :        | 12                  | :          | Configuration Word B     | :        | 5.2.11                                  |

|           | :        | 14                  | :          | Configuration Word C     | :        | 5.2.11                                  |

|           | :        | 02                  | :          | Interrupt Control        | :        | 5.2.12                                  |

|           | :        | 26                  | :          | Identification Code      | :        | 5.2.13                                  |

|           | :        | 06                  | :          | Task Word                | :        | 5.2.14                                  |

|           | :        | 18                  | :          | Status Word 1            | :        | 5.2.15                                  |

|           | :        | 1 A                 |            | Status Word 2            | :        | 5.2.16                                  |

|           | :        | OA                  |            | QLTIs                    | :        | 5.2.17                                  |

|           | :        | 04                  |            | Firmware Revision (LSB)0 | :        | 5.2.18                                  |

|           | :        | 20                  | :          | Retry Count              | :        | 5.2.20                                  |

| Diagnosti | c: A     | ny Even Cod         | e:         | Read IOP Registers       | :        | 5.2.21                                  |

|           | : A      | ny Odd Code         | :          | Write IOP Registers      | :        | 5.2.21                                  |

|           | : 0      | 0 to 27 Hex         | :          |                          | :        |                                         |

|           | : 0      | nly                 | :          | •                        | :        |                                         |

<sup>\*</sup>All other function codes are RFU.

# 5.2.1 IOLD

The I/O Load (IOLD) instruction is transformed by the CPU into the Output Address and Output Range instructions on the CPU bus. Each IOLD instruction results in an Output Address instruction followed by an Output Range instruction.

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS | 60149777  | 37    | В    |

# 5.2.1.1 OUTPUT ADDRESS

This instruction loads a 16-bit address into the address register of the I/O Mailbox for the referenced channel. The address refers to the starting (byte) location in main memory where the DMC commences input or output data transfers. The most significant four bits of the Address are passed on to the IOP via a hardware register and the data bus contains the 16 least significant bits. Data transfers to or from memory are normally on a word basis, but byte mode transfers can occur associated with the first and/or last memory cycle of a particular data transfer if the main memory buffer (identified by this instruction) begins or ends on an odd byte boundary.

Bit 9 of the address bus (direction bit of the channel number) determines the direction of any subsequent data transfer operation. A logical One specifies an output operation (writing on media) while a logical Zero specifies an input operation (reading from media).

### 5.2.1.2 OUTPUT RANGE