| HONEYWELL BULL<br>BILLERICA                                                 | SPECIFICATION NUMBER   DISTRIBUTION   SHEETS   REV.  <br>60149782   CODE C40C   1/90   C |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| SMALL COMPUTER<br>PRODUCT ENGINEERING<br>PREP. BY DATE<br>K.A.Kowal 84.2.1. | TITLE:<br>ENGINEERING PRODUCT SPECIFICATION<br>HIGH SPEED DISK CONTROLLER                |

| APPR. BY DATE<br>85.03.05.                                                  | HSDC                                                                                     |

| REVISION    | AUTHORITY                           | DATE                                | SIGNATURE                     | SHEETS AFFECTED                                 |

|-------------|-------------------------------------|-------------------------------------|-------------------------------|-------------------------------------------------|

| 3           | Approval                            | 84.10.31.                           | K.Kowal                       | l through 79                                    |

| A<br>B<br>C | BLCDF7166<br>BLCDG7066<br>BLCDH7461 | 85.02.18.<br>86.02.06.<br>87.09.25. | K.Kowal<br>K.Kowal<br>K.Kowal | l through 81F<br>1 through 88F<br>1 through 90F |

| 1           | EMD -III                            | <b>`</b>                            | K.KUWAI                       | i thiough sor                                   |

This document and information contained herein are confidential to and the property of Honeywell Bull Inc. and are made available only to Honeywell Bull employees or vendors for the sole purpose of conducting Honeywell Bull's business or providing goods and services to Honeywell Bull. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager or by an authorized Honeywell Bull official in writing; and shall not be disclosed or distributed (a) to persons who are not Honeywell Bull or vendor employees, or (b) to Honeywell Bull or vendor employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the Honeywell Bull or vendor employee in possession of this document no longer has need for the document for the authorized Honeywell Bull purpose, this document and any copies thereof shall be returned to the employee's manager or to Honeywell Bull. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsible Honeywell Bull Vice President.

HONEYWELL BULL CONFIDENTIAL & PROPRIETARY

| HONEYWELL BULL CONFIDENTIAL |          | PAGE   REVISION | ,<br>! |

|-----------------------------|----------|-----------------|--------|

| AND PROPRIETARY             | 60149782 | 2 C             | 1      |

| *                           |          |                 | ,      |

.

Blank

| ,     |     | BULL CONFIDENTIAL |   | SPECIFICATION NUMBER |  |   |   | i |

|-------|-----|-------------------|---|----------------------|--|---|---|---|

| Ì     | AND | PROPRIETARY       | 1 | 60149782             |  | 3 | C | Ì |

| · ' _ |     |                   |   |                      |  |   |   | , |

C

2

C

Table of Contents

| Se | ction             |                         |                                                                                              |         |        |              |          |        |   | Page         |

|----|-------------------|-------------------------|----------------------------------------------------------------------------------------------|---------|--------|--------------|----------|--------|---|--------------|

| 1  | Intr              | oduction                | L                                                                                            | -       | -      | -            | -        | -      | - | - 9          |

|    | 1.1<br>1.2<br>1.3 | Objecti                 |                                                                                              |         |        |              |          |        | · |              |

|    |                   | 1.3.1<br>1.3.2          | Related Documents<br>Reference Documents                                                     | _       | -      | -            | -        | -      | - | - 10         |

|    | 1.4               | Standar                 | ds                                                                                           |         |        |              |          |        |   |              |

|    |                   | 1.4.1<br>1.4.2<br>1.4.3 | General Design, Honeywell Bu<br>Product Maintainability, Hor<br>Manufacturing Testability Gu | neywell | Bull S | Standaı<br>- | rds<br>- | -      | - | - 11         |

|    | 1.5               | Definit                 | ions                                                                                         |         |        |              |          |        |   |              |

| 2  | Arch              | itecture                |                                                                                              | -       | -      | -            | -        | -      | - | - 13         |

|    | 2.1<br>2.2        |                         | ew<br>Components                                                                             |         |        |              |          |        |   |              |

|    |                   | 2.2.2<br>2.2.3          | High Speed Disk Controller<br>Fixed Storage Drive<br>Eight Inch Module Drive                 | -       | -      | -            | -        | -      | - | - 15         |

|    |                   | 2.2.4<br>2.2.5          | Minidiskette Adapter, QDM<br>Streamer Adapter                                                | -       | -      | -            | -        | -      | - | - 16         |

| 3  | Func              | tional F                | Requirements                                                                                 | -       | -      | -            | -        | -      | - | - 17         |

|    | 3.1<br>3.2        |                         | ration a Simultaneity<br>© Control                                                           |         |        |              |          |        |   |              |

| ×  |                   | 3.2.1<br>3.2.2<br>3.2.3 | Command Transfer<br>Data Transfer<br>Interrupts                                              | -       | -      | -<br>-       | -        | -<br>- | - | - 18<br>- 20 |

|    | 3.3               | Overvie                 | w of HSDC Access                                                                             |         |        |              |          |        |   |              |

|    |                   | 3.3.1<br>3.3.2<br>3.3.3 | Memory Addressability<br>Scatter/Gather<br>Dual Ported Drives                                | -       | -      | -            | -        |        | - | - 21         |

|     |      |        |                                                                                              | NFIDENTIAL                                                                                                | SPECIFICATION NUMBER<br>60149782                                                                   | PAGE                               | REV           | ISION |              |

|-----|------|--------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------|---------------|-------|--------------|

|     | ,    | A<br>  | AND PROPRIE                                                                                  | rary                                                                                                      | 60149782                                                                                           | 4                                  | <br>          | C     | ,            |

|     | •    |        |                                                                                              |                                                                                                           |                                                                                                    |                                    |               |       | _            |

| ect | tion |        |                                                                                              |                                                                                                           |                                                                                                    | ,                                  |               |       | Page         |

| , 1 | Inte | rfaces |                                                                                              |                                                                                                           |                                                                                                    | -                                  | -             | -     | - 23         |

|     |      |        | Megabus I<br>Level Inte                                                                      | nterface<br>rface (DLI)                                                                                   |                                                                                                    |                                    |               |       |              |

|     |      | 4.2.1  | Address a                                                                                    | nd Control Fu                                                                                             | unctions ("A" cable)                                                                               |                                    |               |       |              |

|     |      |        | 4.2.1.1<br>4.2.1.2<br>4.2.1.3                                                                | Head & High                                                                                               | er Address (Tag 1)<br>n Cylinder Select (Tag 2<br>lect (Tag 3)                                     | ) -                                | -             | -     | - 25         |

|     |      |        |                                                                                              | $\begin{array}{r} 4.2.1.3.1 \\ 4.2.1.3.2 \\ 4.2.1.3.3 \\ 4.2.1.3.4 \\ 4.2.1.3.5 \\ 4.2.1.3.6 \end{array}$ | Servo Offset Plus (Bus<br>Servo Offset Minus (Bu<br>Fault Clear (Bus Out B                         | 1)<br>Out Bit<br>s Out Bi<br>it 4) | t 3)          |       |              |

|     |      |        |                                                                                              | 4.2.1.3.7<br>4.2.1.3.8<br>4.2.1.3.9<br>4.2.1.3.10                                                         | Return To Zero (Bus Ou<br>Data Strobe Early (Bus<br>Data Strobe Late (Bus<br>Release, Dual Channel | t Bit 6)<br>Out Bit<br>Out Bit     | -<br>7)<br>8) |       | - 26<br>)    |

|     |      |        |                                                                                              | 4.2.2.3.11                                                                                                | Unit Select                                                                                        |                                    |               |       |              |

|     |      |        | 4.2.1.4<br>4.2.1.5<br>4.2.1.6                                                                | Current Sec                                                                                               | Control Lines<br>ctor Status (Tag 4) -<br>ended Status (Tag 5)                                     | -                                  | -             | -     | - 27         |

|     |      |        |                                                                                              |                                                                                                           | Fault Status<br>Operating Status –<br>Diagnostic Status                                            | · _                                | -             | -     | - 28         |

|     |      |        |                                                                                              | 4.2.1.6.4                                                                                                 | Execute Status -                                                                                   | -                                  | -             | -     | - 29         |

|     |      |        | 4.2.1.7<br>4.2.1.8                                                                           | Device Type<br>SMD Status                                                                                 | e Status (Tag 6)<br>Lines                                                                          |                                    |               |       |              |

|     |      |        |                                                                                              | 4.2.1.8.1<br>4.2.1.8.2<br>4.2.1.8.3<br>4.2.1.8.4<br>4.2.1.8.5                                             | Seek Error (Bus In Bit<br>Fault (Bus In Bit 3)                                                     | t 1)<br>2) -                       | -             | -     | - 30<br>- 31 |

|     |      |        |                                                                                              | 4.2.1.3.6                                                                                                 | Address Mark Found (Bu<br>Index Mark (Bus In Bit                                                   | s In Bit<br>6) -                   | 5)<br>-       | -     | - 32         |

|     |      |        | $\begin{array}{c} 4.2.1.9\\ 4.2.1.10\\ 4.2.1.11\\ 4.2.1.12\\ 4.2.1.12\\ 4.2.1.13\end{array}$ | Open Cable<br>Power Seque                                                                                 | t Bits, $2^0$ , $2^1$ , $2^2$ & $2^3$                                                              |                                    |               |       |              |

|     |      | 4.2.2  | Data and                                                                                     | Clock Lines                                                                                               | ("B" cable)                                                                                        | -                                  | -             | -     | - 33         |

|     |      |        | 4.2.2.1                                                                                      | Unit Select                                                                                               | had                                                                                                |                                    |               |       |              |

|     | <br> <br> - |                    | LL BULL CON<br>ND PROPRIET | NFIDENTIAL  <br>MARY      | SPECIFICATIC<br>601497 |   | 1BER | PAGE<br>  5 | REV:<br> <br> | LSION<br>C | <br> <br> |

|-----|-------------|--------------------|----------------------------|---------------------------|------------------------|---|------|-------------|---------------|------------|-----------|

|     |             |                    |                            |                           |                        |   |      |             |               |            |           |

| Sec | ction       | •                  |                            |                           |                        |   |      |             |               |            | Pag       |

|     |             |                    | 4.2.2.2                    | Seek End                  | -                      | - | -    | -           | -             | -          | - 3       |

|     |             |                    | 4.2.2.3                    | Write Data                |                        |   |      |             |               |            |           |

|     |             |                    | 4.2.2.4                    | Servo Clock               |                        |   |      |             |               |            |           |

|     |             |                    | 4.2.2.5                    | Read Data                 |                        |   |      |             |               |            |           |

|     |             |                    | 4.2.2.6                    | Read Clock                |                        |   |      |             |               |            |           |

|     |             |                    | 4.2.2.7                    | Write Clock               |                        |   |      |             |               |            |           |

|     |             | 4.2.3              | Data Forma                 | at                        | -                      | - | -    | -           | -             | -          | - 3       |

|     | 4.3         | EMD Opt            | ions                       |                           |                        |   |      |             |               |            |           |

|     | Inst        | ructions           |                            |                           | -                      | - | _    | -           | -             | -          | - 3       |

|     |             |                    |                            |                           |                        |   |      |             |               |            |           |

|     |             | General<br>Instruc | tions                      |                           | -                      | - | -    | -           | -             | -          | - 3       |

|     |             | 5.2.1              | IOLD                       |                           |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.1.1                    | Output Addres             |                        | - | -    | -           | -             | -          | - 3       |

|     |             |                    | 5.2.1.2                    | Output Range              | -                      | - | -    | -           | -             | -          | - 4       |

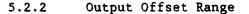

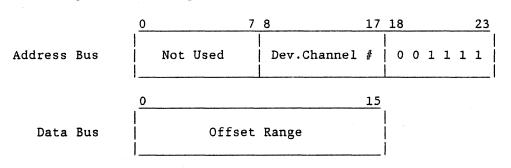

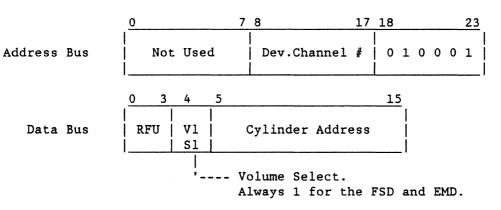

|     |             | 5.2.2              | Output Of                  | fset Range                |                        |   |      |             |               |            |           |

|     |             | 5.2.3              |                            | nfiguration Wor           | rd A                   |   |      |             |               |            |           |

|     |             | 5.2.4              | Output Cor                 | figuration Wo             | cd B                   |   |      |             |               |            |           |

|     |             | 5.2.5              |                            | figuration Wo             |                        | - | -    | -           | -             | -          | -         |

|     |             | 5.2.6              |                            | errupt Contro             | L                      |   |      |             |               |            |           |

|     |             | 5.2.7              | Output Tas                 | sk Word                   |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.1                    | Recalibrate               | -                      | - | -    | -           | -             | -          |           |

|     |             |                    | 5.2.7.2                    | Seek                      |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.3                    | Format Read               | -                      | - | -    | -           | -             | -          |           |

|     |             |                    | 5.2.7.4                    | Format Read               | LD.                    |   |      |             |               |            |           |

|     |             |                    | 5.2.7.5                    | Format Write              | -                      | - | -    | -           | -             | -          | -         |

|     |             |                    | 5.2.7.6                    | Read Data                 |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.7                    | Write Data                | -                      | - | -    | -           | -             | -          |           |

|     |             |                    | 5.2.7.8                    | Diagnostic W              |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.9                    | Diagnostic Re             |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.10                   | Diagnostic Fo             |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.11                   | Diagnostic Fo             |                        |   |      |             |               |            |           |

|     |             |                    | 5.2.7.12                   | Wraparound Re             | ead/Write              | - | -    | -           | -             | -          |           |

|     |             |                    | 5.2.7.13<br>5.2.7.14       | Read SPM<br>Diagnostic De | stail Status           |   |      |             |               |            |           |

|     |             | 5 0 0              |                            | -                         |                        |   |      |             |               |            |           |

|     |             | 5.2.8              | Output Cor                 | ntrol Word                | -                      | - | -    | -           | -             | -          | - 4       |

|     |             |                    | 5.2.8.1<br>5.2.8.2         | Initialize<br>Stop I/O    | -                      | - | -    | -           | -             | -          | - :       |

|     |             | 5.2.9              | Input Memo                 | ory Byte Addres           | 3 S                    |   |      |             |               |            |           |

|     |             | 5.2.10             |                            | ory Module Add            |                        | - | -    | -           | -             | _          | - !       |

|     |             | 5.2.11             | -                          |                           |                        |   |      |             |               |            | -         |

|     |             | J•2•11             | Inpac Kan                  | se                        |                        |   |      |             |               |            |           |

C

۶

C

HONEYWELL BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION | AND PROPRIETARY 60149782 6 C Section Page 5.2.13 Input Configuration Words A, B or C -- 53 5.2.14 Input Interrupt Control - -- 54 5.2.15 Input Identification Code 5.2.16 Input Task Word - 56 5.2.17 Input Status Word 1 5.2.17.1 Device Ready (Bit 0) -- 57 -5.2.17.2 Attention (Bit 1) --- 58 5.2.17.3 Controller Parrity Error 5.2.17.4 Device Fault (Bit 3) 5.2.17.5 Read Error (Bit 4) 5.2.17.6 Program Error (Bit 5) 5.2.17.7 QLT Fault (Bit 6) - 59 5.2.17.8 Unsuccessful Search/Format Error (Bit 7) 5.2.17.9 Error Log Overflow (Bit 8) 5.2.17.10 Successful Recovery (Bit 9) 5.2.17.11 RFU (Bit 10) 5.2.17.12 RFU (Bit 11) - 60 -5.2.17.13 Corrected Memory Error (Bit 12) 5.2.17.14 Nonexistent Resource (Bit 13) 5.2.17.15 Bus Parity Error (Bit 14) 5.2.17.16 Uncorrectable Memory Error (Bit 15) 5.2.18 Input Status Word 2 - 61 5.2.18.1 Corrected Read Error (Bit 0) - 62 5.2.18.2 Successful Retry (Bit 1)

5.2.18.3 RFU - MBZ (Bit 2 through 5)

5.2.18.4 Error Log Overflow - Fixed Medium (Bit 6) 5.2.18.5 RFU - MBZ (Bit 7 through 12) 5.2.18.6 Hardware Fault (Bit 13) 5.2.18.7 Seek Error (Bit 14) 5.2.18.8 Write Protected (Bit 15) -- 63 5.2.19 Input Quick Logic Test Indicators (QLTI's) 5.2.20 Input Firmware Revision 5.2.21 Input Retry Counter - 64 5.2.22 Read/Write Registers - 65 5.3 Defect Management - 67 5.3.1 EDAC Functionality 5.3.2 Read Error Retry Media Defect Handling 5.3.3 - 68 5.3.3.1 Vendor Error Log 5.3.3.2New Error Log-5.3.3.3Error Log Management - 69 -- 70 5.3.3.3.1 Vendor Error Log Management New Error Log Management -5.3.3.3.2 - 71 --5.3.3.3.3 - 72 New Error Management

|    | <br> <br> -       |                | LL BULL CON        | NFIDENTIAL<br>FARY        |                                           | 10N NUM<br>9782 | IBER | PAGE<br>  7 | REV:<br> | C | <br> <br>, |

|----|-------------------|----------------|--------------------|---------------------------|-------------------------------------------|-----------------|------|-------------|----------|---|------------|

| Se | ction             |                |                    |                           |                                           |                 |      |             |          |   | Pa         |

|    |                   |                | 5.3.3.4            | New Error                 | Log Format                                | -               | -    | -           | -        | - | -          |

| 6  | Phys              | ical Str       | ucture             |                           | -                                         | -               | -    | -           | -        | - | -          |

|    | 6.1               | General        |                    |                           |                                           |                 |      |             |          |   |            |

|    |                   | 6.1.1          | Physical S         | Specification             | n                                         |                 |      |             |          |   |            |

|    |                   |                | 6.1.1.3            | Environmen<br>Electrical  |                                           | -<br>FCD        | -    | -           | -        | - | -          |

|    |                   |                | 0.1.1.4            | 6.1.1.4.1                 | Mechanical,<br>Environment                | FSD             | )'s  |             |          |   |            |

|    |                   |                | 6.1.1.5            | Physical S                | pecification,                             | EMD's           | -    | -           | -        | - | -          |

|    |                   |                |                    |                           | Mechanical,<br>Mechanical,<br>Environment | EMD II          | I -  | -           | -        | - | -          |

|    |                   | 6.1.2          | Electrical         | L                         |                                           | -               | -    | -           | -        | - | -          |

| 7  | Perf              | ormance        |                    |                           | -                                         | -               | -    | -           | -        | - | -          |

|    | 7.1<br>7.2        |                | nance Charac       | cteristics                |                                           |                 |      |             |          |   |            |

|    |                   | 7.2.1<br>7.2.2 |                    |                           | istics of HSD<br>istics of FSD            |                 | -    | - *         | -        | - | -          |

| 8  | Avai              | lability       | ,                  |                           | -                                         | -               | -    | -           | -        | - | -          |

|    | 8.1<br>8.2<br>8.3 | Securit        |                    |                           |                                           |                 |      |             |          |   |            |

|    |                   | 8.3.1          | Maintainal         | bility Requi              | rements                                   |                 |      |             |          |   |            |

|    |                   |                | 8.3.1.1<br>8.3.1.2 | Mean Time I<br>(MTBPM)    | Fo Repair (MT<br>Between Preve            | ntive M         |      | nance       | -        | - | -          |

|    |                   |                | 8.3.1.3            | Diagnostic<br>Effectivne: | Facility Loc<br>ss (DFLE)                 | alizati         | .on  |             |          |   |            |

|    |                   |                |                    |                           |                                           |                 |      |             |          |   |            |

|    |                   | 8.3.2          | Maintenand         | ce Strategy               |                                           |                 |      |             |          |   |            |

$\mathbf{C}$

ĺ

| HONEYWELL BULL (<br>AND PROPR | <br>IFICATION NUMBER | <br>REVISION  <br>C |

|-------------------------------|----------------------|---------------------|

|                               | <br>                 | <br>                |

## Section

r

8.4 Reliability 8.4.1 Product Life - 87 8.4.2 Mean Time Between Failures (MTBF) 8.4.3 Mean Time Between Calls (MTBC) 8.4.4 Transient Error Rate - 88 -8.4.5 Recoverable Error Rate 8.4.6 Unrecoverable Error Rate 8.4.7 Recoverable Seek Error Rate

Page

# List of Illustrations

| Figure     |                                                           |           |            |           |    |   |   | Page |

|------------|-----------------------------------------------------------|-----------|------------|-----------|----|---|---|------|

| 2-1        | High Speed Disk Controller Subsystem                      | -         | -          | -         | -  | - | - | - 14 |

| 3-1<br>3-2 | Channel Numbers<br>Address and Data Bus Configuration for | -<br>Read | -<br>and W | -<br>rite | -  | - | - | - 18 |

|            | Memory Access.                                            | -         | -          | -         | -  | - | - | - 19 |

| 3-3        | Address and Data Bus Configuration for                    | Inter     | rupt       | Sequence  | 25 | - | - | - 20 |

| 4-1        | "A" & "B" Interface Cables                                | -         | -          | -         | -  | - | - | - 24 |

| 4-2        | Tag and Control Lines                                     | -         | -          | -         | -  | - | - | - 30 |

| 4-3        | FSD Fixed Sector Format                                   | -         | -          | -         | -  | - | - | - 34 |

| 5-1        | HSDC Device Specific Registers and Addr                   | ressin    | g          | -         | -  | - | - | - 65 |

| 5-2        | FSD Home Address Format                                   | -         | -          | -         | -  | - | - | - 69 |

| 8-1        | QLT Indicator Register Codes                              | -         | -          | -         | -  | - | - | - 86 |

## List of Tables

| Table      |                                                               |   |   |   | -      |   |   | Page         |          |

|------------|---------------------------------------------------------------|---|---|---|--------|---|---|--------------|----------|

| 5-1<br>5-2 | Instructions<br>SMD-E Tag 4, Tag 5 and Tag 6 Functions        | - | - | - | -      | - | - | - 39<br>- 49 |          |

| 7-1<br>7-2 | FSD Device Characteristics<br>FSD Performance Characteristics | - | - | - | -<br>- | - | - | - 80<br>- 81 | <b>N</b> |

| , - |                   |             |   |                 |        | <br> |          | • • |

|-----|-------------------|-------------|---|-----------------|--------|------|----------|-----|

| 1   | HONEYWELL BULL CO | ONFIDENTIAL | 1 | SPECIFICATION N | NUMBER | PAGE | REVISION |     |

| Í   | AND PROPRIE       | ETARY       | 1 | 60149782        |        | 9    | C        | 1   |

| ' _ |                   |             |   |                 |        | <br> |          | . ' |

#### 1 INTRODUCTION

## 1.1 Scope

This Engineering Product Specification (EPS) defines the High Speed Disk Controller (HSDC), which is a DPS-6 High Priority Megabus Interface (16 bit data bus and 24 bit address bus) Printed Circuit Assembly (PWA) with logic providing control over the Storage Module Drive (9.67 MHz. SMD-0 and 14.52 MHz. SMD-E ) interface and connected either up to four Fixed Storage Drives (FSD's) or up to four Eight Inch Module Drives (EMD's). In addition the HSDC can connect to other devices (minidiskette or streamer tape) through unique adapters mountable on the HSDC.

The HSDC consists of one Printed Circuit Assembly (PWA) which can reside in any of the Megabus I/O positions as defined by the 1975 EPS# 60126298 and is also intended to be used on MRX systems on selectable basis.

## 1.2 Objective

To provide a subassembly enabling communication between a DPS-6 Megabus and the HSDC with associated peripherals. The subsystem consists of five parts:

- High Speed Disk Controller motherboard assembly

- Disk Drive(s) with interface cables

- Minidiskette and/or Streamer Tape adapters

- Interface cables for the above

- AC (FSD and EMD with power supply) and DC (Minidiskette and Streamer) power cables to the system Power Distribution Unit and DC power supply

Only the HSDC is described in this EPS with references to other documents describing the remaining components.

#### 1.3 Documentation

1.3.1 Related documents

60126298, EPS-1, Level 6 Bus (Megabus) 60149832, EPS-1, MRX Megabus

60149778, PFS, High Speed Disk Controller 60166413, EPS, High Performance Disk Controller - Enhanced (HPDC E)

| , |           |                   |                      |      |          |

|---|-----------|-------------------|----------------------|------|----------|

| I | HONEYWELL | BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |

| i | AND       | PROPRIETARY       | 60149782             | 10   | С        |

| ; |           |                   |                      |      |          |

60149612, EPS-1, L6 Quarter Daughter Board Subsystem Attachment

60149781, EPS, 1/4-Inch Larkette Streamer Adapter

60149988, EPS, Small Computer System Interface (SCSI) Adapters (WangTek)

64717900, MPI Rev.C, Product Specification for the 9715 Fixed Storage Drive, 160 MB with the SMD-0 Interface.

۵

64400400, MPI Rev.A, Product Specification for the 9716 Fixed Storage Drive, 515 MB with SMD-E Interface.

64401200, MPI Rev.5, Product Specification for the 9720 Eight Inch Module Drive, 368 MB with SMD-E Interface.

64712402, MPI Rev.A, SMD-E Interface Specification For 15 MHz & 24 MHz Devices

#### 1.3.2 Reference documents

Q4.1, PWA/PWB Testability Design Rules

| MG1,  | Component Availability              |

|-------|-------------------------------------|

| MTG2, | PWA Test Documentation Requirements |

PWA Test Monitor/Test Box Design MTG4. MTG5. PWA Quality Logic Test Creation

MTG6. PWA Test and Verification Program Creation

PWA IC Socket Utilization MTG7,

- Design for Producibility, Installability, Maintainability and MTG8.

- Replaceability

MPDG1. PWA/PWB Producibility Guidelines

58035052, Worldwide Maintainance Requirements

#### 1.4 Standards

1.4.1 General Design, Honeywell Bull Standards

B01.08, Environment, Operating

- B01.09, Equipment Safety

- Environment, Transportation, Storage & Installation B01.10.

- B01.48, Primary Power-Utility Supplied

- B03.07. Reliability - Standard Failure Rate Data Base

- B03.08, Reliability Failure Rate & MTBF Predictions

B04.06, System Grounding

#### 1.4.2 Product Maintainability, Honeywell Bull Standards

Logic Nomenclature B07.11, Location Reference Designation B07.12, Identification Nomenclature for IC's, Printed Cards and Card Cages B07.13,

| i |     | BULL CONFIDENTIAL |   | SPECIFICATION NUMBER |   | PAGE |     | , |

|---|-----|-------------------|---|----------------------|---|------|-----|---|

| İ | AND | PROPRIETARY       | İ | 60149782             | İ | 11   | i c | İ |

| , |     |                   |   |                      |   |      |     | , |

B07.38, Logic Symbology B07.39, Logic Block Diagrams G02.01, FE Tools and Test Equipment Catalog G02.05, FE Product Tools & Test Equipment Field Product Maintenance Documentation G07.01, G07.02, Product Manual Content Guide G07.03, Product Style Guide for Manuals . G07.08, Major and Intermediate Block Diagrams G07.09, Repair Documentation, Draft

# 1.4.3 Manufacturing Testability Guidelines

| D.002.01, | PWA/PWB Testability Design Rules                       |

|-----------|--------------------------------------------------------|

| MTG1,     | PWA Test Equipment Connection Requirements             |

| MTG3,     | PWA Microdiagnostic Creation                           |

| 60129949, | Application Rules for Minicomputer & Terminal Products |

## 1.5 Definitions

| CRC<br>CPU  | Cyclic Redundancy Check<br>Central Processor Unit           |

|-------------|-------------------------------------------------------------|

| DMA         | Direct Memory Access                                        |

| EDAC        | Error Detection and Correction                              |

| HDA<br>HSDC | Head Assembly (Disk)<br>High Speed Disk Controller          |

| LSA         | Larkette Streamer Adapter                                   |

| MBZ         | Must be Zero                                                |

| ORU         | Optimum Replaceable Unit                                    |

| PWA         | Printed Wire Assembly                                       |

| RPS         | Rotational Position Sensing, on SMD-E only.                 |

| QDM<br>QLT  | Quarter Daughter Board Diskette Adapter<br>Quick Logic Test |

| SPM         | Scratch Pad Memory                                          |

| RFU         | Reserved for Future Use                                     |

| TCD<br>T&V  | Tape Cartridge Device<br>Test and Verification              |

| HONEYWELL BULL CONFIDENTIAL SPECIFICATIO | N NUMBER   PAGE | REVISION |

|------------------------------------------|-----------------|----------|

| AND PROPRIETARY 601497                   | 82   12         | C I      |

Blank

| , ' |           |                   |                      |      | ,        |

|-----|-----------|-------------------|----------------------|------|----------|

| 1   | HONEYWELL | BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |

| İ   | AND       | PROPRIETARY       | 60149782             | 13   | C        |

| ,   |           |                   |                      |      | ,        |

#### 2 ARCHITECTURE

#### 2.1 Overview

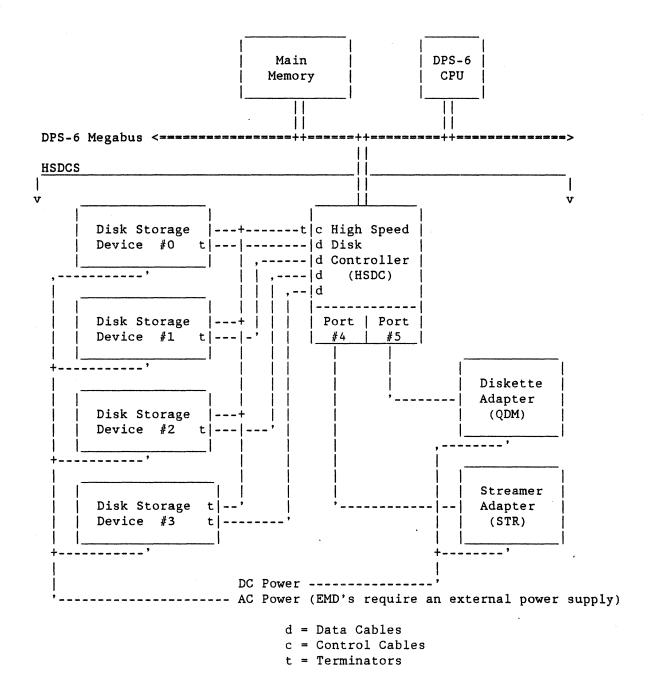

The High Speed Disk Controller Subsystem (HSDCS), Figure 2.1, provides the Megabus systems with facility to store and retrieve data from mass storage media mounted on a disk drive. Up to four Disk Drives (FSD's or EMD's, not mixed types) can be cabled to one HSDC which can process one data transfer and several seek commands simultaneously. The HSDC interfaces with other devices through adapters mountable on the HSDC motherboard; all devices can function independently and interface asynchronously with the Megabus.

### 2.2 Major components

## 2.2.1 High Speed Disk Controller

The HSDC is a microprogrammed peripheral control unit which can interface up to four disks cabled via connectors mounted on the edge of the printed circuit board (PWB). The HSDC firmware is generalized to facilitate its application as a control element for other devices interfaced through Adapters. The HSDC performs the following functions:

- o Execution of DPS-6 command sequences such as ACK, NAK, WAIT, etc...; status and control register storage in dedicated, per channel, random access memory accessible by both the HSDC and the CPU.

- o Direct Memory Access (DMA) data transfer control with data buffer for intermediate storage.

- o Multi-sector data transfers overlapping track and cylinder boundaries.

- o SMD-0 and SMD-E interface dialog control with serial-parallel and parallel-serial data conversion and associated error detection and correction.

- o Self-diagnostic, QLT, functions with an LED go/no-go indicator.

- o Media defect handling using the prerecorded error logs on each track "home address" (first sector) and new error log recorded on the last cylinder; this cylinder is also used for reallocated error sectors.

- o Adapter Interface for up to two additional channels.

| HONEYWELL | BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |

|-----------|-------------------|----------------------|------|----------|

| AND       | PROPRIETARY       | 60149782             | 14   | С        |

o Direct disk to streamer and streamer to disk data transfers are <u>not</u> supported.

Figure 2-1 High Speed Disk Controller Subsystem

| , - |           |                   |   |                      |   |      |          | , |

|-----|-----------|-------------------|---|----------------------|---|------|----------|---|

|     | HONEYWELL | BULL CONFIDENTIAL |   | SPECIFICATION NUMBER |   | PAGE | REVISION | L |

| İ   | AND       | PROPRIETARY       | Í | 60149782             | Ì | 15   | С        | Ĺ |

| · - |           |                   |   |                      |   |      |          | , |

#### 2.2.2 Fixed Storage Drive

The FSD is a small, random access, rotating 9.0" disk, mass memory device with rigid disk media storage and 9.67 MHz. SMD-0 or 14.52 MHz. SMD-E interface. Components of the FSD are: a box casting, integral switching type power supply, direct coupled DC brushless spindle drive motor with digital speed control brake, Disk Module with composite or thin film heads, logic package with read/write (phase-locked data separation and NRZ to 2,7 RLL code conversion), fault detection, transmitters, receiver and microprocessor controlled servo electronics. The Disk Module is an environmentally sealed unit containing the disks, heads, actuator, DC motor and air filter. Disk Logic Address is selectable by a plug on the front panel.

FSD Configurations:

o 9615-515 414 MB formatted (516 MBytes unformatted)

o 9615-160 132 MB formatted (166 MBytes unformatted)

Each FSD interfaces with the HSDC via two cables: one radial to each drive D (data) and one daisy-chainable C (command) cable; external termination is required on the last device on the C cable. Terminator is supplied with each device.

FSD Power:

Each drive requires AC power which can be internally set to the following nominal input voltage/frequency combinations:

100v through 120v @ 3.40 Amps in either 50 or 60Hz, nominal values 208v through 240v @ 2.10 Amps in either 50 or 60Hz, nominal values

#### 2.2.3 Eight Inch Module Drive (EMD II & III)

The EMD is a small, random access, rotating 8.0" disk, mass memory device with rigid disk media storage and 14.52 MHz SMD-E interface. Components of the EMD are: a box casting, integral switching type power supply, closed loop positioner using a dedicated servo surface for both coarse and fine positioning activity, Disk Module which is an environmentally sealed unit containing the oxide disks, thin film heads, balanced rotary actuator, brushless DC motor and air filter. CMOS and ECL technology with extensive use of LSI in all functions logic package, read/write (phase-locked data separation and NRZ to 2,7 RLL code conversion), fault detection, transmitters, receiver and microprocessor controlled servo electronics. The Disk Logic Address is selectable by a plug on the front panel.

FMD Configurations:

o 9720-368 295 MB formatted (368 MBytes unformatted)

o 9720-741 595 MB formatted (741 MBytes unformatted)

Each EMD interfaces with the HSDC via two cables: one radial to each drive D (data) and one daisy-chainable C (command) cable; external termination is required on the last device on the C cable. Terminator is supplied with each device.

| HONEYWELL | . BULL CONFIDENTIAL<br>D PROPRIETARY | SPECIFICATION NUMBER | REVISION |

|-----------|--------------------------------------|----------------------|----------|

| ·         | *****                                |                      | <br>     |

Each EMD drive (DC power required, only) with separate power supply requires AC power which can be internally set to the following nominal input voltage/frequency combinations:

100v through 120v @ 2.20 Amps in either 50 or 60Hz, nominal values 208v through 240v @ 1.30 Amps in either 50 or 60Hz, nominal values

#### 2.2.4 Minidiskette Adapter, QDM

The Quarter Daughter Board Diskette Adapter (QDM), reference EPS-1 #60149612, provides an interface to the 5 1/4 inch minidiskette. The HSDC emulates the MDC III (BDC8) firmware in controlling one minidiskette device attached to the QDM. Adapter functions are as follows:

- o Performs device interface dialog control and data recovery and transmission.

- o Address Mark generation and detection.

- o Control of Seek and Seek overlap; multi-sector data transfers overlapping track and cylinder boundries.

- o CRC generation and verification.

- o Device status monitoring.

Minidiskette Power.

Minidiskette device requires DC power from the system power supply at +5v. and +12v, nominal.

## 2.2.5 Streamer Adapter

The Streamer Adapter (STR) quarter sized daughter board is a microprogrammed peripheral control unit that can interface with one Tape Cartridge Device (TCD) cabled via a connector mounted on the STR printed circuit board. On one side, the STR, provides an interface to the common MDC-4 internal bus and on the other it controls access to the TCD. The STR contains the following functionality:

- o Device interface dialog control

- o Device read/write data buffers control; one 16 K byte buffer on the adapter and one disk track buffer on the HSDC.

- o STR to HSDC, MDC-4 interface control

TCD Power.

The TCD requires DC power from the system power supply. Frame ground and signal grounds are isolated in the TCD and are brought out separately to an external, system level, tie point. The following DC voltages are required: +5v., +12v. and -12v..

| ;-  | BULL CONFIDENTIAL | SPECIFICATION NUMBER | ,    |

|-----|-------------------|----------------------|------|

|     | <br>PROPRIETARY   |                      | C    |

| · - | <br>              |                      | <br> |

## FUNCTIONAL REQUIREMENTS

3

## 3.1 Configuration and Simultaneity

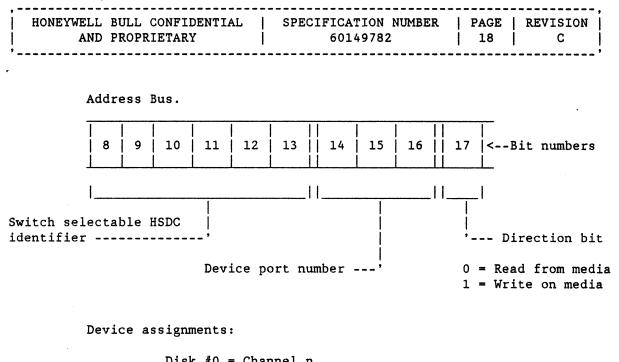

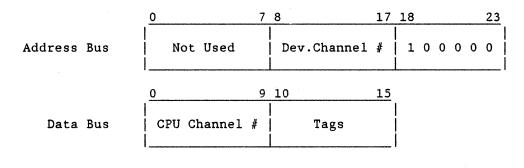

Devices attached to the HSDC are software addressable via channel numbers. Each individual device has two channel numbers assigned, differing from each other only in the low order bit value (the direction bit). When an IOLD instruction is issued to the HSDC, the direction bit of the output address channel number specifies whether it is going to be an input or an output data transfer; for all other commands, the direction bit is ignored. Bits 8 through 13 (reference figure 3-1) are assigned at system installation and must conform to constraints defined in the Megabus EPS-1. Software visibility of the devices attached to the HSDC is such that the devices are independent of each other; except that initiation of a command sequence addressed to one device may be stalled while the HSDC is busy servicing another device.

The HSDC provides a single level of simultaneity (only one data transfer can be active in the subsystem) and supports the following:

- A not busy channel must accept instructions directed to it over the Megabus even though a data transfer may be active over another channel. An instruction may be "waited" for a period not exceeding 100 microseconds; longer delays can affect performance of the entire system.

- o Any seek orders received during a data transfer must be initiated prior to the start of any another data transfer.

- o Channels are serviced on an alternating priority basis so that no channel can dominate controller usage.

- o Controller accepts a data read/write command to channel B while channel A is in the process of moving data but does not initiate a data transfer on B until A's data transfer is complete

- o If the HSDC is configured with less then six devices, it responds to channel numbers associated with the installed devices only.

## 3.2 Megabus Control

## 3.2.1 Command Transfer

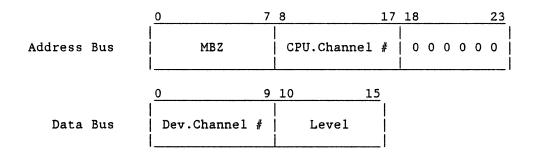

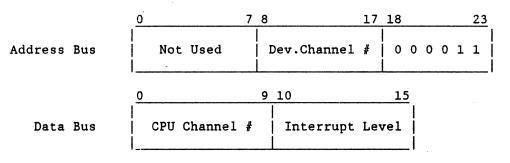

The HSDC recognizes a command transfer request on the Megabus when a valid channel number is decoded in bits 8 through 17 of the address bus. If the addressed

|          | DISK #0 |   | onanner | 11 |   |     |  |

|----------|---------|---|---------|----|---|-----|--|

|          | Disk #1 | = | n       | n  | + | 080 |  |

|          | Disk #2 | = | 11      | n  | + | 100 |  |

|          | Disk #3 | = | 11      | n  | + | 180 |  |

| Streamer | Adapter | = | Ħ       | n  | + | 200 |  |

| Diskette | Adapter | = | **      | n  | + | 280 |  |

channel is not busy, the contents of the data and address buses are stored in the HSDC interface hardware and the HSDC issues an ACK to the CPU to complete the bus cycle; now the HSDC can process the information contained in the registers. If the addressed channel is busy executing a previously received command, the HSDC completes the bus cycle by issuing a NAK (except for the Output Control Word command; reference section 5.). If, however, the HSDC is temporarily busy, processing a not interruptible function, it completes the bus cycle with a WAIT response which must be followed by either an ACK or a NAK response when the function in process terminates. WAIT response must be as short as possible ( $\leq$  100us.) to avoid performance degradation and if too long system hardware or software timeout may occur (lms on 6/9X CPU's).

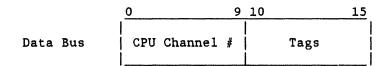

## 3.2.2 Data Transfer

All data transfers associated with the HSDC are executed in Direct Memory Access (DMA) mode; transfers are normally word wide but byte wide operation may occur on the first and/or last memory cycle of a particular data transfer if the memory buffer begins or ends on an odd byte boundary.

If, during memory read/write request cycle on the Megabus, a NAK response is received at the HSDC, data transfer is aborted with a nonexistent resource error posted in Status Word 1 (reference section 5.). A WAIT response to a memory read/write request cycle results in the HSDC retry of the Megabus request cycle; retries continue until an ACK or a NAK response is received. While either this Megabus cycle or the second half read cycle is pending in the HSDC

| , .<br> <br> | HONEYWELL | BULL CONFIDENTIAL<br>PROPRIETARY | <br>SPECIFICATION NUMBER<br>60149782 | ! | REVISION | ,<br> <br> |

|--------------|-----------|----------------------------------|--------------------------------------|---|----------|------------|

| ,            |           |                                  | <br>                                 |   | <br>     | ,          |

interface it is not accessible to the CPU including the Output Control Word command. Once the HSDC is conditioned to do a memory access all other Megabus cycles addressed to the HSDC are completed with either a NAK or a WAIT until the memory reference is terminated.

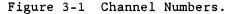

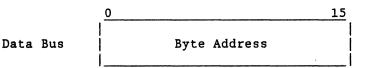

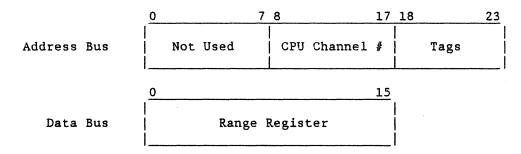

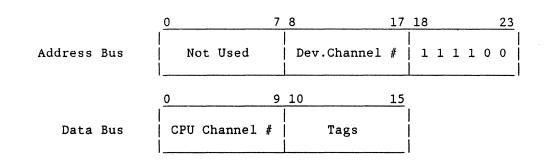

Memory read and write data accesses are illustrated in figure 3-2. During the memory read request cycles, bits 10 through 15 of the data bus may contain an address of a register in the HSDC into which the returned memory data is delivered. Memory responds in the second half of the read cycle by placing on the address bus, bits 8 through 23, the contents of the entire data bus as received, by the memory, during the request cycle.

HSDC Memory Write Request

Address Bus

0

78

HSDC Memory Read Request

Request Cycle.

|             | 0 78                      | 23    |

|-------------|---------------------------|-------|

| Address Bus | Module Number   Byte Ad   | dress |

|             | 0 9 10 15                 |       |

| Data Bus    | Dev.Channel #   Ref.3.2.2 |       |

Response Cycle.

|             | 0         | 78    | 17       | 18 2      | 23        |

|-------------|-----------|-------|----------|-----------|-----------|

| Address Bus | <br>  MBZ | Dev.C | hannel # | Ref.3.2.2 | <br> <br> |

|             | 0         |       | 15       |           |           |

| Data Bus    |           | Data  |          |           |           |

|             |           |       |          |           |           |

Figure 3-2 Address and Data Bus Configuration for Read and Write Memory Access.

| HONEYWELL BULL CONFIDENTIA |  | SPECIFICATION NUMBER | PAGE | REVISION  | Ì |

|----------------------------|--|----------------------|------|-----------|---|

| AND PROPRIETARY            |  | 60149782             | 20   | 1 · · · · | , |

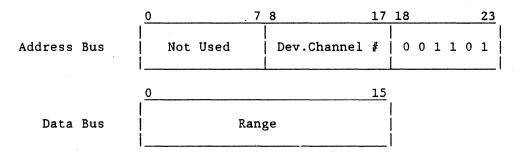

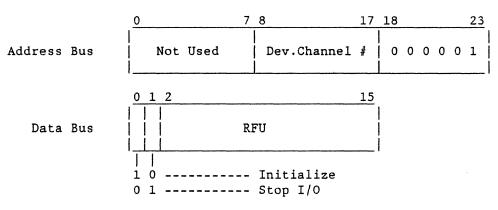

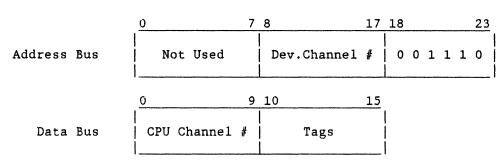

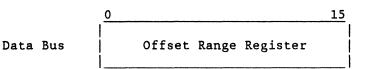

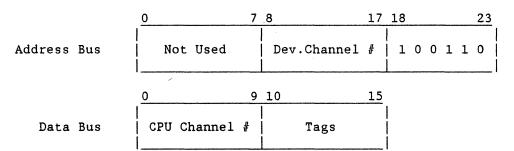

## 3.2.3 Interrupts

Whenever the channel interrupt level is not zero, either an operation initiated by an Output Task Word or an Output Control Word command is completed or the attention bit in the Status Word 1 is set, an interrupt on the Megabus is attempted. If a NAK response is received to an interrupt request, the HSDC saves the interrupt status until it detects the BSRINT pulse on the Megabus; interrupt is then retried. When an interrupt is saved the channel with the pending interrupt is busy and does not accept commands (except Output Control Word), however, other channels on the HSDC are free to function normally.

Channel zero interrupt level (initialized or set to zero) inhibits Megabus interrupts for that channel. If a condition or an event occurs which would normally cause an interrupt, the appropriate bits in a status word are set but no interrupt is attempted on the Megabus nor is the interrupt request saved; specifically, interrupts that would be generated as a result of either Output Control Word Initialize or Master Clear.

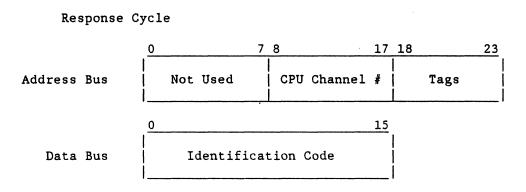

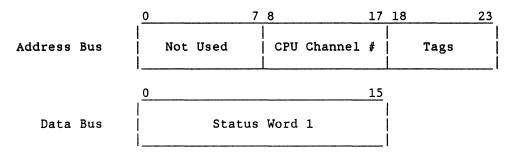

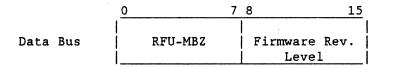

Address and data bus configuration for interrupt sequences is illustrated in Figure 3-3. The channel number supplied on the data bus during an interrupt is the one used in the most recent Output Address instruction to that HSDC channel; if the instruction has not been received the low order bit of the channel number is zero.

## Figure 3-3 Address and Data Bus Configuration for Interrupt Sequences

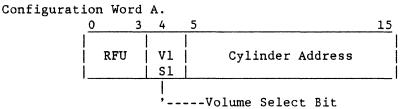

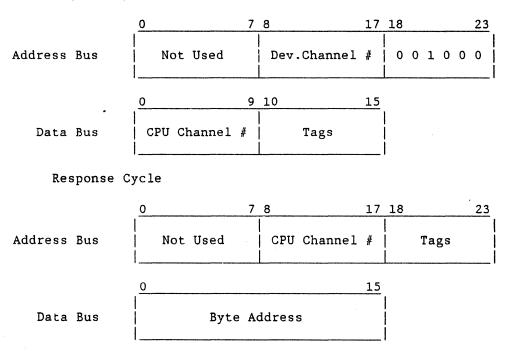

### 3.3 Overview of HSDC Access

Associated with each channel is a set of registers which are loaded by software and specify parameters required for attached device operation. In addition to the range and the address registers, used for DMA operation, there are configuration registers which contain record location and identification information and a task register for command codes. To perform a specific operation software first loads the address, range and configuration registers. The task register is loaded last with a command to be performed which also triggers the HSDC channel operation. Commands addressed to a not busy channel are always accepted, but execution may be delayed because another channel is in the process of data transfer. All commands addressed to a busy channel are rejected (NAK response) except Output Control Word.

| ,        |                     |                      |      | ,        |

|----------|---------------------|----------------------|------|----------|

| HONEYWEL | L BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |

| AN       | D PROPRIETARY       | 60149782             | 21   | С        |

| ,<br>,   |                     |                      |      | ,        |

## 3.3.1 Memory Addressability

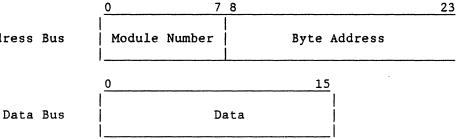

The Megabus interface is 16 bits wide for the data path and 24 bits wide for the address path with provision for the MRX Z01, Z02 and Z03 connectors and its impedance matching components. Memory burst mode of operation is not included in the HSDC design.

### 3.3.2 Scatter/Gather

The Scatter/Gather DMA data transfer is not supported by the HSDC in either hardware or firmware.

## 3.3.3 Dual Ported Drives

The Dual Ported FSD's or EMD's are not supported, presently. However, hardware to provide for dual ported devices is incorporated in the design except (lock/unlock) firmware to control these is not in place. FSD's and EMD's require an additional PWA in their controllers to accommodate this functionality; only EMD III is purchased as a dual ported device.

|                             | REVISION |

|-----------------------------|----------|

| AND PROPRIETARY 60149782 22 | C C      |

Blank

| ,                           |                      |      | ,        |

|-----------------------------|----------------------|------|----------|

| HONEYWELL BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |

| AND PROPRIETARY             | 60149782             | 23   | С        |

| ,                           |                      |      |          |

#### INTERFACES

4

No specific user action is required to load or initialize the HSDC other than during subsystem installation and subsystem configuration identification. Actions required to load/unload removable media devices (minidiskette or tape cartridge) are described in an appropriate EPS; see references in 1.3.1.

## 4.1 HSDC to Megabus Interface

The HSDC attaches to the Megabus as a standard DPS-6 (see Megabus EPS-1) controller with provision for the MRX Z01, Z02 and Z03 connectors and their impedance matching components.

## 4.2 Device Level Interface (DLI)

Refer to the FSD and EMD specifications for information more detailed than that presented in this section which is concerned with the physical interface only. The FSD and EMD specifications (references section 1.3.1) also represents the governing document for device functionalities.

Disk Devices require two cables for attachment to the HSDC. The "A" cable provides the daisy chain linkage between all drives on the DLI while the "B" cable provides a radial connection from each drive to the HSDC. Figure 4-1 shows signals present on each cable. Address and control functions are transferred on ten lines. The significance of the information on these lines is indicated by the three tag lines (refer to figure 4-2).

## 4.2.1 Address and Control Functions ("A" cable)

Three tag lines are used to send information to all connected drives on the "A" cable; only the selected drive responds to the encoded information. The ten control lines are strobed by the individual tag lines when the control data is valid.

### 4.2.1.1 Low Cylinder Address (Tag 1)

The SMD-E is a direct cylinder addressing interface which only needs the new cylinder address on the control lines and strobe Tag 1. The drive must be "On Cylinder" before Tag 1 is issued. To provide for more cylinder addressing than the ten tag lines permit two additional bits are available within Tag 2, reference figure

HONEYWELL BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION | AND PROPRIETARY | 60149782 | 24 | C |

.

| HSDC      |                                        | DR                    | IVE  |

|-----------|----------------------------------------|-----------------------|------|

|           | "A" CABLE                              | LO                    | HI   |

| 1         | Unit Select Tag>                       |                       | 52   |

|           | Unit Select 20>                        | 23                    | 53   |

|           | Unit Select 2 <sup>1</sup> >           | 24                    | 54   |

|           | Unit Select 2 <sup>2</sup> >           | 26                    | 56   |

| 1         | Unit Select 2 <sup>3</sup> /Tag 5-*>   | 27                    | 57   |

| 1         | Tag 1-*                                | 1                     | 31   |

| 1         | Tag 2-*>                               | 2                     | 32   |

|           | Tag 3-*>                               | 3                     | 33   |

|           | Bus Out-Bit 0-*>                       | 4                     | 34   |

|           | Bus Out-Bit 1-*>                       |                       | 35   |

| ĺ         | Bus Out-Bit 2-*>                       | 6                     | 36   |

|           | Bus Out-Bit 3-*>                       |                       | 37   |

|           | Bus Out-Bit 4-*>                       | 8                     | 38   |

|           | Bus Out-Bit 5-*>                       | 9                     | 39   |

|           | Bus.Out-Bit 6-*>                       | 10                    | 40   |

| Ì         | Bus Out-Bit 7-*>                       | 11                    | 41   |

| 1         | Bus Out-Bit 8-*>                       | 12                    | 42   |

| İ         | Bus Out-Bit 9-*>                       | 13                    | 43   |

|           | Open Cable Detector>                   | 14                    | 44   |

| 1         | < Bus In-Bit 0-*                       | 19                    | 49   |

|           | < Bus In-Bit 1-*                       | 17                    | 47   |

| ĺ         | < Bus In-Bit 2-*                       | 16                    | 46   |

|           | < Bus In-Bit 3-*                       | 15                    | 45   |

|           | < Bus In-Bit 4-*                       | 28                    | 58   |

|           | < Bus In-Bit 5-*                       | 20                    | 50   |

| 1         | < Bus In-Bit 6-*                       | 18                    | 48   |

|           | < Bus In-Bit 7-*                       | 25                    | 55   |

|           | Power Sequence Pick(Power On)->        | ·İ                    | 29   |

| 1         | Power Sequence Hold(Power On)->        | ·İ                    | 59   |

| A         | < Busy-*-#                             | 21                    | 51   |

| CONNECTOR | Tag 4-(Ground on SMD-0)>               | 30                    | 60   |

|           | ······································ | • ••••••••••••••••••• |      |

|           | " <u>B" CABLE</u>                      | LO                    | HI   |

| 1         | Urito Data                             | 1 0                   | 1 00 |

|           | " <u>B" CABLE</u>                                                                 | LO    | HI    |  |

|-----------|-----------------------------------------------------------------------------------|-------|-------|--|

|           | Write Data>                                                                       | 8     | 20    |  |

|           | GroundGroundGroundGroundGround                                                    | 7     |       |  |

|           | Write Clock>                                                                      | 6     | 19    |  |

|           | Ground                                                                            | 18    |       |  |

| 1         | <pre><servo clock<="" pre=""></servo></pre>                                       | 2     | 14    |  |

| 1         | Ground                                                                            | 1     |       |  |

| 1         | <pre><read data<="" dataread="" td=""><td>3</td><td>16</td><td></td></read></pre> | 3     | 16    |  |

|           | Ground                                                                            | 15    |       |  |

| 1         | <pre><read clock<="" pre=""></read></pre>                                         | 5     | 17    |  |

|           | Ground                                                                            | 4     | İ     |  |

|           | <pre><seek end<="" endseek="" pre=""></seek></pre>                                | 10    | 23    |  |

|           | <pre><unit pre="" selected<=""></unit></pre>                                      | 22    | 9     |  |

| 1         | Ground                                                                            | 21    | i i   |  |

|           | Reserved for Index                                                                | 12    | 24    |  |

| 1         | Ground                                                                            | 11    | İ     |  |

|           | Reserved for Sector                                                               | 13    | 26    |  |

| B         | Ground                                                                            | 25    | İ     |  |

| CONNECTOR | K Gated by Unit Selected                                                          | CONNI | ECTOR |  |

|           | <pre># Dual channel units only</pre>                                              |       |       |  |

Figure 4-1 "A" & "B" Interface Cables

|    |           |                   |   |                      |      |          | , |

|----|-----------|-------------------|---|----------------------|------|----------|---|

|    | HONEYWELL | BULL CONFIDENTIAL |   | SPECIFICATION NUMBER | PAGE | REVISION |   |

| 1  | AND       | PROPRIETARY       | 1 | 60149782             | 25   | C        |   |

| '_ |           |                   |   |                      | <br> | '        | • |

4-2. The High Order Cylinder Address bits  $(2^{10} \text{ and } 2^{11}, \text{ Tag } 2)$  must be set before Tag 1 since carriage motion begins with Tag 1. Valid Head Select Address must be sent with each Tag 2 to prevent Head Select Fault.

## 4.2.1.2 Head and High Cylinder Select (Tag 2)

The control lines 0 through 4 and 7 through 8 determine the Head Address and High Order Cylinder Address respectively together with the Tag 2 strobe.

## 4.2.1.3 Control Select (Tag 3)

This signal acts as an enable and must be true for the entire control operation.

### 4.2.1.3.1 Write Gate (Bus Out Bit 0)

The Write Gate line enables the Write Data driver circuit during a Write operation.

#### 4.2.1.3.2 Read Gate (Bus Out Bit 1)

The Read Gate line enables the digital Read Data transmission lines.

### 4.2.1.3.3 Servo Offset Plus (Bus Out Bit 2)

When this signal is true, the actuator is offset from the nominal "On Cylinder" (the "On Cylinder" signal becomes not true for 2.75 ms, approximately) position towards the spindle. Write gate must not be made true by the HSDC while in the Offset mode. The time for the carriage to move + to - or - to + offset is 4 ms.

#### 4.2.1.3.4 Servo Offset Minus (Bus Out Bit 3)

When this signal is true, the actuator is offset from the nominal "On Cylinder" (the "ON Cylinder" signal becomes not true for 2.75 ms, approximately) position away from the spindle. Write gate must not be made true by the HSDC while in the Offset mode. The "ON Cylinder" signal goes false for 2.75 ms. after the offset + or - goes false.

#### 4.2.1.3.5 Fault Clear (Bus Out Bit 4)

A 100 ns (minimum) pulse sent to a selected device clears the fault flip-flop if the fault condition no longer exists. A Seek Error is cleared by a Return-to-zero.

4.2.1.3.6 Address Mark Enable (Bus Out Bit 5)

The address Mark (AM) Enable signal, in conjunction with Write Gate or Read Gate, allows the writing or recovering of Address Marks:

| ,-  |     | BULL CONFIDENTIAL |   | SPECIFICATION NUMBER |   |    |       |   |

|-----|-----|-------------------|---|----------------------|---|----|-------|---|

| İ   | AND | PROPRIETARY       | İ | 60149782             | İ | 26 | j c j |   |

| ' - |     |                   |   |                      |   |    |       | ' |

- o When AM Enable is true together with Write Gate, the writer stops toggling and erases the data creating an AM. The HSDC ensures that the written AM is greater than 22 bits and less then 32 bits in length. Write Fault detection is inhibited by the AM Enable signal.

- o When AM Enable is true together with Read Gate, an analog voltage comparator detects the absence of a Read signal. If the duration of the erased area on the medium is 3 bytes long, an AM Found signal is asserted.

- o If AM is not used , Bit 5 must be held inactive during Control Select (Tag 3) functions. AM must be three bytes long with no transitions.

## 4.2.1.3.7 Return To Zero (Bus Out Bit 6)

A 500 ns to 1 ms pulse sent to the device causes the actuator to seek track zero and reset both the head register and Seek Error flip-flop. This seek is significantly longer (1 second, maximum) than normal seek to track zero and should only be used for recalibration, not data aquisition.

## 4.2.1.3.8 Data Strobe Early (Bus Out Bit 7)

When this signal is true, the drive Phase Locked Oscillator (PLO) data separator strobes the data at a time earlier than nominal; when false nominal timing is returned.

#### 4.2.1.3.9 Data Strobe Late (Bus Out Bit 8)

When this signal is true, the drive PLO data separator strobes the data at a time later than nominal; when false nominal timing is returned.

## 4.2.1.3.10 Release, Dual Channel only (Bus Out Bit 9)

Enabling this signal releases Channel Reserve and Channel Priority Select Reserve in the device making alternate channel access possible after selection by the other channel ceases. Reference the Interface specification for more details, 1.3.1.

#### 4.2.1.3.11 Unit Select

Priority Select, Dual Channel only (Bus Out Bit 9 and Unit Select Tag)

When this signal is true during Unit Select Tag (strobe) the device is unconditionally selected and absolutely reserved by the respective channel providing both channels are enabled and a priority select condition does not exist on the opposite channel. Reference the Interface specification for more details, 1.3.1.

## 4.2.1.4 EMD/SMD-E Extended Drive Dependent Status

The EMD provides the following extended functions (Figore 4-4) when in the SMD-E mode, reference the interface specification for timing considerations:

| 1 | ,         |                   |                      |      | ,        |  |

|---|-----------|-------------------|----------------------|------|----------|--|

|   | HONEYWELL | BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |  |

| ĺ | AND       | PROPRIETARY       | 60149782             | 27   | C I      |  |

| 1 |           |                   |                      |      |          |  |

#### 4.2.1.5 Current Sector Status (Tag 4)

Tag 4 allows the current sector address (4 - 128) to be transmitted to the HSDC on BUS IN lines bit - 0 through bit - 7. The sector counter is free running and the count is valid 200ns, maximum, after the leading edge of the Sector or the Index pulse.

#### 4.2.1.6 Device Extended Status (Tag 5)

Tag 5 in conjunction with BUS OUT bits 0 and 1 allows the Fault Status, Operating Status, Diagnostic Status or Execute Command/Status to be presented over the BUS IN lines.

4.2.1.6.1 Fault Status

When all the BUS OUT bits are equal to zero and Tag 5 equals to one, the following fault status is available:

Read and Write fault, BUS IN Bit 0

When true, this bit indicates that Read and Write conditions existed simultaneously.

Read or Write and Off Cylinder, BUS IN Bit 1

When true, this bit indicates that a Read or a Write condition existed during a Seek (Off Cylinder) condition.

First Seek fault, BUS IN Bit 2

When true, this bit indicates that the drive has failed a first seek/load attempt.

Write fault, BUS IN Bit 3

When true, this bit indicates that a write fault has occurred.

Write and Write Protected, BUS IN Bit 4

When true, this bit indicates that a write function was attempted while the drive is in a write protected condition.

Head Select fault, BUS IN Bit 5

When true, this bit indicates that no heads are selected or that multiple heads are selected.

Voltage fault, BUS IN Bit 6

When true, this bit indicates a below normal voltage exists within the drive.

| <b>,</b> • |           |                   |                      |      | ,        |  |

|------------|-----------|-------------------|----------------------|------|----------|--|

| 1          | HONEYWELL | BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |  |

|            |           |                   | 601/0702             | 20   |          |  |

|            | AND       | PROPRIETARY       | 60149782             | 28   | <b>C</b> |  |

| ۰.         |           |                   |                      |      |          |  |

Valid status, BUS IN Bit 7

When true, this bit indicates that a valid fault status exists on BUS IN Bits 0 through 6.

4.2.1.6.2 Operating Status

When BUS OUT bit 0 = 1 and bit 1 = 0, all others are equal to zero, and Tag 5 equals to one, the following operating status, in BUS IN Bits 0 through 7, is available:

Valid status, BUS IN Bit 7

When true, this bit indicates that a valid operating status exists on BUS IN Bits 0 through 6.

| Interface          | Diagnostic   | Status                                |

|--------------------|--------------|---------------------------------------|

| <u>Status Code</u> | Display Code | Description                           |

|                    |              |                                       |

| 00                 | 00           | Ready and On Cylinder                 |

| 01                 | 01           | Carriage parked                       |

| 02                 | 02           | Motor stopping                        |

| 03                 | 03           | Motor stopped                         |

| 04                 | 04           | First load/calbrate                   |

| 05                 | 05           | Sequence delay                        |

| 06                 | 06           | Waiting for, hold + local             |

| 07                 | 07           | Starting motor                        |

| 08                 | 08           | Motor up to speed                     |

|                    |              |                                       |

| 46                 | 46           | Seek timeout                          |

| 4 B                | 4B           | Off-track seek error                  |

| 4D                 | 4D           | Illegal cylinder address              |

| 4F                 | 4F           | Seek error on settle-in               |

|                    | 50           | · · · · · · · · · · · · · · · · · · · |

| 50                 | 50           | Low Vcc glitch                        |

| 51                 | 51           | Control MPU reset                     |

| 54                 | 54           | First seek fault on retract           |

| 55                 | 55           | First seek fault on load              |

| 56                 | 56           | First seek fault on RTZ               |

| 57                 | 57           | First seek fault on Calibrate         |

| 58                 | 58           | Speed loss                            |

| 59                 | 59           | Motor can not start                   |

| 5A                 | 5A           | Emergency retract                     |

|                    |              |                                       |

| 60                 | 60           | Motor MPU failure                     |

| 61                 | 61           | Servo MPU failure                     |

## 4.2.1.6.3 Diagnostic Status

When BUS OUT bit 0 = 0 and bit 1 = 1, all others are equal to zero, and Tag 5 equals to one, the following diagnostic status, in BUS IN Bits 0 through 7, is available:

| , - |           |                   |                      |      | ,        |

|-----|-----------|-------------------|----------------------|------|----------|

| 1   | HONEYWELL | BULL CONFIDENTIAL | SPECIFICATION NUMBER | PAGE | REVISION |

| i   | AND       | PROPRIETARY       | 60149782             | 29   | С        |

| ;_  |           |                   |                      |      | ;        |

Valid status, BUS IN Bit 7