## ASSEMBLY LANGUAGE

SERIES 60 (LEVEL 6)

GCOS/BES2

### SOFTWARE

## ASSEMBLY LANGUAGE

SERIES 60 (LEVEL 6)

GCOS/BES2

SUBJECT:

Detailed Description of Series 60 (Level 6) GCOS/Basic Executive System 2 Assembly Language

SOFTWARE SUPPORTED:

This publication supports Release 0200 of the Series 60 (Level 6) GCOS/Basic Executive System 2. When a later release of the system occurs, see the Subject Directory of the latest Series 60 (Level 6) GCOS/BES2 Software Overview and System Conventions manual (Order No. AU50) to ascertain whether this revision of this manual supports that release.

DATE:

July 1976

ORDER NUMBER: AU43, Rev. 0

## PREFACE

This manual describes the GCOS/Basic Executive System 2 (GCOS/BES2) assembly language, a machine-oriented language for writing programs to execute upon the Series 60 (Level 6) 6/30 Models. Unless stated otherwise herein, the term BES will be used to refer to the GCOS/BES2 software; the term Level 6 will indicate the specific models of Series 60 (Level 6) on which the described software executes.

Where appropriate, the actions performed by the BES Assembler as it processes elements of the assembly language are also discussed. Within this document, the term "assembly language" includes both Assembler control statements and assembly language instructions.

Section 1 introduces the Level 6 describing both data representation and the hardware registers. Section 2 describes the basic elements of the BES assembly language, and Section 3 describes the considerations the programmer must make when writing his source program. Sections 4 and 5 describe, in detail, the Assembler control statements and assembly language instructions, respectively. The macro facility is described in Section 6. Appendix A provides programmer reference information. Appendix B describes the hexadecimal numbering system. Appendix C contains a sample assembly language program. Appendix D describes how to debug an assembly language program. Appendix E contains a list of flags produced by the assembler to notify the user of a source code error. Appendix F describes error flags that may be issued by the Macro Preprocessor. Appendix G contains a list of reserved symbolic names.

Descriptions and examples within this manual use the following conventions:

- { } Indicates that one of the options enclosed in the braces must be selected.

- [] Indicates that one or none of the enclosed options need be selected; if one of the options is underlined, it is selected as the default if you do not select any of the options enclosed in the brackets.

- ... Indicates either a logical sequence (e.g., A,B...) or that the immediately preceding type of value can be repeated (e.g., a...).

- a Indicates that the character must be replaced by any valid ASCII character.

- n Indicates that the character must be replaced by any valid numeric (decimal) digit.

- d Indicates that the character must be replaced with a binary digit.

- h Indicates that the character must be replaced with a hexadecimal digit (0 through 9, A through F).

- c Indicates that the character must be replaced with a, n, or h, above.

- $\triangle$  Indicates that one or more spaces or horizontal tab characters are required.

Uppercase letters, numbers, and any of the following special characters must be coded exactly as shown:

| ()     | \$ |

|--------|----|

| <<br>> | /  |

| =      | *  |

| +      | ,  |

| -      | •  |

|        | ,  |

File No.: 1S23

#### **GCOS/BES2** Subject Directory

This subject directory is designed to assist the user in finding information about specific topics related to GCOS/BES2. Topics are listed alphabetically; each topic is accompanied by the order number of each manual in which the topic is described. At the end of the Subject Directory, all GCOS/BES2 manuals are listed according to the alphabetic/numeric sequence of their order numbers.

| Subject                                                                                                           | Order N | о. |

|-------------------------------------------------------------------------------------------------------------------|---------|----|

| Allocate Disk File (Utility Set 1)                                                                                | AU4     | 47 |

| Application Development (Overview)                                                                                |         |    |

| ASCII Character Set and Conversion Tables                                                                         |         |    |

| Assembling Programs                                                                                               |         |    |

| Assembler Diagnostic Flags                                                                                        |         |    |

| Assembly Source Language                                                                                          |         |    |

| BASIC                                                                                                             |         |    |

| Bootstrap Generator                                                                                               |         |    |

| Bootstrapping and Loading                                                                                         |         |    |

| Buffer Manager                                                                                                    |         |    |

| Building an Online Application                                                                                    |         |    |

| Card Loader                                                                                                       |         |    |

| Clock Manager                                                                                                     |         |    |

| COBOL Compilation                                                                                                 |         |    |

| COBOL Source Language                                                                                             |         |    |

| COBOL Statements                                                                                                  |         |    |

| COBOL Statements COBOL Statements COBOL Statements COBOL Statements COBOL Statements Compiler Diagnostic Messages |         |    |

| COBOL Complete Diagnostic Messages                                                                                |         |    |

| Command Processor                                                                                                 |         |    |

| Communications                                                                                                    |         |    |

| Compare Disk Volumes/Files/Members (Utility Set 3)                                                                |         |    |

| Configuration Load Manager                                                                                        |         |    |

| Console Messages (Error and Informational)                                                                        |         |    |

| Control Panel                                                                                                     |         |    |

| Copy Disk Volume/File/Member (Utility Set 3)                                                                      |         |    |

| Cross-Reference Program                                                                                           |         |    |

| Debugging (Offline)                                                                                               |         |    |

| Debugging (Online)                                                                                                |         |    |

| Delete Disk File/Member (Utility Set 1)                                                                           |         |    |

| Disk Conventions                                                                                                  |         |    |

| Disk Loader                                                                                                       |         |    |

| Dumps                                                                                                             |         |    |

| Dump Edit                                                                                                         |         |    |

| Editor                                                                                                            |         |    |

| Equipment Requirements                                                                                            |         |    |

| Error Reporting by Online Applications                                                                            |         |    |

| Error Reporting by System Software                                                                                |         |    |

| Executive Components                                                                                              |         |    |

| File Manager                                                                                                      |         |    |

| File Naming Conventions                                                                                           |         |    |

| Floating-Point Simulator                                                                                          |         |    |

| FORTRAN Compilation                                                                                               |         |    |

| FORTRAN Compiler Diagnostic Messages                                                                              |         |    |

| FORTRAN Intrinsic Functions                                                                                       |         |    |

| FORTRAN Source Language                                                                                           |         |    |

| FORTRAN Statements and Procedures                                                                                 |         |    |

| Glossary of System Terms                                                                                          |         |    |

| Hexadecimal Numbering System                                                                                      |         |    |

| Initialize Disk Volume/File (Utility Set 1)                                                                       |         |    |

| Input/Output Drivers                                                                                              |         |    |

| · · · · · · · · · · · · · · · · · · ·                                                                             |         |    |

| Linker AU48                                               |

|-----------------------------------------------------------|

|                                                           |

| List Disk Volume/File Description (Utility Set 1) AU47    |

| Loaders AU46                                              |

| Macro Facility Usage AU43                                 |

| Macro Preprocessor                                        |

| Offline Applications AU45                                 |

| Operating Procedures AU46                                 |

| Operator Interface Manager AU45                           |

| Overlay Loader AU45                                       |

| Paper Tape Loader AU46                                    |

| Planning an Online Application AU49                       |

| Print Disk File/Member (Utility Set 2) AU47               |

| Program Development Tools                                 |

| Program Naming Conventions AU50                           |

| Program Patch AU47                                        |

| Punch Disk File/Member to Paper Tape (Utility Set 2) AU47 |

| Rename Disk Volume/File/Member (Utility Set 1) AU47       |

| Replace Memory Values (Utility Set 1) AU47                |

| Scientific Branch Simulator                               |

| Software Release Materials (Contents) AU50                |

| System Conventions                                        |

| System Software and Documentation (Overview)              |

| Task Manager   AU45                                       |

| Trace Trap Handler                                        |

| Transfer Input to Disk File/Member (Utility Set 2)        |

| Trap Handling (Offline)                                   |

|                                                           |

| Trap Handling (Online)                                    |

| Utility Programs                                          |

The following publications constitute the GCOS/BES2 manual set. The Subject Directory in the latest Series 60 (Level 6) GCOS/BES2 Software Overview and System Conventions manual lists the current revision number and addenda (if any) for each manual in the set.

| Order No. | Manual Title                                                     |

|-----------|------------------------------------------------------------------|

| AS32      | Series 60 (Level 6) GCOS/BES FORTRAN Reference Manual            |

| AU41      | Series 60 (Level 6) GCOS/BES2 COBOL Reference Manual             |

| AU43      | Series 60 (Level 6) GCOS/BES2 Assembly Language Reference Manual |

| AU44      | Series 60 (Level 6) GCOS/BES2 BASIC Reference Manual             |

| AU45      | Series 60 (Level 6) GCOS/BES2 Executive and Input/Output         |

| AU46      | Series 60 (Level 6) GCOS/BES2 Operator's Guide                   |

| AU47      | Series 60 (Level 6) GCOS/BES2 Utility Programs                   |

| AU48      | Series 60 (Level 6) GCOS/BES2 Program Development Tools          |

| AU49      | Series 60 (Level 6) GCOS/BES2 Planning and Building an Online    |

|           | Application                                                      |

| AU50      | Series 60 (Level 6) GCOS/BES2 Software Overview and System       |

|           | Conventions                                                      |

In addition to the GCOS/BES2 manual set, the following manual is required by GCOS/BES users as a general hardware reference:

| Order No. | Manual Title |

|-----------|--------------|

|           |              |

AS22 Honeywell Level 6 Minicomputer Handbook

The following manual provides detailed information regarding programming for the Multiline Communications Processor:

| Order No.    | Manual Title                                           |

|--------------|--------------------------------------------------------|

| <b>AT</b> 97 | Series 60 (Level 6) MLCP Programmer's Reference Manual |

# CONTENTS

|                              | Page        |

|------------------------------|-------------|

| Section 1. Introduction      | 1-1         |

| Assembly Languages           |             |

| Level 6 Data                 |             |

| Representations              | 1-1         |

| Signed Integer Data          | 1-2         |

| Unsigned Data                |             |

| Floating-Point Data          |             |

| Level 6 Hardware             |             |

| Considerations               | 1-4         |

| Hardware Registers           | 1-4         |

| Program Counter (P) Register |             |

| Address (Bn) Registers       |             |

| General (Rn) Registers       |             |

| Mode (Control (M1) Register  |             |

| System Status (S) Register   |             |

| Indicator (I) Register       |             |

| Scientific Information       |             |

| Processor (SIP) Registers    | 1-6         |

| Scientific Accumulator       |             |

| (Sn) Registers               | 1-6         |

| Scientific Indicator         |             |

| (SI) Register                | 1-6         |

| SIP Mode (M4) Register       |             |

| SIP Trap Mask                |             |

| (M5) Register                | 1-7         |

| Software Simulation of       |             |

| the Scientific Information   |             |

| Processor                    | 1 <b>-8</b> |

|                              |             |

| Section 2. Elements of BES   |             |

| Assembly Language            |             |

| Mnemonic Codes               |             |

| Symbolic Names               |             |

| Identifiers                  |             |

| Labels                       |             |

| User-Defined Labels          |             |

| Reserved Labels              |             |

| Constants                    |             |

| String Constants             |             |

| ASCII String Constants       | 2-4         |

| Hexadecimal String           |             |

| Constants                    |             |

| Bit String Constants         | 2-5         |

| Truncation/Padding           |             |

| of String Constants          |             |

| Arithmetic Constants         | 2-6         |

| Integer Constants            | 2-6         |

| Decimal Integer Constants    | 2-6         |

| Hexadecimal Integer          |             |

| Constants                    |             |

| Fixed-Point Constants        | 2-6         |

| Floating-Point               |             |

| Constants                    |             |

| Normalization                | 2-8         |

|                                               | Page |

|-----------------------------------------------|------|

| Expressions                                   |      |

| Evaluating Expressions                        | 2-9  |

| Expressions                                   | 2-9  |

| Internal Value Expressions                    |      |

| Location Expressions                          | 2-10 |

| Internal Location<br>Expressions              | 2-10 |

| Expressions                                   | 2-10 |

| Expressions                                   | 2-11 |

| Common Location                               |      |

| Expressions                                   | 2-11 |

| Address Expressions                           |      |

| References                                    | 2-13 |

| Section 3. Programming Considerations         | 3-1  |

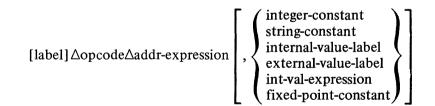

| Assembly Language Source<br>Statement Formats | 3_1  |

| Order of Statements in Source                 | 5-1  |

| Program                                       | 3-2  |

| Calling System Services                       |      |

| Calling External Procedures                   | 3-2  |

| Assembler-Related Utility                     |      |

| Program                                       |      |

| Scientific Instruction Processor (SIP)        | 3-3  |

| Programming Considerations                    | 3-3  |

|                                               |      |

| Section 4. Assembler Control                  | 4 1  |

| Statements<br>Assembly-Controlling Statements |      |

| List-Controlling Statements                   |      |

| Data-Defining Statements                      |      |

| Storage-Allocation Statements                 | 4-2  |

| Symbol-Defining Statements                    |      |

| Program-Linking Statements                    | 4-2  |

| Conditional Assembly-Control<br>Statements    | 1_2  |

| Assembler Control Statements                  |      |

| CALL                                          |      |

| CLST                                          |      |

| COMM                                          |      |

| CTRL                                          |      |

| DC<br>END                                     |      |

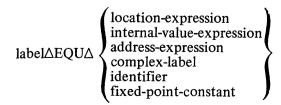

| EQU                                           |      |

| FAIL                                          |      |

| IF                                            |      |

| LIST                                          | 4-8  |

| NLST                                          |      |

| NULL                                          |      |

| ORG                                           |      |

| TEXT                                          |      |

| TITLE                                         |      |

XDEF ..... 4-11

| XLOC | <br> | 4-12 |

|------|------|------|

| XVAL | <br> | 4-12 |

| Section 5. Assembly Language   |      |

|--------------------------------|------|

| Instructions                   | 5-1  |

| Arithmetic Operations          | 5-1  |

| Boolean Operations             |      |

| Branch Operations              | 5-2  |

| Compare Operations             | 5-2  |

| Control Operations             |      |

| Input/Output Operations        |      |

| Load Operations                |      |

| Modify Operations              |      |

| Scientific Instructions        |      |

| Shift Operations               |      |

| Store Operations               |      |

| Swap Operations                |      |

| Assembly Language Instruction  |      |

| Types                          | 5-3  |

| Branch-on-Indicator (BI)       |      |

| Instructions                   | 5-3  |

| Branch-on-Register (BR)        |      |

| Instructions                   | 5-4  |

| Double Operand (DO)            |      |

| Instructions                   |      |

| Generic (GE) Instructions      | 5-5  |

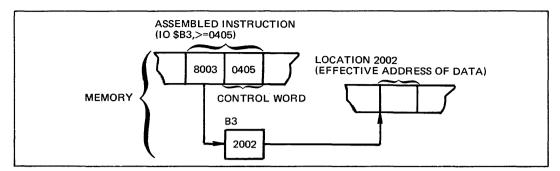

| Input/Output (IO) Instructions | 5-5  |

| Shift (SHS and SHL)            |      |

| Instructions                   | 5-5  |

| Short-Value-Immediate (SI)     |      |

| Instructions                   | 5-6  |

| Single Operand (SO)            |      |

| Instructions                   | 5-6  |

| Addressing Techniques          | 5-7  |

| Register Addressing            | 5-7  |

| Immediate Memory               |      |

| Addressing (IMA)               | 5-7  |

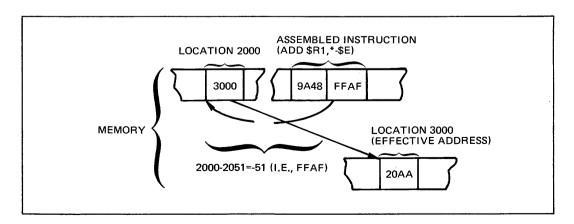

| Direct Immediate Memory        |      |

| Addressing                     | 5-8  |

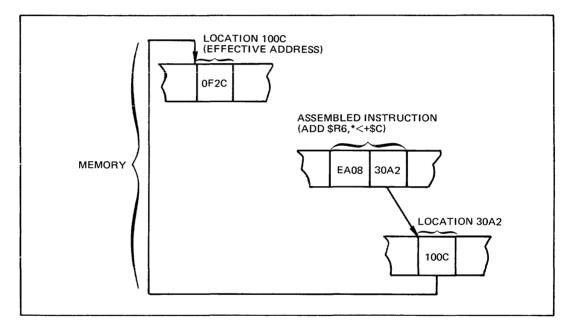

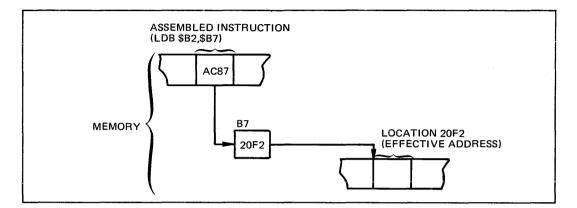

| Indirect Immediate Memory      |      |

| Addressing                     | 5-9  |

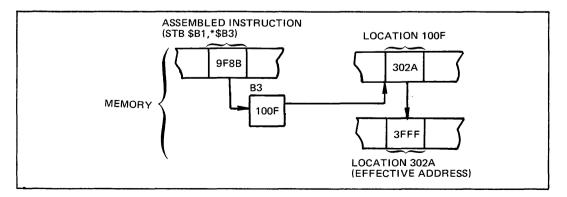

| Indexed Direct Immediate       |      |

| Memory Addressing              | 5-9  |

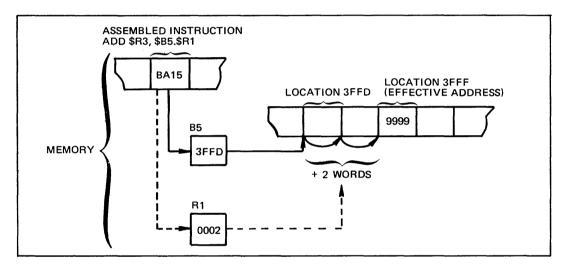

| Indexed Indirect Immediate     |      |

| Memory Addressing              | 5-10 |

| Immediate Operand Addressing   | 5-10 |

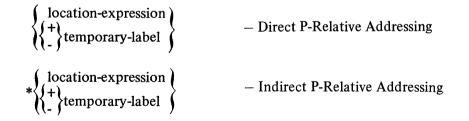

| P-Relative Addressing          |      |

| Direct P-Relative              |      |

| Addressing                     | 5-12 |

| Indirect P-Relative            |      |

| Addressing                     | 5-13 |

| B-Relative Addressing          |      |

| Direct B-Relative              |      |

| Addressing                     | 5-14 |

| Indirect B-Relative            |              |

|--------------------------------|--------------|

| Addressing                     | 5-15         |

| Indexed Direct B-Relative      |              |

| Addressing                     | 5-16         |

| Indexed Indirect B-Relative    |              |

| Addressing                     | 5-16         |

| Direct B-Relative Plus         |              |

| Displacement Addressing        | 5-17         |

| Indirect B-Relative Plus       |              |

| Displacement Addressing        |              |

| B-Relative Push Addressing     |              |

| B-Relative Pop Addressing      | 5-19         |

| Indexed B-Relative Push        |              |

| Addressing                     | 5-20         |

| Indexed B-Relative Pop         | r 20         |

| Addressing                     |              |

| Short Displacement Addressing  |              |

| Specialized Address Expression |              |

| Interrupt Vector Addressing    |              |

| Assembly Language Instructions |              |

| ADD                            |              |

| ADV                            |              |

| AND ANH                        |              |

| В                              |              |

| BAG                            |              |

| BAGE                           |              |

| BAL                            |              |

| BALE                           |              |

| BBF                            |              |

| BBT                            |              |

| BCF                            |              |

| BCT                            |              |

| BDEC                           |              |

| BE                             | 5-31         |

| BEVN                           |              |

| BEZ                            |              |

| BG                             | 5-33         |

| BGE                            | 5-33         |

| BGEZ                           | 5-33         |

| BGZ                            | 5-34         |

| BINC                           | 5-34         |

| BIOF                           | 5-35         |

| BIOT                           | 5-35         |

| BL                             | 5-36         |

| BLE                            | 5-36         |

| BLEZ                           | 5-37         |

| BLZ                            | 5-37         |

| BNE                            | 5-37         |

| BNEZ                           | 5-38         |

| BNOV                           | 5-38<br>5-39 |

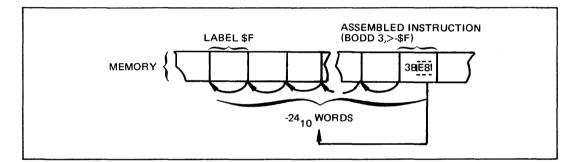

| BODD                           |              |

| BOV<br>BRK                     |              |

|                                | J-+0         |

| BSE      | 0 |

|----------|---|

| BSU      | 1 |

| CAD      |   |

|          |   |

| CL       | _ |

| CLH      | _ |

| СМВ 5-4  | 3 |

| СМН      | 3 |

| CMN      | 4 |

| CMR      | - |

|          | - |

| CMV      | - |

| CMZ      | 6 |

| CPL      | 7 |

| DAL      | 7 |

| DAR      |   |

|          | - |

|          | - |

| DCR      | - |

| DEC 5-5  | - |

| DIV      | 0 |

| DOL      | 1 |

| DOR      | 2 |

| ENT      |   |

|          |   |

| HLT      |   |

| INC      |   |

| IO       | 4 |

| ЮН       | 5 |

| IOLD     | 6 |

| JMP      | - |

| LAB      |   |

|          |   |

| LB       |   |

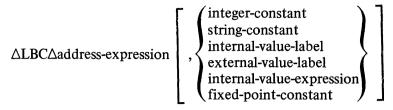

| LBC 5-5  | 8 |

| LBF      | 9 |

| LBS      | 0 |

| LBT      | 1 |

| LDB      | _ |

|          | - |

| LDH      |   |

| LDI      | - |

| LDR      | 3 |

| LDV      | 4 |

| LEV      | 4 |

| LLH      | - |

| * 1 * 7  | - |

|          |   |

| MCL      |   |

| MLV      | 7 |

| MTM      | 8 |

| MUL      | 9 |

| NEG      | - |

| NOP      |   |

|          |   |

| OR       | - |

| ORH 5-7  |   |

| RSTR 5-7 | 2 |

| RTCF     | 3 |

| RTCN     |   |

| RTT      |   |

|          |   |

| SAD      | + |

| SAL                                         | 5-75       |

|---------------------------------------------|------------|

| SAR                                         |            |

| SAVE                                        |            |

| SBE                                         |            |

|                                             |            |

|                                             |            |

| SBEZ                                        |            |

| SBG                                         | . 5-78     |

| SBGE                                        | . 5-79     |

| SBGEZ                                       | . 5-79     |

| SBGZ                                        | . 5-80     |

| SBL                                         | . 5-80     |

| SBLE                                        | . 5-81     |

| SBLEZ                                       | . 5-81     |

| SBLZ                                        | . 5-82     |

| SBNE                                        | 5-82       |

| SBNEU                                       |            |

| SBNEZ                                       |            |

| SBNPE                                       |            |

| SBNSE                                       |            |

|                                             |            |

|                                             |            |

| SBSE                                        |            |

| SCL                                         |            |

| SCR                                         |            |

| SCM                                         | . 5-87     |

| SCZD                                        | . 5-88     |

| SCZQ                                        | . 5-89     |

| SDI                                         | . 5-89     |

| SDV                                         | 5-90       |

| SLD                                         | . 5-91     |

| SML                                         | 5-92       |

| SNGD                                        | 5-93       |

| SNGO                                        | 5-93       |

| SOL                                         | 5-94       |

| SOR                                         | 5-94       |

| SRM                                         | 5-95       |

| SSB                                         | 5-95       |

| SSD SSD SST SST SST SST SST SST SST SST     |            |

|                                             |            |

| SSW                                         |            |

| STB                                         |            |

| STH                                         |            |

| STM                                         |            |

| STR                                         |            |

| STS                                         |            |

| SUB                                         |            |

| SWB                                         |            |

| SWR                                         | 5-102      |

| WDTF                                        | 5-103      |

| WDTN                                        |            |

| ХОН                                         |            |

| XOR                                         |            |

| 24042 · · · · · · · · · · · · · · · · · · · | 5 101      |

| Section 6. Macro Facility                   | 6-1        |

| Order of Statements Within a                | <b>~</b> • |

| Source Module                               | 6-1        |

|                                             | 0-1        |

| Macro Routines                     |     |

|------------------------------------|-----|

| Creating a Macro Routine           | -2  |

| MAC Macro Control Statement,       |     |

| Without Parameters                 |     |

| Contents of Macro Routine6         | -2  |

| ENDM Macro Control                 |     |

| Statement 6                        | -2  |

| Constallation Manuel Densting Inc. |     |

| Parameter Substitution             | -2  |

| MAC Macro Control Statement,       |     |

| Including Parameters               | -3  |

| Protection Operators               |     |

| Situating Macro Routines           |     |

| LIBM Macro Control                 |     |

| Statement                          | -6  |

| Macro Calls                        |     |

| Nested Macro Call                  |     |

| Recursive Macro Call               |     |

| Controlling Expansions             |     |

| Macro Variables                    |     |

| SETA Macro Control                 |     |

| Statement                          | -9  |

| Apostrophes Within                 |     |

| SETA Statements6                   | -10 |

| SETN Macro Control                 |     |

| Statement                          | -10 |

| Conditional Macro Control          |     |

| Statements                         | -11 |

| FAIL Macro Control                 |     |

| Statement                          | -12 |

| GO TO Macro Control                |     |

| Statement                          | -12 |

| IF Macro Control                   |     |

| Statement                          | -12 |

| NULL Macro Control                 |     |

| Statement                          | -15 |

| Macro Functions                    |     |

| Format of Macro                    | 10  |

| Functions                          | -16 |

| First Argument                     |     |

| Middle Argument                    |     |

| Last Argument                      | .17 |

| Length Attribute Macro             | 1,  |

| Function                           | -17 |

| Hexadecimal Conversion Macro       | • ' |

| Function                           | -17 |

| Index Macro Function               |     |

| Search Macro Function              |     |

| Substring Macro Function           |     |

| Vector Orientation Macro           | • / |

| Function                           | .20 |

|                                    |     |

### Page

| Verify Macro Function                |  |

|--------------------------------------|--|

| Facility                             |  |

|                                      |  |

| Macro Variables                      |  |

| Designating Numeric Values           |  |

| Designating Alphanumeric Values 6-25 |  |

| Appendix A. Programmer's Reference   |  |

| Information A-1                      |  |

| Summary of Hardware Registers A-1    |  |

| Assembly Language Internal           |  |

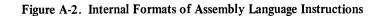

| Formats by Type A-4                  |  |

| Hexadecimal Representation of        |  |

| Instructions A-5                     |  |

| Valid Address Expressions A-9        |  |

| -                                    |  |

| Appendix B. Hexadecimal Numbering    |  |

| System B-1                           |  |

| Decimal-to-Hexadecimal               |  |

| Conversion B-2                       |  |

| Hexadecimal-to-Decimal               |  |

| Conversion B-2                       |  |

| Hexadecimal-to-ASCII                 |  |

| Conversion B-4                       |  |

| Hexadecimal Addition B-6             |  |

| Hexadecimal Subtraction B-7          |  |

| Hexadecimal Multiplication B-7       |  |

| Hexadecimal Division B-8             |  |

| Appendix C. Sample Assembly Language |  |

| Program C-1                          |  |

|                                      |  |

| Appendix D. Debugging Assembly       |  |

| Language Programs D-1                |  |

| Debugger D-1                         |  |

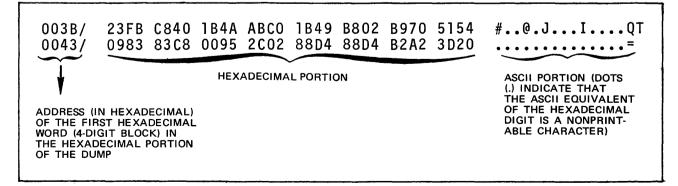

| Reading and Interpreting Memory      |  |

| Dumps D-1                            |  |

| 2 umps 2 1                           |  |

| Appendix E. Source Code Error        |  |

| Notification by                      |  |

| Assembler E-1                        |  |

|                                      |  |

| Appendix F. Source Code Error        |  |

| Notification by Macro                |  |

| Preprocessor F-1                     |  |

|                                      |  |

| Appendix G. Reserved Symbolic        |  |

| Names G-1                            |  |

|                                      |  |

# **ILLUSTRATIONS**

| Figure         | Page                                                     |

|----------------|----------------------------------------------------------|

| 1-1.           | Assembler Functions                                      |

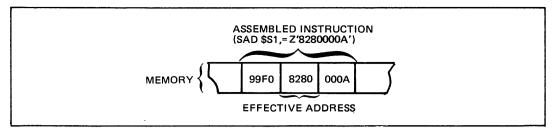

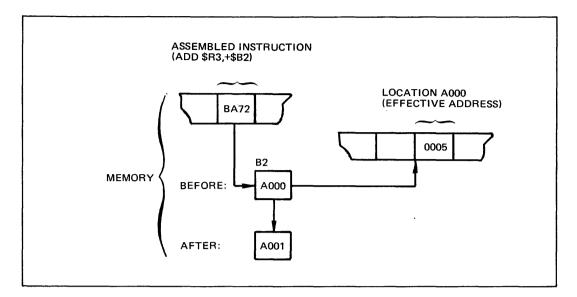

| 5-1.           | Direct Immediate Memory                                  |

|                | Addressing 5-8                                           |

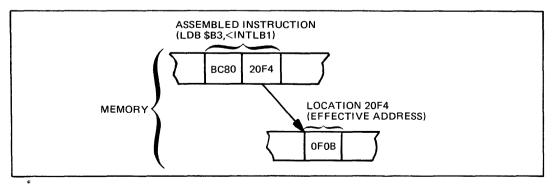

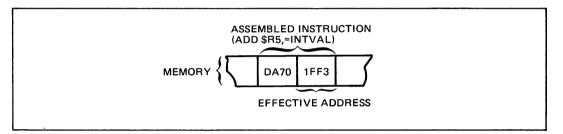

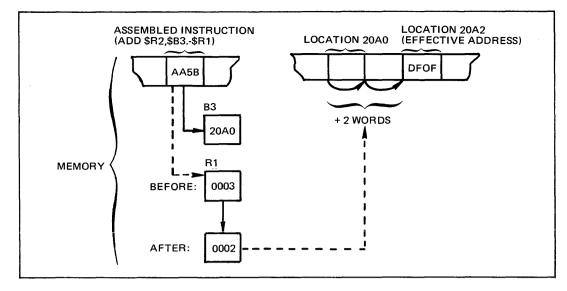

| 5-2.           | Indirect Immediate Memory                                |

|                | Addressing 5-9                                           |

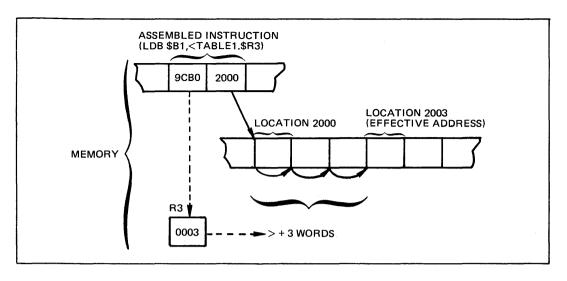

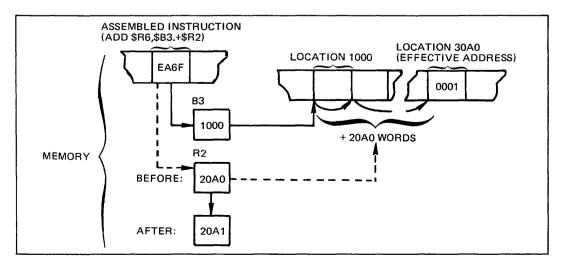

| 5-3.           | Indexed Direct Immediate                                 |

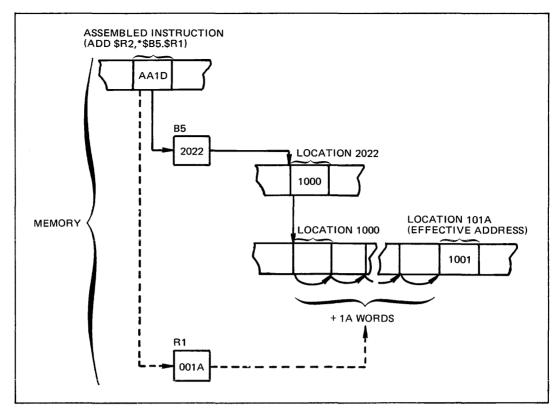

|                | Memory Addressing 5-10                                   |

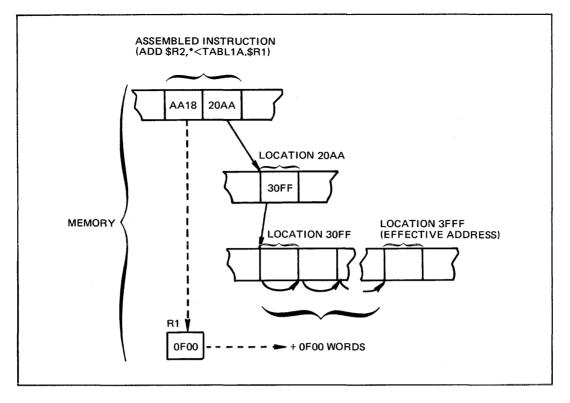

| 5-4.           | Indexed Indirect Immediate                               |

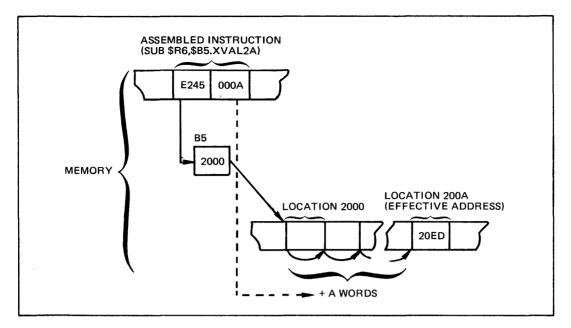

|                | Memory Addressing 5-11                                   |

| 5-5.           | Immediate Operand Addressing-                            |

|                | Scientific Instruction 5-12                              |

| 5-6.           | Immediate Operand Addressing 5-12                        |

| 5-7.           | Direct P-Relative Addressing 5-13                        |

| 5-8.           | Indirect P-Relative                                      |

|                | Addressing 5-13                                          |

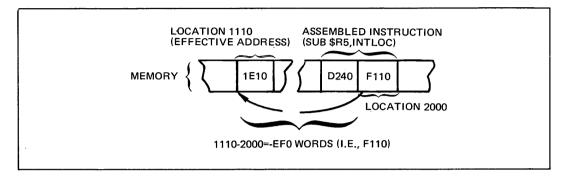

| 5-9.           | Direct B-Relative Addressing 5-15                        |

| 5-10.          | Indirect B-Relative                                      |

|                | Addressing                                               |

| 5-11.          | Indexed Direct B-Relative                                |

| C 1 0          | Addressing                                               |

| 5-12.          | Indexed Indirect B-Relative                              |

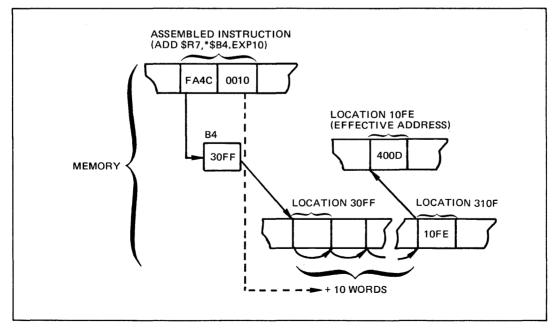

| 512            | Addressing                                               |

| 5-13.          | Direct B-Relative Plus                                   |

| 5-14.          | Displacement Addressing 5-18<br>Indirect B-Relative Plus |

| 5-14.          | Displacement Addressing 5-18                             |

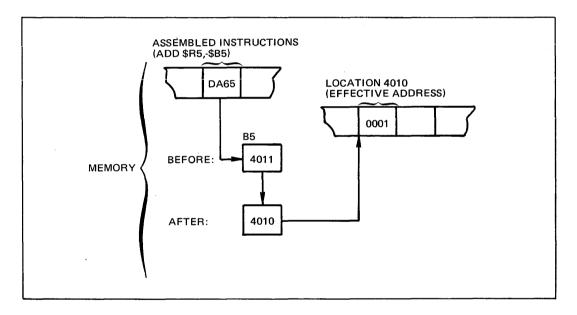

| 5-15.          | B-Relative Push Addressing 5-19                          |

| 5-16.          | B-Relative Pop Addressing 5-19                           |

| 5-10.<br>5-17. | Indexed B-Relative Push                                  |

| 5-17.          | Addressing                                               |

| 5-18.          | Indexed B-Relative Pop                                   |

| 5-10.          | Addressing                                               |

| 5-19.          | Short Displacement Addressing                            |

| 5-20.          | Specialized Address                                      |

| J-20.          | Expressions                                              |

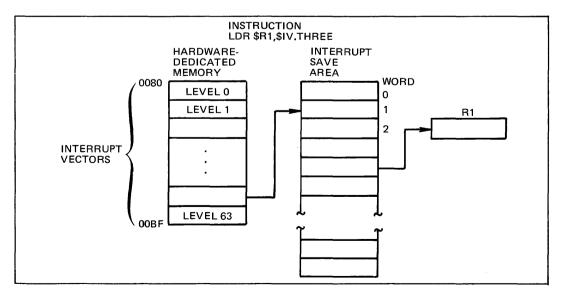

| 5-21.          | Interrupt Vector Addressing 5-23                         |

| 6-1.           | Sample Unexpanded Source Module                          |

| 01.            | and Assembler Listing of Resulting                       |

|                | Expanded Source Module 6-22                              |

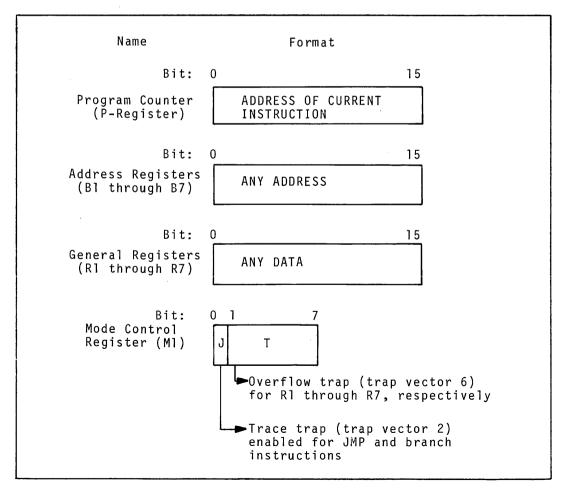

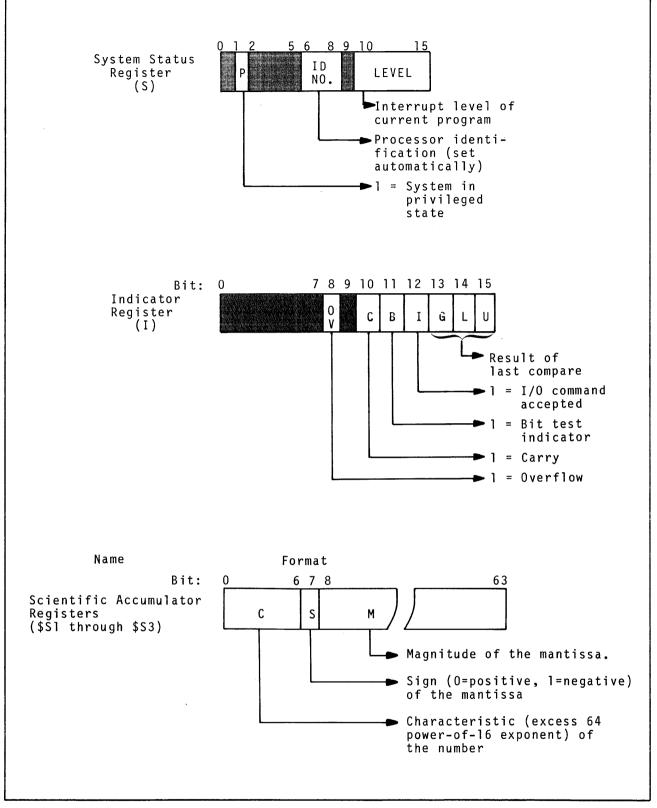

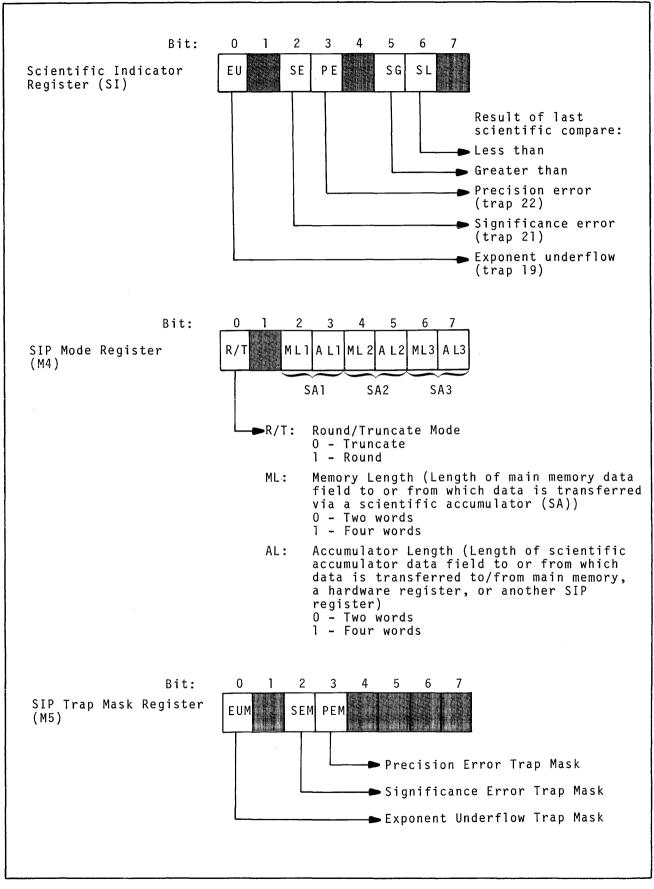

| A-1.           | Level 6 Hardware Registers A-1                           |

| A-2.           | Internal Formats of Assembly                             |

|                | Language Instructions A-4                                |

| D-1.           | ASCII/Hexadecimal Memory                                 |

|                | Dump D-1                                                 |

# TABLES

| Table        |                                                                 | Page        |

|--------------|-----------------------------------------------------------------|-------------|

| 2-1.         | Defining BES Symbolic<br>Names                                  | . 2-3       |

| 2-2.         | Rules of Truncation/Padding<br>String Constants                 | . 2-5       |

| A-1.         | Internal Representation of<br>Assembly Language<br>Instructions | A-5         |

| A-2.         | Address Syllables                                               |             |

| A-3.         | Summary of Valid Forms<br>of Address Expressions                |             |

| B-1.         | Comparison of Binary,<br>Decimal, and Hexadecimal<br>Symbols    |             |

| <b>B-2.</b>  | Storage and Printout of the Value 32                            |             |

| B-3.         | Hexadecimal/Decimal<br>Conversion                               |             |

| B-4.         | Hexadecimal/ASCII                                               |             |

| D 7          | Conversion                                                      | B-5         |

| B-5.<br>B-6. | Hexadecimal Addition Table<br>Hexadecimal Multiplication        | <b>B-</b> 6 |

|              | Table                                                           | <b>B-</b> 7 |

# SECTION 1 INTRODUCTION

Computer programs can be written in high-level languages or machine-oriented lower level languages. High-level languages are generally designed for specific environments (e.g., COBOL is a business-oriented language, and FORTRAN is a scientifically-oriented language). Low-level languages (i.e., assembly languages) support a wide range of application environments.

#### ASSEMBLY LANGUAGES

Computer logic is designed to interpret only machine (i.e., object) code. Since object code is composed of binary digits, it is difficult to interpret unless the binary representation is translated into a more convenient, readable code. As a result, assembly languages have been developed to simplify the problem of writing programs in object code. These intermediate-level assembly languages consist of assemblercontrolling statements and operational instructions.

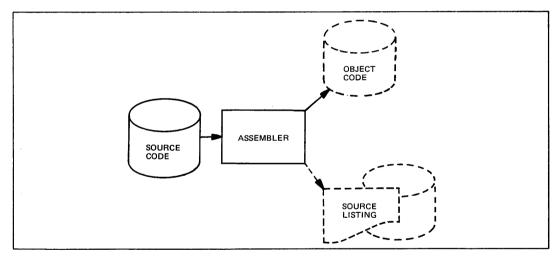

As illustrated in Figure 1-1, an assembler interprets the assembly language (i.e., source code) program and translates it into object code, which the computer executes to produce the desired results.

Figure 1-1. Assembler Functions

One of the primary differences between assembly languages and high-level languages is that each assembly language instruction is equivalent to a single machine-level instruction, whereas a single high-level language instruction can be translated into any number of machine-level instructions. The advantage, then, is that the assembly language gives you more control over the operations to be performed.

#### LEVEL 6 DATA REPRESENTATION

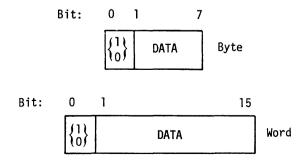

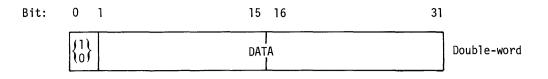

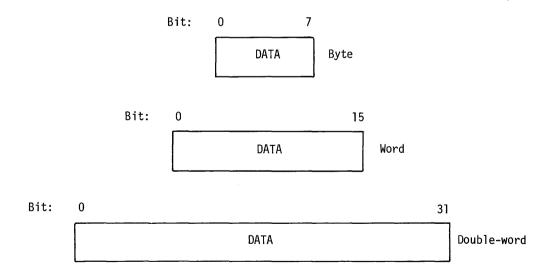

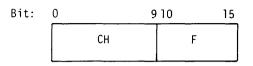

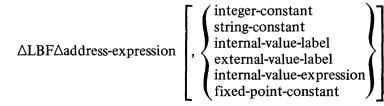

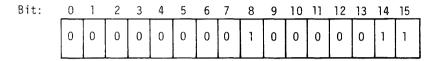

All data stored in main memory must be in predefined, system-recognizable formats. All data elements are based on 16-bit memory words. The format of each word is defined from left to right, with the first bit numbered 0 and the last 15. The leftmost bit (i.e., bit 0) is considered the most significant and the rightmost (i.e., bit 15) is the least significant, with each intervening bit less significant than the one to its left.

Because of this predefined format, it is possible to access data at any of the following levels:

- o Bit 1 bit

- o Byte (half-word) 8 bits

- o Word 16 bits

- o Multiword 32, 64 bits

Regardless of the size of the data item being accessed, addresses generated by the operand(s) in an instruction point to the most significant bit of the item. For example, to access a multiword data item in main memory, the address generated by the Assembler (from the operand contained in the instruction) points to the first bit (i.e., bit 0) in the first word of the item.

The system supports a maximum of 128K bytes (i.e., 64K words) of addressable memory, and each word can be accessed through a 16-bit address pointer.

Each four bits of data are represented by a single hexadecimal value in a listing or printout, although the bits are stored in memory in binary form. The hexadecimal equivalent of a binary value is derived by converting each successive four bits to the hexadecimal value as follows:

| 0000 = 0 | 1000 = 8 |

|----------|----------|

| 0001 = 1 | 1001 = 9 |

| 0010 = 2 | 1010 = A |

| 0011 = 3 | 1011 = B |

| 0100 = 4 | 1100 = C |

| 0101 = 5 | 1101 = D |

| 0110 = 6 | 1110 = E |

| 0111 = 7 | 1111 = F |

|          |          |

Thus, if a listing shows that a word at a given address contains the hexadecimal value 8FD3, it means that the system contains the stored binary value 1000111111010011.

Data stored in memory can be in any of the following forms:

- o Signed integer

- o Unsigned integer

- o Floating-point

A signed or unsigned integer byte can also be stored in a hardware general register. A floating-point constant occupies two (short-precision) or four (long-precision) memory words and may also be stored in the software-simulated scientific register.

#### **Signed Integer Data**

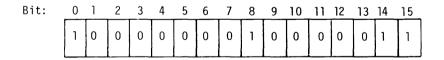

Signed integers stored in memory contain a sign (0 = +; 1 = -) in bit 0 and the data in the remaining bits. Negative numbers appear in twos-complement form. Byte, word, and double-word formats are permitted, as follows:

If the first digit in the hexadecimal representation of a signed integer is 0 through 7, the value is positive and is stored in memory exactly as it was coded; if the first digit is 8 through F, the value is negative and is stored in memory as the twos complement of the coded integer. For example, if the contents of a signed integer word appearing in memory are BDA0, the decimal equivalent is -12640.

When a signed integer byte is loaded from memory into a hardware general register, the seven data bits are placed into bits 9 through 15 of the register and the sign into bit 8. The sign is then extended through bit 0 of the register, as follows:

The sign of the integer byte (i.e., the first bit of the 8-bit byte), which is contained in bit 8 of the register, is extended through the first byte of the register.

If the first byte of the register contains the hexadecimal value FF, the integer in the second byte is a negative value; if the first byte contains the hexadecimal value 00, the value of the second byte is positive.

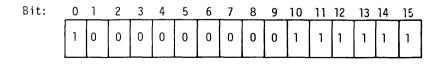

#### **Unsigned Data**

Unsigned data appears in memory in three possible formats:

When an unsigned data byte is loaded from memory into a hardware general register, the byte is placed into register bits 8 through 15, and register bits 0 through 7 are set to 0, as follows:

#### **Floating-Point Data**

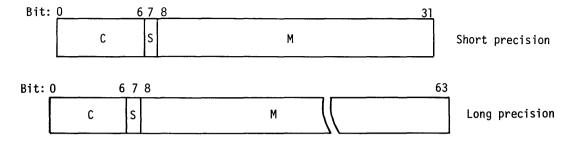

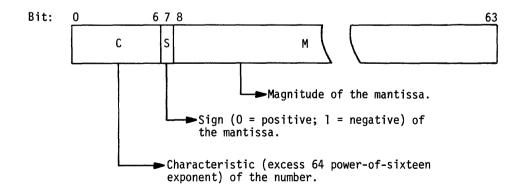

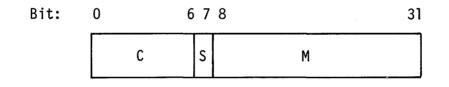

Floating-point data appears in memory either as a short-precision (32-bit) or long-precision (64-bit) constant, as follows:

С

Represents the characteristic (excess 64 power-of-16 exponent) of the number. The characteristic represents exponents with a range from -64 to +63. Since the characteristic has no sign bit, the number 64 (decimal) is effectively added to each exponent, thus allowing a characteristic range of 0 to 127 to represent exponents with a range of -64 to +63.

#### S

Sign bit (0 = +; 1 = -) of the mantissa.

#### Μ

Magnitude of the mantissa.

A floating-point constant in memory may be loaded into the software-simulated scientific register, described later in this section. If the floating-point constant had been specified as long-precision, the low-order (rightmost) 32 bits are ignored during the loading process.

#### **LEVEL 6 HARDWARE CONSIDERATIONS**

#### Hardware Registers

Level 6 provides hardware registers that can be loaded or read by various assembly language instructions. Of these registers, one is the program counter, seven are address registers, seven are general registers (of which three double as index registers), one is a mode control register, one is a system status register, and one is an indicator register.

#### Program Counter (P) Register

The program counter, or P-register, contains the address of the currently executing instruction. It is used by the Central Processor to generate the effective address of data based upon various operands in the assembly language instruction set (see "Addressing Techniques" in Section 5). Its content can be modified only by the JMP and branch instructions. If necessary, you can refer to the P-register for the address of the instruction that caused the system to abort a program. For this purpose, the contents of the P-register can be displayed at the control panel.

#### Address (Bn) Registers

The seven address registers can be used in the formulation of addresses by pointing to any procedure, data, or location in main memory. Typically, the address registers contain addresses, pointers, or base references for use in generating effective addresses and referring to data through relative addresses (see "Addressing Techniques" in Section 5).

#### General (Rn) Registers

The seven general registers can be used as accumulators, and the first three (R1, R2, R3) can be used as index registers (see "Addressing Techniques" in Section 5).

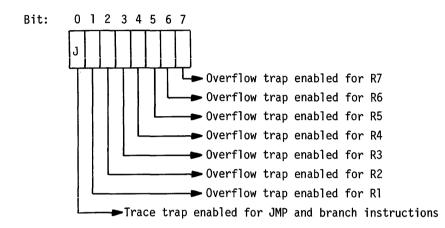

#### Mode (M1) Register

The mode, or M1, register contains the trap enable control bits. Its contents can be altered by the MTM assembly language instruction, and used by other instructions in the assembly language instruction set. The bits in the mode control register have the following meanings when set to binary 1:

Setting one or more overflow trap bits makes it possible to enter the Trace Trap Handler by a trap-to-trap vector 6. See the Executive and Input/Output manual for a detailed description of trap handlers.

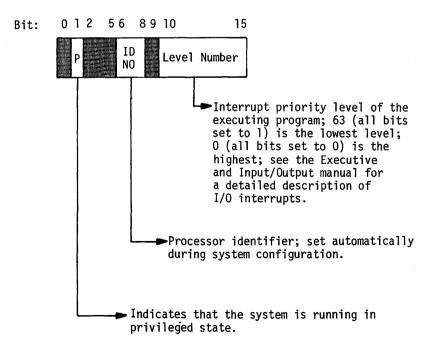

#### System Status (S) Register

The S-register contains the status and security bits for the system. The contents, which can be read by an executing program, have the following meaning, depending on which bits are set to binary 1:

#### Indicator (I) Register

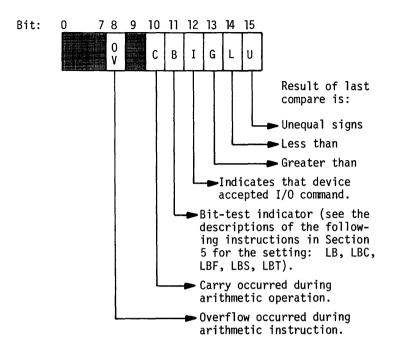

The I-register contains overflow and program status indicators. When set to binary 1, the bits have the following meaning:

#### Scientific Information Processor (SIP) Registers

The Level 6 Scientific Information Processor (SIP) is an optional hardware unit containing three identical scientific accumulator registers, one scientific indicator register, one SIP mode register, and one SIP trap mask register. The SIP performs arithmetic operations on single- and double-precision floating-point data and also provides a set of scientific branch instructions.

#### Scientific Accumulator (Sn) Registers

The SIP provides three 64-bit scientific accumulator registers for use in either shortor long-precision floating-point operations. When these registers are used in shortprecision operations, only the high-order (leftmost) 32 bits participate.

The format of the scientific accumulator registers is shown below.

#### Scientific Indicator (SI) Register

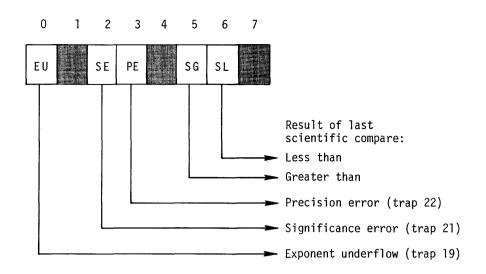

The 8-bit SI-register contains error and status indicators that can be tested with the scientific branch instructions. When set to binary 1, the bits have the following meanings:

Traps and trap handlers are discussed in the Executive and Input/Output manual.

#### SIP Mode (M4) Register

The SIP mode, or M4, register is an 8-bit control register residing in the SIP but with a copy in the CPU. Both versions are set to 0 upon CPU initialization and both may be modified with an MTM instruction (see Section 5). If only the SIP is initialized, the CPU copy of the register is cleared, and the contents of both versions must be reestablished with an MTM.

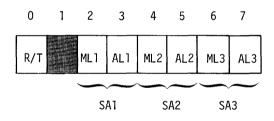

The format of the M4-register is as follows:

- R/T: Round/Truncate Mode

- 0 Truncate

- 1 Round

ML: Memory Length (Length of main memory data field to or from which data is transferred via a scientific accumulator (SA))

- 0 Two words

- 1 Four words

AL: Accumulator Length (Length of scientific accumulator data field to or from which data is transferred to/from main memory, a hardware register, or another SIP register)

- 0 Two words

- 1 Four words

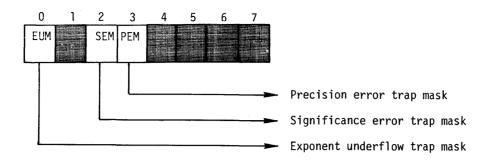

#### SIP Trap Mask (M5) Register

The SIP Trap Mask, or M5, register is an 8-bit control register residing in the SIP but with a copy in the CPU. Both versions are set to 0 upon CPU initialization and both may be modified with an MTM instruction (see Section 5). If only the SIP is initialized, the CPU copy of the register is leared, and the contents of both versions must be reestablished with an MTM.

The format of the M5-register is as follows:

#### Software Simulation of the Scientific Information Processor

For Level 6 systems on which a Scientific Information Processor (SIP) is not installed or available, BES provides a limited equivalent of the SIP functions through software simulation. Two trap handlers, the Floating-Point Simulator, entered via trap vector 3, and the Scientific Branch Simulator, entered via trap vector 5, are available. These two simulators are described in the Executive and Input/Output manual.

The Floating-Point Simulator and Scientific Branch Simulator provide the same functions as the SIP, with the following differences:

- o Only one scientific accumulator register (S1) is supported.

- o Only short-precision floating-point operations may be performed.

- o General registers R4, R5, and R7 must be reserved for use by the simulators while they are executing.

- o Since, in the absence of an SIP, no SI-register is available, the simulators use the G, L, and U bits of the I-register for scientific compares.

- o Not all SIP instructions are simulated. See "Assembly Language Instructions" in Section 5 to determine whether or not an individual instruction is available with one of the simulators.

# **SECTION 2**

# ELEMENTS OF BES ASSEMBLY LANGUAGE

The principal elements of the BES assembly language are:

- o Mnemonic codes

- o Symbolic names

- o Constants

- o Expressions

These elements are combined to form a source program that consists of:

- 1. Machine instructions to be assembled, on a one-to-one basis, into their corresponding object code representations.

- 2. Assembler control statements which are interpreted by the Assembler to control the assembly process, allocate work and storage areas in memory, and to define constant data used by the program.

#### **MNEMONIC CODES**

Assembler control statements, which direct the Assembler in the preparation of object code, and assembly language instructions are specified by predefined mnemonic names of one to five characters in length. These mnemonic (operation) codes are described, in detail, in Sections 4 and 5.

#### SYMBOLIC NAMES

Locations, values, and other data pertinent to the determination of assembly language instruction or Assembler control statement operand values can be referred to by the use of reserved (predefined) and user-defined names.

Character strings can be assigned as names of memory locations, registers, values, or other objects to be referred to in the development of object code. The manner in which a symbolic name is defined depends on the attributes of the object referred to by that name.

Regardless of the manner of definition and the type of object being referred to, the symbolic name must conform to the following rules:

- 1. It must be from one to six characters long.

- 2. It must be composed of alphabetic characters (A,B,...Z), digits (0,1,...9), and/or the special characters \$ and -(underscore).

- 3. The first character must be a \$ or alphabetic character.

The following types of symbolic names can be used in Assembler control statements and assembly language instructions:

- o Identifiers Reserved symbols designating the hardware registers and the scientific register

- o Labels User-defined and reserved symbols designating locations in memory and values

#### Identifiers

Identifiers are reserved symbolic names that refer to hardware registers or to the software-simulated scientific register. In addition, names that are defined to be equivalent to identifiers (through the EQU Assembler control statement) are treated as identifiers.

The following identifiers refer to hardware registers:

- o \$B1 through \$B7 Address (base) registers

- o \$R1 through \$R7 General registers

- o \$R1 through \$R3 Index registers

- o \$M1 through \$M7 Mode control registers

- o \$S1 through \$S3 Scientific accumulator registers

#### Labels

Labels are symbolic names that can be used to refer to locations and values. They must be defined in a manner specific to the attributes of the location or value to which they refer (i.e., each label is typed according to the location or value attributes, which also establish the context in which they can be used). The types of labels and their methods of definition are as follows:

- o Internal location label Refers to a location allocated within the assembled program. It is defined by its occurrence in the label field of an instruction (resulting in the allocation of memory to the program). The definition of labels appearing in certain Assembler control statements that do not cause memory to be allocated (e.g., EQU statement) depend on the statement and its operands.

- o External location label Refers to a location in another, independently assembled program. It is defined by appearing in the operand list of an XLOC statement.

- o Common location label Refers to a location allocated to FORTRANcompatible common blocks. It is possible to specify that the object code resulting from assembly language instructions is to be allocated to a common block area rather than to the area allocated to the program by means of the ORG statement. All labels that appear in instructions that result in the allocation of common block locations are defined as common location labels. In addition, labels specified in the COMM statement are defined as common block by indicating these labels can be used to refer to locations in the common block by indicating their offset from the first word.

- o Internal value label Refers to a value defined within the program. It is assigned by its occurrence in the label field of an EQU statement with an operand expression (see "Expressions" in this section) that yields a scalar value.

- o External value label Refers to a value defined in another, independently assembled program. It is defined by appearing in the operand list of an XVAL statement.

- o Complex label Refers to the label of an EQU statement that has an address expression (see "Expressions" in this section), or the label of another EQU statement that has an address expression, in the operand field.

Table 2-1 summarizes the types of labels and how they are defined.

#### User-Defined Labels

User-defined labels can be either permanent or temporary. Permanent labels can be defined only once in a program; they must conform to the rules listed under "Symbolic Names" in this section.

The 26 temporary labels (A, B, ..., Z) may be defined as often as necessary within a single program. They may be referred to only in the operand of a hardware instruction or of a define constant (DC) assembly control statement. You must be

careful, during programming, that you are referring to the desired definition of a temporary label when the label has multiple definitions within a single program.

Temporary labels must be defined as internal location labels.

#### **Reserved** Labels

Reserved labels are predefined and cannot be redefined by the user. The following reserved labels are available:

- o \$ Refers to the location to be allocated as a result of the statement in which it appears as a reference (i.e., the current location). It can be either an internal location or common location label type.

- o \$AF Refers to the address form of the system configuration. A value of 1 indicates that the system configuration is the short-address form configuration; a 2 indicates a long-address form configuration. \$AF is an internal value label.

- o \$IV Refers to the address of the interrupt vector for the priority level at which the application is currently executing. A description of interrupt vectors and priority levels can be found in the Executive and Input/Output manual.

| Туре                    | How Defined                                                                                                                                                                                                                                                                              |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal location label | Appears in label field of an assembly language instruction or<br>Assembler control statement (except EQU or COMM<br>statements) when the location counter type attribute (set<br>by the ORG statement) is internal.                                                                      |

| External location label | Appears in the operand field of an XLOC statement.                                                                                                                                                                                                                                       |

| Common location label   | Appears in the label field of a COMM statement; or appears<br>in label field of an assembly language instruction or<br>Assembler control statement (except EQU or COMM<br>statements) when the location counter type attribute (set<br>by the ORG statement) is common.                  |

| Internal value label    | Appears in label field of an EQU statement that has an expression that yields a scalar arithmetic value in the operand field.                                                                                                                                                            |

| External value label    | Appears in the operand field of an XVAL statement.                                                                                                                                                                                                                                       |

| Complex label           | Appears in the label field of an EQU statement that<br>contains an address expression in the operand field; or<br>appears in the label field of an EQU statement that contains<br>a label identifying another EQU statement that contains an<br>address expression in the operand field. |

| Same as operand         | Appears in the label field of an EQU statement that contains an operand other than one of those listed above; e.g., an identifier.                                                                                                                                                       |

#### TABLE 2-1. DEFINING BES SYMBOLIC NAMES

#### CONSTANTS

Arithmetic and nonarithmetic values can be expressed in decimal, hexadecimal, character, or binary form, all of which are converted by the Assembler to the appropriate machine code format. Depending on the context, such values may be assigned as object code or be used by the Assembler in the computation of operand locations or values.

The following types of constants are supported:

- o String constants

- o Arithmetic constants

#### **String Constants**

String constants can be expressed as ASCII, hexadecimal, or bit strings. Regardless of how they are expressed, string constants have the following format:

$$[(n)] \quad \begin{cases} \frac{A}{Z} \\ B \end{cases} c[c...]'$$

[(n)]

Specifies an optional decimal integer in the range from 1 to 255, which represents the replication factor (number of times the coded string is to be repeated.

Specifies whether the string is expressed in ASCII (A; default if none of these values is specified), hexadecimal (Z), or bit (B).

#### 'c[c...]'

Identifies the character(s) in the string; to include an apostrophe, a double apostrophe must be specified (i.e., " is interpreted as ').

String constants are left-justified.

#### **ASCII String Constants**

An ASCII string constant is written as the letter A (optionally) followed by a string of any of the valid ASCII characters enclosed within apostrophes.

An ASCII string constant denotes the value formed by replacing all double apostrophes by a single apostrophe and removing the delimiting apostrophes.

The value of an ASCII string constant cannot be more than 255 ASCII characters (each of which is eight bits long).

The format of an ASCII string constant is as follows:

[(n)] [A]'a[a...]'

The following examples illustrate how to specify ASCII string constants:

1. 'ASCII SAMPLE1'

2. A'ASCII SAMPLE2'

3. (4)A 'DATA∆'

The characters enclosed within the apostrophes can be any character shown in Table B-4. The examples shown above result in the following values being stored in memory, respectively:

1. ASCII SAMPLE1

2. ASCII SAMPLE2

3. DATA ΔDATA DATA DATA

#### Hexadecimal String Constants

A hexadecimal string constant is written as the letter Z followed by a string of any of the valid hexadecimal digits (i.e., 0 through F) enclosed within apostrophes.

A hexadecimal string constant denotes the value formed by replacing the characters contained within the delimiting apostrophes with their binary values and removing the delimiting apostrophes.

The value of a hexadecimal string constant cannot be more than 510 hexadecimal digits (each of which is four bits long).

The format of a hexadecimal string constant is as follows:

[(n)] Z'h[h...]'

The following example illustrates how to specify a hexadecimal string constant:

#### Z'5449544C452053414D504C4531'

This example translates into TITLE∆ SAMPLE1 (see Appendix B).

#### **Bit String Constants**

A bit string constant is written as the letter B followed by a string of binary digits (i.e., 0 and 1) enclosed within apostrophes.

A bit string constant denotes the value formed by converting the 0 and 1 characters contained within the delimiting apostrophes to 0 and 1 bits.

The value of a bit string constant cannot be more than 2040 binary digits (each of which is one bit long).

The format of a bit string constant is as follows:

[(n)] B'd[d...]'

The following example illustrates how bit string constants are expressed:

B'00011010'

This bit string provides an 8-bit mask that can be used by an assembly language instruction.

#### Truncation/Padding of String Constants

Various statements require a half-word (8-bit) value, whole-word (16-bit) value, or a value that is an integral number of words in length. In order to satisfy these requirements, string constants are automatically truncated or padded.

If truncation is required, low-order (i.e., the rightmost) bits are discarded, and the Assembler issues a diagnostic message.

If padding is required, low-order bits are appended to the value. ASCII string constants are padded with spaces; hexadecimal and bit strings are padded with 0's.

Table 2-2 describes how the Assembler handles the various situations that require truncation or padding.

| If a string constant appears:                                               | It is converted to:                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In a nontrivial arithmetic expression                                       | A whole-word value.                                                                                                                                                                                                                                                                                                              |

| As the only term of the operand of a short value immediate (SI) instruction | A half-word value.                                                                                                                                                                                                                                                                                                               |

| As the only term of an operand of a DC Assembler control statement          | A value having a length that is an integral<br>number of words; such string constants<br>are never truncated.                                                                                                                                                                                                                    |

| As the operand of a TEXT Assembler control statement                        | A string having an initial bit offset which<br>is a multiple of 4 (for hexadecimal string<br>constants) or a multiple of 8 (for ASCII<br>string constants) with slack bits inserted<br>between successive operands. A bit string<br>constant can begin at any bit position;<br>slack bits never precede a bit string<br>operand. |

| In any context not listed above                                             | A whole-word value.                                                                                                                                                                                                                                                                                                              |

#### TABLE 2-2. RULES OF TRUNCATION/PADDING STRING CONSTANTS

2. Refer to specific statements identified in this table for additional information.

#### **Arithmetic Constants**

An arithmetic constant specifies the value of a real number. An arithmetic constant is either an integer constant, fixed-point constant, or a floating-point constant.

#### Integer Constants

Integer constants can be expressed as decimal or hexadecimal integers. They may be preceded by a plus (+) or minus (-) sign, indicating a positive or negative value, respectively, and must be within the range -32768 to +32767; if unsigned, an integer constant is assumed to be positive.

Integer constants have the following format:

```

+ n[n...]

- X'h[h...]'

```

+

Specifies whether the value is positive (+; the default value) or negative(-).

n[n...]

Is a decimal integer constant as defined below.

#### X'h[h...]'

Is a hexadecimal integer constant as described below.

#### Decimal Integer Constants

Decimal integer constants are expressed as character strings composed of the decimal digits 0 through 9.

The following examples illustrate valid decimal integer constants:

1. 31764

- 2. +4652

- 3. -6781

#### Hexadecimal Integer Constants

A hexadecimal integer constant is written as the letter X followed by a character string composed of the hexadecimal digits 0 through 9 and A through F enclosed within apostrophes.

The following examples illustrate hexadecimal integer constants:

1. +X'2F'

- 2. X'7FFF'

- 3. -X'8000'

Using Table B-3, you can see that the decimal equivalent of the above examples is +47, +32767, and -32768, respectively.

#### Fixed-Point Constants

A fixed-point constant is written as a decimal number with an associated scale factor. When the resultant value is stored in memory, a fixed-point constant appears as a signed integer word with negative values in twos complement form. The scale factor (s) gives the location of the implied binary point in the stored constant. A positive scale factor means that the point is situated s bits to the left of the rightmost bit stored in memory. A negative scale factor means that the point is situated s bits to the right of the rightmost bit stored in memory. Thus, a fixed-point value can be considered to be written as the product formed by multiplying the decimal number by  $2^{\text{S}}$ .

Fixed-point constants have the following format:

$$\begin{bmatrix} + \\ - \end{bmatrix} \left\{ \begin{bmatrix} i & [.[f]] \\ [i] & f \end{bmatrix} \right\} B \begin{bmatrix} + \\ - \end{bmatrix} s$$

[±]

Specifies the sign of the constant. The + sign may be omitted.

i

Specifies the integer part of the decimal number.

f

Specifies the fractional part of the decimal number.

[±]s

Specifies the value and sign of the scale factor.

The value of a fixed-point constant must fall within the range

$2^{-S} \le |R| \le 2^{15-S}$

where R is the value of the decimal number.

The following examples illustrate how to specify fixed-point constants and show the hexadecimal representations of the resultant values in memory.

| Source Language | Stored Value |

|-----------------|--------------|

| 2.5B4           | 0028         |

| 2.5B8           | 0280         |

| 65536B-15       | 0002         |

| 65536B-7        | 0200         |

| -2.5B8          | FD80         |

| -65536B-15      | FFFE         |

#### Floating-Point Constants

BES assembly language provides a convenient method with which you can write a decimal number and have the Assembler convert it into floating-point format. (See Section 1 for a description of floating-point data.)

Two formats for writing floating-point constants are available:

Format 1

$$\begin{bmatrix} + \\ - \end{bmatrix} \left\{ \begin{array}{c} i \ .[f] \\ [i] \ .f \end{array} \right\}$$

SHORT PRECISION

Format 2

$$\begin{bmatrix} + \\ - \end{bmatrix} \begin{Bmatrix} i \cdot [f] \\ [i] \cdot f \end{Bmatrix} E \begin{bmatrix} + \\ - \end{bmatrix} c$$

SHORT PRECISION POWER-OF-10

[±]

Specifies the sign of the constant. The + sign may be omitted if desired.

i

Specifies the integer part of a decimal number.

f

C--

Specifies the fractional part of a decimal number.

Ε

Indicates that a short precision power-of-10 floating-point representation is desired.

#### ELEMENTS OF BES ASSEMBLY LANGUAGE

#### [±]c

Expresses the power of 10 by which the coded decimal number should be multiplied to produce the value wanted. The + sign may be omitted if desired.

NOTE: If the decimal point is omitted, the number is assumed to be an integer.

The absolute value of a floating-point constant must be greater than or equal to  $2^{-260}$  (approximately 3.3753 x  $10^{-80}$ ) and less than  $2^{252}$  (approximately 4.7428 X  $10^{80}$ ).

#### Normalization

Floating-point constants are stored as normalized hexadecimal floating-point numbers with a 7-bit excess 64 power-of-16 characteristic and a 25-bit signed magnitude mantissa. A normalized floating-point number has a nonzero high-order hexadecimal fraction digit. If one or more high-order fraction digits are zero, the number is said to be unnormalized. Normalization consists of shifting the fraction left until the high-order hexadecimal digit is nonzero and reducing the characteristic by the number of hexadecimal digits shifted.

#### Examples

The following examples illustrate how to specify floating-point constants and show the hexadecimal representations of the resultant values in memory. You can determine sign, characteristic, and mantissa of the resulting floating-point numbers by dividing the hexadecimal representations into parts according to the patterns described in Section 1.

| Source Language | Stored Value |

|-----------------|--------------|

| 0.5             | 8080 0000    |

| 0.5E12          | 9474 6A52    |

| 6.665039063E-2  | 8011 1000    |

| -6.665039063E-2 | 8111 1000    |

#### **EXPRESSIONS**

Expressions are combinations of symbolic names and constants used as operands within Assembler control and assembly language (machine) instructions. Expressions can represent locations (internal or external), values, and addresses. Components of an expression can be joined by various functions and arithmetic operators, as follows:

| Arithmetic Operator     | Meaning                  |

|-------------------------|--------------------------|

| +                       | Addition (or Unary +)    |

| -                       | Subtraction (or Unary -) |

| *                       | Multiplication           |

| /                       | Division                 |

| <b>Boolean Function</b> | Meaning                  |