#

#### LEVEL 6

SOFTWARE GCOS 6 ASSEMBLY LANGUAGE REFERENCE

# SERIES 60 (LEVEL 6) GCOS 6 ASSEMBLY LANGUAGE REFERENCE

#### SUBJECT

Detailed description of Series 60 (Level 6) GCOS 6 Assembly Language including:

- Central Processor Unit (CPU) Instructions

- Scientific Instruction Processor (SIP) Instructions

- Commercial Processor Instructions

- Assembler Control Statements

- Macro Control Statements and Macro Calls

#### SPECIAL INSTRUCTIONS

This manual supersedes CB07, Rev. 0 dated January 1978. Change bars indicate new and changed information; asterisks denote deletions.

#### SOFTWARE SUPPORTED

This publication supports Release 0110 of the Series 60 (Level 6) GCOS 6 MOD 400 Operating Systems; see the Manual Directory of the latest GCOS 6 MOD 400 *System Concepts* manual (Order No. CB20) for information as to later releases supported by this manual.

ORDER NUMBER

CB07, Rev. 1

June 1978

# Honeywell

### **Preface**

This manual describes the GCOS 6 assembly language, a machine-oriented language for writing programs to execute on the Series 60 (Level 6) models. In this manual, unless stated otherwise, the term GCOS refers to the GCOS 6 software; the term Level 6 refers to the Series 60 (Level 6) on which the described software is executed.

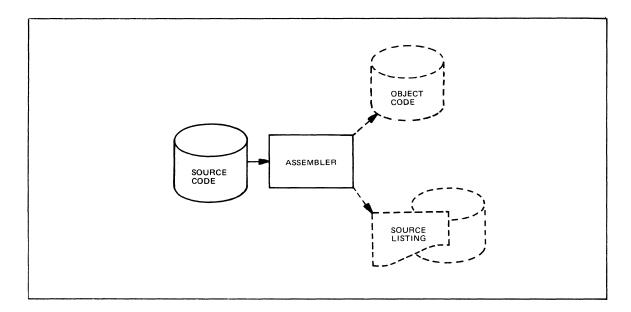

Where appropriate, the actions performed by the GCOS Assembler as it processes elements of the assembly language are also discussed. In this manual, the term assembly language includes both Assembler control statements and assembly language instructions.

Section 1 describes the data prepresentation and the hardware registers. Section 2 describes the basic elements of the GCOS assembly language, and Section 3 describes the considerations the programmer must make when writing a source program. Sections 4 and 5 describe, in detail, the Assembler control statements and assembly language instructions, respectively. Section 6 and Section 7 consist of detailed descriptions of the commercial instructions and the scientific instructions. The macro facility is described in Section 8. Appendix A provides programmer reference information. Appendix B describes the hexadecimal numbering system. Appendix C contains a sample assembly language program. Appendix D describes how to debug an assembly language program. Appendix E lists the flags that may be issued by the Assembler. Appendix F lists the error flags that may be issued by the Macro Preprocessor. Appendix G contains a list of reserved symbolic names. Appendix H provides reference information for Commercial Processor operation. Appendix J and Appendix K provide reference information for queue instructions and stack instructions, respectively.

Descriptions and examples within this manual use the following conventions:

- { } Indicates that one of the options enclosed in the braces must be selected.

- [] Indicates that one or none of the enclosed options need be selected; if one of the options is underlined, it is selected as the default if you do not select any of the options enclosed in the brackets.

- ... Indicates either a logical sequence (e.g., A,B...) or that the immediately preceding type of value can be repeated (e.g., a...).

- a Indicates that the character must be replaced by any valid ASCII character.

- n Indicates that the character must be replaced by any valid numeric (decimal) digit.

- d Indicates that the character must be replaced with a binary digit.

- h Indicates that the character must be replaced with a hexadecimal digit (0 through 9, A through F; the letters a through f are considered equivalent to the corresponding uppercase letters).

- c Indicates that the character must be replaced with a, n, or h, above.

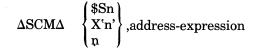

- $\Delta$  Indicates that one or more spaces or horizontal tab characters are required.

© 1978, Honeywell Information Systems Inc.

File No.: 1S23

**CB07**

Uppercase letters, numbers, and any of the following special characters must be coded exactly as shown (lowercase letters that represent keywords, however, are considered equivalent to the corresponding uppercase letters):

Users of the Writable Control Store feature should refer to the Writable Control Store User's Guide for information about the WCS instructions and the WCS Assembler, and to the GCOS 6 MOD 400 Operator's Guide for command information to invoke the WCS Loader.

#### MANUAL DIRECTORY

The following publications comprise the GCOS 6 manual set. The Manual Directory in the latest *GCOS 6 MOD 400 Systems Concepts* manual (Order No. CB20) lists the current revision number and addenda (if any) for each manual in the set.

#### Order

| Oraer       |                                                                   |

|-------------|-------------------------------------------------------------------|

| No.         | Manual Title                                                      |

|             | GCOS 6 Program Preparation                                        |

| CB02        | GCOS 6 Commands                                                   |

| -CB03       | GCOS 6 Communications Processing                                  |

|             | GCOS 6 Sort/Merge                                                 |

| CB05        | GCOS 6 Data File Organizations and Formats                        |

| <u> </u>    | GCOS 6 System Messages                                            |

|             | GCOS 6 Assembly Language Reference                                |

| CB08        | GCOS 6 System Service Macro Calls                                 |

| <b>CB09</b> | GCOS 6 RPG Reference                                              |

| CB10        | GCOS 6 Intermediate COBOL Reference                               |

| <u>CB20</u> | GCOS 6 MOD 400 System Concepts 🖌                                  |

| (CB21)      | GCOS 6 MOD 400 Program Execution and Checkout                     |

| -CB22       | GCOS 6 MOD 400 Programmer's Guide                                 |

| <u> </u>    | GCOS 6 MOD 400 System Building                                    |

| /CB24]      | GCOS 6 MOD 400 Operator's Guide                                   |

| CB25        | GCOS 6 MOD 400 FORTRAN Reference                                  |

| <b>CB26</b> | GCOS 6 MOD 400 Entry-Level COBOL Reference                        |

| CB27        | GCOS 6 MOD 400 Programmer's Pocket Guide                          |

| <b>CB28</b> | GCOS 6 MOD 400 Master Index                                       |

| <b>CB30</b> | Remote Batch Facility User's Guide                                |

| CB31        | Data Entry Facility User's Guide                                  |

| <b>CB32</b> | Data Entry Facility Operator's Quick Reference Guide              |

|             | Level 6/Level 6 File Transmission Facility User's Guide           |

| CB34        | Level 6/Level 62 File Transmission Facility User's Guide          |

| CB35        | Level 6/Level 64 (Native) File Transmission Facility User's Guide |

| CB36        | Level 6/Level 66 File Transmission Facility User's Guide          |

| CB37        | Level 6/Series 200/2000 File Transmission Facility User's Guide   |

| CB38        | Level 6/BSC 2780/3780 File Transmission Facility User's Guide     |

| CB39        | Level6/Level64(Emulator)FileTransmissionFacilityUser'sGuide       |

| CB40        | IBM 2780/3780 Workstation Facility User's Guide                   |

| CB41        | HASP Workstation Facility User's Guide                            |

| <b>CB42</b> | Level 66 Host Resident Facility User's Guide                      |

| CB43        | Terminal Concentration Facility User's Guide                      |

CB43 Terminal Concentration Facility User's Guide

In addition, the following documents provide general hardware information:

| Order |                                                 |

|-------|-------------------------------------------------|

| No.   | Manual Title                                    |

| AS22  | Honeywell Level 6 Minicomputer Handbook         |

| AT04  | Level 6 System and Peripherals Operation Manual |

| AT97  | MLCP Programmer's Reference Manual              |

| FQ41  | Writable Control Store User's Guide             |

# **Contents**

#### Section 1. Introduction

| Assembly Languages                                               | 1-1           |

|------------------------------------------------------------------|---------------|

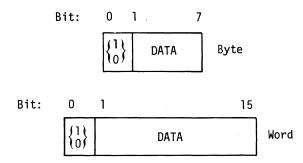

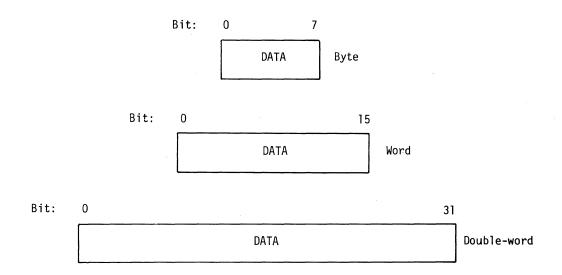

| Level 6 Data Representation                                      | 1-1           |

| Signed Integer Data                                              | 1-2           |

| Unsigned Data                                                    |               |

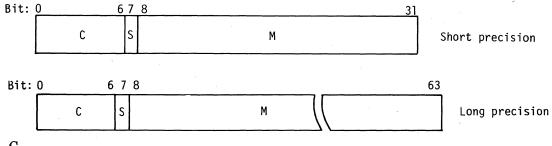

| Floating-Point Data                                              | 1-4           |

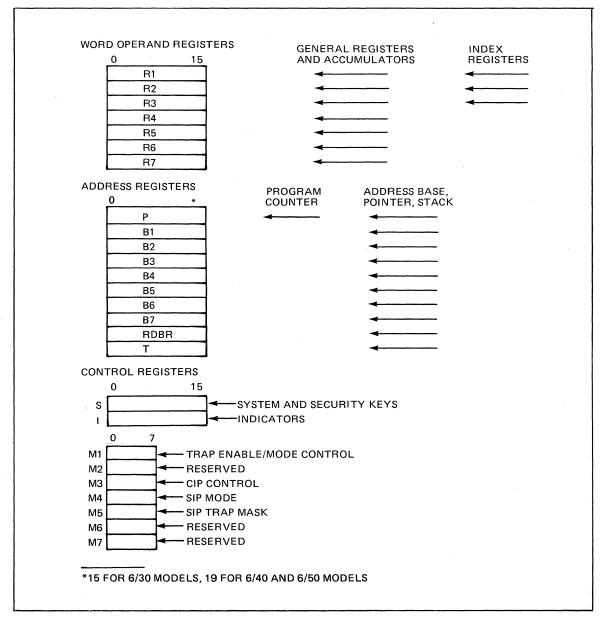

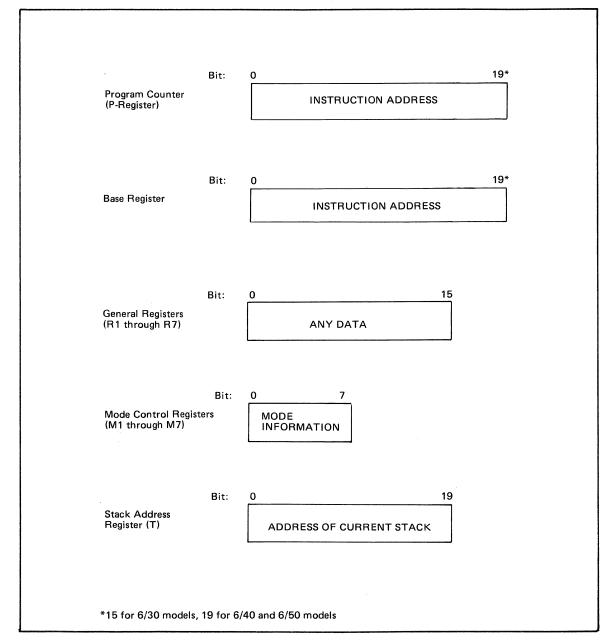

| Hardware Registers                                               |               |

| Address Registers                                                |               |

| Base Address (Bn) Registers                                      |               |

| Program Counter (P-Register)                                     | 1-4           |

| Remote Descriptor Base Register                                  |               |

| $(RDBR) \dots \dots \dots \dots \dots \dots \dots \dots$         | 1-4           |

| Stack Register (T)                                               | 1-5           |

| General (Rn) Registers                                           |               |

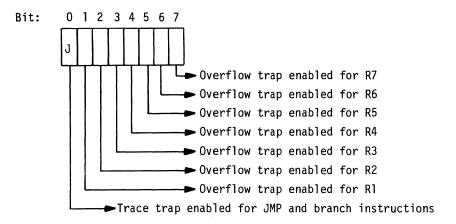

| Mode (M) Registers                                               | 1-5           |

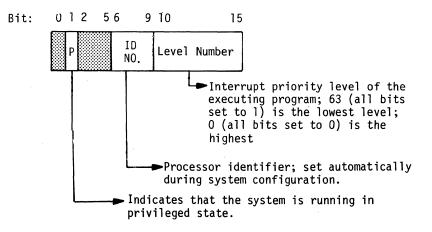

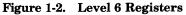

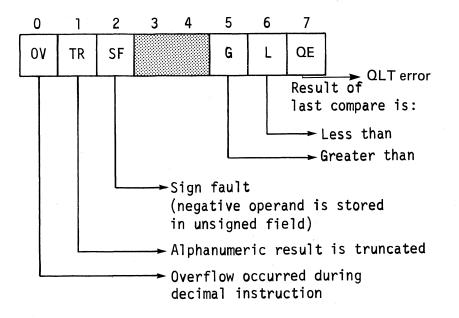

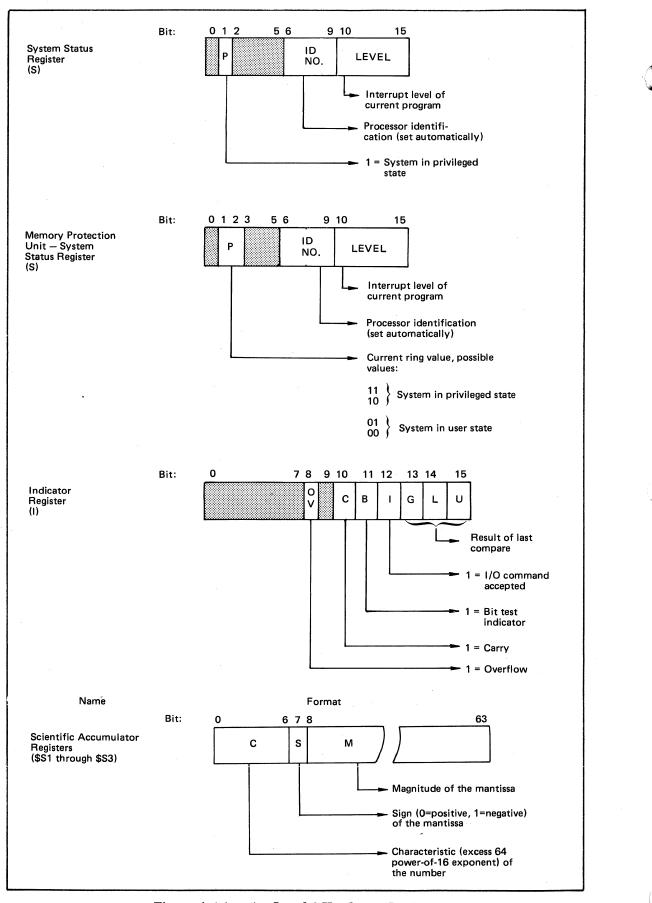

| System Status (S) Register                                       | 1-5           |

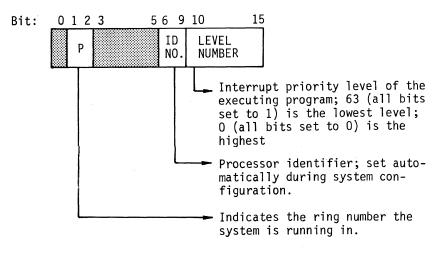

| Indicator (I) Register<br>Scientific Information Processor (SIP) | 1-7           |

| Scientific Information Processor (SIP)                           |               |

| Registers                                                        | 1-7           |

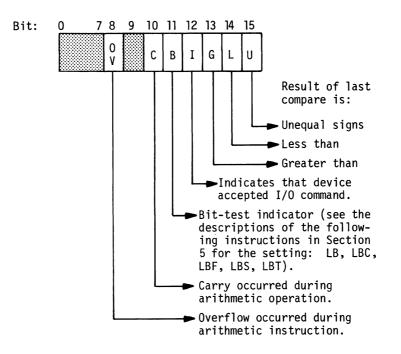

| Scientific Accumulator (Sn)                                      |               |

| Registers                                                        | 1-7           |

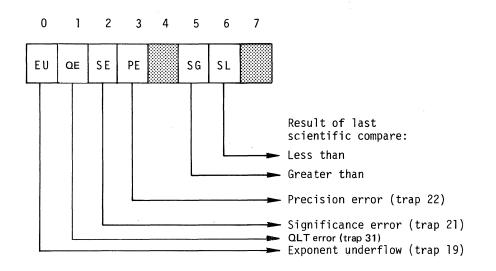

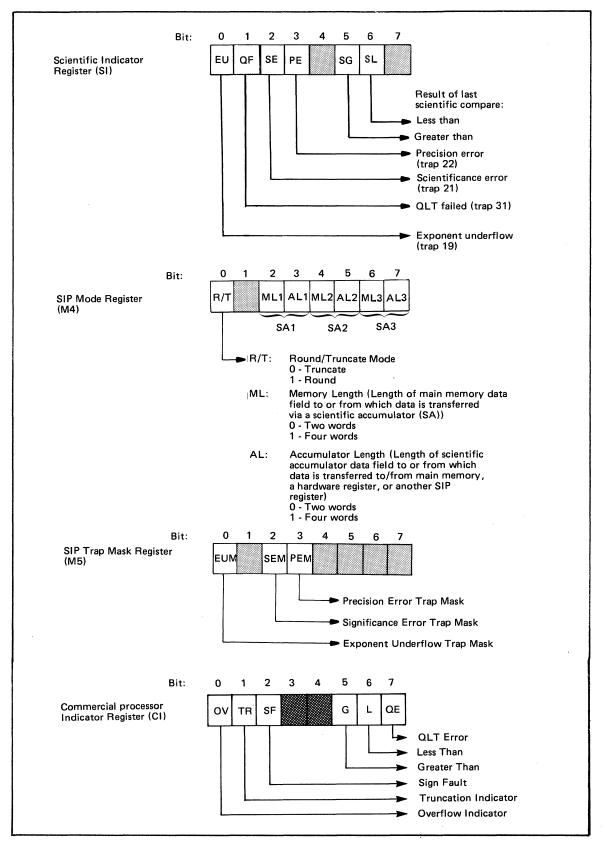

| Scientific Indicator (SI) Register                               | 1-8           |

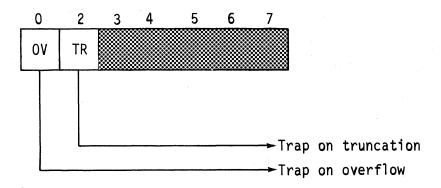

| SIP Mode (M4) Register                                           |               |

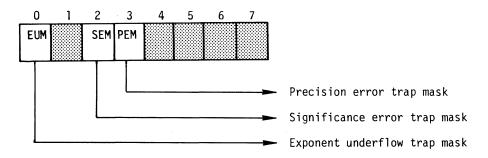

| SIP Trap Mask (M5) Register                                      |               |

| Software Simulation of the Scientific                            |               |

| Instruction Processor                                            | 1-9           |

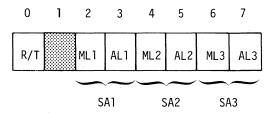

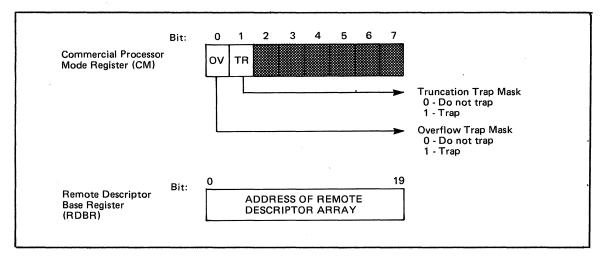

| Commercial Processor Registers                                   | 1-9           |

| Commercial Processor Mode                                        |               |

| Register                                                         | 1-9           |

| Commercial Processor Indicator                                   |               |

| Register                                                         | 1 - 10        |

| Software Simulation of the Commercial                            |               |

| Processor                                                        | 1-10          |

| Initialization and Modification of                               |               |

| M-Registers                                                      | 1-11          |

| Section 2. Elements of Assembly                                  |               |

| Language                                                         |               |

| Mnemonic Codes                                                   | 2-1           |

| Symbolic Names                                                   |               |

| Identifiers                                                      | 2-2           |

| Labels                                                           |               |

| User-Defined Labels                                              |               |

| Reserved Labels                                                  |               |

| Constants                                                        |               |

| String Constants                                                 | 2-5           |

| ASCII String Constants                                           | 2-5           |

| Hexadecimal String Constants                                     | 2-5           |

| Bit String Constants                                             | $2-\tilde{6}$ |

| Truncation/Padding of String Constants.                          | 2-6           |

| Arithmetic Constants                                             | 2-7           |

| Binary Integer Constants                                         |               |

| Binary Integer Constants in                                      |               |

| Decimal Notation                                                 | 2-7           |

.

| Binary Integer Constants in         |

|-------------------------------------|

| Hexadecimal Notation 2-7            |

| Decimal Integer Constants 2-7       |

| Unpacked Decimal Integers 2-8       |

| Packed Decimal Integers 2-8         |

| Examples of Decimal Integers 2-9    |

| Fixed-Point Constants 2-9           |

| Floating-Point Constants 2-10       |

| Normalization 2-11                  |

| Expressions 2-11                    |

| Evaluating Expressions 2-13         |

| Location and Value Expressions 2-13 |

| Value Expressions 2-13              |

| Internal Value Expressions 2-13     |

| External Value Expressions 2-14     |

| Location Expressions                |

| Internal Location Expressions 2-15  |

| External Location Expressions 2-15  |

| Common Location Expressions 2-16    |

| Address Expressions                 |

| References                          |

|                                     |

#### Section 3. Programming Considerations

| eonsider direns              | ,              |

|------------------------------|----------------|

| Assembly Language Source     |                |

| Statement Formats            | 3-1            |

| Order of Statements          |                |

| in Source Program            | 3-2            |

| Calling System Services      | 3-2            |

| Calling External Procedures  | 3-2            |

| Alternate Method of Handling |                |

| Input/Output and             |                |

| File Manipulation            | 3-2            |

| Assembler                    | <b>3</b> - $2$ |

| Cross-Reference Listing      | 3-3            |

| SAF/LAF Considerations       | 3-3            |

| Reentrancy Considerations    | 3-3            |

|                              |                |

#### Section 4. Assembler Control Statements

| Assembly-Controlling Statements 4-1           |

|-----------------------------------------------|

| List-Controlling Statements 4-1               |

| Data-Defining Statements 4-1                  |

| Storage-Allocation Statements 4-2             |

| Symbol-Defining Statements 4-2                |

| Program-Linking Statements 4-2                |

| Conditional Assembly Control Statements . 4-2 |

| Operation Code-Defining Statement 4-2         |

| Assembler Control Statements 4-2              |

| ARGLST                                        |

| BORG4-4                                       |

| BTEXT                                         |

| CALL                                          |

| CALL2 4-7    | 7  |

|--------------|----|

| CLST 4-6     |    |

|              |    |

| COMM 4-9     | 0  |

| CTRL 4-:     | 10 |

| DC 4-5       | 11 |

| DEFGEN 4-    | 12 |

| EDEF 4-      |    |

| END          |    |

|              |    |

| EQU 4-:      | 10 |

| FAIL 4-      | 16 |

| IF 4-:       | 17 |

| LCOMM 4-     | 18 |

| LIST 4-      | 19 |

| ΔLIST        | 19 |

| NLST 4-9     | 20 |

| NULL 4-2     |    |

| ORG          | -  |

| PTRAY 4-2    |    |

| RESV         |    |

| TEXT 4-2     |    |

| TITLE        |    |

| XDEF         | -0 |

|              |    |

| <b>ILLOO</b> |    |

| XVAL 4-2     | 29 |

#### Section 5. Assembly Language Instructions

| Arithmetic Operations 5-1                 |

|-------------------------------------------|

| Boolean Operations 5-2                    |

| Branch Operations 5-2                     |

| Compare Operations                        |

| Control Operations 5-2                    |

| Input/Output Operations 5-2               |

| Load Operations 5-2                       |

| Memory Management Operations 5-3          |

| Modify Operations 5-3                     |

| Move Operations 5-3                       |

| Queue Operations 5-3                      |

| Shift Operations 5-3                      |

| Stack Operations 5-3                      |

| Store Operations 5-3                      |

| Swap Operations 5-3                       |

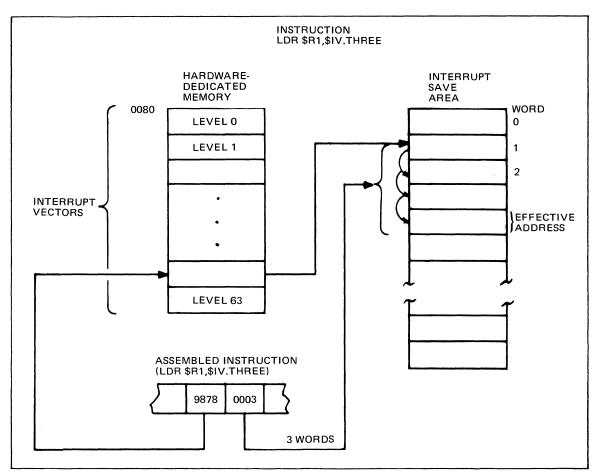

| Assembly Language Instruction Types 5-4   |

| Branch-on-Indicator (BI) Instructions 5-4 |

| Branch-on-Register (BR) Instructions 5-4  |

| Double Operand (DO) Instructions 5-4      |

| Generic (GE) Instructions 5-5             |

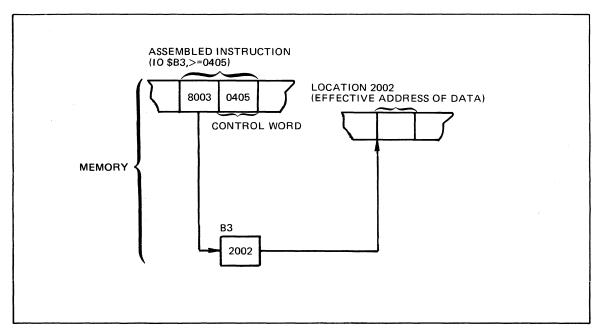

| Input/Output (IO) Instructions 5-5        |

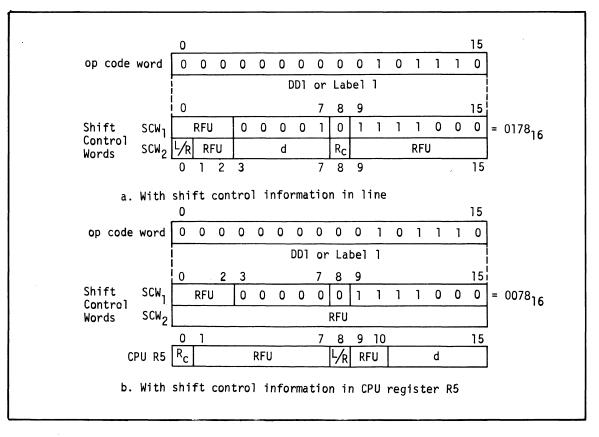

| Shift (SHS and SHL) Instructions 5-5      |

| Short-Value-Immediate (SI)                |

| Instructions 5-6                          |

| Single Operand (SO) Instructions 5-6      |

| Addressing Techniques 5-7                 |

| Register Addressing 5-7                   |

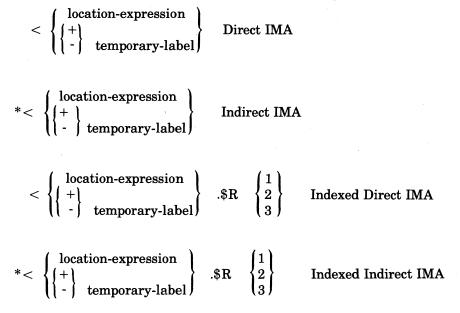

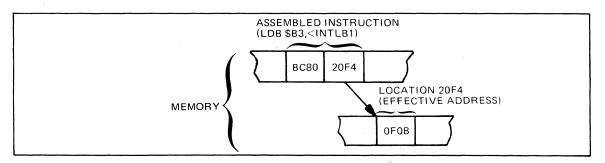

| Immediate Memory Addressing (IMA) 5-8     |

| Direct Immediate Memory                   |

| Addressing 5-8                            |

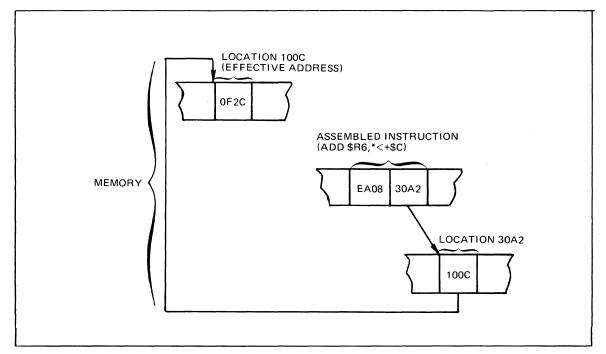

| Indirect Immediate Memory                 |

| Addressing 5-9                            |

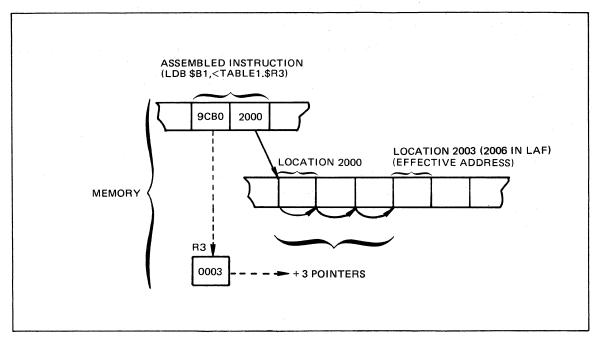

| Indexed Direct Immediate Memory           |

| Addressing 5-9                            |

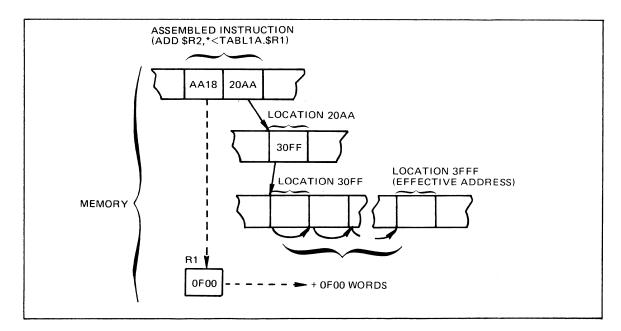

| Indexed Indirect Immediate Memory         |

| Addressing 5-10                           |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Immediate Operand Addressing                                                                                                                                                                                                                                                                                                                                                                                                              | 5 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

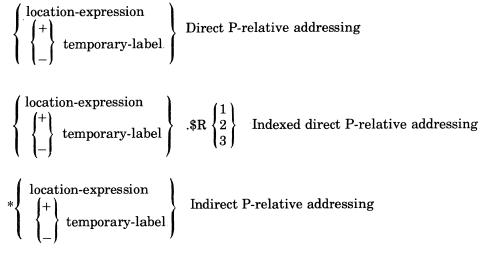

| P-Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                                     | E 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

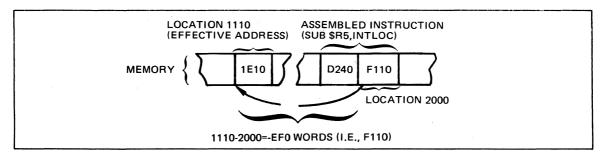

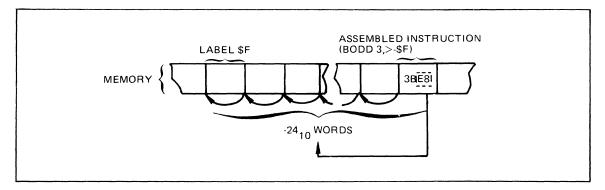

| Direct P-Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                              | 5-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

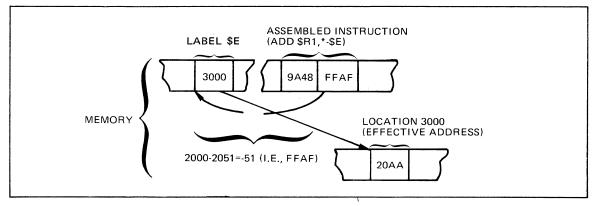

| Indirect P-Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                            | 5-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

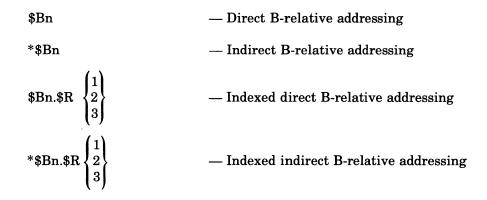

| B-Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

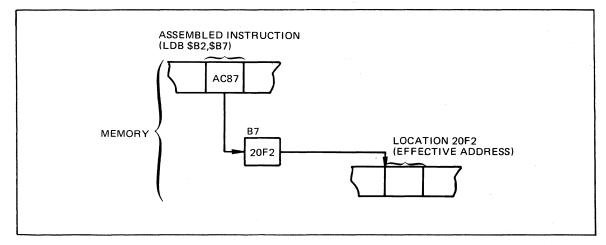

| Direct B-Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                              | 5-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Indirect B-Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                            | 5-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Indexed Direct B-Relative                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Indexed Indirect B-Relative                                                                                                                                                                                                                                                                                                                                                                                                               | 0 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | 516                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                | 0-10 v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

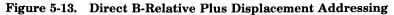

| Direct B-Relative Plus Displacement                                                                                                                                                                                                                                                                                                                                                                                                       | F 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Indirect B-Relative Plus                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Displacement Addressing                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

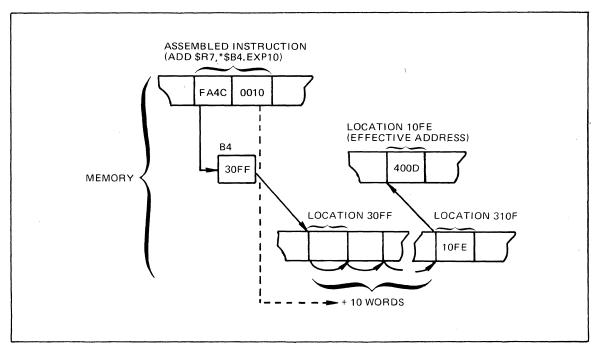

| Direct B6-Relative Plus Local                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Common Block Plus Displacement                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

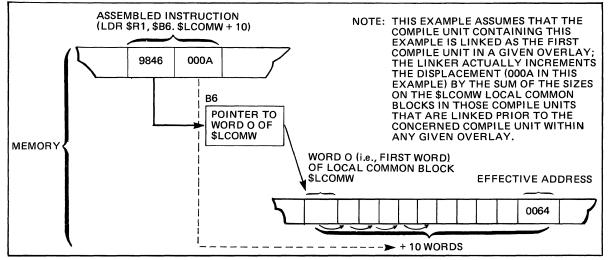

| Indirect B6-Relative Plus Local                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Common Block Plus Displacement                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |