# · HOMEYWE!!

This document and the information contained herein are confidential to and the property of Honeywell information Systems Inc. and are made available only to Honeywell employees for the sole purpose of maintaining Honeywell's products. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager; and shall not be disclosed or distributed (a) to persons who are not Honeywell employees, or (b) to Honeywell employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this document no longer has need for the document for the authorized Honeywell purpose, this document and any copies thereof shall be returned to the employee's manager. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsible Honeywell Vice President.

# LEVEL 6

HARDWARE

TYPE MTC9101 MAGNETIC TAPE CONTROLLER MANUAL This document and the information contained herein are confidential to and the property of Honeywell Information Systems Inc. and are made available only to Honeywell employees for the sole purpose of maintaining Honeywell's products. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager; and shall not be disclosed or distributed (a) to persons who are not Honeywell employees, or (b) to Honeywell employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this document no longer has need for the document for the authorized Honeywell purpose, this document and any copies thereof shall be returned to the employee's manager. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsible Honeywell Vice President.

#### TYPE MTC9101

#### MAGNETIC TAPE CONTROLLER MANUAL

Document No. 71010425-200

Order No. FM88, Rev. 1

This manual has been revised to the -200 level. It supersedes all previous issues.

| REVISION                                                         | DATE      | AUTHORITY     | AFFECTED PAGES |

|------------------------------------------------------------------|-----------|---------------|----------------|

| -100                                                             | Dec. 1976 | Interim Issue |                |

| -200                                                             | Aug. 1977 | BLCO 70311    | All            |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

|                                                                  |           |               |                |

| Hardware Publications, M&TO, Billerica, MA 01821 <sub>FM88</sub> |           |               |                |

| Printed in the United States of America<br>All rights reserved   |           |               |                |

## RECORD OF REVISIONS

#### CONTENTS

C

,

C

C

| Section | F                                                                                                          | Page                                        |

|---------|------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| I       | 1.1General Description11.2Functional Characteristics11.3MTC Subsystem Operational Summary11.4Interfaces1   | 1-1<br>1-2<br>1-2<br>1-5<br>1-6<br>1-7      |

| II      | <pre>2.1 Software</pre>                                                                                    | 2-1<br>2-1<br>2-3<br>2-3<br>2-4             |

|         | 2.3.3Scratch Pad Memory (SPM)22.3.4Megabus Logic22.3.5Adapter/Channel Control Logic22.3.6Test Multiplexer2 | 2-5<br>2-5<br>2-6<br>2-6<br>2-7<br>2-7      |

|         | 2.4 Output Data Operation                                                                                  | 2-7<br>2-8<br>2-8                           |

|         | 2.5 Input Data Operation 2                                                                                 | 2-9                                         |

| III     | 3.1 Interface                                                                                              | 3-1<br>3-1<br>3-1<br>3-3                    |

|         | <ul> <li>3.2 Microprogram Control Store Functional<br/>Components</li></ul>                                | 3-3<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11 |

|         | 3.2.6 Microprogram Instruction Register<br>(UPIR)                                                          | 3-12                                        |

HONEYWELL CONFIDENTIAL & PROPRIETARY

#### CONTENTS

Section

.

e

|    | 3.3    | 3.2.7<br>3.2.8<br>Arithmet | Op-Code Decoder (OPCOD)<br>Scan Logic<br>ic Logic Unit and Accumulator | 3-12<br>3-12 |

|----|--------|----------------------------|------------------------------------------------------------------------|--------------|

|    | J•J    |                            | hal Components                                                         | 3-14         |

|    |        | 3.3.1                      | A-Operand Multiplexer (ALUAX)                                          | 3 - 14       |

|    |        | 3.3.2                      | B-Operand Multiplexer (ALUBX)                                          | 3 - 14       |

|    |        | 3.3.3                      | Arithmetic Logic Unit (ALU)                                            | 3-14         |

|    |        | 3.3.4                      | Accumulator (ACU)                                                      | 3-17         |

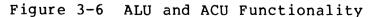

|    | 3.4    | Scratch                    | Pad Memory Functional Components                                       | 3-18         |

|    | •••    | 3.4.1                      | Scratch Pad Memory Index Control                                       |              |

|    |        |                            | Flip-Flop (SPMICF)                                                     | 3-18         |

|    |        | 3.4.2                      | Scratch Pad Memory Index Register                                      | 5 10         |

|    |        | J. I.                      | (SPMIR)                                                                | 3-18         |

|    |        | 3.4.3                      | Scratch Pad Memory Address Counter                                     | 5 10         |

|    |        |                            | (SPMAC)                                                                | 3-19         |

|    |        | 3.4.4                      | Scratch Pad Memory Address Selector                                    |              |

|    |        | <b></b>                    | (SPMAS)                                                                | 3-19         |

|    |        | 3.4.5                      | Scratch Pad Memory (SPM)                                               | 3-19         |

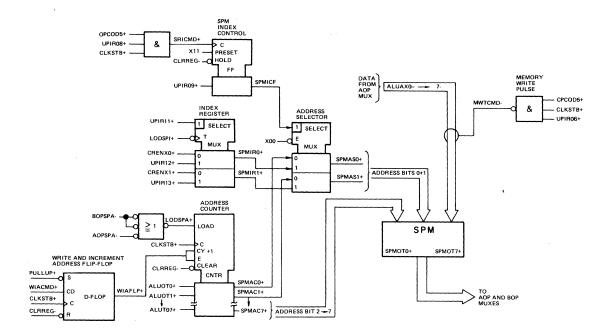

|    | 3.5    | Megabus                    | Logic Functional Components                                            | 3-20         |

|    | 3.3    | 3.5.1                      | Bus Data Register (BDR)                                                | 3-20         |

|    |        | 3.3.1                      | 3.5.1.1 Parallel Load Operation                                        | 3-20         |

|    |        |                            | 3.5.1.2 Byte-Serial Load Operation.                                    | 3-20         |

|    |        | 3.5.2                      | Bus Data Register Control                                              | 3-22         |

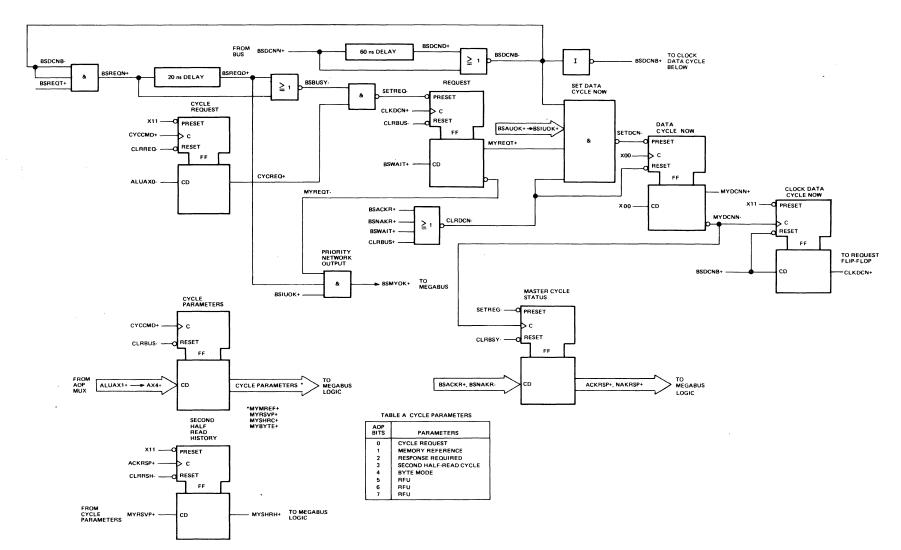

|    |        | 3.5.3                      | Master Cycle Logic and Priority                                        |              |

|    |        |                            | Network                                                                | 3-23         |

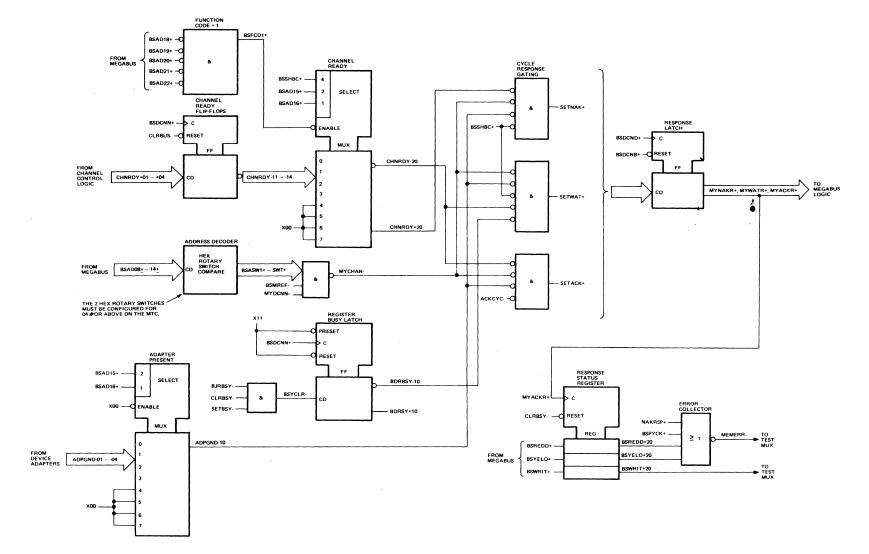

|    |        | 3.5.4                      | Slave Response Logic                                                   | 3-25         |

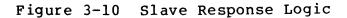

|    | 3.6    |                            | Control Functional Description                                         | 3-28         |

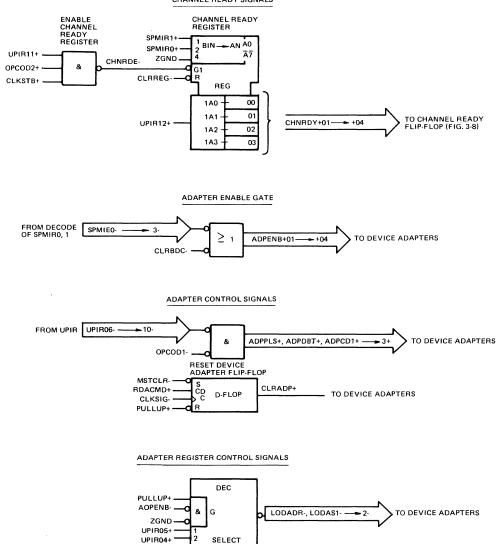

|    |        | 3.6.1                      | Channel Ready Signals                                                  | 3-28         |

|    |        | 3.6.2                      | Adapter Enable Gate                                                    | 3-28         |

|    |        | 3.6.3                      | Adapter Control Signals                                                | 3-28         |

|    |        | 3.6.4                      | Adapter Register Control Signals                                       | 3-30         |

|    |        | 3.6.5                      | Request Logic                                                          | 3-30         |

|    | 3.7    | Test Mul                   | ltiplexer Functional Description                                       | 3-30         |

|    | 3.8    |                            | nd Clock Control Functional                                            |              |

|    |        |                            | tion                                                                   | 3-31         |

| IV | THEORY | COF OPEN                   | RATION - CYCLE FLOW                                                    | 4-1          |

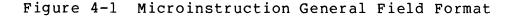

|    |        |                            | structions                                                             | 4-1          |

|    |        | 4.1.1                      | Miscellaneous Commands                                                 | 4-2          |

|    |        | 4.1.2                      | Device Adapter Commands                                                | 4-2          |

|    |        | 4.1.3                      | Megabus Logic Commands                                                 | 4-2          |

|    |        | 4.1.4                      | ALU Commands                                                           | 4-4          |

|    |        | 4.1.5                      | Constant Commands                                                      | 4-4          |

|    |        | 4.1.6                      | Memory Commands                                                        | 4-4          |

|    |        | 4.1.7                      | Test and Return Commands                                               | 4-4          |

|    |        | 4.1.8                      | Branch Commands                                                        | 4-5          |

|    | 4.2    |                            | Pad Memory (SPM)                                                       | 4-5          |

|    | 4.3    |                            | e Cycle Flow                                                           | 4-5          |

|    |        | 4.3.1                      | Quality Logic Test                                                     | 4-5          |

|    |        | 4.3.2                      | Setup Routine                                                          | 4-15         |

|    |        |                            |                                                                        |              |

# HONEYWELL CONFIDENTIAL & PROPRIETARY

iv

# CONTENTS

# Section

(

| 4.3.3 | Wait Routine             | 4-15 |

|-------|--------------------------|------|

| 4.3.4 | Bus Request Routine      |      |

| 4.3.5 | Interrupt Routine        |      |

| 4.3.6 | Resume Interrupt Routine |      |

| 4.3.7 | Point Routine            | 4-17 |

| 4.3.8 | DMA Out Routine          | 4-17 |

| 4.3.9 | DMA In Routine           | 4-17 |

Page

#### ILLUSTRATIONS

| Figure |                                                                 | Page        |

|--------|-----------------------------------------------------------------|-------------|

| 1-1    | MTC System Block Diagram                                        | 1-4         |

| 1-2    | MTC Interfaces                                                  | 1-6         |

| 2-1    | MTC Hardware Major Block Diagram                                | 2-2         |

| 2-2    | Megabus Configuration for Transferring Data to/from the MTC SPM | 2-4         |

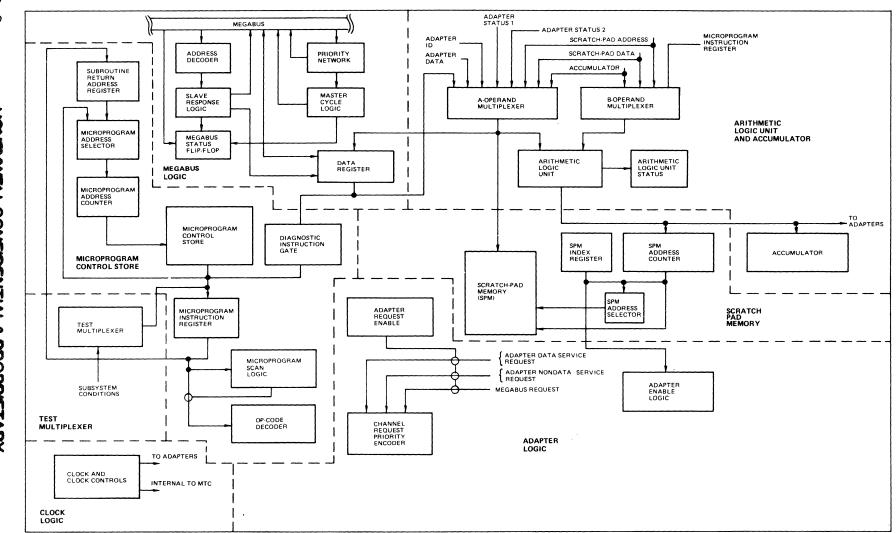

| 3-1    | MTC Hardware Block Diagram                                      | $\bar{3}-2$ |

| 3-2    | Megabus/MTC Interface                                           | 3-4         |

| 3-3    | MTC/Adapter Interface                                           | 3-7         |

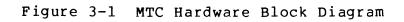

| 3-4    | Microprogram Control Store Functionality                        | 3-10        |

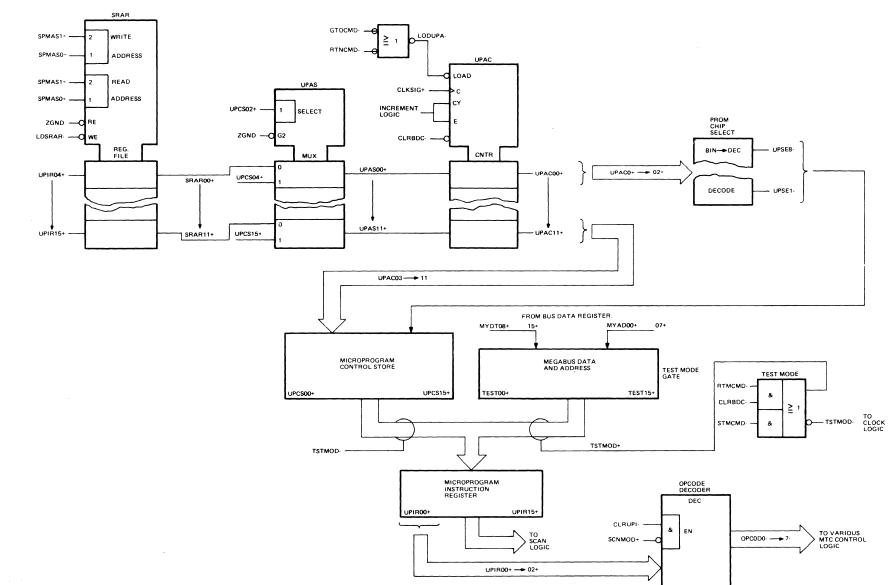

| 3-5    | Scan Logic                                                      | 3-13        |

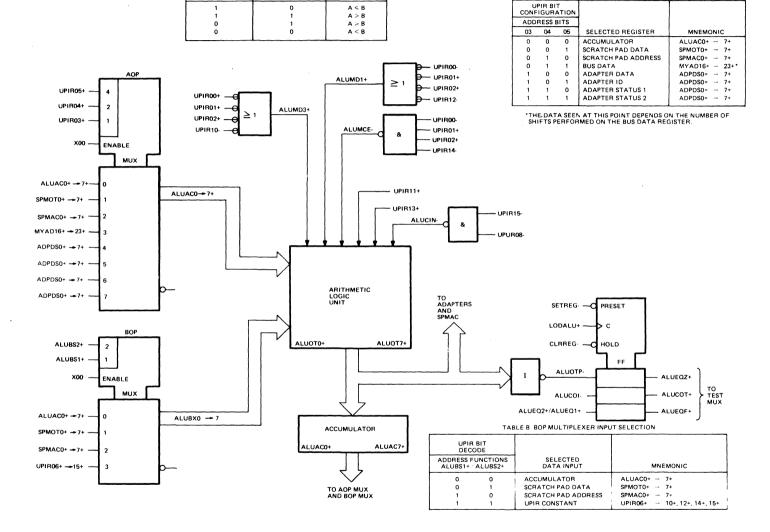

| 3-6    | ALU and ACU Functionality                                       | 3-15        |

| 3-7    | Scratch Pad Memory Functionality                                | 3-18        |

| 3-8    | Bus Data Register                                               | 3-21        |

| 3-9    | Master Cycle Logic and Priority Network                         | 3-24        |

| 3-10   | Slave Response Logic                                            | 3-26        |

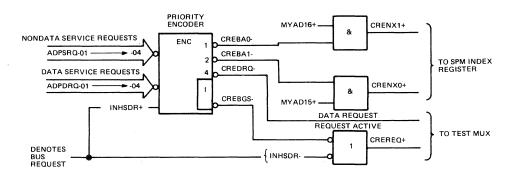

| 3-11   | Channel Controls                                                | 3-29        |

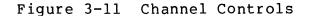

| 3-12   | Test Multiplexer                                                | 3-31        |

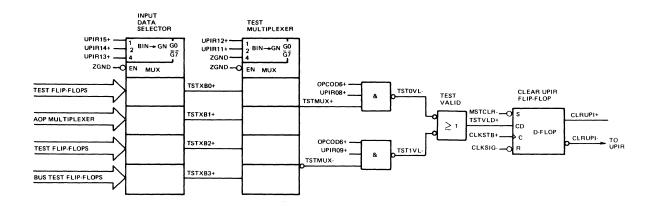

| 3-13   | Clock and Clock Control                                         | 3-32        |

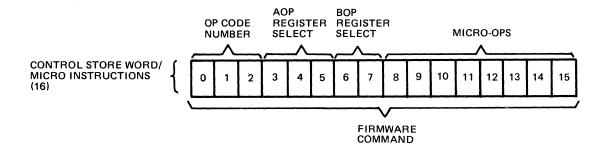

| 4-1    | Microinstruction General Field Format                           | 4-2         |

| 4-2    | MTC Firmware Commands                                           | 4-3         |

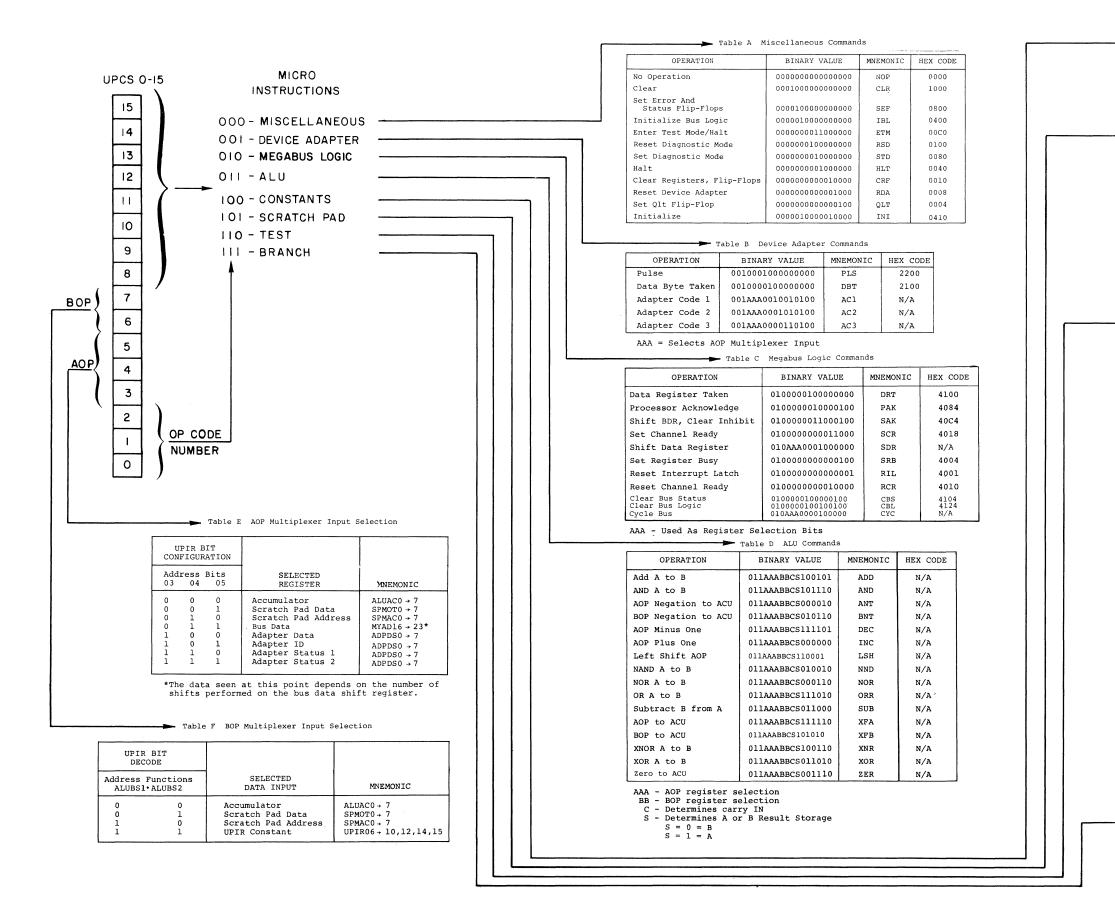

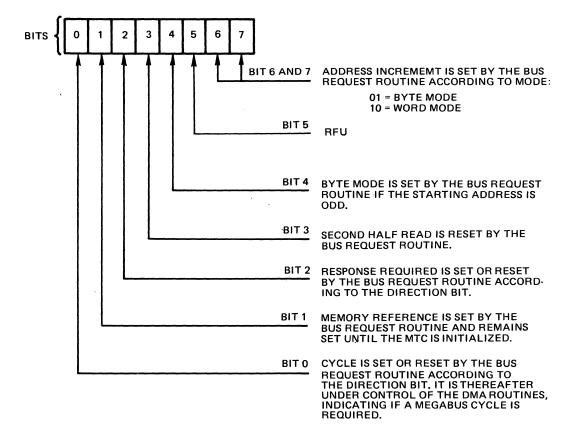

| 4-3    | Control Word Bit Significance                                   | 4-10        |

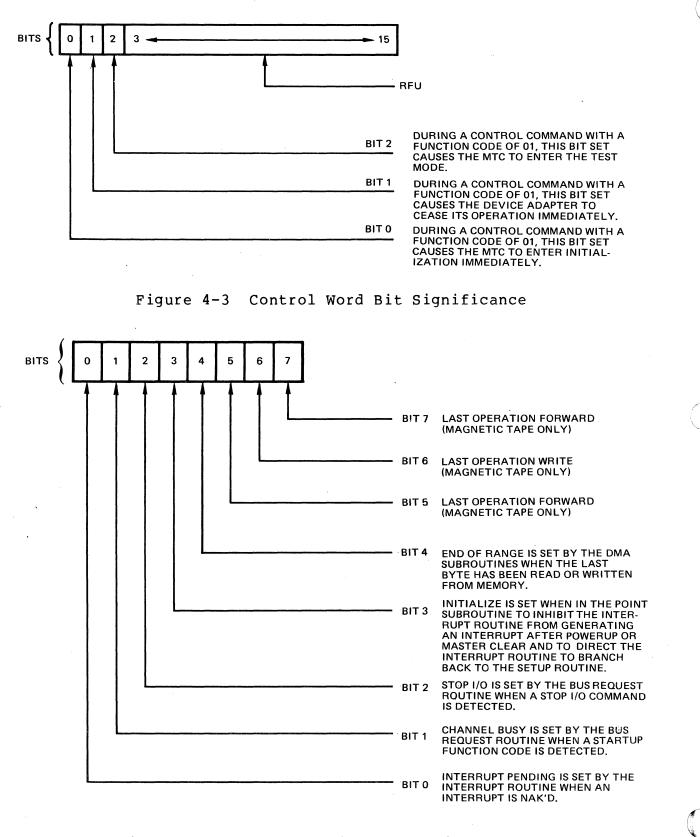

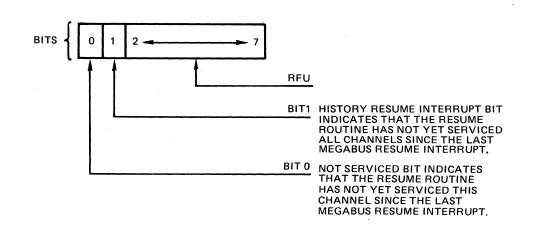

| 4-4    | Channel Monitor Byte Bit Structure                              | 4-10        |

| 4-5    | DMA Flag Byte Bit Structure                                     | 4-11        |

| 4-6    | Resume Interrupt Control Parameter Byte Bit                     |             |

|        | Structure                                                       | 4-11        |

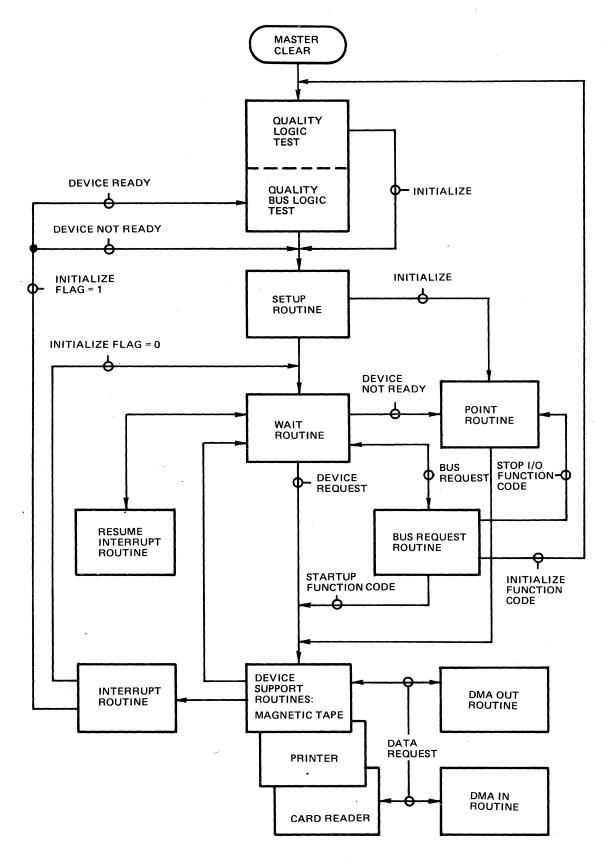

| 4-7    | Firmware Overview Flowchart                                     | 4-12        |

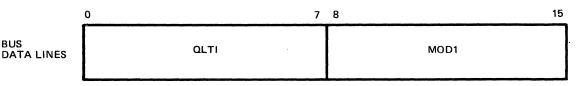

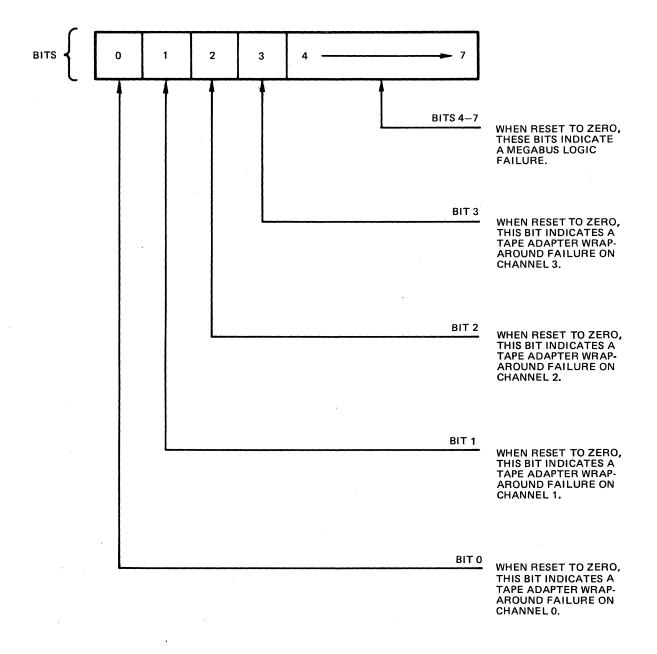

| 4-8    | QLTI Byte Bit Structure                                         | 4-14        |

٠

.

.

#### TABLES

| Table                           |                                                                                                                                                                                                 | Page                            |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1-1<br>2-1<br>3-1<br>3-2<br>3-3 | MTC Attachable Devices/Adapters<br>I/O Commands<br>Megabus/MTC Interface Signal Lines<br>MTC/Adapter Interface Signal Lines<br>MTC/Adapter Interface Line and Mnemonic Cross-<br>Reference List | 1-3<br>2-3<br>3-5<br>3-8<br>3-6 |

| 3-4                             | ALU Functionality                                                                                                                                                                               | 3-16                            |

| 3-5                             | Bus Data Register Application                                                                                                                                                                   | 3-23                            |

| 4-1                             | Scratch Pad Memory Topology                                                                                                                                                                     | 4-6                             |

| 4-2                             | Scratch Pad Memory Word Description                                                                                                                                                             | 4-8                             |

| 4-3                             | MTC Device Identification Codes                                                                                                                                                                 | 4-13                            |

# HONEYWELL CONFIDENTIAL & PROPRIETARY

vi

HONEYWELL CONFIDENTIAL & PROPRIETARY

$\bigcirc$

٠

•

•

•

# I INTRODUCTION

This product manual describes the functionality and operation of the Type MTC9101 Magnetic Tape Controller (MTC). Programming considerations are included to aid in understanding the hardware and firmware\* descriptions. Detailed programming information is contained in the Minicomputer Handbook (Order No. AS22) or the Peripherals Handbook (Order No. AT04).

Operational theory within this manual is designed to acquaint the user with the major functional hardware and firmware elements in order to aid in analyzing the MTC operation at the detail presented in the logic block diagrams (LBDs).

Detailed theory for the MTC hardware logic is related directly to the maintenance philosophy of board replacement rather than on-site board repair.

This product manual is comprised of this section and Sections II through IV as follows:

Section II - Theory of Operation - Overview

This section contains a brief description of the

interrelationship between software and the MTC hard ware and firmware, and supplies an operational

overview of the functional areas.

\*This manual supports firmware Rev. 24.

HONEYWELL CONFIDENTIAL & PROPRIETARY

- Section III Theory of Operation Intermediate

This section contains the intermediate theory of

operation for each area discussed in Section II.

Function names are included in many places to aid

entry into LBDs supplied in the Type MTC9101 Magnetic

Tape Controller Reference Manual (Order No. FM89).

- Section IV Theory of Operation Cycle Flow This section contains a description of the MTC microoperations. An overview flow chart illustrates MTC cycle groupings with their entries and exits.

#### 1.1 GENERAL DESCRIPTION

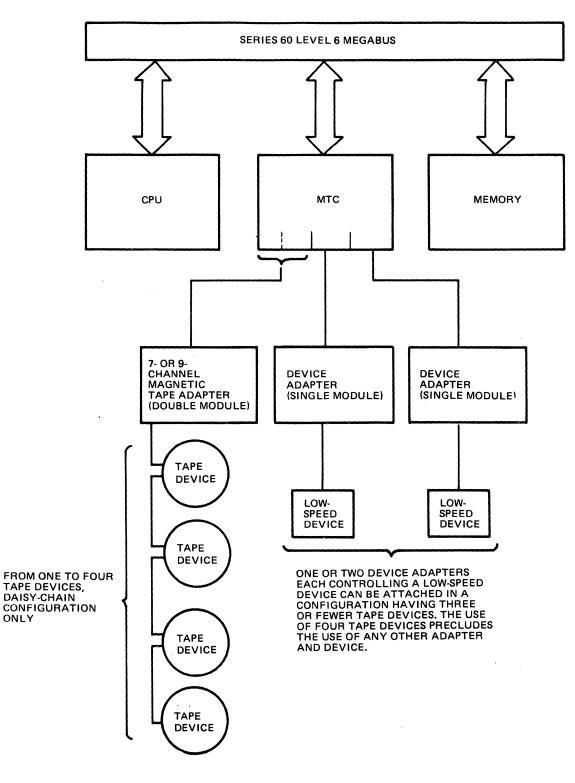

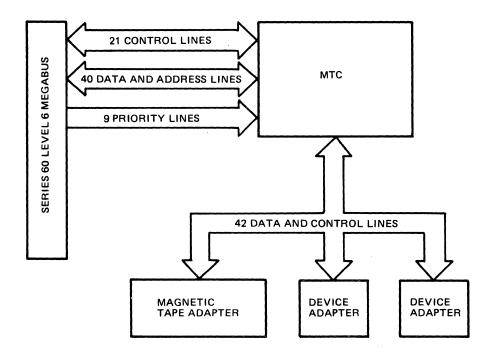

The Type MTC9101 Magnetic Tape Controller (subsequently referred to as the MTC or controller) is a solid state module (BF4MTC) which, in conjunction with seven or nine channel tape adapters, operates up to four daisy-chained tape devices in a Model 6/34, 6/36, or 6/40 configuration of the Series 60 Level 6 computer system. In subsystem configurations of three or fewer tape devices, the controller allows for the attachment of up to two low-speed devices/adapters. The devices and adapters for the MTC subsystem are listed in Table 1-1. The magnetic tape subsystem, whose attachment configuration is illustrated in Figure 1-1, uses 1/2-inch magnetic tape for storage and retrieval of Non-Return-to-Zero (NRZI) formatted data. Regardless of the number of tape devices connected to the subsystem, only one tape adapter can be utilized with a single MTC.

The MTC consists of dual in-line packages (DIPs) mounted on a multilayer Series 60 Level 6 printed wiring assembly module. The MTC provides eight 25-pin in-line connectors for attachment of adapters, and two 50-pin connectors for attachment to the Series 60 Level 6 Megabus.

#### **1.2 FUNCTIONAL CHARACTERISTICS**

The MTC is a microprogrammed peripheral device control unit which, together with the tape adapter, supports from one to four tape devices. Much of the microprocessor portion of the MTC is designed to facilitate its application as a control unit for various unit record and magnetic tape device adapters. The MTC performs the following general purpose control functions.

- Execution of the Series 60 Level 6 Megabus network sequences

- Command decoding

- Status and control register storage

- Data transfer multiplexing to/from device adapters

- Direction of the general flow of command execution.

# 1-2 HONEYWELL CONFIDENTIAL & PROPRIETARY

|                     | DEVICES                                  |                                                                                                      |          | ADAPTERS                       |

|---------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|----------|--------------------------------|

| DEVICE              | TYPE NO.                                 | DESCRIPTION                                                                                          | TYPE NO. | DESCRIPTION                    |

| Tape<br>Drive       | MTU9104<br>MTU9105                       | 45 IPS, 9 Channel, 800 BPI<br>75 IPS, 9 Channel, 800 BPI                                             | MTM9103  | 9-Channel NRZI Tape<br>Adapter |

| (NRZI)              | MTU9112<br>MTU9113                       | 45 IPS, 7 Channel 800/556 BPI<br>75 IPS, 7 Channel, 800/556 BPI                                      | MTM9101  | 7-Channel NRZI Tape<br>Adapter |

| Card<br>Reader (1)  | CRU9101<br>CRU9102<br>CRU9103<br>CRU9104 | 300 CPM<br>300 CPM with Mark Sense<br>500 CPM<br>500 CPM with Mark Sense                             | CRM9101  | Card Reader Adapter            |

| Line<br>Printer (2) | PRU9103<br>PRU9104<br>PRU9105<br>PRU9106 | 240 LPM, 96 Characters<br>300 LPM, 64 Characters<br>480 LPM, 96 Characters<br>600 LPM, 64 Characters | PRM9101  | Printer Adapter                |

| Serial<br>Printer   | PRU9101<br>PRU9102                       | 64 Characters<br>96 Characters                                                                       |          |                                |

Table 1-1 MTC Attachable Devices/Adapters

(1) (2)

CRF9101 51-column card option available PRF9102 vertical format unit option available

\*

Figure 1-1 MTC System Block Diagram

#### 1 - 4HONEYWELL CONFIDENTIAL & PROPRIETARY

.

#### 1.3 MTC SUBSYSTEM OPERATIONAL SUMMARY

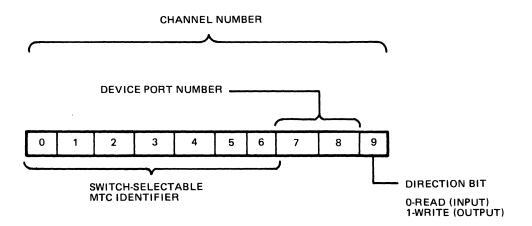

Each device attached to the MTC by way of an adapter is addressable by software via channel numbers. A device has two channel numbers assigned, the numbers differing only in the low order bit position (called the direction bit). When an I/O Load (IOLD) command for the MTC channel is accepted, the direction bit of the channel number specifies whether the command designates an input or output data transfer. The direction bit of a subsequently accepted Output Task Word command is examined to verify that it agrees with the IOLD's direction bit. The following example indicates the composition of a channel number, where bits 0 through 6 are assigned at the time of system installation.

Software usability of the devices attached to the MTC is such that the devices are independent of one another. For example, operations on one device are, in general, independent of the activity of any other device except that the MTC can stall the initiation of a command sequence addressed to one device (channel number) while the it is servicing another device. This apparent device independence looks, to software, as if multiple levels of simultaneity exist.

The tape subsystem command sequencing results in any command addressed to a nonbusy channel being accepted, allowing the MTC to accept any command to a tape device while another tape device is executing a data transfer. The accepted command is not invoked until the present data transfer is completed. Stored commands are executed in the sequence in which they are received, but rewinds/unloads may be executed concurrently with data transfer. Because channels are serviced on a rotating priority basis, no one channel dominates adapter usage.

If an MTC has fewer than four devices attached, it responds only to the channel numbers associated with the installed devices. When a configuration of tape devices is three or fewer, up to two unit record adapters can be implemented by the MTC. To allow for device access, the MTC contains a set of software-loadable scratch pad memory locations (refer to Section IV of this manual) assigned to each device which contain parameters and control information required for device operation. In addition to range and address locations, there is a configuration location which contains the mode of operation information, and a task word location which stores the command codes.

To perform a specific operation, the software first loads the configuration, then address and range into the scratch pad memory. The task word, which is loaded last, designates the operation to be performed. Upon receipt of the task word, execution of the command is initiated.

Commands addressed to a nonbusy device (channel) are always accepted, although their execution can be delayed as previously described. All commands addressed to a busy tape device are rejected (NAK response on the Megabus) with the exception of the Output Control Word command.

#### 1.4 INTERFACES

Two interface networks are associated with the MTC. They are the Megabus/MTC interface and the MTC/device adapter interface (see Figure 1-2). For a detailed description of these interfaces, refer to Section III.

Figure 1-2 MTC Interfaces

### 1-6 HONEYWELL CONFIDENTIAL & PROPRIETARY

# 1.5 REFERENCE DOCUMENTS

The information contained within the following documents supplements the contents of this manual.

| Title                                                                                       | Document No. | <u>Order No.</u> |

|---------------------------------------------------------------------------------------------|--------------|------------------|

| Model 34/36 System Manual                                                                   | 71010200     | FL35             |

| Model 34/36 CP Manual                                                                       | 71010201     | FL36             |

| Model 06 System Manual                                                                      | 71010210     | FL37             |

| Model 06 CP Manual                                                                          | 71010211     | FL38             |

| Type MTM9102 9-Channel NRZI<br>Tape Adapter Manual                                          | 71010282     | FN18             |

| Type MTM9101 7-Channel NRZI<br>Tape Adapter Manual                                          | 71010286     | FN20             |

| Type MTM9102 9-Channel NRZI<br>Tape Adapter Reference Manual<br>(Assembly No. 60130316-001) | 71010283     | FN19             |

| Type MTM9102 9-Channel NRZI<br>Tape Adapter Reference Manual<br>(Assembly No. 60130975-001) | 71010564     | FP44             |

| Type MTM9101 7-Channel NRZI<br>Tape Adapter Reference Manual                                | 71010287     | FN21             |

| Type PRM9101 Printer Adapter<br>Manual                                                      | 71010221     | FL18             |

| Type CRM9101 Card Reader<br>Adapter Manual                                                  | 71010222     | FL13             |

| Power Systems Manual                                                                        | 71010290     | FL34             |

| Level 6 Minicomputer Handbook                                                               |              | AS22             |

| Peripherals Handbook                                                                        |              | AT04             |

| Type PRM9101 Printer Adapter<br>Reference Manual (Assembly No.<br>60127843-001)             | 71010371     | FL27             |

| Type PRM9101 Printer Adapter<br>Reference Manual (Assembly No.<br>60127843-003)             | 71010376     | FM40             |

| Type CRM9101 Card Reader<br>Adapter Reference Manual<br>(Assembly No. 60127840-003) | 71010377 | FM37 |

|-------------------------------------------------------------------------------------|----------|------|

| Type MTC9101 Magnetic Tape<br>Controller Reference Manual                           | 71010426 | FM89 |

1

# HONEYWELL CONFIDENTIAL & PROPRIETARY

1-8

# II THEORY OF OPERATION - OVERVIEW

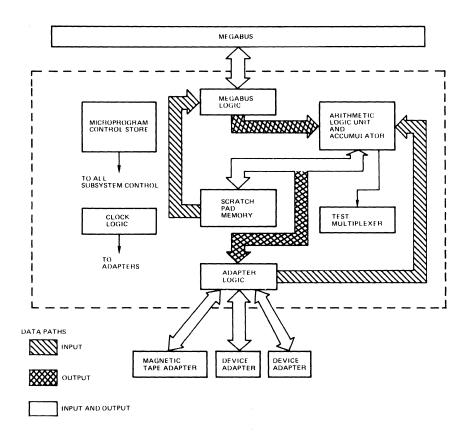

The MTC, in conjunction with adapters and a variable configuration of devices (the maximum being four), is a firmwareoperated peripheral device controller. The MTC allows for attachment of adapters which enable apparent simultaneous control of the attached devices. The MTC hardware, which implements data transfers and control sequences to and from the adapters, is divided into seven fundamental logic areas (see Figure 2-1):

- Microprogram Control Store

- Arithmetic Logic Unit and Accumulator

- Scratch Pad Memory

- Megabus Logic

- Adapter Logic

- Test Multiplexer

- Clock Logic.

These hardware components, in addition to firmware and software, provide for data transfer and efficient control of device operations. During the discussions in the remainder of this manual, only the tape adapter subsystem is considered unless otherwise noted.

#### 2.1 SOFTWARE

The MTC operations are a direct result of an input or output command from the central processor. Table 2-1 lists the input, output, and diagnostic commands applicable to the MTC subsystem. These commands load address, range, and control

HONEYWELL CONFIDENTIAL & PROPRIETARY

Figure 2-1 MTC Hardware Major Block Diagram

information into a device-specific segment of the scratch pad memory (SPM).

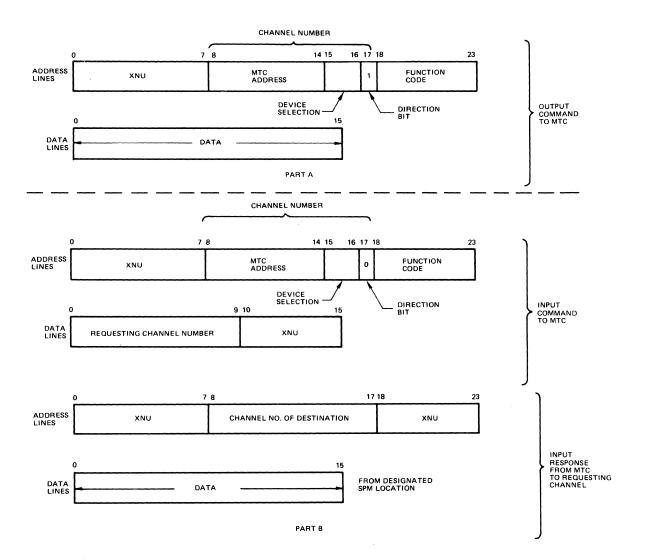

For output commands, the general format of the Megabus address and data lines is as shown in Figure 2-2, part A. The address lines reflect the channel number of the controller being addressed and a function code indicating the purpose of the information on the data lines. The data lines may have control information, address, or control words to be loaded into the MTC scratch pad memory.

For input commands, the general format of the Megabus address and data lines is as shown in Figure 2-2, part B. The address lines reflect the channel number of the controller being addressed and the appropriate function code. The data lines have the number of the channel initiating the command. In response to the input command, the MTC loads the bus address lines with the channel number of the unit that is to receive the information on the data lines.

Device operations are the result of device commands contained in the command code field of the task word. The task word is

# <sup>2-2</sup> HONEYWELL CONFIDENTIAL & PROPRIETARY

| TYPE<br>COMMAND | FUNCTION<br>CODE (HEX) | INSTRUCTION           | ADAPTER APPLICATION                    |

|-----------------|------------------------|-----------------------|----------------------------------------|

| Output          | 01                     | Control Word          | Magnetic Tape*, Card Reader, & Printer |

|                 | 03                     | Interrupt Control     | Magnetic Tape, Card Reader, & Printer  |

|                 | 07                     | Task Word             | Magnetic Tape, Printer                 |

|                 | 09                     | I/O Load Address      | Magnetic Tape, Card Reader, & Printer  |

|                 | 0D                     | I/O Load Range        | Magnetic Tape, Card Reader, & Printer  |

|                 | 11                     | Configuration Word    | Magnetic Tape & Card Reader            |

| Input           | 02                     | Interrupt Control     | Magnetic Tape, Card Reader, & Printer  |

|                 | 06                     | Task Word             | Magnetic Tape, Printer                 |

|                 | 08                     | Memory Byte Address   | Magnetic Tape, Card Reader & Printer   |

|                 | 0A                     | Memory Module Address | Magnetic Tape, Card Reader & Printer   |

|                 | 0C                     | Range                 | Magnetic Tape, Printer, & Card Reader  |

|                 | 10                     | Configuration Word    | Magnetic Tape & Card Reader            |

|                 | 18                     | Status Word 1         | Magnetic Tape, Printer, & Card Reader  |

|                 | 1A                     | Status Word 2         | Magnetic Tape                          |

|                 | 26                     | Identification Code   | Magnetic Tape, Printer, & Card Reader  |

Table 2-1 I/O Commands

\*Both 7- and 9-channel magnetic tape

located in the segment of the SPM dedicated to the device and is loaded there by the Output Task Word I/O command. For information pertaining to the commands that each adapter can perform, refer to the appropriate adapter manual.

#### 2.2 FIRMWARE

Firmware, a sequence of microinstructions resident in the microprogram control store, is the primary control element of the MTC. The main function of the firmware is to interpret external and internal events or conditions and to react in a prescribed manner (i.e., setting or resetting of hardware functions). Efficient data transfer is also a result of firmware control of hardware components in the data path.

Each time the MTC is cleared, a series of firmware operations called the Quality Logic Test is performed. These operations are used to verify the integrity of the MTC hardware. Upon successful completion of the Quality Logic Test, the firmware sets up the hardware for execution of software commands. This is accomplished by setting up control information in the read/write memory and enabling the available adapters. Then the firmware enters a routine and waits for a request from the Megabus or from one of the adapters. When a request occurs, firmware analyzes status and priority before proceeding to the appropriate firmware routine for processing the request. Refer to Section IV for detailed information.

#### 2.3 HARDWARE

The MTC hardware (see Figure 2-1) is organized into seven fundamental logic areas as described in the following subsections. Although each of these major areas is divided into

Figure 2-2 Megabus Configuration for Transferring Data to/from the MTC SPM

Although each of these major areas is divided into various hardware elements, only an overview of each is described in this section; for detailed information, refer to Section III.

#### 2.3.1 Microprogram Control Store

The microprogram control store (UPCS) provides permanent storage for resident control firmware and diagnostic microprograms. The UPCS is enabled during normal operation when the MTC is not in the test mode. It varies address sequencing in order to execute appropriate routines depending upon priority information, test conditions, or channel activity.

# 2-4 HONEYWELL CONFIDENTIAL & PROPRIETARY

The UPCS is configured of either 2K or 4K PROM chips. The internal array of each 2K PROM\* chip is 512 locations by 4 bits wide, providing a maximum of 2,048 bits. The 2K PROM chips are aligned in rows of 4 to create a UPCS output 16 bits wide. The UPCS with 2K PROM chips can be expanded to a maximum of 2K word locations.

The internal array of each 4K PROM\* chip is 1,024 locations by 4 bits wide, providing a maximum of 4,096 bits. The 4K PROM chips are aligned in rows of 4 to establish a UPCS output 16 bits wide. The UPCS with 4K PROM chips is expandable to a maximum of 4K word locations.

#### 2.3.2 Arithmetic Logic Unit (ALU)/Accumulator (ACU)

The ALU is the focal point of all data operations within the MTC, between the MTC and the device adapters, and between the MTC and the Megabus. Two input multiplexers (A-operand and B-operand) to the ALU allow various combinations of registers to be used as operands within the ALU.

The ALU is capable of performing 8-bit arithmetic and logic operations on the outputs of the two multiplexers and determining the destination of the result as a function of the firmware. ALU status is generated as a result of an ALU operation and is stored in ALU status flip-flops for interrogation, or until the initiation of the subsequent ALU firmware command.

The ALU is also able to perform bit operations on one input with a data constant supplied by firmware. The constant can be loaded into the ALU by way of the B-operand multiplexer.

Through the use of multiple byte procedures, word mode operations are performed by firmware and the ALU. In a multiple byte procedure, ALU status (i.e., carry-out) is set each time a byte is operated on, and this status is used to determine the operation required for the subsequent byte.

The ACU is an 8-bit register used for temporary storage of the ALU outputs. Shift operations (left shift only) are performed using the ALU capabilities.

#### 2.3.3 Scratch Pad Memory (SPM)

The SPM is a 256-location by 8-bit wide read/write memory used for storage of information required by or generated by each channel (i.e., data, status, commands, etc.). The SPM is segmented into four parts (64 locations each) with one part designated for each channel. The SPM is addressed by eight bits; the two high-order bits select the correct segment for the

\*The hex rotary switch on the controller is set to 0 for 2K PROM chips, or to F for 4K PROM chips.

channel which is active, and the remaining six select location within the segment.

Data from the ALU A-operand multiplexer is written into the SPM during a firmware Memory Write command at the location specified by the address bits. Because the SPM uses the ALU A-operand multiplexer as the data input, all firmware-visible registers can be implemented as an input local register. The data out of the SPM is delivered to either one of the ALU operand multiplexers and can be subsequently distributed throughout the MTC.

#### 2.3.4 Megabus Logic

The Megabus logic provides an interconnection between the Megabus and each channel on the MTC. Although some of the logic elements are dedicated to an individual channel, the Megabus hardware is primarily common to all the channels.

When Megabus cycles designated for the MTC are detected by a Megabus logic decoder, the response logic is enabled. If the channel being addressed has an adapter installed, a response is generated; otherwise, no response is made, indicating the absence of a device on the desired channel. If the channel is available, the response causes the information on the Megabus address and data lines to be stored. The state of certain control lines are also stored, and the Megabus logic goes busy to inhibit further transfers to the MTC until firmware has dispensed with the stored information.

When the MTC requires a Megabus transfer, firmware loads the address and data registers and sets the proper control lines prior to Megabus cycle initiation. The response of the slave unit is stored by the Megabus logic, and the Megabus logic remains busy until firmware detects completion of the cycle.

Control signals for synchronization of the MTC Megabus requests (and Megabus requests by other units) are also located in the Megabus logic. Finally, the Megabus logic determines the MTC priority with reference to other units when there are simultaneous requests for Megabus activity.

#### 2.3.5 Adapter/Channel Control Logic

A channel consists of the MTC, device adapter, and device. Complete channel control results from a combination of hardware and firmware.

Each channel provides two types of service requests: data and nondata. These service requests are supplied to a channel request encoder where the presence of a data service request signifies that a data byte read from the device is available, or that the need for a data byte to be transferred to the device exists. The nondata service request indicates a change of device

# <sup>2-6</sup> HONEYWELL CONFIDENTIAL & PROPRIETARY

state or the detection of a device condition which requires attention (e.g., head of form on the printer).

The request encoder indicates when a channel request is active. It also sets up the priorities so that any Megabus request has priority over a channel data service request. A similar request from channel 0 would have higher priority than a request from any of the higher channel numbers.

Firmware can test the output of the priority encoder to determine if a request has occurred. It also can test the encoder to ascertain if the request with the highest priority is a Megabus request or a channel request.

The priority encoder has two outputs which are a binary function of the highest priority channel. These lines are used to enable a single adapter at a time corresponding to the appropriate channel. One exception occurs when the Master Clear signal is active: all the adapters are enabled simultaneously to receive the Master Clear signal.

#### 2.3.6 Test Multiplexer

Subsystem conditions, including status, errors, and register bits, can be examined by firmware via the test multiplexer. Firmware operations which regire the bypassing of the microoperation specify a signal and its condition for which a skip should occur. The test multiplexer provides the facilities for comparing the state of the specified signal with the state specified by the firmware. As a result, the instruction register is cleared for one cycle if the two conditions are equal.

#### 2.3.7 Clock Logic

The MTC divides the output of an 8-MHz oscillator to derive a 4-MHz clock cycle. The MTC is supplied with both the assertion and negation of the clock, each having a 250-nanosecond duration. Both of these signals are utilized by the MTC to implement logic in the first and the second 250-nanosecond periods of a single clock cycle. A third type of clock pulse is utilized by the MTC as a strobe pulse for the SPM, the adapters, and various other MTC registers. This strobe occurs during the latter part of the clock cycle and is only 35 to 55 nanoseconds in duration.

#### 2.4 OUTPUT DATA OPERATION

The following subsections describe the MTC hardware and firmware implemented when an output data operation is performed on a selected channel. The discussion centers around the data transfer path, although the firmware control, timing, and data verification checks required to execute the output data operation are also discussed. Two functions are required to complete an output data operation: software initiation and firmware control through hardware implementation.

#### 2.4.1 Software Initiation

Using the output function codes listed in Table 2-1 and the general bus formats illustated in Figure 2-2, the software is capable of initiating the output data operation. This is accomplished by sending the following control information from the central processor to the MTC for storage in the SPM: the configuration words (FC = 11 hex), the memory address (FC = 09 hex), and the range (FC = 0D hex).

At this point, software involvement is terminated if the addressed device is capable of only one functional operation (i.e., card reader). If the addressed device is capable of performing multiple functional operations (i.e., magnetic tape), software is required to make an additional transfer, the task word (FC = 07 hex), to the MTC for storage in the SPM.

After the last software transfer is completed, the remaining control of the output data operation is maintained by the MTC firmware.

#### 2.4.2 Firmware Control Through Hardware Implementation (See Figure 2-1)

Firmware is made aware that an output data operation is to be performed when a bus request is detected which is outputting control information. The control information on the data lines, as a result of the bus request from the central processor, is stored in the SPM in the locations specified by the function code.

With software initiation of the output data operation, either three or four bus transfers to the MTC are executed (refer to subsection 2.4.1). The control information transferred across the bus is the configuration words, the memory address, the range, and, if necessary, the task word. As each transfer occurs, the firmware stores the control information into the SPM of the MTC. Control of the remaining portion of the output data operation (the data transfer) is maintained by the firmware.

The firmware performs all the output data operations (write or print), status verification, channel validity, range determination, and device capabilities. The task is initiated by firmware loading the adapter's control registers with the control information previously stored in the SPM as a result of the software bus request. The adapter then generates requests for data, and the MTC firmware accesses memory, receives data, and transfers the data to the adapter using the hardware path shown in Figure 2-1. All data integrity checks performed on the

#### 2-8 HONEYWELL CONFIDENTIAL & PROPRIETARY

information sent to the adapters is accomplished by the adapter hardware or the device-specific firmware routines.

After detection of the data transfer termination (end of range), the firmware can report the operation's status to the software by generating a bus transfer. Using the transferred status, software then establishes if the operation was successful. Retries of unsuccessful operations are performed according to software parameters.

#### 2.5 INPUT DATA OPERATION

Software and firmware involvement in the input data operation is identical to the output data operation (refer to subsection 2.4). The variations of the input data operation are the hardware data paths between the Megabus and the adapter. The output data operation transfers data from the Megabus logic through the ALU and the SPM to the adapter, whereas the input data operation transfers information from the adapter through the ALU, the SPM, and the Megabus logic to the Megabus.

#### HONEYWELL CONFIDENTIAL & PROPRIETARY

2-9/2-10

٠  $\sum_{i=1}^{n}$ ٠ ,

# III THEORY OF OPERATION - INTERMEDIATE

The MTC is divided into seven fundamental logic areas. These primary areas and the data, instructions, and control flows are illustrated in Figure 3-1. The seven basic areas which comprise the MTC are:

- Microprogram Control Store

- Arithmetic Logic Unit and Accumulator

- Scratch Pad Memory and Addressing

- Test Multiplexer

- Megabus Logic

- Adapter Logic

- Clock Logic.

Each area is an arrangement of several functional components and is described in detail under its appropriate subsection heading.

#### 3.1 INTERFACE

The MTC contains two interface networks, one which allows connection to the Megabus and one which allows attachment of a variable configuration of device adapters.

#### 3.1.1 Megabus/MTC Interface

The MTC/Level 6 Megabus interface is the control and transfer link between the MTC and any other unit within the system. It provides a path for address, data, and control information. This inteface also supplies the paths for determining the priority of

HONEYWELL CONFIDENTIAL & PROPRIETARY

×

\*

3-2

HOMEYWELL CONFIDENTIAL & PROPRIETARY

...

.

a request from any attached controller. Figure 3-2 identifies all the interface lines and their direction, usage, and mnemonics. Table 3-1 describes each signal line used by the Megabus/MTC interface.

#### 3.1.2 MTC/Adapter Interface

Figure 3-3 identifies the MTC/adapter interface lines and their direction, mnemonics, and usage. It depicts the lines as seen from the MTC (not from the adapter, where many of the lines have other mnemonics). Table 3-2 describes each signal line used by the MTC/adapter interface. For a cross-reference of signal names, refer to Table 3-3.

This interface links all three adapters and enables the firmware to select the proper adapter and perform the designated operation. It provides the paths necessary to supply the adapters with data, control, and timing pulses; it also supplies the MTC with requests and data from the adapter.

3.2 MICROPROGRAM CONTROL STORE FUNCTIONAL COMPONENTS (Figure 3-4)

#### 3.2.1 Subroutine Return Address Register (SRAR)

The SRAR is used by firmware to store a microprogram control store (UPCS) address which will be branched to at some later time by a firmware routine or subroutine. To load a location with an address, the firmware issues a Load Return Address command, which generates the write enable function LDSRAR-. This causes the address defined by bits 4 through 15 of the microprogram instruction register (UPIR) to be stored in the SRAR at the location specified by the SPM address selection bits (SPMAS0+, SPMAS1+).

The SRAR is a 4-word by 12-bit register file memory. Each word represents the return address of a particular adapter channel. The SRAR word that is being read or written is determined by the output of the Scratch Pad Memory Index Register (SPMIR0- and SPMIR1-). The Scratch Pad Memory Index Register (SPMIR) contains the number of one of the four device channels in binary code (see subsection 3.4.4).

When firmware performs a Return Branch command, the contents of the location defined by SPMASO+ and SPMASI+ are gated to the SRAR output. The output is then transferred by way of the microprogram address selector (UPAS) to the microprogram address counter (UPAC). Utilizing the Return Branch command, the UPAC is preset to an address previously stored in the SRAR.

|         | Λ                           |                        |        |

|---------|-----------------------------|------------------------|--------|

|         | BSDT00-THRU 15-,BSDP00-,BSD | PO8-,DATA+PARITY LINES |        |

|         | N                           |                        |        |

|         | BSAD00-THRU 23-,BSAP00- ADI | DRESS+PARITY LINES     | K      |

|         | V                           |                        | ~      |

|         | BSAUOK+ THRU BSIUOK+        | PRIORITY LINES         | $\sim$ |

|         | BSMYOK+                     | MY OK                  |        |

|         | BSPWON+                     | POWER ON               |        |

|         | BSQLTA+ (XNU)               | LOGIC TEST ACTIVE      |        |

|         | BSQLTO+                     | LOGIC TEST OUT         |        |

|         | BSQLTI+                     | LOGIC TEST IN          |        |

|         | BSACKR+                     | ACKNOWLEDGE            |        |

|         | BSDCNN-                     | DATA CYCLE NOW         |        |

|         | BSTIMR+ (XNU)               | 60 - HZ SQUARE WAVE    |        |

|         | BSYELO-                     | YELLOW (ERROR)         |        |

|         | BSREDD-                     | RED (ERROR)            |        |

|         | BSBYTE-                     | ВҮТЕ                   |        |

| LEVEL 6 | BSMREF-                     | MEMORY REFERENCE       | мтс    |

| MEGABUS | BSDTOA- (GND)               | DATA BIT A             |        |

|         | BSDTOB- (GND)               | DATA BIT B             |        |

|         | BSWAIT-                     | WAIT                   |        |

|         | BSNAKR-                     | NO ACKNOWLEDGE         |        |

|         | BSREQT-                     | BUS REQUEST            |        |

|         | BSSHBC-                     | SECOND HALF BUS CYCLE  |        |

|         | BSLOCK- (XNU)               | LOCK                   |        |

|         | BSWRIT-                     | BUS WRITE              |        |

|         | BSMCLR-                     | MASTER CLEAR           |        |

|         | BSRINT-                     | RESUME INTERRUPT       |        |

|         | ZVP18- (XNU)                | +18 VOLTS              |        |

|         | ZGND                        | GROUND                 |        |

|         | ZVP12                       | +12 VOLTS              |        |

|         | ZVP05                       | +5 VOLTS               |        |

|         | ZVN12                       | -12 VOLTS              | *      |

|         | BSSPR1- THRU 4-             | SPARE LINES            | K      |

NOTE: XNU = NOT USED

Figure 3-2 Megabus/MTC Interface

# HONEYWELL CONFIDENTIAL & PROPRIETARY

3-4

# Table 3-1 Megabus/MTC Interface Signal Lines (Sheet 1 of 2)

(

| TERM/MNEMONIC                                   | DESCRIPTION                                                                                                                                                                                |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Bits 0 to 7<br>(BSDT00- to 07-)            | These 8 data bit lines represent the most significant byte of data.                                                                                                                        |

| Data Bits 8 to 15<br>(BSDT08- to 15-)           | These 8 data bit lines represent the least significant byte of data.                                                                                                                       |

| Data Parity - Left<br>Byte (BSDP00-)            | This signal contains odd parity for data bits 0 through 7.                                                                                                                                 |

| Data Parity - Right<br>Byte (BSDO08-)           | This signal contains odd parity for data<br>bits 8 through 15.                                                                                                                             |

| Address Bus Bits<br>0 to 23<br>(BSAD00- to 23-) | These 24 address bit lines contain an address to be used by memory or by a controller or central processor.                                                                                |

| Address Parity<br>(BSAP00-)                     | This signal contains odd parity for the<br>most significant byte of the address bus,<br>bits 0 through 7.                                                                                  |

| Priority Lines<br>(BSAUOK+ to<br>BSIUOK+)       | These lines are used to establish priority of the units attached to the Megabus.                                                                                                           |

| My Ok<br>(BSMYOK+)                              | This signal indicates the unit that is presently using the Megabus.                                                                                                                        |

| Power On<br>(BSPWON+)                           | This signal is true when all power<br>supplies in the system are operating<br>correctly.                                                                                                   |

| Logic Test In<br>(BSQLTI+)                      | This signal initiates the Internal Logic<br>Test in a unit attached to the Megabus.                                                                                                        |

| Logic Test Out<br>(BSQLTO+)                     | This signal indicates the unit has suc-<br>cessfully completed running its Internal<br>Logic Test and is used as the Logic Test<br>In signal for the next unit attached to<br>the Megabus. |

| Acknowledge<br>(BSACKR+)                        | This signal indicates that the information on the Megabus has been accepted.                                                                                                               |

| Data Cycle Now<br>(BSDCNN-)                     | This signal indicates that the information on the bus is valid.                                                                                                                            |

# Table 3-1 Megabus/MTC Interface Signal Lines (Sheet 2 of 2)

| TERM/MNEMONIC                      | DESCRIPTION                                                                                                                                     |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Yellow<br>(BSYELO-)                | This signal indicates that the accompany-<br>ing transferred information is correct but<br>that a memory correction operation was<br>performed. |  |  |  |

| Red<br>(BSREDD-)                   | This signal indicates that the accompany-<br>ing transferred information is in error.                                                           |  |  |  |

| Byte<br>(BSBYTE-)                  | This signal indicates that the current<br>transfer is a byte transfer rather than a<br>word transfer.                                           |  |  |  |

| Memory Reference<br>(BSMREF-)      | This signal indicates that the address<br>leads contain a memory address.                                                                       |  |  |  |

| Wait<br>(BSWAIT-)                  | This signal indicates that the transfer<br>will be accepted when the Megabus data<br>register is available.                                     |  |  |  |

| No Acknowledge<br>(BSNAKR-)        | This signal indicates that the information on the Megabus has been refused.                                                                     |  |  |  |

| Bus Request<br>(BSREQT-)           | This signal indicates that one or more<br>units on the Megabus have requested a bus<br>cycle.                                                   |  |  |  |

| Second Half Bus<br>Cycle (BSSHBC-) | This signal identifies the second bus<br>cycle in response to a memory read<br>request.                                                         |  |  |  |

| Bus Wríte<br>(BSWRIT-)             | This signal indicates that information on the Megabus is ready to be transferred.                                                               |  |  |  |

| Master Clear<br>(BSMCLR-)          | This signal initializes the units attached to the Megabus.                                                                                      |  |  |  |

| Resume Interrupt<br>(BSRINT-)      | This signal is a 200-nanosecond pulse<br>which is issued by the central processor<br>when it is capable of receiving interrupts<br>again        |  |  |  |

|     | 1                       |                   |          |

|-----|-------------------------|-------------------|----------|

|     |                         |                   |          |

|     | ADAPTER ENABLE          | ADPENB+01 THRU 03 |          |

|     | CONTROL LINES           | ADPCD1+ THRU 3+   |          |

|     | LOAD STATUS             | LODAS1+ AND 2+    |          |

|     | LOAD DATA REGISTER      | LODADR+           |          |

|     | DATA BYTE TAKEN         | ADPDBT+           |          |

|     | MULTIPLEXER SELECT      | UPIR04+ AND 5+    |          |

|     |                         |                   |          |

|     | DATA OUT LINES          | ALUOTO+ THRU 7+   |          |

| F   | CLOCK SIGNAL            | CLKSIG+           |          |

|     | CLOCK STROBE            | CLKSTB+           |          |

| МТС | ADAPTER PULSE           | ADPPLS+           | ADAPTERS |

|     | CLEAR ADAPTER           | CLRADP+           |          |

|     | GROUND                  | ZGND              |          |

|     | +5 VOLTS                | ZVP05             |          |

|     | +12 VOLTS               | ZVP12             |          |

|     | -12 VOLTS               | ZVN12             |          |

| Г   | ADAPTER PRESENT         | ADPGND-           |          |

|     | Λ                       |                   |          |

|     | DATA IN LINES           | ADPDS0+ THRU 7+   |          |

|     | DATA SERVICE REQUEST    | DATSRQ+           |          |

|     | NONDATA SERVICE REQUEST | NDTSRQ+           |          |

|     |                         |                   |          |

|     |                         |                   |          |

|     |                         |                   |          |

(

Figure 3-3 MTC/Adapter Interface

# Table 3-2 MTC/Adapter Interface Signal Lines (Sheet 1 of 2)

.

| TERM/MNEMONIC                          | DESCRIPTION                                                                                                                                                        |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Adapter Enable<br>(ADPENB+01 to +03)   | The Magnetic Tape Adapter uses these 3<br>lines as device selection bits. The low-<br>speed device adapters use these lines as<br>enables for the device adapters. |  |  |  |  |

| Control Lines<br>(ADPCDl+ to 3+)       | These 3 signals are used for adapter-<br>specific operations.                                                                                                      |  |  |  |  |

| Load Status<br>(LODAS1+ to 2+)         | These 2 signals to the device adapter are<br>used to load data in the control registers<br>of the device adapter.                                                  |  |  |  |  |

| Load Data<br>(LODADR+)                 | This signal is used to load data in the data register of the device adapter.                                                                                       |  |  |  |  |

| Data Byte Taken<br>(ADPDBT+)           | This signal notifies the device adapter<br>that the contents of its data register<br>have been stored.                                                             |  |  |  |  |

| Multiplexer Select<br>(UPIR04+ to 05+) | These 2 signals are the selection bits for the input multiplexer of the device adapter.                                                                            |  |  |  |  |

| Data Out Lines<br>(ALUOT0+ to 7+)      | These 8 data lines from the MTC to the device adapter represent the information to be used by the adapter.                                                         |  |  |  |  |

| Clock Signal<br>(CLKSIG+)              | A clock function from the MTC to the device adapter.                                                                                                               |  |  |  |  |

| Clock Strobe<br>(CLKSTB+)              | A clock function from the MTC to the device adapter.                                                                                                               |  |  |  |  |

| Clear Adapter<br>(CLRADP+)             | This signal clears the major logic areas of the adapter.                                                                                                           |  |  |  |  |

| Adapter Present<br>(ADPGND-)           | This signal notifies the MTC that an adapter is present by indicating a ground connection.                                                                         |  |  |  |  |

| Data In Lines<br>(ADPDS0+ to 7+)       | These 8 data lines from the device adapter<br>to the MTC represent the information to be<br>used by the MTC.                                                       |  |  |  |  |

| Data Service<br>Request (DATSRQ+)      | This signal notifies the MTC that the<br>device adapter has a data byte ready or<br>that a data byte is required.                                                  |  |  |  |  |

# Table 3-2 MTC/Adapter Interface Signal Lines (Sheet 2 of 2)

| TERM/MNEMONIC                        | DESCRIPTION                                                                                                                                   |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Nondata Service<br>Request (NDTSRQ+) | This signal notifies the MTC that the<br>device adapter has a nondata service<br>request to be processed (e.g., a change<br>in device state). |  |

| Adapter Pulse<br>(ADPPLS+)           | This signal is used by the printer device<br>adapter to generate a strobe for the<br>printer                                                  |  |

|                         |              | ADAPTER      |            |            |

|-------------------------|--------------|--------------|------------|------------|

| MTC                     |              | TAPE         | READER     | PRINTER    |

| FUNCTION                | MNEMONIC     | MNEMONIC     | MNEMONIC   | MNEMONIC   |

| Adapter Enable          | ADPENB+01+03 | ADPENB+01+03 | ADPENX     | ADPENX     |

| Control Lines           | ADPCD1+      | ADPCD1+      | XNU        | XNU        |

|                         | ADPCD2+      | ADPCD2+      | XNU        | XNU        |

| Control Lines           | ADPCD3+      | ADPCD3+      | XNU        | XNU        |

| Load Status l           | LODAS1+      | LODAS1+      | ADPCN1+    | ADPCN1+    |

| Load Status 2           | LODAS2+      | LODAS2+      | ADPCN2+    | ADPCN2+    |

| Load Adapter Data       | LODADR+      | LODADR+      | XNU        | ADPDAT+    |

| Data Byte Taken         | ADPDBT+      | ADPDBT+      | ADPDBT+    | XNU        |

| Data Out                | ALUOT0+→7+   | ALUOT0+→7+   | ALUOT0+→7+ | ALUOT0+→7+ |

| Multiplexer Select      | UPIR04+      | UPIR04+      | ADPIC0+    | ADPIC0+    |

| Multiplexer Select      | UPIR05+      | UPIR05+      | ADPIC1+    | ADPIC1+    |

| Data Service Request    | DATSRQ+      | DATSRQ+      | DATSRQ+    | DATSRQ+    |

| Nondata Service Request | NDTSRQ       | NDTSRQ+      | NDTSRQ     | NDTSRQ+    |

| Data In                 | ADPDS0+→7+   | ADPDS0+→7+   | INFOI0+→7+ | INFOI0+→7+ |

| Clock Signal            | CLKSIG+      | CLKSIG+      | XNU        | XNU        |

| Clock Strobe            | CLKSTB+      | CLKSTB+      | CLKSTB+    | CLKSTB+    |

| Adapter Pulse           | ADPPLS+      | ADPPLS+      | XNU        | ADPPLS+    |

| Adapter Present         | ADPGND-      | ADPGND-      | ZGND       | ZGND       |

| Clear Adapter           | CLRADP+      | CLRADP+      | ADPCLR+    | ADPCLR+    |

| Ground                  | ZGND         | ZGND         | ZGND       | ZGND       |

| +5 Volts                | ZVP05        | ZVP05        | ZVP05      | ZVP05      |

| -12 Volts               | ZVN12        | ZVN12        | ZVN12      | ZNV12      |

| +12 Volts               | ZVP12        | ZVP12        | ZVP12      | ZVP12      |

Table 3-3 MTC/Adapter Interface Line and Mnemonic Cross-Reference List

Note: XNU = Not used.

Figure 3-4 Microprogram Control Store Functionality

3-10

HOMEYWELL CONFIDENTIAL & PROPRIETARY

free constructions

.

#### 3.2.2 Microprogram Address Selector (UPAS)

The UPAS selects one of its two inputs to be used as a preset for the UPAC. When performing firmware operations with the output of the Microprogram Control Store bit 2 (UPCS02+) high, indicating a Go To command, the 12-bit output of the UPAS reflects bits 4 through 15 of the UPCS. When UPCS02+ is low, the 12 bits of the SRAR are selected for the UPAS outputs to implement a Return Branch command (RTN).

#### 3.2.3 Microprogram Address Counter (UPAC)

The UPAC is a 12-bit counter which is incremented once at the start of every clock cycle, except in the instance of a clear or load operation. The UPAC is cleared by CLRBCD-, which is active only during an MTC Initialize (Master Clear); it is loaded when a Load UPAC operation (LODUPA-) is active. The LODUPA- function causes the UPAC to reflect the address on the microprogram address selector (UPAS) output. The Load UPAC operation is performed when a Go To command or a Return Branch command is decoded in the address control logic.

The low-order nine bits (3 through 11) of the UPAC are gated directly to the address lines of the UPCS. The high-order three bits (0 through 2) are fed to the Microprogram Control Enable (UPCSE1- through UPCSE8-), which is a 3-bit to 1-of-8-line decoder. The eight UPCSE functions are used to enable one of the eight rows within the microprogram control store.

#### 3.2.4 Microprogram Control Store (UPCS)

For a description of the UPCS, shown in Figure 3-4, refer to subsection 2.3.1 of this manual.

#### 3.2.5 Diagnostic Instruction (Test) Gate

When the diagnostic mode is specified in the control word issued to the MTC by software, the MTC firmware executes a Set Test Mode (STMCMD-) command. This command sets the TSTMOD+ flipflop, which in turn puts the MTC clock in the step mode and disables the microprogram control store outputs. At this time the diagnostic instruction (test) gate is enabled, allowing the transfer of information from the bus data register to the ORing network of the microprogram control store. Any subsequent transfer to the MTC while the TSTMOD+ flip-flop is set generates one clock cycle. During this cycle the data on the Megabus is transferred by the test mode gate and the ORing network to the microprogram instruction register. It is then executed as if it were a resident firmware command.

The TSTMOD flip-flop remains set until software issues a Reset Test Mode (RTMCMD-) instruction or until a Master Clear signal occurs.

#### 3.2.6 Microprogram Instructon Register (UPIR)

The microprogram instruction register (UPIR) is a 16-bit wide register used to store the output of the microprogram control store (UPCS) or the test gate for one clock cycle during a microinstruction execution. The UPIR is loaded at the leading edge of each cycle by CLKSIG+ unless the signal Clear Microprogram Instruction Register (CLRUPI-) is active, which causes a reset to Zero. CLRUPI is active during the Master Clear operation and during a skipped cycle due to a successful test instruction.

#### 3.2.7 Op-Code Decoder (OPCOD)

The high-order three bits (UPIR00+ through UPIR02+) of the UPIR are fed to the op-code decoder, which performs a 3-bit to 1-of-8-lines decode. These lines indicate what type of firmware command is being performed. The op-code decoder is enabled unless the MTC is in the process of performing a UPCS scan or unless the UPIR is being cleared by the CLRUPI- function. The eight output lines of the op-code decoder, in conjunction with various other UPIR bits, implement and control the MTC and device adapter hardware.

To increase the speed of operation during the firmware routines, the op-code of the branch (Go To) command is decoded directly from the output of the UPCS rather than from the UPIR. For the same reason, the address for the Go To and Return command is taken from the output of the UPCS. For all other command types, the op-code is decoded from the output of the UPIR.

#### 3.2.8 Scan Logic (Figure 3-5)

The scan logic in the MTC ensures the integrity of the UPCS. This logic performs a longitudinal check on each bit position of the UPCS outputs and causes the MTC clock to halt if an error is detected. If no errors are detected, the MTC goes on to execute the firmware portion of the Quality Logic Test.

The Scan Mode flip-flop (SCNMOD+) sets with Master Clear (MSTCLR-), disabling the op-code decoder (see Figure 3-4) and inhibiting branch commands. With the commands inhibited, the MTC loads the UPIR with the output of the UPCS and increments the UPAC to the next location at each sequential clock cycle. This process continues from location 000 to location FFF, at which time a carry-out of the UPAC (UPAC2C-) is detected. The UPAC then returns to Zero, beginning another scan.

The scan bit selectors (SCNBSH+ and SCNBSL+) select one bit of the UPIR, using the output of the scan bit address counter as an address. The selected UPIR bit provides the input to the Scan Bit Sum flip-flop (SCNBSM+). The SCNBSM+ half adds the selected bit at the start of each clock cycle with its previous contents. At the end of one scan through the UPCS, the Scan Bit Sum flip-flop has added the specified bit of each location with an

Figure 3-5 Scan Logic

expected result of zero (no error). If the sum is not zero at the termination of each scan, the Scan Error gate output (SCNERR+) is high and sets the Scan Error flip-flop (UPIERR+). UPIERR- causes the MTC clock to halt, and the contents of the scan bit address counter indicates which bit column of the UPCS is in error.

If an error is not detected at the end of a scan, the scan bit address counter increments due to the overflow of the UPAC (UPAC2C-), and the UPAC wraps around to location 0. The scan operation is repeated with the next bit of the UPIR as an input to the Scan Bit Sum flip-flop. The scan operation continues until an error is detected or until all bits of the UPIR have been checked, at which time the scan bit address counter (SCNBAC+) overflows and resets the Scan Mode flip-flop. When the Scan Mode flip-flop is reset, the op-code decoder and branch commands are re-enabled, and normal execution of firmware begins.

## 3.3 ARITHMETIC LOGIC UNIT AND ACCUMULATOR FUNCTIONAL COMPONENTS

#### 3.3.1 A-Operand Multiplexer (ALUAX) (Figure 3-6)

The A-operand multiplexer (AOP MUX) selects one of five types of data fields according to a 3-bit multiplexer address defined by bits 3 through 5 of the UPIR. Table A of Figure 3-6 shows the various bit configurations and the selected register.

For addresses equal to 4 through 7, UPIR bit 3 set, the output of the adapter's data selector is used as an input to the AOP MUX. Bits 4 and 5 of the UPIR then select one of the four adapter registers visible to the MTC: data, ID, status 1, or status 2.

Only the adapter which is active has its data enabled at the selector output. The outputs of the adapter's data selectors are ORed on the MTC, and the ORed outputs are fed only to the AOP MUX.

The destinations of the 8-bit output of the AOP MUX are the ALU, the test multiplexer, the scratch pad memory, and the bus data register.

#### 3.3.2 B-Operand Multiplexer (ALUBX) (Figure 3-6)

The B-operand multiplexer (BOP MUX) selects one of four data fields as a B-input to the ALU. The BOP is defined during ALU commands by UPIR bits 6 and 7. When performing Constant commands, the BOP MUX selects the output of the UPIR bits 6 through 10, 12, 14, and 15 for the input to the ALU. These particular UPIR bits represent the data constant to be operated with during the Constant command.

The address for the data field to be loaded into the BOP MUX is a two-function decode (ALUBS1+, ALUBS2+) of the operation code (UPIR bits 0+ through 2+) and UPIR bits 6- and 7-. Table B of Figure 3-6 shows the four possible configurations of ALUBS1+ and ALUBS2+ and the data input selected.

#### 3.3.3 Arithmetic Logic Unit (ALU) (Figure 3-6)

The ALU performs an 8-bit arithmetic or logic operation on the data supplied by the AOP and BOP multiplexers. The type of operation performed is determined by the four mode signals (ALUMD3+, UPIR11+, ALUMD1+, UPIR13+), the carry enable function (ALUMCE-), and the carry input (ALUCIN-) to the ALU. Table 3-4 shows the relationship between these functions and the operations performed by the ALU.

These mode signals, as well as Carry Enable and Carry In, are explicitly defined by bits of the UPIR during ALU commands (opcode of 3). The firmware can also set Carry Enable.

TABLE C ALU CARRY FLIP-FLOP INDICATIONS ALU CARRY-OUT (ALUCOT+)

AOP AND BOP RELATIONSHIP

ALU CARRY-IN (ALUCIN-)

.

.

.

.