#

LEVEL 6

HARDWARE

TYPE MTM9102 NINE-CHANNEL NRZI TAPE ADAPTER MANUAL

This document and the information contained therein is confidential and proprietary to and the exclusive property of Honeywell Information Systems Inc. It is made available only to Honeywell authorized recipients for their use solely in the maintenance and operation of Honeywell products. This document and information must be maintained in strictest confidence; it must not be reproduced in whole or in part; and it shall not be disclosed to any other party without prior written consent of Honeywell.

This document and the information contained therein is confidential and proprietary to and the exclusive property of Honeywell Information Systems Inc. It is made available only to Honeywell authorized recipients for their use solely in the maintenance and operation of Honeywell products. This document and information must be maintained in strictest confidence; it must not be reproduced in whole or in part; and it shall not be disclosed to any other party without prior written consent of Honeywell.

> TYPE MTM9102 NINE-CHANNEL NRZI TAPE ADAPTER MANUAL

Document No. 71010282-200

Order No. FN18, Rev. 1

This manual has been revised to the -200 level. It supersedes all previous issues.

#### RECORD OF REVISIONS

| REVISION                                                                     | DATE      | AUTHORITY                                  | AFFECTED PAGES |  |  |

|------------------------------------------------------------------------------|-----------|--------------------------------------------|----------------|--|--|

| -100                                                                         | Nov. 1976 | Original issue                             | -              |  |  |

| -200                                                                         | July 1977 | BLCOS 61787,<br>61873, 70299,<br>and 70395 | Entire manual  |  |  |

|                                                                              |           |                                            |                |  |  |

|                                                                              |           |                                            |                |  |  |

|                                                                              |           |                                            |                |  |  |

|                                                                              |           |                                            |                |  |  |

|                                                                              |           |                                            |                |  |  |

|                                                                              |           |                                            |                |  |  |

|                                                                              |           |                                            |                |  |  |

| Hardware Publications, M&TO, Billerica, MA 01821                             |           |                                            |                |  |  |

| Printed in the United States of America0282/FN18All rights reserved0282/FN18 |           |                                            |                |  |  |

#### CONTENTS

C

Section

Ι

Page

| I   | INTRODU | JCTION              |                                 |                         | 1-1   |  |  |

|-----|---------|---------------------|---------------------------------|-------------------------|-------|--|--|

|     | 1.1     | General I           | Description                     |                         | 1-1   |  |  |

|     | 1.2     |                     | al Character                    | rs                      | 1-3   |  |  |

|     |         | 1.2.1               | Magnetic Ta                     | ape Controller          | 1-3   |  |  |

|     |         | 1.2.2               | MTM9102 Nin                     | ne-Channel Tape Adapter | r 1-4 |  |  |

|     |         | 1.2.3               | Nine-Channe                     | el NRZI Tape Devices    | 1-4   |  |  |

|     | 1.3     |                     |                                 |                         |       |  |  |

| 1.4 |         | naracterist:        |                                 | 1-4<br>1-6              |       |  |  |

|     |         | 1.4.1               | Tape Charad                     |                         | 1-6   |  |  |

|     |         |                     | Tape Format                     |                         | 1-6 , |  |  |

|     | 1.5     | Interface           |                                 |                         | 1-10  |  |  |

|     | 1.6     | Options             |                                 |                         | 1-10  |  |  |

|     | 1.7     | Reference Documents |                                 |                         |       |  |  |

| II  | THEORY  | OF OPERAT           | TON                             |                         | 2-1   |  |  |

|     | 2.1     | Software            | 11011                           |                         | 2-1   |  |  |

|     |         | 2.1.1               | I/O Command                     | d Set                   | 2-1   |  |  |

|     |         | 2.1.2               |                                 | stem Device Commands    | 2-3   |  |  |

|     | 2.2     |                     | Into pasel.                     |                         | 2-6   |  |  |

|     | 2.3     | Hardware            | Overview De                     | escription              | 2-6   |  |  |

| 2.5 |         | 2.3.1               |                                 | Description             | 2-10  |  |  |

|     |         | 2.3.2               | Read Path Functional Components |                         | 2-16  |  |  |

|     |         | 2.3.3               | Write Path                      |                         | 2-16  |  |  |

|     |         | 2.3.4               | Write Clock Logic               |                         | 2-17  |  |  |

|     |         | 2.3.5               |                                 |                         | 2-17  |  |  |

|     |         | 2.3.6               |                                 |                         |       |  |  |

|     |         | 2.3.7               | Control Loo                     |                         | 2-18  |  |  |

|     | 2.4     |                     | iate Hardware Description       |                         | 2-18  |  |  |

|     |         | 2.4.1               | Write Opera                     | ations                  | 2-18  |  |  |

|     |         |                     | 2.4.1.1                         | Write Control Logic     | 2-19  |  |  |

|     |         |                     | 2.4.1.2                         | Write Clock Logic       | 2-21  |  |  |

|     |         |                     | 2.4.1.3                         | Write Initiation        | 2-24  |  |  |

|     |         |                     | 2.4.1.4                         | Write Data Path         | 2-24  |  |  |

|     |         |                     | 2.4.1.5                         | Write Termination       | 2-27  |  |  |

|     |         | 2.4.2               | Read Operat                     | tion                    | 2-29  |  |  |

|     |         |                     | 2.4.2.1                         | Read Control Logic      | 2-29  |  |  |

| 4   |         |                     | 2.4.2.2                         | Read Initiation         | 2-29  |  |  |

|     |         |                     | 2.4.2.3                         | Read Data Path          | 2-30  |  |  |

|     |         |                     | 2.4.2.4                         | Read Termination        | 2-35  |  |  |

|     |         | 2.4.3               | Rate Error                      | Detection               | 2-36  |  |  |

#### CONTENTS

| Section |                             |                                                   |                                                                                                     |                                                                                                                                                | Page                                                                             |

|---------|-----------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

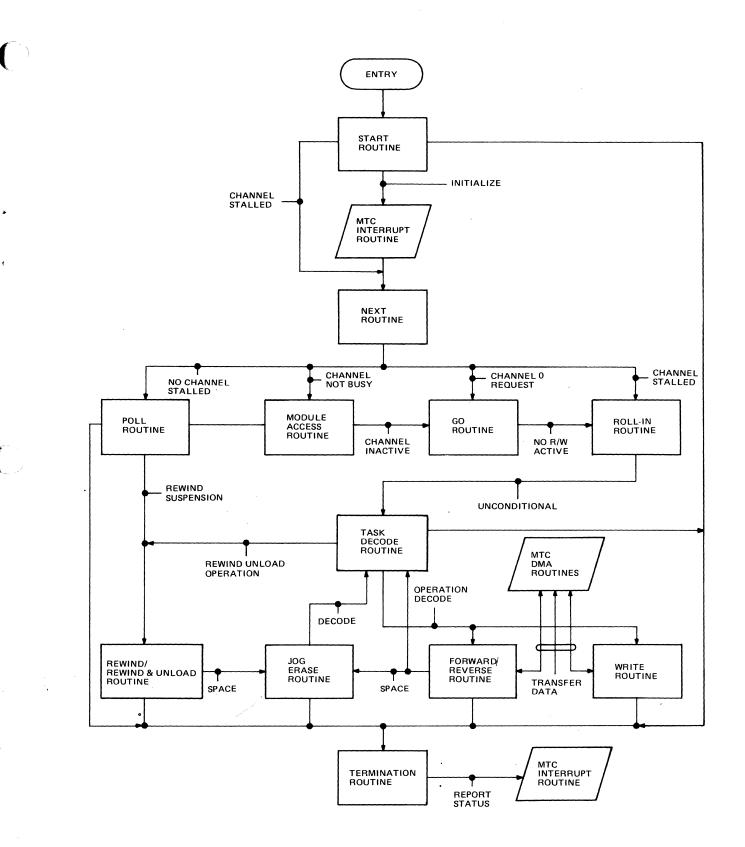

| III     | THEORY<br>3.1<br>3.2<br>3.3 | Firmware<br>Scratch<br>Firmware<br>3.3.1<br>3.3.2 | Overview<br>Process Ma<br>3.3.2.1<br>3.3.2.2<br>3.3.2.3<br>3.3.2.4<br>3.3.2.5<br>3.3.2.6<br>3.3.2.7 | nagement Routines<br>Start Routines<br>Next Routine<br>Go Routines<br>Module Access Routines<br>Roll-In Routine<br>Poll Routine<br>Task Decode | 3-1<br>3-2<br>3-2<br>3-2<br>3-2<br>3-3<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4 |

|         |                             | 3.3.3                                             | Execution                                                                                           | Routines                                                                                                                                       | 3-4                                                                              |

#### ILLUSTRATIONS

| Figure                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                                                             |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8                        | Nine-Channel NRZI Tape Adapter Subsystem Block<br>Diagram<br>Tape Adapter to First Tape Device Cabling<br>Nine-Track Tape Layout<br>BOT and EOT Formats<br>NRZI Tape Data Recording<br>Data Block Format<br>Tape Mark Format<br>MTC/Tape Adapter/Tape Device Interfaces                                                                                                                                                                                                                                    | 1-2<br>1-3<br>1-6<br>1-7<br>1-7<br>1-8<br>1-9<br>1-10                                                                            |

| 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-13 2-14 2-15 2-16 2-17 | Tape Adapter Major Block Diagram<br>Output Task Word I/O Command<br>Tape Adapter Intermediate Block Diagram<br>Input Multiplexer Data Structure<br>MTC/Tape Adapter/Tape Device Interfaces<br>Adapter and Controller Interface<br>Adapter and Tape Device Interface<br>Adapter Selection Logic<br>Subcommand Generator<br>Control Registers 1 and 2<br>Write Clock Logic<br>Write Data Path<br>End of Write Logic<br>Read Operation<br>Data Request Logic<br>End-of-Read/RAW Logic<br>Rate Error Detection | 2-2<br>2-3<br>2-7<br>2-9<br>2-10<br>2-11<br>2-12<br>2-20<br>2-22<br>2-23<br>2-25<br>2-25<br>2-28<br>2-31<br>2-33<br>2-37<br>2-39 |

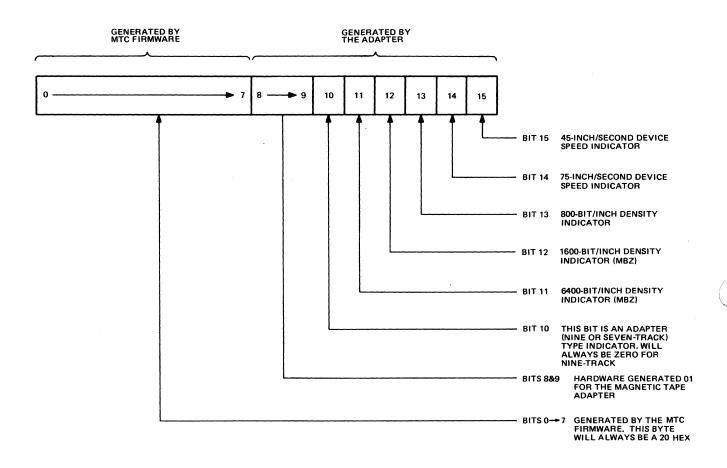

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7                               | Scratch Pad Memory<br>Configuration Word 1 Bit Significance<br>Adapter/MDC Status Relationship<br>Task Queue/Task Pointer Relationship<br>Channel Mask Magnetic Tape Application<br>Device Identification Word<br>Nine-Channel Tape Adapter Overview Flow Chart                                                                                                                                                                                                                                            | 3-5<br>3-9<br>3-10<br>3-11<br>3-11<br>3-12<br>3-13                                                                               |

#### TABLES

| Table |                                            | Page |

|-------|--------------------------------------------|------|

| 2-1   | Tape Adapter Major Block Diagram           | 2-2  |

| 2-2   | Tape Adapter/Device Interface Signal Lines | 2-13 |

| 3-1   | Scratch Pad Memory Topology                | 3-6  |

| 3-2   | SPM Word Description                       | 3-7  |

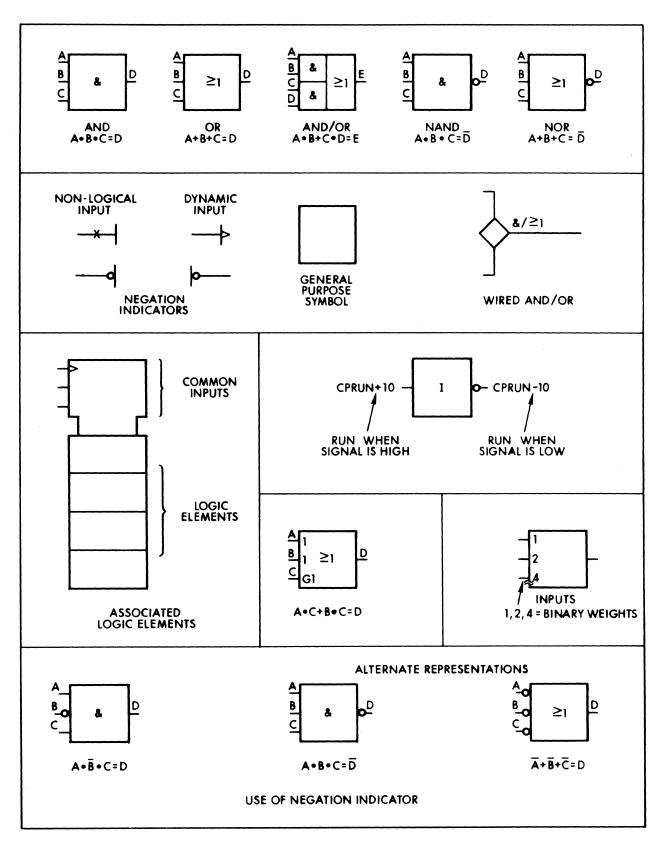

LOGIC SYMBOLOGY

vi

## INTRODUCTION

This product manual describes the functionality and operation of the Type MTM9102 Nine-Channel NRZI Tape Adapter, the adapter/ device-specific software and the tape medium formats. Since the adapter is designed for use with the Type MTC9101 Magnetic Tape Controller (MTC), this unique firmware for both the adapter and controller is described in this manual. The operational theory within this document acquaints the reader with the functional logic areas of the adapter at both the major and intermediate levels. Refer to the adapter reference manual (listed in subsection 1.7) for detailed logic block diagrams and physical location information.

#### 1.1 GENERAL DESCRIPTION

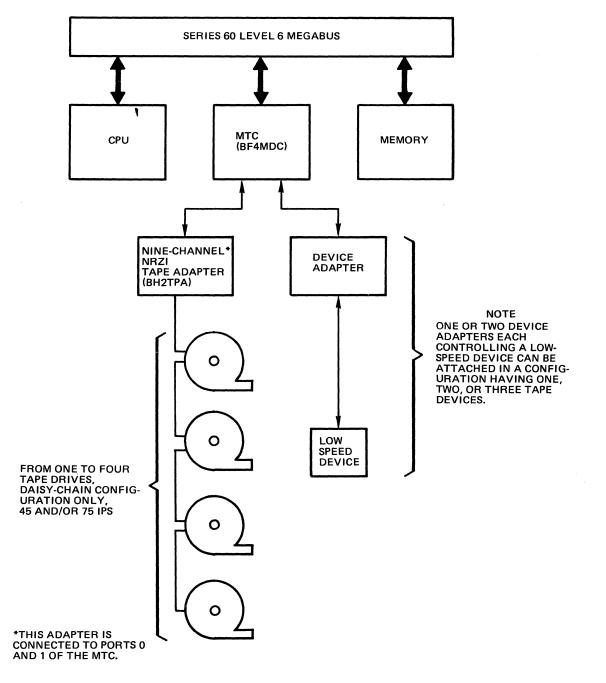

The MTM9102 Nine-Channel NRZI Tape Adapter (subsequently referred to in this manual as the tape adapter) is a solid-state module (BH2TPA) which, used in conjunction with the magnetic tape controller (BF4MDC), can operate up to four daisy-chained, ninechannel tape devices in Model 34 or 36 configurations of the Series 60 Level 6 computer system. The magnetic tape subsystem, whose attachment configuration is illustrated in Figure 1-1, uses ½-inch magnetic tape for storage and retrieval of NRZI-formatted data. Regardless of the number of drives connected to the tape adapter, only one tape adapter can be utilized with a single controller.

Figure 1-1 Nine-Channel NRZI Tape Adapter Subsystem Block Diagram

The tape adapter consists of dual in-line packages (DIPs) mounted on a double-size Series 60 Level 6 Device-Pac assembled by utilizing printed wiring techniques. The tape adapter is mounted on the MTC package and is plugged into its two 25-pin, in-line connectors. The first rack-mounted nine-channel tape device attaches to the tape adapter via a single cable which has multiple connectors on each end as shown in Figure 1-2. Each subsequent tape device attached to the subsystem uses daisy-chain cabling from the previous device. Individual tape devices derive their power from a power supply located within the device itself.

1-2

Figure 1-2 Tape Adapter to First Tape Device Cabling

#### 1.2 FUNCTIONAL CHARACTERS

The tape adapter provides the device-specific hardware which, in conjunction with the tape adapter firmware (physically located in the MTC), enables the MTC to control the positioning and the reading/writing of data at various tape speeds on the device in NRZI data format at an 800-bpi density.

#### 1.2.1 Magnetic Tape Controller

The MTC is a microprogrammed peripheral device control unit which, together with the tape adapter, supports from one to four tape devices. Much of the microprocessor portion of the MTC is generalized to facilitate its application as a control element for various unit record and magnetic tape device adapters. The MTC performs the following general purpose control functions:

- Execution of the Series 60 Level 6 Megabus network sequences

- Command decoding

- Status and control register storage

- Data transfer multiplexing to devices/adapters

- Direction of the general flow of command execution.

#### 1.2.2 MTM9102 Nine-Channel Tape Adapter

The tape adapter can support from one to four nine-channel magnetic tape devices. It is attached to these devices via a device level interface (DLI) which allows the intermixing of 45and 75-ips device speeds. The tape adapter performs the following device-specific functions:

- Controls device interface dialogs

- Generates vertical and longitudinal parity and the CRC character

- Verifies data integrity

- Detects noise and dropped characters from tape

- Detects tape marks

- Allows data to be wrapped from the MTC to the DLI and back to the MTC.

#### 1.2.3 Nine-Channel NRZI Tape Drives

The ½-inch magnetic tape devices are capable of reading or writing nine-channel American National Standard ½-inch magnetic tape at a speed of 45 or 75 ips. (These devices are purchased by Honeywell.)

The tape device performs the following basic functions:

- Receive and generate control signals for device operation

- Position the tape at the beginning of tape marker

- Put the device in an off-line state

- Write data received from the adapter onto tape

- Read data from tape and send it to the adapter

- Perform all digital-analog and analog-digital conversions required for read/write operations.

#### 1.3 SUBSYSTEM OPERATIONAL SUMMARY

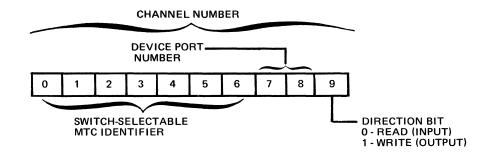

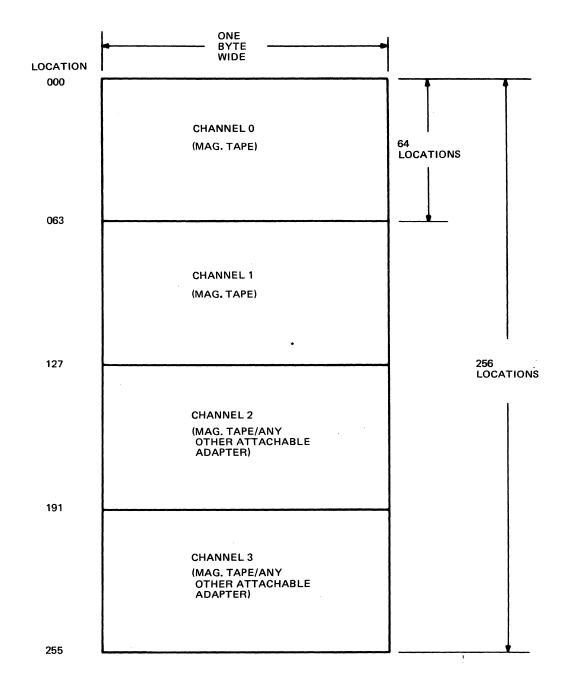

Each device attached to the MTC by way of an adapter is addressable by software via channel numbers. A device has two channel numbers assigned, with the numbers differing only in the low-order bit position (called the direction bit). When an I/O Load (IOLD) command for a device is accepted, the direction bit of the channel number specifies whether the command is for an input or output data transfer. The direction bit of a subsequently accepted Output Task Word command is examined to verify that it agrees with the IOLD's direction bit. The following example indicates the composition of a channel number, where bits 0 through 6 are assigned at system installation.

Software usability of the devices attached to the MTC is such that the devices are, in general, independent of one another. For example, operations on one device are independent of the activity of any other device except that the MTC can stall the initiation of a command sequence addressed to one device (channel number) while the MTC is servicing another device. This apparent device independence looks, to software, as if multiple levels of simultaneity exist.

The tape subsystem command sequencing results in any command addressed to a nonbusy channel being accepted, allowing the MTC to accept any command to a tape device while another tape device is executing a data transfer. The accepted command is not invoked until the present data transfer is completed. Only rewind and rewind/unload commands are executed concurrently with data transfer operations. Because channels are serviced on a rotating priority basis, no one channel can dominate adapter usage.

If a tape adapter has fewer than four devices attached, it responds only to channel numbers associated with the installed devices. When a configuration of tape devices is fewer than four, one or two unit record adapters can be implemented by the MTC.

To allow for tape access, the MTC contains a set of softwareloadable scratch pad memory locations (refer to Section III of this manual). These locations are assigned to each tape device and contain parameters and control information required for tape operation. In addition to range and address locations, there is a configuration location which contains the mode of operation information, and there is a task word location which stores the command codes.

To perform a specific operation, the software first loads the configuration (and then the address and range) into the scratch pad memory. The task word, which is loaded last, designates the operation to be performed. Upon receipt of the task word, execution of the command is initiated.

1-5

Commands addressed to a nonbusy tape device (channel) are always accepted, although their execution can be delayed as previously described. All commands addressed to a busy tape device are rejected (NAK response on the Megabus) with the exception of the Output Control Word command.

#### 1.4 MEDIUM CHARACTERISTICS/FORMATS

#### 1.4.1 Tape Characteristics

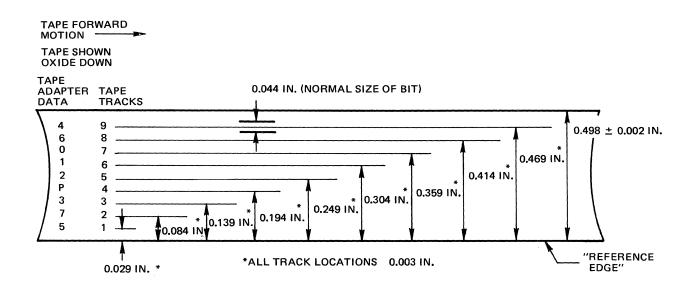

Certain physical relationships and data layout dimensions are maintained when nine-channel tape is implemented as the recording medium on the nine-channel tape adapter subsystem. Optimum physical dimensions of the tape and the correlation between tape adapter data bits and tape tracks are shown in Figure 1-3.

Figure 1-3 Nine-Track Tape Layout

#### 1.4.2 Tape Formats

#### Beginning and End of Tape

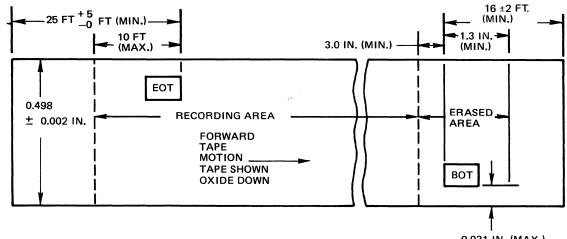

Each tape used on the nine-channel tape adapter subsystem has two markers (see Figure 1-4): a beginning-of-tape (BOT) marker affixed near the reference edge at the start of the tape and an end-of-tape (EOT) marker on the opposite edge at the trailing end of the tape reel. To ensure maximum reliability in the storage of data, an erased area must be maintained at the BOT marker and an unrecorded area is left after the EOT marker.

0.031 IN. (MAX.)

#### Figure 1-4 BOT and EOT Formats

#### Non-Return-to-Zero-Inverted (NRZI) Data Recording

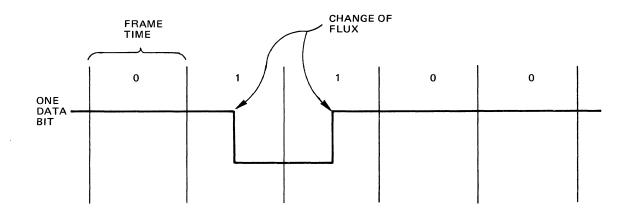

In NRZI coding, the logic One bits are reflected on the tape adapter/tape device interface lines as a ground level and the logic Zero bits as a high voltage. However, when recording data on the tape, a logic One is represented by a change of flux during a frame time and a logic Zero as no change of flux (see Figure 1-5) during a frame time.

Figure 1-5 NRZI Tape Data Recording

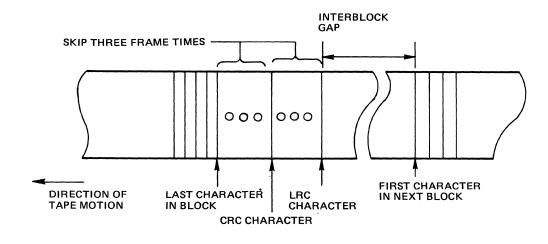

The data from the tape adapter is formatted and recorded on the tape in blocks. Each block consists of a variable data field, a cyclic redundancy check (CRC) character, and a longitudinal redundancy check (LRC) character. The CRC character is positioned

1-7

four frame times after the final data byte, and the LRC character must occur four frame times after the CRC. Figure 1-6 shows the relationship between two sequential blocks of data indicating the nominal interblock gap.

#### Beginning-of-Tape (BOT) Gap

As shown in Figure 1-4, an erased section of tape must surround the BOT marker. This erased section serves as a defined area in which a read operation can begin. The total erased area is approximately 4.3 inches; it starts a minimum of 1.3 inches prior to the occurrence of the BOT marker and extends for a minimum of 3 inches beyond the marker.

#### Interblock Gaps

Interblock gaps are areas of tape between data blocks without data, where all tracks are restored to the erase polarity. The nominal length of the gap is 0.6 inch (see Figure 1-6) with a minimum length of 0.5 inch and a maximum length of 25 feet.

#### Tape Marks

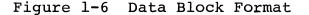

A tape mark character (13 hexadecimal) is distinctive in that it is a single character block followed by seven frame times and then the LRC character. Figure 1-7 shows the relationship between the tape mark character, its check character, and another data block.

Figure 1-7 Tape Mark Format

#### Vertical Parity

The nine-channel tape adapter subsystem uses eight tracks for data recording and the remaining track for a parity bit. When performing a write operation, odd parity is generated on the data coming from the MTC. This parity bit accompanies the data to the device and is written in the track shown in Figure 1-3.

When executing a read operation or a read after write (RAW), the parity read from the device is compared against a new parity bit generated on the data byte read from the device. When a nocompare condition arises, the parity error bit is set in the adapter status. However, if an even number of bits in the data byte are dropped or picked up, vertical parity will not detect this condition. Therefore, two other data integrity checks are performed by the tape adapter: CRC and LRC.

#### Cyclic Redundancy Check (CRC) Character

The CRC character is derived by the adapter hardware and, along with the vertical parity and LRC character, minimizes the possibility of undetected data errors. This character is written on the tape four frame times after the last data byte, as shown in Figure 1-6.

#### Longitudinal Redundancy Check (LRC)

The LRC character is written on tape following the data portion of each block. It is separated from the end of the data by the CRC character and six skipped frame times as shown in Figure 1-6. The LRC character has one bit per track and is calculated so that an even number of One bits including those of the data, CRC, and LRC are received in each track of a data block. During a read operation an error is detected if the parity is odd in any track. The possibility of not detecting a data error still exists if an even

number of bits is dropped or picked up in a given track. However, when this check is combined with the CRC, the vertical parity check, and the dropped frame check, the probability of not detecting an error is minimal.

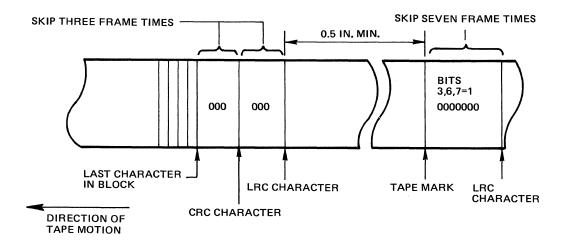

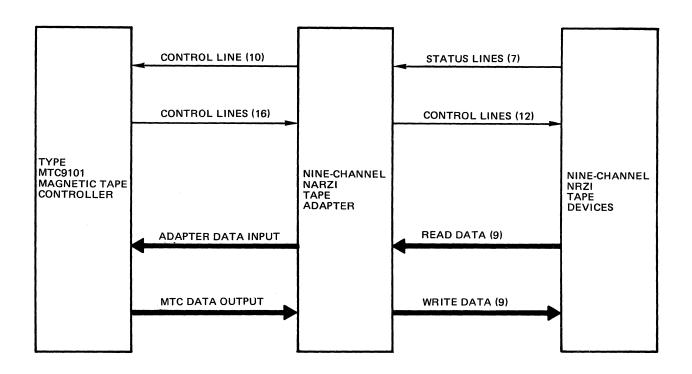

#### 1.5 INTERFACES

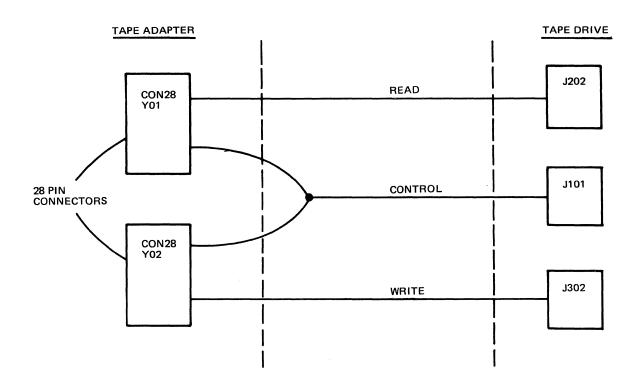

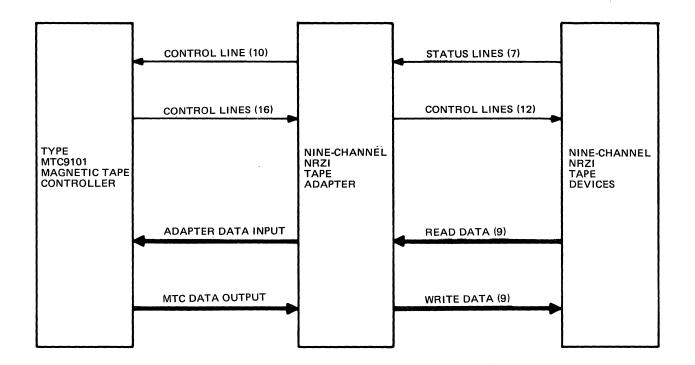

Figure 1-8 is a simplified block diagram showing the basic interface relationships between the adapter and the MTC and between the adapter and the tape devices. A more detailed description of these adapter interfaces can be obtained from Section II of this manual.

Figure 1-8 MTC/Tape Adapter/Tape Device Interfaces

#### 1.6 OPTIONS

The nine-channel NRZI tape adapter has no options.

#### 1.7 REFERENCE DOCUMENTS

The information contained within the following documents should facilitate an understanding of the tape adapter and the system of which it is a part.

| TITLE                                                                                 | DOC. NO. | ORDER NO. |

|---------------------------------------------------------------------------------------|----------|-----------|

| Model 34/36 System Manual                                                             | 71010200 | FL35      |

| Type MTC9101 Magnetic Tape Controller<br>Manual                                       | 71010425 | FM88      |

| MTM9102 Nine-Channel NRZI Tape Adapter<br>Reference Manual                            | 71010283 | FN19      |

| Circuits Description Reference Manual                                                 | 71010206 | FL47      |

| Power Systems Manual                                                                  | 71010290 | FL34      |

| Series 60 Level 6 Peripherals Manual                                                  | N/A      | AT04      |

| Series 60 Level 6 Minicomputer Handbook                                               | N/A      | AS22      |

| Type MTC9101 Magnetic Tape Controller<br>Reference Manual (Assy. No.<br>60130148-003) | 71010326 | FM89      |

ſ

(

1-11/1-12

.,  $\sim$ .

$\bigcirc$

### II THEORY OF OPERATION

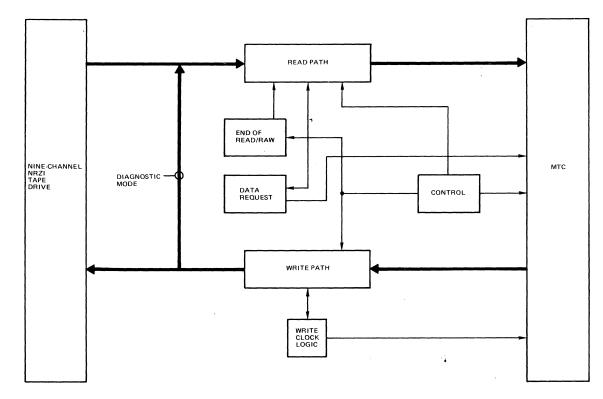

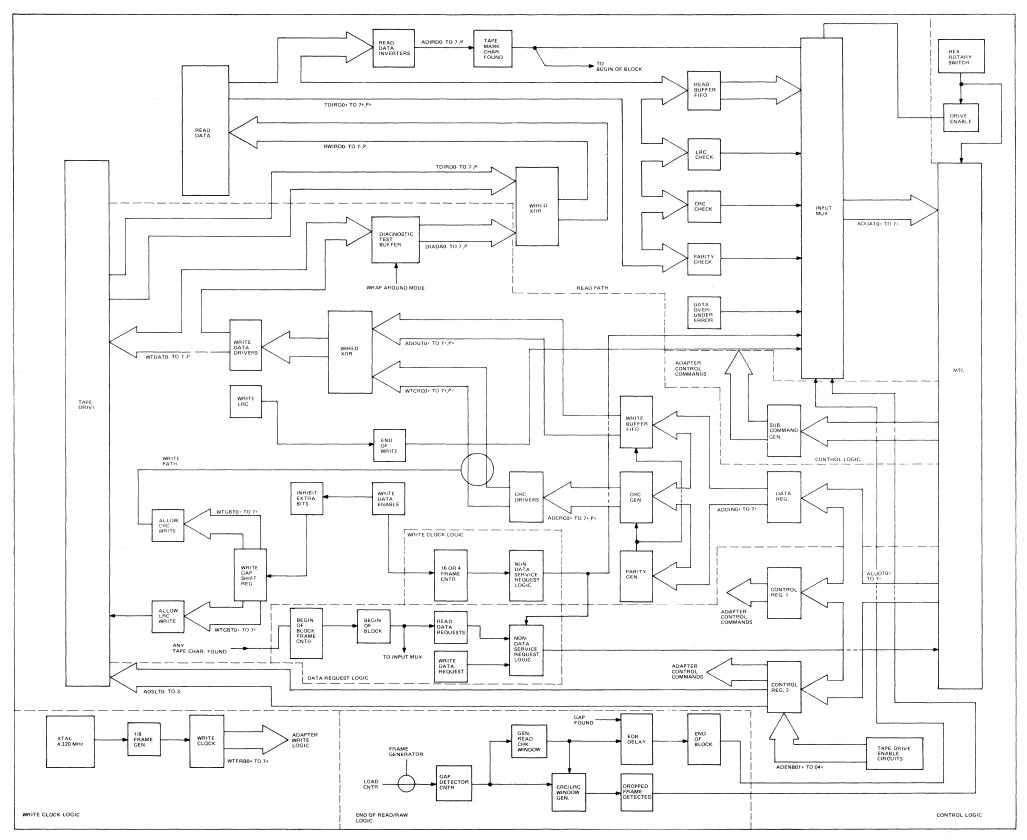

The tape adapter, in conjunction with the MTC and a variable configuration of tape devices (the maximum being four), is a firmware-operated peripheral device adapter. The adapter is attached to the MTC and enables apparent simultaneous control of the connected tape devices. The tape adapter hardware, which implements data transfers and control sequences to and from the tape devices, is divided into six major logic components: Read Path, End-of-Read/RAW, Data Request, Control, Write Path, and Write Clock Logic (see Figure 2-1). These logic components provide for data transfer and efficient control of tape operations.

#### 2.1 SOFTWARE

Operations which affect the tape adapter are the result of two types of commands: software I/O commands that read/write the firmware-accessible locations of scratch pad memory (refer to Section III for the scratch pad memory topology) and those commands contained in the software-supplied task word which cause specific device operations.

#### 2.1.1 I/O Command Set

Table 2-1 lists the input, output, and diagnostic commands applicable to the tape adapter subsystem. These commands load address, range, and control information into a tape device specific segment of the scratch pad memory (SPM). For complete information relative to the command set and the function of the individual commands, refer to the Type MTC9101 Magnetic Tape Controller Manual, Order No. FM88.

| Table | 2-1 | I/0  | Command                 | Set |

|-------|-----|------|-------------------------|-----|

|       |     | -/ - | • • • • • • • • • • • • |     |

| TYPE       | FUNCTION CODE                          | INSTRUCTION                                                                                                            |

|------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Output     | 09 (Hex)<br>11<br>03<br>07<br>01       | IOLD<br>Address (09)<br>Range (0D)<br>Configuration Word<br>Interrupt Control<br>Task Word<br>Control Word             |

| Input      | 0C<br>10<br>02<br>26<br>06<br>18<br>1A | Range<br>Configuration Word<br>Interrupt Control<br>Identification Code<br>Task Word<br>Status Word 1<br>Status Word 2 |

| Diagnostic | Any Even Code<br>Any Odd Code          | Read RWS<br>Write RWS                                                                                                  |

2-2

#### 2.1.2 Tape Subsystem Device Commands

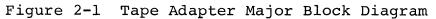

The device commands are contained in the command code field of the task word. The task word is located in the devices' segment of SPM and is loaded there by the Output Task Word I/O command (see Figure 2-2). The device commands that the tape adapter subsystem is capable of performing are described in the remainder of this subsection.

MEGABUS CONFIGURATION FOR OUTPUT TASK WORD COMMAND

Figure 2-2 Output Task Word I/O Command

#### Rewind

The Rewind command rewinds the tape to the BOT marker provided that the Rewind command has not been immediately preceded by a write-type command (i.e., Write, Write Tape Mark, Erase). If the previous command is a write, an erase in the forward direction across approximately 1 inch of tape is performed prior to the Rewind operation. The tape device remains in the busy state until the rewind is complete or a firmware-generated timeout occurs. If the tape on the device is at BOT when the command is issued, tape motion is not implemented, and a normal termination of the command results.

The rewinding of a device can be initiated when the device is off-line by depressing the REWIND pushbutton on the device. The firmware polling cycle detects this activity and updates the status of the rewinding, device ready, and attention bits to their present condition (see Figure 3-3). When the manually propagated rewind is

complete, the rewinding status condition is reset, device ready changes state, and attention is set again.

#### Rewind and Unload

The Rewind and Unload command implements a rewind, as previously described, and following detection of the BOT marker activates the device's unload sequence prior to termination of the command. If the device is at BOT when the command is issued, only the unload sequence is utilized before command termination.

The unload sequence places the selected tape device into the off-line state, extinguishes the ON LINE indicator, and causes tape motion in the reverse direction until tape is wound off the takeup reel.

#### Forward Space Block

The Forward Space Block command spaces forward over the subsequent block on tape provided this command has not been immediately preceded by a write-type command, (i.e., Write, Write Tape Mark, Erase). If the previous command is a write, an erase in the forward direction across approximately 1 inch of tape is performed prior to the Forward Space Block operation. This command terminates when the tape is in the next interblock gap (refer to subsection 1.4.2) or as the result of a firmware timeout.

#### Backspace Block

The Backspace Block command spaces backwards over the previous block on tape provided this command has not been immediately preceded by a write-type command (i.e., Write, Write Tape Mark, Erase). If the previous command is a write-type command, an erase in the forward direction across approximately 1 inch of tape is performed prior to the Backspace Block operation. The command terminates when the tape is in the previous interblock gap (refer to subsection 1.4.2) or when the firmware times out.

If the command is issued when the tape is positioned at the BOT, tape motion is not initiated, and the order is immediately terminated.

#### Forward Space Tape Mark

The Forward Space Tape Mark command spaces forward across one or more blocks until a tape mark or EOT is detected provided this command has not been immediately preceded by a write-type command (i.e., Write, Write Tape Mark, Erase). If the previous command is a write, an erase in the forward direction over approximately 1 inch of tape is performed prior to the Forward Space Tape Mark operation. The command terminates when the tape is in the interblock gap (refer to subsection 1.4.2) following the block containing the tape mark. The command can also be terminated upon EOT detection or a firmware timeout.

#### Backspace Tape Mark

The Backspace Tape Mark command spaces backwards over one or more blocks until the tape mark is detected provided this command was not immediately preceded by a write-type command (i.e., Write, Write Tape Mark, Erase). If the previous command is a write, an erase in the forward direction across approximately 1 inch of tape is performed prior to the Backspace Tape Mark operation. The command terminates when the tape is in the interblock gap (refer to subsection 1.4.2) preceding the block containing the tape mark, when the tape is at the BOT, or when a firmware timeout is detected.

When this command is issued with the tape positioned at BOT, tape motion is not initiated and firmware timeout termination of the command follows.

#### Read Forward

The Read Forward command reads forward over the next block on tape provided this command has not been immediately preceded by a write-type command. If the previous command is a write, an erase in the forward direction across approximately 1 inch of tape is performed prior to the read forward operation. This command terminates when the tape is in the next interblock gap (refer to subsection 1.4.2) or as the result of a firmware timeout.

In addition to the transfer of data, vertical parity and the LRC character are read, and integrity checks are performed.

#### Erase

The Erase command erases tape in a forward direction to produce a 2-inch gap on tape provided this command has been immediately preceded by another write-type command (i.e., Write, Write Tape Mark). If the previous command is not a write, an erase in the forward direction across approximately 2 inches is performed prior to the normal 2-inch erase operation.

#### Write Tape Mark

The Write Tape Mark command erases tape for 2 inches followed by the recording of a tape mark block (refer to subsection 1.4.2) provided this command is immediately preceded by a write-type command (i.e., Write, Erase). If the previous command is not a write, an additional erase in the formward direction across approximately 2 inches of tape is performed prior to the Write Tape Mark operation. The command terminates normally when the tape is positioned in the gap beyond the new tape mark block.

#### Write

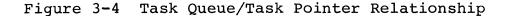

The Write command records data on tape (in a forward direction) in a data block equal to or greater than the minimum block length allowed by the American National Standard (see bit 4 configuration Figure 3-2). If the command has not beem immediately preceded by a

write-type command (i.e., Write Tape Mark, Erase), an erase in the forward direction across approximately 2 inches is performed prior to the Write operation

In addition to the writing of data, vertical parity and the LRC character are written within the data block for read operation integrity checks.

An attempt to write a data block of less than the minimum length or to write on a drive in the write protect mode results in no data transfer, no tape motion, and an operation check reported in the status.

The command terminates when the tape is positioned in the gap beyond the new data block just written.

#### 2.2 FIRMWARE

The firmware that controls the hardware operations of the tape adapter is contained in the MTC microprogram control store. The main function of the firmware is to interpret external and internal events or conditions pertaining to the tape adapter and to react in a prescribed manner (i.e., setting or resetting of hardware functions). Efficient data transfers are also a result of firmware control of hardware components in the data path.

An overview flow chart of the tape adapter firmware routines, as well as a description of the control data and routine utilization, are provided in Section III of this manual.

#### 2.3 HARDWARE OVERVIEW DESCRIPTION

As shown in Figure 2-1 the tape adapter is organized into six fundamental logic areas. Figure 2-3 is an intermediate block diagram of the tape adapter which depicts the components in each of these areas and the interconnections with the MTC and the tape devices. Although the primary function of the tape adapter is to control the data flow between the MTC and the device, the tape adapter performs the following secondary functions:

- Assisting the MTC in formatting data written on the tape device

- Developing signals for device operation

- Generating operational error signals for MTC interrogation

- Generating data and nondata service requests and sending them to the MTC

- Generating status information and sending it to the MTC.

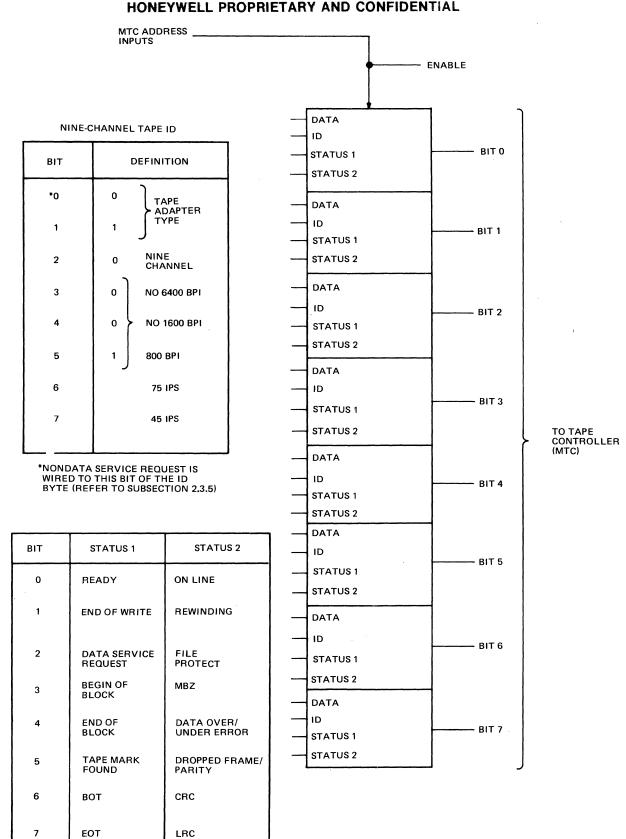

See Figure 2-4 for a listing of the status developed and Figure 3-3 for detailed MTC/tape adapter status relationship. The descriptions in subsections 2.3.1 through 2.3.7 pertain to the logic blocks shown in Figure 2-3.

2-6

HONEYWELL PROPRIETARY AND CONFIDENTIAL

.

C

Figure 2-3 Tape Adapter Intermediate Block Diagram

,

Figure 2-4 Input Multiplexer Data Structure

2-9

#### 2.3.1 Interface Description

The tape adapter provides the interfaces necessary to transfer data to/from a tape device and to/from the controller. Figure 2-5 is a simplified block diagram showing the basic interface relationships between the tape adapter and the MTC and between the tape adapter and the tape devices.

Figure 2-5 MTC/Tape Adapter/Tape Device Interfaces

#### Adapter/MTC Interface

The interface signal lines between the adapter and the MTC are shown in Figure 2-6. A description of the application of these lines is provided in the Magnetic Tape Controller Manual, Order No. FM88. Signal line mnemonics are shown in Figure 2-6 as they are designated for the adapter. It must be kept in mind that certain lines within the MTC may have different mnemonics.

2-10

|                      |                                   | 1                        |     |

|----------------------|-----------------------------------|--------------------------|-----|

|                      | DATA SERVICE REQUEST (4 LINES)    | DATASRQ+                 |     |

|                      | NONDATA SERVICE REQUEST (4 LINES) | NDTSRQ+                  |     |

|                      | ADAPTER PRESENT (4 LINES)         | ADPGND-                  |     |

|                      |                                   | ADPDS0+ TO 7+            |     |

|                      | ADPENB+01 TO 03                   | ADAPTER ENABLES          |     |

|                      | LODAS1+                           | LOAD CONTROL REGISTER 1  |     |

| NINE-CHANNEL<br>NRZI | LODAS2+                           | LOAD CONTROL REGISTER 2  | мтс |

| TAPE<br>ADAPTER      | CLKSIG+                           | CLOCK SIGNAL             |     |

|                      | ADPDBT+                           | DATA BYTE TAKEN          |     |

|                      | UPIRO4+                           | INPUT MUX SELECTION      |     |

|                      | UPIRO5+                           | INPUT MUX SELECTION      |     |

|                      | CLRADP+                           | CLEAR ADAPTER            |     |

|                      | CLKSTB+                           | CLOCK STROBE             |     |

|                      | LODADR+                           | LOAD ADAPTER DATA        |     |

|                      | ADPPLS+                           | ADAPTER PULSE            |     |

|                      | ALUOT0+ TO 7+                     | ALU OUTPUT               |     |

|                      | ADPCD1+ TO 3+                     | MTC OUTPUT CONTROL LINES |     |

|                      |                                   |                          |     |

Figure 2-6 Adapter and Controller Interface

#### Tape Adapter/Device Interface

A diagram of the tape adapter/device interface interconnections is shown in Figure 2-7. This figure identifies the interface lines, their direction, mnemonics, and applications. It depicts the lines for the tape adapter to the device using tape adapter mnemonics. For a detailed description concerning the usage of all the signal lines, refer to Table 2-2.

This interface, which links all four tape devices, allows the adapter hardware and firmware to select a device and perform a designated operation. It also provides the paths for supplying the devices with data, control, and timing pulses, and for supplying the adapter with timing, data, and status from the device.

2-11

| CON28<br>Y01             | CON28<br>Y02           |                    |                  | J101   | J202                                  | J302                  |

|--------------------------|------------------------|--------------------|------------------|--------|---------------------------------------|-----------------------|

| 27                       | 2,3,4                  | SELECT             | ADSLT0- TO 3-    | J,A,18 |                                       |                       |

| 27                       | 2,0,4                  | READ LOW THRESHOLD | ADRDT2 –         | V      |                                       | F                     |

|                          | 06                     | FORWARD            | ADISFC-          | с      |                                       |                       |

|                          | 07                     | REVERSE            | ADISRC-          | E      |                                       |                       |

|                          | 09                     | REWIND             | ADIRWC-          | н      |                                       |                       |

|                          | 10                     | REWIND AND UNLOAD  | ADOFFL-          | L      |                                       |                       |

|                          | 11                     | WRITE              | ADIWRT-          | к      |                                       |                       |

|                          | 13                     | WRITE DATA STROBE  | ADIWDS-          |        |                                       | А                     |

|                          | 14                     | WRITE AMP RESET    | ADWARS-          |        |                                       | с                     |

| (                        | 17,18,19,21            | WRITE DATA         | WTDAT0- TO 7-,P- | :      |                                       |                       |

| 5,6,7,9,10,              | 22,23,25,26<br>15<br>] | TDIRDO- TO 7-,P-   | READ DATA        |        | 3,4,8,9                               | M,N,P,R,<br>S,T,U,V,L |

| 11,13,14,1               | }                      |                    |                  |        | 14,15,17,<br>18,1                     |                       |

| 03                       |                        | TDIRDS-            | READ DATA STROBE |        | 2                                     |                       |

| 19                       |                        |                    | READY            | т      |                                       |                       |

| 21                       |                        | TDIONL-            | ON LINE          | м      |                                       |                       |

| 22                       |                        |                    | REWINDING        | N      |                                       |                       |

| 22                       |                        | TDIEOT-            | ЕОТ              |        |                                       |                       |

| 23                       |                        | TDILDP-            | вот              | U      |                                       |                       |

| 24                       |                        |                    |                  | R      |                                       |                       |

| 26                       |                        |                    | WRITE PROTECT    | Р      |                                       |                       |

| 15                       |                        | TDLOSP-            | LOW SPEED        |        | 13                                    |                       |

|                          |                        |                    |                  |        |                                       |                       |

| ADAPT<br>CONNE<br>PIN NU |                        |                    |                  |        | CAPE DEVIC<br>CONNECTOR<br>PIN NUMBER |                       |

Figure 2-7 Adapter and Tape Device Interface

2-12

Table 2-2 Tape Adapter/Device Interface Signal Lines (Sheet 1 of 3)

| OUTPUT LINES<br>TERM AND MNEMONIC | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unit Select<br>(ADSLT0→3)         | Four lines used for selection in a<br>magnetic tape configuration. These<br>lines are switch selectable within<br>the device, enabling individual<br>selection by any one of the four lines.<br>All other interface output signals<br>are gated with the unit select<br>lines.                                                                                       |

| Forward<br>(ADISFC)               | This signal line causes the device,<br>when ready, to initiate forward motion<br>or when reset to cease forward motion.<br>Due to acceleration and deceleration<br>times, a delay is required after the<br>change of state of this line.                                                                                                                             |

| Reverse<br>(ADISRC)               | This signal line causes the device,<br>when ready, to initiate motion in a<br>reverse direction or when reset to<br>cease reverse motion. Due to accelera-<br>tion and deceleration times, a delay<br>is required after the change of state<br>of this line.                                                                                                         |

| Rewind<br>(ADIRWC)                | This pulse, whose minimum width is 2 $\mu$ s, causes the device, when ready, to move tape in a reverse direction at three/ four times the normal forward speed. Upon sensing BOT, the device overshoots the BOT marker and stops, reverses direction, and comes to rest at the marker. The Rewind indicator is illuminated for the duration of the rewind operation. |

| Rewind and Unload<br>(ADOFFL)     | This pulse, whose minimum width is 2 µs,<br>resets the device ON LINE indicator and<br>the interface On-Line signal line to<br>the adapter. The device then executes<br>its rewind (see above) and unload se-<br>quences to remove tape from the take-up<br>reel.                                                                                                    |

| Write<br>(ADIWRT)                 | To perform a write operation, this line<br>is required to be true for a minimum of<br>20 $\mu$ s after forward motion is initiated.<br>If a read operation is desired, this<br>line must be false for a minimum of<br>20 $\mu$ s after the initiation of forward or<br>reverse motion.                                                                               |

| Table | 2-2 | Tape | Adapter/Device | Interface | Signal | Lines |

|-------|-----|------|----------------|-----------|--------|-------|

|       |     |      | (Sheet 2 of    | 3)        |        |       |

| OUTPUT LINES                   |                                                                                                                                                                                                                                                                                         |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM AND MNEMONIC              | DESCRIPTION                                                                                                                                                                                                                                                                             |

| Read Low Threshold<br>(ADRDT2) | This line selects a low level for the<br>read circuits in the device. This line<br>is used when it is required to recover<br>very low amplitude data and must remain<br>steady for the duration of the block.                                                                           |

| Write Data Strobe<br>(ADIWDS)  | This is a pulse whose minimum width is 2 $\mu$ s. It is sent with each character to be recorded on the media. The frequency of this pulse is equal to the transfer rate and the data must remain steady 0.5 $\mu$ s before and after the pulse.                                         |

| Write Amp Reset<br>(ADWARS)    | This is a $1-\mu s$ pulse (minimum) which re-<br>sets the device write register, causing<br>the LRC character to be written. This<br>pulse is generated at the end of the<br>data block and occurs eight frame times<br>after the last data character (refer to<br>subsection 2.2.2.8). |

| Write Data<br>(WTDAT0→7,P)     | These lines, when true at write data<br>strobe time with the device in write,<br>result in a flux reversal on the cor-<br>responding tape track (see Figures 2-4<br>and 2-6). These lines must be held<br>steady 0.5 $\mu$ s before and after write<br>data strobe.                     |

| INPUT LINES                    |                                                                                                                                                                                                                                                                                         |

| TERM AND MNEMONIC              | DESCRIPTION                                                                                                                                                                                                                                                                             |

| Ready<br>(TDIRDY)              | This line is valid when the device is<br>prepared to accept an adapter command.<br>This line indicates that the tape is<br>under tension, a rewind is not being<br>performed, and the device is in the<br>on-line state.                                                                |

| On-Line<br>(TDIONL)            | This line indicates, when true, that<br>the device is under control from the<br>adapter. When false the line indicates<br>to the adapter that the device is under<br>manual control.                                                                                                    |

| Rewinding<br>(TDIRWD)          | This line is valid while the device is performing a rewind operation.                                                                                                                                                                                                                   |

2-14

Table 2-2 Tape Adapter/Device Interface Signal Lines (Sheet 3 of 3)

| INPUT LINES                  |                                                                                                                                                                                                                                                                      |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM AND MNEMONIC            | DESCRIPTION                                                                                                                                                                                                                                                          |

| EOT<br>(TDIEOT)              | This line being true indicates the EOT<br>reflective marker is positioned under<br>or has passed beneath the photo-sensor<br>during a forward tape motion command.<br>The line is reset after the marker<br>passes the sensor in a reverse tape<br>motion direction. |

| BOT<br>(TDILDP)              | When valid this line indicates the de-<br>vice is ready and the tape is posi-<br>tioned with the BOT marker under the<br>photo-sensor. When the BOT marker<br>leaves the photo-sensor area, this<br>line changes state.                                              |

| Write Protect<br>(TDFPRT)    | This line is valid when tape is loaded<br>and the supply reel has the write<br>enable ring removed.                                                                                                                                                                  |

| Low Speed<br>(TDLOSP)        | This line is set when the device has<br>been conditioned, via device mechanical<br>hardware, to move tape at the lower of<br>the two available speeds (45 or 75 ips).                                                                                                |

| Read Data Strobe<br>(RWIRDS) | This line supplies the adapter with a l $\mu$ s pulse for each character read from tape. The read data lines must remain steady for 0.5 $\mu$ s before and after the read data strobe.                                                                               |

| Read Data<br>(RWIRD0→7,P)    | These lines each represent one bit of<br>the character recorded on the tape<br>tracks (see Figure 2-4). The state of<br>each of the nine lines must remain<br>steady 0.5 µs before and after the read<br>data strobe.                                                |

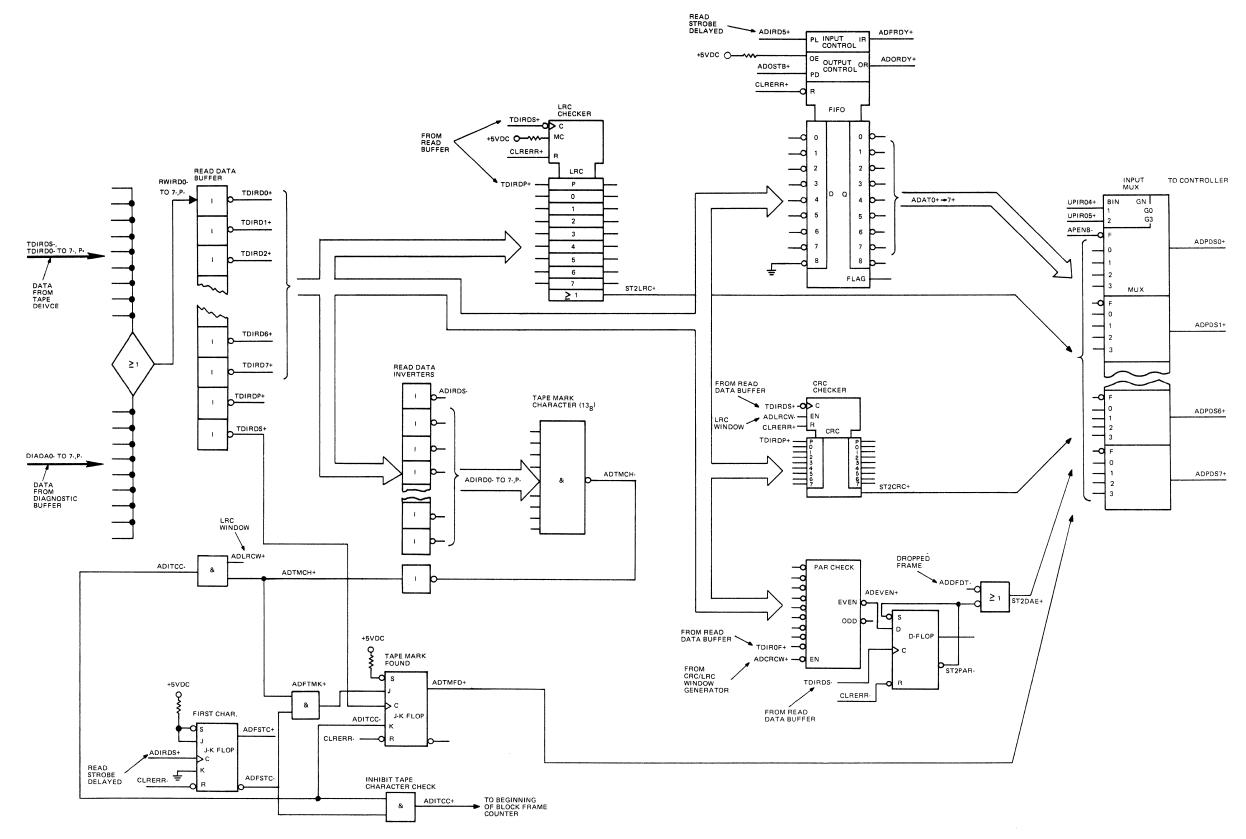

#### 2.3.2 Read Path Functional Components

The data from the device is received in parallel form and is ORed with the data from the diagnostic test buffer. In normal operation the output of the read data reflects the data from the device, whereas in the diagnostic mode the read data logic accepts the output of the diagnostic test buffer. The read data is fed to a set of read data inverters whose outputs in conjunction with the read data are used in the tape mark character found logic to decode a tape mark from the device. This decoded output is sent to the data request logic and the MTC as a status function.

The read buffer is a 32-byte fall-through FIFO (first-in first-out) buffer which receives its input from the read data logic. The first byte of the FIFO acts as an independent input register, and the last byte acts as an independent output register whose contents are sent back to the MTC.

Four other logic areas of the read path receive the data from the read data: LRC check, CRC check, parity check, and tape mark detection. Each area verifies data integrity in a different manner, and when an error is detected, the appropriate error signal is raised and sent back to the MTC via an adapter status input.

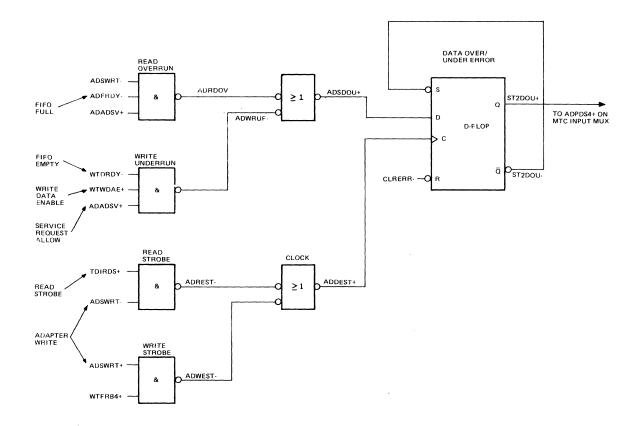

Another read path component is the data over/under error logic. When this logic detects a rate error, an indicator signal is sent to the MTC by way of the status register.

All information (data, status, and ID) sent to the MTC utilizes a four-input multiplexer (see Figure 2-4). The outputs (ADPDS0 through ADPDS7) of the input multiplexer are firmwarecontrolled and reflect the input selected by the two interface select lines.

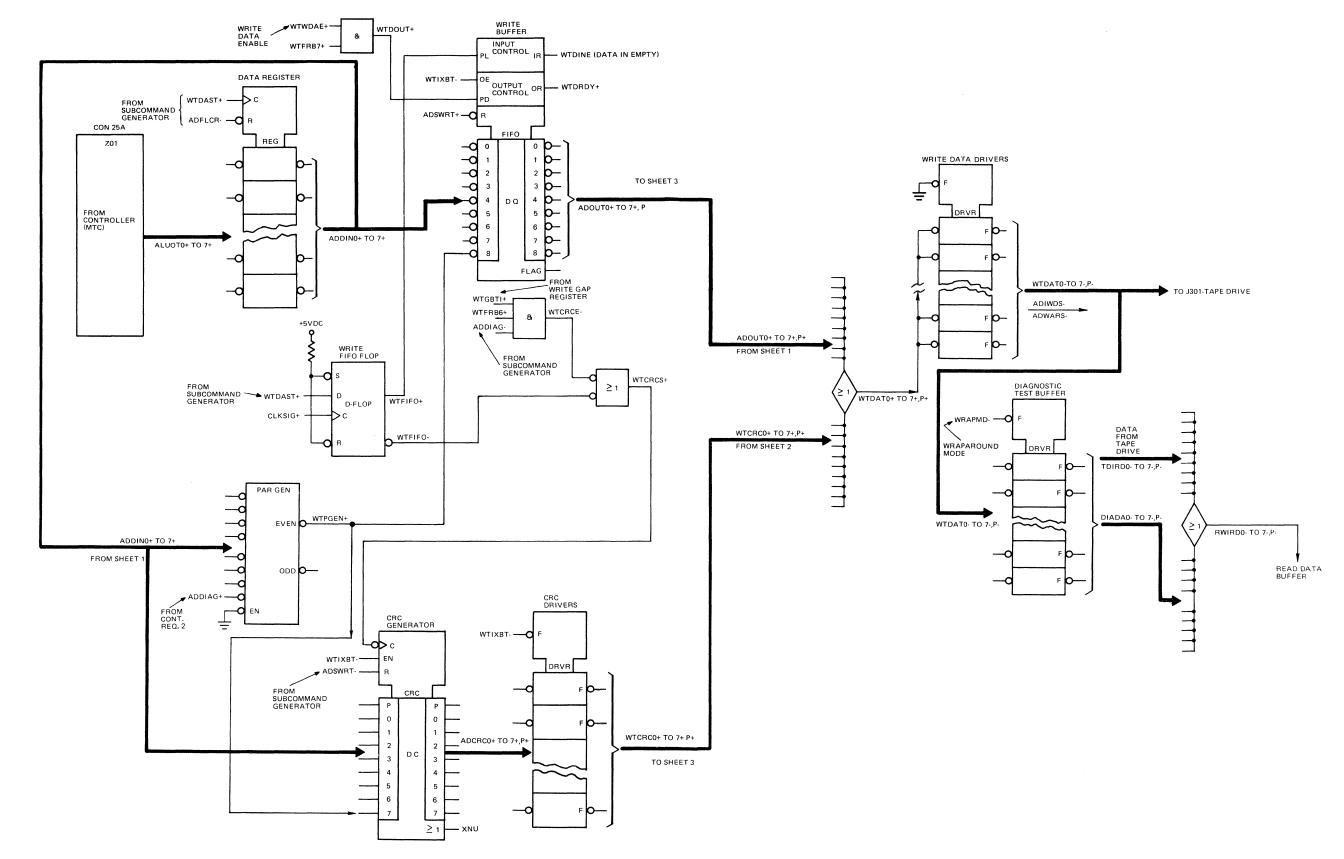

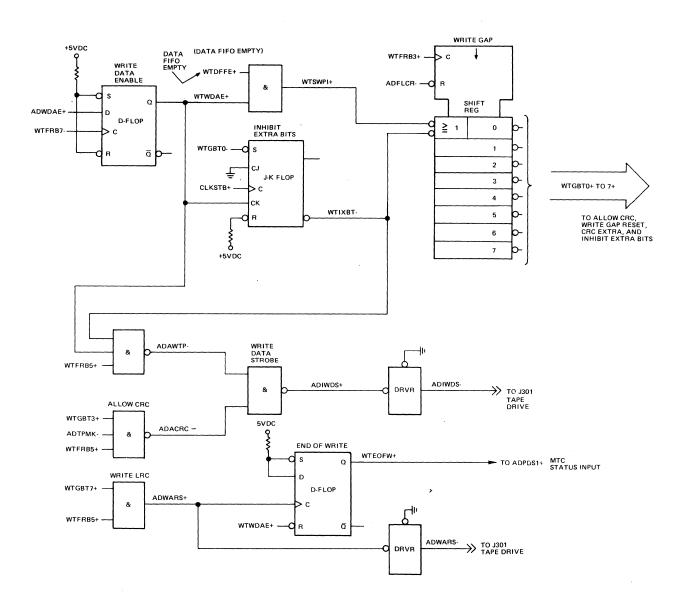

#### 2.3.3 Write Path

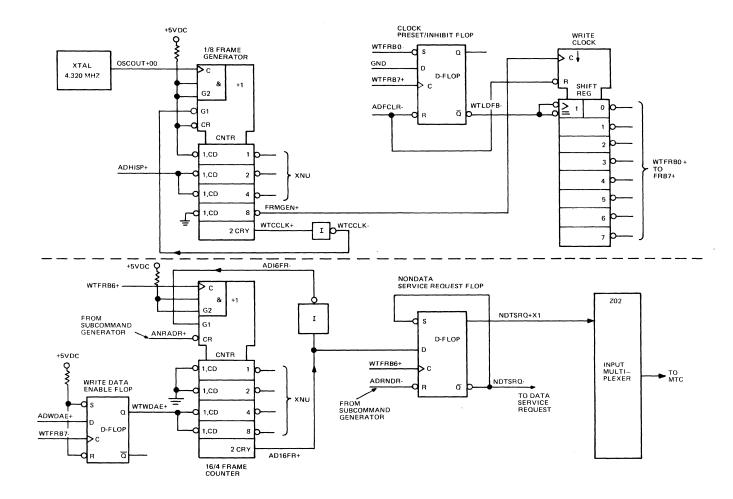

Data received from the MTC is in parallel form with no parity and is stored in the data register. The output of the data register is simultaneously present at the write buffer (FIFO), the CRC generator, and the parity generator. Although the data is available at the write buffer, it is not stored until a parity bit is sent from the parity generator allowing for the 9-bit transfer to the device. The parity bit is also sent to the CRC generator to allow for computation of a nine-bit CRC character.

The CRC generator's outputs are applied to the CRC drivers, the outputs of which are ORed within the write buffer outputs. During the data transfer (Write Data Enable), the output of the CRC drivers is inhibited, and the write data drivers reflect the write data. The CRC character is recognized when the write shift register and its associated logic (Inhibit Extra Bits) generate the Allow CRC Write at the end of the data transfer. After the CRC character is written, the Allow LRC Write causes the LRC character to be written and the End of Write to be set.

2-16

The write data drivers send data to the devices or to the diagnostic test buffer. When executing a normal write command, the data goes to the devices. If the command is a wraparound write, the diagnostic test buffer is enabled, and the data is returned to the MTC via the read path (refer to subsection 2.3.2).

#### 2.3.4 Write Clock Logic

The write clock logic contains a free-running oscillator (4.320 MHz). The oscillator outputs are the basis for producing all the timing pulses required for operation. The 1/8 frame generator, using the oscillator as a source, counts 1/8 segments of a frame regardless of the tape speed. Implementing a strobe from the 1/8 frame generator, the write clock generates eight sequential pulses that are distributed throughout the tape adapter.

The 16-frame/4-frame counter feeding the nondata service request logic enables the adapter to issue a nondata request to the MTC at 0.005-inch intervals of tape duirng the data transfer portion of a unit operation or 0.02-inch intervals of tape at other times.

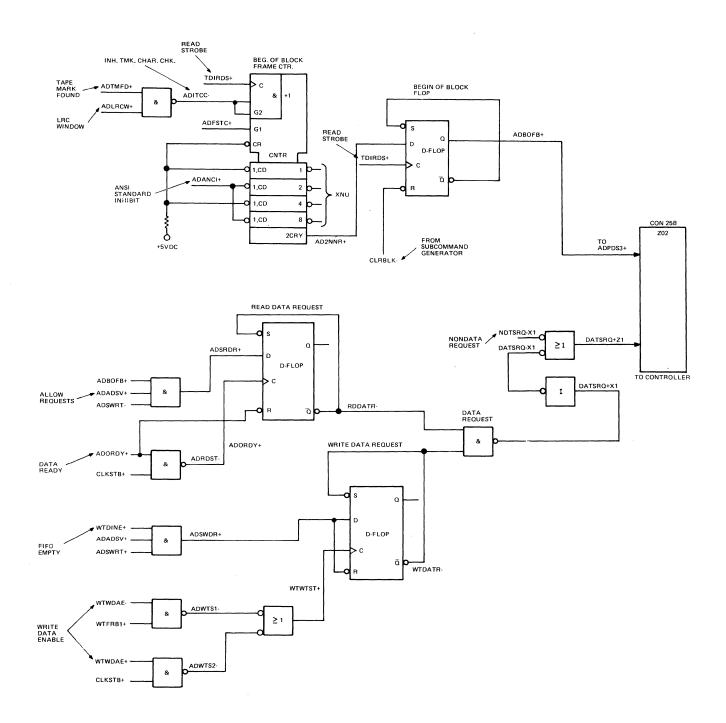

#### 2.3.5 Data Request Logic

The data request logic requests data from the MTC for a write operation, requests to send data to the MTC for a read operation, or indicates the presence of a nondata service request to the MTC.

The read operation implements the beginning-of-block frame counter to discriminate against noise records encountered while seeking a valid record. Upon detection of a valid record, the beginning of block sets, allowing read data request to generate data requests each time the read buffer (FIFO) has information available.

The write data request causes a data request during the write operation any time there is available storage in the write buffer (FIFO).

Each time a nondata service request is generated in the write clock logic, a data request is issued to the MTC. The MTC responds as if this were a normal data request (high priority) and determines that it is actually a nondata request by reading the ID byte through the input multiplexer (see Figure 2-4) and examining bit 0. This procedure of channeling the nondata requests through the data request logic is required due to the timing considerations encountered in the firmware processing of nondata requests. Because all tape data requests appear on channel 0, it makes tape nondata requests higher priorities than other data requests.

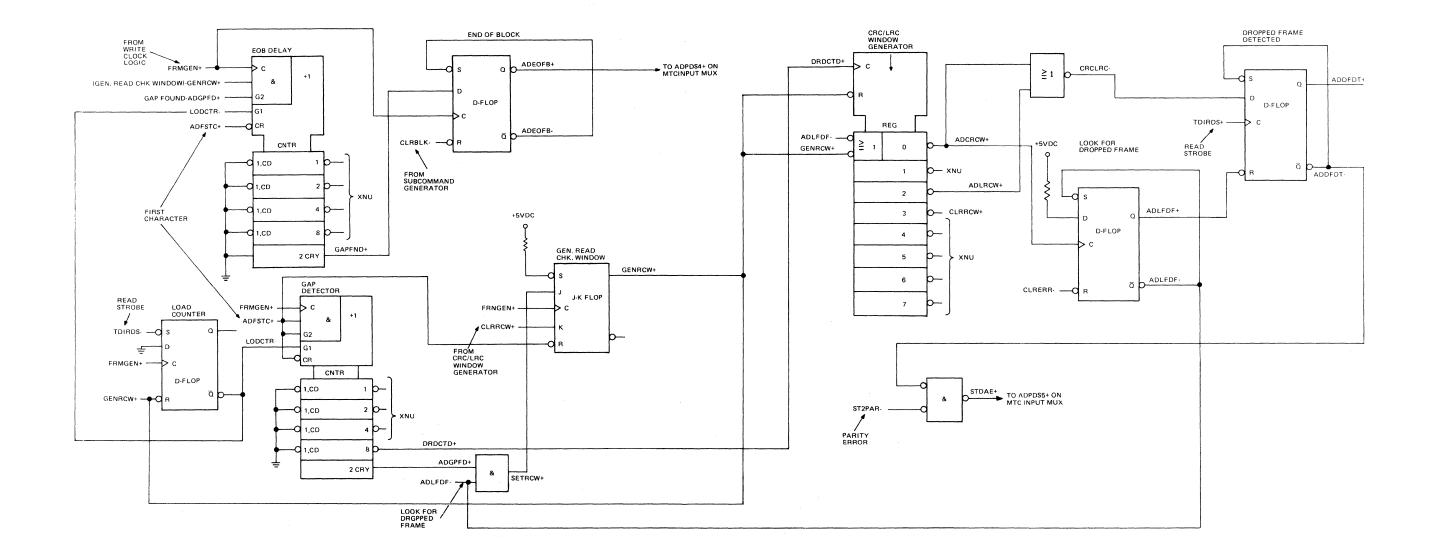

#### 2.3.6 End of Read/Read After Write (RAW) Logic

Two-frame time lapses between read strobes are detected by the gap detector counter. This counter sets and increments the CRC/LRC window generator, which inhibits the setting of the dropped frame detected logic during the time intervals of from three to five and from seven to nine frames after the last read strobe. The time

period of three through five allows the CRC character to be read without producing a dropped frame detected error. The time period of seven through nine allows the LRC character to be read without producing an error. When a read strobe is encountered at any time other than during the CRC/LRC windows, the Dropped Frame Detected signal sets and can be read by the MTC via status information.

The gap detector counter is also used in conjunction with the generate read check window to initiate the EOB delay. The EOB delay counts 32 frame times before the end-of-block indicator is set. Firmware then resets the end-of-block indicator, which has been sent to the MDC via a status register, and allows the EOB delay to count another 32 frame times and set end of block again. If a read strobe is detected during the second count of 32, end of block does not set. This condition is reported to software as an uncorrectable read error.

# 2.3.7 Control Logic

The tape adapter control logic uses two control registers to store the contents of the MTC data and adapter enable lines during a firmware load control register command. This stored information is distributed throughout the adapter and is sent to the device to establish the type of the mode of operation.

The subcommand generator stores the interface control signals from the MTC. The subcommand generator outputs are "store" and "clear" functions resulting from firmware manipulation of the MTC/ tape adapter interface lines.

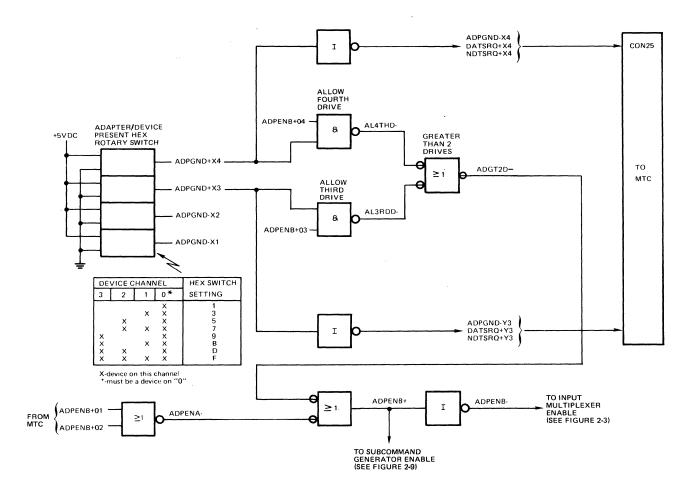

The hex rotary switch inhibits the data request, nondata request, and adapter present logic from other adapter positions when a system with more than two devices is supported. This inhibiting allows the request logic of other low-speed device adapters to function if only one, two, or three tape devices are attached. The drive enable circuitry controls the enabling of the input multiplexer for the tape adapter. When there are more than three devices on the tape adapter, the input multiplexer is always enabled. If three or fewer tape devices are supported, the input multiplexer is enabled only when a tape device is addressed.

# 2.4 INTERMEDIATE HARDWARE DESCRIPTION

Figure 2-3 is an intermediate level block diagram of the tape adapter logic. This illustration is designed to guide the user through the detailed logic block diagrams contained in the Tape Adapter Reference Manual (Order No. FN19), and is the overview diagram applicable to the following text.

#### 2.4.1 Write Operations

The subsequent subsections describe the adapter hardware implemented when a write operation is to be performed on a selected tape device. The data transfer path, as well as the control, timing, and data integrity logic required to execute the write operation,

2-18

are described. There are only three functional types of write operation: write data, write tape mark, and erase. The hardware application is basically the same for all three operations. Firmware determines how the transfers will differ. Wherever possible variations in the hardware utilization are noted.

# 2.4.1.1 Write Control Logic

Since the tape adapter can control up to four devices (each of which is handled as a channel), the logic is designed to allow other adapters to function as if the tape adapter has two or fewer devices. Figure 2-8 shows the hex rotary switch and the associated logic used to allow or inhibit other adapter positions and data request, nondata request, and adapter present functions.

Figure 2-8 Adapter Selection Logic

2-19

When the rotary switch is put in positions which select either ADPGND+X3 or ADPGND+X4 (5, 7, 9, B, D, or F), a positive voltage is applied to the corresponding output. This positive voltage is inverted and the ground level is applied to the data request, nondata request, and adapter present functions (ADPGND, DATSRQ, and NDTSRQ) on the MTC interface for the appropriate adapter position. The grounding of these functions inhibits any erroneous requests when channel 2 or 3 is occupied by a tape device.

The positive voltage output of the switch (ADPGND+X3/ADPGND+X4), in conjunction with the applicable adapter enable function (ADENB-03/ADENB+04), allows the output of the greater-than-two device logic (ADGT2D-) to go to ground. As a result of this, the input multiplexer and the subcommand generator are enabled (ADPENB±) for a command sent to an adapter. If ADGT2D- is high, the input multiplexer and the subcommand generator only react as a result of commands sent to device 1 or 2 (ADPENB+01/ADPENB+02).

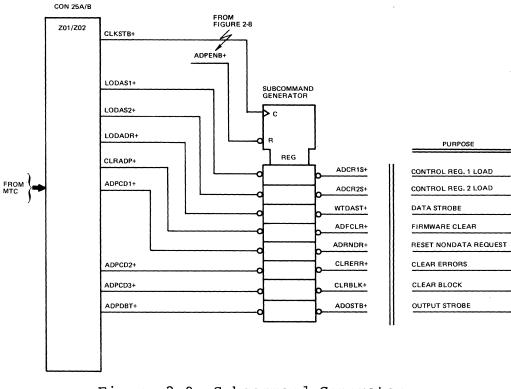

The tape adapter receives firmware-generated load register commands, reset pulses, and timing pulses through the MTC's use of individual interface lines. As these lines must remain steady for a full firmware cycle, they are latched in the subcommand generator (see Figure 2-9). The subcommand generator latches the interface control lines at the leading edge of Clock Strobe (CLKSTB+) from the MTC when the adapter is enabled as reflected by ADPENB+ from the selection logic (see Figure 2-8). At the leading edge of the following clock strobe (CLKSTB+), the new condition of the interface control lines is latched or all the outputs are reset to Zero if the adapter is no longer selected (ADPENB+ low).

Figure 2-9 Subcommand Generator

2-20

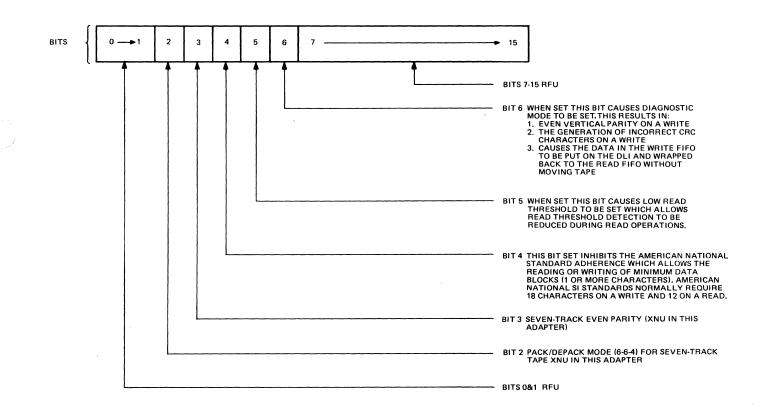

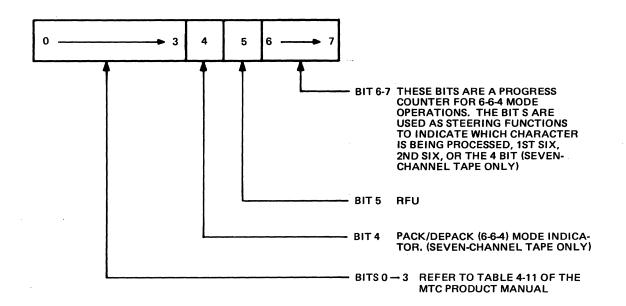

The tape adapter has two control registers (see Figure 2-10) that store all the device commands and control information from the scratch pad memory to complete a device operation. These registers (control registers 1 and 2) are loaded with the information on the MTC data output lines (ALUOT0+ to ALUOT7+) when the subcommand generator stores the appropriate load control register command (ADCR1S+ or ADCR2S+). The registers are reset when the firmware loads the subcommand generator with Firmware Clear (ADFLCR+). The high-order bits (0 through 3) of control register 2 are loaded from the MTC interface enable signals (ADPENB+01 through ADPENB+03) and the tape adapter enable signal (ADPENB+04). The outputs of the control register (ADDRV0+ through ADDRV3+) are sent to the device interface drivers and used by the device as selection lines.

# 2.4.1.2 Write Clock Logic

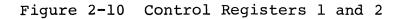

The write clock logic is comprised of three primary elements: a crystal oscillator, a 1/8 frame generator, and a write clock. The nondata service request flip-flop and its associated logic are also considered part of the write clock logic (see Figure 2-11).

The crystal oscillator is a free-running 4.320-MHz crystal that generates pulses at a 231-nanosecond rate. This rate is the basis for all timing pulses generated within the adapter.

The 1/8 frame generator creates a pulse (FRMGEN+) at the rate of one per 1/8 frame time regardless of the device speed (75 ips or 45 ips). This is accomplished by utilizing the output of the oscillator (OSCOUT+00) as the clock input to the 1/8 frame generator and the High Speed (ADHISP+) signal derived from the device interface, and +5 Vdc as the preset. When a 75-ips device is attached, ADHISP+ is set and the counter is preset to 7 hex; when a 45-ips device is attached, the counter is preset to 1 hex. This allows FRMGEN+ (1/8 of a frame) to set once every 2  $\mu$ s for a high-speed device and once every 3.5  $\mu$ s for a low-speed device. (Both times are approximate.)

The write clock uses FRMGEN+ to clock its eight-output shift register. The first time FRMGEN+ sets, the output of the Clock Preset/Inhibit flip-flop negation (MTLDFB-) is set due to Firmware Clear (ADFCLR-) from the subcommand generator (see Figure 2-9). This allows bit 0 of the write clock (WTFRB0+) to set (this set condition is returned to the Clock Preset/Inhibit flip-flop), inhibiting the insertion of any other bits into the write clock. At each generation of FRMGEN+, the subsequent stage of the write clock is set and the preset stage resets, resulting in the development of eight uniform clock pulses during each frame time. The output of the last write clock stage (WTFRB7+) clocks the ground data input of the Clock Preset/Inhibit flip-flop, setting WTLDFB-. WTLDFB-, in turn, starts the cycle over again.

FROM SUBCOMMAND GENERATOR CON 25A Z01 CONTROL REGISTER 2 ADCR2S+ Ьc DRIVE ADFCLR-ENABLE CIRCUITS R ÷ DRVR REG TO J01 ADSLTO- TO 3-ADENB01+ TO 04+ ADDRV0+ ---- 3+ Fb -C (DRIVES) FROM CONTROLLER CONTROL COMMANDS CONTROL REGISTER 1 ADCR1S+ Ьc TO DRIVES/ ADAPTER LOGIC CONTROL COMMANDS FROM **S4B COMMAND** REG GENERATOR CONTROL COMMANDS ~ n MNEMONIC DESCRIPTION ADANCI+ ANSI COMP. INHIBIT ALUOT4+ --LOW READ THRESHOLD ADLRTH+ CONTROL ADD1AG+ DIAGNOSTIC MODE COMMANDS ALLOW NONDATA SRQ. ADANDR+ ADRFWD+ REWIND -С ADOFFL+ REWIND/UNLOAD ADSWRT+ SET WRITE -0 n ADTPMK+ TAPE MARK FORWARD MOTION ADFWDM+ ADREVM+ REVERSE MOTION ADWDAE+ WRITE DATA ENABLE ALLOW DATA SERVICE REQUESTS ADADSV+

HONEYWELL PROPRIETARY AND CONFIDENTIAL

4

2-22

HONEYWELL PROPRIETARY AND CONFIDENTIAL

$\left(\begin{array}{c} \\ \end{array}\right)$

÷

Figure 2-11 Write Clock Logic

The time interval between nondata service requests is determined by the carry-out function (AD16FR+) of the 16/4 frame counter. The counter is preset to 0 hex or C hex as determined by the Write Data Enable flip-flop (WTWDAE+). This preset is done to allow a nondata service request to be generated at 0.005-inch intervals of tape when a write data transfer is taking place or at 0.02-inch intervals of tape during initial gap generation. Firmware uses the nondata service request outputs (NDTSRQ±) to establish distances on tape for gaps, start-up and stay delays, timeouts, etc.

The Write Data Enable flip-flop (WTWDAE+) sets as the result of Write Data Enable (ADWDAE+) from control register 1 (see Figure 2-10) and the negation of the last stage of the write clock (WTFRB7-). The 16/4 frame counter increments at each sixth stage of the write clock (WTFRB6+) with the WTWDAE+ determining how many frames are to be counted (16/4) prior to the setting of the carryout (AD16FR+) function. After the carry out sets, which is the

2-23

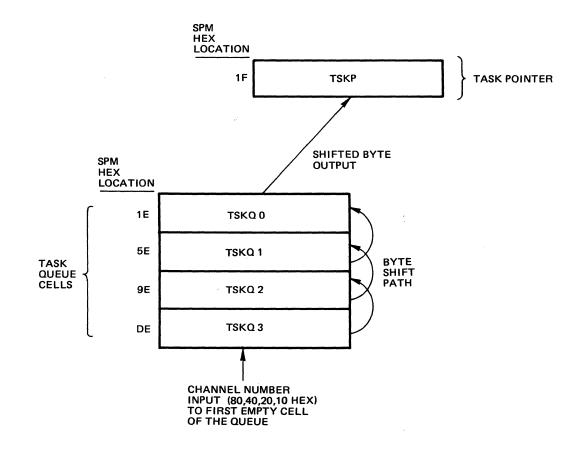

data input to the Nondata Service Request flip-flop (NDTSRQ+X1), NDTSRQ+X1 sets at the following sixth write clock output (WTFRB6+). NDTSRQTX1 is sent to the data request logic (see Figure 2-15) to notify the MTC that a request is present. It is also sent to bit 0 of the ID byte (see Figure 3-4) to signify to firmware that the present request is a nondata service request. The Nondata Service Request flip-flop remains set until the request is acknowledged and firmware loads Reset Nondata Service Request (ADRNDR+) into the Subcommand Generator.

# 2.4.1.3 Write Initiation

Prior to the initiation of a write order the Nondata Service Request flip-flop (NDTSRQ+X1) is reset, using the output of the subcommand generator (ADRNDR+). The status is also reset, using the Clear Errors (CLRERR+) output of the subcommand generator.

Control Register 1 is then loaded with the write command (29 hex) minus the write data enable bit (see Figure 2-10). This sets Write (ADSWRT+), Forward Motion (ADFWDM+), and Allow Data Request (ADADSV+) in the control register. At this point drive motion is started by sending ADFWDM+ from the control register to the device.

#### 2.4.1.4 Write Data Path (See Figure 2-12)

With Write Data Enable reset and the conditions that are now set in control register 1, a Data Request (DATSRQ+X1) is issued to the controller each time the input register to the write FIFO is empty (WTDINE+) but at a rate not to exceed one-frame time intervals. The firmware loads Data Strobe (WTDAST+) into the subcommand generator, clocking the data from the controller (ALUOTO through ALUOT7) into the data register. WTDAST+ from the subcommand generator is also the input to the Write FIFO flip-flop, and at CLKSTG+ time the output of the flip-flop (WTFIFO+) sets, allowing the output of the data register to be written into the write buffer (FIFO). This process is repeated until all 32 locations of the write buffer are loaded.

When the firmware has determined that the device is up to maximum speed and the proper gap has been allowed from the previous block, it loads control register 1 with the write command (2B hex), including Write Data Enable. With Write Data Enable (WTWDAE+) set, the contents of the write buffer are shifted with Write Data Out (WTDOUT+) each Write Clock Time 7 (WTFRB7+), and the data in the output register of the write buffer (ADOUTO+ through ADOUT7+ and ADOUTP+) is sent through an ORing network to the write data drivers (WTDAT0+ through WTDAT7+ and WTDATP+) and on to the device.

At the same time that data is being sent to the device, data requests (DATSRQ+X1) start being generated (see Figure 2-16) because the FIFO input register will again be empty (WTDINE+).

2-24

HONEYWELL PROPRIETARY AND CONFIDENTIAL

# Figure 2-12 Write Data Path

2-25/2-26

As data is being sent to the adapter and loaded into the data register, it is also applied to a parity generator and a CRC generator. The parity generator creates odd parity (WTPGEN+) on each byte of data received using the data register output (ADDIN0+ through ADDIN7+). When the data is written into the write buffer (FIFO) at CLRSIG+ time, the parity bit (WTPGEN+) is also written.

The data (ADDINO+ through ADDIN7+) and the parity bit (WTPGEN+) are written into the CRC generator at the same time as it is written into the write buffer. This is accomplished by using the output of the Write FIFO flip-flop (WTFIFO+) to develop the clock input to the CRC generator. The outputs (ADCRCO+ through ADCRC7+ and ADCRCP+) of the CRC generator are isolated from the write data drivers by the tristate CRC drivers (WTCRC0+ through WTCRC7+ and WTCRCP+). These drivers are enabled (WTIXBT-) when the CRC character is to be written on tape. The outputs of the drivers are sent through an ORing network (WTDAT0+ through WTDAT7+ and WTDATP+) to the write data drivers (WTDAT0- through WTDAT7- and WTDATP-), which are always enabled, and then on to the device.

#### 2.4.1.5 Write Termination (See Figure 2-13)

When the firmware recognizes the end of the data transfer (end of range detected), it resets the Allow Data Requests (ADADSV+) in control register 1. This inhibits the adapter from generating any further data requests (DATSRQ+X1) and allows the data buffer (FIFO) to empty. When the last data byte has been transferred from the write buffer to the device, the Data FIFO Empty (WTDFFE+) function WTDFFE+ set in conjunction with the output of the Write Data sets. Enable flip-flop, sets the data input (WTSWPI+) to the write gap shift register (WTGBT0+ through WTGBT7+). At Write Clock Time 3 (WTFRB3+), the first stage of the shift register (WTGBT0+) is allowed; the inverted output is the force set of the Inhibit Extra Bits flip-flop (WTIXBT- reset). WTIXBT- remains set until the firmware resets the write data enable output of control register 1 (ADWDAE+). WTIXBT- from the Inhibit Extra Bits flip-flop prevents any further bits from being inserted into the data input of the write gap shift register and inhibits normal generation of Write Data Strobes (ADIWDS+).

WTIXBT- also enables the CRC drivers (see Figure 2-12) and inhibits the write buffer. This condition permits the write drivers to reflect the CRC output of the ORing network (WTCRC0+ through WTCRC7+ and WTCRCP+) rather than the data output (ADOUT0+ through ADOUT7+ and ADOUTP+).

Figure 2-13 End of Write Logic