# HP 3000 SERIES II COMPUTER SYSTEM

### **SYSTEM SERVICE MANUAL**

Manual Part No. 30000-90018 Microfiche Part No. 30000-90032

> Printed in U.S.A. 8/76 Updates through #2 incorporated 2/77 Update 3 3/77

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

### LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the most recent date on which the technical material on any given page was altered. If a page is simply re-arranged due to a technical change on a previous page, it is not listed as a changed page. Within the manual, changes are marked with a vertical bar in the margin.

| te Pages         | Effective Date |

|------------------|----------------|

| 77 4-5 to 4-17   | Aug 1976       |

| 76 4-18 and 4-19 | Dec 1976       |

| 77 4-20 to 4-22  | Aug 1976       |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  |                |

|                  | 77 4-5 to 4-17 |

### PRINTING HISTORY

New editions incorporate all update material since the previous edition. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The date on the title page and back cover changes only when a new edition is published. If minor corrections and updates are incorporated, the manual is reprinted but neither the date on the title page and back cover nor the edition change.

|          | •••••• |          |

|----------|--------|----------|

| Update 2 | <br>   | Dec 1976 |

Revised and reprinted in Aug 1976 to incorporate information concerning Fault Correcting Memory. Appendix A (IC Logic Symbology) has been removed from this manual and will appear in the Engineering Diagrams Set, part number 30000-90076.

Update 1 adds troubleshooting information to Section II and card cage for replacement procedures in Section V.

Update 2 adds information about the 7920A Verifier Program to Section I and two new appendices (B and C).

Update 3 adds information about the 30360A HSI PCA Diagnostic (D432) to Section I.

This manual is intended for use by a trained Hewlett-Packard Customer Engineer (CE) trained in the principles of operation and troubleshooting procedures for the HP 3000 Series II Computer System.

This maintenance manual contains the following sections:

Section I System Verification — Verification procedures that permit the CE to determine the system operates properly.

Section II System Troubleshooting — Troubleshooting procedures designed to aid in the location of a system problem.

Section III Maintenance Panel Operating Procedures — Description and use of the HP 30354A Maintenance Panel to aid the CE analyzing system operation.

Section IV Maintenance Procedures — Repair philosophy and general servicing information (PCA jumper and switch position information), and system servicing points to aid the CE when troubleshooting the system. Principles of operation of the memory module is included in this section to assist in troubleshooting memory problems.

Section V Replaceable Parts — A list of replaceable assemblies and their part numbers. Also included is a list of replaceable cables and their part numbers, and miscellaneous items that may require replacement.

Appendix A Microdiagnostics — Instructions for executing the microdiagnostics that are built into the system.

Appendix B System Power Supplies — Detailed information on the system power supplies.

Appendix C Battery Care — Background material about system batteries and their care.

Related manuals and other documents the CE may require or find useful to maintain the system are:

HP 3000 Series II Engineering Diagrams Set, part number 30000-90076

HP 3000 Series II Computer System Reference Manual, part number 30000-90020 (System description from a hardware standpoint.)

HP 3000 Series II Computer System Operator's Guide, part number 30000-90013

HP 3000 Series II Computer System Manual of Diagnostics

HP 3000 Series II Computer System Installation Manual, part number 30000-90019.

JAN 1977

## **CONVENTIONS USED IN THIS MANUAL**

| NOTATION      | DESCRIPTION                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| []            | An element inside brackets is <i>optional</i> . Several elements stacked inside a pair of brackets means the user may select any one or none of these elements. |

|               | Example: $\begin{bmatrix} A \\ B \end{bmatrix}$ user may select A or B or neither                                                                               |

| { }           | When several elements are stacked within braces the user must select one of these elements.                                                                     |

|               | Example: $ \begin{cases} A \\ B \\ C \end{cases} $ user must select A or B or C.                                                                                |

| italics       | Lowercase italics denote a parameter which must be replaced by a user-supplied variable.                                                                        |

|               | Example: CALL name name one to 15 alphanumeric characters.                                                                                                      |

| underlining   | Dialogue: Where it is necessary to distinguish user input from computer output, the input is underlined.                                                        |

|               | Example: NEW NAME? <u>ALPHA1</u>                                                                                                                                |

| superscript C | Control characters are indicated by a superscript C                                                                                                             |

|               | Example: Y <sup>c</sup>                                                                                                                                         |

| return        | return in italics indicates a carriage return                                                                                                                   |

| linefeed      | linefeed in italics indicates a linefeed                                                                                                                        |

|               | A horizontal ellipsis indicates that a previous bracketed element may be repeated, or that elements have been omitted.                                          |

### **CONTENTS**

| Section I                                    | Page         | Facilities Required                                 |

|----------------------------------------------|--------------|-----------------------------------------------------|

| SYSTEM VERIFICATION                          |              | CPU Register Test - Diagnosis and Repair2-6         |

| Introduction                                 | 1-1          | Memory Configuration Test - Diagnosis               |

| Diagnostic and Verification Programs         | 1-1          | and Repair                                          |

| On-Line Verification Programs                | 1-1          | CPU Stand-Alone Diagnostic -                        |

| Stand-Alone Diagnostic Programs              | 1-1          | Diagnosis and Repair2-6                             |

| Microdiagnostics                             | $\dots$ 1-2  | Error Correcting Memory Diagnostic -                |

| Purpose                                      | $\dots 1$ -2 | Diagnosis and Repair2-7                             |

| Facilities Required                          |              | System Test - Diagnosis and Repair                  |

| System Verification Procedures               | 1-3          | Cold Load Procedure - Diagnosis and Repair 2-7      |

| SLEUTH 3000                                  | 1-3          | System Test - (Load)                                |

| System Control Panel                         | 1-4          | Cold Load Procedure (Tape)2-7                       |

| Maintenance Panel                            | 1-4          | Section III Page                                    |

| Cold Load (Diagnostic)                       | 1-6          | MAINTENANCE PANEL OPERATING                         |

| HP 30129 Cartridge Disc Diagnostic           |              | PROCEDURES                                          |

| (D419)                                       | 1-6          | Purpose of Maintenance Panel                        |

| HP 30008A/30009A Fault Correction            |              | Items Supplied                                      |

| Memory Diagnostic (D430)                     | 1-7          | Additional Equipment                                |

| HP 30036A Multiplexer Channel                |              | Options                                             |

| Diagnostic (D422)                            | 1-9          | Switches and Lamps                                  |

| HP 30102A Disc File Diagnostic (D423)        | 1-10         | Operating Methods                                   |

| HP 30110A Cartridge Disc Diagnostic          |              | Precautions                                         |

| (D424)                                       | 1-11         | Preparation for Use                                 |

| HP 30031A System Clock Console               |              |                                                     |

| Interface Diagnostic (D425)                  | 1-11         | General Operating Method                            |

| HP 30032A Terminal Data Interface (TDI)      |              | Control Panel                                       |

| PCA Diagnostic (D427)                        | 1-13         | Stack Register Loading                              |

| HP 2660A Fixed Head Disc Diagnostic          |              |                                                     |

| (D428)                                       | 1-15         | CPU Register Displays                               |

| HP 30033A Selector Channel Diagnostic        |              | General Use Display                                 |

| (D429)                                       | 1-15         |                                                     |

| HP 30012A Extended Instruction Set           |              | Lamp Test       3-21         Switch Test       3-22 |

| Diagnostic (D431)                            | 1-17         | Switch Test                                         |

| HP 30115A Nine-Track Magnetic Tape           |              | Section IV Page                                     |

| Diagnostic (D433)                            | 1-17         | MAINTENANCE PROCEDURES                              |

| HP 30055A Synchronous Single Line            |              | Introduction                                        |

| Controller (SSLC) PCA Diagnostic (D434)      | 1-18         | Safety Precautions                                  |

| Universal Interface, Card Reader Punch       |              | Repair Philosophy4-1                                |

| Interface PCA Diagnostic (D435)              | 1-19         | General Servicing Information                       |

| HP 30061A Terminal Controller Interface      |              | I/O Error Logging                                   |

| (TCI) PCA Diagnostic (D438)                  | 1-21         | Memory Error Logging                                |

| HP 30226A Plotter Interface Diagnostic       |              | Adjusting System Voltages                           |

| (D439)                                       | 1-23         | Selector Channel Maintenance PCA                    |

| HP 3000 Series II Computer System            |              | (SCMB) 30033-60001                                  |

| CPU Diagnostic (D420)                        | 1-25         | Jumpers                                             |

| HP 30104A Paper Tape Reader, HP 30105A       |              | Selector Channel Installation 4-5                   |

| Paper Tape Punch On-Line Verification        |              | Multiplexer Channel Installation                    |

| Program                                      | 1-26         | SCMB Verification                                   |

| Paper Tape Punch Verification                |              | SCMB State Display 4-6                              |

| Paper Tape Reader Verification               |              | Programming                                         |

| HP 7920A Disc Drive Verifier, SLEUTH07       |              | I/O Instructions                                    |

| HP 30360A Hardwired Serial Interface (HSI)   |              | I/O Program Orders                                  |

| , ,                                          | 1 90         | Control Word4-9                                     |

| PCA Diagnostic (D432)                        | 1-30         | Status Word                                         |

| Section II                                   | Page         | Program Execution                                   |

| SYSTEM TROUBLESHOOTING                       | 1 age        | PCA Jumpers and Switches                            |

| Introduction                                 | 9_1          | ROM PCA 30003-60001                                 |

| Purpose                                      |              | ROM Loading                                         |

| · arkono · · · · · · · · · · · · · · · · · · |              | TOTAL LOCALING4-15                                  |

MAR 1977 vii

# **CONTENTS** (continued)

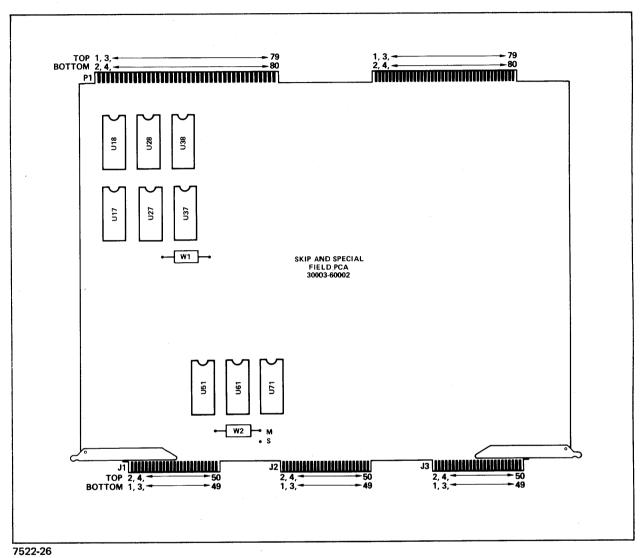

| Skip and Special Field PCA 30003-60002 4-15        | Error Correction                          |

|----------------------------------------------------|-------------------------------------------|

| Sync Jumpers                                       | Memory Error Logging Facility 4-39        |

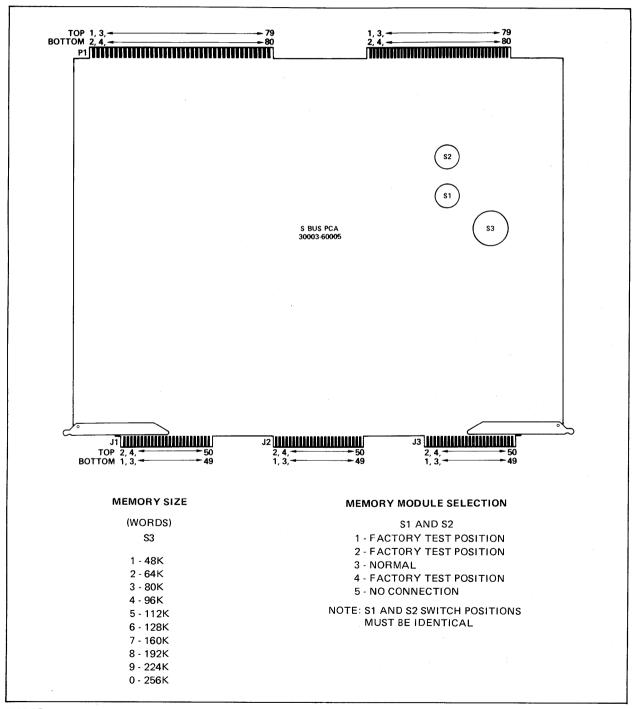

| S-Bus PCA 30003-60005                              | Output                                    |

| Memory Size 4-16                                   | Errors4-44                                |

| Memory Module Selection                            | CE Operating Procedures 4-44              |

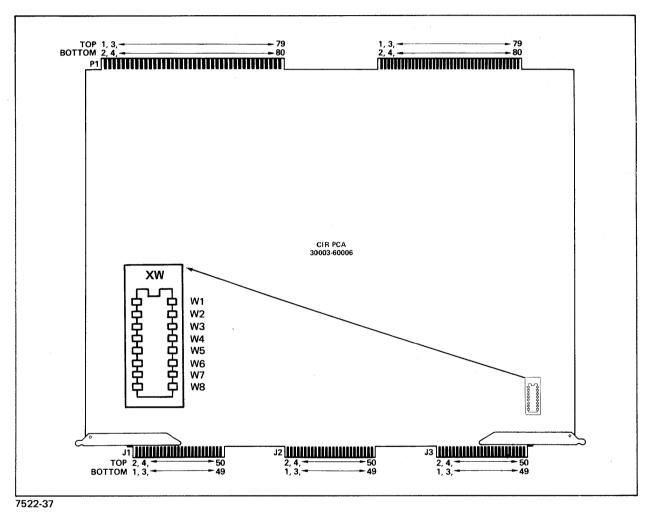

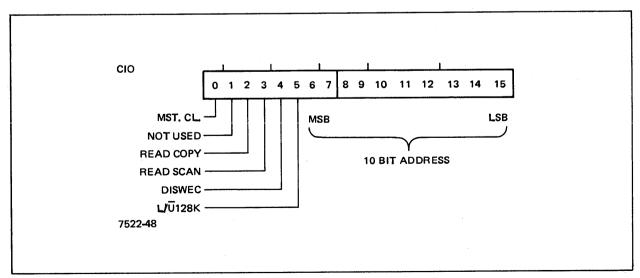

| Current Instruction Register (CIR)                 | FLI PCA Programming4-44                   |

| PCA 30003-60006, Extended Instruction Set          | TIO Command4-45                           |

| (EIS) PCA 30012-60001                              | CIO Command4-46                           |

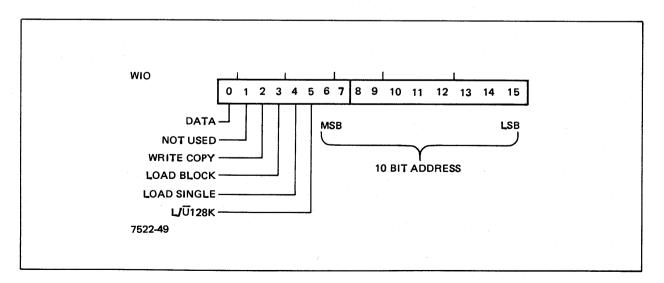

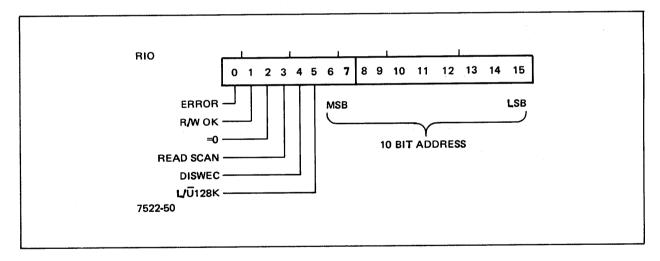

| Jumpers                                            | WIO Command                               |

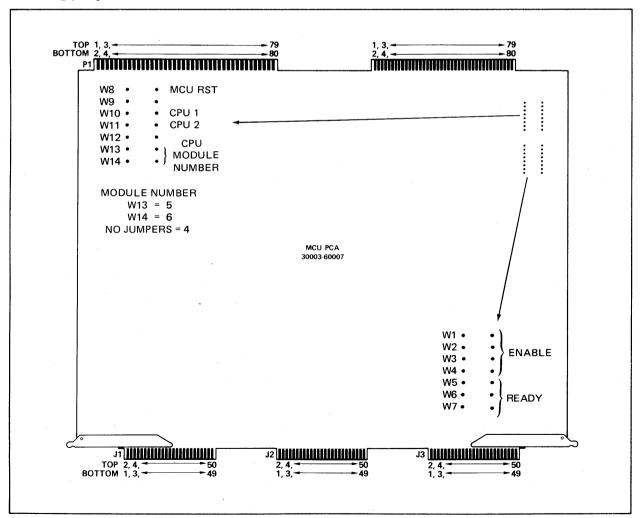

| MCU PCA 30003-600074-19                            | RIO Command4-48                           |

| Enable                                             | Interfacing                               |

| Ready                                              | CTL Data Bus4-48                          |

| CPU Number 4-19                                    | IOP Bus 4-49                              |

| CPU Module Number                                  | Fault Logging Interface Bus4-49           |

| MCU Reset                                          | Power Bus 4-49                            |

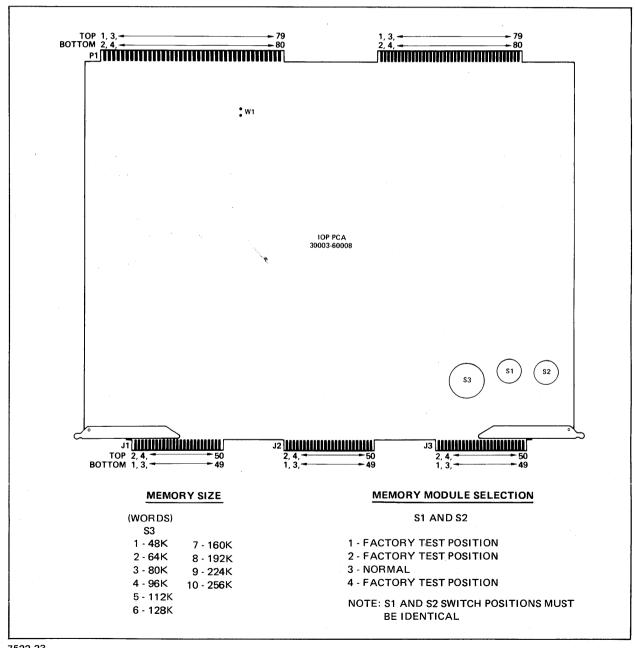

| IOP PCA 30003-600084-20                            | Error Correcting Memory Module            |

| Enable/Disable                                     | SMA PCA                                   |

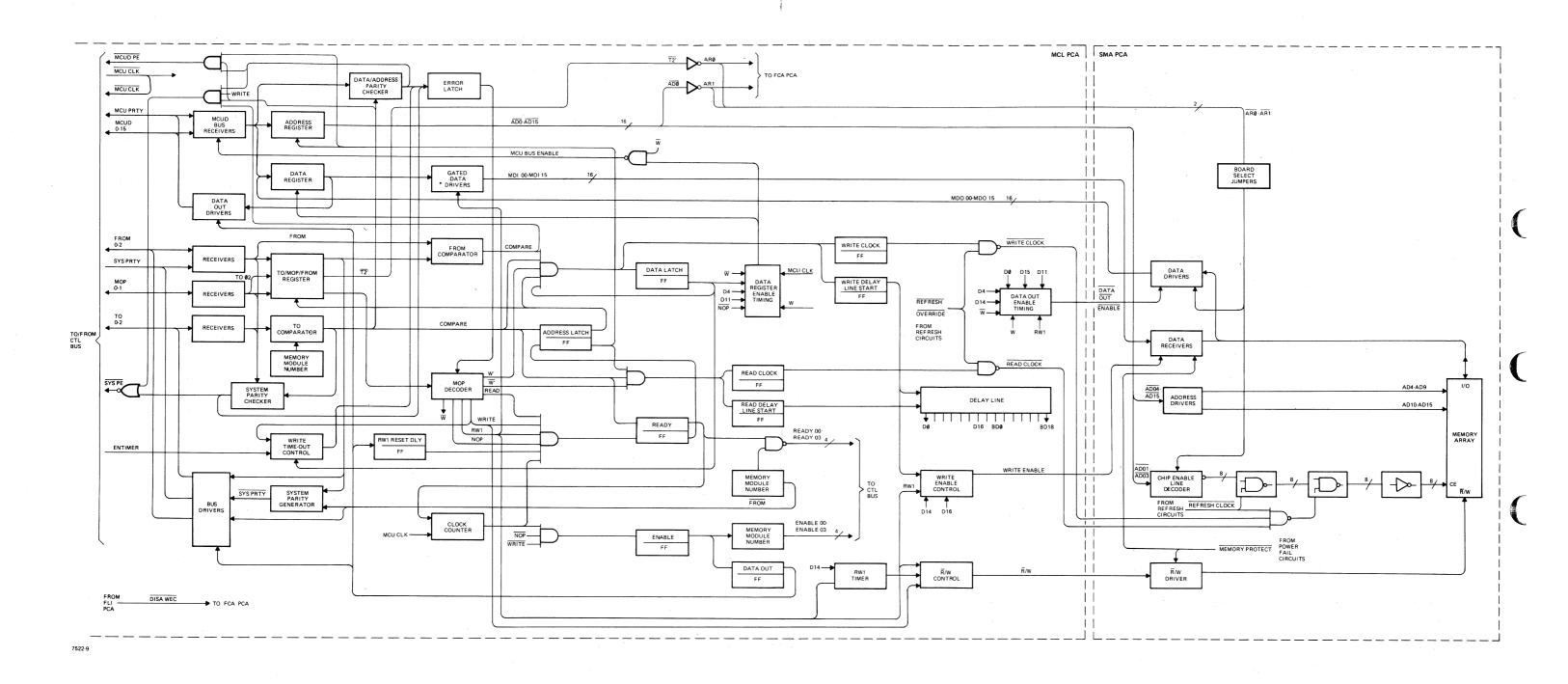

| Memory Size                                        | MCL PCA4-52                               |

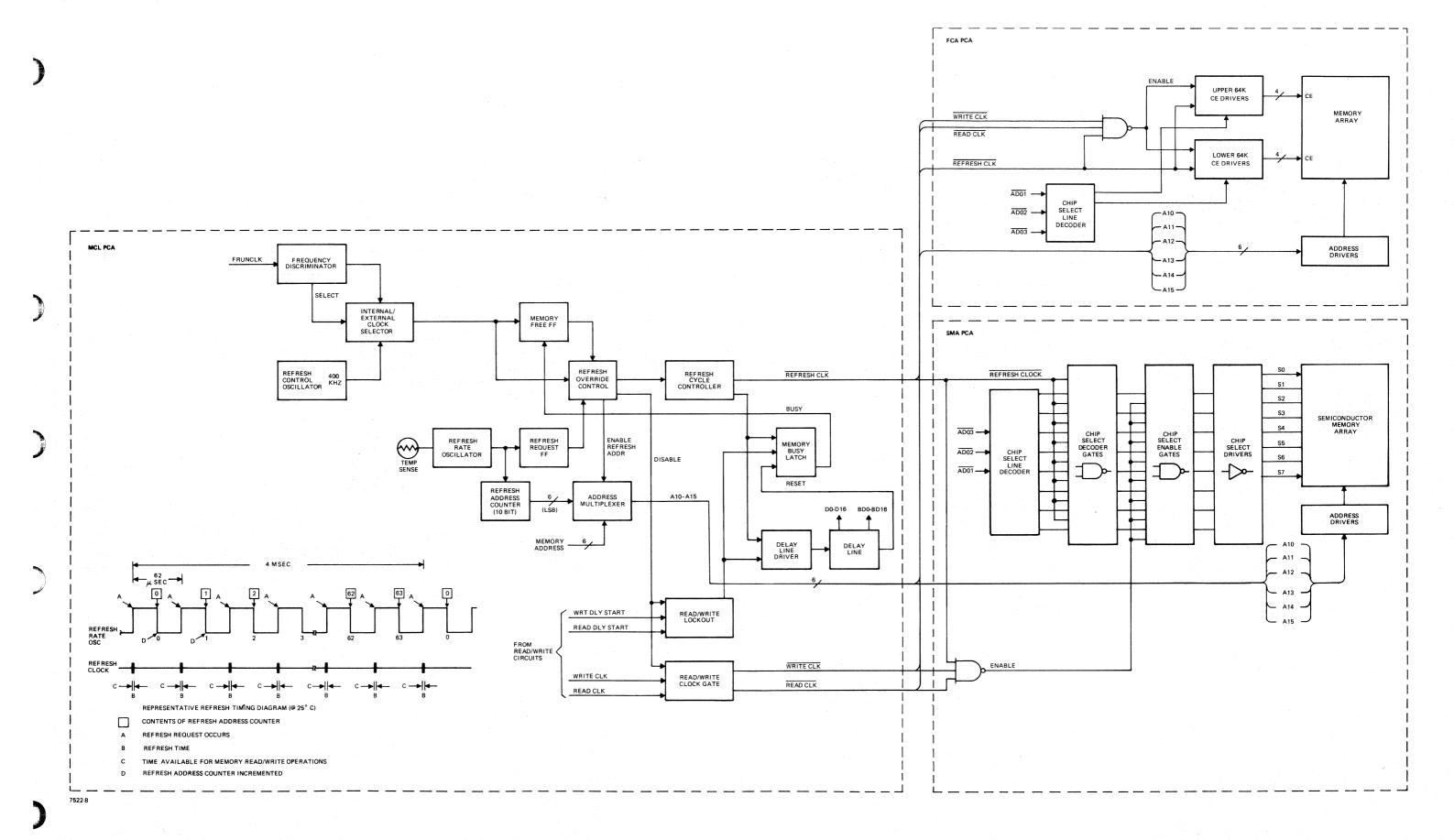

| Memory Module Selection 4-20                       | Refresh 4-52                              |

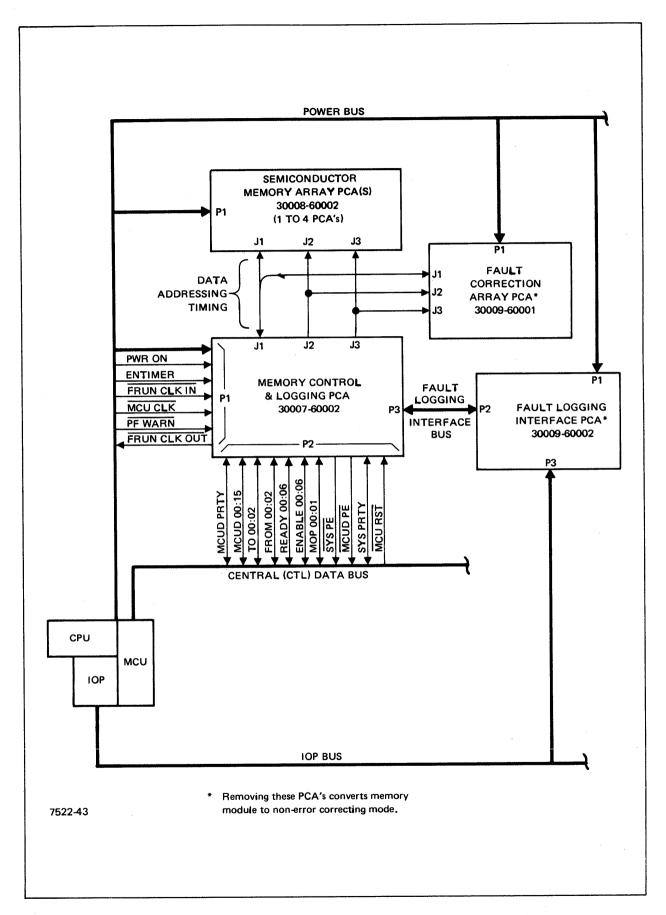

| Semiconductor Memory Array (SMA)                   | Memory Operations4-58                     |

| PCA 30008-60002 4-21                               | Read                                      |

| Memory Module Configuration                        | Write                                     |

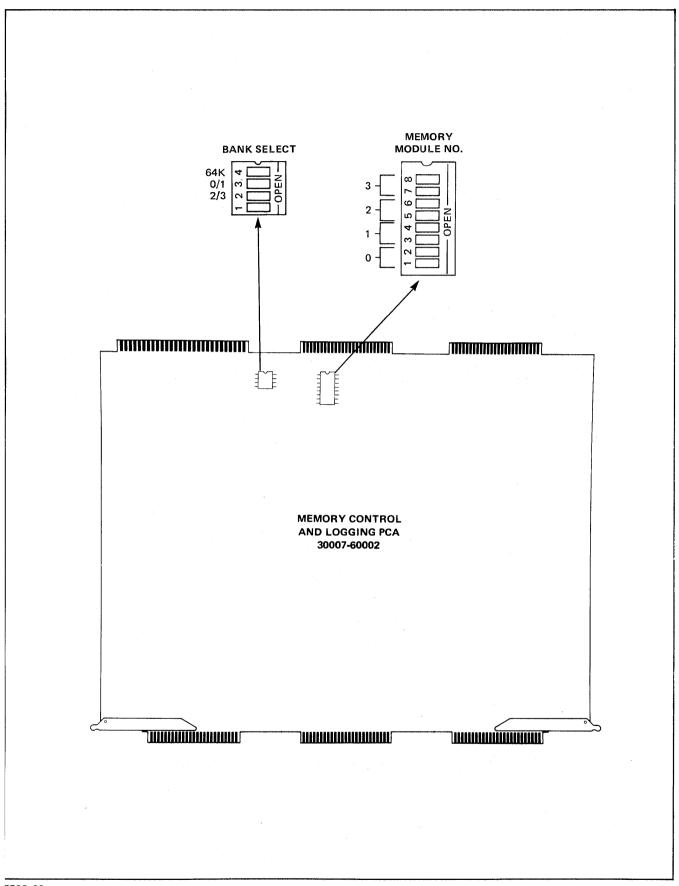

| Memory Control and Logging (MCL)                   | RW1                                       |

| PCA 30007-60002                                    | NOP 4-64                                  |

| Memory Module Configuration                        | Fault Correction and Error Logging 4-64   |

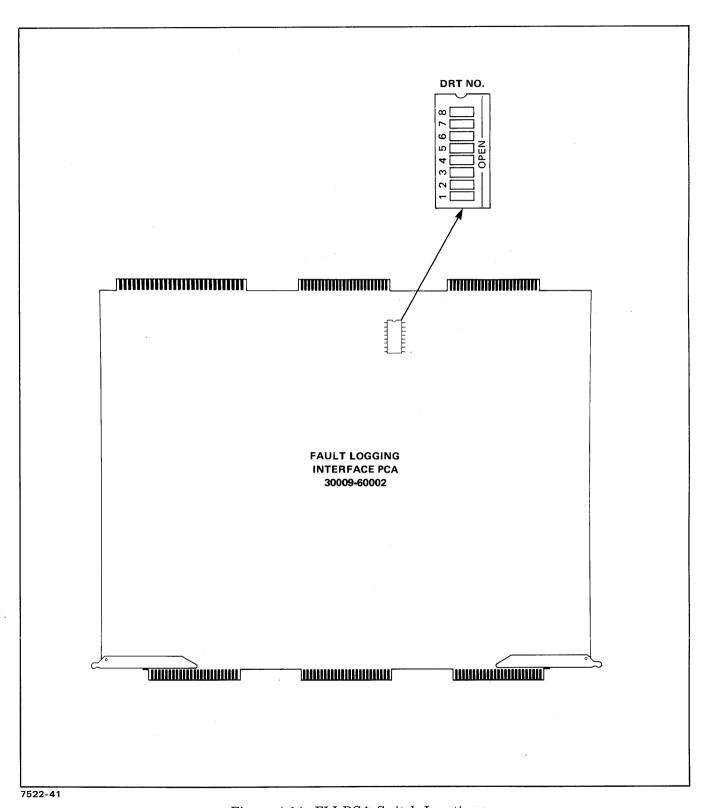

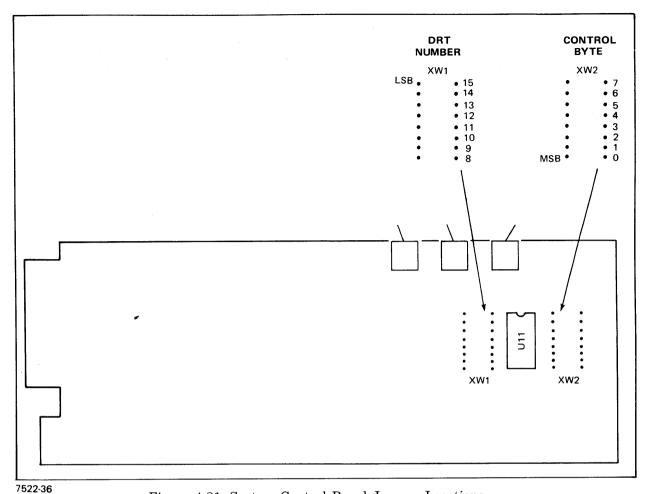

| Fault Logging Interface (FLI) PCA 30009-60002 4-24 | Fault Correction                          |

| DRT Number                                         | Fault Logging Interface PCA               |

| Fault Correction Array (FCA) PCA 30009-60001 4-25  | Power Fail                                |

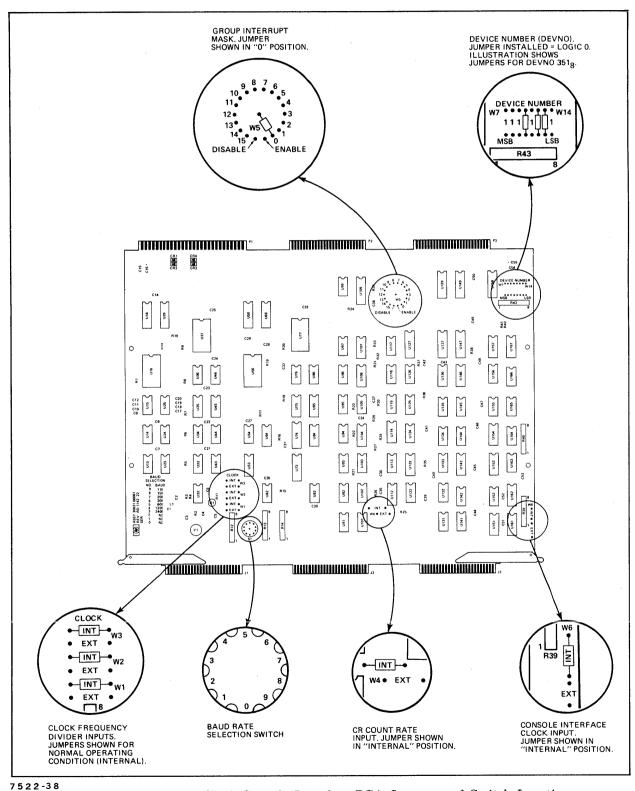

| System Clock/Console Interface PCA                 | PCA Jumpers                               |

| 30031-60001                                        | TOA dumpers                               |

|                                                    |                                           |

| Frequency Divider Input Selection W1, W2, W34-27   | Section V Page                            |

| CR Count Rate Input W4                             | REPLACEABLE PARTS                         |

| Group Mask Interrupt Mask W54-27                   | Introduction                              |

| Serial Interface Clock Input W6                    | Replaceable Parts                         |

| Device Number W7 thru W6                           | Card Cages                                |

| Baud Rate Selection S1                             | HP 30002B Card Cage5-2                    |

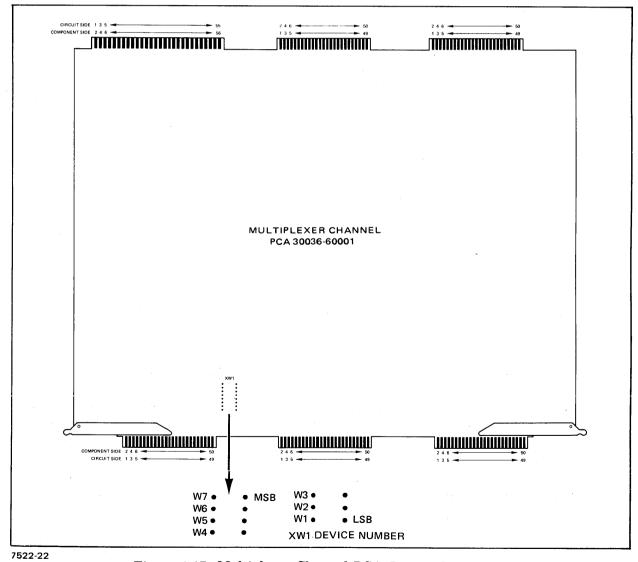

| Multiplexer Channel PCA                            | HP 30002C Card Cage5-2                    |

| 30036-600014-27                                    | HP 30002B Card Cage - Fan Replacement 5-3 |

| Device Number                                      | HP 30002C Card Cage - Fan Replacement 5-4 |

|                                                    |                                           |

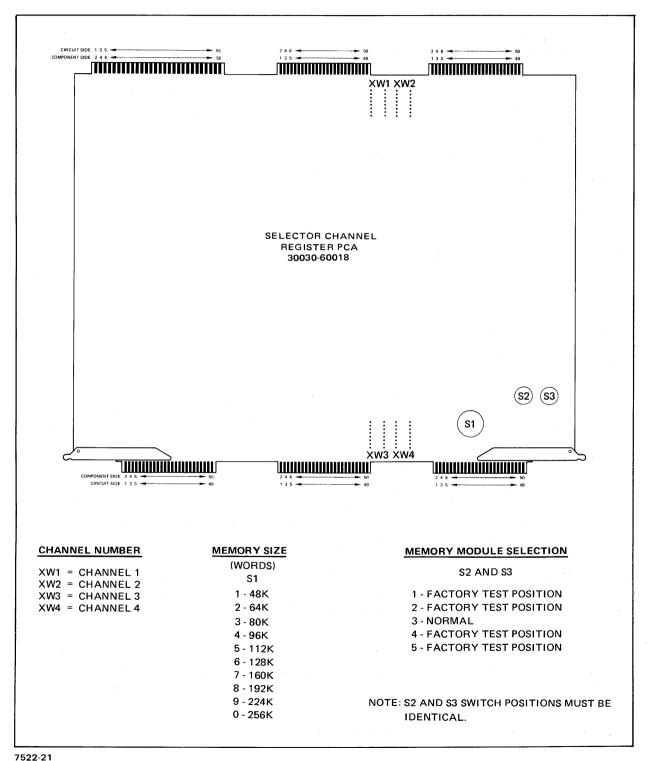

| Selector Channel Register PCA 30030-60018          |                                           |

| Channel Number                                     | Appendix A Page                           |

|                                                    | MICRODIAGNOSTICS                          |

| Memory Size                                        | Microdiagnostics                          |

| Memory Module Selection 4-30                       | CPU Register Test                         |

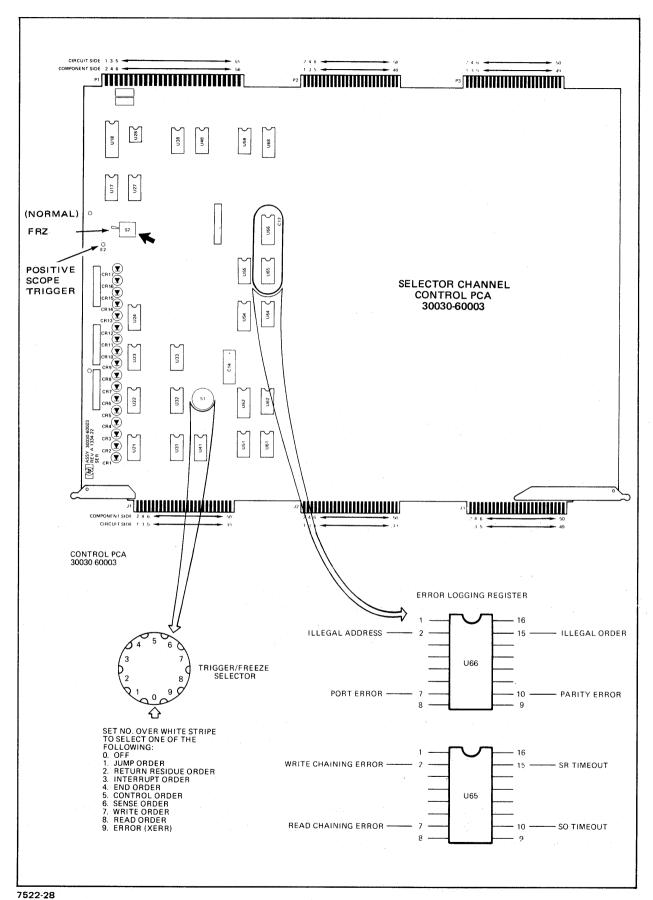

| Selector Channel Control PCA                       | Memory Test A-2                           |

| 30030-60003                                        | I/O Test                                  |

| Selectable Trigger/Freeze4-30                      |                                           |

| Error Logging Register 4-30                        | A II D                                    |

| Indicators 4-32                                    | Appendix B                                |

| Selector Channel Maintenance PCA                   | SYSTEM POWER SUPPLIES                     |

| (SCMB) 30033-60001                                 | Introduction                              |

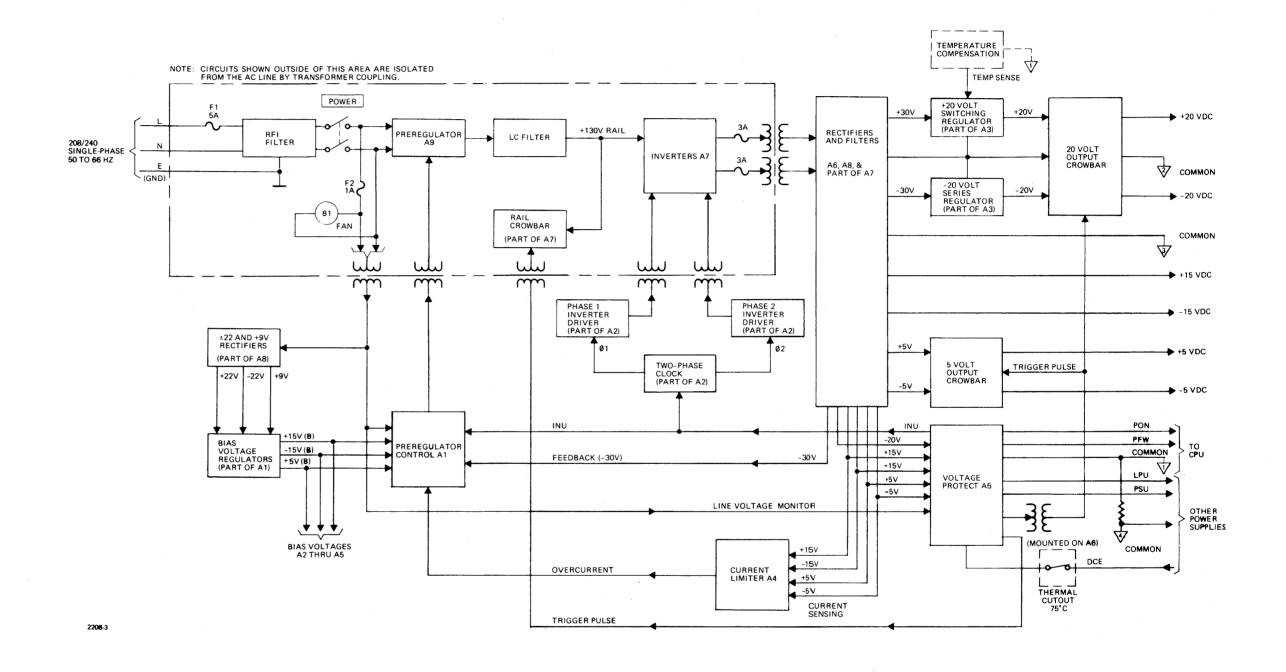

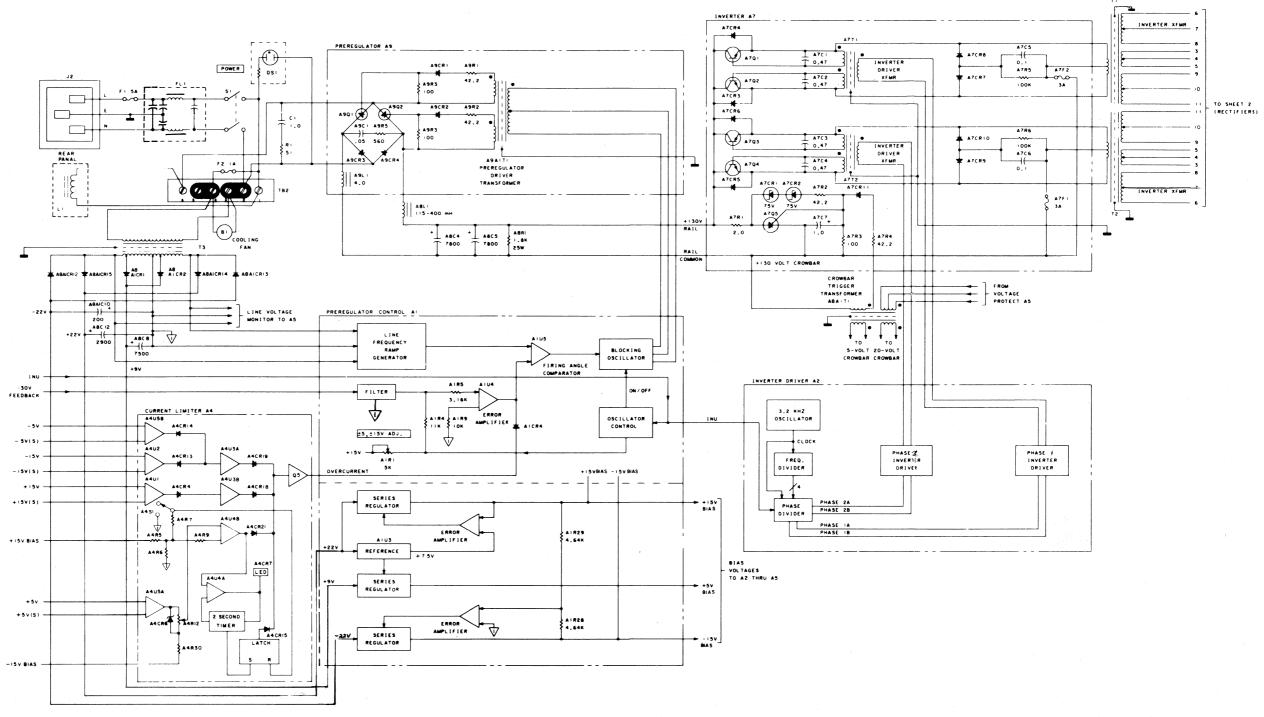

| Configuration                                      | HP 30310A Power Supply B-1                |

| System Control Panel 30003-60012 4-33              | mission of Onesetten                      |

| DDT Manakan 4 99                                   | Theory of Operation                       |

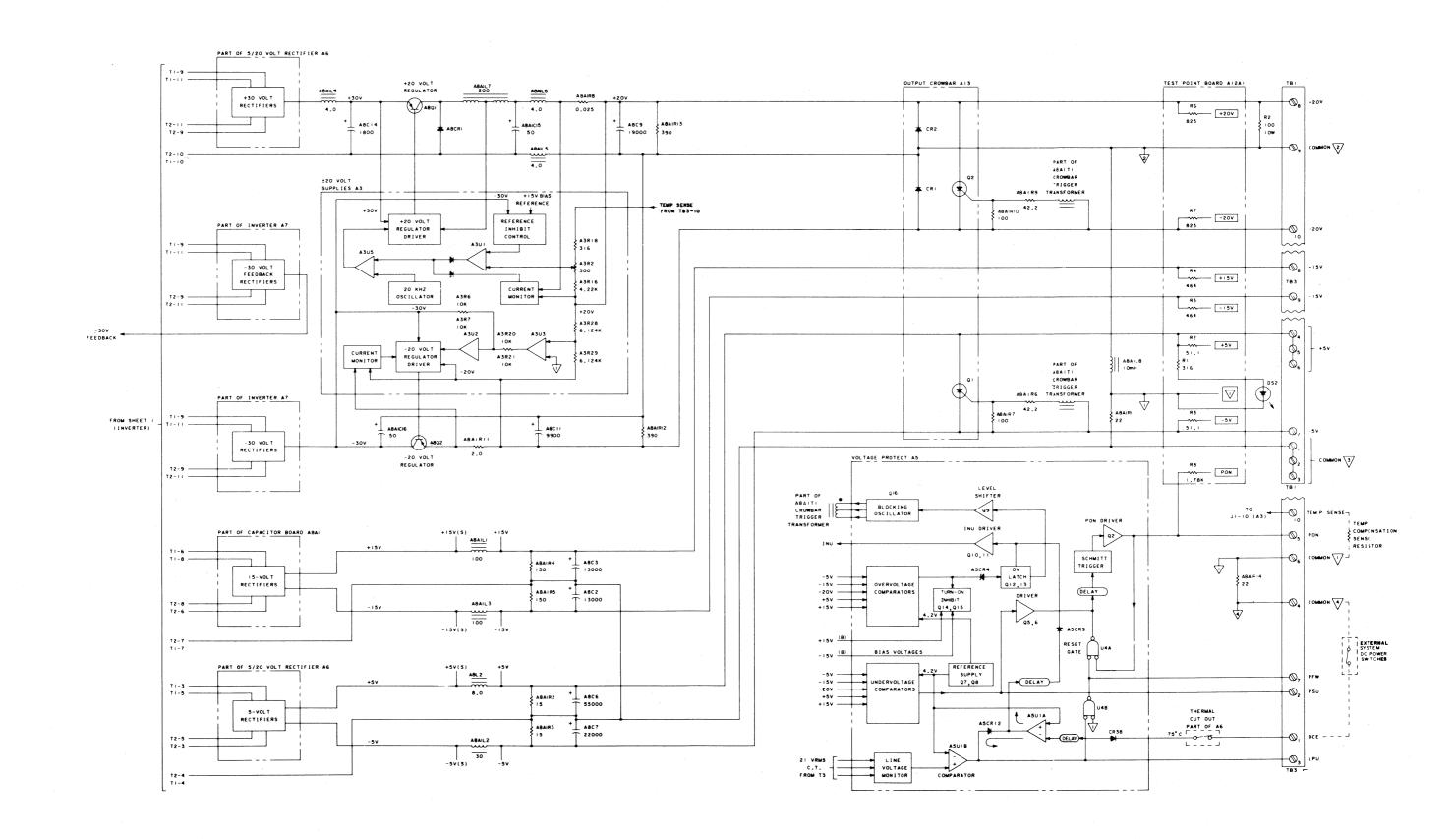

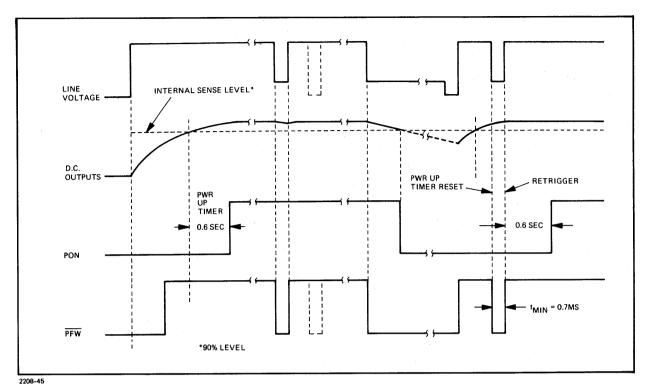

| DRT Number                                         | Block Diagram Description B-4             |

| Memory IC Replacement4-33                          | Block Diagram Description                 |

|                                                    | Block Diagram Description B-4             |

## **CONTENTS** (continued)

| Test Equipment Ground B-10                   | Replacement Procedures B-36             |

|----------------------------------------------|-----------------------------------------|

| Test Equipment Common B-1'                   | Power Supply Replacement B-36           |

| Preventive Maintenance B-1'                  |                                         |

| HP 30310A Adjustments B-13                   |                                         |

| Preregulator Adjustment B-13                 | TO A |

| 20-Volt Adjustment B-19                      | HP 30312A Power Supply B-39             |

| Voltage Protect PCA Adjustment B-19          | Theory of Operation B-39                |

| Troubleshooting an HP 30310A B-20            | Overcurrent Protection                  |

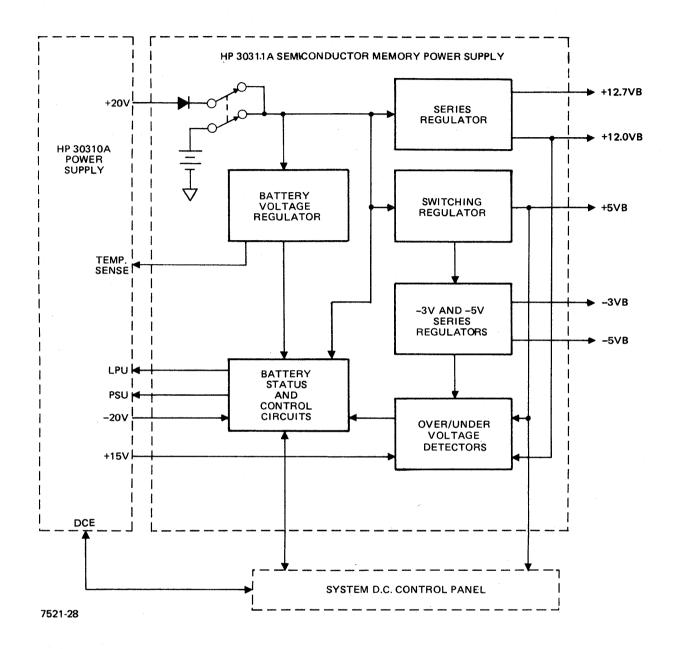

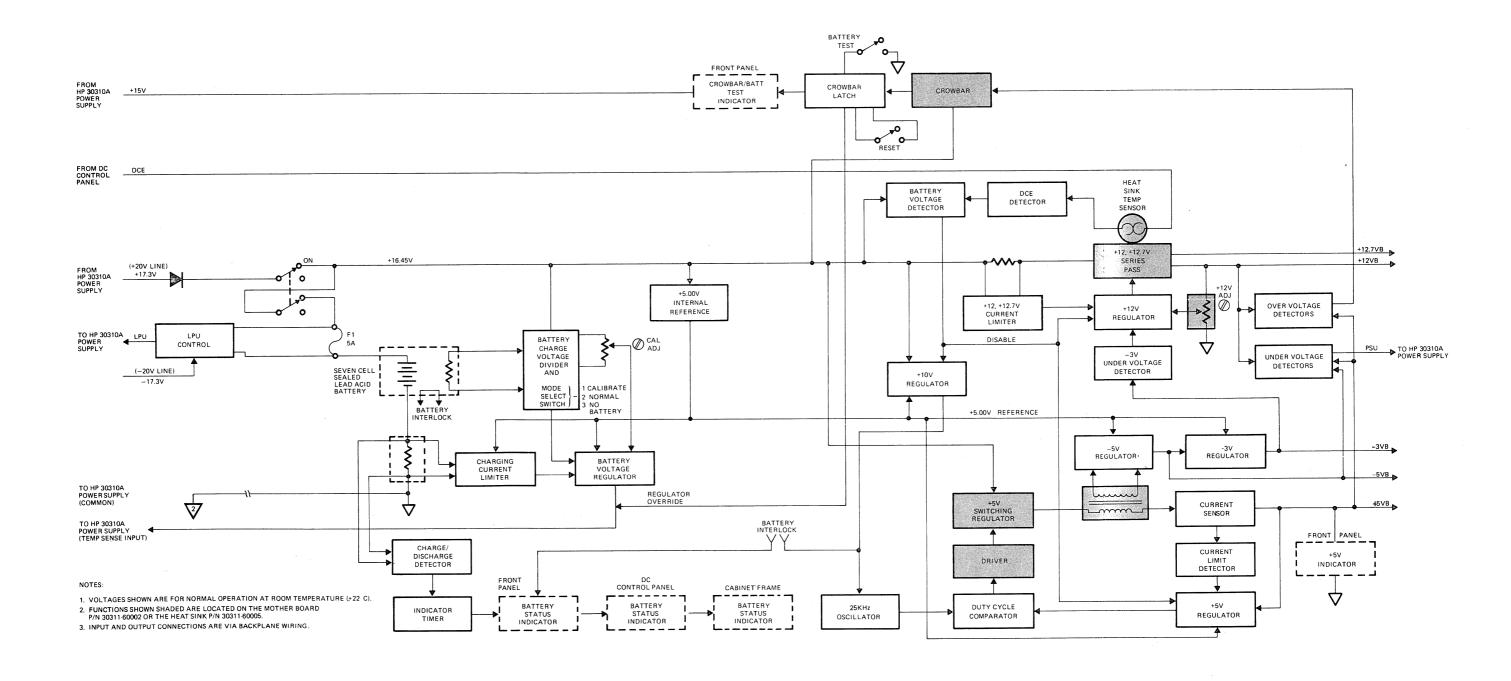

| HP 30311A Power Supply                       | Under Voltage Protection B-41           |

| Theory of Operation                          | Power Failures                          |

| Block Diagram Description B-23               | B DC Enable                             |

| Detailed Block Diagram Description B-25      | 3 HP 30312A Maintenance                 |

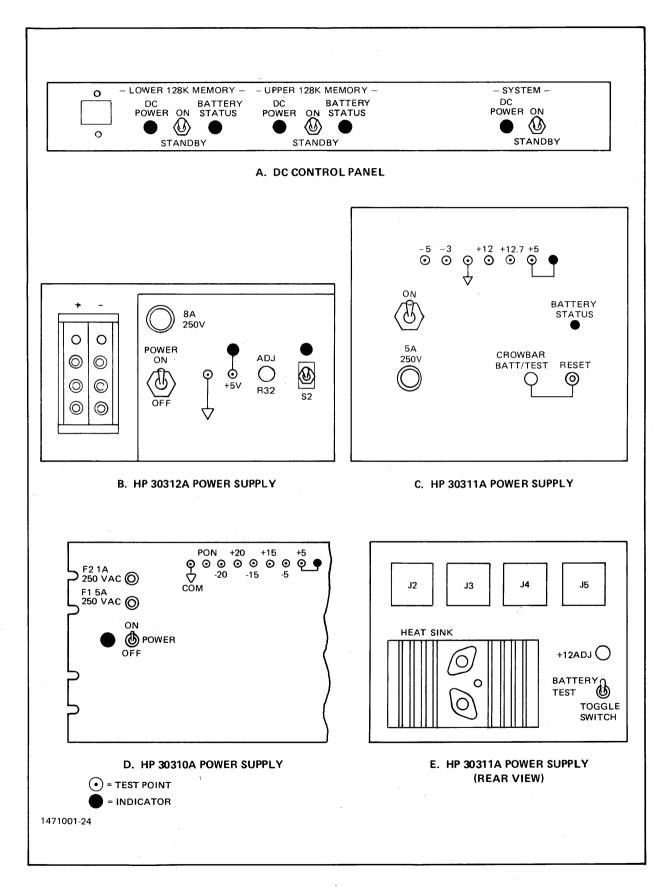

| Controls and Indicators B-2s                 | 8 Wiring InformationB-41                |

| HP 30311A Maintenance B-30                   |                                         |

| Wiring Information B-30                      |                                         |

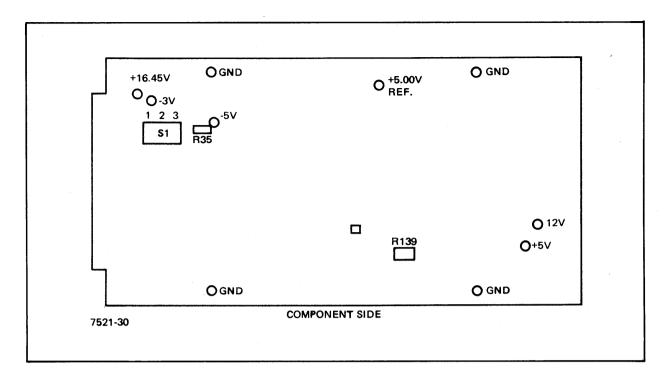

| Principal Servicing Points B-3               |                                         |

| Troubleshooting an HP 30311A B-3             |                                         |

| Preventive Maintenance                       | BATTERY CARE                            |

| Voltage Checks B-3                           | Introduction                            |

| Battery Test                                 | 2 Environment                           |

| HP 30311A Adjustments B-33                   | Shelf Life                              |

| Battery (Float) Voltage Adjustment B-32      | Restoring Damaged Cells                 |

| +12 Volt Adjustment B-3                      | Shipping Batteries                      |

| +5.00 Volt Internal Reference Adjustment B-3 | 5 Summary                               |

## **TABLES**

| Table                                                | Title                                                                                                                                                                                                         | Page                                | Table                                        | Title                                                                                                            | Page              |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|

| 1-1.<br>1-2.<br>1-3.                                 | On-Line Verification Programs                                                                                                                                                                                 | 1-2                                 | 4-7.<br>4-8.<br>5-1.                         | Memory Configurations                                                                                            | 4-38              |

| 1-4.                                                 | System Control Panel, Switch and Lamp Functions                                                                                                                                                               |                                     | 5-2.<br>5-3.                                 | Replaceable Cables                                                                                               | $\dots 5$ -2      |

| 3-1.                                                 | Maintenance Panel Controls and Indicators                                                                                                                                                                     |                                     | A-1.<br>A-2.                                 | CPU Register Codes                                                                                               |                   |

| 3-2.<br>4-1.<br>4-2.<br>4-3.<br>4-4.<br>4-5.<br>4-6. | Pin Connections, J3 of MPI PCA HP 30311A Test Jack Voltages SMA PCA Board Select Jumpers MCL PCA Switch Positions S1 Baud Rate Selection External Baud Rate Selection Selector Channel Control PCA Indicators | 4-4<br>4-22<br>4-22<br>4-27<br>4-28 | B-1.<br>B-2.<br>B-3.<br>B-4.<br>B-5.<br>B-6. | HP 30310A Power Supply Specifications DC Output Voltages for the HP 30310A HP 30311A Power Supply Specifications | B-19 B-29 B-3 B-3 |

JAN 1977 ix

## **ILLUSTRATIONS**

| Figure       | Title                                   | Page             | Figure        | e Title Page                                    |

|--------------|-----------------------------------------|------------------|---------------|-------------------------------------------------|

| 1-1.         | System Control Panel                    | 1-5              | 4-22.         | Check Bit Assignments4-36                       |

| 1-2.         | Type 500 Plot                           | $\dots 1-24$     | 4-23.         | Check Bits and Error Code (No Error) 4-36       |

| 1-3.         | Type 600/700 Plot                       | 1-24             | <b>4-24</b> . | Check Bits and Error                            |

| 1-4.         | Master Tape                             | 1-27             |               | (Error Condition)                               |

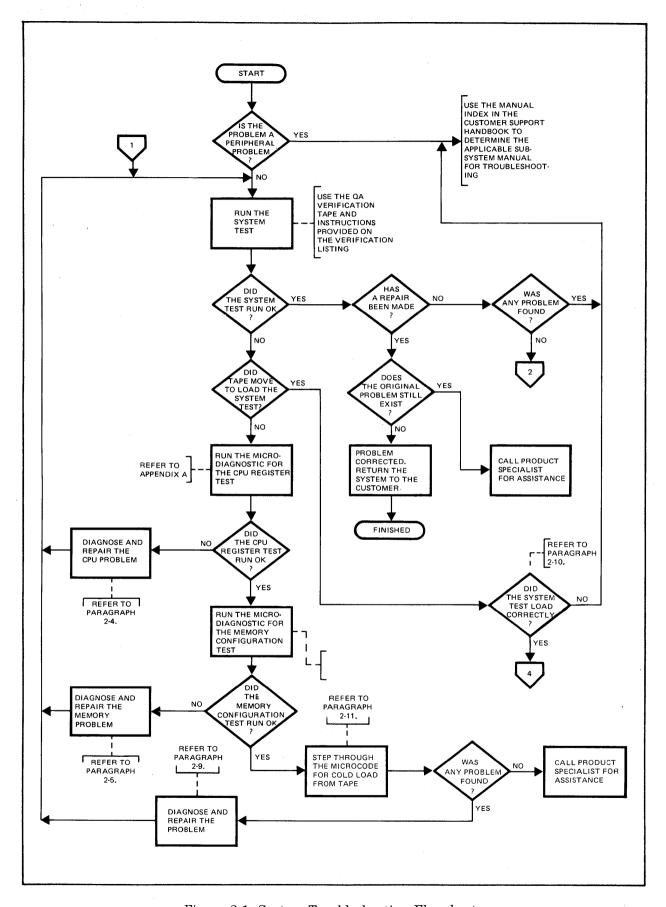

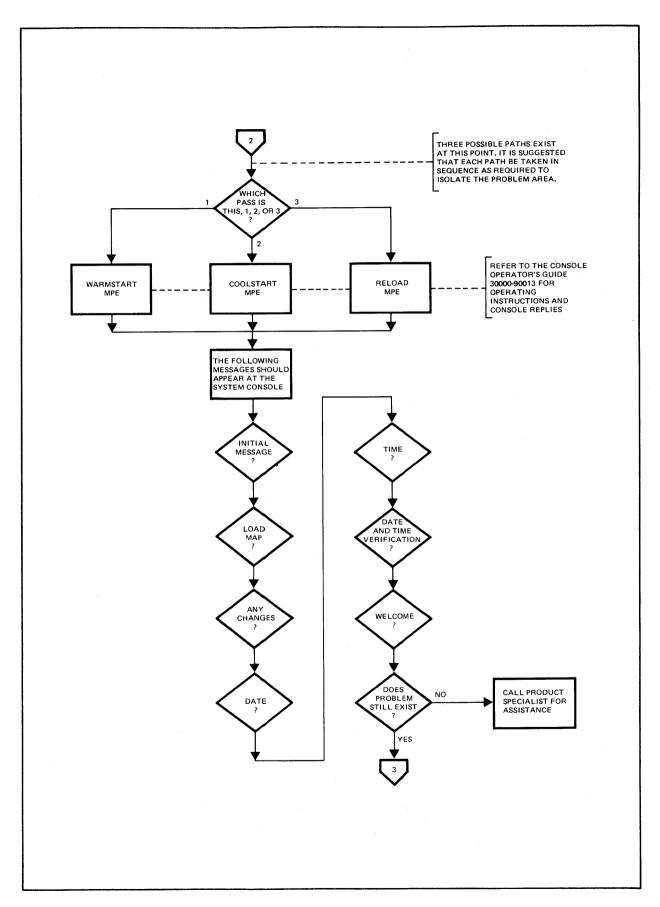

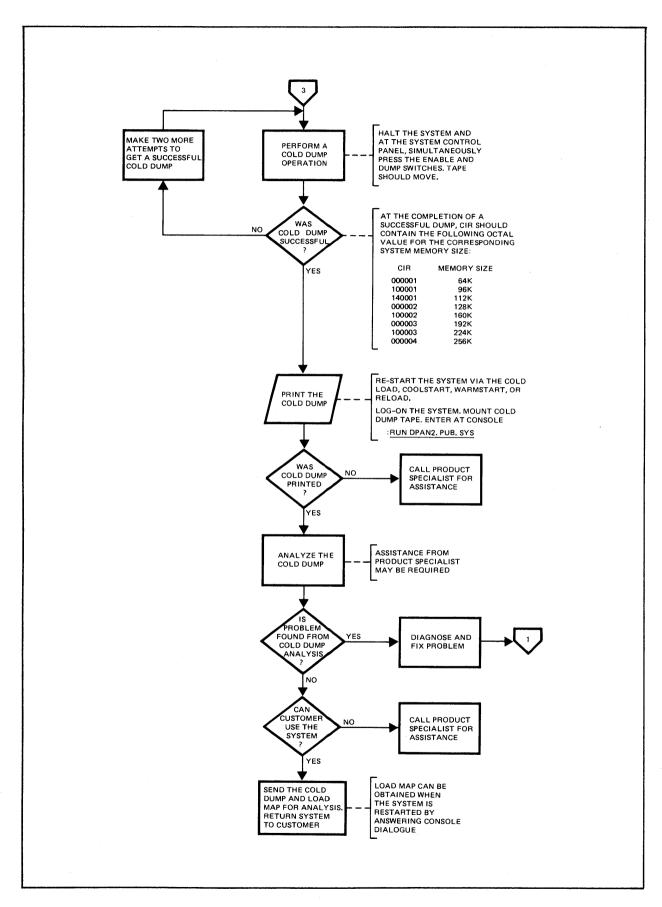

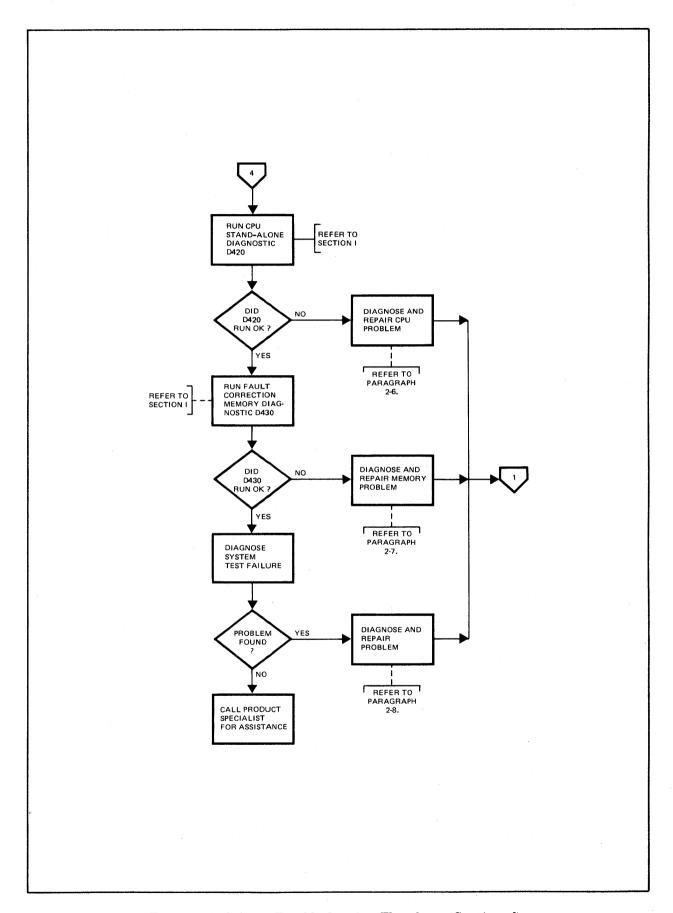

| 2-1.         | System Troubleshooting Flowchart        | 2-9              | 4-25.         | Error Logging Array Address Structure 4-38      |

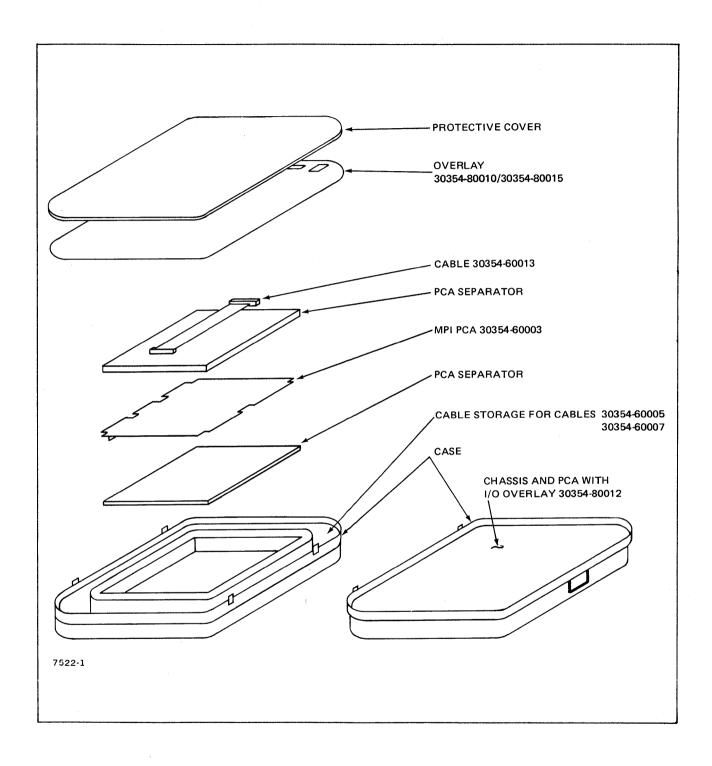

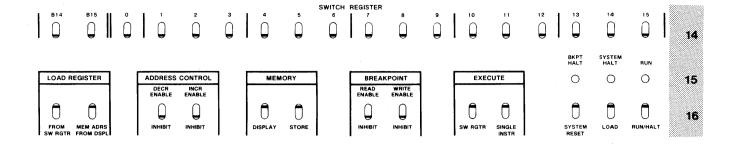

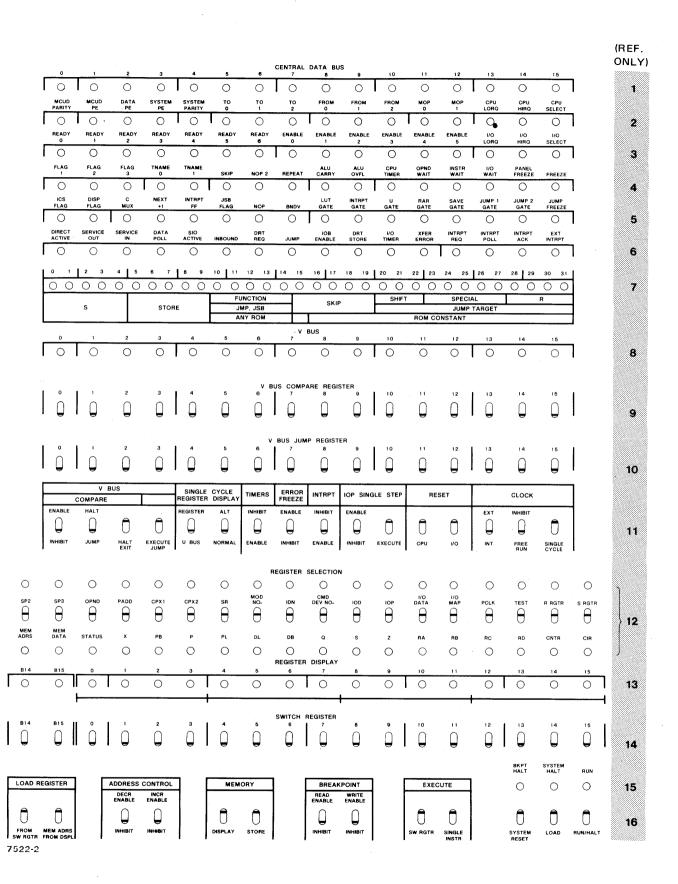

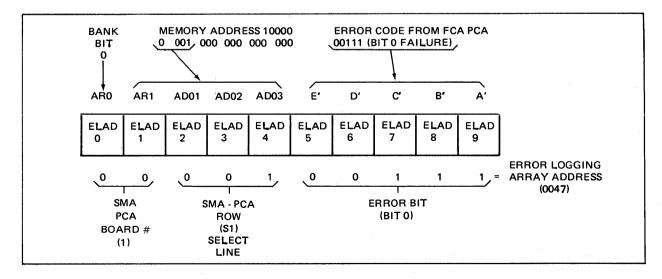

| 3-1.         | HP 30354A Maintenance Panel             | $\dots 3-2$      | 4-26.         | Error Printout Format                           |

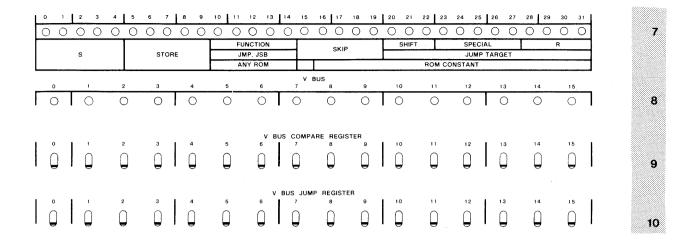

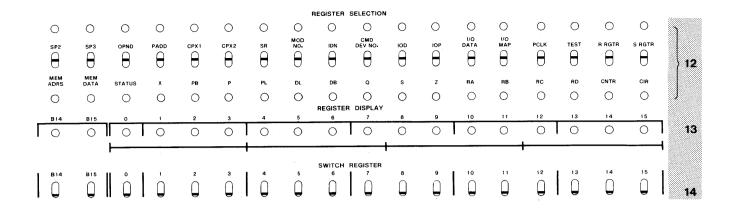

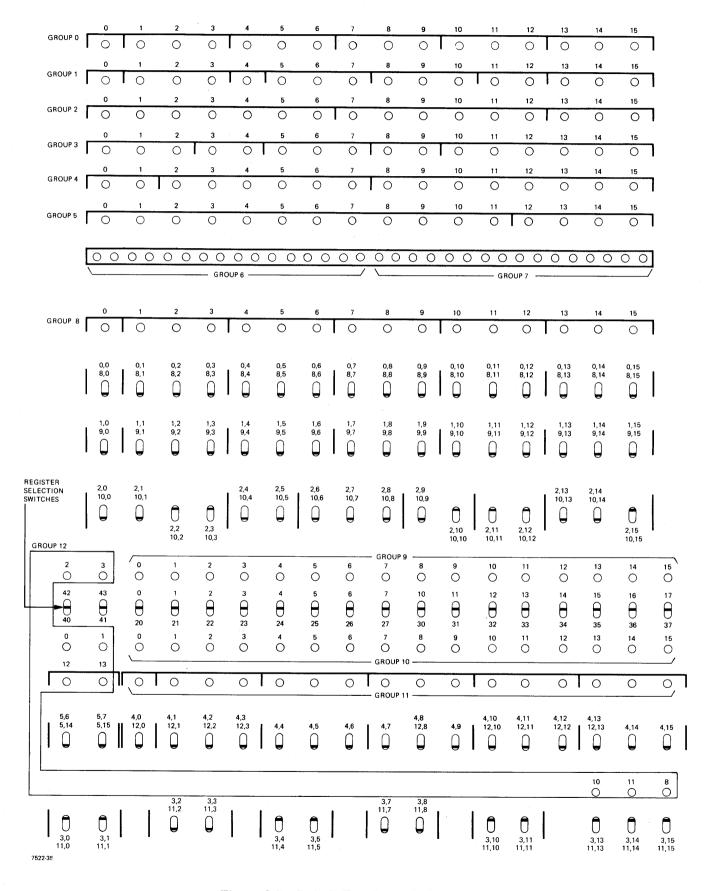

| 3-2.         | Maintenance Panel Switches and Lamps .  | 3-17             | 4-27.         | Typical Error Message                           |

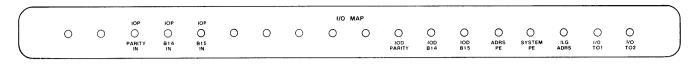

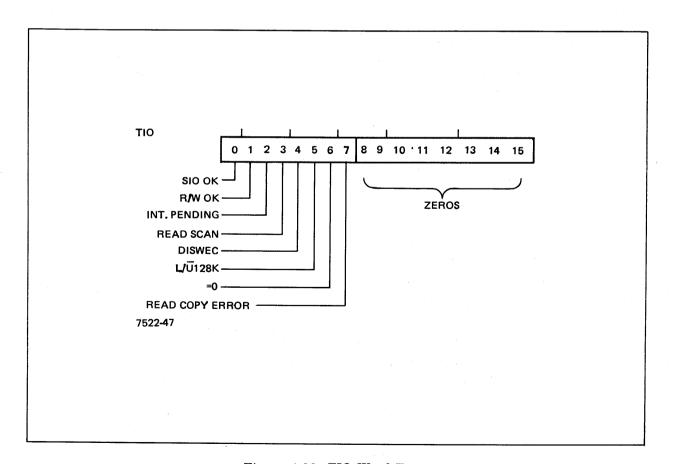

| 3-3.         | I/O Overlay                             | 3-18             | 4-28.         | TIO Word Format                                 |

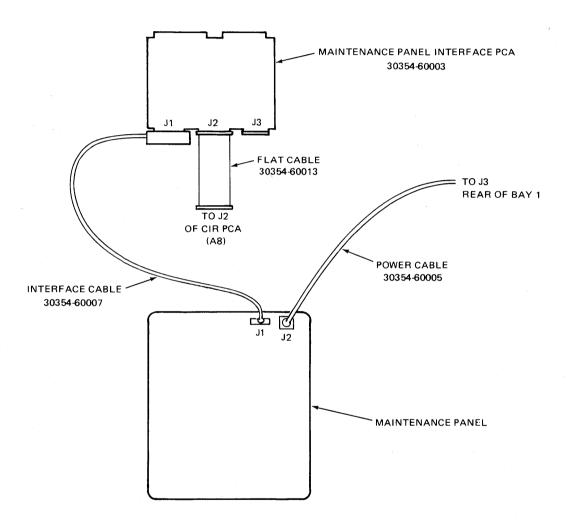

| 3-4.         | Connections for Use                     | 3-20             | 4-29.         | CIO Word Format                                 |

| 3-5.         | Switch Test Lamp Indications            | 3-24             | 4-30:         | WIO Word Format                                 |

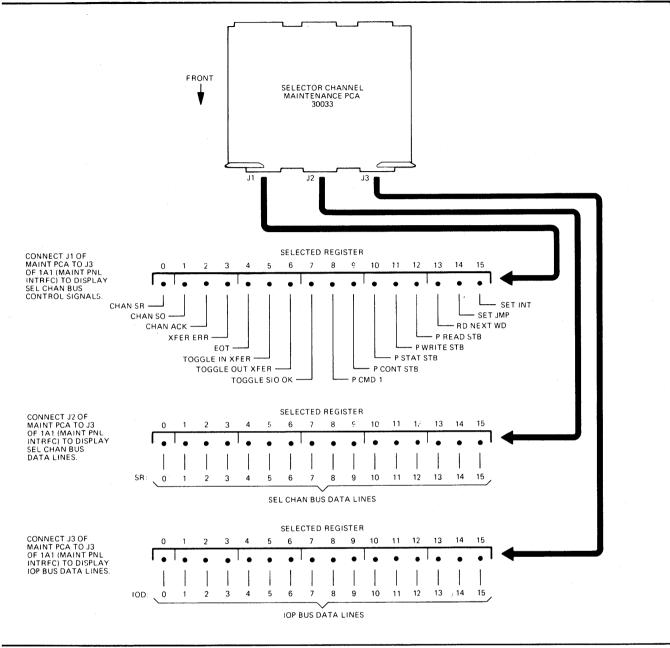

| <b>4-1</b> . | SCMB State Display                      | 4-7              | 4-31.         | RIO Word Format                                 |

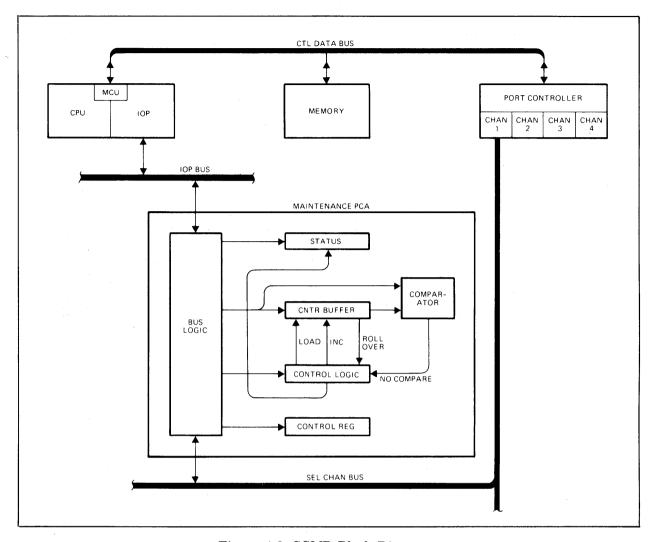

| <b>4-2</b> . | SCMB Block Diagram                      | 4-8              | 4-32.         | Memory Module Interface Diagram 4-50            |

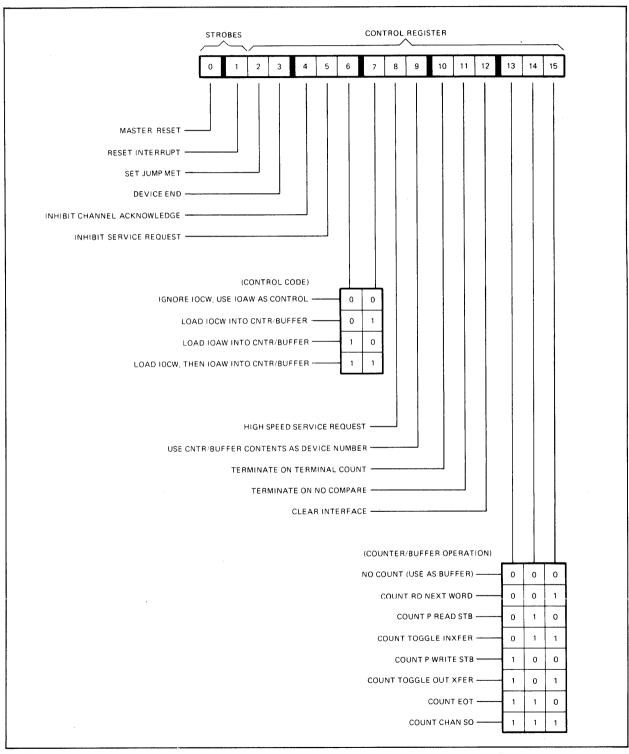

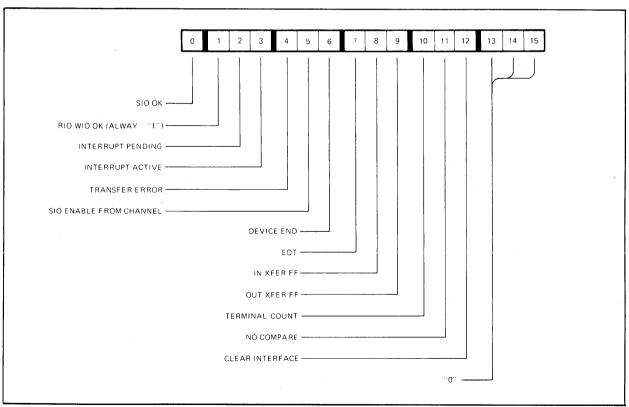

| 4-3.         | SCMB Control Word Format                | 4-10             | 4-33.         | Error Correcting Memory Functional              |

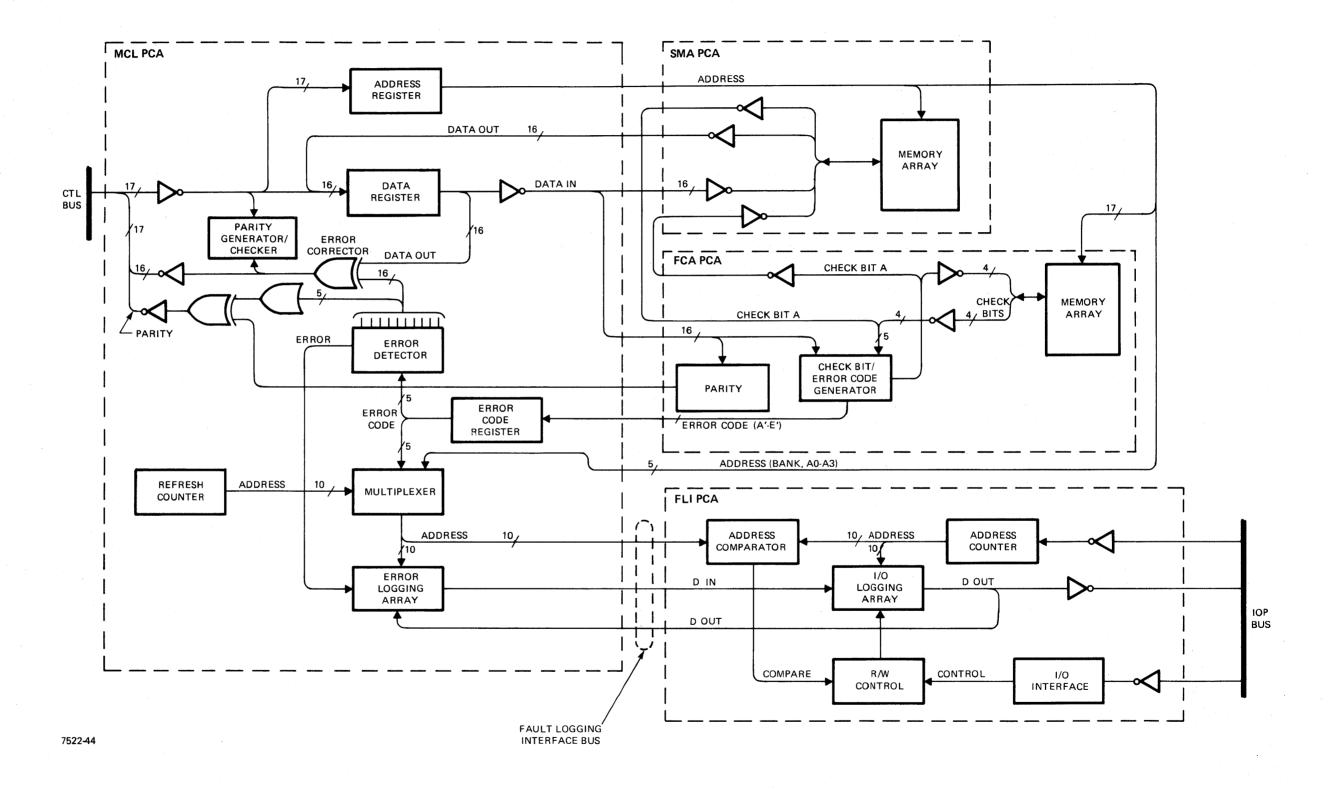

| 4-4.         | SCMB Status Word Format                 | 4-12             | - 00.         | Block Diagram 4-53                              |

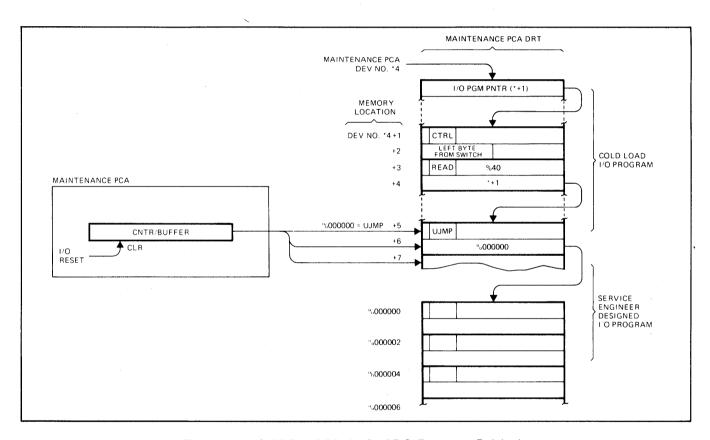

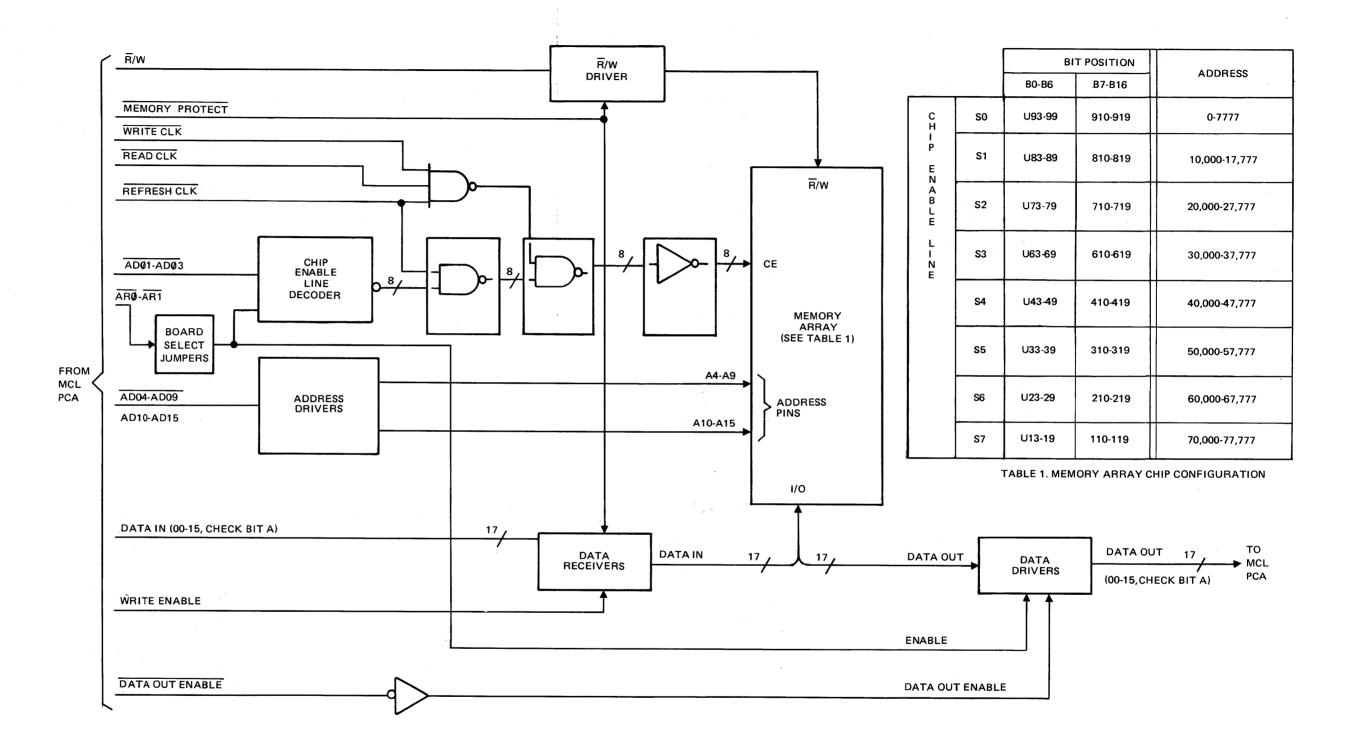

| <b>4-5</b> . | Cold Load Method of I/O Program         |                  | 4-34.         | SMA PCA Functional Block Diagram 4-55           |

|              | Initiation                              | 4-14             | 4-35.         | Refresh Circuit Functional Block Diagram . 4-59 |

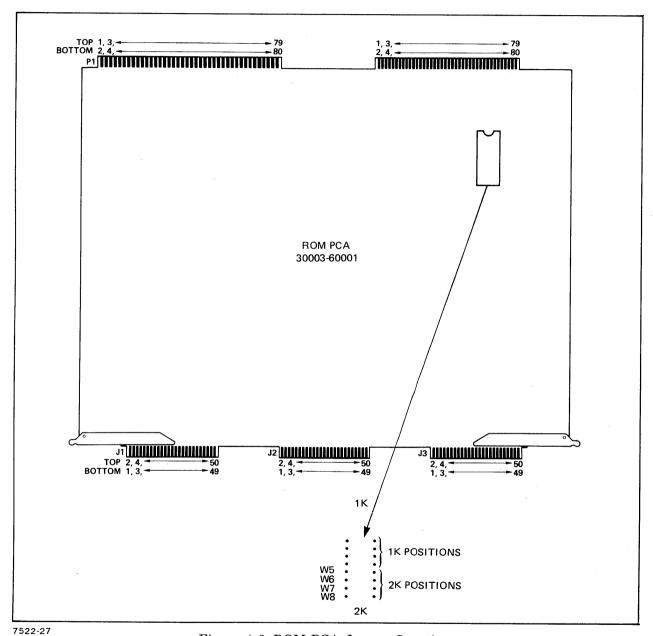

| 4-6.         | ROM PCA Jumper Locations                | 4-15             | 4-36.         | Memory MCU Functional Block Diagram . 4-61      |

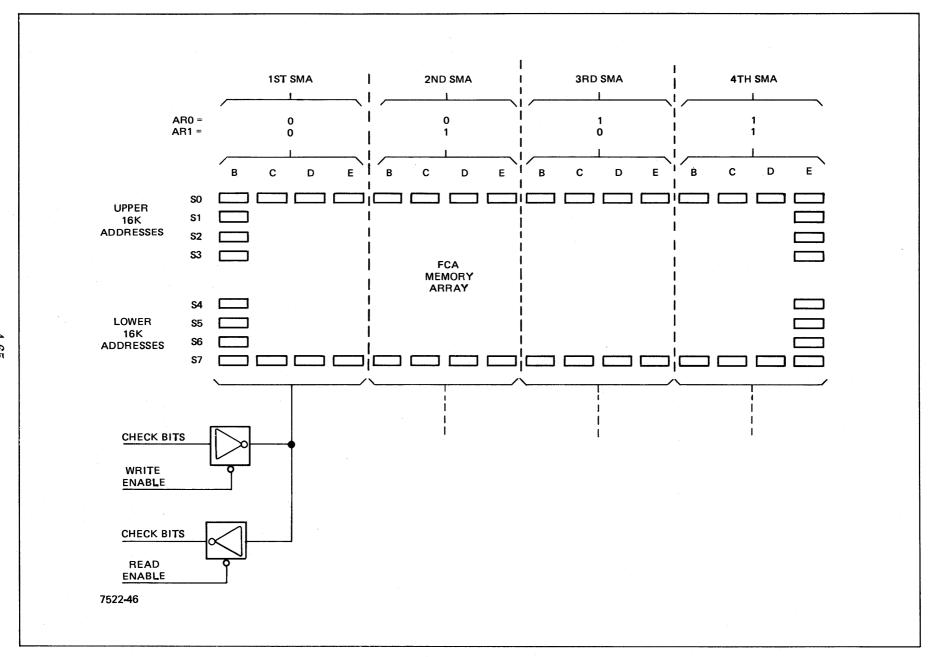

| <b>4-7</b> . | Skip and Special Field PCA              |                  | 4-37.         | FCA PCA Memory Array4-65                        |

|              | Jumper Locations                        | 4-16             | 4-38.         | Fault Correction and Error Logging              |

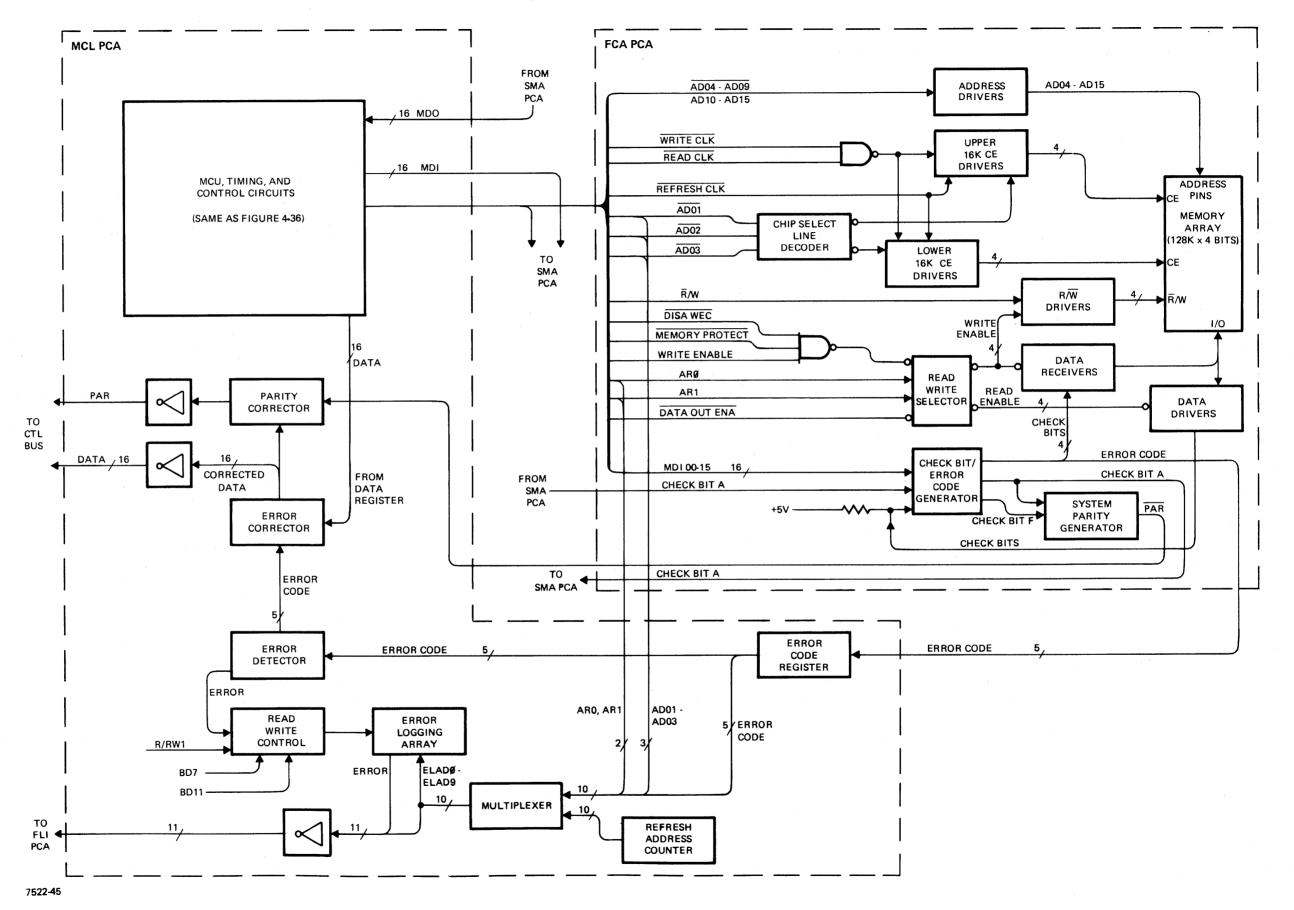

| <b>4-8</b> . | S-Bus PCA Switch Locations              | 4-17             | - 00.         | Functional Block Diagram 4-67                   |

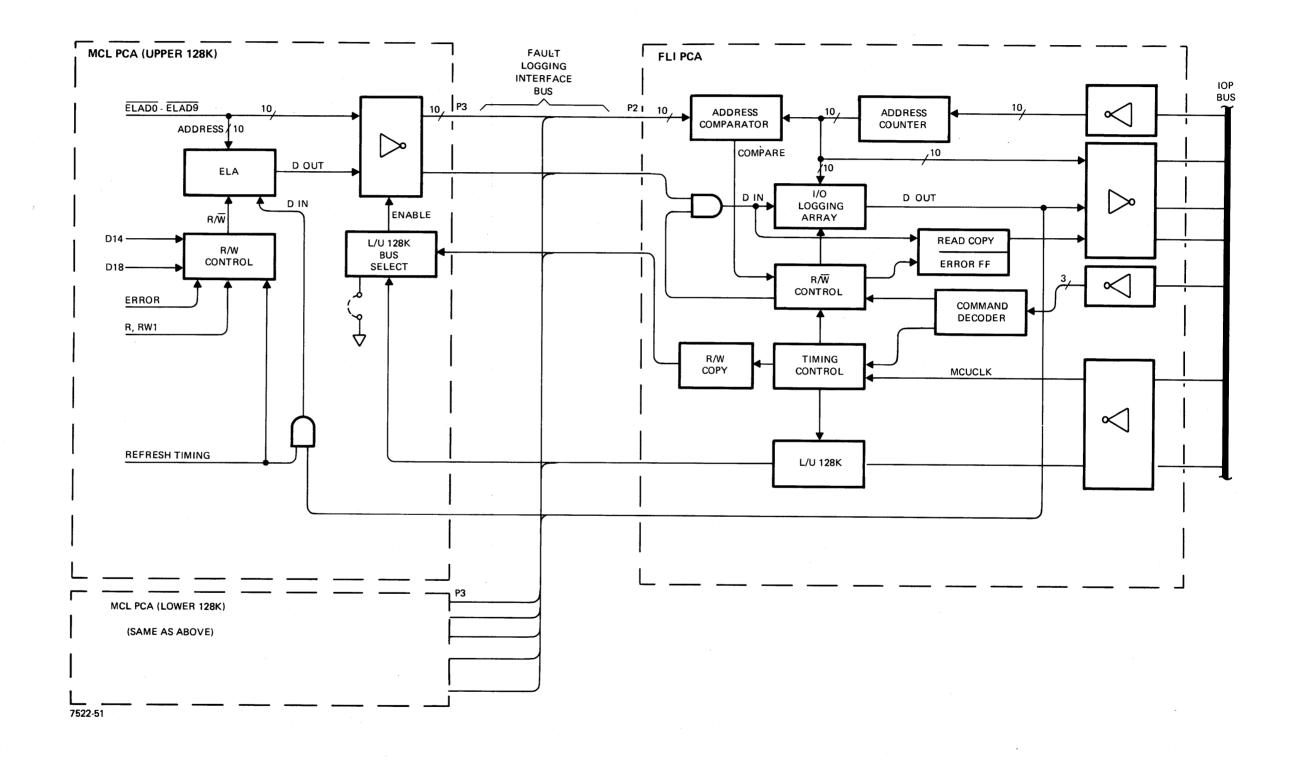

| 4-9.         | CIR PCA Jumper Locations                | 4-18             | 4-39.         | FLI PCA Functional Block Diagram 4-69           |

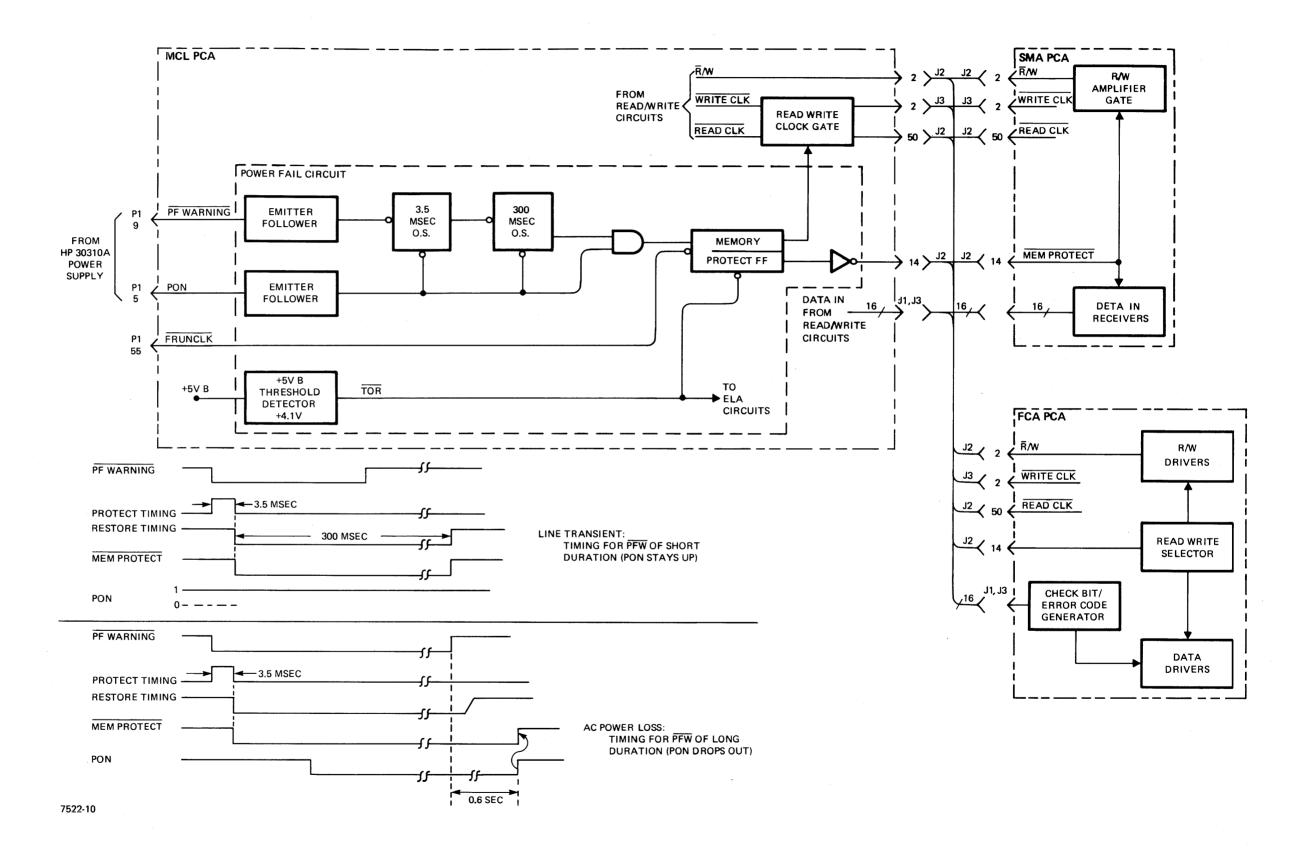

| 4-10.        | MCU PCA Jumper Locations                | 4-19             | 4-40.         | Power Fail Circuit Functional                   |

| 4-11.        | IOP PCA Jumper and Switch Locations     | 4-20             | ,             | Block Diagram 4-73                              |

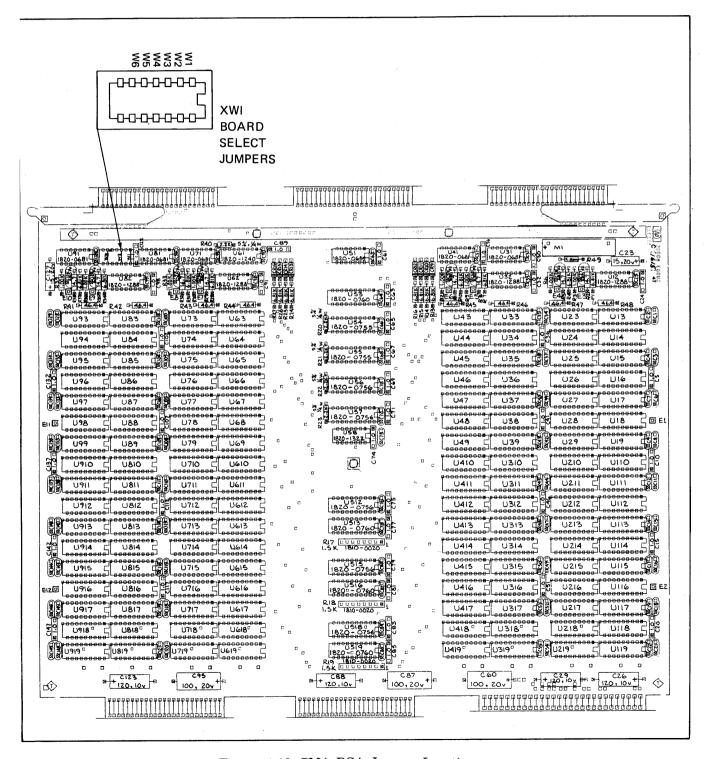

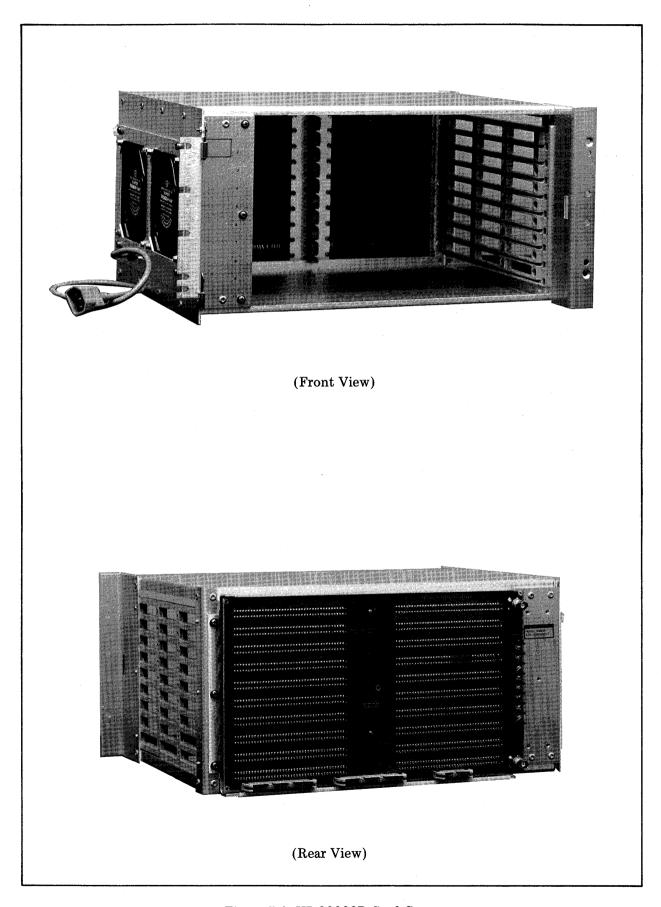

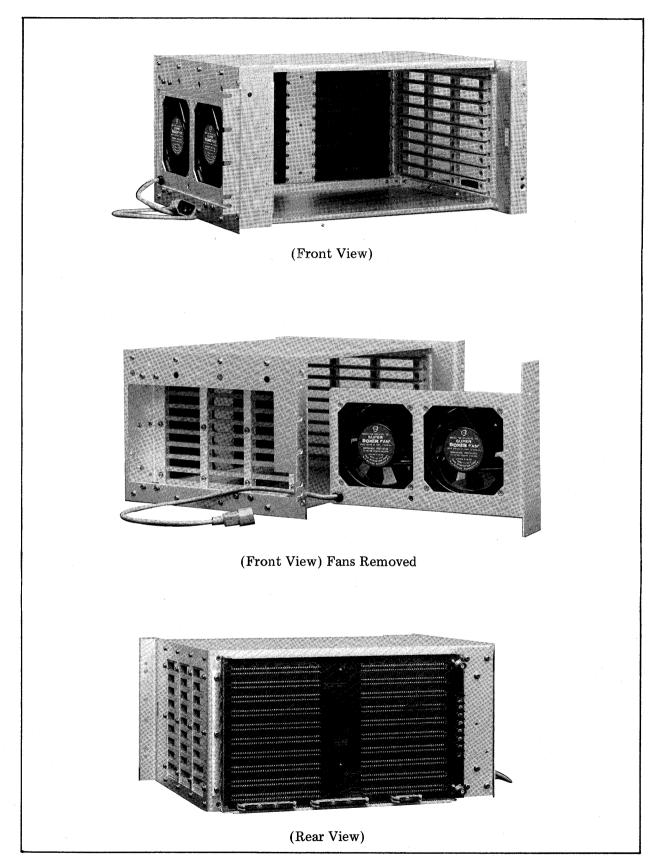

| 4-12.        | SMA PCA Jumper Locations                | 4-21             | 5-1.          | HP 30002B Card Cage                             |

| 4-13.        | MCL PCA Jumper Locations                | 4-23             | 5-2.          | HP 30002C Card Cage                             |

| 4-14.        | FLI PCA Jumper Locations                | 4-24             | B-1.          |                                                 |

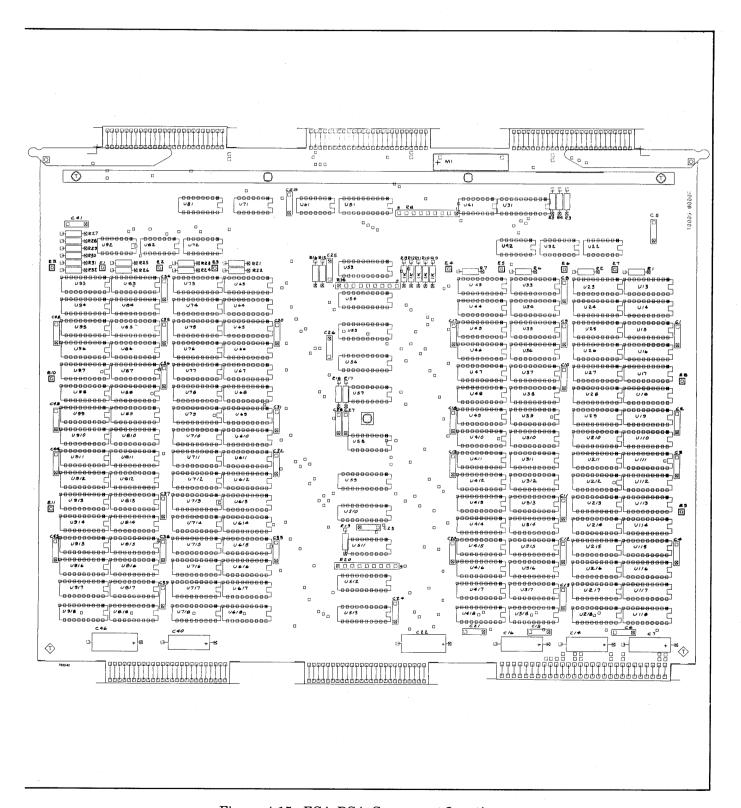

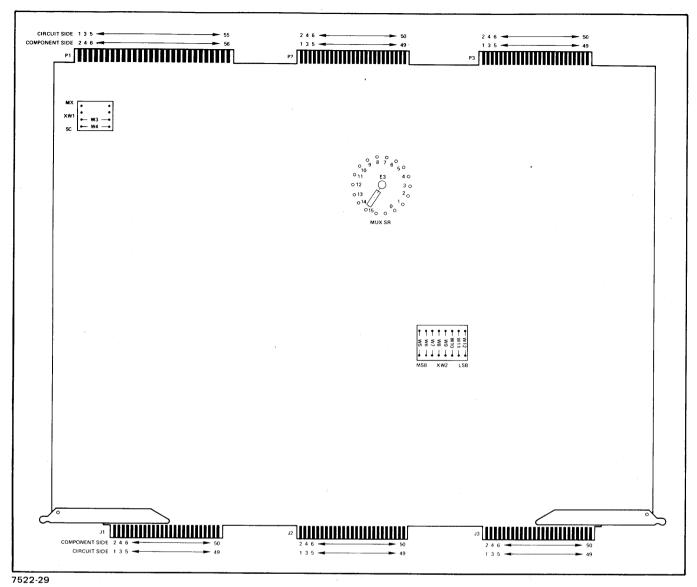

| 4-15.        | FCA PCA Component Location              | 4-25             | Б-1.<br>В-2.  | HP 30310A Power Supply Block Diagram B-5        |

| 4-16.        | System Clock/Console Interface PCA      |                  | D-2.          | HP 30310A Power Supply Functional               |

|              | Jumper and Switch Locations             | 4-26             | B-3.          | Block Diagram                                   |

| 4-17.        | Multiplexer Channel PCA Jumper          |                  | в-э.<br>В-4.  | HP 30310A Functional Timing Diagram B-15        |

|              | Locations                               | 4-28             | D-4.          | HP 30311A Power Supply Simplified               |

| 4-18.        | Selector Channel Register PCA Jumper    |                  | DE            | Block Diagram B-24                              |

|              | and Switch Locations                    | 4-29             | B-5.          | HP 30311A Power Supply Detailed Block           |

| 4-19.        | Selector Channel Control PCA Switch     | <del>1</del> -20 | B-6.          | Diagram                                         |

|              | and Register Locations                  | 4-31             | в-ю.<br>В-7.  | Power Controls and Indicators B-29              |

| 4-20.        | SCMB Jumper Locations                   | 4-33             |               | Control Board Adjustment Locations B-33         |

| 4-21.        | System Control Panel Jumper Locations . | 4-34             | D-0.          | HP 30312A Power Supply Simplified               |

|              |                                         | 07               |               | Block Diagram B-40                              |

X

JAN 1977

SECTION

#### 1-1. INTRODUCTION

This section contains verification procedures that are extracts from stand-alone diagnostics to provide quick, easy to run diagnostics that verify system operation.

#### 1-2. DIAGNOSTIC AND VERIFICATION PROGRAMS

The HP 3000 Series II Computer System uses three types of test programs. They are ON-LINE VERIFICATION PROGRAMS, STAND-ALONE DIAGNOSTICS, and MICRODIAGNOSTICS.

#### 1-3. ON-LINE VERIFICATION PROGRAMS

The on-line verification programs are used to confirm proper operation of peripheral devices (i.e. printer, terminals, readers, punches etc). These programs run concurrently with other programs under control of the Multiprogramming Executive Operating System (MPE) and permit uninterrupted system operation. If the minimum hardware configuration required for MPE is inoperable, on-line verification programs cannot be run. The stand-alone diagnostics must then be used. The verification programs are described in the Manual of On-Line Verification Programs. The verification programs and their manual part numbers are listed in table 1-1. Access to the verification programs is obtained by entering the following:

:HELLO FIELD. SUPPORT, HP 32230

:RUN fname

Table 1-1. On-Line Verification Programs

| PRODUCT NUMBER                                                                     | DIAGNOSTIC<br>NUMBER                         | DESCRIPTION                                                                                                                    | DIAGNOSTIC MANUAL<br>PART NUMBER                                                                                     |

|------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 30106A<br>26XX Series L.P.<br>2640A<br>2762A/B<br>2644A<br>2615A<br>30219<br>7260A | D465<br>D466<br>D469<br>D475<br>D477<br>D478 | Card Reader Line Printer Display Terminal Terminal/Printer Display Terminal CRT Terminal Card Reader Punch Optical Mark Reader | 30106-90008<br>30209-90007<br>30000-90056<br>30120-90007<br>03000-90129<br>30122-90005<br>30119-90007<br>07260-90013 |

NOTE: Refer to paragraph 1-29 for the on-line verification procedure for the HP 30104A Paper Tape Reader and HP 30105A Paper Tape Punch.

The Optical Mark Reader on-line verification program resides in the PUB group of the SYS account.

#### 1-4. STAND-ALONE DIAGNOSTIC PROGRAMS

The stand-alone diagnostic programs allow Customer Engineers to run maintenance and troubleshooting tests on system hardware and peripheral devices. Each of these programs is independentlyoperated and runs directly on the central processor. MPE is not required and the operating system is

DEC 1976 1-1

shut-down while stand-alone programs are running. When a problem occurs that prevents the use of both on-line or stand-alone programs, then the microdiagnostics can be used. The stand-alone diagnostics are described in the Manual of Stand-Alone Diagnostics. The stand-alone programs and their manual part numbers are listed in table 1-2. The CPU diagnostic (D420) is available from the CPU-Cold Load tape, part number 30000-10016 (11016). (-11016 is a 1600 BPI tape.)

The stand-alone diagnostic tapes are created under control of SDUPII (Standalone Diagnostic Utility Program II). Updating stand-alone diagnostics is also accomplished under control of SDUPII. For detailed information on the use and functions of SDUPII, refer to the HP 3000 Series II Computer System Diagnostic Utility Program II Manual, part number 03000-90125.

Table 1-2. Non-CPU Cold Load Diagnostics

| PRODUCT NO.                  | DIAGNOSTIC NO. | DESCRIPTION                                                  | DIAGNOSTIC MANUAL<br>PART NUMBER |

|------------------------------|----------------|--------------------------------------------------------------|----------------------------------|

| SLEUTH                       | D411           | SLEUTH                                                       | 03000-90123                      |

| 7905A                        | D419           | Disc Subsystem (30129A)                                      | 30129-90007                      |

| 30036A                       | D422           | Multiplexer Chan.                                            | 30036-90001                      |

| 288 <b>8</b> A               | D423           | Disc File                                                    | 30102-90015                      |

| 7900A                        | D424           | Cartridge Disc                                               | 30110-90012                      |

| 30031A                       | D425           | System Clock/Console                                         | 30031-90008                      |

| 30032B                       | D427           | Terminal Data Interface                                      | 30032-90011                      |

| 2660A                        | D428           | Fixed Head Disc                                              | 30103-90015                      |

| 30030A                       | D429           | Selector Channel                                             | 30030-90011                      |

| 30007B/<br>30008A/<br>30009A | D430           | Fault Correction Memory                                      | 30008-90001                      |

| 30012A                       | D431           | Extended Instruction Set                                     | 30012-90001                      |

| 30360A                       | D432           | Hardwired Serial Interface                                   | 30360-90007                      |

| 7970B/E                      | D433           | Nine Track (NRZI-PE) Mag Tape                                | 30115-90014                      |

| 30055A                       | D434           | Synchronous Single Line<br>Controller                        | 30055-90008                      |

| 30050A/51                    | D435           | Universal Interface and 30219<br>Card Reader Punch Interface | 30050-90012                      |

| 30061A                       | D438           | Terminal Controller Interface                                | 30061-90003                      |

| 30226A                       | D439           | Plotter Interface                                            | 30226-90009                      |

#### 1-5. MICRODIAGNOSTICS

The microdiagnostics are microprograms that are built into the system. These are microprograms that replace the instruction set microprograms in the central processor and in some controllers. They identify problems by checking the hardware from the most basic level. The operating procedures for the built in microdiagnostics are contained in Appendix A, and also in the HP 3000 Series II Computer System Console Operator's Guide, manual part number 30000-90013. The program list is contained in the Microprogram Listing Manual, part number 30000-90023.

#### 1-6. PURPOSE

System verification procedures are used to verify that the system operates correctly. The procedures may be run after a repair has been made, after a system modification or update has been completed, or as a confidence check if some functional area of the system is suspected of a malfunction. Section II of this manual contains procedures to isolate a fault to a functional area.

A detected malfunction will provide an error message that can be interpreted by referring to the specific diagnostic contained in the manual of stand-alone diagnostics. The diagnostic manuals also provide detailed operating instructions that allow additional testing and analysis to be performed on a suspected subsystem.

#### 1-7. FACILITIES REQUIRED

Table 1-3 lists the diagnostic tapes required to perform the system verification. Table 1-2 lists the contents of the Non-CPU Cold Load diagnostic tape. This table lists the contents of a maximum configured system. Consult the System Configuration Guide shipped with the system to determine the specific subsystems available at a particular installation. Diagnostics on the tape are in the order listed in the table. Table 1-1 lists the contents of the on-line diagnostic tape.

TITLE PART NUMBER

CPU-Cold Load 30000-10016/11016

Non CPU-Cold Load 30000-10017/11017

Table 1-3. Diagnostic Tapes

NOTE: -11016 and -11017 are 1600 bpi tapes.

### 1-8. SYSTEM VERIFICATION PROCEDURES

The system verification procedures contain the instructions required to execute the diagnostic programs. Each program is loaded using the Cold Load procedure. The verification procedures presented in this section were preconfigured using SDUP. If a diagnostic is run that has not been preconfigured, operating instructions and console messages will differ from those presented in this section. In addition to the verification procedures provided in this section, the on-line diagnostics for the peripheral equipment should also be exercised for a total system verification. Refer to the appropriate on-line diagnostic manual for the peripherals in the system.

#### 1-9. SLEUTH 3000

SLEUTH 3000 is a stand-alone utility written in SPL/3000. It is designed to give service personnel the capability of generating unique I/O test programs that run under the control of SLEUTH 3000. These programs allow isolation of I/O problems and ease the troubleshooting of these problems. SLEUTH 3000 has the ability to run up to five different types of I/O device concurrently. It can also write and execute SIO programs, store and restore programs on magnetic tape, and edit the programs.

Peripheral devices that do not have on-line and/or stand-alone verification programs require that SLEUTH 3000 programs be written to test these devices. Several such test programs have been written for specific I/O peripherals (for example, the SLEUTH07 program described in paragraph 1-32).

JAN 1977 1-3

SLEUTH 3000 will run on a minimum HP 3000 Series II. Refer to the HP Manual of Diagnostics for complete information on the use of SLEUTH 3000 I/O Diagnostic D411, manual part number 03000-90123.

#### 1-10. SYSTEM CONTROL PANEL

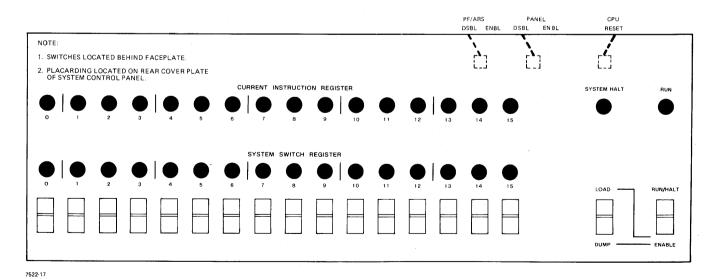

The system control panel located at the top front of equipment bay 1 provides the system operator and service personnel the controls and lamps to perform the following functions:

- cold load and run diagnostics

- load and run user programs

- halt programs

- system dump

- observe the current instruction register

- reset the CPU

- enable or disable the auto restart function after a power failure

All switches located on the front of the control panel are three-position spring-return rocker switches. These switches have a center-off position. They are pressed on the top or bottom half to produce the desired function. When released, they return to the center position.

Located behind the upper right portion of the panel are three switches accessible when the cabinet door is opened:

CPU RESET-A two-position spring-return switch used to reset the circuits of the CPU.

PANEL DISABLE/ENABLE-A two position switch that enables or disables the system panel for use.

PF/ARS DISABLE ENABLE-A two position switch to enable or disable the auto restart program in the event of a power failure.

Table 1-4 lists and explains the function of the switches and lamps that are illustrated in figure 1-1.

#### 1-11. MAINTENANCE PANEL

The HP 30354A Maintenance Panel can be used to perform the functions of System Control Panel. In addition, the maintenance panel can assist in localizing faults, show the contents of selected registers and the state of major signals, and modify the contents of selected registers. The function and use of the panel is described in Section III of this manual.

1-4 JAN 1977

Table 1-4. System Control Panel Switch and Lamp Functions

| PANEL MARKING                               | FUNCTION                                                                                                                                                                                              |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CURRENT INSTRUCTION REGISTER (lamps)        | Displays the content of the Current Instruction Register                                                                                                                                              |

| SYSTEM SWITCH REGISTER (lamps and switches) | Displays the contents of the switch register as determined by pressing the switches on or off. Switches provide a 16-bit word to be used as a device number and control byte for cold load procedure. |

| RUN<br>(lamp)                               | Indicates the system is executing a program                                                                                                                                                           |

| SYSTEM HALT (lamp)                          | Indicates a system halt caused by an irrecoverable error detected by the firmware.                                                                                                                    |

| RUN/HALT<br>(switch)                        | Reverses the run/halt condition of the system.                                                                                                                                                        |

| ENABLE (switch)                             | Must be held in the ENABLE position to permit the LOAD or DUMP switch function to become active.                                                                                                      |

| DUMP<br>(switch)                            | Sends the contents of memory and CPU registers to a device specified by internal DRT jumpers.                                                                                                         |

| LOAD<br>(switch)                            | Used to load memory from a device specified by the SYSTEM SWITCH REGISTER contents.                                                                                                                   |

Figure 1-1. System Control Panel

#### 1-12. COLD LOAD (DIAGNOSTIC)

Perform the following steps to cold load a diagnostic tape.

#### NOTE

When the SYSTEM SWITCH REGISTER bit 8 is set to 0, all memory is initialized with a HALT %10 instruction (%030370) prior to executing the cold load. If bit 8 is set to 1, no initialization occurs prior to the cold load.

- a. Load tape on tape unit 0.

- b. Enter %003006 on SYSTEM SWITCH REGISTER. Simultaneously press LOAD and ENABLE switches.

- c. Select the appropriate diagnostic file number from the tape and enter this octal number in the SYSTEM SWITCH REGISTER.

- d. Press RUN. The diagnostic loads and the tape rewinds at the end of the load.

- e. Set SYSTEM SWITCH REGISTER to 000000.

#### NOTE

The following verification procedures can only be used with tapes shipped with the system and listed in Table 1-2. Unless directed otherwise, all operator entries are made using the system console.

#### NOTE

Prior to performing any maintenance or shutdown procedures, have the System Operator verify that all jobs/sessions have been terminated before proceeding.

#### NOTE

Do not power-up or power-down any peripheral device when a diagnostic is running. Failure to observe this note could adversely effect the diagnostic that is executing.

#### 1-13. HP 30129 CARTRIDGE DISC DIAGNOSTIC (D419)

The diagnostic verifies the input, output, and control functions of the HP 30129A Cartridge Disc subsystem. The following procedure is used to verify operation.

#### NOTE

A SYSDUMP should be performed prior to executing the diagnostic. A RELOAD must be performed after completing the diagnostic.

| OPERATOR ACTION/COMMENTS                                                  | CONSOLE MESSAGES                                                        |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Cold load diagnostic D419 from stand-alone diagnostic tape.  Press RETURN |                                                                         |

| Press REIURN                                                              | D99 01 CARTRIDGE DISC (HP 30129A) DIAGNOSTIC                            |

|                                                                           | CONFIGURATION (D419X.YY.Z)                                              |

|                                                                           | Q99 02 DECIMAL DEVICE NUMBER?                                           |

| X = Version                                                               |                                                                         |

| YY = Update level $Z = Fix level$                                         |                                                                         |

| Enter the decimal device number of the disc controller.                   |                                                                         |

| Press RETURN                                                              |                                                                         |

|                                                                           | Q99 03 MAXIMUM ERROR PRINT COUNT                                        |

| Enter in decimal the maximum number of error messages                     |                                                                         |

| you wish to receive (4-6). Press RETURN                                   | ·                                                                       |

| 11055 1001 01014                                                          | P99 55 UPDATE SWITCH REGISTER                                           |

| Set SYSTEM SWITCH REGISTER bit 0 off.                                     |                                                                         |

| Press RETURN                                                              | DOO OF DESEM DOWN DOWN DAMA SWITCHES SET                                |

|                                                                           | P99 05 RESET BOTH PROT. DATA SWITCHES, SET SWITCH FORMAT AND UNIT TO 0. |

| On the disc unit, set the LOWER and UPPER DISC PRO-                       | SWITCH FORMIT MAD CAME TO 0.                                            |

| TECT switches down. Set the FORMAT switch to the right                    |                                                                         |

| position. Set UNIT SELECT switch to position 0.                           |                                                                         |

| Press RETURN                                                              | Q99 42 WISH TO EXECUTE INTERACTIVE PORTION                              |

|                                                                           | IN SECTION 1 (YES/NO)                                                   |

| Enter NO                                                                  | 21 (200 1201 2 (2000 210)                                               |

| Press RETURN                                                              |                                                                         |

|                                                                           | D99 07 CARTRIDGE DISC (HP 30129A) DIAGNOSTIC                            |

| Program runs approximately one hour.                                      | OFF-LINE (D419X.YY.Z)                                                   |

| riogram rums approximatery one nour.                                      |                                                                         |

## 1-14. HP 30008A/30009A FAULT CORRECTION MEMORY DIAGNOSTIC (D430)

The fault correction memory diagnostic performs the following functions:

- Verifies the Fault Logging Interface (FLI) PCA array and reads the previous history of both arrays (when present) and lists all errors.

- Clears and verifies both Memory Control and Logging (MCL) PCA arrays.

- Verifies all Semiconductor Memory Array (SMA) PCA arrays and lists any errors.

- Checks the capability to detect and correct single bit errors in both data and check bits, detects most multi-bit errors, and detects I/O failures in the Fault Correction Array (FCA) PCA.

- Executes the main diagnostic program for all SMA PCA's.

- Reads and lists the error history of both MCL logging arrays.

The following procedure is used to verify operation:

| OPERATOR ACTION/COMMENTS                                                                                 |                                                                                                                                                        |                               | CONSOLE MESSAGES                                                                                             |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------|

| Cold load diagnostic D430 from stand-alone diagnostic tape.                                              |                                                                                                                                                        |                               |                                                                                                              |

| Set SYSTEM SWITCH REGISTER bit 0 off. Press RETURN.                                                      |                                                                                                                                                        |                               | HP 3000 SERIES II FAULT CORRECTING MEMORY<br>TEST D430X.YY.ZZ<br>(C) COPYRIGHT HEWLETT-PACKARD COMPANY 1976. |

| X = Version<br>YY = Update level<br>ZZ = Fix level                                                       |                                                                                                                                                        |                               |                                                                                                              |

| N                                                                                                        | OTE                                                                                                                                                    |                               |                                                                                                              |

| The following message and 3 are not present                                                              | e only appears<br>in the system                                                                                                                        | if banks 2                    |                                                                                                              |

|                                                                                                          |                                                                                                                                                        |                               | E0.02 UPPER MCL, NOT RESPONDING                                                                              |

|                                                                                                          | Enter in decimal the lowest memory bank number (0).                                                                                                    |                               | LOW BANK ?                                                                                                   |

|                                                                                                          | Press RETURN.  Enter in decimal the low memory address (1). (Do Not enter                                                                              |                               | LOW ADDRESS?                                                                                                 |

| 0).<br>Press RETURN.                                                                                     | 0).                                                                                                                                                    |                               | HIGH BANK ?                                                                                                  |

| Enter in decimal the highes<br>system (0,1,2, or 3).<br>Press RETURN                                     | st memory ban                                                                                                                                          | k number in the               |                                                                                                              |

|                                                                                                          | Enter in octal the highest memory address that is addressable from the memory bank specified in the previous entry.                                    |                               | HIGH ADDRESS ?                                                                                               |

| Memory Word Size                                                                                         | Bank                                                                                                                                                   | Address                       |                                                                                                              |

| 64K<br>96K<br>128K                                                                                       | 0<br>1<br>1                                                                                                                                            | %177777<br>%077777<br>%177777 | ·                                                                                                            |

| 160K                                                                                                     | 2                                                                                                                                                      | %077777                       |                                                                                                              |

| 192K<br>224K                                                                                             | $rac{2}{3}$                                                                                                                                           | %177777<br>%077777            |                                                                                                              |

| 256K                                                                                                     | 3                                                                                                                                                      | %177777                       |                                                                                                              |

| Press RETURN                                                                                             |                                                                                                                                                        |                               |                                                                                                              |

|                                                                                                          | Program executes and takes approximately 62 minutes to fully test each bank. (All banks specified above are tested during one pass of the diagnostic.) |                               |                                                                                                              |

|                                                                                                          |                                                                                                                                                        |                               | D1.04 END OF SECTION 1<br>D2.10 END OF SECTION 2<br>D3.17 END OF SECTION 3                                   |

|                                                                                                          |                                                                                                                                                        |                               | D4.25 END OF SECTION 4<br>P5.50 END OF STEP 50                                                               |

|                                                                                                          |                                                                                                                                                        |                               | P5.51 END OF STEP 51 P5.52 END OF STEP 52 P5.54 END OF STEP 54                                               |

| NOTE                                                                                                     |                                                                                                                                                        |                               | LOTOR FIND OL SIEL 94                                                                                        |

| Messages P5.55 through P5.65 will appear when addresses in the range of 10K to 40K in bank 0 are tested. |                                                                                                                                                        |                               | •                                                                                                            |

|                                                                                                          |                                                                                                                                                        |                               |                                                                                                              |

| OPERATOR ACTION/COMMENTS                                                                                                                                        | CONSOLE MESSAGE                                                                                                                                                                                                            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NOTE  The following message appears if the upper 128K MCL PCA is not present in the system.  Program restarts and continues to run until operator presses HALT. | P5.55 END OF STEP 55 P5.60 END OF STEP 60 P5.61 END OF STEP 61 P5.62 END OF STEP 62 P5.64 END OF STEP 64 P5.65 END OF STEP 65 D5.25 END OF SECTION 5  E6.66 UPPER MCL, NOT RESPONDING D6.66 END OF SECTION 6 D6.66 01 PASS |  |

#### 1-15. HP 30036A MULTIPLEXER CHANNEL DIAGNOSTIC (D422)

The multiplexer channel diagnostic verifies the functional operation of the Multiplexer PCA by testing order RAM, order register, address RAM, address register, state RAM, state register, and related SIO. Two Selector Channel Maintenance PCA's (SCMB) should be installed with the correct device numbers before executing the diagnostic. Refer to Section IV of this manual for installation information. The diagnostic may be run with none, or one SCMB installed, console messages will be different. The following procedure is used to verify operation.

| OPERATOR ACTION/COMMENTS                                                                                                                                                                                                                                                                                   | CONSOLE MESSAGES                                               |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Cold load diagnostic D422 from stand-alone diagnostic tape.<br>Press RETURN                                                                                                                                                                                                                                | D01 30036A MPX CHANNEL TEST (HP D422X.YY.Z) Q01 SELECT OPTIONS |  |

| <ul> <li>X = Version</li> <li>YY = Update level</li> <li>Z = Fix level</li> <li>Set SYSTEM SWITCH REGISTER bit 0 off.</li> </ul>                                                                                                                                                                           |                                                                |  |

| NOTE                                                                                                                                                                                                                                                                                                       |                                                                |  |

| The SYSTEM SWITCH REGISTER may be set to %101000 (bits 0 and 6 set) when only one SCMB is installed in the multiplexer channel. This switch register setting will cause steps 75-78 of the diagnostic to be skipped. These steps are used only when a second SCMB is installed in the multiplexer channel. |                                                                |  |

| OPERATOR ACTION/COMMENTS                                                                                       | CONSOLE MESSAGE                                                      |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| Press RUN (Time for one pass is approximately two minutes.)                                                    |                                                                      |  |

|                                                                                                                | P02 END SECTION IORES                                                |  |

|                                                                                                                | P02 END SECTION ARADDR                                               |  |

|                                                                                                                | P02 END SECTION ARDATA                                               |  |

|                                                                                                                | P02 END SECTION ARCPP                                                |  |

|                                                                                                                | P02 END SECTION ORADDR                                               |  |

|                                                                                                                | P02 END SECTION ORDATA                                               |  |

|                                                                                                                | P02 END SECTION ORCP                                                 |  |

|                                                                                                                | P02 END SECTION AREG                                                 |  |

|                                                                                                                | P02 END SECTION OREG                                                 |  |

|                                                                                                                | P02 END SECTION NSGP1                                                |  |

|                                                                                                                | P02 END SECTION NSGP2                                                |  |

|                                                                                                                | P02 END SECTION NSGP3                                                |  |

|                                                                                                                | P02 END SECTION NSGP4                                                |  |

|                                                                                                                | P02 END SECTION STPAR                                                |  |

| NOTE                                                                                                           |                                                                      |  |

| The following console message appears if no SCMB's are installed in the multiplexer channel.                   |                                                                      |  |

| chamiei.                                                                                                       | P18 1ST SCMB DRT# NOT ENTERED; STEPS 41-74                           |  |

|                                                                                                                | ABORTED                                                              |  |

|                                                                                                                | P19 2ND SCMB DRT# NOT ENTERED; STEPS 75-78                           |  |

|                                                                                                                | ABORTED                                                              |  |

| With one SCMB installed, message P18 is not displayed.<br>With both SCMB's installed, messages P18 and P19 are |                                                                      |  |

| supressed, and the following messages appear.                                                                  |                                                                      |  |

|                                                                                                                | P16 FAST SR READ MODE (2K XFER); TIME = 4 MSEC.;<br>BANK 00; STEP 63 |  |

|                                                                                                                | P16 FAST SR READ MODE (2K XFER); TIME = 4 MSEC.;<br>BANK 01; STEP 63 |  |

|                                                                                                                | P17 FAST SR WRITE MODE (2K XFER); TIME = 4                           |  |

|                                                                                                                | MSEC.; BANK 00; STEP 68                                              |  |

|                                                                                                                | P17 FAST SR WRITE MODE (2K XFER); TIME = 4                           |  |

|                                                                                                                | MSEC.; BANK 01; STEP 68                                              |  |

|                                                                                                                | PO2 END SECTION SIOTST                                               |  |

|                                                                                                                | DO2 END MPX CHAN TEST                                                |  |

|                                                                                                                | D03 END: PROGRAM CYCLE: PASS=1                                       |  |

| Program restarts and continues to run until operator presses                                                   |                                                                      |  |

| HALT switch.                                                                                                   |                                                                      |  |

#### 1-16. HP 30102A DISC FILE DIAGNOSTIC (D423)

The diagnostic verifies the input, output, and control functions of the HP 30102A Disc File. The following procedure is used to verify operation.

#### NOTE

Prior to running this diagnostic a SYS DUMP should be performed to save information stored on the disc pack. When answering the dialogue for the SYS DUMP, enter 0 for the date so that all the data is saved.

| OPERATOR ACTION/COMMENTS                                                                                                                                                                                                | CONSOLE MESSAGES                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Cold load diagnostic D423 from stand-alone diagnostic tape.  Press RETURN  X = Version YY = Update level Z = Fix level Enter in decimal the DRT number of the disc controller. Press RETURN                             | D99 01 DISC FILE (30102A) DIAG CONFG (D423X.YY.Z) Q99 02 DECIMAL DEVICE NUMBER |

| Enter ON Press RETURN                                                                                                                                                                                                   | Q99 03 INTERRUPTS ON OR OFF? P99 61 PAUSE AFTER CONFIGURATION                  |

| (The message means the hardware has paused (%030040 in CIR) and is waiting for an update of the switch register.) Set SYSTEM SWITCH REGISTER bit 0 off. Press RETURN Program runs approximately one hour to completion. |                                                                                |

#### 1-17. HP 30110A CARTRIDGE DISC DIAGNOSTIC (D424)

The diagnostic verifies the input, output, and control functions of the HP 30110A Cartridge Disc. The following procedure is used to verify operation.

| OPERATOR ACTION/COMMENTS                                                                                                                                                                                        | CONSOLE MESSAGES                                                                           |