### \* \* \* DRAFT \* \* \*

## A-link CIO Adapter

Preliminary External Reference Specification

**Roseville Networks Division**

Location Code: 52-5528

Project Number: 27111A

February 11, 1987

This Revision: Feb 12, 1987

Tom Keaveny 1-786-5620

### \* HP Confidential \*

The HP27111A Alink CIO Adapter External Reference Specification document is still in a preliminary version, and, to some extent, incomplete.

The intent of the document is to provide a source of information for internal HP customers to aid them in understanding the HP27111A for their particular application, whether it be product marketing support or diagnostic integration.

All information in this document is SUBJECT TO CHANGE. Any changes in the HP27111A's external specifications will be noted for those who are on the document distribution list. The update will appear as either errata or a revised ERS depending upon the nature and extent of the modifications.

At release, the following information should still be considered to be VERY PRELIMINARY and are currently under review:

Section 4: Electrical Specifications Section 6: Field Diagnostics Section 7: Theory of Operation

Comments and questions should be directed to:

Tom Keaveny Roseville Networks Division 8000 Foothills Blvd. Roseville,CA 95678 Mailstop: R3NF

1-786-5620

# **PREFACE** (continued)

1

### **CURRENT DISTRIBUTION**

Distribution of the current version of the HP27111A ERS/IMS is to those listed below under the "distribution" heading. Those under the "notification" heading will receive an HPDESK message indicating that the document is available.

Further copies of this document may be made available by contacting:

Tom Keaveny Roseville Networks Division 8000 Foothills Blvd. Roseville,CA 95678 Mailstop: R3NF HPDESK: HP5200/02

### Distribution:

| ABE, STEVE                      |

|---------------------------------|

| ALEXANDER, TOM                  |

| BOULDIN, DANNY                  |

| BROMLEY, DAVE                   |

| BROWN, HAL                      |

| BROWN, JERRY                    |

| BUCKTHAL, ROGER                 |

| BURGER, STEPHEN                 |

| CANTU,IGNACIO                   |

| CHANG, PAUL                     |

| CHEUNG, NANCY                   |

| CONRY, KEVIN                    |

| CRAIG, BARBARA                  |

| DUNN, PAUL                      |

| ESPLIN, GREG                    |

| GREEN, JUDY                     |

| HOLLAND, ED                     |

| HUGINS, CHRIS                   |

| JAHR, STEVE                     |

| JENKINS, LYNN                   |

| LECHTENBERG, DAVE               |

| MATTHEWS, RANDY                 |

| MEANS, DAVID                    |

| MEIER, (hpfcll)                 |

| MILLER, DAVID                   |

| NAKAMURA, TOM                   |

| NELSON, MARVIN                  |

| NISHIME, KAZ                    |

| OUYE, DARRYL                    |

| PEPIN, ROGER                    |

| SANDERS, JIM                    |

| SCHREMPP, MIKE                  |

| SILL, GALE                      |

| SKOKAN, STAN                    |

| SONTAG, JOHN                    |

| SORENSON, HANS<br>SPOHN, NORRAE |

| •                               |

| TANI, JON                       |

| HP5200/04 |

|-----------|

| HP4700/UX |

| HP0100/20 |

| HP1900/01 |

| HPG200/11 |

| HP5200/07 |

| HP4800/03 |

| HPG200/13 |

| HP5200/04 |

| HPG200/13 |

| HP5200/07 |

| HPG200/05 |

| HPG200/XX |

| HP1900/UX |

| HP4800/03 |

| HP5200/07 |

| HPG200/14 |

| HPG200/13 |

| HPG200/05 |

| HP5200/04 |

| HP4000/UX |

| HP4800/03 |

| HP4700/UX |

| HP4000/UX |

| HPG200/08 |

| HP5200/07 |

| HP4800/03 |

| HPG200/13 |

| HPG200/13 |

| HPG200/04 |

| HP4800/10 |

| HPG200/14 |

| HP5200/07 |

| HP1900/01 |

| HP4700/UX |

| HP0100/20 |

| HP4800/03 |

| HP1900/UX |

14

JAN 86 viii

### VOGELSBERG, GARY

#### HP4800/MK

#### Notification:

BORG,MIKE BRUBAKER, RAY CAMPBELL, DUNCAN CHATTERTON, CRAIG CHIOCHIOS, JIM CONNER, DON CORCORAN, JOHN GOULD, RON GUBITZ, GARY HARRIS, DAVE HO, GARY HODAPP, MARK HUNT, CRAIG KENYON, DAVE KIZZIER, CHRIS KONDOFF,AL KUNTZ, DAVID LIU, MARTIN LUTGARDO, ALBERTO MCANALLY, GARY MCCONNELL, KAY MORRIS, HOWARD PEARSON, RICH SCHOMMER, NICK SNOW, DAVE STEADMAN, HOWARD SWISLEY, RANDI WALKER, NATE WILKES, JOHN WU, FRANCIS

HPG200/04 HP5200/02 HP5200/07 HPG200/14 HPG200/13 HP5200/07 HP1900/01 HP0080/01 HP5200/07 HP5200/07 HP4700/UX HP4000/UX HP2414/04 HP5200/07 HPG200/11 HPG200/08 HP5200/07 HP4700/UX HPG200/08 HP5200/02 HP5200/04 HPG200/08 HPG200/13 HP0100/06 HPG200/13 HP4700/L3 HP5200/07 HP0100/06 HP1900/UX HP0100/06

### FUTURE RELEASE DISTRUBUTION

Details on revised ERS/IMS releases will be made through HPDESK, to both those on the "distribution" or "notification" (CC) lists.

To inquire about or receive an ERS/IMS simply reply to the HPDESK message detailing the release as a form of acknowledgement.

JAN 86 viii

:

The A-link is a high speed serial fiber optic data link which may be used by the host in conjunction with high speed disks or disk clusters as well as for host to host data transfers. Target "absolute" speed of the link itself is initially 80 megabits, with intended growth path to 120 megabits. In terms of byte transfers, and accounting for link efficiency, the previous figures translate to transfer rates of 5.0 Mbytes and 7.5 Mbytes, respectively.

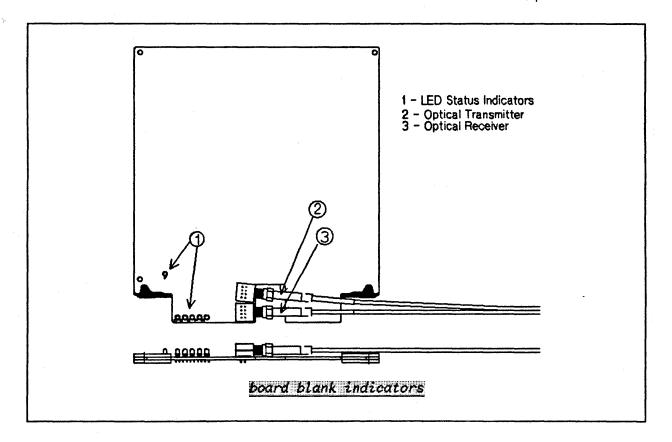

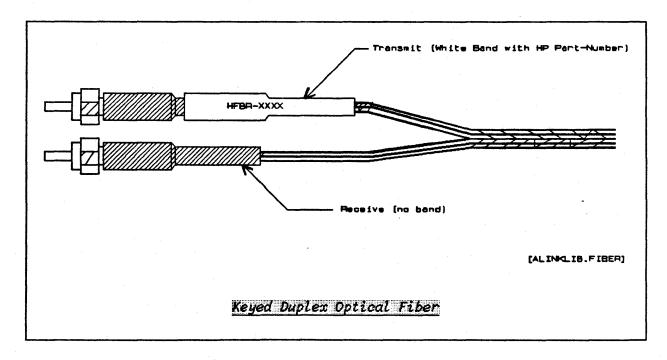

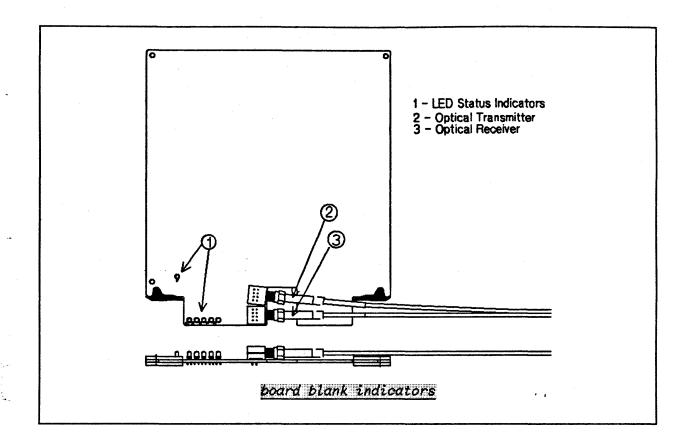

Physically, the card consists of two interfaces: backplane and frontplane. The A-link card will support existing CIO backplanes, and will also have the facilities to support an enhanced CIO backplane which implements additional error and fault detection functions. The frontplane has both an optical transmitter and receiver, providing a full duplex communication link to the external device. This remote device may be located as far as 1 km from the host in standard operation.

Functionally, the card is capable of processing up to 64 current outstanding requests from the host. The card is also capable of responding to request from the remote device. In general, the A-link card may also serve as either a master or a slave to the remote node, depending upon the configuration and the application.

Actual data transmission from card to remote node is controlled by hierarchical levels of protocol, much of which is implemented in hardware to achieve high performance. From the channel or backplane the card responds to the Channel I/O protocol implementation of CS-80 (essentially levels 4-0) and reformats the data according to A-link protocol (levels 3-0).

The card is equipped with a full set of diagnostic/self test code and associated circuitry.

### SECTIONAL OVERVIEW

The topics covered in the following sections are as follows:

| INTRODUCTION (this section!) | Brief description of card and it function followed by one or two<br>statements highlighting what will be covered in each major<br>section of the document |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE                    | A listing of helpful documents in better understanding the A-link<br>adapter along with a list of conventions and a glossary of<br>commonly used terms    |

| SPECIFICATIONS               | A list of electrical, physical and functional specifications as seen<br>by the backplane (CIO) and front plane (A-link) users.                            |

| FUNCTIONAL OVERVIEW          | A functional block diagram description of the CIO Adapter is<br>given followed by an example of how each block operates during a<br>disc read.            |

| FIRMWARE DESCRIPTION         | A description of firmware as seen by the host system and the                                                                                              |

Introduction

remote device. Supported requests and programming modes are identified.

### USER INTEGRATION

A description of how the A-link CIO Adapter is integrated into a host system and how it is intended to be maintained

THEORY of OPERATION

A description of the internal circuital behaviour of the A-link CIO adapter.

### CHANGES and UPDATES

This document now serves as both an ERS and an Internal Maintenance Specification (IMS). With this change, some of the technical information deleted in the last release has been added again.

Three more releases are planned for this document.

(1) Production Prototype ERS/IMS - (2) Manufacturing Release (MR1 rev) ERS/IMS:- (3) Manufacturing Release (MR2 rev) ERS/IMS - *if necessary*

If there is any information not present in this document that is required by any of those on the distribution list, now is the time to make your requests!

Updates and Changes for this release:

NEW Theory of Operation Specifications (section 7)

NEW Appendix Material

(appendices)

REVISED

(sections 1,2,4,5,6)

\* Preliminary Version \* 1-2

### REQUIRED DOCUMENTS

The following documents are required to exist on the document account or must be accessible in order for the ERS to be printed:

ALBOX000. TAK. ALINK ALBOX001. TAK. ALINK ALBOX002. TAK. ALINK ALBOX003. TAK. ALINK ALBOX004. TAK. ALINK ALBOX005. TAK. ALINK ALBOX006. TAK. ALINK ALBOX007. TAK. ALINK ALBOX008. TAK. ALINK ALBOX009. TAK. ALINK ALBOX010. TAK. ALINK ALBOX011. TAK. ALINK ALBOX012. TAK. ALINK ALBOX013. TAK. ALINK ALBOX014. TAK. ALINK ALBOX015. TAK. ALINK ALBOX016. TAK. ALINK ALBOX017. TAK. ALINK ALBOX018. TAK. ALINK ALBOX019. TAK. ALINK ALBOX020. TAK. ALINK ALBOX021.TAK.ALINK ALBOX022. TAK. ALINK ALBOX023. TAK. ALINK ALBOX024. TAK. ALINK ALBOX025. TAK. ALINK ALBOX026. TAK. ALINK ALBOX027. TAK. ALINK ALBOX028. TAK. ALINK ALBOX029. TAK. ALINK ALBOX030. TAK. ALINK ALBOX101 ALBOX201 ALBOX202 ALBOX302 ALBOX401 ALBOX402 ALBOX403 ALBOX404 ALBOX405 ALBOX406 ALBOX407 ALBOX408 ALBOX409 ALBOX410 ALBOX411

ALBOX412 ALBOX501 ALBOX502 ALBOX503 ALBOX504 ALBOX601 ALBOX602 ALBOX603 ALCIOCOD ALCIOPIN. TAK. ALINK ALEQDEV. TAK. ALINK ALFIG999 ALFIGURE. TAK. ALINK ALI186BW.TAK.ALINK ALI186CS. TAK. ALINK "" ALI186CT. TAK. ALINK ALI186GC. TAK. ALINK ALI186GS. TAK. ALINK ALI186IN. TAK. ALINK ALI186PO. TAK. ALINK ALIAD2LD ALIARBSG ALIARRST ALIAUTO. TAK. ALINK ALIBARST ALIBOOL ALIBYT86. TAK. ALINK ALIBYTSW. TAK. ALINK **ALICIOPA** ALICIORG. TAK. ALINK ALICIOSG ALIDCDC ALIDCLBK. TAK. ALINK ALIDCLS2. TAK. ALINK ALIDCLST ALIERCOD. TAK. ALINK ALIFORST ALIGRDTB. TAK. ALINK ALIGWRTB. TAK. ALINK ALIHYST ALILEDMP. TAK. ALINK ALIMCHOP. TAK. ALINK ALIMSAPP. TAK. ALINK **ALIMSAR0 ALIMSBA0 ALIMSFO0**

| ALIMSMIO                                     | ALIR020              |

|----------------------------------------------|----------------------|

| ALIMSPC0                                     | ALIR022              |

| ALIMSPRO                                     | ALIR023              |

| ALIMSRG2. TAK. ALINK                         | ALIR024              |

| ALINCLUD. TAK. ALINK                         | ALIR025              |

| ALINK001.TAK.ALINK                           | ALIR026              |

| ALINK002. TAK. ALINK                         | ALIR027              |

| ALINK003. TAK. ALINK                         | ALIR028              |

| ALINK004. TAK. ALINK                         | ALIR029              |

| ALINK005. DOC. ALINK                         | ALIR030              |

| ALINK006.TAK.ALINK                           | ALIR031              |

| ALINK007. TAK. ALINK                         | ALIR032              |

| ALINKACC. TAK. ALINK                         | ALIR033              |

| ALINKDI2. TAK. ALINK                         | ALIR034              |

| ALINKFIG                                     | ALIR035              |

| ALINKFLC. TAK. ALINK                         | ALIRAMCT             |

| ALINKIMP. TAK. ALINK                         | ALIRXCHR             |

| ALINKMAT. TAK. ALINK                         | ALITXCHR             |

| ALINKMAT. TAK. ALINK<br>ALINKPRE. TAK. ALINK | APPENDX1.IN.MANU     |

|                                              | ARBLP4S1.TAK.ALINK   |

| ALINKREQ. TAK. ALINK<br>ALINKSTC. TAK. ALINK |                      |

|                                              | ARBLP4X2             |

| ALINKSTI                                     | ARBNXT04             |

| ALINKSTI. TAK. ALINK                         | AXTCLKEN             |

| ALIPAUT2                                     | AXTDMARD             |

| ALIPAUTO TAK ALINK                           | AXTDMAWR             |

| ALIPBFHD. TAK. ALINK                         | AXTGRD               |

| ALIPCBLK. TAK. ALINK                         | AXTGWR               |

| ALIPCRST                                     | AXTLATCH             |

| ALIPINIT. TAK. ALINK                         | AXTLINK              |

| ALIPP1PR                                     | AXTPCNTL             |

| ALIPRREG. TAK. ALINK                         | AXTPRORD             |

| ALIPRRST                                     | AXTRAMRD             |

| ALIPSTAT                                     | AXTRAMWR             |

| ALIPWRSH TAK. ALINK                          | AXTRLR               |

| ALIR000                                      | AXTROM               |

| ALIR001                                      | BITS TAK. ALINK      |

| ALIR002                                      | BLOCFIGS             |

| ALIR003                                      | BULLETS. IN. MANU    |

| ALIR004                                      | BYTES. TAK. ALINK    |

| ALIR005                                      | CALAYOUT             |

| ALIR006                                      | CDSTAT. DOC. ALINK   |

| ALIR007                                      | CHANHINT. TAK. ALINK |

| ALIR008                                      | CHANOP. TAK. ALINK   |

| ALIR 009                                     | CIOLBK. DOC          |

| ALIR010                                      | COVER 1. IN. MANU    |

| ALIR011                                      | DEVIDY. DOC. ALINK   |

| ALIR012                                      | DEVLBK. DOC          |

| ALIR013                                      | END2COL              |

| ALIR013                                      | END2COL. TABLE. MANU |

| ALIR015                                      | END3COL. TABLE. MANU |

| ALIR016                                      | END4COL. TABLE. MANU |

| ALIR017                                      | ENDSCOL. MANU. ALINK |

| ALIR018                                      | ENDSCOL. TAK. ALINK  |

| ALIR018<br>ALIR019                           | ENDBULL.IN. MANU     |

| ALINU17                                      | EINDULL. IN. WAINU   |

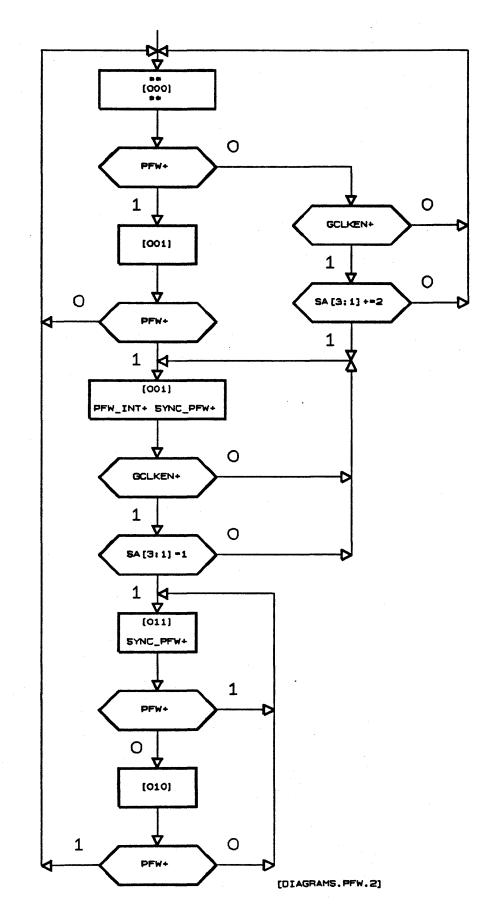

ENDLCOV.IN.MANU ENDNOTE.IN.MANU ENDPREF. IN. MANU **ENDVER1. TABLE. MANU ENDVER 2. TABLE. MANU ENDVER 3. TABLE. MANU ENDVER4. TABLE. MANU** ENDVER40. TAK. ALINK **ENDVER 5. TABLE. MANU ENDVER6. TABLE. MANU ENDVER7. TABLE. MANU ENDVER 8. TABLE, MANU ENDVER9. TABLE. MANU** EXTLBK.DOC FIBERKEY. TAK. ALINK FLOWFIG1 **FLOWFIGS** FORMAT. IN. MANU IDYBLK. DOC. ALINK IMAGE.IN.MANU INTLBK. DOC LABCOV. IN. MANU LEVEL1.IN MANU LEVEL1X.IN. MANU LEVEL2. IN. MANU LEVEL 3. IN. MANU LEVEL3X.IN.MANU LEVEL4.IN.MANU M4LESS2.TAK.ALINK MANSTART.IN.MANU MEMPAL7. TAK. ALINK MID2COL. TABLE. MANU MID3COL. TABLE. MANU MID4COL. TABLE. MANU

MID5COL MANU. ALINK MID SCOL. TAK. ALINK NOTE. IN. MANU PASSCTL5 **PFWPAL6. TAK. ALINK** PREFACE. IN. MANU PREFCNTD.IN.MANU **PWRFAIL 5. TAK. ALINK REOBLK. DOC. ALINK RTSAES DOC. ALINK** SANS3COL. TABLE. MANU SANS4COL. TABLE. MANU SANS5CL2. TAK. ALINK SANS5COL. MANU. ALINK SECTION1.IN. MANU TAB2COL. TABLE. MANU TAB3COL. TABLE. MANU TAB4COL. TABLE. MANU TAB5COL. MANU. ALINK TAB5COL. TAK. ALINK TXSTAT. DOC. ALINK **VER 1. TABLE. MANU** VER 2. TABLE. MANU **VER 3. TABLE. MANU** VER 4. TABLE. MANU VER 40. TAK. ALINK VER 5. TABLE. MANU VER 6. TABLE. MANU **VER7. TABLE. MANU VER 8. TABLE. MANU VER 9. TABLE. MANU** WARNING.IN.MANU WTCAEK. DOC. ALINK

### Introduction

The following is a description of the locations of the various illustrations in the document

Only illustrations contained in boxes are noted...

| Tasluda  | Finune Fil |                                       | draw or     | <b>P! P!</b> . | <b>P !</b> |

|----------|------------|---------------------------------------|-------------|----------------|------------|

| Include  | Figure_Fil | le Figure I                           | npdraw file | Figure_File    | Figure     |

| a1box000 | alfig999 t | ward blank ind                        | alfig101    |                |            |

| albox001 | alfig999 e |                                       | alfig300    |                |            |

| albox002 |            | mi_jumper_block                       |             |                |            |

|          |            | link board                            | alfig303    | alfig004:alink | board      |

| albox003 | alfig999 i |                                       | alfig302    | alinklib:crd b |            |

| albox016 | alinkfig r |                                       | alinklib    |                |            |

|          | alinkfig r |                                       | alinklib    |                |            |

| albox017 | alinkfig s |                                       | alinklib    |                |            |

| albox014 | alinkfig s |                                       | alinklib    |                |            |

| albox004 | alinkfig d |                                       | alinklib    |                |            |

| albox007 | alinkfig p |                                       | alinklib    |                |            |

| albox008 | alinkfig f |                                       | alinklib    |                |            |

| albox009 | alinkfig p |                                       | alinklib    |                |            |

| albox005 | alinkfig t |                                       | alinklib    |                |            |

| albox015 | alinkfig w |                                       | alinklib    |                |            |

| albox018 | alinkfig r |                                       | alinklib    | • •            |            |

| albox013 | alinkfig c |                                       | alinklib    |                |            |

| albox006 | alinkfig d |                                       | alinklib    |                |            |

| albox010 | alinkfig a |                                       | alinklib    |                |            |

| albox011 | alinkfig c |                                       | alinklib    |                |            |

| albox012 | alinkfig 1 |                                       | alinklib    |                |            |

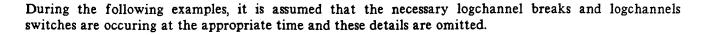

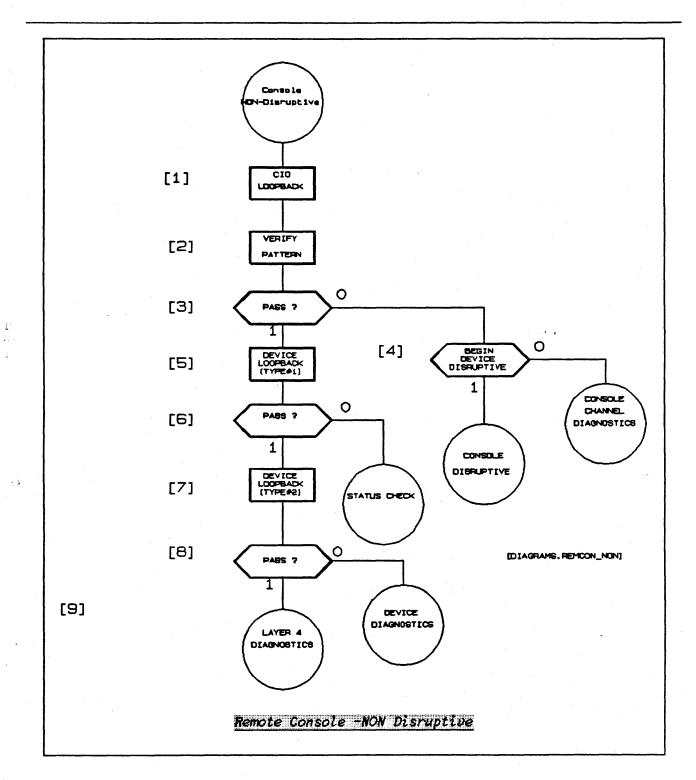

| albox019 | alinkflo r |                                       | diagrams    |                |            |

| albox020 |            | remcon non 2                          | diagrams    |                |            |

| albox021 | alinkflo s |                                       | diagrams    |                |            |

| albox022 | alinkflo r |                                       | diagrams    |                |            |

| albox023 | alinkflo p |                                       | diagrams    |                |            |

| albox024 | alinkflo c |                                       | diagrams    |                |            |

| albox025 | alinkflo 1 | · · · · · · · · · · · · · · · · · · · | diagrams    |                |            |

| albox026 | alinkflo f |                                       | diagrams    |                |            |

| albox027 | alinkflo f |                                       | diagrams    |                |            |

| albox028 | alinkflo e |                                       | diagrams    |                |            |

| albox029 | alinkflo e |                                       | diagrams    |                |            |

| albox030 | alinkflo c |                                       | diagrams    |                |            |

| albox101 | timefig? t |                                       | timing      |                | •          |

| albox201 | timefig? t |                                       | timing      |                |            |

| albox202 | timefig? t |                                       | timing      |                |            |

| albox302 | blocfigs i |                                       | blocdiag    |                |            |

| albox401 | timefig? t |                                       | timing      |                |            |

| albox402 | timefig? t |                                       | timing      |                |            |

| albox403 | timefig? t |                                       | timing      |                |            |

| albox404 | timefig? t |                                       | timing      |                |            |

| albox405 | timefig? t |                                       | timing      |                |            |

| albox406 | timefig? t |                                       | timing      |                |            |

| albox407 | timefig? t |                                       | timing      |                |            |

| albox408 | timefig? t |                                       | timing      |                |            |

| a1box409 | timefig? t |                                       | timing      |                |            |

|          |            |                                       |             |                |            |

\* Preliminary Version \*

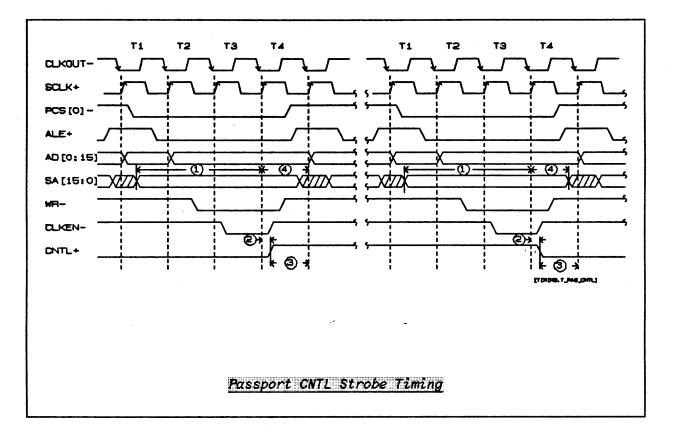

| albox410 | timefig? | t_pas_cntl | timing   |

|----------|----------|------------|----------|

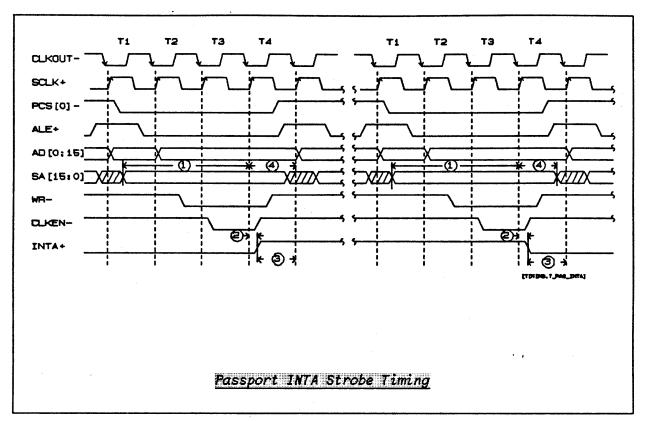

| albox411 | timefig? | t_pas_inta | timing   |

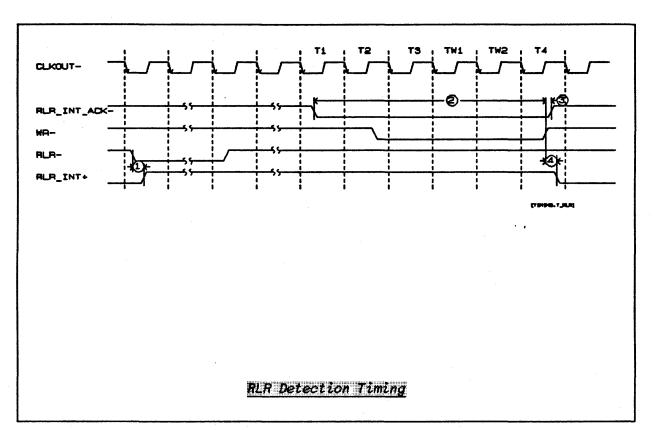

| albox412 | timefig? | t_rlr      | timing   |

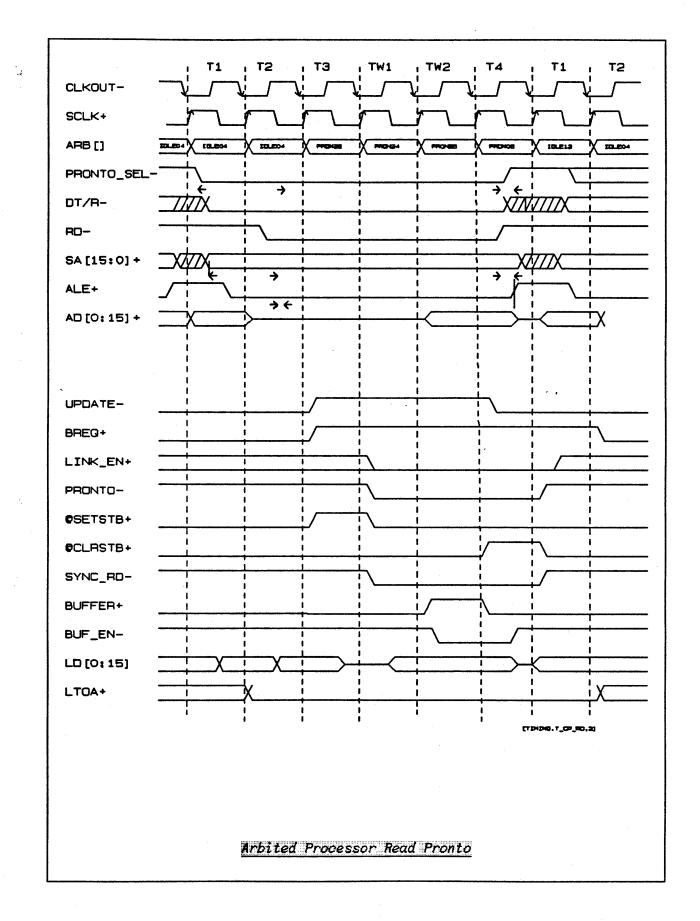

| albox501 | timefig? | t_cp_rd_2  | timing   |

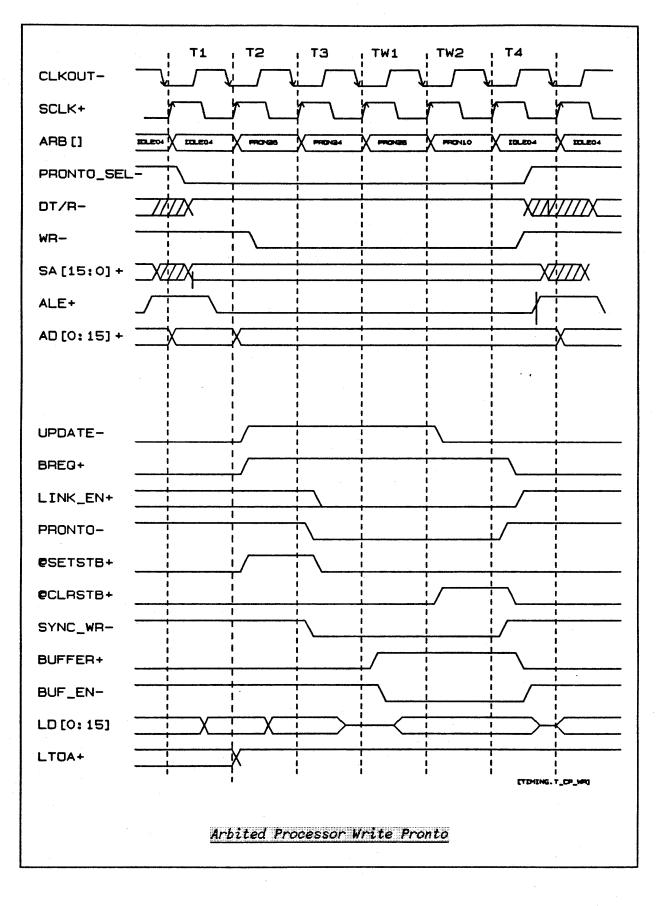

| albox502 |          | t_cp_wr_2  | timing   |

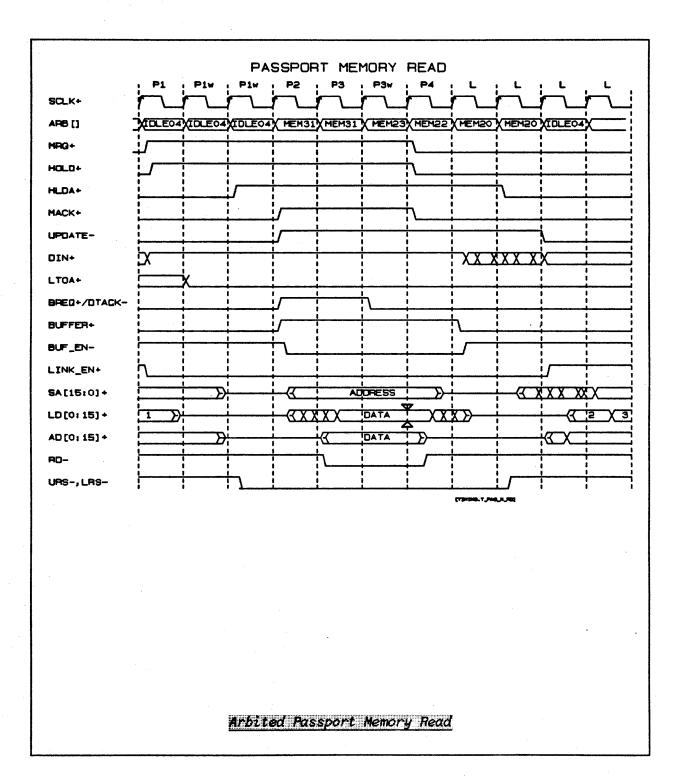

| albox503 | timefig? | t_pas_m_rd | timing   |

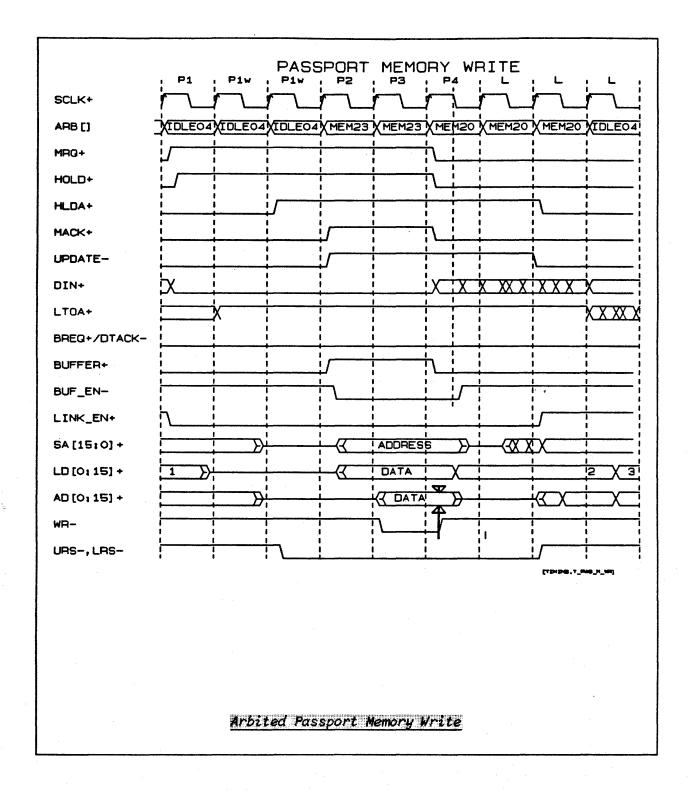

| albox504 | timefig? | t_pas_m_wr | timing   |

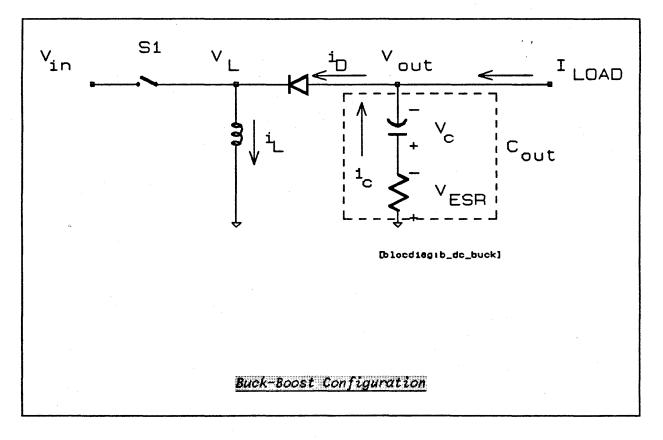

| albox601 | blocfigs | b_dc_buck  | blocdiag |

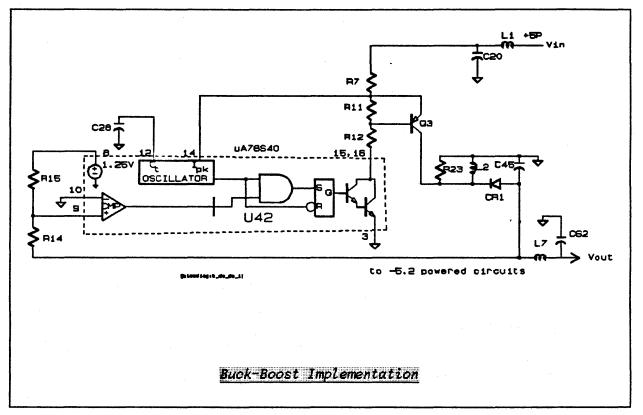

| albox602 | blocfigs | b_dc_dc    | blocdiag |

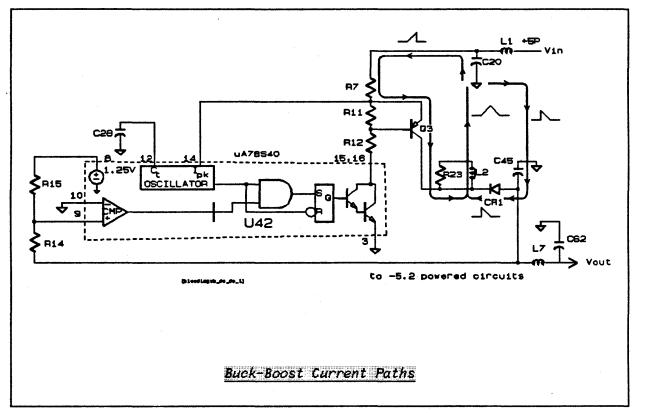

| albox603 | blocfigs | b_dc_dc_i  | blocdiag |

.

The REFERENCE section provides references, both for supplemental reading and for commonly used terms to aid the reader in better understanding the A-Link CIO Adapter product.

### **RELATED DOCUMENTS**

A-Link Protocol Document by Greg Dolkas, Randy Haagens

HP-CIO Standard Document by Roseville Networks Division

A-Link Protocol Chip (PRONTO) Hardware Description Document by Bill Martin, Kurt Chan, Vince Cavanna

Passport VLSI External Reference Specifications (ERS) by Mike Leclere

Jupiter External Reference Specifications by HP Labs

Passport Programmer's Guide by Bill Haffey

Channel I/O A-link Preliminary Support Plan by Nancy Cheung

Amux Hardware ERS by Earl Bergquist

Amux Diagnostics by Marvin Nelson

Eagle/Amux CS/80 INSTRUCTION SET Programming Manual by NorRae Spohn

### CONVENTIONS

This document has defined standards for interpreting bit numbering, byte numbering, and logic notation as described in the following.

### **Bit and Byte Notations**

#### Bit Numbering.

Bit numbering follows the rule that the most significant bit (MSB) of any unit is assigned bit position 0. Bits are numbered sequentially from most to least significant.

Any exceptions to this Bit Numbering scheme will be explicitly notated!

|      | 0   | 1 | 2 | З | 4 | 5 | 6 | 7   | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15         |

|------|-----|---|---|---|---|---|---|-----|---|---|----|----|----|----|----|------------|

| Word | MSB |   |   |   |   |   |   |     |   |   |    |    | 1  |    | 1  | LSB        |

| Byte | MSB |   |   |   |   |   |   | LSB |   |   |    |    |    |    |    | <b>-</b> - |

### Byte vs. Word.

| Byte          | 8 bit unit of information                                                                          |

|---------------|----------------------------------------------------------------------------------------------------|

| word          | 16 bit unit of information                                                                         |

| upper<br>byte | most significant 8 bits of a word unit<br>-OR-<br>most significant byte (MSByte) of a word unit.   |

| lower<br>byte | least significant 8 bits of a word unit<br>-OR-<br>least significant byte (LSByte) of a word unit. |

### Byte Numbering.

The same rule holds true for bytes of data arranged in block form The most significant byte (MSByte) is numbered 0 and the remaining bytes are numbered sequentially from most to least significant.

|          | MSB    | LSB | MSB      | LSB |           |

|----------|--------|-----|----------|-----|-----------|

| MSByte-> | byte O |     | byte 1   |     | <- LSByte |

|          | byte 2 |     | byte 3   |     |           |

|          | byte 4 |     | byte 5   |     |           |

| ŧ        | ŧ      |     | +        | ļ   | :         |

|          | byte N |     | byte N+1 |     |           |

### **Logic Notation**

Assertion vs. Deassertion.

Assertion of a signal indicates that a signal has gone from a false to a true state.

Deassertion of a signal indicates that a signal has gone from a true to a false state.

Assertion vs. Deassertion.

All signals referred to in the hardware descriptions will contain a suffix that indicates the logical "L" or "H" level at which they are asserted.

signal+ indicates that the signal is asserted at a logical H level

signal - indicates that the signal is asserted at a logical L level

Logical O vs. Logical 1.

Use of logical "0" and "1" states ordinarily indicates whether a signal is asserted or deasserted

logic 0 is equivalent to Deasserted

logic 1 is equivalent to Asserted

### Reference

#### Active vs. Passive.

Output signals (or busses of signals) are either in an active or passive state.

active indicates that the output is driven to an asserted or deasserted state

passive indicates that the output is neither asserted nor deasserted (often the case when an output has been placed in a high impedance state)

### Schematic Notation

Some of the figures contain logic symbols following the anticipated enhancements to ANSI Y32.14. No attempt will be made to explain the nature of the symbols used here, but a good reference is Texas Instruments' Bipolar Microcomputer Components Data Book mentioned in the Reference section.

#### SIGNAL NAMING.

All LOGIC signals mentioned in the theory of operation section follow the format:

| Logic Signal := | <signal name=""><br/><bus values(optional)=""><br/><polarity><br/></polarity></bus></signal> | AD<br>AD[0:15]<br>AD[0:15]+<br>BREQ+/DTACK- |

|-----------------|----------------------------------------------------------------------------------------------|---------------------------------------------|

| Bus Values :=   | <[> <most#(opt)<:least#(opt)>&lt;]&gt;</most#(opt)<:least#(opt)>                             | [][5][5:7]                                  |

| Polarity ::=    | <{+,-}>                                                                                      | POS_TRUE+<br>NEG_TRUE-                      |

All ANALOG signal names follow the format:

Analog Signal ::= <SIGNAL NAME>

VCC

#### **BOOLEAN OPERATORS.**

The basic boolean operator notations are shown in the following table.

| OR  |       |         | +         |

|-----|-------|---------|-----------|

| OR  | (Abel | Format) | #         |

| AND |       | •       | *         |

| NOT |       |         | !         |

| NOT | (Abel | Format) | /         |

| XOR |       | -       | · · · · % |

[alibool]

### **REFERENCE DESIGNATORS.**

All reference designators are printed in Elite Italic.

E.g., U20, U15-8, C23.

### GLOSSARY

CS-80

FRONTPLANE

BACKPLANE

NMI

DMA

PAL

CHANNEL

VIRTUAL CIRCUIT COMMUNICATION

CONTROL BYTE

**INFORMATION BYTE**

DEVICE

LOGCHANNEL

SUBCHANNEL

JUPITER

PASSPORT

PRONTO

LAYERED ARCHITECTURE

Command Set 80. A command set used to access and control mass storage devices

the optical fiber interface, configuration jumpers, and status indicators

the channel and support circuitry interface

A Non Maskable Interrupt which is optionally driven by the A-Link adapter to the channel across the backplane

direct memory access

Programmable Array Logic

a physical entity that consists of the I/O channel and I/O channel adapter, consisting of data, control and addressing busses

the process of multiplexing many circuit operations onto a smaller number of available circuits, creating the appearance to anything requesting a circuit that a "dedicated" rather that a "virtual" circuit exists

a byte used to identify layer 1 CONTROL information, typically indicating such status as link idle, frame end delimiter, and variable length frame follows

a byte used to identify layer 1 DATA information

the entity that is connected to the remote end of the optical fiber

a virtual data path that is established between the I/O channel adapter and an I/O card

a path to/from an I/O card, through the I/O channel, and the I/O channel adapter

high speed parallel/serial converter for layer 1

backplane adapter

protocol controller for layer 2

hierarchical architecture that describes a method of implementing data transactions across a data communications link

Alink's layer 2 message unit

FRAME

| INFORMATION FRAME         | layer 2 data frame containing layer 3 data or control information                                                                                                  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROL FRAME             | layer 2 control frame                                                                                                                                              |

| HEADER Layer 2            | accompanying every frame, the header communicates<br>protocol control and status information back and forth<br>across the link                                     |

| HEADER Layer 3            | accompanying every level 3 message segment, level 3 headers contain virtual circuit number, message type, and other level 3 control information                    |

| CRC                       | cyclic redundancy check                                                                                                                                            |

| HP-CIO                    | Hewlett Packard Channel-I/O                                                                                                                                        |

| MESSAGE                   | basic unit of information passed by level 3                                                                                                                        |

| EOF                       | level 2 control code indicating end of frame                                                                                                                       |

| VLF                       | level 2 control code indicating a Variable Length<br>Information Frame                                                                                             |

| IDLE CODE                 | level 2 control code indicating link is idle                                                                                                                       |

| BYTE SYNCHRONIZATION CODE | level 2 control code indicating a start of frame                                                                                                                   |

| DATA CODE                 | level 2 code type indicating that the following code is of type data                                                                                               |

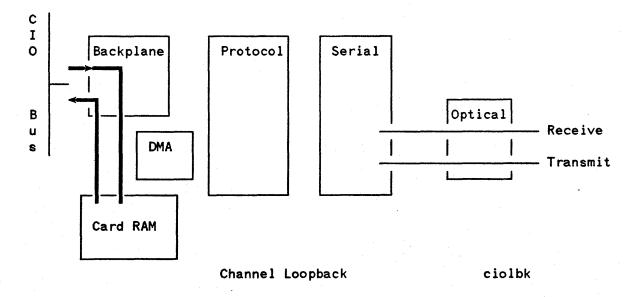

| LOOPBACK                  | mode of operation of the CIO Alink card in which front<br>and backplane are disabled and the receiver and<br>transmitter at each end are tied together for testing |

| END OF FRAME              | level 1 control byte indicating end of frame                                                                                                                       |

| IDLE STATE                | level 1 control byte indicating that the link is idle                                                                                                              |

|                           | [add infinitum ]                                                                                                                                                   |

.

\* Preliminary Version \* 2-8

## FUNCTIONAL OVERVIEW

SECTION

3

The functional overview section describes the major functional blocks that comprise the HP27111A as well as presenting a typical scenario for data read and data write operations. Each functional block description highlights the features of the particular block. The scenario examples point out the interaction of the blocks as data moves between frontplane and backplane.

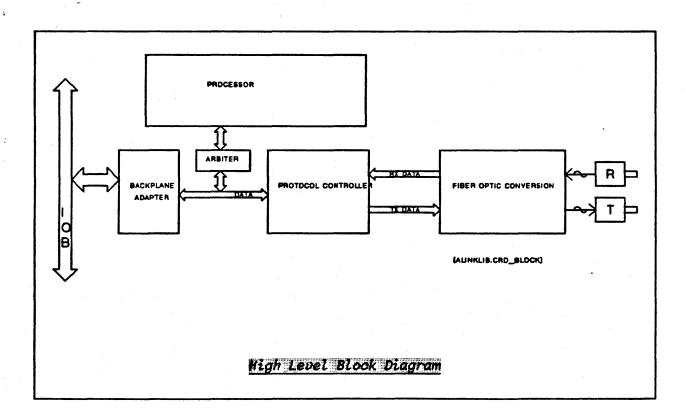

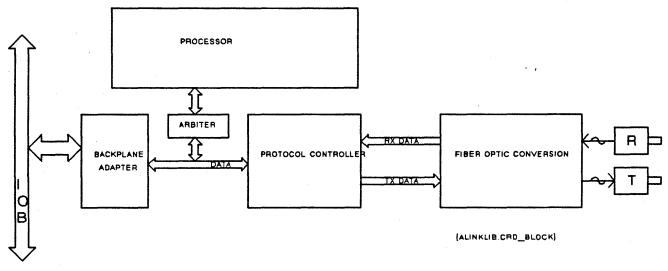

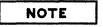

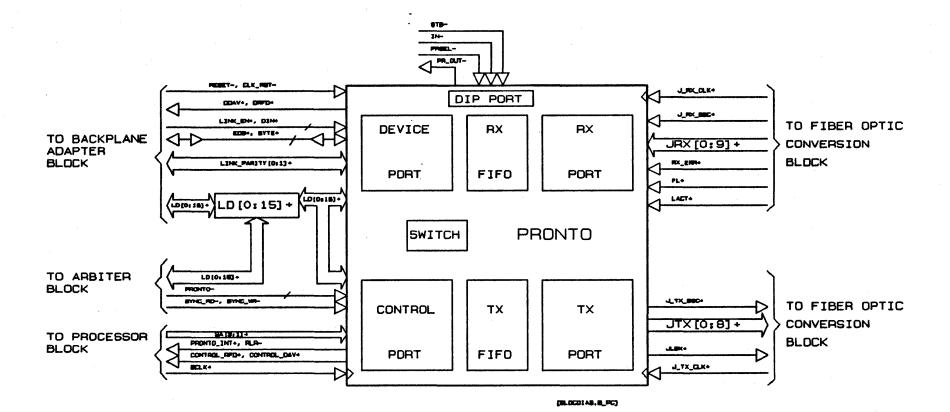

### HIGH LEVEL BLOCK DIAGRAM DESCRIPTION

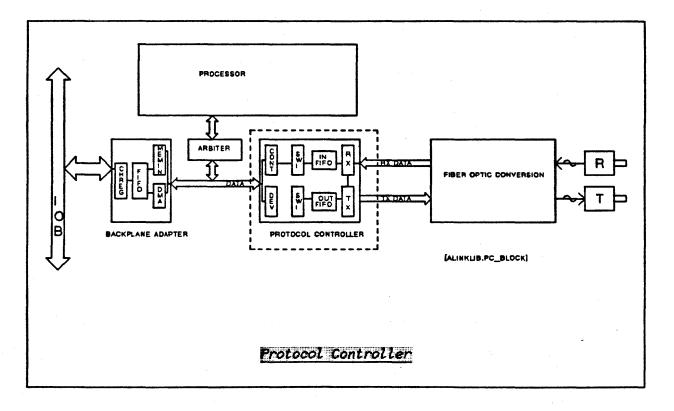

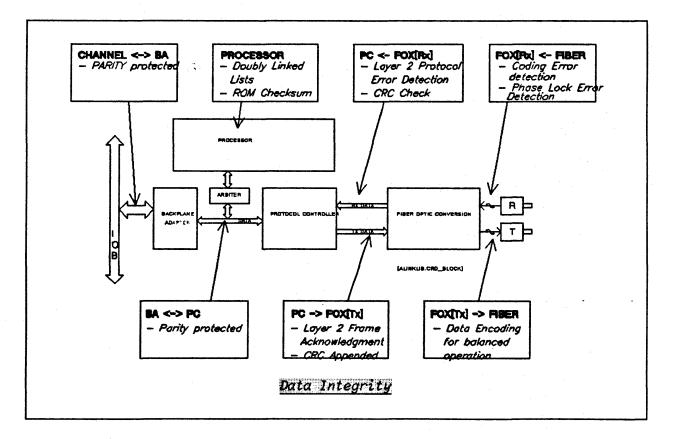

The HP-CIO version of A-link can be divided into four functional areas. The areas consist of the Backplane Adapter(BA), Processor(PB), Protocol Control(PC), and Fiber Optic Conversion(FOC). A simplified black box outline of the relations between these functions is shown in Figure 3.0. Most I/O transactions between backplane and the Fiber Optic frontplane occur by taking the direct route from Backplane Adapter to Protocol Control to the actual Fiber Optic Conversion; most Processor functions can be performed concurrently and independently of the actual data flow.

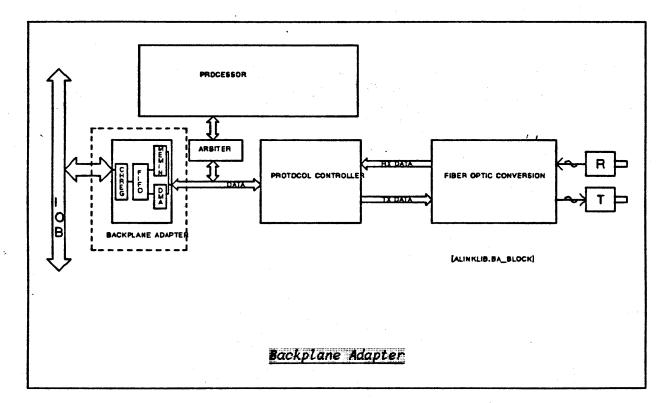

### **Backplane Adapter**

The Backplane Adapter serves as A-link's interface to the HP-CIO backplane and is the mechanism by which data, control and status information is passed to and from the card across the backplane. To the backplane, the adapter appears as a register oriented device that is selectable through the backplane's addressing mechanism, dependent upon which type of backplane operation is being performed. To increase data throughput, a DMA type "bursting" feature is provided for data transfers to allow the backplane to source or to sink succesive elements of data once the adapter's data register has been selected.

Internally, the backplane adapter appears as a memory list based control device and a high speed DMA machine. By memory list based control device, it is meant that the backplane adapter appears as a peripheral that acts upon lists of tasks that are stored in various locations in memory. The backplane adapter is also capable of interrupting the Processor block when certain conditions are detected.

### Channel operations.

Channel operations provide the most primitive programatic access to the internal operation of the CIO A-link Adapter from the host computer's perspective. In CIO syntax these are known as level 1 operations. The nine Channel operations accompanied by a brief description are given below

| chanop. tak. alink | chanop. | tak. | alink |

|--------------------|---------|------|-------|

|--------------------|---------|------|-------|

| OPERATION              | DESCRIPTION                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------|

| Read Data              | used to transfer Data from A-Link card to CIO channel<br>through the current active Subchannel                   |

| Write Data             | used to transfer Data from CIO channel to A-Link card<br>through the current active Subchannel                   |

| Write Order            | used to control Subchannels and to connect, control, and destroy Logchannels                                     |

| Write Command          | used mainly to connect and destroy Subchannels.                                                                  |

| Read Status            | used mainly to return physical status of A-Link card<br>and its local Subchannel                                 |

| Write Control          | used to control the state of the Backplane Adapter                                                               |

| Read Sense             | used to determine status of the Backplane Adapter and<br>its physical interface to the channel                   |

| Poll Service Request   | A-link responds when it is capable of processing an<br>order or data on its current active subchannel            |

| Poll Attention Request | A-link responds when it has been programmed to<br>request a new command from the channel and is able to<br>do so |

### Subchannel interactions.

A Subchannel interaction is a series of related channel operations (often referred to as sequences) for a particular subchannel. A Subchannel establishes a path from CIO to the actual Link I/O Data path. A subchannel is prerequisite to transferring data between CIO and the A-link.

A typical subchannel sequence would be the actual establishment of a subchannel on the A-link CIO Adapter for later use by the host in transferring data. This interaction is referred to as a Connect Functional Overview

Subchannel sequence. The following psuedo code illustrates the sequence of Channel operations that compose the sequence.

```

PROCEDURE Connect Subchannel( Subchannel Number : Subchannel type ) ;

BEGIN

{ form the subchannel connect command code }

Subchannel_connect := Subchannel_connect + Subchannel_Number ;

\{ get sense of I/0 card \}

CHANNEL_OPERATION(Read_Sense,A-link_card,Sense_Variable);

IF Sense Variable [Ready For Command] THEN

BEGIN

{

send the Connect command }

CHANNEL OPERATION(Write Command, A-link card, Subchannel_Connect);

END

ELSE

BEGIN

{ request notification when the card empties its command register ! }

CHANNEL OPERATION(Write Control, A-link Card, Request Attention);

Delay Until Attention Requested ;

{ verify ready for command }

CHANNEL OPERATION (Read Sense, A-link card, Sense Variable);

{ send the Connect command }

CHANNEL OPERATION(Write Command, A-link card, Subchannel Connect);

END;

END ;

```

Certain Subchannel Interactions are handled automatically by the Backplane Adapter. Remaining interactions are passed on to the Processor Block for further action. The Connect Subchannel interaction is handled automatically, for example. Connect Logchannel transactions, on the other hand, always require the intervention of the Processor Block.

Supported Subchannel Interactions and Transactions are detailed in the Firmware Description Section. (see Supported Commands and Orders)

### Logchannel transactions.

Logchannel transactions are composed of series of subchannel interactions. They provide the A-link CIO Adapter with its multiplexing capabilities. A-link, itself has only one physical duplex link to the outside world. Logchannels are logical replications of this physical link and are structured such that they appear to the host CPU as individual physical A-link connections. They are, in a sense, virtual data paths between the Channel and the A-link card.

For more details on Logchannel transactions, consult the Channel I/O Handbook.

Processor communications.

The Backplane Adapter block communicates to the Processor block through Memory located within the Processor block. Status, data and control information is posted in various lists in Memory according to a predefined data structure.

The Backplane Adapter block interrogates these data structures to determine, for example, which subchannel interactions must be passed on to the Processor block, and which to process automatically. It also determines the source and destination for data transactions it is instructed to perform.

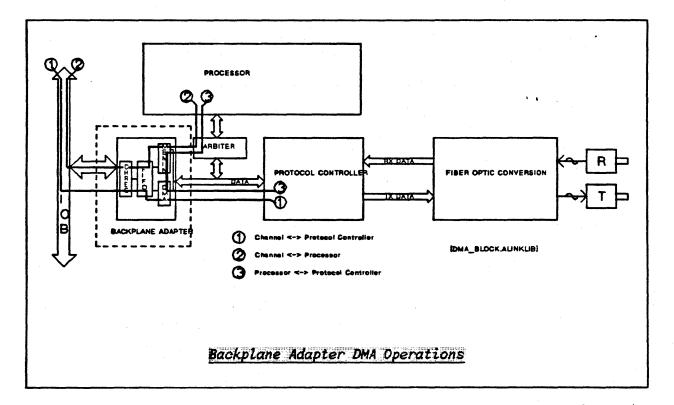

### DMA operations.

DMA operations are used to transfer data between any of the ports accessible to the Backplane Adapter. These three ports are illustrated below.

As mentioned before, the source and destination ports are determined by examining the lists stored in Memory.

An internal half-duplex FIFO is used to buffer data and help pace data transfers.

### **Protocol Controller**

The Protocol Control section of the A-link card is responsible for transforming data to and from the A-link Layer 2 Protocol format, dependent upon direction of data flow. It consists of a bi-directional half duplex and a full duplex interface which form four ports: Control, Device, Receive and Transmit. A special function, knowns as the "switch" manages the half duplex interface which is shared by the Control and Device port. Outbound data passes from either the Control or Device port to the Transmit port, where it is formatted. Inbound data, from the Receive port, is stripped of Layer 2 formatting and passes to the Control or Device port. Both inbound and outbound data paths contain a FIFO.

The actual protocol control takes place in the management of data that is sent and received by the Transmit and Receive ports. In the case of data in the Outbound FIFO, the Protocol Control block guarantees that any data loaded into the Outbound FIFO will not be overwritten until it has been correctly received by the remote node, and furthermore, that the Inbound FIFO of the remote node will not be overrun.

For inbound data, the Protocol Control block guarantees that all data has been received in the order it was loaded into the remote's Outbound FIFO, and that any attempts at overrun will generate a Protocol error.

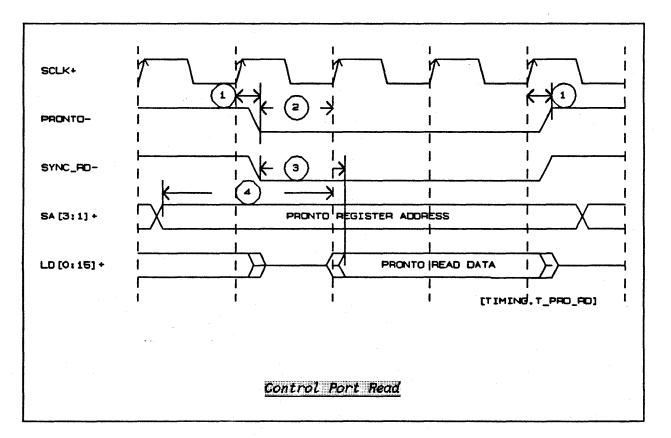

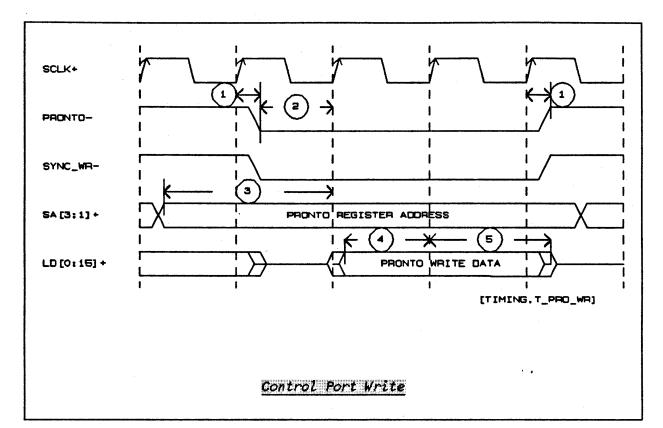

#### Control Port.

The Control port is used by the Processor block to access control registers internal to the Protocol Control block and to transfer data to and from the link. The registers are used to control and monitor the behaviour of the link and data transfers active on it. Error conditions and recovery measures are managed through this path.

Data transfers via the Control port usually consist of *Header Messages* which are follow the A-link Layer 3 protocol. These Headers are used to setup and execute data transfers between the local A-link CIO Adapter and the remote device.

#### Device port.

The Device port is a high speed direct access port which handles the majority of I/O traffic on the link. It provides a direct data path to the Inbound or Outbound internal FIFOs depending upon the direction of data transfer.

Status indicators are provided to the Backplane Adapter block to indicate whether the Device port is ready to send or receive data as well as means of identifying when a particular stream of data has reached a termination condition.

#### Switch.

The Switch is a special feature of the Protocol Control block that allows the Inbound and Outbound data paths to be either manually or automatically pointed to the Device port (Backplane Adapter) or Control port (Processor). Each FIFO (Inbound and Outbound) has its own independent *switch*. When the Switch is operated manually, the Processor explicitly establishes the connection to the I/O data paths by pointing the switch to one of the ports. In automatic mode, each switch toggles between Control and Device port depending upon information previously loaded into the Control port registers by the Processor.

The Switch only affects data transfer paths; it does not inhibit Control port register accesses.

#### Transmit port.

The Transmit port is used by the Protocol Control block to send data from the Outbound FIFO to the Fiber Optic Conversion block. It also supplies state information to the remote node to allow management of the link (Layer 2 Protocol). Data and state information is packaged in units known as Control and Information Frames.

Control Frames contain the current state of the Inbound FIFO as well as link control commands.

Information Frames consist of formatted buffers obtained from the Outbound FIFO. The formatting basically involves prefacing the buffer of data with an Information Header which identifies the particular buffer to be sent, and then appending a CRC to the buffer to protect the data buffer's contents.

Two main factors influence whether the Protocol Control block will send an Information Frame out the Transmit port: the ability of the remote node to accept another buffer and the presence of a buffer to be sent. The Protocol Control block can determine the state of the remote node's Inbound FIFO from data received through the Receive port. Control Frames are sent if the block is incapable of sending an Information Frame.

Acknowledgement of outstanding buffers, and transmission retry is also caused by examination of the state of the remote node's Inbound FIFO.

A detailed description of the A-link layer 2 Protocol is found in the A-link Protocol Document.

### Receive port.

The Receive port takes parallel data from the Fiber Optic Conversion block, processes it, verifies its integrity, and then extracts the essential A-link Protocol Layer 2 information from it. Valid data extracted from *Information Frames* is loaded into the Inbound FIFO. Remote node state information is extracted from *Information and Control Frames* and directs behaviour of the Transmit port as described previously.

The Receive port also monitors the state of the Fiber Optic Conversion block's receiver and provides this information to the Processer block via the Control port.

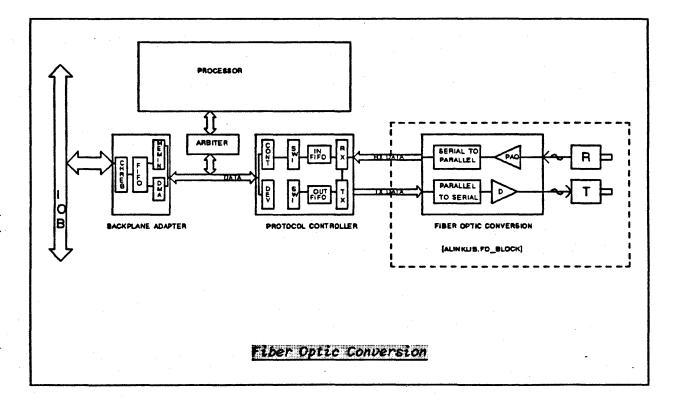

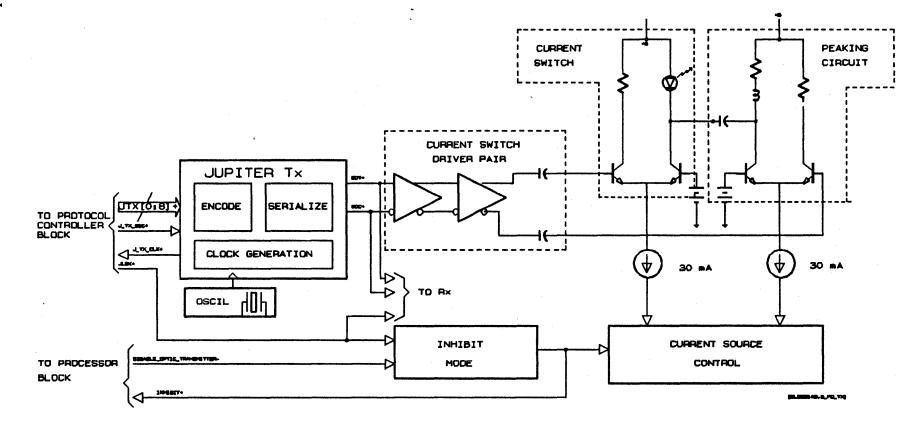

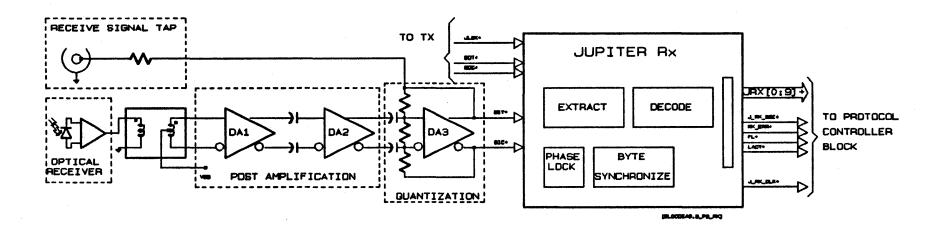

### **Fiber Optic Conversion**

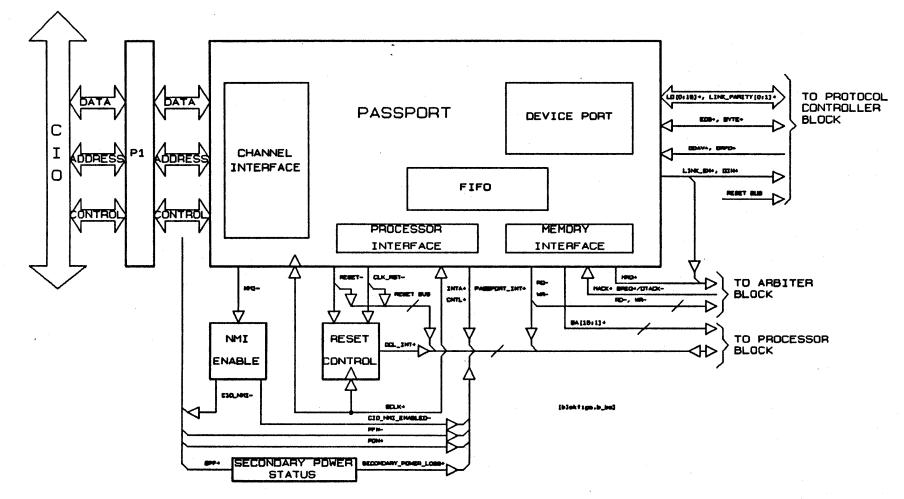

The Fiber Optic Conversion block provides the conversion between byte-parallel and serial data streams. The block consists of two independent serial to parallel and parallel to serial converters that link the optic transmitter and receiver to the Protocol Control block's Receive and Transmit ports.

#### Optical receiver.

The Optical receiver converts flux on the input fiber into an analog waveform proportional to the intensity of the incoming flux.

#### Post Amplifier and Quantizer.

The analog signal from the Optical Receiver must be conditioned before information may be extracted from it. The Post Amplifier and Quantizer block amplifies the low-level analog signal and quantizes it to boolean logical levels. The quantized signal is then passed on to the Serial to Parallel Conversion block.

#### Serial to parallel conversion.

The Serial to parallel conversion block locks onto the incoming serial waveform and decodes and extracts the original layer 2 synchronization, control and data information, reconstructing it into a parallel format which is then sent to the Protocol Control block.

Illegal codes are flagged when the pattern is transferred to the Protocol Control block. Other status provided includes the presence of activity on the fiber, and the ability to lock onto the serial data stream, all of which are monitored by the Protocol Control block.

### Parallel to serial conversion.

**Parallel to serial conversion** takes parallel data from the Protocol Control block; encodes it, and then serializes the data to prepare it for transmission on the optical fiber.

The encoding operation is required to accomodate some of the electrical characteristics of the analog and optical circuitry and media.

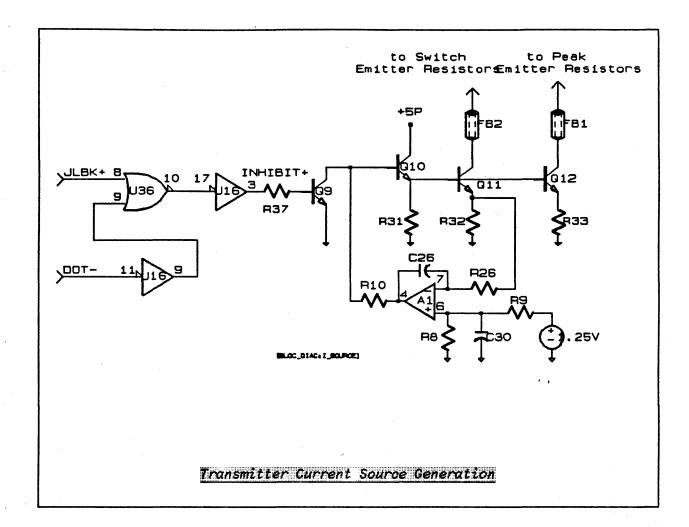

Driver.

脖

The Driver takes the serialized output from the Parallel to Serial Converter and conditions it to meet the input requirements of the Optical Transmitter and the power requirements of the attached fiber.

#### **Optical Transmitter.**

The Optical Transmitter transforms the output of the Driver into optical flux energy which then may drive the outbound optic fiber.

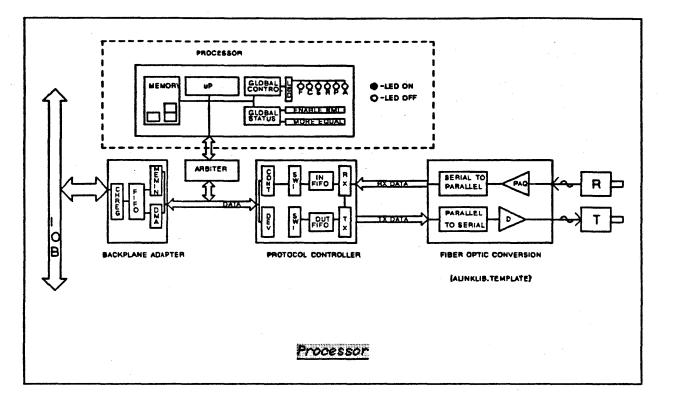

### Processor

The Processor block's main responsibility is to transform Channel requests (channel operations, subchannel and logchannel transactions) into A-link protocol format; it is essentially the A-link Protocol Layer 3 engine.

Channel requests are managed in conjunction with the Backplane Adapter. The Processor block initiates and processes requests to the remote node that involve the transfer of data through the Protocol Control

### Functional Overview

block. Once the Processor block has determined that a requested transfer may begin it gives the go-ahead to the Backplane Adapter and Protocol Control block, and continues its own processing independently.

The Processor block also responds to requests from remote nodes that appear at the Protocol Control block and maintains error, status and control operation of the link.

Link Control/Layer 3 engine.

Link Control/Layer 3 engine transforms a Channel read or write request into the series of steps necessary to communicate to the remote node. Basically, this involves obtaining one of the link's resources and then sending the necessary commands across this resource in order to transfer data.

Where the Channel views the A-link card as multiple I/O devices using Logchannels, A-link uses the concept of Virtual Circuits in multiplexing it's front-plane resources.

All data that is transferred on the link must be preceded by this Virtual Circuit identifier in what is known as a *Layer 3 Header*. Information within this Header also indicates what sort of use is intended for the Virtual Circuit resource.

Further details on types and formats of Headers is found in the section on Firmware Description.

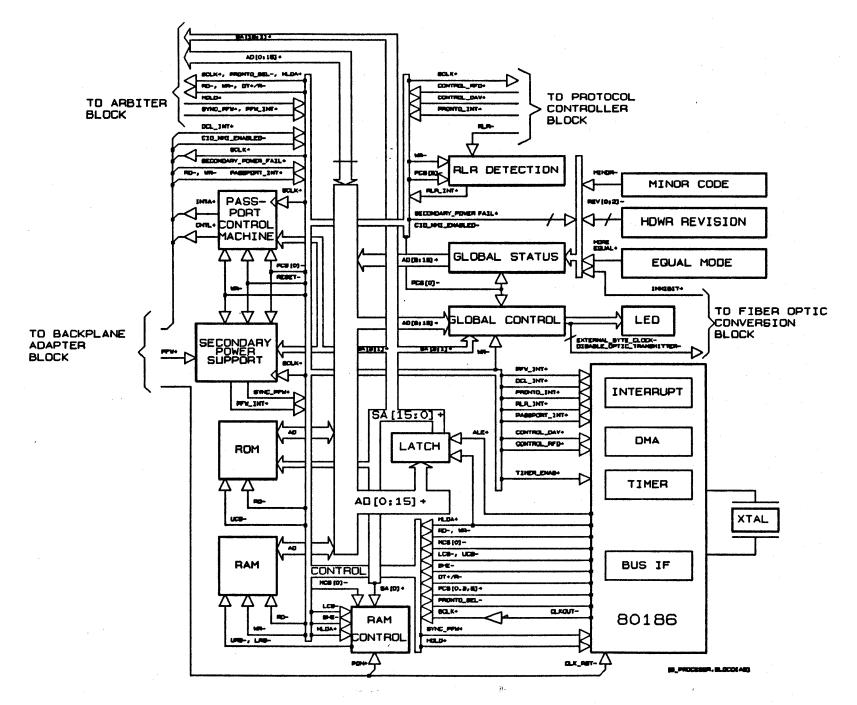

#### Microprocessor/80186.

The Microprocessor/80186 gives the Processor block its processing power. It has access to the Protocol Control block's Control port, the Backplane Adapter through Memory, and Configuration and Status

registers which control and indicate the A-link adapters current state and mode of operation. Firmware, described later in this document, is executed by the 80186.

The translation of Channel request to Command Set 80 (CS-80) format is done by the 80186.

Requests originating from the remote node are handled by the Microprocessor.

The Microprocessor is also responsible for performing the on-card diagnostics and monitoring link behavior characteristics.

#### Memory.

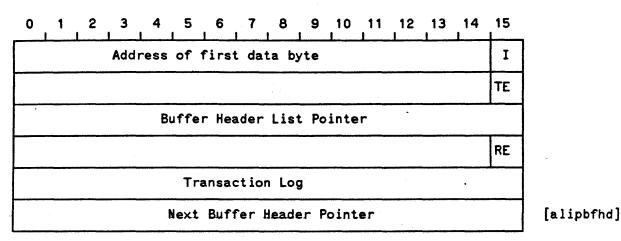

Memory is the basic communications path between the Processor block and the Backplane Adapter. Certain types of Channel requests and Channel data messages are passed on to the Processor block through the Backplane Adapter into memory. The Processor responds by building lists of tasks for the Backplane Adapter to process. These lists allow the Processor to control the flow of data from the Channel to the DMA interface of the BA.

Memory is also used to maintain the state of outstanding Virtual Circuits. As each stage of the A-link Protocol or phase of a CS-80 transaction is completed, the state of the Virtual Circuit executing that process is updated.

#### Global Status/Control LED's.

The Global Status/Control LED's block is used by A-link to obtain information regarding card configuration, hardware revision codes, to display link status through LED's and to provide control over modes of operation.

During normal operation, the LED's provide a quick indication of link activity(a), signal quality(s), remote (r), and proper configuration(c).

The LED's come in one of two colors, green indicating normal activity, red indicating an error condition.

Details on the significance of each LED are found in the section on Specifications.

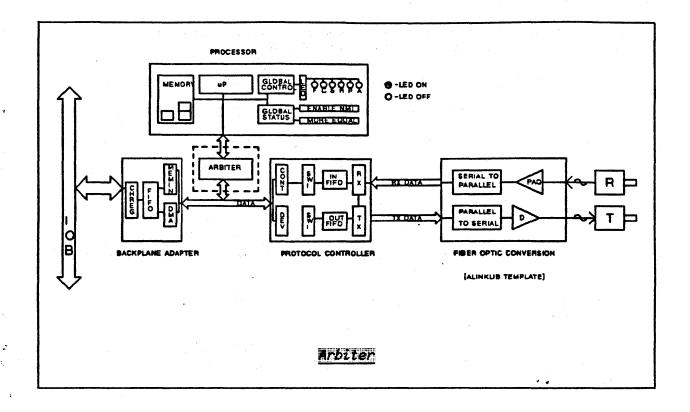

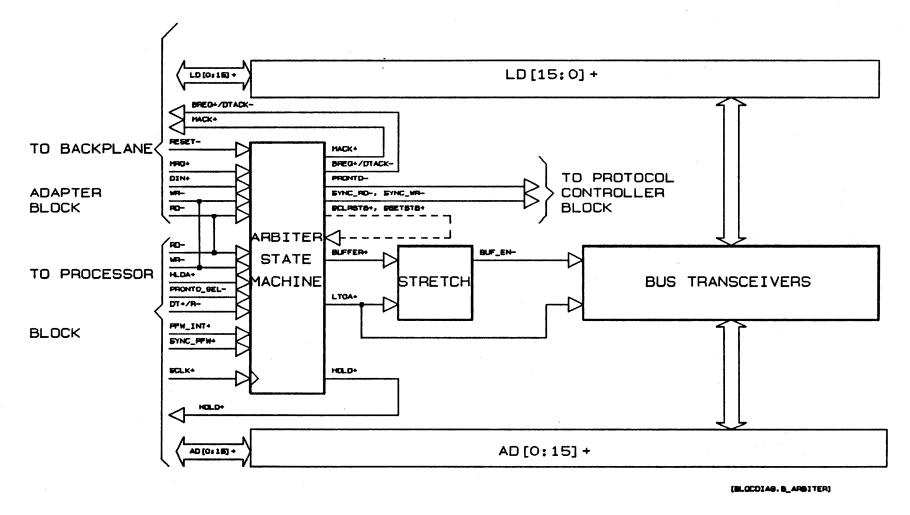

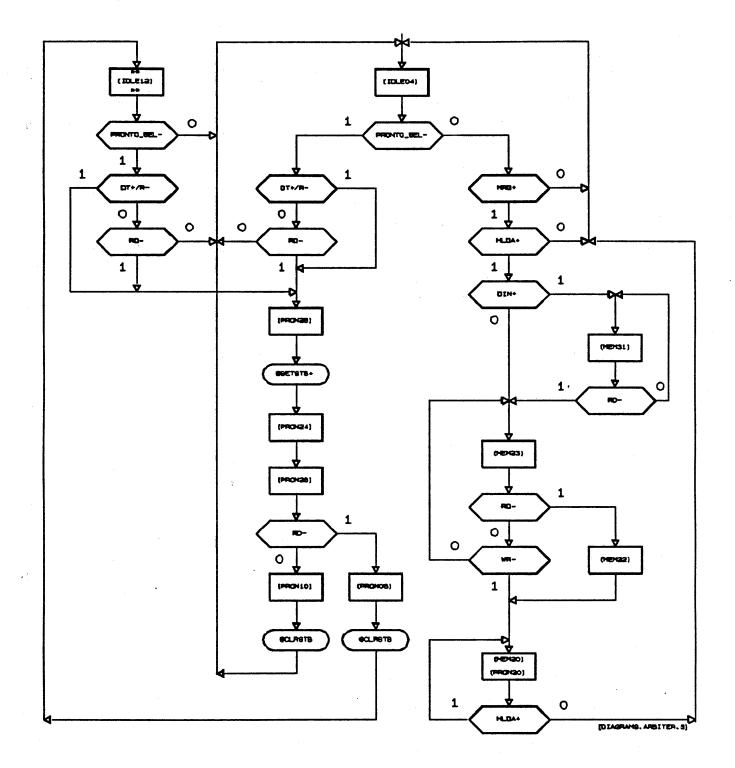

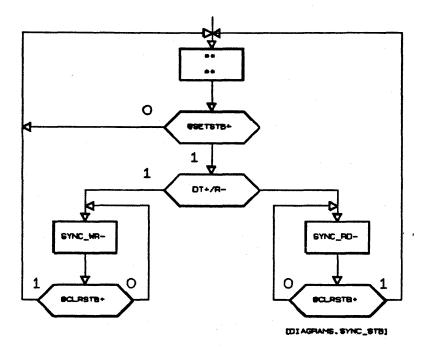

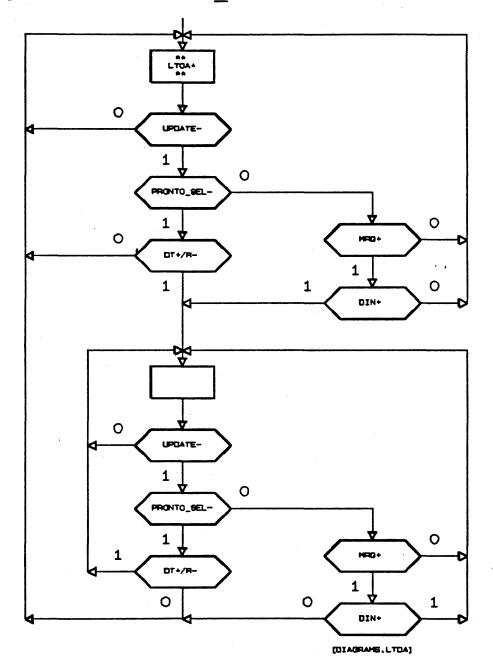

### Arbiter

The Arbiter block isolates the Processor block's data path from the link data communication's path between the Backplane Adapter and the Protocol Controller. The Arbiter then controls any data accesses that must span both busses, allowing either the Backplane Adapter of the Processor to be effective master of both busses.

#### Processor to Protocol Controller Control Port.

All I/O operations between the microprocessor and the control port must be initiated through the arbiter. During these operations the Backplane Adapter is prevented from accessing either the Protocol Controller or Processor Memory. It should be noted that card requests that require a great deal of interaction between Processor and Protocol Controller may impede other pending link operations.

#### Backplane Adapter to Processor Memory.

All Backplane Adapter accesses to Processor Memory must be initiated through the arbiter. During these operations the microprocessor may only execute internally queued instructions (if any are present). Once again card requests that require significant interaction between Backplane Adapter and Processor/Memory may impede other pending link operations. Also, in this case, Processor background processes are slowed.

### SAMPLE READ TRANSACTION

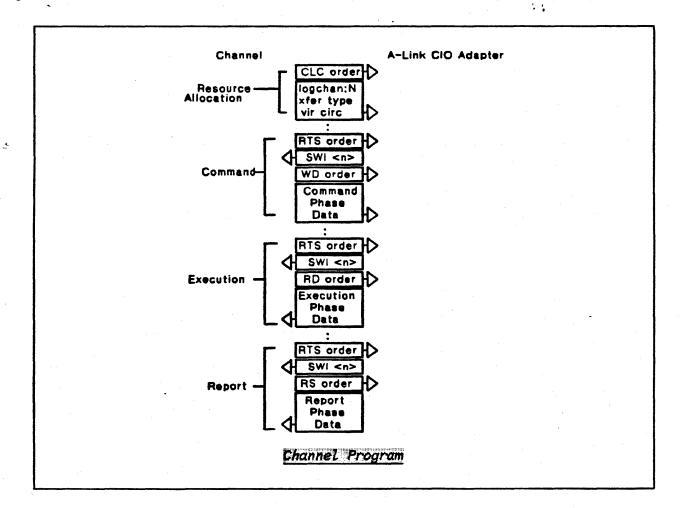

Following, is a sample read transaction in which data is transferred from the remote device to the channel. The program sequence for the backplane and frontplane are described and then the effect these sequences have on the A-link CIO adapter is illustrated.

The read transaction performed is a standard CS-80 Read sequence with the normal Command, Execution, and Report phases. In brief review of the phases of this sequence, the Command phase directs the disc to retrieve data from a particular disc location, the data is transmitted during the Execution phase, and the status of the read is returned in the Report phase.

It should be noted that both the card and the link have been initialized prior to the read transaction and that a subchannel path is actively connected on the card.

Also, for the sake of simplicity, only one transaction is assumed to be in effect and the response time of both the channel and the remote device are optimum. (i.e., this is a STRAIGHTFORWARD explanation...)

### **Backplane Program Sequence**

The Backplane Program Sequence consists of obtaining one of the A-link adapter's logchannel resources followed by the three phases of the CS-80 transaction: Command, Execution, Report.

In each of the CS-80 phases of the sequence, the channel program determines that the card is ready to proceed and then sends an order after which data is either sent to or received from the card.

#### Functional Overview

#### **Resource Allocation.**

The resource that the channel establishes with the card is known as a Logical Channel or Logchannel as described earlier.

The Logchannel is established by the channel performing a Connect Logchannel Interaction upon the card. Basically, this interaction consists of a Connect Logchannel Order followed by data that indicates the type of CS-80 transaction to be performed (in our example, a *READ*) as well as the number of the logchannel and the A-link virtual circuit that the transaction will be associated with.

#### Command Phase.

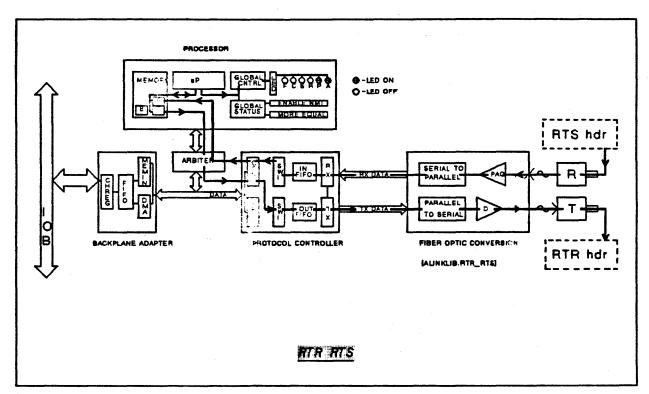

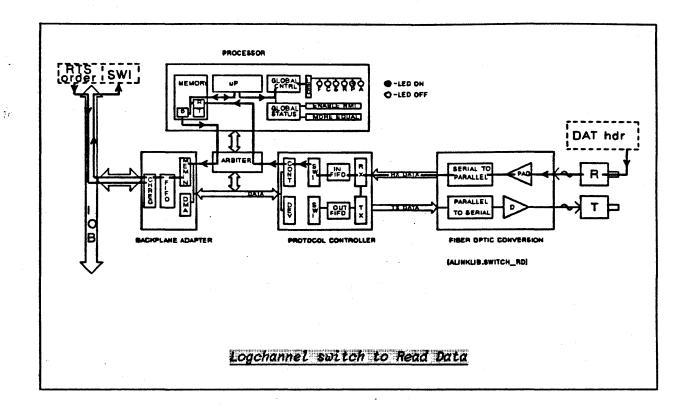

In the Command Phase, the channel program determines that it may proceed with its desired logchannel by issuing a Read Transparent Status Order (RTS). Since the card is ready to proceed, it responds with a Switch to Logchannel #n (SWI) status message. In CIO terminology this is also known as a logchannel break and Activation.

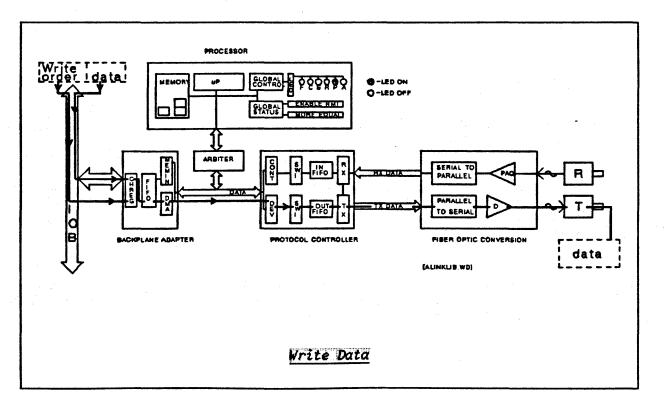

The channel program then sends a Write Data Order followed by a buffer of data that contains the set of CS-80 commands that are to be executed by the disc. In this case, the data specifies a disc read as well as disc address and control parameters. The end of this data buffer is tagged to indicate transmission has completed.

#### **Execution Phase**.

During the Execution Phase, the channel program again issues a RTS Order and obtains a status message of SWI and passes through the logchannel break.

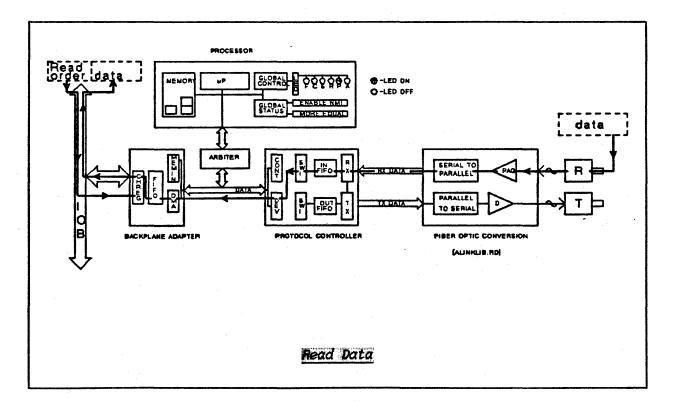

Since we are performing a *READ* operation on the disc, the channel program sends a **Read Data Order** to the card in order to retrieve the requested data.

#### **Report Phase**.

Finally, during the Report Phase, the channel program proceeds through one more logchannel break, and then sends a Read Status order (RS) to the card in order to verify the results of the CS-80 transaction.

The A-link CIO Adapter is now ready to proceed with further requests.

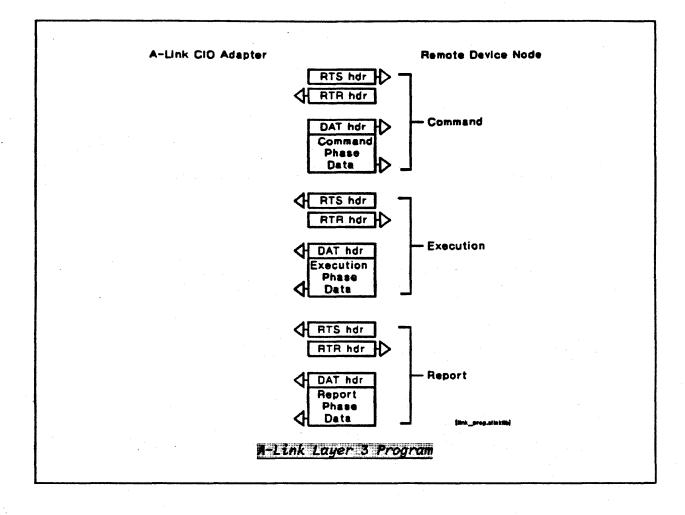

### Frontplane Program Sequence

The Frontplane Program Sequence uses the A-link Layer 3 protocol to structure the three phases of the CS-80 transaction.

During each phase of a CS-80 transaction, the source of data (local card or remote device) requests the use of a particular virtual circuit. Once the receiver of data indicates that it is ready, the data for that particular phase is transferred.

#### **Resource Allocation.**

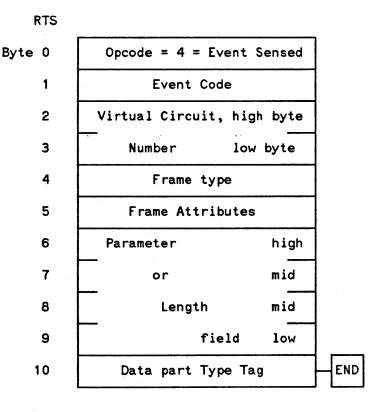

The frontplane effectively performs a Resource allocation during each phase of the CS-80 transaction. This resource allocation consists of a Request to Send(RTS) / Ready to Receive(RTR) header exchange between source and sink of data.

The RTS header is a standard A-link layer 3 header, and thus indicates the nature of data to follow as well as the virtual circuit to associate the data with.

The RTR header indicates that the data sink is ready to receive a block of data for a particular virtual circuit.

#### Command Phase.

In the Command Phase, the A-link CIO Adapter sends an RTS header onto the link indicating that it is about to initiate a CS-80 transaction.

When the remote device returns an RTR header, the Adapter sends out a DAT header followed by the data that forms the CS-80 Command.

#### **Execution Phase**.

In the Execution Phase for a *READ* from the remote device, the remote will respond with an **RTS** header indicating that it is ready to send the execution data. The card will respond with an **RTR** header which causes the remote device to send a **DAT** header followed by the data retrieved from the disc.

#### **Report Phase.**

In the Report Phase, the remote device initiates an RTS/RTR header exchange, and the card receives a DAT header followed by data that describes the success of the just completed Read.

### **Functional Block Interaction**

The Functional Block Interaction on the A-link CIO Adapter ties the frontplane and backplane program sequences together.

Each of the major functional blocks described previously (BA,PC,PROC,FO,ARBITER) plays a specific role in the process.

To illustrate this block interaction, the data flow during the various phases of the Read Transaction is presented, as well as the cause and effect nature of the action.

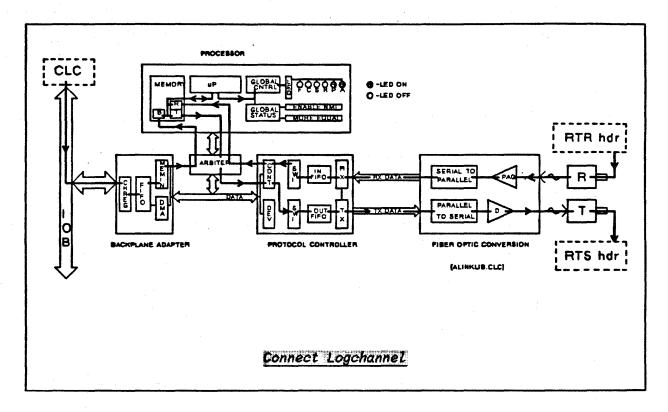

#### **Resource Allocation.**

When the Channel sends the CLC order to the adapter, the CLC data travels from the I/O Backplane (IOB) to the BA's internal FIFO. The BA discovers that the CLC does not match any of the entries in the lists provided by the PROC block, and therefore gains access to PROC Memory through the Arbiter and transfers the CLC data into it.

The uP is alerted of this new data, parses it, and adds the Logchannel and Virtual Circuit pair to its list of requests. Since we are assuming there are no pending requests, the Processor builds up an RTS Header which includes the new Virtual Circuit. This initial RTS is used to mark the beginning of the Command Phase.

The uP issues a request to the Arbiter to access the Protocol Controller, and proceeds to send the RTS Header out through the Control Port. The RTS passes through the outbound FIFO, has control and CRC information added to it, and is then sent to the Tx portion of the FO block.

3

The FO Block serializes the data, converts it into a photon stream and sends it out onto the fiber.

The action of sending the RTS Header onto the link (actually, any header) causes the Activity lamp on the adapter to light.

When the RTR Header appears on the fiber, it is converted back to parallel form by the FO Block Rx section and passed on to the Receive Port of the PC block. The PC determines that the data is valid and is the expected buffer in the current sequence. The RTR Header is then placed in the Inbound FIFO.

The PROC retrieves the RTR Header from the PC, checks its Virtual Circuit and thus determines that the remote device is ready to proceed with the Command Phase

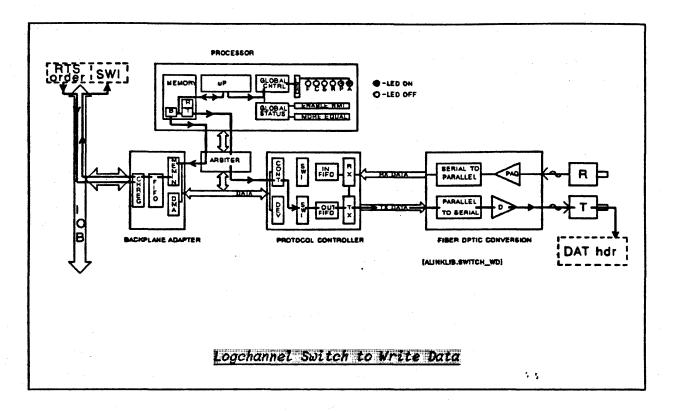

#### **Command Phase**.

To the adapter the Command Phase has two basic steps: the Switch and the actual Command Data Transfer.

During the Switch, the adapter prepares the link and the channel for the transfer of command data. In the case of the link, the adapter sends out a DAT Header onto the link via the Arbiter and PC, which indicates to the remote device that the actual Command Data is to follow. Just before sending out the DAT header, the Processor placed the PC in *Transmit Automatic Mode*. This special mode will cause the PC to *SWITCH* from the Control Port to the Device Port once the header has passed through the Control Port.

For the channel, the Processor programs the Backplane Adapter to respond to a Read Transparent Status (RTS) Order with a SWITCH to Logchannel < n >. It also tells the BA to expect a Write Data order to follow and to transfer the incoming data to the PC.

Ę.

3

During the Command Data Transfer, the channel sends the Write Data order, which the BA accepts, and then lets the incoming data (the CS-80 Command) pass through it and into the PC where it is readied for transfer onto the link.

When the BA encounters a word tagged with an end delimiter, it passes this final transfer to the PC and then waits for the next list of events to be supplied by the Processor.

When the PC encounters the last word(byte), it flags this event by marking a bit in the level 2 header and points its Transmit Switch back to the Control Port.

#### Execution Phase.

Before the actual Execution Phase data is transferred, the adapter waits for the remote device to request use of the desired virtual circuit by an RTS Header.

When the Processor sends out the acknowledging RTR Header, it proceeds through the Arbiter to the Protocol Controller, as before, and flashes the Activity light.

Once the RTR Header has been sent, the Processor provides a new list of events for the Backplane Adapter to follow. It programs the BA to wait for the Protocol Controller to indicate that it has data, respond with a SWI <n> to the next Read Transparent Status Order, and then wait for a Read Data order, at which time it will transfer data from the Protocol Controller to the Channel.

Meanwhile, the Processor places the Protocol Controller in Receive Automatic Mode. This is similar to the Transmit Auto mode, in that once the DAT header is received, the SWITCH points to the Device port, and the remaining incoming data will transfer through this port.

Assuming that the adapter has received the DAT header, the PC will now indicate that it has data at the Device Port. The BA will proceed through the RTS Order and start passing the *Execution Phase Data* from the PC to the channel until it detects an end delimiter.

\* Preliminary Version \* 3-20

#### **Report Phase.**

The adapter interaction during Report Phase is almost exactly the same as during the Execution Phase.

The main difference, is that the Processor builds a slightly different list of events for the Backplane Adapter to follow. Instead of looking for a Read Data (RD) Order, the Backplane Adapter looks for a Read Status (RS) Order before allowing *Report Phase Data* to travel from the Protocol Controller to the channel.

\* Preliminary Version \* 3-22 Three types of specifications will be covered in this section: Functional, Electrical, and Physical.

Functional specifications are concerned with card performance and the basic end user interface.

Electrical specifications outline power and timing requirements of the card when installed in the host system and connected to a remote device.

Physical specifications describe the card in terms of size, connectivity and operating environment.

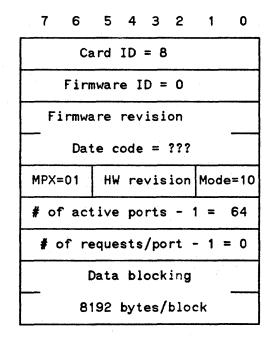

# FUNCTIONAL

The A-Link CIO Adapter is a high speed full duplex serial interface capable of transmitting over distances up to 1 Kilometer to a remote device. To product has two basic interfaces: the CIO Backplane and the A-Link Frontplane. Given these two interfaces, the card is capable of operation in any of several Configurations, depending upon the requirements of the host channel and the remote device. The A-Link card also has several features that allow it to maintain a high level of data integrity, including local Self-Test and a set of Status Indicators that are visible on the card and available for backplane interrogation.

- A-link Protocol Frontplane

- Channel I/O Protocol Backplane

- up to 64 active Logchannels

- up to 64 active Virtual Circuits

- up to 5 Mbyte frontplane

- up to 5 Mbyte backplane (10 Mbyte for < 128 byte bursts)

- optional Channel NMI capability

- host to host, host to disc capabilities

- parity and CRC data protection

- future support for secondary power

- full duplex optical interface

- LED status indicators

- programmable loopback

- on card self test

- link performance and status monitoring capabilities

#### SPECIFICATIONS

# **Communication Path Configurations**

Currently, the A-link CIO Adapter supports only the point to point configuration with an A-MUX Disc Cluster.

Within this configuration, two basic communication paths exist: Host to Disc, and (at remote device's option) Host to Host.

Special diagnostic communication paths, such as Loopback, will be described later.

#### Host to Disc.

The Host to Disc configuration connects the A-link CIO Adapter to any of the discs in an A-MUX Disc Cluster (or any disc controller with an A-link interface and CS-80 capability). The host SPU can access any of the discs in the cluster according to the virtual circuit mapping as specified by the disc cluster.

#### Host to Host.

The Host to Host configuration connects the A-link CIO Adapter to another SPU A-link adapter through the A-MUX Cluster, assuming that more than one SPU has an A-link connection to the remote device.

### Frontplane (A-Link)

The A-Link CIO Adapter Frontplane consists of a full duplex fiber optic connection used to transmit and receive data. This provides a high speed interface which is controlled by A-Link Protocol.

A-Link Protocol.

The A-link Protocol defines an I/O communications link between host System processing unit(SPU) and a remote device, either another SPU or an I/O device controller, such as a disc controller.

The A-link CIO Adapter supports and implements all four layers of the A-link Protocol.

For a detailed description of these layers, refer to the A-Link Protocol document.

For a description of the layer 3 format see the section on Firmware description.

#### Virtual Circuit Capabilities.

The A-link CIO Adapter is capable of communicating over any of 65536 virtual circuits. One of these circuits, **OFFFFH** is reserved for link control independent of the remaining 65535 circuits.

The number of active virtual circuits is limited to 64. This number represents the combination of virtual circuit requests from both the local host SPU and any requests for access to a virtual circuit from the remote device.

#### Transfer Rates.

Both the A-link card's receiver and transmitter are capable of operating at 80 Mbaud, which translates to approximately 5 Megabytes. This 5 Megabyte figure accounts for the control and information mix present on the link.

Actual 5 Megabyte performance will be limited due to the half duplex nature of the A-link adapter's backplane, loading of the channel, and the ability of the remote device to sink and source data at the described rate.

Link ID.

The Link ID of the A-link CIO Adapter is type 0. It may communicate with any remote device that supports type 0 access.

# Backplane

The A-link card uses Channel I/O (CIO) protocol to communicate with the host SPU across its backplane. The card supports logchannel multiplexing. Logchannel accesses to the link should be setup in a CS-80 structure.

The A-Link CIO Adapter supports the CIO Standard Document layers 0 through 3. It is considered to be a NON Level 1 Device Adapter. Though the card agrees with the CIO Standard not all Level 2 and Level 3 operations are supported.

Channel I/O compatibility.

The A-Link CIO Adapter is compatible with channels built to either CIO Standard Version 1.5 or 2.0(draft).

Performance differences between these two standards should be solely due to the host SPU's channel implementation.

Feature differences are mainly the lack of parity protection on data and control on the 1.5 backplane. The adapter cannot determine backplane bus faults in this case.

#### SPECIFICATIONS

#### Supported Orders and Commands.

The A-link CIO Adapter supports the following commands and orders:

Commands [CSC, DSC, RSC, ETA]

Orders [CLC, WC, RD, WD, RS{,d}, IDY, RTS, WTC, DIS]

Details on support are found in the section on Firmware Description.

#### Transfer Rates.

For a typical block of data (=2048 bytes), the adapter is capable of an average transfer rate of 5 Megabytes.

The A-link adapter has an internal FIFO that may be active in either the input or output direction. The FIFO length is 128 bytes. Burst mode operation ( $n \le 128$  bytes) will equal 2 times the IOSB rate for the particular channel. Thus, for a 200 nanosecond IOSB a 10 Megabyte burst rate over 128 bytes is achieveable.

#### Logchannel Capabilities.

The adapter supports up to 64 connected logchannels. Each of these logchannels may optionally have a virtual circuit associated with it.

For a disc interface, this implies that a combination of 64 outstanding Read and Write requests are possible.

### **Configurable Options**

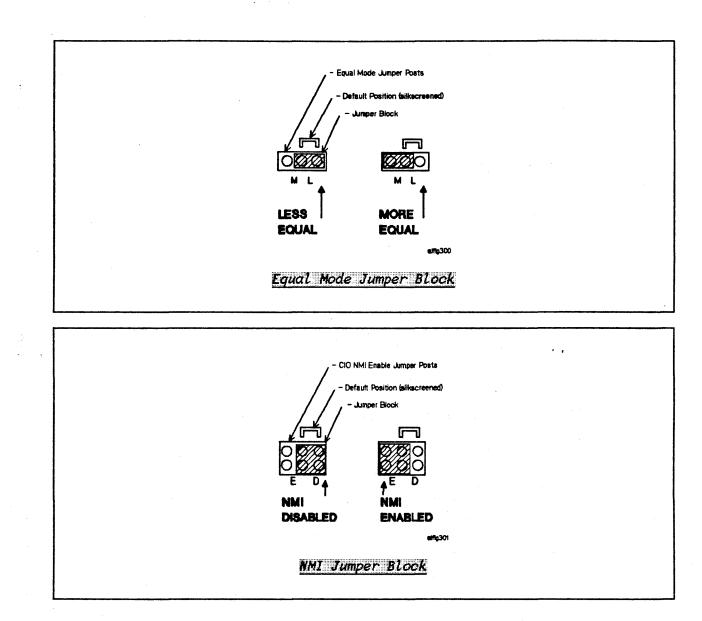

The A-Link CIO Adapter has three basic configurable options: Equal mode, Channel NMI, and Power Fail Support.

#### Equal mode.

Equal mode is a jumperable option that places the A-link card in either the LESS Equal or MORE Equal state.

This option is used to maintain deadlock avoidance with the remote device.

More Equal mode allows the card to proceed with a write operation to the link when all of its resources are ready (*i.e.*, data is available).

Less Equal mode prevents the card from proceeding with sending data onto the link until the remote device indicates that it is capable of proceeding.

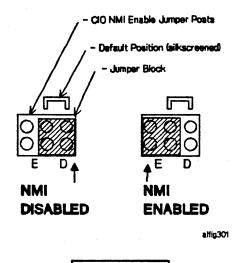

#### Channel NMI Enable.

Channel NMI Enable is a jumperable option that allows the card to drive the NMI line on the CIO backplane.

When Channel NMI Enable- is TRUE the card is capable of driving the NMI line.

When Channel NMI Enable- is FALSE the card cannot drive the NMI line.

The card can detect the state of the option and report that status to the host SPU through the channel.

#### Power Fail Support.

The A-link card provides optional power fail support by the secondary power available jumper. If a backplane supports secondary power and the associated channel signals, the card will enter a power down mode during a *Power Fail Warning* and will maintain its on card memory should Primary Power fail and Secondary Power remain.

Note that the state of the link will be lost during a Primary Power fail, and that pending transactions may need to be aborted.

Note that this circuitry will probably not be tested extensively since none of the current channels implement secondary power or power fail.

# **Status Indicators**

The A-Link card has two basic report mechanisms of card operational status: LED indicators, and Backplane Status Requests.

#### LED indicators.

The A-Link CIO Adapter has six LED indicators that are used to communicate two types of status: Operational Status during normal operations or a Self Test Failure Code (STFC)

The significance of the LED indicators is determined by the state of the Failed Self Test indicator as shown in the following tables.

### **SPECIFICATIONS**

. V.2

сź.

÷,

alinksti

| ID | COLOR | DEFINITION                                         | STATE | DESCRIPTION                                                                                                                                                                                         |

|----|-------|----------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F  | red   | Failed selftest                                    | on    | Card failed selftest.<br>The C,S, and R LED's indicate the<br>type of self test failure                                                                                                             |

|    |       |                                                    | off   | card passed self test                                                                                                                                                                               |

| С  | red   | Configuration error                                | on    | More equal jumper is in wrong<br>position<br>(F must be OFF)                                                                                                                                        |

|    |       |                                                    |       |                                                                                                                                                                                                     |

|    |       |                                                    | off   | Card is correctly configured (F must be OFF)                                                                                                                                                        |

| S  | red   | Signal not present<br>-OR-<br>unacceptable quality | on    | one or more of the following are<br>true:<br>No transitions detected on link<br>Phase lock receiver could not<br>acquire signal<br>Link error rate exceeds<br>maximum threshhold<br>(F must be OFF) |

|    |       |                                                    | off   | signal is of acceptable quality<br>(F must be OFF)                                                                                                                                                  |

| R  | red   | Remote not<br>responding                           | on    | Remote fails to respond to a periodic request for identification                                                                                                                                    |

|    | A.    |                                                    |       | (F must be OFF)                                                                                                                                                                                     |

|    |       |                                                    | off   | Remote has identified itself                                                                                                                                                                        |

|    |       |                                                    |       | (F must be OFF)                                                                                                                                                                                     |

# **SPECIFICATIONS**

| alinksti |  |

|----------|--|

|          |  |

|          |  |

| ID | COLOR | DEFINITION                            | STATE | DESCRIPTION                                                                                       |

|----|-------|---------------------------------------|-------|---------------------------------------------------------------------------------------------------|

| Р  | green | Passed self test,<br>card oPerational | on    | card has passed self test and is operational                                                      |

|    |       |                                       |       | (F must be OFF)                                                                                   |

|    |       |                                       | blink | Firmware awaiting for backplane<br>to issue an initial connect<br>subchannnel command             |

|    |       |                                       |       | (F must be OFF)                                                                                   |

|    |       |                                       | off   | Firmware detected a link Protocol<br>Error or determined that the pca<br>was no longer functional |

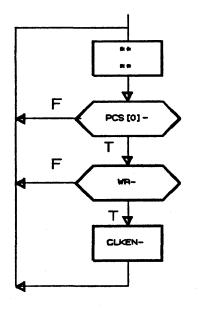

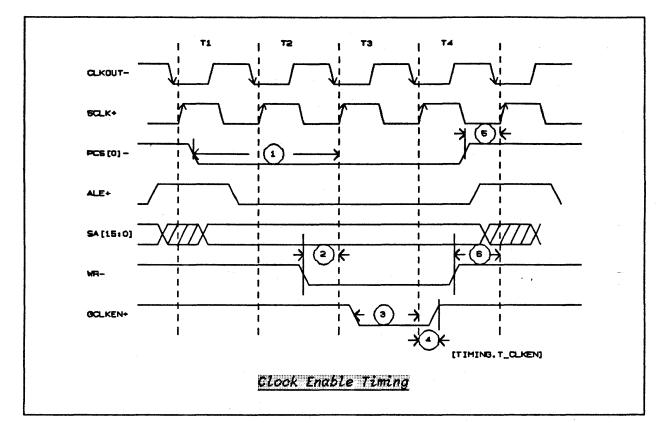

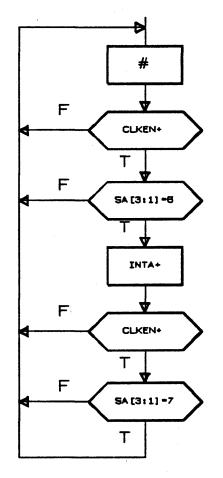

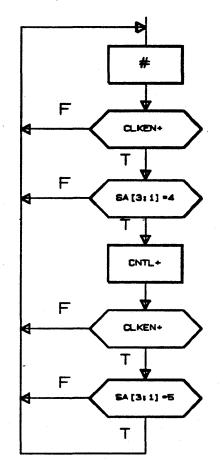

|    |       |                                       |       | (F must be OFF)                                                                                   |