# HEWLETT-PACKARD

## CONFIDENTIAL

# **DIO BUS SPECIFICATION**

## VERSION 1.0

APRIL 16, 1984

HP DRAWING NO: 5955-7669

DOCUMENT CONTROL

CHANGES TO THIS DOCUMENT SHOULD BE COORDINATED THROUGH THE RND R&D LAB.

DISTRIBUTION

THIS DOCUMENT IS DISTRIBUTED BY THE RND R&D LAB.

PRINTING HISTORY

First draft: December 14, 1982 Second draft: March 27, 1983

Version 1.0: April 16, 1984

Copyright © Hewlett-Packard Co. 1984

This material contains proprietary information protected by copyright laws. Any reproduction, photocopying or translation of any portion of this document to any foreign or computer language without the expressed written consent of Hewlett-Packard Company is forbidden.

## TABLE OF CONTENTS

| CHAPTER                         | 1 FOREWARD1                                                                                                                            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 2                       | 2 INTRODUCTION                                                                                                                         |

| 2.2<br>2.3                      | OBJECTIVES OF THE DIO BUS SPECIFICATION 2<br>PROCEDURE FOR RESOLVING CHANGES                                                           |

| CHAPTER 3                       | 3 DIO BUS BACKGROUND INFORMATION                                                                                                       |

| 3.2<br>3.3                      | SPECIFICATION TERMINOLOGY.5INTERFACE SYSTEM ELEMENTS.6BUS SUBSYSTEMS8BUS TIMING BACKGROUND.9                                           |

| CHAPTER )                       | I/O MEMORY MAP AND I/O CARD REGISTERS                                                                                                  |

| 4.2                             | SERIES 200 MEMORY MAP                                                                                                                  |

| CHAPTER 5                       | 5 DATA TRANSFERS                                                                                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6 | READ CYCLE                                                                                                                             |

| CHAPTER 6                       | 5 BUS ERROR AND STRETCH OPERATION                                                                                                      |

| 6.2<br>6.3<br>6.4<br>6.5        | BUS ERROR SIGNALS.37BERR TIMING.38BUS TIMEOUT.38AUTO LOCATE OF PROCESSOR RAM39BERR FOR PAGE FAULTING39GUIDELINES FOR UTILIZING BERR.40 |

## CHAPTER 7 INTERRUPT OPERATION

| 7.1 | INTERRUPT SIGNALS                  |   | • | • | • | • | • | • | 41 |

|-----|------------------------------------|---|---|---|---|---|---|---|----|

| 7.2 | EXTERNAL VECTORED INTERRUPT CYCLE. | • | • | • | • | • | • | • | 43 |

| 7.3 | AUTOVECTORED INTERRUPT CYCLE       | • | • | • | • | • | • | • | 45 |

#### CHAPTER 8 BUS ARBITRATION

| 8.1 | BUS ARBITRATION | SIGNALS. | • | • | • |   |   | • |   | • |   | • | • | • | 46 |

|-----|-----------------|----------|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 8.2 | BUS ARBITRATION | OVERVIEW |   | • | • |   |   |   | • |   |   |   | • |   | 47 |

| 8.3 | BUS ARBITRATION | SEQUENCE | • | • | • | • | • |   | • |   | • | • | • |   | 49 |

4.

.

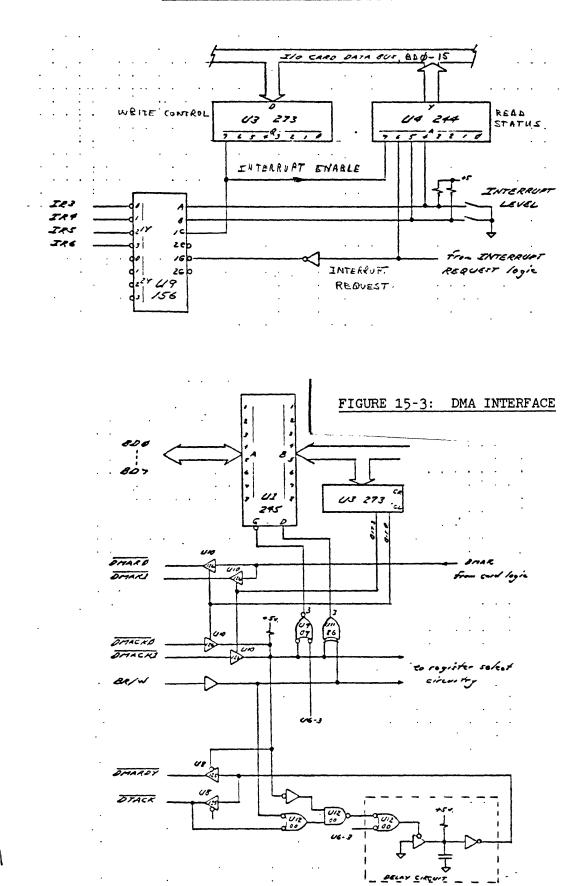

## CHAPTER 9 DMA OPERATION

| 9.1 | DMA  | SI  | GNAI | S.   | •   | •   | •  | •  | •  | •  | • | • | • | • |   | • | • | • | • | • | • | • | 52 |

|-----|------|-----|------|------|-----|-----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 9.2 | DMA  | OV  | ÆRV1 | EW.  | •   | •   | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • | • | • | • | 53 |

| 9.3 | 986: | 20  | DMA  | CON  | ITR | OL: | LE | R  | •  | •  | • | • | • | • |   | • | • | • | • | • | • | • | 54 |

| 9.4 | DMA  | OŬ  | TPUI | CZ 1 | CL  | Е   | •  | •  | •  | •  |   | • | • | • | • | • | • | • | • | • | • | • | 55 |

| 9.5 | DMA  | IN  | IPUT | CYC  | LE  | •   | •  | •  | •  | •  | • | • | • |   |   | • | • | • | • | • | • | • | 58 |

| 9.6 | DMA  | SF  | EED  | CON  | ISI | DEI | RA | TI | ON | S  | • | • | • | • | • | • | • | • | • | • | • | • | 61 |

| 9.7 | TERI | MIN | ATIN | IG I | MA  | T   | RA | NS | FE | RS | • | • | • | • |   | • | • | • | • | • | • | • | 62 |

## CHAPTER 10 DIO BUS UTILITIES

| 10.1 | BUS D | RIVE  | DISA  | BLE | ].  | •  | • | • | • |   | • | • |   | • | • | • |   | • | • | 63 |

|------|-------|-------|-------|-----|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 10.2 | RESET | OPEI  | RATIC | DN. | •   |    | • | • | • |   | • | • |   | • | • | • | • |   | • | 63 |

| 10.3 | HALT  | OPER  | ATION | Γ.  | •   | •  | • | • |   | • | • | • | • | • | • | • |   | • | • | 64 |

| 10.4 | FUNCT | ION ( | CODE  | SIC | INA | LS | • | • | • |   | • | • |   | • |   |   |   | • | • | 65 |

## CHAPTER 11 ELECTRICAL SPECIFICATIONS

| 11.1 | POWER DISTRIBUTION AND GROUNDING |   |   | • | • |   |   | • | • | 66 |

|------|----------------------------------|---|---|---|---|---|---|---|---|----|

|      | POWER SUPPLY TOLERANCES          |   |   |   |   |   |   |   |   | •  |

|      | I/O CARD CURRENT REQUIREMENTS    |   |   |   |   |   |   |   |   |    |

| 11.4 | ON-CARD FUSE SPECIFICATION       | • | • | • | • | • | • | • | • | 68 |

| 11.5 | SIGNAL LOADING                   | • | • | • | • | • | • |   | • | 69 |

#### DIO BUS SPECIFICATION

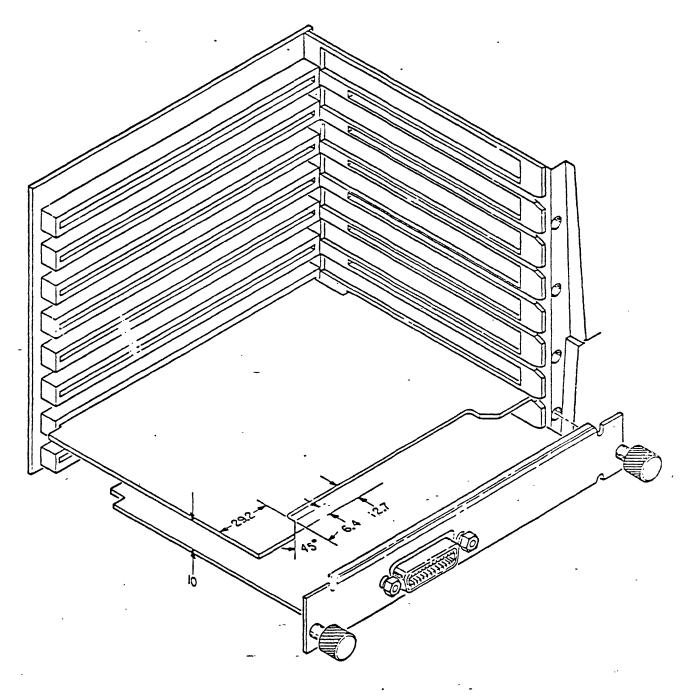

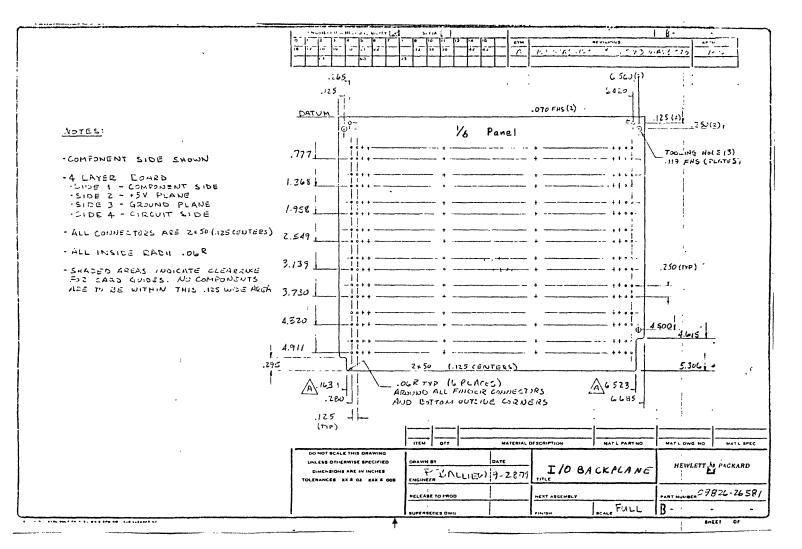

CHAPTER 12 MECHANICAL SPECIFICATIONS

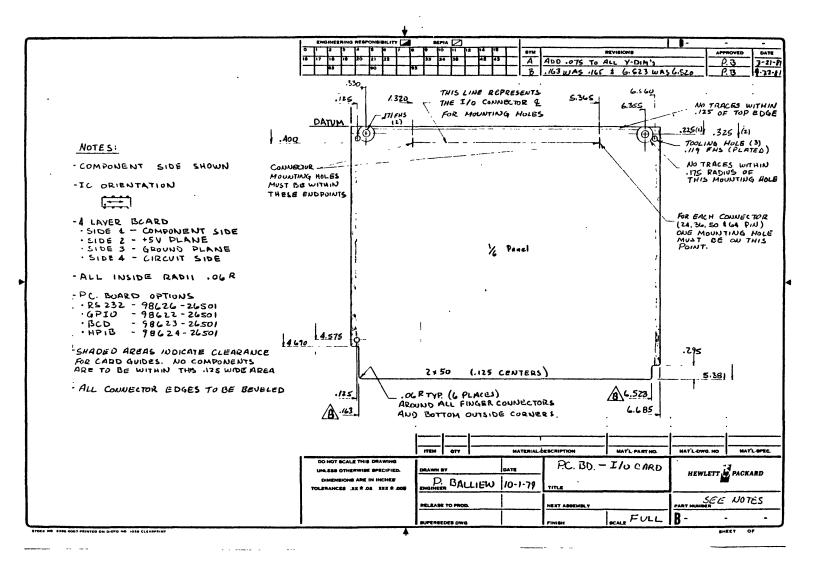

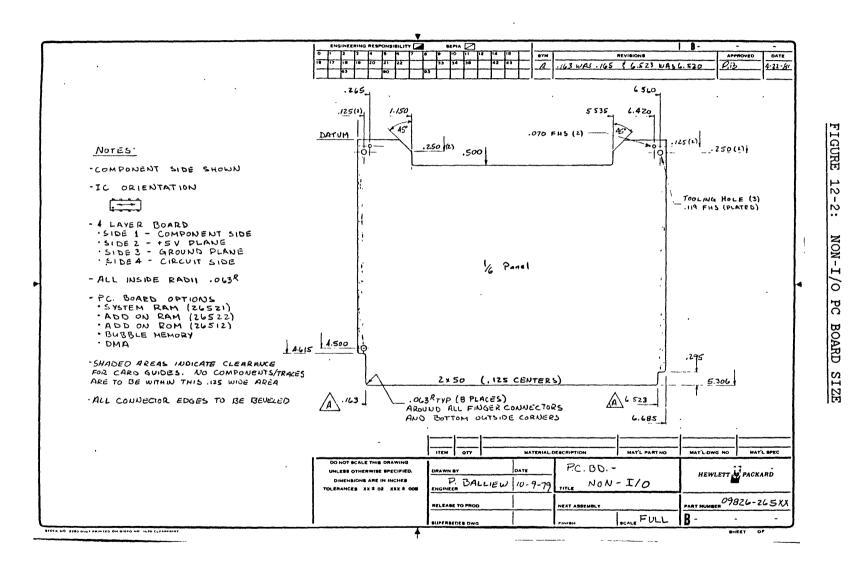

| 12.1 | DIO BUS CARD SPECIFICATIONS. | • |   | • |   | • | • |   |   |   |   | 70 |

|------|------------------------------|---|---|---|---|---|---|---|---|---|---|----|

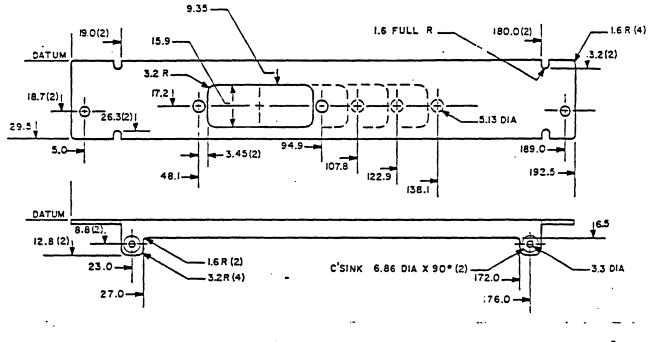

| 12.2 | CARDCAGE SPECIFICATIONS      | • | • | • | • | • | • | • |   | • | • | 74 |

|      | MINIMIZING EMI               |   |   |   |   |   |   |   |   |   |   |    |

| 12.4 | PC CARD LAYOUT RULES         | • |   | • | • | • | • | • | • | • | • | 77 |

| 12.5 | DIO BUS PINOUTS              | • | • | • | • | • | • | • | • | • | • | 78 |

CHAPTER 13 OPERATION IN THE 9888A BUS EXPANDER

| 13.1 | FEATURES C | F THE  | BUS E  | XPAN | DER | • • | • • |      | ٠   | •  | • | • | • | 80 |

|------|------------|--------|--------|------|-----|-----|-----|------|-----|----|---|---|---|----|

| 13.2 | OPERATING  | LIMITA | ATIONS | IN   | THE | BUS | EXI | PANI | DEF | ₹. | • | • | • | 81 |

CHAPTER 14 SYSTEM AND BUS MASTER DESIGN GUIDELINES. . . 83

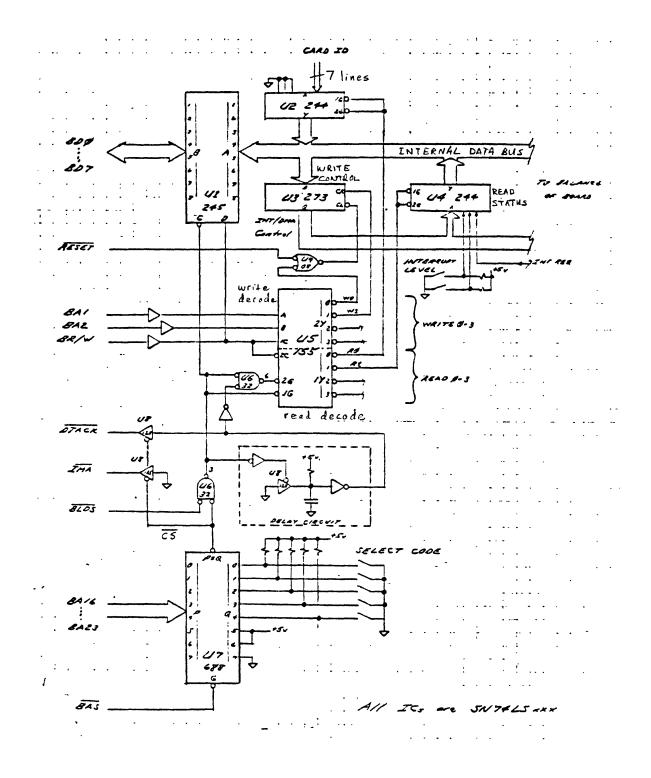

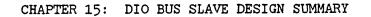

## CHAPTER 15 DIO BUS SLAVE DESIGN SUMMARY

| 15.1 | EXTERNAL | I/0 | CARD | DESIGN | GUIDELINES. |   | • | • |   | • | • | 84 |

|------|----------|-----|------|--------|-------------|---|---|---|---|---|---|----|

| 15.2 | EXTERNAL | I/0 | CARD | DESIGN | EXAMPLE     | • | • |   | • | • | • | 86 |

CHAPTER 16 REQUIRED DIO BUS FUNCTIONS FOR AN I/O BUS

| 16.1 | SIGNALS | NOT SUPPORTED | ON A DIO-BASED 1 | <b>I/O</b> 3 | BUS | • | • 9 | 91 |

|------|---------|---------------|------------------|--------------|-----|---|-----|----|

| 16.2 | SIGNALS | REQUIRED ON A | DIO-BASED I/O BU | US.          | • • | • | • 9 | 93 |

#### CHAPTER 17 I/O CARD QUALIFICATION

| 17.1 | SOFTWARE QUAL | IFICATIO | Ν. | • |   | • | • | • | • | • | • | • |   | • | • | 94 |

|------|---------------|----------|----|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 17.2 | HARDWARE QUAI | IFICATIO | Ν. | • | • | • | • | • | • | • | • | • | • | • | • | 94 |

| 17.3 | SAFETY COMPLE | ANCE     | •  | • | • | • | • | • | • | • | • | • | • | • | • | 96 |

|          |   |         |   | - d |

|----------|---|---------|---|-----|

| FOREWARD | 1 | CHAPTER | 1 |     |

|          |   |         |   |     |

This standard is the result of a cooperative effort involving engineers at FSD, RND, CSY and DSD during the period from November 1982 to the present. The following people have contributed to this document; their assistance and the assistance of others is greatly appreciated:

FSD: Doug Buhler John Byrnes Steve Chorak Greg Herman Bill Hirth Greg Lawson Nick Mati Tim Mikkelsen Shaw Moldauer Jon Rubinstein Martin Speer Dan Swanson Tom Thrasher Keith Weeks Jerry Wick Steve Wolf

- RND: Vince Cavanna Steve Haddock

- CSY: Paul Zimmer

DSD: Tom Szolyga

In addition, the assistance of our managers is acknowledged:

FSD: Ken Watts

RND: Doug Boliere

Again, thank you for your cooperation and assistance.

Dave Sweetser, FSD

#### 2.1 OBJECTIVES OF THE DIO BUS SPECIFICATION

The DIO (Desktop computer I/O) BUS was first introduced in 1981 with FSD's 9826A computer along with several I/O cards. Since then, several other DIO BUS mainframes and I/O cards have been introduced. Because several divisions will be designing or using hardware based on the DIO BUS, a decision was made to document the DIO BUS as an HP standard. The objectives of this effort are two-fold:

- 1. The primary objective is to provide sufficient information to design a DIO BUS slave device, such as an I/O card. However, while the DIO BUS is the system bus for several mainframes, future products may utilize the DIO BUS solely as an I/O bus. A DIO-based I/O bus does not require all of the functions presently defined by the DIO BUS. Therefore, the Chapter REQUIRED DIO BUS FUNCTIONS FOR AN I/O BUS lists those signals which would not supported on a DIO-based I/O bus. I/O card designers must adhere to the limitations specified in this chapter.

- 2. A secondary objective is to support the design of Bus Masters. While Bus Master design is not covered explicitly, the DIO BUS specifications must be followed by Bus Master designers to guarantee that Bus Slave timing requirements are met. Additional Bus Master guidelines are available in the document SERIES 200 SYSTEM SPECIFICATION, available from the FSD Hardware R&D Lab. The purpose of that document is to support Series 200 system design activities.

#### CHAPTER 2: INTRODUCTION

#### 2.2 PROCEDURE FOR RESOLVING CHANGES

The specifications provided in this document must be followed. In certain cases, however, a designer may not be able to comply with one or more specifications. In such a case, the designer must either: (1) seek to change the specification or (2) obtain approval for area(s) of non-compliance.

Changes to this document require a consensus from FSD, RND and any other division currently using the DIO BUS. Change requests will be coordinated through the RND R&D Lab, with RND reviewing all change requests relative to their necessity and implementation. If an agreement is reached between RND and the requesting division, RND will submit in writing the proposed change to FSD and other using divisions for their concurrence. If all divisions concur, the change will be made. If concurrence is lacking, the change will not be made and the requesting division has the option of pursuing the change through management channels.

In a similar manner, a designer that finds it necessary to violate a specification should notify RND R&D of his intent. RND, if unable to find a solution, will notify all affected divisions in writing of the proposed violation. Each division must respond in writing, either agreeing to the non-compliance or disagreeing. In the case of a disagreement, an effort will be made to resolve it at the lowest possible level; if this is not possible, successive levels of management will become involved as necessary.

#### 2.3 WHAT IS NOT COVERED IN THIS DOCUMENT

The following information is not contained within this document:

- As stated above, Bus Master design is not covered in this document. Refer to the SERIES 200 SYSTEM SPECIFICATION available from the FSD Hardware R&D Lab for information on Bus Master design and other system design issues.

- 2. Previous releases of this document contained a card ID Table and a card SELECT CODE Table. However, because of the changing nature of this information, the ID and SELECT CODE Tables have been removed from this document; they can be obtained from the RND R&D Lab. Designers should obtain ID and SELECT CODE assignments from RND before beginning a new design.

3. Several of the DIO BUS timing and electrical specifications were derived from characteristics of the 74LS244 and 74LS245 drivers. Characterization of other logic families (e.g. ALS), however, has not been done. This is an area requiring future work.

#### 2.4 RECOMMENDED DESIGN METHODOLOGY

Listed below is a recommended methodology for designing a card for the DIO BUS.

- 1. Prior to beginning a project, the designer should contact RND to obtain ID and SELECT CODE assignments as well as to ensure that he has the latest version of this specification.

- 2. Designers should review the design of existing DIO BUS products. The products listed in the separately-available ID and SELECT CODE Tables provide a good reference of existing DIO BUS products. The divisions with ER for these products can be contacted for more information, i.e. the schematic, theory of operation, etc. Designers should also reference the SERIES 200 SYSTEM SPECIFICATION available from the FSD Hardware R&D Lab.

- 3. An alternative that may expedite I/O card development is the 98630A breadboard interface card available from FSD. This card contains the essential circuitry to support data transfers, interrupt requests and DMA operation and provides approximately 15 square inches for breadboarding.

- 4. Even though a designer follows this document rigorously, testing of the product in its intended environments is ABSOLUTELY ESSENTIAL. The Chapter I/O CARD QUALIFICATION gives guidelines for this testing.

- 5. One of the keys to ensuring timely completion of a product is successful interdivisional cooperation. Marketing plans, product data sheets, hardware ERS's, software specifications, etc. should be prepared by the designing division(s) and distributed to those who are involved with the development, manufacturing and marketing of these products or their host systems.

This chapter provides basic background information on the DIO BUS, including terminology, a description of bus interface elements and timing information.

#### 3.1 SPECIFICATION TERMINOLOGY

The following terminology is used throughout this document:

1. Active low signals are denoted with a \* following the name. This is equivalent to a bar over the signal name which is often used for active low signals. Thus, the following are equivalent:

$BAS^* = \overline{BAS}$

- 2. When a signal is referenced as 'asserted', 'true', 'false', etc., it is relative to the signal FUNCTION. For example, to say that BAS is asserted means the Buffered Address Strobe is active, i.e. performing its function of strobing the address. Whether it exists as BAS or BAS\* on the backplane is irrelevant.

- 3. References to 'high' and 'low' refer directly to TTL voltage levels. When referring to high and low signals, the actual name of the signal is used. For example, when the signal BAS\* is described as being low, the signal entitled BAS\* has a TTL logic low level. The TTL levels are defined as follows:

HIGH >= 2.0V

LOW <= .8V

- 4. The composite signal BR/W is denoted as BR/W\*. BR/W\* high indicates a read operation; BR/W\* low indicates a write operation.

- 5. The definition of 'byte' is agreed upon by all -- 8 bits. A 'word' is defined to be 16 bits. The least significant bit of a byte or word is defined as Bit 0.

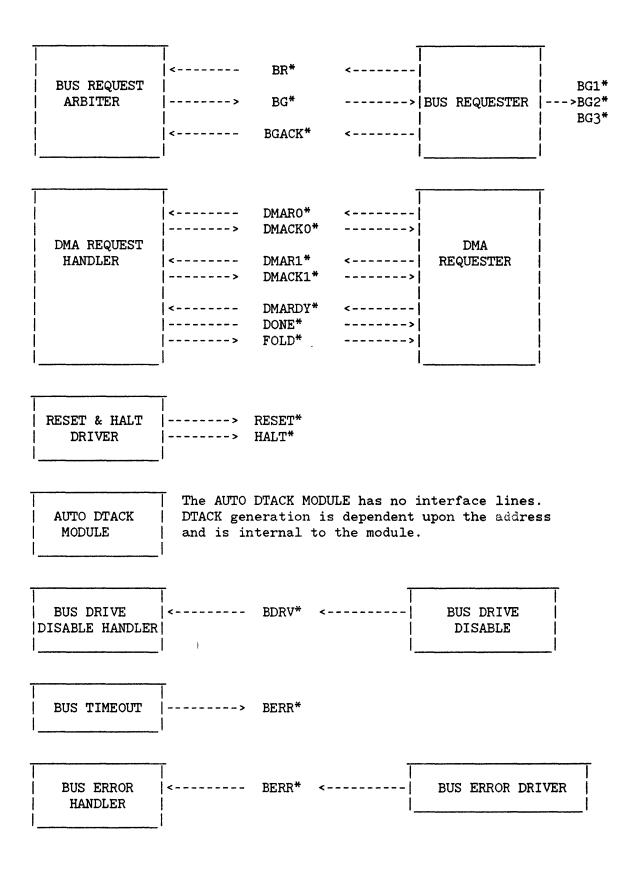

## 3.2 INTERFACE SYSTEM ELEMENTS

$\sim$

The functional modules of the DIO BUS are shown below. Where signals go specifically from one functional module to another functional module, the two modules are shown side-by-side for clarity. Modules that drive many other modules (e.g. RESET) are shown as stand-alone.

|        | >  | BA1 - BA23  | >  |       |

|--------|----|-------------|----|-------|

|        | <> | BDO - BD15  | <> |       |

| BUS    | >  | BAS*        | >  | BUS   |

|        | <  | IMA*        | <  |       |

| MASTER | >  | BR/W*       | >  | SLAVE |

|        |    | •           |    |       |

| 1      | >  | BLDS*       | >  | ,     |

|        | >  | BUDS*       | >  |       |

|        | >  | ENDT*       | >  | <br>  |

|        | <  | DTACK*      | <  |       |

|        | >  | BFCO - BFCI | L> |       |

|        |    |             |    |       |

| INTERRUPT | _<br>  <       | IR1* - IR7*          | <> |                        |

|-----------|----------------|----------------------|----|------------------------|

| REQUEST   | >              |                      | >  | INTERRUPT<br>REQUESTER |

|           | <br>  <<br>  < | VECTOR*<br>BD0 - BD7 | <  |                        |

|           |                |                      |    |                        |

6

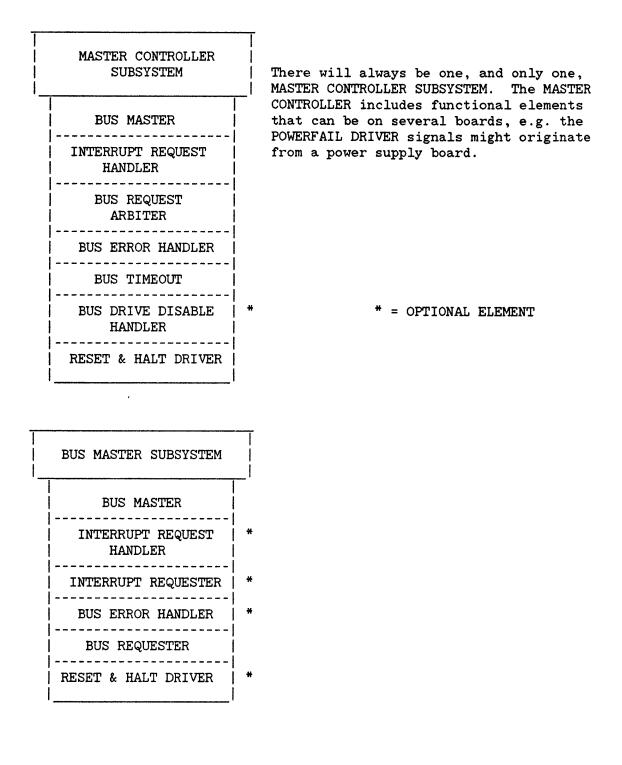

#### 3.3 BUS SUBSYSTEMS

Bus subsystems that are defined are shown below:

#### 3.4 BUS TIMING BACKGROUND

Before discussing DIO BUS timing, it should be pointed out that in most mainframes (e.g. the 9836A), all slots are identical. There is no ordering or prioritizing of address, interrupt capability, etc. by location in the backplane. All timing specifications apply equally to all slots. It is possible, however, that future mainframes may have slot-dependent features (e.g. interrupt prioritizing). Thus, designers must be aware of features of each mainframe that their products will operate in.

Note also that timing specifications for the DIO BUS were developed using the 8 Mhz 68000. Designs incorporating other processors must ensure that the DIO BUS specifications are met.

The DIO BUS is ASYNCHRONOUS; that is, there is no clock on the backplane to reference signals to. While address and data generation are related to the CPU clock, the actual clock does not appear on the bus. The presence of address or data is indicated by various control lines which execute interlocked handshakes to convey address and data. Because the address, data and control lines are not referenced to a clock on the backplane, signal skew must be controlled to maintain the relative timing between these signals. For example, the 68000 is guaranteed to drive the address bus lines 30 nsec prior to asserting Address Strobe. Most receiving devices require at least 15 nsec of address setup time prior to Address Strobe. To guarantee 15 nsec of address setup time, the following rules were developed to control gate delays and bus loading (these are expanded on in more detail in later chapters).

- 1. Each board is limited to one LS load on the address bus, data bus, the address strobe, the data strobes and the read/write signal.

- 2. The PC board trace length on bus signals should be as short as possible and, in any case, must not exceed 3 inches.

- 3. The SN74LS245 (or equivalent SN74LS244) is used to drive the above signals.

- NOTE: IN SOME CASES, EXISTING DEVICES VIOLATE THESE RULES; HOWEVER, NEW DESIGNS MUST ADHERE TO THESE RULES.

At this point, a historical perspective is worthwhile to show how the above guidelines originated. During the early development of the 9826, it became clear that controlling bus capacitance was essential, hence Rules 1 and 2 above. Also, to minimize bus skew, it was decided to specify a 'standard' bus driver, hence Rule 3. Next, to develop detailed timing specifications, further analysis was performed on the 74LS245.

To define bus skew, two efforts were made: (1) model the 74LS245 and determine formulas for worst-case minimum and maximum gate delays as a function of bus capacitance and (2) measure delays for a number of 74LS245 parts with different date codes. The formulas for gate delay, if used with worst-case conditions (fully loaded bus, fast address strobe driver, slow bus driver, etc.), yield unworkable numbers (negative setup times). It was felt that such a worst-case scenario is a low probability and not the appropriate design center. Therefore, effort 2 (measuring delays) was investigated.

#### CHAPTER 3: DIO BUS BACKGROUND INFORMATION

Using a sample of 74LS245 parts with different date codes, the worst-case difference in gate delays was measured for a 500 pf load. The difference between the fastest gate and the slowest gate (in different packages) was 9.5 nsec. This was derated by 50% to 15 nsec for margin as well as to cover skew on the bus itself caused by different signal loading. Returning to the 68000 example, if the address precedes the address strobe by 30 nsec at the 68000 output, then (using 74LS245's to drive the bus) all receiving devices are guaranteed to have 15 nsec (30 -15) of address setup time prior to the address strobe.

In addition to determining bus skew, the worst-case high-to-low and low-to-high delay times were determined for a 74LS245 driving a 500 pf load. Delay times were measured relative to the output reaching the nominal device threshold. For example, experimental and published data indicates that 1.7V is sufficient to be seen as a high for the 74LS245; hence, the low-to-high time delay measurement concluded when the output reached 1.7V. The results, which are shown below, have been used in calculating several timing specs. Drivers for signals such as DTACK\* (which has a pullup resistor) require approximately 50 ns to drive the bus from high to low. Likewise, a buffer without a pullup has approximately 40 ns of delay (e.g. the DMA Controller's Fold Buffer). These times include propagation delays.

> WITH PULL UP RESISTOR: 47.5 ns high to low (1 kohm) 37.5 ns low to high WITHOUT PULL UP RESISTOR: 39.5 ns high to low 39.5 ns low to high

Data was not taken for pull up resistors larger than 1 kohm. However, larger pullups will 'group' the rise and fall times closer to the non-pull up rise and fall times.

The original DESIGNER'S GUIDE TO THE 9826 CARDCAGE had several timing diagrams labeled 'Bus Master'. These diagrams were basically the timing of the 68000 and did not represent DIO BUS signals. Such diagrams are not included in this document.

11

In summary, the following points can be made:

- The skews due to the bus drivers and the bus itself are not specified separately. Instead, a 'lumped' skew specification of 15 ns is provided. Between any two signals driven by 74LS245 drivers, 15 ns of skew can develop between their inputs and outputs, where the outputs are measured at the receiving device on the bus.

- 2. In many cases, the DIO BUS timing specifications have been derived using the minimum or maximum 68000 timing specifications plus or minus the 15 ns skew, whichever is appropriate.

- 3. The guideline does not take into account signals driven by devices other than the 74LS245. Such guidelines may be added by RND in a future release of this document.

The terms CYCLE and STATE need to be explained as these terms are sometimes used erroneously. CYCLE refers to a <u>complete</u> clock cycle, e.g. 125 ns for an 8 Mhz clock. STATE refers to <u>one half</u> of a clock cycle and is based on Motorola's nomenclature; STATES are numbered from S0 to S7, representing 8 states, or 4 cycles. In a bus transaction, the 68000 inserts wait states between states S4 and S5 as necessary. An example of erroneous usage of these terms is in reference to RAM access times: it is often referred to as a 5-state access when the correct description is a 5-cycle access.

| I/0 | MEMORY | MAP | AND | I/0 | CARD | REGISTERS |  |

|-----|--------|-----|-----|-----|------|-----------|--|

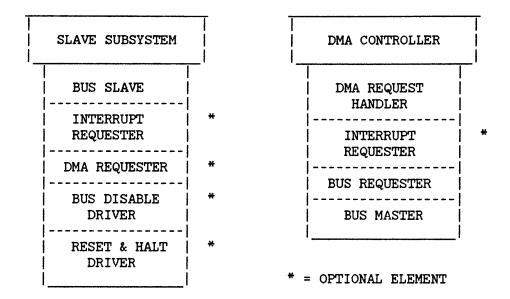

## 4.1 SERIES 200 MEMORY MAP

The DIO BUS SPECIFICATION is not intended to document in detail the Series 200 memory map. Instead, memory map documentation is limited to the External I/O memory map. For reference only, the Series 200 Memory Map is shown below.

This Series 200 memory map is shown above; addresses are in HEX. The 68000's 24 bit address can address 16 Mbytes of memory. The External I/O occupies 2 Mbytes (600000 - 7FFFFF). The Internal I/O address space (400000 - 5FFFFF) is used for internal peripherals (e.g. the graphics board) and is discussed in detail in Appendix A.

#### 4.2 EXTERNAL I/O MEMORY MAP

The External I/O address space is divided into 32 segments of 64 kbytes each. The I/O cards contain Select Code switches which determine the physical address of the card in the External I/O address space. 5 switches permit the user to set 32 Select Codes, from 0-31, to determine which 64 Kbyte memory space the card resides in. The address format is shown below:

#### 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

| 1                  | 1 1 1 1 1<br><br>0 0 0 0 0 | & Device Memory |

|--------------------|----------------------------|-----------------|

| Ext. I/O<br>Select | Select Code 0-3            | 1               |

Not all External I/O Select Codes can be used with existing operating systems. For example, Select Code 7 is assigned by all operating systems to the internal HP-IB interface which resides in the Internal I/O address space. If an I/O card is installed with Select Code 7, the operating system will ignore it and direct Select Code 7 activity to the internal HP-IB interface operating in the Internal I/O space.

With Pascal and BASIC, all Select Codes from 0-7 reference internal I/O devices only. It is important to realize that, ELECTRICALLY speaking, I/O cards can be set to Select Codes 0-7 but that the OPERATING SYSTEMS map Select Codes 0-7 to addresses in the Internal I/O space. Thus, with BASIC and Pascal, I/O cards set from 0-7 are inaccessible; only I/O cards set from 8-31 can be accessed. At the assembly language level, however, I/O cards with Select Codes over the entire range of 0-31 can be accessed. HPL permits setting of I/O cards to Select Codes 1-6 and 8-15; refer to HPL OPERATING MANUAL AND PROGRAMMING UPDATE FOR THE HP 9826 AND 9836 COMPUTERS, 09826-90040, for more information.

#### 4.3 I/O CARD REGISTERS

The function of certain registers within I/O devices are pre-assigned. Note that because I/O cards are byte-oriented and these registers are connected to the lower byte of the data bus, their system addresses are 1, 3, 5... relative to the card's base address. The designer is free to implement registers in addition to (not in lieu of) the ones listed below. Also, the designer is not required to uniquely map each register within the card's I/O space, i.e. registers may be multipli-mapped (which simplifies address decoding) as long as registers do not 'exist outside' the card's 64 kbyte I/O space (unless the card is specifically designed to occupy multiple 64K chunks).

| ADDRESS 1   | 7          | 6 | 5              | 4          | 3     | 2 | 1     | 0 |

|-------------|------------|---|----------------|------------|-------|---|-------|---|

| READ ID     | <br>  R/L* |   | NDARY<br>  ID0 | PRIMARY ID |       |   |       |   |

| WRITE RESET | x          | x | x              | x          | x<br> | x | x<br> | x |

The defined I/O registers are:

Good system design requires that the operating system must be capable of resetting an I/O card to its power-on state. One of two methods must be implemented:

- 1. If the card contains LSI circuitry such as an interface controller chip, a sequence of commands can be defined to reset the interface controller to its power-on state.

- 2. If the card does not have such a sequence, the card must be capable of being reset to its power-on state via a memory write cycle to address 1 as shown above. The data written is 80 hex (this can be ignored to simplify the design).

R/L\* - REMOTE/LOCAL\*: A 1 indicates that the mainframe may be controlled from a remote source via this I/O card. For example, under software control, a mainframe may receive its keyboard inputs from an RS-232 card and likewise output its display data via the card. This has uses in certain environments where it is desireable to lock out local access and provide remote control of the mainframe.

This feature has not been used to date (except for the 98628 card, where the card's firmware monitors this bit). In future data communications cards (e.g. a terminal multiplexer card, Ethernet, etc.), it is recommended that this function be provided, either via a jumper or a switch. Non-communications oriented cards (e.g. an A/D card) should set this bit to 0. NOTE: Except in rare cases, software is lacking to use this feature; if the remote feature is to be used, software development is required.

PRIMARY ID - Bits 0-4 contain the PRIMARY ID, which identifies each device. Because 5 bits can only define 32 unique devices, Bits 5 & 6 are defined as Secondary ID bits as discussed below.

Whereas the Select Code bits are switch-selectable, the ID bits must be hardwired. Designers should obtain their ID assignment from RND. If possible, the ID and default Select Code should be the same.

SECONDARY ID0,1 -- The 2 SECONDARY ID bits are used to provide 4 additional IDs for each PRIMARY ID. Although these bits are located in a higher order position than the PRIMARY ID bits, they should be consider lower order in that they are used to extend the range of each of the PRIMARY ID's defined in Bits 0-4.

Initially, only bits 0-4 defined the device ID; software typically masked off the upper 3 bits and examined the lower 5 bits. However, because future Internal I/O devices as well as I/O cards will have IDs, it became necessary to increase the number of IDs. Accordingly, Bits 5 and 6 have been defined as the SECONDARY ID bits. Formerly these bits were S (Smart Card Identifier) and R (Reserved), respectively.

#### CHAPTER 4: I/O MEMORY MAP AND I/O CARD REGISTERS

Unfortunately, not all 128 IDs (7 bits) are available. This is because, as stated above, existing software only looks at the lower 5 bits. For example, the 98625 Disc Interface card uses ID 8. If another external I/O card wanted to use this same PRIMARY ID with a different SECONDARY ID, problems will result. This is because the SECONDARY ID bits may be ignored, causing the card to be interpreted as the 98625. However, this same PRIMARY ID can be used (with a different SECONDARY ID) by an INTERNAL I/O device in a new mainframe since the operating system will look at all 7 bits. Therefore, certain existing PRIMARY IDs are used by new Internal I/O devices where the functions are the same or similar.

To be completely safe, additional IDs can be defined using Register 5, the EXTENSION ID REGISTER. If the PRIMARY ID is 0 (SECONDARY ID = don't care), then the device ID is defined by the EXTENSION ID in Register 5. Register 5 contains the EXTENSION ID only if the PRIMARY ID is 0.

As with the Select Code table, the ID Assignment Table has been removed from this document and is available from the R&D Lab at Roseville Network Division.

| ADDRESS 3     | 7            | 6  | 5            | 4            | 3 | 2 | 1   | 0   |

|---------------|--------------|----|--------------|--------------|---|---|-----|-----|

| READ STATUS   | <br>  IE<br> | IR | INTEI<br>LEV | RRUPT<br>VEL | x | x | DE1 | DEO |

| WRITE CONTROL | IE           | x  | x            | x            | x | x | DE1 | DEO |

x - These bits are not defined and may be assigned functions by the card designer.

IE - Interrupt Request Enabled, set or cleared by a Write Control, is read by a Read Status. IE is cleared by both a bus reset (RESET\* = low) and a card reset (write to Register 1).

17

CHAPTER 4: I/O MEMORY MAP AND I/O CARD REGISTERS

- IR Card is requesting interrupt, used for software polling to determine interrupt origin. If IR is true and IE is set, one of the DIO BUS interrupt lines (IR3\*, IR4\*, IR5\* or IR6\*) is asserted, depending on the Interrupt Level switches. A software-accessible means of clearing IR must be provided on the card. IR should NOT be cleared by a read of this register.

- INTERRUPT LEVEL These bits permit reading of the interrupt level as shown below:

00 Interrupt Level 3 01 Interrupt Level 4 10 Interrupt Level 5 11 Interrupt Level 6

Current I/O cards have 2 switches to set the interrupt level; these switches map into the 2 INTERRUPT LEVEL bits. Alternately, a card could permit the interrupt level to be programmable (e.g. using the corresponding bits in the writeable CONTROL REGISTER). Refer to the Chapter DIO BUS SLAVE DESIGN SUMMARY for more details on interrupt levels.

DEO, DE1 - DMA Enabled on Channel 0, DMA Enabled on Channel 1, set or cleared by a Write Control, read by a Read Status. If the card does not implement DMA, these bits can be used for other functions in both the Control and Status Registers. DE0 and DE1 are cleared by both a bus reset (RESET\* = low) and a card reset (write to Register 1).

| ADDRESS 5      |         | 7 | 6 | 5    | 4      | 3     | 2     | 1 | 0 |

|----------------|---------|---|---|------|--------|-------|-------|---|---|

| READ EXTENSION | ]<br>ID |   |   | EXTI | ENSION | ID (0 | - 255 | ) |   |

The EXTENSION ID register is valid only if the PRIMARY ID in Register 1 is 0.

18

This chapter discusses the transfer of data between Bus Masters and Bus Slaves. Timing background information is given in Chapter 3 and should be reviewed prior to reading this chapter.

#### 5.1 DATA TRANSFER SIGNALS

The bus signals used in data transfers are shown below. Signal names starting with B (buffered) are derived from 68000 signal names -- the 68000 name is that which follows the B. A brief description of each signal is given; for more detailed information, refer to the 68000 data sheet. Two of the signals, IMA and ENDT, are HP-defined.

- 1. BA1-BA23 The 23 bit address bus. Note that BA0 is not on the bus; its value is conveyed in BUDS and BLDS.

- 2. BAS\* BUFFERED ADDRESS STROBE, defines when the address is valid, used to delimit bus cycle.

- 3. BD0-BD15 BUFFERED DATA 0 15, the 16 bit data bus.

- 4. BR/W\* BUFFERED READ/WRITE, high for read, low for write.

- 5. BUDS\* BUFFERED UPPER DATA STROBE, BUFFERED LOWER

BLDS\* DATA STROBE and BUFFER DATA STROBE. BUDS

BDS\* indicates that BD8-BD15 are involved; BLDS indicates that BD0-BD7 are involved. BDS is

NOT a bus signal and is used generically to refer to either BLDS or BUDS.

- 6. DTACK\* DATA TRANSFER ACKNOWLEDGE is issued by the Bus Slave (RAM, I/O card, etc.) to inform the CPU that it can complete the memory cycle. During a read, it indicates that the Bus Slave's data is valid on the bus. During a write operation, it indicates that the Bus Slave has accepted the data.

- 7. IMA\* I'M ADDRESSED, an output from a card that is addressed. This is used by the Bus Expander to reverse its data bus buffers if a card in the Bus Expander is addressed. All DIO cards must generate IMA, including DMA Controllers when registers are read (the 98620 DMA Controller does not generate IMA, which has complicated system design).

- 8. ENDT\* ENABLE DTACK, generated by Processor boards, used by Bus Slaves to control generation of DTACK. Permits a pseudo-synchronous, repeatable access time equivalent to 5 clock cycles.

- 9. BFC0-BFC2 BUFFERED FUNCTION CODES, defines type of transaction occurring on the bus.

#### 5.2 OVERVIEW OF THE DATA TRANSFER

BAS, which defines when the bus address BA1-BA23 is valid, begins the data transfer operation.  $3R/W^*$  defines whether the operation is a read or a write. BLDS and BUDS indicate which byte(s) of the 16 bit data bus are involved in the data transfer.

An interlocked handshake is used to transfer data between the Bus Master and the Bus Slave. DTACK (Data Transfer Acknowledge) is the signal that indicates when the Bus Slave has accepted data from the bus or provided data to the bus. The data handshake occurs as follows:

- 1. Bus Master asserts BA1-BA23, BAS, BR/W, BUDS, BLDS and the data bus BD0-BD15 (if a write operation).

- 2. Bus Slave asserts DTACK when data accepted from bus or provided to bus.

- 3. Bus Master negates BAS when DTACK seen (cycle complete).

- 4. Bus Slave negates DTACK when BAS negated.

#### CHAPTER 5: DATA TRANSFERS

DTACK is needed because the response time of devices can vary. For example, the access time of RAM can vary due to refresh. However, other devices, such as the ROM card, are guaranteed to respond to accesses in a fixed time. To simplify design for those devices that respond in a fixed time, certain Processor Boards implement a feature called AUTO DTACK in which the DTACK signal is generated on the Processor Board itself. Processor Boards generate DTACK based on the device address; DTACK is generated for all devices in the address range 0-4FFFFF. This covers ROM cards and devices in the Internal I/O space 400000-4FFFFF. The actual BAS-to-AUTO DTACK timing depends on address bits A14 and A15. Refer to the SERIES 200 SYSTEM SPECIFICATION available from FSD Hardware R&D Lab for more details.

The DIO SPEC permits DTACK\* to be driven either by a tri-state buffer or an open collector gate. Assuming a 500 pf bus and a 3.3K pullup resistor (as used on the 09826-66515 CPU board) on DTACK\*, an RC time constant of 1.6 usec results. Because this would result in an unacceptably slow rise time on DTACK\*, Bus Masters actively pull up DTACK\* after a cycle when BAS\* goes high. Likewise, Bus Slaves release DTACK\* when BAS\* goes high but with some inherent delay relative to the active pullup.

This contention (Bus Master pulling DTACK\* high, Bus Slave momentarily holding it low) has been observed to cause glitches on DTACK\*. This contention problem has been fixed in new processor designs (e.g. by using a delay line to delay the active pullup). However, because of the many machines in the field which could have DTACK\* glitches, DTACK\* should not be used as a clock (at least not on the rising edge).

Another signal related to DTACK is ENDT (Enable DTACK). ENDT is generated by the Bus Master and may be used to improve the response time of Bus Slaves. On 68000-based Bus Masters, ENDT is basically Address Strobe delayed by 1-1/2 clock cycles. Bus Slaves can optionally use ENDT to generate an 'early' DTACK, permitting 5 cycle read/write accesses. ENDT is discussed in detail in Sections 5.6, 5.7 and 5.8.

21

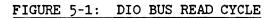

#### 5.3 READ CYCLE

Figure 5-1 depicts a read cycle. As discussed in Chapter 3, timing requirements are specified on the bus measured at the signal receiver. The key aspects of a read cycle are:

- Prior to the beginning of the read cycle, BR/W\*, BUDS\* and BLDS\* are set high by the CPU. A pullup device on the Processor Board actively pulls up DTACK\*. The setup time on BR/W\* high is 15 nsec before BAS\* goes low. Because this is a read cycle, BR/W\* remains high during the entire cycle.

- 2. The Bus Master drives the address bus BA1-BA23 with a minimum address setup time of 15 ns before BAS is asserted.

- 3. All Bus Slaves determine if they are being addressed using BAS as a decode enable; the device being addressed responds with IMA within 70 ns after BAS is asserted, i.e. the receiver must see IMA within 70 ns of BAS.

- 4. If a Bus Slave is being addressed, it puts data on the bus after BDS goes true. Note that BDS can precede or follow BAS by up to 75 ns; even though BDS may precede BAS, the Bus Slave cannot drive the bus until it has decoded that it is being addressed. Bus Slaves must not drive the upper/lower data lines unless they are specifically strobed; otherwise, folding by the DMA Controller can be affected.

- NOTE: It is worthwhile to use the above BAS to BDS timing as an example of how some of the timing specifications were derived. Relative to the 68000 clock, BDS or BAS occurs a maximum of 60 ns after the clock. Assuming (very worse case) that one signal occurs 0 ns after the clock and the other occurs 60 ns after the clock, then the signals can be 60 ns apart (in either direction). Adding in 15 ns for bus skew yields the 75 ns specification.

- 5. The time from BDS to data valid is device-dependent; DTACK is generated by the Bus Slave to qualify this data. There are 3 cases affecting data setup time prior to DTACK:

- A. When using ENDT, data may be placed on the bus after DTACK. Refer to Sections 5.6 and 5.7 for more detail.

- B. If the device does not use ENDT and cannot be a DMA source, then the data setup time prior to DTACK is 15 ns. As usual, this setup time must be met at the receiving device.

C. If the device being read is a DMA source (e.g. memory during a DMA output), then an additional 40 ns of data setup time prior to DTACK must be provided, or 55 ns total. The additional 40 ns is required due to the Fold Buffer delay when transferring data from the upper byte of memory to the low data byte for the I/O card. DMA and Fold Buffer operation is discussed in the Chapter DMA OPERATION.

For I/O-to-memory DMA (DMA input) transfers, the data setup time from the I/O card is still specified at 15 ns, measured with respect to DMARDY (which the DMA Controller uses to generate BLDS and/or BUDS for the RAM). Unlike DMA output, additional setup time is not required because there are matching delays in both the data (Fold Buffer delay) and in generating BLDS and/or BUDS from DMARDY.

- 6. The Bus Master detects that DTACK has occurred, accepts the data on the bus and then ends the cycle by negating BAS and BDS. The Bus Master must set BAS false within 350 ns of assertion of DTACK.

- 7. The Bus Slave detects that the cycle has ended when BAS or BDS go false (whichever occurs first) and then stops driving IMA, DTACK and the Data Bus. Likewise, the Bus Master stops driving the address bus.

Bus Slaves drive IMA\* and DTACK\* with either an open collector gate or a tri-state driver. While the high-to-low transition is controlled by this driver, the low-to-high transition is dependent on 2 factors external to the Bus Slave: (1) A pullup resistor to +5V and (2) an active pullup driver. For DTACK\*, the pullup resistor is either on the Processor board or the Bus Expander (depending where the card is installed). For IMA\*, the pullup is only in the Bus Expander. To provide a faster rise time than is provided by the pullup resistor, these signals are also actively pulled high. The active pullup devices (either on the Processor board or the Bus Expander) are activated after BAS\* goes high. Because the active pullup may be activated before the Bus Slave releases its low-driven signal, a short conflict may occur. To minimize this conflict, the Bus Slave must release IMA\* and DTACK\* within 50 nsec of BAS\* going high.

Because the Bus Expander does not assert IMA\* high until 70 ns after BAS\* goes high, there should be no conflict. However, problems have been seen with DTACK\* since certain Processor boards assert DTACK\* high immediately after BAS\* goes high. This contention has been observed to cause glitches in DTACK; thus, DTACK\* should not be used as a clock. Note that during DMA cycles, the DTACK\* pullup is still asserted by the Processor board, not the DMA Controller.

Relative to BAS or BDS, the following signals change with the indicated delay:

| A. | Address hold:     | 15ns. min. |

|----|-------------------|------------|

| в. | IMA* release:     | 50ns max.  |

| C. | DTACK* release:   | 50ns max.  |

| D. | Data Bus release: | 100ns max. |

## CHAPTER 5: DATA TRANSFERS

READ CYCLE TIMES (ns)

•

MIN

MAX NOTES

•

| • • • | BAS* low to DTACK* low w/o bus error,non-DMA<br>DTACK* low to BAS* high<br>BAS* high<br>Address setup before BAS* low | 140<br>15 | 3500<br>1500<br>3000<br>350 |       |

|-------|-----------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------|-------|

| 6     | BR/W* high to BAS* low or BDS* low                                                                                    | 15        | 70                          | 5     |

|       | BAS* low to IMA* low<br>BAS* low to BDS* low                                                                          | -75       | 70<br>75                    | 7     |

| 9a    | Data setup before DTACK* low, non-DMA source                                                                          |           |                             | 8     |

| 9b    | Data setup time before DTACK* low,DMA source                                                                          |           |                             | 8     |

| 10    | BAS* or BDS* high to data release                                                                                     | 0         | 100                         | 9     |

| 11    | BR/W* hold after BAS* or BDS* high                                                                                    | 65        |                             | 10    |

| 12    | Address hold after BAS* or BDS* high                                                                                  | 15        |                             | 10,11 |

| 13    | BAS* high to IMA* release                                                                                             | 0         | 50                          | 12    |

| 14    | BAS* high to DTACK* release                                                                                           | 0         | 50                          | 12    |

|       | · · · · · · · · · · · · · · · · · · ·                                                                                 |           |                             | I     |

- NOTES: 1. As discussed in the Chapter BUS ERROR AND STRETCH OPERATION, the BAS\* low time is limited in Series 200 mainframes by the Bus Error timer. This timer is set at 4.0 usec on early CPU boards; later CPU boards, however, have increased this time.

- 2. To provide margin, the maximum BAS\* low time is specified as 3500 ns.

- 3. The Bus Error timer does not 'know' whether a DMA cycle is being executed. The shorter time for the DMA cycle reflects the fact that the memory must be read and the I/O operation completed within a single memory cycle.

- 4. Meeting this timing spec ensures that the maximum BAS\* low time of 3500 ns will be achieved, i.e. 3000 ns + 350 ns < 3500 ns.

- 5. The 68000 specification permits 40 ns; however, the 15 ns limit documented in the DESIGNER'S GUIDE TO THE 9826A CARDCAGE is retained.

- 6. This time was previously specified at 50 ns; however, because 50 ns is too restrictive and because the Bus Expander (the only user of IMA) allows 70 ns, this time has been increased. Since the IMA\* bus driver itself can have up to 50 ns of delay (see Section 3.4), the on-board delay in address decoding must be less than 20 ns.

- 7. This time was derived from the min/max delays (0/60 ns) for BDS\* and BAS\* relative to the 68000 clock. Assuming (very worse case) that one signal is delayed 0 ns while the other is delayed 60 ns and adding in 15 ns for bus driver skew yields the +/- 75 ns spec. Because the skew between LDS\* and UDS\* is not specified by Motorola, one must assume a similar skew is possible between these 2 signals.

- 8. As usual, these times are measured at the bus receiver.

- 9. Whichever goes high first of BAS\* or BDS\*.

- 10. Whichever goes high last of BAS\* or BDS\*. If the 68000 gives up the bus to another bus master at the completion of the cycle, the 65 ns is still guaranteed since the other bus master must wait 100 ns after BAS\* and DTACK\* are high before assuming control. For a 68000 read cycle followed by a write cycle, the 65 ns is provided by the fact that BR/W\* stays high until BAS\* goes low at the beginning of the write cycle.

#### FIGURE 5-1 NOTES (continued)

- 11. Based on the 68000 and buffer/bus skew, the address hold time is 15 ns. However, the 98256A (256 kbyte RAM board) requires 40 ns of address hold time. This is presently achieved because the address bus is typically driven longer than the specified minimum and is tri-stated after the cycle (i.e. it floats at its current value).

- 12. The release time specifies when the open collector gate or tri-state driver must stop driving the low signal. The low-to-high transition is then controlled by external pullup resistors and drivers as described above.

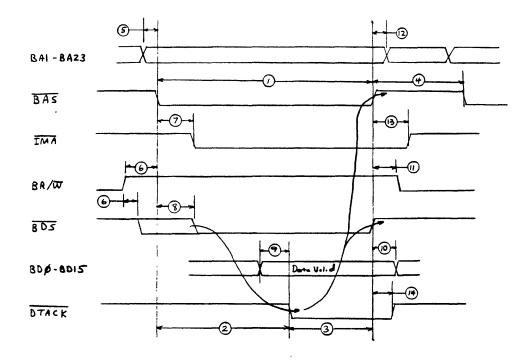

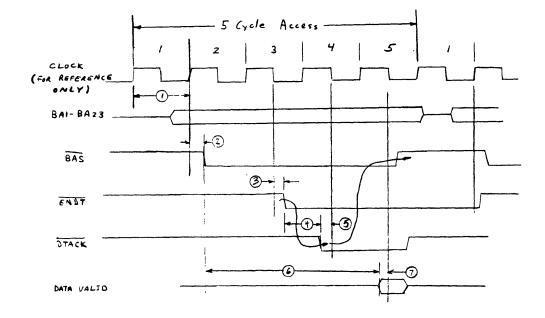

#### 5.4 WRITE CYCLE

Figure 5-2 shows the write cycle. As discussed in Chapter 3, timing requirements are specified on the bus measured at the signal receiver. The key aspects of a write cycle are:

- 1. Prior to the beginning of the write cycle, BR/W\*, BUDS\* and BLDS\* are pulled high by the processor. A pullup device on the Bus Master actively pulls up DTACK\*.

- 2. Address and BFCO-BFC2 are valid with a minimum address setup time of 15ns before BAS is asserted. BR/W\* goes low 75ns before to 35ns after the assertion of BAS.

- 3. All devices on the bus determine if they are being addressed using BAS as a decode enable; the device being addressed responds with IMA within 70 nsec after BAS occurs.

- 4. Data is valid on the data bus BDO-BD15 a minimum of 15 nsec prior to BDS (BLDS or BUDS, whichever occurs first). The occurrence of BDS indicates that data is valid. Notice that the time from BAS to the data strobes can vary over a wide range (50 ns to 2500 ns). The longer times typically occur during DMA operation because a read must be performed prior to the write operation.

- 5. When BDS goes true, BR/W\* is guaranteed to be low; BR/W should NOT be qualified with BAS because of the potential for bus conflicts since BR/W\* can still be changing up to 35 nsec after BAS goes true.

- 6. The Bus Slave stores the data and asserts DTACK, indicating to the Bus Master that the storage operation is complete.

- 7. The Bus Master detects that DTACK is true and negates BAS and BDS within 350 nsec. The Bus Master then removes the data BD0-BD15 from the data bus. To allow data hold time so that the Bus Slave can clock the data at the same time it asserts DTACK, the minimum Bus Master data hold time after detection of DTACK is 85ns.

- 8. The following signals change with the indicated delay after the negation of BDS and BAS (whichever occurs last).

- 15 ns min. A. Address hold:

- B. BR/W\* hold: 25 ns min.

- C. IMA\* release:

- 50 ns max.

- D. DTACK\* release: 50 ns max. E. DTACK\* pull-up asserted 0 ns min. on current Processor boards

#### 5.5 READ-MODIFY-WRITE

The 68000's Read-modify-write cycle is not supported on any current Series 200 hardware. One problem is the requirement for DTACK\* to be asserted twice during the cycle. Memory boards do not actively pull DTACK\* high; only Processor boards do this (after BAS\* goes high). Therefore, between DTACK's, DTACK\* is pulled up only by a pullup resistor and is not guaranteed to go high before the second DTACK occurs.

FIGURE 5-2: DIO BUS WRITE CYCLE

WRITE CYCLE TIMES (ns)

.

MIN MAX

NOTES

|   | 1a | BAS* low when Bus Error occurs                | 4000 |      | 1 |

|---|----|-----------------------------------------------|------|------|---|

|   | 1b | BAS* low to avoid Bus Error                   |      | 3500 | 2 |

|   | 2a | BAS* low to DTACK* low w/o bus error, DMA     |      | 1500 | 3 |

|   | 2Ъ | BAS* low to DTACK* low w/o bus error, non-DMA |      | 3000 | 3 |

| 1 |    | DTACK* low to BAS* high w/o bus error         |      | 350  |   |

|   | 4  | BAS* high                                     | 140  |      |   |

| 1 | 5  | Address setup before BAS*                     | 15   |      |   |

| 1 | 6  | BAS* low to IMA* low                          | 0    | 70   |   |

|   | 7  | BAS* low to BR/W* low                         | -75  | 45   |   |

| 1 | 8  | BAS* low to BDS* low                          | 50   | 2500 | 4 |

| 1 | 9  | BR/W* low to BDS* low                         | 65   |      | 5 |

| 1 | 10 | Data setup before BDS* low                    | 15   |      |   |

|   | 11 | Data hold after DTACK* low                    | 85   |      |   |

|   | 12 | BR/W* hold after BAS* or BDS* high            | 15   |      | 6 |

|   | 13 | Address hold after BAS* or BDS*               | 15   |      | 7 |

|   | 14 | BAS* high to IMA* release                     | 0    | 50   | 8 |

| 1 | 15 | BAS* high to DTACK* release                   | 0    | 50   | 8 |

|   | I  | ·                                             |      | l    |   |

29

- NOTES: 1. As discussed in the Chapter BUS ERROR AND STRETCH OPERATION, the BAS\* low time is limited in Series 200 mainframes by the Bus Error timer. This timer is set at 4.0 usec on early CPU boards; later CPU boards, however, have increased this time.

- 2. To provide margin, the maximum BAS\* low time is specified as 3500 ns.

- 3. The Bus Error timer does not 'know' whether a DMA cycle is being executed. The shorter time for the DMA cycle reflects the fact that the memory must be read and the I/O operation completed within a single memory cycle.

- 4. The minimum time was listed in previous documentation at 85 ns. However, based on the 68000 timing, a minimum time of 50 ns is required.

- 5. Specs 7 & 8 imply that BDS\* could go low within 5 nsec of BR/W\* going low (50-45). In actuality, this cannot happen as guaranteed by Spec 9.

- 6. Whichever goes high last of BAS\* or BDS\*.

- 7. Based on the 68000 and buffer/bus skew, the address hold time is 15 ns. However, the 98256A (256 kbyte RAM board) requires 40 ns of address hold time. This is presently achieved because the address bus is typically driven longer than the specified minimum and is tri-stated after the cycle (i.e. it floats at its current value).

- 8. The release time specifies when the open collector gate or tri-state driver must stop driving the signal low. The low-to-high transition is then controlled by external pullup resistors and drivers as described above.

#### 5.6 ENDT OVERVIEW

As discussed previously, Enable DTACK (ENDT) is used to improve the response time of certain DIO BUS devices such as RAM cards. These devices use ENDT (which is basically BAS delayed by 1-1/2 clock cycles) to generate an 'early' DTACK. For example, during a CPU read, ENDT is used to generate DTACK before the data is even on the bus; however, because the 68000 accepts the data up to 90 ns after DTACK, the read cycle will be completed successfully as long as the device provides the data within 90 ns of DTACK. The following comments on ENDT usage are necessary:

- ENDT can be used to provide 5 cycle read/write accesses. However, during those memory cycles where the card is unable to accept or provide data within the required time (e.g. during a RAM refresh cycle), then the card must inhibit use of ENDT to generate the early DTACK.

- 2. While ENDT is currently used only for certain cards such as RAM and EPROM, other devices which contain memory, such as new I/O cards, could use ENDT to improve their response time. In general, the RAM on Bus Masters does not use ENDT since the RAM control logic can use the CPU clock.

- 3. Cards that use ENDT must also be able to work without it. For example, the 98620A DMA Controller does not generate ENDT. Likewise, new Bus Masters are not required to generate ENDT.

- 4. If a new DMA Controller is designed that generates ENDT during a DMA cycle, ENDT should be used by memory (not the I/O card) during the DMA cycle.

In the timing discussions that follow, the timing margins appear very tight, if not unworkable. This is attributable to using worse-case timing specs for all parameters. In actuality, sufficient margin exists to ensure that 5 cycle accesses are achievable. For example, the worse-case ENDT-DTACK timing on the 09826-66522 board violates the timing specification; however, the production test for 5 cycle timing has yet to detect a failure of this board to achieve 5 cycle accesses (except, of course, during memory refresh cycles). The maximum time from ENDT-in to DTACK-out is calculated below. This applies to both read and write cycles.

- 125 ns Clock cycle period. ENDT is generated on the falling edge of the clock and DTACK must be valid prior to the next falling edge in order to achieve 5 cycle accesses.

- -9 ns Maximum delay in the 74S74 flip-flop that generates ENDT.

- -30 ns Maximum delay in the 74LS245 buffer that drives ENDT. This delay is less than the standard 47.5 ns delay since the loading on ENDT is typically less than 500 pf (call this 'engineering judgement').

- -12 ns Delay of the Processor's DTACK receiver (LS125). The typical spec (not the maximum) is used here since the loading on the signal is much less than the 45 pf load that the part is characterized at (more engineering judgement).

- -20 ns Maximum DTACK setup time prior to the trailing edge of the clock.

- 54 ns This represents the Bus Slave's requirement for generating DTACK from the ENDT input. Because the DTACK bus driver requires a maximum of 47.5 ns, approximately 6.5 ns remain for internal logic delay. However, because all these timing specifications are worse-case and thus statistically unlikely to occur together, more delay than 6.5 ns is allowed. Specifying the permissable time delay is difficult; the guideline is to keep the internal delay as small as possible. The penalty for larger time delays is 6 cycle accesses in some systems, not the desired 5 cycle accesses.

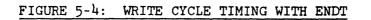

#### 5.7 READ CYCLE USING ENDT

The following read cycle timing using ENDT is based on Series 200 Bus Masters. As discussed above, devices that use ENDT to generate DTACK must provide data within a certain time after DTACK. Because Bus Slaves begin memory accesses using BAS, the time from BAS\* going low to data valid on the bus is calculated. The method of calculating this timing is explained so that users can apply ENDT to their application.

- 437.5 ns Represents 3-1/2 clock cycles. BAS\* starts with the rising edge of the CPU clock; data must be valid just before the clock's falling edge, 3-1/2 cycles later.

- -60 ns Maximum delay from rising edge of clock to AS\*.

- -47.5 ns Maximum delay of BAS\* bus driver.

1

-12 ns Maximum data delay on CPU board due to bus receivers.

-15 ns CPU data setup time before trailing edge of clock.

303 ns Thus, the Bus Slave must have data valid within 303 ns of BAS\* going low if ENDT is used to generate DTACK as discussed above. Because the Bus Slave's data bus drivers can require up to 39.5 ns, internal delays in accessing data must be less than 303 - 39.5 = 263.5 ns.

### CHAPTER 5: DATA TRANSFERS

FIGURE 5-3: READ CYCLE TIMING WITH ENDT

| READ TIMING | (ns) | MIN | MAX | NOTES |

|-------------|------|-----|-----|-------|

|             |      |     |     |       |

| T |   |                                   | 1      |         |   |

|---|---|-----------------------------------|--------|---------|---|

| 1 | 1 | Clock period @ 8 Mhz              | 125 ns | nominal | 1 |

| 1 | 2 | BAS* delay from clock high        | 1      | 107.5   |   |

|   | 3 | ENDT* delay from clock low        | 1      | 39      |   |

| 1 | 4 | ENDT* low to DTACK* low           | 1      | 54      |   |

| 1 | 5 | DTACK* low setup before clock low | 32     |         | 2 |

| Ì | 6 | BAS* low to read data valid       | 1      | 303     |   |

| 1 | 7 | Data setup before clock           | 27     | l       |   |

|   |   | · -                               | Ì      |         |   |

- NOTES: 1. The clock is on the Bus Master and does not appear on the DIO BUS; it is shown for REFERENCE ONLY.

- 2. As it should, Spec 3 +Spec 4 +Spec 5 = 125 ns.

- 3. These times assume ENDT\* loading is less than the 500 pf assumed for the data bus, address bus, etc.

### 5.8 WRITE CYCLE USING ENDT

During write cycles, the time from BAS\* going low to data becoming invalid (indicating completion of the cycle) is of interest. Likewise, the time from the data strobes BLDS and BUDS going true (indicating valid data on the bus) to the data becoming invalid is also of interest. These times are calculated below:

- 1. MINIMUM BAS\* LOW TO DATA INVALID TIME:

- 437.5 ns 3-1/2 clock cycles

- -60 ns Maximum delay from rising edge of clock to AS\*.

- -47.5 ns Maximum delay of BAS\* bus driver.

- -15 ns Maximum skew between BAS\* and data

- 0 ns Minimum delay of data bus drivers. Any delay extends the time from BAS\* low to data invalid; however, to continue with the worse-case analysis, 0 must be used.

- +30 ns Minimum data hold after BAS\* goes high. Because the data bus buffers continue to drive the bus after BAS\*and BDS\* go high, this hold time does occur on the bus.

- 345 ns

- 2. MINIMUM DATA STROBES LOW TO DATA INVALID TIME -- The data strobes are delayed from BAS\* by one clock cycle (125 ns). Therefore, the time from the data strobes going low to data invalid is 345 - 125 = 220 ns.

# CHAPTER 5: DATA TRANSFERS

| WRITE TIMI         | NG WITH ENDT (ns)   | MIN    | MAX     | NOTES |

|--------------------|---------------------|--------|---------|-------|

|                    |                     | T      |         |       |

| 1   Clock period @ | 8 Mhz               | 125 ns | nominal | 1     |

| 2   BAS* delay fro | m clock high        | 1      | 107.5   |       |

| 3   ENDT* delay fr | om clock low        | 1      | 39      |       |

| 4   ENDT* low to D | TACK* low           | 1      | 54      |       |

| 5   DTACK* low set | up before clock low | 32     |         |       |

| 6   BAS* low to BD | S* low (nominal)    | 1      | 125     |       |

| 7   Data setúp bef | ore BDS* low        | 15     |         |       |

| 8   BAS* low to da | ta invalid          | 345    |         |       |

| 9   BDS* low to da | ta invalid          | 220    |         |       |

NOTES: 1. The clock is on the Bus Master and does not appear on the DIO BUS; it is shown for REFERENCE ONLY.

2. These times assume ENDT\* loading is less than the 500 pf assumed for the data bus, address bus, etc.

An exception sequence is generated when the CPU's bus error input signal BERR\* is asserted. This signal is open collector, permitting it to be generated by any device (including the Processor board). Applications of the bus error signal are device dependent; several applications that DIO BUS designers should be aware of are discussed in this chapter.

An addition (4-83) to the DIO BUS was the signal STRETCH\*, which was assigned to the previously-spare pin 98. The STRETCH\* signal, which was to be generated by the 1 Mbyte parity RAM card in case of a parity error, would cause certain processor boards (e.g. the Memory Management Processor board) to insert an extra half cycle in the CPU clock. This would permit BERR\* (also generated by the RAM card) to have sufficient setup time at the CPU.

The situation, however, has changed. It was recently (11-83) discovered that even with STRETCH, the BERR signal generated by the RAM card would not have sufficient setup time on the processor board. Therefore, the STRETCH function has been abandoned and will not be generated by RAM cards. However, because Processor boards (09826-66517) have been shipped which respond to STRETCH, it is not possible to free the pin (98) as a spare. The pin, however, has been designated as a 'processor spare' in that future processor boards can use this pin as an OUTPUT since they will not be operating in the same machine as those processor boards which respond to this signal as an input.

#### 6.1 SIGNALS

- BERR\* BUS ERROR, when asserted, causes the Processor to terminate the bus cycle. When BERR is negated, the Processor begins its exception processing.

- Pin 98 This signal was called STRETCH\*, is now a 'processor spare' as discussed above.

## 6.2 BERR TIMING

BERR timing is different for 68000 and 68010 processors. The 68000 BERR input can be asynchronous; the only requirement is that BERR arrive before DTACK. The 68010 permits BERR to arrive after DTACK; however, BERR must meet a setup time before the CPU clock. According to Motorola, "this setup time is critical to proper operation, and the MC68010 may exhibit erratic behavior if it is violated". Because BERR timing varies for different mainframes and different Processor boards, timing diagrams are not included in this document. The reader is referred to Section 6.6 which provides guidelines for utilizing BERR.

### 6.3 BUS TIMEOUT

Series 200 Processor boards generate the bus error signal, BERR, when an accessed card fails to respond within a certain time. As discussed previously, a device responds with DTACK, so logically the time from BAS going true to the arrival of DTACK would be monitored. However, DTACK causes BAS to go false (with some delay) so the BERR circuit simply monitors the length of BAS; if DTACK occurs too late or fails to occur, BAS will remain true and a counter will time out.

A 4-bit BERR counter is located on Series 200 Processor boards and is cleared when BAS is false. When BAS is true, it begins counting (4 Mhz clock) and generates a BERR when it overflows (after 16 counts); 16 x 250 nsec = 4.0 usec. To provide margin, the maximum width of BAS is spec'd at 3.5 usec. To ensure that DTACK has time to reset BAS prior to 3.5 usec, DTACK must arrive 2 CPU clocks (250 nsec, synchronizing time) earlier. Because of this time, other delays and to provide ample margin, the maximum time from BAS\* going low to DTACK\* going low has been spec'd at 3.0 usec.

From the above, it appears that devices have 3.0 usec to DTACK. However, for devices that implement DMA, it is not this simple. For example, during a DMA output cycle, RAM must be read and the I/O card written to within one BAS cycle. Thus, the <u>combined</u> RAM read time and I/O card write time must be less than 3.0usec. CHAPTER 6: BUS ERROR AND STRETCH OPERATION

For a DMA input (I/O read, memory write), DMARDY must be true (indicating valid I/O card data) within 2.5 usec of DMACK. As usual, DTACK (indicating the memory card has accepted the data) must be true within 3.0 usec of BAS going true to prevent a BERR timeout.

For a DMA output (memory read, I/O write), memory is ready within 1.5 usec as evidenced by DTACK; the I/O card has another 1.5 usec to accept the data, as evidenced by DMARDY.

Because the Master Controller implements the BUS TIMEOUT function, other Bus Masters do not have to generate it; however, other Bus Masters <u>do have to respond to it</u> if the Master Controller generates it while another Bus Master has control of the bus. Acceptable responses are: (1) handle the bus timeout problem or (2) give up the bus to the Master Controller and let it resolve the problem. Refer to the SERIES 200 SYSTEM SPECIFICATION for more details.

### 6.4 AUTO LOCATE OF PROCESSOR RAM

The BERR signal generated by the BAS timeout counter is used to auto-locate RAM on 9826/36 Processor boards (but not on the 9816 Processor board). The Processor RAM auto-locates itself at the bottom (lower addresses) of RAM memory, eliminating the need for the user to set switches on an internal board. This works as follows: at power-on, the processor writes to and reads from each block of memory to determine how much memory is available. When there is no response from a memory card (indicating that the access is below all plug-in memory), the BERR counter times out and generates BERR. A latch then latches the bus-error address as the Processor board's RAM address. Auto location is a Series 200 implementation detail, not a Bus Master requirement.

### 6.5 BERR FOR PAGE FAULTING

1

Memory management Processor boards such as the 09826-66517 generate BERR upon detection of a page fault. DTACK is not generated so that a normal BERR trap occurs. Note: due to the unavailability of the 68010, early 09826-66517 boards have the 68000 and thus do not support page faulting.

### 6.6 GUIDELINES FOR UTILIZING BERR

This section gives guidelines for using BERR in new designs. It should be noted that presently (4-84) BERR is generated only by Processor boards. The only card which uses BERR (in addition to the Processor boards themselves) is the 98620 DMA Controller.

- Because of the critical nature of BERR timing and the differences in operation with different mainframes and Processor boards, the FSD & RND R&D Labs should be consulted prior to designing a card which generates BERR. In addition, the following information should be studied:

- A. BERR specifications for the different 680xx Processors.

- B.\_Hardware and software documentation on BERR operation and limitations in current mainframes.

- 2. Even though a Processor board or another board may generate BERR, a Bus Slave may not 'see' it. For example, BERR is an <u>input only</u> from the 9888 Bus Expander; thus, a Processor generated BERR is not seen by cards in the expander. Therefore, cards may utilize BERR if it is present, but they must not depend on it being available unless the stipulation is made that the card must reside in the mainframe. Such a stipulation is acceptable for a one-per-system type of card (e.g. the 98620 DMA Controller) but is not acceptable for generic I/O cards.

- 3. If a Bus Slave does respond to BERR, it should terminate all DIO BUS transactions, i.e. 'get off of the bus'.

The DIO BUS supports seven interrupt levels and 2 methods of responding to interrupts: (1) External Vectored and (2) Autovectored. External vectoring requires the interrupting device to put an 8-bit vector on the bus and assert the VECTOR signal. With autovectoring, the interrupting device does not provide a vector and the Processor generates its own default vector.

<u>CAUTION</u>: External vectored interrupts do not operate as described in the predecessor to this document, the DESIGNERS GUIDE TO THE 9826A CARDCAGE. Existing Processor boards do not generate several of the control signals described in that document.

> However, as discussed in the Chapter REQUIRED DIO BUS FUNCTIONS FOR AN I/O BUS, I/O card designers should <u>NOT</u> design cards that implement externally vectored interrupts, i.e. only autovectored interrupts should be used. Therefore, the description of external vectored interrupts in this document (section 7.2) should be viewed as primarily historical in nature, to describe an existing (but never used) DIO BUS feature. While external vectored interrupts should not be used in products, they may be used in special, one-of-a-kind projects as long as the designer accepts the risks involved.

### 7.1 INTERRUPT SIGNALS

The interrupt signals on the DIO BUS are shown below. Interrupts 3-6 are for external I/O cards. Interrupts 1,2 and 7 are for internal I/O. The assignment of these interrupt levels for the 9826/36 is shown below as an example; however, the SERIES 200 SYSTEM SPECIFICATION should be referenced for the most current information.

- 1. IR1\* Interrupt 1, Keyboard/real time clock LOWEST LEVEL

- 2. IR2\* Interrupt 2, 9826/36 internal floppy controller

41

CHAPTER 7: INTERRUPT OPERATION

3. IR3\* Interrupt 3, External I/O .

4. IR4\* Interrupt 4, External I/O .

5. IR5\* Interrupt 5, External I/O .

6. IR6\* Interrupt 6, External I/O .

7. IR7\* Interrupt 7, Reset key, powerfail HIGHEST LEVEL

8. IACK\* Interrupt Acknowledge, output from the Bus Master

9. VECTOR\* Output of interrupting device if it has an interrupt vector to put on BD0-BD7.

There is no IRO\* signal; level 0 is the quiescent (noninterrupting) state. For 68000-based Bus Masters, logic is needed to encode these interrupt signals into the 3 processor inputs, IPL0, IPL1 and IPL2. For example, Series 200 Bus Masters use an 74LS148 8-to-3 priority encoder to encode INT1 -INT7 to generate IPL0, IPL1 and IPL2.

The following interrupt levels are the only I/O interrupt levels which have been 'hardwired'; all plug-in I/O cards have a 2-bit switch to select levels 3-6.

| 98620A DMA Controller       | - | Level 3               |

|-----------------------------|---|-----------------------|

| 98620B DMA Controller       | - | Programmable from 3-7 |

| Internal HP-IB (9816/26/36) | - | Level 3               |

| Internal RS-232 (9816)      | - | Level 4               |

Even though IR1, IR2 and IR7 are not currently used for external I/O, the signals have been put on the backplane for expandability and compatibility with future products. Any cards which use these interrupt levels should be designed to respond to the Internal I/O memory space since the operating system protocol for these levels is designed around a known set of internal peripherals and is different than the protocol for the external I/O memory space.

Level 1 and 7 interrupts are driven by open collector gates in the 9826/36. However, Level 2, used by the 09826-66561 and 09826-66562 floppy controller boards, is driven by a standard LS-TTL gate and thus cannot be used by other devices.

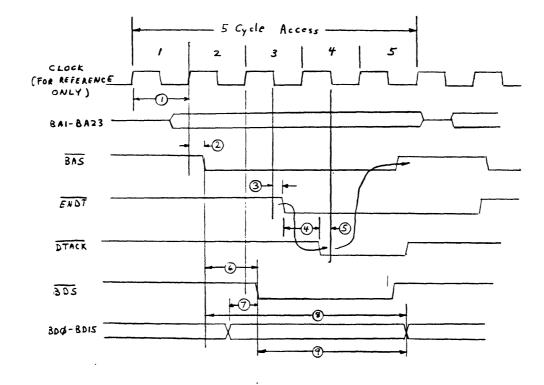

### 7.2 EXTERNAL VECTORED INTERRUPT ACKNOWLEDGE CYCLE

If the priority of the pending interrupt is greater than the current processor priority, the following interrupt sequence begins in which the Bus Master attempts to read an 8-bit interrupt vector from the interrupting I/O card. This operation is the same as a normal read, except IACK serves in lieu of BAS; BAS remains false. Interrupt timing is shown in Figure 5-1.

- Prior to the beginning of the cycle, the lowest three address bits (BA1- BA3) are set equal to the interrupt level being acknowledged. Likewise, the 68000 Function Code bits FC0, FC1 and FC2 are set to 1. The Bus Master decodes the Function Code bits and gates with Address Strobe to generate IACK\*.

- When FCO, FC1 and FC2 are 1, the bus driver for BLDS\*, ENDT\*, BUDS\*, BR/W\*, BAS\*, BFCO, BFC1 and BFC2 is disabled on these CPU boards: 09826-66514, -66515, -66516 and the 09816-66511. These signals should be considered undefined.

- 3. In response to IACK, each interrupting card detects: (1) if it is interrupting and (2) if its interrupt level is being acknowledged (by looking at BA1-BA3). If so, the card asserts the VECTOR signal within 100 nsec after IACK occurs to indicate to the processor that it has an 8-bit interrupt vector to put on the lower byte of the data bus. If the interrupting card does not respond within 100 ns, Bus Master circuitry will initiate an Autovector interrupt response, as discussed in the next section.

- 4. If the VECTOR is asserted within 100 ns, reading of the 8-bit vector occurs. Because the data strobes are disabled, the interrupting card provides its vector in response to IACK, as described:

- A. After detecting IACK, the interrupting card drives its vector on BDO-BD7. Data is setup a minimum of 15 ns prior to assertion of DTACK (as measured at the receiver).

- B. The CPU detects that DTACK has occurred, accepts the vector and ends the interrupt acknowledge by setting IACK false.

- C. The interrupting card then releases the VECTOR signal within 50 nsec after IACK goes false and releases the drive on the data bus within 100 nsec after IACK is false.

CHAPTER 7: INTERRUPT OPERATION

# FIGURE 7-1: EXTERNAL VECTORED INTERRUPT ACKNOWLEDGE CYCLE

INTERRUPT ACKNOWLEDGE CYCLE TIMING

MIN MAX

|    | IACK* low                             |    | 4500 |

|----|---------------------------------------|----|------|

| 2  | IACK* low to DTACK* low w/o bus error | 1  | 3000 |

| 3  | Address setup before IACK* low        | 15 |      |

| 4  | IACK* low to IMA* low                 | 0  | 70   |

| 5  | IACK* low to VECTOR* low              | 0  | 100  |

| 6  | Data setup before DTACK* low          | 15 |      |

| 7  | Data hold after IACK* high            | 0  | 100  |

| 8  | Address hold after IACK* high         | 15 |      |

| 9  | IACK* high to IMA* high               | 0  | 50   |

|    | IACK* high to VECTOR* high            | 0  | 50   |

| 11 | IACK* high to DTACK* high             | 0  | 50   |

|    | I                                     |    |      |

44

### CHAPTER 7: INTERRUPT OPERATION

External Vectoring has not been implemented on any I/O card to date (4-84) and thus its operation has not been tested. If External Vectoring is implemented, extensive qualification will be required to verify that it works with the different mainframes and processor boards. Also, designers should be aware that only <u>one</u> vectoring card per interrupt level is allowed unless a hardware arbitration scheme is included. Multiple autovectoring I/O cards may reside on the same level as a single vectoring card since the vectoring card will override autovectoring cards.

Refer to the Chapter OPERATION IN THE 9888A BUS EXPANDER for problems relative to vectored interrupt operation in the Bus Expander.

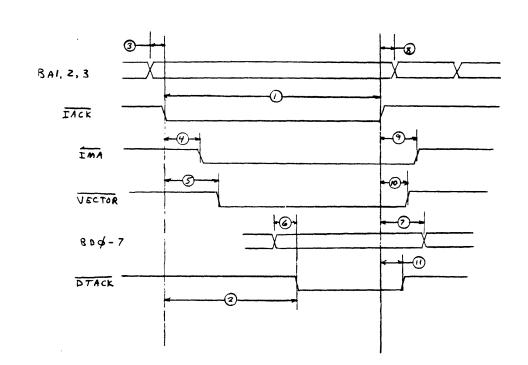

### 7.3 AUTOVECTORED INTERRUPT CYCLE

If an interrupting card does not generate VECTOR, the Bus Master automatically generates its own vector as follows:

- 1. Steps 1-3 outlined above occur (the Bus Master does not 'know' yet that it is an Autovector cycle).

- 2. With Autovectoring, the interrupting card does not assert VECTOR in response to IACK, nor does it provide the vector itself. Logic on the Processor Board detects that VECTOR\* remains high and, within 100 ns of IACK, asserts VPA (Valid Peripheral Address), an input to the 68000.

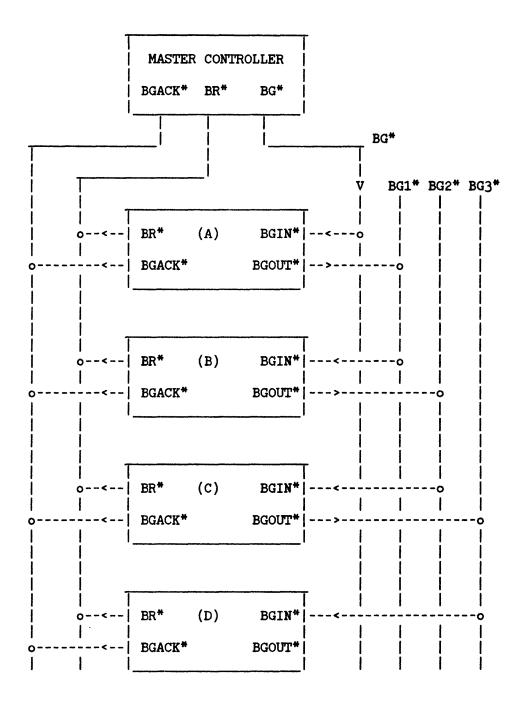

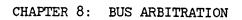

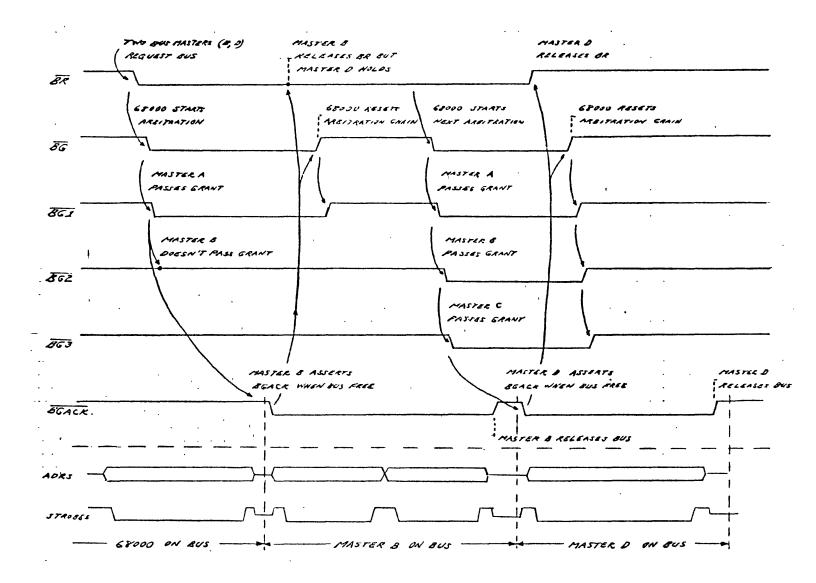

- 3. The processor recognizes that, if VPA is asserted during the interrupt acknowledge cycle, it is an Autovector cycle. The processor uses an internally generated vector that is a function of the interrupt level being serviced. The 7 interrupt vectors, corresponding to interrupt levels 1-7, are 25 through 31 decimal. These are used to access 4-byte addresses from 100 - 124 which vector operation to RAM. Refer to the 68000 Data Sheet for more information.