IBM

Instruction–Reference 1410 System Fundamentals

# Preface

This publication, Form 223-2589, obsoletes and contains information formerly found in the following Customer Engineering Instruction-Reference manuals: *IBM* 1410 System Fundamentals and 1411 Functional Units, Form R23-2589; *IBM* 1410 Component Circuits, Form R23-9776; *IBM* 1410 Timing Charts and Second Level Diagrams, Form R23-9774-1; and *IBM* 1410 Data Processing System, Form 225-6549-1.

The information formerly contained in the 1410 System Fundamentals and 1410 Component Circuits manual remains unchanged, but the 1410 Timing Chart and Second Level Diagrams manual has been revised. The revised portion eliminates many diagrams that can now be found in their related manuals. For example, diagrams for Input-Output or Console Operations can be found in *IBM 1410 Input-Output Operations*, Form R23-2692, or in *IBM 1415 Console*, Form R23-2648.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Corporation, CE Manuals, Dept. B96, PO Box 390, Poughkeepsie, N.Y.

| System Fundamentals                              | 7  |

|--------------------------------------------------|----|

| Operation of Functional Units                    | 7  |

| Operating Fundamentals of a Computer System      | 8  |

| 1410 Components                                  | 8  |

| IBM 1411 Processing Unit                         | 8  |

| IBM 1414 Input-Output Synchronizer               | 8  |

| IBM 1415 Console and Input-Output Printer        | 8  |

| ивм 1402 Card Read Punch                         | 8  |

| IBM 1403 Printer                                 | 8  |

| IBM 729 and 7330 Magnetic Tape Units             | 9  |

| ивм 1405 Disk Storage                            | 9  |

| вм 1301 Disk Storage                             | 9  |

| ивм 1412 and ивм 1419 Magnetic Character Readers | 9  |

| ивм 7750 Programmed Transmission Control         | 9  |

| IBM 1009 Data Transmission Unit                  | 9  |

| ивм 1011 Paper Tape Reader                       | 9  |

| IBM 1014 Remote Inquiry Unit                     | 9  |

| Program Addressable Clock                        | 10 |

| Telegraph Input-Output                           | 10 |

| 1410 Fundamentals                                | 10 |

| Machine Language                                 | 10 |

| Packaging and Component Parts                    | 12 |

| Storage Principles                               | 12 |

| Stored Programming                               | 13 |

| Control                                          | 13 |

| Data Flow                                        | 14 |

| 1411 Functional Units                                                                                                                                                                                                                                                                                                                                                                                                              | 17                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

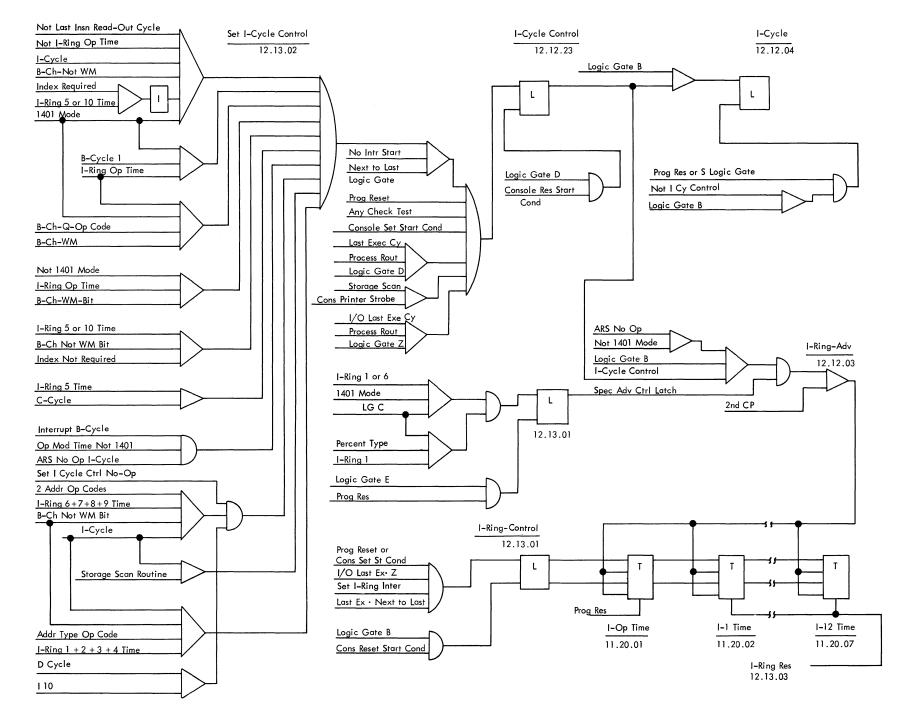

| Control Unit<br>Logic Clock<br>Cycle Control                                                                                                                                                                                                                                                                                                                                                                                       | $17 \\ 17 \\ 20$                                                            |

| Address Unit<br>Address Registers<br>Address Modification<br>Address Exit-Channel Validity Check<br>Address-Channel Validity Check                                                                                                                                                                                                                                                                                                 | 21<br>22<br>22<br>27<br>27                                                  |

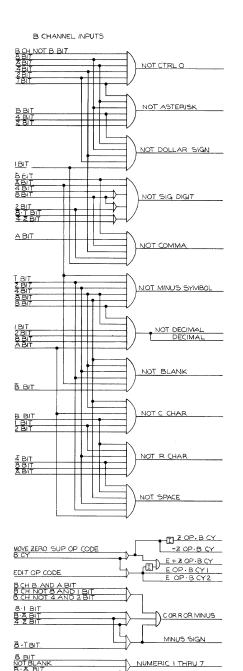

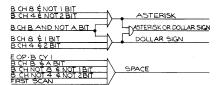

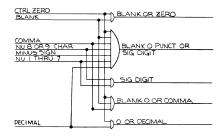

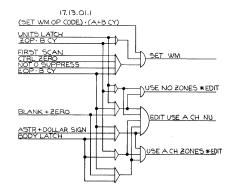

| Operational Unit         B Data Register         B Register Set Check         B Character Select Check         B Channel Validity Check         A Data Register         A Register Set Check         A Channel         A Character Select Check         A Channel         A Character Select Check         A Channel         A Seembly         Assembly         Assembly Channel Validity Check         Adder         Compare Unit | 27<br>28<br>29<br>29<br>29<br>31<br>31<br>31<br>32<br>33<br>36<br>36<br>39  |

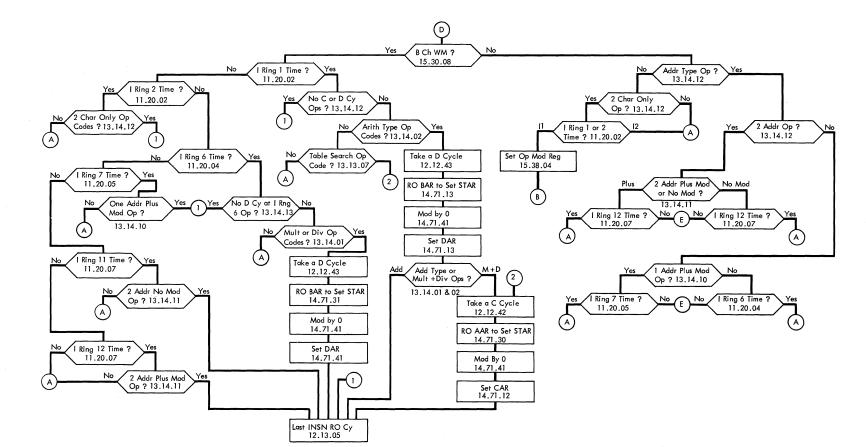

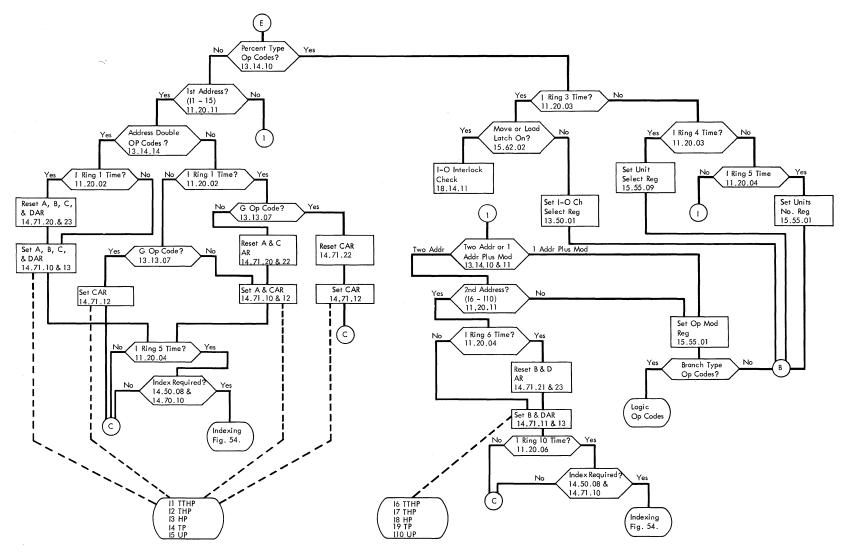

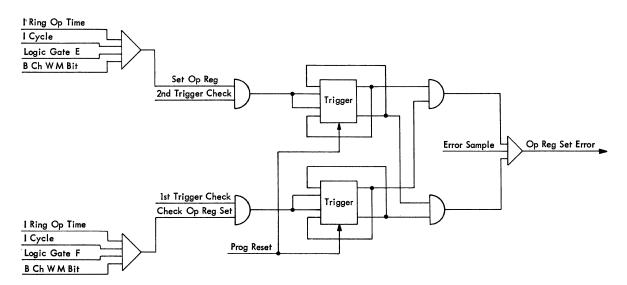

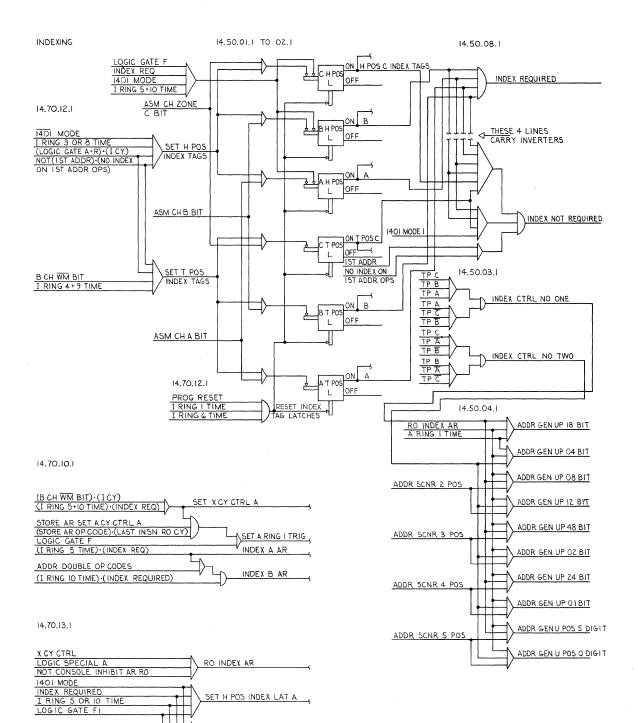

| Instruction Read-Out<br>Operating Principles<br>Op Register Set Check<br>Op Modifier Register Set Check<br>Instruction Check<br>Address Check<br>Indexing<br>Operating Principles                                                                                                                                                                                                                                                  | $\begin{array}{c} 41 \\ 41 \\ 52 \\ 53 \\ 53 \\ 54 \\ 54 \\ 56 \end{array}$ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                             |

| Power Supplies                                                    | 61       |

|-------------------------------------------------------------------|----------|

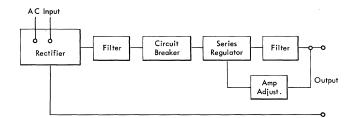

| Regulation                                                        | 61       |

| Special-Voltage Power-Supply Unit                                 | 61       |

| Power-On Sequence                                                 | 61       |

| Emergency Off                                                     | 61       |

| pc-Off                                                            | 61       |

| Power-Off                                                         | 66       |

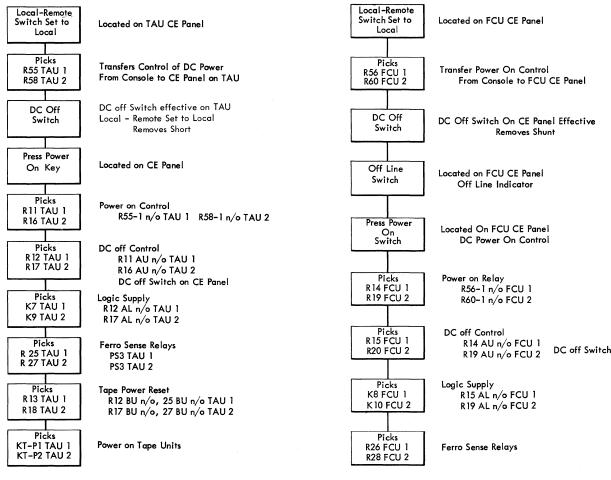

| Local Remote Operation — I-0                                      | 66       |

| TAU Off-Line Operation — Local Remote Switch                      | 67       |

| 1301 File Control Unit (FCU) Off-Line Operation-                  |          |

| Local-Remote                                                      | 67       |

| 1405 FCU Off-Line Operation                                       | 67       |

| Power-Fault Indicators                                            | 67       |

| Thermal Reset                                                     | 68       |

| Overcurrent Failure                                               | 68       |

| Overvoltage Failure                                               | 68<br>68 |

| Marginal Checking                                                 | 68<br>68 |

| Portable Marginal-Check Power-Supply Unit<br>Power Unit Locations | 68<br>69 |

| Frame and Chassis Designations                                    | 69<br>69 |

|                                                                   | 05       |

| Component Circuits                                                | 73       |

| Logic Families                                                    | 73       |

| Automated Logic Diagrams                                          | 73       |

| Line Levels                                                       | 76       |

| Basic Circuits                                                    | 77       |

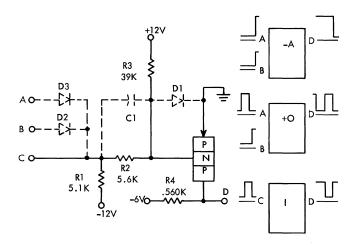

| Positive AND — Negative OR (SDTRL)                                | 77<br>78 |

| Negative AND — Positive OR — Inverter (SDTDL)<br>Trigger (SDTDL)  | 78<br>78 |

| Emitter Follower (sdtrl)                                          | 79       |

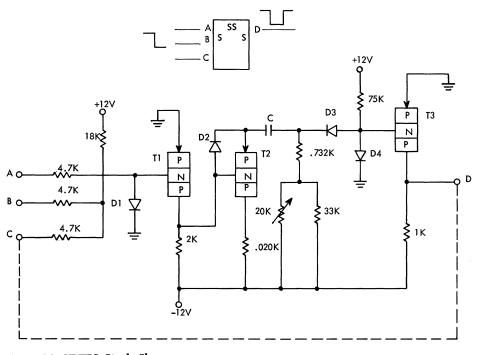

| Single Shot (SDTRL)                                               | 79       |

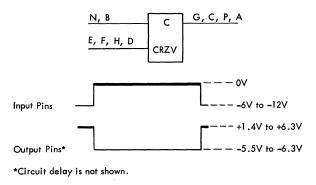

| Drift Sense Amplifier                                             | 81       |

| Card Descriptions                                                 | 83       |

| ABN                                                               | 83<br>83 |

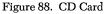

| CD—                                                               | 83       |

| CRZV                                                              | 83       |

| DBX                                                               | 83       |

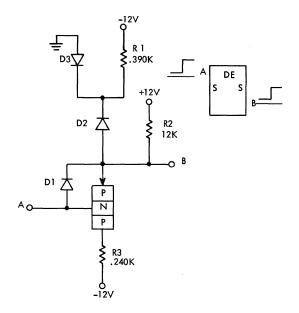

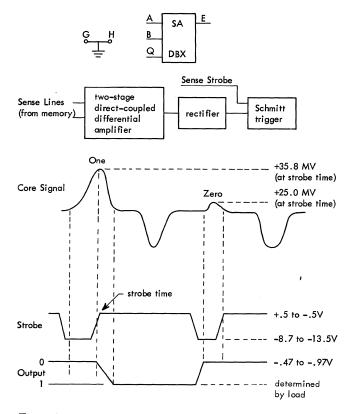

| DEA                                                               | 83       |

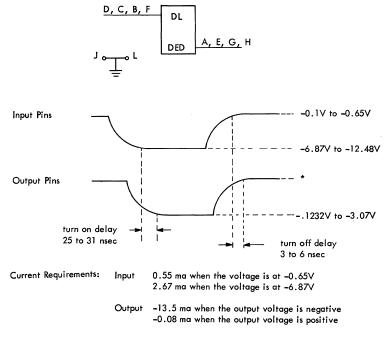

| DED<br>DEF                                                        | 84<br>84 |

| DEG                                                               | 84       |

| DEH                                                               | 84       |

| DEJ                                                               | 84       |

| DEK                                                               | 84<br>84 |

| DEL                                                               | 84       |

| DGU                                                               | 84       |

| DGV                                                               | 84       |

| DGW                                                               | 84       |

| DGX                                                               | 84<br>84 |

| DGY                                                               | 84<br>84 |

| DHA                                                               | 84       |

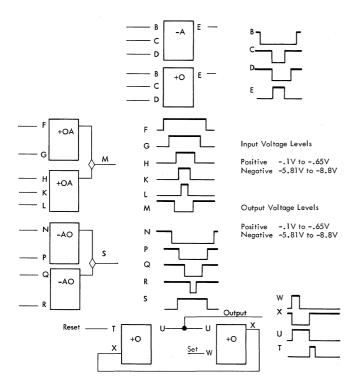

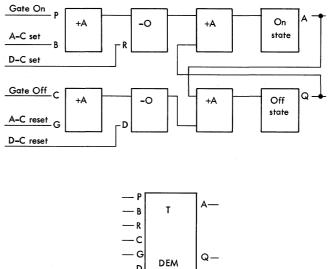

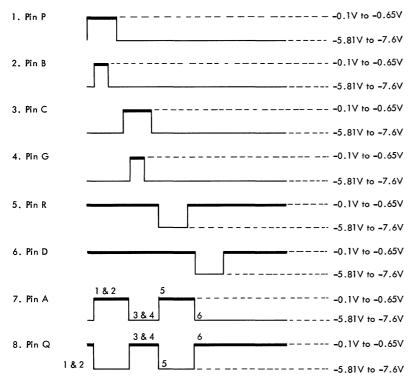

| DEM                                                               | 85       |

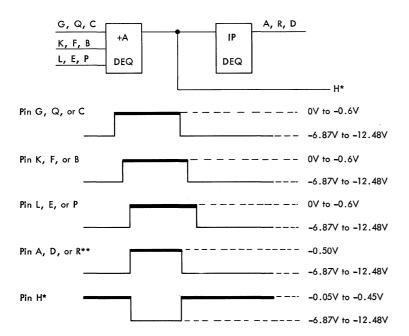

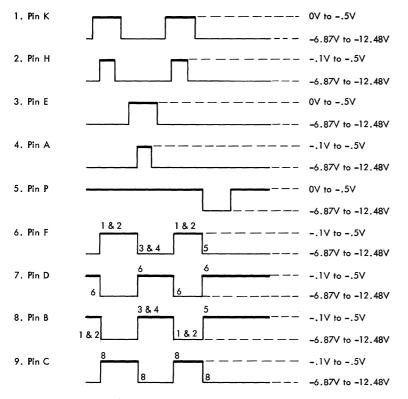

| DEQ                                                               | 85       |

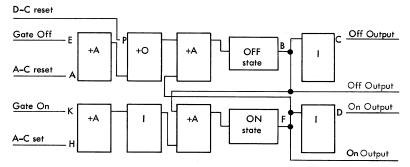

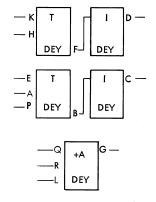

| DEY                                                               | 86<br>86 |

| 17124                                                             |          |

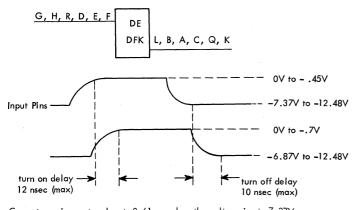

| DFK                                                                                                                                                                                                                                                                         | 86                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| DFS                                                                                                                                                                                                                                                                         | 86                                                 |

| DFV                                                                                                                                                                                                                                                                         | 86                                                 |

| DFW                                                                                                                                                                                                                                                                         | 86                                                 |

| DFY                                                                                                                                                                                                                                                                         | 86                                                 |

| DFZ                                                                                                                                                                                                                                                                         | 86                                                 |

| DGK                                                                                                                                                                                                                                                                         | 86                                                 |

| DGM                                                                                                                                                                                                                                                                         | 88                                                 |

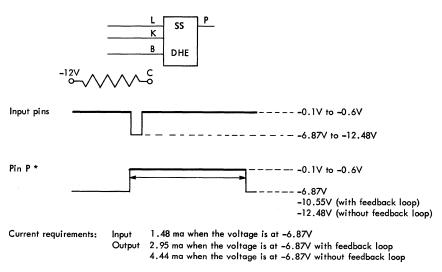

| DHE                                                                                                                                                                                                                                                                         | 88                                                 |

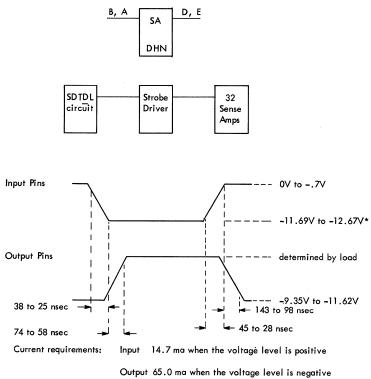

| DHN                                                                                                                                                                                                                                                                         | 88                                                 |

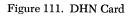

| KG                                                                                                                                                                                                                                                                          | 88                                                 |

| ТАМ                                                                                                                                                                                                                                                                         | 88                                                 |

|                                                                                                                                                                                                                                                                             |                                                    |

|                                                                                                                                                                                                                                                                             |                                                    |

| Reference Information                                                                                                                                                                                                                                                       | 96                                                 |

| Reference Information                                                                                                                                                                                                                                                       |                                                    |

| Reference Information                                                                                                                                                                                                                                                       | 96                                                 |

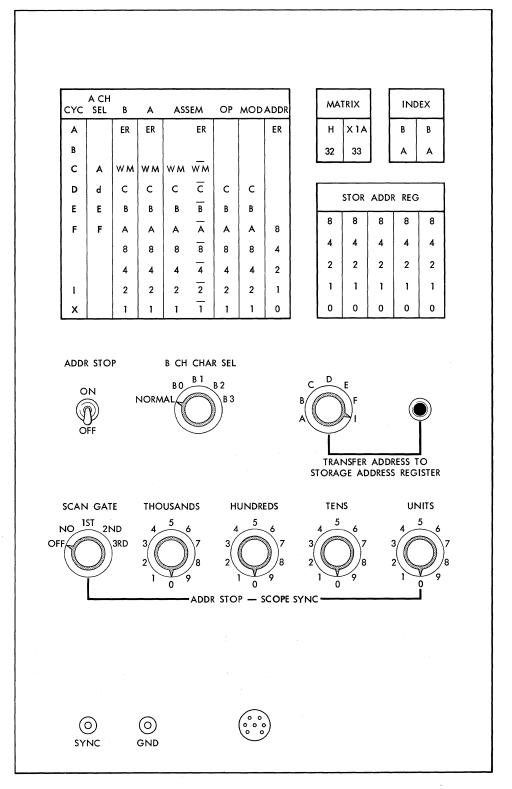

| Reference Information<br>IBM 1411 се Console<br>Address Display                                                                                                                                                                                                             | 96<br>96                                           |

| Reference Information<br>IBM 1411 CE Console<br>Address Display<br>B Character Select Switch                                                                                                                                                                                | 96<br>96<br>96                                     |

| Reference Information<br>IBM 1411 CE Console<br>Address Display<br>B Character Select Switch<br>Portable Controls                                                                                                                                                           | 96<br>96<br>96<br>96                               |

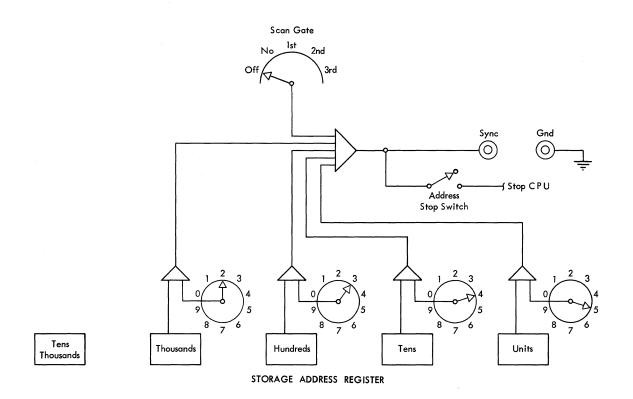

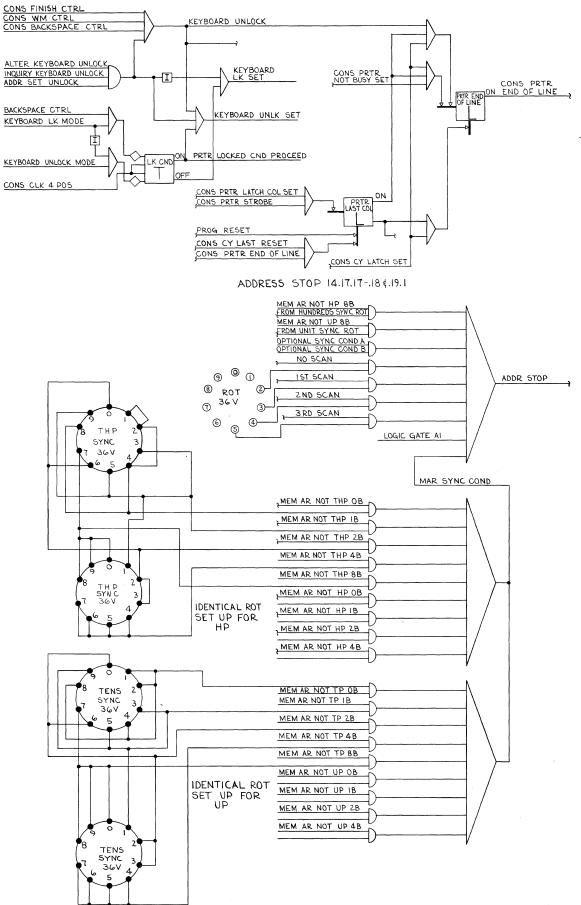

| Reference Information<br>IBM 1411 CE Console<br>Address Display<br>B Character Select Switch<br>Portable Controls<br>Address Stop and Scope Sync                                                                                                                            | 96<br>96<br>96<br>96<br>96<br>96                   |

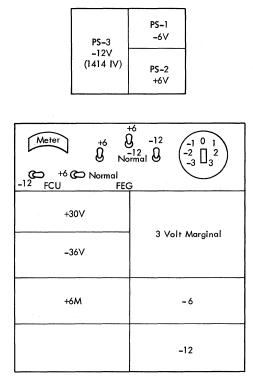

| Reference Information         IBM 1411 CE Console         Address Display         B Character Select Switch         Portable Controls         Address Stop and Scope Sync         System Voltages                                                                           | 96<br>96<br>96<br>96<br>96<br>96<br>96             |

| Reference Information<br>IBM 1411 CE Console<br>Address Display<br>B Character Select Switch<br>Portable Controls<br>Address Stop and Scope Sync<br>System Voltages<br>IBM 1411 Voltages                                                                                    | 96<br>96<br>96<br>96<br>96<br>96<br>96<br>96       |

| Reference Information<br>IBM 1411 CE Console<br>Address Display<br>B Character Select Switch<br>Portable Controls<br>Address Stop and Scope Sync<br>System Voltages<br>IBM 1411 Voltages<br>IBM 1414A Voltages                                                              | 96<br>96<br>96<br>96<br>96<br>96<br>96<br>96<br>96 |

| Reference Information         IBM 1411 CE Console         Address Display         B Character Select Switch         Portable Controls         Address Stop and Scope Sync         System Voltages         IBM 1411 Voltages         IBM 1414A Voltages         TAU Voltages | 96<br>96<br>96<br>96<br>96<br>96<br>96<br>96       |

| Check Test                      | 98  |

|---------------------------------|-----|

|                                 | 98  |

|                                 | 98  |

|                                 |     |

|                                 | .00 |

| Single Shot 1                   | 00  |

|                                 | 00  |

| ивм 1402-2 Attachment Timings 1 | .01 |

|                                 | 01  |

|                                 | 01  |

|                                 | 01  |

|                                 |     |

| Delay Lines 1                   | .01 |

| Service Aids 1                  | 01  |

| General 1                       | .01 |

|                                 | .02 |

|                                 | .02 |

|                                 | 03  |

|                                 | 03  |

| Magnetia Tana Operations        | .03 |

|                                 |     |

|                                 | .03 |

| Component Locations 1           | .03 |

| Input Voltage Change 1          | .03 |

|                                 |     |

|                                 |     |

| Second Level Diagrams           | 05  |

# **Illustration List**

#### FIGURE

TITLE

PAGE FI

| 1.                | Operation of Functional Units                                             | 7                                       |

|-------------------|---------------------------------------------------------------------------|-----------------------------------------|

| 2.                | Synchronizer Models Required for Each I-O Device                          | 8                                       |

| 3.<br>4.          | Standard BCD Interchange Code<br>Two-Out-of-Five Code                     | 11<br>12                                |

|                   | Qui-Binary Code                                                           | 12                                      |

|                   | Instruction Phase                                                         | 14                                      |

| 7.                | Data Flow                                                                 | 15                                      |

| 8.                |                                                                           | 16                                      |

| 9.                |                                                                           | 18                                      |

| 10.               |                                                                           | 18                                      |

| 11. 12.           |                                                                           | 19<br>20                                |

|                   | Overlap                                                                   | 20                                      |

| 14.               |                                                                           | $\overline{21}$                         |

| 15.               | Control Latches                                                           | 21                                      |

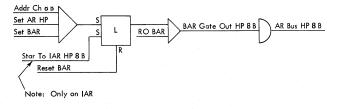

| 16.               | Address Register Latch (14.11.03)                                         | 22                                      |

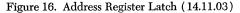

| 17.               | Address Modify Operation                                                  | 23                                      |

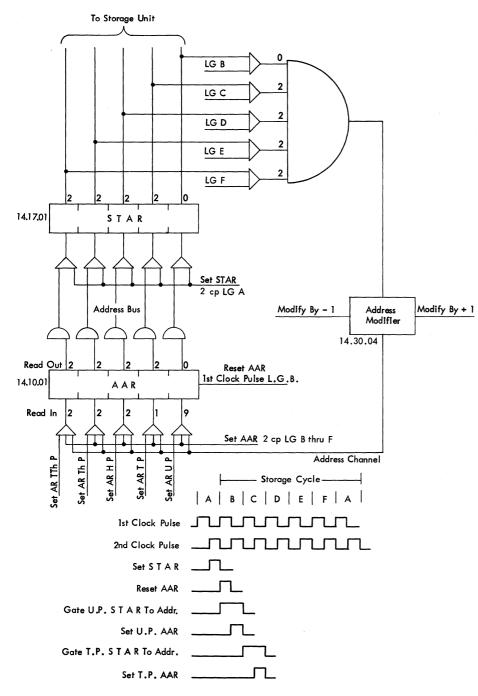

|                   | Address Modification of ARR                                               | 24                                      |

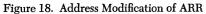

|                   | Address Modify Latches                                                    | 25<br>26                                |

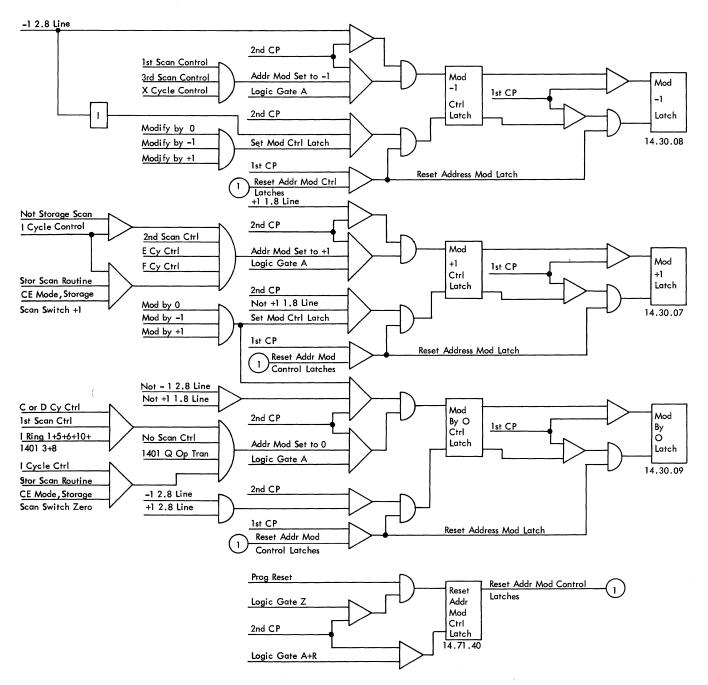

| 20.<br>21.        |                                                                           | 20<br>27                                |

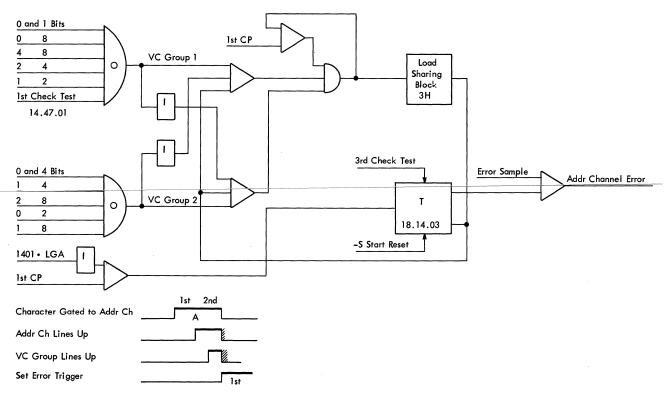

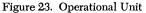

| $\frac{21}{22}$ . |                                                                           | 27                                      |

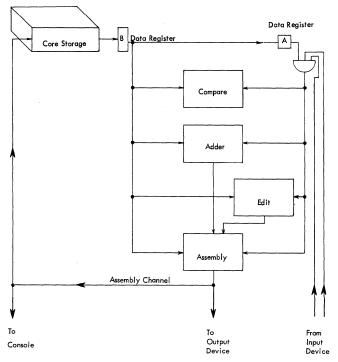

| $\frac{-}{23}$ .  | Operational Unit                                                          | $\overline{28}$                         |

| 24.               | ······································                                    |                                         |

| ~~                | Channels)                                                                 | 30                                      |

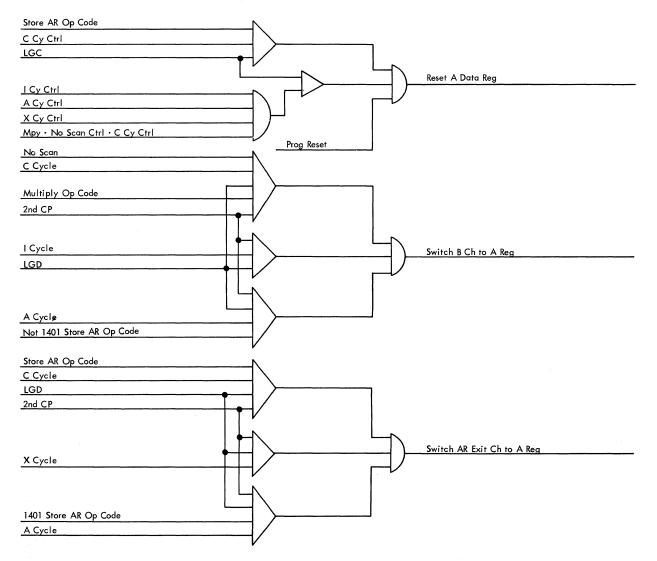

|                   | A Data Register Reset and Switching                                       | 31                                      |

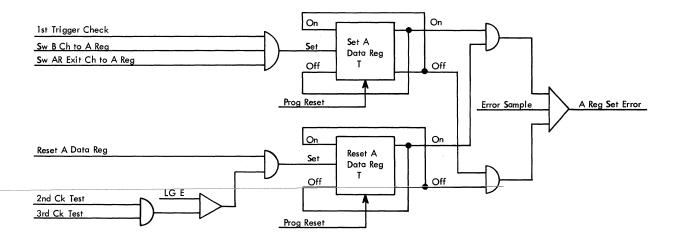

|                   | A Register Set Check (18.14.07)                                           | 32                                      |

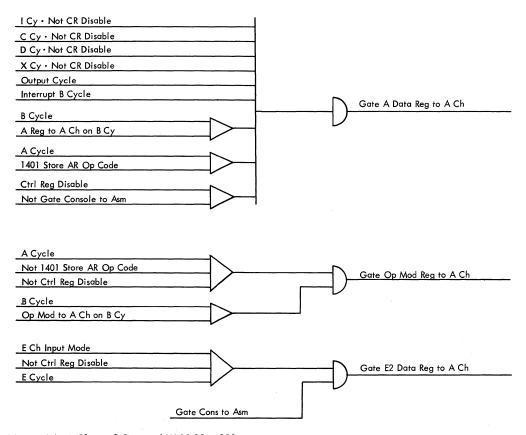

|                   | A Channel Gating (15.38.02 and 03)<br>A Character Select Check (18.14.01) | 32<br>33                                |

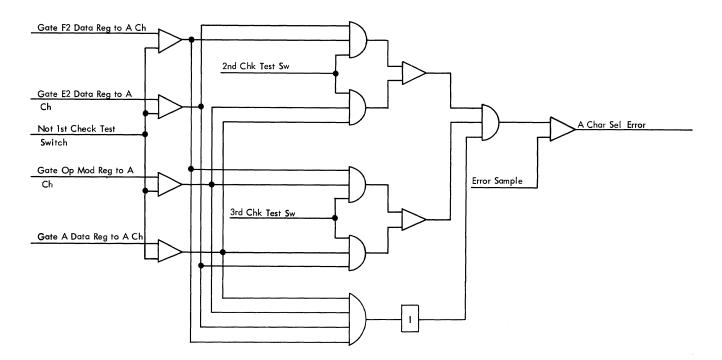

|                   | A Channel Validity Check (18.11.01-03)                                    | - 33<br>- 34                            |

| 30.               |                                                                           | 34                                      |

| 31.               |                                                                           | 35                                      |

| 32.               | Zone Assembly A Bit (15.50.05)                                            | 35                                      |

| 33.               | , , , , , , , , , , , , , , , , , , , ,                                   | 35                                      |

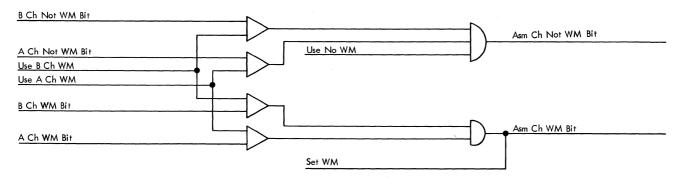

| 34.               |                                                                           | 36                                      |

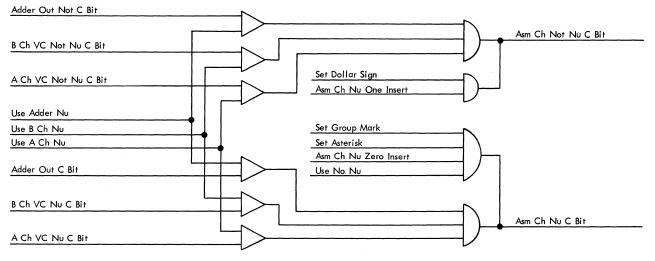

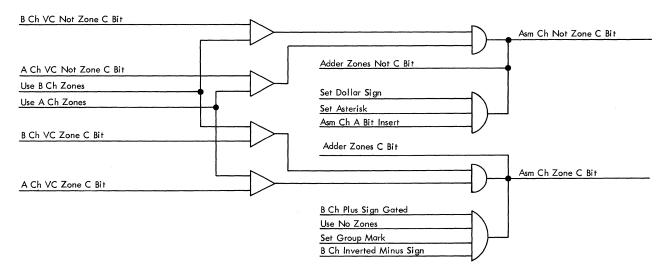

| 36.               | Zone C Bit Assembly (15.50.10)<br>C Bit Assembly (15.50.07)               | 36                                      |

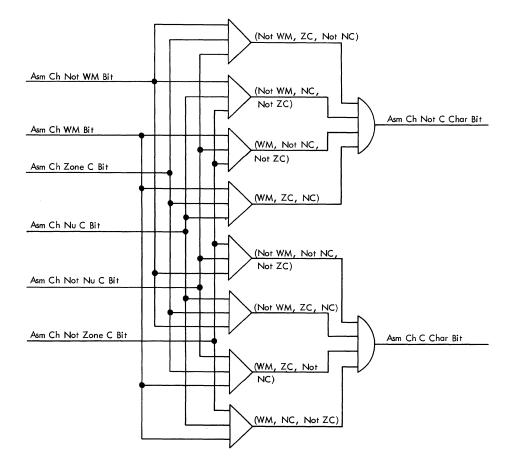

| 30.<br>37.        |                                                                           | 37<br>38                                |

| 38.               | True Complement Controls (16.20.12)                                       | 39                                      |

| 39.               | Qui-Binary Combination                                                    | 39                                      |

| <b>4</b> 0.       |                                                                           | 40                                      |

| 41.               |                                                                           | 41                                      |

| 42.<br>43.        | The Free Free (Trigoton of) the tricter                                   | 42                                      |

| 43.<br>44.        | (Sheeds 1 0) It                                                           | 3-45<br>46                              |

|                   | I Phase Latches                                                           | 40                                      |

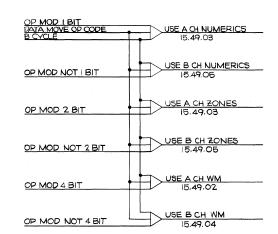

| 46.               | IBM 1410 Common Op Code Grouping Lines                                    |                                         |

|                   | (13.14.01-14)                                                             | 49                                      |

| 47.               | Op Register Set Check (18.14.04)                                          | 53                                      |

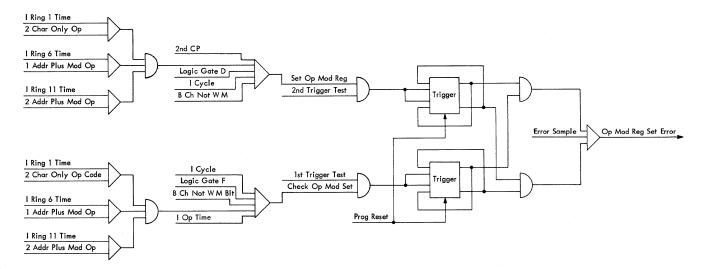

| 48.               | Op Mod Register Set Check (18.14.05)                                      | 53                                      |

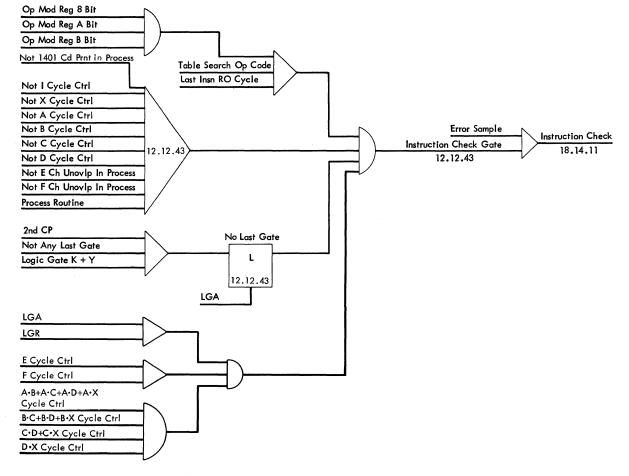

| 49.<br>50.        | Op Code Lengths<br>Instruction Check                                      | $\frac{54}{55}$                         |

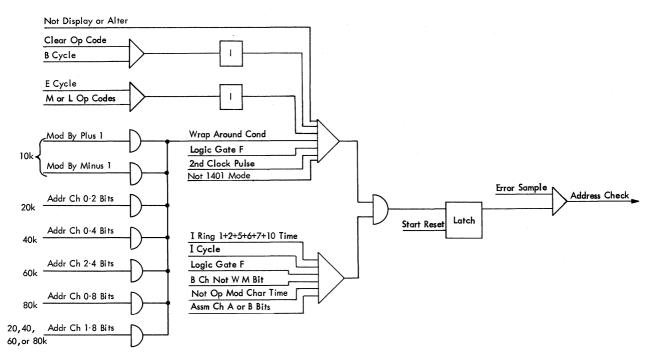

| 51.               |                                                                           | 56                                      |

| 52.               | Index Register Locations                                                  | 50<br>57                                |

| 53.               | Index Tag                                                                 | 57                                      |

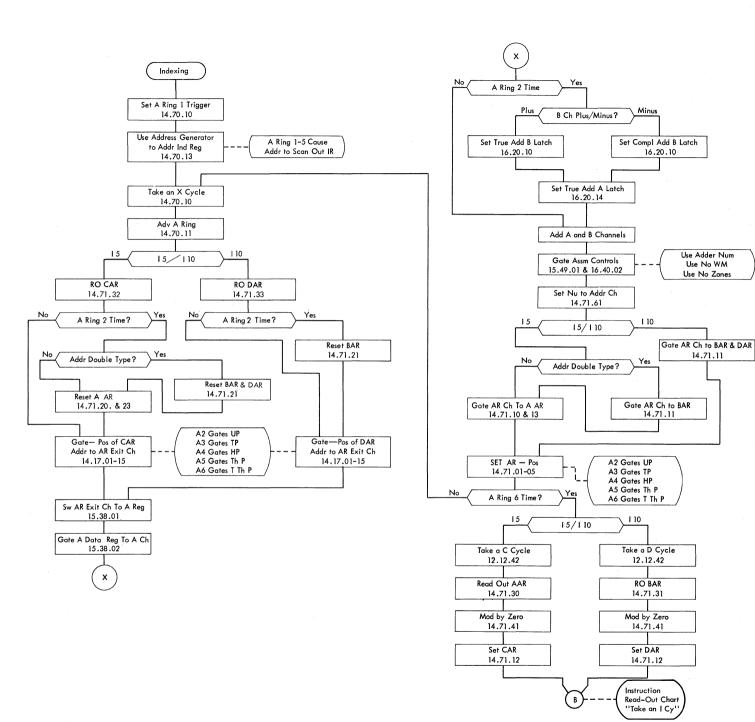

| 54.               | Indexing Operation                                                        | 58                                      |

|                   | Indexing Timings                                                          | 59                                      |

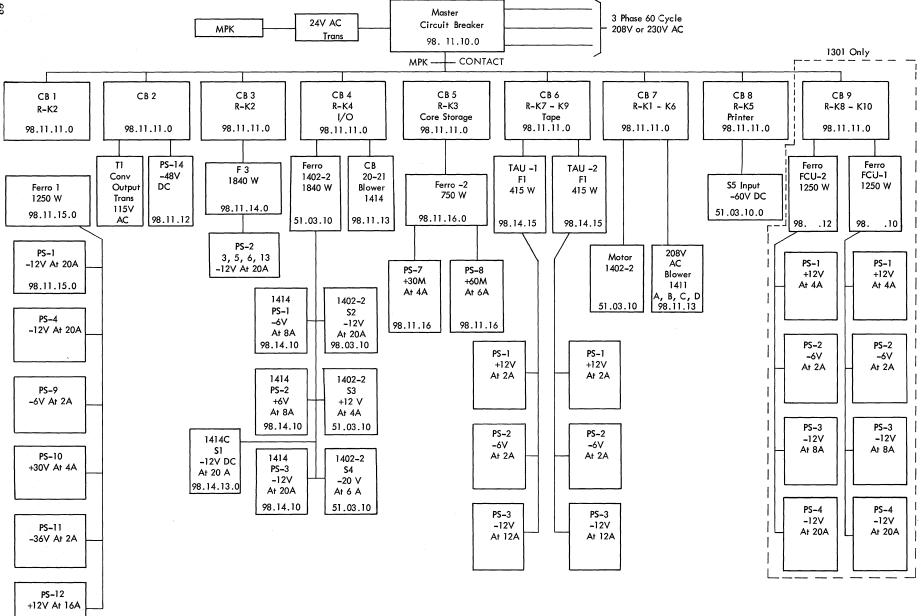

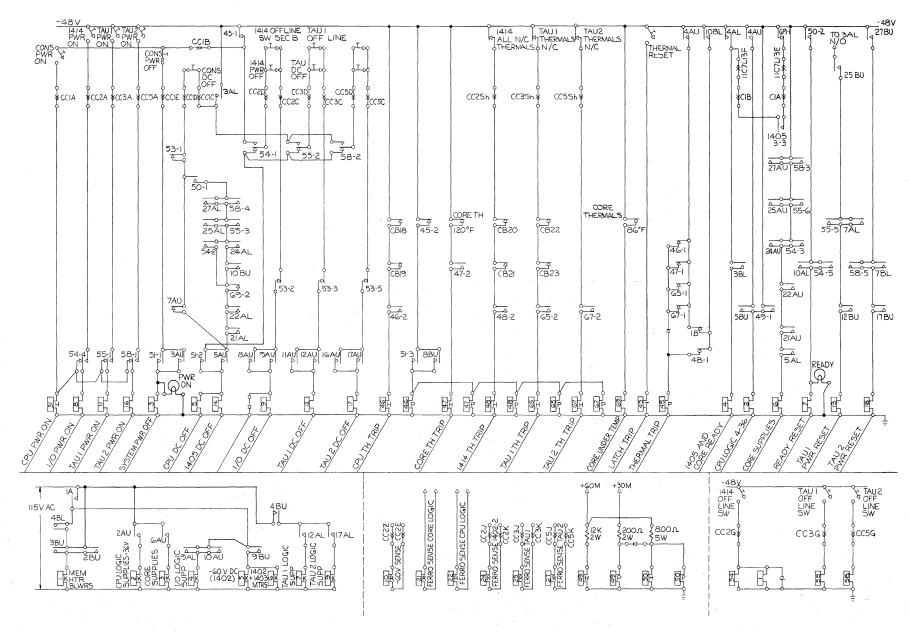

| 56.               | IBM 1410 Power Distribution                                               | 62                                      |

| 57.<br>58         | Power-On Timing Chart                                                     | 63                                      |

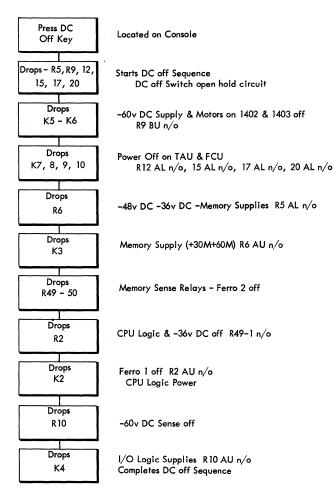

| 59.               | Power On<br>DC Off Timing Chart                                           | $\begin{array}{c} 64 \\ 65 \end{array}$ |

|                   | DC Off                                                                    | 66                                      |

|                   |                                                                           |                                         |

| FIGU           | RE TITLE                                                                       | PAGE              |

|----------------|--------------------------------------------------------------------------------|-------------------|

| 61.            |                                                                                |                   |

|                | Power On, Tape Units<br>Power On, File Units (1301 Only)                       |                   |

|                | Marginal-Check Power Supply (Portable Unit)                                    |                   |

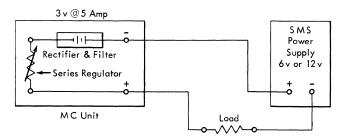

| 65.            | Marginal-Check Unit in Series with SMS Power                                   |                   |

|                | Supply                                                                         |                   |

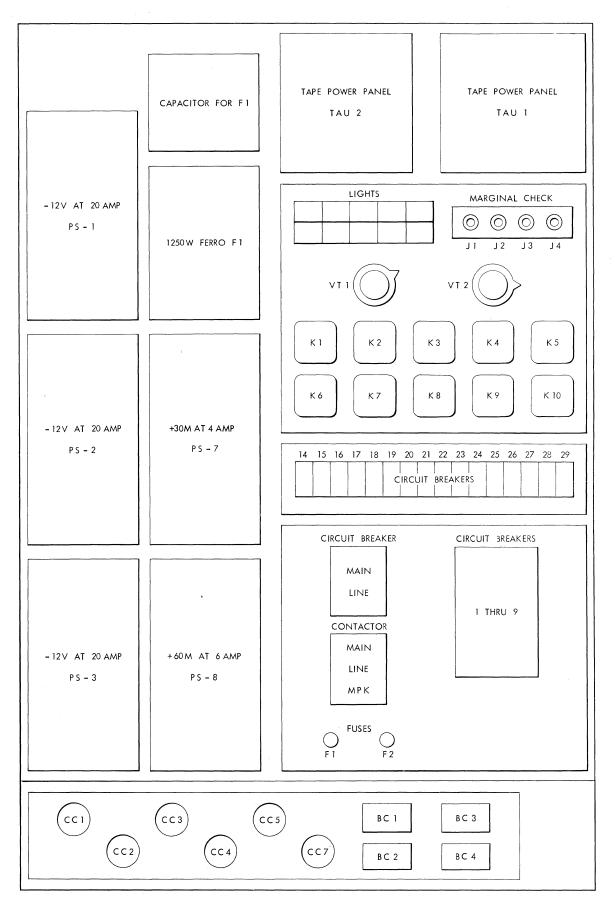

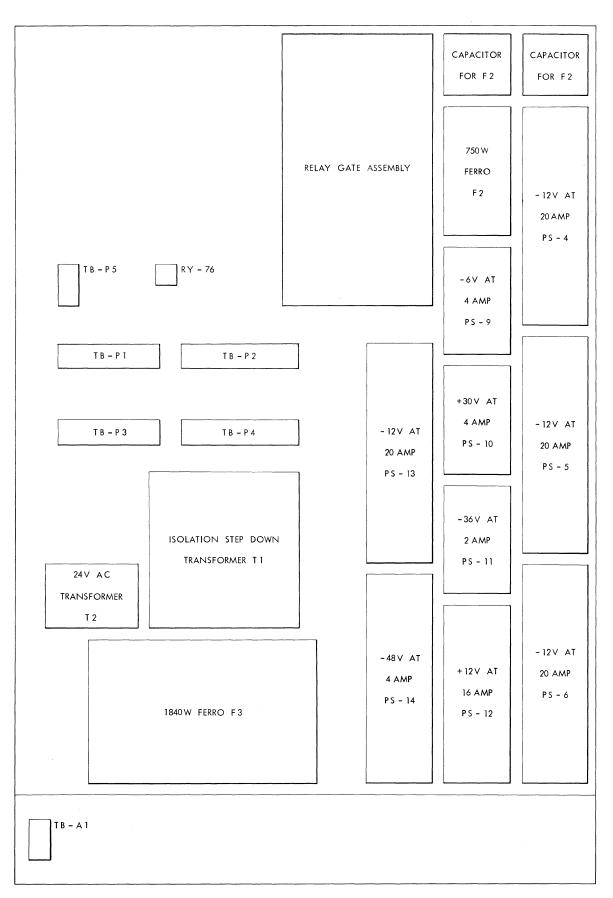

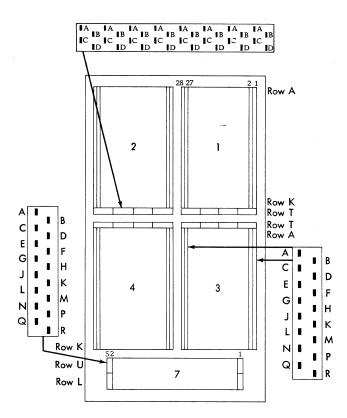

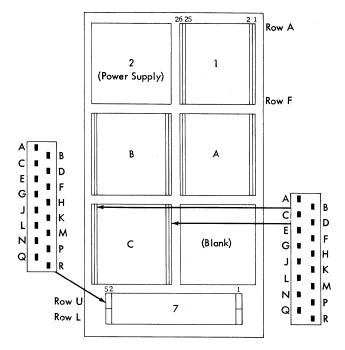

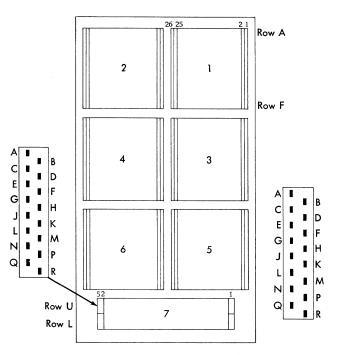

|                | IBM 1411 A Frame Front                                                         |                   |

|                | IBM 1411A Frame Rear                                                           |                   |

| 69.            | Frame and Chassis Designation<br>Two Logic Families in One Operation           |                   |

| 70.            |                                                                                |                   |

| 71.            |                                                                                |                   |

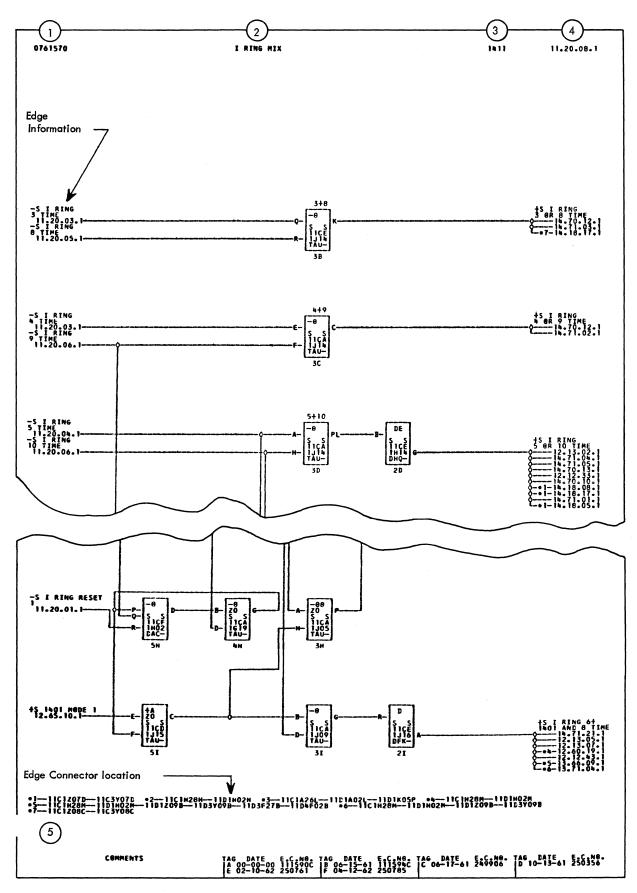

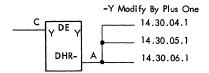

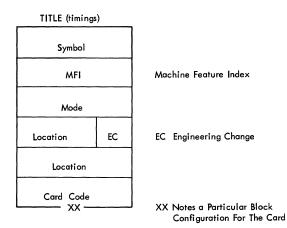

| 72.            | 0                                                                              |                   |

|                | Typical 1410 Logic Block<br>Logic Block Pin Connections                        |                   |

|                | Extender Application                                                           |                   |

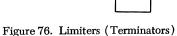

| 76.            |                                                                                |                   |

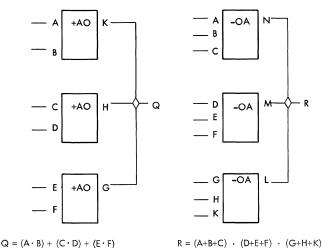

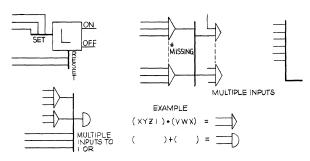

| 77.            | Dot Functions                                                                  | 77                |

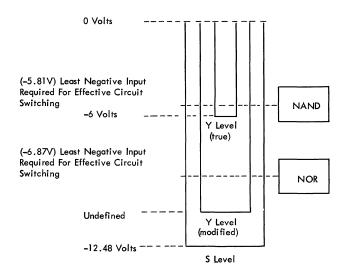

|                | NOR and NAND Driving Requirements                                              |                   |

| 79.            | Line Characteristics                                                           | . 77              |

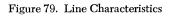

| 80.<br>81.     | SDTRL Positive AND—Negative OR                                                 |                   |

| 01.            | (Single Level)                                                                 |                   |

| 82.            |                                                                                |                   |

|                | SDTRL Emitter Follower                                                         |                   |

|                | SDTRL Single Shot                                                              | 81                |

| 85.            | Drift Sense Amplifier                                                          |                   |

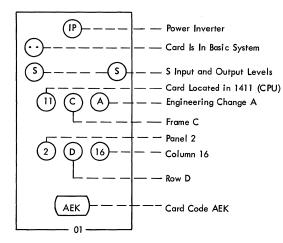

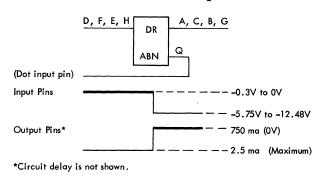

| 87<br>87       | ABN Card<br>AEK Card                                                           | . 83<br>. 83      |

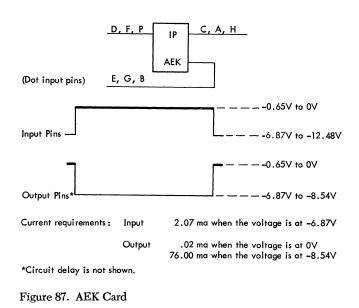

|                | CD Card                                                                        |                   |

| 89.            | CRZV Card                                                                      | 84                |

| 90.            |                                                                                |                   |

|                | DEA Card                                                                       | . 84              |

| 92.<br>93      | DED Card<br>High and Low Speed SDTDL Circuits                                  | 85<br>85          |

|                | SDTDL Circuits                                                                 |                   |

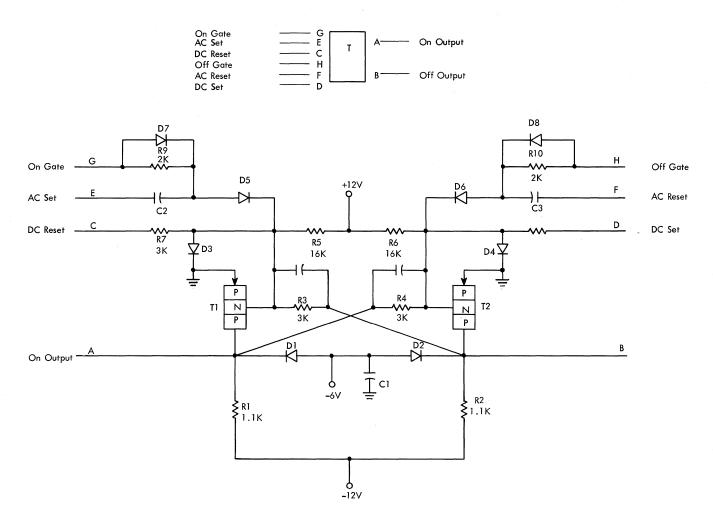

| 95.            | DEM Trigger                                                                    |                   |

|                | DEM Timings                                                                    | 87                |

| 97.            | DEQ Card                                                                       | 87                |

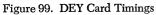

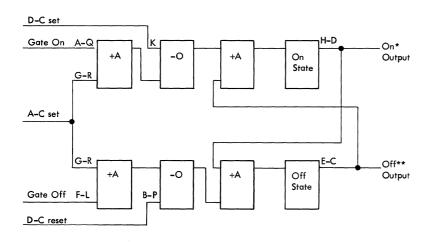

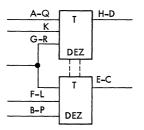

| 98.<br>99.     | DEY Card                                                                       | 88<br>89          |

| 100.           | DEZ Card                                                                       | 89                |

|                | DEZ Timings                                                                    |                   |

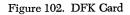

| 102.           | DFK Card                                                                       | 90                |

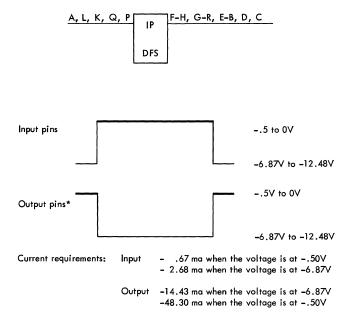

| $103. \\ 104.$ | DFS Low Power Inverter                                                         | 91                |

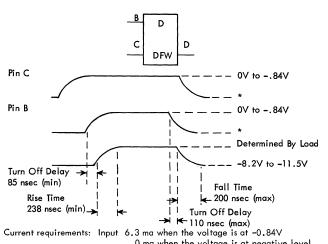

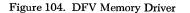

|                | DFV Memory Driver                                                              | $91 \\ 91$        |

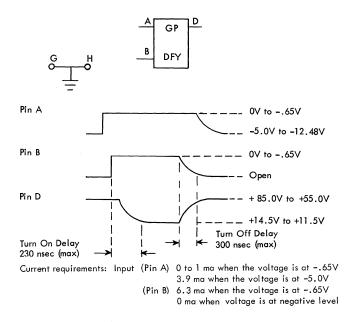

| 106.           | DEY Power Gate                                                                 | 91                |

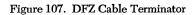

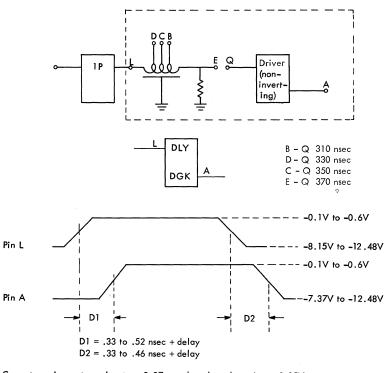

| 107.           | DFZ Cable Terminator                                                           | 92                |

| 108.           | DGK Delay Line                                                                 | 92                |

| $109. \\110.$  | DGM Card<br>DHE Single Shot                                                    | 93                |

| 111.           |                                                                                | 93                |

| 111. 112.      | DHN Card KG Card                                                               | 94<br>94          |

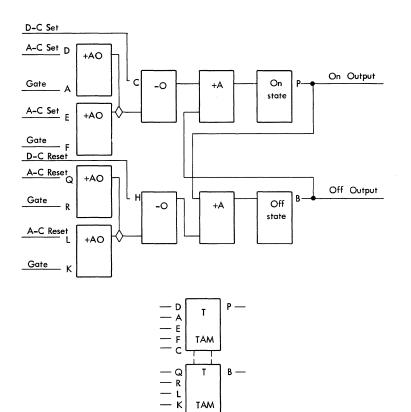

| 113.           | TAM Logic                                                                      | 95                |

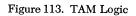

| 114.           | TAM Timings                                                                    | 95                |

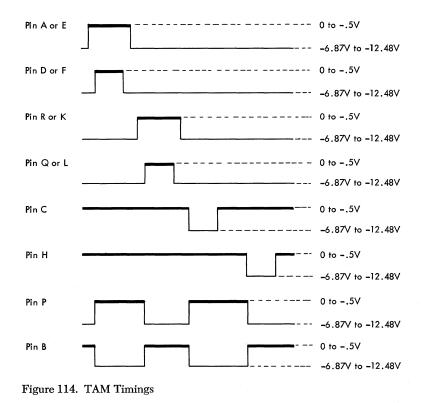

| 115.           | IBM 1411 CE Panel                                                              | 97                |

| 116.           | Address Stop or Scope Sync                                                     | 98                |

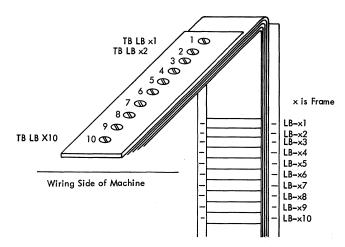

| 117.<br>118.   | 1411 CE Panel Address Stop and Keyboard Control .<br>Laminar Bus Pin Locations | 99<br>100         |

| 110.<br>119.   | IBM 1405 and 1414A Power-Supply Locations                                      | $\frac{100}{100}$ |

| 120.           | Frame Designation Large Chassis (Wiring Side)                                  | 104               |

| FIGURE |

|--------|

|--------|

TITLE

| PAGE |

|------|

|------|

| 121. | Frame Designation, Tape Adapter Unit (Wiring       |     |

|------|----------------------------------------------------|-----|

|      | Side)                                              | 104 |

| 122. | Frame Designation, I/O Synchronizer (Wiring        |     |

|      | Side)                                              | 104 |

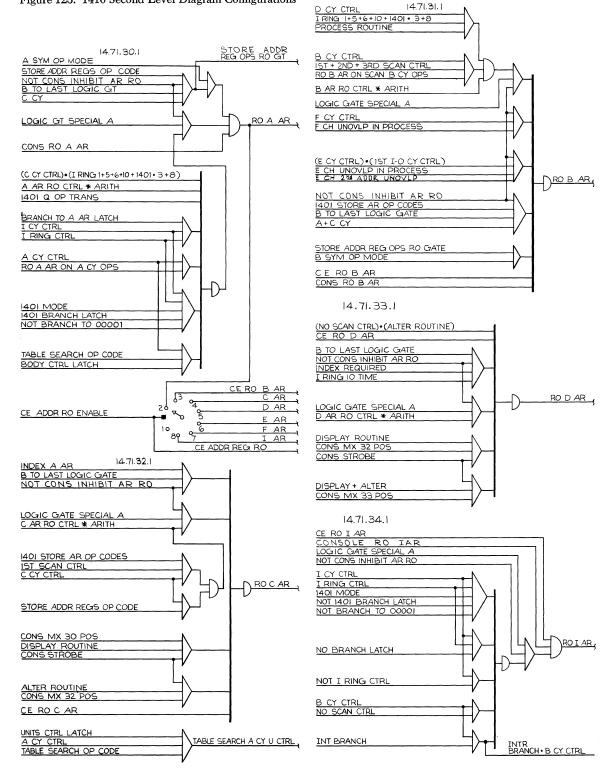

| 123. | 1410 Second Level Diagram Configurations           | 105 |

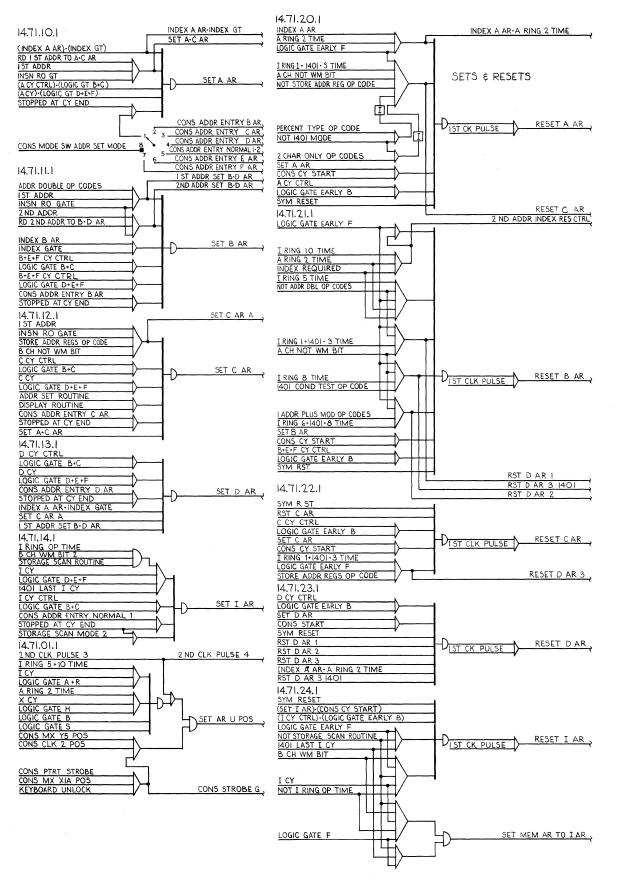

| 124. | ADDR Registers Read-Out CTRLS                      | 105 |

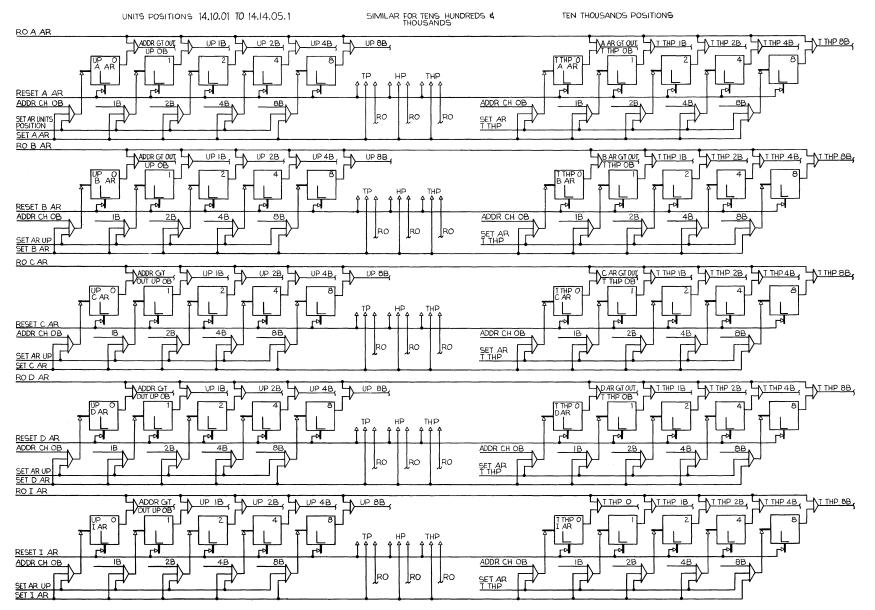

| 125. | Address Register Sets and Resets                   | 106 |

| 126. | AAR, BAR, CAR, DAR, and IAR Latches                | 107 |

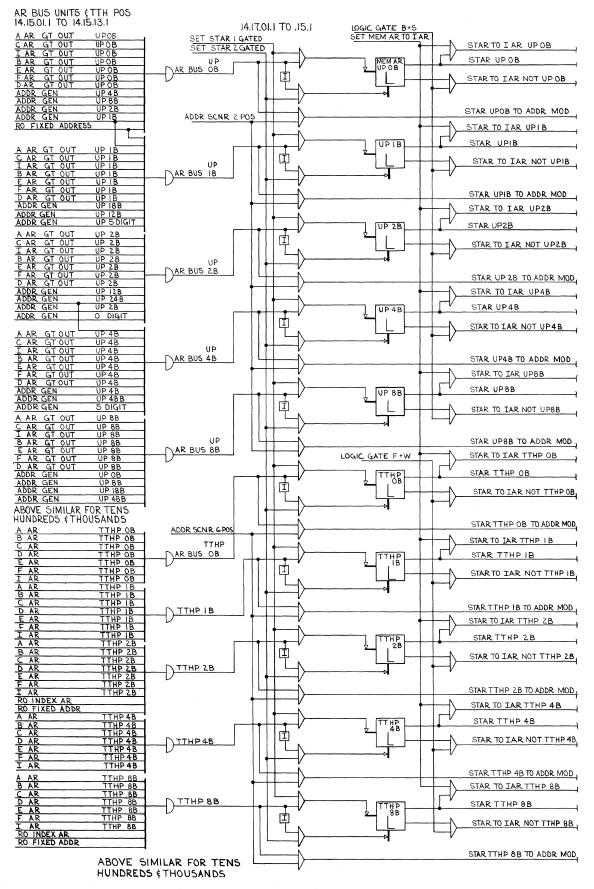

| 127. | AR Bus and MEM AR to IAR Latches                   | 108 |

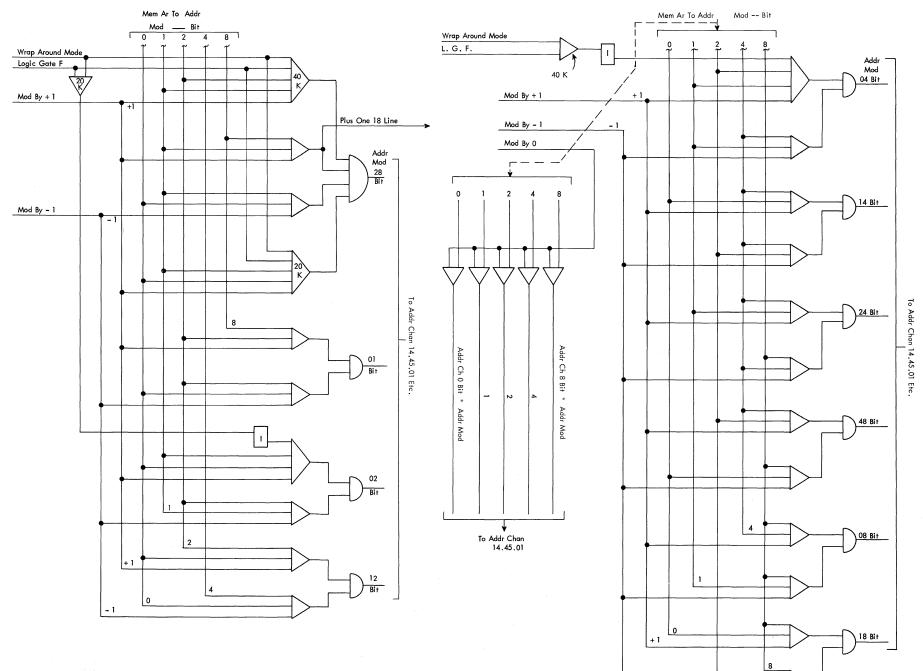

| 128. | Address Modification                               | 109 |

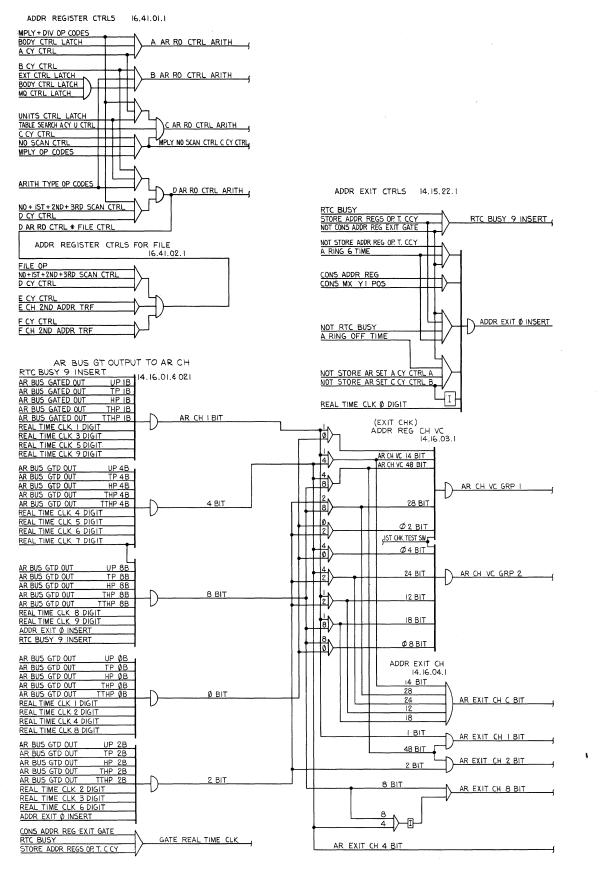

| 129. | ADDR REG CTRLS, ADDR Bus Gated, ADDR EX            |     |

|      | CH and EX CHK                                      | 110 |

| 130. | Cycle CTRLS, Cycle Length CTRLS, and Special       |     |

|      | Logic Gates                                        | 111 |

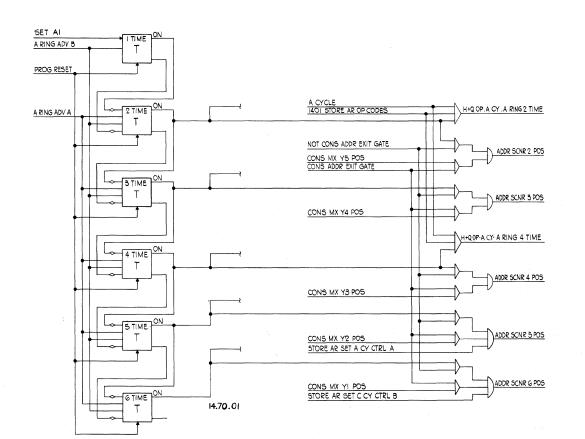

| 131. | A and I Ring Controls                              | 112 |

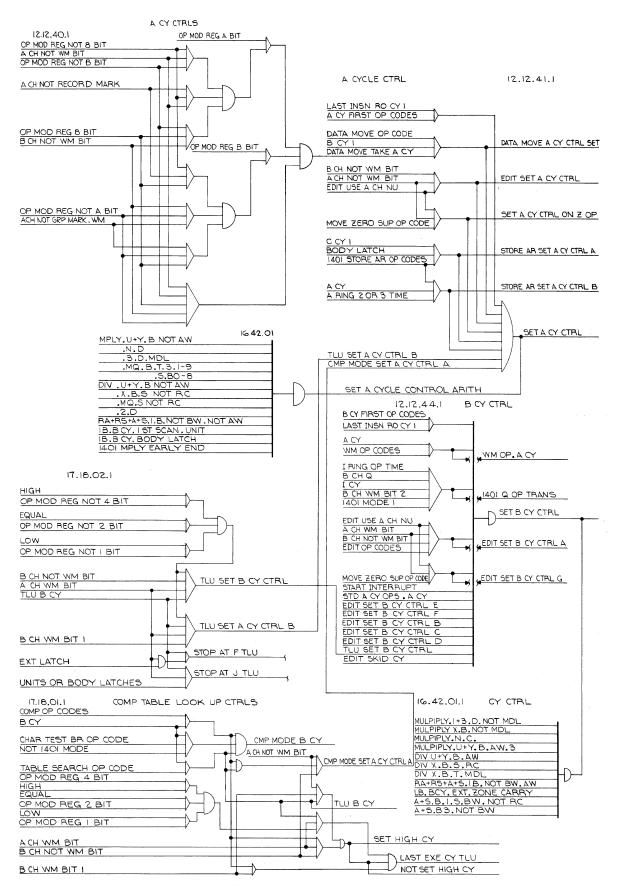

| 132. | A and B Cycle Controls                             | 113 |

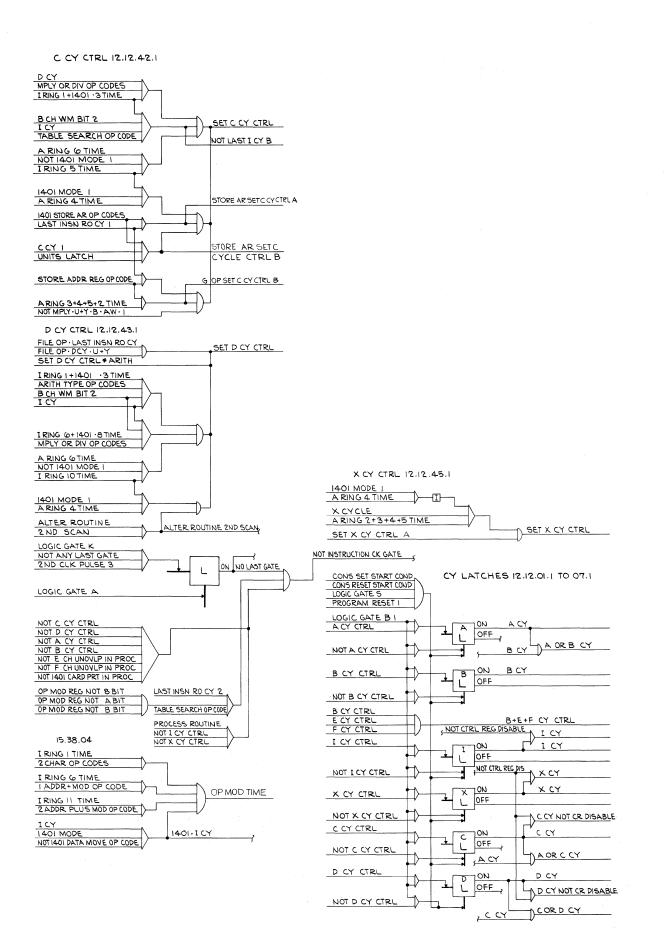

| 133. | C, D, I, X Cycle Controls                          | 114 |

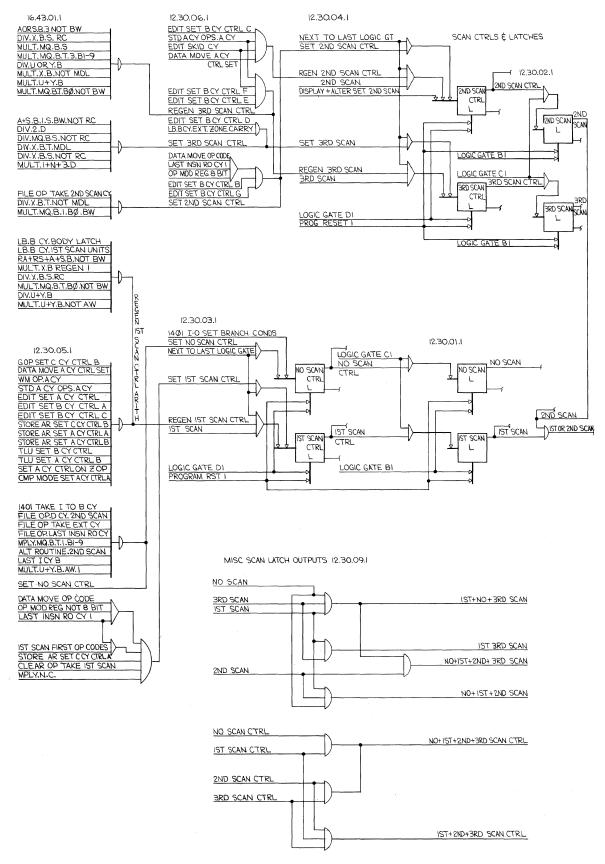

| 134. | Scan Controls and Latches                          | 115 |

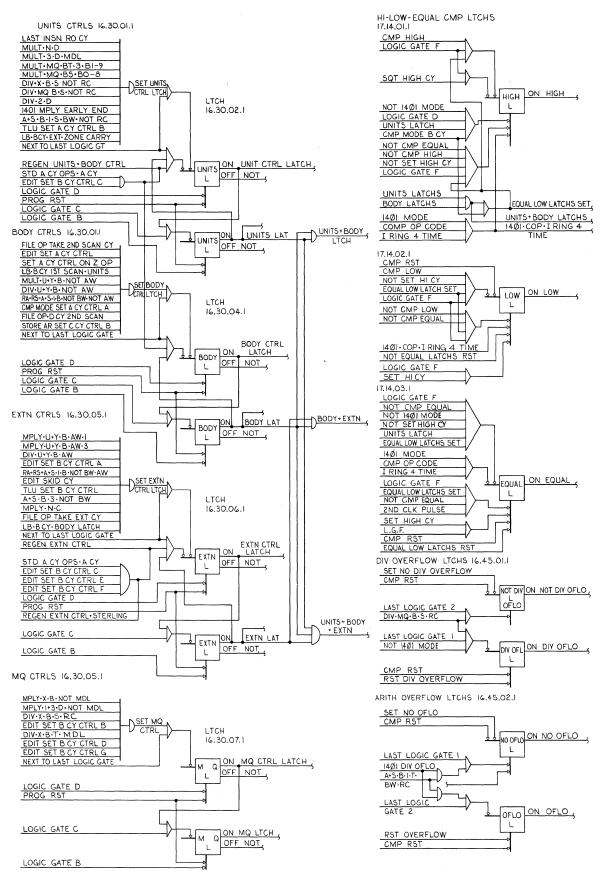

| 135. | Units, Body, Extension, MQ Controls, and Divide    |     |

|      | and Arith Overflow Latches                         | 116 |

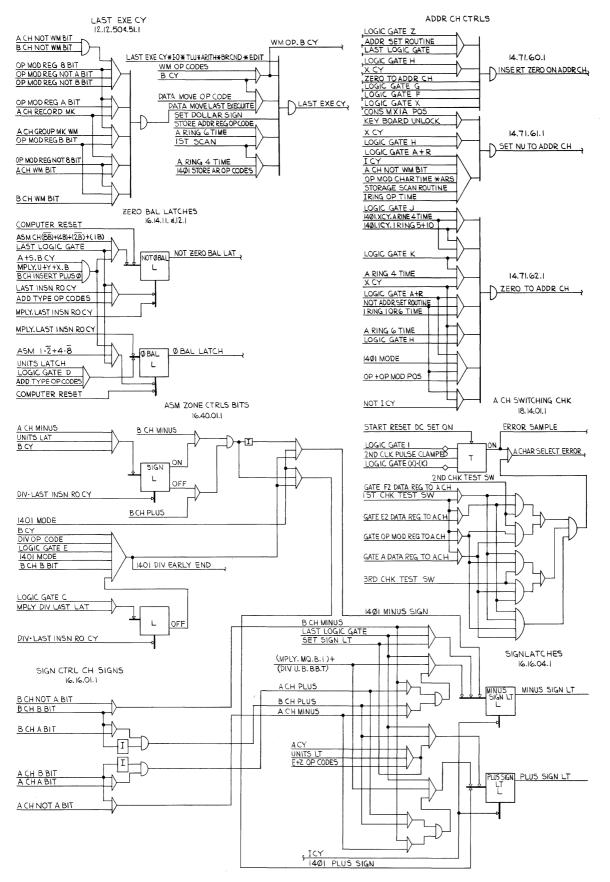

| 136. | Address Channel Controls, Last Execute Cycle, Bal- |     |

|      | ance Zero and Sign Controls, and Latches           | 117 |

| FIGUE                | RE TITLE                                                                                                                                                           | PAGE                                     |

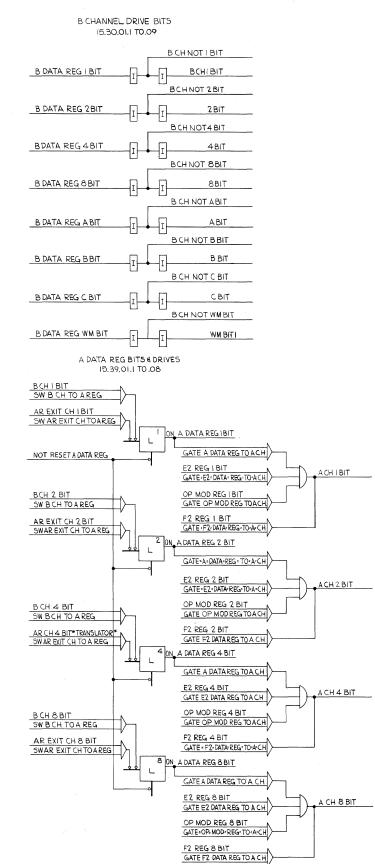

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

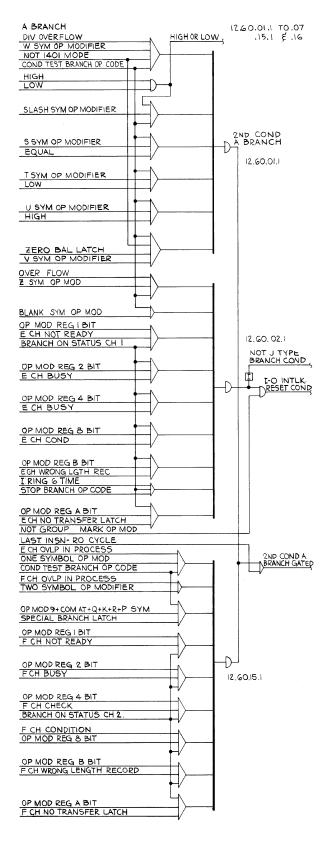

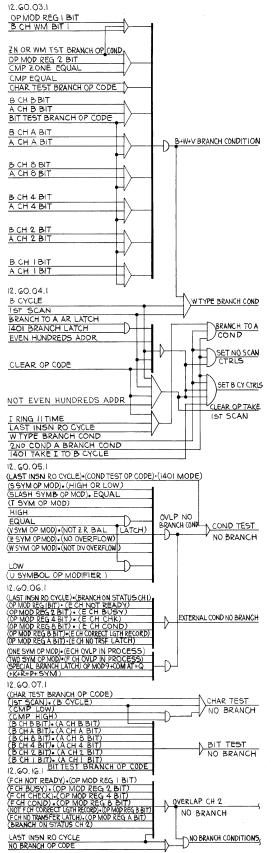

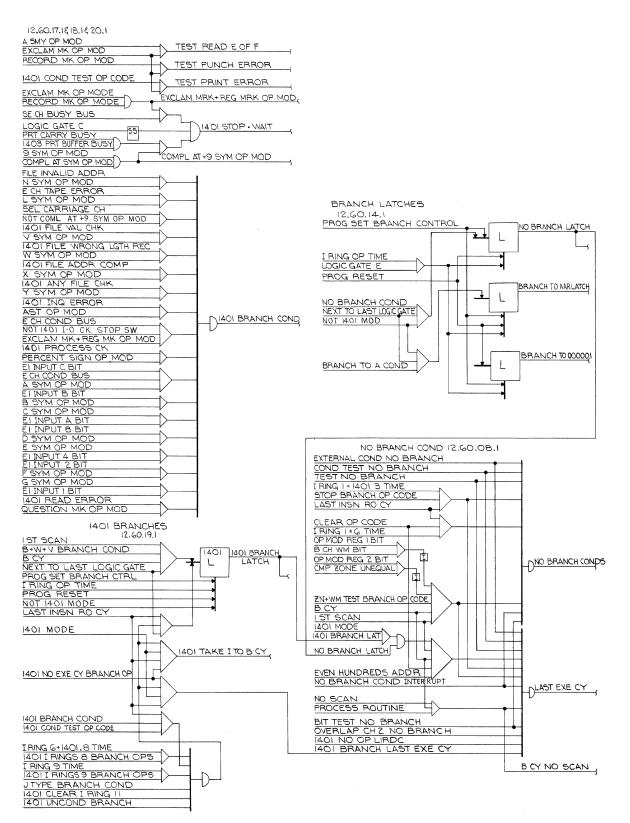

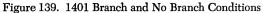

| 138.<br>139.         | A and B Bits, Drives and Channel Characters<br>Branch Conditions                                                                                                   | $\begin{array}{c} 119\\ 120 \end{array}$ |

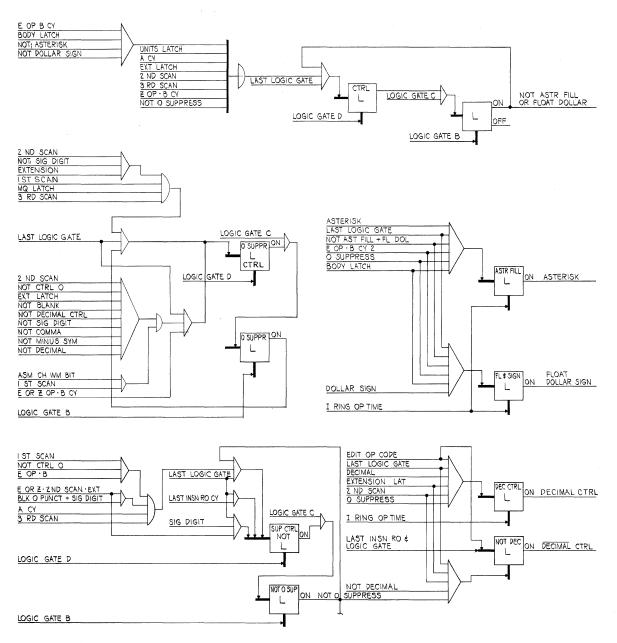

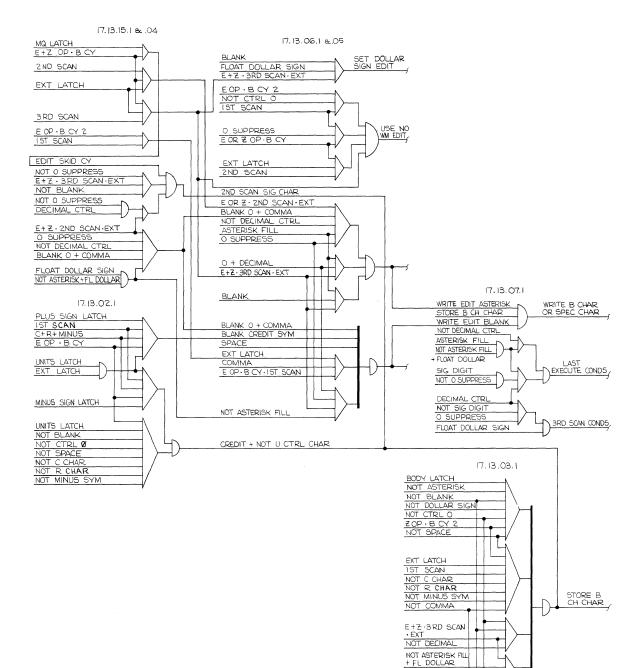

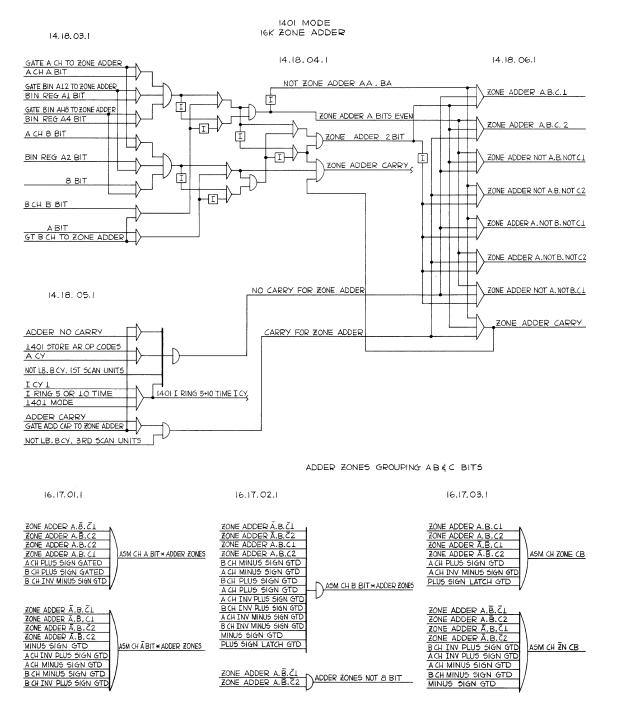

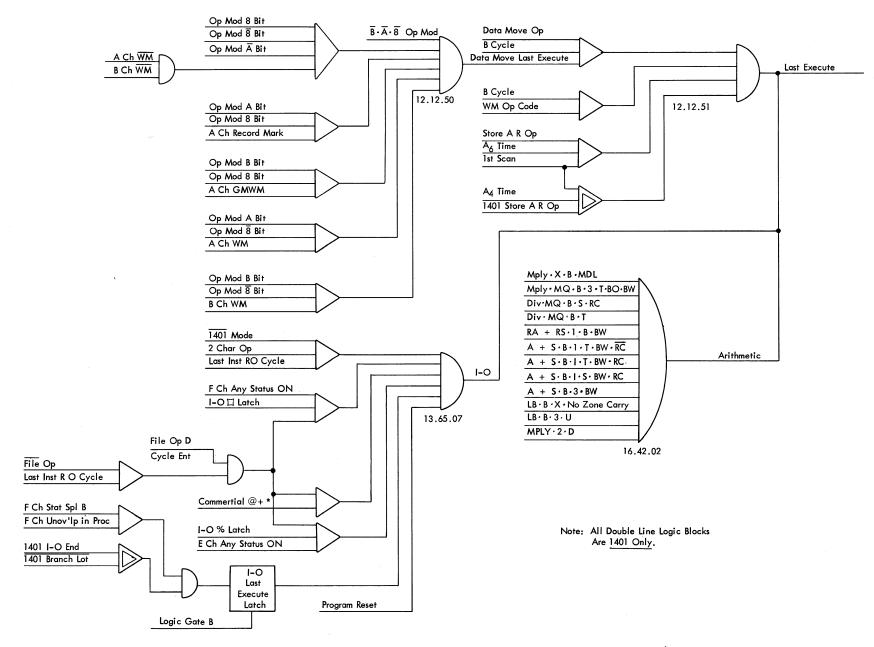

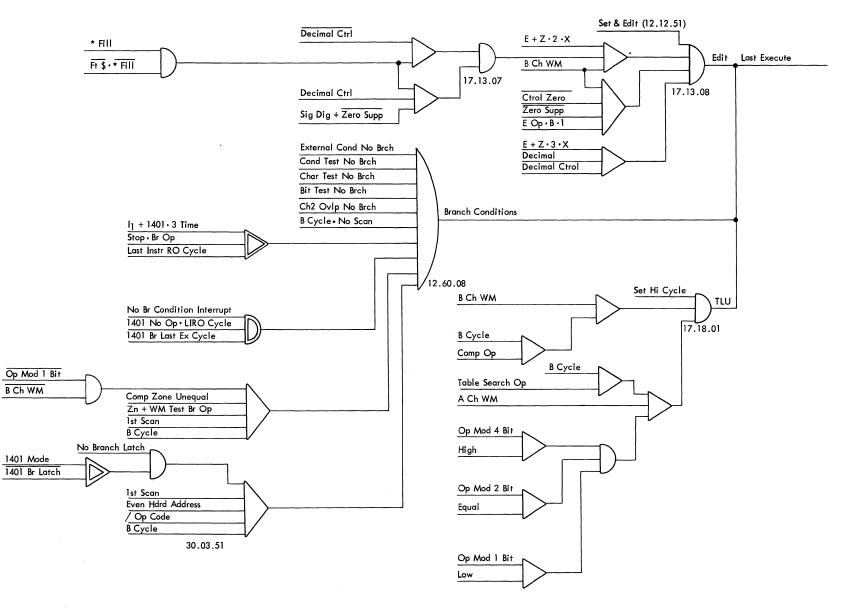

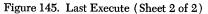

| 142.<br>143.<br>144. | Edit Latches         Edit Controls         Indexing         16K Zone Adder and Grouping         Last Execute (Sheets 1 and 2)                                      | $123 \\ 124 \\ 125$                      |

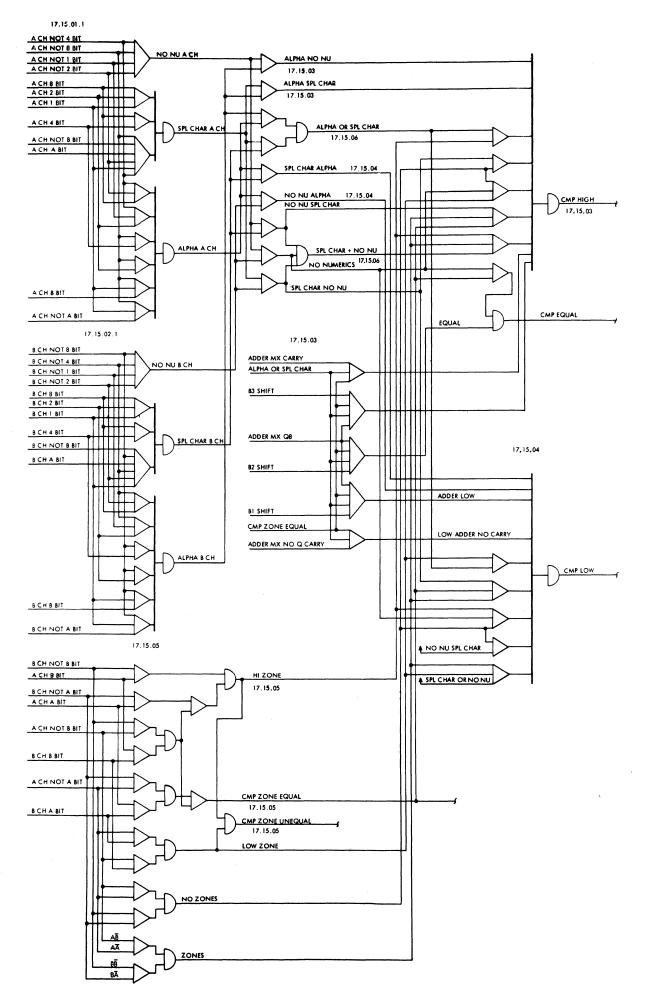

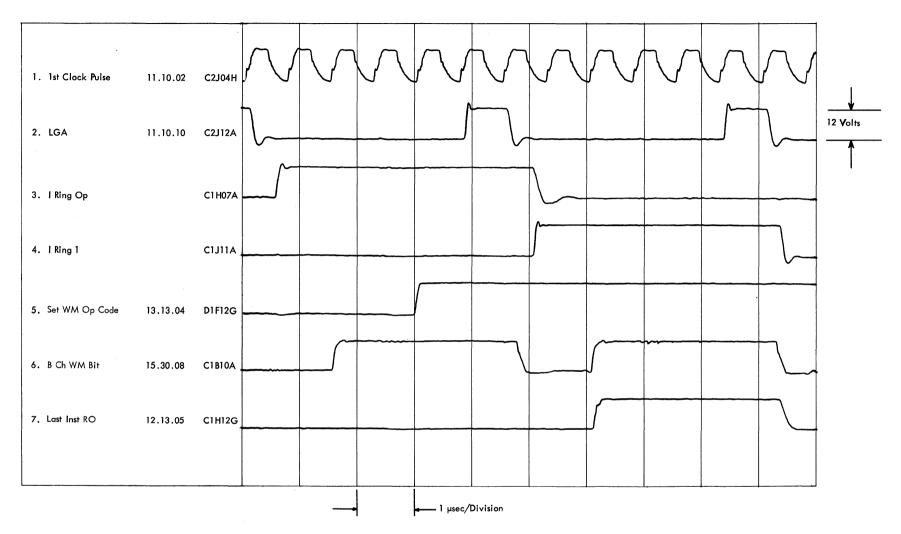

| 147.<br>148.<br>149. | Last Instruction Read-Out<br>1410 Power Distribution<br>Compare Matrix<br>One Character Instruction Read-Out Op Code<br>Six Character Instruction Read-Out Op Code | $129 \\ 130 \\ 131$                      |

| 152.                 | Eleven Character Instruction Read-Out Op Code<br>Add Execute Phase Op Code (Sheet 1 and 2)134<br>Subtract Execute Phase Op Code (Sheet 1 and 2)                    | , 135                                    |

| 154.                 | Data Move Execute Phase Op Code (Sheet 1 and 2)                                                                                                                    | , 137<br>, 139                           |

| 155.                 | Compare Execute Phase                                                                                                                                              |                                          |

# PAGE

The IBM 1410 Data Processing System is an intermediate-range computer that has a variety of storage capacities, optional features, and input-output devices designed to meet customer needs. To process data, the 1410:

1. Receives data and instructions from an input device: card reader, paper tape reader, etc.

2. Stores the data and instructions until they are needed.

3. Adds, compares, edits, or performs other data operations.

4. Delivers the results of these operations to an output device: card punch, printer, etc.

The 1410 is made up of five functional units: input, storage, control, operational, and output. These units, controlled by instructions, process data.

# **Operation of Functional Units**

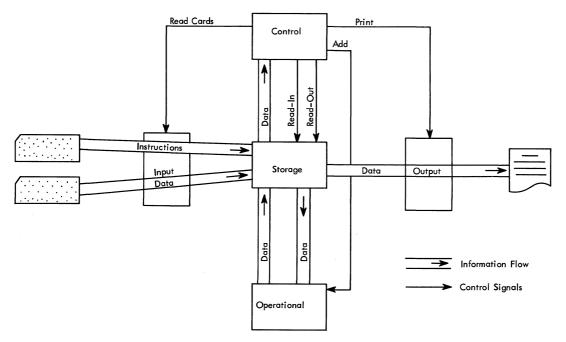

The five functional units of the 1410 operate as follows (Figure 1):

1. An *input device*, such as a card reader, feeds data and instructions into the computer. Data consists of alphameric information on which specific operations are performed by the computer. Instructions consist of characters that determine the operations according to a particular code utilized by the 1410. The character A, used as the first character of an instruction, signifies an add operation.

2. The *storage unit* receives both the data and the instructions and retains them for use as they are needed. Each unit of information is stored in a numbered location, called an address, in storage. The 1410 uses a fivecharacter-position address, i.e., 04322, 06744, etc. If the contents of a specific area in storage are needed for an operation, these contents are read out and sent to the appropriate unit.

3. The *control unit* receives the instructions, one character at a time, from storage. The control unit interprets each instruction to determine appropriate action. When interpreting the A (add) instruction, for example, the control unit requests the storage unit to read out the data to be added together and sends it to the operational unit. The address of the data to be added is in another part of the instruction.

4. The operational unit contains all units necessary to add, compare, edit or move data. This unit performs these operations, which are specified by the instruction,

Figure 1. Operation of Functional Units

under command of the control unit. The results are returned to storage.

5. Obeying a subsequent instruction, the control unit requests the storage unit to read out the results of a particular operation. These results are then sent to an *output device*, such as a printer or a card punch.

# Operating Fundamentals of a Computer System

With the add operation as an example, note these important fundamentals of computer operation:

1. A single instruction causes the computer to execute only one operation, i.e., add, compare, edit, or print. To perform a payroll operation, for example, the computer must be given many instructions. A group of sequential instructions with the objective of performing a particular job is called a program.

2. All five functional units are interdependent. The control unit cannot function without the storage unit as a source of instructions. The adder, which is part of the operational unit, depends on storage as a source of data. The units of a computer thus work together as parts of a complete system that processes data.

3. All information entering or leaving the computer must pass through storage. Input data cannot go directly from the input unit to the adder; results cannot go directly from the adder to the output unit.

# 1410 Components

### IBM 1411 Processing Unit

The IBM 1411 Processing Unit (CPU) contains the magnetic core storage unit and the controlling circuitry of the IBM 1410 system, as well as various data and address registers, logic and checking circuits, etc., associated with the flow of data in the 1410. The 1411 is available in five models ranging in capacity from 10,000 to 80,000 positions of magnetic-core storage.

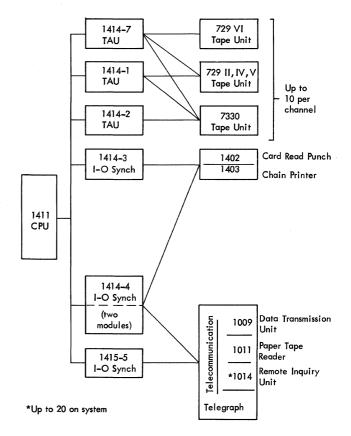

#### IBM 1414 Input-Output Synchronizer

The IBM 1414 Input-Output Synchronizer contains the circuitry necessary for transmitting data to and from the processing unit and various I-O units. The 1414 is available in several models, depending on the type of I-O units used (Figure 2). In addition to the control circuitry necessary to transmit data, the 1414 contains checking circuits to insure accurate transfer of data to and from the CPU and the I-O units. Two data channels are available: Channel 1 (E Channel), Channel 2 (F Channel). (Channel 1 is standard; Channel 2 is optional.)

Figure 2. Synchronizer Models Required for Each I-O Device

### IBM 1415 Console and Input-Output Printer

The IBM 1415 Console provides operator communication with the 1410 System. The console consists of a control section containing the keys and switches that control the 1410 System, an indicator panel, and the system I-O printer. Through the console, the operator can enter or display storage data. Console controls simplify program testing and customer engineering maintenance. The I-O printer prints all 64 characters valid in the 1410.

#### IBM 1402 Card Read Punch

The IBM 1402-2 Card Read Punch contains two separate unit-record devices under one cover. The card reader processes 800 cards per minute, and the card punch processes 250 cards per minute. Through the 1414-3, the reader sends data into the CPU via an 80position read buffer, and the punch receives data from the system via an 80-position punch buffer.

### **IBM 1403 Printer**

The IBM 1403 Printer produces output documents with 100 or 132 characters per line at 600 or 1,285 lines per minute. The standard alphameric chain can print 48 different characters in each position, and the optional numeric chain feature can print 16 characters in each position. With this feature installed, the 1403 printing speed increases to 1,285 lines per minute.

A dual-speed carriage controlled by a closed loop of paper tape permits skipping at 33 inches per second (low speed) or at 75 inches per second (high speed), depending on the length of the skip.

### IBM 729 and IBM 7330 Magnetic Tape Units

Four models (II, IV, V, or VI) of the IBM 729 Magnetic Tape Unit or the IBM 7330 Tape Unit can be attached to the 1410 System. The 729 Tape Units are used when the goal is high volume and high speed. The 7330 Tape Units are used where volume and speed justify a lower cost tape system. All units have dual recording densities (characters per inch), enabling transfers of tape reels from one IBM system to another.

### IBM 1405 Disk Storage

The IBM 1405 Disk Storage can retain 20 million characters of information, maximum. Data are stored in the form of magnetized spots on the surface of the circular disks that are coated with a magnetic oxide material. Storage disks are mounted on a vertical shaft that turns at a speed of 1,200 revolutions per minute. Data can be recorded on both sides of each disk.

Read-write heads, mounted on movable access arms, read and write on the disk faces. The arms seek specified records in the disk-storage unit by moving up or down and in or out to the desired record. Maximum character rate is approximately 25,000 characters per second.

### IBM 1301 Disk Storage

The IBM Disk Storage can retain as many as 56 million characters of information on circular disks similar to those of the 1405. In the 1301, however, each surface has its own read-write head. This reduces maximum access time to 180 milliseconds. Disk rotation of 1,800 rpm results in a maximum character rate of 90,000 characters per second.

### IBM 1412 and IBM 1419 Magnetic Character Readers

Attaching an IBM 1412 or IBM 1419 Magnetic Character Reader to a 1410 System provides banks with a timesaving method of reading and processing large numbers of daily transactions. These machines handle card or paper documents (or both intermixed) inscribed with the E13B type font designated by the American Bankers Association.

Documents can be read into the 1410 System at a maximum rate of 950 per minute with the 1412, or 1,600 per minute with the 1419. While the data entering the

1410 via the magnetic character reader are being processed, the actual documents are stacked in pockets selected by the stored program.

Two 1412 readers or two 1419 readers can be attached to a 1410 System. Each magnetic character reader, however, must be connected to a different data channel. A single magnetic character reader can be attached to either channel 1 or channel 2.

### IBM 7750 Programmed Transmission Control

The IBM 7750 Programmed Transmission Control serves as a buffer and telecommunications message control unit that links the 1410 System with a variety of remote transmitting and receiving terminal devices. The 7750 stored program assembles messages, distributes messages under priority to and from the network, converts codes, edits, checks messages for validity, etc., while directing data at high character rates to and from the host 1410.

One 7750 can be assigned to a system, provided the system has a 1411 Processing Unit having an A-suffixed model number, a control adapter, and the priority and processing overlap features.

### IBM 1009 Data Transmission Unit

The IBM 1009 Data Transmission Unit is the intermedium for high-speed two-way communication between the 1410 System and another 1009 (or a 1009 simulated by a 7750 Programmed Transmission Control) attached to any 1400- or 7000-series data processing system. Data are transmitted or received over message-service or leased-wire circuits at fixed character rates ranging from 75 to 300 per second.

The 1414-4 or 1414-5 1-0 Synchronizer allows the 1410 System to continue processing during a 1009 operation. Data are transferred to or from the processing unit via two 80-position buffers.

### IBM 1011 Paper Tape Reader

One IBM 1011 Paper Tape Reader can be attached to a 1410 System providing for data sources stored on paper tape. Data can be read at up to 500 characters per second. The paper tape can be in the widths commonly used for five-, six-, seven-, or eight-track tape, in strips, reels, or rolls that feed from the center, and can be chad or chadless.

The 1414-4 or 1414-5 1-0 Synchronizer allows the system to continue processing during a paper tape reading operation. Data are read into the processing unit via an 80-position buffer.

### IBM 1014 Remote Inquiry Unit

A 1410 System containing one or more IBM 1014 Re-

mote Inquiry Units can reply to remote or local requests for information. Each 1014, whether installed locally or remotely, receives and prints almost instantaneous replies from the 1410 and prints both the inquiry and the reply at character rates up to 12½ per second for the inquiry and 15½ per second for the reply. A modified 1-0 printer is used.

An adapter, in a 1414-4 or 1414-5 1-0 Synchronizer, controls and sequences the acceptance by the 1410 of request messages from as many as ten 1014 remote inquiry units. Either one or two adapters can be installed in the 1414 to handle up to ten remote inquiry units each. With two adapters, two 1014 remote inquiry units controlled by separate adapters can transmit or receive at the same time.

The 1414 also allows the system to continue processing during a 1014 operation. Inquiries and replies are transferred to and from the processing unit via two 80position buffers, one for input and one for output, in each adapter.

#### **Program Addressable Clock**

The program addressable clock, which can be installed in the 1415 Console, provides a method of logging system time. Clock time can be obtained by the program for recording any start or stop point or other event. Time is indicated in 24-hour (continental) style, and each hour is graduated in hundredths.

Among the many uses or aids provided by the program addressable clock are:

1. Better scheduling of system time through time studies of previous jobs.

2. Determining exact processing time, system setup time, program testing time, maintenance time, and idle time.

3. Distributing more accurate job charges to users of the system.

4. Logging the time of the telecommunication messages.

#### **Telegraph Input-Output**

Installation of the telegraph input-output feature in a 1414-4 or 1414-5 permits connection of a telegraph network to the 1410 System. Data can thus be accepted directly by the 1410 from any station in the network or transmitted directly from the 1410, through local telegraph terminals, to any or all of the stations.

The 1414 I-O Synchronizer allows the system to continue processing during a transfer to or from the telegraph network. The feature consists of one input adapter and one output adapter in the 1414. One or two more adapters can be added; these additional adapters can consist of one input or output adapter (or both), or two input or two output adapters. Data are transferred to and from the telegraph via 80-position buffers, one for each input or output adapter.

## 1410 Fundamentals

### **Machine Language**

Normally, individual units of a coding system are referred to as bits of information or "bits." All components in a computer are always in one of two possible states: a line is active or inactive, a latch is on or off, a trigger is set or reset, a magnetic core is magnetized in one direction or the other. Components that operate in this manner—on or off, set or reset—are called binary. When a latch is on, it represents the presence of a bit; when it is off, it represents the absence of a bit. The three coding systems used by the 1410 use this principle. Various bit combinations represent all alphameric characters valid to the system.

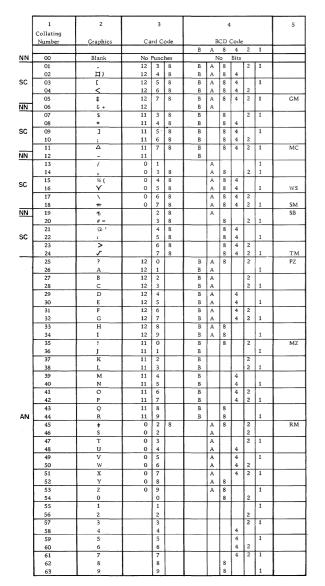

#### BINARY CODED DECIMAL

In the binary coded decimal (BCD) system, the numeric values are expressed in combinations of four bits (Figure 3). Each of these bits is assigned a value of 1, 2, 4, or 8. Combinations of these bits make up any of the 10 digits. A 5 would be represented by a 1 bit and a 4 bit; a 7 would be represented by a 1, 2, and 4 bit. Two additional bit positions, B and A, handle the zone information of alphabetic and special characters. The combination of B and A bit represents the 12-zone portion of a character. The B bit only represents the 11 zone; the A bit only represents the 0 zone.

1410 System reliability is improved by checking each character to insure that an odd number of bits is present. Because many bit combinations do not naturally contain an odd number of bits, a seventh bit position is made available in which a check or C bit can be stored when necessary to make the total bit count odd. The proper number of bits for any given character is the *parity* of that character. The checking of bit count per character is *parity checking*.

#### TWO-OUT-OF-FIVE CODE

The two-out-of-five code (2/5) as used by the 1410 is strictly a numeric code (Figure 4). Numeric values are expressed in combinations of two out of the five bits (0, 1, 2, 4, and 8) used to make up this code. Therefore, a 5 is a bit 4 and bit 1 combination; a 7 is a bit 8 and bit 4 combination. An important advantage of the 2/5code is convenient error checking. Because every digit is expressed by only two bits, any digit position with more or fewer than two bits is in error and a validity check light is turned on to indicate an invalid bit combination.

| 1                   | 2           | 3                | 4                                                               | 5    |

|---------------------|-------------|------------------|-----------------------------------------------------------------|------|

| Collating<br>Number | Graphics    | Card Code        | BCD Code                                                        |      |

| 00                  | Blank       | No Punches       | B A 8 4 2 1<br>No Bits                                          |      |

| 00                  |             | 12 3 8           | B A 8 2 1                                                       |      |

| 02                  | <u>п)</u>   | 12 4 8<br>12 5 8 | B         A         8         4                                 |      |

| 03<br>04            | t<br><      | 12 5 8<br>12 6 8 | B A 8 4 1<br>B A 8 4 2                                          |      |

| 05                  | ŧ           | 12 7 8           | B A 8 4 2 1                                                     | GM   |

| 06 07               | • & +<br>\$ | 12<br>11 3 8     | B A B 2 1                                                       |      |

| 08                  | *           | 11 4 8           | B 8 4                                                           |      |

| 09<br>10            | ]           | 11 5 8<br>11 6 8 | B 8 4 1<br>B 8 4 2                                              |      |

| 10                  | ;<br>       | 11 7 8           | B 8 4 2 1                                                       | MC   |

| 12<br>13            | - /         | 11<br>0 1        | B A 1                                                           |      |

| 13                  | ,           | 0 3 8            | A 8 2 1                                                         |      |

| 15<br>16            | % (<br>Y    | 0 4 8<br>0 5 8   | A 8 4<br>A 8 4 1                                                | WS   |

| 10                  | Y \         | 0 5 8            | A 8 4 1<br>A 8 4 2                                              | vv 3 |

| 18                  | #           | 0 7 8            | A 8 4 2 1                                                       | SM   |

| 19<br>20            | ъ<br># =    | 2 8<br>3 8       | A 8 2 1                                                         | SB   |

| 21                  | @ '         | 4 8              | 8 4                                                             |      |

| 22                  | :           | 58               | 8         4         1           8         4         2           |      |

| 24                  | ~           | 7 8              | 8 4 2 1                                                         | ТМ   |

| 25<br>26            | ?<br>A      | 12 0<br>12 1     | B A 8 2<br>B A 1                                                | PZ   |

| 27                  | В           | 12 2             | B A 2                                                           |      |

| 28<br>29            | C<br>D      | 12 3<br>12 4     | B A 2 1<br>B A 4                                                |      |

| 30                  | E           | 12 5             | B A 4 1                                                         |      |

| 31<br>32            | F<br>G      | 12 6<br>12 7     | B A 4 2<br>B A 4 2 1                                            |      |

| 33                  | H           | 12 8             | B A 8                                                           |      |

| 34<br>35            | I<br>!      | 12 9<br>11 0     | B         A         8         1           B         8         2 | MZ   |

| 35                  | J           |                  | B   1                                                           | IVIZ |

| 37                  | К           | 11 2             | B 2                                                             |      |

| 38<br>39            | L<br>M      | 11 3<br>11 4     | B 2 1<br>B 4                                                    |      |

| 40                  | N           | 11 5             | B 4 1                                                           |      |

| 41 42               | O<br>P      | 11 6<br>11 7     | B 4 2<br>B 4 2 1                                                |      |

| 43                  | Q           | 11 8             | B 8                                                             |      |

| 44 45               | R +         | 11 9<br>0 2 8    | B 8 1<br>A 8 2                                                  | RM   |

| 46                  | S           | 0 2              | A 2                                                             |      |

| 47<br>48            | T<br>U      | 0 3<br>0 4       | A 2 1<br>A 4                                                    |      |

| 49                  | V           | 0 5              | A 4 1                                                           |      |

| 50<br>51            | W<br>X      | 0 6              | A 4 2<br>A 4 2 1                                                |      |

| 52                  | Y           | 0 8              | A 8 4 2 1<br>A 8                                                |      |

| 53                  | Z           | 0 9 0            | A 8 1<br>8 2                                                    |      |

| 54<br>55            | 0           |                  |                                                                 |      |

| 56                  | 2           | 2                | 2                                                               |      |

| 57<br>58            | 3           | 3 4              |                                                                 |      |

| 59                  | 5           | 5                | 4 1                                                             |      |

| 60<br>61            | 6 7         | 6 7              |                                                                 |      |

| 62                  | 8           | 8                | 8                                                               |      |

| 63                  | 9           | 9                | 8 1                                                             |      |

Figure 3. Standard BCD Interchange Code

| 2/5 Bits |   |   |   |   |   |  |  |  |

|----------|---|---|---|---|---|--|--|--|

|          | 0 | 1 | 2 | 4 | 8 |  |  |  |

| 0        |   |   | x |   | x |  |  |  |

| 1        | x | x |   |   |   |  |  |  |

| 2        | х |   | х |   |   |  |  |  |

| 3        |   | х | x |   |   |  |  |  |

| 4        | x |   |   | x |   |  |  |  |

| 5        |   | х |   | x |   |  |  |  |

| 6        |   |   | x | x |   |  |  |  |

| 7        |   |   |   | x | x |  |  |  |

| 8        | x |   |   |   | x |  |  |  |

| 9        |   | x |   |   | х |  |  |  |

Figure 4. Two-Out-of-Five Code

#### QUI-BINARY CODE

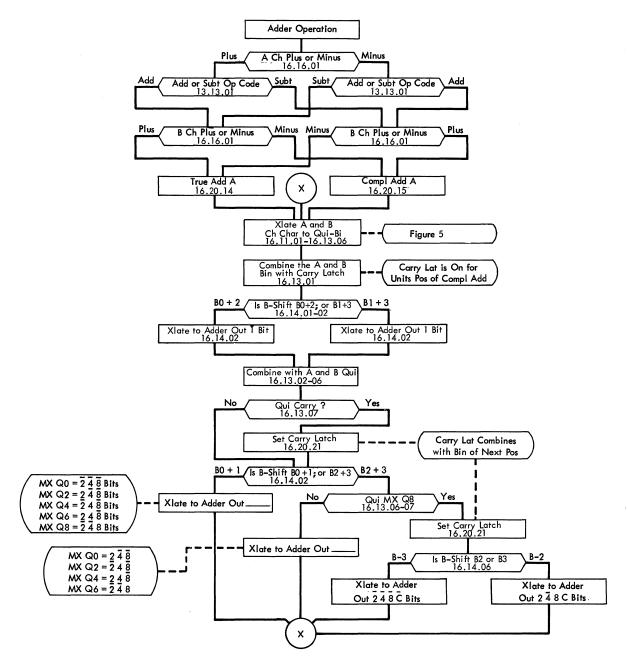

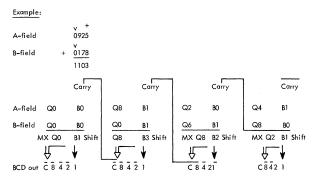

1410 arithmetic units use qui-binary representation of numeric characters (Figure 5). The qui-binary code offers more advantages than BCD in numeric addition and carry generation. During operations involving the arithmetic unit, data in BCD form is translated into quibinary, treated arithmetically, and retranslated into BCD. To translate from BCD to qui-binary, the 1 bit becomes a binary 1 (B1). The 2, 4 and 8 bits become a quinary 0, 2, 4, 6, or 8 (Q0, Q2, Q4, Q6, or Q8). For example a 9 in qui-binary is a B1 and a Q8; an 8 is a B0 and Q8; a 1 is a B1 and Q0; etc.

### **Packaging and Component Parts**

All units of the IBM 1410 System use the standard modular system (SMS) concept of design. Electronic circuitry is completely solid-state, using transistors and

| Card Code | BCD   | True Add | Complement Add |

|-----------|-------|----------|----------------|

| 0         | 8.2   | Q0 B0    | Q8 B1          |

| 1         | 1     | Q0 B1    | Q8 B0          |

| 2         | 2     | Q2 B0    | Q6 B1          |

| 3         | 1.2   | Q2 B1    | Q6 BO          |

| 4         | 4     | Q4 B0    | Q4 B1          |

| 5         | 1.4   | Q4 B1    | Q4 B0          |

| 6         | 2.4   | Q6 B0    | Q2 B1          |

| 7         | 1.2.4 | Q6 B1    | Q2 B0          |

| 8         | 8     | Q8 B0    | Q0 B1          |

| 9         | 1.8   | Q8 B1    | Q0 B0          |

Figure 5. Qui-Binary Code

magnetic cores. Maximum usage is made of saturating drift transistor registor logic (SDTRL) circuits. These circuits are used because of their reliability, high speed, and low cost. All circuitry is in the form of plugable cards containing transistors and their associated circuits.

#### **Storage Principles**

Magnetic core storage is used in the IBM 1411 Central Processing Unit. Characters are stored in the corestorage unit in binary-coded decimal (BCD) form. This requires seven bit locations, or core planes (C, B, A, 8, 4, 2, 1) for each character position. An eighth core plane provides for the storage of word marks (see "Word Mark").

### ADDRESSING

Core-storage units are available with 10,000, 20,000, 40,000, 60,000, or 80,000 character positions. The arrays are arranged so that each character position can be individually addressed.

Each core-storage address is five character positions. Valid addresses for a machine with 10,000 characters of storage are 00000 to 09999. Valid addresses for a machine with 20,000 characters of storage are 00000 to 19999. Valid addresses for a maximum-capacity machine with 80,000 characters of storage are 00000 to 79999.

An attempt to use an invalid address results in an error. The numeric portion of the five-character address must consist only of valid numbers from 0 to 9. An attempt to use special character or blank codes in addresses results in an error-stop (address validity). The zone bits over the tens and hundreds positions are reserved for index tags as explained in "Indexing." The units-, thousands-, and ten-thousands-positions must contain a no-zone indication, or an error stop results.

Core storage addressing is as follows:

1. To address an instruction in core storage, specify the location of the high-order character (operation code).

2. Data fields to be moved from one core storage area to another, or fields to be operated on arithmetically, are addressed by specifying the location of the low-order character of the field. Characters are moved or operated on arithmetically in a low- to high-order sequence.

3. For all data movements that originate or terminate outside the core storage, and for record moves within core storage, the data is addressed by specifying the location of the high-order character. Therefore, data addresses of all input-output operations, including the file, specify the location of the high-order character. On an I-O operation, characters are moved from high to low order. NOTE: Low order and high order refer to the positions of an instruction word or a data word as they would appear on a printed form or as a field in a card. Do not confuse these terms with the storage addresses which are numbered left to right, low to high in relation to a data word or an instruction word.

### DATA WORD

A data word is one complete unit of information that is comparable to a field in a card, such as an account number.

### VARIABLE WORD LENGTH

A data word may be a single character, or a group of characters. Words are not limited to any fixed number of character positions in the storage unit.

#### WORD MARK

To define the length of a word, a word mark is stored as a single bit in the eighth core plane of storage in the high-order position of that word. This word-mark coreplane is in all storage positions. Thus, the high-order position of a word can be placed at any storage address.

#### SCANNING

The core-storage unit can read out only one character at a time. A whole word must be read out character by character. The order in which these characters are read out is determined by the machine. For example, when two fields are added together, the units position of the fields must be read out first to determine the signs of the fields. Information read out to an output machine is read out high order to low order.

The treatment of these words, character by character, is known as scanning. Reverse scanning is the reading out from high order to low order, as in reading out to I-O machines. Forward scanning is the reading out of the low-order position first.

### **Stored Programming**

The IBM 1410 System is controlled entirely by stored programming. A sequence or program routine of operations is stored or loaded in the core-storage unit before the system processes data. The processing unit then proceeds, step by step, through the stored-program routine, analyzing each instruction and performing the function called for before proceeding to the next instruction.

Just as program routines or jobs in the machines using control panels can be changed by changing control panels, a stored-program routine can be changed by loading a new routine into the storage unit via an input machine.

### INSTRUCTION WORD

The instructions in core storage consist of a variable number of alphameric characters that combine to make up an instruction word. Valid instruction words vary in length from 1 to 12 characters, depending on the amount of information that the operation requires.

Valid instruction formats are:

0

- O d O XXX d

- O AAAAA

- O AAAAA d

- O XXX BBBBB d O AAAAA BBBBB

- O AAAAA BBBBB d

O signifies the single-character operation code; AAAAA is the five-character address of the A field. BBBBB is the five-character address of the B field. xxx is the three character 1-0 unit and control field, and d is the operation modifier.

The instruction words are arranged sequentially in core storage. Subsequent instructions are located in higher-numbered storage positions. Each instruction word must have a word mark with its operation code. Any other word marks will result in a machine-stop when the word reads out. A word mark must also be in the location immediately to the right of the low-order character of the instruction word. Usually this is the operation code for the next instruction.

The address of an instruction is the location of its operation code. No operation code has two valid lengths that differ by only one character. Instructionlength checking insures that the instruction length as read out of storage is one of the valid lengths for the particular operation code. The add op code, for example, has three valid lengths: 1, 6, or 11 characters.

#### Control

The central processing unit (CPU) is made up of four major areas: a storage unit, an address unit, an operational unit, and a control unit.

1. The storage unit is the center of all data flow in the 1410. Information reads into storage from the assembly channel and reads out through a B data register to the B channel. A five-position address is fed to the storage unit to control the position of storage to be used.

2. The address unit stores and modifies the five-position addresses that locate the position of storage to be used.

3. The operational unit contains all the units necessary to edit, compare, move or add data.

4. The control unit contains registers, cycle controls, and a clock that are necessary to perform the various functions of the CPU.

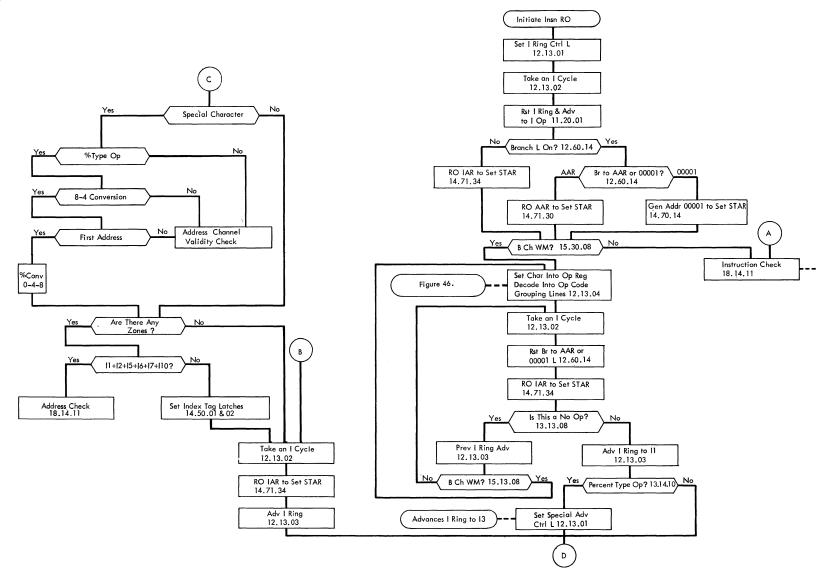

The operation of the IBM 1410 System is controlled by the program routine stored in the core-storage unit. The completion of each program step requires two phases: instruction (I) phase and execute (E) phase.

### INSTRUCTION PHASE

I phase is the first portion of the program step that is required to read the instruction word out of storage. The instruction word is made up of addresses, op code, op modifier, and control characters for 1-0 operations. As the characters read out during I phase, they are stored in registers in the control or address units. A storage cycle is required to read each character out onto the B channel. Because the length of the instruction words is variable, the number of cycles in I phase is variable.

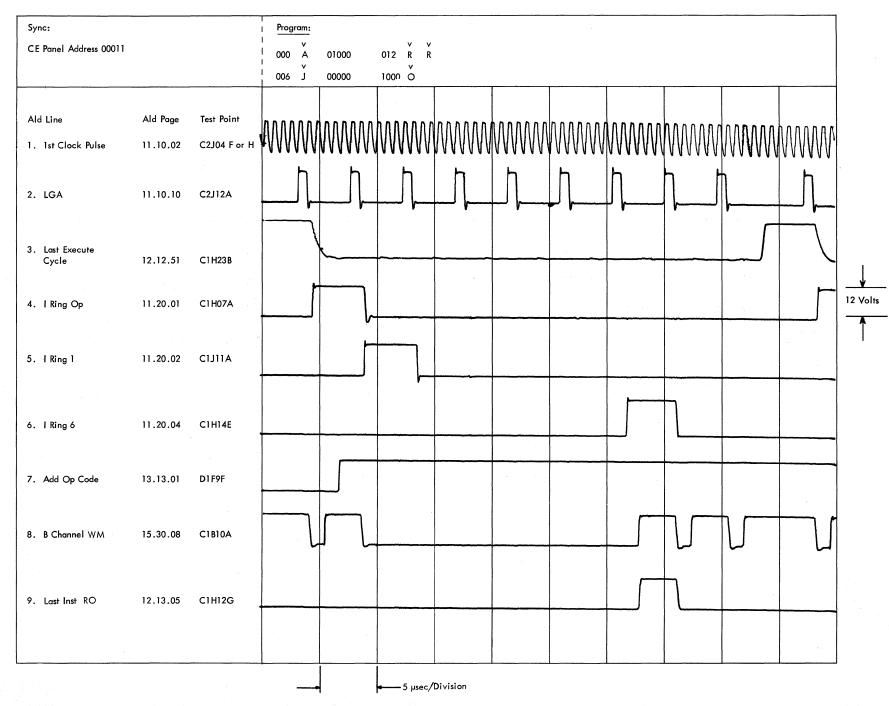

I phase is further divided into I cycles. To identify which character of the instruction word is reading out of storage during an I cycle, an I ring counts the characters or cycles. The I ring consists of 13 triggers labelled I ring op, and I ring 1 through I ring 12 (Figure 6).

As the first I cycle of I phase is taken, the I ring is set to I ring op time to identify this character as the op code. The I ring then advances to I ring 1-time to identify the next character that reads out as either a modifier, or the ten-thousands position of an address, depending on the op code character that has already been read out and recognized.

An example of I phase is a data move instruction word which can consist of the op code, followed by an A field and B field address and a d modifier character:

## D AAAAA BBBBB d

At I ring op time, the op code reads out of the storage unit and is set into the op register in the control unit. The op register is decoded to identify the next five characters as the A field address.

I rings 1 through 5 gate the characters into the proper positions of an address register, located in the address unit, called the A address register.

I rings 6 through 10 gate the next five characters to the B address register in the address unit. The character read out at I ring 11 time is the d modifier. It is stored in the op-modifier (op mod) register in the control unit. During I ring 12 time, the next character is read out to insure that a word mark is located in the next position of storage.

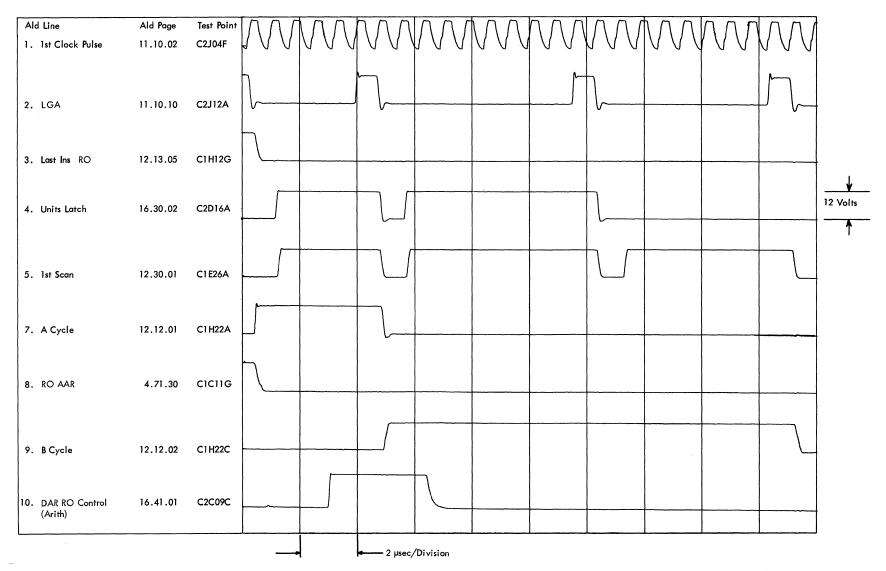

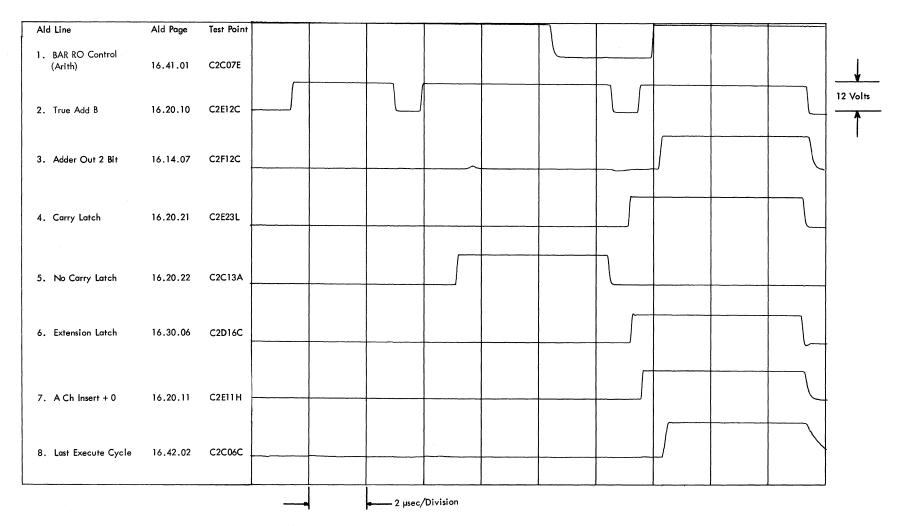

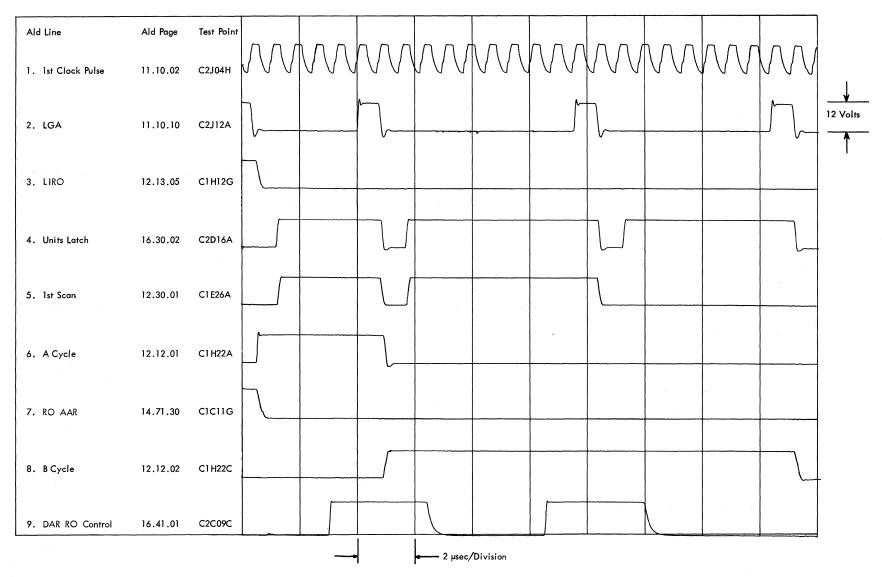

#### EXECUTE PHASE

At the completion of I phase, the machine is ready to perform the actual operation. This portion of the program step is the execute phase (E phase). The length and complexity of E phase depends on the type of op code. E phase can consist of A, B, C, D, E, or F cycles, with storage either forward- or reverse-scanned. Each cycle length varies from 4.5 to 7.5 (4.0-6.67) microseconds. At the completion of E phase, the machine normally returns to I phase to initiate the next instruction.

### Data Flow

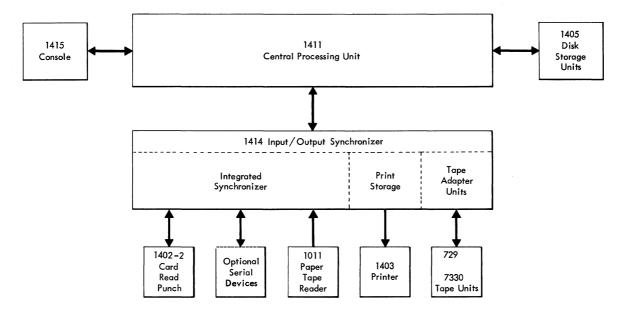

The center of data flow in the IBM 1411 Central Processing Unit is the core-storage unit that receives data from the IBM 1405 Disk Storage Unit, the IBM 1415 Console, or the IBM 1414 Input-Output Synchronizer (Figures 7 and 8). When processing is complete, the data can be sent to the 1405, 1415, or 1414.

The 1414 I-O Synchronizer controls the various inputoutput units that are used in conjunction with the 1410 System. The 1414 includes the integrated synchronizer, print storage, and tape adapter units.

The integrated synchronizer is an input-output control unit that contains up to eight 80-character magnetic-core storage units. These units provide independent buffering for all associated 1-0 units. A data transfer between the CPU and the card read punch or paper tape reader takes place through the integrated synchronizer. Processing time is saved because the CPU does not have to wait for a mechanical unit to pick up speed, etc.

The print storage unit contains a 132-position corestorage unit that is an intermediate storage device between the CPU and the IBM 1403 Printer. Included in the print area is the circuitry necessary to control the carriage for forms handling.

The tape adapter units provide a control system for the various tape units that may be used with the 1410 System.

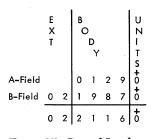

| I-cy      | I-cy | I-cy | I-cy | I-cy | I-cy | I-cy | I-cy | I-cy | I-cy | I-cy | I-cy              | I-cy |

|-----------|------|------|------|------|------|------|------|------|------|------|-------------------|------|

| I Op      | I 1  | I 2  | I 3  | I 4  | I 5  | I 6  | I 7  | I 8  | I 9  | I 10 | I 11              | I 12 |

| D         | A    | A    | A    | A    | A    | в    | в    | в    | в    | в    | d                 | ŏ    |

| -         |      |      | ~    |      |      |      |      |      |      |      |                   | 1    |

| Op<br>Reg |      |      | AAR  |      |      |      |      | BAR  |      |      | Op<br>Mod.<br>Reg |      |

Figure 6. Instruction Phase

Figure 7. Data Flow

Figure 8. CPU Data Flow

16

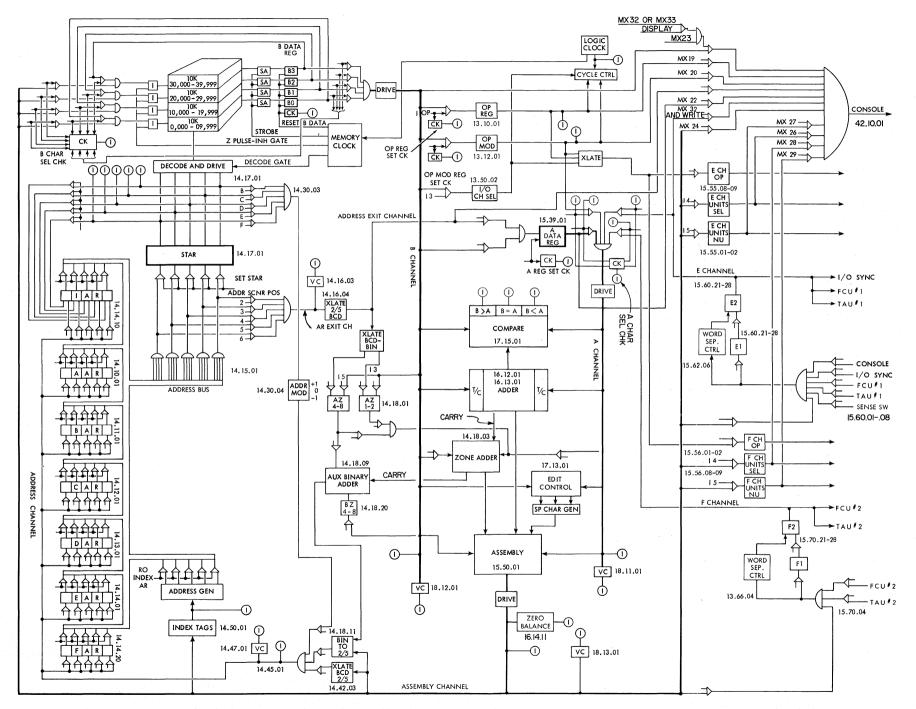

The IBM 1411 Central Processing Unit is the hub of all 1410 System operations. Four frames form the integral units of the basic 1411. Frame A contains power supplies, circuit breakers, and relays necessary for power control and distribution throughout the system. Frame B contains the magnetic core storage unit. Instructions that define operations to be performed and the data to be operated upon can be stored in this unit indefinitely. Frame B also contains the SMS transistor cards that make up the address unit circuitry. The address unit stores the five-position addresses that locate positions in core storage to be used.

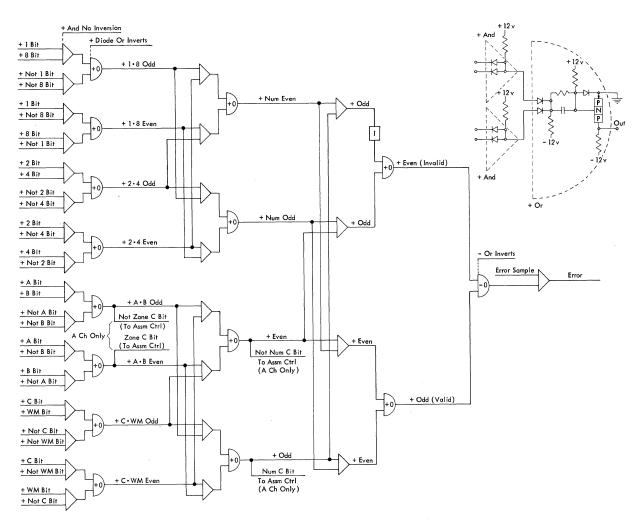

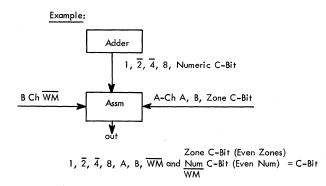

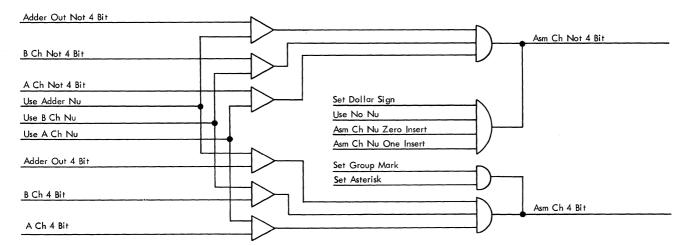

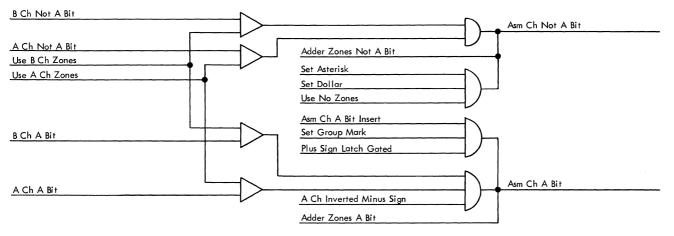

Frame C contains logic clock circuitry that generates timing pulses for the 1411 and also contains the cycle control unit. The adder and assembly circuits are also located in frame C. Internal data flow in the 1411 is controlled partially by the assembly unit. Operation decode circuits in frame D analyze each instruction word to determine the what, where, when, and how of any operation. Also in frame D are the compare and edit control units. Input-output circuits necessary for the flow of data into and out of the 1411 are located in both C and D frames.

# **Control Unit**

The logic clock generates timed impulses that are used to form gates that control all functional units of the 1411.

### **Logic Clock**

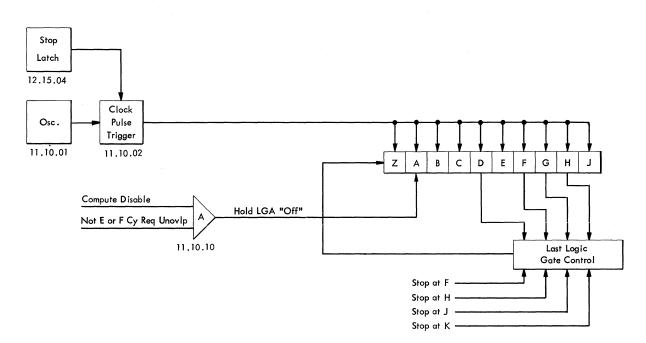

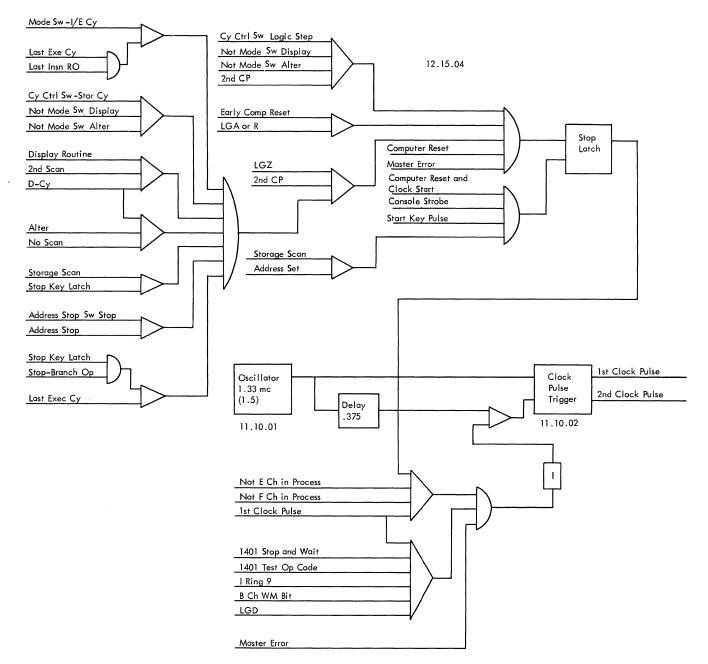

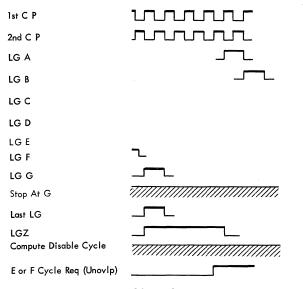

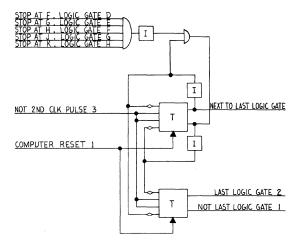

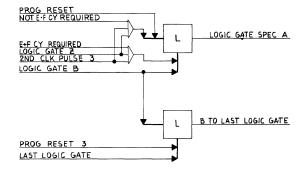

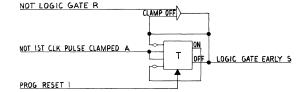

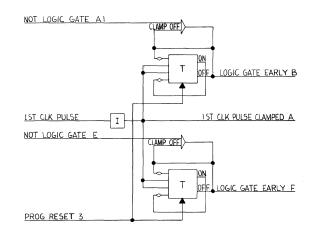

Various 1410 System operations require different length storage cycles. These cycles range from six to ten pulses; the number of pulses depend on the type of operation being performed. The pulses are called logic gates A through K. The logic clock circuit uses a freerunning crystal-controlled oscillator and a ten-trigger ring to develop the number of logic gate pulses required (Figure 9).

The oscillator drives a binary input trigger called the clock pulse trigger. The outputs of the clock pulse trigger are called "first clock pulse" (1CP) and "second clock pulse" (2CP). The clock is normally stopped with the stop latch that, by collector pullover, clamps the clock pulse trigger at 1CP. The logic gate A trigger is also on. When the stop latch is reset, the clock pulse trigger is advanced by the oscillator. At the end of 2CP, the ring

is advanced from logic gate A (LGA) to logic gate B (LGB). Since clock pulses are .375 (.333) microseconds long, the ring advances every .750 (.666) microseconds (Figure 10).

Cycle length is defined by controlling the point at which the ring stops advancing and returns to its starting position. Type of cycle and type of operation control cycle length by conditioning the "stop at F, H, J, or K line." This line combines with the corresponding logic gate pulse to bring up "last logic gate (LLC)." LLC sets the logic gate Z latch that gates the ring back to LCA. To stop the clock at the end of a cycle, the stop latch is set on by the 2CP of the last logic gate. The stop latch combines with 1CP to clamp the clock pulse trigger at 1CP, LCA (Figure 11).

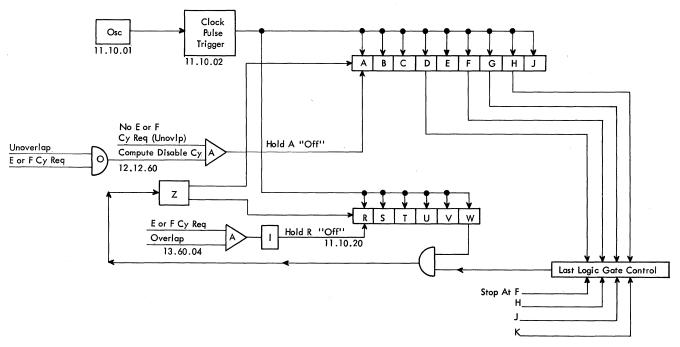

### UNOVERLAP OPERATION

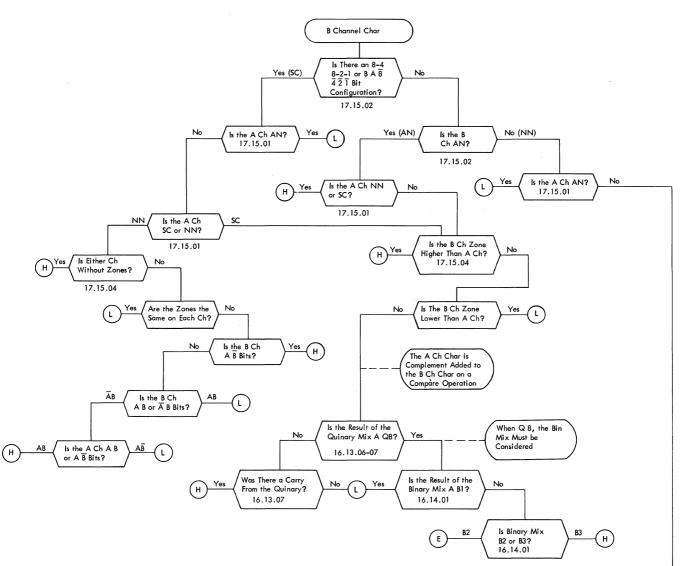

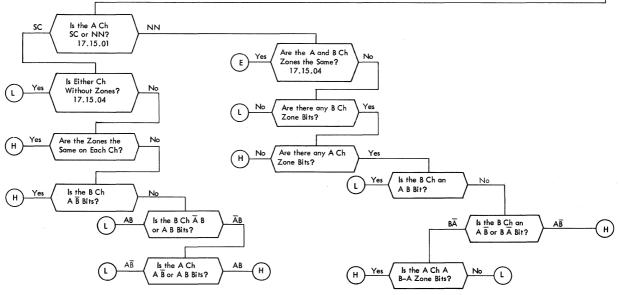

All I-O commands (except F or K) can be executed one of two ways: unoverlapped or overlapped. An unoverlapped command causes the CPU to take E cycles (channel 2) or F cycles (channel 2), as required, to read in or read out each I-O character. Because the CPU reads in or reads out characters at a faster rate than any I-O machine, the CPU must wait between each E or F cycle until the I-O device sends, or is able to receive, another character.