For Sale Through IBM Branch Offices

For Sale Through IBM Branch Offices

#### PREFACE

This manual describes the 1800 system adapter features for the following IBM data processing input/output units:

1053 Printer

1816 Printer-Keyboard

1054 Paper Tape Reader

1055 Paper Tape Punch

1442 Card Read Punch

1443 Printer

1627 Plotter

2401/2402 Magnetic Tape Units

Chapter 4 (Features), normally found in the FETOM, does not apply to this manual.

Electromechanical and operational details of the DP I/O units are described in the manuals written for each unit. These unit manuals are referenced in the related chapters and listed, with form numbers, in the FE Bibliography - 1800 System, Order No. SY26-0560.

Information that is necessary to the understanding of this manual is in the IBM Field Engineering Theory of Operation, 1800 Data Acquisition and Control System, Processor-Controller (See FE Bibliography -- 1800 System, Order No. SY26-0560.) It contains a comprehensive introduction to the 1800 system and specific descriptions of the 1801 and 1802 Processor-Controllers, including channel control.

The functional unit and operation descriptions in this manual refer to diagrams contained in the IBM Field Engineering Maintenance Diagrams Manual, 1800 Data Acquisition and Control System (see FE Bibliography -- 1800 System, Order No. SY26-0560).\*

## Seventh Edition (July 1970)

This manual, Order No. SY26-3617-6, is a reprint of Order No. SY26-3617-5 and of Supplement SS27-0706.

Significant changes or additions to the specifications contained in this publication are continually being made. When using this publication in connection with the operation of IBM equipment, check the latest FE Publications Systems Sequence Listing, Order No. SY20-0070, for revisions or contact the local IBM branch office.

The illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter,

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form for reader's comments is provided at the back of this publication. If the form has been removed, send your comments to the address below.

This manual was prepared by the IBM Systems Development Division, Product Publications, Department G24, San Jose, California 95114.

© Copyright International Business Machines Corporation 1965

<sup>\*</sup>Manuals referred to in this publication that have a form number with a four character prefix are identical in content to the same manual without the initial prefix character. (e.g., SY26-xxxx is the same in content as Y26-xxxx.)

# CONTENTS

| PREFACEii                                    | PART 4 IBM 1443 PRINTER                       |

|----------------------------------------------|-----------------------------------------------|

| LIST OF ILLUSTRATIONSv                       | Printer Functional Description                |

| ABBREVIATIONSvi                              | I/O Interface4-5                              |

| PART 1 IBM 1816 PRINTER-KEYBOARD AND         | Chapter 2 Functional Units                    |

| IBM 1053 PRINTER 1-1                         | Word Counter4-7                               |

| Chapter 1 Introduction                       | Seven Bit Serial Buffer 4-8                   |

| Printer Functional Description               | Seven Bit Print Buffer                        |

| Keyboard Functional Description1-2           | Timing Pulse Generator                        |

| Adapter Functional Description1-2            | Chapter 3 Principles of Operation             |

| I/O Interface                                | Chapter 5 Power Supplies and Control*         |

| Chapter 2 Functional Units                   |                                               |

|                                              | Chapter 6 Console and Maintenance Features**  |

| Function Register                            | DADE C IDM 1005 DI OMEDD                      |

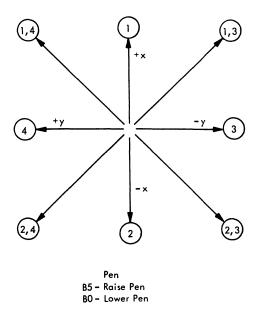

| Shift Circuits                               | PART 5 IBM 1627 PLOTTER 5-1                   |

| Buffer Register                              | Chapter 1 Introduction                        |

| Chapter 3 Principles of Operation 1-8        | Plotter Functional Description 5-1            |

| Printer Operations                           | Adapter Functional Description 5-3            |

| Keyboard Operations1-10                      | I/O Interface                                 |

| Printer-Keyboard Sense and CE Mode           | Chapter 2 Functional Units 5-5                |

| Operations                                   | Function Register                             |

| Chapter 5 Power Supplies and Control*        | Plotter Control Buffer5-5                     |

| Chapter 6 Console and Maintenance Features** | Chapter 3 Principles of Operation 5-6         |

|                                              | Chapter 5 Power Supplies and Control*         |

| PART 2 IBM 1054 PAPER TAPE READER AND        | Chapter 6 Console and Maintenance Features**  |

| IBM 1055 PAPER TAPE PUNCH2-1                 |                                               |

| Chapter 1 Introduction                       | PART 6 IBM 2310 DISK STORAGE6-1               |

| Reader-Punch Functional Description 2-1      |                                               |

| Adapter Functional Description2-2            | PART 7 MAGNETIC TAPE CONTROL 7-1              |

| I/O Interface2-3                             | Chapter 1 Introduction                        |

| Chapter 2 Functional Units                   | Functional Description - Tape Units7-1        |

| Function Register                            | Functional Description - Tape Control Unit7-1 |

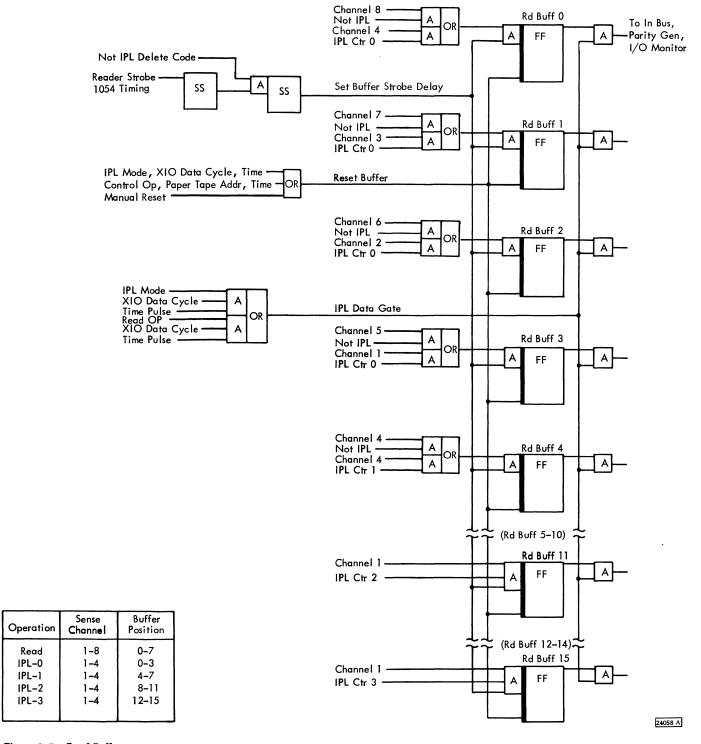

| Read Buffer2-5                               | I/O Interface                                 |

| IPL Counter                                  | Chapter 2 Functional Units                    |

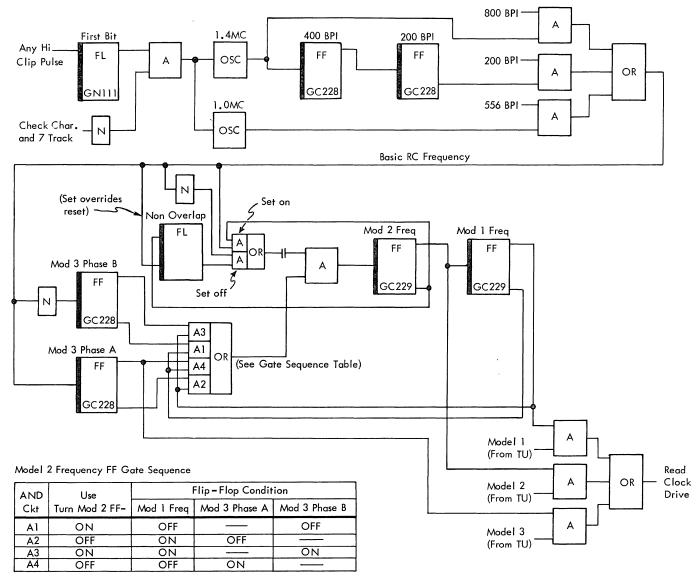

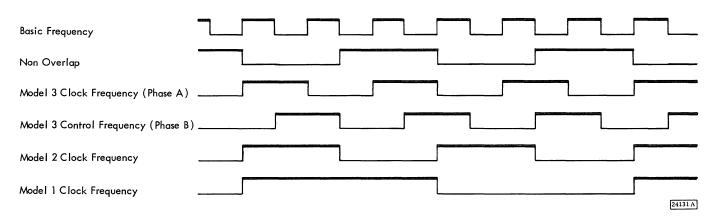

| Punch Buffer2-7                              | Read Clock                                    |

| Chapter 3 Principles of Operation 2-8        | Write Clock                                   |

| Reader Operations                            | Delay Counter (DC)7-12                        |

| Punch Operations                             | Word Counter                                  |

| Reader-Punch Sense Operations                | Byte Generator                                |

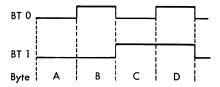

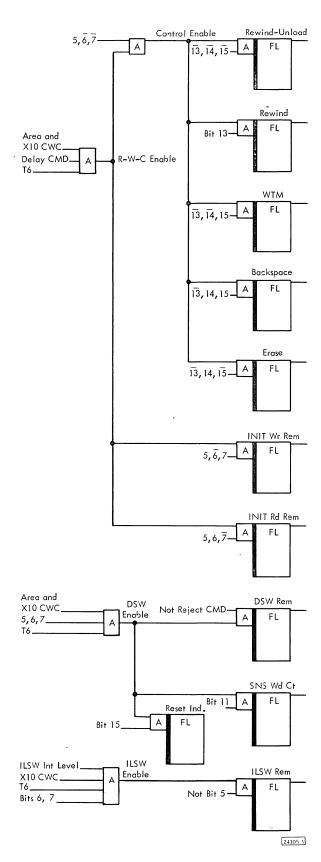

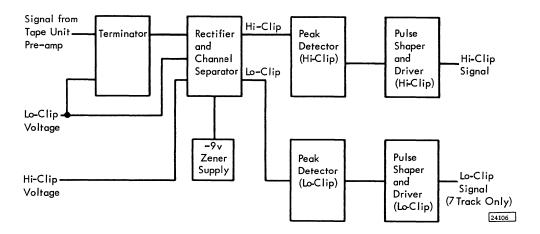

| Chapter 5 Power Supplies and Control*        | Function Register                             |

| Chapter 6 Console and Maintenance Features** | Final Amplifiers                              |

| omapion o combore and maintenance i catal es | Skew Register                                 |

| PART 3 IBM 1442 CARD READ PUNCH 3-1          | Read/Write Register (R/W)                     |

| Chapter 1 Introduction                       | Data Register                                 |

| Read-Punch Functional Description            | Longitudinal Redundancy Check                 |

|                                              | · · · · · · · · · · · · · · · · · · ·         |

| Adapter Functional Description3-3            | Register (LRCR)                               |

| I/O Interface                                | Cyclic Redundancy Check Register (CRCR)7-17   |

| Chapter 2 Functional Units                   | Error Pattern Register (EPR)                  |

| Function Register                            | Chapter 3 Principles of Operation             |

| Data Register                                | Read Operation                                |

| Chapter 3 Principles of Operation            | Write Command Operation                       |

| Chapter 5 Power Supplies and Control*        | Turnaround                                    |

| Chapter 6 Console and Maintenance Features** | Error Correction                              |

| Control Operations                           | APPENDIX B Special Circuits                  |

|----------------------------------------------|----------------------------------------------|

| Sense Interrupt Level Status Word (ILSW)7-43 | APPENDIX C I/O Device Addressing             |

| Sense Device7-43                             | APPENDIX D Device Status Words               |

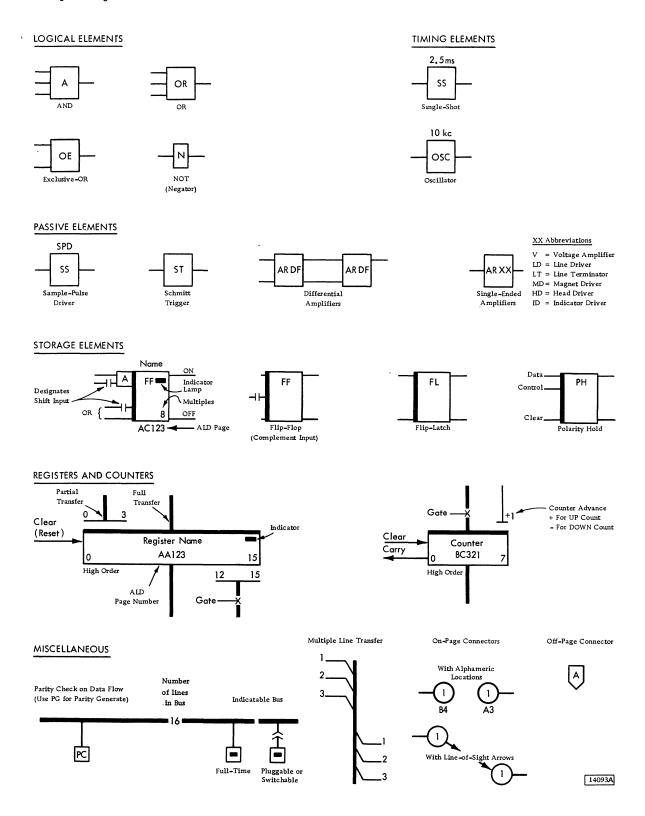

| Chapter 5 Power Supplies and Control*        | APPENDIX E Maintenance Diagram Symbology E-1 |

| Chapter 6 Console and Maintenance Features** |                                              |

| APPENDIX A Machine Characteristics           | Index                                        |

<sup>\*</sup>Not applicable. Power supplied by Processor-Controller.

<sup>\*\*</sup>Console and maintenance facilities for this feature are described in Chapter 6 of the Processor-Controller FETO manual.

# LIST OF ILLUSTRATIONS

| Figure |                                    | Page | Figure |                                         | Page |

|--------|------------------------------------|------|--------|-----------------------------------------|------|

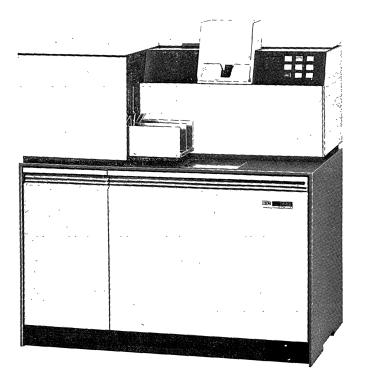

| 1-1    | IBM 1816 Printer-Keyboard          | 1-1  | 5-7    | 1627 Device Interface Lines             | 5-4  |

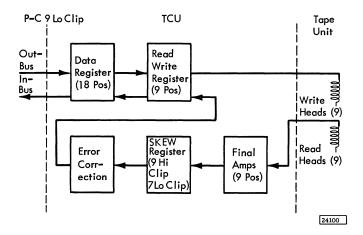

| 1-2    | IBM 1054 Printer                   | 1-1  | 7-1    | Tape Control Unit Basic Data Flow       | 7-1  |

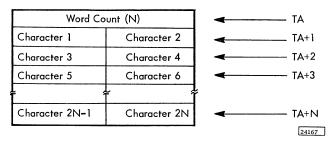

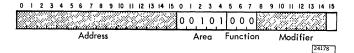

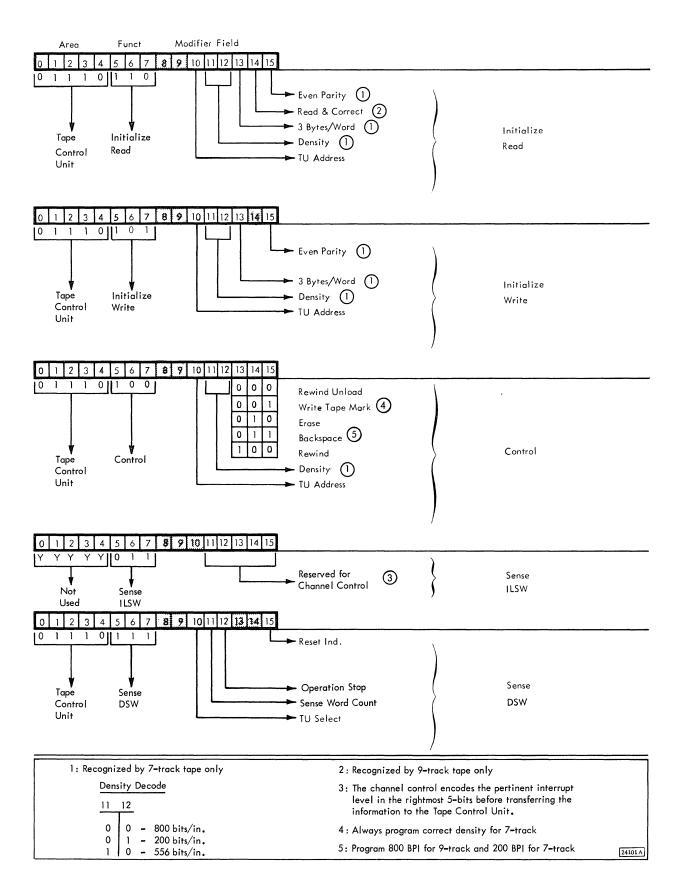

| 1-3    | Keyboard Character Code            | 1-3  | 7-2    | Control Words, 1800 Tape Control Unit.  | 7-3  |

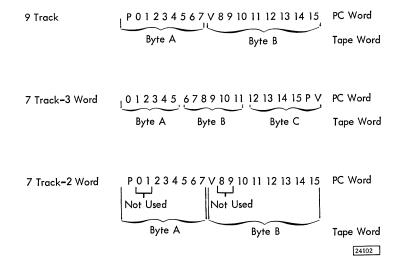

| 1-4    | 1816 Device Interface Lines        | 1-5  | 7-3    | Data Word Format                        | 7-4  |

| 1-5    | 1053 Device Interface Lines        | 1-6  | 7-4    | 2401/2402 Device Interface Lines        | 7-8  |

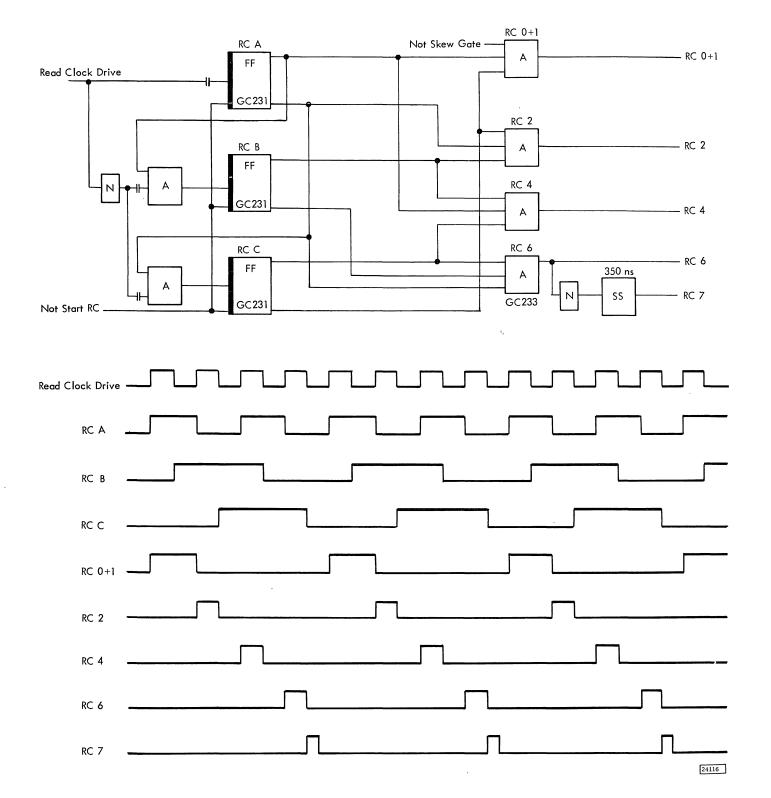

| 1-6    | Printer Data Character Coding      | 1-9  | 7-5    | Read Clock                              | 7-10 |

| 1-7    | Printer Control Characters         | 1-9  | 7-6    | Read Clock Drive                        | 7-11 |

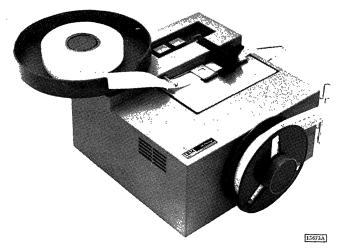

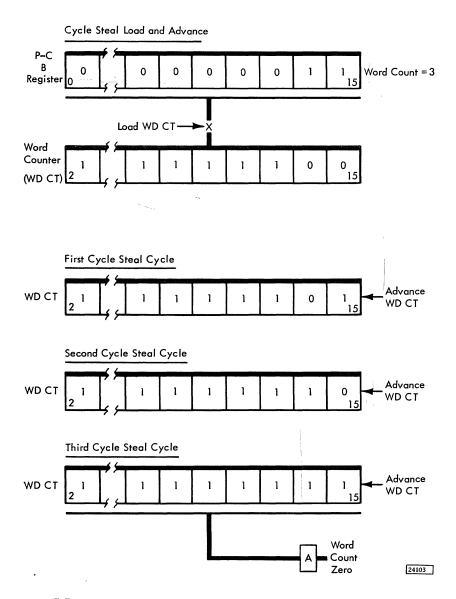

| 2-1    | IBM 1054 Paper Tape Reader         | 2-1  | 7-7    | Word Counter Advance to Zero            | 7-13 |

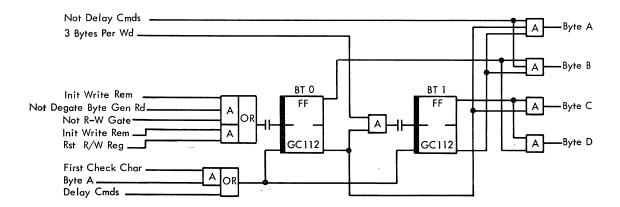

| 2-2    | IBM 1055 Paper Tape Punch          | 2-1  | 7-8    | Byte Generator                          | 7-14 |

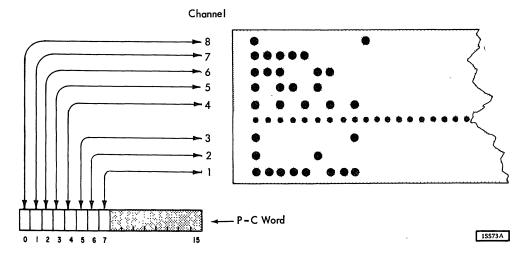

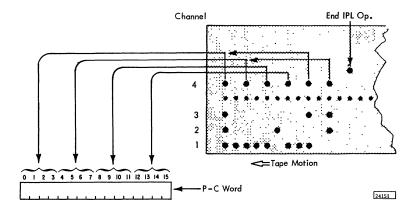

| 2-3    | Word Format, Read Mode             | 2-2  | 7-9    | Function Register                       |      |

| 2-4    | Word Format, IPL Mode              | 2-2  | 7-10   | Final Amplifier                         | 7-16 |

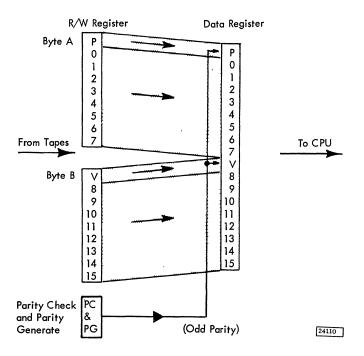

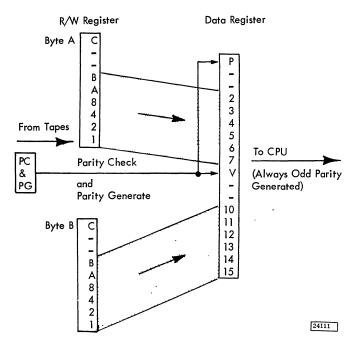

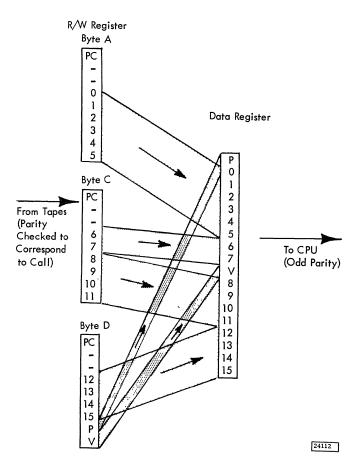

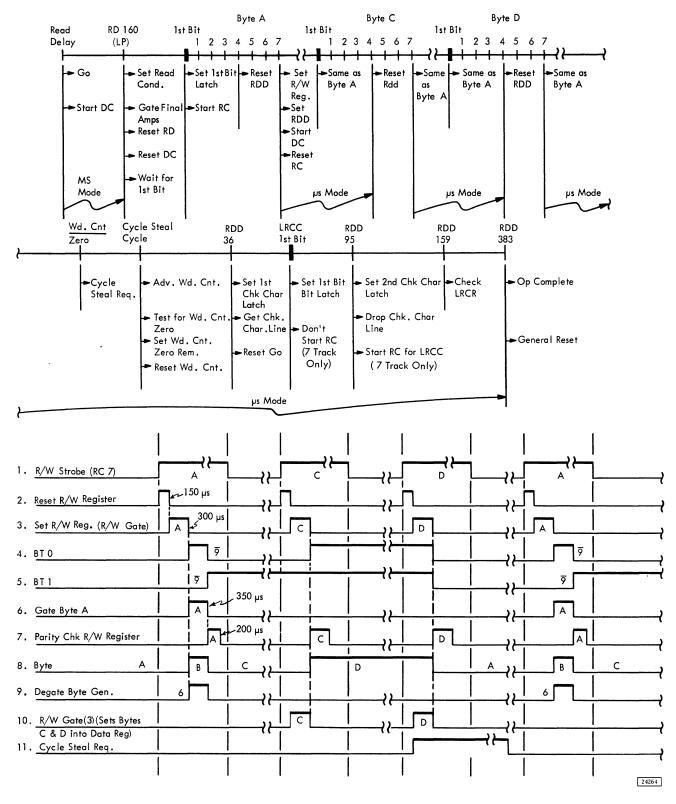

| 2-5    | 1054 Device Interface Lines        | 2-4  | 7-11   | Data Register Input                     | 7-17 |

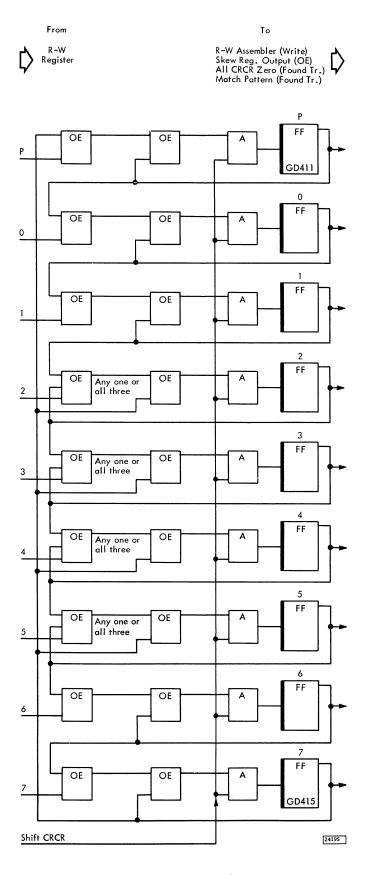

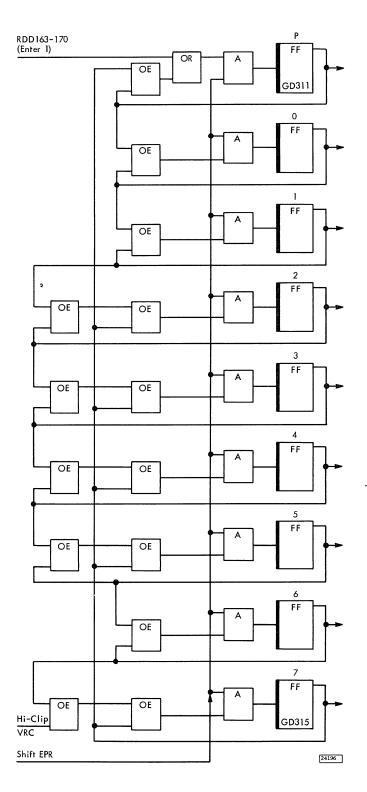

| 2-6    | 1055 Device Interface Lines        | 2-4  | 7-12   | Cyclic Redundancy Check Register        | 7-18 |

| 2-7    | Read Buffer                        | 2-6  | 7-13   | Error Pattern Register                  | 7-19 |

| 2-8    | Punch Buffer Loading               | 2-7  | 7-14   | Tape Control Unit Block Diagram         | 7-21 |

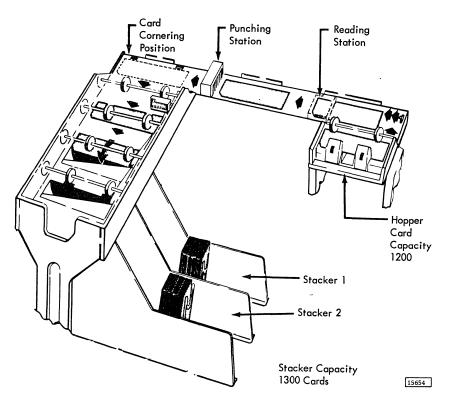

| 3-1    | IBM 1442 Card Read Punch           | 3-1  | 7-15   | Cycle Steal Acknowledge Control         |      |

| 3-2    | Card-Image-Mode Read               | 3-2  |        | Triggers                                | 7-22 |

| 3-3    | Packed-Mode Read                   | 3-2  | 7-16   | Read Data Gating, Nine-Track            | 7-24 |

| 3-4    | 1442 Device Interface Lines        | 3-5  | 7-17   | Read Data Gating, Seven-Track Two-      |      |

| 3-5    | Data Register Output, Read and IPL |      |        | Byte                                    | 7-24 |

|        | Operations                         | 3-6  | 7-18   | Format: Read Data Gating, Seven-        |      |

| 3-6    | Card Path                          | 3-9  |        | Track Three-Byte                        | 7-25 |

| 4-1    | IBM 1443 Printer                   | 4-1  | 7-19   | Timing: Read Data Gating, Seven-        |      |

| 4-2    | Core Storage Word Format           | 4-1  |        | Track Three-Byte                        | 7-26 |

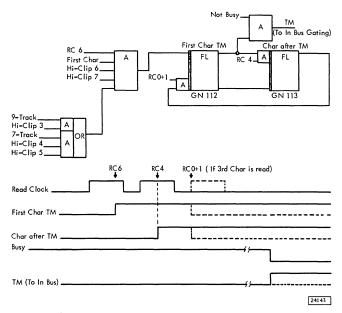

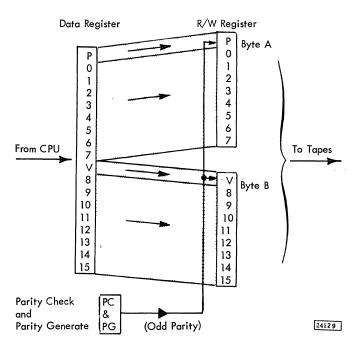

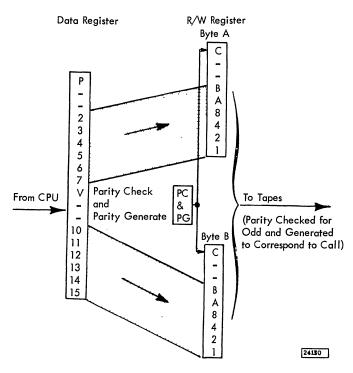

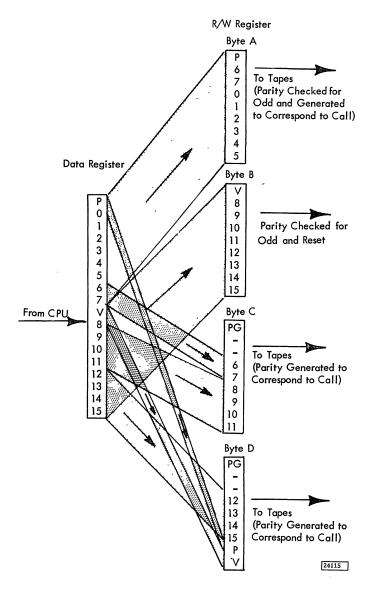

| 4-3    | Printing Speeds                    | 4-1  | 7-20   | Tape Mark Recognition                   | 7-29 |

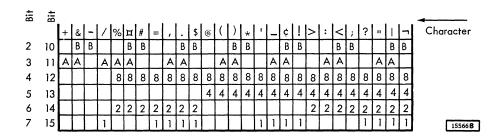

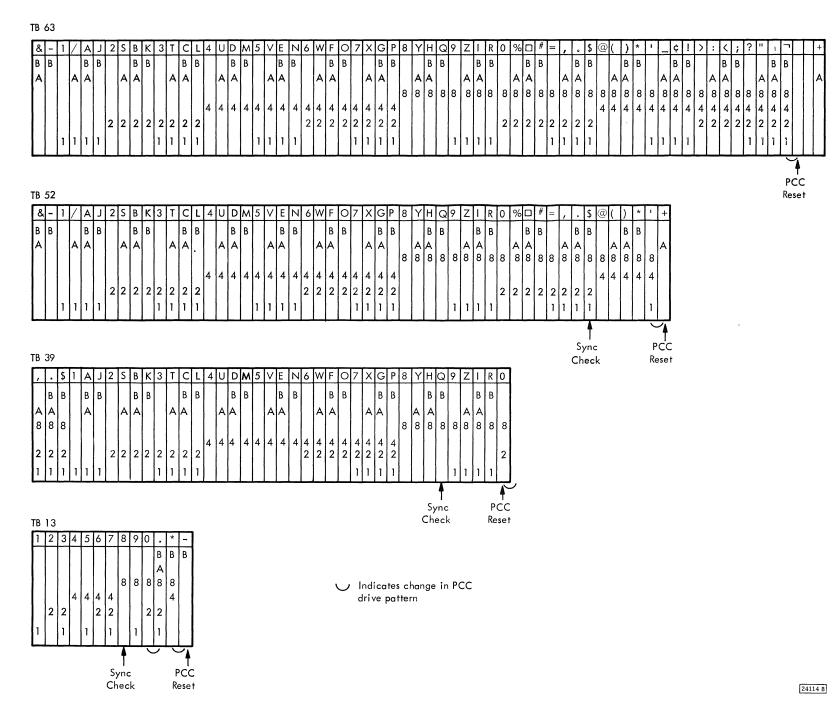

| 4-4    | Character Coding                   | 4-2  | 7-21   | Write Data Gating, Nine-Track           | 7-31 |

| 4-5    | Type Bars and Associated Bit       |      | 7-22   | Write Data Gating, Seven-Track Two-Byte | 7-32 |

|        | Configurations                     | 4-3  | 7-23   | Format: Write Data Gating, Seven        |      |

| 4-6    | Carriage Control Characters        | 4-4  |        | Track Three Byte                        | 7-33 |

| 4-7    | 1443 Device Interface Lines        | 4-6  | 7-24   | Timing: Write Data Gating, Seven        |      |

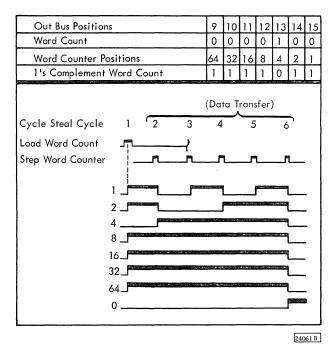

| 4-8    | Word Count Register Load and Count | 4-7  |        | Track Three Byte                        | 7-34 |

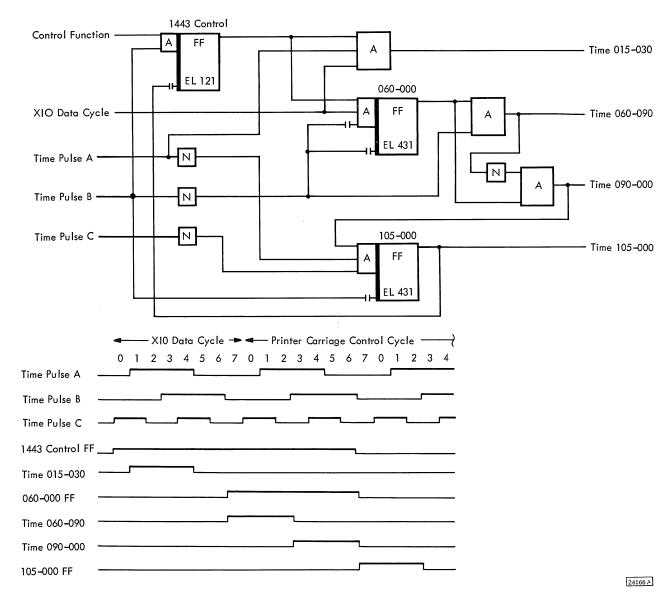

| 4-9    | Timing Pulse Generator             | 4-9  | 7-25   | Generation of CRC Character During      |      |

| 4-10   | 1443 Data Table                    | 4-10 |        | Write                                   | 7-39 |

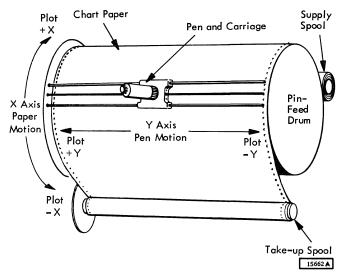

| 5-1    | IBM 1627 Plotter                   | 5-1  | 7-26   | Generation of CRC Character During      |      |

| 5-2    | Paper and Pen Motions              | 5-1  |        | Read                                    | 7-39 |

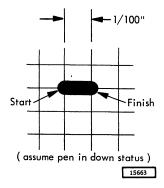

| 5-3    | Plotter Result for One Horizontal  |      | 7-27   | EPR During Read                         | 7-40 |

|        | (4 axis) Movement                  | 5-2  | 7-28   | CRCR Shifting for Error Track Detection | 7-40 |

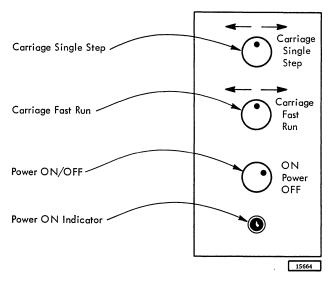

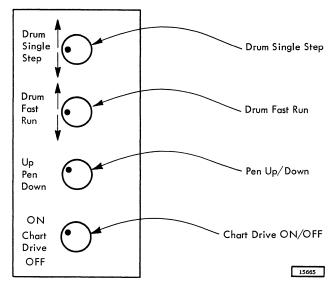

| 5-4    | Output Record Control              |      | 7-29   | Error Correction Example                |      |

| 5-5    | Left Console Controls              |      | 7-30   | CRCR Operation with No Errors           | 7-41 |

| 5-6    | Right Console Controls             |      |        | -                                       |      |

# ABBREVIATIONS

| A Reg<br>ALD*                        | Accumulator Automated logic diagram                                                                  | LC*<br>LP<br>LRC          | Lower case<br>Load point<br>Longitudinal redundancy check                                                                                   |

|--------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| B Reg<br>BCD<br>BPI                  | Storage buffer register<br>Binary coded decimal<br>Bytes per inch                                    | M Reg<br>MDM*<br>Mod Reg  | Storage address register<br>Maintenance diagram manual<br>Modifier register                                                                 |

| CAB*                                 | Channel address buffer                                                                               | Op Reg                    | Operation code register                                                                                                                     |

| CAR*<br>CPU<br>CRC*                  | Channel address register Central processing unit Cyclic redundancy check                             | P-C*                      | Processor-controller                                                                                                                        |

| CRP*                                 | Card read punch (IBM 1442)<br>Cycle steal                                                            | Q Reg                     | Accumulator extension register                                                                                                              |

| CWC*                                 | Control word cycle                                                                                   | RDD*<br>R/W*              | Read disconnect delay<br>Read/write                                                                                                         |

| D Reg<br>DC*<br>DPC*<br>DSW*<br>DWC* | Arithmetic factor register Data channel Direct program control Device status word Data word cycle    | SC* SLD* SLT* SMS SRL* SS | Shift counter Simplified logic diagram Solid logic technology Standard modular system Systems reference library Single-shot (multivibrator) |

| EA* ECAD* EOC* EOT* EPR*             | Effective address Error check analysis diagram End of conversion End of table Error pattern register | T Reg<br>TCU*<br>TU       | Tag register Tape control unit Tape unit                                                                                                    |

| F Reg<br>FF*<br>FL*                  | Format register Flip-flop Flip-latch                                                                 | U Reg<br>UC*<br>UDCD*     | Temporary accumulator register Upper case Unit data and control diagram                                                                     |

| TL                                   | Tip faces                                                                                            | VRC                       | Vertical redundancy check                                                                                                                   |

| I Reg<br>ILSW*                       | Instruction register Interrupt level status word                                                     | WC*<br>WDD*               | Word counter<br>Write disconnect delay                                                                                                      |

| IOCC*                                | Input/output control command Initial program load                                                    | XR*<br>XIO*               | Index register<br>Execute input/output                                                                                                      |

<sup>\*</sup> Non-standard ALD abbreviation.

## CHAPTER 1 INTRODUCTION

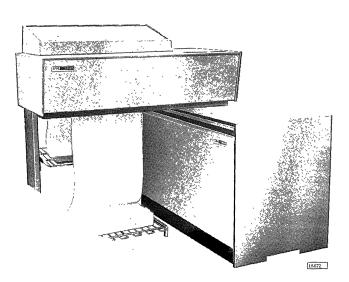

- The 1816 (Figure 1-1) provides a console keyboard and console printer for the IBM 1800 System.

- The 1053 (Figure 1-2) provides additional output typewriter printers for the IBM 1800 System.

- For a detailed description of the printer mechanics, see <u>IBM Field Engineering Theory of Operation</u>, <u>I/O Printer</u> (<u>Modified IBM SELECTRIC</u>®). (see <u>FE Bibliography</u> -- <u>1800 System</u>, Form Y26-0560.)

- For a detailed description of the keyboard mechanics, see <u>IBM Field Engineering Theory-Maintenance</u>, 1052-1053. (see <u>FE Bibliography -- 1800 System</u>, Form Y26-0560.)

The 1816 is a combination of an IBM 1052 Keyboard and a 1053 Printer. The printer portion of the 1816 and the 1053 are therefore physically and functionally the same. The printer description presented here applies to both of these units.

A maximum of two 1816s and eight 1053s can be attached to the 1800 system; however, no more than a total of eight of these units in combination can be attached.

All printers operate in the overlapped mode; that is, each can print a different message at the

Figure 1-1. IBM 1816 Printer-Keyboard

Figure 1-2. IBM 1053 Printer

same time. The 1816 can be installed up to 50 feet from the processor-controller (P-C). The 1053 can be installed up to 2000 feet from the P-C.

#### PRINTER FUNCTIONAL DESCRIPTION

- Maximum output rate of the printer is 14.8 characters per second.

- Data to be printed is transferred from core storage to the typewriter by direct program control.

- Data and control characters (space, tabulate, etc.) are sent to the typewriter by means of the write command.

Because control characters and data characters are sent in the same manner, the message to be printed contains a mixture of data characters and control characters in the sequence necessary to provide output in the desired format.

NOTE: The illustrations in this manual have a code number in the lower corner. This is a publishing control number and is unrelated to the subject matter.

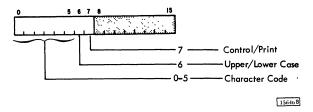

The character format within a core storage word to be transmitted to the typewriter printer is:

Each word transmitted to the typewriter printer contains one data character or one control character.

#### KEYBOARD FUNCTIONAL DESCRIPTION

- The keyboard of the 1816 printer-keyboard is similar to the keyboard of the IBM 1052.

- The keys are not connected to the printer; therefore, keyboard entries are not printed unless the P-C is programmed to do so.

- Maximum input speed of the keyboard is 20 characters per second but is usually limited by the speed of the operator.

- The keyboard operates under direct program control.

- The keyboard emits an IBM-card-coded character for each operation of a key.

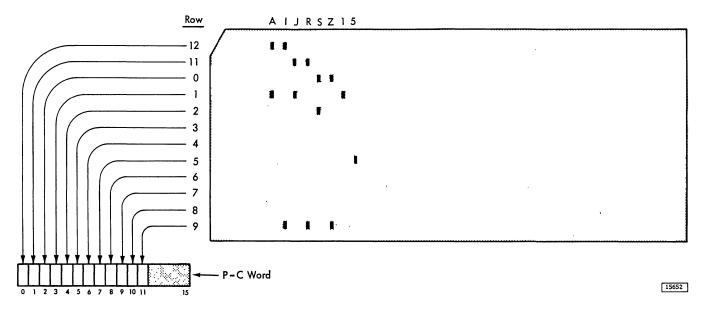

The character coding emitted by the keyboard is shown in Figure 1-3. The character enters the P-C left justified. Thus, bit 0 corresponds to IBM card code 12, bit 1 to IBM card code 11, etc. Bits 12, 13, and 14 have special significance and indicate end of field, erase character, and erase field respectively. (See description of these three keys.) Odd-bit parity is generated to provide a data-transmission check on the input data at the processor-controller B-register.

## Keys and Lights

Keys with special functions are:

KBD REQ (Keyboard Request Interrupt): This key initiates an interrupt in the P-C and turns off the proceed light.

END FLD (End of Field): When a read command is executed in response to this key, a word with only bit 12 = 1 is placed in core storage. Analysis of this word allows the program to determine that no further characters are to be sent in this message.

ER CHR (Erase Character): When a read command is executed in response to this key, a word with bit 13 = 1 is placed in core storage.

Analysis of this word allows the program to determine that the last character received is to be replaced by the next character to be entered.

ER FLD (Erase Field): When a read command is executed in response to this key, a word with bit 14 = 1 is placed in core storage. Analysis of this word allows the program to determine that the message being entered is to be deleted and replaced by a corrected message.

REST KB (Restore Keyboard): This key allows the operator to unlock the keyboard to release any key that is locked down.

The following lights appear on the keyboard:

<u>Proceed:</u> This light comes on when the P-C has performed the XIO (control) instruction. The keyboard is unlocked when proceed is on. This light goes off 25 milliseconds after the key is pressed or when the XIO (read) is executed.

Alpha: When on, this light indicates that keyboard characters on the lower half of the keybutton will be placed on the in bus for entry into the processor-controller.

<u>Numeric</u>: When on, this light indicates that keyboard characters on the upper half of the keybutton will be placed on the in bus for entry into the processor-controller.

#### ADAPTER FUNCTIONAL DESCRIPTION

- The 1816-1053 adapter provides a means of attaching keyboard input and typewriter-printer output to the 1800 system.

- The 1816-1053 adapter is contained on one SLT board located in the 1801 or 1802 at location A1 of gate C. A second adapter (expander) can be installed at B1 of gate D.

- Each 1816-1053 adapter accommodates four 1053s or one 1816 and three 1053s.

The adapter performs one or more of the following functions for each I/O command sent to it:

- Selects the specified printer or printer-keyboard.

- 2. Decodes the function to be performed.

| Key IBM C      | ard Code | 0 | 1        | 2 | 3         | 4        | 5 | 6 | 7 | 8 | 9 | 10       | 11       | 12       | 13       | 14 | 15           | Key IBM C      | ard Code | 0        | 1 | 2 | 3 | 4        | 5 | 6        | 7 | 8        | 9 | 10 | 11 1   | 12       | 3 1    | 4      |

|----------------|----------|---|----------|---|-----------|----------|---|---|---|---|---|----------|----------|----------|----------|----|--------------|----------------|----------|----------|---|---|---|----------|---|----------|---|----------|---|----|--------|----------|--------|--------|

| *              | 11,8,4   |   | 1        |   |           |          |   | 1 |   |   |   | ī        | Γ        |          | Γ        |    | П            | J              | 11,1     |          | 1 |   | 1 |          |   |          |   |          |   |    |        |          |        | $\Box$ |

| /              | 0,1      |   |          | 1 | 1         |          |   |   |   |   |   |          |          |          | Γ        | Γ  | $\Box$       | K              | 11,2     |          | 1 |   |   | 1        |   |          |   |          |   |    |        |          |        |        |

| 0              | 0        |   | T        | 1 |           |          |   |   |   |   |   | $\vdash$ |          |          | T        | r  | $\top$       | L              | 11,3     | <b>†</b> | 1 | T |   |          | 1 | Г        |   | П        |   |    |        | T        | T      | 7      |

| 1              | 1        |   | <u> </u> | П | 1         |          |   |   |   |   |   |          |          |          | T        |    | П            | М              | 11,4     |          | 1 |   |   |          |   | 1        |   |          |   |    | П      | 1        | $\top$ | 7      |

| 2              | 2        |   |          | П |           | 1        |   |   |   |   |   |          | Г        |          | T        |    | П            | Ν              | 11,5     |          | 1 |   |   |          |   |          | 1 |          |   |    |        | T        | T      |        |

| 3              | 3        |   |          |   | ٦         |          | 1 |   |   |   |   |          |          |          | Γ        |    | П            | 0              | 11,6     |          | 1 |   |   |          |   |          |   | 1        |   |    |        | T        | T      |        |

| 4              | 4        |   |          |   |           |          |   | 1 |   |   |   |          |          |          | Г        | Γ  |              | Р              | 11,7     |          | 1 |   |   |          |   |          |   |          | 1 |    |        |          | T      | Ţ      |

| 5              | 5        |   |          |   |           |          |   |   | 1 |   |   |          |          |          |          |    |              | Q              | 11,8     |          | 1 |   |   |          |   |          |   | П        |   | 1  |        | T        |        |        |

| 6              | 6        |   | Г        |   |           |          |   |   |   | 1 |   |          |          | Г        | T        | r  |              | R              | 11,9     | Г        | 1 |   |   |          |   |          |   | П        |   |    | 1      | 1        | T      | ٦      |

| 7              | 7        |   | $\vdash$ | П |           |          |   |   |   |   | 1 |          |          |          | <u> </u> |    | П            | S              | 0,2      |          |   | 1 |   | 1        |   |          |   | $\sqcap$ |   |    |        | 1        | T      | ٦      |

| 8              | 8        |   |          | П | 1         |          |   |   |   |   |   | ī        |          |          |          |    | $\Box$       | Т              | 0,3      | Γ        |   | 1 |   |          | 1 |          |   | $\sqcap$ |   |    |        | T        | Ţ      | 7      |

| 9              | 9        |   | Γ        | П |           |          |   |   |   |   |   |          | 1        | -        | T        | -  | $\Box$       | U              | 0,4      |          |   | 1 |   |          |   | 1        |   | П        |   |    |        | 7        | 1      | 7      |

| \$             | 11,8,3   |   | 1        |   |           |          | 1 |   |   |   |   | ī        |          |          | T        |    | 17           | ٧              | 0,5      |          |   | 1 |   | $\vdash$ |   |          | 1 |          |   |    | П      | $\dashv$ | T      | 7      |

| . (Period)     | 12,8,3   | 1 |          | П |           |          | 1 |   |   |   |   | 1        |          | <u> </u> | T        | T  | $\Box$       | w              | 0,6      | T        |   | 1 |   | $\vdash$ |   | ┢        | П | 1        |   |    | T      | 7        | $\top$ | 7      |

| , (Comma)      | 0,8,3    | _ | $\vdash$ | 1 | 7         |          | 1 |   |   |   |   | 1        |          | -        | $\vdash$ | -  | $\top \top$  | Х              | 0,7      | T        |   | 1 |   | h        | ┢ | $\vdash$ |   | П        | 1 |    | П      | +        | $\top$ | ٦      |

| EOF            | None     |   | Г        | П | 1         |          |   |   |   |   |   |          | $\vdash$ | ī        | T        | _  | $\top$       | Υ              | 0,8      | Γ        |   | 1 |   |          |   |          |   |          |   | 1  |        | T        | T      | ٦      |

| ER<br>CHR      | None     |   |          | П |           |          |   |   |   |   |   |          |          |          | 1        |    |              | Z              | 0,9      | Γ        |   | 1 |   |          |   |          |   |          |   |    | 1      |          | T      | 7      |

| ER             | None     |   |          | H | 1         |          |   |   |   |   |   |          |          |          | T        | 1  | $\sqcap$     | Space          | Blank    | 0        | 0 | 0 | 0 | 0        | 0 | 0        | 0 | 0        | 0 | 0  | 0      | 0        | 0      | 0      |

| FLD            |          | _ | _        | Н | -         | $\dashv$ |   |   |   | _ |   | -        |          |          | ┝        | -  | +            | ¢              | 12,8,2   | 1        |   |   |   | 1        |   |          |   | $\sqcup$ |   | 1  | Ц      |          |        |        |

| =              | 6,8      |   | _        | Н | -         |          |   |   |   | 1 | H | 1        |          | -        | ⊢        | -  | $\mathbb{H}$ | <              | 12,8,4   | 1        |   |   |   |          |   | 1        |   |          |   | 1  |        |          |        |        |

| ' (Apostrophe) | 5,8      | _ | L        | Ц | 4         |          |   |   | 1 |   | L | 1        |          | _        | L        | L  | Ш            | l              | 12,8,7   | 1        |   |   |   |          |   |          |   |          | 1 | 1  |        |          |        |        |

| (              | 12,5,8   | 1 |          | Ц |           |          |   |   | 1 |   |   | 1        |          | _        | <u> </u> |    | Ш            | &              | 12       | 1        |   |   |   |          |   |          |   |          |   |    |        |          |        |        |

| )              | 11,5,8   |   | 1        | Н | _         |          |   |   | 1 |   |   | 1        |          | _        | <u> </u> | L  | $\sqcup$     | !              | 11,8,2   |          | 1 |   |   | 1        |   |          |   |          |   | 1  |        |          |        |        |

| +              | 12,8,6   | 1 | _        | Н | 4         | _        |   |   |   | 1 | L | 1        |          | _        | <u> </u> | L  | $\sqcup$     | ; (Semi-colon) | 11,8,6   |          | 1 |   |   |          |   |          |   | 1        |   | 1  |        |          |        |        |

| – (Dash)       | 11       |   | 1        | Ц | 4         |          | _ |   |   |   |   |          |          | _        | <u> </u> | L  | 1-1          | _              | 11,8,7   |          | 1 |   |   |          |   |          |   |          | 1 | 1  |        |          |        |        |

| Α              | 12,1     | 1 | _        | Ц | 1         |          | _ |   |   |   |   |          |          | _        | <u> </u> | L  | 1.1          | %              | 0,8,4    |          |   | 1 |   |          |   | 1        |   | П        |   | 1  |        |          | T      |        |

| В              | 12,2     | 1 |          | Ц | _         | 1        |   |   |   |   |   |          |          | _        | <u> </u> | L  | Ш            | (Underscore)   | 0,8,5    |          |   | 1 |   |          |   |          | 1 | П        |   | 1  | T      | 1        | 7      | ٦      |

| С              | 12,3     | 1 | _        | Ш | _         |          | 1 |   |   |   |   |          |          |          |          | L  |              | >              | 0,8,6    |          |   | 1 |   |          |   |          |   | 1        |   | ī  | П      | 1        | T      | ٦      |

| D              | 12,4     | 1 | L        |   |           |          | _ | 1 |   |   |   |          |          |          | L        | L  |              | ?              | 0,8,7    |          |   | 1 |   |          |   |          |   | П        | 1 | 1  | П      |          |        | ٦      |

| Е              | 12,5     | 1 |          | Ц |           |          |   |   | 1 |   |   |          |          |          |          | L  |              | : (Colon)      | 8,2      |          |   |   |   | 1        |   |          |   |          |   | 1  |        |          |        | ٦      |

| F              | 12,6     | 1 |          | Ш | $\perp$   |          |   |   |   | 1 |   |          |          |          |          |    |              | #              | 8,3      |          |   |   |   |          | 1 | Γ        |   | $\sqcap$ |   | 1  | $\Box$ | 7        | $\top$ | 7      |

| G              | 12,7     | 1 |          |   |           |          |   |   |   |   | 1 |          |          |          |          |    |              | @              | 8,4      |          |   |   |   |          | Г | ı        |   | $\neg$   |   | 1  | П      | 1        |        | 7      |

| Н              | 12,8     | 1 |          | Ц | $\rfloor$ | $\perp$  |   |   |   |   |   | 1        |          |          |          |    |              | п              | 8,7      | Γ        |   |   |   |          |   |          |   | П        | 1 | 1  |        | 7        |        | 7      |

| 1              | 12,9     | 1 |          | П | - [       |          |   |   |   |   |   |          | 1        |          |          |    |              | 0-8-2          | 0,8,2    | Г        |   | ī |   | 1        | Г |          |   | П        | П | 1  |        | 1        | $\top$ | ╛      |

Figure 1-3. Keyboard Character Code

1-3

- Controls the mechanical motion of the printer or keyboard.

- 4. Transfers a data or control word to or from the processor-controller.

- 5. Indicates the status of the 1816, 1053, and the adapter to the P-C.

- 6. Initiates interrupts in the processor-controller program when the 1816 or 1053 requires service.

The adapter circuits include a buffer register to store the printer data word or printer control word for the printer operations. The keyboard data and control signals are stored in the keyboard contacts until the adapter gates them to the processor-controller.

Indicators are provided for keyboard, printer, and adapter status. Analysis of these indicators enables the program to determine the functions to be performed by the 1816 and 1053. A CE-mode circuit enables the adapter to be placed in an on-line-service mode.

#### I/O INTERFACE

- The 1816-1053 adapter connects to the 1801 or 1802 P-C channel control through the standard I/O channel interface.

- The 1816 printer-keyboard and 1053 printer connect to the adapter through a unique interface.

## Channel Interface

• All I/O adapters in the 1800 system share a standard interface that is described in the IBM Field Engineering Theory of Operation (Manual of Instruction), 1800 Data Acquisition and Control System, Processor Controller. (see FE Bibliography - 1800 System, Form Y26-0560.)

The I/O channel interface consists of two sets of 60 signal and control lines. These lines connect to each I/O adapter in the 1800 system. Each adapter receives all 60 lines, and exits all 60 lines to the next adapter in sequence. If the 1816-1053 adapter is the last in the sequence, the channel interface lines must be

jumpered through the remaining adapter positions (dummy boards). The lines are then terminated at the mixer panel (gate H).

The 1816-1053 adapter taps off and uses signals from these lines:

Out-bus bits 0 through 9 and 11 through 15

(not bit 10)

In-bus bits 0 through 15

Parity bit for bits 0 through 7

Parity bit for bits 8 through 15

Poll interrupt level 0-13

Poll interrupt level 14-23

Time pulse A

Time pulse B

Time pulse C

CAR check or parity error

Storage protect violation

XIO data cycle

XIO control cycle

Reset

## I/O Device Interface

• The I/O device interface includes the signal and data lines that connect the 1816-1053 adapter to the keyboard and the printer.

The printer signals connect from the adapter board, through a flat cable and a serpent connector, to the P-C signal tailgate. The signals connect from the tailgate, through a serpent connector and signal cable to Amp connectors at the printer.

The keyboard signals connect from the adapter, through a flat cable, to the rear of the F gate. The front side of the F gate facilitates the connection of a special serpent connector that contains the integrator circuits for the key-contact signals. From this gate a flat cable connects the signals to the signal tailgate. The signals connect from the tailgate, through a serpent connector and signal cable to Amp connectors at the keyboard.

The 1816 keyboard interface lines and their functions are listed in Figure 1-4. The 1053 printer lines and functions are listed in Figure 1-5.

| Line                            | Adapter<br>In/Out | Function                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dc Ground                       | Out               | One line transmits dc ground to device.                                                                                                                                                                                                                                                                                                                    |

| Keyboard contact<br>0–9, 11, 12 | In                | These twelve lines transmit the condition of bail contacts in the keyboard. A unique combination of these contacts are closed for each key depressed on the keyboard. This combination of contacts closed is sent to core storage when the keyboard is read. Any contact closure causes a keyboard service request to be sent to the processor-controller. |

| Keyboard End Field              | ln                | This line causes a keyboard service request and causes a 12 bit to be placed in core storage in response to the read command. Analysis of this word allows the program to determine that no further characters are to be sent in this message                                                                                                              |

| Kybd . Re-enter Char .          | In                | This line causes a keyboard service request and enters a 13 bit in core storage in response to a read command.  Analysis of this word allows the program to determine that the last character received is to be replaced by the next character to be entered.                                                                                              |

| Kybd. Re-enter Field            | ln                | This line causes a keyboard service request and enters a 14 bit in core storage in response to a read command.<br>Analysis of this word allows the program to determine that the message being entered is to be deleted and replaced by the corrected message.                                                                                             |

| Kybd. Restore Key               | In                | This line turns on the keyboard-restore magnet driver in the adapter and causes the keyboard to be restored.                                                                                                                                                                                                                                               |

| Keyboard Space                  | In                | This line causes a keyboard service request and enters a zero data word in core storage in response to a read<br>command.                                                                                                                                                                                                                                  |

| Kybd. Interrupt Req.<br>Key     | In                | This line causes a keyboard interrupt request to the P–C and turns on the manual-status flip–flop. This informs the program that the operator wishes to enter a message on the keyboard.                                                                                                                                                                   |

| Keyboard Ready                  | In                | Indicates presence of +12 vdc in keyboard.                                                                                                                                                                                                                                                                                                                 |

| Kybd. Proceed Lamp              | Out               | This line turns on the proceed lamp on the keyboard, indicating the adapter is ready to receive a keyboard service request.                                                                                                                                                                                                                                |

| Kybd. Restore Mag.              | Out               | This line energizes the keyboard restore magnet and resets the keyboard.                                                                                                                                                                                                                                                                                   |

24197

Figure 1-4. 1816 Device Interface Lines

| Line                              | Adapter<br>In/Out | Function                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ready                             | In                | Indicates presence of d-c power and paper in place at the printer.                                                                                                                                                                                                                                                                                                                             |

| Carrier Return<br>Line Feed & Tab | In                | Indicates when the printer is busy performing a line feed, tab, or carrier return. The rise of the line turns on the printer-response flip-flop and the fall resets the printer-response flip-flop.                                                                                                                                                                                            |

| Printer Cam                       | In                | Indicates the printer is taking a cam cycle. Line is active when cam contact 2, 5, or 7 is open due to printer taking a cycle to perform an operation. Cam 2 is active on a print cycle. Cam 5 is active on a tab, space or backspace. Cam 7 is active on a shift. The printer-response flip-flop is turned on when this line becomes active and is turned off when the line becomes inactive. |

| Motor On                          | In                | Indicates the motor is stopped. Forces shift required and starts a 35 millisecond single-shot if motor is stopped when the adapter receives a command.                                                                                                                                                                                                                                         |

| End of Line                       | In                | Indicates the carrier is at the right hand margin. When next print cycle occurs, turns on last-col flip-flop, causing a carrier return to take place.                                                                                                                                                                                                                                          |

| Upper Case                        | Out               | Picks a magnet in the printer, causing a shift to upper case and a shift cycle in the printer (Cam 7 cycles) if the printer is not already at upper case.                                                                                                                                                                                                                                      |

| Lower Case                        | Out               | Picks a magnet in the printer, causing a shift to lower case and a shift cycle in the printer (Cam 7 cycles) if the printer is not already at lower case.                                                                                                                                                                                                                                      |

| Carrier Return                    | Out               | Picks a magnet in the printer, causing the carrier to return to the left hand margin and a line feed.                                                                                                                                                                                                                                                                                          |

| Tab                               | Out               | Picks a magnet in the printer, causing a tab cycle (Cam 5 cycles). The carrier advances to the right until it reaches the position of the next tab stop.                                                                                                                                                                                                                                       |

| Space                             | Out               | Picks a magnet in the printer, causing the carrier to advance one print position to the right, (Cam 5 cycles).                                                                                                                                                                                                                                                                                 |

| Drop Motor Relay                  | Out               | Energizes motor-control time-delay relay. If energized continually for 2 minutes, the time delay relay picks and holds as long as energized. When time delay relay picks, $TD1-1 \text{ N/C}$ drops relay 6 which drops printer motor. $TD1-2 \text{ N/O}$ informs the adapter that the motor is stopped with the motor-on line.                                                               |

| 48 v                              | Out               | Four lines are used to transmit 48 volts to the printer for magnet and relay power.                                                                                                                                                                                                                                                                                                            |

| +12 v                             | Out               | 12 volts to the printer to power ready, end of line, carrier-return, line-feed, and tab status contacts.                                                                                                                                                                                                                                                                                       |

| d-c Ground                        | Out               | Two lines are used to transmit dc ground.                                                                                                                                                                                                                                                                                                                                                      |

| T2,T1,R1,R2A                      | Out               | Picks magnets in the printer to control the positioning of the print ball and cause the printer to take a print cycle (Cam 2 cycles).                                                                                                                                                                                                                                                          |

| Backspace                         | Out               | Picks a magnet in the printer, causing the carrier to advance one print position to the left (Cam 5 cycles).                                                                                                                                                                                                                                                                                   |

| R2                                | Out               | Picks a magnet in the printer to control the positioning of the print ball and cause the printer to take a print cycle (Cam 2 cycles).                                                                                                                                                                                                                                                         |

| Red                               | Out               | Picks a magnet in the printer, causing a shift of the ribbon mechanism so printing will take place on red portion of ribbon.                                                                                                                                                                                                                                                                   |

| R5                                | Out               | Picks a magnet in the printer to control the positioning of the print ball and cause the printer to take a print cycle (Cam 2 cycles).                                                                                                                                                                                                                                                         |

| Black                             | Out               | Picks a magnet in the printer, causing a shift of the ribbon mechanism so printing will take place on black portion of ribbon.                                                                                                                                                                                                                                                                 |

| Line Feed                         | Out               | Picks a magnet in the printer to cause the platen to advance.                                                                                                                                                                                                                                                                                                                                  |

| Aux.                              | Out               | Picks a magnet in the printer to cause a print cycle to occur if the character to be printed is all zeros and does not pick any other print-positioning magnet. The ball prints its home position character. The printer takes a print cycle (Cam 2 cycles).                                                                                                                                   |

24205

Figure 1-5. 1053 Device Interface Lines

## CHAPTER 2 FUNCTIONAL UNITS

• The interrelationship of the functional units described in this section is shown in the 1800 System Maintenance Diagram Manual (MDM) page EA 40160.

#### FUNCTION REGISTER

- One three-position register decodes the functions for both the keyboard and the printer.

- Loaded from out-bus bits 5, 6, and 7 during the XIO control cycle.

Bits 5, 6, and 7 of the IOCC control word, placed of the out bus during the XIO control cycle, are the gal inputs to the function register. The pulse that sets the register, called function set, is activated by the XIO-control-cycle line if the printer-keyboard area or interrupt level is on the out bus and if there is no parity error indicated by the processor-controller (P-C). The function register is reset at the end of the XIO data cycle. The decoded output of the function register provides the following functions:

<u>001 Write</u>: This command sends the P-C word at the core storage location specified by the IOCC address word to the typewriter-printer. The word sent to the typewriter-printer is either printed or it causes a control operation to be performed.

<u>010 Read</u>: This command enters a single input character from the keyboard into the P-C core storage location specified by the IOCC address word. This command turns off the proceed status. It also turns on the parity or storage-protect indicator if either error is detected during the read operation.

011 Sense Interrupt: This command directs the printer keyboard adapter to place its assigned interrupt-level-status-word (ILSW) bit on the in bus if any of its interrupt indicators are on. The ILSW is loaded into the P-C accumulator for program analysis.

100 Control: This command restores the keyboard and turns on the proceed lamp. The proceed lamp indicates to the operator that the P-C is ready to receive a keyboard character. The depression of a character key will then cause a service interrupt.

111 Sense Device: This command causes the selected printer or printer-keyboard to place its device status word (DSW) on the in bus. The DSW is loaded into the P-C accumulator for program analysis.

000 CE Mode: This special use command is not decoded by the function register. It is decoded by the CE mode circuit, to place the selected printer or printer-keyboard in, or take it out of, the CE mode.

#### CHARACTER SHIFT CIRCUITS

- Consists of a single flip-flop, named "shift required."

- Controls the upper- and lowercase magnets in the printer.

- Delays printing to allow time for shifting.

- Controlled by bit 6 of the data word.

- Refer to FEMDM page EA 60100 for explanation of write operation with shift.

#### BUFFER REGISTER

- Eight flip-flops, loaded from out-bus bits 0 through 7.

- Loaded at T7 time of the XIO data cycle.

- Six positions are dual purpose; their function is determined by out-bus bit 7.

Reset by a single-shot after the print operation has commenced.

If out-bus bit 7 = 1, specifying a control operation, buffer-register position 7 is not turned on. The off condition of position 7 gates the output of positions 0 through 6 to the printer control magnets. If out-bus bit 7 = 0, specifying a print operation, buffer-register position 7 is turned on. The on condition of position-7 gates the output of positions 0 through 5 to the print magnets.

#### CHAPTER 3 PRINCIPLES OF OPERATION

#### PRINTER OPERATIONS

- An execute I/O instruction places the control word of the addressed I/O control command (IOCC) on the out bus.

- Bits 5, 6, and 7 are loaded into and decoded by the printer-keyboard function register.

- The printer performs any of the following functions:

- 1. Control (carrier return, tabulate, etc.)

- 2. Shift and print

- 3. Print without a shift

- 4. Sense device

- The write function, modified by bit 7 of the data word, can initiate either a print or a control operation.

- The sense device function places the status of the printer indicators on the in bus.

#### Write

- Reads data word from core storage location specified by IOCC address word and places it on the out bus.

- Data word is either printed or it is decoded to cause a printer control operation.

- The I/O operation diagrams for the write function are on MDM page EA 40111 and EA 40112.

- The write operation objectives are shown for each type of operation on MDM page EA 60100.

- The timing diagrams for the write function are on MDM page EA 60105, and EA 70100.

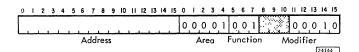

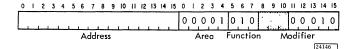

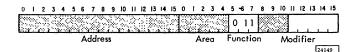

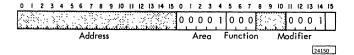

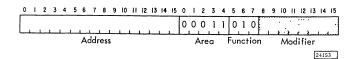

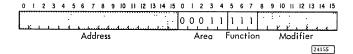

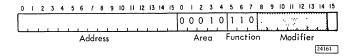

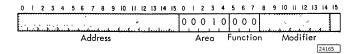

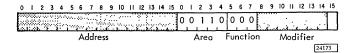

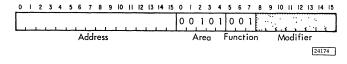

IOCC - Write

Address: These 16 bits specify the core storage location of the data word. It is used during the XIO data cycle.

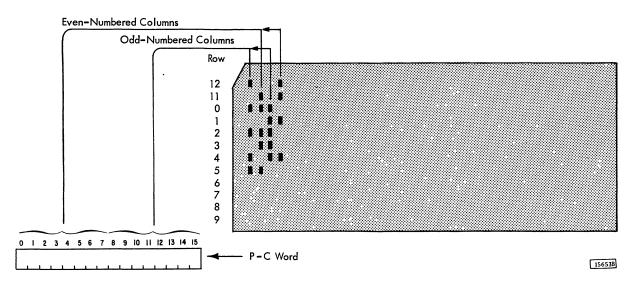

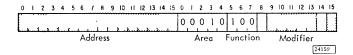

Area: Bits 0 through 4 decode as 00001 to specify the printer-keyboard adapter.

<u>Function:</u> Bits 5, 6, and 7 decode as 001 to specify a write function.

Modifier: Bits 11 through 14 select the printer. Bit 14 addresses the first printer, bit 13 addresses the second, bit 12 the third, and bit 11 the fourth. If two or more printers are addressed, all those addressed will print the same data simultaneously.

#### Data Word

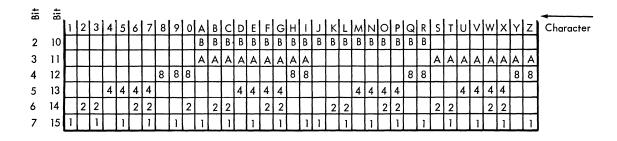

Data to be printed by the typewriter-printer is coded by the program into the typewriter code. Figure 1-6 shows the characters which can be printed by the standard print element for IBM 1800 typewriterprinters.

Bit 6 of the data-character determines the upper-case (UC) shift or lower-case (LC) shift characters. The printer shifts automatically as required for each data character.

A typewriter-printer write command is effectively modified by bit 7 position of the output character word. If bit 7 = 1, the write command to the printer results in a control function. If bit 7 = 0, the write command results in a print function.

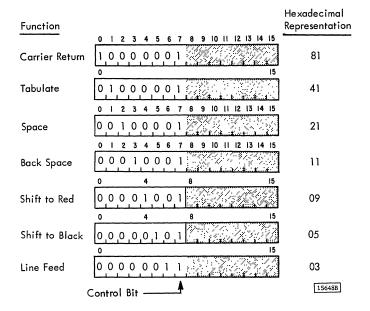

The codes for typewriter-printer control functions are shown in Figure 1-7.

## Description

E-1 Cycle: This cycle is referred to as the XIO control cycle. The effective address (EA), loaded into the accumulator during the I cycle, must be an even address. This address, which is the location of the IOCC, is loaded into the M register. The on output line of the M register bit-15 flip-flop is activated. This causes EA+1, the location of the IOCC control word, to be addressed. The control word, which includes the area, function, and modifier bits, is placed on the out bus.

The channel function register is loaded at T5 time to perform I/O bus gating, etc. The function register in the printer-keyboard adapter is loaded if the printer

| во                                                                                          | В1                                                                                                                                                                                    | B2                                                                                                                                                                                              | В3                                                                                                                                                                                    | B4                                                                                               | B5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B6≡0<br>LC                                          | B6≘ 1<br>UC                                         | B <i>7</i>                                                                                  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A B C D E F G H I J K L M N O P Q R S T U V W X Y Z | A B C D E F G H I J K L M N O P Q R S T U V W X Y Z | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                     |

| 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0                | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0                                                                                                                              | 1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0                                                                                                | 1<br>1<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                     | 1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 10011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011001100110011000110001100011000110001100011000110000 | 1 2 3 4 5 6 7 8 9 0 # / - · & \$ @ •                | ( + < 「 ) ; * - = -   - ? :. >% ¢                   | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

Figure 1-6. Data Character Coding (1816/1053)

area code is specified in the IOCC and if there is no parity error signal from the processor-controller. The decoded output of the function register is used during the E-3 data cycle to specify the write function (Code 001).

Figure 1-7. Control Characters (1816/1053)

E-2 Cycle: The  $M_{15}$  bit output is no longer forced active so that EA, which is the location of the address word, is addressed. The address word is therefore read from core storage and loaded into the accumulator for use in the E-3 cycle.

E-3 Data Cycle: The address word of the IOCC, loaded into the accumulator during the E-2 cycle, addresses the data word which is placed on the out bus. The XIO instruction execution is terminated and the program continues with the next instruction.

Print and Control Execution: FEMDM pages EA 60100 through EA 60110 illustrate the following printer operations:

- Print character with motor on/off.

- Print with shift.

- Print last column (EOL).

- Control operation.

- Color shift.

## KEYBOARD OPERATIONS

- Request key initiates an interrupt request and locks the keyboard. When the interrupt is serviced, an XIO instruction with an IOCC specifying a control function is executed.

- The control operation selects the keyboard, places it in the proceed status, unlocks the keyboard, and turns on the proceed lamp.

- Operation of a character key places the card code of that character into the keyboard contacts and initiates another interrupt request.

- When this interrupt is serviced, an XIO instruction with an IOCC specifying a read function is executed.

- The read operation transfers the data word (card-code character) from the keyboard contacts to the processor-controller (P-C) core storage.

- The I/O operation diagram for the keyboard control and read operations is on MDM page EA 40101.

- The timing diagram for the control and read operations is on MDM page EA 70101.

The keyboard operation, for the first character, requires these four steps:

- 1. <u>Keyboard Request</u>. The operator presses the request key to signal the P-C that a character is to be entered from the keyboard.

- 2. <u>Control Command</u>. The P-C signals the key-board adapter that it is ready to accept the character.

- 3. Character Key Operation. The operator presses the character key and the keyboard adapter signals the P-C that the character is ready to be placed on the in bus.

- 4. Read Command. The P-C executes a read operation to take the character and store it.

The operation for subsequent characters requires steps 2 through 4.

## Keyboard Request

- Initiated by operation of the keyboard request key.

- Generates an interrupt request to the P-C.

- Locks the keyboard.

Operating the keyboard request key activates a 25-millisecond keyboard-service-request single-shot. The timing out of this single-shot turns on the manual-status flip-flop which activates a second single-shot, the output of which restores the keyboard. Manual-status also conditions the typewriter interrupt-request circuit that is activated when its assigned interrupt level is polled by the P-C.

## Control Command

- Initiated by an XIO instruction as a result of an interrupt.

- Selects the keyboard, restores the keyboard, and turns on the proceed lamp.

When the P-C satisfies all conditions to service the interrupt initiated by the request key, a branch is forced to a subroutine containing an XIO instruction with an IOCC specifying the keyboard and a control function.

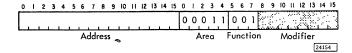

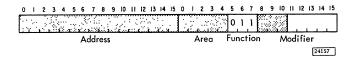

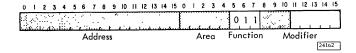

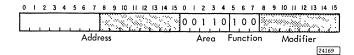

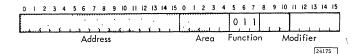

IOCC Control

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 1 12 13 14 15 0 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 1 12 13 14 15 0 1 12 13 14 15 0 1 1 12 13 14 15 0 1 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13 14 15 10 11 12 13

Address: Not used.

Area: Bits 0 through 4 decode as 00001 to select the printer-keyboard area.

<u>Function</u>: Bits 5, 6, and 7 decode as 100 to cause the keyboard to perform a control operation.

Modifier: Bits 11 through 14 decode to select the specified printer or keyboard. Bit 14 must be a one to select the keyboard.

#### Description

E-1 Control Cycle: The keyboard area code and bit 14 of the IOCC turn on the select-keyboard flip-flop. The control function is decoded by the function register.

E-2 Data Cycle: At T6 of this cycle, the 25 millisecond restore single-shot is activated to energize the keyboard restore magnet. The restore single-shot also turns on the proceed flip-flop, the output of which turns on the proceed lamp on the keyboard. The proceed lamp signals the operator to press a character key. The fall of the XIO data cycle line activates the function reset line to reset the function register.

## Character Key Operation

- Stores the character code in the keyboard contacts.

- Initiates an interrupt request after a 25-millisecond delay.

The operation of any keyboard contact activates the keyboard-service-request line. Keyboard-service-request activates a 25-millisecond single-shot. The timing out of the single-shot resets the proceed flip-flop and turns on the service-request flip-flop. The output of the service-request flip-flop conditions the typewriter interrupt-request circuit that is activated when its level is polled by the P-C.

## Read Command

- Initiated by an XIO instruction as a result of an interrupt.

- Gates the character from the keyboard to the in bus.

- Stores the character at the location specified by the address portion of the IOCC.

- Resets the proceed flip-flop.

- The I/O operation diagram for the read operation is on MDM page EA 40101.

When the P-C satisfies all conditions to service the keyboard interrupt, a branch is forced to a subroutine containing an XIO instruction with an IOCC specifying keyboard and a read function.

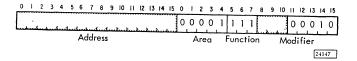

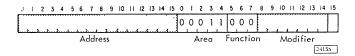

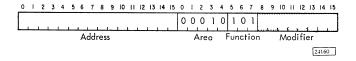

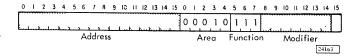

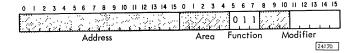

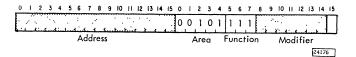

IOCC Read

<u>Address</u>: This 16-bit address word specifies the core storage location into which the keyboard character is stored.

<u>Area:</u> Bits 0 through 4 decode as 00001 to select the printer-keyboard area.

<u>Function</u>: Bits 5, 6, and 7 decode as 010 to cause the keyboard to perform the read operation.

<u>Modifier:</u> Bits 11 through 14 decode to select the specified printer or keyboard. Bit 14 must be a one to select the keyboard.

Example: Bit 14 = 1 selects 1816 number 1

Bit 13 = 1 selects 1053 number 2

## Description

$\underline{\text{E-1 Control Cycle:}}$  The on output line of the M register bit-15 flip-flop is activated to address EA + 1 (odd). This address is the location of the control word of the IOCC. The control word is set into the B register and placed on the out bus.

The keyboard area code and bit 14 of the IOCC turn on the select-keyboard flip-flop. The area code also activates the function-set line to load the function register with bits 5, 6, and 7.

E-2 Cycle: The decoded output of the function register is used to specify the read function (Code 010). The P-C drops the forced M<sub>15</sub>-bit line, reads the IOCC address word (at EA) and loads it into the accumulator to be used during the E-3 cycle to address core storage.

<u>E-3 Data Cycle:</u> The select-keyboard and read-function lines activate the keyboard-read-gate line

which gates the character from the keyboard contacts to the in bus. The character is stored at the core storage location specified by the IOCC address word. The keyboard-read-gate also conditions parity or storage-protect flip-flops to be turned on at T7 if either error is detected.

The fall of XIO-data-cycle activates the functionreset line to reset the function register. The fall of keyboard-read-gate resets the proceed flip-flop.

If additional characters are to be entered, the program must execute another XIO control command to return the keyboard to the proceed condition. After the last character is entered, the end-of-message key is operated to indicate to the program that the subroutine need not be repeated.

# PRINTER-KEYBOARD SENSE AND CE MODE OPERATIONS

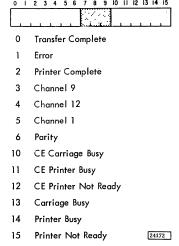

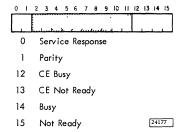

#### Sense Device

- Places the printer or printer-keyboard device status word (DSW) on the in bus.

- The DSW is loaded into the P-C accumulator to be analyzed by the program.

- If specified by bit 15 of the IOCC control word, the sensed indicators are reset.

- The I/O operation diagram for the sense device operation is on MDM page EA 40151.

The first printer and the keyboard are both selected by the same modifier code. Therefore, the first printer indicators and the keyboard indicators are all placed on the in bus as one DSW. If any printer other than the first printer is selected, the indicators for that printer only will be placed on the in bus as the DSW.

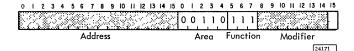

IOCC - Sense Device

Address: Not used.

Area: Control-word bits 0 through 4 decode as 00001 to select the printer-keyboard area.

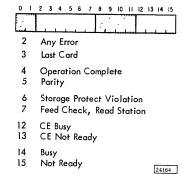

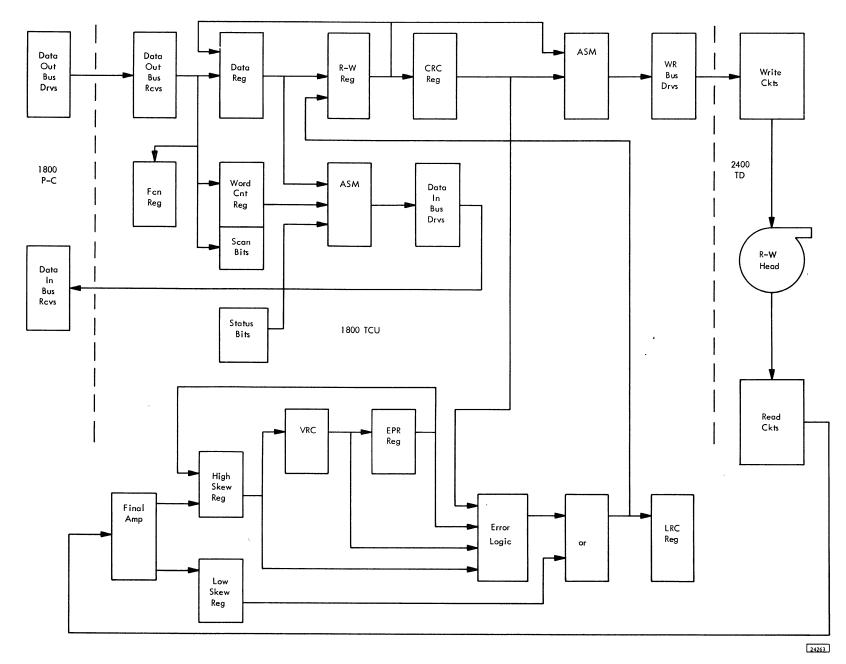

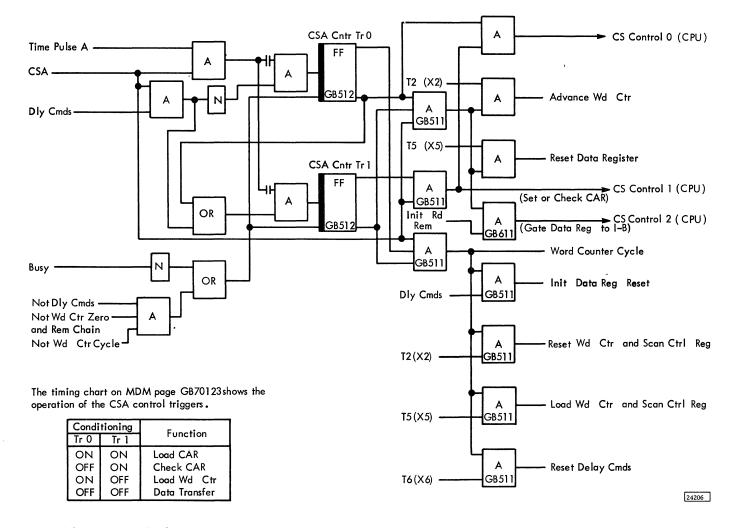

<u>Function</u>: Bits 5, 6, and 7 decode as 111 to cause the printer-keyboard to perform a sense device operation.