IBM

Field Engineering Manual of Instruction

Field Engineering

# Manual of Instruction

| Issued to:                                                                  |  |

|-----------------------------------------------------------------------------|--|

| Branch Office:                                                              |  |

| Department:                                                                 |  |

| Address:                                                                    |  |

| If this manual is misplaced, it should<br>be returned to the above address. |  |

#### PREFACE

This manual describes the theory and operation of the IBM 2481 Storage Control Unit with the IBM 2311 Disk Storage Unit.

The following is a list of companion and prerequisite manuals necessary for understanding of the 2841.

IBM Field Engineering Diagram Manual, 2841 Storage Control Unit (Form 227-3644)

IBM Systems Reference Library Manual, System 360 Component Descriptions (Form A26-5988)

IBM Field Engineering Preschool Manuals, System/360

IBM Systems Reference Library Manual, System/360 Principles of Operation (Form A22-6821)

IBM Field Engineering Maintenance Manual, 2841 Storage Control Unit (Form 227-3615)

IBM Field Engineering Manual of Instruction, SLT Packaging

IBM Installation Manual, 2841 Storage Control Unit (included in System Diagram Manual)

IBM Maintenance Diagram Manual, 2841 Storage Control Unit (included in System Diagram Manual

It is assumed that the student has completed IBM System/360 preschool training and has been trained on the 2311 Disk Storage Unit.

Because the 2311 is the standard device used with the 2841, most of the references in Chapters 1 through 4 of this manual are to operation with the 2311 interface.

The users of this manual are cautioned that machine specifications are subject to change at any time and without prior notice by IBM. Wiring diagrams (logics) at the engineering change level of that specific machine are included in each machine shipment.

This edition (Form 227-3614-2) is a major revision of Form 227-3614-1. The latter is made obsolete by this revision.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. A form has been provided at the back of this publication for readers' comments. If the form has been detached, comments may be directed to: IBM, Product Publications Department, San Jose, Calif. 95114

© International Business Machines Corporation 1966

| CHAPTE   | R 1 INTRODUCTION                                                                                              | 1.1        |

|----------|---------------------------------------------------------------------------------------------------------------|------------|

| 1.1      | GENERAL INFORMATION                                                                                           | 1.1        |

| 1.2      | PHYSICAL DESCRIPTION                                                                                          | 1.2        |

|          | 1.2.1 Dimensions                                                                                              | 1.2        |

|          | 1.2.2 Power Requirements.                                                                                     | 1.2        |

|          | <b>1.2.</b> 3 Cable Entry                                                                                     | 1.2        |

|          | 1.2.4 Operator's Position.                                                                                    | 1.2        |

|          | 1.2.5 Environmental Conditions                                                                                | 1.2        |

| 4.0      | 1.2.6 Power Control                                                                                           | 1.2        |

| 1.3      | FUNCTIONAL DESCRIPTION.                                                                                       | 1.2        |

|          | 1.3.1 System/360 Channel Interface                                                                            | 1.2<br>1.2 |

|          | 1.3.2 Arithmetic/Logical Unit (ALU)<br>1.3.3 Serializer/Deserializer Unit (SERDES)                            | 1.2        |

|          | <ol> <li>3.3 Serializer/Deserializer Unit (SERDES)</li> <li>3.4 Fourteen General Purpose Registers</li> </ol> | 1.2        |

|          | 1.3.5 Transformer Read-Only-Storage (TROS).                                                                   | 1.3        |

|          | 1.3.6 Device Interfaces                                                                                       | 1.3        |

|          | 1.3.7 Basic Write Data Flow                                                                                   | 1.3        |

|          | 1.3.8 Basic Read Data Flow                                                                                    | 1.3        |

| 1.4      | TRACK FORMAT.                                                                                                 | 1.3        |

|          | 1.4.1 Index Marker                                                                                            | 1.3        |

|          | 1.4.2 Home Address Area                                                                                       | 1.3        |

|          | 1.4.3 Track Descriptor Record (R0)                                                                            | 1.4        |

|          | 1.4.4. Data Record                                                                                            | 1.5        |

|          | 1.4.5 Gaps                                                                                                    | 1,6        |

|          | 1.4.6 Error Detection                                                                                         | 1.6        |

| 1.5      | PROGRAMMING                                                                                                   | 1.7        |

| System/3 | 60 I/O Interface                                                                                              | 1.7        |

| 1.6      | CHANNEL INTERFACE INTRODUCTION                                                                                | 1.7        |

| 1.7      | INTERFACE LINES                                                                                               | 1.7        |

|          | 1.7.1 Bus Lines                                                                                               | 1.8        |

|          | 1.7.2 Scan Controls                                                                                           | 1.8        |

|          | 1.7.3 Outbound Tøg Lines                                                                                      | 1.9        |

|          | 1.7.4 Inbound Tag Lines                                                                                       | 1.11       |

|          | 1.7.5 Interlock Lines                                                                                         | 1.11       |

|          | 1.7.6 Special Controls                                                                                        | 1.12       |

| 1,8      | INTERFACE OPERATIONS                                                                                          | 1.13       |

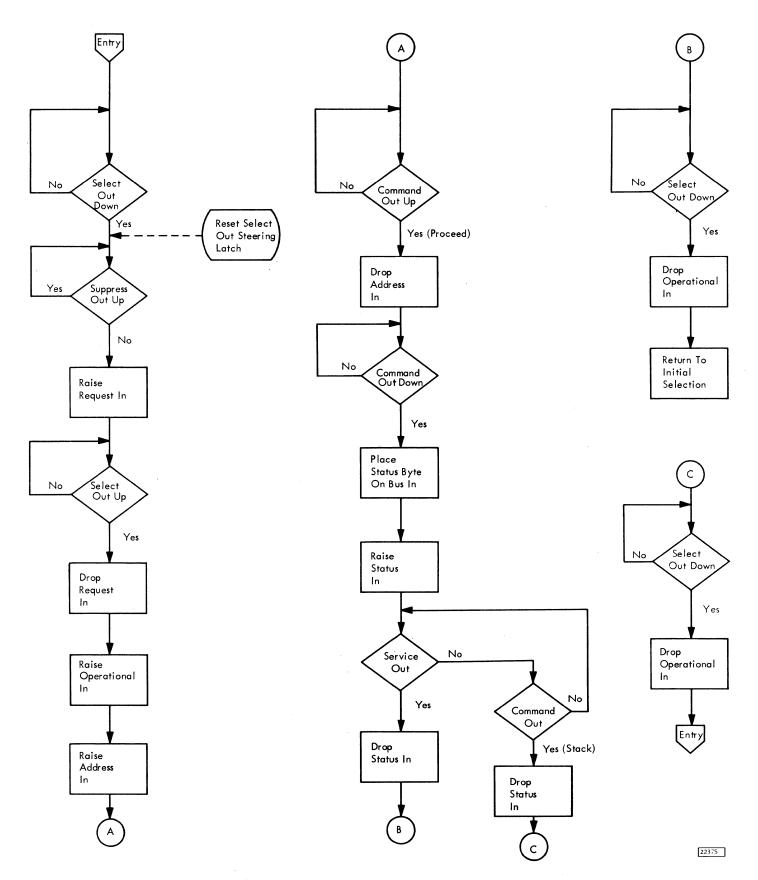

|          | 1.8.1 Initial Selection Sequence                                                                              | 1.13       |

|          | 1.8.2 Data Transfers                                                                                          | 1.14       |

|          | 1.8.3 End Operation                                                                                           | 1.14       |

| CUADTE   | R 2 FUNCTIONAL UNITS                                                                                          | 2, 1       |

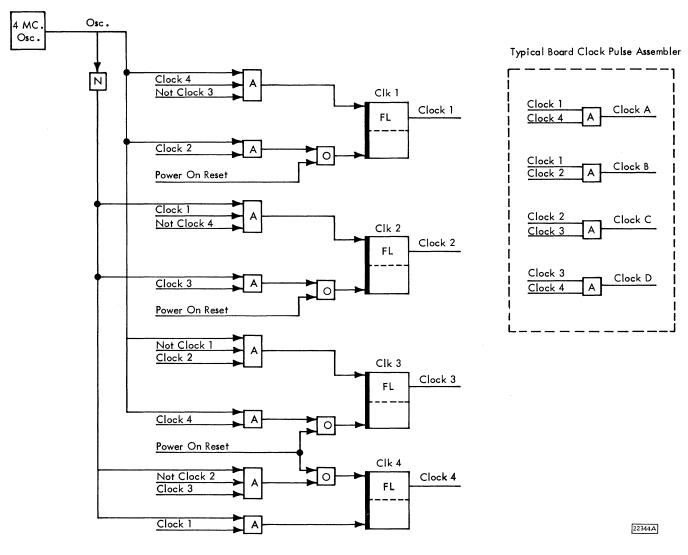

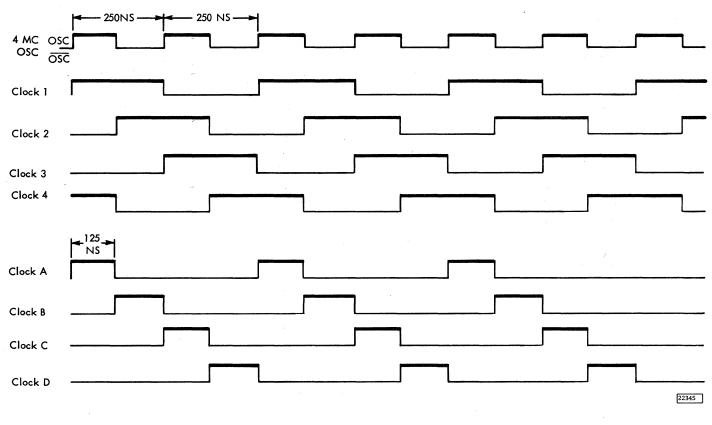

|          | MACHINE CLOCK                                                                                                 | 2,1        |

|          | REGISTERS                                                                                                     | 2,1        |

|          | 2.2.1 General Purpose Registers                                                                               | 2,1        |

|          | 2.2.2 A Register                                                                                              | 2.1        |

|          | 2.2.3 B Register                                                                                              | 2, 1       |

|          | 2.2.4 DR Register - Data Read Register                                                                        | 2.2        |

|          | 2.2.5 ST Register - Status Register                                                                           | 2.2        |

|          | 2.2.6 ER - Error Register                                                                                     | 2.2        |

|          | 2.2.7 Miscellaneous Registers and Controls                                                                    | 2,2        |

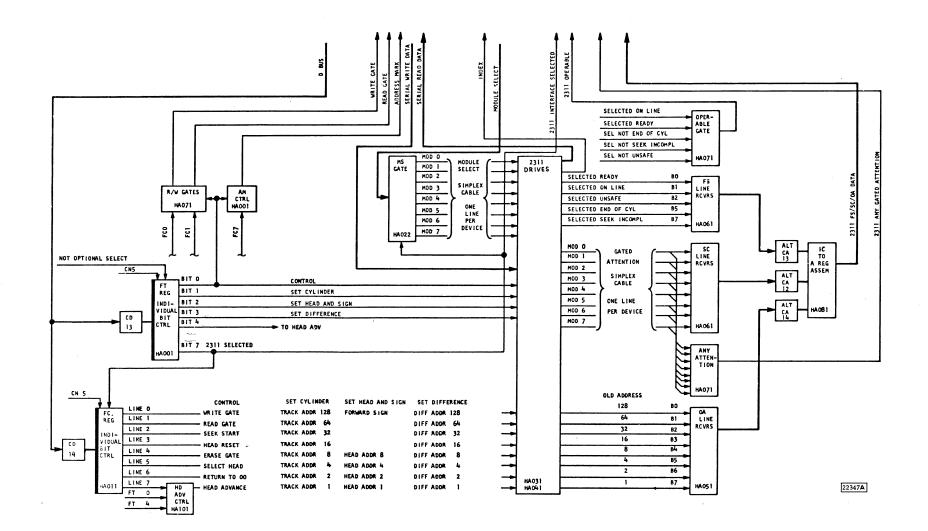

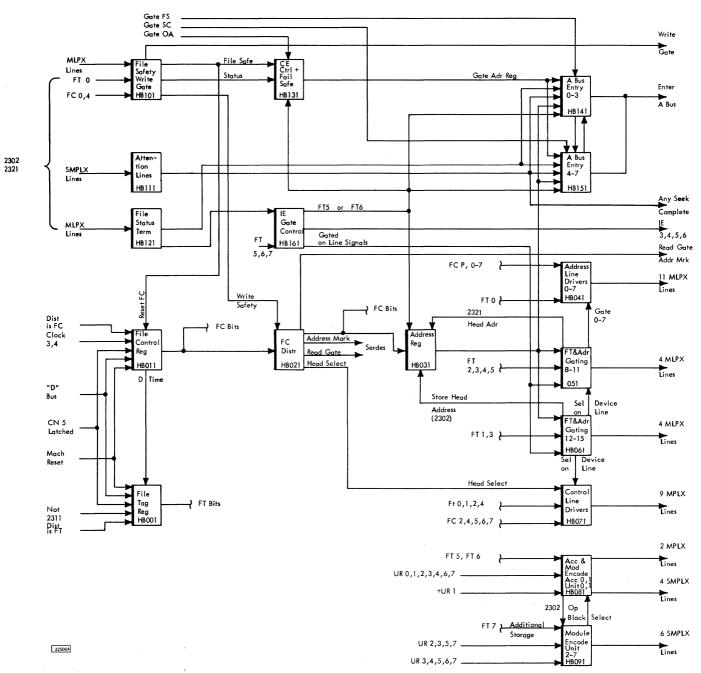

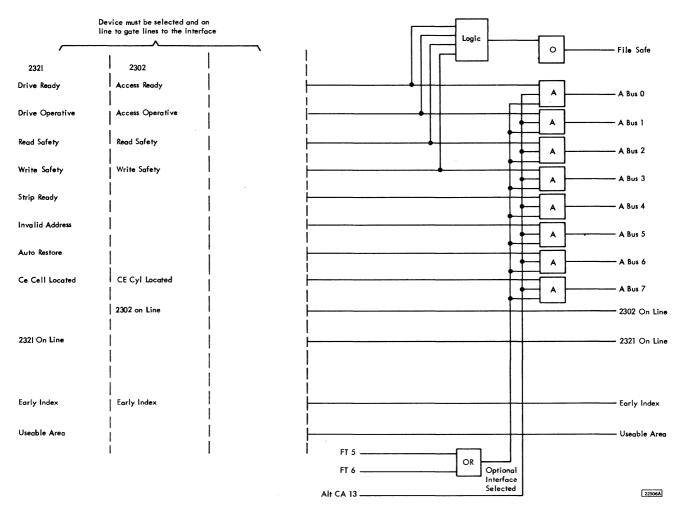

| 2.3      | 2311 INTERFACE ATTACHMENT                                                                                     | 2.3        |

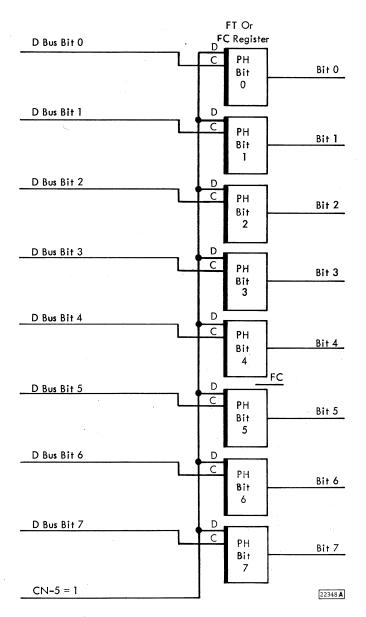

|          | 2.3.1 FT - File Tag Register                                                                                  | 2.3        |

|          | 2.3.2 FC - File Control Register                                                                              | 2.3        |

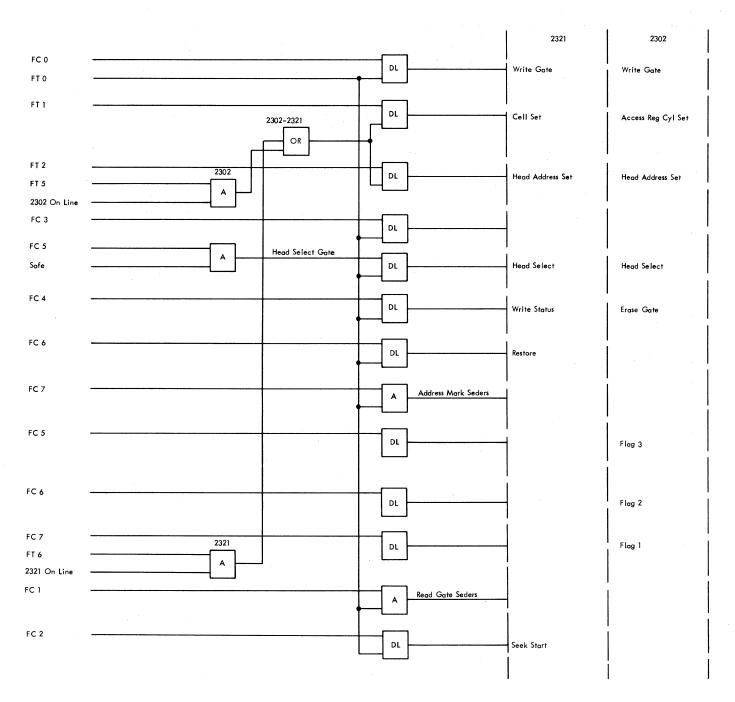

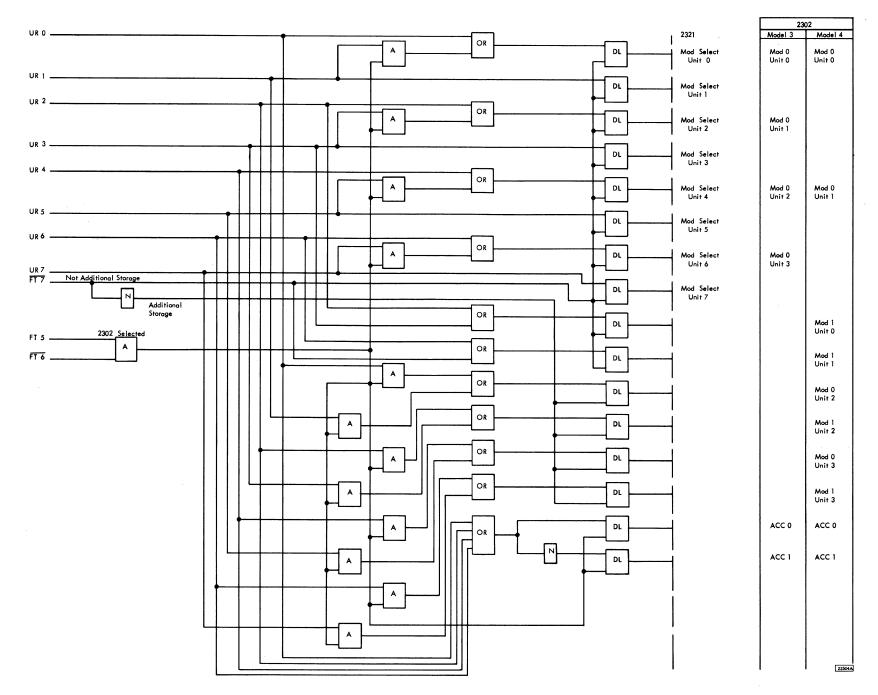

|          | 2.3.3 MS - Module Select Gates                                                                                | 2.4        |

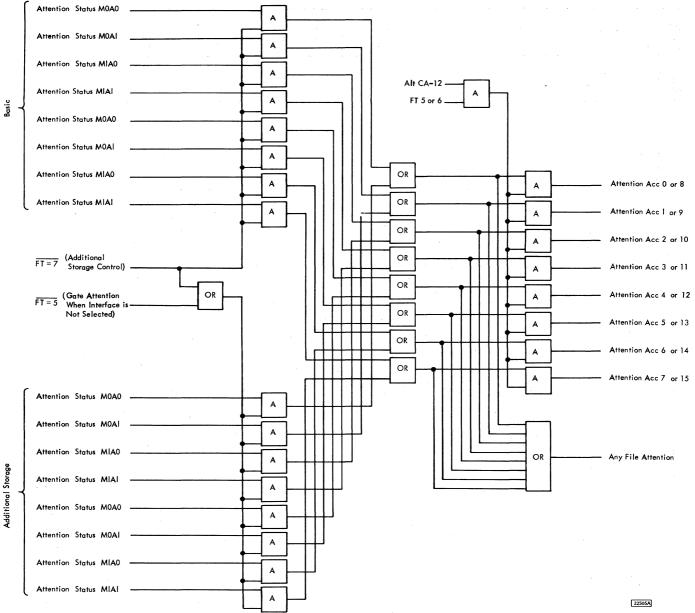

|          | 2.3.4 SC - Seek Complete Gates                                                                                | 2.4        |

|          | 2.3.5 FS - File Status Gates                                                                                  | 2.4        |

|          | 2.3.6 OA - Old Address Gates                                                                                  | 2.4        |

|          | 2.3.7 IE - Input Element Gates                                                                                | 2.4        |

|          |                                                                                                               |            |

| 2.4 | TRANSFORMER READ ONLY STORAGE - TROS.    | 2.4          |

|-----|------------------------------------------|--------------|

|     | 2.4.1 Purpose and Use of TROS            | 2.4          |

|     | 2.4.2 Characteristics and Capacity       | 2.5          |

|     | 2.4.3 Principles of Operation            | 2.5          |

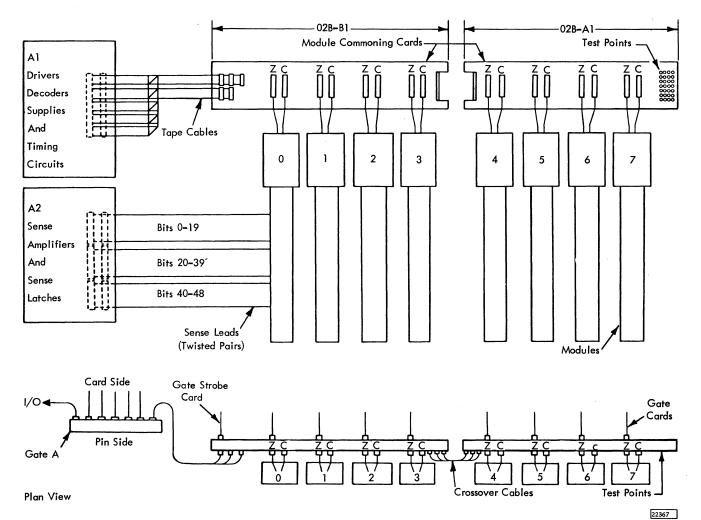

|     | 2.4.4 Module Physical Construction       | 2.6          |

|     | 2.4.5 TROS Tape Deck                     | 2.7          |

|     | 2.4.6 Addressing TROS                    | 2.7          |

|     | 2.4.7 Decoding the Address Register      | 2.8          |

|     | 2.4.8 TROS Functional Operation          | 2.9          |

|     | 2.4.9 Array Layout                       | <b>2.</b> 9  |

|     | 2.4.10 TROS Output Word                  | 2,10         |

|     | 2.4.11 Control Latches                   | 2.10         |

|     | 2.4.12 TROS Address Check                | 2,10         |

|     | 2.4.13 TROS Sense Amplifier Check        | 2, 11        |

|     | 2.4.14 TROS Control Register Check       | 2, 11        |

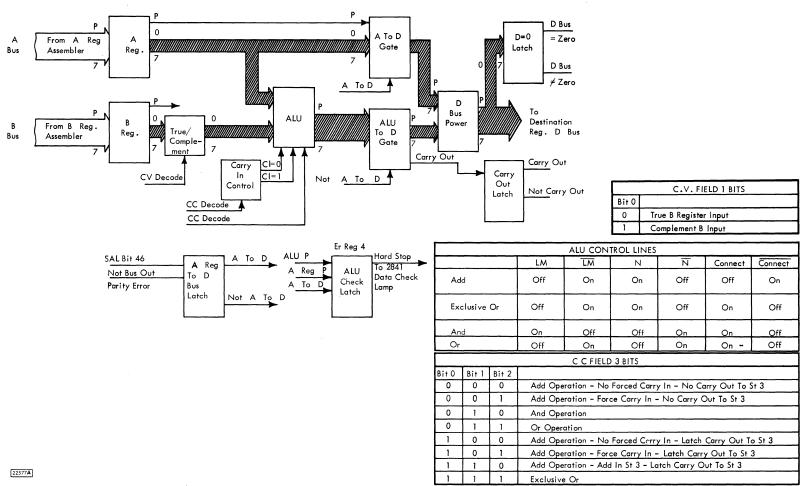

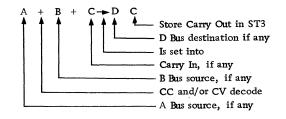

| 2.5 | ARITHMETIC/LOGICAL UNIT (ALU)            | 2.11         |

|     | 2.5.1 ALU General Description            | 2.11         |

|     | 2.5.2 Summary of ALU Statements          | 2.12         |

|     | 2.5.3 ALU Functional Description and     |              |

|     | Basic Timing                             | 2.14         |

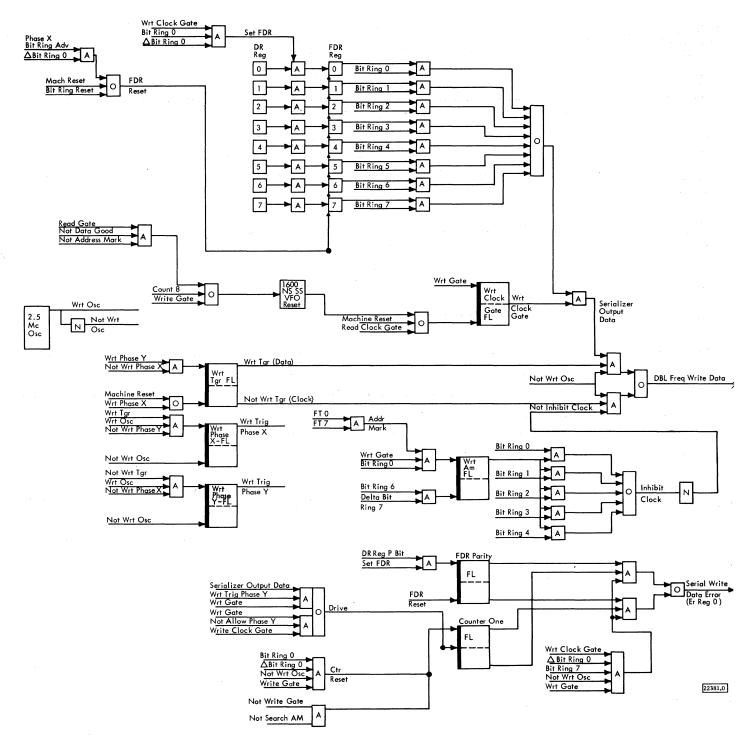

| 2.6 | SERIALIZER/DESERIALIZER UNIT             | 2,15         |

|     | 2.6.1 SERDES General Description         | 2,15         |

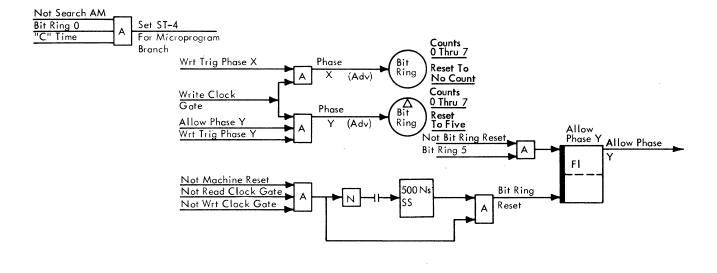

|     | 2.6.2 Write Operation                    | 2.15         |

|     | 2.6.3 Read Operation                     | 2.16         |

| 2.7 | CHANNEL INTERFACE ATTACHMENT • • • • • • | 2.18         |

|     | 2.7.1 Initial Selection Sequence         | 2.18         |

|     | 2.7.2 Data Transfer Sequences            | <b>2.</b> 19 |

|     | 2.7.3 Ending Sequence                    | 2, 20        |

|     | 2.7.4 Short Control Unit Busy Sequence   | 2, 20        |

|     | 2.7.5 Halt I/O Instruction               | 2.21         |

|     | 2.7.6 Polling Interrupts                 | 2, 21        |

|     | 2.7.7 Resets                             | 2.22         |

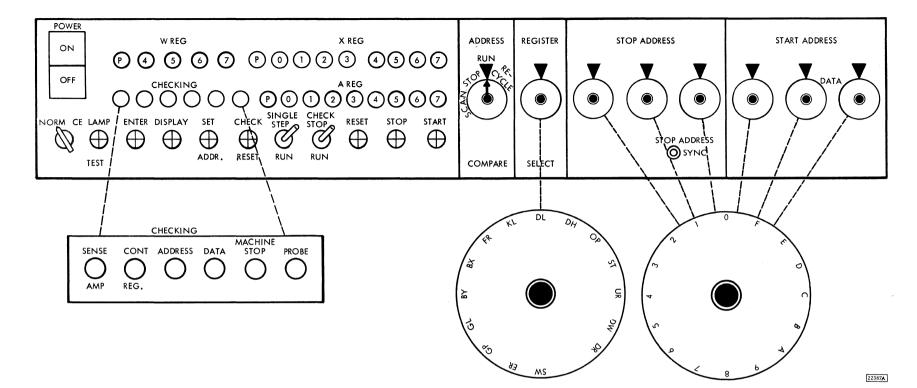

| 2.8 | CE PANEL                                 | 2, 23        |

|     | 2.8.1 CE Switches                        | 2,23         |

|     | 2.8.2 CE Indicators                      | 2, 24        |

| 2.9 | CAS MICROBLOCK                           | 2, 25        |

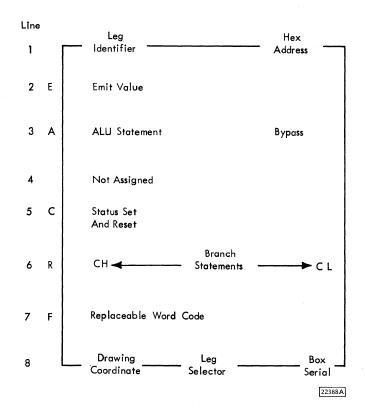

|     | 2.9.1 TROS Bit Assignment Chart          | 2, 25        |

|     | 2.9.2 Microblock Symbology               | 2, 27        |

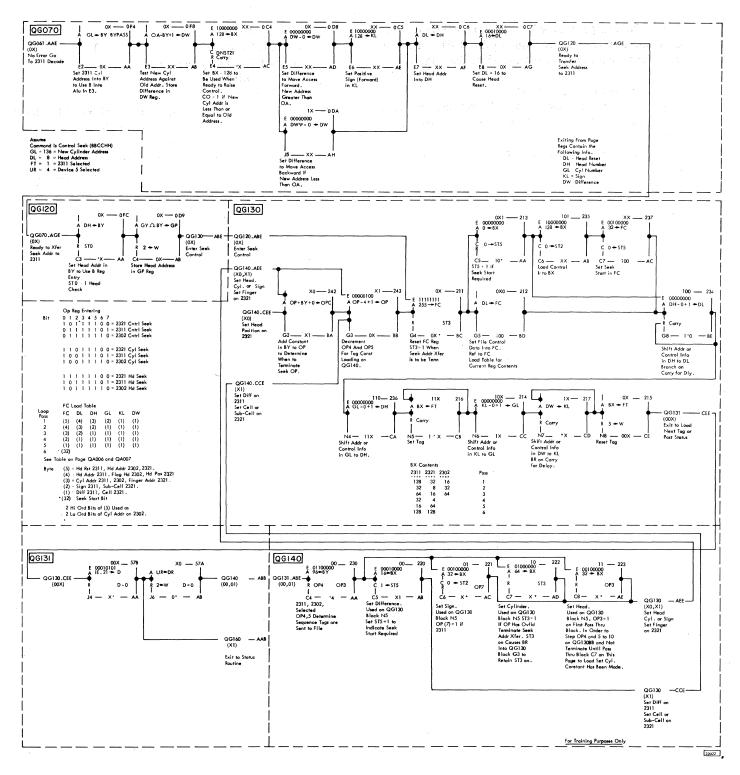

|     | 2.9.3 Sample Usage of Microblocks        | 2, 28        |

|     |                                          |              |

| CHAPTE | R 3 THEORY OF OPERATION                | 3.1 |

|--------|----------------------------------------|-----|

| 3.1    | STATUS INFORMATION                     | 3.1 |

| 3.2    | SENSE INFORMATION                      | 3,2 |

|        | 3.2.1 Sense Byte 0                     | 3.2 |

|        | 3.2.2 Sense Byte 1                     | 3.3 |

|        | 3.2.3 Sense Byte 2                     | 3.4 |

|        | 3.2.4 Sense Byte 3                     | 3.4 |

|        | 3.2.5 Sense Byte 4                     | 3.5 |

|        | 3.2.6 Sense Byte 5                     | 3.5 |

| 3.3    | MISCELLANEOUS OPERATIONS               | 3.5 |

|        | 3.3.1 Multiple Track (M/T) Operation   | 3.5 |

|        | 3.3.2 End-of-File                      | 3,5 |

|        | 3.3.3 Defective Surfaces               | 3.6 |

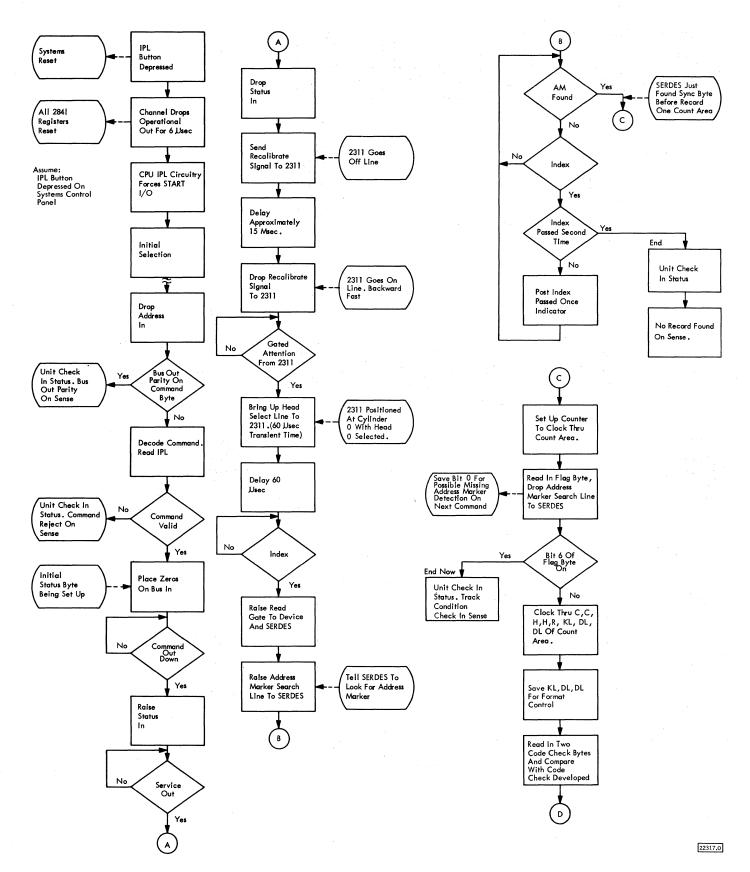

|        | 3.3.4 Initial Program Load (0000 0010) | 3.8 |

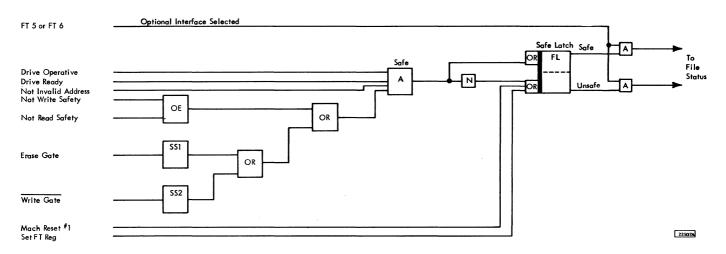

|        | 3.3.5 File Protection                  | 3.8 |

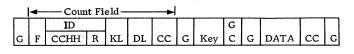

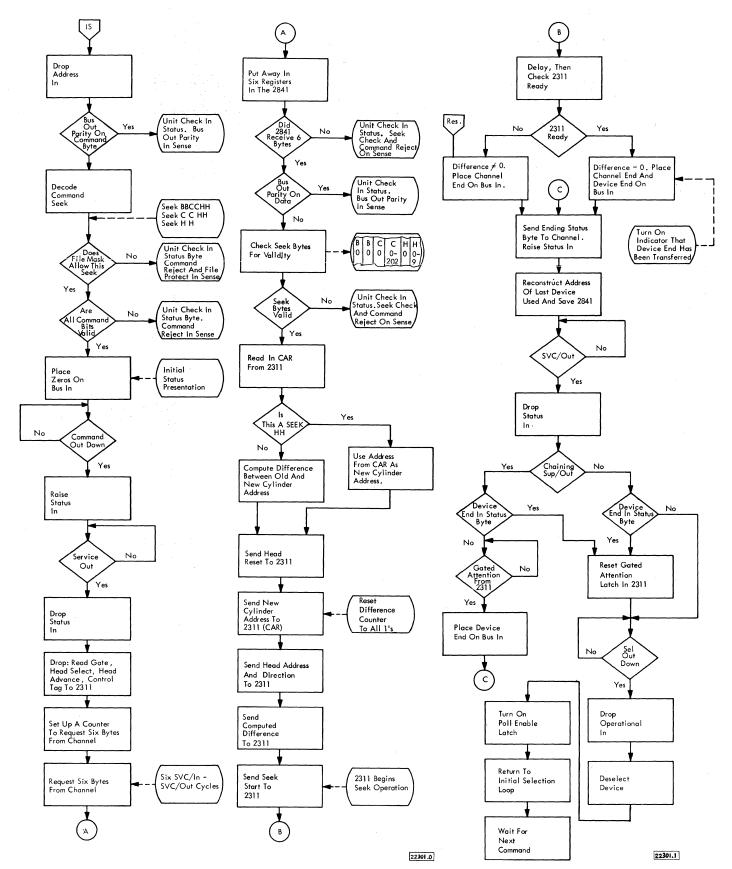

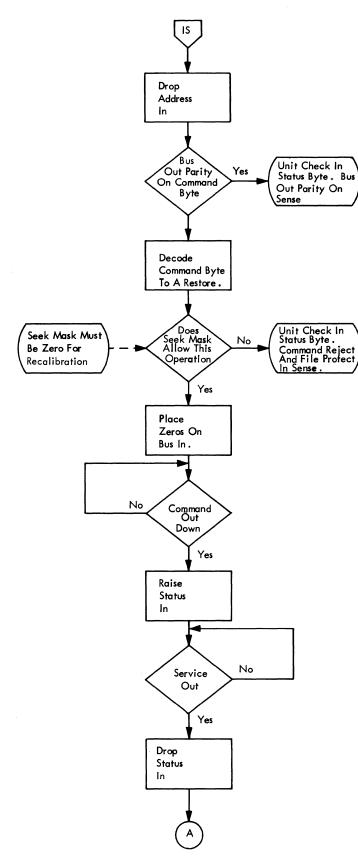

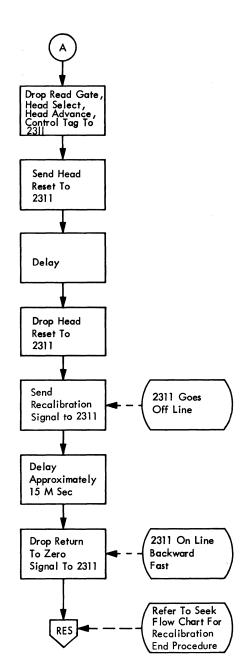

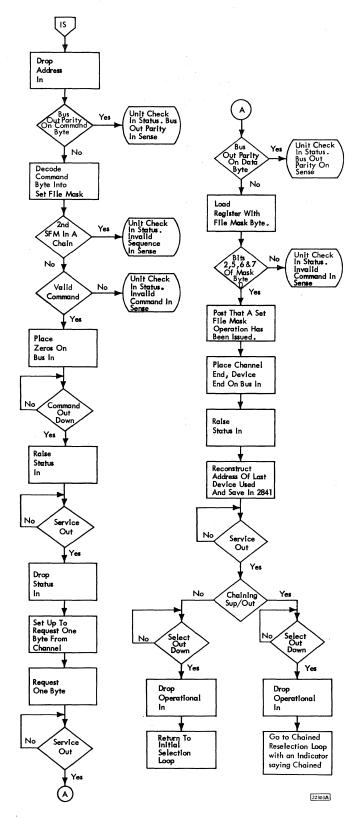

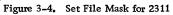

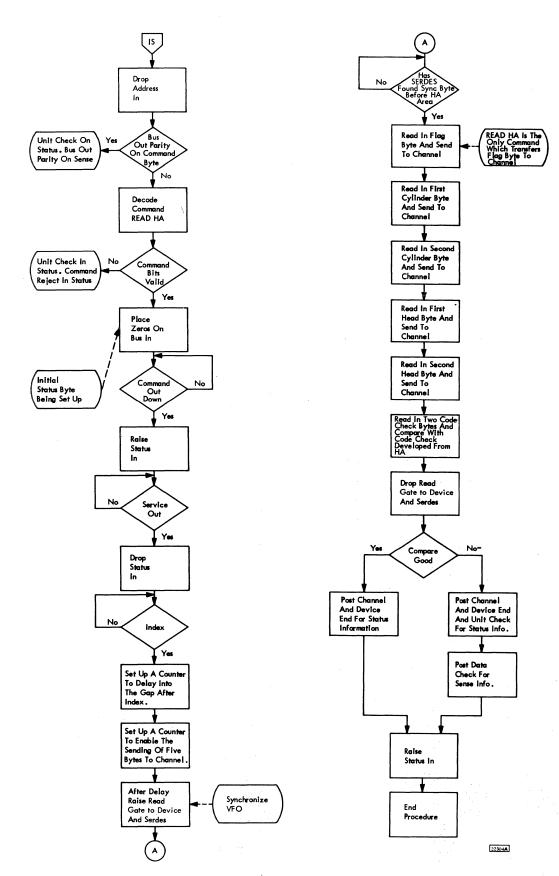

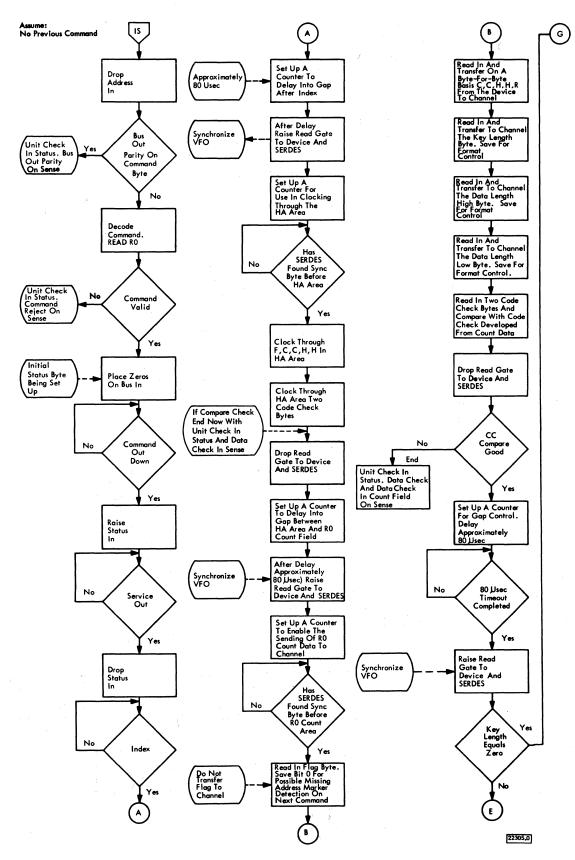

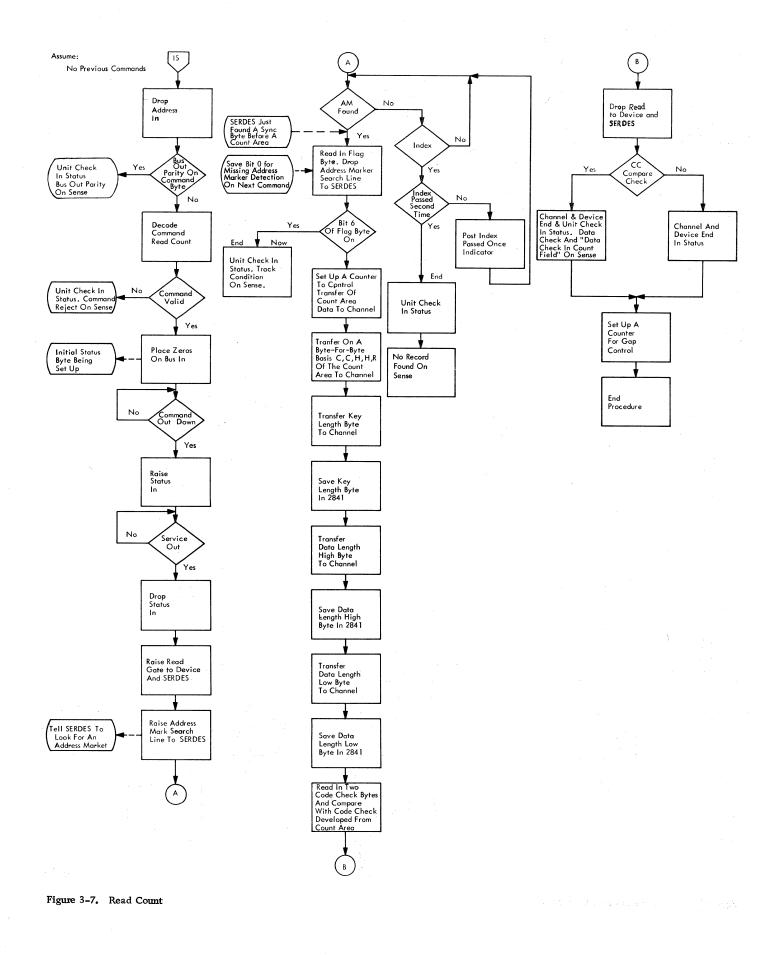

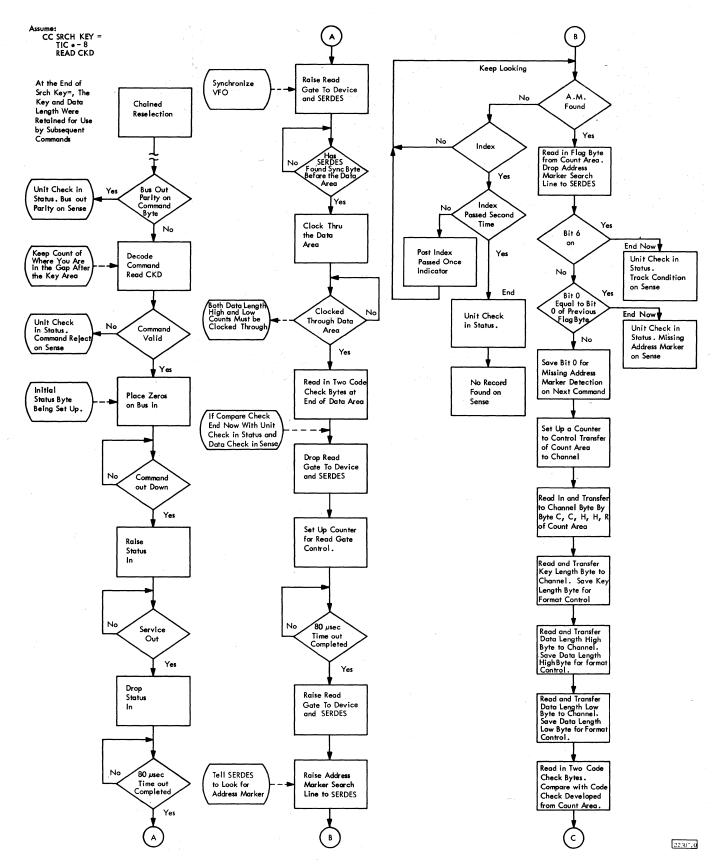

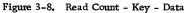

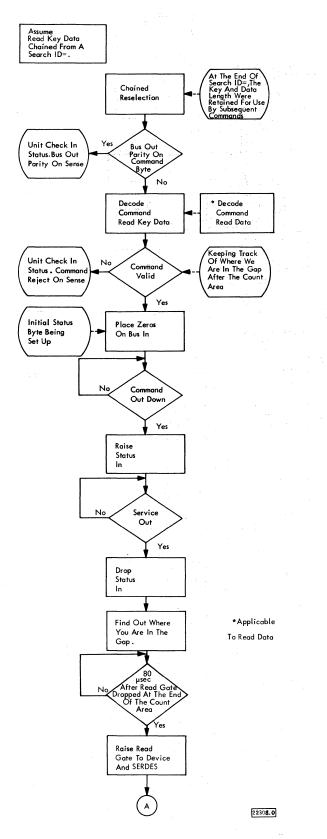

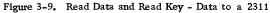

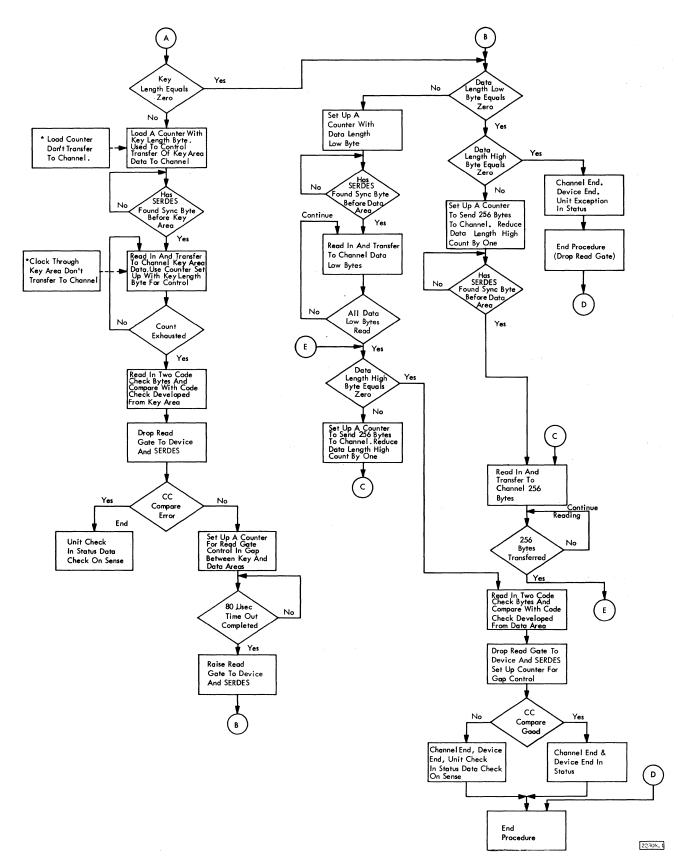

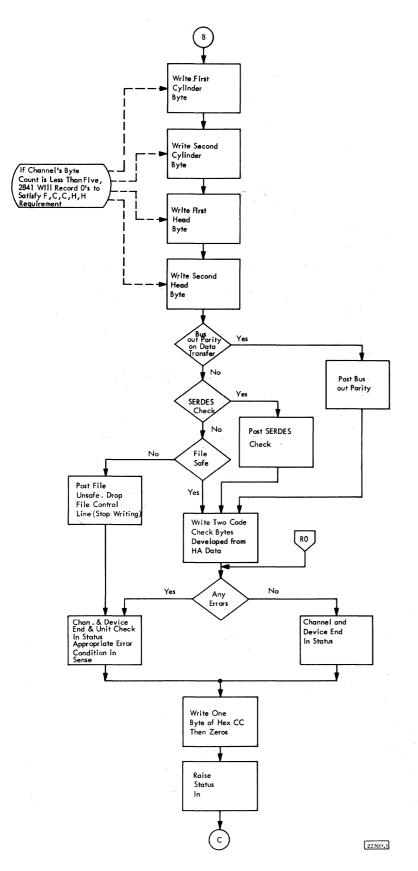

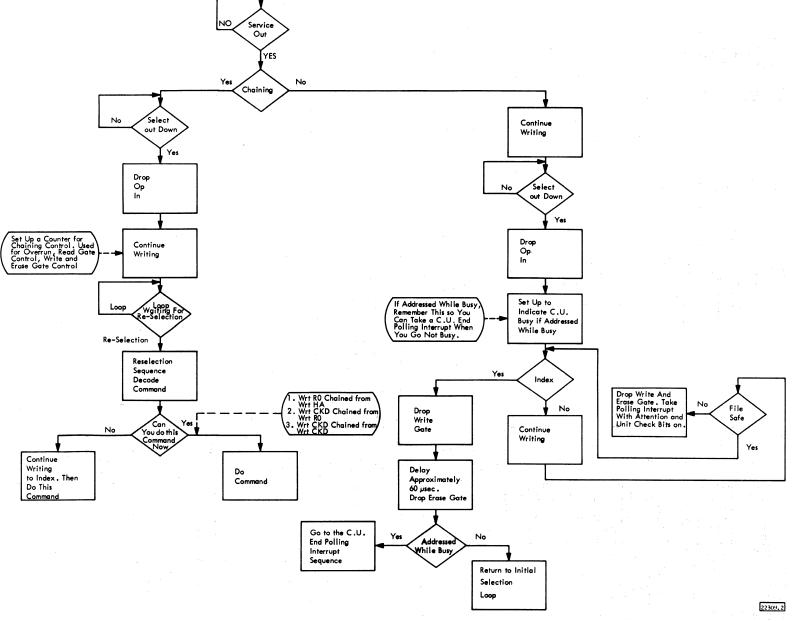

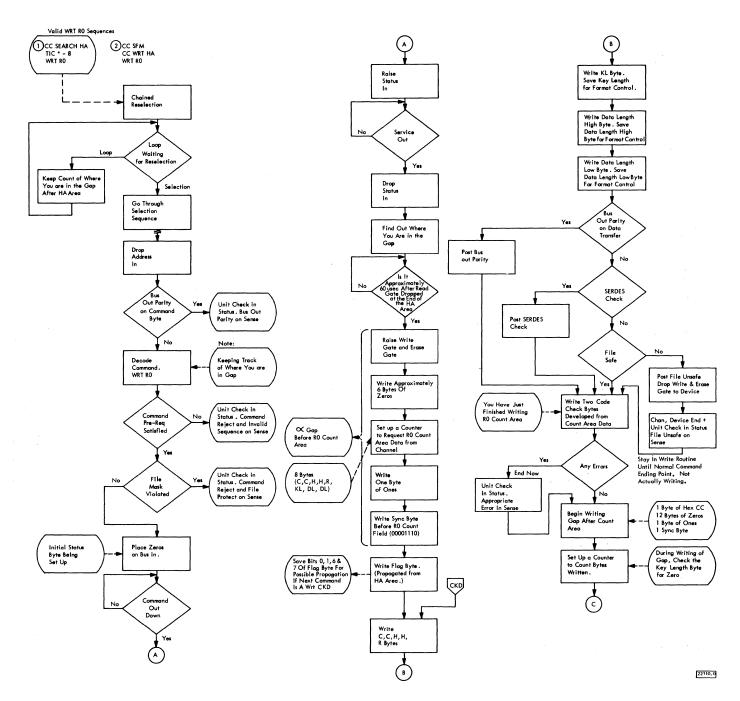

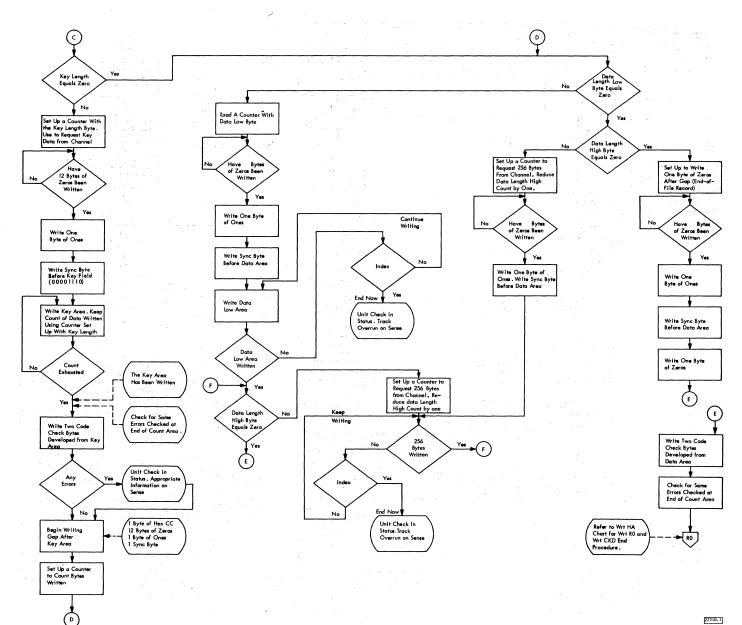

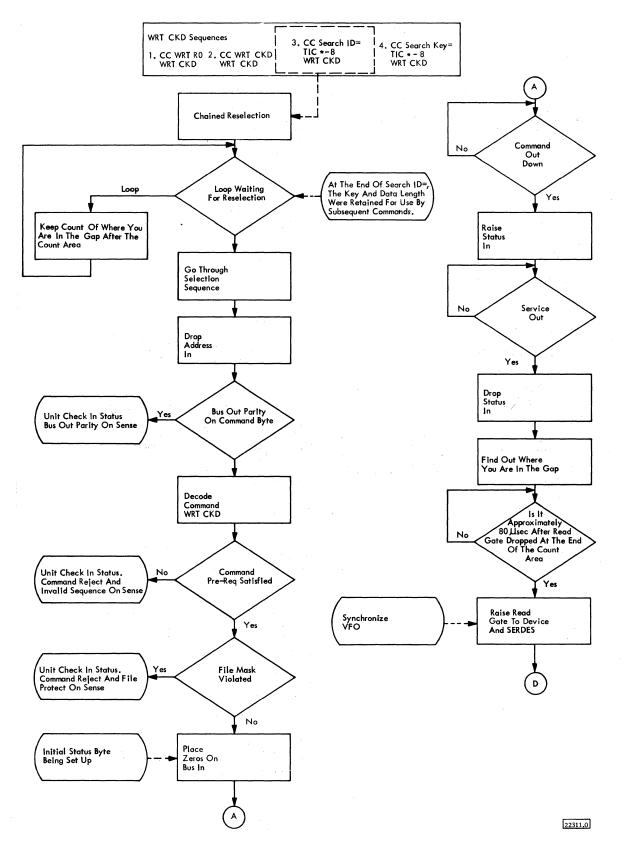

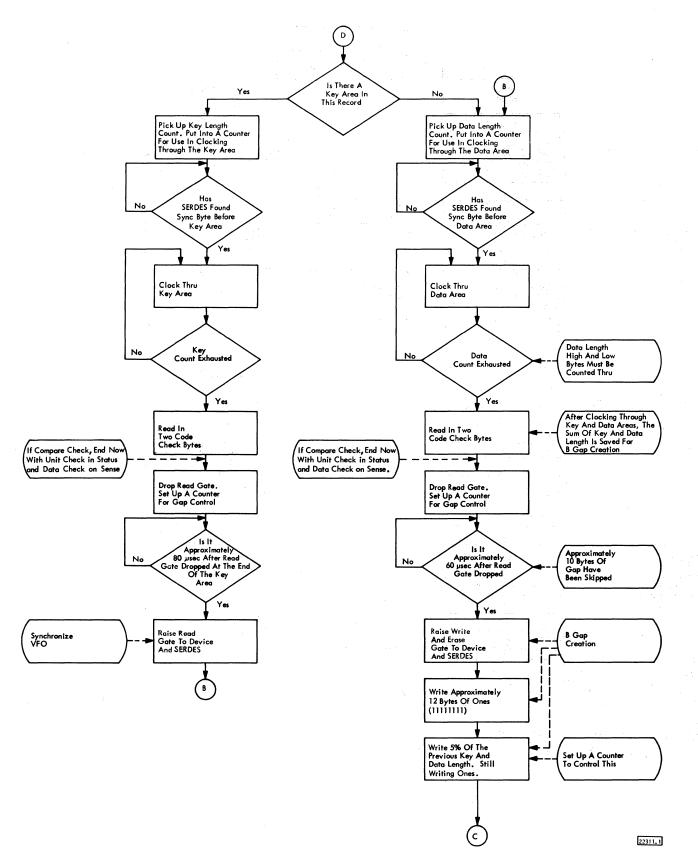

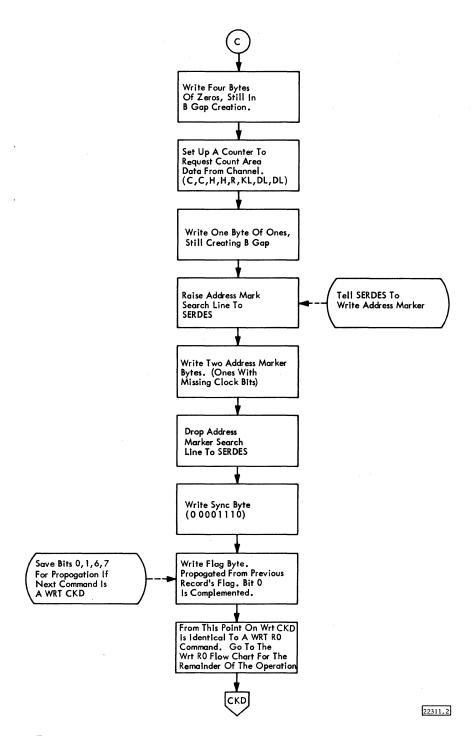

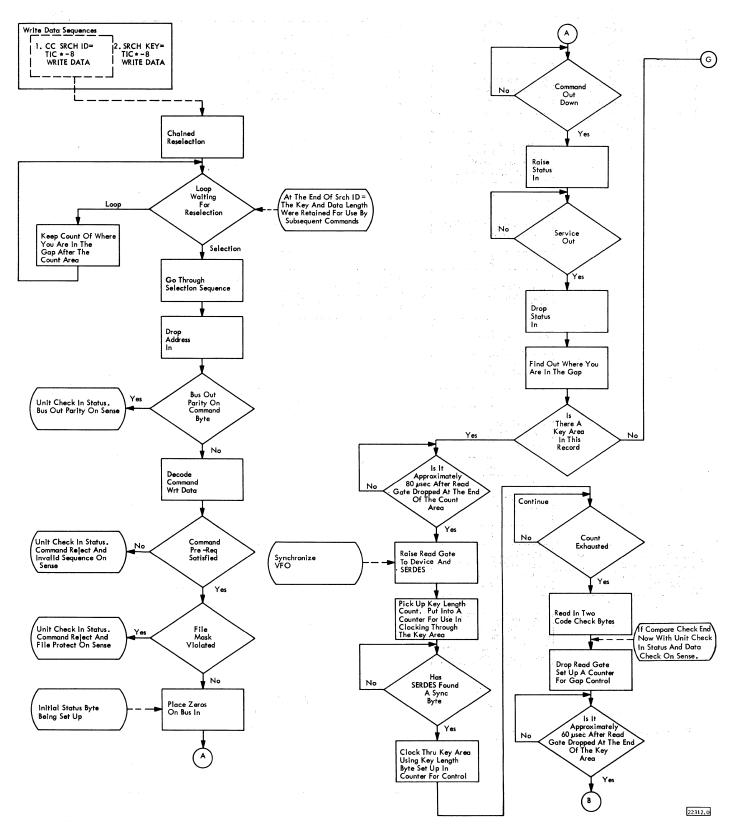

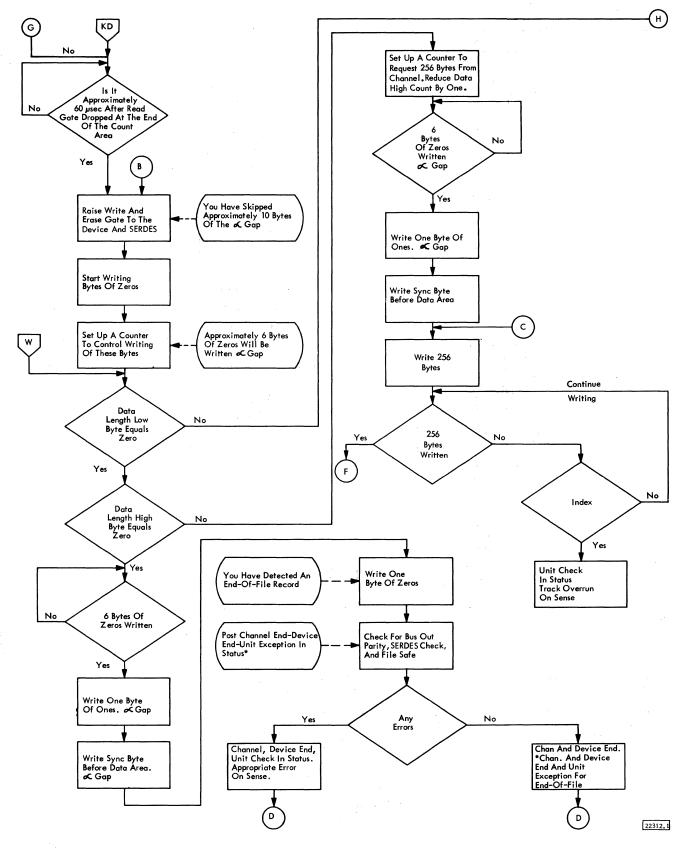

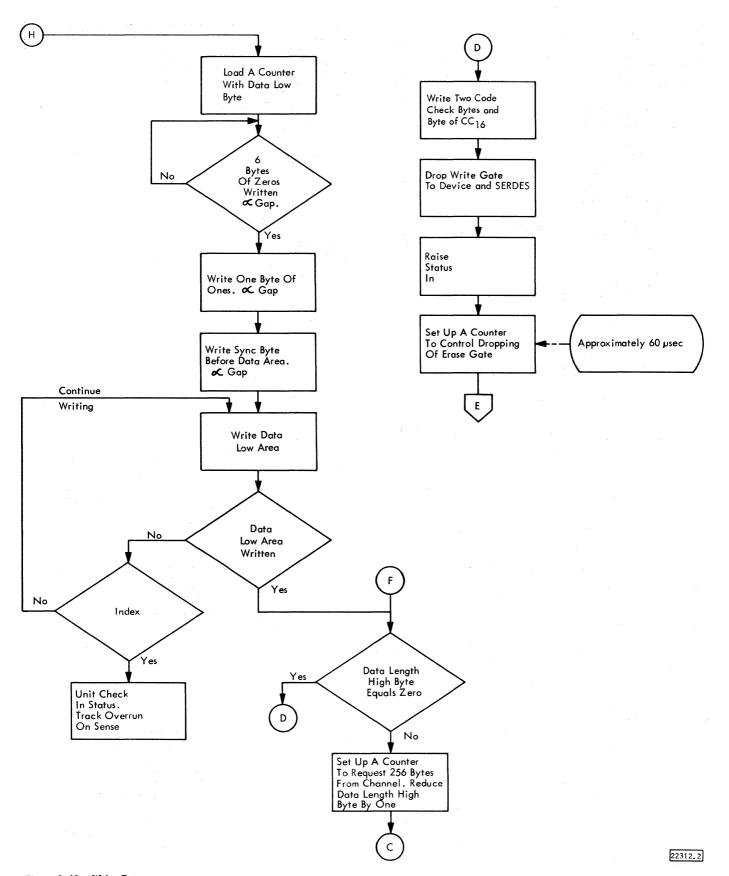

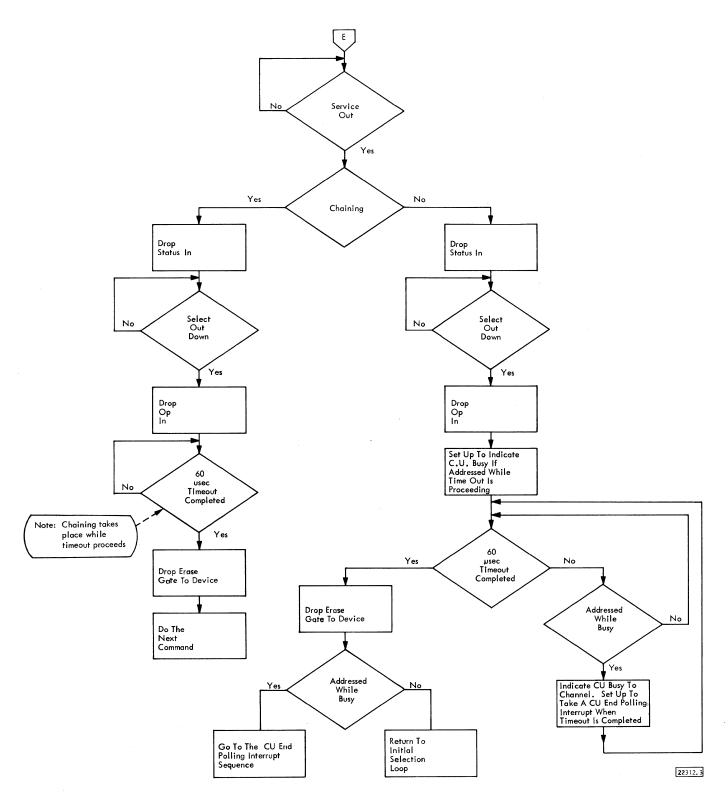

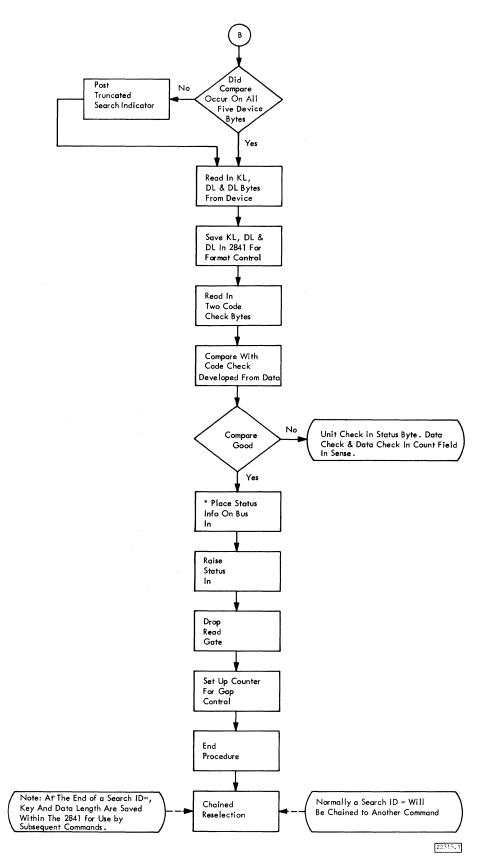

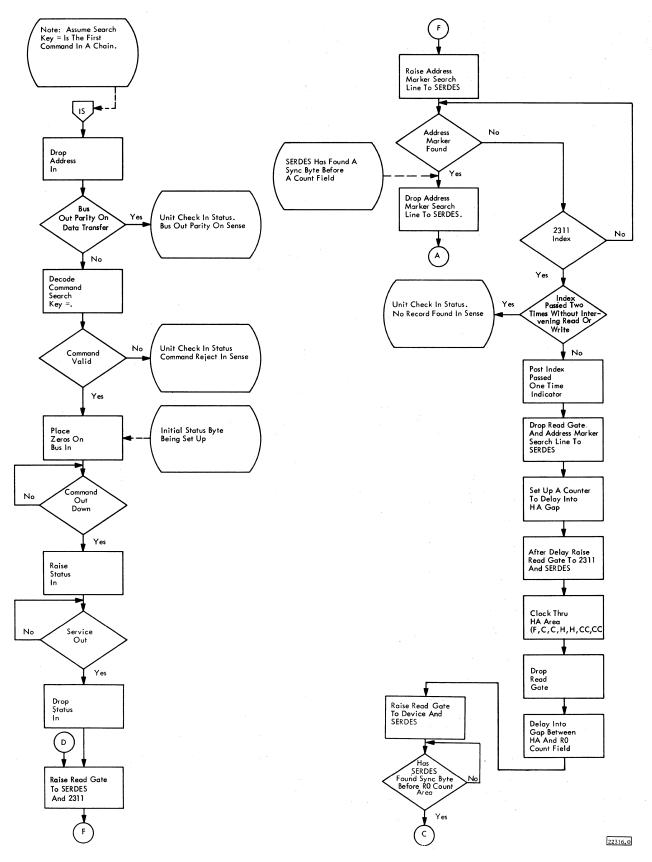

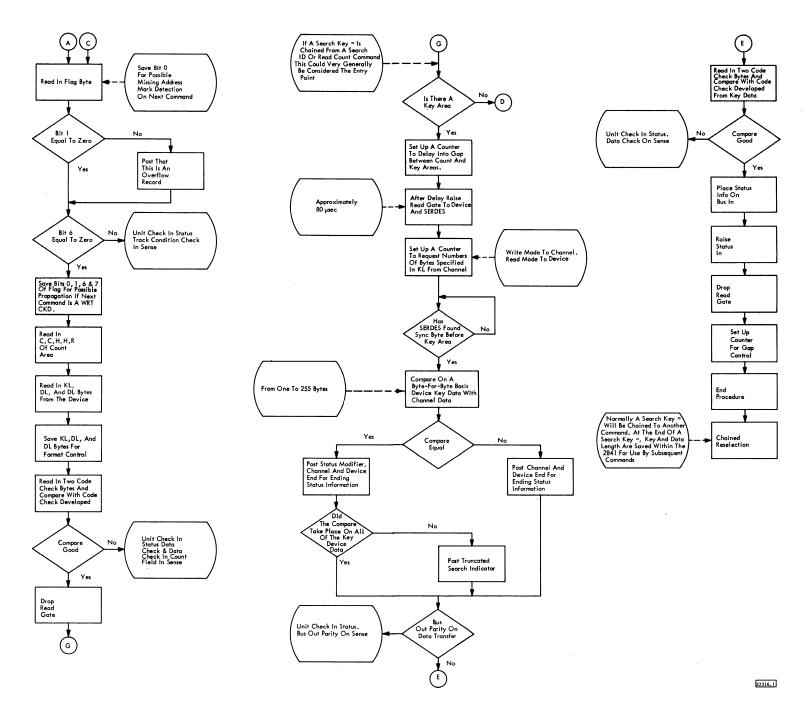

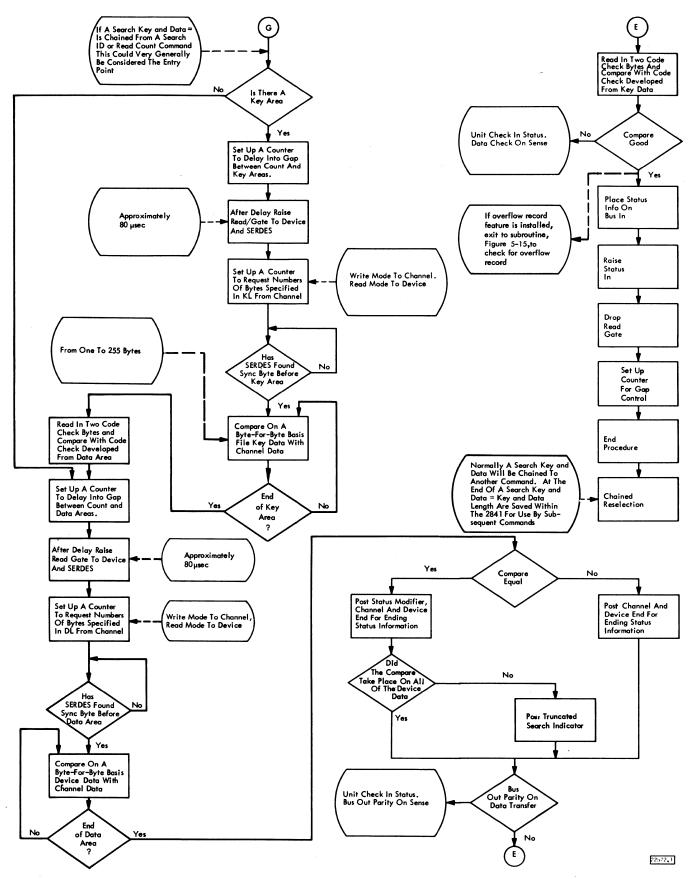

| 3.4    | COMMAND FLOW CHARTS                    | 3.9 |

|        |                                        |     |

| 3.5     | CONDENSED MICRO PROGRAM LOGIC        | 3.9  |

|---------|--------------------------------------|------|

|         | 3.5.1 General                        | 3.9  |

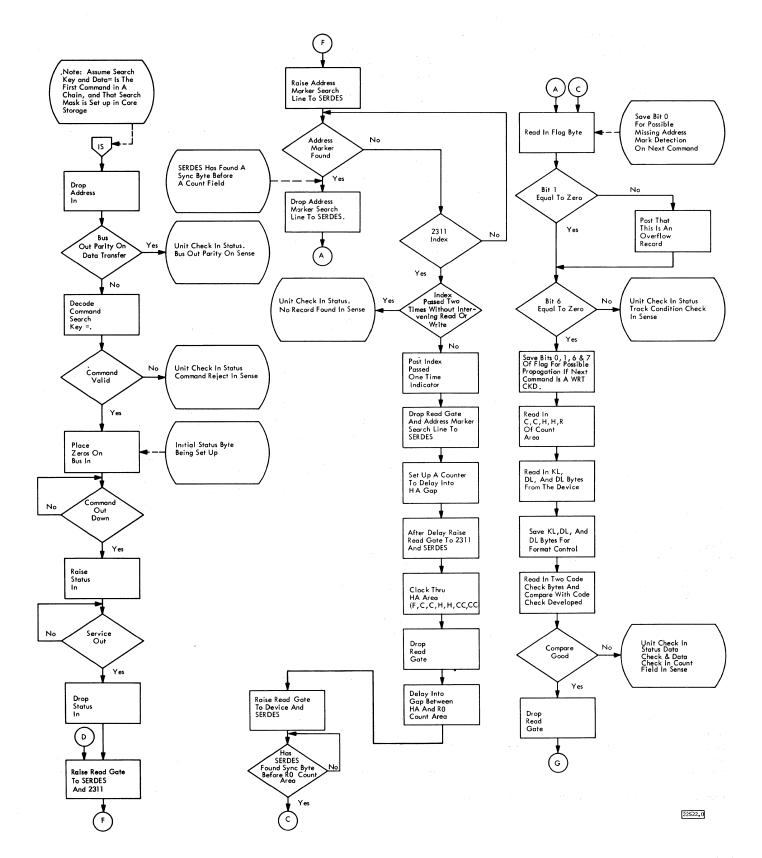

|         | 3.5.2 Initial Selection              | 3,10 |

|         | 3.5.3 Command Decode                 | 3,10 |

|         | 3.5.4 Initial Status Presentation    | 3.11 |

|         | 3.5.5 Load Counts                    | 3.11 |

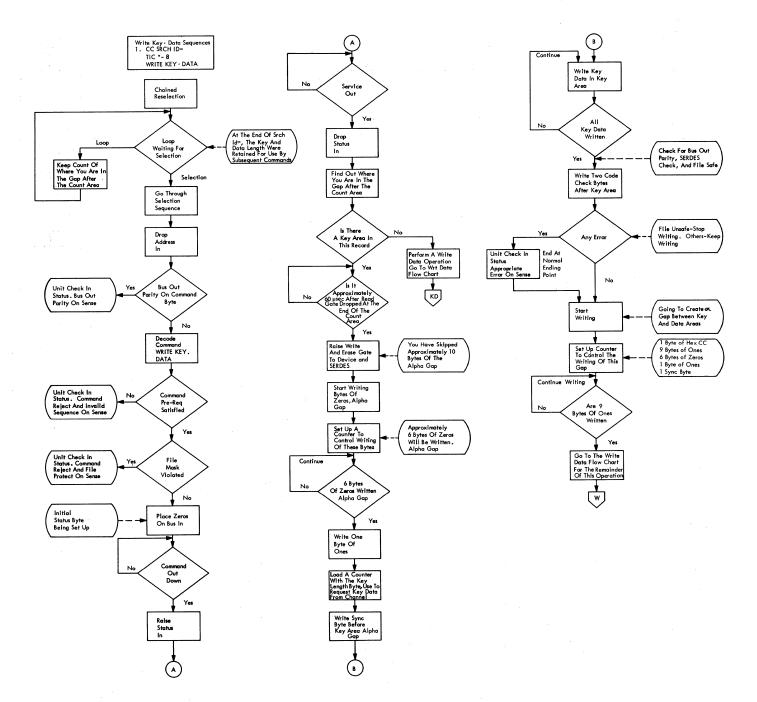

|         | 3.5.6 Write Operations               | 3.11 |

|         | 3.5.7 Control Operations             | 3.11 |

|         | 3.5.8 Sense Operations               | 3.11 |

|         | 3.5.9 Flag Byte Processing           | 3.11 |

|         | 3.5.10 Index Processing              | 3.12 |

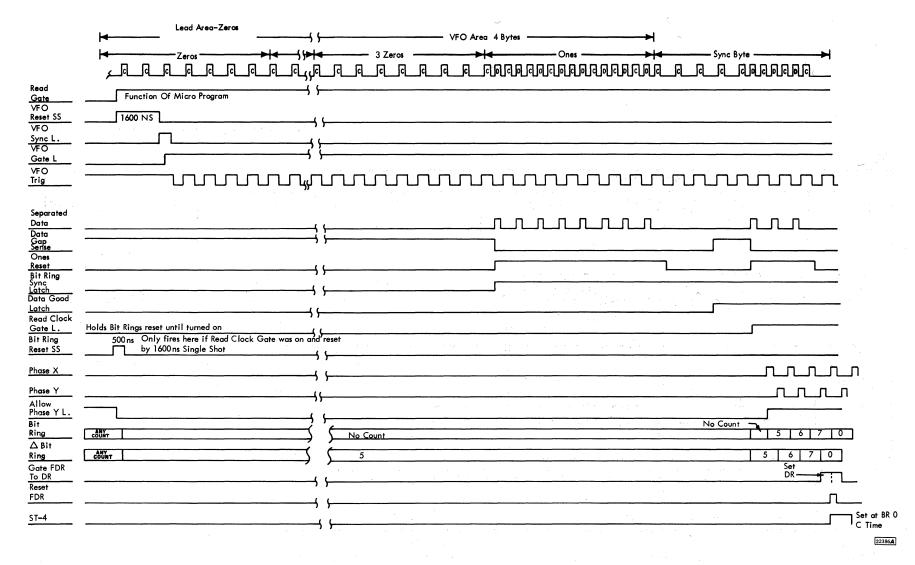

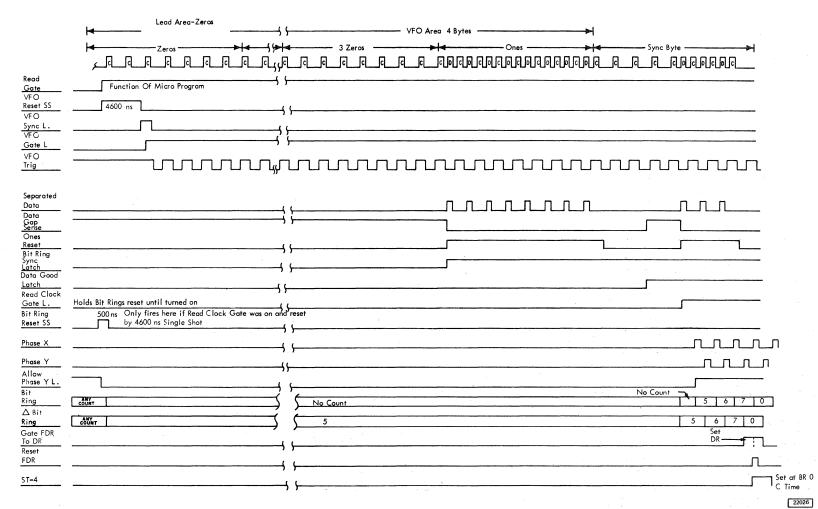

|         | 3.5.11 Read/Clocking                 | 3.12 |

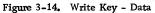

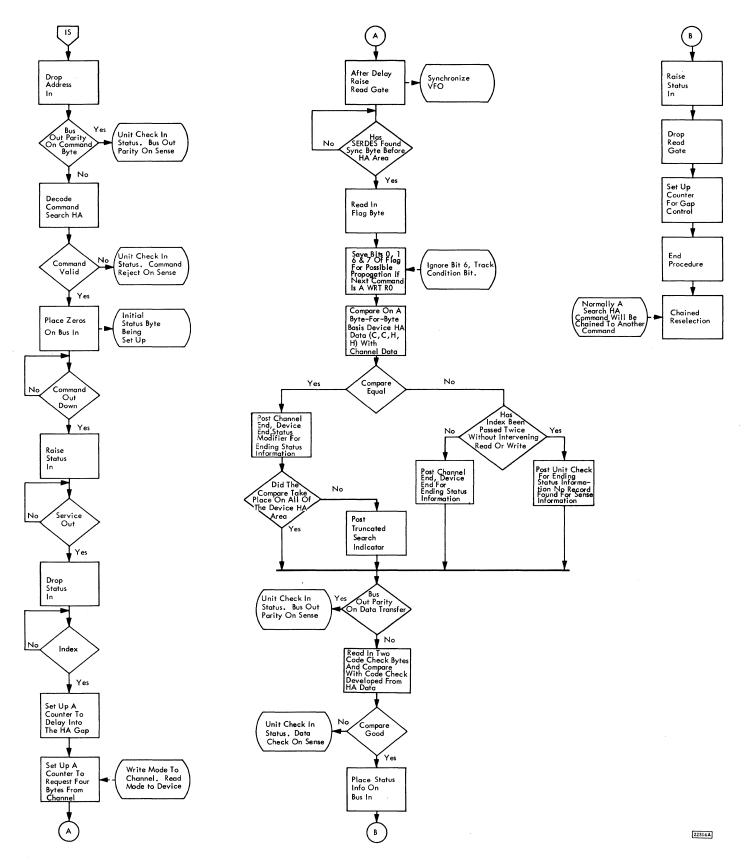

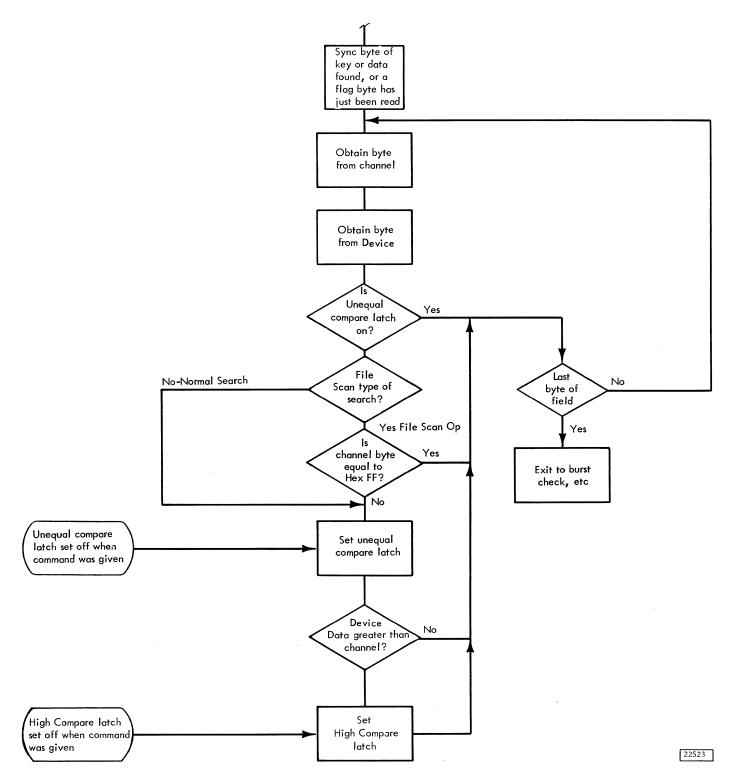

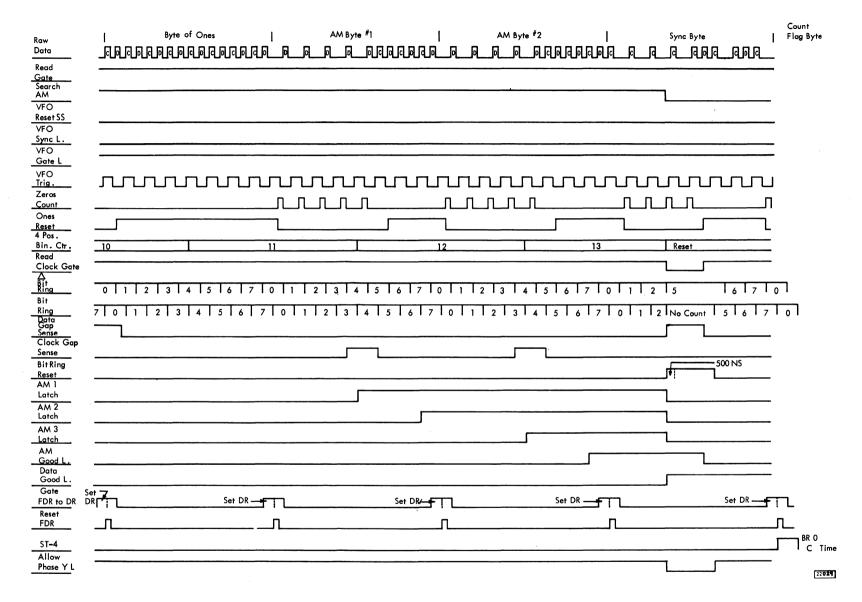

|         | 3.5.12 Search Operations             | 3.12 |

|         | 3.5.13 Scan Operations               | 3.12 |

|         | 3.5.14 Burst Byte and Exit Decisions | 3.12 |

|         | 3.5.15 Gap Spacing Operations        | 3.12 |

|         | 3.5.16 End Procedure                 | 3.13 |

|         | 3.5.17 Chained Reselection           | 3.13 |

|         | 3.5.18 Command Orientation Summary   | 3.13 |

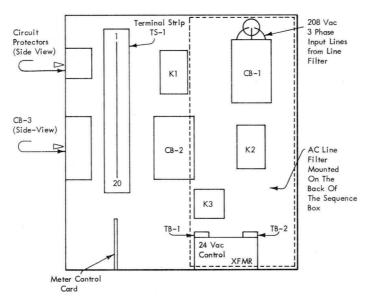

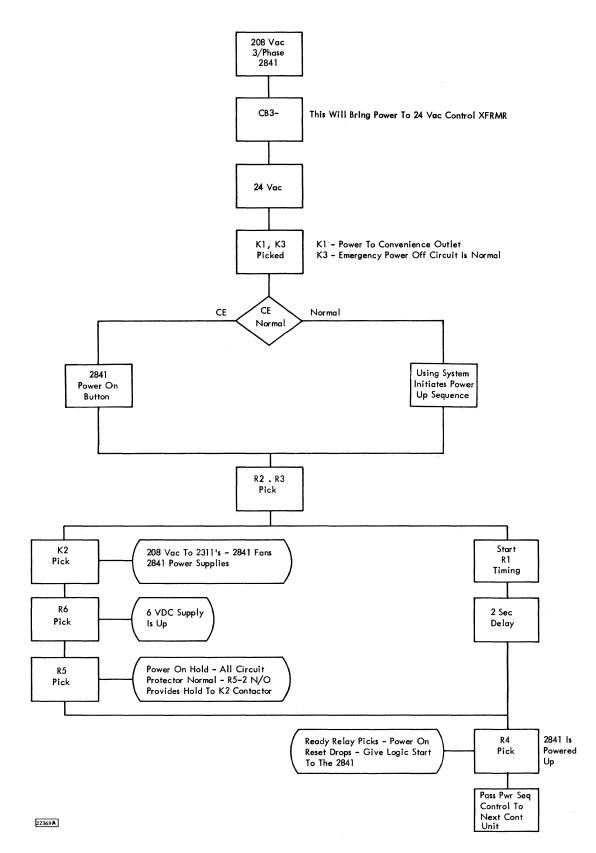

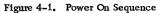

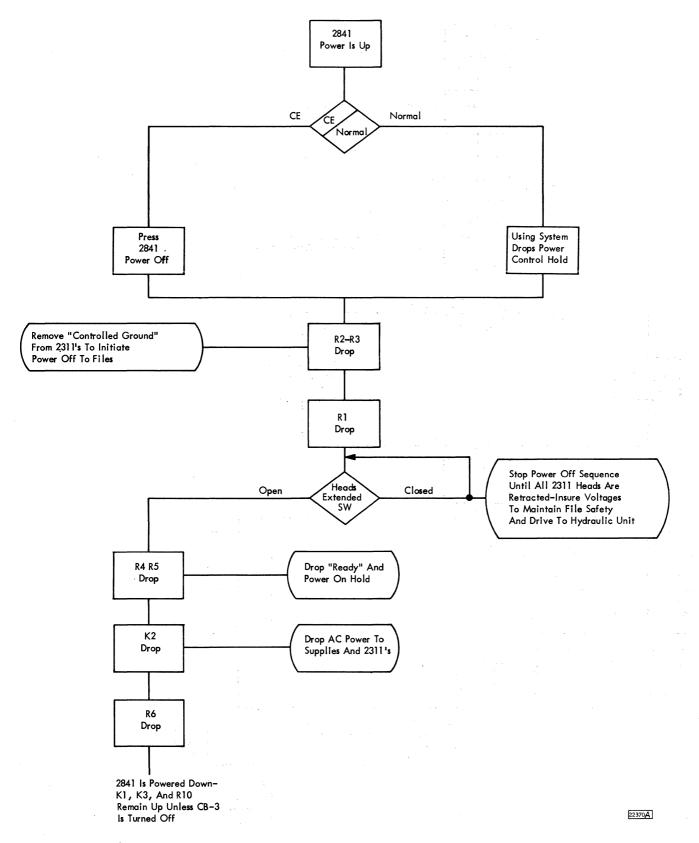

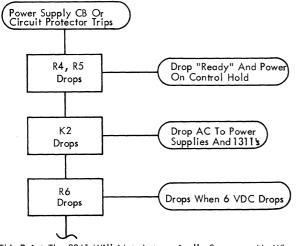

| CHAPTEI | R 4 POWER SUPPLIES AND SEQUENCING    | 4.1  |

|         | GENERAL POWER SUPPLY DESCRIPTION     | 4.1  |

|         | 4.1.1 Power Supply Components        | 4.1  |

|         | 4.1.2 Thermal Considerations         | 4.1  |

|         | 4.1.3 Marginal Checking              | 4.1  |

|         | 4.1.4 Power Distribution             | 4.1  |

|         | 4.1.5 Power Interlocks               | 4.2  |

|         |                                      |      |

-

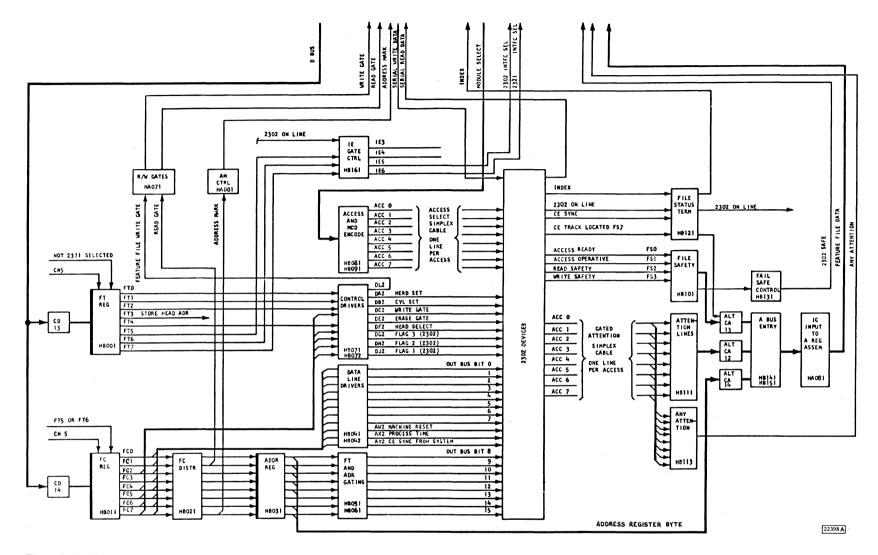

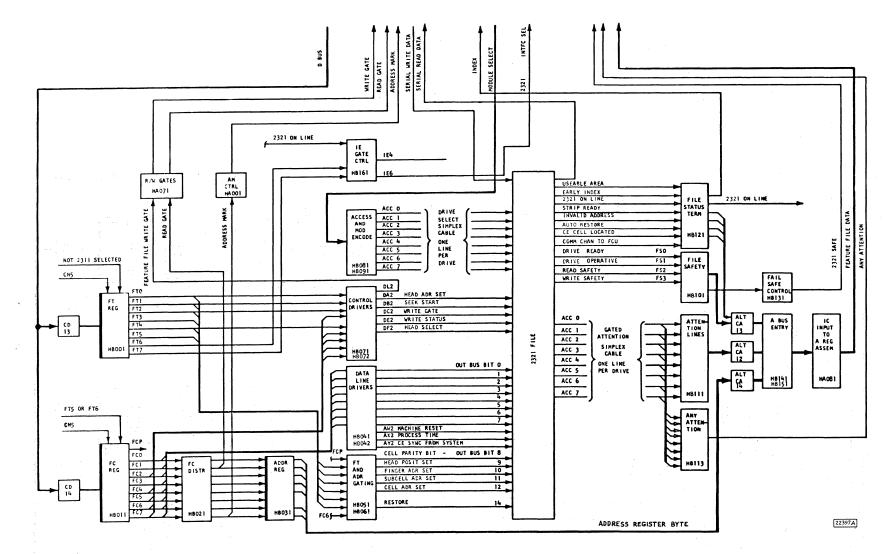

| CHAPTE  | R 5 FE  | ATURES                                 | 5.1          |

|---------|---------|----------------------------------------|--------------|

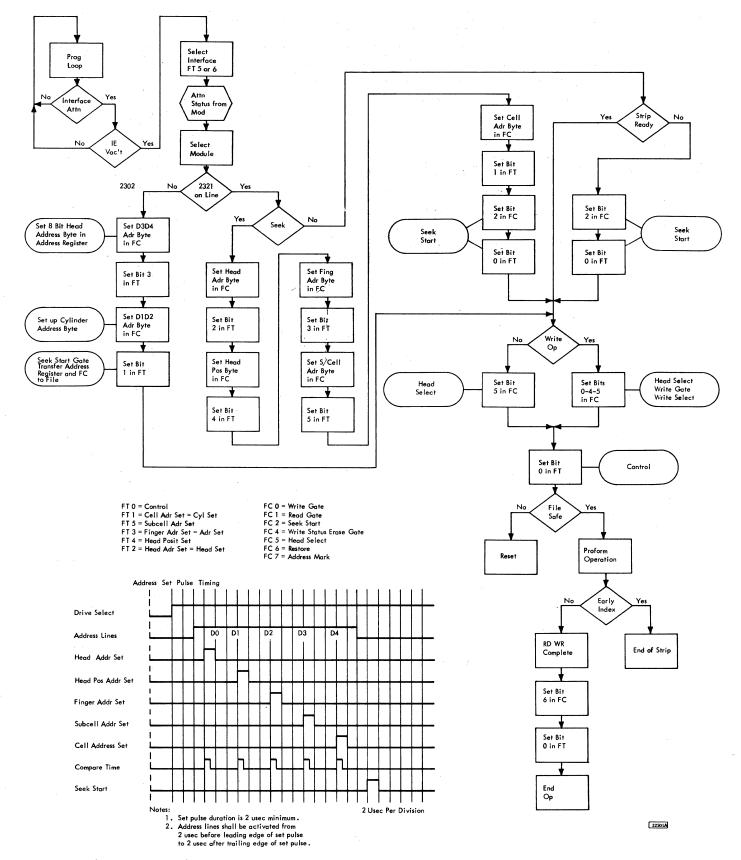

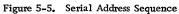

|         |         | MODELS 3 AND 4, 2321,                  |              |

| -       |         | CHMENT                                 | 5.1          |

|         | 5.1.1   | Device Attachment Limits               | 5,2          |

|         | 5.1.2   | 2302 Operation                         | 5.2          |

|         | 5.1.3   | 2321 Operation                         | 5.2          |

| 5.2     | ADDI    | TIONAL STORAGE FEATURE                 | 5.2          |

| 5.3     | FILE S  | CAN FEATURE                            | 5.3          |

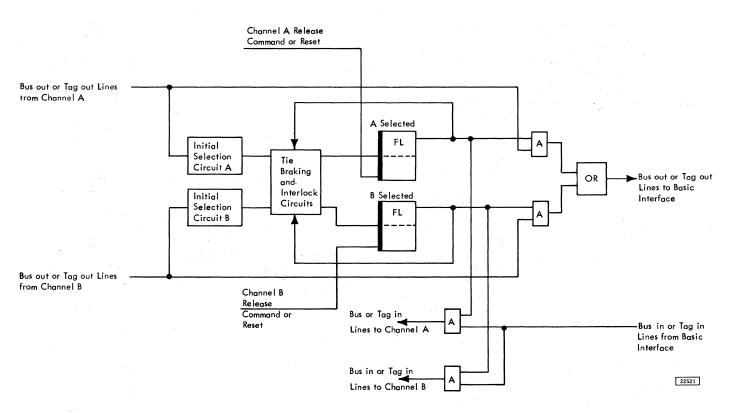

| 5.4     | TWO-    | CHANNEL SWITCH FEATURE                 | 5.3          |

|         | 5.4.1   | Device Reserve Command (1011 0100)     | 5.4          |

|         | 5.4.2   | Device Release Command (1001 0100)     | 5.4          |

|         | 5.4.3   | Device Status                          | 5.4          |

|         | 5.4.4   | Miscellaneous                          | 5, 5         |

|         | 5.4.5   | Two Channel Switch Circuit Description | 5.6          |

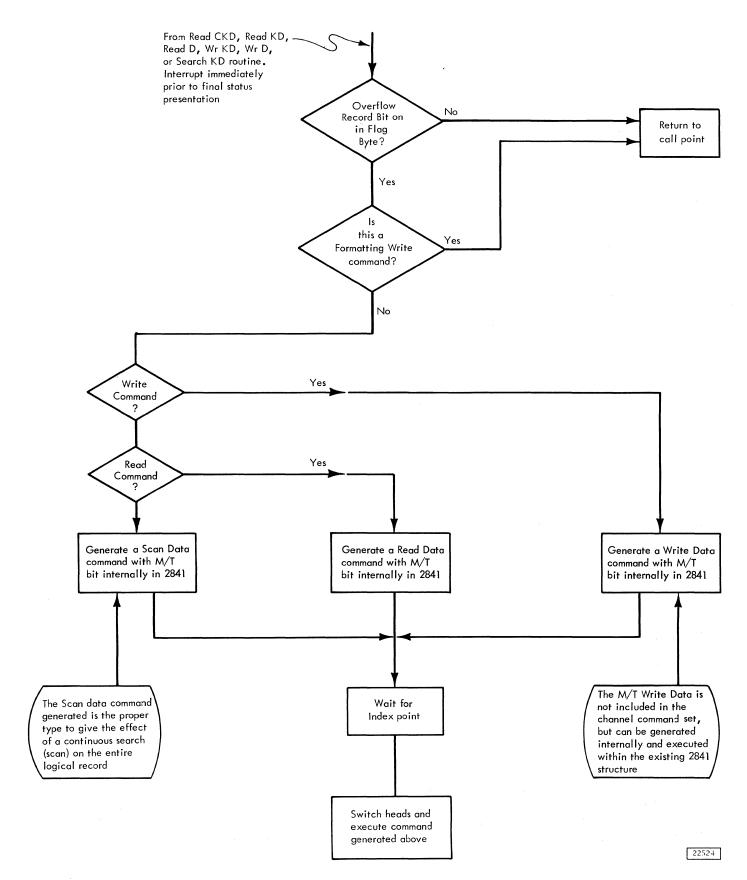

| 5.5     | RECO    | RD OVERFLOW FEATURE                    | 5.6          |

|         | 5.5.1   | Formatting Overflow Records            | 5.6          |

|         | 5.5.2   | Processing Overflow Records            | 5.6          |

|         | 5. 5. 3 | Unusual Conditions                     | 5.7          |

| CHAPTEI | R6 AP   | PENDIX                                 | 6 <b>.</b> 1 |

| 6.1     | CAS I   |                                        | 6, 1         |

|         | 6.1.1   | TROS Bit Assignment Chart              | 6.1          |

|         | 6.1.2   | Micro Block Symbology                  | 6.3          |

|         | 6.1.3   | Sample Usage of Micro Block            | 6,4          |

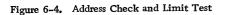

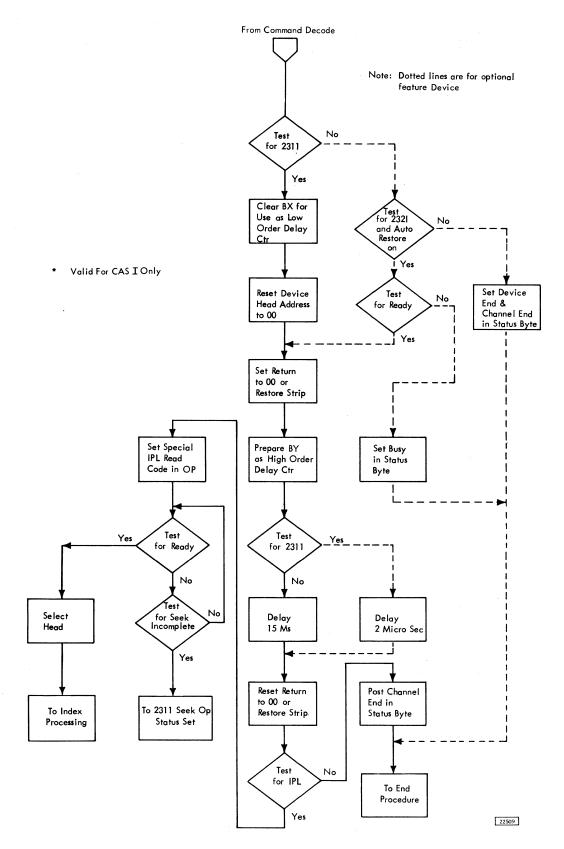

|         |         | Feature Device Command Flow Charts     | 6.4          |

| INDEX . |         |                                        | I. 1         |

#### CHAPTER 1 INTRODUCTION

## 1.1 GENERAL INFORMATION

- Provides a method of attaching serial direct access storage units to System/360.

- Up to eight 2841's may be attached to a channel.

- Basic 2841 can control up to eight 2311 Disk Storage Units.

- Types of units 2311 (standard) 2302, and 2321 (optional).

- Any combination of units can be connected to one 2841.

- 2841 uses Solid Logic Technology.

- 2841 uses Read Only Storage for control.

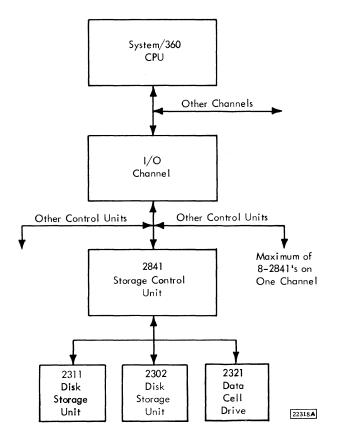

The IBM 2841 Storage Control Unit (SCU) is designed to attach serial direct access storage devices to IBM System/360, Model 30 and above. The SCU provides all the buffering and control necessary to attach these devices to the I/O channels through the standard I/O interface (Figure 1-1).

The 2841 provides the ability to interpret and execute commands, translate data as it moves between the serial-by-bit direct access device and the parallel-by-byte System/360 interface, check the integrity of the information that is transmitted to and from the device, and furnish status information to the using system.

The design of the 2841 is such that circuits common to all direct access devices are housed in one section of the unit while circuits associated with a specific device are housed in a separate area.

The available features for the 2841 Storage Control are:

- 1. 2311 Attachment (standard part of 2841).

- 2. 2302 Attachment (Optional).

- 3. 2321 Attachment (Optional).

- 4. Additional Storage 2302 (Optional).

- 5. Two-Channel Switch (Optional).

- 6. File Scan (Optional).

- 7. Record overflow (Optional)

2302 Attachment: This feature provides the circuitry required to attach a 2302 Disk Storage to a system via the 2841. This feature is described in Chapter 5.

2321 Attachment: The 2321 Attachment Feature provides the circuitry required to attach a 2321 Data Cell Drive to a system via the 2841. This feature is described in Chapter 5.

<u>Two-Channel Switch</u>: The Two-Channel Switch Feature provides the switching circuitry required to attach the 2841 Storage Control to a second channel. This feature is described in Chapter 5.

Additional Storage: The Additional Storage Feature provides circuitry to attach up to 16 access mechanisms to a 2841. The additional eight access mechanisms must be 2302 accesses. This feature is described in Chapter 5.

<u>File Scan:</u> The File Scan Feature provides an automatic rapid search for a specific identifier condition. This feature is described in Chapter 5.

<u>Record Overflow</u>: The Record Overflow Feature allows a record to overflow from one track to another. This feature is described in Chapter 5.

As the 2311 Disk Storage is the standard unit, this manual is primarily written for 2311 operations. The other units and additional features are described in Chapter 5.

The 2841 is packaged in Solid Logic Technology and utilizes Read Only Storage (ROS) to control its operations.

The use of disk storage provides IBM System/ 360 with the ability to either sequentially or randomly record and retrieve externally stored data. It permits the immediate access to specific areas of information without the need to sequentially examine all data recorded in the same file. The fast speed of access to data storage locations enables the user to maintain up-to-the minute files and to make frequent direct reference for the retrieval of stored data, regardless of the time of record insertion or the physical location of the data. The extensive data storage capacity, swift access to recorded data, high data transmission rates, and broad flexibility of file maintenance and organization provided by disk storage devices introduce new and advanced data processing methods and faster simplification of procedures.

#### 1.2 PHYSICAL DESCRIPTION

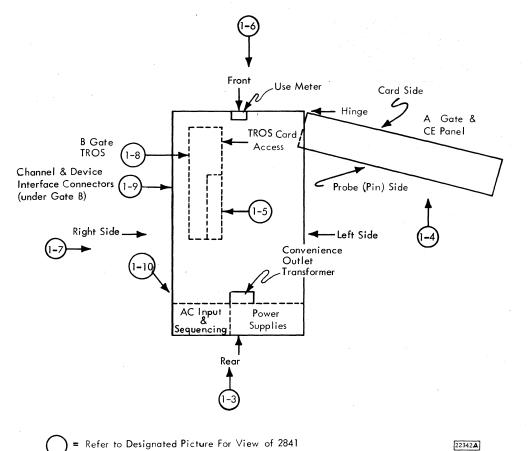

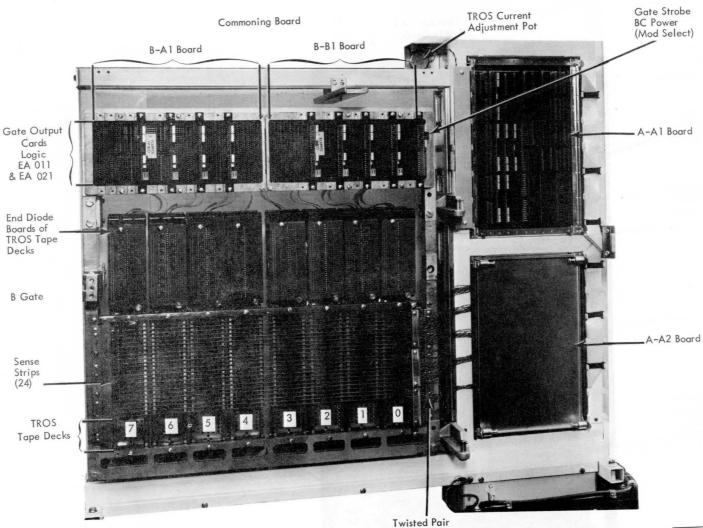

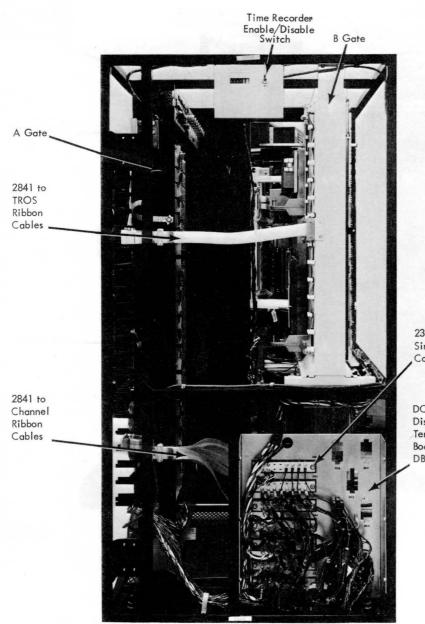

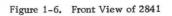

The physical characteristics of the 2841 are: (Figures 1-2 through 1-10.)

### 1.2.1 Dimensions

| Height | 60" (from floor) |

|--------|------------------|

| Depth  | 30"              |

| Width  | 44"              |

| Weight | 800 lbs.         |

Two swinging covers in front and two swinging covers in back.

#### 1.2.2 Power Requirements

| Voltage:          | 3-phase 208 vac ±10%, 30 amp,     |

|-------------------|-----------------------------------|

|                   | 60-cycle, four wire cable (fourth |

|                   | wire is equipment ground)         |

| Plug:             | Russell & Stoll FS 3760           |

| Mating Connector: | FS 3934                           |

| KVA:              | 1.9                               |

NOTE: The 2841 can be adapted to operate on the following 50-cycle, 3 phase voltages in accordance with IBM Corporate Standard 3-2-5103-0:

- 1. 195 volts  $\pm 10\%$

- 2. 220/380 volts  $\pm 10\%$

- 3. 235/408 volts  $\pm 10\%$

1.2.3 Cable Entry

Power and signal cables enter the unit from underneath. A raised floor is desirable but not required.

1.2.4. Operator's Position

The control unit has no operator's position other than the Meter Enable switch on the front of the 2841 (Figure 1-2).

#### 1.2.5 Environmental Conditions

|                   | Onemating | Non-      |

|-------------------|-----------|-----------|

|                   | Operating | Operating |

| Temperature       | 60-90°F   | 50-110°F  |

| Relative Humidity | 8-80%     | 8-80%     |

| Maximum Wet Bulb  | 78°       | 80°       |

## 1.2.6 Power Control

The control unit may be placed in a local or remote mode by means of a switch in the control unit. When in the remote mode, power sequencing is controlled by the processor. When in the local mode, the power switches in the control unit must be operated. In this mode the processor cannot control sequencing. The switch is normally in the remote position. When power is present in the control unit, it is available to all devices attached to the unit.

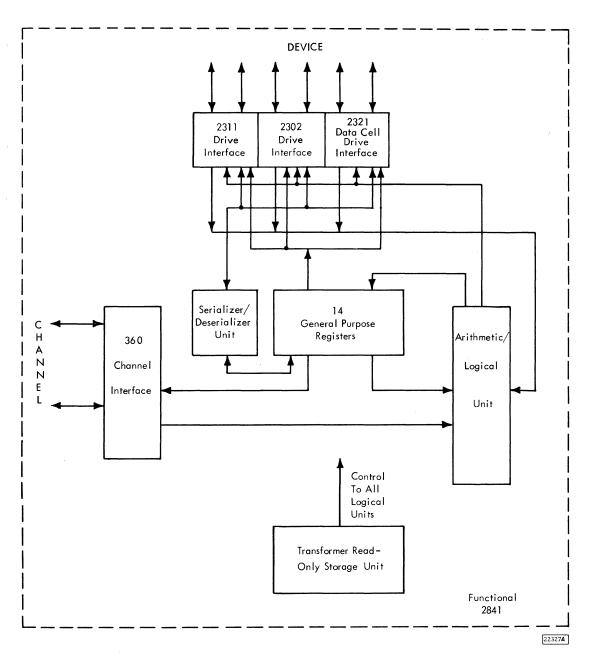

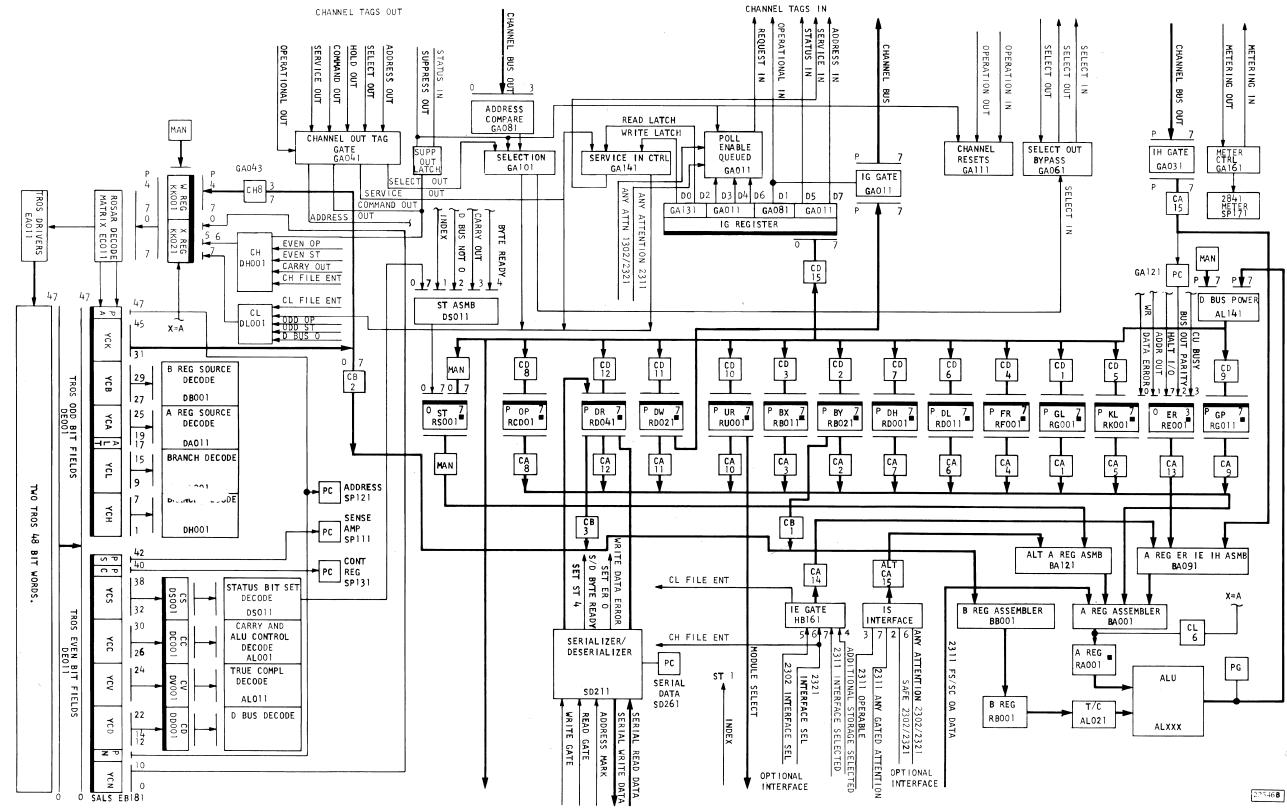

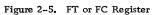

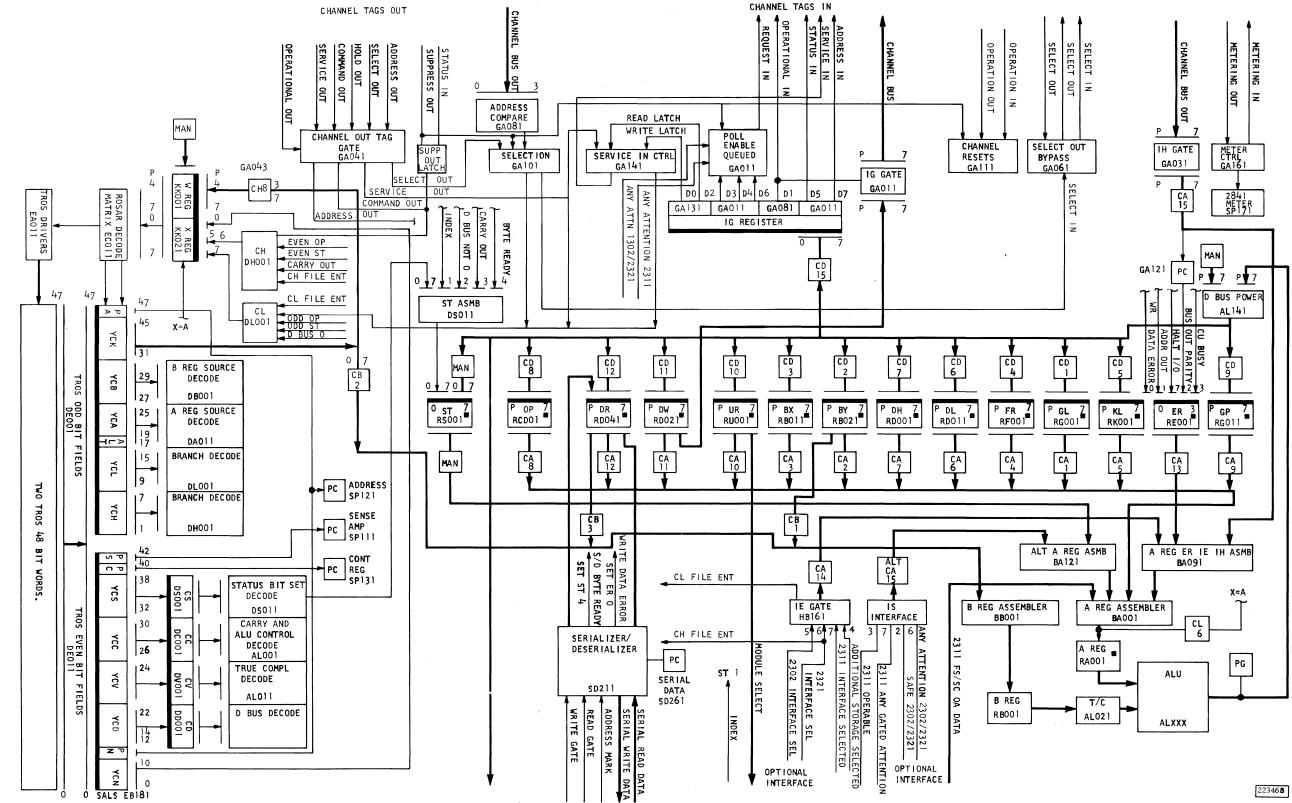

## 1.3 FUNCTIONAL DESCRIPTION (Figure 1-11)

- The 2841 consists of six logical sections:

- 1. System/360 Channel Interface

- 2. Arithmetic/Logical Unit

- 3. Serializer/Deserializer Unit

- 4. Fourteen General Purpose Registers

- 5. Transformer Read-Only Storage Unit

- 6. Device Interfaces

- a. 2311 Disk

- b. 2302 Disk

- c. 2321 Data Cell Drive

#### 1.3.1 System/360 Channel Interface

The System/360 Channel interface provides a method of attaching I/O control units to System/360 channels.

#### 1.3.2 Arithmetic/Logical Unit (ALU)

ALU can add, subtract, OR, AND, exclusive OR, and generate correct parity.

#### 1.3.3 Serializer/Deserializer Unit (SERDES)

SERDES is used to convert parallel-by-byte data to serial-by-bit data when writing, and serial-by-bit data to parallel-by-byte data when reading.

Figure 1-1. 2841 Storage Control Unit Configuration

.

.

22342

Figure 1-2. Top View of 2841

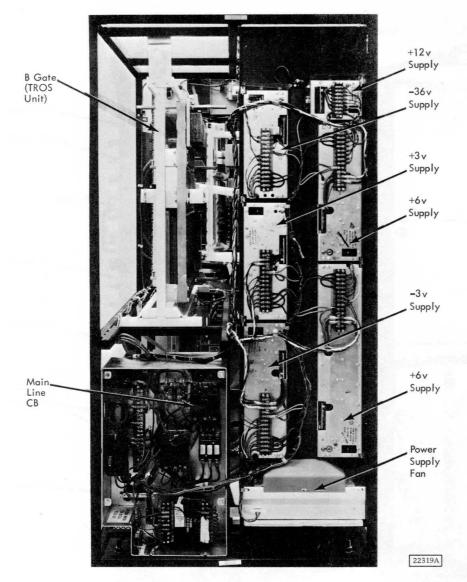

Figure 1-3. Rear View of 2841

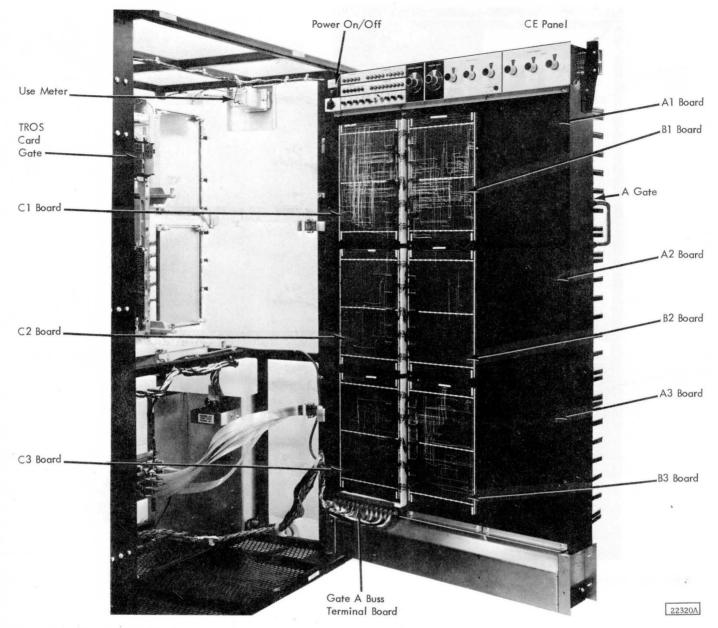

Figure 1-4. Gate A and CE Panel

Twisted Pair Inputs to the Sense Amplifiers

22321A

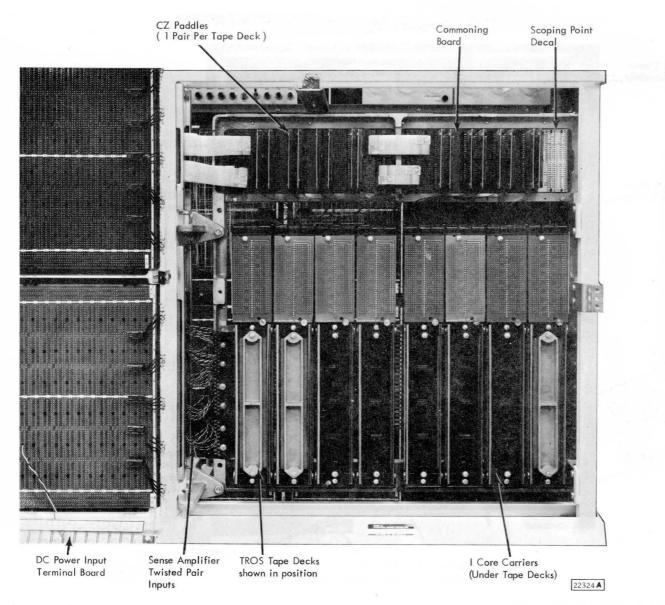

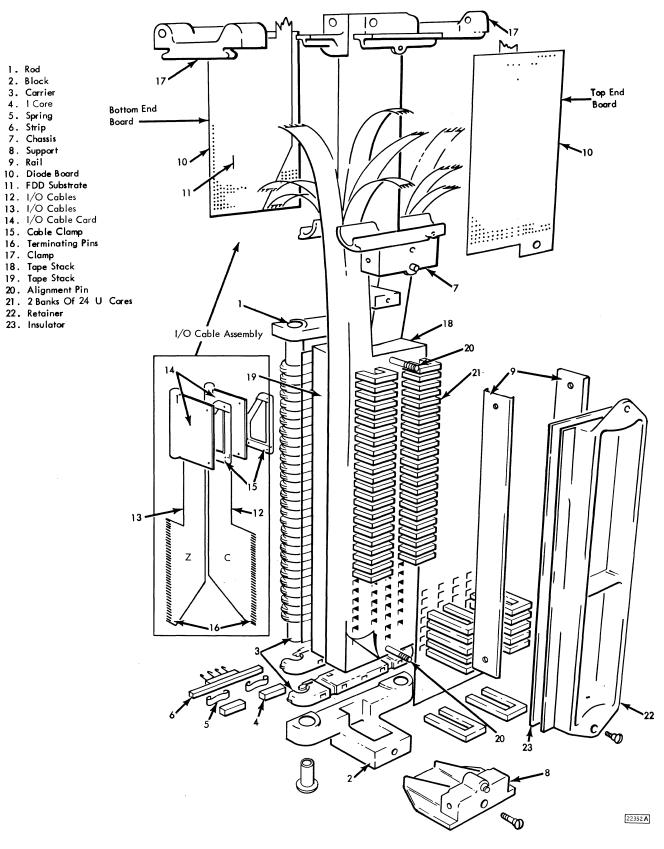

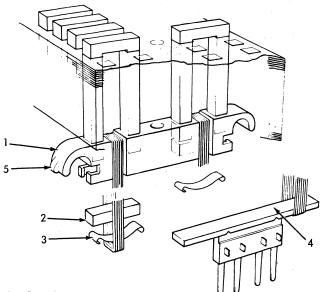

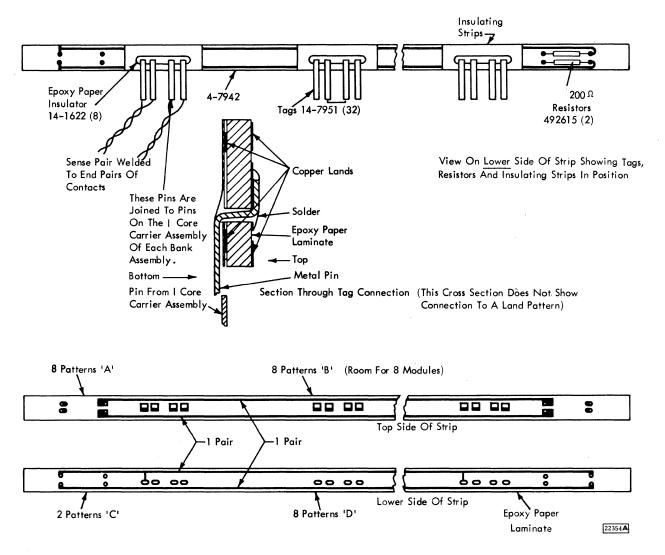

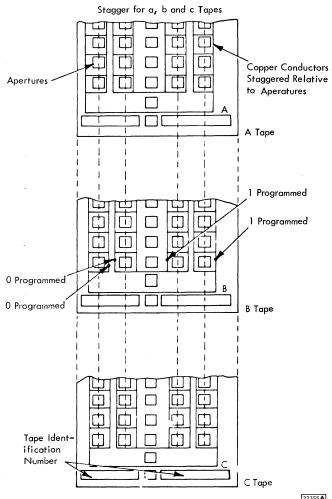

Figure 1-5. Right Side View of 2841 TROS Unit

2311 DC Simplex Connectors

DC Power Distribution Terminal Boards DB 1**-**7

22322A

Figure 1-7. Right Side View of 2841

Figure 1-8. 2841 TROS Unit - Tape Deck Side

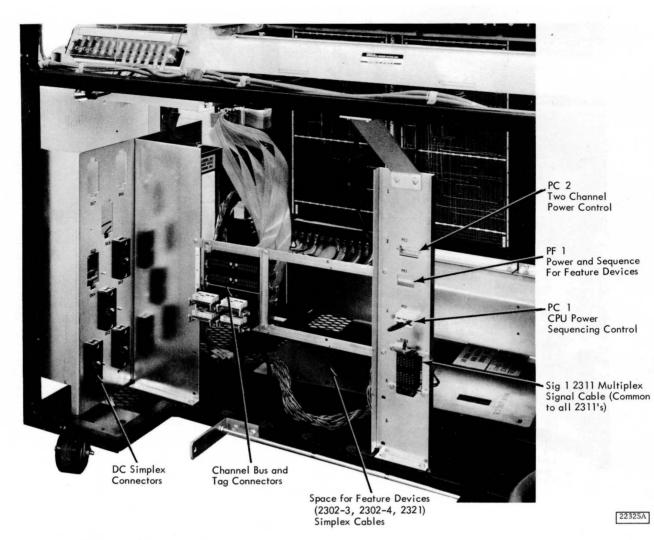

Figure 1-9. 2841 Device/Channel Cabling

22326 A

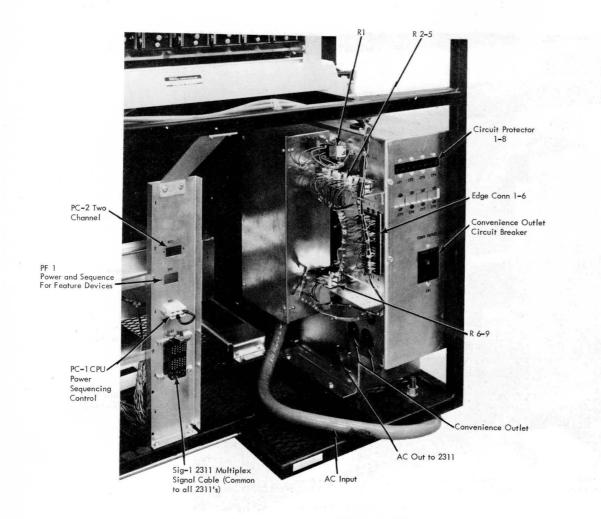

Figure 1-10. Power Sequencing Panel Area

Figure 1-11. Functional Data Flow

## 1.3.4 General Purpose Registers

There are 14 general purpose registers within the 2841. They are used for various purposes by the microprogram. A more detailed description of the usage of these registers is included in Chapter 3.

## 1.3.5 Transformer Read-Only-Storage (TROS)

TROS consists of 2,048 addressable words. Each word is 48 bits in length and is one step in a sequence of words called a microprogram. The TROS storage cycle is 500 ns. TROS furnishes control for all logical units within the 2841. A more detailed description of TROS is included in Chapter 2.

## 1.3.6 Device Interfaces

The device interfaces contain data and control lines unique to a particular device type.

## 1.3.7 Basic Write Data Flow

- 1. A byte of data is requested from channel by the channel interface.

- 2. Channel places the byte on the bus-out lines and notifies the channel interface that the data is ready.

- 3. The byte is transferred from the channel interface through ALU (No arithmetic operation is performed on it.) to one of the general purpose registers.

- 4. The byte is transferred from the general purpose register to SERDES.

- 5. SERDES converts the parallel-by-byte data to serial-by-bit data, and sends this data through the device interface to the device.

- 6. Each of these operations is under control of TROS except for the parallel to serial conversion within SERDES.

#### 1.3.8 Basic Read Data Flow

- 1. Serial-by-bit data from the device is read-in through the device interface and sent to SERDES.

- 2. SERDES converts the serial-by-bit data to parallel-by-byte data.

- 3. When SERDES has a complete byte (8 bits), the byte is transferred to one of the general purpose registers. TROS is notified of this transfer.

- 4. The byte is transferred from this general purpose register through ALU to another general purpose register. Correct parity is generated when the byte is transferred through ALU.

- 5. The channel interface notifies the channel that the 2841 has a byte ready for transfer.

- 6. When the channel is ready to receive the byte, the channel interface is notified and the byte is placed on the Bus In lines.

- 7. The channel takes the byte and notifies the 2841 of this action.

## 1.4. TRACK FORMAT

- A track consists of these areas and records:

- 1. Home Address

- 2. Record Zero

- 3. One or more variable length data records

- An Index Marker indicates the physical beginning of each track.

- Record Zero (Track Descriptor Record) has been designed for a special purpose Flagging.

- An Address Marker designates the beginning of data records.

- Each record is self-formatting. That is, it contains information defining the length of the records.

- Each record contains:

- 1. Count area

- 2. Data area

- 3. Possibly a key area.

- Two areas facilitate the finding of data: Identifier (part of count) and Key Area.

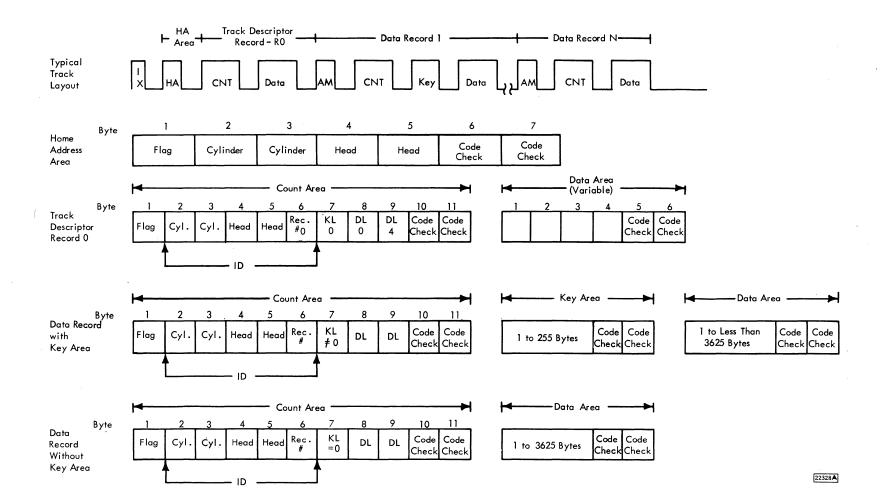

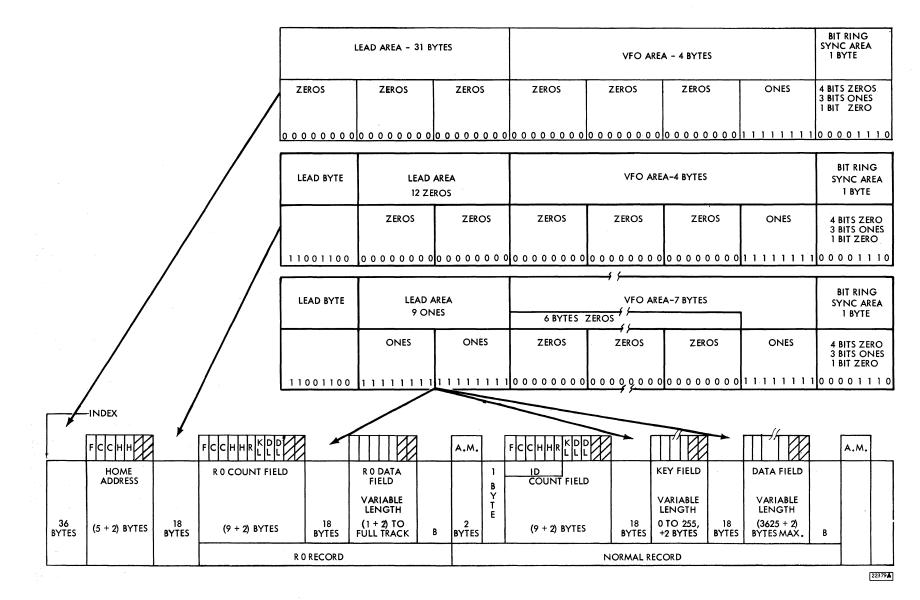

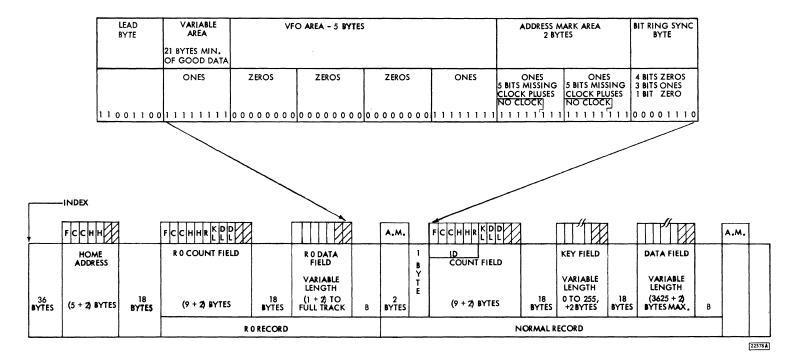

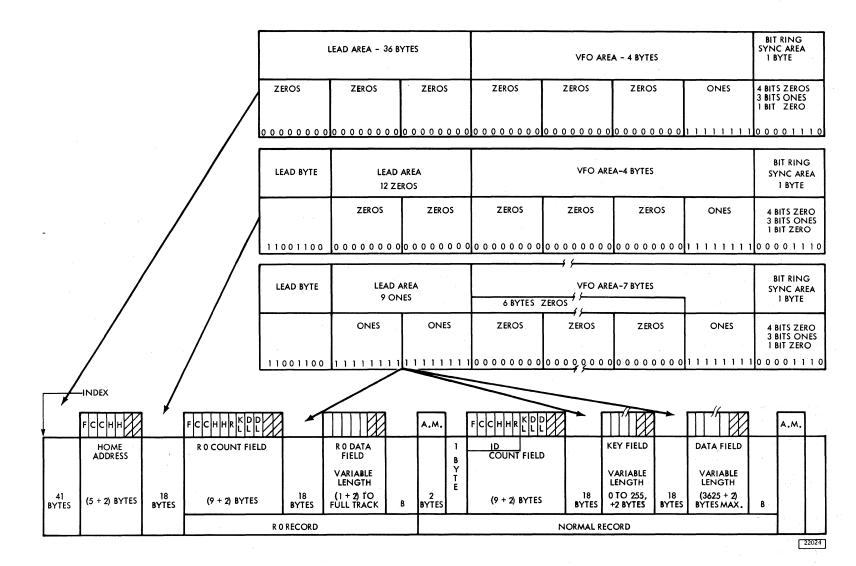

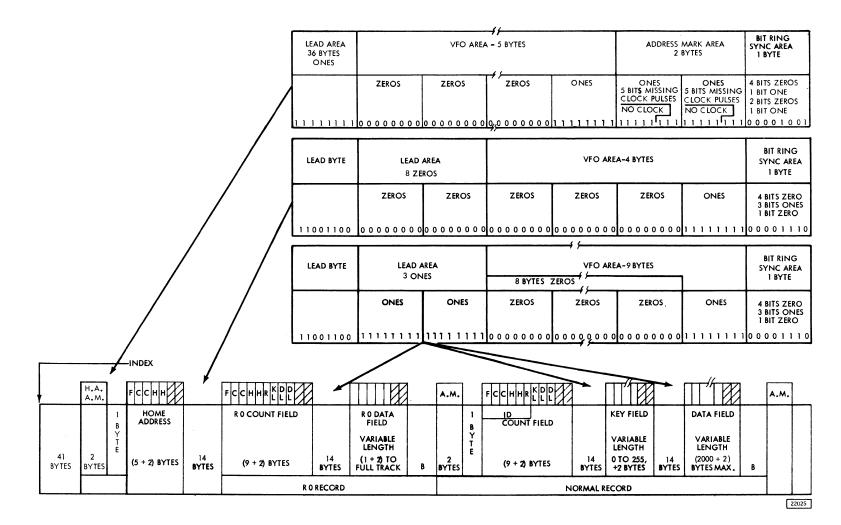

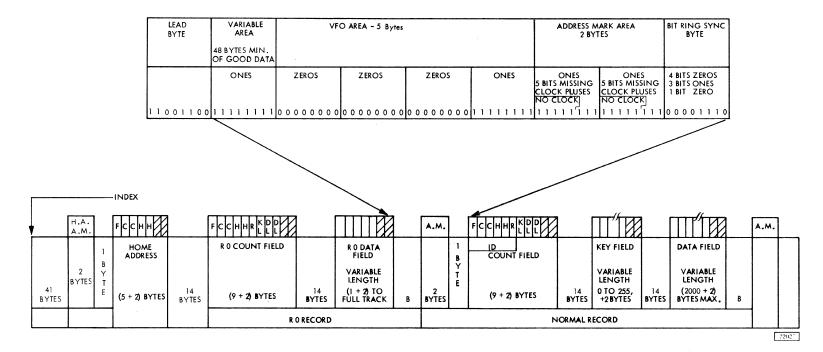

The following information concerning track format (Figure 1-12) pertains to the 2311 drive. However, all units which attach to the 2841 use basically a common track format differing mainly in the maximum capacity of an individual track.

## 1.4.1 Index Marker

The index marker (IX) indicates the physical beginning of each track. All tracks use the same index marker.

#### 1.4.2 Home Address Area

The home address area (HA) consists of seven bytes which define track condition and the physical location within the storage device. There is one HA area per track. This must be the first area written on each track and is created by a write HA operation. Contained within HA are five data bytes.

| Byte     | Name          | Bits     | Function                                                 |

|----------|---------------|----------|----------------------------------------------------------|

| 1        | Flag          | 0-5      | No purpose - always<br>zero                              |

|          |               | 6        | Track Condition<br>0 - good track<br>1 - defective track |

|          |               | 7        | Track Use<br>0 – primary track<br>1 – alternate track    |

| 2,3 C    | ylinder**     | All      | Specifies cylinder<br>address                            |

| 4,5      | Head**        | A11      | Specifies head<br>address                                |

| 6,7      | Code<br>Check | A11      | Error detection                                          |

| Example: | Assume the    | track is | good, the cylinder is                                    |

Example: Assume the track is good, the cylinder is 173, the head is 3. Then the HA area equals:

F C C H H CC CC

$0 \quad 0 \quad 173 \quad 0 \quad 3 \quad *$

\*Value assigned by microprogram during a write HA operation

\*\*There is a requirement that the data recorded in the cylinder and head bytes agree with the physical address of the track. The requirement is that the HH bytes must differ by one in ascending sequence from surface to surface.

#### 1.4.3 Track Descriptor Record (R0)

The first record following home address on each track is the track descriptor record (record zero). It is created by a write R0 operation. Although it may be used to store data, R0 has been designed to enable an entire track's data to be moved to an alternate track if a portion of the recording surface becomes defective. This process is called "flagging" and is described in Chapter 3.

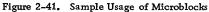

Contained within R0 are a count area and a data area. Although a key area may be included, IBM Programming Systems do not require a key area in R0. 1.4.3.1 Count Area

This area is always 11 bytes in length. It can be divided into four logical sections.

- Flag, Byte 1. This byte is generated by the microprogram as R0 is written. Bits 0-5 equal zero. Bits 6 and 7 are propogated from bits 6 and 7 of the HA flag byte.

- Identifier (ID), Bytes 2-6. This section is composed of five bytes-cylinder, cylinder, head, head, record number (CCHHR). (CCHH) is normally identical to the (CCHH) recorded in the HA Area. (R) is the record number of this record. In the case of R0, the record byte is always zero.

Basically, the user has two ways in which to locate data. One of these is by searching for a particular ID, that is, a particular (CCHHR). Therefore, the purpose of the ID section of a count area is to furnish the user a method for locating the desired information. The second

- method is searching for a particular key area.

Format, Bytes 7-9. On some previous disk storage systems, records were of fixed length (1401-1311), or a separate track (format track) was used 7631-1301) to describe the length of a record. Records on devices attaching to the 2841 can be of variable lengths, therefore, some method was needed to define these record lengths. Bytes 7, 8, and 9 of each count field fully describe the record length as follows:

Byte 7-Key Length (KL). This byte defines the number of bytes (excluding code check bytes) in the key area. If the record has no key area, the KL byte is zero. KL can indicate a key length of 0 to 255 bytes. Normally for R0, the byte is 0.

Bytes 8 and 9 – Data Length (DL). These two bytes define the number of bytes (excluding code check bytes) in the data area. Two bytes (16 bits) can indicate a data length of 0 to 65,535 bytes.

Zero data length indicates an end-of-file record. This may be used for any purpose by the user. The maximum quantity appearing in these two bytes for a 2311 is 3625.

4. Code Check-Bytes 10 and 11. Used for error detection.

#### 1.4.3.2 Key Area

The use of a key area in R0, is at the discretion of the programmer. Standard use of R0 by IBM Programming Systems does not include a key area.

Figure 1-12. 2841 and 2311 Data Track Format

Refer to Data Record Key Area for a descritpion of key area.

#### 1.4.3.3 Data Area

The length and content of the data within R0 is dependent upon the type of IBM Programming System used.

In Figure 1-12, the data area is four plus two code check bytes long.

In Figure 1-12 if the track is good, the four data bytes contain the same information as is recorded in CCHH of the R0 count area.

If the track is bad, the four data bytes contain the cylinder and head address of the alternate track. Refer to Flagging in Chapter 3, for a more detailed description of this process.

Code check bytes are recorded at the end of the data area for error detection.

### 1.4.4 Data Record

One or more data records may follow R0 on a track. Count areas make each record self-formatting for maximum data organization and flexibility. Before each data record is an address marker area, a count area and a data area. Depending upon the type of file organization, there may be a key area between count and data areas.

#### 1.4.4.1 Address Marker

This 3-byte area indicates the beginning of each data record. Address markers are written by the 2841 as data records are created. They are used by the 2841 to locate the beginning of a record for searching, writing, and reading operations. This allows the 2841 to begin an operation anywhere on the track instead of at index point.

#### 1.4.4.2 Count Area

This 11-byte area describes the key and data areas which follow. Bytes 2-9 are created in the CPU by the program used to write the record.

Flag: Byte 1 of the count area is generated by the  $\overline{2841}$  as each record is written. It is not sent from the CPU.

Bit Function

0

1

Flag

Byte

- 0 for even-count records (R0,  $R_2$ ,  $R_4$ ,  $R_6$ ).

- 1 for odd-count records (R<sub>1</sub>, R<sub>3</sub>, R<sub>5</sub>). Used by the 2841 to ensure that all address markers (and records) are present. The 2841 signals a missing address marker when two consecutive, identical bits are encountered (unless an index point intervenes). Used with Record Overflow feature.

- 0 for all non-overflow records and for the last record of an overflow chain.

- 1 for each record except the last segment of an overflow record.

ment of an overflow record

| 2 | Zero                                                                          |

|---|-------------------------------------------------------------------------------|

| 3 | Zero                                                                          |

| 4 | Zero                                                                          |

| 5 | Zero                                                                          |

| 6 | Track Condition<br>0 indicates operative track<br>1 indicates defective track |

| 7 | Track Use<br>0 indicates primary track<br>1 indicates alternate track         |

Bits 6 and 7 are propagated from the flag byte of the preceding record.

Cylinder - Bytes 2 and 3 contain the cylinder number of the track on which the data is stored.

<u>Head</u> - Bytes 4 and 5 contain the read/write head number of the track on which the data is stored. Generally the cylinder and head information are identical to the cylinder and head information recorded in the HA Area.

<u>Record Number</u> - Byte 6 designates the sequential number of the record on the track.

<u>Key Length</u> - Byte 7 specifies the number of bytes in the Key Area. This may vary from 0 to 255 bytes (0 meaning no Key Area). Data Length - Bytes 8 and 9 specify the number of bytes in the Data Area. This may vary from 0 to 3625 bytes for a 2311.

Cyclic Code Check - Bytes 10 and 11 are used for error detection. See Error Detection.

## 1.4.4.3 Key Area

As mentioned previously, the user has two ways of locating his data, one of which is searching for a particular ID (CCHHR).

Another way of locating data is by searching for a particular key area. The key area length ranges from 1 to 255 bytes. The key area could contain identifying information about a record, such as serial number, social security number, policy number, etc.

Cyclic code check bytes are recorded at the end of the key area for error detection.

1.4.4.4 Data Area

This area contains the information identified by the count (ID) and key areas. This area may vary in length from 1 to 3625 bytes for a 2311.

Cyclic code check bytes are recorded at the end of the data area for error detection.

#### 1.4.5 Gaps

Gaps are used to separate records and areas within records on the tracks. There are three types of gaps.

|               | RO    |           | 1000  | ORD 1    |      |

|---------------|-------|-----------|-------|----------|------|

| I HA<br>X 1 2 | CNT 2 | DATA 3 AM | CNT 2 | KEY<br>2 | DATA |

Gap 1 - The gap between index and the HA area. A fixed length -36 bytes. This gap is referred to as the HA gap.

Gap 2 - The gap between the end of HA and R0 count field. Also the gap between areas of a record. Fixed length -18 bytes. This gap is referred to as the alpha ( $\alpha$ ) gap.

Gap 3 – The gap between the end of the data area of one record and the beginning of the count area of the next record. Variable length -27 bytes plus 5% of the sum of the previous records key and data length. This gap is referred to as the beta ( $\beta$ ) gap. The beta gap also contains two address mark bytes. A more detailed description of the contents of these gaps is in Chapter 2, under the heading – Serializer/Deserializer Unit.

Gap size and byte contents vary with the feature devices (refer to Chapter 5).

#### 1.4.6 Error Detection

As information is being transferred from the parallelby-bit using system to the serial-by-bit device (write), the 2841 strips off the parity bit associated with each byte. Parity bits are not recorded on the storage devices. For transfer to the channel (read) the 2841 assembles the serial-by-bit device data into a parallel-by-bit byte, adds a parity bit, and transmits the complete byte to the using system.

In the serial/direct access storage devices, checking the validity of the recorded information is accomplished by adding a string of 16 bits (two bytes) to the end of each area. This type of checking is called cyclic code checking.

Code checking is accomplished by first filling two 1-byte registers with all bits. Then each character read or written is exclusive ORed to one of the two registers. All even numbered characters go to the same register and all the odd characters go to the other. The final result is two "hash" total characters. These are used as the two code check characters.

For a write operation the two bytes of cyclic check code are added to the end of the record and written on the track.

On a read operation, the process is continued until the cyclic code bytes on the end of the record are operated upon. If no error has occurred, the result is all zeros in the cyclic code check registers.

Example: Write

#### Register 1

| Set to ones | 11111111 |

|-------------|----------|

| 1st Char.   | 11110001 |

| Result      | 00001110 |

| 3rd Char.   | 11110011 |

| Result      | 11111101 |

Code Check byte one

|                                                                                       | Register 2                                                                                                                                                                                                        |  |  |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Set to ones<br>2nd Char.<br>Result<br>4th Char.<br>Result                             | $ \begin{array}{c} 1 1 1 1 1 1 1 1 \\ \underline{1 1 1 1 0 0 1 0} \\ 0 0 0 0 1 1 0 1 \\ \underline{1 1 1 0 0 0} \\ 1 1 1 1 0 0 1 \end{array} $ Code Check byte two                                                |  |  |  |  |  |

| Example: Read                                                                         | ·                                                                                                                                                                                                                 |  |  |  |  |  |

|                                                                                       | Register 1                                                                                                                                                                                                        |  |  |  |  |  |

| Set to ones<br>1st Char.<br>Result<br>3rd Char.<br>Result<br>Code Check one<br>Result | $ \begin{array}{c} 1 1 1 1 1 1 1 1 1 \\ 1 1 1 1 0 0 0 1 \\ \hline 0 0 0 0 1 1 1 0 \\ 1 1 1 1 0 0 1 1 \\ \hline 1 1 1 1 1 1 0 1 \\ 1 1 1 1 1 1 0 1 \\ \hline 0 0 0 0 0 0 0 0 0 \\ \end{array} $ Register 2         |  |  |  |  |  |

| Set to ones<br>2nd Char.<br>Result<br>4th Char.<br>Result<br>Code Check two<br>Result | $ \begin{array}{c} 1 1 1 1 1 1 1 1 1 \\ \underline{1 1 1 1 0 0 1 0} \\ \hline 0 0 0 0 1 1 0 1 \\ \underline{1 1 1 1 0 1 0 0} \\ 1 1 1 1 1 0 0 1 \\ \underline{1 1 1 1 1 0 0 1} \\ 0 0 0 0 0 0 0 0 0 \end{array} $ |  |  |  |  |  |

The cyclic code check used in the 2841 has the following checking properties:

- 1. Detects all errors in which an odd number of bits is wrong.

- 2. Detects single bursts of errors that are 16 bits or less in length.

#### 1.5 PROGRAMMING

Refer to SRL, Form Number A26-5988 for input/output operations and programming of the 2841.

A summary of the 2841 operation codes is included in table 1.

#### SYSTEM/360 I/O INTERFACE

#### **1.6 CHANNEL INTERFACE INTRODUCTION**

- The IBM System/360 Interface:

- 1. Provides a method of attaching I/O units to the IBM System/360.

2. Consists of 34 lines.

3. Accommodates up to eight control units.

The input-output interface provides a uniform method of attaching input/output (I/O) control units to IBM System/360 channels. The interface can accommodate up to eight control units with addressing capabilities for up to 256 I/O devices.

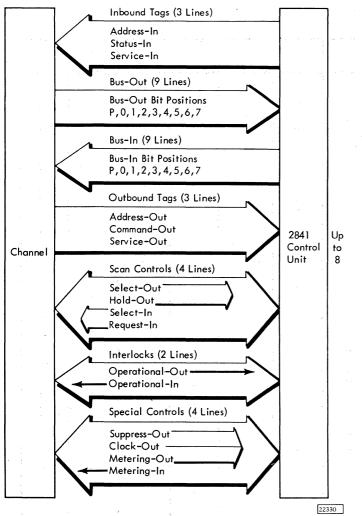

The interface establishes requirements for signal transfers between control units and the servicing channel. Therefore, interface lines provide a common information format and signal sequence for all input/output devices. Figure 1-13 categorizes interface lines according to their general functions.

Except for signals that establish priority among control units, all interface signals are sent over a common bus. Any interface signal that the channel generates is available to all control units, but, only one control unit at a time is logically connected to the interface. After a control unit is selected, it remains logically connected to the interface until the control unit transmits or receives the required information or until the channel signals the control unit to disconnect.

The rise and fall of signals transmitted over the interface are interlocked with the corresponding responses. This interlocking makes the interface applicable to a wide variety of circuits and data rates, and permits the connection of control units of different circuit speeds.

Each control unit contains an address card that designates its interface address; no two control units on the same interface can have identical addresses. To begin an I/O operation, the channel must transmit the address of the desired unit.

Interface adapter circuits located in each control unit:

- 1. Convert interface line sequences and coded commands to the control lines necessary to operate the control unit.

- 2. Establish communication between the control circuits in the unit and the interface.

#### **1.7 INTERFACE LINES**

- Interface lines are divided into five types:

- 1. Bus lines.

- 2. Scan controls.

- 3. Tag lines.

- 4. Interlock lines.

- 5. Special controls.

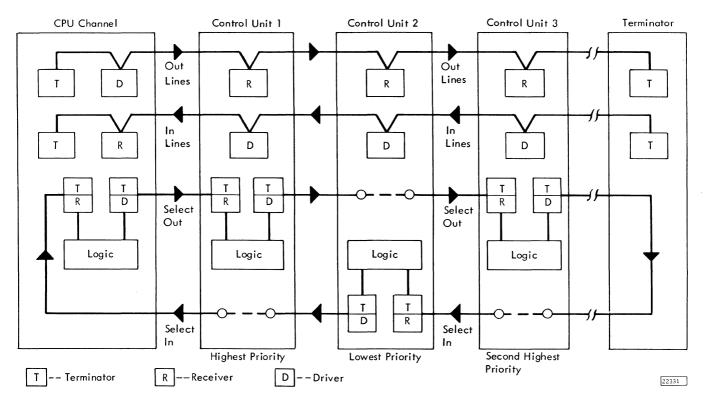

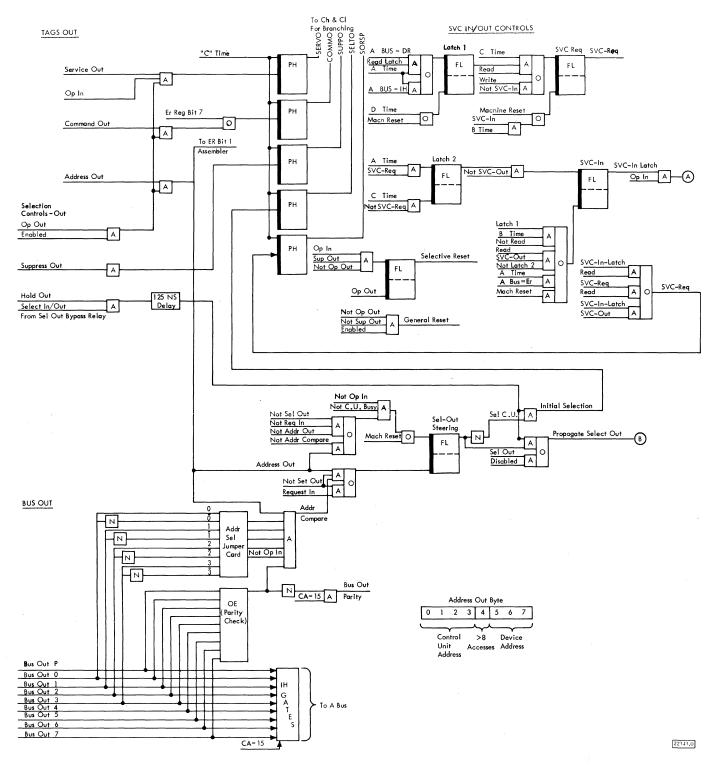

Figure 1-14 shows channel and control unit connections to the interface. Observe that the select lines (select-out and select-in) connect serially through each control unit for the purpose of establishing priority; other lines connect in parallel.

#### 1.7.1 Bus Lines

- Bus lines carry information between the channel and control unit.

- There are nine bus-in lines and nine bus-out lines.

Information is transmitted over the interface from the channel to the control unit on bus-out, and from the control unit to the channel on bus-in. Bus-in and bus-out each contain eight information lines and one line for odd parity.

Information on the in and the out bus is arranged so that bit position 7 of a bus always carries the lowest-order bit within an eight-bit byte. The highest-order bit is in position 0.

### 1.7.1.1 Bus-Out

- Bus-Out transfers information from the channel to the control unit.

- There are eight data lines and one parity line.

The nine bus-out lines transfer information from the channel to control units. The channel conditions an outbound tag line to identify the type of data transmitted on bus-out lines. For example, when the address-out tag and bus-out lines are active concurrently, information on bus-out lines designates an address.

Tag lines control the period during which busout lines contain valid information. When transferring the address of an I/O device, information on bus-out lines is valid from the rise of address-out to the rise of one of the following: operational-in, select-in, or status-in. When transferring information other than an address, signals on bus-out lines are valid from the rise of the identifying outbound tag to the fall of the responding inbound tag.

## 1.7.1.2 Bus-In

- Bus-In transfers information from the control unit to the channel.

- There are eight data lines and one parity line.

The nine bus-in lines transfer information from the selected control unit to the channel. The control

unit conditions an inbound tag line to identify the type of information transmitted on bus-in lines. For example, when the status-in tag and bus-in lines are active concurrently, bus-in lines contain a status byte.

Tag lines control the period during which bus-in lines contain valid information. Signals on bus-in lines are valid 100 nanoseconds (ns) after the rise of the identifying inbound tag to the rise of the responding outbound tag.

#### 1.7.2 Scan Controls

- Select-out, hold-out, and select-in are controlled by the channels. Request-in is controlled by the control unit.

- The scan controls are independent of CPU non-I/O operations.

- Scan controls enable the channel to contact control units attached to it.

- Scan controls permit control units to request service from the channel.

- Scan controls establish contact between the channel and the control units on a priority basis.

#### 1.7.2.1 Select-Out

- Select-out connects each control unit in series.

- It determines the priority of control units.

The select-out lines provide the loop that allows the channel to interrogate each control unit in priority sequence.

Logically, the select-out line connects serially through each control unit by connecting:

- 1. The channel to the control unit having the highest priority.

- 2. A control unit to the next control unit in descending priority sequence.

The physical location of a control unit (with respect to the channel) does not establish the unit's designated priority. For example, the control unit farthest from the channel might be the first unit to which select-out logically connects; this unit would then be the unit to which the highest priority is assigned.

When an I/O control unit receives the select-out signal it must either raise its operational-in line in response to it (request service) or immediately propagate the select-out signal to the next control unit in

#### Table 1. Bit Structure of 2841 Op Codes

|                                                                                                                                                                                                             | 0<br>м/т                             | 1<br>HI                              | 2<br>=                          | 3<br>C                               | 4<br>K                               | 5<br>D                               | 6 7<br>CHANNEL                            |                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|---------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------|---------------------------------|

| Write Data<br>Write Key, Data<br>Write Count, Key, Data<br>Write Home Address<br>Write R0<br>Control Erase                                                                                                  | 0<br>0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>0                | 0<br>0<br>0<br>0<br>0           | 0<br>0<br>1<br>1<br>1<br>1           | 0<br>1<br>1<br>0<br>0                | 1<br>1<br>0<br>1<br>0                | 0<br>0<br>0<br>0<br>0<br>0                | 1<br>1<br>1<br>1<br>1<br>1      |

| Search Equal ID<br>Search Equal Key<br>Search Equal Home Address<br>Search Equal Key, Data<br>Search Hi ID<br>Search Hi Key, Data<br>Search Hi Equal ID<br>Search Hi Equal Key<br>Search Hi Equal Key, Data |                                      | 0<br>0<br>1<br>1<br>1<br>1<br>1      | 1<br>1<br>0<br>0<br>1<br>1<br>1 | 1<br>0<br>1<br>0<br>0<br>1<br>0<br>0 | 0<br>1<br>1<br>0<br>1<br>1<br>0<br>1 | 0<br>0<br>1<br>0<br>1<br>0<br>0<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                                 |

| Read Data<br>Read Key, Data<br>Read Count, Key, Data<br>Read Home Address<br>Read RO<br>Read Count<br>Read Initial Program Load (IPL)                                                                       | -<br>-<br>-<br>-<br>-<br>-<br>0      | 0<br>0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>0<br>1<br>1<br>1<br>1<br>0      | 0<br>1<br>1<br>0<br>0<br>0           | 1<br>1<br>0<br>1<br>0<br>0           | 1<br>1<br>1<br>1<br>1                     | 0<br>0<br>0<br>0<br>0<br>0      |

| Control Seek (BBCCHH)<br>Control Recalibrate<br>Control Restore<br>Control Space Count<br>Control No Op<br>Control Cyl. Seek (CCHH)<br>Control Head Seek (HH)<br>Control Set File Mask                      | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>0<br>0<br>1<br>1      | 0<br>0<br>1<br>0<br>1<br>1<br>1      | 1<br>0<br>1<br>0<br>0<br>0           | 1<br>1<br>1<br>1<br>1<br>1<br>1           | 1<br>1<br>1<br>1<br>1<br>1<br>1 |

| Test I/O                                                                                                                                                                                                    | 0                                    | , O                                  | 0                               | 0                                    | 0                                    | 0                                    | 0                                         | 0                               |

| Sense I/O                                                                                                                                                                                                   | 0                                    | +                                    | +                               | +                                    | 0                                    | 1                                    | 0                                         | 0                               |

| Write Spec–Count, Key, and Data (used with Record<br>Overflow)                                                                                                                                              | 0                                    | 0                                    | 0                               | 0                                    | 0                                    | 0                                    | . 0                                       | 1                               |

| Reserved                                                                                                                                                                                                    | 0                                    | 0                                    | 1                               | 0                                    | 0                                    | 0                                    | 1                                         | 1                               |

Note: On Search and Read commands B0 can be either 0 or 1. If "0", head switching will not take place when Index Point is detected. If 1, head switching will take place when Index Point is detected. On a Sense Command Bits 1, 2, and 3 of the Code are "don't care" conditions (+).

22329**A**

Figure 1-13. Interface Lines

Figure 1-14. Interface Connections

the series. Once a control unit has propagated select-out, it cannot raise its operational-in line until the next incoming select-out line to the control unit rises.

The channel must hold select-out active until it receives a signal on either the select-in or the address-in line. When select-out is transferred to the control unit with the lowest priority, the control unit either 1) raises its operation-in line, and later, its address-in line, initiating a signal sequence with the channel, or 2) sends the incoming selectout to the channel. The signal on the select-out line's return path to the channel is called select-in.

If a control unit conditions operational-in when the incoming select-out is active, it does not transfer select-out to the next control unit (or select-in to the channel). By conditioning operational-in, the control unit interrupts the channel's scan loop. Then, the control unit transmits an address byte on bus-in lines and conditions address-in. The control unit must hold operational-in active until communication with the channel is complete. The channel can drop select-out after receiving address-in, or can hold select-out active through the complete I/O operation. In no case can the control unit cancel operational-in before the channel drops select-out.

- 1.7.2.2 Select-In

- The select-out line's return path to the channel is select-in.

The control unit provides an option of connecting its selection logic in series on either the select-out or select-in line (Figure 1-14). Descending-order priority from the channel can be established on the select-out line, and the remaining control units can maintain the decending-order priority from the channel on the select-in logic. For clarity, in this manual, the selection logic is assumed to be connected to the select-out line.

Select-in is a line from the lowest-priority control unit to the channel. It is the outgoing select-out line of that control unit and provides a return path to the channel for the select-out signal. The definition of the select-in line is the same as that of a selectout line coming from any control unit.

## 1.7.2.3 Request-In

- This is a request for service from the control unit to the channel.

- May initiate a polling sequence at the channel.

A control unit conditions the request-in line to indicate that it will initiate a signal sequence when select-out polls that unit again. The channel need not condition select-out to scan the attached control units until the request-in line indicates that a control unit requires servicing. This operation allows the control unit with the highest priority to receive attention in a minimum amount of time after the requestin line is conditioned. To illustrate the function of request-in, consider the following example:

Assume that the highest interface priority is assigned to the I/O device with the highest data rate and that the device with the slowest data rate has the lowest priority. The unit with the lowest priority can wait longest for service; so, each time that the request-in line is conditioned, that unit is the last to be polled. Because the I/O device with the highest priority can wait the least time for service, each request-in indication causes that unit to be polled first.

# 1.7.2.4 Hold-Out

- Hold-out is used in conjunction with select-out.

- It allows the channel to cancel the effects of select-out and control polling.

The channel conditions the hold-out line to all control units in parallel to allow select-out to perform its designated function in a control unit. The hold-out line allows the channel to cancel the effects of selectout at each control unit at the same time. If the channel is holding select-out active and cancels holdout, no control unit can make use of select-out; a unit can only propagate the incoming select-out to the next unit. Therefore, the channel receives select-in in the shortest possible time.

## 1.7.3 Outbound Tag Lines

- These lines carry instructional signals to an attached control unit.

- They identify information on bus-out lines.

- Two out-tags cannot be active at the same time.

- Each line remains active until an inbound tag responds to it.

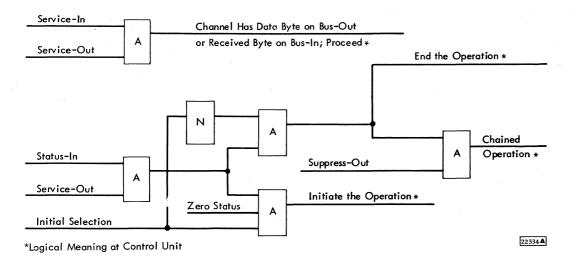

1.7.3.1 Address-Out

• Address-out normally identifies information on bus-out as an address.

• On a halt-I/O instruction, address-out instructs the control unit on the interface to disconnect.

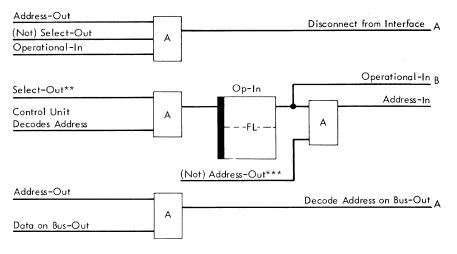

The channel transmits a signal over the address-out line (Figure 1-15) to indicate either of two conditions:

- Address-out initiates selection of an I/O device 1. causing all attached control units to attempt to decode the address on bus-out lines. Because each control unit address is different, only one unit can decode the address. If the control unit that recognizes the address is not busy, it must respond by conditioning operational-in when select-out is conditioned to that control unit. Address-out precedes the rise of select-out by at least 400 nanoseconds. The channel must hold address-out active until it receives operationalin, select-in, or status-in. Select-in indicates that no control unit decoded the address. This occurs when the specified control unit is off line. Status-in indicates that the designated control unit is busy and cannot be interrupted to execute another operation. The channel responds to the status-in reply by canceling select-out. It then waits for status-in to fall and cancels addressout.

- 2. On a Halt I/O instruction, address-out instructs the control unit on the interface to disconnect. If the unit is selected, the channel will:

- a. Condition the select-out line (may already be up).

- b. Receive operational-in from a control unit, (will already be up).

- c. Condition the address-out line.

- d. Cancel select-out and hold address-out active until the control unit allows operational-in to fall.

The control unit must cancel operational-in within 6 microseconds ( $\mu$ sec) after receiving the interface disconnect indication. The I/O operation proceeds to the normal end, but the data is not transferred across the interface.

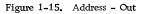

#### 1.7.3.2 Command-Out

- This indicates a command byte on bus-out in response to address-in during channel initiated selection.

- It means "proceed" in response to address-in during control unit initiated selection.

- It causes the control unit to stack the status-in response to status-in.

- It means "stop" in response to service-in.

The channel conditions the command-out line (Figure 1-16) to respond to a signal on an inbound tag line. During the initial selection sequence, the channel activates command-out to reply to address-in, indicating that a command byte is on bus-out lines. This command byte specifies the I/O operation to be performed. Only at this point in the initial selection sequence does command-out cause the selected control unit to decode the byte on bus-out lines.

A command-out response to service-in means "stop" and causes the control unit to terminate the data transfer. Whether during the initial selection sequence or at the end of the operation, the commandout reply to status-in causes the selected control unit to stack (hold) the status data. The control unit can present the stacked status only if suppress-out and address-out are down when select-out rises at the control unit.

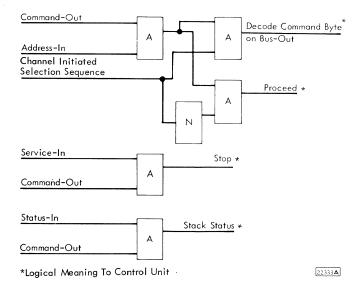

1.7.3.3 Service-Out

- This identifies information on bus-out as data in response to service-in on write, search, and control operations.

- It indicates that the channel received data in response to service-in on read, and sense operations.

- It indicates that the channel accepted the status information in response to status-in.

- It indicates chaining in response to status-in with suppress-out active.

Service-out, a line from the channel to all attached control units, is used to signal the selected device in recognition of a signal on the service-in or status-in line (Figure 1-17). A signal on the service-out line indicates to the selected device that the channel has accepted the information on bus-in or has provided on bus-out the data requested by service-in.

When service-out is sent in response to servicein during read or sense operations, or to status-in, the service-out signal must rise after the channel accepts the information on bus-in. In these cases, the rise of service-out indicates that the information is no longer required to be valid on bus-in. When service-out is sent in response to service-in during a write, search, or control operation, the rise of service-out indicates that the channel has provided the requested information on bus-out. In this case, the signal must rise after the information is placed on the bus. Service-out must stay up until the fall of the associated service-in or status-in signal.

\* Control Unit must drop Op-in within 6µsec.

\*\* Select-out rises a minimum of 400 ns after address-out

\*\*\* Rise of Op-in causes address-out to fall.

A Meaning to 2841

B Logical Circuit

22332 A

Figure 1-16. Command - Out

Figure 1-17. Service - Out

Service-out cannot be up concurrently with any other "out" tag.

A service-out response to status-in while suppress-out is up indicates to the control unit that the operation is being chained. See Suppress-Out for further details. The status is accepted by the channel.

#### 1.7.4 Inbound Tag Lines

- These lines carry instruction signals from the control unit to the channel.

- They identify information on bus-in lines.

- They remain active until an outbound tag responds to it.

- Two "in" tags cannot be active at the same time.

Control units transmit instructional signals to the channel over inbound tag lines. Two or more inbound tag lines cannot be active concurrently. The control unit must hold the inbound tag line active until the channel responds by conditioning an outbound tag line. The control unit must then cancel the signal on the inbound tag line to allow the channel to drop the responding outbound tag line.

1.7.4.1 Address-In

- This identifies information on bus-in as an I/O unit address.

- The channel responds with command-out.

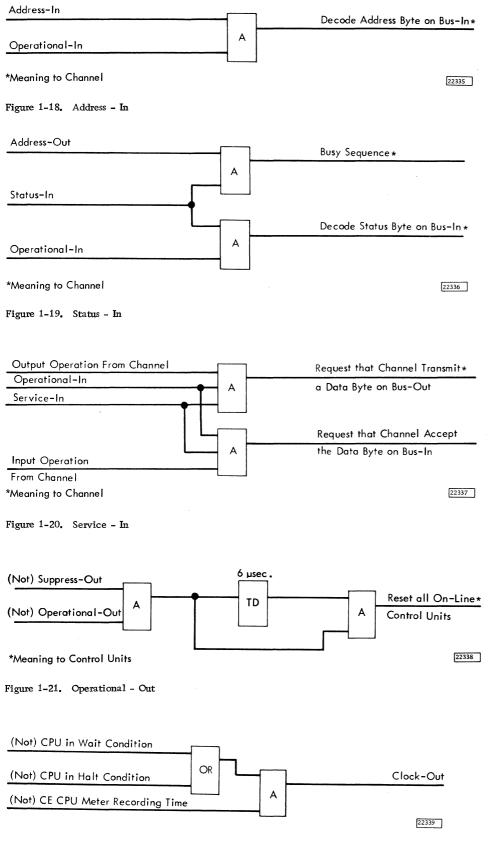

Address-in is a line from all attached control units to the channel (Figure 1-18). It is used to signal the channel that the address of an I/O unit is on bus-in. The channel responds to address-in with commandout.

Address-in remains active until the rise of command-out. It must then fall in order that command-out can fall.

1.7.4.2 Status-In

- This identifies information on bus-in as status information.

- It remains up until command-out or service-out rises, or until select-out falls if Address-In is up.

A control unit activates the status-in line to indicate to the channel that a status byte is on the bus-in lines (Figure 1-19). The status byte has a fixed format and contains bits describing the current status at the control unit.

Status-in must remain up until the channel responds with:

- 1. Service-out, indicating that the channel accepted the status.

- 2. Command-out, indicating that the channel has suppressed the status.

If status-in is the control unit's reply to addressout, during initial selection, it must remain up until select-out falls.

## 1.7.4.3 Service-In

- This identifies information on bus-in on data read or sense operations.

- It indicates a control unit request for data on write and control operations.

- It remains up until command-out or service-out rises.

A control unit activates the service-in line (Figure 1-20) to:

- 1. Signal the channel that a data byte is on the busin lines (read, or sense operations).

- 2. Request that the channel transmit a data byte on the bus-out lines (write, search, or control oper-ations).

The channel responds to service-in with:

- 1. Service-out, when data is accepted or transmitted.

- 2. Command-out, to stop data transfers and end the operation.

#### 1.7.5 Interlock Lines

- These lines permit only one control unit on the interface at a time.

- They gate the tag lines.

- They reset the control unit.

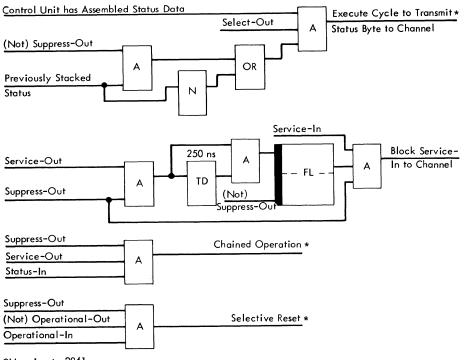

#### 1.7.5.1 Operational-Out

• Gates on all interface lines except suppress-out.

• Operational-out provides a reset to the control units.

Operational-out originates at the channel, rising when the CPU is power-on reset. It stays up as long as the channel is operable. The fall of operational-out resets control units on the interface either selectively or concurrently depending on the status of suppress-out, a special control line (Figure 1-21). Operational-out is a gate on all outbound tag lines. They have no effect if operational-out is down. If the channel drops operational-out while a control unit is operating on the interface, the operation must be reset. If the operational-out and the suppress-out lines are down concurrently for 6 microseconds, all control units operating in the on-line mode are reset.

1.7.5.2 Operational-In

- This line signals the channel that a device is selected.

- It remains up until select-out falls and the signal sequence is completed.

To initiate an interface signal sequence, a control unit conditions operational-in while the incoming select-out line to the control unit is up. The control unit must, at the same time, block select-out from reaching the next control unit. No other control unit can connect to the interface while operational-in is up.

When operational-in is raised for a particular signal sequence, it must stay up until all required information is transmitted between the channel and the device. Operational-in must drop at the same time, or after the rise of the outbound tag associated with the transfer of the last byte of information, if select-out is down. For burst-mode devices, operational-in can drop if select-out is down or drops after receipt of the stop signal sequence.

Signals on bus-in and on the inbound tag lines are significant only when operational-in is up except in the case of the control-unit-busy selection sequence. When operational-in is down, the channel must disregard any signals on these lines. On the other hand, each control unit must provide interlocks to ensure that it does not place any signals on bus-in and the incoming tag lines unless its operational-in line is up.

## 1.7.6 Special Controls

- The four special-purpose lines are:

- 1. Clock-Out.

- 2. Metering-Out.

- 3. Metering-In.

- 4. Suppress-Out.

1.7.6.1 Clock-Out

- This indicates when the CPU is in a halt or wait condition.

- It designates when the control unit is free to change status.

The clock-out line (Figure 1-22) carries signals from the channel to indicate to each control unit that the processing unit is not in the halt or wait condition. Because a control unit can switch between the enable and disable states only when the processing unit is halted or waiting, clock-out designates the interval at which a control unit is free to change states. When the customer meter that registers processing unit time is disabled and the meter that indicates CE processing unit time is recording, the channel does not condition clock-out.

1.7.6.2 Metering-Out

• This conditions customer meters to register time.

The channel transmits metering-out to each control unit when the customer meter is recording processing unit time. Metering-out causes customer meters to register time in each control unit that is not disabled.

1.7.6.3 Metering-In

• This indicates to the channel that the customer meter is recording time.

A control unit transmits metering-in to the channel when the customer meter on the control unit is recording time. Metering-in causes the customer meter that records use of the processing unit to accumulate time even though the processing unit may be in the halt or wait condition.

Figure 1-22. Clock - Out

#### 1.7.6.4 Suppress-Out

- The suppress-out line has these functions:

- 1. Suppress status.

- 2. Suppress data transfer.

- 3. Chain command control.

- 4. Selective reset.

Suppress-out is used alone or with an outbound tag line to provide the following special functions (Figure 1-23).

<u>Suppress Status</u>: When a control unit ends an I/O operation, it transmits a status byte on bus-in lines and conditions the status-in tag line to the channel. The status byte indicates whether errors were encountered in performing the operation and signals the channel that the operation is complete. A channel may respond to status-in with command-out, causing the control unit to stack the status data.

The next time select-out rises at a control unit holding stacked status data, that control unit will not activate the interface to present the status byte if suppress-out is active. The channel must condition suppress-out at least 250 ns before the control unit receives select-out to ensure that the stacked status data is not transmitted. The rise of suppress out, after a control unit begins a status cycle, does not interfere with the transmission of the status byte. If a control unit conditions request-in to offer status data, and suppress-out rises before the control unit receives select-out, suppress-out drops request-in.

<u>Suppress Data Transfer</u>: For noncyclic I/O devices (buffered I/O devices, not applicable to 2841) that can wait for data transfers without indicating an overrun condition, suppress-out blocks service-in. The channel must condition suppress-out at least 250 nanoseconds before the previous service-out tag drops to ensure that the subsequent request for data or offer of data will be suppressed.

<u>Chain Command Control</u>: To indicate a chained command, the channel conditions suppress-out after the selected control unit begins the cycle to transfer the ending status byte and before the channel responds to status-in with service-out. The active state of the suppress-out line and the service-out response to status-in combine to hold selection of the control unit and the I/O device. The next command from channel must be directed to that control unit and I/O device. <u>Selective Reset</u>: If the channel conditions suppressout at least 250 nanoseconds before allowing operational-out to fall and holds suppress-out active until 250 ns after operational-out rises again, only the I/O device presently operating on the interface is reset.

## **1.8 INTERFACE OPERATIONS**

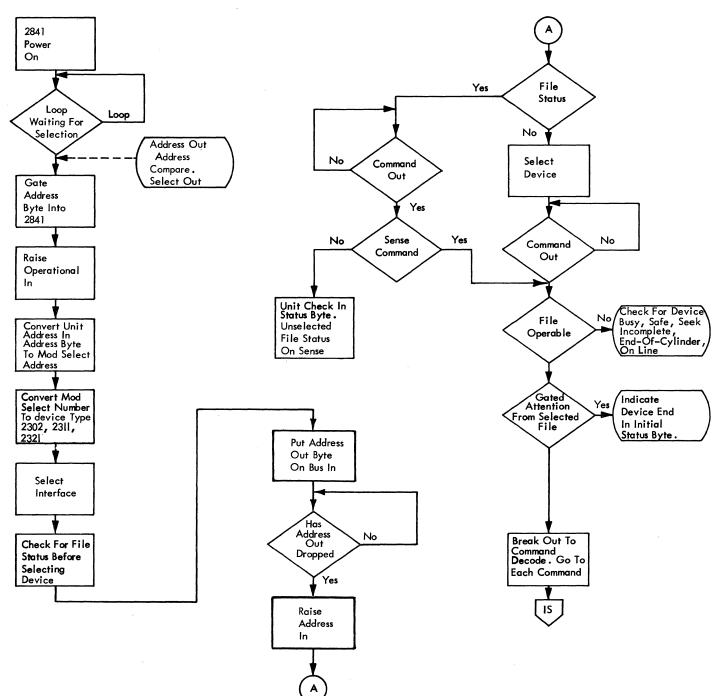

## 1.8.1 Initial Selection Sequence

- In this sequence the channel:

- 1. Selects a control unit and device.

- 2. Specifies the operation to be performed.

- The sequence is standard for all units and operations.

The interface signal sequence in which the channel selects a control unit and I/O device and specifies an operation to be performed is called the initial selection sequence (Figure 1-24). Regardless of the unit selected or the operation designated, the signal sequence in the initial selection is standard.

The channel begins the initial selection sequence by transmitting an address byte on bus-out lines and conditioning address-out. The address byte selects the unit to execute the operation. Each control unit attached to the interface attempts to decode the address, but, because all interface addresses are different, only one unit can interpret the coded byte.

When select-out is active at the control unit that successfully decodes the address byte, that control unit conditions either:

- 1. Status-in, indicating that the selected unit is busy and cannot execute another operation, or

- 2. Operational-in, indicating that the designated unit will complete the initial selection sequence. However the operational-in response to addressout does not commit the control unit or the channel to perform an operation.

If no control unit decodes the address byte (specified control unit is off line, the address byte is invalid, etc), the control unit with the lowest priority propagates select-in to the channel when its incoming select-out is conditioned. The select-in or status-in reply to address-out causes the channel to cancel-out and terminate the selection sequence. When operational-in causes the channel to drop address-out, the selected control unit transmits an address byte on bus-in lines and conditions the address-in line. The channel compares this address to the address it placed on the bus-out lines to ensure that the right device has answered.

After checking the address, the channel responds to address-in by transmitting a command byte and conditioning command-out to the control unit. The command byte designates one of the thirty-four operations and establishes conditions to control execution of the operation.

The control unit must then drop address-in, and after command-out falls, the control unit places its status information on bus-in and raises status-in. If the I/O device is available, the status byte is zero. If the channel accepts this status byte, it responds with service-out. This signal completes the initial selection sequence.

<u>Polling</u>: When a control unit that does not have operational-in up requires service, it raises its request-in line to the channel. The next time selectout rises at any control unit requiring service and no I/O selection is being attempted by the channel (address-out down), the control unit places the address of the device on bus-in. It then signals on both the address-in and the operational-in lines, and removes the request-in signals. When the channel recognizes the address, a command-out signal is sent to the control unit, indicating "proceed." After address-in drops, the channel responds by dropping the command-out signal. The remainder of the sequence is the same as a channel-initiated initial selection sequence.

# 1.8.2 Data Transfers

- A control unit can send data to, or request data from the channel.

- Service-in and service-out are the controlling tag lines.

Data transfer may be requested by a control unit after a selection sequence. To transmit to the channel, the control unit places a data byte on bus-in and raises service-in; the tag and the validity of bus-in must be held until an outbound tag is raised in response. To request data from the channel, servicein is raised. The channel places the data on bus-out and signals with service-out. The channel maintains the validity of bus-out until service-in falls. When service-in falls, the channel responds by dropping service-out.

#### 1.8.3 End Operation

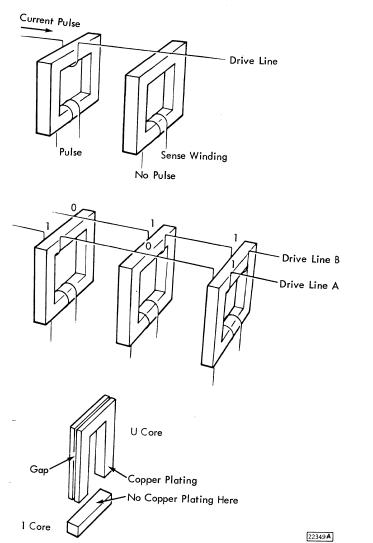

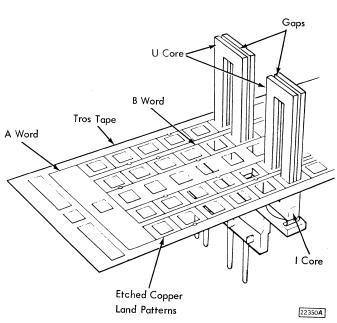

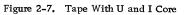

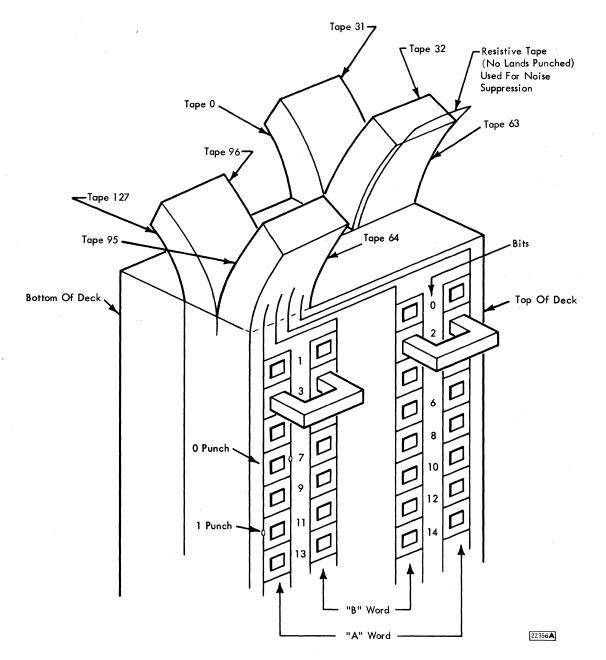

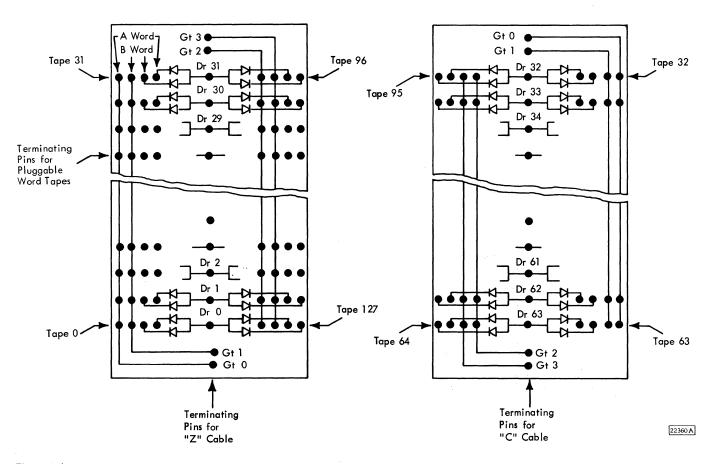

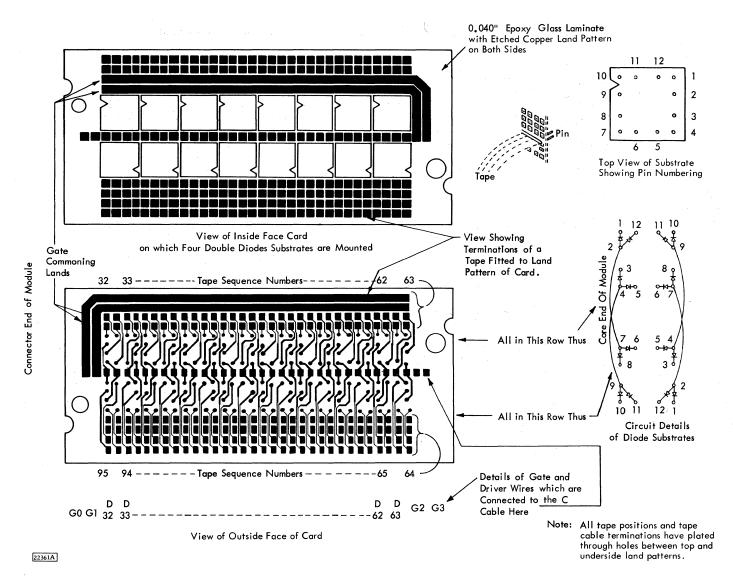

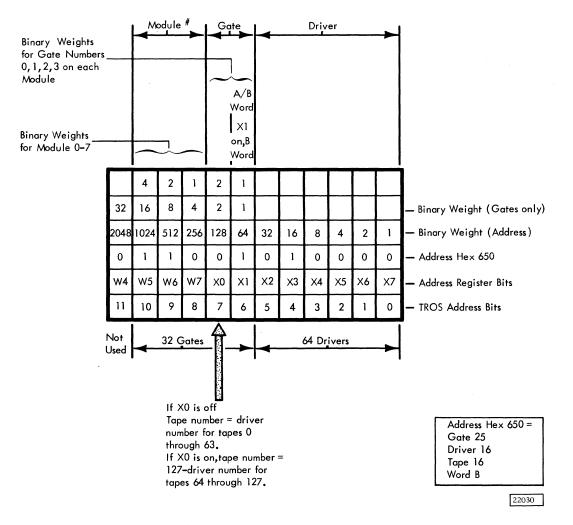

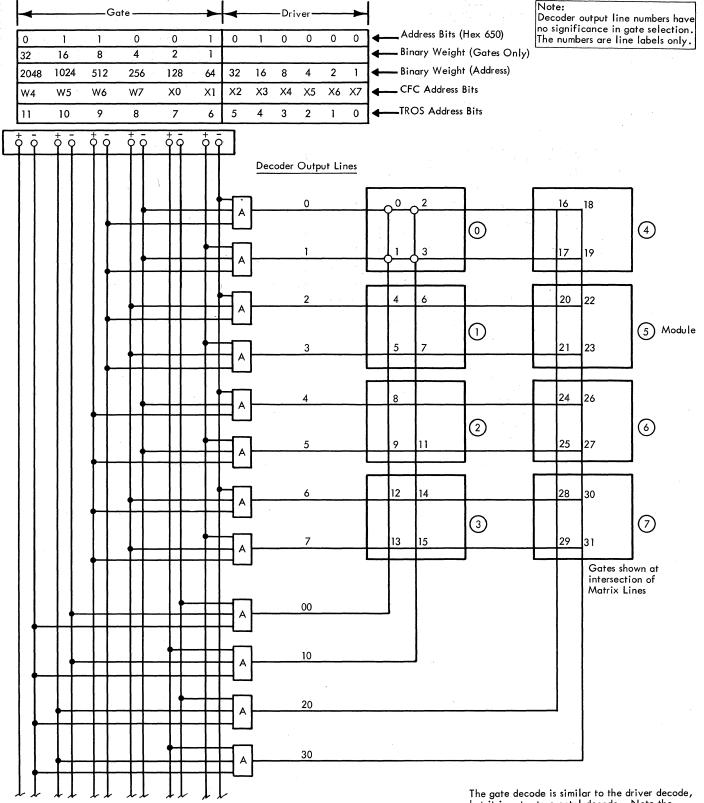

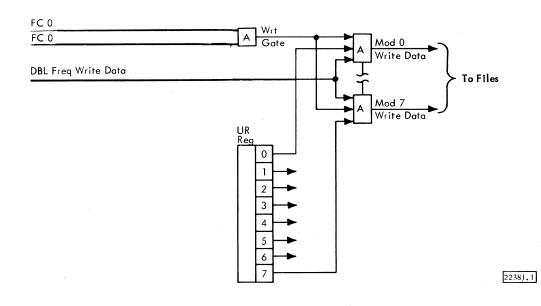

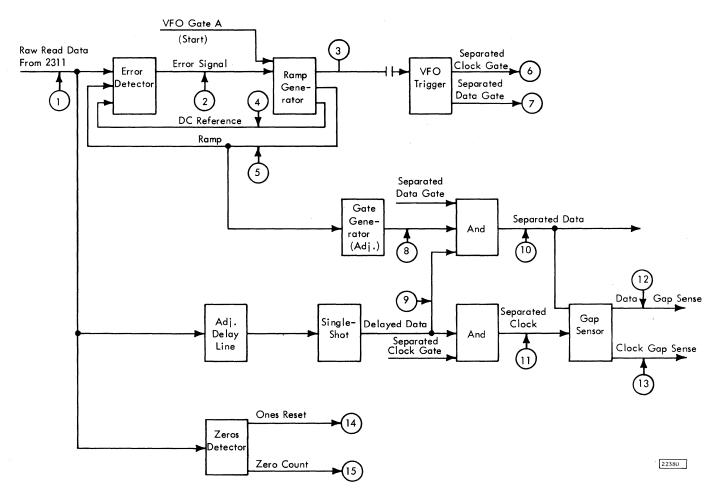

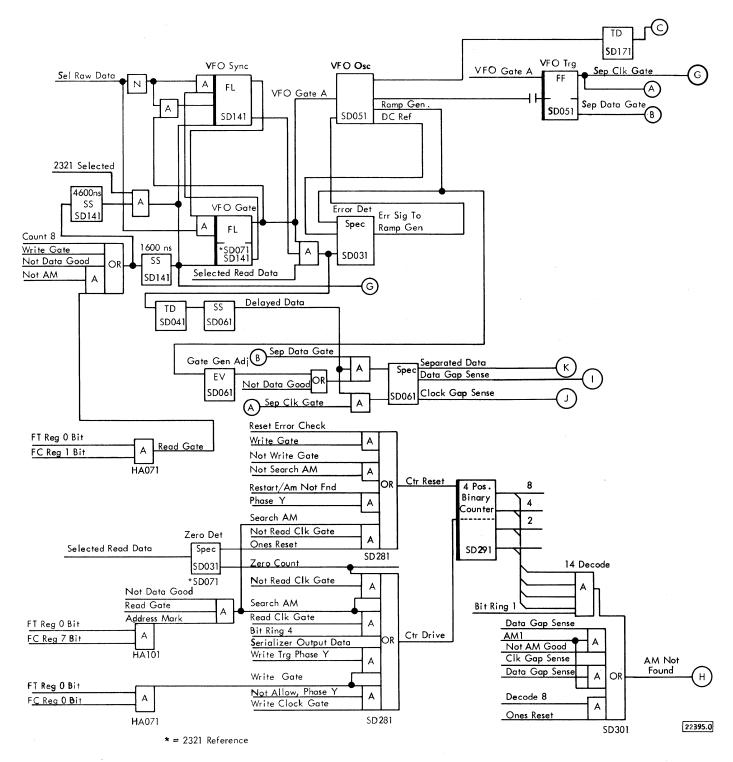

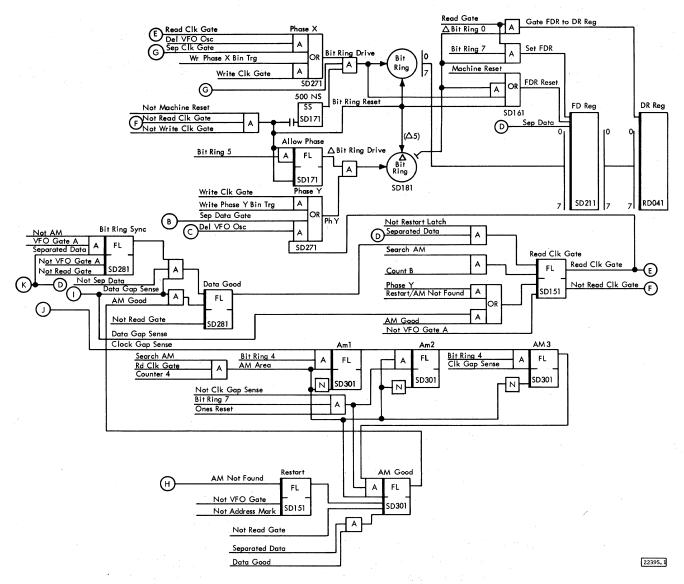

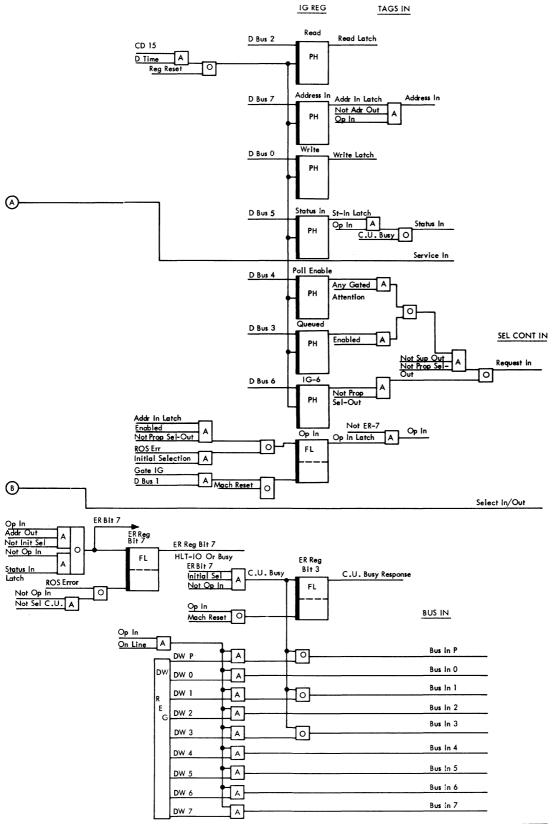

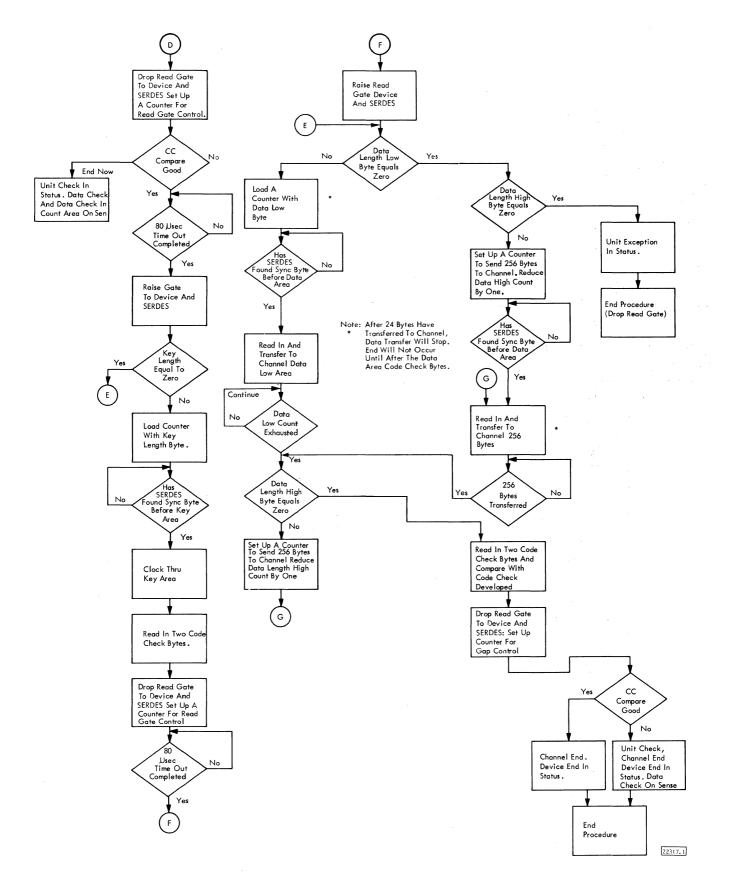

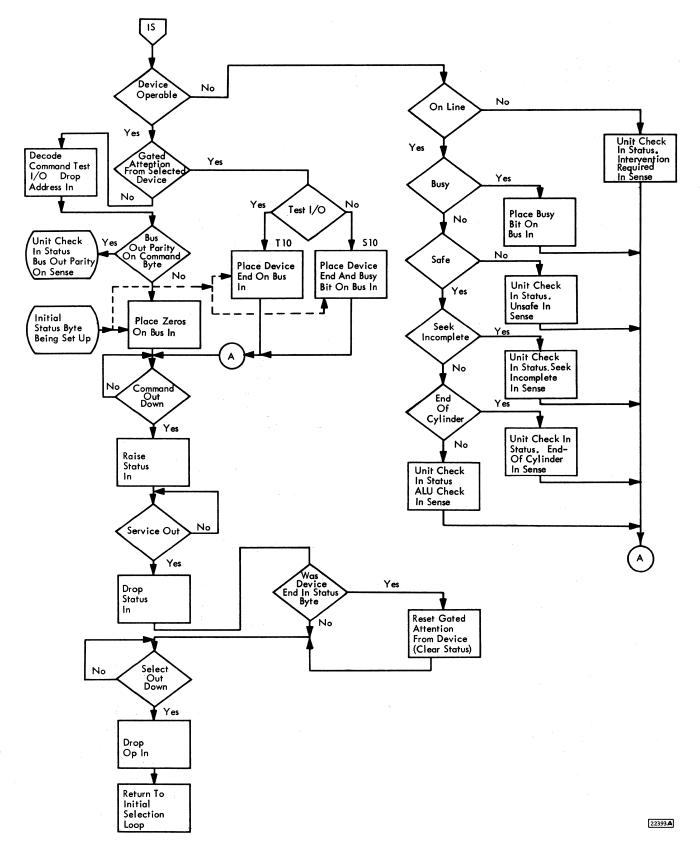

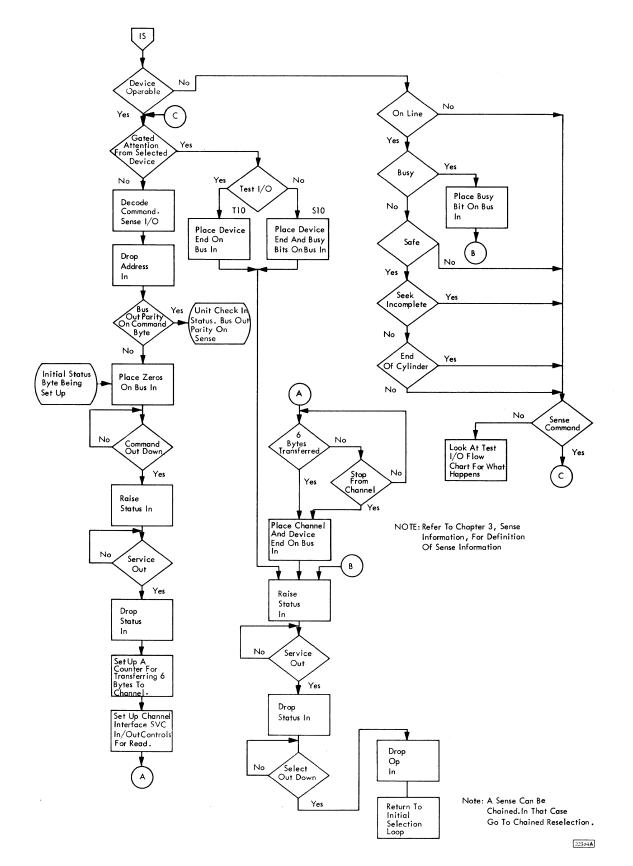

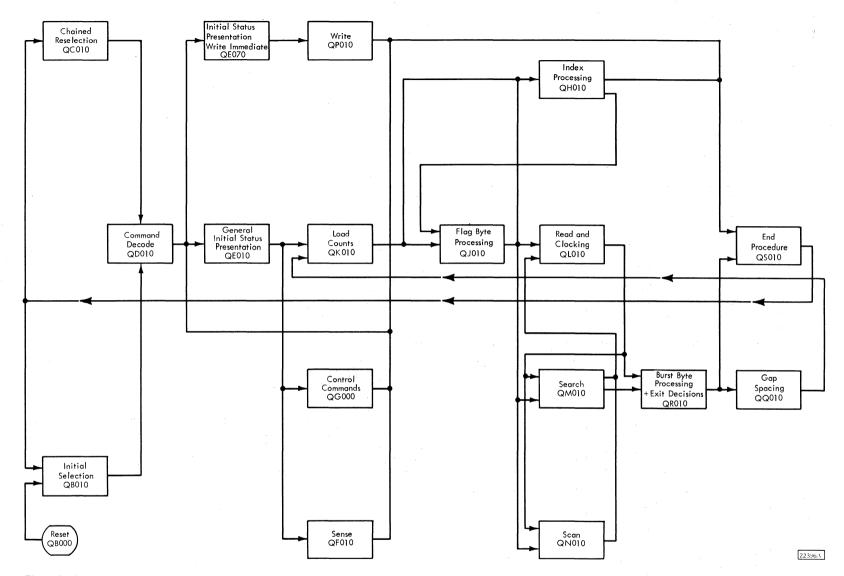

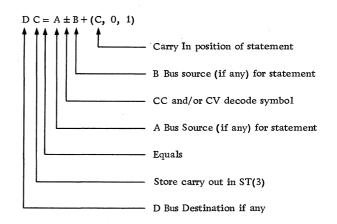

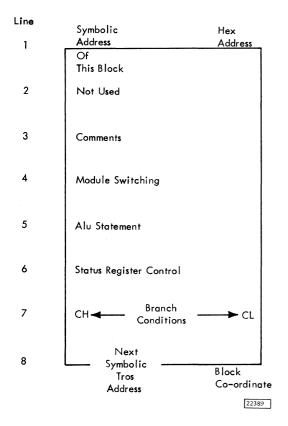

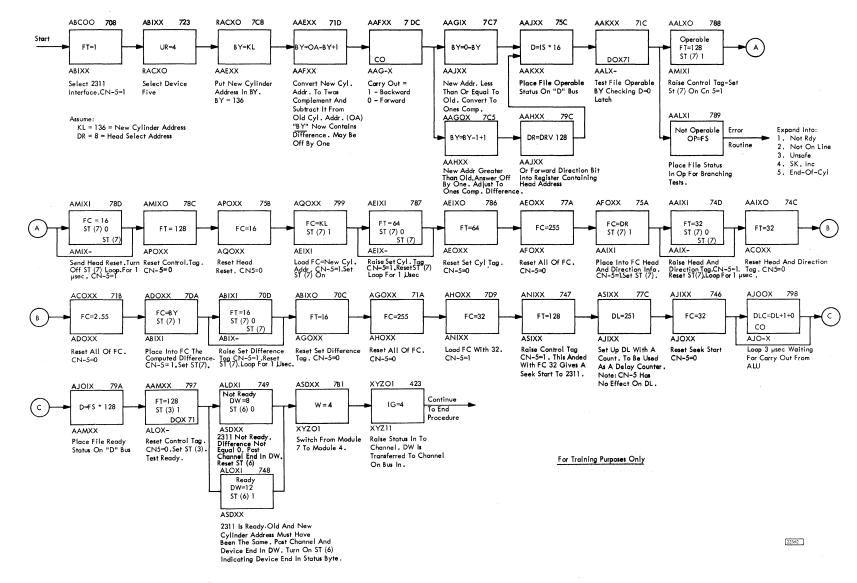

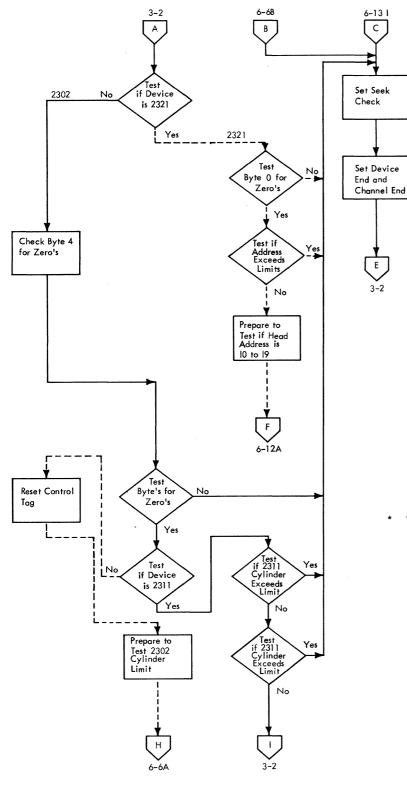

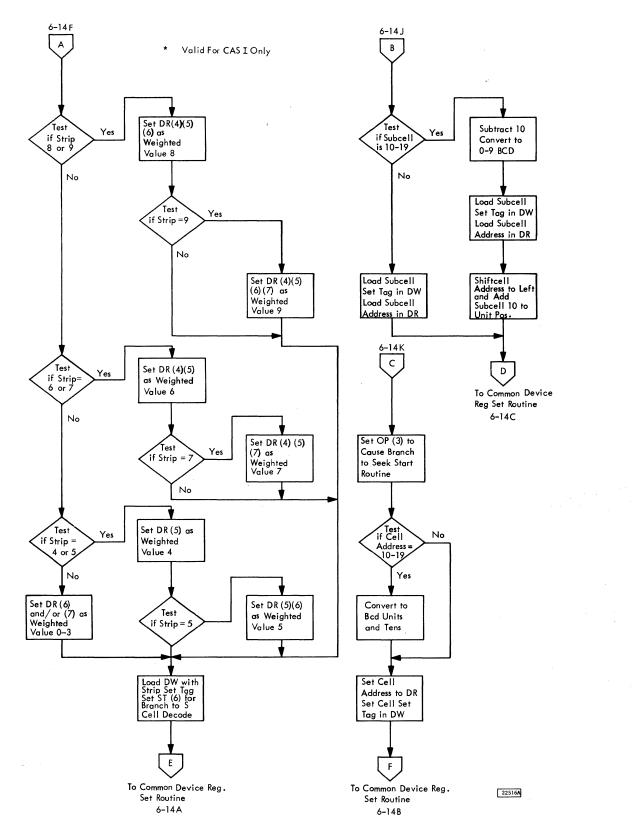

- An operation is completed when the control unit and device present ending status to the channel.