# IIBM Field Engineering Maintenance Manual

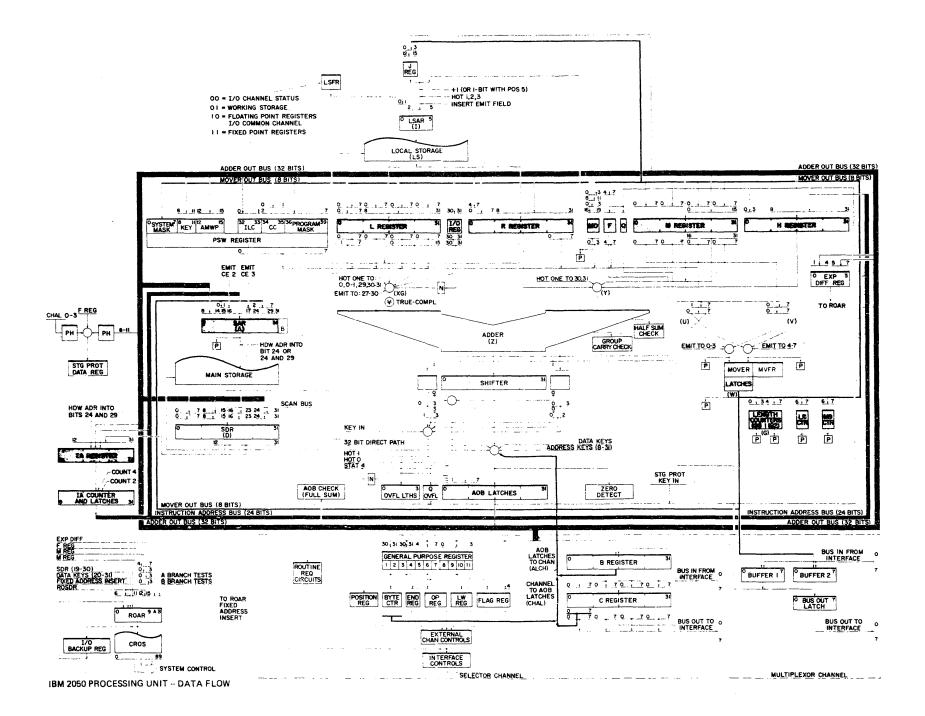

System/360 Model 50 2050 Processing Unit

## PREFACE

To obtain the most benefit from this manual, the reader should have a basic knowledge of System/360 concepts and general programming, and a working knowledge of the logical and physical operation of the 2050 Processing Unit. The manual includes diagnostic aids, maintenance features, and maintenance procedures along with reference material that will aid in troubleshooting and maintaining the System/360 Model 50.

Other Field Engineering Manuals written for the System/360 Model 50 include:

| Comprehensive Introduction, FETOM       | SY22-2821 |

|-----------------------------------------|-----------|

| Functional Units, FETOM                 | SY22-2822 |

| Capacitor Read-Only Storage, FETOM      | SY22-2823 |

| RR, RX Instructions, FETOM              | SY22-2824 |

| RS, SI, SS Instructions, FETOM          | SY22-2825 |

| Selector Channel, Common Channel, FETOM | SY22-2826 |

| Multiplexor Channel, FETOM              | SY22-2827 |

| Main Storage, Local Storage, Storage    |           |

| Protection, FETOM                       | SY22-2828 |

| Power Distribution and Control, FETOM   | SY22-2829 |

| Features, FETOM                         | SY22-2830 |

| 2050 Processing Unit, FEMDM             | SY22-2833 |

| 2050 Processing Unit, FEIM              | SY22-9501 |

#### Fifth Edition (March 1971)

This is a major revision of, and obsoletes, SY22-2832-3. Maintenance strategy diagrams have been revised, expanded, and placed in the 2050 FEMDM. All CPU timing information has been removed from this manual and placed in the ALD's, Volume 1, Page AA000. Other changes or additions to text and illustrations are indicated by a vertical line to the left of the change.

Changes are periodically made to the specifications herein; any such changes will be reported in subsequent revisions or FE Supplements.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B96, PO Box 390, Poughkeepsie, N.Y. 12602. A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be sent to the above address.

# CONTENTS

| DIAGNOSTIC TECHNIQUES                        |   |   |   |    | 11       |

|----------------------------------------------|---|---|---|----|----------|

| Maintenance Philosophy                       | • |   | • | •  | 11       |

|                                              | • | • | • | ٠  | 11       |

| Deferred Maintenance                         | • | • | • | •  | 11       |

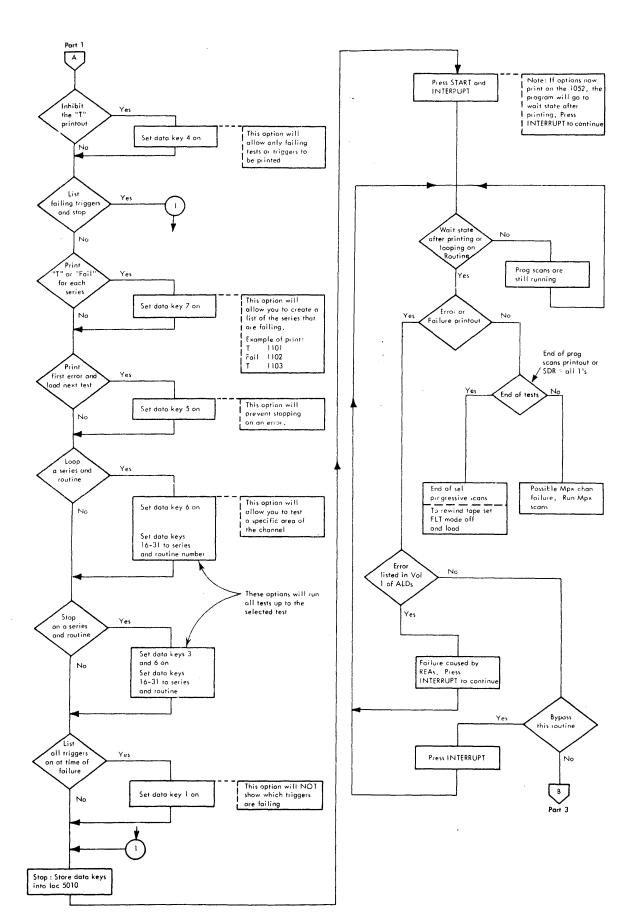

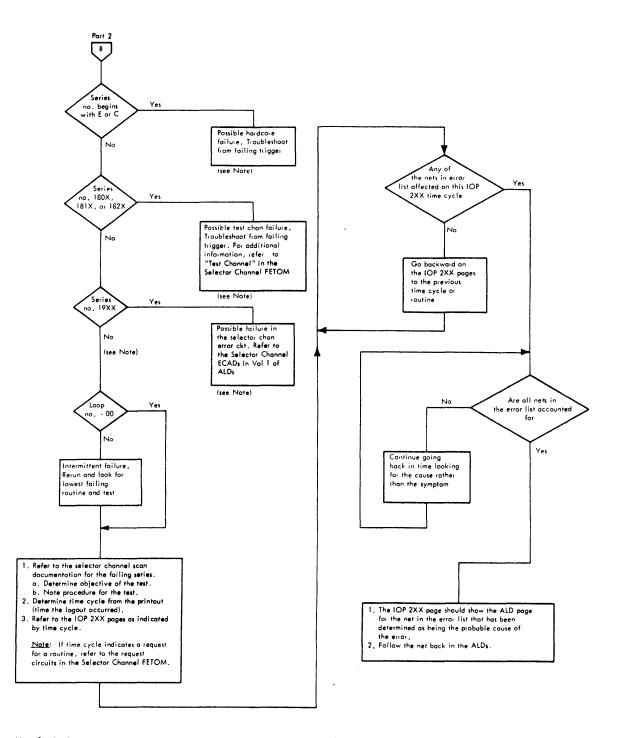

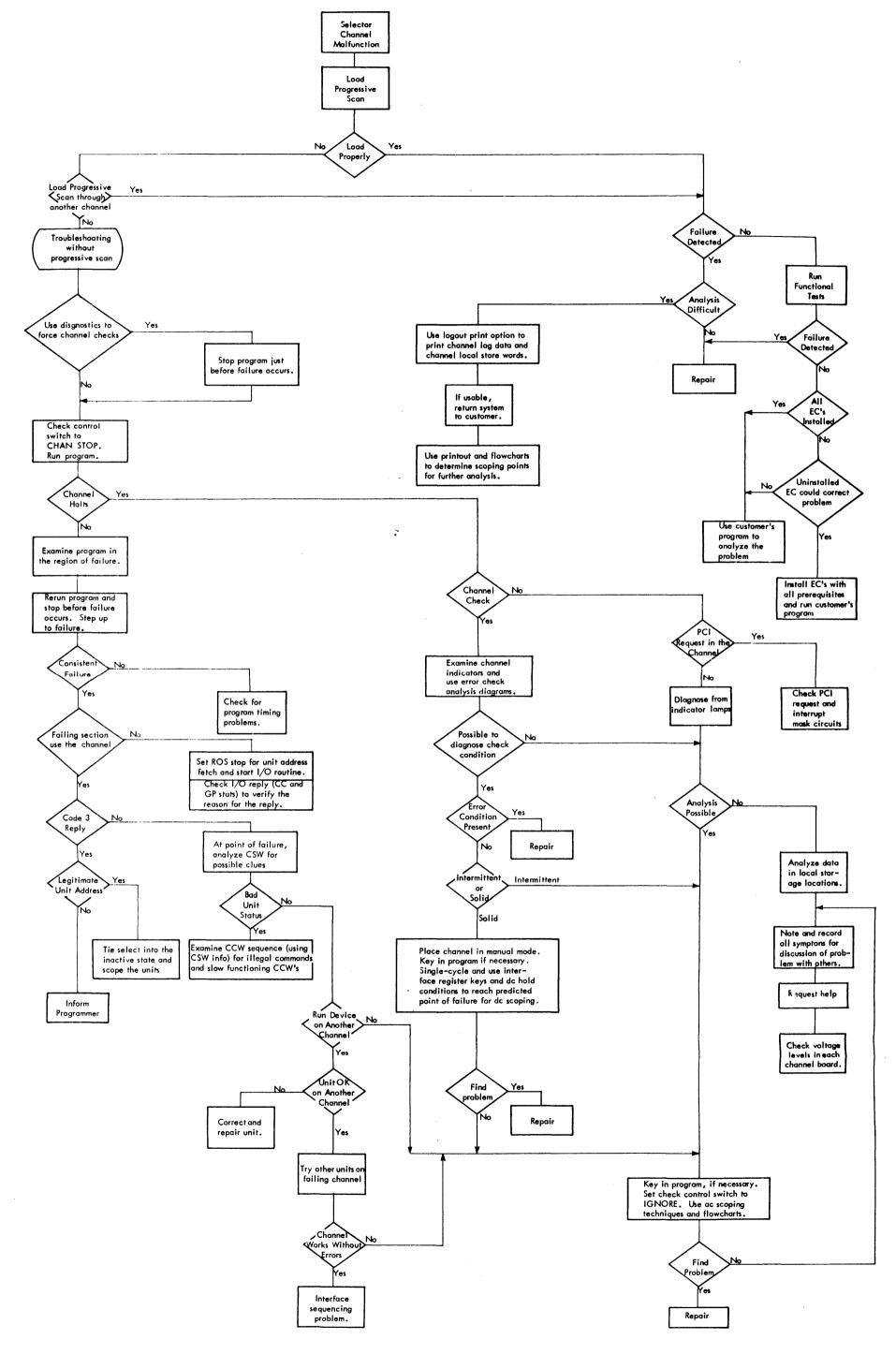

| Troubleshooting Flowcharts                   | • | • | ٠ | •  | 11       |

|                                              | • | ٠ | ٠ | •  | 12       |

| Loading Faults                               | • | • | • | •  | 12       |

| Programming Faults and Error Stops           | • | • | ٠ | •  | 12       |

|                                              | • | • | • | ۰. | 12       |

| Error Check Analysis Diagrams                |   | • |   | •  | 12       |

| Service Aids                                 | • |   | • | •  | 12       |

| ALD Page Key                                 | • |   | • | •  | 12       |

|                                              | • |   | é | •  | 13       |

| Optional Feature Version Codes               | • |   | ٠ | •  | 13       |

| Diagnostic Mode Codes                        |   | • | • | •  | 13       |

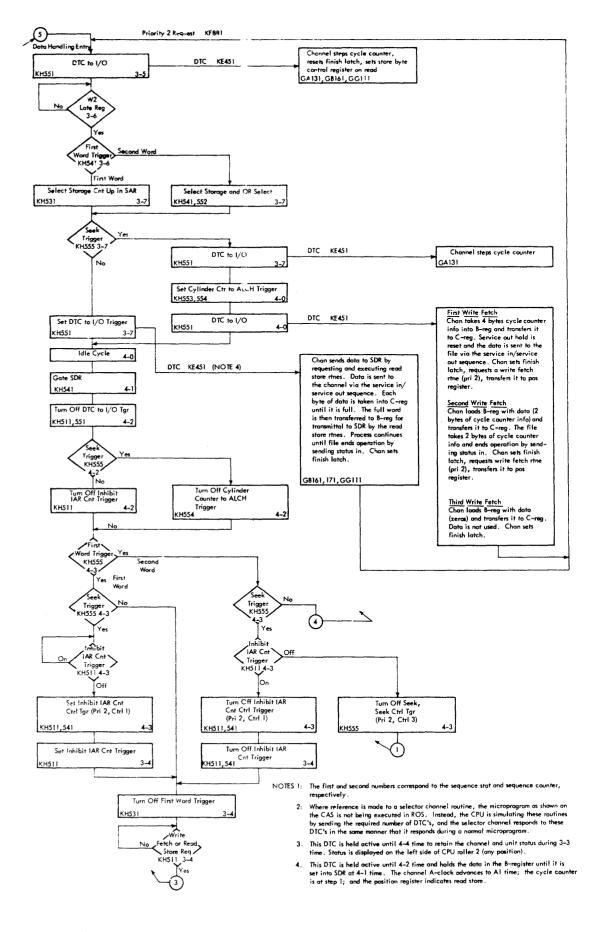

| Selector Channel Error Handling              |   |   | • |    | 15       |

| Interface Control Check                      |   |   | • |    | 15       |

| Channel Control CheckChannel Detected .      |   |   |   |    | 15       |

| Channel Control CheckCPU Detected            |   |   |   |    | 15       |

| Program, Storage-Protect, and Chaining Check |   |   |   |    | 15       |

| Data Check                                   |   |   |   |    | 16       |

| SIM Check                                    |   |   |   |    | 16       |

| Incorrect Length Indication (ILI)            |   |   |   |    | 16       |

| Error Priority.                              |   |   |   |    | -        |

|                                              |   |   |   |    |          |

| MAINTENANCE FEATURES                         |   |   |   |    | 18       |

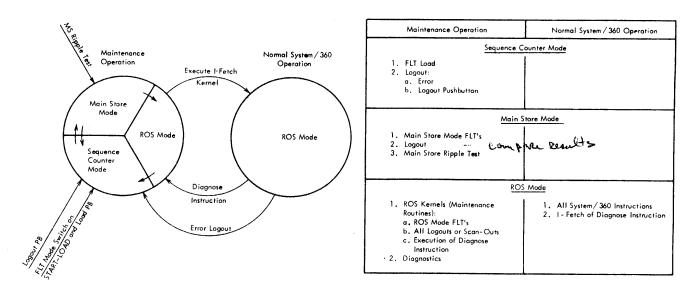

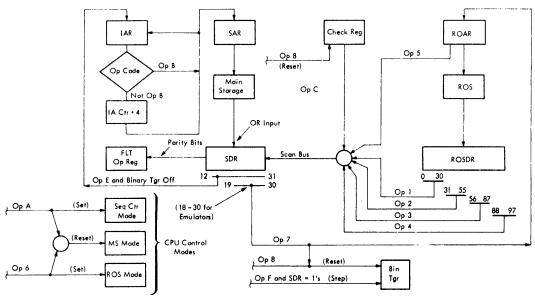

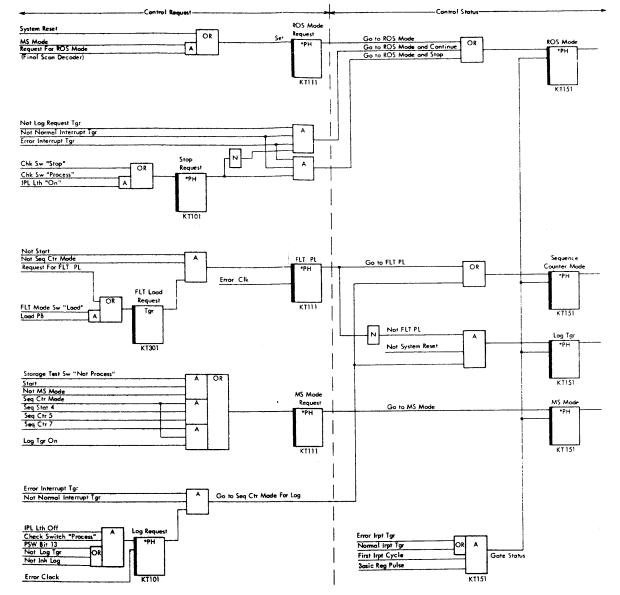

| CPU Control Modes                            |   |   |   |    | 18       |

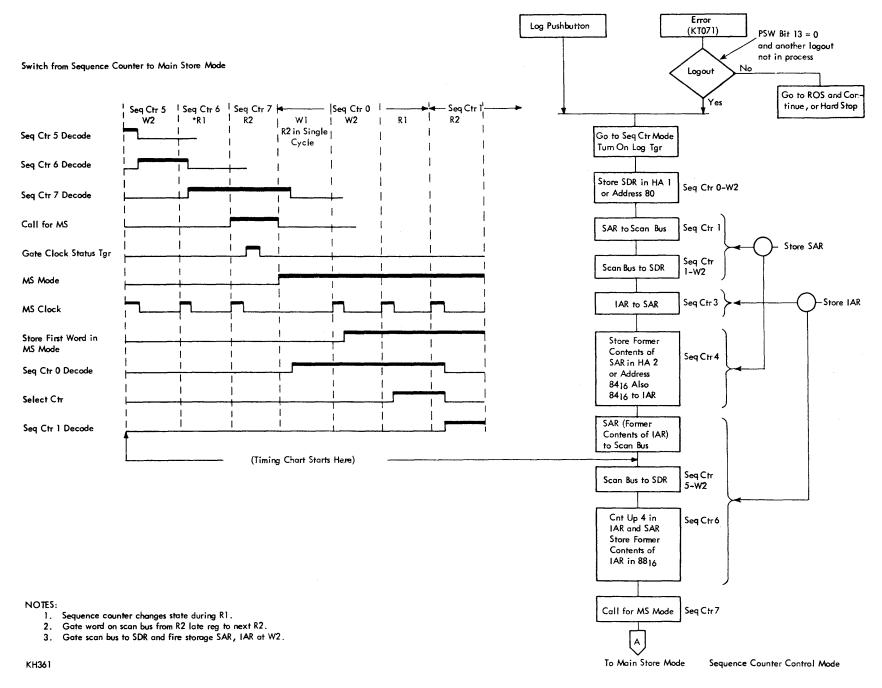

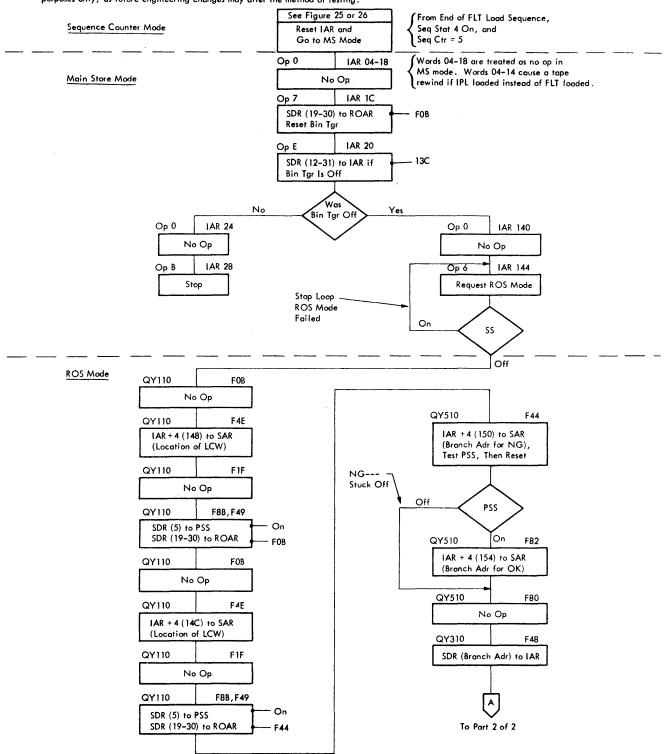

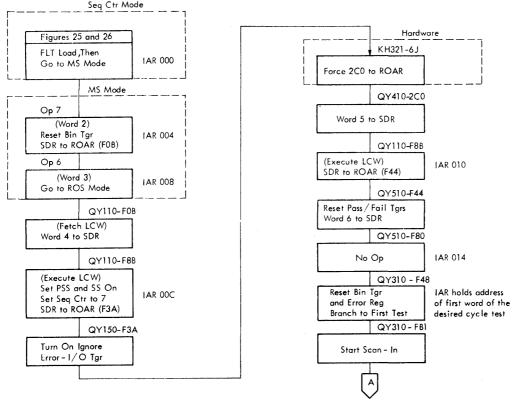

| Sequence Counter Mode                        |   |   |   |    | 18       |

| Main Store Mode                              |   |   |   |    | 20       |

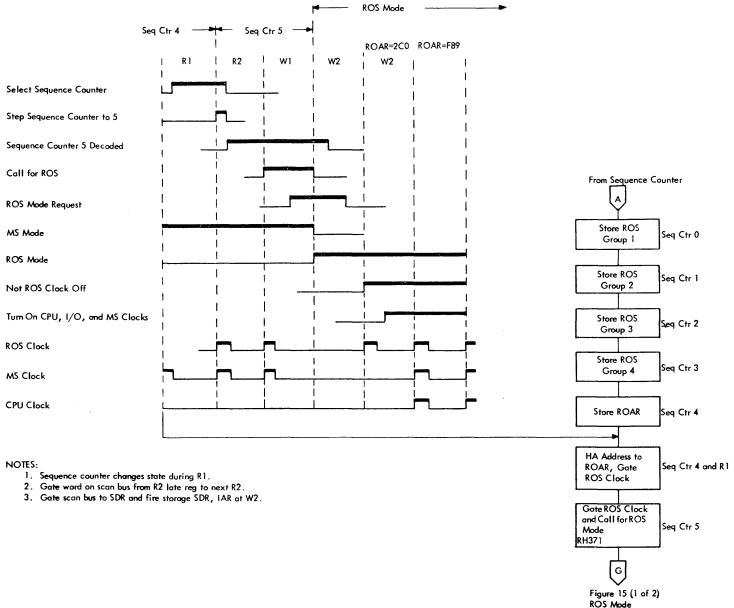

| ROS Mode                                     |   |   |   |    | 20       |

| FUNCTIONAL UNITS.                            |   |   |   |    | 21       |

|                                              |   |   |   |    | 21       |

| Sequence Stats                               |   |   |   |    | 21       |

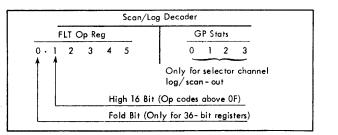

| FLT Op Reg                                   |   |   |   |    | 21       |

|                                              |   |   | • |    | 21       |

| ROS Kernels                                  |   |   |   |    | 21       |

|                                              |   |   |   |    | 32       |

| Supervisory Stat                             |   |   |   |    | 32       |

| Progressive Scan Stat.                       | ÷ |   |   |    | 32       |

| Supervisory Enable Storage Stat              |   |   |   |    | 32       |

| Binary Trigger                               |   |   |   |    | 32       |

| Scan Test Counter                            |   |   |   |    | 32       |

| Pass/Fail Triggers                           |   |   |   |    |          |

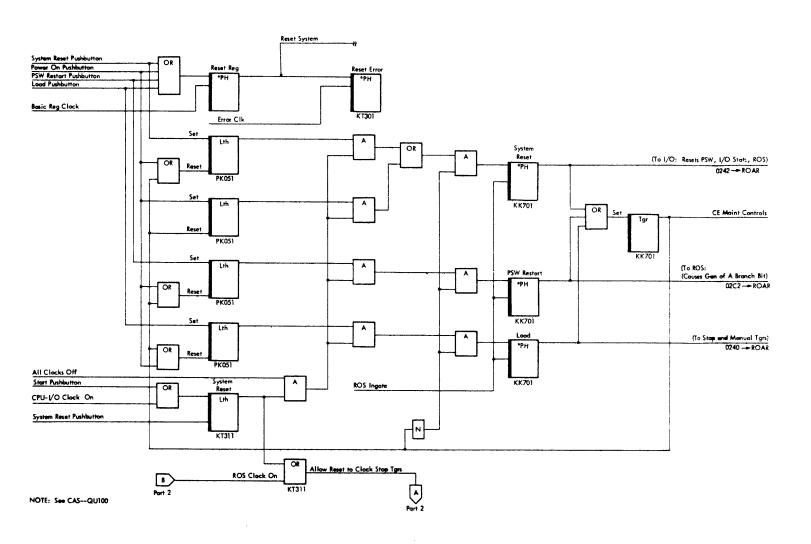

| SUPERVISORY CONTROLS                         |   |   |   |    | 35       |

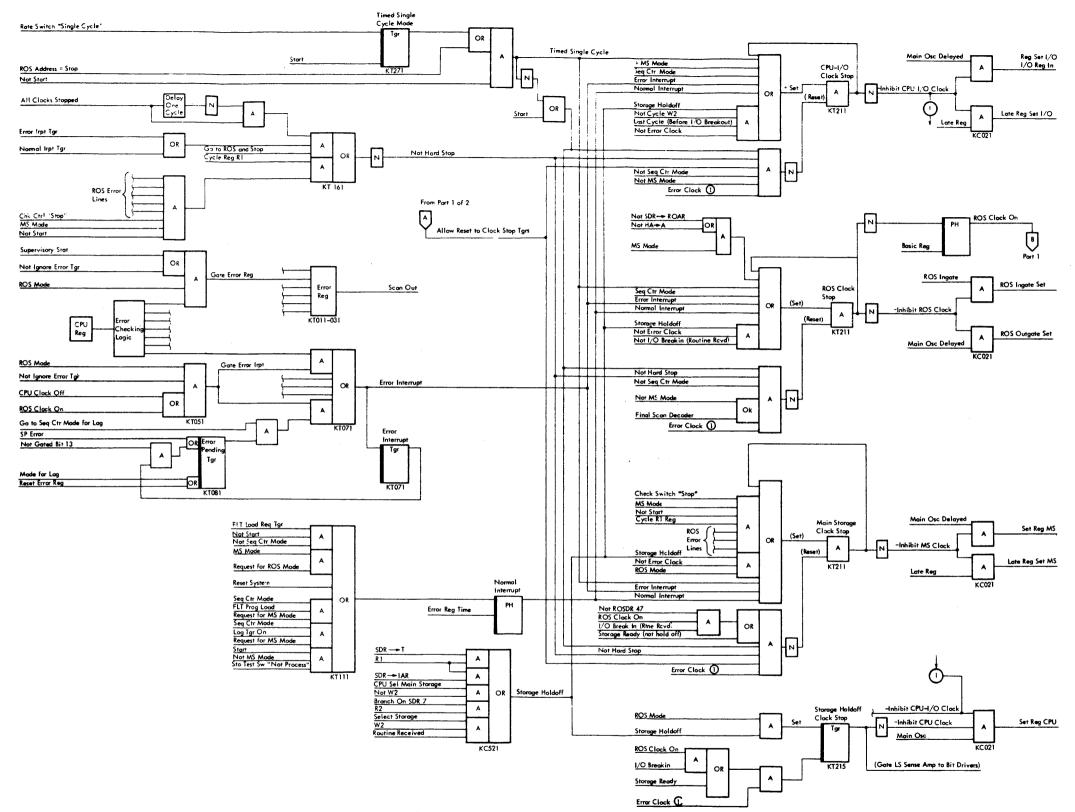

| Clock Gating Control Circuits                | ÷ |   |   |    |          |

| CPU Control Status Circuits.                 | • | • |   | •  | 35       |

| Changing CPU Control Status                  |   | • |   | ÷  | 35       |

| Supervisory Interrupts.                      | • | • | · |    | 35       |

| LINKAGE CONTROL WORD.                        | : |   | : | :  | 40       |

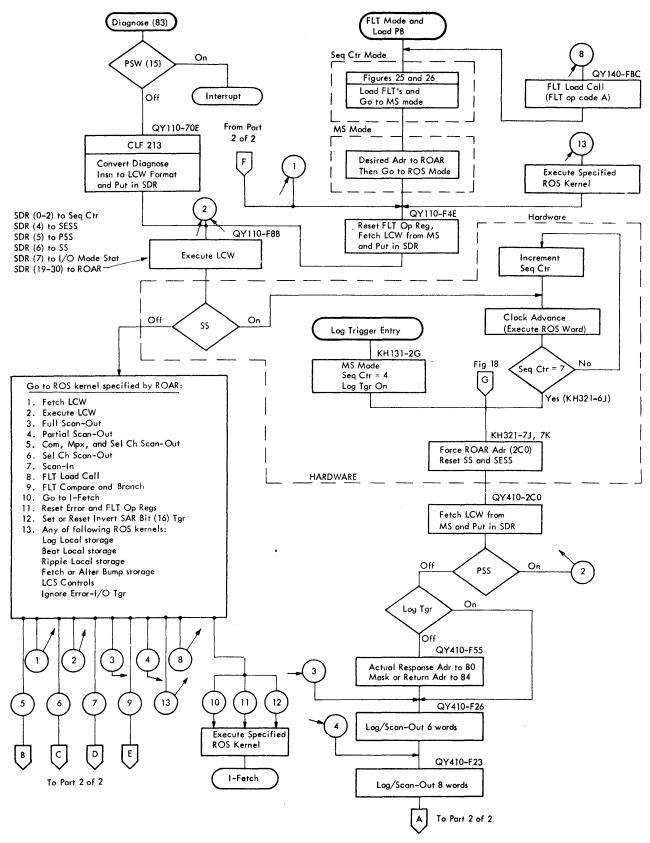

| DIAGNOSE INSTRUCTION                         |   | • | • | •  | 40       |

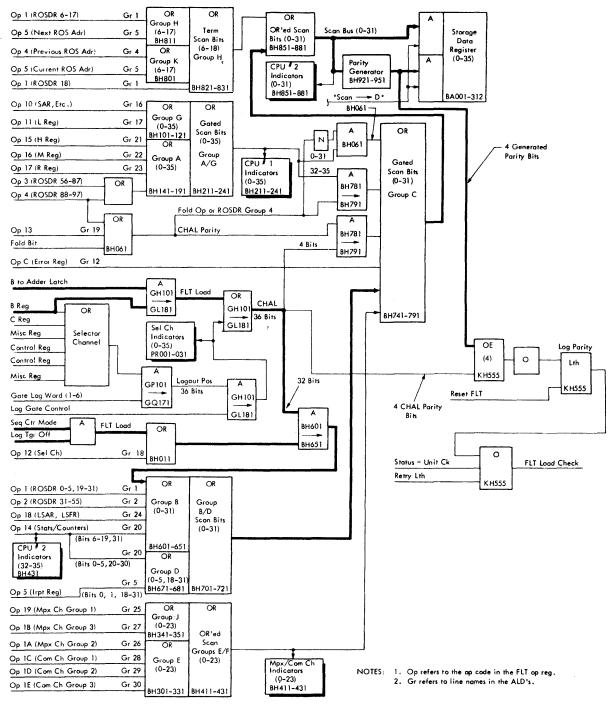

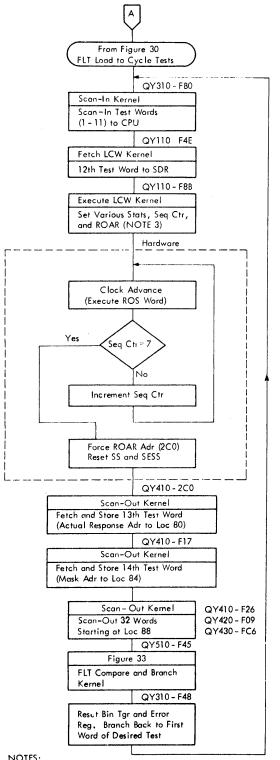

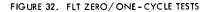

| FAULT LOCATING TESTS (FLT's)                 | • | • | : | •  | 41       |

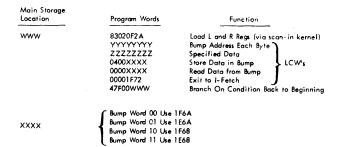

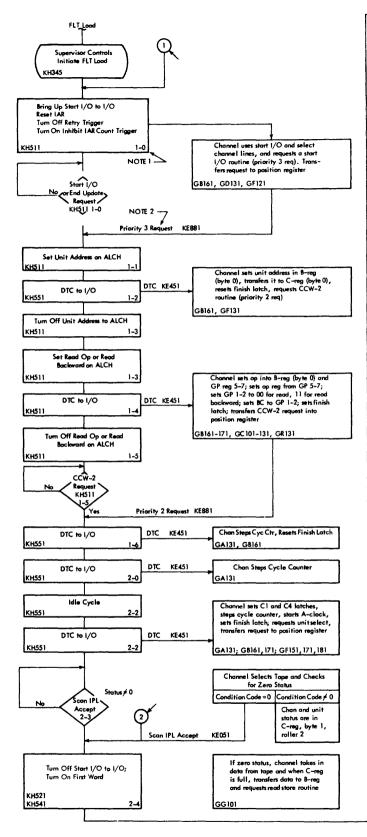

| FLT Load                                     | : | : | : |    | 42       |

| - · · · -                                    |   |   | • | •  | 42       |

|                                              | • | • | • | •  | 45       |

|                                              | • | • | • | •  | 45<br>45 |

|                                              |   |   | · | •  | 45<br>45 |

|                                              |   |   | • | •  | 45<br>45 |

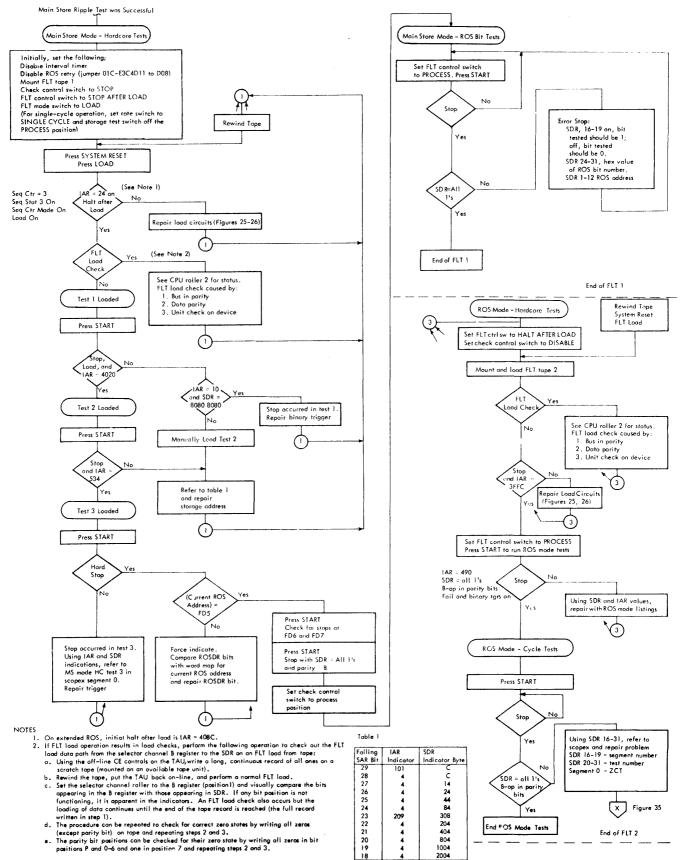

| Main Store Mode FLT's                        |   |   | • | •  | 45<br>46 |

| MG MOUE HARDOFE LESIS                        | • | • | • | •  | -#0      |

| FLT Load Checking Program                    |      |   |   |   | 46        |

|----------------------------------------------|------|---|---|---|-----------|

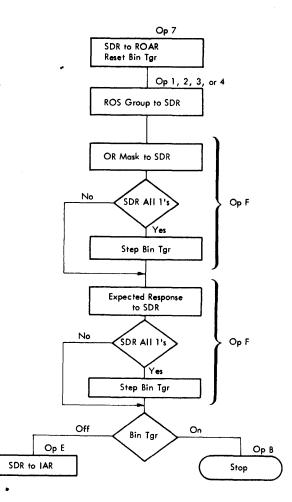

| Test Methods (Mask and Expected Response)    |      |   |   |   | 46        |

| MS Mode ROS Bit Tests                        |      |   |   |   | 47        |

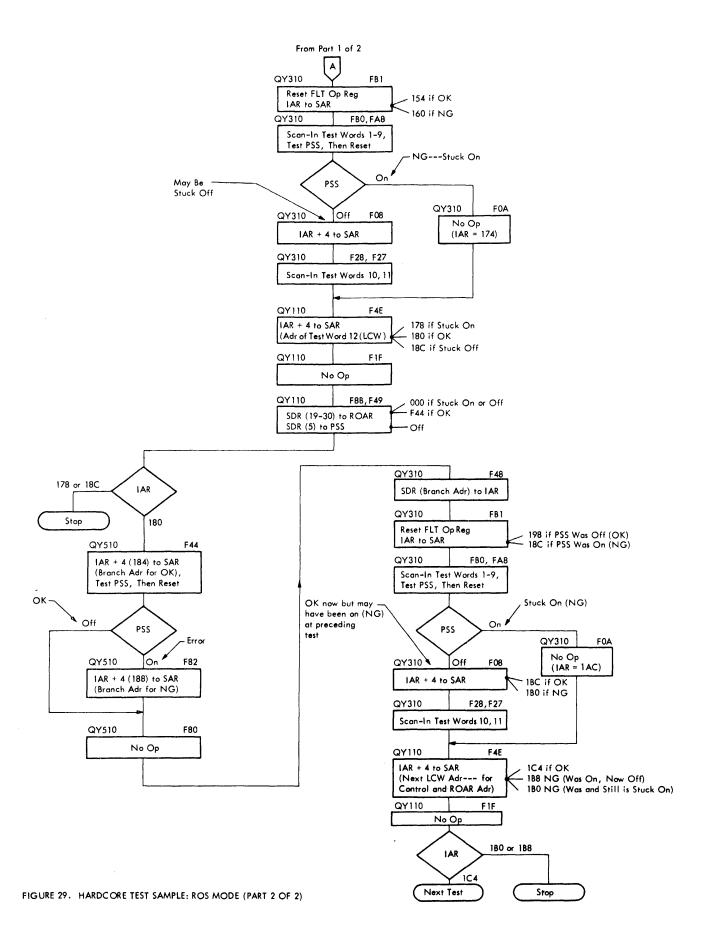

| ROS Mode FLT's                               | •••• |   |   |   | 48        |

| ROS Mode Hardcore Tests                      |      |   | • |   | 48        |

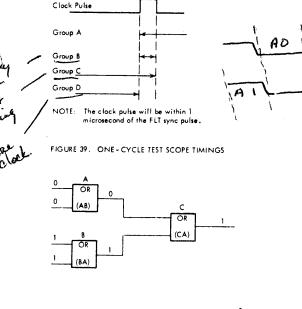

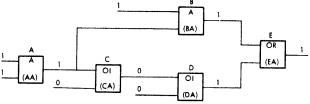

| ROS Mode Zero/One-Cycle Tests                |      |   |   |   | 51        |

| Zero/One-Cycle Test Methods                  |      |   |   |   | 51        |

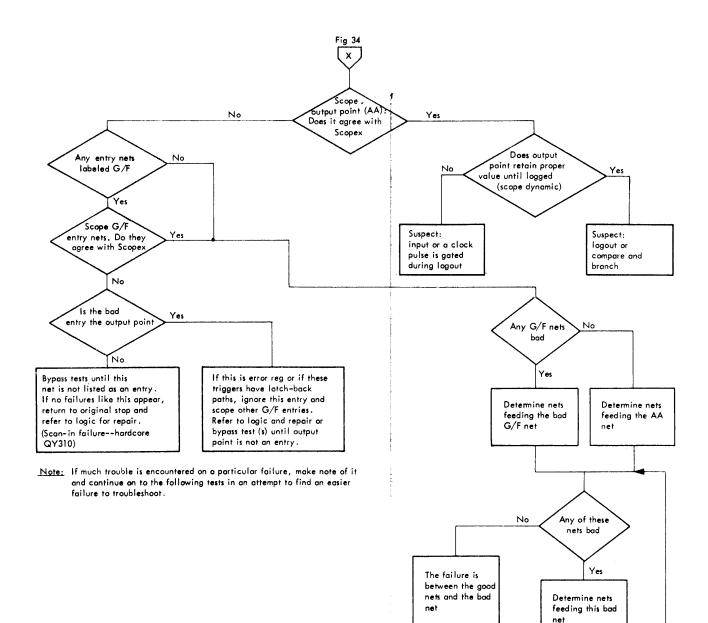

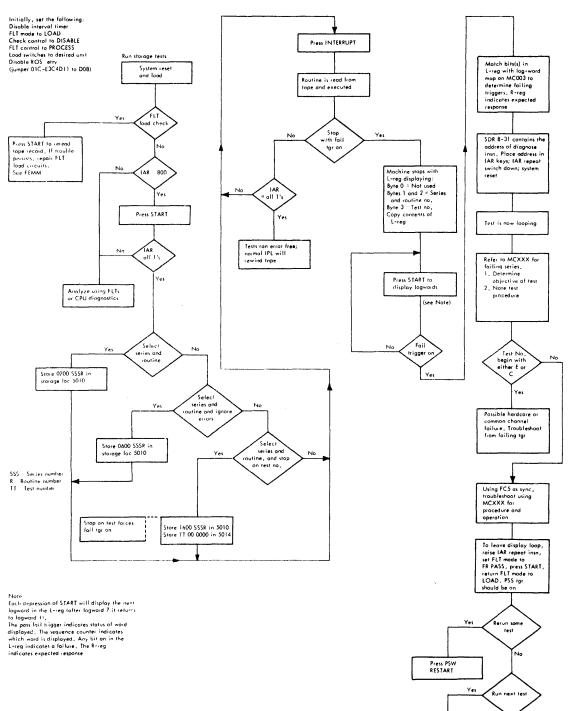

| FLT Operating/Repair Procedures              |      |   |   |   | 53        |

| Main Storage Ripple Test                     |      |   |   |   | 56        |

| Skipping Bad FLT Records                     |      |   |   |   | 57        |

| Disk (FLT) Operating Procedures              |      |   |   |   | 57        |

| Cycle Test Repair Procedures (Tape/Disk)     |      |   |   |   | 58        |

| Checkout After Repair                        |      |   |   |   | 61        |

| FLT Documentation                            |      |   |   |   | 61        |

|                                              | ·    | • | • |   |           |

| PROGRESSIVE SCAN                             |      |   |   |   | 63        |

|                                              |      |   |   |   | 63        |

| Test Patterns                                |      |   |   |   | 71        |

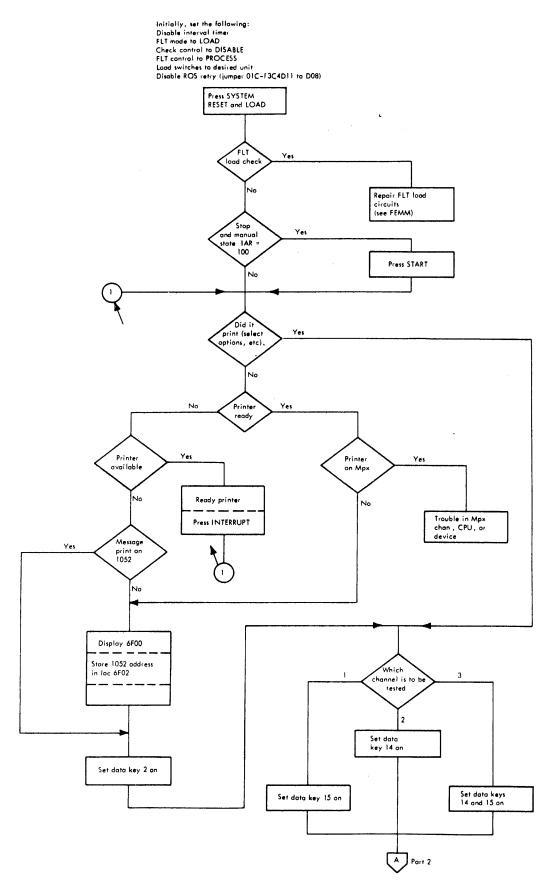

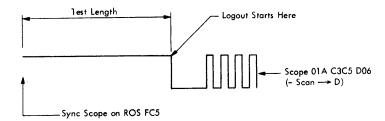

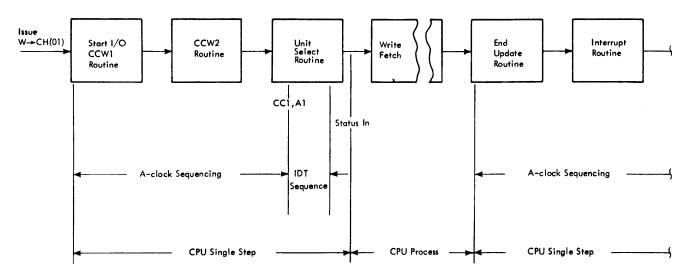

| Selector Channel Tape or Disk                |      |   |   |   | 71        |

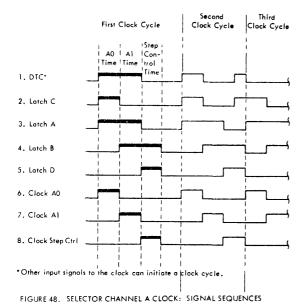

| Selector Channel Clock Control               |      |   |   |   | 71        |

| Selector Channel Operating Procedure Example |      |   |   |   | 72        |

| Selector Channel Test Documentation          |      |   |   |   | 72        |

| Selector Scan Monitor                        | :    |   |   |   | 74        |

| Multiplexor Channel Tape or Disk             |      |   |   |   | 74        |

| Multiplexor Channel Operating Procedure      | :    | : | : |   | 74        |

| Multiplexor Channel Test Documentation       |      |   | : |   | 74        |

|                                              |      | • | • | • | 74        |

|                                              | •    | • | • | • | 74        |

|                                              | •    | • | • | • | 74        |

|                                              | ٠    |   |   | • | 75        |

|                                              | ٠    | • | • | • | 76        |

|                                              | •    | • | • | • | 76        |

| Marginal Voltage Limits                      | •    | • | • | • | 76        |

| Marginal Checking Procedure                  |      | • | • | • | 76        |

| Error Checking                               | ·    | • | • | • | 76        |

| Identification                               | ٠    | • |   | • | 76        |

| Failure Detection Facilities                 | •    | • | · | • | /0        |

|                                              |      |   |   |   | 79        |

| PREVENTIVE MAINTENANCE                       | •    | • | • | • | 79        |

| Lamp Te <b>st</b>                            |      |   | • | • | 79<br>79  |

| Diagnostics                                  | ٠    | • | • | • | /9        |

| SERVICE CHECKS, ADJUSTMENT AND REMOVAL       |      |   |   |   |           |

|                                              |      |   |   | • | 80        |

| PROCEDURES                                   |      |   |   | • | 80        |

|                                              | •    | • | • | • | 80        |

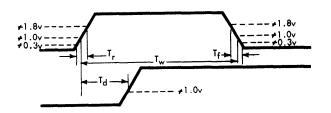

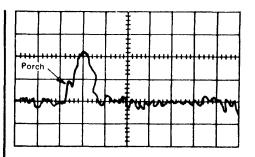

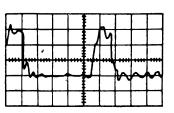

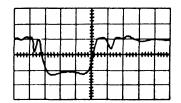

| Waveform Measurements                        | •    | • | · | • | •••       |

|                                              | •    | • | • | • | 80        |

| MAIN STORAGE (MS) SERVICE CHECKS             | •    | • | • | • | 80<br>80  |

| Storage Test                                 | •    | · | • | • |           |

| Main Storage Test Points                     | •    | • | · | • | 80        |

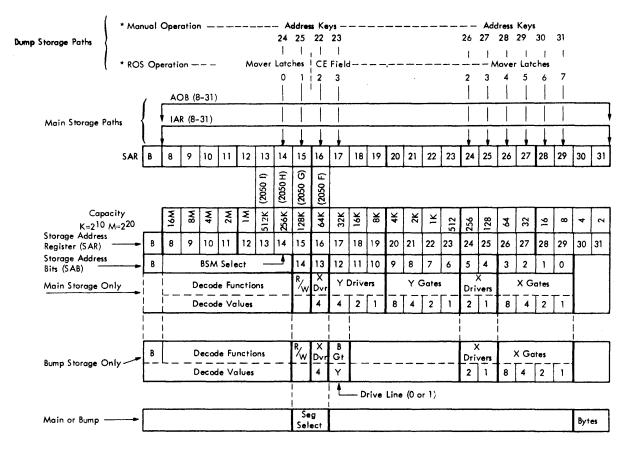

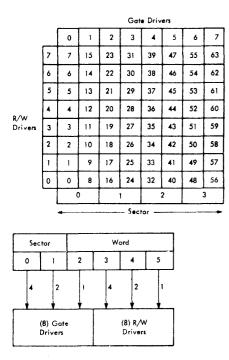

| Main Storage Addressing                      | •    | • | • | • | 81<br>81  |

| Main Storage Temperature and Humidity        | •    | • | • | • |           |

| Main Storage Power Information               | •    | • | • | • | 81        |

| Exercise Bump Storage                        | •    | • | • | • | 82        |

| Continually Address One MS Location          | •    | • | • | • | 82<br>° 7 |

| Scan MS for Bad Parity                       | •    | • | • | • | 82        |

| Bit Arrangement of MS Word                   | •    | • | • | • | 82        |

| Check Strobe of Main Storage                 | •    | • | • | • | 82        |

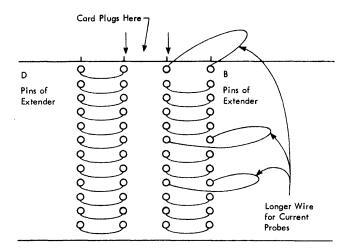

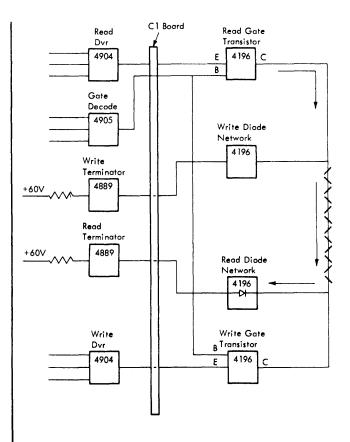

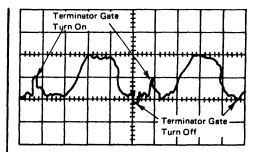

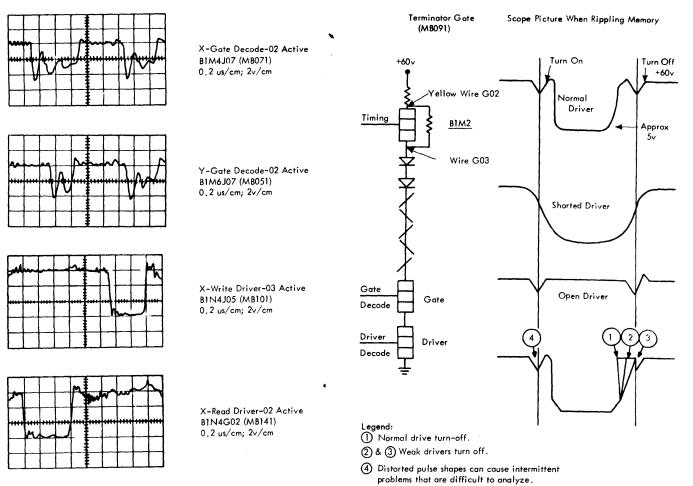

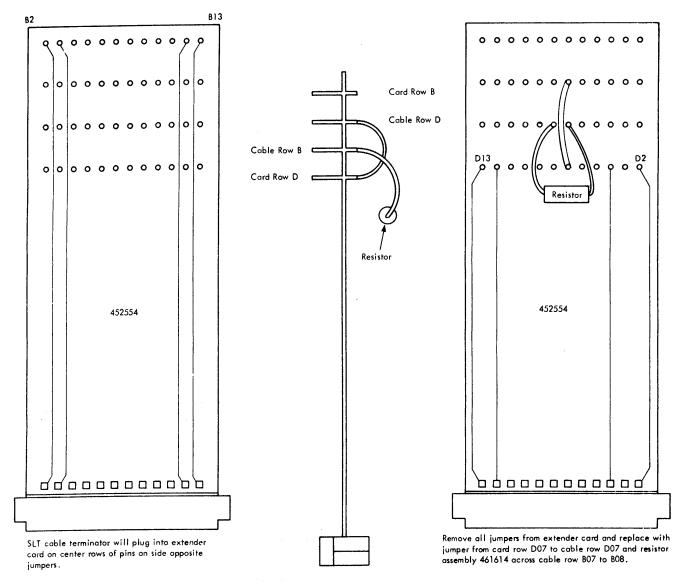

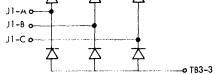

| Checking MS Drivers and Terminating Diodes . | •    | • | • | • | 83        |

÷

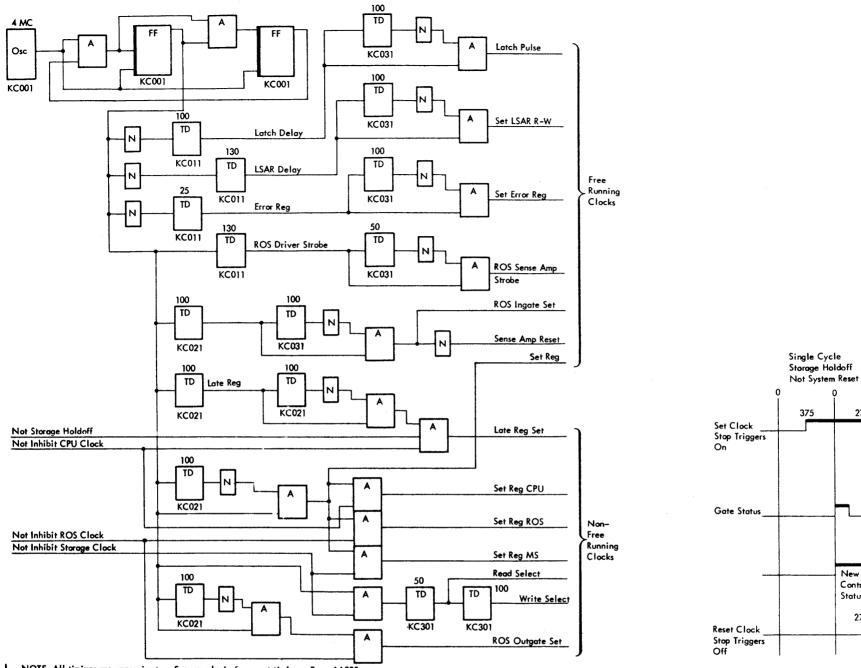

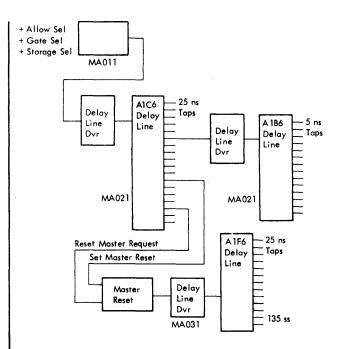

| Delay Line Clock                            | • | • | • | • | ٠ | 83         | Switch            |

|---------------------------------------------|---|---|---|---|---|------------|-------------------|

| Delay Line Driver                           |   | • | • | • | • | 84         | EMULATO           |

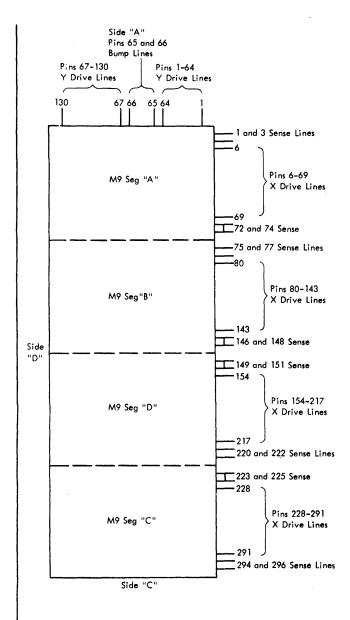

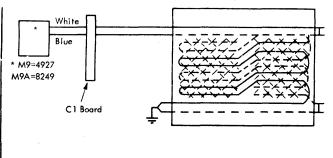

| Layout of M9/M9A Planes                     | • |   | • | • | • | 84         | 1410/701          |

| X Drive Current                             | • | • | • | • | • | 84         | 1410/701          |

| Y Drive Current                             | • | • | • | • | • | 85         | 2302 I            |

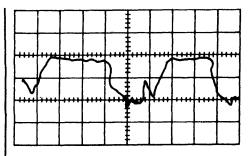

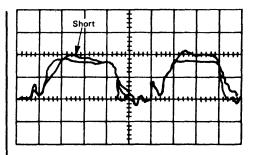

| Shorted X Drive Line                        | • | • | • | • | • | 85         | 2302 7            |

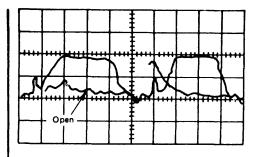

| Open X Drive Line                           |   |   | • | • | • | 85         | 2314 I            |

| Drive Line Shorted to Ground                | • | • | • | • | • | 86         | 2314 7            |

| Sense Inhibit                               | • | • | • | • | • | 87         | 1410/701          |

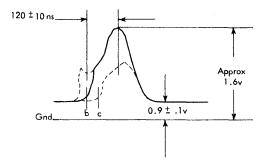

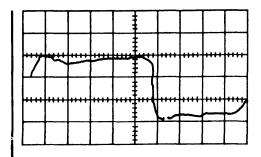

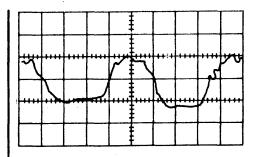

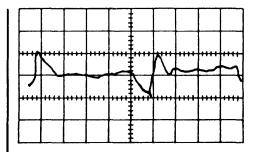

| Storage Waveforms (Voltage Probe)           |   |   | • |   | ٠ | 88         | Start I/O         |

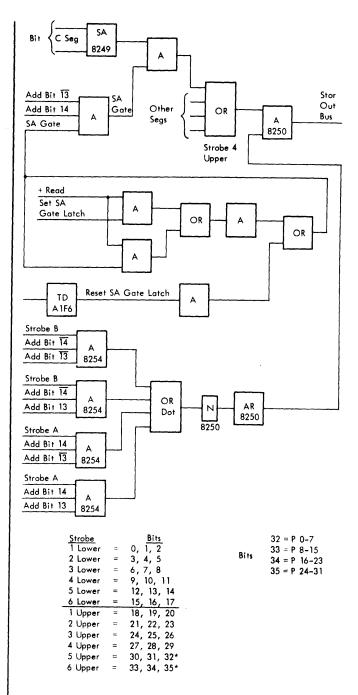

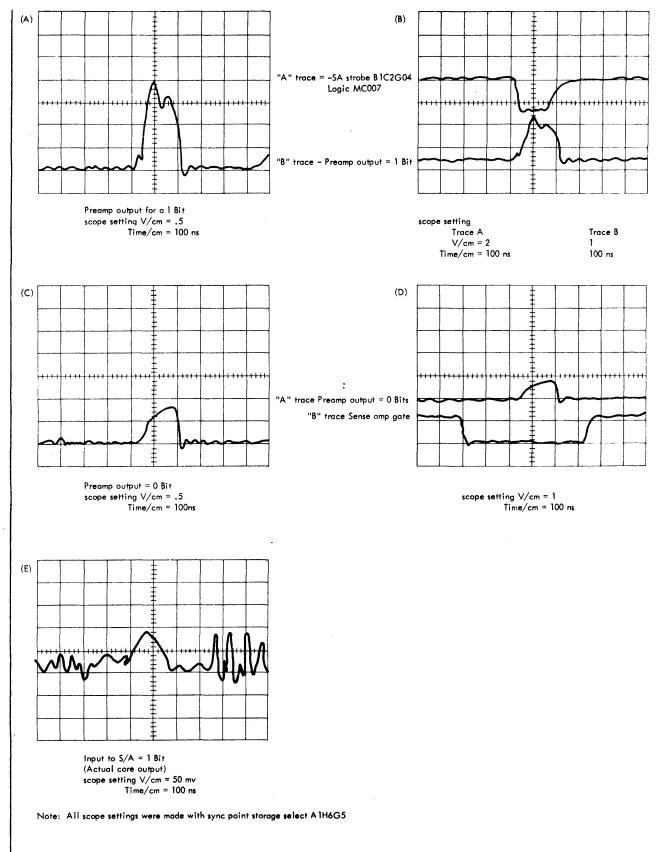

| Sense Amplifier Output (M9)                 |   | • | • | • | • | 88         | 7070/707          |

| M9A Differences                             |   | • |   | • | • | 89         |                   |

| LOCAL STORAGE (LS) SERVICE CHECKS           |   |   |   |   | • | 90         | POWER S           |

| Local Storage Timings                       | • |   | • | • | • | 90         | Conve             |

| LS Read Operations                          | • | • | • | • | • | 90         | SCR C             |

| LS Write Operation                          |   |   | • | • | • | 90         | Types             |

| LS Functional Packaging                     |   |   |   | • |   | 90         | Conve             |

| Local Storage Word Selection                | • | • | • | • | • | 92         | Conve             |

| LS Temperature Control Unit Check           |   |   |   |   |   | 92         | Voltag            |

| Local Storage Waveforms                     | • |   | • | • | • | 92         | Chang             |

| Optimize LS Drive Currents (Shmoo)          | • | • | • | • | • | 93         | Voltag            |

| LS Strobe Driver Identification             | • | • | • | • | • | 95         | Plus 18           |

| ROS 201Cycle One Sector of Local Storage    | • | • | • | • | • | 95         | Overcu            |

| Array Temperature                           | • | • | • | • | • | 95         | Voltag            |

| Local Storage Heater                        | • | • | • | • | • | 95         | Overvo            |

| Checking Drivers and Terminating Diodes.    |   |   |   |   |   | 95         | Low Vo            |

| READ ONLY STORAGE (ROS) SERVICE CHECKS      | • | • | • | • | • | 95         | Power             |

| Ros Retry Adjustment                        |   |   |   |   |   | 95         | Dual o            |

| ROS Waveforms                               |   |   |   |   |   | 96         |                   |

| ROS Parity Errors                           |   |   |   |   |   | 96         | LOCATIO           |

| ROS F00-F03ROSDR Test All Ones              |   |   |   |   |   |            | Power             |

| ROS F01-F02ROSDR Test All Zeros             |   |   |   |   |   | 97         | Frame             |

| ROS Address 000                             |   |   |   |   |   |            | Relay             |

| Extra or Missing Bits                       |   |   |   | • | • |            | Circuit           |

| Sense Latch and Strobe                      |   |   |   | • | • | 98         | Fuse Lo           |

| ROS Ripple Test                             |   |   |   |   |   |            | Voltag            |

| ROS BIT PLANE REMOVALS AND ADJUSTMENTS      |   |   |   |   |   |            | Overvo            |

| ROS Bit Plane Adjustments                   |   |   |   |   |   |            | · 1/0 Ta          |

| ROS Bit Plane Removal                       |   |   |   |   |   |            | I/O Ad            |

| ROS Bit Plane Cleaning                      |   |   |   |   |   |            |                   |

| ROS Bit Plane Installation                  |   |   |   |   |   |            | APPENDI           |

| Connector Installation                      |   |   |   |   |   |            | Physical I        |

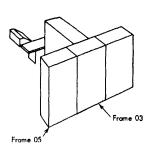

| STORAGE PROTECT (SP) SERVICE CHECKS .       |   |   |   |   |   |            | Frame             |

| Reference Voltage and Sense Level Adjustmen |   |   |   |   |   |            | Cablin            |

| Checking SP Drivers and Terminating Diodes  | • | • | • | • | • |            | Power Re          |

| Inhibit Drivers and Sense Amplifiers        | • | • | • | • | • | 102        |                   |

| SP Sense Windings                           | • | • | • | • |   | 102        |                   |

| Termination Diodes                          | • | • | • | • |   | 103        |                   |

|                                             | • | • | • | • |   | 103        | APPENDI           |

| Storage Protect Test Points                 | • | • | • | • | • | 103<br>103 | Controls a        |

|                                             | • | • | • | • | • | 103        | Section           |

|                                             | • | • | • | • | • | 103        | Section           |

| - ,                                         | • | • | • | • | • | 103        | Section           |

|                                             | • | • | • | • | • | 107        | Section           |

|                                             | • | • | • | • | • | 107        | Section           |

| •                                           | • | • | • | • | • | 107        | Section           |

| B-Clock Check                               | • | • | • | • | • | 107        | Select            |

| •                                           | • | • | • | • | ٠ | 107        | Section           |

| Indicator Check                             | • | • | • | • | • | 108        | Section           |

| A-Clock Manual Controls                     | • | • | • | • | • | 108        | Section           |

| -                                           | • | • | • | • | • | 109        | Key               |

|                                             |   | • | • |   | • | 109        | Sectio            |

| Singleshot Adjustment                       |   |   | • | • | · | 109        | Section           |

|                                             |   |   |   | · | • | 112        | Operating         |

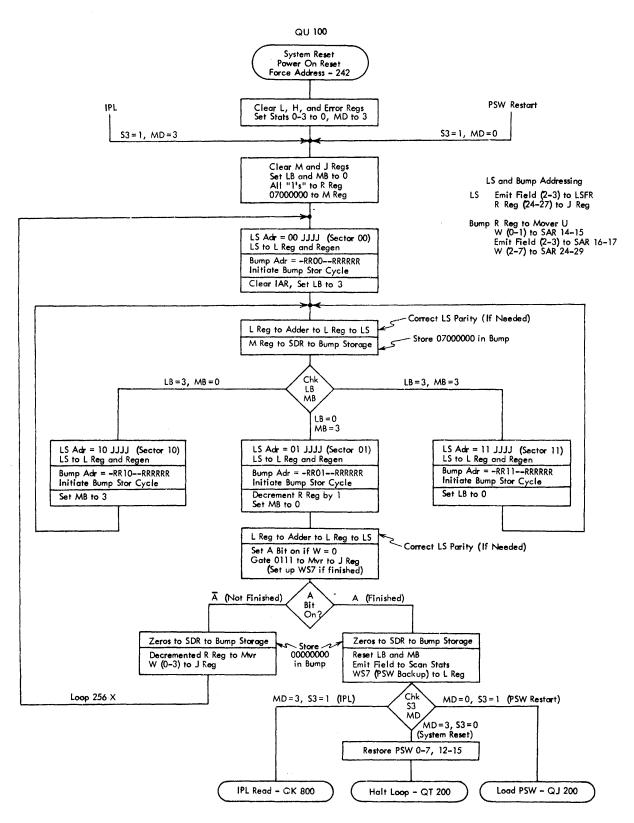

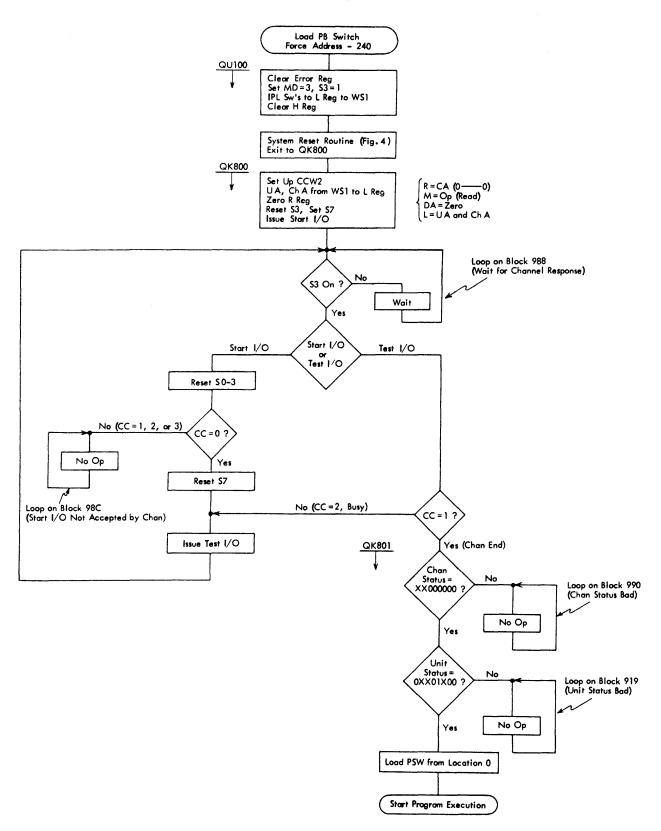

| Singleshot Adjustment                       |   |   |   | • | : |            | Systen<br>Initial |

| Singleshot Aufustment                       | • | • | • | ٠ | • | 2          | initial           |

|   |                  |   |                                       | ~ ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|------------------|---|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | •                | • | ٠                                     | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Switch and Indicator Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                  |   |                                       | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EMULATOR SERVICE AIDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                  |   |                                       | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1410/7010 Emulator Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | •                | ٠ | •                                     | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                  |   |                                       | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1410/7010 Disk Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                  |   |                                       | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2302 Disk Storage Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                |   |                                       | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2302 Track Correspondence 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                  |   |                                       | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2314 Disk Storage Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                | • | ٠                                     | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2314 Track Correspondence 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                  |   |                                       | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1410/7010 Diagnose Instruction Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • | •                | • |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| • | ٠                | • | •                                     | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Start I/O Diagnose Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                  |   |                                       | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7070/7074 Operation Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | •                | - |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| , | •                | ٠ | •                                     | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                  |   |                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | POWER SYSTEM SERVICE CHECKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

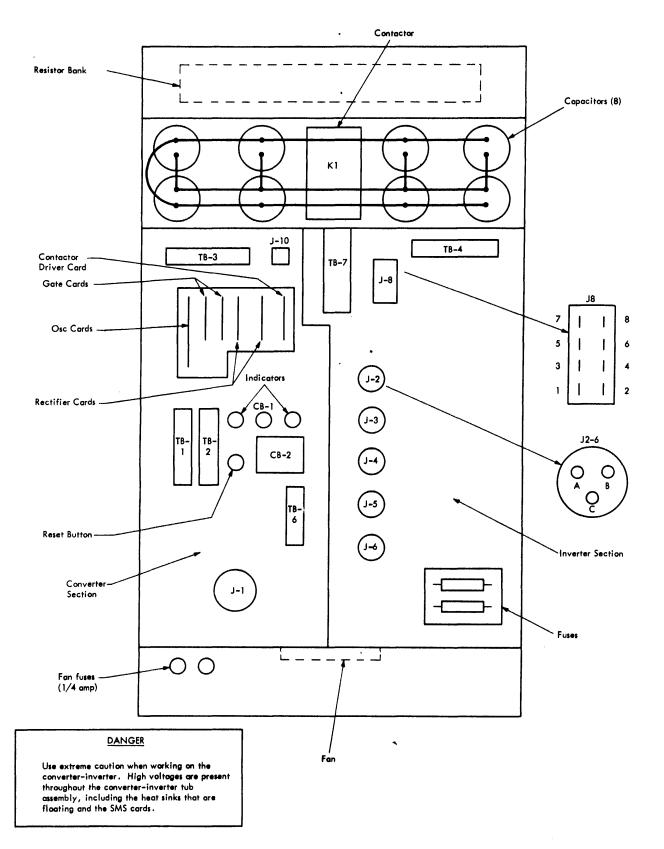

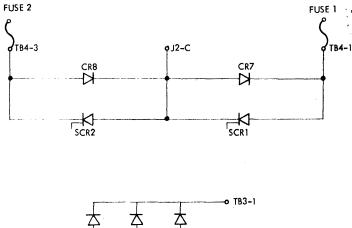

|   | •                | • | •                                     | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Converter-Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

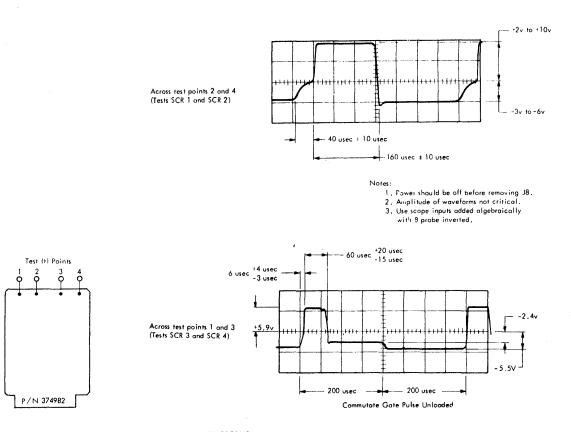

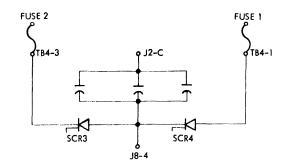

|   |                  |   |                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SCR Gate Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | •                | • | •                                     | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                | • | ٠                                     | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Types of Failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                  |   |                                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Converter-Inverter Fuse Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | -                |   |                                       | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Converter-Inverter Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                  |   |                                       | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Voltage Regulator Test Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                  |   |                                       | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Changing Voltage Regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

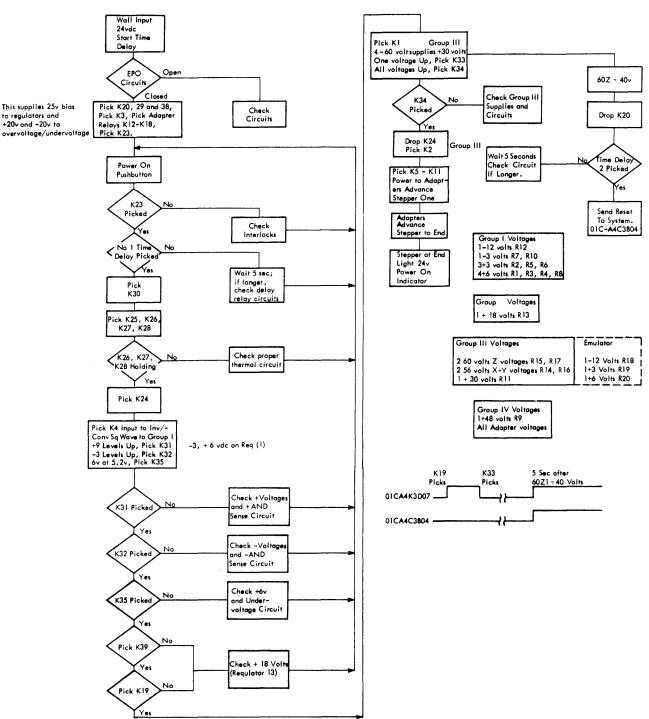

|   |                  |   |                                       | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Voltage Sequence Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                  |   |                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                | • |                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Overcurrent Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                  |   |                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | •                | • | •                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

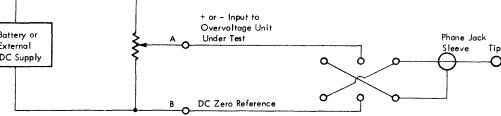

|   | •                | • | •                                     | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Overvoltage Unit Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                  |   |                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Low Voltage AC Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | •                | • |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

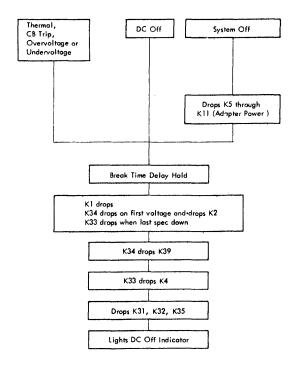

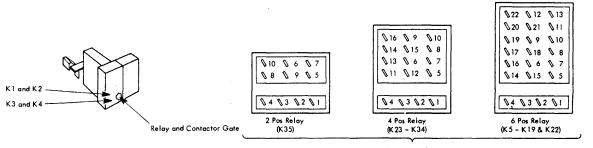

|   | •                | • | •                                     | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power Sequencing Relays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                  |   |                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Dual or Multi System Emergency Power Off 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | •                |   | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | •                | • | •                                     | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                  |   |                                       | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LOCATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                  |   |                                       | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

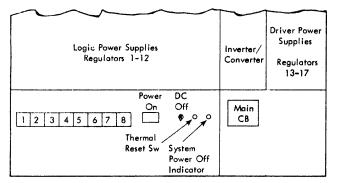

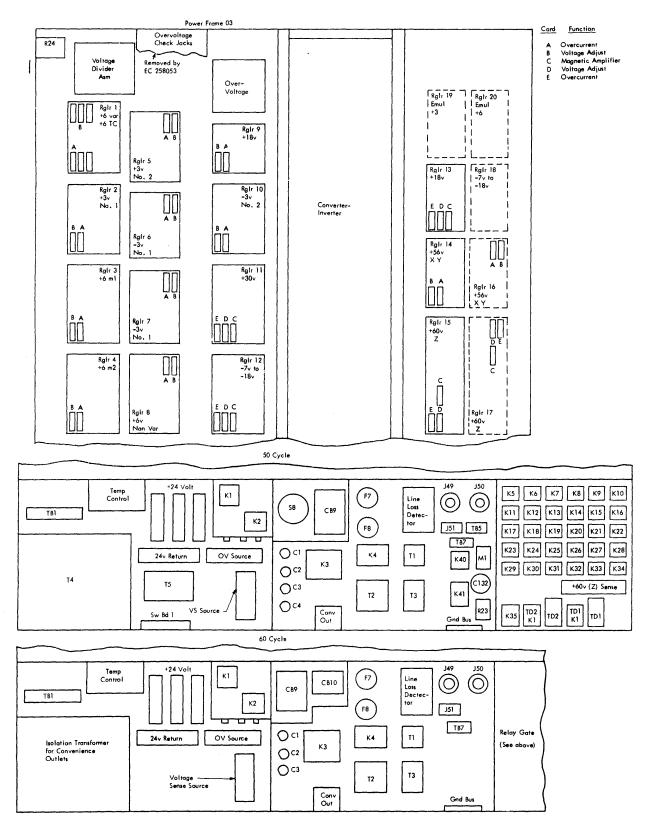

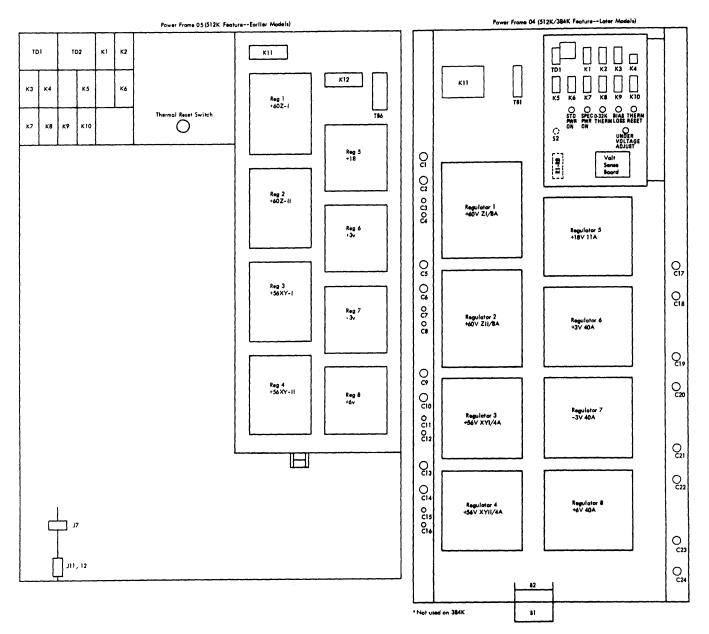

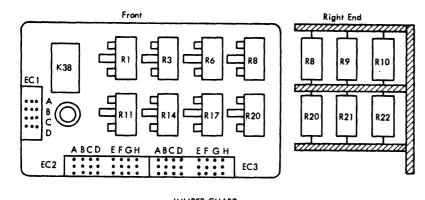

|   | •                | • | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power Distribution Frame Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

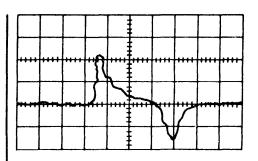

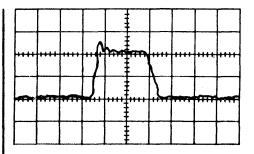

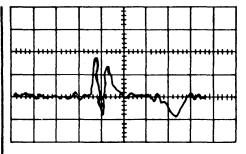

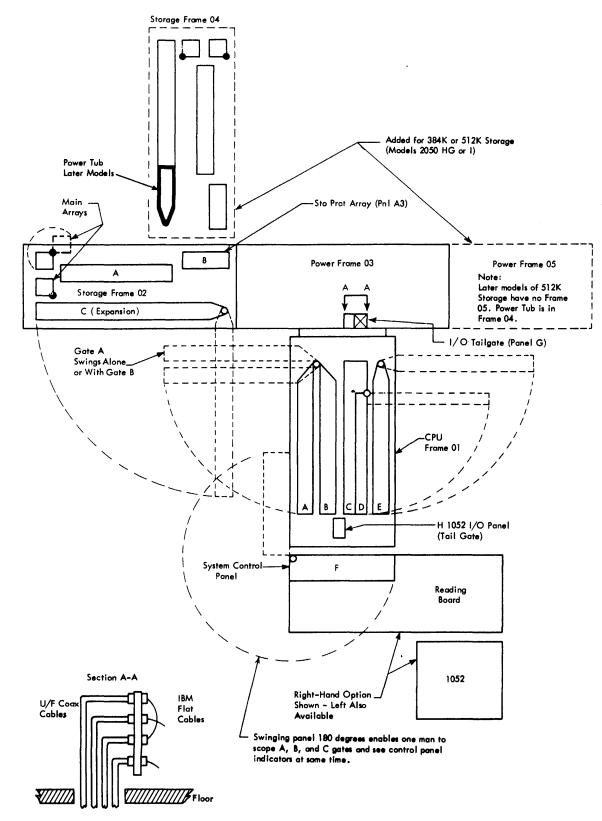

|   |                  |   | •                                     | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Frame and Gate Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |