File Number 360/20-13 Form Number A26-5622-0

# Systems Reference Library

# IBM System/360 Model 20 Universal Code Synchronous Transmit-Receive (RPQ)

This publication describes the universal code synchronous transmit-receive (UCSTR) custom communications feature. The units and features of the IBM System/360 Model 20 are described briefly, and a more complete description is provided for the UCSTR feature.

## PREFACE

This publication describes the universal code synchronous transmit-receive (UCSTR) custom communications feature. This feature is available on a request for price quotation from IBM basis (RPQ M24798). Other RPQ features can be used in conjunction with the UCSTR. The following is a list of features and their respective RPQ number. For a complete description of each feature, refer to UCSTR Special Features.

| Feature                          | RPQ Number |

|----------------------------------|------------|

| High speed                       | M24418     |

| Six-bit and seven-bit level code | e M24421   |

| Longitudinal redundancy check    |            |

| (LRC)                            | M25019     |

| Vertical redundancy check (VRC)  | 834533     |

| Terminal address recognition     | M34070     |

This publication includes sufficient information about the IBM System/360 Model 20 to provide a foundation for the special devices and operations included with the UCSTR feature. For more detailed information about the IBM System/360 Model 20; refer to the Systems Reference Library publication IBM System/360 Model 20 Functional Characteristics Form A26-5847.

#### First Edition

Specifications contained herein are subject to change from time to time. Any such change will be reported in subsequent revisions or Technical Newsletters.

The illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter.

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form is provided at the back of this publication for your comments.

This manual was prepared by the IBM Systems Development Division, Product Publications, Dept. 455, Bldg. 014, San Jose, California 95114. Send comments concerning the contents of this manual to this address.

© International Business Machines Corporation, 1967

ii System/360 Model 20 UCSTR (RPQ)

# CONTENTS

| INTRODUCTION<br>COMMUNICATION FACILITIES<br>Point-to-Point Configurations<br>Multipoint Configurations<br>MODES OF OPERATION<br>Basic Mode<br>Full Transparent Mode<br>Response Mode<br>TRANSMISSION CODES<br>TRANSMISSION ERROR CHECKING<br>TRANSMISSION SPEEDS<br>COMMUNICATIONS WITH IBM EQUIPMENT<br>COMMUNICATIONS WITH NON-IBM<br>EQUIPMENT                                                                                                     | 1<br>1<br>1<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>IBM SYSTEM/360 MODEL 20 UNITS<br/>IBM 2020 Central Processing Unit<br/>GENERAL INFORMATION<br/>Main Storage<br/>General Registers<br/>Parity Checking<br/>Data Formats<br/>Instruction Format<br/>Information Positioning<br/>UCSTR Information Positioning<br/>ADDRESSING<br/>OPERANDS<br/>Explicitly Addressed Operands<br/>Immediate Operands<br/>Operands in Registers<br/>TIME-SHARING<br/>UCSTR Time-Sharing<br/>Program Status Word</pre> | 4   4   4   5   5   6   7   8   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9 |

| UCSTR FEATURE<br>GENERAL INFORMATION<br>Control Characters<br>Control Field<br>Synchronization<br>Record Length<br>Error Checking<br>UCSTR Time-Sharing<br>MODES OF OPERATION<br>Basic Mode<br>Transparent Mode<br>Interruption<br>UCSTR Interrupt Conditions<br>PROGRAM INSTRUCTIONS<br>Data Format<br>Condition Code<br>Test I/O and Branch<br>Instructions<br>Control Input/Output<br>Instructions<br>UCSTR Control I/O                            | 11<br>11<br>13<br>13<br>13<br>13<br>14<br>14<br>14<br>14<br>14<br>15<br>17<br>18<br>18<br>18<br>18<br>18<br>19<br>19<br>21                                                        |

١..

4

Ċ

| Transfer Input/Output                                    |          |

|----------------------------------------------------------|----------|

| Instructions<br>UCSTR Transfer Input/Output              | 23       |

| Instructions                                             | 23       |

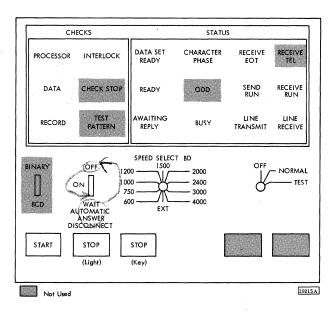

| KEYS AND SWITCHES                                        | 24       |

| Keys                                                     | 24       |

| Switches                                                 | 25<br>25 |

| INDICATOR LIGHTSStatus Indicators                        | 25       |

| Check Indicators                                         | 27       |

| UCSTR SPECIAL FEATURES                                   | 28       |

| High SpeedBit Level Code                                 | 28       |

| LRC Check                                                | 29<br>29 |

| VRC Check                                                | 29       |

| Terminal Address Recognition                             | 29       |

| Special Feature Summary                                  | 30       |

| IBM System/360 Model 20 Input/Output<br>Units            | 30       |

| IBM 1442 CARD PUNCH, MODEL 5                             | 30       |

| IBM 2501 CARD READER, MODELS Al                          |          |

| AND A2                                                   | 30       |

| IBM 2520 CARD READ PUNCH AND CARD                        | 31       |

| PUNCH<br>IBM 2560 MULTI-FUNCTION CARD                    | 21       |

| MACHINE                                                  | 31       |

| IBM 2203 PRINTER                                         | 31       |

| IBM 1403 PRINTER, MODELS 2,                              | 22       |

| 7, AND N1<br>IBM 2415 MAGNETIC TAPE DRIVE                | 32       |

| AND CONTROL UNIT                                         | 32       |

| IBM 2311 DISK STORAGE,                                   |          |

| MODELS 11 AND 12                                         | 32       |

| Storage Capacity<br>IBM 1419 MAGNETIC CHARACTER          | 33       |

| READER                                                   | 33       |

|                                                          |          |

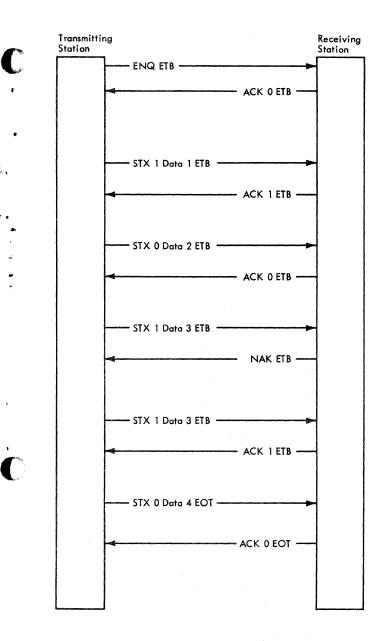

| UCSTR OPERATIONS                                         |          |

| LINE-CONTROL PROCEDURES                                  |          |

| Establishing Communications<br>Sending the First Message |          |

| Identifying Records                                      |          |

| Responses to Messages                                    | 36       |

| Error Retransmission                                     | 37       |

| Terminating Communications                               | 37       |

| CONTROL CHARACTERS                                       | 37       |

| LINE CODES                                               |          |

| MESSAGE FORMATS                                          | 38       |

| Message and Acknowledgement<br>Response                  | 38       |

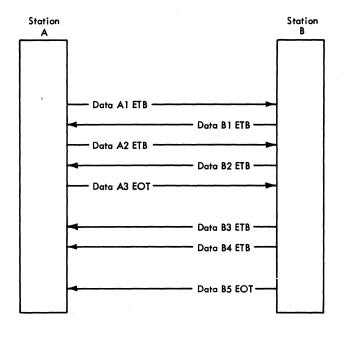

| Message and Message Response                             | 40       |

| Multiple Messages and One                                |          |

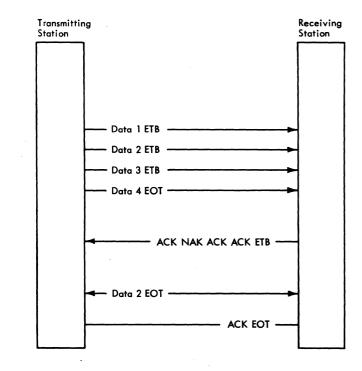

| Response                                                 | 41       |

| Multipoint Operation                                     | 41       |

| APPENDIX A. UCSTR TIMING                                 | 42       |

| INDEX                                                    | 43       |

The universal code synchronous transmitreceive (UCSTR) feature provides a means of communication that is independent of the transmission code used. The UCSTR is designed for flexibility, allowing communication in several modes of operation.

## COMMUNICATION FACILITIES

Private line or switched (dial-up) communications facilities may be used to implement UCSTR operation. These facilities can be obtained from communications common carriers or, if equivalent to the common carrier facilities, they may be customer provided. The communication facilities must provide for either half-duplex message transmission (alternate transmission in either direction, over one pair of wires, on a non-simultaneous basis), or four-wire half-duplex facilities may be used, reducing the normal turn-around delays associated with two-wire half-duplex message transmission. Message transmission for either two-wire or four-wire facilities is in only one direction at a time.

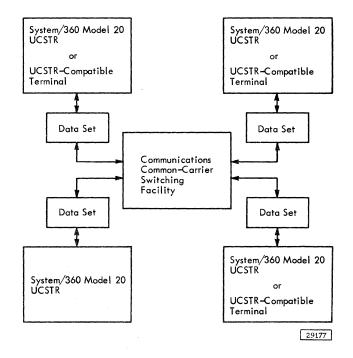

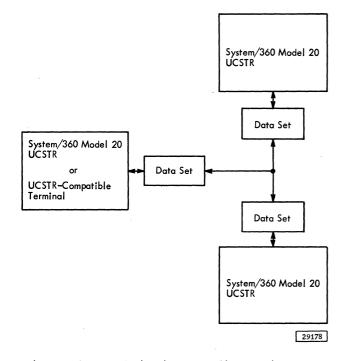

For UCSTR operations, the communications configuration can be designed for either a point-to-point or multipoint operation, depending on the requirements of the user. The specific data set equipment used at each channel termination point (station) is determined by the type of communications channel as well as the operating speed of the terminal equipment located at each station.

#### Point-to-Point Configurations

When operating on a point-to-point basis (Figure 1) all message exchanges are between only two stations. If the pointto-point configuration is a permanent installation (e.g. leased line or private line), message exchanges are always between the same two stations. However, if the facilities are the switched type, any station on the network can transmit to or receive from any other station on the network.

Figure 1. Point-to-Point Configuration

#### Multipoint Configurations

When operating on a multipoint basis (Figure 2), all message exchanges are between a master station and one or more remote stations. Control of message exchanges is performed by the master station. All message exchanges are initiated by a remote station selection operation (polling) that is performed by the master station.

Introduction 1

#### MODES OF OPERATION

This section provides a brief description of UCSTR modes of operation. For a more complete description of each mode, refer to UCSTR Feature.

#### Basic Mode

The basic mode of operation is the full binary minus three mode of operation. This term means that the 256 possible characters (eight-bit level) can be transmitted or received as data, with the exception of three bit combinations (characters) that are defined as control characters by the user's program. The three control characters are: end-ofblock (ETB), end-of-transmission (EOT) and synchronization(sync). The bit combination used for each character is selected by the user. See UCSTR Control Field.

The seven-bit level code (special feature) can, in the basic mode, transmit or receive, as data, the 128 possible bit combinations (characters) minus the three control characters defined by the user's program.

The six-bit level code (special feature) can, in the basic mode, transmit or receive, as data, the 64 possible bit combinations (characters) minus the three control characters defined by the user's program.

## Full Transparent Mode

The full transparent mode provides the capability of transmitting or receiving all 256 bit combinations (128 combinations in seven-bit level and 64 combinations in six-bit level).

## Response Mode

The UCSTR has the capability of automatically setting to receive mode (after a transmit XIO instruction is completed) to receive a response from the terminal that received the message block. The automatic response operation can be in conjunction with either the basic mode or transparent mode. For a complete description of response mode, refer to UCSTR Feature.

## TRANSMISSION CODES

Messages are transmitted and received in any eight-bit transmission code. However, an additional feature is available that allows the UCSTR to transmit and receive in any six-bit code or any sevenbit code.

## TRANSMISSION ERROR CHECKING

The cyclic redundancy check (CRC) is the basic transmission error checking method of the UCSTR. The cyclic redundancy check is accomplished by an arithmetic accumulation of the message characters at both the transmitting and receiving stations. The transmitting UCSTR automatically sends the accumulated check character (CRC character) immediately following the message ending character (ETB or EOT). The receiving station automatically subtracts the transmitting station's check character from its own accumulated check character. If the result is zero, the message was correct. If the result is not zero, the CRC error indicator in the receiving UCSTR is set on.

CRC checking is used for eight-bit level, seven-bit level, or six-bit level operations.

With the addition of a special feature, the UCSTR can perform longitudinal redundancy checking (LRC) or vertical redundancy checking (VRC). See UCSTR Special Features.

## TRANSMISSION SPEEDS

Transmission speeds from 600 to 50,000 bits per second (baud) are available.

The basic UCSTR operates at speeds of 600 to 4,000 baud with timing control provided by the UCSTR (internal clocking). The basic UCSTR can operate at any speed (600 to 4,800 baud) with the timing control provided by the appropriate data set (external clocking).

With the addition of a special feature, the UCSTR can operate at speeds up to 50,000 baud, with the timing control provided by the appropriate data set (external clocking). However, take show in lost at speeds that 7200 pps, d

#### COMMUNICATIONS WITH IBM EQUIPMENT

The UCSTR can communicate with another System/360 Model 20 with the UCSTR feature, or the UCSTR can communicate with another model of System/360 via the IBM 2701 Data Adapter Unit with the inter-processor communications adapter feature (RPQ M24802).

## COMMUNICATIONS WITH NON-IBM EQUIPMENT

Flexibility of the UCSTR allows it to communicate in a variety of line formats. The UCSTR communicates in an eight-

appropriate special feature, it communicates in eight-bit level, sevenbit level, or six-bit level line codes.

Checking is accomplished by a cyclic redundancy check (CRC), but the addition of the appropriate special feature, provides longitudinal redundancy checking (LRC) and/or vertical redundancy checking (VRC). In order for a non-IBM device to communicate with the UCSTR, it must meet the following criteria:

- It must be capable of sending at least two synchronization (sync) characters preceding each data message or control sequence. The sync character can be any eight-, seven-, or six-bit combination.

- It must be capable of synchronizing its timing circuitry with the UCSTR by receiving from two to seven sync characters.

- 3. It must end all control sequences and message blocks with an ending character.

No more than two unique end-of-block or end-of-message characters can be used. The UCSTR can recognize only two ending characters. The ending character can be any eight-, sevenor six- bit combination.

- It must send the CRC (or LRC) character immediately following the ending character.

- 5. It must place the low-order bit of each character on the transmission line first.

- 6. If the system uses CRC checking, the message polynomial must agree with the UCSTR message polynomial:

$x^{16} + x^{15} + x^2 + 1$ Eight-Bit  $x^{14} + x^{13} + x^5 + x^3 + x^2 + 1$ Seven-Bit  $X^{12} + X^{11} + X^3 + X^2 + X + 1$ Six-Bit 29222

- 7. The UCSTR uses a "mark" (down-level) to and from the data set as a logical one (up-level) in the UCSTR, and the UCSTR uses a "space" (up-level) as a logical zero (down-level) in the UCSTR. A non-IBM terminal must be compatible with this operation.

- The terminals must use the same clocking. If the non-IBM terminal uses data set clocking, the UCSTR must also use data set clocking.

- 9. If the data set provides the clocking, the UCSTR uses the positive going clock transition as a negative transition in UCSTR logic. The non-IBM terminal must be compatible with this operation.

- 10.The UCSTR does not operate in full transparency when the LRC check feature is used.

- 11.The UCSTR full transparent feature is not the same as the full transparent operation defined by the American Standard Association (ASA). As an example, the UCSTR uses a DLE-sync as an idle character rather than a sync sync.

## IBM SYSTEM/360 MODEL 20 UNITS

The UCSTR feature can be installed on an IBM 2020 Central Processing Unit that has the prerequisite feature: communications adapter special feature. The communications adapter special feature is altered by the UCSTR feature so that normal System/360 Model 20 synchronous transmit-receive (STR) operations are no longer possible.

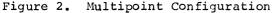

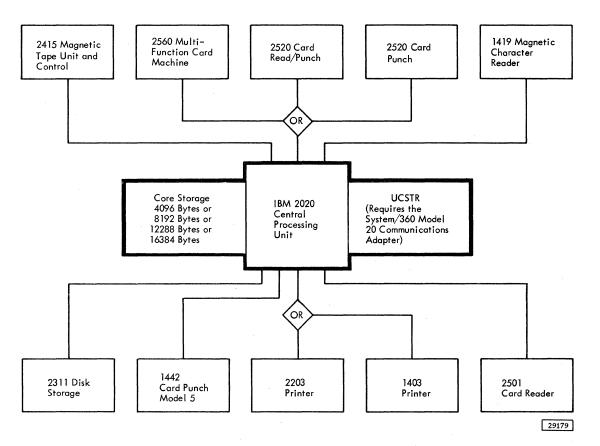

All other units and features of the IBM System/360 Model 20 are available for a system that contains the UCSTR feature. Figure 3 illustrates the variety of card reading, card punching, magnetic tape, disk storage, and printing units that can be attached to the IBM 2020 Central Processing Unit. For a more complete illustration of IBM System/360 Model 20 units and features, refer to the Systems Reference Library publication IBM System/360 Model 20 Configurator Form A26-3572.

#### IBM 2020 CENTRAL PROCESSING UNIT

The IBM 2020 Central Processing Unit (CPU) operation is unchanged by the addition of the UCSTR feature. The UCSTR feature uses the same interrupt priority level as the standard communications adapter. Input/output instructions used by the UCSTR are described in the section for UCSTR Feature.

## GENERAL INFORMATION

## Main Storage

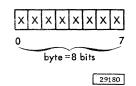

Main storage consists of 4,096, 8,192, 12,288, and 16,384 positions of magnetic core storage. Each position has an address and contains an eight-bit unit of information referred to as a byte.

Figure 3. IBM System/360 Model 20 Units

Coded combinations of bits within a byte can represent alphabetic, numeric, binary, or logical data.

Main storage is used to hold all the data that is to be operated upon, or processed, at a given time. It also holds the instructions, or program, which control the operation of the system. For each individual job performed by the system, certain portions of main storage are assigned to store instructions, and certain portions to store data to be processed.

## General Registers

Eight general purpose registers, small auxiliary storage units, are provided for temporary storage of small amounts of data. Each register is the equivalent of two bytes (one halfword) and is loaded or unloaded under the control of the stored program. Information may flow from register to register, from main storage to register, or from register to main storage.

The registers are numbered 8-15 and are selected by the four-bit R- or B-field of an instruction.

#### Parity Checking

To ensure the accurate transfer of data, an extra (parity) bit is generated for each four bits transferred to or from main storage or register storage. The parity bit is added during transfer, if it is needed, to maintain an odd number of bits. The bit count is monitored continuously, and any missing or extra bits which result in an even number of bits cause a CPU parity error.

## Data Formats

The basic unit of addressable data is an eight-bit byte. Each address contains eight bits of data and can be considered a byte boundary. The byte is divided into two sections of four bits each. A check (parity) bit is provided for each four bits.

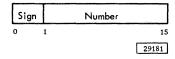

Halfword Binary Number

A halfword binary number has a fixed length of two bytes (16 bits). The leftmost bit is reserved for sign (+ or -) control.

## Decimal Number

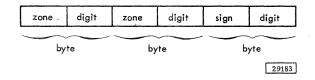

A decimal number may be in either of two forms: packed decimal or zoned decimal.

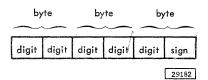

Packed Decimal: This format allows two numeric digits to be stored within one eight-bit byte.

An eight-bit byte may contain two numeric digits, except in the case of the rightmost byte, which has a sign to the right. Variable field length in this format allows for fields up to 16 bytes in length.

Zoned Decimal: This format contains one digit in the rightmost four positions of each byte.

The left four bits of each byte in this format are called zone bits, and are not used except for the low-order (rightmost) byte, which uses them for the sign. Zone bits do not affect the value of the numeric digit contained in the right four bits of the byte.

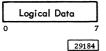

## Logical Data

Logical data may be contained in the instruction or it may reside in core storage as an operand (An operand is data contained in or addressed by the instruction and used to execute the instruction.) Logical data may have a fixed length of one byte or may be variable in length up to a maximum of 256 bytes.

Fixed-Length Logical Data

Variable-Length Logical Data

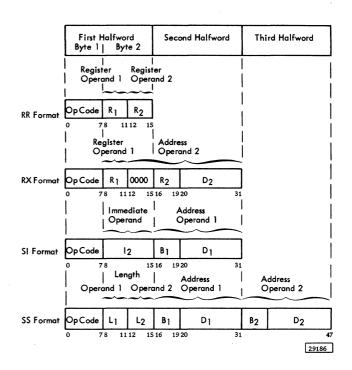

## Instruction Format

The instruction format specifies the length of the instruction and the type of operation to be performed. The length of the instruction can be one, two, or three halfwords. The types of instruction formats are RR, RX, SI, and SS.

RR Format: Denotes a register-to-register operation.

RX Format: Denotes a register-to-storage or a storage-to-register operation. In this format, bits 12 through 15 must be zero.

SI Format: Denotes a storage-immediate operation. In this format the I2 field of the instruction is the second operand. <u>SS Format</u>: Denotes a storage-to-storage operation.

In each format, the first instruction halfword consists of two parts. The first byte contains the operation code (op code). The length and format of an instruction are specified by the first two bits of the operation code. The second byte may be used to contain data, specify operand lengths, or specify registers to be used by the operation.

The field names refer to the manner in which the operands participate. The operand to which a field in an instruction format applies is generally denoted by the number following the code name of the field, for example, Rl, Bl, L2, D2. Normally, the operation of the CPU is controlled by instructions taken in sequence. An instruction is fetched from a location specified by the current instruction address. The current instruction address itself is located in the program status word (PSW). After the fetch operation, the current instruction address is increased by the number of bytes in the fetched instruction to enable addressing of the next instruction in sequence.

The instruction is then executed by adding, subtracting, multiplying etc., both operands with each other. The result that is thus obtained usually replaces operand 1. Upon the execution of certain instructions, a condition code, which reflects the nature of the result, is set into the PSW.

Subsequently, the updated address in the PSW is used to read out the next instruction from the main storage, and the processing continues.

## Information Positioning

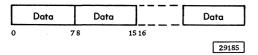

Byte locations in storage are consecutively numbered from 0, each number being considered the address of the corresponding byte. Bytes may be handled singly or strung together in fields. A group of two consecutive bytes is called a "halfword". The location of any field or group of bytes is specified by the address of the leftmost byte.

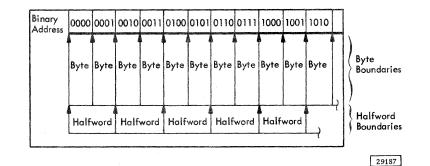

Information positioned in storage may be in fixed-length format or variablelength format. The length of fields is either implied by the operation to be performed or stated explicitly as part of the instruction. When the length is implied, the information is said to have a fixed length, which can be one, two, or four bytes. Fixed-length fields must be located in main storage on an integral (halfword) boundary (Figure 4) for that unit of information. A boundary is called integral for a unit of information when its storage address is a multiple of the length of the unit in bytes. For example, a halfword (two bytes) must have an address that is a multiple of the number 2.

In the 2020, all instructions and all data of fixed word length (operands addressed by RX-format instructions) must begin on a halfword boundary. An instruction (or data with fixed word length) is properly located at a halfword boundary when its address is even or, in other words, when the low order bit of the address is zero. An improperly placed instruction causes an error stop. When the length of a field is not implied by the operation code, but is stated explicitly, the information is said to have a variable-length field.

Within any instruction format or any fixed-length operand format, the bits are consecutively numbered from left to right, starting with bit number 0.

Variable-length fields are not restricted to half-word boundaries and may contain up to 256 bytes. Length is variable in increments of one byte.

## UCSTR Information Positioning

The UCSTR can transmit a record of 4,095 bytes, and it can receive a record 1,023 bytes. Protection boundaries are provided by the UCSTR to protect data and programs if, for any reason, a message ending character is not recognized by the UCSTR. The storage address protection boundaries are located at core storage location 1023, 2047, 3071, 4095, 5119, etc. A receive field must be contained between two boundary locations (e.g. core storage location 1024 through core storage location 2047). The receive field cannot be located so that it ends at the highest core storage location installed (4,095, 8,191, 12,287, or 16,383).

If the receive field is improperly located, the record check indicator is turned on, the receive error TIOB indicator is set on, and the audible alarm sounds when the receive field overruns a protection boundary.

#### ADDRESSING

Byte locations in storage are expressed in binary form and consecutively numbered from 0000 to the upper limit of available storage. The first 144 bytes (bytes 0000-0143) are reserved for internal CPU control and are not available to the program. The location of any field or group of bytes is specified by the address of the left most byte.

An address used to refer to main storage may be specified by either of two methods: direct addressing or effective address generation.

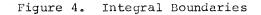

Direct Addressing: Direct addressing is used when the high-order bit in the Bfield of an instruction is zero.

When the direct addressing method is employed, the low-order 14 bits of the combined B- and D-fields are used to refer directly to byte locations in main storage. The twelve binary bits in the D-field allow an address specification

8 System/360 Model 20 UCSTR (RPQ)

of up to 4,095. To address additional (optional) storage, the adjacent two bits in the low-order position of the B-field are used, allowing address specification of up to 16,383.

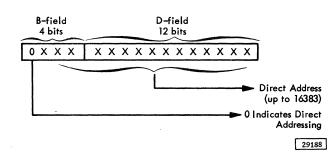

Effective Addressing: Effective addressing is used when the high-order bit in the B-field of an instruction is one.

In the effective-address generation method, the contents of the general register specified by the B-field of an instruction, are added to the contents of the D-field of the instruction to form the effective address. The content of the general register specified by the B-field is referred to as the "base address." The content of the D-field is referred to as the "displacement." (This type of address modification is commonly referred to as indexing.) Effective addressing may be either in a positive or a negative direction, depending on the sign of the base address. Caution should be exercised because a resultant effective address that is negative or that refers to the first 144 bytes of main storage results in an error condition.

Any of the eight general registers, 8 through 15, may be specified in the B-field as the location of the base address for effective-address generation.

If there are 0s in either the general register specified, or in the displacement field of the instruction when effectiveaddress generation is specified, the effective address generated is the same as direct addressing with the nonzero component.

Effective addressing is useful for program routines which require address modification.

#### OPERANDS

For addressing purposes, operands can be grouped in three classes: explicitly addressed operands in main storage, immediate operands placed in main storage as part of the instruction stream, and operands located in the general registers.

## Explicitly Addressed Operands

An explicitly addressed operand is selected from a main-storage location not related to the location of the instruction referring to it. It is always specified by means of a storage address. When the operand contains more than one byte, the address gives the location of the first byte of the field, subsequent bytes being located in higher addresses. Both the first and second operands of an instruction can be explicitly addressed.

Explicitly addressed operands can be of fixed length or variable length. The length of variable-field-length operands is specified in the L-field of the instruction. The L-field, either four or eight bits long, specifies the length in terms of the number of bytes to the right of the addressed byte, and thus can specify a maximum field length of 256 bytes.

## Immediate Operands

An immediate operand consists of one eight-bit byte of data which is located in the instruction itself. Only the instructions in the SI format contain immediate data. The immediate data is always the second operand; the first operand is located in the main-storage location specified by the B1-D1 field.

#### Operands in Registers

Information referred to by an instruction may be located in one of eight general registers. The registers are identified by numbers 8-15 and are selected by the four-bit R-or B-field of an instruction. The registers are not designated by mainstorage addresses. An operand located in a register has a fixed length of one halfword, or 16 bits.

## TIME-SHARING

The 2020 has the ability to operate in a mode referred to as "time-sharing." Time-sharing is a means of overlapping input/output operations with each other and with processing. Time-sharing is based on a system of monitoring the operation of input/output devices and sequencing the transfer of data to or from the I/O devices so as to make the most efficient use of processing time. Processing operations in the CPU are time shared with the transfer of data between main storage and the I/O devices. When an I/O device requests service, processing is suspended only for the time required to send or to accept the input/output data.

Time-sharing allows the CPU to perform useful processing functions while card or forms movement is taking place. A system of signaling that the I/O device is finished with the data transfer to or from the CPU is referred to as an "interruption" system.

## UCSTR Time-Sharing

When operating at speeds below 4800 bits per second, the UCSTR time-shares its operation with all System/360 Model 20 input/output devices. When operating at speeds above 4800 bits per second the UCSTR time-shares only with the 2020. Central Processing Unit and the 1403 buffered printer. Charged in 7200 fr

#### Program Status Word

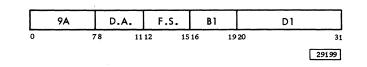

The program status word (PSW) contains the information necessary for proper program execution. It is located in an internal register in the CPU and is not directly addressable. The programmer can change the PSW by means of a set PSW instruction. The PSW has a fixed-length format of two halfwords.

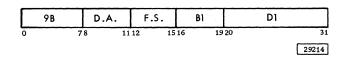

| cc         | C<br>AM | D.A.                  | F.S.       | Instruction Address |

|------------|---------|-----------------------|------------|---------------------|

| 0123       | 4567    | 8 11                  | 12 15      | 16 31               |

| 0-1        | l Na    | ot used               |            |                     |

|            | Co      | ndition Co            | de         |                     |

|            |         | ot used               | •••        |                     |

| 6          |         | CII Mode<br>annel Mas |            |                     |

| ,<br>8 - 1 |         | vice Addre            |            |                     |

| 12 - 1     | 15 Fui  | nction Spe            | cification |                     |

| 16 - 3     | 31 Ins  | truction A            | dress      |                     |

| * Ameri    | ican St | andard Co             | le for     |                     |

|            |         | Interchang            |            | 29190               |

The PSW is used to control instruction sequencing and to hold and indicate the status of the system in relation to the program being executed. The active or controlling PSW is called the "current PSW."

By storing the current PSW during an interrupt, the status of the CPU can be preserved for subsequent inspection. By loading a new PSW or part of a PSW, the state of the CPU can be initialized or changed. When the current PSW is stored during an input/output interruption, the status of the CPU and the next sequential address are preserved for use after the interruption is serviced. An instruction to load a new PSW is equivalent to an unconditional branch to the instruction address contained in the new PSW.

Operation of the program load key or system reset key causes the condition code (bits 2-3), the ASCII mode bit (bit 6), and the channel mask bit (bit 7) of the current PSW to be reset to 0.

#### INTERRUPTION

In the 2020, an automatic interrupt system is provided to make optimum use of the I/O devices and available processing time. The I/O devices signal the CPU to store an end condition when a data transfer has been terminated. Upon completion of the execution of each instruction, during the time that the CPU is in an interruptible mode, the CPU checks the various end conditions according to a built-in priority sequence. The first end condition thus found causes the actual interrupt. The interrupt is an automatic branch from the main program to a subroutine. This subroutine may be designed to test the received data for validity or to perform some other

action. Since the interrupt occurs at the earliest moment possible after a data transfer has been completed, it is the primary means of controlling I/O operations.

The branch to the subroutine is accomplished by replacing the current PSW with a new PSW which contains the start address of the subroutine in its instruction address portion. The former current PSW is stored into a particular core-storage location and thus becomes the old PSW. During the transfer, the old PSW is furnished with the device address and the function specification of the I/O unit that caused the interrupt. If the last instruction in the subroutine is a branch with the address of the old PSW specified as the branch address, the normal course of the main program is resumed because the next sequential instruction of the main program is specified in the old PSW. The entire exchange of the program status words (PSWs) is fully automatic; however, the channel mask bit in the PSW, which determines whether the CPU is interruptible or not, may be set or reset under program control. The CPU is interruptible when the channel mask bit is set to 1; it is not interruptible if the channel mask bit is 0. The channel mask bit is 0 when the CPU is in a reset state.

## GENERAL INFORMATION

The universal code synchronous transmitreceive (UCSTR) feature is a flexible system of communications that allows the user to define the control characters, determine the message format and establish the line-control procedure best suited for a specific application.

The IBM System/360 Model 20 communications adapter is a prerequisite feature for the UCSTR feature. However, the communications adapter is altered to accomodate the UCSTR so that normal System/360 Model 20 synchronous transmitter receiver (STR) operations are not possible.

UCSTR operation can be with two-wire or four-wire half duplex communications facilities. Half duplex means that transmission can be in only one direction at a time. Two-wire facilities require approximately 250 milliseconds (ms) to condition the facility for transmission in one direction. This conditioning of the facility is commonly referred to as turn around delay. Each time the direction of transmission is changed a turn around delay occurs. Depending on the specific application, the turn around delay time can be used for System/360 Model 20 internal processing or input/output operations.

If the application requires less turn around delay, a four-wire facility can reduce turn around delay to 3.3 ms to 26.0 ms depending on the line speed selected. At higher speeds on four-wire facilities, turn around delay can practically be disregarded in connection with long records.

Transmission speeds can be from 600 bits per second to 50,000 bits per second. (See Speed Select.)

Transmission codes can be eight-bit level on the basic UCSTR, or with the addition of a special feature, they can be eight-bit level, seven-bit level, or six-bit level (See UCSTR Special Features.)

#### Control Characters

The basic mode of UCSTR operation uses three control characters. The three control characters can be any three bit combinations selected by the user. The three control characters are stored in the UCSTR control field, and they can be changed to another bit combination under program control. The three control characters are as follows. Sync: The UCSTR (or any synchronous communications device) must have a method of obtaining synchronization of the timing circuitry in the receiving station and the transmitting station. For this purpose, one character (bit combination) must be defined as a synchronization (sync) character. The sync character is stored in the control field by the program. (See Control Field.)

ETB: The end-of-block (ETB) character is one of two ending characters used by the UCSTR. This character is used to define the end of a message block. When the transmitting station sends the ETB character, it ends the transmission after sending the CRC character. When the receiving station receives the ETB, it ends the receiving operation after it subtracts the incoming CRC characters. The ETB character ends a message transfer but does not define the end of transmission.

EOT: The end-of-transmission (EOT) character is one of two ending characters used by the UCSTR. The UCSTR functions the same as when sending an ETB character except that the receiving station sets the receive EOT test-and-branch indicator. The receive EOT test-and-branch indicator is tested by the program to determine when the last record has been received.

## Transparent Control Characters

When the UCSTR is operating in the transparent mode, one additional control character is used. The data link escape (DLE) character has a bit configuration of 00010000, and it cannot be changed by the program. The ending characters in transparent mode are two characters that form a 16-bit ending character. The end-of-block character is DLE-ETB, and the end-of-transmission character is DLE-EOT. The use of the DLE character is described in the section for Transparent Mode.

## Control Field

The UCSTR control field is any five consecutive bytes of storage used as a link between the System/360 Model 20 program and the UCSTR feature. The control field is defined by the user, and can be altered by the program according to the requirements of the application. The program transfers the control field or the control byte (see Control Byte) to the UCSTR feature when a set-totransmit or set-to-receive instruction is executed.

The program addresses the control field by addressing the high-order byte.

| Contr<br>Byte |    | ETB<br>Byte | EOT<br>Byte |    | YNC<br>yte | LRC Subtract<br>Field |

|---------------|----|-------------|-------------|----|------------|-----------------------|

| )             | 70 | 7           | 0           | 70 | 7          | 0 7                   |

|               |    |             |             |    |            | 29191                 |

## Control Byte

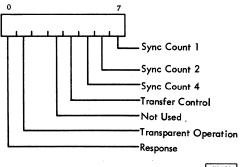

The control byte is used to control UCSTR mode of operation and to indicate the number of sync characters that will be emitted by the transmitting unit. The following illustration shows the purpose of each bit in the control byte.

29192

Response Bit: The response bit (bit 0) places the UCSTR in response mode. Response mode allows the UCSTR to automatically set to receive after a message block has been transmitted. Thus, a single XIO transmit record instruction initiates the transmission of a message block and the receiving of a response. See Program Instructions.

Transparent Operation: The transparent operation bit (bit 1) places the UCSTR in the transparent mode of operation. See Transparent Mode.

Transfer Control: The transfer control bit (bit 4) provides the program the means to transfer the control byte or

the entire control field (five bytes) to the UCSTR feature. If the transfer control bit is a one the entire fivebyte control field is transferred when a set-to-transmit or set-to-receive instruction is executed. If the transfer control bit is a 0, only the control byte is transferred when a set-to-transmit or set-to-receive instruction is executed. Thus, for the first set-to-transmit or set-to-receive instruction, the transfer control bit must be set to 1 so that the complete control field is transferred. The complete control field must be transferred when the system has been "powered up" or if the system reset key has been pressed. For subsequent setto-transmit or set-to-receive instructions, the transfer control bit can be set to 0. If a control character is to be redefined (different bit configuration) by the program, the entire control field must be transferred to the UCSTR feature.

Sync Count: These three bits (bits 5-7) indicate the number of sync characters (2-7) that the UCSTR will automatically send preceding each message block.

#### ETB Byte

This byte contains the bit configuration defined by the user as the ETB character. The ETB byte defined for the transmitting and receiving stations must be the same bit configuration.

## EOT Byte

This byte contains the bit configuration defined by the user as the EOT character. The EOT character defined for the transmitting and receiving stations must be the same bit configuration.

## Sync Byte

This byte contains the bit configuration defined by the user as the sync character. The sync character defined for the transmitting and receiving stations must be the same bit configuration.

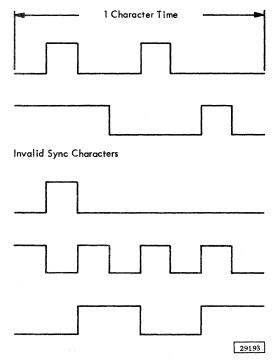

The sync character selected must have four transitions from space to mark or mark to space. If the 0-bit position contains a bit, the 7-bit position must contain a no-bit. The sync character should not be a repeating pattern of bits (e.g., 0,2,4,6, or 2,3,6,7.) The following shows an example of a valid and an invalid sync character.

Valid Sync Characters

## LRC Subtract Field

The LRC subtract field (byte) is used in conjunction with the LRC special feature. When the UCSTR communicates with a non-IBM communications device. that uses LRC checking, the UCSTR accumulates an LRC character from all characters placed on the transmission line except the beginning and ending sync characters. If the non-IBM devices excludes certain control characters from its LRC accumulation, the sum of the characters not accumulated is entered into the LRC subtract field (byte). The LRC subtract field is subtracted from the accumulated LRC in the UCSTR prior to transmitting (or receiving) the LRC character.

## Synchronization

Before a message exchange can occur, the transmitting station and the receiving station must have their timing circuits synchronized with each other. The receiving UCSTR can synchronize its timing circuits with the timing circuits of the transmitting station by receiving two consecutive sync characters. The transmitting UCSTR automatically sends the number of sync characters specified in the control byte (two to seven) preceding each transmission.

## Record Length

Normal System/360 Model 20 byte counting for byte length termination is not used by the UCSTR. The UCSTR depends on the ending character (ETB or EOT) to end the block transfer. In the transparent mode the ending character is a DLE-ETB or DLE-EOT. If the DLE-ETB or DLE-EOT is to be sent as data in the transparent mode, a byte count can be used to control the record length. If a byte count is used to control record length, the automatic response operation cannot be (See Program Instructions.) If used. the byte count is not used, any DLE-ETB or DLE-EOT in the message area of core storage will end the transfer. This happens only in response mode.

Maximum record length for a transmit operation is 4,095 bytes, and maximum record length for a receive operation is 1,023 bytes.

## Error Checking

Transmission error detection in the UCSTR is performed by cyclic redundancy checking (CRC). This check is performed automatically during normal UCSTR operation. Both the transmitting and receiving stations develop a CRC character which is an arithmetic accumulation of each character placed on the line excluding the beginning sync characters and the ending sync character (pad). The transmitting station sends the CRC character immediately after it sends the ending character or sequence. The receiving station subtracts the CRC character from the CRC character accumulated in the receiving station. If the longitudinal redundancy check (LRC) feature is installed, the UCSTR can perform either a CRC or an LRC check under control of a switch provided by the LRC feature (See UCSTR Special Features.)

LRC or VRC checking is not required or possible when the CRC checking is used or when transparent mode is used.

A CRC or LRC error turns on a UCSTR error indicator that can be tested by a test I/O and branch (TIOB) instruction. The error indicator is turned on when the CRC (or LRC) check is made at the end of a receive operation.

If the vertical redundancy check (VRC) feature (see UCSTR Special Features) is installed, the error indicator can be turned on for a VRC error on either transmit or receive. A VRC error indicates that a character with an even number of bits was contained in the previous message. A UCSTR error condition set during a transmit operation indicates only a VRC error. A UCSTR error condition during a receive operation indicates either a VRC or LRC error (or both).

When the UCSTR is transmitting with the response bit on, the UCSTR error indicator can be set because of an error under any or all of the following conditions:

- 1. VRC error in the transmitted message.

- 2. VRC error in the response message received.

- 3. LRC error in the response message received.

-mont 7200 At speeds of 4,800 bits per second and below, the UCSTR time-shares its operation with all System/360 Model 20 input/output units. At speeds above 4,800 bits per second, the UCSTR time-shares its operation only with the CPU and the 1403 buffered printer.

MODES OF OPERATION

UCSTR Time-Sharing

The UCSTR has two modes of operation, either of which can be used in conjunction with the automatic response mode.

#### Basic Mode

The basic mode of UCSTR operation is the full binary minus three mode. The UCSTR can send or receive all 256 possible binary combinations (characters) minus the three control characters (sync, ETB and EOT) defined by the users program. The following illustrates a message format for basic mode. If this message is the last message to be transmitted, the ETB character could be replaced by an EOT character.

Message in Transmitting Station Core Storage

## IBMETB

Message Transmitted by the UCSTR

## SYNC SYNC I BM ETB CRC 1 CRC 2 PAD

Message in Receiving Station Core Storage

> IBMETB 29194

The preceding illustration shows a message block consisting of three message characters and an ending character. The UCSTR precedes the message with two (up to seven) sync characters. Immediately following the ending character, the UCSTR automatically sends the 16-bit CRC character as two eight-bit characters. (In seven-bit level, the CRC character is 14 bits, and in six-bit level, the CRC character is 12 bits.) The UCSTR sends a "pad" character after the CRC character. The pad character is made up of the defined sync bit combination. The pad character is used to ensure that the last meaningful bits in a transmission are properly sent by the data set. It is not required to be received by the UCSTR.

The transmitting station can send, as data, the bit combination that has been defined as a sync character, but the receiving station does not enter the sync character in core storage. If sync characters must be sent as data, transparent mode should be used.

The capability of the UCSTR to receive but not store the sync character allows the UCSTR to communicate with equipment that sends a sync character (as an idle character) when, for any reason, it cannot send the next data character. The following illustration shows a threecharacter data message (with a sync character inserted) as placed on the transmission line, and it shows the portion of the message that is stored in System/360 Model 20 core storage by the UCSTR.

Message in Transmitting Station Core Storage

## IBMETB

Message Transmitted

#### SYNC SYNC I SYNC B METB CRC 1 CRC 2 PAD

Message in Receiving Station Core Storage

## I B M ETB

29195

The receiving station response to a message depends upon the user's program. Flexibility of the UCSTR allows the following types of response:

- A response (acknowledgment) for each message received.

- A response message (may or may not contain an acknowledgment) for each message received.

- After receiving several messages, sending one response message that defines any messages received in error. For specific response operations see UCSTR Operation.

## Transparent Mode

Transparent mode provides the UCSTR with the capability of transmitting and receiving, as data, all 256 possible bit combinations (128 combinations in sevenbit level or 64 combinations in six-bit level).

For the control required for transparent operation, the UCSTR uses a data link escape (DLE) character. The DLE character has a fixed bit configuration of 00010000. The DLE character for seven-bit mode is 0010000, and the DLE character for sixbit mode is 010000.

The DLE character is used in combination with the ETB or EOT to form a 16-bit ending sequence. Since the ending sequence in transparent mode is DLE-ETB or DLE-EOT, any of the 256 possible bit combinations can be transmitted individually, but an ETB or EOT character cannot be transmitted, as data, following a DLE character.

In transparent mode the transmitting station automatically inserts an extra DLE character for each DLE character in the message. The extra DLE is used to control UCSTR operations in transparent mode, but the extra DLE is not entered into core storage at the receiving station. (See Transparent without Response and Transparent with Response.) Transparent Without Response

Transparent mode without automatic response is an important function of the UCSTR when used in applications that require transmitting programs or binary data that can possibly contain message ending characters or sequences.

Transparent mode without automatic response allows the UCSTR to send all 256 (128 or 64) bit combinations including all control characters and ending characters (sync, ETB, EOT, DLE, DLE-ETB, and DLE-EOT). This type of operation is accomplished by using a byte count in the B2-D2 fields of the XIO transmitrecord instruction (See Program Instructions.) With response off, the UCSTR transfer ending operation is controlled by the byte count in the XIO transmit-record instruction. When operating in this mode, the UCSTR transmits the number of bytes specified in the byte count before checking for an ending sequence (DLE-ETB or DLE-EOT). Thus any combination of bits can be transmitted, and characters can be in any sequence. The following illustration shows a message format for transparent mode without an automatic response.

Message in Transmitting Station Core Storage

A DLE SYNC B DLE ETB C DLE ETB

A DLE SYNC B DLE ETB C DLE ETB

Message Transmitted by the UCSTR

SYNCSYNCADLE DLESYNCBDLE DLEETBC DLEETBCRC 1 CRC 2 PAD

Message in Receiving Station Core Storage

29196

The preceding illustration shows a nine byte message in the transmitting station core storage. The beginning sync, CRC1, CRC2, and ending sync characters are transmitted in the same manner as basic mode. The byte count in the B2-D2 fields of the XIO transmit-record instruction should be seven. The transmitting station will not test for an ending sequence until the byte count has been reduced to zero. After the byte count is reduced to zero, the transmitting UCSTR starts testing each character for an ending sequence (DLE-ETB or DLE-EOT). The eighth and ninth bytes contain the ending sequence that will end the transfer operation.

The transmitting UCSTR inserts an extra DLE character for each DLE character in the message while in transparent mode. The byte count reaching zero takes the UCSTR out of full transparent mode so that the extra DLE is not inserted for the ending sequence. The preceding illustration shows that a DLE-sync combination (normally an idle sequence in transparent mode) and a DLE-ETB combination (normally an ending sequence in transparent mode) have been transmitted as data.

The receiving UCSTR does not require a byte count to control recognition of the ending sequence. The extra DLE inserted (by the transmitting station) for each DLE in the message controls the receiving station ending transfer operation. The receiving station stores the first of each pair of DLE characters. The second DLE of each pair is "stripped out" by the UCSTR. The second DLE of each pair also sets up a control in the UCSTR so that the next character (following the two DLE characters) is not tested for an idle sequence or ending sequence (sync, ETB or EOT). The transmitting station ending sequence is a single DLE (instead of a pair) followed by an ETB or EOT. The receiving station recognizes the single DLE followed by an ETB or EOT as the ending sequence.

The UCSTR recognizes a DLE-sync combination as an idle sequence and does not place this combination into core storage.

The capability of the UCSTR to recognize the DLE-sync combination as an idle sequence allows the UCSTR to communicate with equipment that sends an idle sequence when, for any reason, it cannot send the next data character. The following illustration shows a three-character data message (with an idle sequence inserted) as placed on the transmission line, and it shows the portion that is stored in System/360 Model 20 core storage by the UCSTR.

Message in Transmitting Station Core Storage

## A B DLE DLE ETB

Message Transmitted

## SYNC SYNC A DLE SYNC B DLE DLE DLE ETB CRC 1 CRC 2 PAD

Message in Receiving Station Core Storage

A B DLE DLE ETB

29197

#### Transparent with Response

Transparent mode with automatic response operations cannot attain full transparency. Any character can be transmitted in this mode, but the 16-bit ending sequence (DLE-ETB or DLE-EOT) will end the transmission. Thus, if these combinations exist within the message, the program must search for them and split the combination before transmission. The ending character combinations (DLE-ETB or DLE-EOT) can be transmitted in transparent mode without response. (See Transparent without Response.) The transparent with response operation is similar to the transparent without response except that the transparent with response operation ends with any DLE-ETB or DLE-EOT combination rather than the first DLE-ETB or DLE-EOT after the byte count reaches zero.

The B2-D2 fields of the XIO transmitrecord instruction contain the starting core storage address where the response message will be stored. The following illustration shows a message format for transparent mode with the response bit on.

Message in Transmitting Station Core Storage

ASYNC DLE BEOT ETB DLE ETB

Message Transmitted by the UCSTR

SYNC SYNC A SYNC DLE DLE BEOT ETB DLE ETB CRC 1 CRC 2 PAD

Message in Receiving Station Core Storage

A SYNC DLE BEOT ETB DLE ETB

29198

The preceding illustration shows that a sync, DLE, EOT, and ETB can be sent as individual characters, but a DLE-ETB (or DLE-EOT) combination ends the transfer. The idle sequence (DLE-sync) for transparent with response is the same as the idle sequence for transparent without response. The UCSTR receives the idle sequence but does not transfer the characters to core storage. The capability of the UCSTR to receive but not store the idle sequence allows the UCSTR to operate with equipment that sends an idle sequence when, for any reason, it cannot send the next data character. The following illustration shows a message (with an idle sequence inserted), and it shows the portion that is stored in System/360 Model 20 core storage.

Normally, response mode allows a message to be received on a four-wire service without issuing a set-to-receive-mode instruction and receive-record instruction.

In non-response mode, there is a possibility of an I/O device interrupting before a set-to-receive-mode instruction and a receive-record instruction can be executed. To allow non-response mode to operate on a four-wire service additional sync characters can be sent by the transmitting station to allow the System/360 Model 20 to service an interrupt.

Message in Transmitting Station Core Storage

Message Transmitted

## SYNC SYNC A DLE SYNC B DLE DLE DLE ETB CRC 1 CRC 2 PAD

Message in Receiving Station Core Storage

## A B DLE DLE ETB

29197

## Interruption

Interruption is the general term applied to an automatic branch in the CPU program. The branch is automatic in the sense that it occurs when the condition exists, and is independent of a programmed branch instruction. In the System/360 Model 20, interruption is provided only for the channel end input/output condition. Channel end condition of an input/output device is defined as the time (in the mechanical cycle of the device) at which the data transfer has been completed.

In the time-shared mode of operation of the CPU and the input/output devices, the transfer of data between the input/output devices and main storage in the CPU is asynchronous with respect to processing operations. Thus, the channel end condition of an input/output data transfer operation may occur at any time in the instruction or execution phase of any processing operation. It is also possible that more than one input/output device reaches the channel end condition during a specific processing operation. The channel end conditions are stored in the form of interrupt bits. These bits are reset when the respective interrupts occur or are reset by a system reset or load operation.

The CPU is in an interruptible state when the channel mask bit in the program status word (PSW) is 1, and is in a noninterruptible state when this bit is 0. The channel mask bit is reset to 0 by operation of the system reset or program load key. The channel mask bit may be altered by a set PSW instruction or by an interruption.

When the CPU is in the interruptible state (channel mask bit is 1), a test is performed by the CPU at the end of each processing operation to determine whether or not a channel end condition exists for any input/output device. (The instruction and start phases of input/output operations are also considered as processing operations.)

The test for a channel end condition is performed in an established priority sequence. The program continues with the next sequential instruction if no channel end conditions exist. When one or more end conditions exist, the first one encountered in the priority sequence causes an interruption to occur. The channel end condition which causes the interruption is reset. The interruption is performed by storing the PSW in fixed main-storage location 144 and obtaining a new PSW from another fixed main-storage location (148) before the program continues. Since the new PSW contains the address of the next sequential instruction, the interrupt is equivalent to a branch operation. The PSW stored in main storage location 144 is referred to as the old PSW.

The old PSW (stored at main storage location 144 when an interrupt occurs) contains the device address of the I/O device which caused the interruption (bits 8-11), the primary function which the device was performing (bits 12-15), the address of the next sequential instruction, and the condition code. Primary functions are read, punch, or print; not included are details such as which feed was in use for a read operation on the MFCM.

The following is a list of device addresses and function specifications contained in bits 8 to 15 of the old PSW stored at main-storage location 144 when an interruption due to the corresponding channel end condition occurs. The list is in the priority sequence for these interruptions.

| Channel End Condition     | DA   | FS   |

|---------------------------|------|------|

|                           |      |      |

| 1419 Read                 | 0110 | 0110 |

| 2501 Read Card            | 0001 | 0010 |

| 2520 or 2560 Read Card    | 0010 | 0010 |

| 1403 or 2203 Print        | 0100 | 0000 |

| UCSTR Receive or Transmit | 0101 | 0110 |

| 2560 Punch Card           | 0010 | 0100 |

| 1442 Punch Card           | 0011 | 0100 |

| 2560 Write Card           | 0010 | 0000 |

| 2520 Punch Card           | 0010 | 0100 |

| Input/Output Channel      | 0111 | 0000 |

The channel mask bit in the new PSW (obtained from main-storage location 148) may be used to disable further interruptions in the routine which begins at the next sequential instruction address specified in the new PSW. As a means of returning to the point in the program at which the interruption occurred, a set PSW instruction, in which the specified address is 144, may be used as the last instruction in the routine.

## UCSTR Interrupt Conditions

The following functions cause a UCSTR interrupt condition:

- 1. An end condition when an XIO transmitrecord instruction has been executed with the response bit off.

- 2. An end condition when an XIO receiverecord instruction has been executed.

- 3. An end condition when a responsemessage ending character or sequence is received as a result of an XIO transmit-record instruction being executed with the response bit on. (The interrupt condition is not set after the transmit operation if the response bit is on.)

- 4. A response time-out has occurred. The response time-out interrupt occurs when a receive-record instruction has been executed but no data is received within three seconds, or a transmitrecord instruction has been executed (with the response bit on) but no response is received within three seconds.

#### PROGRAM INSTRUCTIONS

Transfers of information to main storage from the UCSTR and from main storage to the UCSTR are referred to as input/output operations. There are three types of instructions for input/output operations: transfer, control, and test I/O and branch instructions.

A transfer instruction (XIO) controls the transfer of data between main storage and the UCSTR.

A control instruction (CIO) directs the UCSTR to perform a specified function; e.g., set-to-transmit, or set-to-receive.

A test I/O and branch instruction (TIOB) causes an inquiry to the UCSTR for a particular condition (e.g., busy, response time-out, etc); if the tested indicator is on, the program branches to the specified address.

If the time-sharing switch is on, processing operations in the CPU are time-shared with the transfer of data between main storage and the input/output devices. When an input/output device requests service, processing is suspended only for the time required to send or accept the input/output data. See UCSTR time-sharing.

#### Data Format

Input/output data is located in eightbit bytes in main storage in variablelength fields. Data for the seven-bit level operation is positioned in the low-order seven bits (1-7) of each core storage byte. Data for the six-bit level operation is positioned in the low order six bits (2-7) of the core storage byte. Input/output data may be in the zoned, binary, or packed format.

No code translation is required for UCSTR operation. The UCSTR transmits the bit configuration contained each byte of the transfer field, and when receiving; the transfer field receives the same bit configuration that is received by the UCSTR.

## Condition Code

The status of an I/O device addressed by a transfer I/O instruction, and under certain conditions, a control I/O instruction, is used to set the condition code of the PSW at the time the execution of the instruction is completed. The condition code indicates whether or not the I/O device has initiated the operation specified, and if not, the reason for the rejection. The condition code can be used for decision-making by subsequent branching operations.

The UCSTR sets a condition code only when an XIO instruction is issued. The condition code is set to 00,01, 10, or 11 by an instruction to indicate the status of the I/O device addressed.

| Condition Code | Status              |

|----------------|---------------------|

| 0 0            | Available (A)       |

| 01             | Working (W)         |

| 10             | High-Speed UCSTR    |

| 11             | Not Operational (N) |

Available: Indicates that the addressed I/O device is operational, does not contain data or error check conditions, and is not busy with a previously initiated operation.

Working: Indicates that the addressed I/O device is executing a previously initiated operation.

High-Speed UCSTR: Indicates that the high-speed UCSTR feature is installed and operating when another I/O device is addressed, or it indicates that an I/O device is operating when the UCSTR is addressed. High-speed UCSTR timeshares only with the 1403 buffered printer; thus, the 1403 is the only device that can operate at the same time as the high-speed UCSTR.

Not Operational: Indicates that the addressed I/O device is in a not ready status, or an error or a data check condition exists on the device.

The operation specified by an XIO instruction is initiated only when the addressed I/O device is in the available state. If an I/O device which is not a part of the system is specified, a nooperation occurs, and the condition code is not changed.

## Test I/O and Branch

The device address (DA) specifies the I/O device in which a condition is to be tested.

The function specification (FS) specifies the particular condition or indicator to be tested in the I/O device addressed.

If the condition tested in the addressed I/O device is on, the updated instruction address is replaced by the branch address derived from the B1-D1 fields; otherwise, normal instruction sequencing continues with the updated instruction address.

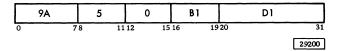

#### UCSTR Test I/O and Branch Instructions

## UCSTR Busy

The UCSTR busy TIOB instruction is available after a transmit or receive record XIO instruction has been issued. If the UCSTR feature is in a busy condition when the TIOB instruction is issued, the updated instruction address is replaced by the branch address in the BI-DI field of the TIOB instruction. If the UCSTR feature is not in a busy condition when the TIOB instruction is issued, normal instruction sequencing<sup>46</sup>proceeds.

The UCSTR becomes busy when the transmitrecord or receive-record XIO instruction is executed, and the UCSTR remains busy until an end-condition interrupt occurs, a response time-out interrupt occurs, or a nullify transfer instruction is executed.

#### CRC or LRC Error

The UCSTR error TIOB instruction is available after a receive record XIO is issued, or it is available after a transmit record XIO with the response bit (see Control Word) on is issued. If the UCSTR feature is in a busy condition when the TIOB instruction is issued, the CPU is interlocked, and the CPU performs the UCSTR error test after the UCSTR interrupt condition is set.

If the UCSTR error condition exists at the time the test is performed, the updated instruction address is replaced by the branch address in the Bl-Dl fields of the TIOB instruction. If no error exists when the test is performed, normal program sequencing continues.

UCSTR Feature 19

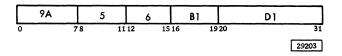

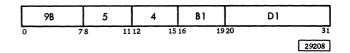

|   | 9A | 5    | 1     | B1    | DI |       |

|---|----|------|-------|-------|----|-------|

| 0 | 7  | 8 11 | 12 15 | 16 19 | 20 | 31    |

|   |    |      |       |       |    | 29201 |

A UCSTR error condition indicates that an error occurred during the preceding receive operation. The error is detected by the CRC, LRC or VRC check. (See Error Checking.)

If the vertical redundancy check (VRC) feature is installed, the UCSTR error TIOB instruction is available after a receive or transmit XIO instruction (See Error Checking.)

The UCSTR error indicator is reset when a receive-record or transmit-record XIO instruction is executed.

#### Receive EOT

The receive EOT TIOB instruction is available after a UCSTR interrupt condition is set. The indicator is turned on when the UCSTR receives an EOT character (DLE-EOT in transparent mode).

If this indicator is on when tested, the updated instruction address is replaced by the branch address in the Bl-Dl fields of the TIOB instruction. If the indicator is not on, normal instruction sequencing proceeds with the updated address.

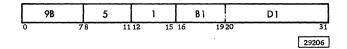

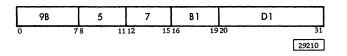

| 9A | T  | 5     | 5  | Bl    | DI |       |

|----|----|-------|----|-------|----|-------|

| 0  | 78 | 11 12 | 15 | 16 19 | 20 | 31    |

|    |    |       |    |       |    | 29202 |

The receive EOT indicator is reset when it is tested by a TIOB instruction. If the receive EOT indicator is not tested by the program, the EOT indicator light will turn on and the audible alarm will sound until the operator presses the stop key.

#### Response Time-Out

The response time-out TIOB instruction is available after a UCSTR interrupt condition is set. The response timeout indicator is turned on by the following conditions.

- A receive-record XIO instruction has been executed, but no message block has been received within three seconds.

- A transmit-record instruction is executed with the response bit on (see Control Byte), but no acknowledgment or message has been received within three seconds of sending the ending character or sequence.

If the response time-out indicator is on when tested by a TIOB instruction, the updated instruction address is replaced by the branch address in the Bl-Dl field of the TIOB instruction. If the indicator is off, normal instruction sequencing proceeds with the updated instruction address.

The response time-out indicator is turned off when one of the following occurs.

- 1. When the indicator is tested by a TIOB instruction.

- When a message block or response message has been received.

## Ring

The ring indicator indicates that a ringing signal is being received from a remote terminal. The ring TIOB instruction is available after a set-to-receive-mode CIO instruction, but prior to issuing a receive-record XIO instruction.

The ring indicator is used in conjunction with a data set that has the unattended answer feature installed.

The indicator is turned on by a ring signal from the data set when the UCSTR auto answer/disconnect switch is in the on position, the UCSTR start key has been pressed, and a set-to-receive mode CIO instruction has been executed.

The ring indicator being on indicates that a remote station is trying to call.

If the ring indicator is on when it is tested by a TIOB instruction, the updated instruction address is replaced by the branch address in the B1-D1 field of the TIOB instruction.

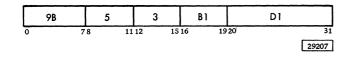

| 9A |    | 5  | 7     | B1    | DI  |    |

|----|----|----|-------|-------|-----|----|

| 0  | 78 | 11 | 12 15 | 16 19 | 20  | 31 |

|    |    |    |       |       | 292 | 04 |

The ring indicator is turned off by an automatic disconnect CIO instruction.

Control Input/Output Instructions

The device address (DA) specifies the I/O device in which a control function is to be performed.

The function specification (FS) specifies the particular component (it may also specify the primary function of that component) in the I/O device addressed.

A detailed specification of the control function to be performed is derived from the contents of the Bl-Dl fields, according to the rules for direct or effective address generation. If the detailed specification derived from the Bl-Dl field is all zero, a no-operation occurs.

field is all zero, a no-operation occurs. The BI-DI field of the set-to-receive and set-to-transmit instructions contains the address of the core storage location that contains the first byte of the fivebyte control field.

The Bl-Dl field is not used during the other UCSTR control I/O instructions, but the Bl-Dl fields must contain some bits to prevent a program error condition.

None of the UCSTR control I/O instructions will cause the UCSTR to be in a busy condition.

## UCSTR Control I/O

. .

The following control input/output (CIO) instructions are used by the UCSTR.

#### Set to Receive Mode

The set-to-receive-mode instruction conditions the UCSTR for a receive operation.

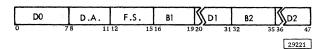

| 9B  | 5    | 0     | B 1   | DI    |   |

|-----|------|-------|-------|-------|---|

| 0 7 | 8 11 | 12 15 | 16 19 | 20 3  | 1 |

|     |      |       |       | 29205 | 5 |

This instruction is issued prior to an XIO receive-record instruction to set the direction of transmission for the receiving UCSTR.

The UCSTR remains in receive mode until a set-to-transmit-mode instruction is executed. Thus, the set-to-receivemode instruction is issued only when needed to set the initial direction of transmission, when the direction of transmission is to be changed from transmit to receive, or when a new control field byte is to be defined during a continuous receive mode operation. A continuous receive mode operation is when the UCSTR is receiving multiple message blocks without sending any response messages.

A data transfer will not occur until an XIO receive-record instruction is executed. (See Transfer Input/Output Instruction.)

The set-to-receive-mode instruction is available under the following conditions.

- 1. Prior to the execution of an XIO receive-record instruction to set the initial direction of transmission for the receiving UCSTR.

- 2. After the end-condition interrupt of an XIO transmit-record instruction to set the direction of transmission for receiving a response or message in reply to the message transmitted.

- 3. After the end-condition interrupt of an XIO receive-record instruction when defining a new control field byte (sync, ETB, EOT, or LRC subtract field) during a continuous receive operation.

Set to Transmit Mode

The set-to-transmit-mode instruction conditions the UCSTR for a transmit operation.

This instruction is issued prior to an XIO transmit-record instruction to set the direction of transmission for the transmitting UCSTR.

The UCSTR remains in transmit mode until a set-to-receive-mode instruction is executed, or a transmit-record operation has been completed with the response bit on. Thus, the set-to-transmit-mode instruction is issued only when needed to set the initial direction of transmission, when the direction of transmission is to be changed from receive to transmit, when the response bit is on and the UCSTR is ready to send the next message after receiving a response, or when a new control field byte is to be defined during a continuous transmit mode operation. A continuous transmit operation is an operation in which the UCSTR is transmitting multiple message blocks without receiving any responses or messages.

A data transfer will not occur until an XIO transmit-record instruction is executed. (See Transfer Input/Output Instruction.)

The set-to-transmit-mode instruction is available under the following conditions.

- 1. Prior to the execution of an XIO transmit-record instruction to set the initial direction of transmission for the transmitting UCSTR.

- After the end-condition interrupt of an XIO receive-record instruction to set the direction to send the next message after receiving a response or message in reply to the last message transmitted.

- 3. After the end-condition interrupt of an XIO transmit-record instruction when defining a new control field byte (sync, ETB, EOT or LRC subtract field) during a continuous transmit operation.

- 4. After the end-condition interrupt of an XIO transmit-record instruction with the response bit on. (The endcondition interrupt occurs after the response is received.)

Inhibit Audible Alarm

The inhibit-audible-alarm instruction suppresses the three-second processor

timer. If this timer is allowed to time out, the audible alarm will sound. The timer is started by pressing the UCSTR start key, or by a not busy condition. (Not busy exists after an end-condition interrupt following a previous XIO.) The timer resets with an XIO transfer instruction.