# Systems Reference Library

# IBM System/360 Model 20 Disk and Tape Programming Systems Assembler Language

This publication provides the information enabling the programmer to write programs in the IBM System/360 Model 20 DPS/TPS Assembler language and the macro language.

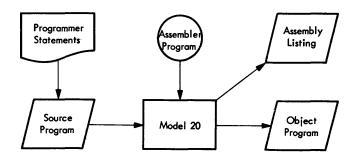

The Model 20 Assembler language allows the use of mnemonic operation codes and symbolic representations of storage addresses and other values. A program is written in symbolic language. This program is processed by the DPS/TPS Assembler program, which reads the symbolic statements and produces a program in machine language.

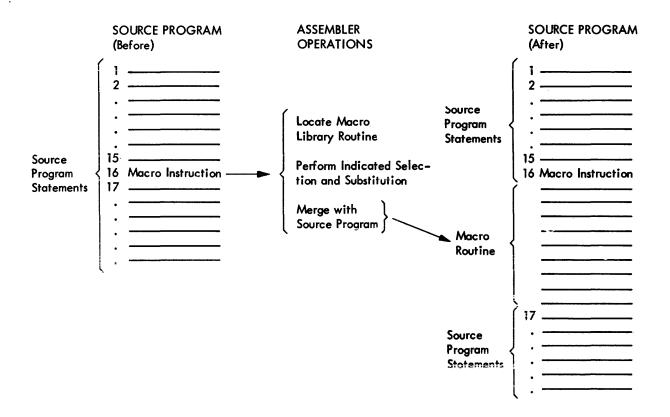

By means of the macro language, the programmer can reduce considerably the amount of repetitive coding required for routines used frequently within a given program or in many different programs. The programmer must code the routine only once and include it in the macro library. He writes a macro instruction at the point in the source program where the routine is required. During assembly, the Assembler reads the macro instruction, extracts the routine from the library, and inserts it in the object program. The programmer can cause the Assembler to tailor the routine to fit the particular problem program by specifying the appropriate symbolic operands in the macro instruction.

The reader of this publication should be familiar with basic programming concepts and with the operating principles of his system as described in the appropriate SRL publications. For a list of pertinent publications see <a href="IBM\_System/360\_Model\_20">IBM\_System/360\_Model\_20</a>, <a href="Bibliography">Bibliography</a>, Form GA26-3565.

# Sixth Edition (April, 1970)

This is a major revision of, and obsoletes, GC24-9002-4 and Technical Newsletters GN33-9059 and GN33-9076.

Minor changes have been made throughout the text. Many sections have been rearranged to improve readability. Therefore, the table of contents should be studied carefully. A section on Planned Overlay Structure has been added. Changes to the text and small changes to the illustrations are indicated by a vertical line to the left of the change; changed or added illustrations are denoted by the symbol • to the left of the caption.

This edition applies to release 9 of IBM System/360 Model 20 DPS, to release 13 of IBM System/360 Model 20 TPS, and to all subsequent releases until otherwise indicated in new editions or Technical Newsletters.

Changes are continually made to the specifications herein; before using this publication in connection with the operation of IBM systems, consult the latest IBM System/360 Model 20 SRL Newsletter, Form GN20-0361, for the editions that are applicable and current.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer using a special print chain.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Laboratories, Programming Publications, 703 Boeblingen/Sermany, P.O. Box 210.

o copyright IBM Germany 1966, 1967

copyright International Business Machines Corporation 1967, 1969, 1970

# Contents

| Introduction 5                                                                                         | Machine Hermate of Tuelousia                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                       |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                                                                        | Machine Formats of Instructions                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                     |

| Types of Assembler-Language Statements 5                                                               | for Logical Operations Condition Code After Logical                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                                     |

| Character Set                                                                                          | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                     |

| Major Assembler Language                                                                               | Instructions for Logical                                                                                                                                                                                                                                                                                                                                                                                                                        | ٠,                                                                    |

| Features 7                                                                                             | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3'                                                                    |

| Operating Environment 7                                                                                | MVI Move Immediate                                                                                                                                                                                                                                                                                                                                                                                                                              | 3!                                                                    |

|                                                                                                        | MVC Move Characters                                                                                                                                                                                                                                                                                                                                                                                                                             | 3!                                                                    |

| Assembler Language Coding                                                                              | MVZ Move Zones                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3!                                                                    |

| Conventions 8                                                                                          | MVN Move Numerics                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                     |

| Description of Conventions 8                                                                           | CLI Compare Logical Immediate                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                     |

| Summary of Coding Conventions 9                                                                        | CLC Compare Logical                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                       |

|                                                                                                        | Characters                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                     |

| Terms and Expressions 12                                                                               | ED Edit                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                                                                     |

| Terms                                                                                                  | NI And Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                | 39                                                                    |

| Self-Defining Terms                                                                                    | OI Or Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39                                                                    |

| Assembler Program Defined Terms . 13                                                                   | TM Test Under Mask                                                                                                                                                                                                                                                                                                                                                                                                                              | 4(                                                                    |

| Expressions                                                                                            | TR Translate                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                    |

| Evaluation of Expressions 15 Absolute and Relocatable                                                  | Branch Operations                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.                                                                    |

| Expressions 16                                                                                         | Machine Formats of Instructions                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.                                                                    |

| Expressions                                                                                            | for Branch Operations                                                                                                                                                                                                                                                                                                                                                                                                                           | u'                                                                    |

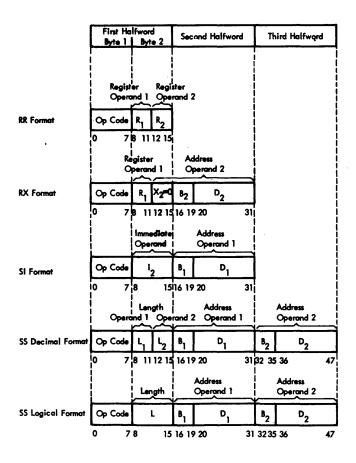

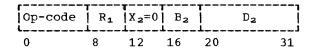

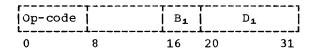

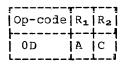

| Machine Instructions 17                                                                                | Error Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                    |

| Object Format of Machine                                                                               | Instructions for Branch                                                                                                                                                                                                                                                                                                                                                                                                                         | 7 2                                                                   |

| Instructions ,                                                                                         | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                    |

| Machine-Instruction Alignment 17                                                                       | BCR Branch on Condition                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       |

| Machine-Instruction Mnemonic Codes 17                                                                  | Register                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42                                                                    |

| Extended Mnemonic Codes 18                                                                             | BC Branch on Condition                                                                                                                                                                                                                                                                                                                                                                                                                          | 43                                                                    |

| Machine Instruction Operands 18                                                                        | BASR Branch and                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |

| Operand Fields and Subfields 18                                                                        | Store/Register                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                                                                    |

| Explicit and Implicit Addressing . 19                                                                  | BAS Branch and Store                                                                                                                                                                                                                                                                                                                                                                                                                            | 44                                                                    |

| Explicit Addressing 19                                                                                 | SPSW Set PSW                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44                                                                    |

| Implicit Addressing 20                                                                                 | Input/Output Operations                                                                                                                                                                                                                                                                                                                                                                                                                         | 45                                                                    |

| Explicit and Implicit Lengths 20                                                                       | Literals                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       |

| Examples 21                                                                                            | Literal Pool                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                    |

| Types and Functions of Machine Operations                                                              | miceiai rooi                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                    |

| Binary Arithmetic Operations 22                                                                        | Assembler Instructions                                                                                                                                                                                                                                                                                                                                                                                                                          | 47                                                                    |

| Machine Formats of Instructions                                                                        | Symbol-Definition Instruction                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

| for Binary Operations 23                                                                               | EQU Equate Symbol                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                                                                    |

| Binary Arithmetic Error                                                                                | Data-Definition Instructions                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                       |

| Conditions 23                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                    |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |

| Instructions for Binary                                                                                | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                                                                    |

| Instructions for Binary Arithmetic 24                                                                  | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52                                                              |

| Instructions for Binary Arithmetic 24 AR Add Register 24                                               | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54                                                        |

| Instructions for Binary Arithmetic 24 AR Add Register 24 SR Subtract Register 24                       | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54                                                        |

| Instructions for Binary Arithmetic 24 AR Add Register 24 SR Subtract Register 24 STH Store Halfword 25 | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54                                                  |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54                                                  |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54                                                  |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 54<br>54<br>54<br>54<br>55                                            |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>55<br>56                                      |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>54<br>55<br>56<br>57                          |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>57                          |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>57                          |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>57<br>58                    |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol                                                                                                                                                  | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>57<br>58                    |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>57<br>58<br>58              |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol                                                                                                                                                  | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>57<br>58<br>58              |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol EXTRN Identify External Symbol Addressing an External Control Section                                                                            | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>58<br>58<br>59              |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>58<br>58<br>59              |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol EXTRN Identify External Symbol Addressing an External Control Section Section Base Register Instruction Statements                               | 48<br>52<br>54<br>54<br>55<br>56<br>57<br>58<br>58<br>59<br>59        |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol EXTRN Identify External Symbol Addressing an External Control Section Section Statements USING Use Base Address                                  | 48<br>52<br>54<br>54<br>55<br>55<br>57<br>57<br>58<br>59<br>60        |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol EXTRN Identify External Symbol Addressing an External Control Section Section Statements USING Use Base Address Register                         | 48<br>5 5 4<br>5 5 5<br>5 5<br>5 5<br>5 5<br>5 5<br>5 6<br>6 0<br>6 0 |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol EXTRN Identify External Symbol Addressing an External Control Section Section Statements USING Use Base Address Register DROP Drop Base Register | 482<br>5 5 5 5 5 5 5 5 5 5 5 6 6 6 2                                  |

| Instructions for Binary Arithmetic                                                                     | DC Define Constant DS Define Storage DCCW Define Channel Command Word Program Sectioning and Linking Instructions Control Sections START Start Assembly CSECT Identify Control Section Dummy Control Sections DSECT Identify Dummy Section Symbolic Linkages ENTRY Identify Entry-Point Symbol EXTRN Identify External Symbol Addressing an External Control Section Section Statements USING Use Base Address Register                         | 48<br>5 5 4<br>5 5 5<br>5 5<br>5 5 5<br>5 5 5<br>5 5 5<br>6 6 6 2     |

| TITLE Identify Assembly Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |

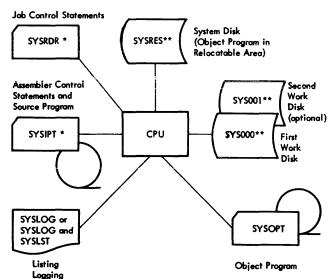

| SPACE Space Listing 6 PRINT Print Optional Data 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Job Control Statements                               |

| Program-Structure Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | riogiam control statements 103                       |

| Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | scacement                                            |

| Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AOPTN (Assembler Option) Statements                  |

| XFR Generate a Fransfer Card . 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |

| ORG Set Location Counter 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TSEO Input Sequence Checking 107                     |

| LTORG Begin Literal Pool 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 06                                                   |

| END End Assembly 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Cataloging a Macro Definition 108                    |

| Planned Overlay Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Job Control Statements (DPS) 108                     |

| Overlay Using the FETCH Macro 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67 SOB CONCLOS SCACCINCINCS (115)                    |

| Coding of Phases Without Subphases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | riogram concior scatements                           |

| Coding of a Phase with Subphases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |

| Overlay Using the LOAD Macro 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | , a                                                  |

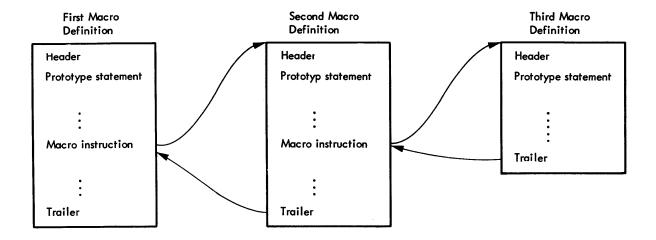

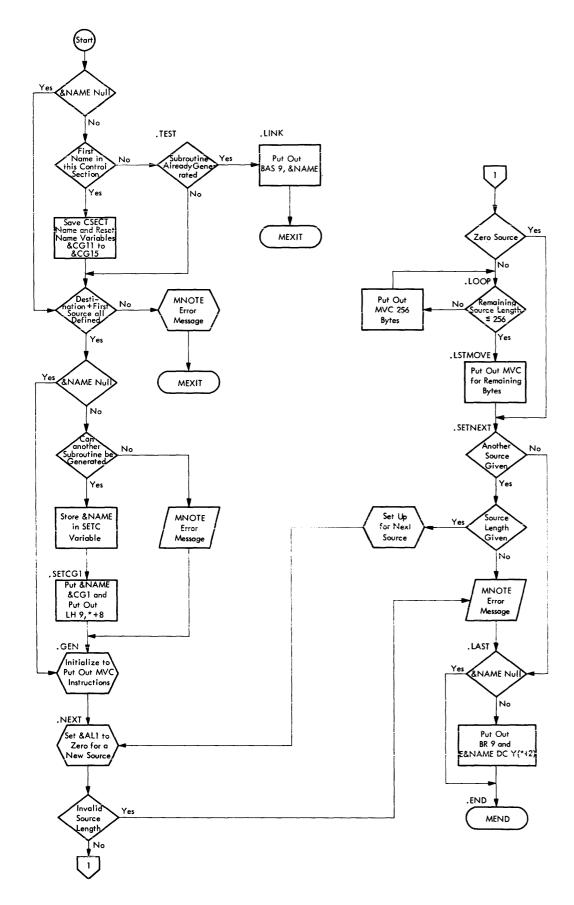

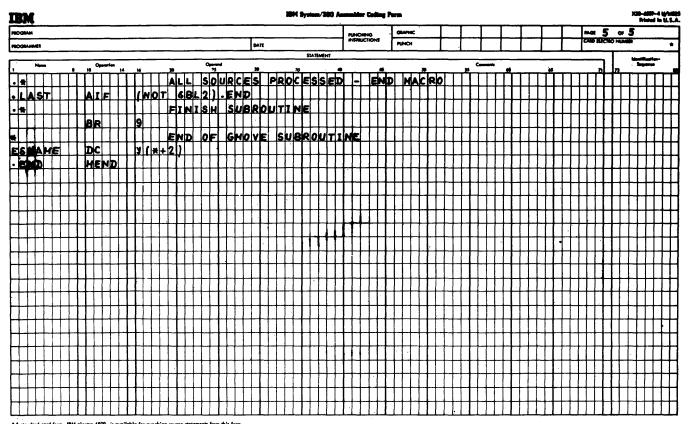

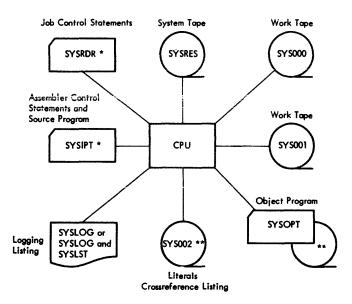

| Macro Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -anguage companionity                                |