IBM

## 3745 Communication Controller

SY33-2059-5

## **Diagnostic Descriptions**

# TEM

IBM 3745 Communication Controller SY33-2059-5 Models 130, 150, 170, 210, 310, 410, and 610

IBM 3746 Expansion Unit Models A11, A12, L13, L14, and L15

**Diagnostic Descriptions**

#### - Note! --

Before using this information and the product it supports, be sure to read the general information under "Notices" on page vii.

#### Sixth Edition (August 1991)

The information contained in this manual is subject to change from time to time. Any such changes will be reported in subsequent revisions. Changes have been made throughout this edition, and this manual should be read in its entirety.

Order publications through your IBM representative or the IBM branch office serving your locality. Publications are not stocked at the addresses given below.

A form for readers' comments appears at the back of this publication. If the form has been removed, address your comments to:

International Business Machines Corporation Department 6R1LG 180 Kost Road Mechanicsburg PA 17055-0180 U.S.A.

or

IBM France Centre d'Etudes et Recherches Service 0762 BP 79 06610 La Gaude France

When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1987, 1991. All rights reserved.

Note to U.S. Government Users – Documentation related to restricted rights – Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# Contents

| Chapter 1. Diagnostic Overview            | . 1-1 |

|-------------------------------------------|-------|

| Introduction                              |       |

| Concurrent and Non-Concurrent Maintenance | . 1-3 |

| Diagnostic Package                        |       |

| Diagnostic Monitoring                     |       |

| Diagnostic Structure                      | . 1-5 |

| Diagnostic Identification                 | . 1-5 |

| List and Duration of IFTs                 | . 1-6 |

| Manual Routines                           |       |

| Format of Repair Action Codes             | . 1-7 |

| FRU List for Unexpected DCF Errors        | 1-8   |

| Power Diagnostics                         | . 1-9 |

| Control Panel Test                        | 1-9   |

| Power Control Bus Test                    | . 1-9 |

| MMIO Bus Test                             | 1-9   |

| Power Analog Card Test                    | 1-9   |

| Power Logic Card Test                     | 1-9   |

|                                           |       |

| Chapter 2. CCU Diagnostics.               |       |

| Introduction                              |       |

| Additional Information Field Descriptions |       |

| Manual Intervention Routine               |       |

| RAC-to-FRU Conversion List for CCU        | 2-14  |

| Routine Descriptions                      |       |

| AA01 - AT05                               |       |

| BA01 - Bl01                               |       |

| DB01 - DH01                               |       |

| EB01 - ES05                               |       |

| <b>FA01 - FN03</b>                        |       |

| GA01 - GN01                               |       |

| HA01 (or HE10) - HA58 (or HE58)           |       |

| HA5A - HD78                               |       |

| HE10 (see HA10) - HE5C (see HA5C)         |       |

| HG01 - HI08                               |       |

| SBXT SETP SIOD SLST SRGI                  | 2-140 |

|                                           |       |

| Chapter 3. IOCB Diagnostics               |       |

|                                           |       |

| Requirements                              |       |

| RAC-to-FRU Conversion List for IOCB       |       |

| Concurrent Diagnostics                    |       |

| Routines Description                      |       |

| IA01 - IC05                               |       |

| JA01 - JC05                               |       |

| KA01 - KA12                               |       |

| WA01 - PIO Scoping                        | 3-30  |

|                                           |       |

| Chapter 4. CA Diagnostics                 |       |

| Introduction                              |       |

| Requirements                              |       |

| Manual Intervention Routines              | 4-4   |

| RAC-to-FRU Conversion List for CA |                                       |

|-----------------------------------|---------------------------------------|

| Routines Description              |                                       |

| LA01 - LQ02                       |                                       |

|                                   |                                       |

| Chapter 5. TSS Diagnostics.       |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   | S                                     |

| •                                 |                                       |

|                                   |                                       |

|                                   |                                       |

| •                                 | Internal) 5-                          |

| •                                 |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

| LVL0 LVL1 LVL2                    |                                       |

|                                   |                                       |

| Chapter 6. TRSS Diagnostics       |                                       |

|                                   |                                       |

| · .                               |                                       |

|                                   |                                       |

|                                   | ГЕ)                                   |

|                                   |                                       |

|                                   |                                       |

| •                                 |                                       |

| TA 0.4 TION                       |                                       |

| TAUT - 1102                       | б-                                    |

| Chapter 7. ESS Diagnostics        |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

| •                                 |                                       |

| RAC-to-FRU Conversion List for ES |                                       |

|                                   | errupt Handling                       |

|                                   | · · · · · · · · · · · · · · · · · · · |

| •                                 |                                       |

| QAUI-0103                         | · · · · · · · · · · · · · · · · · · · |

| Chapter 7 HDTSS Discretion        |                                       |

| Chapter 7. HPTSS Diagnostics      |                                       |

|                                   |                                       |

|                                   |                                       |

|                                   |                                       |

| •                                 |                                       |

| Wrap Mode                         |                                       |

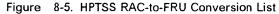

| RAC-to-FRU Conversion List for HPTSS8-            | g  |

|---------------------------------------------------|----|

| Unexpected Level 0 and Level 2 Interrupt Handling | 0  |

| Routines Description                              | 1  |

| VA01 - VK03                                       |    |

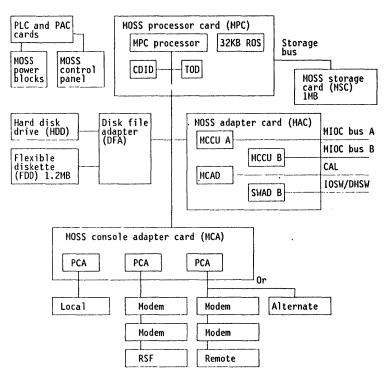

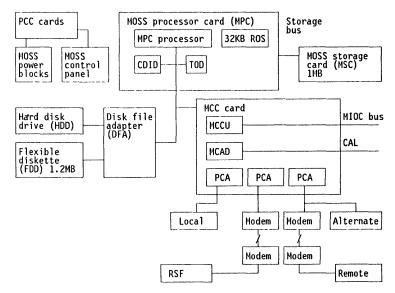

| Chapter 8. MOSS Diagnostics                       | -1 |

| MOSS Overview                                     | 3  |

| MOSS Structure                                    | 4  |

| MOSS Diagnostics Hexadecimal Display Codes        | 5  |

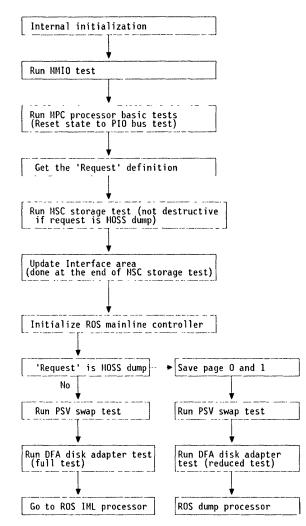

| Starting the ROS MOSS Sequence                    | 8  |

| MOSS Diagnostics - General Data Flow              | 0  |

| MMIO Test                                         | 3  |

| Basic Tests                                       | 4  |

| Post-Basic Tests                                  | 3  |

| MOSS Diagnostics Bypass Option                    | 2  |

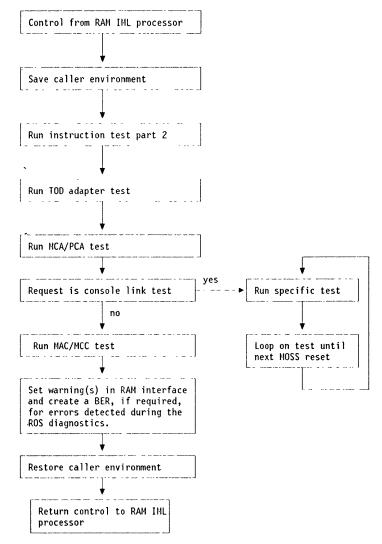

| RAM Mainline Controller                           | 4  |

| Instruction Test - Part 2                         | 5  |

| TOD Adapter Test                                  | 6  |

| MCA/PCA Diagnostics                               | 8  |

| MAC/MCC Diagnostics                               | 2  |

| Exit to RAM IML Processor                         | 7  |

| List of Abbreviations                             | 1  |

| Glossary X-                                       | 7  |

| Bibliography X-1                                  |    |

| Index                                             | 5  |

.

## Notices

References in this publication to IBM products, programs or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product, program, or service is not intended to state or imply that only IBM's product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any of IBM's intellectual property rights may be used instead of the IBM product, program, or service. Evaluation and verification of operation in conjunction with other products, except those expressly designated by IBM, is the user's responsibility.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577, U.S.A.

## **Electronic Emission Notices**

#### Federal Communications Commission (FCC) Statement

**Note:** This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

Properly shielded and grounded cables and connectors must be used in order to meet FCC emission limits. IBM is not responsible for any radio or television interference caused by using other than recommended cables and connectors or by unauthorized changes or modifications to this equipment. Unauthorized changes or modifications could void the user's authority to operate the equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

For Canada, Canadian Department of Communication Statement, GX27-3883, applies.

## **Trademarks and Service Marks**

The following terms, denoted by an asterisk (\*), used in this publication, are trademarks or service marks of IBM Corporation in the United States or other countries:

IBM System/370

The following terms, denoted by a double asterisk (\*\*), used in this publication, are trademarks of other companies:

Ethernet Xerox Corp.

## **Product Safety Information**

#### **General Safety**

This product meets IBM\* safety standards.

For more information, see the *IBM Telecommunication Products Safety Handbook*, GA33-0126.

#### **Safety Notices**

See Safety Notices located at the beginning of the Maintenance Information Procedures (MIP) manual, SY33-2054.

#### **Service Inspection Procedures**

The Service Inspection Procedures help service personnel check whether the IBM 3745 Communication Controller conforms to IBM safety criteria. They have to be used each time the 3745 safety is suspected.

The Service Inspection Procedures section is located at the beginning of the 3745 Maintenance Information Procedures manual.

The 3745 areas and functions checked through service inspection procedures are:

- 1. External covers

- 2. Safety labels

- 3. Safety covers and shields

- 4. Grounding

- 5. Circuit breaker and protector rating

- 6. Input power voltage

- 7. Power-ON indicator

- 8. Emergency power OFF.

## **About This Book**

## Who Should Use This Book

This book is intended for product support-trained customer engineers (PST CE) who maintain IBM 3745 Communication Controllers.

It describes the diagnostic programs used with the IBM 3745.

## How this Book Is Organized

This manual is divided into the following chapters:

Chapter 1. Diagnostic Overview

The diagnostic structure and the power diagnostic routines.

Chapter 2. CCU Diagnostics

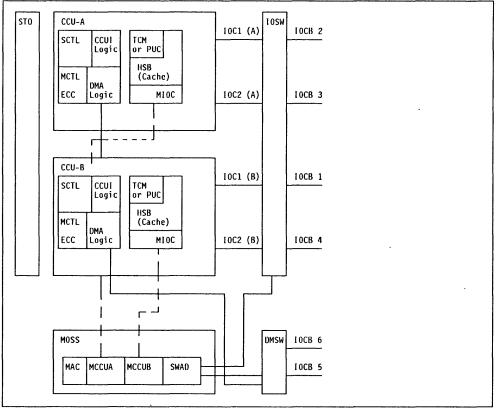

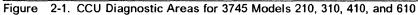

The CCU diagnostic group is divided into the following internal function tests (IFTs), which test:

Direct/indirect operations (IFT A) High-speed buffer (IFT B) Storage control CCUI/MCTL (IFT D) Storage control ECC/MCTL, storage access, and storage/high-speed buffer (IFT E) Storage control DMA functions (IFT F) IOC bus switch and DMA bus switch (IFT G) Full instruction set and interrupt mechanism, storage test and branch trace/address compare (IFT H)

Chapter 3. IOCB Diagnostics

The IOCB diagnostic group is divided into three IFTs that test:

IOC primary bus (IFT I) IOC secondary bus (IFT J) LSS and HSS attachment (IFT K)

Chapter 4. CAL Diagnostics

The CAL diagnostic group has only one IFT (IFT L), that tests the channel adapter data streaming functions.

Chapter 5. TSS Diagnostics

The TSS diagnostic group is divided into three IFTs that test:

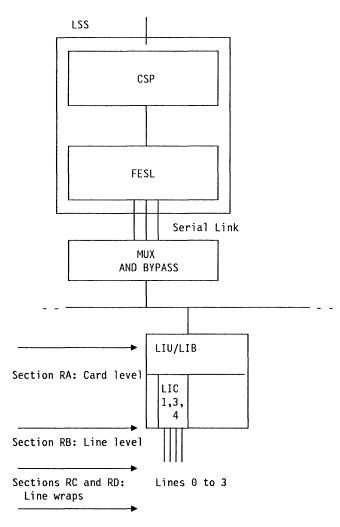

Front end scanner low-speed (IFT P) Multiplexing functions (IFT Q) Line interface coupling (IFT R)

• Chapter 6. TRSS Diagnostics

The TRSS diagnostic group has one IFT (IFT T), which tests the token-ring subsystem functions.

#### • Chapter 7. ESS Diagnostics

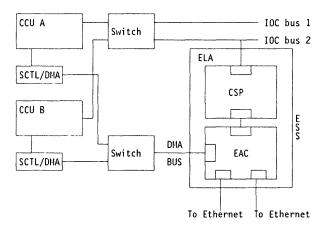

The ESS diagnostic group has one IFT (IFT U), which tests the Ethernet<sup>\*\*</sup> subsystem (ESS) and the Ethernet adapter card (EAC).

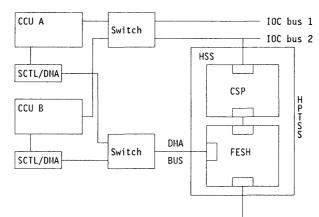

#### Chapter 8. HPTSS Diagnostics

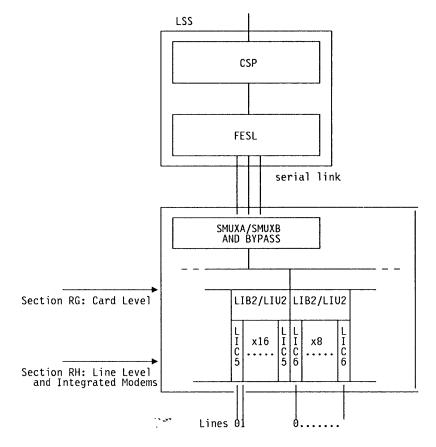

The HPTSS diagnostic group has one IFT (IFT V), which tests the high-performance TSS subsystem functions and DMA bus.

#### Chapter 9. MOSS Diagnostics

MOSS hardware diagnostics is split into two groups:

ROS diagnostics, which test the processing and control functions of  $\ensuremath{\mathsf{MOSS}}$

RAM diagnostics, which test MOSS adapter cards.

- · Appendixes for:

- Abbreviations

- Glossary

- Bibliography

- Index

### What is New in This Book

This book gives information about:

- The diagnostics routines for all Models of the IBM 3745 Communication Controller (including Models 130, 150, 170, 210, 310, 410, and 610).

- The Ethernet feature diagnostic routines.

-

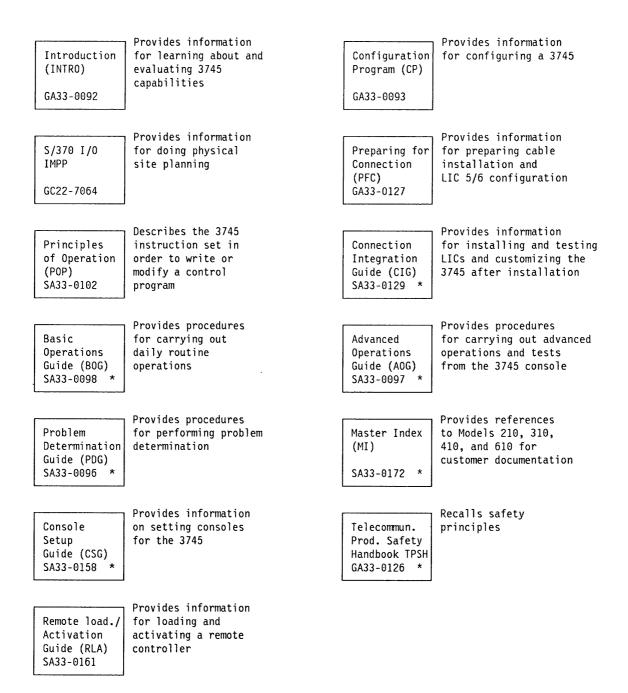

## Where to Find More Information

This manual complements:

- The IBM 3745 Maintenance Information Reference (MIR), SY33-2056, for IBM 3745 Models 210, 310, 410, and 610.

- The IBM 3745 Hardware Maintenance Reference (HMR), SY33-2066, for IBM 3745 Models 130, 150, and 170.

- The IBM 3745 Maintenance Information Procedures (MIP), SY33-2054 (for IBM 3745 Models 210, 310, 410, and 610) or SY33-2070 (for IBM 3745 Models 130, 150, and 170).

The reader should be trained on the 3745, and have an understanding of data communications and modems.

Prerequisite publication:

The Introduction to the IBM 3745 Communication Controller, GA33-0092 (for IBM 3745 Models 210, 310, 410, and 610) or GA33-0138 (for IBM 3745 Models 130, 150, and 170).

Corequisite manuals are:

- The 3745 Communication Controller, Problem Determination Guide, SA33-0096 (for all 3745 Models).

- The 3745 Communication Controller, Advanced Operation Guide, SA33-0097 (for all 3745 Models).

- The 3745 Communication Controller, Service Functions, SY33-2055 (for IBM 3745 Models 210, 310, 410, and 610) or SY33-2069 (for IBM 3745 Models 130, 150, and 170).

These manuals provide the procedures for operating the communication controller.

## **Service Personnel Definitions**

See the 3745 Maintenance Information Procedures (MIP).

XII IBM 3745 Diagnostic Descriptions

# Chapter 1. Diagnostic Overview

| Introduction                              |

|-------------------------------------------|

| Concurrent and Non-Concurrent Maintenance |

| Diagnostic Package 1-4                    |

| Diagnostic Monitoring                     |

| Diagnostic Control Monitor (DCM)          |

| Command Processor (CP) 1-5                |

| Diagnostic Control Facilities (DCF) 1-5   |

| Diagnostic Structure 1-5                  |

| Diagnostic Identification 1-5             |

| List and Duration of IFTs 1-6             |

| Manual Routines                           |

| Format of Repair Action Codes             |

| Power Diagnostics                         |

| Introduction                              |

| Control Panel Test                        |

| Power Control Bus Test                    |

| MMIO Bus Test                             |

| Power Analog Card Test 1-9                |

| Power Logic Card Test 1-9                 |

1-2 IBM 3745 Diagnostic Descriptions

· ·

-

## Introduction

The diagnostic programs are run to detect solid failures caused by the hardware in the 3745, and to isolate the field-replaceable unit (FRU) that caused the failure.

They are also run after a repair is performed to check that the controller is working correctly, and at first installation. Diagnostics must be run before and after an EC or an MES is installed.

Only the channel adapters, scanners, and telecommunication lines defined in the 3745 configuration data file (CDF) are tested.

Run the CDF 'VERIFY' option when you suspect a discrepancy between the machine configuration and the CDF. See the *3745 Service Functions* manual.

A reference code, an error return code, and error messages are displayed on the console when a diagnostic program detects a failure (Figure 1-1). Refer to the 3745 *Maintenance Information Procedures (MIP)* manual for handling the reference code.

| FUNCTION ON SCREEN: | OFFLINE DIAGS                    | FRU REMOVAL => POWER OFF |

|---------------------|----------------------------------|--------------------------|

| R RERUN REQUEST     | *RH R303B160 *                   |                          |

| A ABORT ROUTINE     | *RAC 911010012 * ERR BIT DDDB    |                          |

| C CANCEL REQUEST    | *ERC RB052B05 *                  | ERROR COUNT 00001        |

| G GO                | ****                             |                          |

| N MODIFY OPTIONS:   |                                  |                          |

| S/LE/AL/ALS/B/DM    |                                  |                          |

| NW/W                | START 21:22:08 STOP 21:23:02     |                          |

| C1/CNNN/C           | REQUEST: RB05                    | TSS DIAG RUNNING         |

| R1/RNNN             | OPTIONS: S NW C1 R1 BR           | ROUTINE RB05 TSS 01 L 00 |

| BR/NBR              |                                  | LINE AD 0176             |

|                     |                                  |                          |

| ĺ                   | ENTER REQUEST ACCORDING TO THE D | IAG MENU                 |

|                     | ==>                              |                          |

| ===> *              | ***ERROR FOUND***                |                          |

|                     |                                  |                          |

| F1:END F2:MENU F3   | : ALARM                          |                          |

Figure 1-1. Error Found Panel - Example

The RAC field contains the **repair action code** (911 in the example), see "Format of Repair Action Codes" on page 1-7, and the address number.

The error return code (ERC) field contains the routine ID and a 4-byte ERC code (routine RB05 and ERC 2B05 are shown in the example).

The RH field contains the reference code (R303B160 in the example).

#### **Concurrent and Non-Concurrent Maintenance**

Most components or subsystems of the 3745 can be diagnosed and repaired while the controller continues to run in a partially degraded mode.

The CCU must be initialized by an IPL before concurrent diagnostics can be run. See the 3745 Service Functions, for more details.

For 3745 Models 210, 310, 410, and 610, the modularity of the power supplies allows concurrent repair per subsystem (CCU, MOSS), or per group of adapters (CAL, TSS, TRSS, ESS, HPTSS). Repair action is done with the affected subsystem powered off.

Warning: When you are running offline diagnostic programs, the customer cannot use the 3745.

### **Diagnostic Package**

The 3745 diagnostics consist of:

- 1. Channel adapter OLTs are stored in the host, and the OLT responder is stored on the 3745 disk. OLTs are run under the control of the host. Refer to *Channel Adapter Online Tests*, *D99-3745A*.

- 2. ST370 and ST4300 (system tests).

- 3. IML checkout programs, for details of these programs, see the "IML/IPL" chapter in the 3745 Maintenance Information Reference manual (for 3745 Models 210, 310, 410, and 610).

- 4. Diagnostics stored on the 3745 disk, which can be run off-line or online (concurrent).

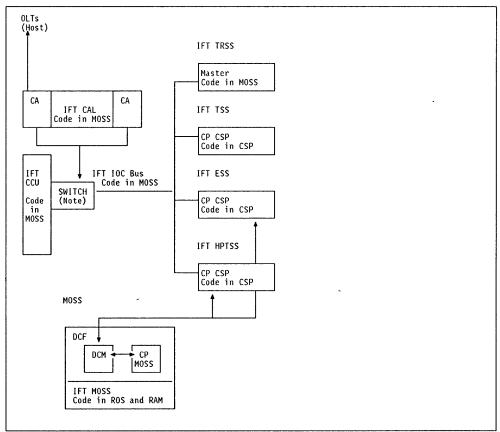

Figure 1-2. Diagnostic Code Locations

Note: SWITCH applies only to 3745 Models 210, 310, 410, and 610.

#### **Diagnostic Monitoring**

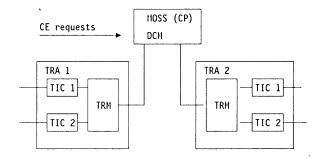

To run offline diagnostics, MOSS must be initialized with its microcode (IML). Concurrent diagnostics can be run when the machine is in use. The diagnostics are monitored by the diagnostic control monitor (DCM) and the associated command processor (CP).

The DCM can operate in *offline* mode (function ODG on the maintenance menu), or in *concurrent* mode (function CDG).

#### **Diagnostic Control Monitor (DCM)**

The *diagnostic control monitor* is loaded when you select the diagnostic programs from the 3745 menu 3 display. It automatically restricts the diagnostic testing to elements defined in the *configuration data file* (CDF), and it selects the type of diagnostic run depending on the selected mode (offline or concurrent).

To communicate with the DCM use the operator console. The DCM allows *diagnostic program selection* and choice of options within the selection. It sends your commands to the command processor, and displays diagnostic results, such as a reference code, on the console.

#### **Command Processor (CP)**

The *command processor* is loaded in the 3745 subsystem (MOSS, ESS, HPTSS, or TSS) where the selected diagnostic is to be run. It reports diagnostic events and diagnostic results.

#### **Diagnostic Control Facilities (DCF)**

The DCM and the CP together provide a set of facilities for running the diagnostics, which are collectively referred to as the *diagnostic control facilities (DCF)*. See also "FRU List for Unexpected DCF Errors" on page 1-8.

Testing the 3745 with the diagnostics assumes that MOSS and scanner IML is possible. When the option *run all diagnostics* is selected, testing starts from the smallest element in a subsystem, and builds up step-by-step on error-free elements until a subsystem is completely tested. The diagnostics then continue with the other subsystems until the 3745 is completely tested.

For more information on how to run the diagnostics, see the 3745 Service Functions manual.

#### **Diagnostic Structure**

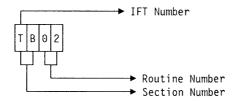

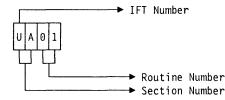

The diagnostics are arranged in groups, internal functional tests (IFTs), sections, and routines.

- Group:

Set of IFTs that tests a 3745 subsystem (the TSS group, for example).

IFT:

Internal functional test that is often divided into sections that can be loaded and executed one at a time

Section:

Set of routines that tests a particular adapter, or a component of a subsystem.

- Routine: The shortest executable test.

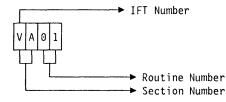

#### **Diagnostic Identification**

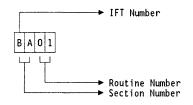

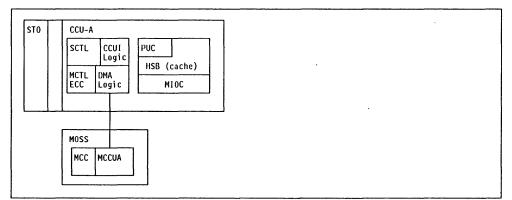

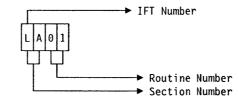

The identification contains the IFT number, the section number, and the routine number:

### List and Duration of IFTs

The timing estimates for the diagnostics groups and their IFTs are the following:

- CCU IFTs: more than 38 minutes per CCU.

- IOCB IFTs: 5 minutes per IOCB + 1 minute per adapter.

- CAL IFT: more than 2 minutes per CA.

- TSS IFTs: 2-8 minutes for a TSS without LIC types 5 and 6, 1-12 minutes for a TSS with LIC types 5 and 6.

- TRSS IFTs: 1-15 minutes for the TRSS.

- · ESS IFTs: 3 minutes per ELA in the ESS.

- HPTSS IFT: 4 minutes per HSS in the HPTSS.

Total run 'all' = 50 minutes (minimum) to 470 minutes (maximum).

Note: MOSS diagnostics are not run as part of the offline or concurrent diagnostics. The MOSS is diagnosed upon one of five events, for details of starting MOSS diagnostics see the MOSS Diagnostics chapter in this manual.

#### Manual Routines

A definition of manual routines is given in the 3745 Service Functions manual.

Manual Intervention Routines include:

AT05 (Network Power Off), AR04, and BF03.

WA01, scoping routine. LO01 (external wrap test for CA), LG02, LI03, LI04, LJ03, and LK02.

RCxx, Worldwide wrap test routines.

RDxx, Japan-only wrap test routines. RH59, Loop-3 wrap test routine with line wrap block (applicable to TSS with LIC5 or LIC6).

UF02 and UF03, external wrap tests for ESS.

Vixx and VJxx, external wrap tests for HPTSS.

All manual routines of a given diagnostic group are listed at the beginning of each chapter.

### Format of Repair Action Codes

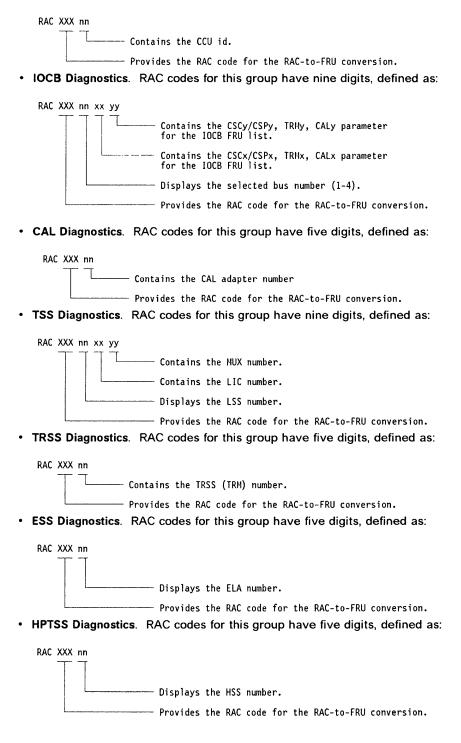

The RAC code field displayed in an *Error Found* panel is formatted depending on the diagnostic group selected. RAC codes for the individual groups are described below.

• CCU Diagnostics. RAC codes for this group have five digits, defined as:

## FRU List for Unexpected DCF Errors

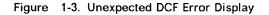

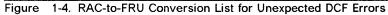

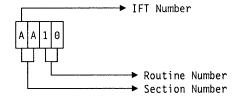

The RAC field displays codes after an *unexpected DCF error* has occurred, see the display example in Figure 1-3. Descriptions of the codes possible in the field and of the associated FRUs are given in Figure 1-4.

| ¢                 | ***************** ORIGIN: MOSS<-DCM<br>*RN 3050541 * LEVEL : X'01'<br>*RAC 541 * LVLNSK: X'00'<br>* |

|-------------------|-----------------------------------------------------------------------------------------------------|

|                   | *************** ADDIT INFO:                                                                         |

| ***** ABEND ***** | MAC I/O RC=X'1162'                                                                                  |

| PF1 : RETURN TO   | ON MACRO KO OFS=058C                                                                                |

| MAIN MENU         | START 00:07:40 STOP 00:08:01                                                                        |

|                   | DIAG HUNG                                                                                           |

| ===>              | JNEXPECTED ERROR                                                                                    |

| F1:END F2:MENU F  | 3: ALARM                                                                                            |

| RAC                                                                                                                                                                                                                                                                                                                                     | Associated FRU List                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 501, 502, 503, 504, 505, 509<br>507, 508<br>506, 50A, 50B, 50C, 50D, 50E, 50F<br>511, 514, 515, 516, 517, 518, 519<br>510, 512, 51A, 51B, 51C, 51D, 51E, 51F<br>520, 528, 529, 528, 522, 520, 52E, 52F<br>521, 522, 523, 524, 525, 526, 527, 52A<br>530, 535, 536, 537, 53F, 540<br>531<br>532, 533, 534, 539<br>538<br>53A<br>53B, 53C | Microcode error<br>CSC/CSP, FES, MUX, EAC<br>Microcode error<br>DFA, HDD<br>Microcode error<br>MAC/MAC2/MCC, TCN/PUC<br>MAC/MAC2/MCC, SCTL/SCTL2, TCN/PUC<br>SCTL/SCTL2, TCM/PUC<br>TCN/PUC<br>SCTL/SCTL2, ST0/STG1, TCM/PUC<br>MAC/MAC2/MCC, TCM/PUC |

| 53D<br>541, 542, 543, 544, 546, 547, 548<br>545<br>549<br>54A<br>54B<br>54C<br>54C<br>54C<br>54F<br>54F<br>550, 552, 553, 557, 559, 558, 55C                                                                                                                                                                                            | Microcode error<br>CSP, FES, EAC<br>TCM/PUC<br>MAC/MAC2/MCC, TCM/PUC<br>MAC/MAC2/MCC, CAL<br>PLC/PCC, PS-4<br>MAC/MAC2/MCC<br>SCTL/SCTL2, TCM/PUC<br>Microcode error<br>MAC/MAC2/MCC, IOSW/IOSW2, DMSW                                                |

| 551, 554, 555, 556<br>558, 559<br>55D, 55E, 55F, 560, 561, 566, 567, 568,<br>569, 56A, 568, 56C, 56D, 56E, 56F<br>561, 562, 563<br>564                                                                                                                                                                                                  | MAC/MAC2/MCC, IOSW/IOSW2<br>MAC/MAC2/MCC<br>Microcode error<br>Microcode error<br>CSP, FES, EAC<br>PLC/PCC, PS-4                                                                                                                                      |

| Note: MAC/MAC2, SCTL/SCTL2, IOSW/IOSW2, I<br>apply to 3745 Models 210, 310, 410,<br>MCC, CSC, and PCC apply to 3745 Moc<br>TCM applies to 3745 Models 210 and                                                                                                                                                                           | and 610.<br>lels 130, 150, and 170.                                                                                                                                                                                                                   |

## **Power Diagnostics**

#### Introduction

The power diagnostics test the interfaces and some internal functions of the 3745 power control subsystem.

Power diagnostics are run when manually selected at the 3745 control panel, and when the power on reset (POR) sequence is running in the power control card(s).

#### Notes:

- 1. For Models 130, 150, and 170: There is only one power control card (PCC) and no power logic card.

- 2. For Models 210, 310, 410, and 610: There are several power control cards (PAC) and a power logic card (PLC).

During normal 3745 operation with the machine powered on and MOSS IML completed, the MOSS code performs cyclic testing of the power control code (using watchdog counters). If a loop is detected, a BER indicating **power control microcode error** is logged, and a **recovery** request is sent to the power control code.

#### **Control Panel Test**

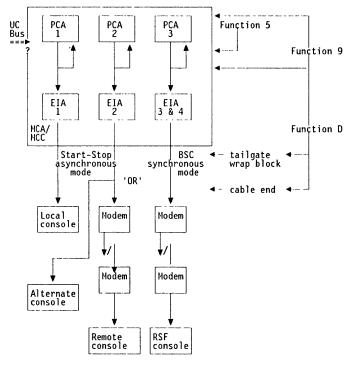

This test checks the control panel and its interface with the power control card(s). It is manually selected by setting Function 5 on the control panel.

#### **Power Control Bus Test**

The power control buses connecting the power blocks to the power control card(s) are checked using a wrap block. This test is selected by setting Function C on the control panel. The test result is displayed on the control panel: code '004' indicates test OK, code '005' indicates that the test failed.

#### MMIO Bus Test

This test verifies that the MMIO bus connecting the power control card(s) to the MOSS, is running error-free. The test is done at each MOSS IML phase, see "MMIO Test" on page 9-13. If the test is not successful, the MOSS IML phase is stopped and code '002' is displayed on the control panel.

#### **Power Analog Card Test**

When the 3745 machine is powered on, the power logic code or the power logic card (PLC) code performs a cyclic test of the PAC/PCC card. If an error is detected, a BER is logged indicating 'PAC/PCC KO'.

#### **Power Logic Card Test**

At each power on reset (POR) sequence on the Power Control Subsystem, or when the MOSS code generates a 'recovery' process on the power control code, a number of diagnostic routines are run by the power control code:

- Microprocessor test

- ROS checksum test

- RAM (non-destructive) test

- TOD adapter test.

If one of these tests fails, the power control code hangs and the display on the control panel goes blank.

1-10 IBM 3745 Diagnostic Descriptions

. •

.

-

# Chapter 2. CCU Diagnostics.

## **Conventions Used in This Chapter**

CCU diagnostics are applicable to all 3745 models unless the routine or function description is qualified as follows:

- (Models 130, 150, 170) for 3745 Models 130, 150, and 170 only.

- (Models 310 and 610) for 3745 Models 310 and 610 only.

- (Models 210 and 410) for 3745 Models 210 and 410 only.

| Introduction                                                                                                       | 2-9          |

|--------------------------------------------------------------------------------------------------------------------|--------------|

| Requirements                                                                                                       | 2-10         |

| Selection                                                                                                          | 2-10         |

| Additional Information Field Descriptions                                                                          | 2-11         |

| Concurrent Mode (CDG)                                                                                              | 2-13         |

| Running Time                                                                                                       | 2-13         |

| Manual Intervention Routine                                                                                        | 2-13         |

| Pattern Table for Parity Checkers (SPATG)                                                                          | 2-13         |

| RAC-to-FRU Conversion List for CCU                                                                                 | 2-14         |

| CCU Unexpected Errors                                                                                              | 2-14         |

| Routine Descriptions                                                                                               | 2-15         |

| AA01 - MOSS Inoperative                                                                                            | 2-13         |

| AA03 - CCU Parity Check During Write                                                                               | 2-15         |

| AA05 - MCCU-to-MIOC Interconnection                                                                                | 2-16         |

| AA06 - Scan Register                                                                                               | 2-16         |

| AA07 - String Select Register                                                                                      | 2-16         |

| AA08 - Step Register - First Part                                                                                  | 2-17         |

| AA09 - Step Register - Second Part                                                                                 | 2-17         |

| AA10 - String Address Decoder AA11 - Step Register - Third Part                                                    | 2-17         |

| AA11 - Step Register - Inird Part                                                                                  | 2-1/         |

| AB01 - CCU LSSD String - First Part AB02 - CCU LSSD String - Second Part                                           | 2-10         |

| AB03 - CCU LSSD String - Third Part                                                                                | 2-18         |

| AB04 - Storage Error 1 and 2 Tags                                                                                  |              |

| AC01 - CCU-to-MOSS status C Register                                                                               | 2-19         |

| AC02 - CCU-to-MOSS Status A Register AC03 - CCU-to-MOSS Status B Register                                          | 2-19         |

| AC03 - CCU-to-MOSS Status B Register                                                                               | 2-19         |

| AC05 - Low Level Interrupt to MOSS Interconnection                                                                 | 2-20         |

| AC06 - MIOC Error Check After CCU Initialization                                                                   | 2-20         |

| AC07 - High Level Interrupt Line from CC0-10-MOSS                                                                  | 2-20         |

| AC09 - MOSS IOC2 Error Path                                                                                        | 2-21         |

| AC10 - CCU Hard Check Adapter Stop Path                                                                            | 2-21         |

| AC10 - CCU Hard Check Adapter Stop Path                                                                            | 2-21         |

| AC13 - Bypass CCU Check Stop                                                                                       | 2-22         |

| AC14 - CCU Check Stop Path                                                                                         | 2-22         |

| AC15 - CCU Check Reset Function AC15 - CCU Check Reset Function                                                    | 2-22         |

| AD01 - ROSAR Byte 0 Parity Checker                                                                                 | 2-22         |

| AD02 - ROSAR Byte 1 Parity Checker                                                                                 | 2-23         |

| AD03 - LSAR Parity Checker                                                                                         | 2-23         |

| AD06 - Address Compare Control Register Parity Checker                                                             | 2-24         |

| AD08 - MOSS Data Operand Register Byte X Parity Checker<br>AD09 - MOSS Data Operand Register Byte 0 Parity Checker | 2-24         |

| AD09 - MOSS Data Operand Register Byte 0 Parity Checker                                                            | 2-24         |

| AD10 - MOSS Data Operand Register Byte 1 Parity Checker<br>AE01 - Mode Control Register B                          | 2-24         |

| AE01 - Mode Control Register B                                                                                     | 2-25<br>2-25 |

| AE03 - Branch Trace Level Control Register                                                                         |              |

| AE04 - Address Compare Control Register                                                                            | 2-25         |

| AE05 - Mode Control Register a                                                                                     |              |

| AE06 - Local Store Address Register                                                                                |              |

| AE07 - ROS Address Register Byte 0                                                                                 |              |

| AE08 - ROS Address Register Byte 1                                                                                 | 2-26         |

| AE09 - MOSS-to-CCU Status Register AE13 - CCU-to-MOSS Status D Register                                            | 2-27         |

| AE13 - CCU-to-MOSS Status E Register                                                                               |              |

| AE15 - CCU-to-MOSS Status F Register                                                                               | 2-27         |

| AE16 - MOSS Data Operand Register Byte X                                                                           | 2-28         |

| AE17 - MOSS Data Operand Register Byte 0                                                                           | 2-28         |

| AE18 - MOSS Data Operand Register Byte 1                                                                           | 2-28         |

| AK01 - ROS Contents                                                                                                | 2-29         |

| AK02 - ROS Addressing Control                                                                                      | 2-29         |

| AK03 - ROS Word Chaining, CCU                                                                                      | 2-29<br>2-30 |

| AL01 - Address Compare Address 1 Register, CC0                                                                     |              |

| AL02 - Address Compare Address 2 Register                                                                          |              |

| AL04 - Branch Trace Upper Limit Register                                                                           |              |

| AL06 - Local Store Addressing                                                                                      |              |

|                                                                                                                    |              |

~~'

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.04                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| AL07 - Local Store Data Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-31                                                                                                                                 |

| AM01 - Work Register 1 Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |

| AM03 - Work Register 2 Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-32                                                                                                                                 |

| AM04 - Work Register 3 Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-32                                                                                                                                 |

| AM05 - Work Register 4 Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-32                                                                                                                                 |

| AM06 - Work Register 5 Indirect Read AM07 - Work Register 6 Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-33                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                      |

| AM08 - Work Register 7 Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-33                                                                                                                                 |

| AM10 - Storage Address Register Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                      |

| AM11 - IOC1 Address Register Indirect Read AM12 - IOC1 Data Register Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-33                                                                                                                                 |

| AM12 - IOC1 Data Register Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-34                                                                                                                                 |

| AM14 - IOC2 Data Register Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-34                                                                                                                                 |

| AM15 - Lagging Address Register Indirect Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-34                                                                                                                                 |

| AN01 - Work Register 1 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-35                                                                                                                                 |

| AN02 - Work Register 2 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-35                                                                                                                                 |

| AN03 - Work Register 3 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |

| AN04 - Work Register 4 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-35                                                                                                                                 |

| AN05 - Work Register 5 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-35                                                                                                                                 |

| AN06 - Work Register 6 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-36                                                                                                                                 |

| AN07 - Work Register 7 Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-30                                                                                                                                 |

| ANOG - Mistruction Address Register Indirect Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-30                                                                                                                                 |

| AN09 - Storage Address Register Indirect Write A001 - ALU Compare Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-30                                                                                                                                 |