# 3745 Communication Controller

SY33-2066-2

# Hardware Maintenance Reference (HMR)

#### Third Edition (March 1991)

This major revision obsoletes SY33-2066-1. Extensive changes have been made throughout this edition, and this manual should be read in its entirety.

Changes are made periodically to the information herein. Any such changes will be reported in subsequent revisions or Technical Newsletters. Before using this publication in connection with the operation of IBM systems, consult the latest *IBM System/370, 30xx, 4300, and 9370 Processors Bibliography*, GC20-0001.

The drawings and specifications contained herein shall not be reproduced in whole or in part without written permission. IBM has prepared this service manual for the use of IBM customer engineers in the installation, maintenance. or repair of the specific machines indicated. IBM makes no representations that it is suitable for any other purpose.

Publications are not stocked at the addresses given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to either of the following:

- International Business Machines Corporation Department 6R1LG 180 Kost Road, Mechanicsburg. PA 17055 U.S.A.

- IBM France, Centre d'Etudes et Recherches Service 0762 BP 79 06610 La Gaude France

#### © Copyright International Business Machines Corporation 1989, 1991. All rights reserved.

Note to U.S. Government Users – Documentation related to restricted rights – Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# **Special Notices**

References in this publication to IBM products, programs. or services do not imply that IBM intends to make these available in all countries in which IBM operates.

Any references to an IBM licensed program or other IBM product in this publication is not intended to state or imply that only IBM's program or other product may be used. Any functionally equivalent program that does not infringe any of IBM's intellectual property rights may be used instead of the IBM product. Evaluation and verification of operation in conjunction with other products. except those expressly designated by IBM, is the user's responsibility.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license enquiries, in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577.

The following terms, DENOTED BY AN ASTERISK (\*). used in this publication, are trademarks of the IBM Corporation in the United States or other countries:

IBM LPDA MVS NetView OS/2 PS/2 RETAIN VSE VTAM

## Safety

#### **General Safety**

For general safety information, see:

• Telecommunication Products Safety Handbook, GA33-0126.

#### **Safety Notices**

See Safety Notices located at the beginning of the Maintenance Information Procedures manual.

#### **Service Inspection Procedures**

The *Service Inspection Procedures* help service personnel check whether the 3745 conforms to IBM\* safety criteria. They have to be used each time the 3745 safety is suspected.

The Service Inspection Procedures section is located at the beginning of the 3745 Maintenance Information Procedures (MIP) manual, SY33-2070.

The 3745 areas and functions checked through service inspection procedures are:

- 1. External covers

- 2. Safety labels

- 3. Safety covers and shields

- 4. Grounding

- 5. Circuit breaker and protector rating

- 6. Input power voltage

- 7. Power-ON indicator

- 8. Emergency power OFF.

#### Federal Communications Commission (FCC) Statement

**Note:** This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

Properly shielded and grounded cables and connectors must be used in order to meet FCC emission limits. IBM is not responsible for any radio or television interference caused by using other than recommended cables and connectors or by unauthorized changes or modifications to this equipment. Unauthorized changes or modifications could void the user's authority to operate the equipment.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

--!ŧ

# Contents

0

0

0

1

0

D

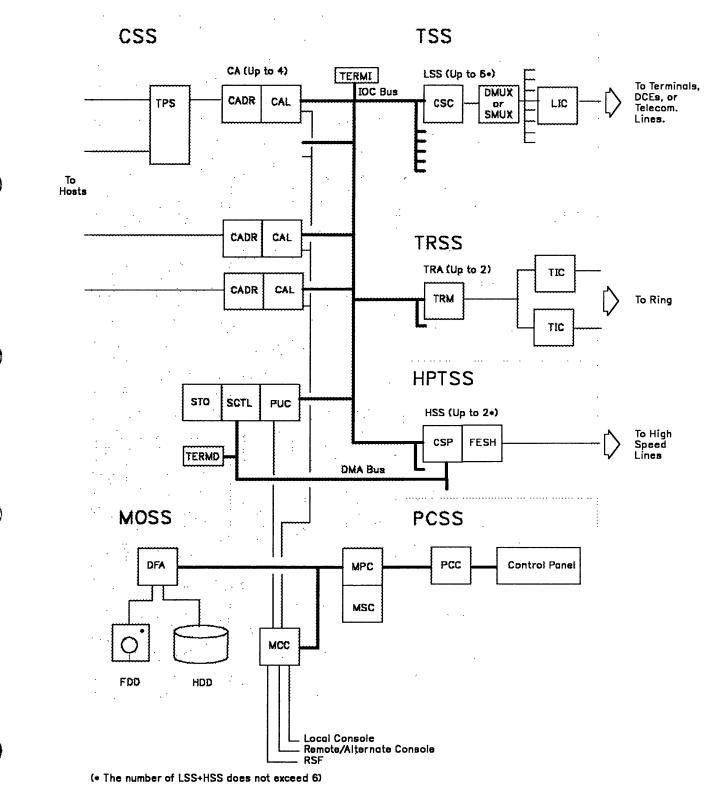

| Chapter 1. General Information                             |       |

|------------------------------------------------------------|-------|

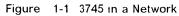

| 3745 in a Network                                          |       |

| Identification and Capacity                                | 1-5   |

| Controller Structure                                       | 1-6   |

| Programming Support and Network Management                 | 1-17  |

| Using the Library for Service                              |       |

| Maintenance                                                |       |

|                                                            | . 20  |

| Chapter 2. Central Control Unit (CCU)                      | 2-1   |

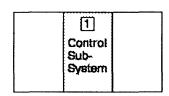

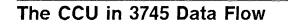

| The CCU in 3745 Data Flow                                  |       |

|                                                            |       |

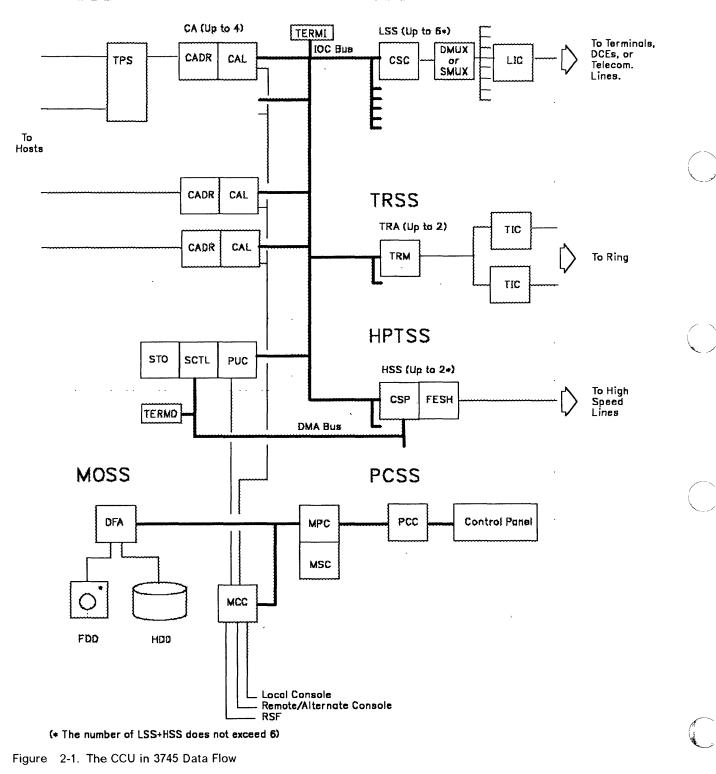

| General Description                                        |       |

| Functional Description                                     |       |

| CCU Environment                                            |       |

| Main Storage                                               |       |

| CCU-to-Storage Interconnection                             |       |

| CCU to and from Adapters                                   |       |

| CCU to and from MOSS                                       | 2-39  |

| CCU Diagnostics                                            | 2-40  |

| Performance Test Points                                    | 2-46  |

|                                                            |       |

| Chapter 3. Buses                                           | 3-1   |

| The Buses in 3745 Data Flow                                |       |

| Generalities                                               |       |

| Bus Propagation Cards (BPC1/BPC2)                          |       |

|                                                            |       |

| Adapter Addressing                                         |       |

| Adapter Bypass Mechanism                                   |       |

| IOC Bus Scoping Routine                                    | 3-49  |

| Chapter 4. Transmission Subsystem (TSS)                    | 4-1   |

|                                                            |       |

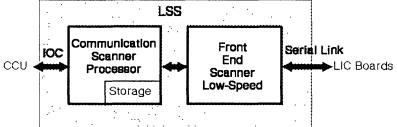

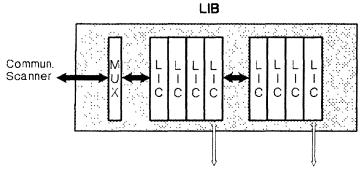

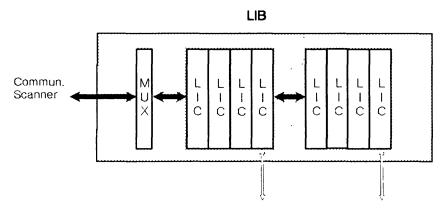

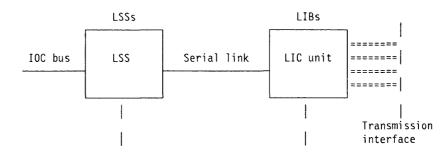

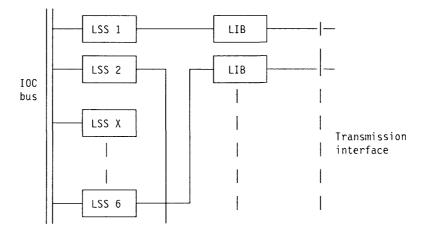

| Low-Speed Scanner (LSS)                                    |       |

| LIC Board                                                  |       |

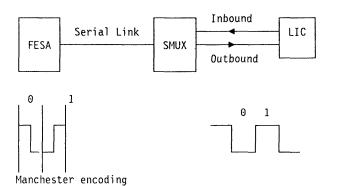

| Serial Link (SL)                                           |       |

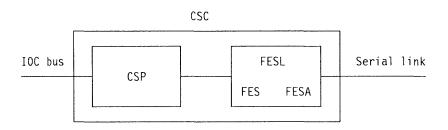

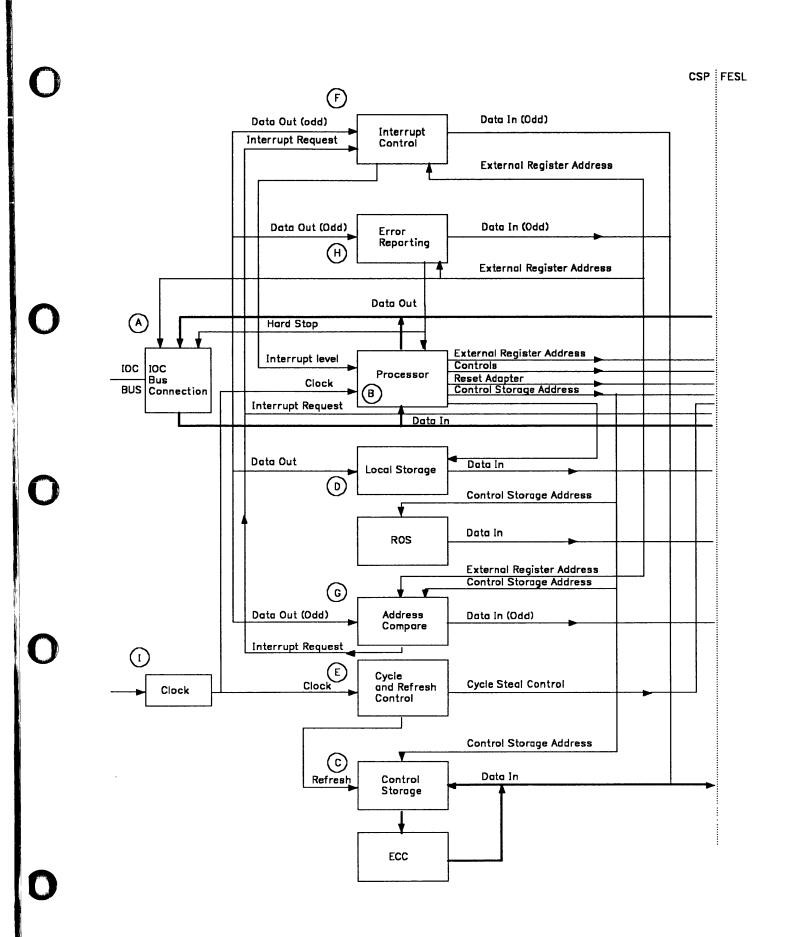

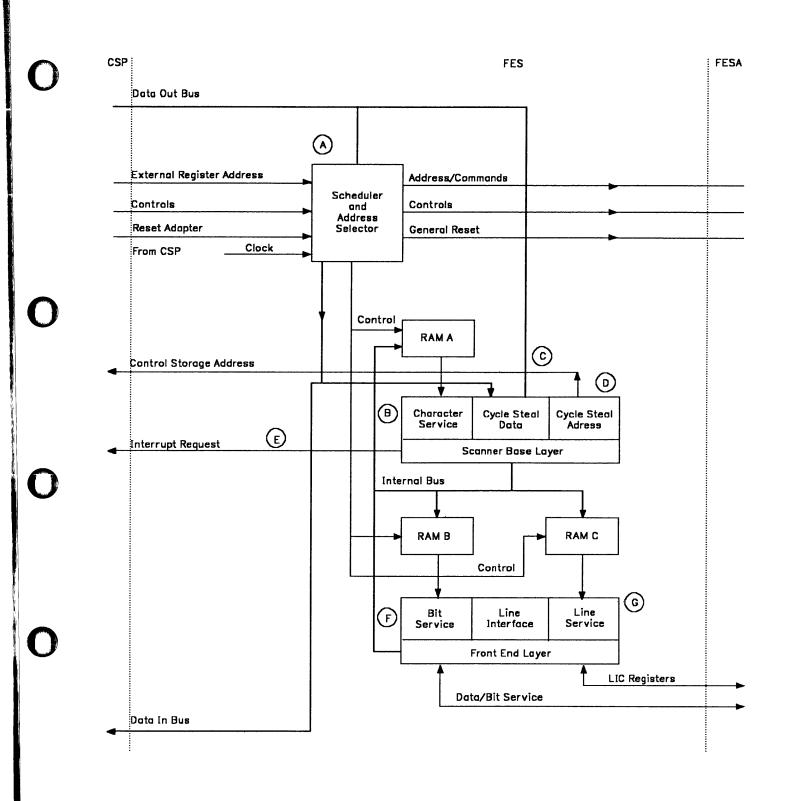

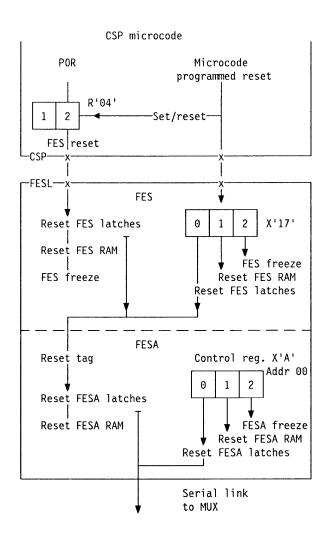

| Communication Scanner Processor (CSP)                      |       |

| Front-End Scanner (FES)                                    |       |

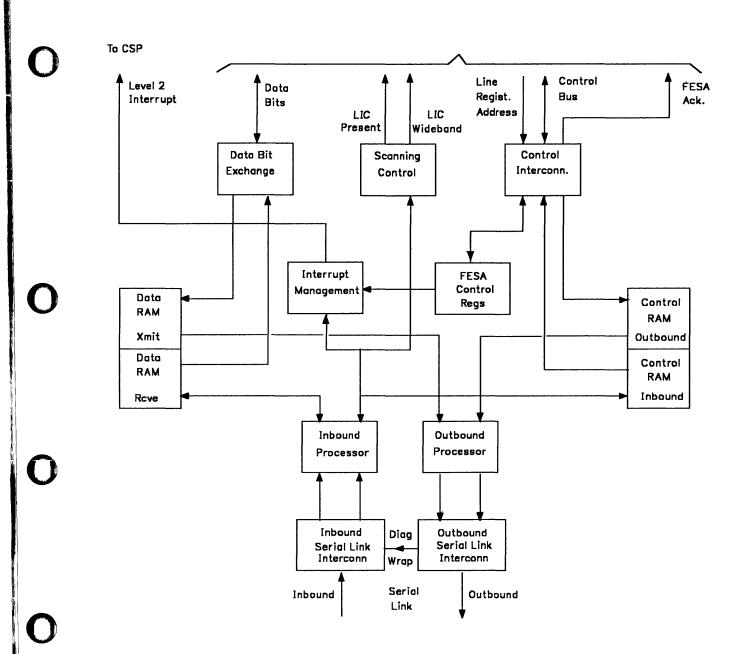

| Front-End Scanner Adapter (FESA)                           | 4-26  |

| Serial Link (SL)                                           | 4-34  |

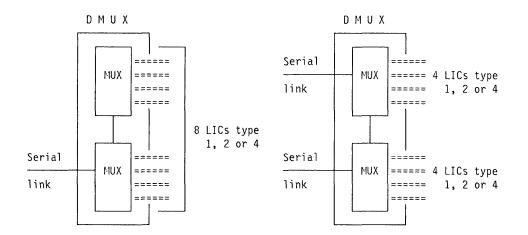

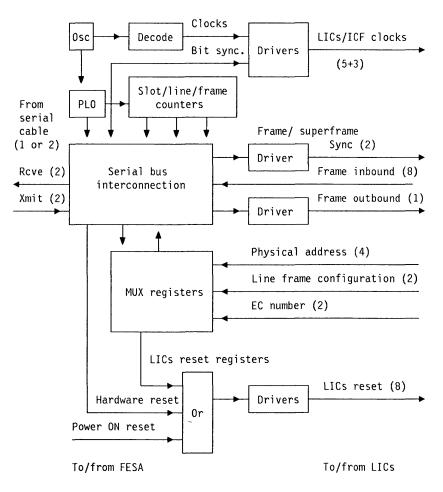

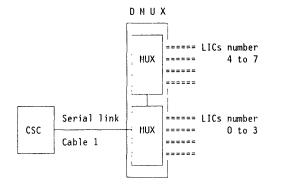

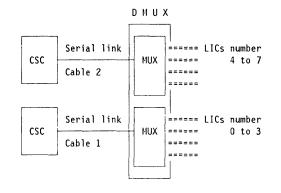

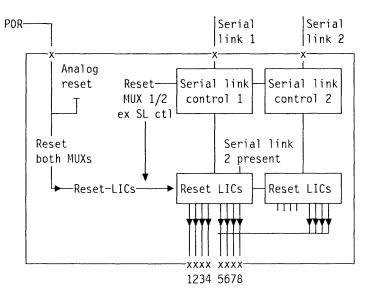

| Double Multiplexer Card (DMUX)                             | 4-35  |

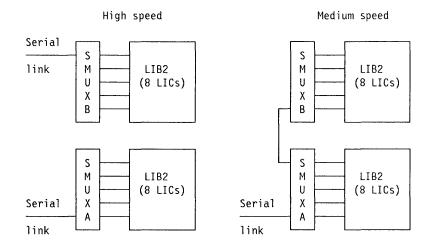

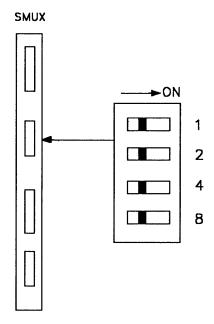

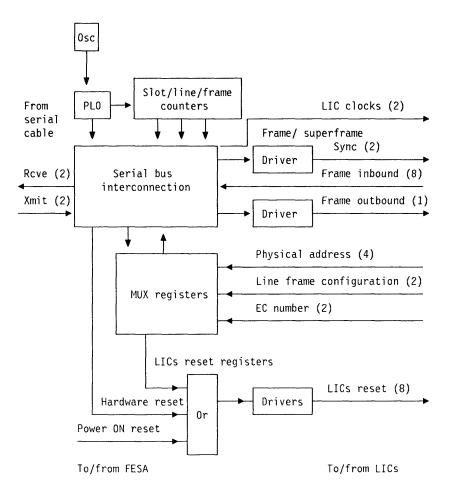

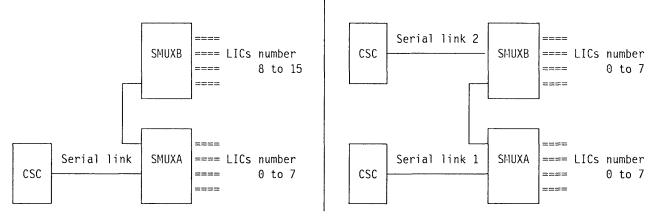

| Single Multiplexer Card (SMUXA/B)                          | 4-39  |

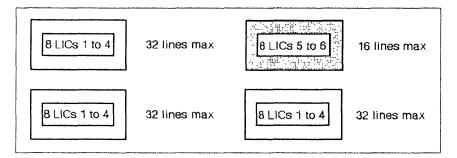

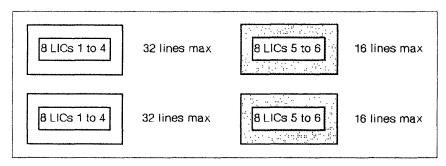

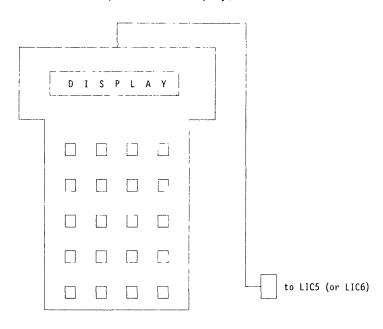

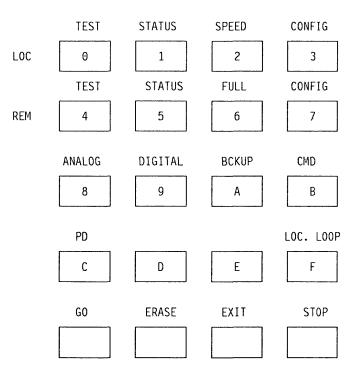

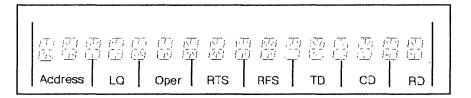

| LIC Types 1 to 4 Cards                                     |       |

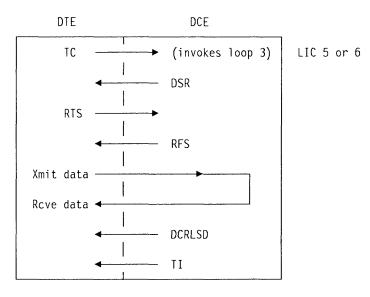

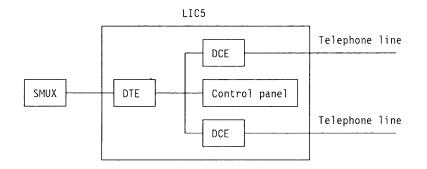

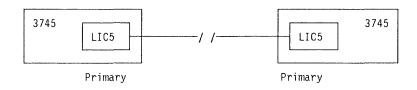

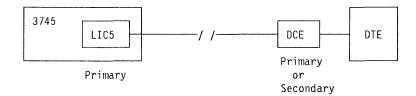

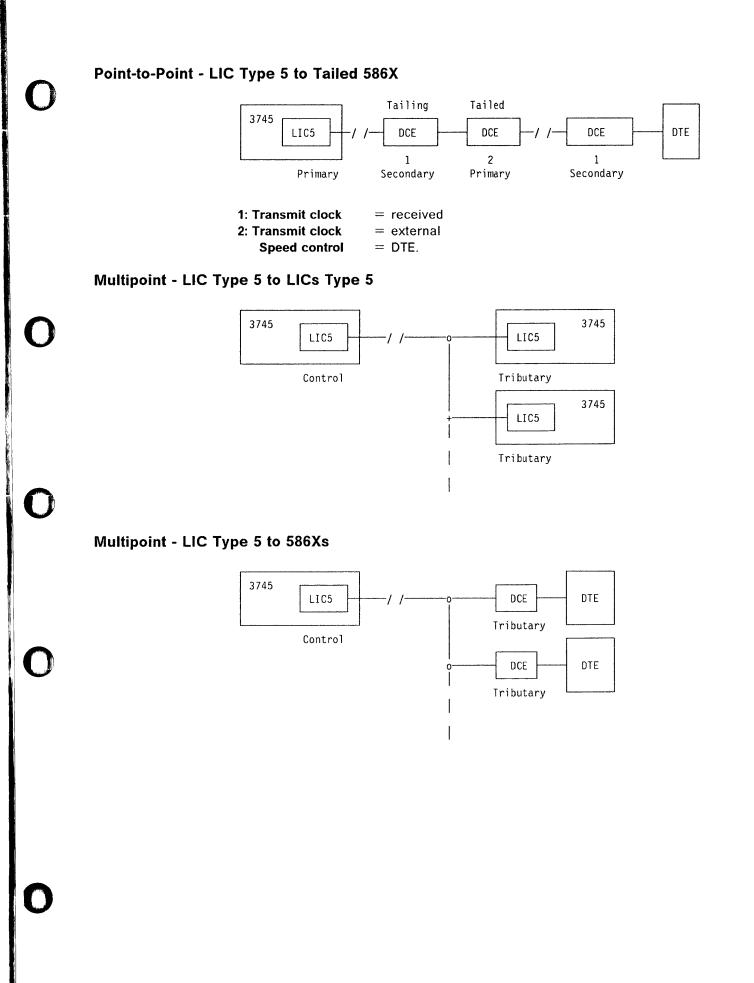

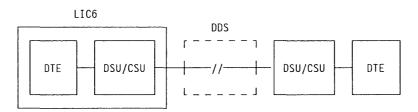

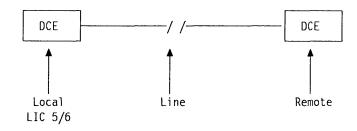

| LIC Types 5 and 6 DTE Function                             |       |

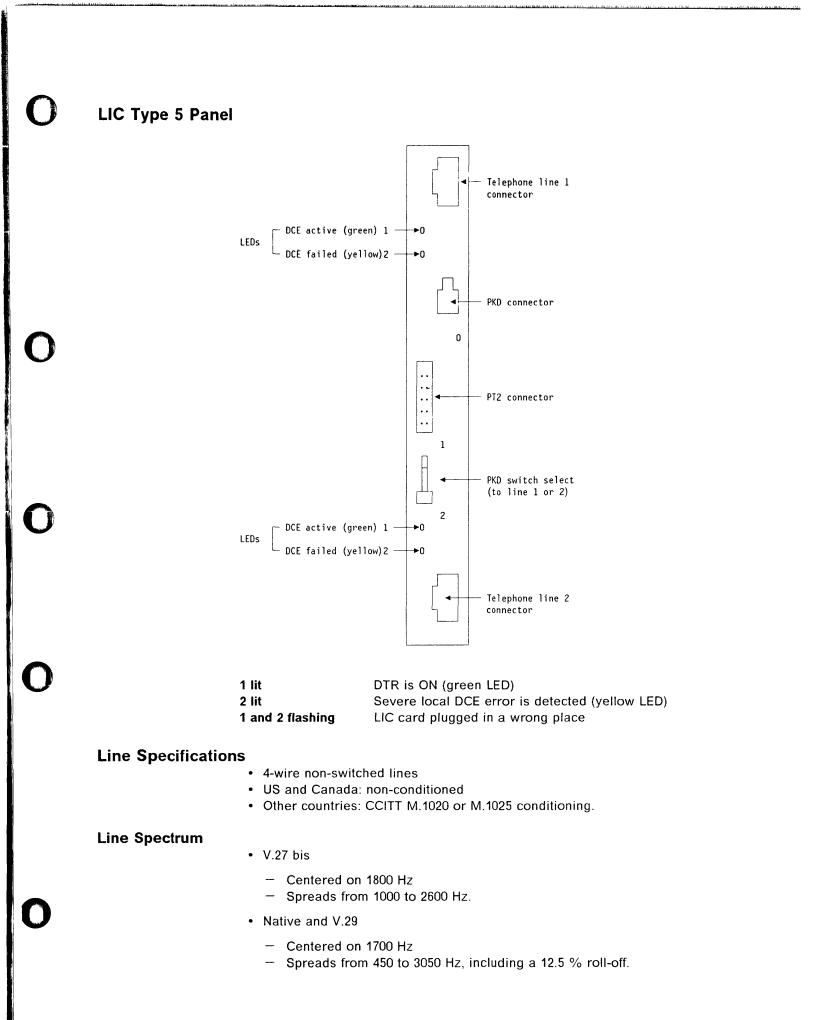

| LIC Type 5 DCE Function                                    |       |

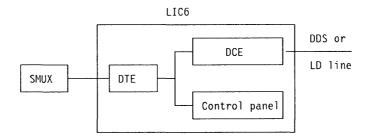

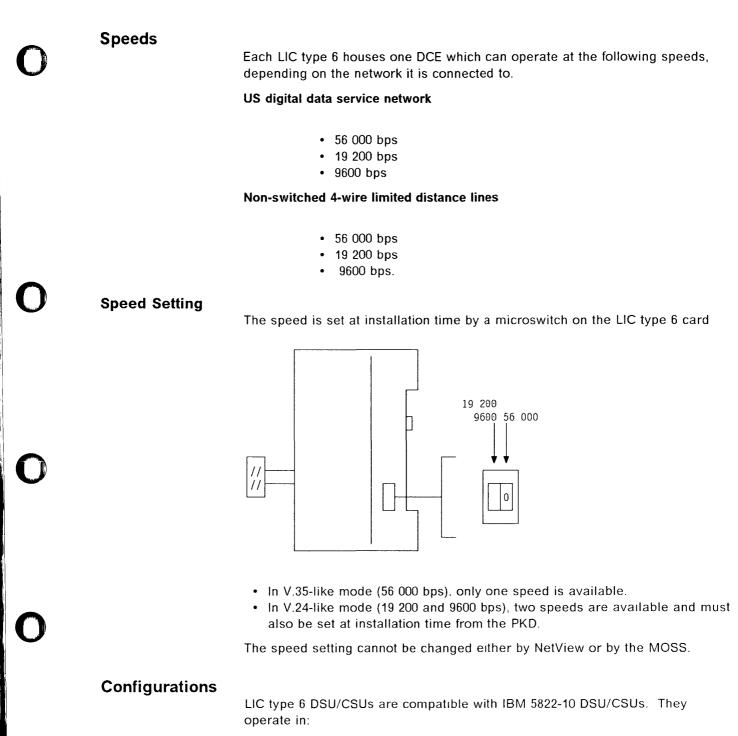

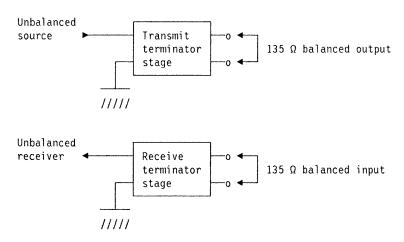

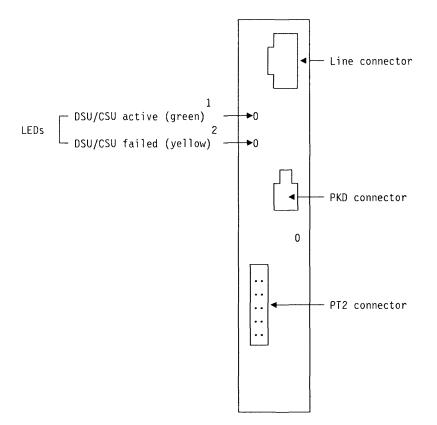

| LIC Type 6 DSU/CSU Function                                |       |

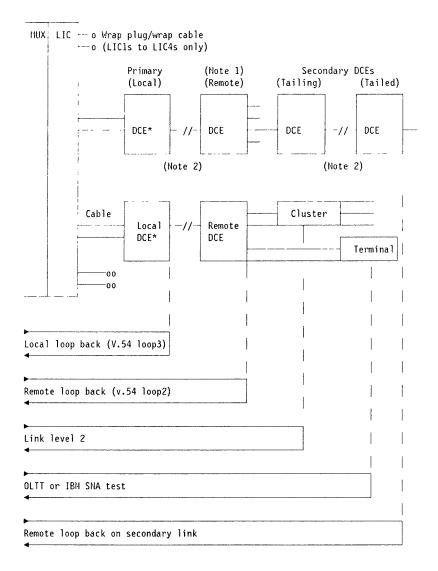

| Problem Determination Aid for LIC Types 1 to 4             |       |

| •••                                                        |       |

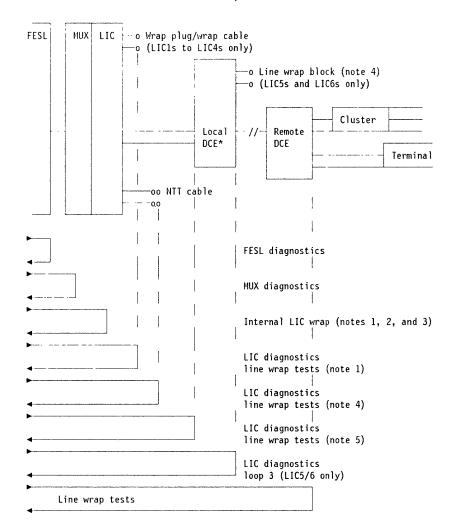

| Problem Determination Aid for LIC Type 5 and LIC Type 6    |       |

| TSS interface cables                                       | 4-100 |

|                                                            |       |

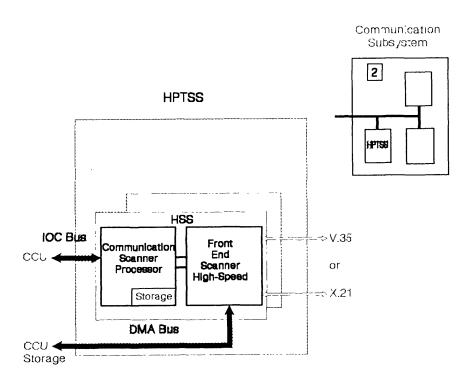

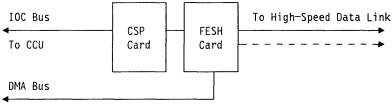

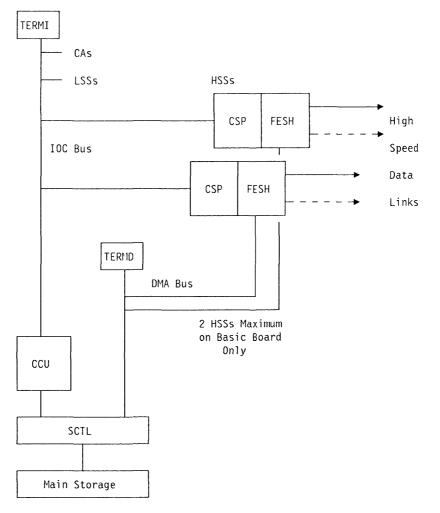

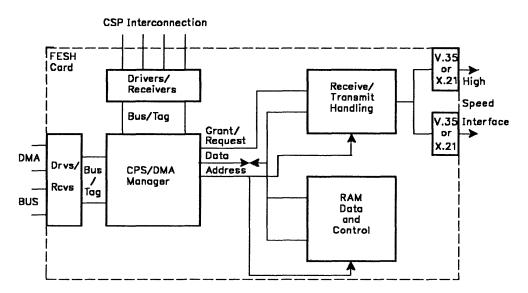

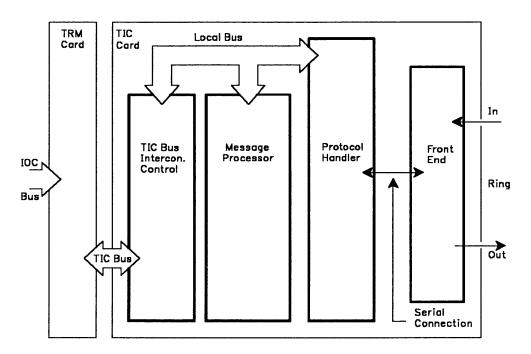

| Chapter 5. High Performance Transmission Subsystem (HPTSS) |       |

| HPTSS in 3745 Data Flow                                    | 5-3   |

| Introduction                                               | 5-4   |

| Internal Interconnections                                  | 5-9   |

|                                                            | 5-9   |

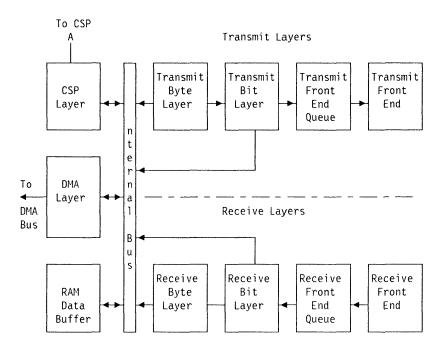

| Communication Scanner Processor (CSP)                      |       |

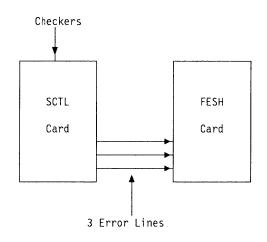

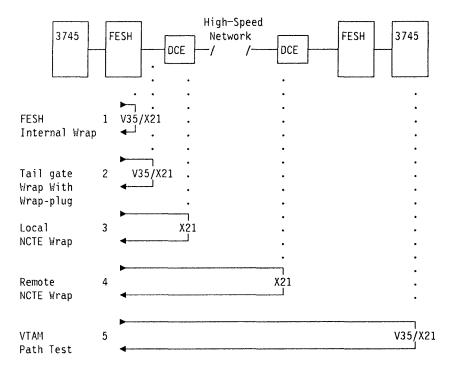

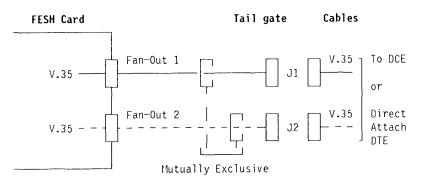

| Transmit Operation       E         Receive Operation       E         Modem Interface Management       E         Error Detection and Reporting       E         Miscellaneous Status Fields       E         Problem Determination Aid       E         Communication Interfaces       E                                                                                                            | 5-11<br>5-14<br>5-16<br>5-19<br>5-23<br>5-31<br>5-37<br>5-40<br>6-1                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

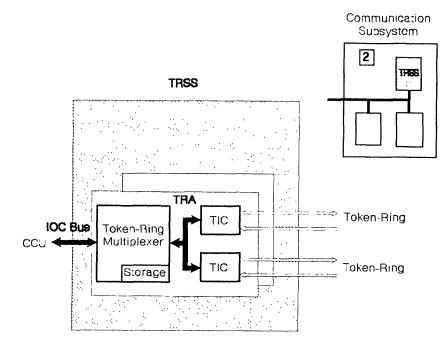

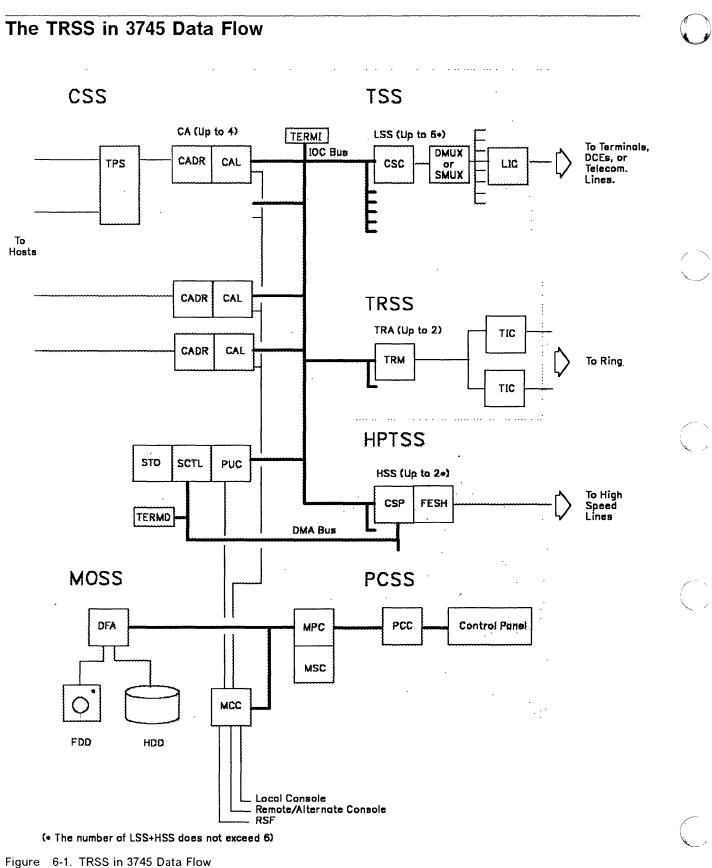

| The TRSS in 3745 Data Flow                                                                                                                                                                                                                                                                                                                                                                      | 6-2                                                                                                              |

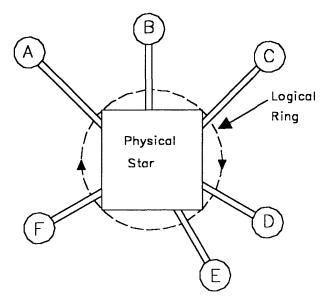

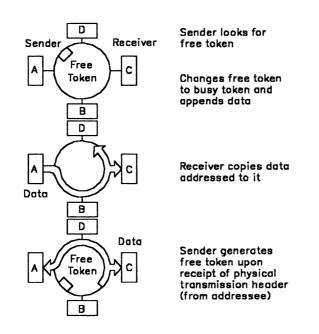

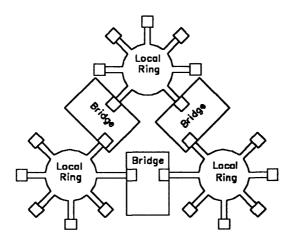

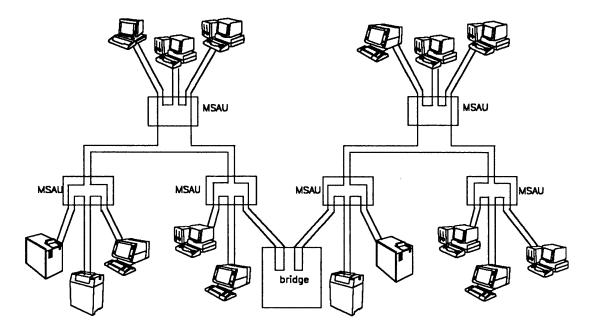

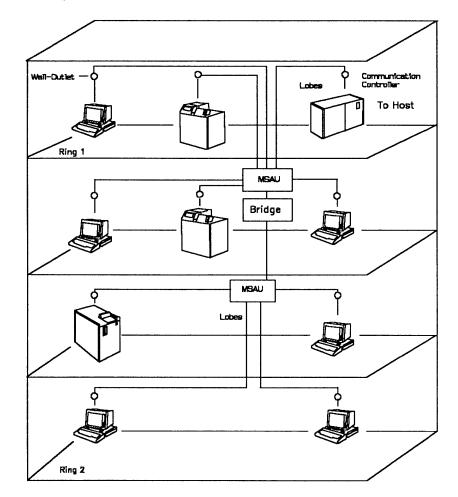

| Token-Ring Network                                                                                                                                                                                                                                                                                                                                                                              | 6-3                                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                  |

| The Token-Ring Adapter in the 3745                                                                                                                                                                                                                                                                                                                                                              | 6-9                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 5-11                                                                                                             |

| <b>3 1</b> (,                                                                                                                                                                                                                                                                                                                                                                                   | 6-15                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 5-19                                                                                                             |

| Error Detection and Reporting                                                                                                                                                                                                                                                                                                                                                                   | 6-20                                                                                                             |

| Problem Determination Aid                                                                                                                                                                                                                                                                                                                                                                       | 6-28                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                  |

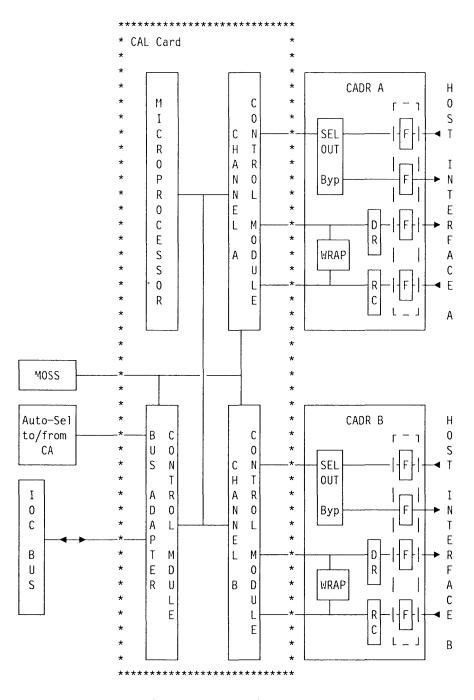

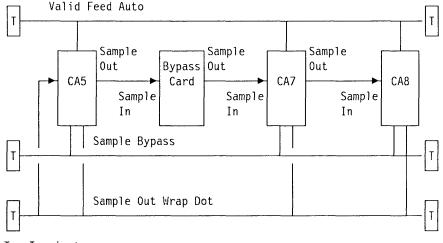

| Chapter 7. Channel Adapter (CA)                                                                                                                                                                                                                                                                                                                                                                 | 7-1                                                                                                              |

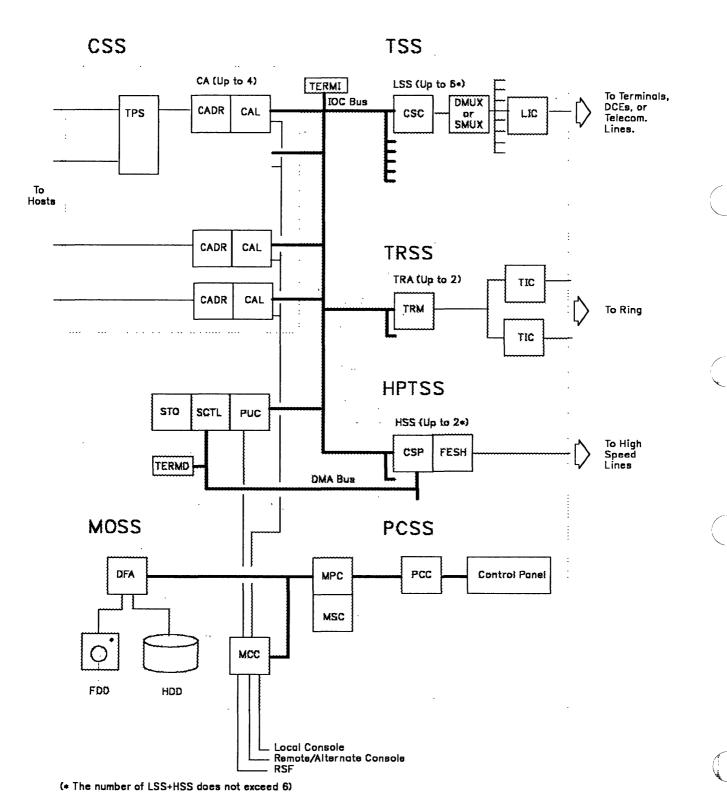

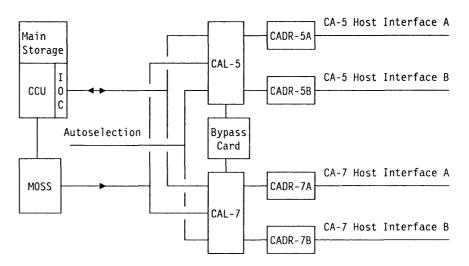

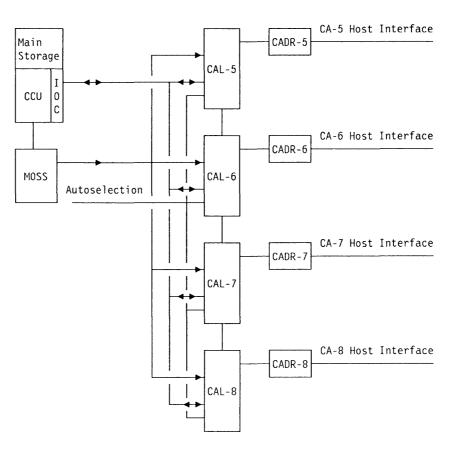

| Channel Adapters in the 3745 Model 130/170 Data Flow                                                                                                                                                                                                                                                                                                                                            | 7-2                                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                               | 7-3                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 7-7                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 7-7<br>7-8                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 7-11                                                                                                             |

| ,                                                                                                                                                                                                                                                                                                                                                                                               | 7-13                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 7-14                                                                                                             |

| • •                                                                                                                                                                                                                                                                                                                                                                                             | 7-15                                                                                                             |

| ······································                                                                                                                                                                                                                                                                                                                                                          | 7-16                                                                                                             |

| •                                                                                                                                                                                                                                                                                                                                                                                               | 7-20                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                 | 7-20                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                 | <b>7-2</b> 0                                                                                                     |

| <b>5 5 5 5 5 5 5 5 5 5</b>                                                                                                                                                                                                                                                                                                                                                                      | <b>'-21</b>                                                                                                      |

| CA Initialization                                                                                                                                                                                                                                                                                                                                                                               | 1 00                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                 | <b>'-2</b> 3                                                                                                     |

| ······································                                                                                                                                                                                                                                                                                                                                                          | 8-1                                                                                                              |

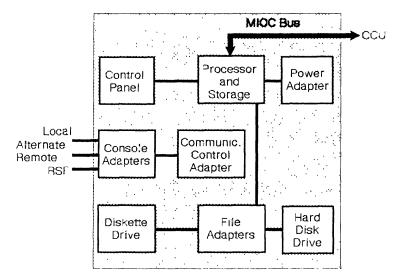

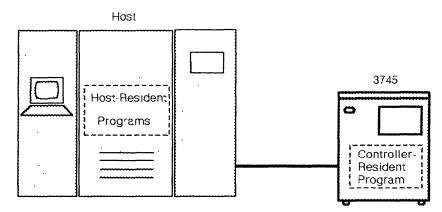

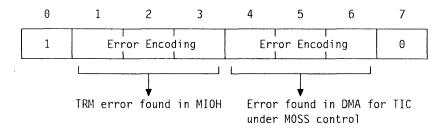

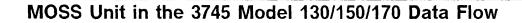

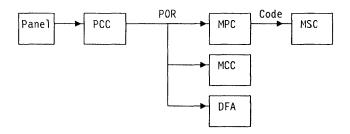

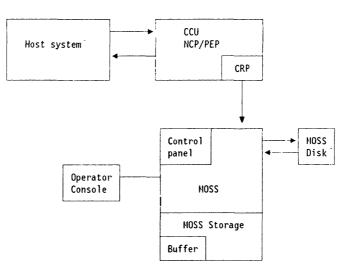

| MOSS Unit in the 3745 Model 130/150/170 Data Flow                                                                                                                                                                                                                                                                                                                                               | 8-1<br>8-2                                                                                                       |

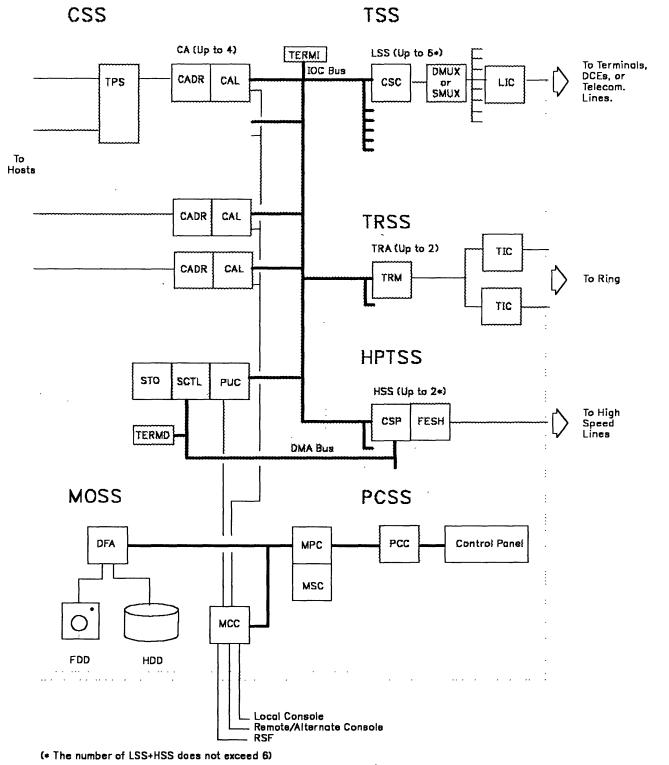

| MOSS Unit in the 3745 Model 130/150/170 Data Flow                                                                                                                                                                                                                                                                                                                                               | 8-1<br>8-2<br>8-3                                                                                                |

| MOSS Unit in the 3745 Model 130/150/170 Data Flow                                                                                                                                                                                                                                                                                                                                               | 8-1<br>8-2<br>8-3<br>8-4                                                                                         |

| MOSS Unit in the 3745 Model 130/150/170 Data Flow         Introduction         MOSS Reset         MOSS Functions                                                                                                                                                                                                                                                                                | 8-1<br>8-2<br>8-3<br>8-4<br>8-6                                                                                  |

| MOSS Unit in the 3745 Model 130/150/170 Data Flow         Introduction         MOSS Reset         MOSS Functions         MOSS States                                                                                                                                                                                                                                                            | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7                                                                           |

| MOSS Unit in the 3745 Model 130/150/170 Data Flow         Introduction         MOSS Reset         MOSS Functions         MOSS States         Branch Trace                                                                                                                                                                                                                                       | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9                                                                    |

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox Description8                                                                                                                                                                                                                                                                | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>8-11                                                            |

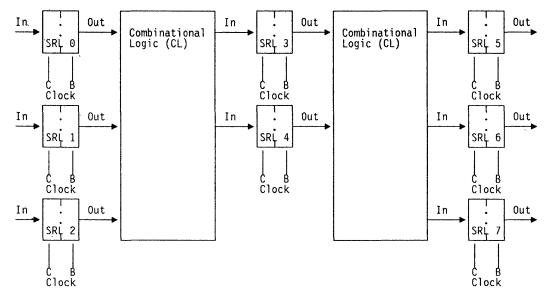

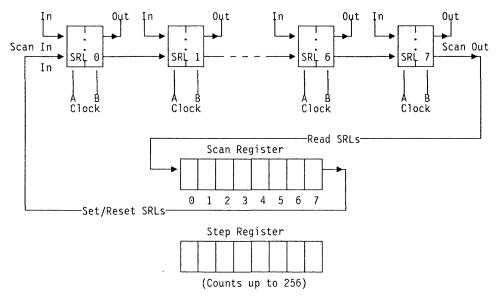

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox Description8LSSD Operation8                                                                                                                                                                                                                                                 | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>8-11<br>8-15                                                    |

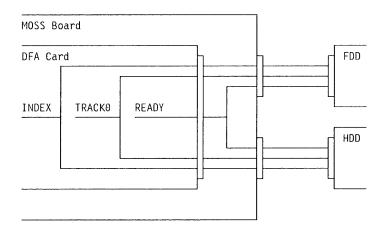

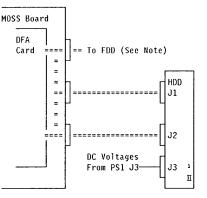

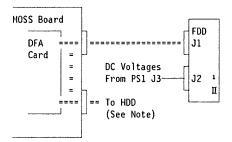

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox Description8LSSD Operation8MOSS/Disk Drive Interaction                                                                                                                                                                                                                      | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>9-11<br>8-15<br>9-17                                            |

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox DescriptionLSSD Operation8MOSS/Disk Drive Interaction                                                                                                                                                                                                                       | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>8-11<br>8-15                                                    |

| MOSS Unit in the 3745 Model 130/150/170 Data Flow         Introduction         MOSS Reset         MOSS Functions         MOSS States         Branch Trace         Mailbox Description         Btast Description         MOSS/Disk Drive Interaction         MOSS/Operator Console Connections         States         MOSS/Operator Consoles, Disk/Diskette Drives                               | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>9-11<br>8-15<br>9-17                                            |

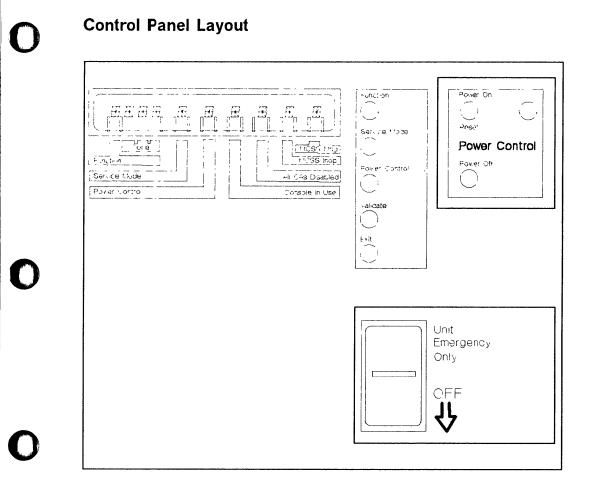

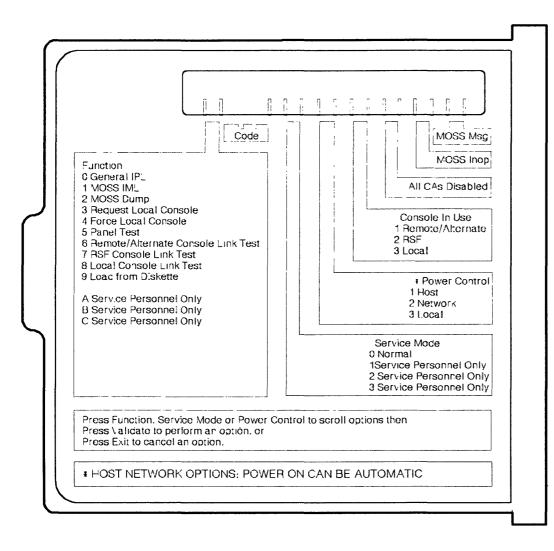

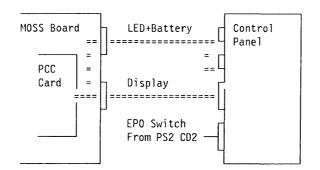

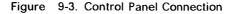

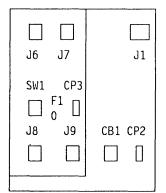

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox DescriptionLSSD OperationMOSS/Disk Drive InteractionMOSS/Operator Console Connections8Chapter 9. Control Panel, Operator Consoles, Disk/Diskette DrivesControl Panel                                                                                                        | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>8-11<br>8-15<br>8-17<br>8-18<br>9-1                             |

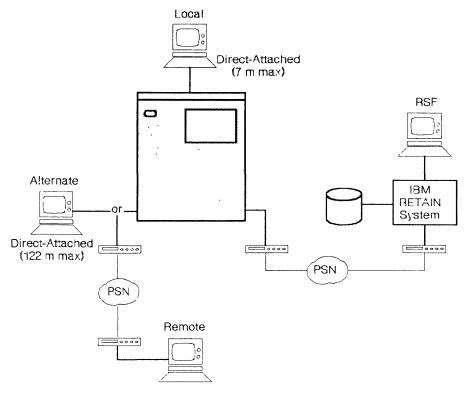

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox DescriptionLSSD OperationMOSS/Disk Drive InteractionMOSS/Operator Console Connections8Chapter 9. Control Panel, Operator Consoles, Disk/Diskette DrivesControl PanelOperator Consoles                                                                                       | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>9-11<br>9-1<br>9-1<br>9-2                                       |

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox DescriptionLSSD OperationMOSS/Disk Drive InteractionMOSS/Operator Console Connections8Chapter 9. Control Panel, Operator Consoles, Disk/Diskette DrivesControl PanelOperator Consoles                                                                                       | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>9-11<br>9-15<br>9-1<br>9-2<br>9-6                               |

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox DescriptionLSSD OperationMOSS/Disk Drive InteractionMOSS/Operator Console Connections8Chapter 9. Control Panel, Operator Consoles, Disk/Diskette DrivesControl PanelOperator ConsolesDisk/Diskette Drive                                                                    | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>9-11<br>9-15<br>9-1<br>9-2<br>9-6<br>9-9                        |

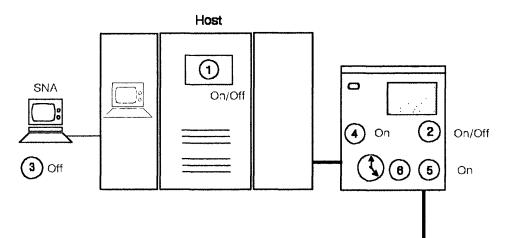

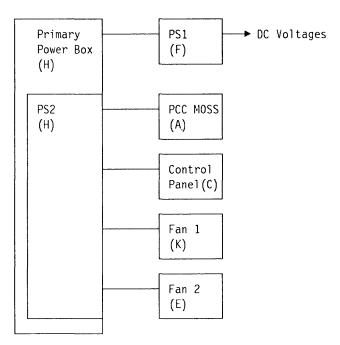

| MOSS Unit in the 3745 Model 130/150/170 Data Flow         Introduction         MOSS Reset         MOSS Functions         MOSS States         Branch Trace         Mailbox Description         LSSD Operation         MOSS/Disk Drive Interaction         MOSS/Operator Console Connections         Reset         Operator Consoles         Disk/Diskette Drive         Chapter 10. Power System | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>8-11<br>8-15<br>8-17<br>8-18<br>9-1<br>9-2<br>9-6<br>9-9<br>0-1 |

| MOSS Unit in the 3745 Model 130/150/170 Data FlowIntroductionMOSS ResetMOSS FunctionsMOSS StatesBranch TraceMailbox DescriptionLSSD OperationMOSS/Disk Drive InteractionMOSS/Operator Console Connections8Chapter 9. Control Panel, Operator Consoles, Disk/Diskette DrivesControl PanelOperator ConsolesDisk/Diskette Drive1The Power System in 3745 Data Flow1                                | 8-1<br>8-2<br>8-3<br>8-4<br>8-6<br>8-7<br>8-9<br>9-11<br>9-15<br>9-1<br>9-2<br>9-6<br>9-9                        |

$A^{-}$

×.

ļ

States - C

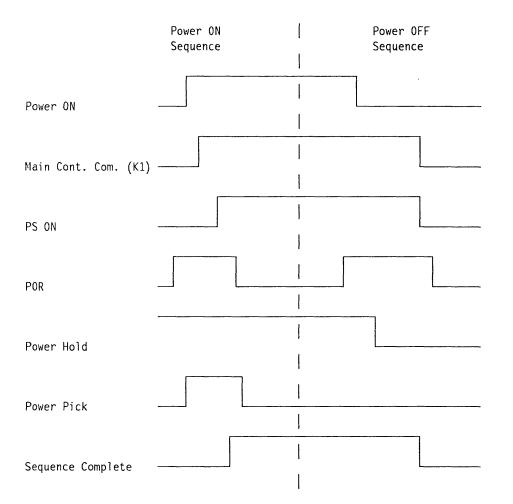

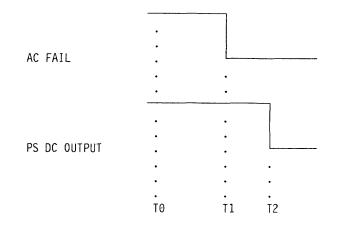

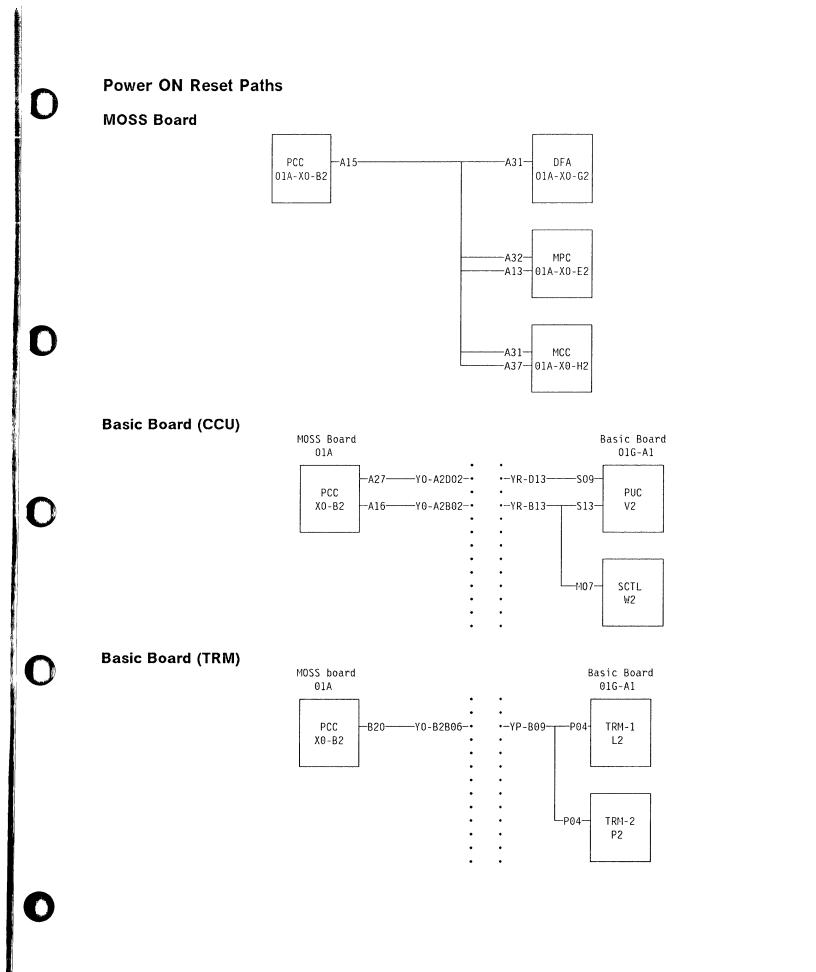

| AC Voltages Input       10         Power Control Subsystem       10-7         Power Mode of Operation       10-7         Power ON/OFF Sequence       10-7         Power ON Reset (POR)       10-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14<br>19<br>21 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

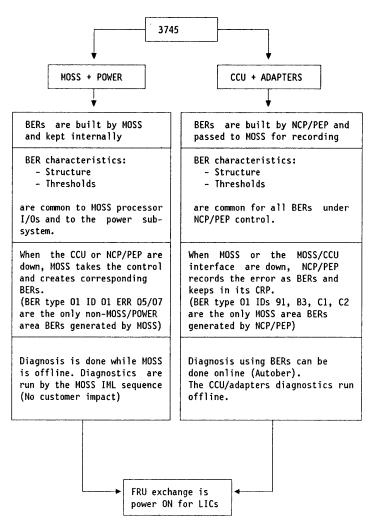

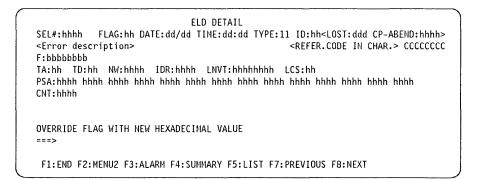

| Chapter 11. Error Logging 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -1             |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -4             |

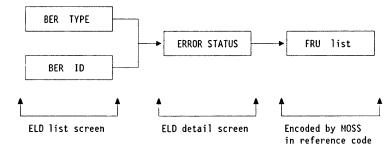

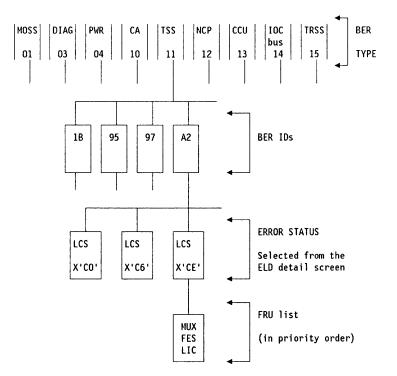

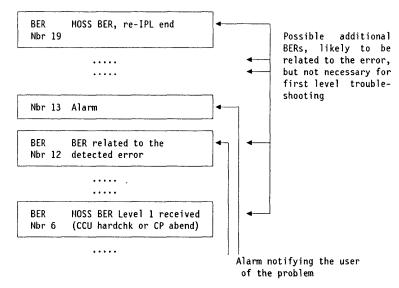

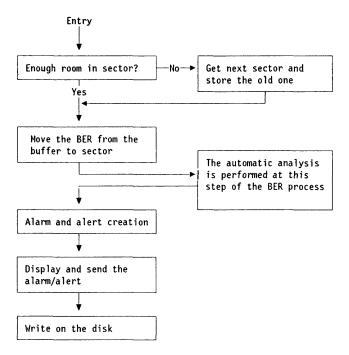

| BER Generalities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -6             |

| BERs Which Are Not Machine Errors 11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12             |

| Specific Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13             |

| AutoMaint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17             |

| BER Recovery Procedures 11-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25             |

| Unresolved Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26             |

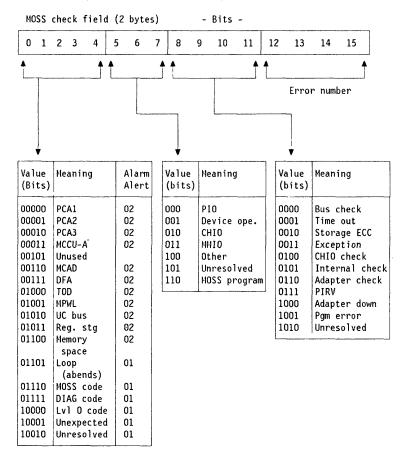

| MOSS Error Logging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30             |

| MOSS BERs Used With the IPL Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34             |

| Diagnostics BER Type 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )6             |

| Power BER Type 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | )8             |

| NCP CA BER Type 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15             |

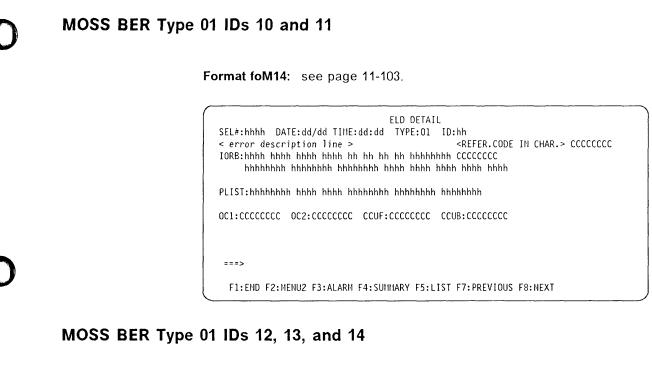

| NCP TSS/HPTSS BER Type 11 11-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27             |

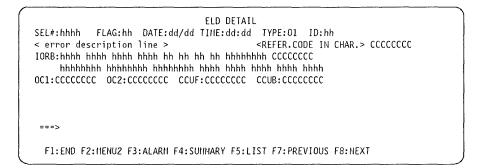

| NCP/PEP BER, Type 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38             |

| NCP CCU BER Type 13 11-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11             |

| NCP IOC BER Type 14 11-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45             |

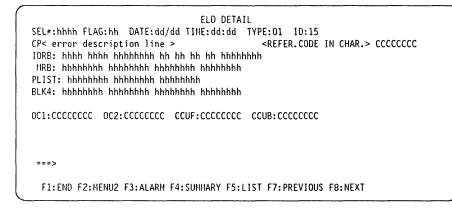

| NCP TRSS BER Type 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17             |

| List of Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1             |

| Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -5             |