### **Maintenance Library**

Storage Control, Model 2

### PREFACE

The 3830-2 Maintenance Library is designed to assist the Customer Engineer in achieving a repair when a failure is discovered either by a customer who has placed a call, or by the CE performing system checkout or routine EREP analysis. The manual assumes that the majority of calls can be handled by a product-trained CE with help available from a supporttrained CE when needed. Maintenance material is given prominence in the manual organization, with emphasis on "how to fix" rather than on theory of operation.

Information pertaining to MST component circuits, ALD's, and FEALD's will be found in the IBM Maintenance Library, Logic Blocks Automated Logic Diagrams SLT, SLD, ASLT, MST, Order No. SY22-2798.

Information pertaining to MST packaging, tools, and wiring change procedure will be found in the FE Theory of Operation, IBM Monolithic System Technology, Order No. SY22-6739.

Information pertaining to MST power supplies and components will be found in the FE Theory of Operation, IBM Power Supplies, Order No. SY22-2799.

### MAINTENANCE LIBRARY ORDERING PROCEDURE (IBM INTERNAL)

Individual pages of the 3830-2 Maintenance Library can be ordered from the San Jose plant by using the Wiring Diagram/ Logic Page Request (Order No. 120-1679). Indicate machine type (3830-2) and, in the columns headed "Logic Page", enter the sequence number, part number, and EC number. Groups of pages can be ordered by including a description (section, volume, etc.) and the machine serial number,

CE-MLM Feedback forms are provided at the front of this volume for reader comments. If the forms have been removed, send your comments to the address below.

This manual was prepared by the IBM General Products Division, Product Publications, Department G24, San Jose, California 95193.

### SAFETY

Be constantly aware of hazardous situations when working on the 3830-2 Storage Control. Take time to review the CE safety practices listed below which have been reprinted from the pocket-size card available from Mechanicsburg (Order No. S229-1264).

### **CE SAFETY PRACTICES**

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment:

- 1. You should not work alone under hazardous conditions or around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

- 2. Remove all power, ac and dc, when removing or assembling major components, working in immediate areas of power supplies, performing mechanical inspection of power supplies, or installing changes in machine circuitry.

- 3. After turning off wall box power switch, lock it in the Off position or tag it with a "Do Not Operate" tag, Form 229-1266 Pull power supply cord whenever possible.

- 4. When it is absolutely necessary to work on equipment having exposed operating mechanical parts or exposed live electrical circuitry anywhere in the machine, observe the following precautions

- a. Another person familiar with power off controls must be in immediate vicinity.

- b. Do not wear rings, wrist watches, chains, bracelets, or metal cuff links

- c. Use only insulated pliers and screwdrivers.

- d. Keep one hand in pocket.

- e. When using test instruments, be certain that controls are set correctly and that insulated probes of proper capacity are used.

- f. Avoid contacting ground potential (metal floor strips, machine frames, etc.). Use suitable rubber mats, purchased locally if necessary.

- 5. Wear safety glasses when:

- a. Using a hammer to drive pins, riveting, staking, etc.

- b. Power or hand drilling, reaming, grinding, etc.

- c. Using spring hooks, attaching springs

- d. Soldering, wire cutting, removing steel bands. e. Cleaning parts with solvents, sprays, cleaners, chemicals. etc.

- f. Performing any other work that may be hazardous to your eyes. REMEMBER - THEY ARE YOUR EYES.

- 6. Follow special safety instructions when performing specialized tasks, such as handling cathode ray tubes and extremely high voltages. These instructions are outlined in CEMs and the safety portion of the maintenance manuals.

- 7. Do not use solvents, chemicals, greases, or oils that have not been approved by IBM.

- 8. Avoid using tools or test equipment that have not been approved by IBM.

- 9. Replace worn or broken tools and test equipment.

- 10. Lift by standing or pushing up with stronger leg muscles this takes strain off back muscles. Do not lift any equipment or parts weighing over 60 pounds.

- 11. After maintenance, restore all safety devices, such as guards, shields, signs, and grounding wires

- 12. Each Customer Engineer is responsible to be certain that no action on his part renders products unsafe or exposes customer personnel to hazards

- 13 Place removed machine covers in a safe out-of-the-way place where no one can trip over them

- 14. Ensure that all machine covers are in place before returning nachine to custome

- 15. Always place CE tool kit away from walk areas where no one can trip over it; for example, under desk or table.

16. Avoid touching moving mechanical parts when lubricating, checking for play, etc.

- 17. When using stroboscope, do not touch ANYTHING it may be moving

- 18. Avoid wearing loose clothing that may be caught in machinery. Shirt sleeves must be left buttoned or rolled above the elbow

- 19. Ties must be tucked in shirt or have a tie clasp (preferably nonconductive) approximately 3 inches from end. Tie chains are not recommended.

- 20. Before starting equipment, make certain fellow CEs and customer personnel are not in a hazardous position

- 21. Maintain good housekeeping in area of machine while performing and after completing maintenance.

Knowing safety rules is not enough. An unsafe act will inevitably lead to an accident. Use good judgment - eliminate unsafe acts.

### **ARTIFICIAL RESPIRATION**

#### **General Considerations**

- 1. Start Immediately Seconds Count Do not move victim unless absolutely necessary to remove from danger. Do not wait or look for help or stop to loosen clothing, warm the victim, or apply stimulants.

- 2. Check Mouth for Obstructions Remove foreign objects. Pull tongue forward.

- 3. Loosen Clothing Keep Victim Warm Take care of these items after victim is breathing by himself or when help is available.

- 4. Remain in Position After victim revives, be ready to resume respiration if

- necessary. 5. Call a Doctor

- Have someone summon medical aid

- 6. Don't Give Up Continue without interruption until victim is breathing without help or is certainly dead.

### **Rescue Breathing for Adults**

- 1. Place victim on his back immediately

- 2. Clear throat of water, food, or foreign matter.

- 3. Tilt head back to open air passage

- 4. Lift jaw up to keep tongue out of air passage

- 5. Pinch nostrils to prevent air leakage when you blow.

- 6. Blow until you see chest rise

- 7. Remove your lips and allow lungs to empty. 8. Listen for snoring and gurglings - signs of throat obstruc-

- 9. Repeat mouth to mouth breathing 10-20 times a minute.

- Continue rescue breathing until victim breathes for himself.

mouth position

Thumb and finger positions

3330-2

437402A 437405 437408 2346970 AA0200 437414 15 Mar 72 15 Aug 72 16 Oct 72 Seq 2 of 2 Part Number 4 Jun 73

© Copyright IBM Corporation 1972, 1973

#### PREFACE, SAFETY

PREFACE, SAFETY

### **IBM 3830-2 MAINTENANCE LIBRARY**

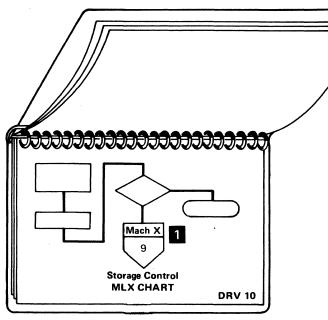

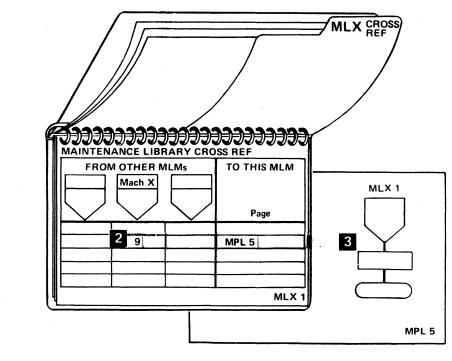

### HOW TO FIND INFORMATION:

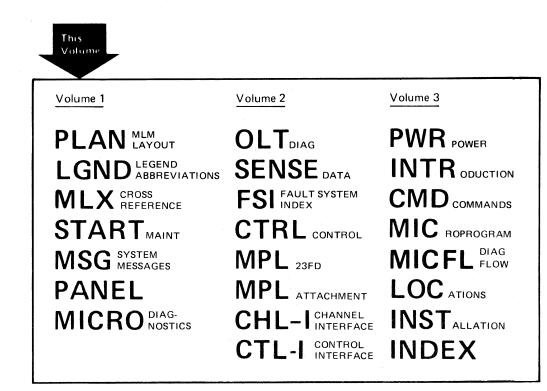

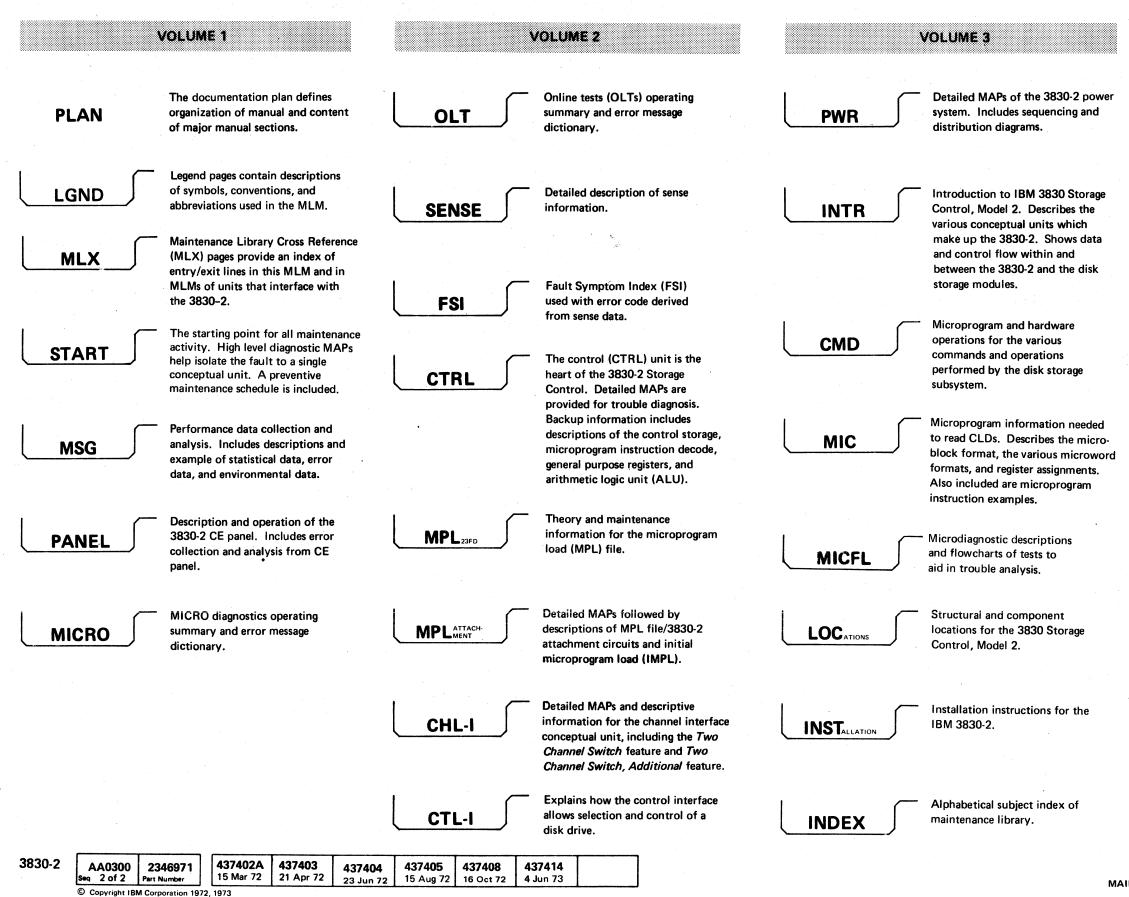

DOCUMENTATION PLAN (PLAN 10) defines major sections of the manual. Where practical, documentation is arranged in sections corresponding to the natural breakdown of machine elements.

A SUBJECT INDEX gives access to specific subjects.

FIRST PAGE OF EACH SECTION indicates the contents of the section and may contain other pertinent information.

CTRL 1

DIVIDER TABS provide rapid accessibility and allow efficient cross referencing between and within maintenance library sections.

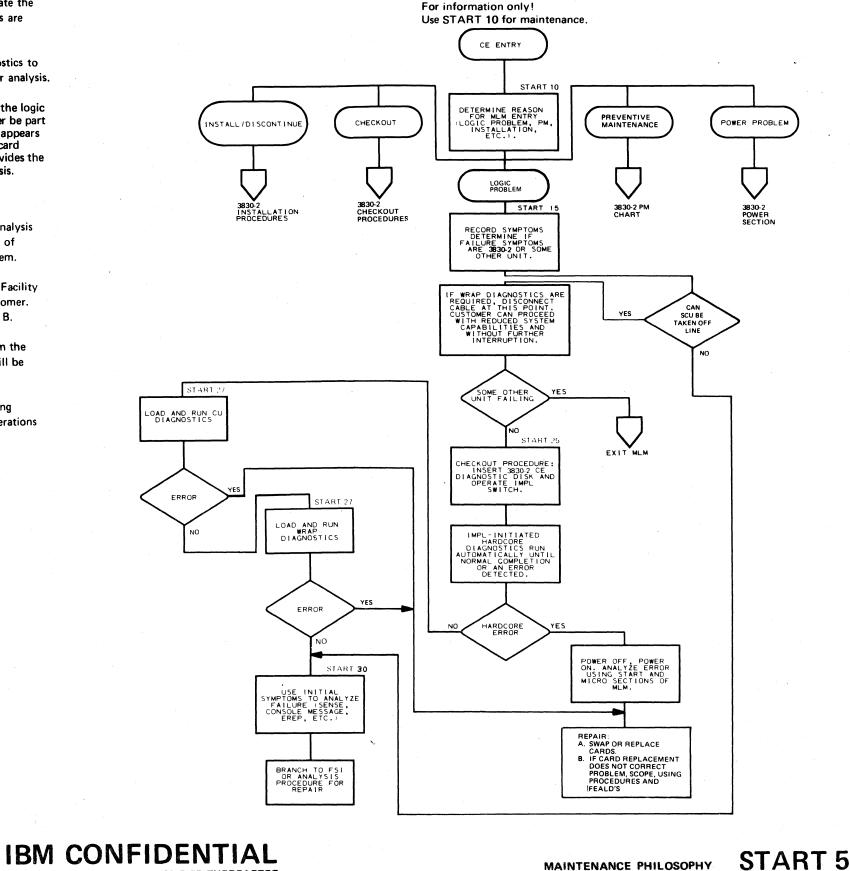

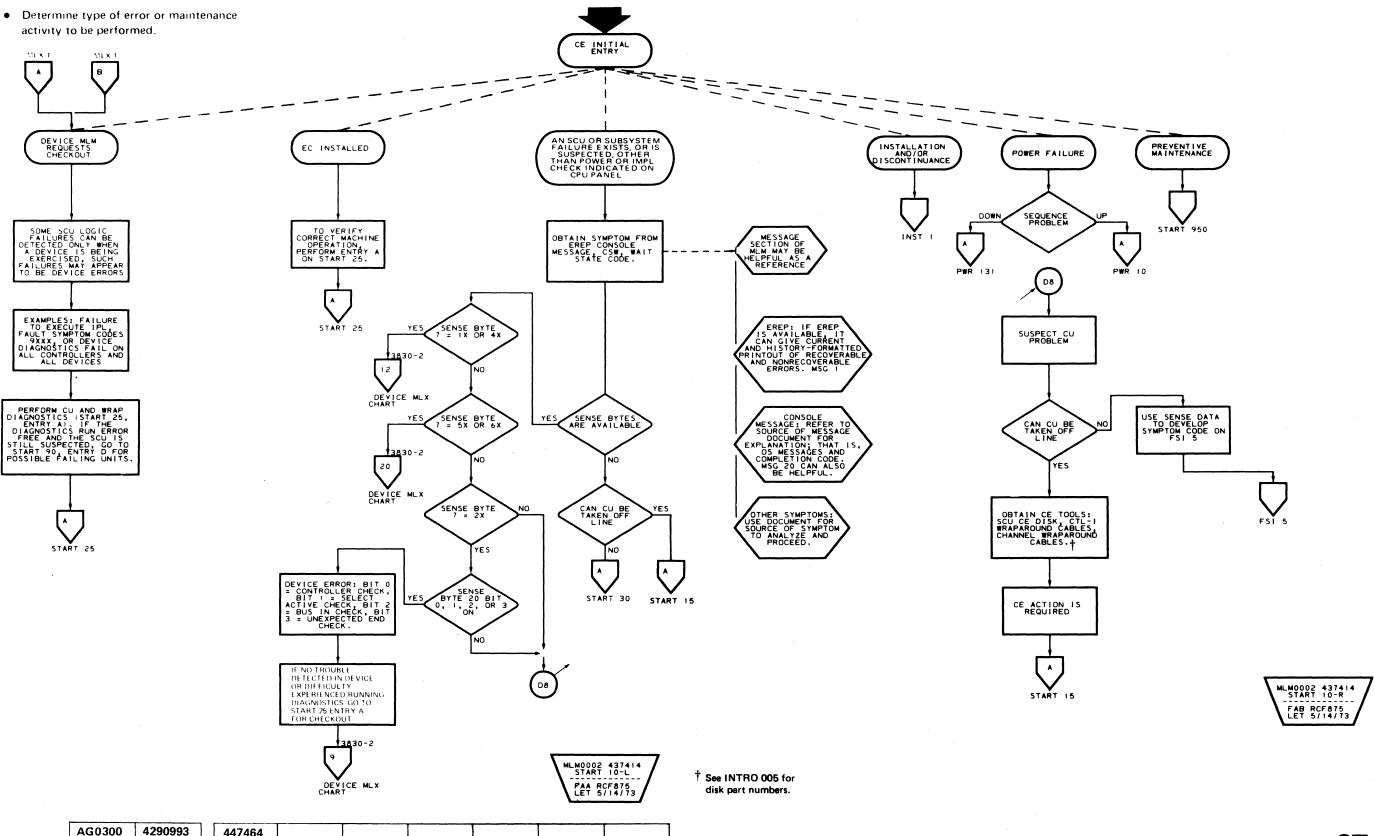

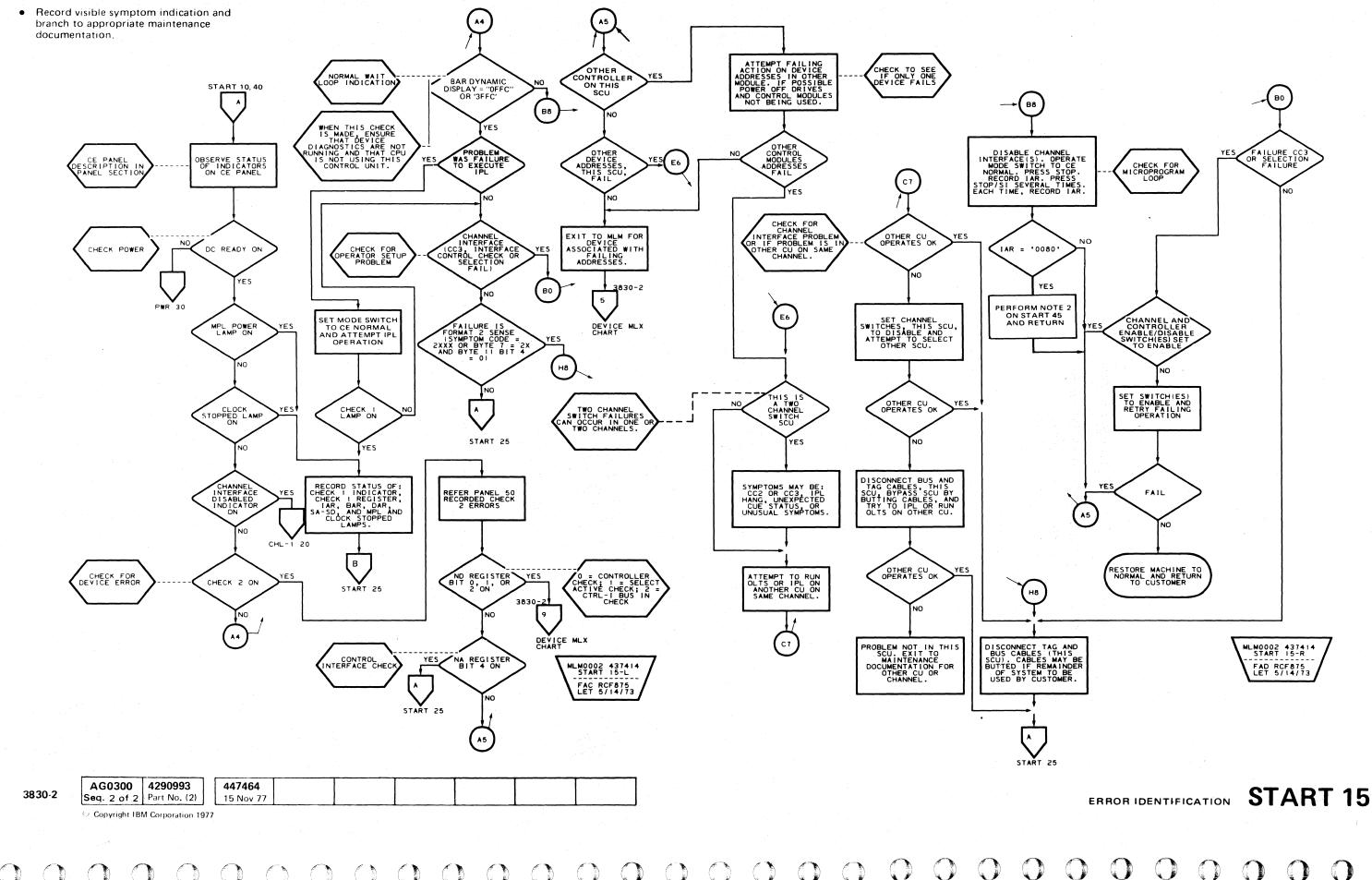

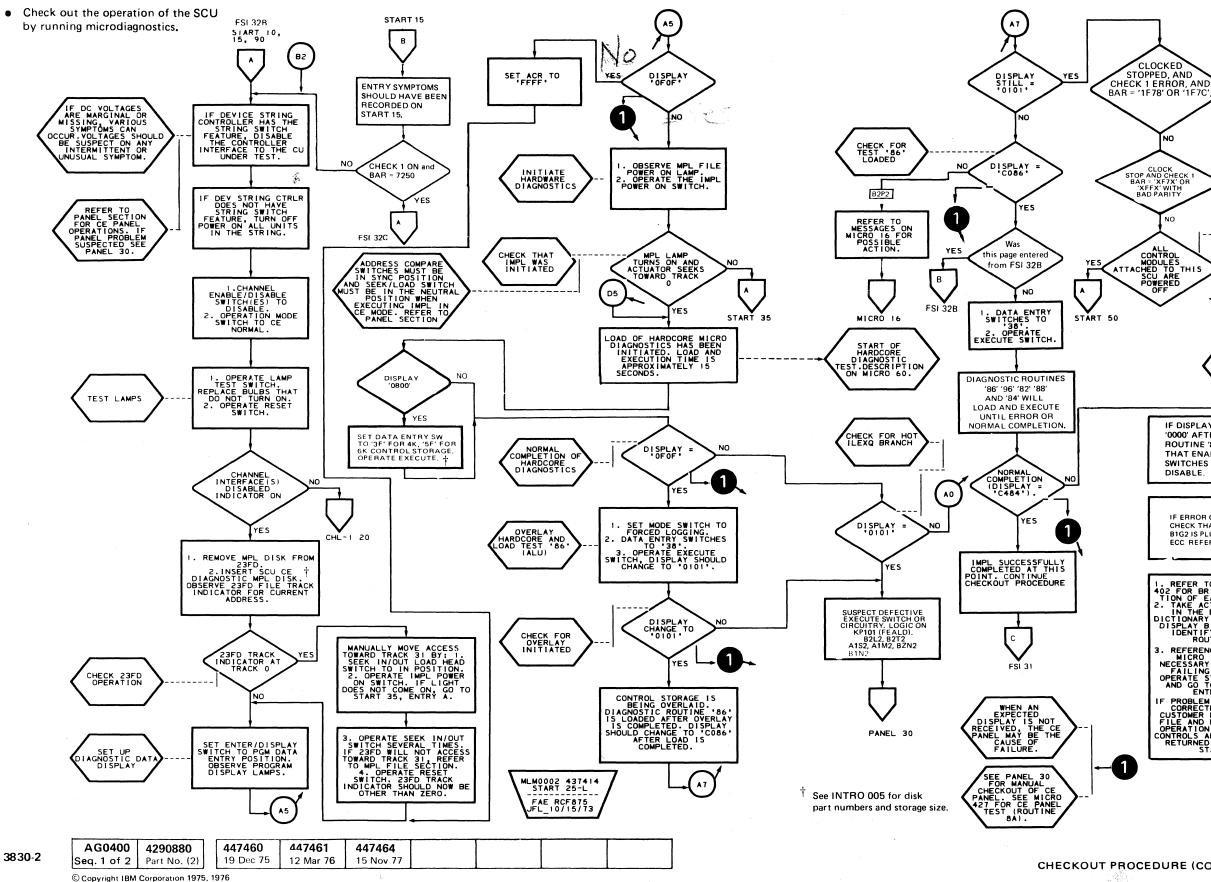

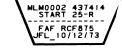

START is the starting point for all maintenance. This section is designed to get you quickly on the right track and either lead you to a solution or direct you to more specialized information elsewhere in the manual

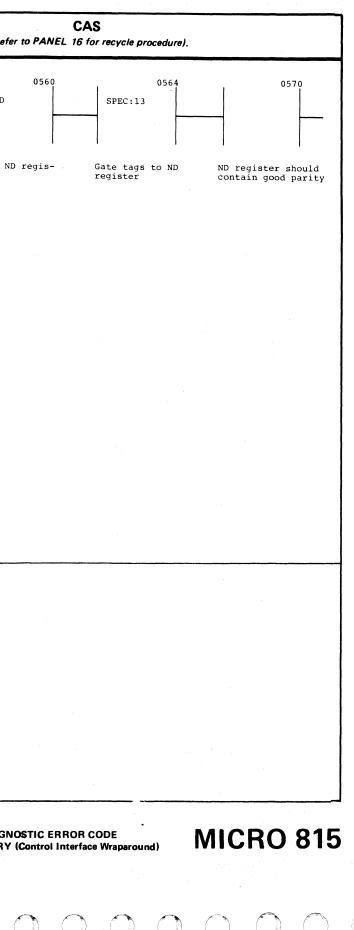

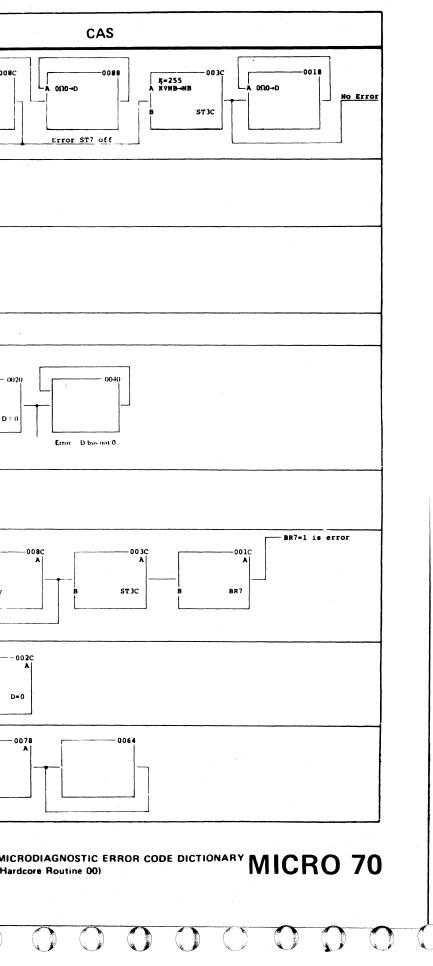

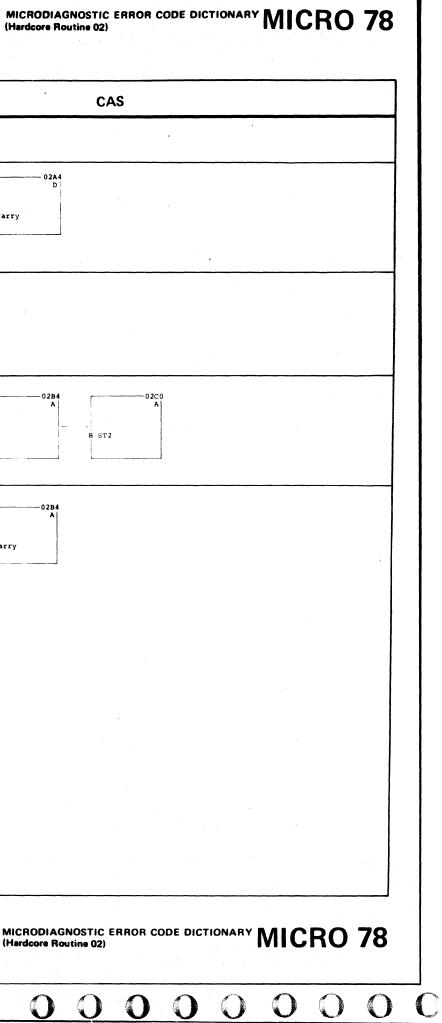

ERROR DICTIONARIES (MICRO and OLTS) reference appropriate maintenance procedures for microdiagnostic and online-test error messages.

FAULT SYMPTOM INDEX (FSI) references appropriate maintenance procedures for errors identified by sense data.

INTRODUCTION TO THE IBM 3830 STORAGE CONTROL, MODEL 2

INTR 10

WANT TO LEARN THE 3830-2? The INTR, CMD, and MIC sections contain instructional and recall material that is useful either for initial training or as backup information during the maintenance activity.

CTRL.

PAGE NUMBERS in "thumbing" position may be rapidly scanned by flipping pages.

| 3830-2 | AA0300<br>Seg 1 of 2 | 2346971<br>Part Number | <b>437402A</b><br>15 Mar 72 | <b>437403</b><br>21 Apr 72 | <b>437404</b><br>23 Jun 72 | <b>437405</b><br>15 Aug 72 | <b>437408</b><br>16 Oct 72 | <b>437414</b><br>4 Jun 73 |  |

|--------|----------------------|------------------------|-----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|---------------------------|--|

|        | Copyright IB         | M Corporation 197      | 2, 1973                     |                            |                            |                            |                            |                           |  |

#### IBM 3830-2 MAINTENANCE LIBRARY PLAN 5

IBM 3830-2 MAINTENANCE LIBRARY PLAN 5

### MAINTENANCE LIBRARY DOCUMENTATION PLAN

$\mathbf{O} = \mathbf{O} = \mathbf{O}$

MAINTENANCE LIBRARY DOCUMENTATION PLAN AN 10

## MAINTENANCE LIBRARY DOCUMENTATION PLAN PLAN 10

### CONTENTS

### LGND

| Legend                                     |   |

|--------------------------------------------|---|

| Logic Diagrams                             |   |

| Function Blocks                            |   |

| Logic Block Special Symbols                |   |

| Logic Block Suffixes                       |   |

| Storage Elements                           |   |

| togic Diagrams                             |   |

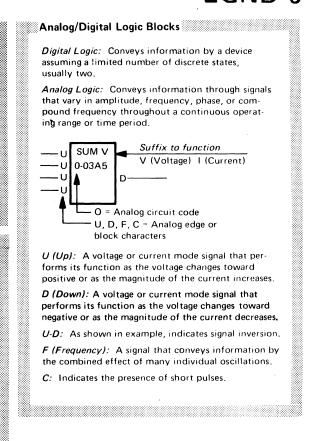

| Analog/Digital Logic Blocks                |   |

| Flowcharts LGND 8                          |   |

| Solid Logic Design Automation LGND 1       | 0 |

| 2 Level Symmetrical                        |   |

| 2 Level Asymmetrical                       |   |

| Voltage Levels                             |   |

| Functional Symbols                         | 2 |

| Descriptions                               |   |

| Decode                                     |   |

| Matrix                                     |   |

| Elements With Common Inputs/Outputs LGND 1 | 4 |

|                                            |   |

| Abbreviations and Definitions LGND 1       | 6 |

· .

| 1      |             | -           |           | 1        |           |  |  |

|--------|-------------|-------------|-----------|----------|-----------|--|--|

| 3830-2 | AB0200      | 2354652     | 437405    | 437414   | 437417    |  |  |

|        | Seq. 1 of 1 | Part No. () | 15 Aug 72 | 4 Jun 73 | 15 Apr 74 |  |  |

C Copyright IBM Corporation 1972, 1973 ,1974

### LEGEND (Part 1 of 6)

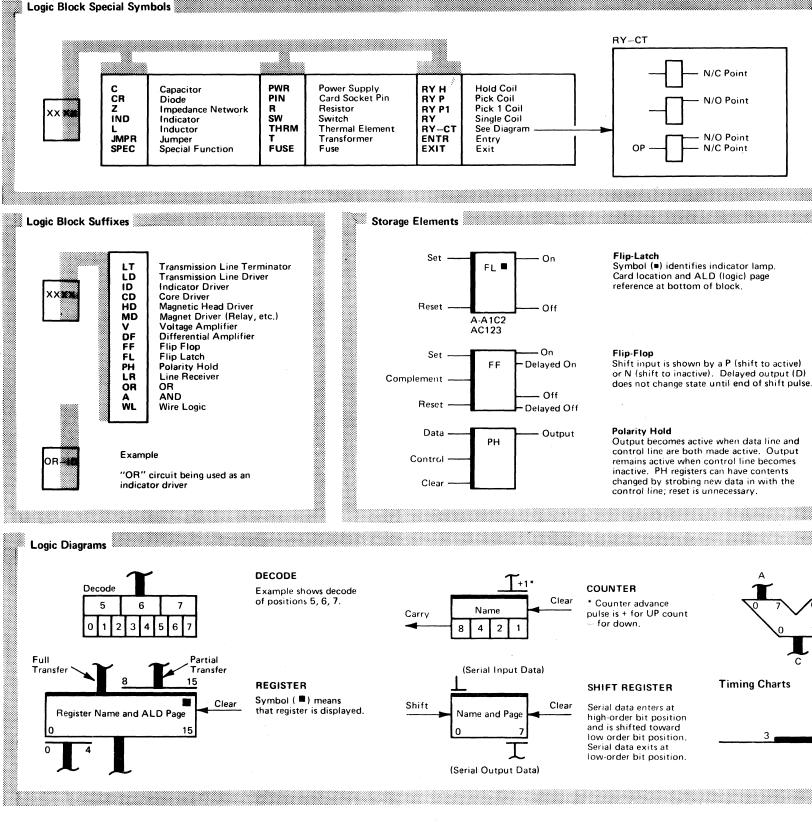

### Logic Diagrams

In the following logic representation, line signal levels are disregarded. The purpose of the symbols and descriptions is to provide a reference for servicing. Additional information can be found in IBM Maintenance Library, *Logic Blocks, Automated Logic Diagrams SLT, SLD, ASLT, MST,* Order No. SY22-2798; and IBM Maintenance Library, *Monolithic System Technology, Theory of Operation, Packaging, Tools and Wiring Change Procedure,* Order No. SY22-6739.

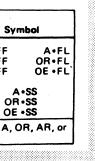

Function Blocks

| OR       OR         OE       Exclusive Or<br>Output is active if either input, but not both<br>is active.         EV       An even number of inputs (including zero)<br>must be active to produce an active output.         OD       Odd<br>An odd number of inputs must be active to<br>produce an active output.         LIM       Limiter<br>Limits one or both extremes of a wave form. | ۱. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| OE       Output is active if either input, but not both is active.         Ev       Even         An even number of inputs (including zero) must be active to produce an active output.         OD       Odd         An odd number of inputs must be active to produce an active output.         Lima       Limiter                                                                          | ۱, |

| EV       An even number of inputs (including zero) must be active to produce an active output.         OD       Odd         An odd number of inputs must be active to produce an active output.         Limiter                                                                                                                                                                             |    |

| OD An odd number of inputs must be active to produce an active output.                                                                                                                                                                                                                                                                                                                      |    |

|                                                                                                                                                                                                                                                                                                                                                                                             |    |

|                                                                                                                                                                                                                                                                                                                                                                                             |    |

| (time)                                                                                                                                                                                                                                                                                                                                                                                      |    |

| SS Single Shot ST Schmitt Trigger                                                                                                                                                                                                                                                                                                                                                           | r  |

| (time)                                                                                                                                                                                                                                                                                                                                                                                      |    |

| TD Time Delay PG Pulse Generato                                                                                                                                                                                                                                                                                                                                                             | r  |

| (frequency)                                                                                                                                                                                                                                                                                                                                                                                 |    |

| OSC Oscillator Driver                                                                                                                                                                                                                                                                                                                                                                       |    |

| AR Amplifier A-(N) Threshold                                                                                                                                                                                                                                                                                                                                                                |    |

| CV Signal Mode Z Impedance<br>Converter                                                                                                                                                                                                                                                                                                                                                     |    |

| N Negator SUM Algebraic Sum                                                                                                                                                                                                                                                                                                                                                                 |    |

| CS Current Switch FLTR Filter                                                                                                                                                                                                                                                                                                                                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 2020.0 | AB0300         | 2354653            | 437405    | 437408    | 437414    |  |  |

|--------|----------------|--------------------|-----------|-----------|-----------|--|--|

| 3830-2 | Seq. 1 of 2    | Part No. ()        | 15 Aug 72 | 16 Oct 72 | 4 June 73 |  |  |

|        | C Copyright IB | M Corporation 1972 | . 1973    |           |           |  |  |

### LEGEND (Part 1 of 6) LGND 6

ADDER A + B = C

#### ACTIVE STATE

Numerals at the beginning and end of the bar identify the signals (numbered on the same chart) that activate and deactivate this line. A bar over the numeral (2) indicates that the lack of the signal activates or deactivates the line. The active-state bar indicates the polarity shift.

LEGEND (Part 1 of 6) LGND 6

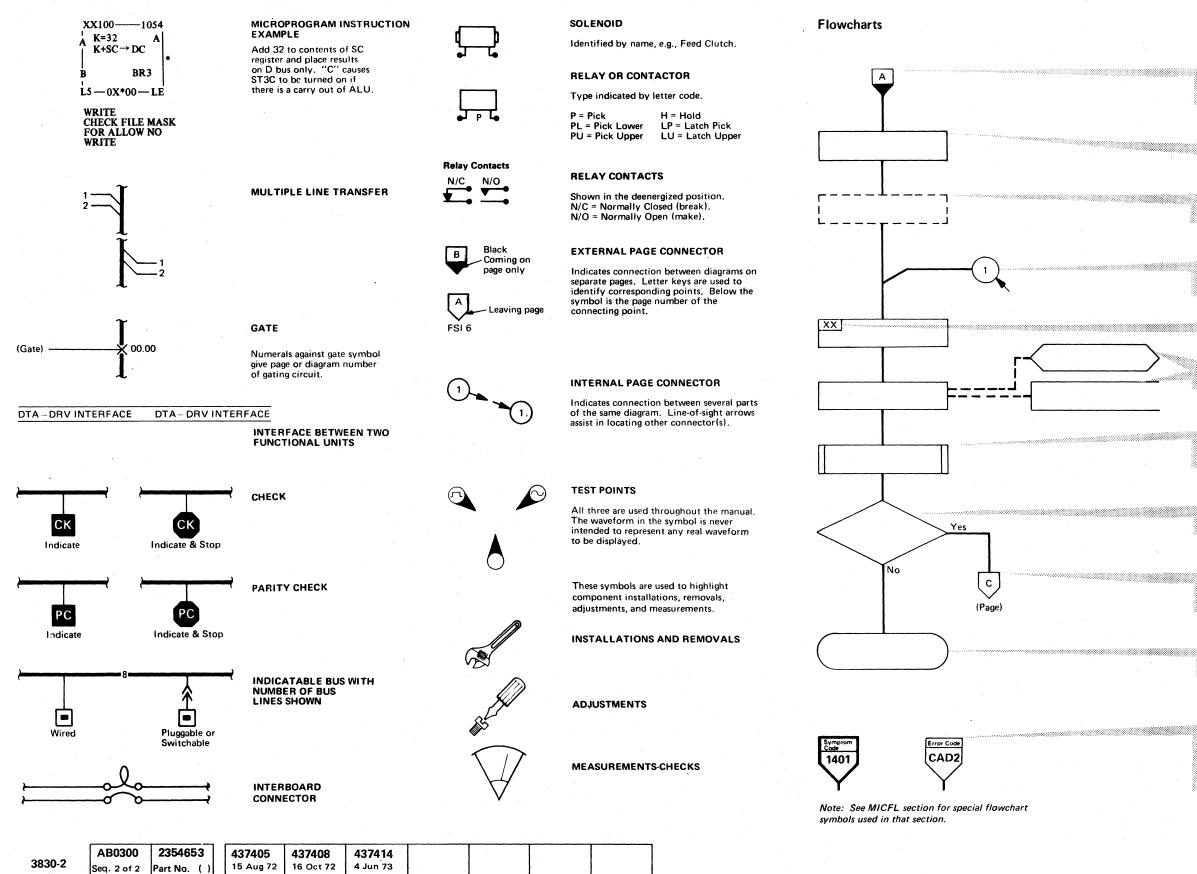

### LEGEND (Part 2 of 6)

© Copyright IBM Corporation 1972, 1973

LEGEND (Part 2 of 6)

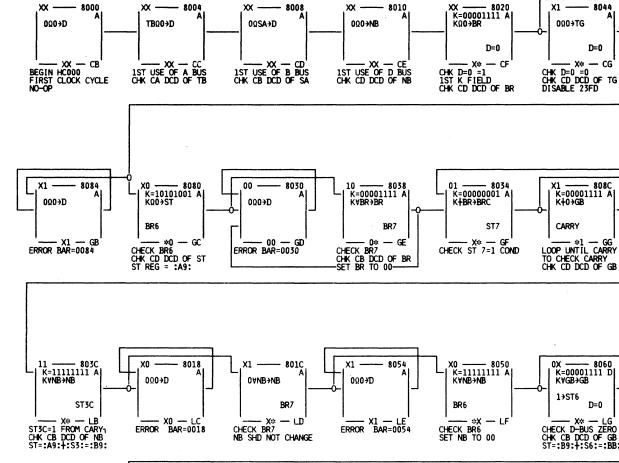

### LGND 8

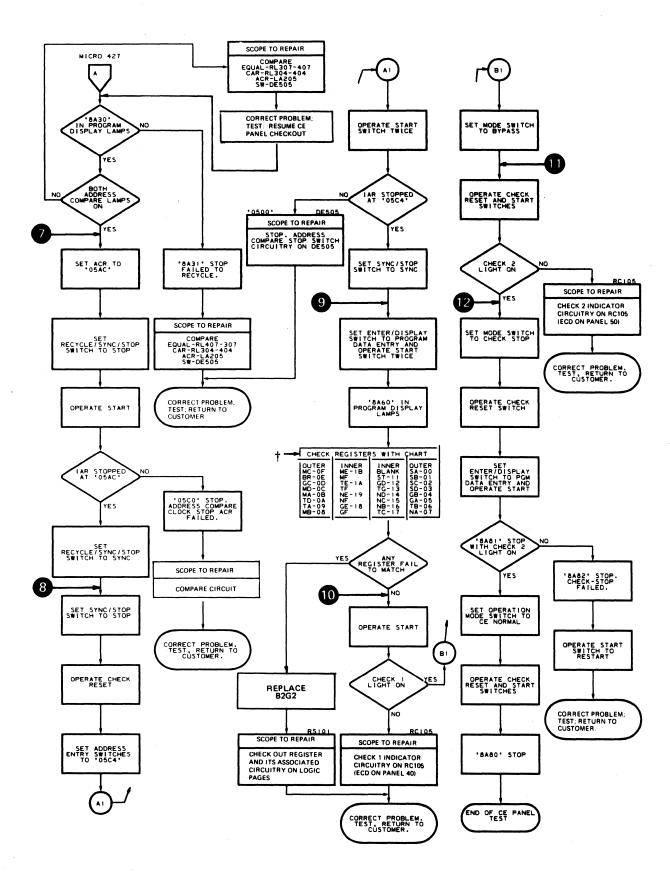

### PROCESS, MAJOR FUNCTIONS OR EVENTS

#### **EXTERNAL PAGE CONNECTOR (Entry)**

Indicates entrance from correspondingly lettered symbol on referenced page.

#### BASIC ACTION BLOCK

#### **ANNOTATION** (In-Line)

Gives descriptive comment or explanatory note.

#### **INTERNAL PAGE CONNECTOR**

Internal page connector shows entry from correspondinglynumbered symbol elsewhere on page. Flow is top to bottom from the reentry point.

XX identifies register used for function or event.

#### ANNOTATION (Supplementary)

Gives descriptive comment or explanatory note.

#### FUNCTION OR PROCESS DETAILED ELSEWHERE

Block identifies process and indicates where the detailed flowchart is located.

#### DECISION

Indicates a branch to alternate paths.

#### **EXTERNAL PAGE CONNECTOR (Exit)**

Indicates exit to correspondingly lettered symbol on referenced page.

### TERMINAL

Indicates beginning or end of flow path.

### SPECIAL EXTERNAL PAGE CONNECTORS (Entry)

Symptom Code: Developed from sense information.

Error Code: Used with microdiagnostics.

LEGEND (Part 2 of 6) LGND 8

$\bigcirc \bigcirc \bigcirc \bigcirc$

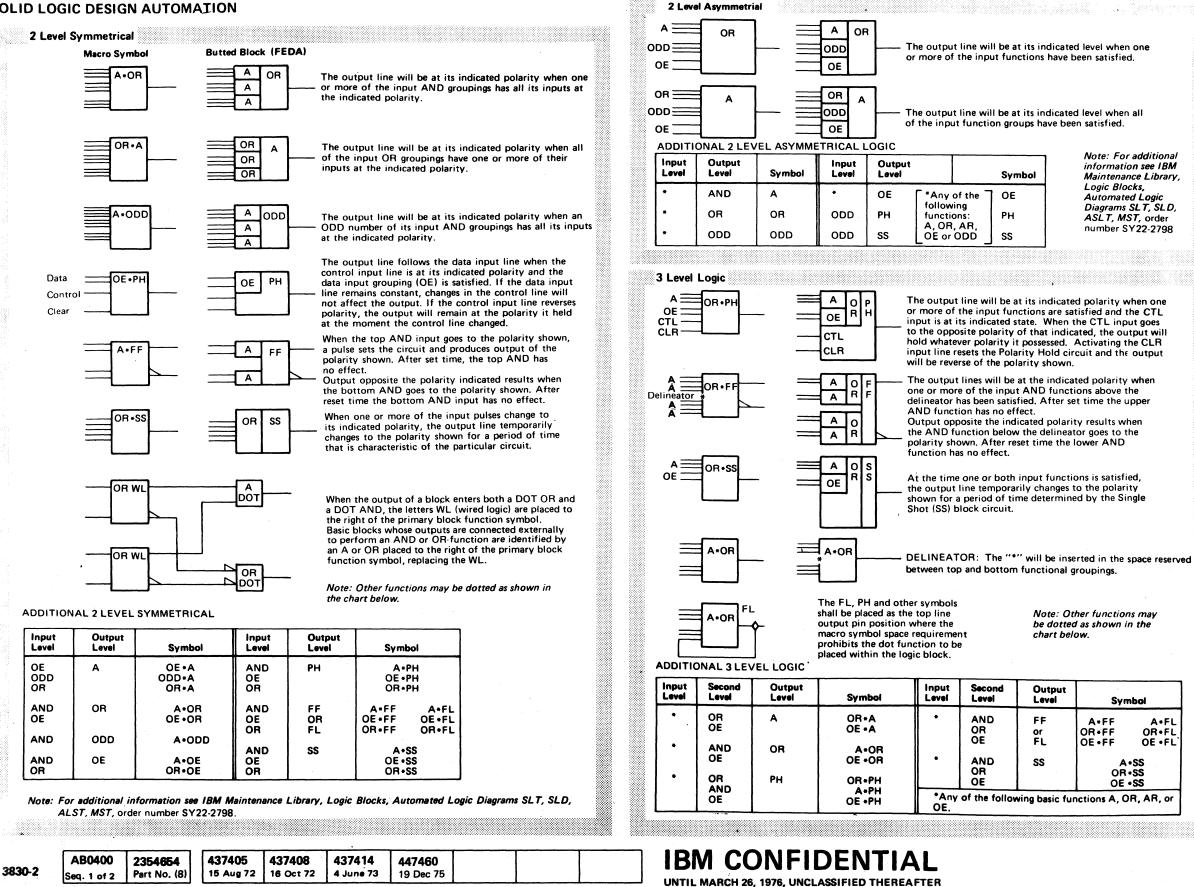

2 Level Asymmetrial

### LEGEND (Part 3 of 6)

### SOLID LOGIC DESIGN AUTOMATION

Copyright IBM Corporation 1972, 1973, 1975

## LEGEND (Part 3 of 6) LGND 10

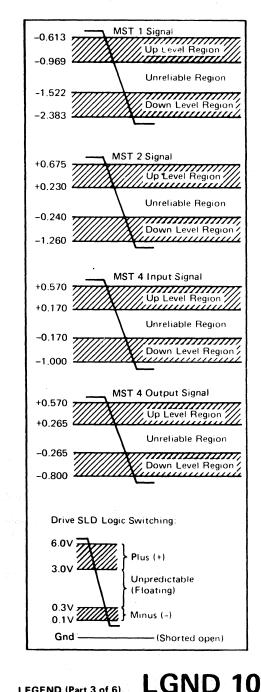

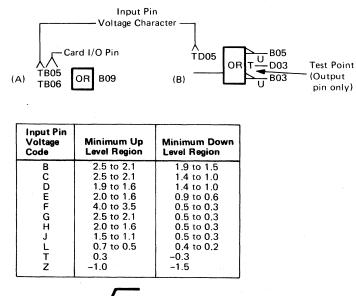

#### Voltage Levels

| Technology | MST-1  | MST-2  | MS     | <b>T</b> ∙4 |

|------------|--------|--------|--------|-------------|

|            |        |        | Input  | Output      |

| MPUL       | -0.613 | +0.675 | +0.570 | +0.570      |

| LPUL       | -0.969 | +0.230 | +0.170 | +0 265      |

| LNDL       | -1.522 | -0.240 | -0.170 | -0 265      |

| MNDL       | -2.383 | -1.260 | -1.000 | -0.800      |

MPUL = Most positive up level

LPUL = Least Positive up level

LNDL = Least negative down level

MNDL = Most negative down level

a da la serie de la serie d

information see IBM Maintenance Library, Automated Logic Diagrams SLT, SLD, ASLT, MST, order number SY22-2798

LEGEND (Part 3 of 6)

### LEGEND (Part 4 of 6)

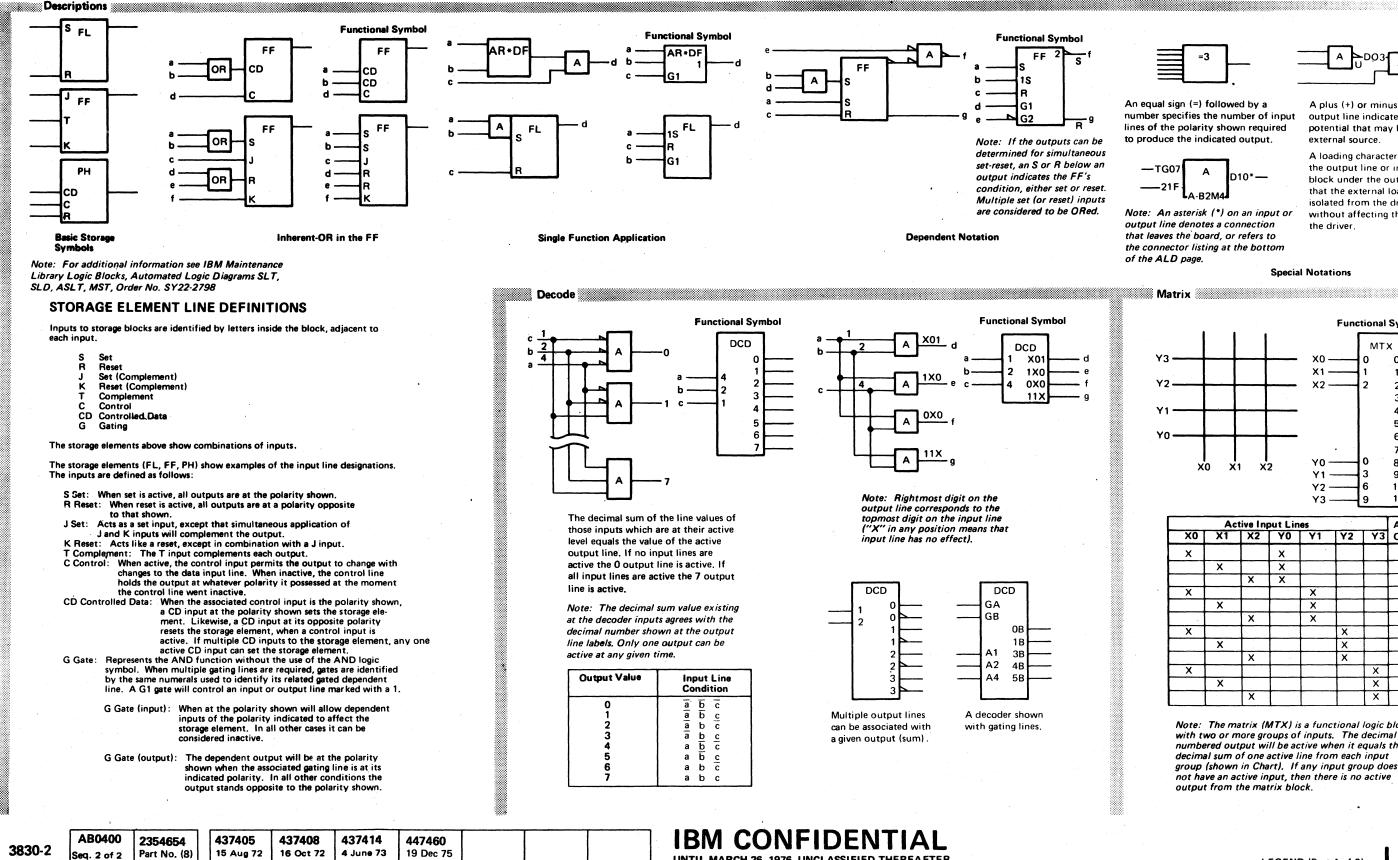

### FUNCTIONAL SYMBOLS

UNTIL MARCH 26, 1976, UNCLASSIFIED THEREAFTER

Copyright IBM Corporation 1972, 1973, 1975

LEGEND (Part 4 of 6)

An equal sign (=) followed by a number specifies the number of input lines of the polarity shown required to produce the indicated output.

Note: An asterisk (\*) on an input or output line denotes a connection that leaves the board, or refers to the connector listing at the bottom of the ALD page.

**LGND 12**

A plus (+) or minus ( ) under an output line indicates the extreme potential that may be forced by an external source.

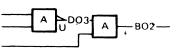

A loading character (L or U) under the output line or in the edge of the block under the output line indicates that the external load cannot be isolated from the driving circuit without affecting the output of the driver

#### **Special Notations**

Matrix

Functional Symbol MTX 0 X 1 ¥2 VO-Y1 Y2 **Y**3

|    | Active Input Lines |    |     |    |    |    |        |

|----|--------------------|----|-----|----|----|----|--------|

| X0 | X1                 | X2 | YO  | Y1 | Y2 | Y3 | Output |

| x  |                    |    | X   |    |    |    | 0      |

|    | x                  | 1  | X   | 1  |    |    | 1      |

|    |                    | X  | X   |    |    | I  | 2      |

| X  |                    |    | · · | X  |    |    | 3      |

|    | X                  |    |     | X  |    |    | - 4    |

| 5  |                    | X  |     | X  |    |    | 5      |

| X  |                    |    |     |    | X  |    | 6      |

|    | X                  |    |     | 1  | X  |    | 7      |

|    |                    | X  |     |    | X  |    | 8      |

| X  |                    |    |     |    |    | X  | 9      |

|    | X                  |    |     |    | 1  | X  | 10     |

|    |                    | X  |     |    | 1  | X  | 11     |

Note: The matrix (MTX) is a functional logic block with two or more groups of inputs. The decimal numbered output will be active when it equals the decimal sum of one active line from each input group (shown in Chart). If any input group does not have an active input, then there is no active output from the matrix block.

## LEGEND (Part 4 of 6) LGND 12

### LEGEND (Part 5 of 6)

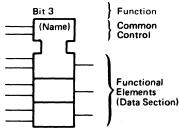

### **Element Description**

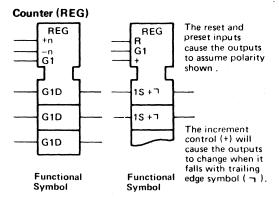

COMMON CONTROL SECTION: Used only for dependency (gating) and/or common lines for the register. There are no outputs from the common section.

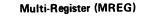

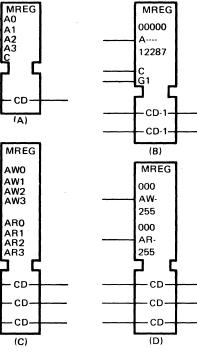

NAME: May be any of the following: selector (SEL), register (REG), decoder (DCD), matrix (MTX), multiregister (MREG), and delay (DLY).

DATA SECTION: A group of vertically stacked functional elements. The number of stacked elements will vary with the number of inputs.

Note: The function of the logic element may be placed above the common control section outside the logic block.

#### **Common Function (COM)**

**DEFINITION:** Common Function block may be associated with any group of basic logic elements functionally related by their dependent gating. Each functional element shall contain the proper letter(s) that makes it an approved logic symbol. The common section may contain the letters COM at the very top line.

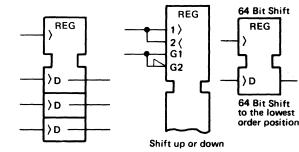

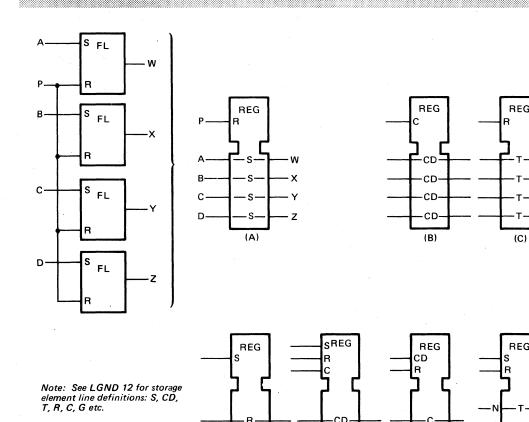

### Shift Register (REG)

DEFINITION: The control input causes the data in each bit position to shift one position as indicated by one of the following designations.

" > " (greater than) When this line goes active the data content will shift from the top (uppermost) bit position. Similarly, the contents of each bit position will shift down the symbol.

" ( " (less than) When this line goes active, the data content will shift from the bottom to the next bit position above and similarly for each bit position in the shift register symbol

Note: A time difference in shifting will be indicated by a trailing edge symbol ( - ).

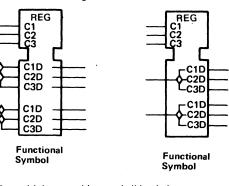

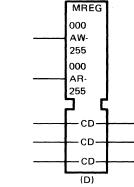

#### **Multi-Control Register (REG)**

The multiple control inputs shall be designated by sequential numbers shown entering the common section; for example, C1, C2.

The control data shall enter the data section of the symbol and will normally be diagrammed as multiple outputs.

The "C" designator must be a suffix to differentiate it from a gate.

437414

#### Example

437408

15 Aug 72 16 Oct 72 4 June 73

CID = Storage Data output controlled by C1. Note: The "\o" symbol represents the OR function connection in the data section.

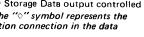

The numeric address span shall be specified in the common section. "G" will replace the C to control the data information in the MREG. The C is reserved for the condition that would place a zero in all storage cells not addressed.

SEL CD CD Functional Symbol Α CD

Address notation A, AR, or AW must prefix

on an address

(A)

(B)

(C)

(D)

AWCD).

the data. This indicates the data is dependent

A = Read Only Storage (ROS) or when

AW = Write address. AW must be shown as data input dependent; (for example,

AR = Read address. AR must be shown as

a dependency with the output.

Example Input Lines Needed Output Lines Needed

A(0, 1, 2, 3)

A(0-12287)

G1 (gate)

CD (data)

CD (data)

AR(0-255)

CD (data)

AR(0, 1, 2, 3)

CD (data)

A(0, 1, 2, 3)

A(0-12287)

AW(0, 1, 2, 3)

AW(0-255)

CD

CD

CD

CD

the read/write address is identical.

Output "h" is active when input lines "e' and "a" are active and the output gate line "b" is active

REG

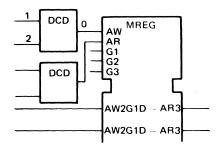

DEFINITION: A register logic block consisting of a group of associated storage elements with common input and/or output gating or other common input lines such as reset.

Note: Descriptive nomenclature such as bit 1, may be placed above each logic element

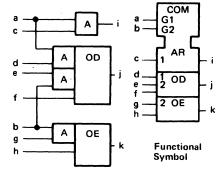

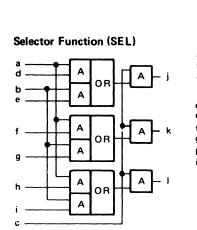

**DEFINITION:** A selector is a functional logic block consisting of two or more OR blocks having input and/or output signals dependent upon common gates,

### Example

Output line "i" is active when line "c" is active and lines "d" and "a" or lines "e" and "b" are active.

Note: The "\" symbol represents the **OR** function connection in the data section.

3830-2

AB0500 Seq. 1 of 2 Part No. (

Copyright IBM Corporation 1972, 1973

2354655

437405

#### LEGEND (Part 5 of 6) **LGND 14**

ELEMENTS WITH COMMON INPUTS/OUTPUTS (Part 1 of 2)

#### ORDER AND SELECTION OF FUNCTIONAL SYMBOLS HAVE THE FOLLOWING EFFECT

Note: No writing will take place in the addressed storage cell unless G1 is active. No readout will occur from the decoded address unless G3 is active.

- G1 Active at its indicated polarity:

- (a) Data and G2 active with a decoded address = write a one

- (b) Data or G2 inactive for a decoded address = write a zero

Note: The output will be active from a decoded address if a one had been stored in the storage element and G3 is active. If a zero had been stored or G3 is inactive, the outputs will be inactive.

DEFINITION: A Register to be incremented or decremented under control of input lines drawn to the common section of the symbol with the follow notations.

"+n" When this line goes to its indicated polarity the decimal quantity n is added to the binary count contained in the register. The n need not appear when it is a one.

"-n" When this line goes to its indicated polarity, the decimal quantity n is subtracted from the binary count contained in the register, The n need not appear when it is a one.

### LEGEND (Part 5 of 6) LGND 14

### LEGEND (Part 6 of 6)

(E)

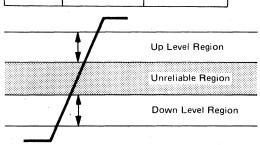

Example A shows four FL blocks with a common reset.

Example B shows four PH blocks with a common control line.

Example C shows four FF blocks with a common reset.

Example D shows a register with gate. The G1 gate-in line is needed to set bits into the register (upper set of inputs); ORed with each of these inputs (by a diamond) is an ungated input. The G2 gate-out line is necessary to produce an output.

Example E shows a set line common to two positions.

Example F shows two data positions capable of being set or reset by a single S or R input.

Example G shows a data line common to more than one control input; whatever data is available at CD is stored into a position when the appropriate C input is active.

Example H shows a multiposition register in which the state of a position depends on the data stored in the previous position. In the example, each position can be set or reset by the common S or R line. Whenever a negative shift appears at the input to the first position, the position complements; the second position, likewise, complements only if the first position changes from plus to minus.

1♦ C D-

l⊘CD

(D)

BEG

CD

Example J is similar to H except that CD lines appear in the data section. At any time, the data available to the first position is stored in that position (and reflected at its output) when the control line shifts negatively. All remaining positions of the register store the data available at the immediately previous position. Note: The N external to the block indicates that a negative pulse or shift activates the control line (nonstandard).

Note: The "O" symbol represents the OR function connection in the data section of the logic block.

| 3830-2 | AB0500<br>Seq. 2 of 2 | 2354655<br>Part No. () | <b>437405</b><br>15 Aug 72 | <b>437408</b><br>16 Oct 72 | <b>437414</b><br>4 June 73 |  |  |

|--------|-----------------------|------------------------|----------------------------|----------------------------|----------------------------|--|--|

| 1 S .  | C Copyright IB        | M Corporation 1972,    | 1973                       |                            |                            |  |  |

CD

(F)

(G)

ELEMENTS WITH COMMON INPUTS/OUTPUTS (Part 2 of 2)

Voltage Codes

#### **Additive Card Code**

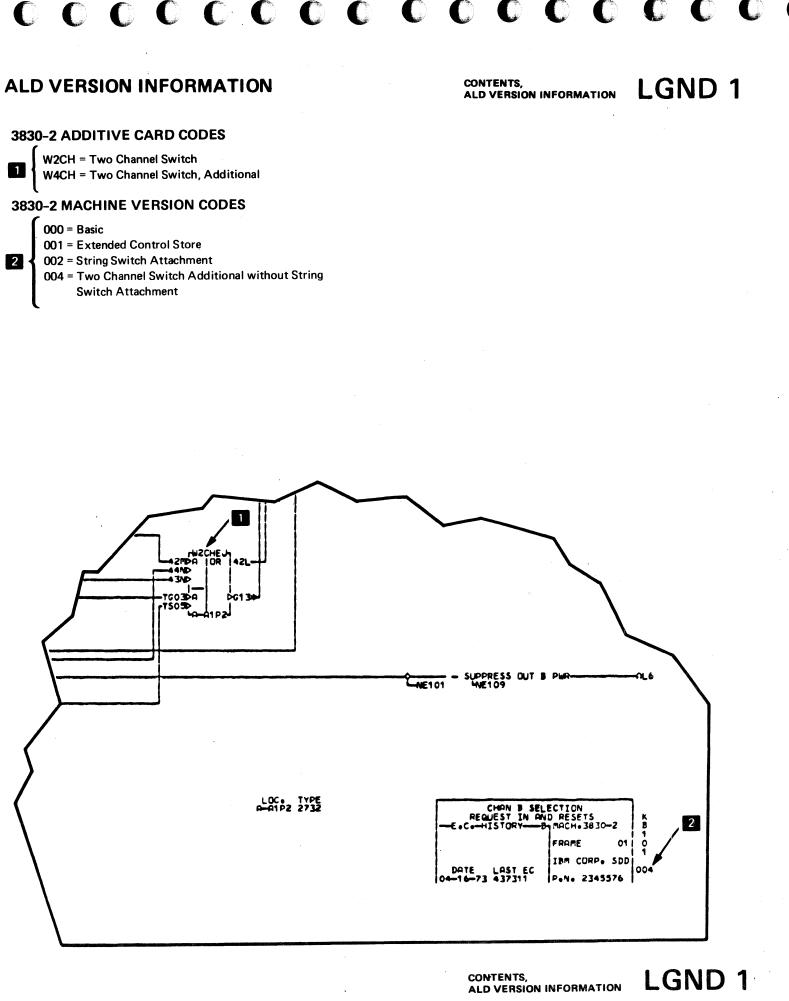

Line 1 (top line) of the logic block contains the additive card code. The additive card code may contain as many as four characters. The additive card code identifies the logic associated with special features and unique functions. See example.

W2CH = With 2 channel switch. W4CH = With 4 channel switch. = Optional feature (not designated) OPF-WM4K = With more than 4K of memory. WISC = With integrated storage control. = Not integrated storage control NISC N2CH Not 2 channel switch.

LEGEND (Part 6 of 6)

LGND 15

### Edge of Block Character

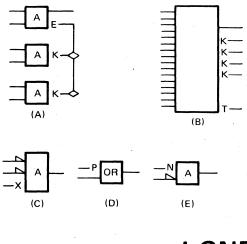

An edge of block character, alongside or in the edge of an FEALD (MST) block, serves the following functions: Example A E An extender. In combination with a K output, shows that additional blocks act as inputs to the first block. Example A K At the output of a block, a K can connect to another K output or to an E output; these K "outputs" are actually inputs to the first block (with the output E) and extend its function. Example B K At times, the number of inputs to a logic block exceeds design automation program capabilities. In this case, the excess inputs are shown as outputs but identified with the letter K. Example C X A nonlogic input or output. The driving circuit to this input is usually a fixed voltage or bias. An X line does not influence the state of a circuit. Example D P A positive-going shift or pulse activates the block. Example E N A negative-going shift or pulse activates the block. Example B T A test point. Do not confuse this with T as an input voltage character.

Note: U (unloaded) may be used in the edge of a block below the line affected. See LGND 12 for definition.

LEGEND (Part 6 of 6)

### LGND 15

### ABBREVIATIONS AND DEFINITIONS (Part 1 of 3)

Α

| <b>V</b>           | AND function; Amperes                                | CCHHR         | Cylinder (2 bytes), Head (2 bytes), Record (1 b | yte)            | Microinstruction field, the contents of which              |

|--------------------|------------------------------------------------------|---------------|-------------------------------------------------|-----------------|------------------------------------------------------------|

| .*OR               | AND-OR function                                      | CCU           | Common Control Unit (Same as CU, SCU)           |                 | are gated to IAR high;                                     |

| CR                 |                                                      | CCW           | Channel Command Word                            |                 | Converter (Logic block)                                    |

| DDRO               |                                                      | CD            | Microinstruction field that is decoded to       | CW              | Microinstruction field, the contents of which              |

| DD, ADR, ADDR      | Address                                              |               | select a GP register to serve as destination    |                 | are gated to IAR high and the A register.                  |

| GC                 | Automatic Gain Control                               |               | -                                               | сх              | Microinstruction field, the contents of whi                |

| LD                 | Automated Logic Diagram                              |               | register;                                       | CX .            |                                                            |

| LT                 | Alternate                                            |               | Core driver                                     |                 | are gated to IAR low                                       |

| LU                 | Arithmetic Logic Unit                                | CDS           | Configuration Data Set                          | CYC             | Cycle                                                      |

| M                  | Address Marker                                       | CE            | Customer Engineer;                              | CYLINDER        | A vertical surface formed of tracks                        |

| NPC                | Angular Position Counter                             |               | Channel End                                     |                 | on a storage device that can be                            |

| .R                 |                                                      | CEB           | Command Execution Byte                          |                 | accessed without repositioning the                         |

| R-MD               | Amplifier, Magnet Driver (Logic block)               | CFEALD        | Condensed Field Engineering                     |                 | access mechanism                                           |

|                    | A bit configuration that bears                       | UI LALD       | Automated Logic Diagram                         |                 |                                                            |

|                    |                                                      | 011           |                                                 |                 |                                                            |

| SLT                | Advanced Solid Logic Technology                      | СН            | Microinstruction field that is decoded to       | D               |                                                            |

| SM, ASY, ASSM      | Assembly                                             |               | select a hardware branch condition              |                 |                                                            |

| 131VI, AST, ASSIVI | Assembly                                             | CH, CHL, CHAN | Channel                                         | DAR             | Data Address Register                                      |

| 2                  |                                                      | CHAINING      | Sequential linking of instructions or data      | DASD            | Direct Access Storage Device                               |

| 3                  |                                                      | CHANB, CHB    | Channel B                                       | DCC             | Disconnected Command Chain                                 |

|                    | Blower, air                                          | CHK-1         | Check 1                                         |                 |                                                            |

|                    | •                                                    | CHK-2         | Check 2                                         | DCD             | Decoder (Logic Block)                                      |

| AR                 | Backup Address Register                              | СНКА          | Check A                                         | DCI             | (See CI – CTL-I)                                           |

| BCCHH              | Bin (2 by tes), by inder (2 by tes), neud (2 by tes) |               | Channel Interface                               | DDA             | Direct Disk Attachment (125)                               |

| CD                 | Binary Coded Decimal                                 | CHL-I         |                                                 | DE              | Device End                                                 |

| DY-2               | Boundary 2 (Branch Indicator)                        | CI, CTL-I     | Control Interface                               | DEC             | Decode                                                     |

| FRDY               | Buffer Ready                                         | CIB           | Compressed Index Block                          | DEC0            | Decode Time 0 (Branch Indicator)                           |

| IN                 | Binary                                               | СК            | Microinstruction field the contents of which    | DELTA, $\Delta$ | A three-terminal circuit configuration                     |

| LK                 | Block                                                |               | are gated to the A-register                     | DELIA, A        | -                                                          |

| OPAR               |                                                      | CKD           | Count-Key-Data                                  |                 | (usually refers to the primary winding                     |

| OUNDARY            |                                                      | CL            | Microinstruction field that is decoded to       |                 | arrangement of a transformer).                             |

|                    | Limit or extent as: a Word Boundary                  | 02            | select a hardware branch condition              |                 | Also used to indicate a change in some                     |

| R, BRCH            | Branch                                               |               |                                                 |                 | dimension, such as:                                        |

| SCA                | Bit Significant Controller Address                   | CLD           | CAS Logic Diagram                               |                 | $\Delta t$ = change in time; $\Delta d$ = change in distar |

| SDA                | Bit Significant Device Address                       | CLK           | Clock                                           | DEV             | Device                                                     |

| SM                 | Basic Storage Module                                 | CM            | Centimeters; Control Module                     | DF              |                                                            |

| TRDY               | Byte Ready                                           | CMMD, CMD     | Command                                         |                 | Differential Amplifier                                     |

| TU                 | British Thermal Units                                | COM           | Common Function (Logic Block)                   | DIAG            | Diagnostic                                                 |

| UF, BFR            | Buffer                                               | COMMO         | Command Out (Branch Indicator)                  | DIFF            | Difference Counter                                         |

| UFUL               | Buffer full                                          | COMP          | Compare                                         | DISC            | Disconnect                                                 |

| YTE                | Eight bits plus a parity bit                         | COND          | Condition                                       | DISP            | Display                                                    |

|                    | Eight bits plus a parity bit                         | CP            | Circuit Protector                               | DL              | Data (area) length                                         |

|                    |                                                      |               | Central Processing Unit                         | DLY             | Delay (Logic Block)                                        |

| <b>_</b>           |                                                      | CPU           | -                                               | DLYD            | Delayed                                                    |

| ;                  | Capacitor: coulombs                                  | CR            | Diode; rectifier (semiconductor)                |                 | •                                                          |

| A                  | Microinstruction field that is decoded to            | CRY           | Carry                                           | DM              | Data Module                                                |

| <b>A</b>           |                                                      | CS            | Current Switch;                                 | DO              | Data Out                                                   |

|                    | select a GP register to serve as A-entry register    |               | Microinstruction field that is decoded to       | DRV             | Drive                                                      |

| AR                 | Cylinder Address Register                            |               | set or reset specific ST register bits          | DS              | Lamp (indicator)                                           |

| AS                 | Control Automation System;                           | CSW           | Channel Status Word                             | DVM             | Digital Voltmeter                                          |

|                    | Compare Address Switches                             | CTL-I, CI     | Control Interface                               |                 | -                                                          |

| B                  | Circuit Breaker;                                     |               |                                                 |                 |                                                            |

|                    | Microinstruction field that is decoded to            | CTR, CNT      | Counter, Count                                  |                 |                                                            |

|                    | select a GP register to serve as B-entry register    | CTRL          | Control                                         |                 |                                                            |

|                    |                                                      | CU            | Control Unit (Same as CCU, SCU)                 |                 |                                                            |

| C=3                | Condition Code 3                                     | CUDI          | Control Unit Device Interface                   |                 |                                                            |

| CB                 | Correction Code Byte                                 | CUEND         | Control Unit End (Branch Indicator)             |                 |                                                            |

| CC 30              | Correction Code Check                                | CURR          | Current                                         |                 |                                                            |

| СНН                |                                                      |               |                                                 |                 |                                                            |

© Copyright IBM Corporation 1972, 1973, 1974

Seq. 1 of 2 Part No. ()

15 Aug 72 16 Oct 72

4 June 73 15 Apr 74

3830-2

### ABBREVIATIONS AND DEFINITIONS (Part 1 of 3)

**LGND 16**

### Ε

EC ECC ECD EDI EL ENTR EOF EREP ERP ERR Eν EXPTD EXT

C

F FCCHH

FEALD

FET FF FL FM

FRU FSC FSI

Edge connector; Engineering Change Error Correction Code Error Condition (check) Diagram Expected Device Interrupt Error Log Entry •End of File Environmental Record Edit and Print Error Recovery Program Error Even (Logic Block) Expected External

Flag; Fuse; farads (capacitor) Flag (1 byte), Cylinder (2 bytes), Head (2 bytes) Field Engineering Automated Logic Diagram Fetch Flip-Flop (Logic block) Flip Latch (Logic block); Filter Microinstruction bit that is decoded to perform a specific CU gating function that determines format; Frequency Modulator; File Mask Field Replaceable Unit Fault Symptom Code Fault Symptom Index

**LGND 16**

### ABBREVIATIONS AND DEFINITIONS (Part 1 of 3)

### ABBREVIATIONS AND DEFINITIONS (Part 2 of 3)

|               | Giga – (10 <sup>9</sup> ); grams     | 10,1/0        | Input/output                                                           | MIC, MICRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Microprogram, microdiagnostic                      |

|---------------|--------------------------------------|---------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| G             |                                      | ID,I/O<br>IPL | Initial program load                                                   | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Minimum; minutes                                   |

| G1            | Gap between index point and R0       | ISCB          | Initial selection control block                                        | ML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Microinstruction field whose contents are          |

| G2            | Gap between count area and key area  | ISCB          |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | gated to DAR high                                  |

| G3            | Gap between data area and address    |               |                                                                        | MLM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maintenance Library Manual                         |

| C4            | marker of the following record       |               |                                                                        | MLX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maintenance library cross reference index          |

| G4            | Gap after data area of the last      | J             |                                                                        | MODULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A functional unit built to operate with            |

| OFN           | record on a track                    | J             | Connection, receptacle; jack plug                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | other components                                   |

| GEN           | Generator                            | JCL           | Job control language                                                   | MPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Microprogram load                                  |

| GND           | Ground                               | JMPR          | Jumper                                                                 | MREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Multiregister (logic block)                        |

| GPR           | General purpose register             |               |                                                                        | MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Message                                            |

|               |                                      | 1/            |                                                                        | MST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Monolithic System Technology; master               |

|               |                                      | Κ             |                                                                        | МТ, М/Т                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Multiple track                                     |

|               |                                      |               | K                                                                      | MTX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Matrix (logic block)                               |