0

GA34-0289-1 File No. S1-16

IBM Series/1 4956 Processor Models E and E10 Description Series/1

Series/1

GA34-0289-1 File No. S1-16

IBM Series/1 4956 Processor Models E and E10 Description

#### Second Edition (January 1986)

Use this publication for the purpose stated in the preface.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or service in your country.

Publications are not stocked at the address given below. Request for copies of IBM publications should be made to your IBM representaive or the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, address your comments to IBM Corporation, Information Development, Department 28E, Internal Zip 1803, P. O. Box 1328, Boca Raton, Florida 33429-1328. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

© Copyright International Business Machines Corporation 1984, 1986

# Preface

|                          | This publication describes the unique functional characteristics and the optional features of the IBM Series/1 4956 Processor Models E and E10. This publication also provides reference information about the possible configurations and feature operations of the processor. Refer to the <i>IBM Series/1 Principles of Operation</i> , GA34-0152, for the common Series/1 processor functional characteristics and instructions. |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | This publication is intended primarily as a reference manual for experienced programmers who require machine code information to plan, correct, and modify programs written in the assembler language. The reader should understand data processing terminology and be familiar with binary and hexadecimal numbering systems.                                                                                                       |

|                          | Chapter 1, "Introduction," contains a general description of the processor, processor storage, and processor features. This chapter also contains information about changes to the programming instruction set.                                                                                                                                                                                                                      |

|                          | Chapter 2, "Processor Storage Addressing Using the Relocation Translator," describes the relocation translator, including:                                                                                                                                                                                                                                                                                                           |

|                          | Relocation addressing                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | Storage-protection mechanism                                                                                                                                                                                                                                                                                                                                                                                                         |

|                          | • Error-recovery considerations.                                                                                                                                                                                                                                                                                                                                                                                                     |

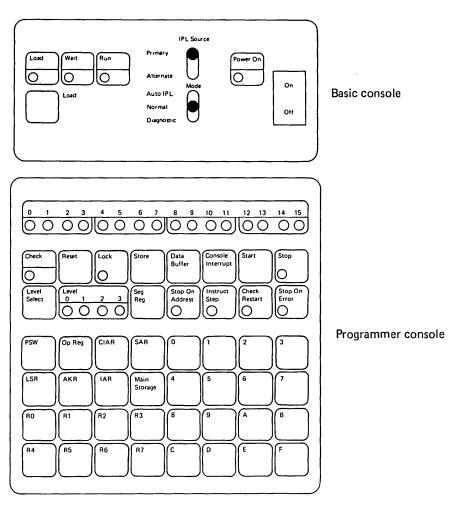

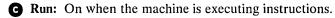

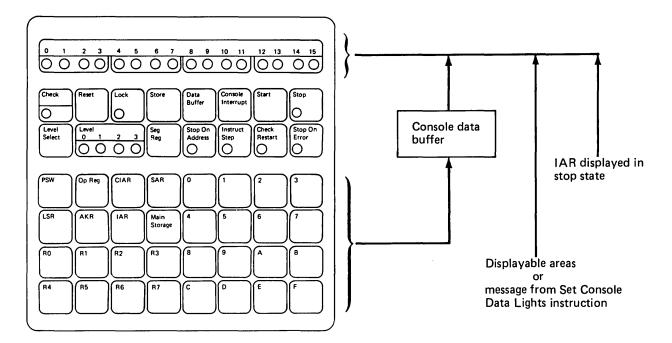

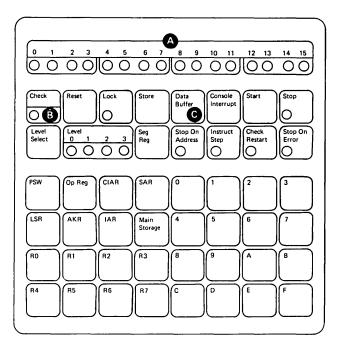

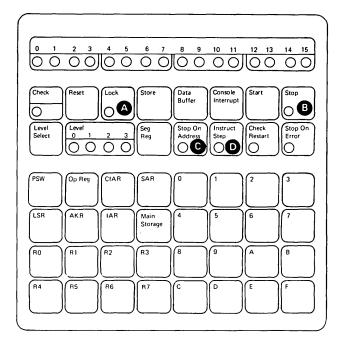

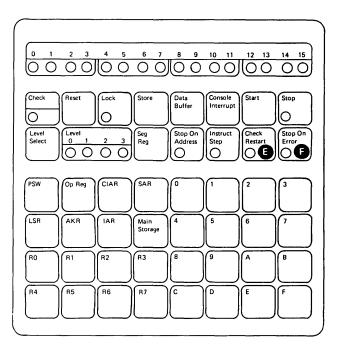

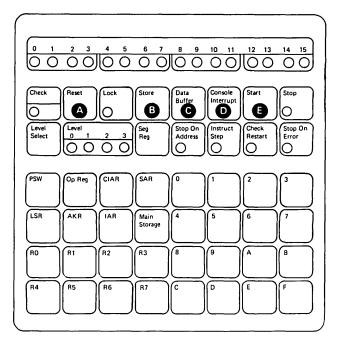

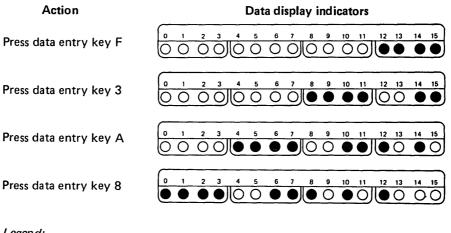

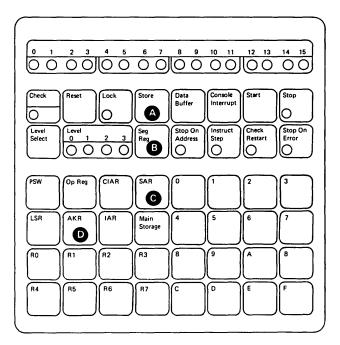

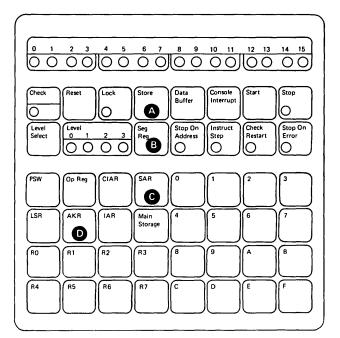

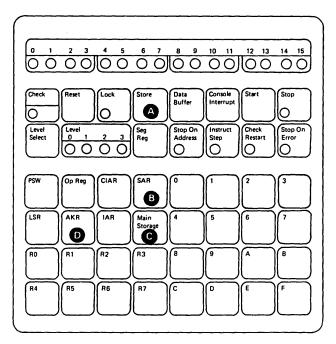

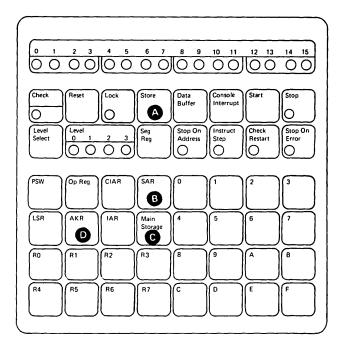

|                          | Chapter 3, "Console," describes the keys, switches, and indicators for the basic console and the optional programmer console. Typical manual operations, such as storing into and displaying processor storage, are presented.                                                                                                                                                                                                       |

|                          | Chapter 4, "Diagnose (DIAG) Instruction," describes the Diagnose instruction.                                                                                                                                                                                                                                                                                                                                                        |

|                          | Appendix A, "Instruction Execution Times," contains information for determining instruction execution times and instruction throughput.                                                                                                                                                                                                                                                                                              |

|                          | Appendix B, "Software Notes," lists some software notes for the processor.                                                                                                                                                                                                                                                                                                                                                           |

|                          | Appendix C, "Error Log," describes the error log and explains its use as an aid in isolating errors.                                                                                                                                                                                                                                                                                                                                 |

| Prerequisite Publication |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                          | For a description of the processor architecture and a detailed description of the instruction set for the IBM Series/1 processors, refer to the <i>IBM Series/1 Principles of Operation</i> , GA34-0152.                                                                                                                                                                                                                             |

۹

4

-

## Contents

Chapter 1. Introduction 1-1 Processor Description 1-4 Storage Cards 1-7 Card Plugging Assignments 1-8 Input/Output Units, I/O Features, and Processor Options 1-9 Program-Controlled Mode Switching 1-10 Address Key Register (AKR) 1-10 Processor Status Word (PSW) Register 1-11 Modified Instructions 1-12 Set Address Key Register (SEAKR) 1-12 Copy Address Key Register (CPAKR) 1-16 Set Segmentation Register (SESR) 1-20 Copy Segmentation Register (CPSR) 1-23 Copy Processor Status and Reset (CPPSR) 1-26 Enable (EN) 1-27 Disable (DIS) 1-28 New Instructions 1-29 ARIB Instruction Format 1-29 **ARIBON Instruction Format 1-31 ARIBOFF Instruction Format 1-31** ARIB Execution 1-32 Chapter 2. Main Storage Addressing Using the Relocation Translator 2-1 Translator Description 2-1 Storage Mapping 2-2 Relocation Addressing 2-2 I/O Storage Access Using the Relocation Translator 2-4 Status of Translator After Power Transitions and Resets 2-4 Error-Recovery Considerations 2-5 Invalid Storage Address (ISA) 2-5 Protect Check 2-5 Address Space Management 2-6 Active Address Key 2-6 Equate Operand Spaces (EOS) 2-6 Address Space 2-7 Address Key Values After Interrupts 2-9 Chapter 3. Console 3-1 Basic Console 3-2 Indicators 3-3 Programmer Console 3-3 Console Display 3-4 Indicators 3-5 Combination Keys/Indicators 3-6 Keys and Switches 3-12 **Displaying Registers 3-17** Storing Into Registers 3-17 **Displaying Segmentation Registers 3-18** Storing Into a Segmentation Register 3-20 Displaying Main Storage Locations 3-22 Storing Into Main Storage 3-24 Chapter 4. Diagnose (DIAG) Instruction 4-1 Storage Select 4-3 Storage Select Word 4-3 Storage Select Byte/ECC Code Bits 4-4 Local Storage Register Select 4-5 Channel Select 4-6 Set System ID 4-6 Error Log Select 4-7 Indicators 4-7 Program-Check Condition 4-7

Appendix A. Instruction Execution Times A-1

Appendix B. Software Notes B-1

Appendix C. Error Log C-1 Purpose C-1 Structure C-1 Machine Check C-2 Program Check C-2 Stall Detector/Timer Overrun Error C-2 Format of Log Entries C-3 Machine Check C-3 Program Check C-3 Priority Interrupt Entries C-4

.

a.

•

Index X-1

## **Chapter 1. Introduction**

The IBM Series/1 4956 Processor Models E and E10 are compact general-purpose computers. The models are the same, except for basic storage. Model E has 256 or 512 kilobytes of basic storage; Model E10 has 1024 kilobytes of basic storage.

The processor is microcode-controlled for both automatic functions and program instruction functions. It occupies the full width of a standard 483-millimeter (19-inch) rack (see Figure 1-1). It contains thirteen card sockets for data channel features and a channel repower card. Three of the thirteen card sockets can also be used for additional processor storage cards.

Figure 1-1. IBM Series/1 4956 Processor Models E and E10

The processor has the following characteristics:

- Four priority interrupt levels, with independent registers and status indicators for each level.

- Automatic and program-controlled level switching.

- An instruction set that includes stacking and linking facilities, multiply and divide, variable-field-length byte operations, and a variety of arithmetic and branching instructions.

- Supervisor and problem states.

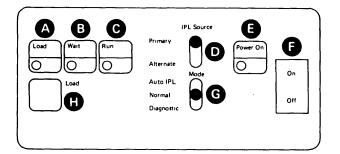

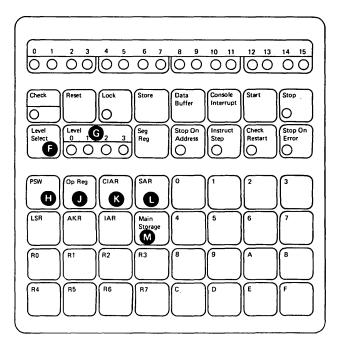

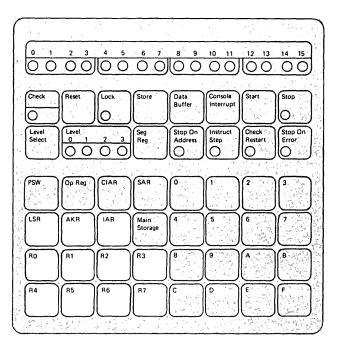

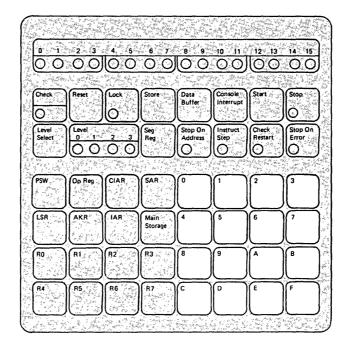

- A basic console that is a standard feature; a programmer console that is an optional feature.

- Basic main storage and up to three additional storage increments of either 256 kilobytes, 512 kilobytes, or 1024 kilobytes, with a maximum possible storage of 2048 kilobytes (2 megabytes).

- A storage address relocation translator that allows addressing of main storage larger than 64 kilobytes.

- Program-controlled mode switching that allows the user to specify the maximum mappable storage range:

- 512K bytes in 3-bit mode

- 1024K bytes (1 MB) in 4-bit mode

- Prefetching instruction stream. (Refer to Appendix B.)

- An error correction code (ECC) that is implemented on the storage card to provide the capability for single-bit error correction and double-bit error detection.

- An error log that provides a history of errors that have occurred since power-on. (Refer to Appendix C.)

- A clock/comparator with four instructions provided to set or copy the clock and comparator.

- Channel capability as follows:

- Asynchronous, multidropped channel

- 256 input/output (I/O) devices can be addressed

- Direct program control and cycle-steal operations

- Maximum burst output data rate of 1.11 million 16-bit words per second (see Note)

- Maximum burst input data rate of 1.54 million 16-bit words per second (see Note).

**Note:** The burst output and burst input data rates are reduced from the values shown by data channel attachment characteristics, channel loading during instruction processing, channel repowering, and processor storage refresh requirements.

- Throughput that is approximately 50% greater than previous models of the 4956.

- A redefined 16-bit address key register (AKR).

- A redefined 16-bit processor status word (PSW) register.

- Several instructions modified for 4-bit mode:

- Set Address Key Register (SEAKR)

- Copy Address Key Register (CPAKR)

- Set Segmentation Registers (SESR)

- Copy Segmentation Registers (CPSR)

- Enable (EN)

- Disable (DIS)

- Copy Processor Status and Reset (CPPSR)

Note: For an explanation of the standard Series/1 instruction set, refer to *IBM Series/1 Principles of Operation*, GA34-0152.

- Three new instructions in the instruction set:

- Address Resolution with Indirect Branch (ARIB)

- Address Resolution with Indirect Branch—On (ARIBON)

- Address Resolution with Indirect Branch—Off (ARIBOFF)

## **Processor Description**

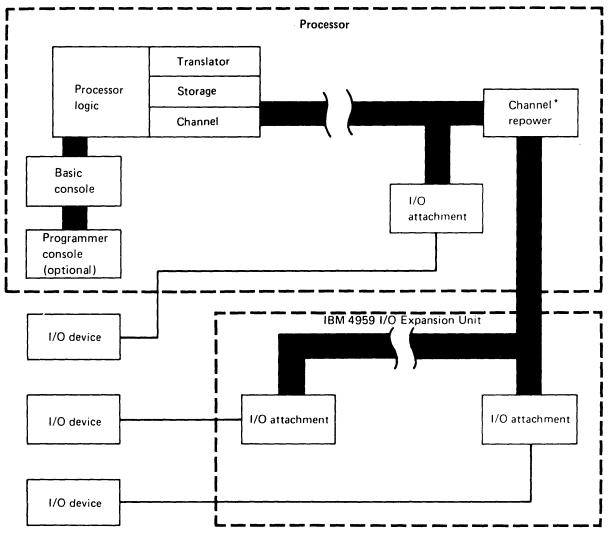

The basic processor includes the processor card, a basic storage card, and a basic console. Figure 1-2 shows a block diagram of the processor and an IBM Series/1 4959 Input/Output Expansion Unit.

\*Required with an expansion unit.

Figure 1-2. Block Diagram of the Processor and an IBM 4959 I/O Expansion Unit

Four priority interrupt levels (0-3) are implemented in the processor. Each level has an independent set of machine registers. Level switching can occur in two ways: (1) by program control, or (2) automatically upon acceptance of an I/O interrupt request. The interrupt mechanism provides 256 unique entry points for I/O devices.

Note: A Prepare command to levels 4-15 is executed so that condition code reporting occurs; however, the Prepare command is not executed at the addressed device and effectively results in a no-operation.

The processor instruction set contains a variety of instruction types. These include:

- bit manipulation

- shift

- branch

- register immediate

- storage immediate

- register to register

- register to storage

- storage to register

- storage to storage

- system register to storage

- multiple register to storage

- variable byte field.

Supervisor and problem states are implemented, with appropriate privileged instructions for the supervisor.

The basic console is intended for dedicated systems that are used in a primarily unattended environment. Only minimal controls are provided. A programmer console, which can be added as a feature, provides a variety of indicators and controls for operator-oriented systems.

An error correction code (ECC) is implemented on the storage card. ECC gives the storage card the capability of single-bit error correction and double-bit error detection. ECC provides the user a higher system availability.

**Note:** When a double-bit error in storage is detected during a processor read, a machine check interrupt occurs with PSW bit 8 set to 1 (storage parity error).

There is no storage-protect feature in the processor. However, there is a read-only protect capability provided by the address translator when it is enabled.

**Note:** Execution of the Set Storage Key (SESK) and Copy Storage Key (CPSK) instructions results in a no-operation.

I/O devices are attached to the processor through the processor data channel. The data channel directs the flow of information between the I/O devices, the processor, and main storage. The data channel supports a maximum of 256 addressable devices.

The data channel supports:

- **Direct program control operations**. Each Operate I/O instruction transfers a byte or word of data between main storage and the device. The operation may or may not terminate in an interrupt.

- Cycle-steal operations. Each Operate I/O instruction initiates multiple data transfers between main storage and the device. The maximum cycle-steal transfer per device control block (DCB) is 65,535 bytes. Cycle-steal operations are overlapped with processor operations and always terminate in an interrupt.

- **Interrupt servicing**. Interrupt requests from the devices, along with cycle-steal requests, are presented and polled concurrently with data transfers.

## **Storage Cards**

The processor supports three different size storage cards: 256 KB, 512 KB, and 1024 KB. The processor has a maximum of 2048 KB of storage. Any combination of storage cards may be used (with the exception of one 512 KB card with three 256 KB cards) to obtain the desired system storage size, up to the maximum of 2048 KB. (The relocation translator must be enabled to select addresses above 64K bytes.)

Several other rules apply for proper storage card plugging:

- All storage cards are plugged in decrementing order from the processor card.

- No card sockets may be left unused between storage cards.

- Storage cards must be plugged in the order for which they are jumpered.

- Any card socket that is not used for additional storage may be used for any data channel feature or a repower card.

## **Card Plugging Assignments**

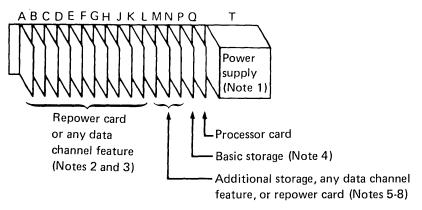

The processor unit contains power and space for additional features. The IBM Series/1 4959 Input/Output Expansion Unit and the IBM Series/1 4965 Storage and I/O Expansion Unit are available for adding additional features, if desired. Figure 1-3 shows the card plugging assignments for the processor.

Figure 1-3. Card Plugging Assignments

#### Notes:

- 1. The pluggable high-frequency power supply plugs into card socket T.

- 2. If a channel repower card is used, it must be plugged to the left of and adjacent to the leftmost I/O card installed.

- 3. A maximum of five serially-connected channel repower features can be driven by each processor. Any processor system that includes an IBM I/O expansion unit with the two-channel switch feature is limited to three channel repower features.

- 4. The processor contains 256 KB (kilobytes), 512 KB, or 1024 KB of basic storage in socket P.

- 5. The processor supports three different size storage cards; 256 KB, 512 KB, and 1024 KB. Sockets N, M, and L are available for additional storage cards. Any combination of storage cards is permitted (except the combination of a single 512KB card with three 256KB cards), up to the maximum storage capacity of 2048 KB. Any card socket that is not used for additional storage may be used for any data channel feature or a repower card.

- 6. All storage cards are plugged in decrementing order from the processor card.

- 7. No card sockets may be left unused between storage cards.

- 8. Storage cards must be plugged in the order for which they are jumpered.

## Input/Output Units, I/O Features, and Processor Options

A variety of I/O units and features, plus several processor options, are available for use with the processor. For a list and description of system units and features, refer to the *IBM Series/1 System Selection Guide*, GA34-0143, and the *IBM Series/1 Digest*, G360-0061. Detailed information about I/O units and features can be found in separate publications. The order numbers for these publications are contained in the *IBM Series/1 Graphic Bibliography*, GA34-0055.

The floating-point feature is one of the available options. If the floating-point feature is installed, refer to Appendix A for instruction execution times. For a detailed description of this feature, refer to the *IBM Series/1 Principles of Operation*, GA34-0152.

## **Program-Controlled Mode Switching**

Program-controlled mode switching allows the user to specify the maximum mappable storage range:

- In 3-bit mode, the maximum mappable storage is 512K bytes. Operand 1 key (OP1K), operand 2 key (OP2K), and instruction space key (ISK) are specified in three bits. The translator uses 3 bits from the active address key and the five high-order bits of the logical address to select one of 256 segmentation registers when the translator is enabled.

- In 4-bit mode the maximum mappable storage is 1024K bytes (1 MB). In 4-bit mode, OP1K, OP2K, and ISK are specified in four bits. Eight additional stacks of 32 registers per stack are available for I/O operations. This allows 512K bytes of storage to be mapped for I/O only, independent of program mapping.

Bit 7 of the processor status word (PSW) indicates which mode the processor is currently in:

- When bit 7 is a 0, the processor is in 3-bit mode.

- When bit 7 is a 1, the processor is in 4-bit mode.

When both bit 7 and bit 14 (translator bit) are 1's, the I/O translator is enabled.

## Address Key Register (AKR)

The address key register (AKR) contains 16 bits. It is formatted as follows:

| For 3-bit mode: |                       | For 4 | -bit mode:            |

|-----------------|-----------------------|-------|-----------------------|

| Bit             | Data                  | Bit   | Data                  |

| 0               | Equate operand spaces | 0     | Equate operand spaces |

| 1               | 0                     | 1     | 0                     |

| 2               | 0                     | 2     | 0                     |

| 3               | 0                     | 3     | 0                     |

| 4               | 0                     | 4     | OP1K bit 0            |

| 5               | OP1K bit 0            | 5     | OP1K bit 1            |

| 6               | OP1K bit 1            | 6     | OP1K bit 2            |

| 7               | OP1K bit 2            | 7     | OP1K bit 3            |

| 8               | 0                     | 8     | OP2K bit 0            |

| 9               | OP2K bit 0            | 9     | OP2K bit 1            |

| 10              | OP2K bit 1            | 10    | OP2K bit 2            |

| 11              | OP2K bit 2            | 11    | OP2K bit 3            |

| 12              | 0                     | 12    | ISK bit 0             |

| 13              | ISK bit 0             | 13    | ISK bit 1             |

| 14              | ISK bit 1             | 14    | ISK bit 2             |

| 15              | ISK bit 2             | 15    | ISK bit 3             |

## Processor Status Word (PSW) Register

The processor status word (PSW) register contains 16 bits. It is formatted as follows:

#### Bit Data

- 0 Specification check

- 1 Invalid storage address

- 2 Privilege violation

- 3 Protect check

- 4 Invalid function

- 5 Floating point exception

- 6 Stack exception

- 7 4-bit mode enabled

- 8 Storage parity check

- 9

- 10 Processor control check

- 11 I/O check

0

- 12 Sequence indicator

- 13 Auto IPL

- 14 Translator enabled

- 15 Power thermal warning

.

## **Modified Instructions**

Modifications have been incorporated into several Series/1 instructions pertaining to their use with the processor. These modifications apply only for 4-bit mode operation; they do not apply for 3-bit mode operation. The instructions that have been modified are:

- Set Address Key Register (SEAKR)

- Copy Address Key Register (CPAKR)

- Set Segmentation Registers (SESR)

- Copy Segmentation Registers (CPSR)

- Enable (EN)

- Disable (DIS)

- Copy Processor Status and Reset (CPPSR).

**Note:** For an explanation of the standard Series/1 instruction set, refer to *IBM Series/1 Principles of Operation* GA34-0152.

## Set Address Key Register (SEAKR)

The Set Address Key Register (SEAKR) instruction has two formats:

- System register/register format for operations that load data from a specified register into the AKR.

- System register/storage format for operations that load data from main storage into the AKR.

#### System Register/Register Format

The system register/register format is:

| Mnemonic | Syntax | Instruction name            | K-field |

|----------|--------|-----------------------------|---------|

| SEAKR    | reg    | Set Address Key<br>Register | 011     |

| Extended<br>mnemonic                  | Syntax        | Instruction name                                                                                         | K-field |

|---------------------------------------|---------------|----------------------------------------------------------------------------------------------------------|---------|

| SEISK                                 | reg           | Set Instruction<br>Space Key                                                                             | 000     |

| SEOOK                                 | reg           | Set Operand 1 Key                                                                                        | 010     |

| SEOTK                                 | reg           | Set Operand 2 Key                                                                                        | 001     |

| <i>Op code</i><br>0 1 1 1<br><i>0</i> | K<br>1<br>4 5 | R         Function           1         0         1         0           7         8         10         15 |         |

The address key register (AKR) field specified by the K-field is loaded from the register specified by the R-field. The contents of the register are not changed.

**Note:** The K-field can specify either a field within the AKR or an entire AKR.

## For 3-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 13-15 |

| 001     | Operand 2 key                   | 9-11  |

| 010     | Operand 1 key                   | 5-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

### For 4-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 12-15 |

| 001     | Operand 2 key                   | 8-11  |

| 010     | Operand 1 key                   | 4-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

If the K-field specifies a specific field within the AKR, bits 13-15, for 3-bit mode, or bits 12-15, for 4-bit mode, from the register specified by the R-field are loaded into the AKR field. If the K-field specifies the entire AKR, bits 0-15 from the specified register are loaded into the AKR.

*Indicators*: The indicators are not changed.

*Program Checks*: This instruction format has the following program check:

• **Privilege violate** — The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

| Mnemonic                              | Syntax          | Instruction name                                                                                                                                     | K-field    |

|---------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| SEAKR                                 | addr4           | Set Address Key<br>Register                                                                                                                          | 011        |

| Extended<br>mnemonic                  | Syntax          | Instruction name                                                                                                                                     | K-field    |

| SEISK                                 | addr4           | Set Instruction                                                                                                                                      | 000        |

| SEOOK<br>SEOTK                        | addr4<br>addr4  | Space Key<br>Set Operand 1 Key<br>Set Operand 2 Key                                                                                                  | 010<br>001 |

| <i>Op code</i><br>0 1 0 1<br><i>0</i> | K<br>1<br>4 5 7 | RB         AM         Function           0         0         1         0           7         8         9         10         11         12         15 |            |

| Address/Di<br>Displac<br>16           | cement 1        | Displacement 2<br>3 24 31                                                                                                                            |            |

The address key register (AKR) field specified by the K-field is loaded from the word location in main storage that is specified by the effective address. The contents of the word in main storage are not changed.

Note: The K-field can specify either a field within the AKR or an entire AKR.

٠

.

#### For 3-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 13-15 |

| 001     | Operand 2 key                   | 9-11  |

| 010     | Operand 1 key                   | 5-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

#### For 4-bit mode:

.

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 12-15 |

| 001     | Operand 2 key                   | 8-11  |

| 010     | Operand 1 key                   | 4-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

|         |                                 |       |

If the K-field specifies a specific field within the AKR, bits 13-15, for 3-bit mode, or bits 12-15, for 4-bit mode, from the word location in main storage are loaded into the AKR field. If the K-field specifies the entire AKR, bits 0-15 from the word location in main storage are loaded into the AKR.

Indicators: The indicators are not changed.

*Program Checks*: This instruction format has the following program checks:

- Invalid storage address One or more words of the instruction or the effective address are outside the installed storage size of the system. The instruction ends and a program check interrupt occurs with invalid storage address set in the PSW.

- **Privilege violate** The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

- Specification check The effective address or indirect address results in an even-byte boundary violation. The instruction ends and a program check interrupt occurs with specification check set in the PSW.

## Copy Address Key Register (CPAKR)

The Copy Address Key Register (CPAKR) instruction has two formats:

- System register/register format for operations that load data from the AKR into a specified register.

- System register/storage format for operations that load data from the AKR into main storage.

## System Register/Register Format

| The system register/register format is: |                |                                                                                                                       |            |

|-----------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------|------------|

| Mnemonic                                | Syntax         | Instruction name                                                                                                      | K-field    |

| CPAKR                                   | reg            | Copy Address Key<br>Register                                                                                          | 011        |

| Extended<br>mnemonic                    | Syntax         | Instruction name                                                                                                      | K-field    |

| CPISK                                   | reg            | Copy Instruction                                                                                                      | 000        |

| СРООК<br>СРОТК                          | reg<br>reg     | Space Key<br>Copy Operand 1 Key<br>Copy Operand 2 Key                                                                 | 010<br>001 |

| <i>Op code</i><br>0 1 1 1<br><i>0</i>   | 1 K<br>1 4 5 7 | R         Function           1         1         0         1         0           8         1011         15         15 |            |

The contents of the address key register (AKR) field specified by the K-field are loaded into the register specified by the R-field. The contents of the AKR are not changed.

Note: The K-field can specify a field within the AKR or the entire AKR.

## For 3-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 13-15 |

| 001     | Operand 2 key                   | 9-11  |

| 010     | Operand 1 key                   | 5 - 7 |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

## For 4-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 12-15 |

| 001     | Operand 2 key                   | 8-11  |

| 010     | Operand 1 key                   | 4-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

|         |                                 |       |

If the K-field specifies a specific field within the AKR, the specified field is loaded into bits 13-15, for 3-bit mode, or bits 12-15, for 4-bit mode, of the register specified in the R-field. Bits 0-12, for 3-bit mode, or bits 0-11, for 4-bit mode, are set to 0's. If the K-field specifies the entire AKR, the AKR is loaded into the register.

Indicators: The indicators are not changed.

**Program Checks:** This instruction format has the following program check:

• **Privilege violate** — The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

## System Register/Storage Format

| •                    | -     |        |   | -             |               |      |     |     |    |         |

|----------------------|-------|--------|---|---------------|---------------|------|-----|-----|----|---------|

| Mnemonic             | Sy    | ntax   |   | Instru        | ction         | nan  | ne  |     |    | K-field |

| CPAKR                | ad    | ldr4   |   | Copy<br>Regis |               | 011  |     |     |    |         |

| Extended<br>mnemonic | Sy    | /ntax  |   | Instru        | iction        | nan  | ne  |     |    | K-field |

| CPISK                | ad    | ldr4   |   | Сору<br>Ѕрасе | Instru<br>Kev | ıcti | on  |     |    | 000     |

| CPOOK                | ad    | ldr4   |   | -             | Oper          | anc  | 11  | Ke  | ey | 010     |

| СРОТК                | ad    | ldr4   |   |               | Oper          |      |     |     | -  | 001     |

| Op code              | _     | κ      |   | RB            | AM            | Fι   | inc | tio | n  |         |

| 0101                 | 1     |        |   |               |               | 1    | 0   | 1   | 0  |         |

| 0                    | 4     | 5      | 7 | 89            | 10 1 1        | 12   |     |     | 15 |         |

| Address/D            | ispla | acemen | t |               |               |      |     |     |    |         |

The system register/storage format is:

**Displacement 1** Displacement 2 16 23 24 31

The contents of the address key register (AKR) field specified by the K-field are stored in the word location specified by the effective address. The contents of the AKR are not changed.

Note: The K-field can specify a field within the AKR or the entire AKR.

#### For 3-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 13-15 |

| 001     | Operand 2 key                   | 9-11  |

| 010     | Operand 1 key                   | 5-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

#### For 4-bit mode:

| K-field | Address key register field name | Bits  |

|---------|---------------------------------|-------|

| 000     | Instruction space key           | 12-15 |

| 001     | Operand 2 key                   | 8-11  |

| 010     | Operand 1 key                   | 4-7   |

| 011     | Address key register            | 0-15  |

| 100     | Should not be used              |       |

| 101     | Should not be used              |       |

| 110     | Should not be used              |       |

| 111     | Should not be used              |       |

|         |                                 |       |

If the K-field specifies a specific field within the AKR, the specified field is stored in bits 13-15, for 3-bit mode, or bits 12-15, for 4-bit mode, of the word location in main storage. Bits 0-12, for 3-bit mode, or bits 0-11, for 4-bit mode, of the word in main storage are set to 0's. If the K-field specifies the entire AKR, the AKR is stored in the word location in main storage.

Indicators: The indicators are not changed.

Program Checks: This instruction format has the following program checks:

- Invalid storage address One or more words of the instruction or the effective address are outside the installed storage size of the system. The instruction ends and a program check interrupt occurs with invalid storage address set in the PSW.

- **Privilege violate** The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

- Specification check The effective address or indirect address results in an even-byte boundary violation. The instruction ends and a program check interrupt occurs with specification check set in the PSW.

## Set Segmentation Register (SESR)

The syntax for this instruction is:

SESR reg,addr4

| Op code |   | R |   | RI | 3 | AM     | Function |   |   | n  |

|---------|---|---|---|----|---|--------|----------|---|---|----|

| 0101    | 1 |   |   |    |   |        | 0        | 0 | 0 | 1  |

| 0       | 4 | 5 | 7 | 8  | 9 | 10 1 1 | 12       |   |   | 15 |

| Ad | ldress/Displacement | ······································ |    |

|----|---------------------|----------------------------------------|----|

|    | Displacement 1      | Displacement 2                         |    |

| 16 | 23                  | 24                                     | 31 |

This instruction loads the contents of one or more doubleword storage locations, the first of which is specified by the effective address, into the segmentation registers specified by the contents of the register specified by the R-field.

For processors with 3-bit keys enabled, the format of the register specified by the R-field is:

| 0   | 4        | 5 | 7   | 8 | 9 | 10 |       | 14 | 15 |

|-----|----------|---|-----|---|---|----|-------|----|----|

| L   | ogical   | ~ |     | 0 | 0 |    | 0     |    |    |

| se  | ector    | ^ | 'ey | U | U |    | Count |    | 0  |

| Key | bits 01. | 2 |     |   |   |    |       |    |    |

Bits 0-7 form the number of the segmentation register to be loaded (0-255). This number is comprised of 3-bits from the address key (values 0-7) and the five high-order bits of the logical storage address which is the logical segment (values 0-31). Bits 8, 9, and 15 of the register are reserved and must be set to 0's.

Bits 10-14 specify the number of contiguous segmentation registers to be set from contiguous doubleword storage locations.

#### Notes:

- 1. The count is equal to count plus 1. For example a count of 0 loads one register.

- 2. If AM=01, the register selected by the RB field is incremented by 4 for each segmentation register set.

For 4-bit mode, the format of the register specified by the R-field is:

| 0  |                   | 4  | 5 |     | 8 | 9 | 10 |       | 14 | 15 |

|----|-------------------|----|---|-----|---|---|----|-------|----|----|

|    | Logical<br>sector |    |   | Key |   | 0 |    | Count |    | x  |

| Ke | ey bits 12        | 23 | 0 |     |   |   |    |       |    |    |

Note: Bit 8 is the most significant bit in the key field, and bit 7 is the least significant bit. For example, 0011 in the key field would indicate stack 9.

Bits 0-8 form the number of the segmentation registers to be referenced (0-511) where the value of key bit 0 provides a select control between the first and second 256 segment register groups. This number is comprised of four bits from the address key (values 0-15) and the five high-order bits of the logical storage address, which is the logical segment (values 0-31). Bit 9 of the register is reserved and must be set to 0.

Bits 10-14 specify the number of contiguous segmentation registers to be set from contiguous doubleword locations (count plus 1). The instruction ends when the count is exhausted or when register 31 is loaded.

Bit 15, when a 1, indicates that the segmentation register stack referenced is the one reserved for I/O. Bit 8 (in the key field) is ignored in this case.

Notes:

- 1. If AM=01, the register selected by the RB field is incremented by 4 for each segmentation register set.

- 2. All indicators are unchanged.

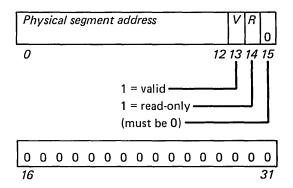

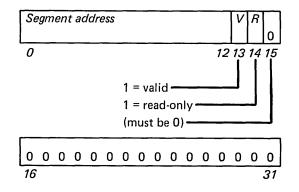

The first word (bits 0-15) of the specified doubleword that is loaded into the selected segmentation register has the following format:

The segment address (bits 0-12) contains the high-order bits of the physical address.

Bit 13, if a 1, signifies that the contents of the segmentation register are valid, and translation can be performed. If an attempt is made to use a segmentation register with bit 13 set to 0, a program check interrupt occurs with invalid storage address set in the PSW.

Bit 14, if a 1, signifies that the block is read-only. If an attempt is made to write into the block when bit 14 of the associated segmentation register is a 1 and while

in problem state, a program check interrupt occurs, with protect check set in the PSW. When in supervisor state or on a cycle-steal access, bit 14 is ignored. The contents of main storage can be changed.

The second word (bits 16-31) of the specified doubleword should be set to 0's.

Indicators: The indicators are not changed.

**Program Checks:** This instruction has the following program checks:

- Invalid function In the supervisor state, an attempt has been made to invoke this instruction when the translator is not enabled.

- Invalid storage address One or more words of the instruction or the effective address are outside the installed storage size of the system. The instruction ends and a program check interrupt occurs with invalid storage address set in the PSW.

- **Privilege violate** The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

- Specification Check The effective address or indirect address results in an even-byte boundary violation. The instruction ends and a program check interrupt occurs with specification check set in the PSW.

## Copy Segmentation Register (CPSR)

The syntax for the register/storage format is:

CPSR reg,addr4

| Op code |   | R |   | RE | 3 | AM    | Fι | inc | ction |    |

|---------|---|---|---|----|---|-------|----|-----|-------|----|

| 0101    | 1 |   |   |    |   |       | 1  | 0   | 0     | 1  |

| 0       | 4 | 5 | 7 | 8  | 9 | 10 11 | 12 |     |       | 15 |

| Ad | dress/Displacement |                |

|----|--------------------|----------------|

|    | Displacement 1     | Displacement 2 |

| 16 | 23 2               | 24 31          |

This instruction stores the contents of one or more segmentation registers, specified by the contents of the register specified by the R-field, into contiguous doubleword storage locations, the first of which is specified by the effective address.

In the 3-bit mode, the format of the general register specified by the R-field is:

| 0           | 4        | 5 | 7  | 8 | 9 | 10 |       | 14 | 15 |

|-------------|----------|---|----|---|---|----|-------|----|----|

| Log<br>sect |          | к | ey | 0 | 0 |    | Count |    | 0  |

| Key bi      | ts 0 1 2 | , |    |   |   |    |       |    |    |

Bits 0-7 form the number of the segmentation register to be copied (0-255). This number is comprised of 3-bits from the address key (values 0-7) and the five high-order bits of the logical storage address which is the logical segment (values 0-31). Bits 8, 9 and 15 of the register are reserved and must be set to 0.

Bits 10-14 specify the number of contiguous segmentation registers to be copied to contiguous doubleword storage locations and is equal to the count plus 1 (for example a count of zero loads one doubleword storage location). The instruction ends when the count is exhausted or when register 31 of the key space has been copied.

**Note:** If AM=01, the register selected by the RB field is incremented by 4 for each segmentation register copied.

For processors with 4-bit mode enabled, the format of the register specified by the R-field is:

| 0  | 4                 | 5  |     | 8 | 9 | 10 |       | 14 | 15 |

|----|-------------------|----|-----|---|---|----|-------|----|----|

|    | Logical<br>sector |    | Key |   | 0 |    | Count |    | х  |

| Ke | ey bits 123       | 30 |     |   |   |    |       |    |    |

**Note:** Bit 8 is the most significant bit in the key field, and bit 7 is the least significant bit. For example, 0011 in the key field would indicate stack 9.

Bits 0-8 form the number of the segmentation register to be referenced (0-511) where the value of key bit 0 provides a select control between the first and second 256 segment register groups. This number is comprised of 4-bits from the address key (values 0-15) and the five high-order bits of the logical storage address which

is the logical segment (values 0-31). Bit 9 of the register is reserved and must be set to 0.

Bit 15, when set to 1, indicates that the segmentation register stack referenced is the one reserved for I/O. Bit 8 (in the key field) is ignored in this case.

Bits 10-14 specify the number of contiguous segmentation registers to be copied to contiguous doubleword storage locations, with the count equal to the count plus 1 (for example if the count is zero, one doubleword storage location is loaded).

**Note:** If AM=01, the register selected by the RB field is incremented by 4 for each segmentation register copied.

The first word of the specified doubleword that is copied from the selected segmentation register has the following format:

The segment address (bits 0-12) contains the high-order bits of the physical address, which is used by the translator to select a 2K-byte block of main storage.

Bit 13, if a 1, signifies that the contents of the segmentation register is valid, and the translation can be performed. If an attempt is made to use a segmentation register in which bit 13 is a 0, a program check interrupt occurs, with invalid storage address set in the PSW.

Bit 14, if a 1, signifies that the block is read-only. If an attempt is made to write into the block when bit 14 of the associated segmentation register is a 1 and while in problem state, a program check interrupt occurs, with protect check set in the PSW. When in supervisor state or on a cycle-steal access, bit 14 is ignored; the contents of main storage can be changed.

The second word (bits 16-31) of the specified doubleword should be set to 0's.

Indicators: The indicators are not changed.

,

Program Checks: This instruction has the following program checks:

- Invalid function In the supervisor state, an attempt has been made to invoke this instruction when the translator is not enabled.

- Invalid storage address One or more words of the instruction or the effective address are outside the installed storage size of the system. The instruction ends and a program check interrupt occurs with invalid storage address set in the PSW.

- **Privilege violate** The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

- Specification check The effective address or indirect address results in an even-byte boundary violation. The instruction ends and a program check interrupt occurs with specification check set in the PSW.

The syntax for this instruction is:

CPPSR addr4

| Op | С | ode | , |   |   |   |   | R | B | AM   | Function |   |   | n  |

|----|---|-----|---|---|---|---|---|---|---|------|----------|---|---|----|

| 0  | 1 | 0   | 1 | 1 | 0 | 0 | 0 |   |   |      | 1        | 1 | 1 | 1  |

| 0  |   |     |   | 4 | 5 |   | 7 | 8 | 9 | 1011 | 12       |   |   | 15 |

| Ad | Address/Displacement |                |  |  |  |  |  |  |  |  |  |  |

|----|----------------------|----------------|--|--|--|--|--|--|--|--|--|--|

|    | Displacement 1       | Displacement 2 |  |  |  |  |  |  |  |  |  |  |

| 16 | 23 2                 | 24 31          |  |  |  |  |  |  |  |  |  |  |

The contents of the processor status word (PSW) are stored at the word location in main storage specified by the effective address.

This instruction resets PSW bits 0-6 and 8-12. of Bits 7 and 13-15 are not changed. Bits 5-7 of the instruction are not used and should be set to 0's.

Indicators: The indicators are not changed.

Program Checks: This instruction has the following program checks:

- Invalid storage address One or more words of the instruction or the effective address are outside the installed storage size of the system. The instruction ends and a program check interrupt occurs with invalid storage address set in the PSW.

- **Privilege violate** The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

- **Specification check** The effective address or indirect address results in an even-byte boundary violation. The instruction ends and a program check interrupt occurs with specification check set in the PSW.

The syntax for this instruction is:

EN ubyte

| Οµ | ) C | ode | ; |   | Fι | inc |   | Parameter |    |

|----|-----|-----|---|---|----|-----|---|-----------|----|

| 0  | 1   | 1   | 0 | 0 | 0  | 1   | 0 |           |    |

| 0  |     |     |   | 4 | 5  |     | 7 | 8         | 15 |

The parameter field bits have the following significance:

#### Bit Significance

- 8 Not used

- 9 Not used

- 10 Enable 4-bit mode (PSW bit 7=1)

- 11 Not used

- 12 Enable storage protect

- 13 Enable equate operand spaces (AKR bit 0 set to 1)

- 14 Enable translator (PSW bit 14 set to 1)

- 15 Enable summary mask (LSR bit 11 set to 1)

Note: Bits not used must be set to 0's.

If bit 12 is set to 1, the relocation translator (if enabled) is disabled and bit 14 is not checked.

If bit 14 is set to 1, and bit 12 is set to 0, the relocation translator is enabled.

If parameter bit 14 and parameter bit 10 are both 1's or if parameter bit 14 and PSW bit 7 are both 1's, the I/O translator is enabled.

If parameter bit 14 is a 1, parameter bit 10 is a 0, and PSW bit 7 is a 0, the I/O translator is not enabled.

Indicators: The indicators are not changed.

**Program Checks:** This instruction has the following program check:

• **Privilege violate** — The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

The syntax for this instruction is:

DIS ubyte

| Oļ | ) C | ode | <i>;</i> |   | Fι | ınc |   | Parameter |    |

|----|-----|-----|----------|---|----|-----|---|-----------|----|

| 0  | 1   | 1   | 0        | 0 | 0  | 1   | 1 |           |    |

| 0  |     |     |          | 4 | 5  |     | 7 | 8         | 15 |

The bits in the parameter field have the following significance:

#### Bit Significance

- 8 Not used

- 9 Not used

- 10 Disable 4-bit mode (PSW bit 7=0)

- 11 Not used

- 12 Disable storage protect

- 13 Disable equate operand spaces (AKR bit 0 set to 0)

- 14 Disable translator (PSW bit 14 set to 0)

- 15 Disable summary mask (LSR bit 11 set to 0)

Note: Bits not used must be set to 0's.

If a Disable instruction immediately follows an Enable summary mask instruction, the interrupt disable function may occur prior to the time that an interrupt can be accepted. Thus, at least one other instruction (for example, no-op) must be inserted between the Enable summary mask and Disable instructions to ensure the occurrence of the interrupt.

If parameter bit 14 is set to 1 and the relocation translator is enabled (bit 14 of the PSW is a 1), then the translator is disabled and bit 14 of the PSW is set to a 0. If parameter bit 14 is a 1, the I/O translator is always disabled.

If PSW bit 14 is a 1 and parameter bit 10 is a 1, the I/O translator is disabled.

Indicators: The indicators are not changed.

**Program Checks:** This instruction has the following program check:

• **Privilege violate** — The instruction is encountered while in problem state. The instruction is suppressed and a program check interrupt occurs with privilege violate set in the PSW.

## **New Instructions**

The processor has three additional instructions:

- Address Resolution with Indirect Branch (ARIB)

- Address Resolution with Indirect Branch—On (ARIBON)

- Address Resolution with Indirect Branch—Off (ARIBOFF).

## **ARIB Instruction Format**

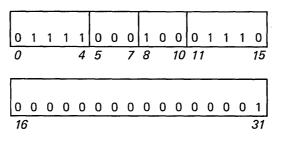

The ARIB instruction is a three-word instruction that performs the mapping actions. This instruction is intended to be used exclusively by the operating system. Mapping actions are the operation of fetching a command with an op code, operand 1, operand 2, and resolving the addressing modes used by those operands. The format of the instruction follows:

| Word 1 | 0              | 1   | 1  | 1  | 1    | 0    | 0   | 0  | 1  | 0 | 0              | 0  | 1 | 1 | 1 | 1  |  |

|--------|----------------|-----|----|----|------|------|-----|----|----|---|----------------|----|---|---|---|----|--|

|        | 0              |     |    |    | 4    | 5    |     | 7  | 8  |   | 10             | 11 | 1 |   |   | 15 |  |

|        |                |     |    |    |      | _    |     |    |    |   |                |    |   |   |   |    |  |

| Word 2 | Displacement 1 |     |    |    |      |      |     |    |    |   | Displacement 2 |    |   |   |   |    |  |

|        | 16             |     |    |    |      |      |     | 23 | 24 | 1 |                |    |   | - |   | 31 |  |

|        |                |     |    |    |      |      |     |    |    |   |                |    |   |   |   |    |  |

| Word 3 | TE             | 3L, | ٩D | DR | l ad | ldre | ess |    |    |   |                |    |   |   |   |    |  |

|        | 32             | ,   |    |    |      |      |     |    |    |   |                |    |   |   |   | 47 |  |

The instruction uses the values of displacement 1, displacement 2, and the address of the first word of the branch table TBLADDR for loading the ARIB instruction work registers, where:

- Displacement 1 is the index parameter displacement byte used with the control block designated by R2.

- Displacement 2 is the displacement byte parameter used with the control block designated by R2 to store R1.

- TBLADDR is the address of the first word of the branch-to table.

#### **Register and Storage Conventions**

The register conventions used by the mapping routine of the ARIB are as follows:

- Entry conditions:

- R1 is the address of first word of the current command for ARIB.

- R2 is the address of a control block.

- Exit conditions:

- R1 and R2 are unchanged.

- R3 is the resolved address of operand 1.

- R4 is the resolved address of operand 2.

- R5 is the contents of storage word pointed to by R1.

- R6 is the TBLADDR index value that is defined as the command op code, multiplied by 2.

- IAR is the contents of the storage location at the effective address TBLADDR, plus the contents of R6.

- Storage location is the effective address of the contents of R2, plus displacement 2 of ARIB instruction word 2, containing the contents of R1.

Indicators: The indicators are not changed.

*Program Checks*: This instruction has the following program checks:

- Invalid function The instruction encountered the ARIB mode condition off. The instruction is suppressed, and a program check interruption occurs, with invalid function set in the PSW.

- Invalid storage address One or more words of the instruction or any of the effective addresses is outside the installed storage size of the system. The indirect branch does not occur, and the instruction is terminated. Some of the level registers may have changed.

- Specification check The effective address or indirect address results in an even-byte boundary violation. Branching does not occur, and the instruction is terminated. Some of the level registers may have changed.

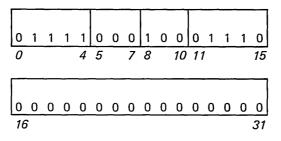

The ARIBON instruction is a two-word instruction that activates the address resolution and indirect branch feature by turning on an internal flag that allows execution of the ARIB instruction. This mode is only reset by an IPL, a system reset, a power-on reset, or the ARIBOFF instruction. The ARIBON instruction is intended to be used by the operating system, and it may be issued in either the problem state or the privilege state.

Word 2 bits 0-14 are reserved and must be set to 0. Bit 15 must be set to 1.

Indicators: The indicators are not changed.

## **ARIBOFF Instruction Format**

The ARIBOFF instruction is a two-word instruction that deactivates the address resolution and indirect branch feature by turning off the ARIBON flag. This instruction is intended to be used by the operating system, and it may be issued in either the problem state or the privilege state.

Word 2 is set to all 0's.

Indicators: The indicators are not changed.

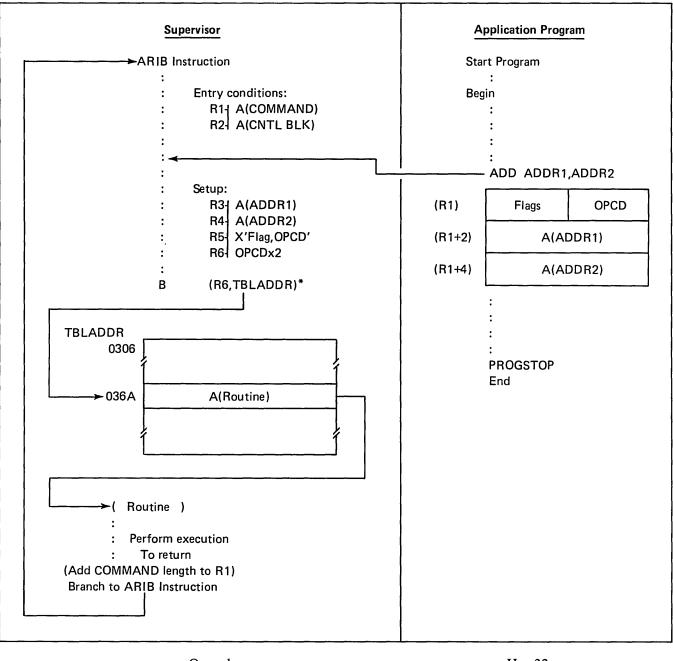

# **ARIB** Execution

The required operations for the ARIB instruction are as follows:

*Initialization*: Prior to the invocation of the ARIB instruction, the operating system must issue the ARIBON instruction. For ordinary usage, this should be part of the IPL procedure.

*Setup*: The content of R1 is placed in the main storage location designated by the effective address of displacement 2 of the ARIB instruction word 2, plus the control block address in R2 and with OP2K to generate the physical storage address.

**Note:** There is no use of this storage address during the ARIB instruction, and the R1 register is maintained intact.

**Command**: A high level command is fetched from the main storage location specified by the contents of R1, and placed into R5. The contents of R5 are defined as a command with the following definition.

| 1 | Х | Х | Х | OP | R2 | OP | R1 | Op code function |    |

|---|---|---|---|----|----|----|----|------------------|----|

| 0 | 1 |   | 3 | 4  | 5  | 6  | 7  | 8                | 15 |

#### Bit Meaning

0 Operand 2 type (1=constant, 0=address)

- 1–3 Not defined

- 4–5 Register flag for operand 2

- 6–7 Register flag for operand 1

- 8–15 Operation code function

The I-field of the op code indicates to the mapping routine that the second operand is an immediate value. The OPR2 and OPR1 fields are used to define the addressing mode used for each of the operands.

The op code function field is used by the mapping routine to generate the index value for displacement in the table "TBLADDR."

The 2-bit register flag for each operand is defined as follows:

| Field value | Meaning                                          |

|-------------|--------------------------------------------------|

| 0           | Register not specified                           |

| 1           | Operand 1 used in the form (d, index register 1) |

| 2           | Operand 2 used in the form (d, index register 2) |

| 3           | Operand 1 or operand 2 used explicitly           |

**Operand Address Resolution**: Operand 1 is fetched from the main storage location at the effective address specified by the contents of R1 plus 2, and placed into R3.

Operand 2 is fetched from the main storage location specified by the contents of R1 plus 4, and placed into R4. If operand 2 is a constant, R4 contains the value R1 plus 4, which is a pointer to that constant.

If operand 1 is an indexed value (parameter or index register), the setup routine adds the contents of the selected register (operand 1 or operand 2) to R3. If operand 2 is an indexed value (parameter, index register), the setup routine adds the contents of the selected register (operand 1 or operand 2) to R4.

These are accomplished as follows: An effective address is generated by adding displacement 1 with the contents of level register R2. The effective address is used with OP2K to generate the physical address. The contents of main storage at the generated address contains an address which points to the first word of a pair of index values. Reference to this storage location is required whenever command word bits 4-5 or 6-7 are respectively non-zero. Another address is then formed by adding to these contents the bits 4-5, for operand 1, or bits 6-7, for operand 2, to the low-order address word bit positions, thus adding bit positions 13, 14, and 15 where bit 15 is 0. This address is then used to fetch the storage location that is added to the appropriate operand register, either R3 or R4. This represents the operand indexed addressing.

After setting up the registers with the proper addresses, the branch-to table address is resolved as follows:

*Address Resolution*: The address of the routine that processes the next instruction is located in the branch-to table at an offset that is equal to the command op code multipled by 2. Thus, add the TBLADDR base address to twice the product of the op code in hex.

#### Example:

The next instruction routine for the ARIB processing shown is calculated as follows:

| Op code                                     | Hex 32   |

|---------------------------------------------|----------|

| Multiplied by 2                             | Hex 64   |

| Plus TBLADDR base offset of                 | Hex 0306 |

| Equals the offset into TBLADDR of the       |          |

| routine that processes the next instruction | Hex 036A |

Using the content of R6, plus the table address (TBLADDR), as an effective address used with the ISK to generate the physical address, the content of that storage location is loaded into the level instruction address register (IAR). Thus,

performing an indirect branch through the branch-to table to the proper next instruction routine completes the ARIB instruction execution.

1-36 GA34-0289

2

÷

# Chapter 2. Main Storage Addressing Using the Relocation Translator

The relocation translator and segmentation registers permit addressing of main storage locations beyond 64K bytes and provide a read-only type of storage protection. The first 64K bytes can be addressed directly when the translator is disabled; therefore, the translator must be enabled when main storage above 64K bytes is accessed.

#### **Translator Description**

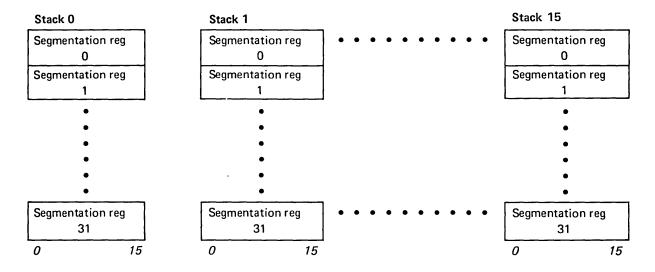

The translator provides 16 stacks of 16-bit segmentation registers. The stacks are numbered 0-15 to correspond to the 16 possible values of the address keys. Each stack consists of 32 registers (0-31). In 3-bit mode, only stacks 0-7 (eight stacks) are used for translation, thereby allowing only 512K bytes of direct mappable storage.

#### Segmentation registers

The stacks of segmentation registers are under supervisory program control. Four privileged instructions are used with the relocation translator and segmentation registers.

- Set Segmentation Register (SESR). This instruction loads segmentation registers.

- Copy Segmentation Register (CPSR). This instruction allows the supervisor to inspect the contents of segmentation registers.

- Enable (EN). This instruction enables the relocation translator. Until the translator is enabled, 16-bit addressing is in effect for the low-order 64K bytes of storage. Any storage above 64K bytes is not accessible to the program until the translator is enabled.

- Disable (DIS). This instruction disables the relocation translator.

For further information about the preceding instructions, refer to their descriptions in chapter 1.

## Storage Mapping

Mapping of main storage is achieved through the segmentation registers. Each segmentation register controls a 2K-byte segment of storage. The SESR instruction is used to load each segmentation register with the unique physical address of a 2K-byte segment of storage.

**Note:** More than one segmentation register can be loaded with the same segment address. For example, stack 0, register 15 (associated with the supervisor address key of 0), can be loaded with the same number as stack 1, register 6. This arrangement allows the supervisor to address control blocks within a problem program even though the address key for the supervisor is different than the key for the problem program. Once loaded, each stack of segmentation registers contains a complete map of 64K bytes divided into 2K-byte physical segments.

#### **Relocation Addressing**

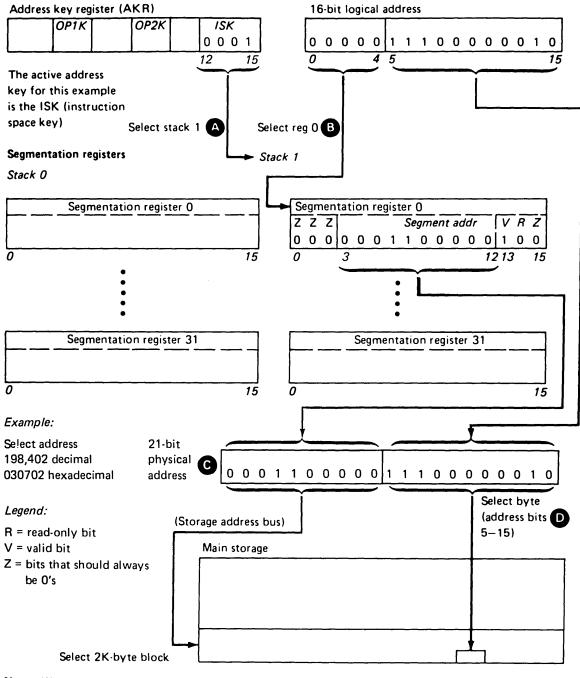

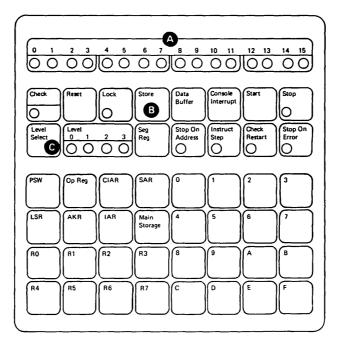

The relocation translator generates a physical address that allows any byte in storage to be addressed. Figure 2-1 shows an example of address translation. The letters in the following description correspond to the letters in Figure 2-1:

A The active address key from the address key register selects a segmentation register stack. The address key pertains to the instruction being executed on the current priority level. Bit 12 is ignored in 3-bit mode.

**B** The five high-order bits (0-4) of the 16-bit address (generated for the instruction being executed) select a segmentation register within the stack selected in description (A). These bits define the logical segment.

C The physical address is generated. The high-order bits are from the segmentation register; these bits specify the physical address of a 2K-byte segment of storage.

Segmentation Register Bit 13 — Valid Bit: When set to 1, this bit specifies that the contents of the segmentation register are valid; the segmentation register can be used to perform the translation. When bit 13 is a 0, the segmentation register cannot be used for translation (no access). If translation is attempted, a program-check interrupt occurs with invalid storage address set in the processor status word (PSW). (All valid bits are set to 0's after power is switched on.)

Segmentation Register Bit 14 — Read-Only Bit: When set to 1, this bit specifies that the block is read-only. If an attempt is made to write into storage using a segmentation register with the read-only bit set to 1, a program-check interrupt occurs with protect check set in the PSW. Storage is not changed. Bit 14 is ignored by a cycle-steal access or when the processor is in supervisor state.

• The 11 low-order bits (5-15) of the physical address are the 11 low-order bits (5-15) of the 16-bit logical address (generated for the instruction being executed); these bits specify the byte address within the 2K-byte segment.

Note: When the translator is disabled, address bits 0-15 only are used for main storage address selection.

Figure 2-1. Address Translation Example

## I/O Storage Access Using the Relocation Translator

All storage access requests from I/O devices are translated by the same hardware that handles storage requests from the processor. The device control blocks (DCBs) must reside in the supervisor's address space; therefore, all I/O devices must use address key 0 to gain access to the DCBs and to store the individual residual status blocks. The address key of the process requiring a cycle-steal operation resides in a DCB. An I/O device presents this address key, along with a 16-bit logical address, to the relocation translator. This allows an I/O device to directly address the storage space for a particular process. The address key allows I/O storage protection to be established between address spaces, assuming that the supervisor ensures the integrity of the DCBs. In 4-bit translated mode, cycle-steal operations gain access to main storage through the I/O segmentation registers.

# Status of Translator After Power Transitions and Resets

The translator is enabled by the Enable (EN) instruction, or by the PSW key of the programmer console, if installed. The translator is disabled by any of the following:

- Disable (DIS) instruction

- Power-on reset

- Check Restart key on programmer console

- Initial program load (IPL)

- System Reset key on programmer console.

All translator controls are reset when the translator is disabled.

#### Notes:

- 1. A machine-check interrupt does not disable the translator.

- 2. The segmentation registers are not reset when the translator is disabled.

- 3. The valid bits are all set to 0's when power is switched on.

## **Error-Recovery Considerations**

### Invalid Storage Address (ISA)

The invalid storage address bit (bit 1 of the PSW) is set to 1 by any one of the following:

- Storage access was attempted using a physical address greater than the physical storage size installed.

- Storage access was attempted with bit 13 (valid bit) of the segmentation register set to 0. This signifies that the contents of the segmentation register are invalid.

The specific nature of the invalid storage address can be resolved as follows:

- Store the segmentation register following the program-check interrupt.

- Test the value of bit 13 in the selected segmentation register. When set to 1, this bit specifies that the contents of the segmentation register are valid; the segmentation register can be used to perform the translation. When bit 13 is a 0, the segmentation register cannot be used for translation (no access). If translation is attempted, a program-check interrupt occurs with invalid storage address set in the processor status word (PSW).

- Ensure that the segment address does not exceed the limits of the physical processor storage installed.

# **Protect Check**

When the translator is enabled, a program-check interrupt with protect check set in the PSW is caused by an attempt to write into storage, while in the problem state, using a segmentation register with bit 14 (read-only) set to 1.

Storage is not changed. Bit 14 is ignored by a cycle-steal access, or when in supervisor state.

## **Address Space Management**

#### Active Address Key

Cycle-steal devices have a cycle-steal address key specified in their device control block.

Any one of the four address keys (ISK, OP1K, OP2K, or cycle-steal address key) may be used during a storage access as the active address key. The address key in use (active) depends on the type of operation being performed at a specific instant in time. The active address key defines storage access through a particular block of segmentation registers.

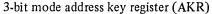

Each priority level in the processor has an associated address key register (AKR) that contains an equate-operand-spaces (EOS) bit and three address keys (OP1K, OP2K, and ISK). In 3-bit mode, three bits are used in each address key; in 4-bit mode, four bits are used in each address key.

4-bit mode address key register (AKR)

| хo              | 0 0 0 X X X 0          | x x x 0 x x x                           | X 0 0 0           | x          | x x x x             | x x x x              |

|-----------------|------------------------|-----------------------------------------|-------------------|------------|---------------------|----------------------|

| 0 1<br>¥<br>EOS | 4 <u>5 7</u> 8<br>OP1K | 9 <u>11</u> 12 <u>13</u> 15<br>OP2K ISK | 0 1 3<br>¥<br>EOS | 47<br>0P1K | 8 <u>11</u><br>OP2K | 1 <u>2</u> 15<br>ISK |

- EOS *Equate operand spaces.* This bit, when set to 1, causes all data operands to use the OP2K address key. See "Equate Operand Spaces (EOS)" in this chapter.

- OP1K Operand 1 key. These bits contain the binary-coded operand 1 address key, with bit 7 as the low-order bit.

- OP2K Operand 2 key. These bits contain the binary-coded operand 2 address key, with bit 11 as the low-order bit.

- ISK *Instruction space key.* These bits contain the binary-coded instruction-space address key, with bit 15 as the low-order bit.

#### Equate Operand Spaces (EOS)

The equate operand spaces bit (bit 0) in the address key register controls the use of the OP1K address key.

When the EOS bit is set to 1 (enabled), all processor data fetches use a single address space defined by the OP2K address key. The OP1K is ignored, but not changed, and all normal OP1K operations use OP2K as an active key. When the EOS bit is set to 0 (disabled), the OP1K address key functions in a normal manner.

Equate operand spaces (EOS) may be enabled by an Enable (EN) instruction, a Set Level Block (SELB) instruction, or a Set Address Key Register (SEAKR) instruction. EOS may be disabled by a Disable (DIS) instruction, a Set Level Block (SELB) instruction, or a Set Address Key Register (SEAKR) instruction. The EOS is also disabled by a priority interrupt or a class interrupt. These instructions are described in chapter 1 and in *IBM Series/1 Principles of Operation*, GA34-0152.

## Address Space

When the relocation translator is enabled, an address key defines a specific address space where:

- The address space is a range of logically contiguous storage.

- The address space is accessible by the effective address without operating system intervention (the address space is not greater than 64K bytes).

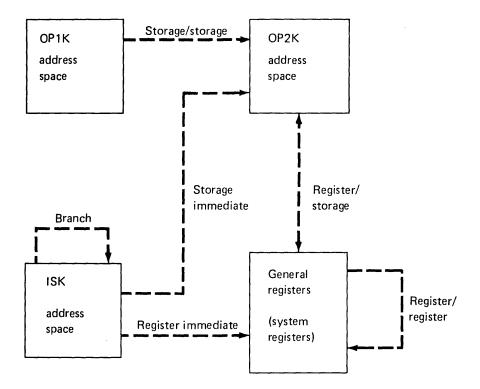

All instruction fetches use the address space defined by the instruction space key (ISK). For storage-to-storage instructions, all reads and writes for data operand 1 use the address space defined by the OP1K, assuming that the EOS bit is a 0. All other storage data accesses, reads, and writes use the address space defined by the OP2K, excluding branch and jump instructions.

#### Examples:

**ISK=OP1K=OP2K**. For instruction processing, all storage accesses occur within the same address space.