SA21-9275-0 File No. S34/S32-36

# IBM System/34 and IBM System/32 Scientific Macroinstructions Functions Reference Manual

Program Numbers 5725-SC1 5726-SS1

SA21-9275-0

File No. S34/S32-36

# IBM System/34 and IBM System/32 Scientific Macroinstructions Functions Reference Manual

Program Numbers 5725-SC1 5726-SS1

SA21-9275-0

File No. S34/S32-36

# IBM System/34 and IBM System/32 Scientific Macroinstructions Functions Reference Manual

Program Numbers 5725-SC1 5726-SS1

#### First Edition (July 1978)

This publication obsoletes and replaces SA21-9274.

This edition applies to release 2 modification 0, of the IBM System/34 System Support Program Product (Program Number 5726-SS1) and to release 7 modification 0, of the IBM System/32 System Control Program Product (Program Number 5725-SC1) and to all subsequent releases and modifications until otherwise indicated in new editions or technical newsletters. Changes are periodically made to the information herein; before using this publication in connection with the operation of IBM systems, refer to the latest IBM System Bibliography for the editions that are applicable and current; for System/34, see GH30-0231, and for System/32, see GC20-0032.

This publication contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

Use this publication only for the purposes stated in the Preface.

Publications are not stocked at the address below. Requests for copies of IBM publications and for technical information about the system should be made to your IBM representative or to the branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. Use the Reader's Comment Form at the back of this publication to make comments about this publication. If the form has been removed, address<sup>5</sup> your comments to IBM Corporation, Publications, Department 245, Rochester, Minnesota 55901. Comments become the property of IBM.

This reference manual is for computer programmers, system analysts, system engineers, and other technical people who are interested in the operation and characteristics of the IBM System/34 and System/32 scientific macroinstructions at the machine code level.

Note: This manual follows the convention that he means he or she.

This publication contains:

- Introductory information regarding instruction and data formats, addressing, and registers

- A description of the linkage and support macroinstructions

- A description of the arithmetic macroinstructions

#### **Related Publications**

- IBM System/34 and IBM System/32 FORTRAN IV Logic Manual, LY21-0568

- IBM System/34 System Support Reference Manual, SC21-5155

- IBM System/34 Functions Reference Manual, SA21-9243

- IBM System/34 Basic Assembler and Macro Processor Reference Manual, SC21-7705

- IBM System/32 System Control Programming Reference Manual, GC21-7593

- IBM System/32 Functions Reference Manual, GA21-9176

- IBM System/32 Basic Assembler and Macro Processor Reference Manual, GC21-7673

Titles and abstracts of other related publications are listed in the *IBM* System/34 Bibliography, GH30-0231 or the *IBM* System/32 Bibliography, GC20-0032.

#

.

٩

# Contents

| CHAPTER 1. INTRODUCTION                                         |     |   |     |   | . 1 |

|-----------------------------------------------------------------|-----|---|-----|---|-----|

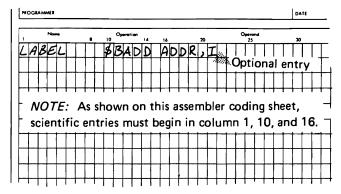

| Scientific Macroinstruction Statements                          |     |   |     |   |     |

| Data Formats                                                    |     |   |     |   | . 2 |

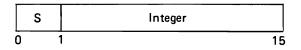

| Binary Format                                                   |     |   |     |   | . 2 |

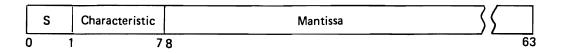

| Floating-Point Format                                           |     |   |     |   | . 2 |

| Addressing                                                      |     |   |     |   |     |

| Direct Addressing                                               |     |   |     |   |     |

| Indexed Addressing                                              |     |   |     |   |     |

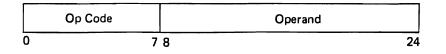

| Machine Instruction Format                                      |     |   |     |   |     |

| Registers                                                       |     |   |     |   | -   |

|                                                                 |     |   |     |   |     |

| CHAPTER 2. SCIENTIFIC MODE LINKAGE<br>SUPPORT MACROINSTRUCTIONS |     |   |     |   | . 7 |

| Scientific Environment and Subroutine Linkage                   |     |   |     |   |     |

| Scientific Implementation (\$CSET)                              |     |   |     |   |     |

| Execute Scientific Subroutine (\$CALL)                          |     |   |     |   |     |

| Start Scientific Subroutine (\$CSUB)                            |     |   |     |   |     |

| Exit Scientific Subroutine (\$CRTN)                             |     |   |     |   |     |

| Return to System Mode (\$INVK)                                  |     |   |     |   |     |

|                                                                 |     |   |     |   |     |

| Return to Scientific Mode (\$CRSM)                              |     |   |     |   |     |

| Enter Scientific Microcode (\$CNTR)                             | • • | · | • • | · | 10  |

| CHAPTER 3. INSTRUCTIONS                                         |     |   |     |   | 13  |

| ADDRESS REGISTER INSTRUCTIONS                                   |     |   |     |   | 13  |

| Address Register Load (\$ALI, \$ALD)                            |     |   |     |   | 13  |

| Macroinstruction Format                                         |     |   |     |   | 13  |

| Machine Instruction Format                                      |     |   |     |   | 13  |

| Operation                                                       |     |   |     |   | 13  |

| Example (Nonindexed) (\$ALD)                                    |     |   |     | · | 13  |

|                                                                 |     |   |     | • | 13  |

| BINARY REGISTER INSTRUCTIONS                                    |     |   |     | • | 14  |

| Data Format                                                     |     |   |     | • | 14  |

| Number Representation                                           | ••• | • | ••• | · | 14  |

|                                                                 |     |   |     |   | 15  |

| Binary Register Add (\$HADD)–2 Bytes                            |     |   |     |   | 15  |

| Macroinstruction Format                                         |     |   |     |   | 15  |

|                                                                 |     |   |     | · | 15  |

|                                                                 | • • |   |     | • | 15  |

| Example (Nonindexed)                                            | • • | · | • • | • | 15  |

|                                                                 |     |   |     |   |     |

|                                                                 | ••• | · | ••• | · | 16  |

| Binary Register Add (\$BADD)-4 Bytes                            |     |   |     |   |     |

| Macroinstruction Format                                         | • • | · | • • | • | 16  |

| Machine Instruction Format                                      | • • | · | • • | · | 16  |

|                                                                 | • • | · | ••• | · | 16  |

| Example (Nonindexed)                                            |     |   | • • | • | 16  |

| Example (Indexed)                                               | • • | · | ••• | · | 17  |

| Binary Register Compare (\$HCMP)–2 Bytes                        | • • | · | • • | · | 17  |

| Macroinstruction Format                                         | • • | · | • • | • | 17  |

| Machine Instruction Format                                      |     | · | • • | · | 17  |

| Operation                                                       | ••• | · | • • | · | 17  |

| Resulting Condition Code Register Settings                      | •   | · |     | · | 17  |

.

(

| Binary Register Compare (\$BCMP)-4 Bytes  |     |   |   |   |   |   | 18 |

|-------------------------------------------|-----|---|---|---|---|---|----|

| Macroinstruction Format                   |     | • | • | • | • | • | 18 |

| Machine Instruction Format                |     |   |   |   | • | • | 18 |

| Operation                                 |     |   |   |   | • |   | 18 |

| Resulting Condition Code Register Setting | js  |   |   |   |   |   | 18 |

| Binary Register Divide (\$HDIV)-2 Bytes . |     |   |   |   |   |   | 18 |

| Macroinstruction Format                   |     |   |   |   |   |   | 18 |

| Machine Instruction Format                |     |   |   |   |   |   | 18 |

| Operation                                 |     |   |   |   |   |   | 18 |

| Example (Nonindexed)                      |     |   |   |   |   |   | 18 |

| Example (Indexed)                         |     |   |   |   |   |   | 19 |

| Binary Register Divide (\$BDIV)-4 Bytes   |     |   |   |   |   |   |    |

| Macroinstruction Format                   |     |   |   |   |   |   | 19 |

| Machine Instruction Format                |     |   |   |   |   |   | 19 |

| Operation                                 |     |   |   |   |   |   | 19 |

| Example (Nonindexed)                      |     |   |   |   |   |   | 19 |

| Example (Indexed)                         |     |   |   |   | • | • | 20 |

| Binary Register Load (\$HLD)-2 Bytes      |     |   |   |   | • | • | 20 |

| Macroinstruction Format                   |     |   |   |   | · | : | 20 |

| Machine Instruction Format                | • • | • | · | • | • | · | 20 |

|                                           |     |   |   |   |   |   | 20 |

| Operation                                 | • • | • | · | · | • | · | 20 |

|                                           |     |   |   |   |   |   |    |

| Example (Indexed)                         |     |   |   |   | · | · | 21 |

| Binary Register Load (\$BLD)-4 Bytes      |     |   |   |   | • | · | 21 |

| Macroinstruction Format                   | • • | · | · |   | · | · | 21 |

| Machine Instruction Format                | ••• | · | · | • | · | · | 21 |

| Operation                                 | • • | · | · | · | · | · | 21 |

| Example (Nonindexed)                      |     |   |   |   |   |   | 21 |

| Example (Indexed)                         | • • | • | · | · | · | · | 22 |

| Binary Register Multiply (\$HMLT)-2 Bytes | • • | · | · | · | · | · | 22 |

| Macroinstruction Format                   |     |   |   |   |   | · | 22 |

| Machine Instruction Format                |     |   |   |   |   |   | 22 |

| Operation                                 |     |   |   |   |   |   | 22 |

| Example (Nonindexed)                      |     |   | • | • | • | • | 23 |

| Example (Indexed)                         |     |   |   |   |   |   | 23 |

| Binary Register Multiply (\$BMLT)-4 Bytes |     |   |   |   |   |   | 23 |

| Macroinstruction Format                   |     |   |   |   |   |   | 23 |

| Machine Instruction Format                |     |   |   |   |   |   | 23 |

| Operation                                 |     |   |   |   |   |   | 23 |

| Example (Nonindexed)                      |     |   |   |   |   | • | 24 |

| Example (Indexed)                         |     |   |   |   |   |   | 24 |

| Binary Register Store (\$HST)-2 Bytes     |     |   |   |   |   | - | 24 |

| Macroinstruction Format                   |     |   |   |   |   |   | 24 |

| Machine Instruction Format                |     |   |   |   |   |   | 24 |

| Operation                                 |     |   |   |   |   |   | 24 |

| Example (Nonindexed)                      |     |   |   |   |   |   | 24 |

| Example (Indexed)                         |     |   |   |   |   |   | 25 |

| Binary Register Store (\$BST)-4 Bytes     |     |   |   |   |   |   | 25 |

| Macroinstruction Format                   |     |   |   |   |   |   | 25 |

| Machine Instruction Format                |     |   |   |   |   |   | 25 |

| Operation                                 |     |   |   |   |   |   | 25 |

| Example (Nonindexed)                      |     |   |   |   |   |   | 25 |

| <b>F</b>                                  |     |   |   |   |   |   | 26 |

|                                           |     |   |   |   |   |   |    |

| Binary Register Subtract (\$HSUB)-2 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Macroinstruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                                                                                                           |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26                                                                                                                                           |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                                                                                                                                           |

| Example (Nonindexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

| Binary Register Subtract (\$BSUB)-4 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                           |

| Macroinstruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27                                                                                                                                           |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                                                                                           |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                           |

| Example (Nonindexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                                           |

| Example (Indexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                                                           |

| FLOATING-POINT REGISTER INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

| Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29                                                                                                                                           |

| Single-Precision Floating-Point Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29                                                                                                                                           |

| Double-Precision Floating-Point Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                                                                                                                           |

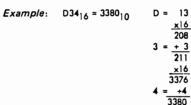

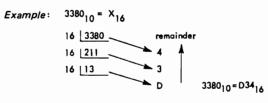

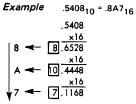

| Number Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30                                                                                                                                           |

| Normalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                                                                                                                                           |

| Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                                                                           |

| Floating-Point Register Add (\$RADD)-Single-Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                           |

| Mossipativetian Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                                                                                                           |

| Macroinstruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                                           |

| <b>Operation</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                                                           |

| Example (Nonindexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                                                                           |

| Example (Indexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32                                                                                                                                           |

| Floating-Point Register Add (\$DADD)-Double-Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                                                                                                           |

| Macroinstruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32                                                                                                                                           |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                                                                                           |

| Example (Nonindexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                                                           |

| Example (Indexed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                                                                                                           |

| Floating-Point Register Compare (\$RCMP)-Single-Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                                                                                                           |

| Marchard Contraction - Francisco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                                                                                           |

| Macroinstruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                                                           |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33<br>33                                                                                                                                     |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33<br>33<br>33                                                                                                                               |

| Machine Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33<br>33<br>33<br>34                                                                                                                         |